#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand comer and continuing from left to right in equal sections with small overlaps.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# A Computer Aided Design System for Transformation and Optimization of Multirate DSP Systems

Qing Ma

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at Concordia University Montréal, Québec, Canada

March 2003

© Qing Ma, 2003

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-77685-9

#### **ABSTRACT**

# A Computer Aided Design System for Transformation and Optimization of Multirate DSP systems

# Qing Ma

Multirate Digital Signal Processing (DSP) theory and technique are essential to digital communications, sonar and radar systems, speech and image processing, as well as many other applications. A computer aided design system that can significantly simplify the design and optimization of multirate signal processing structures has been presented in this thesis.

The thesis starts with the introduction of fundamentals of multirate digital signal processing. It is followed by the introduction of the principle and technique of Multirate Signal Flow Graph (MSFG). A number of MSFG identities and transformations are also given in the thesis.

The computer aided design system that has been presented in this thesis is based on the MSFG representation and transformations. With this system, instead of manual manipulation of MSFGs, the transformations and optimization of MSFGs that represent multirate signal processing systems can be performed in an automatic or interactive manner.

With this system, one can represent a multirate system in the form of a MSFG and then optimizes it by performing a series of MSFG transformations interactively. The system has the capability of calculating the output response at any CELL in the MSFG. This feature can be used to verify the correctness of the derived network.

To perform the MSFG transformation automatically or interactively, following functions have been implemented in the system.

- MSFG transformation and identities

- Simulation of MSFG response

- Verification of the transformed MSFG

- Complexity information of MSFG

To demonstrate the usefulness and the effectiveness of the system, some design examples have been given in chapter 5. In these examples, step-by-step MSFG transformations are provided, which would otherwise be very difficult or extremely tedious to derive.

Dedicated to my wife and my daughter ...

# **ACKNOWLEDGEMENTS**

I would like to thank my academic advisor, Dr. Ronggang Qi and co-supervisor Dr. M. Reza Soleymani, for the invaluable support, guidance and encouragement they have provided over the past year.

I would like to thank all my friends who have provided me all kinds of help in my graduate study.

Most of all, I would like to thank my family for their love and encouragement. I could not have completed my degree without their continuous and immeasurable support.

# TABLE OF CONTENTS

| LIST O    | F FIGURES                                                          | x   |

|-----------|--------------------------------------------------------------------|-----|

| LIST O    | FTABLES                                                            | xi  |

| LIST O    | F ACRONYMS                                                         | xii |

| Chapter   | 1 Introduction                                                     | 1   |

| 1.1       | Background                                                         | 1   |

| 1.2       | Classical Signal Flow Graph and Multirate Signal Flow Graph        | 3   |

| 1.3       | MSFG Transformation                                                | 4   |

| 1.4       | A Computer Aided Design System for Transformation and Optimization | of  |

| Multin    | rate DSP systems                                                   | 5   |

| Chapter   | 2 Theory of Multirate Digital Signal Processing                    | 7   |

| 2.1       | Band-limited signals                                               | 7   |

| 2.1.      | Lowpass signals and bandpass signals                               | 7   |

| 2.1.      | 2 Analytic signals and Hilbert transform                           | 8   |

| 2.1.      | 3 Frequency translations and bandpass signals                      | 9   |

| 2.2       | Multirate systems and signal processing                            | 11  |

| 2.2.      | l Discrete signal representations                                  | 11  |

| 2.2.      | 2 Sampling rate alteration                                         | 12  |

| 2.2.      | Rational sampling rate conversion                                  | 14  |

| Chapter . | 3 Theory of Multirate Signal Flow Graph Transformation             | 21  |

| 3.1       | MSFG                                                               | 21  |

| 3.2       | MSFG Operators                                                     | 22  |

| 3.2.      | l Fundamental MSFG operators                                       | 22  |

| 3.2.2     | Basic MSFG operators                                               | 23  |

| 3.2.3     | 3 MIMO MSFG operators                                              | 26  |

| 3.3       | MSFG transformation                                                | 27  |

| 3.4       | Superposition theorem                                              | 28  |

| 3.5       | The noble identities                                               | 20  |

| 3.6 Ge         | neral identities                                               | 29   |

|----------------|----------------------------------------------------------------|------|

| 3.6.1          | Complex filter identities                                      | 29   |

| 3.6.2          | Modulation identities                                          | 30   |

| 3.6.3          | Identities associated with composite rate-changing operators   | 31   |

| 3.7 Pol        | lyphase decomposition                                          | 32   |

| 3.7.1          | Filter Polyphase decomposition                                 | 32   |

| 3.7.2          | Modulation polyphase decomposition                             | 33   |

| 3.8 Cas        | scade of operators                                             | 36   |

| 3.8.1          | Cascade of samplers                                            | 36   |

| 3.8.2          | Cascade of commutators                                         | 38   |

| 3.8.3          | Commutator-modulator cascades                                  | 40   |

| 3.8.4          | Commutator-filter cascades.                                    | 42   |

| 3.8.5          | Commutator-sampler commutability                               | 43   |

| Chapter 4      | A Computer Aided Design System for Transformation and Optimiza | tion |

| of Multirate I | DSP systems                                                    | 45   |

| 4.1 Obj        | ectives and requirements of the computer aided design systems  | 45   |

| 4.2 Ope        | eration System and Programming Language                        | 47   |

| 4.3 Dat        | a Structure                                                    | 47   |

| 4.3.1          | CELL Graph                                                     | 49   |

| 4.3.2          | CELL                                                           | 50   |

| 4.3.3          | DATA                                                           | . 51 |

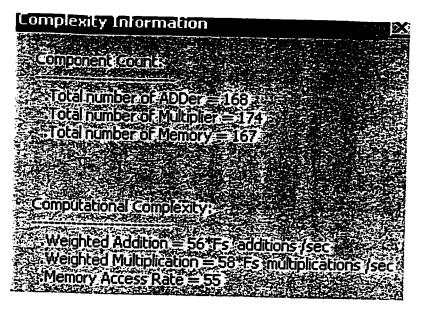

| 4.3.4          | Complexity Information                                         | . 52 |

| 4.3.5          | MSFG Operator                                                  | . 52 |

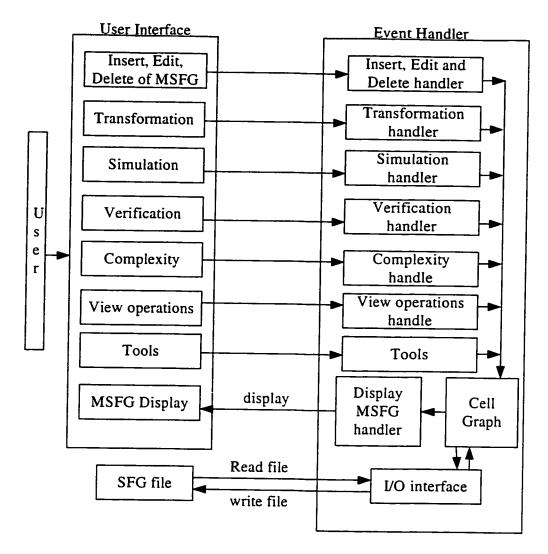

| 4.4 Syst       | tem Block Diagram                                              | . 59 |

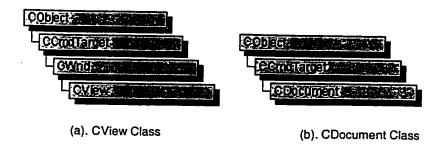

| 4.5 Clas       | ss Model                                                       | . 60 |

| 4.5.1          | Class Model for general application program with MFC           | . 60 |

| 4.5.2          | Class Model for this computer aided design system              | . 62 |

| 4.6 Inter      | rface                                                          | . 67 |

| 4.6.1          | User Menu                                                      | . 67 |

| 4.6.2          | Dialog Window                                                  | . 70 |

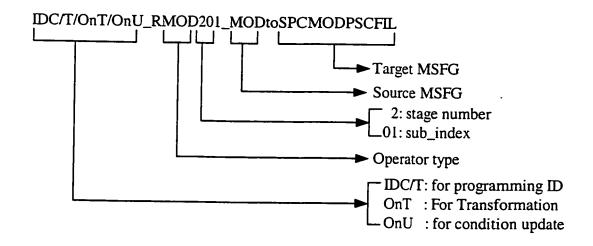

| 4.6.3          | File Input, Output and File Structure                          | 72   |

| 4.7      | MSFG Transformations                                    | 73 |

|----------|---------------------------------------------------------|----|

| 4.8      | Simulation and Verification of MSFG Transformation      | 74 |

| 4.9      | Complexity of MSFG                                      | 75 |

| Chapter  | 5 Application Examples                                  | 77 |

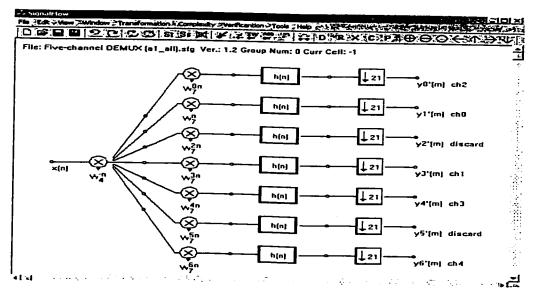

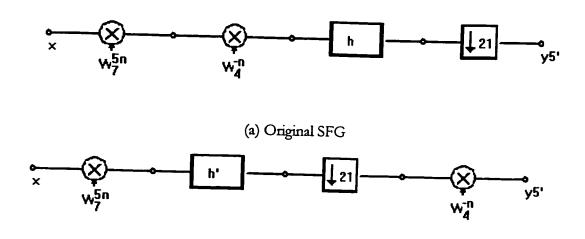

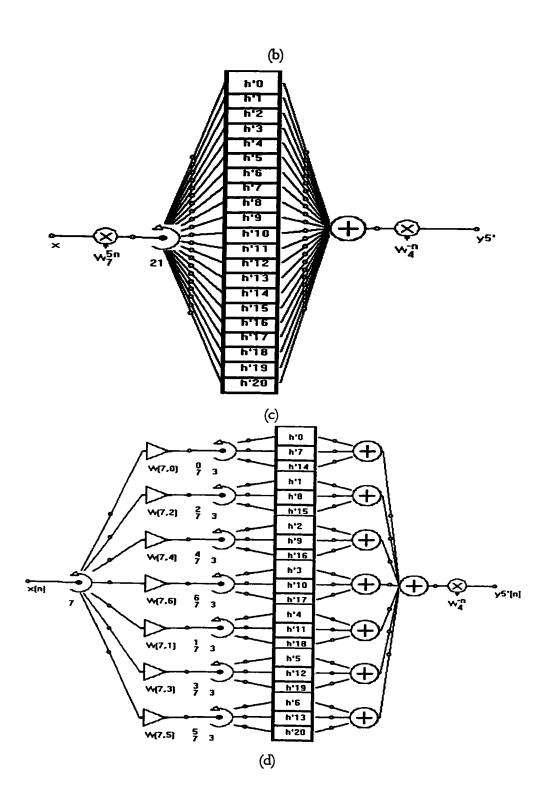

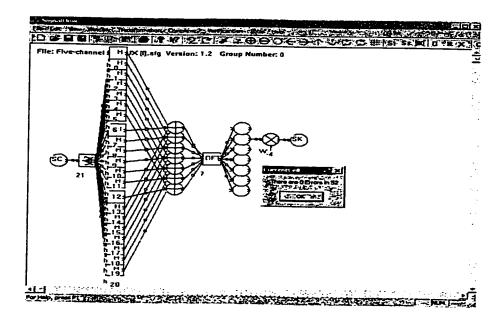

| 5.1      | Five-channel Frequency Demultiplexer (DEMUX)            | 77 |

| 5.1.     | .1 MSFG transformation                                  | 79 |

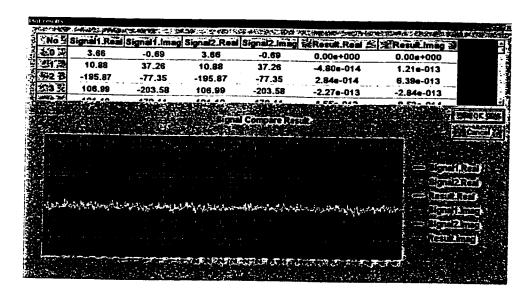

| 5.1.     | 2 Simulation and Verification                           | 83 |

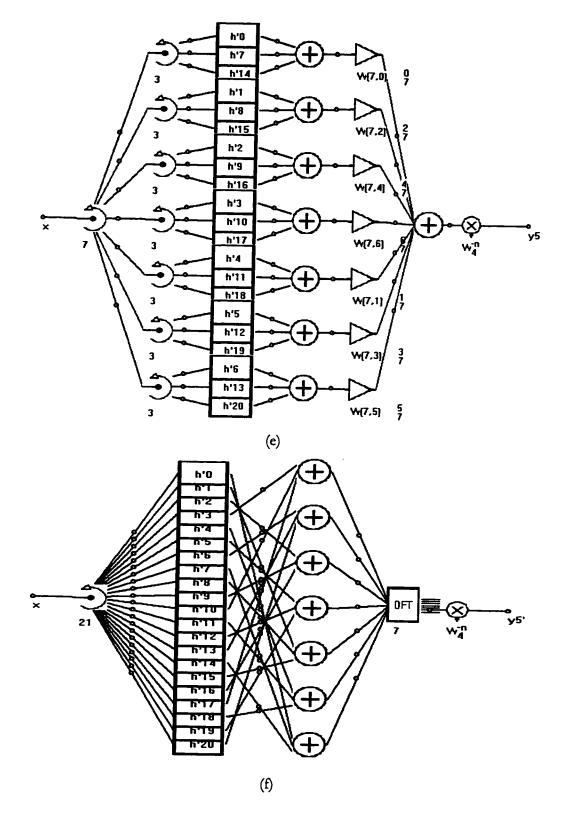

| 5.2      | The optimal complex BSF structure for binary tree DEMUX | 84 |

| 5.2.     | 1 MSFG transformation                                   | 84 |

| 5.2.     | 2 Simulation and Verification                           | 89 |

| Chapter  | 6 Conclusion and future work                            | 92 |

| 6.1      | Conclusion                                              | 92 |

| 6.2      | Future Work                                             | 93 |

| Referenc | es                                                      | 94 |

# **LIST OF FIGURES**

| Figure 1-1 Basic MSFG Operators                                                      | 4          |

|--------------------------------------------------------------------------------------|------------|

| Figure 2-1 Lowpass signals                                                           |            |

| Figure 2-2 Bandpass signals                                                          | 9          |

| Figure 2-3 Spectra relation for integer rate alteration: (a) to (e) for integer rate | decimation |

| (M=3); (f) to (j) for integer rate interpolation (L=3)                               |            |

| Figure 2-4 Rational sampling rate conversion:                                        |            |

| Figure 2-5 Polyphase analysis of signal                                              | 18         |

| Figure 2-6 Polyphase synthesis of signal                                             | 18         |

| Figure 2-7 Transposition of LTI polyphase network                                    |            |

| Figure 2-8 Polyphase decimation filter                                               |            |

| Figure 2-9 Polyphase interpolation filter                                            |            |

| Figure 3-1 DFT                                                                       |            |

| Figure 3-2 Interleaver                                                               |            |

| Figure 3-3 Superposition theorem                                                     | 28         |

| Figure 3-4 Noble identities                                                          | 29         |

| Figure 3-5 Complex filtering identities                                              | 30         |

| Figure 3-6 Modulation identities                                                     | 31         |

| Figure 3-7 Identities associated with composite rate-changing operators              |            |

| Figure 3-8 Polyphase decomposition transforms (PDT)                                  |            |

| Figure 3-9 Two types of MPDT structures in conventional SFG                          | 35         |

| Figure 3-10 MSFGs of type 1 and type 2 MPDT                                          |            |

| Figure 3-11 MPDT for complex modulation                                              |            |

| Figure 3-12 Cascade of samplers                                                      |            |

| Figure 3-13 Cascades of Commutators                                                  |            |

| Figure 3-14 Commutator-SPC and SPC-commutator identities                             |            |

| Figure 3-15 Commutator-filter identities                                             |            |

| Figure 3-16 Sampler-commutator identities                                            |            |

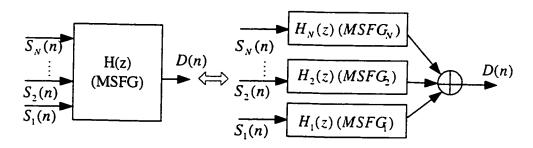

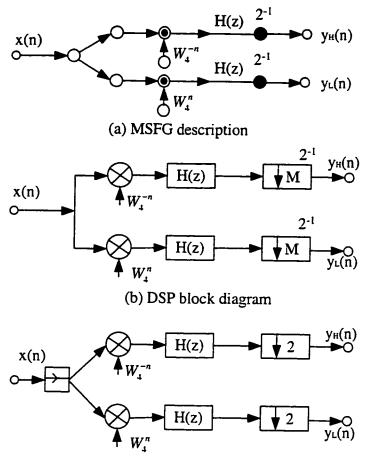

| Figure 4-1 Description of an example in MSFG and DSP block diagram                   | 10         |

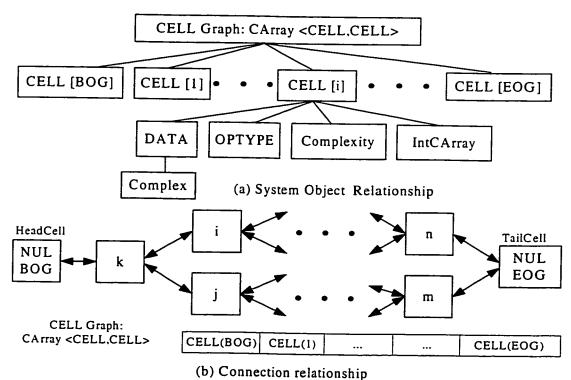

| Figure 4-2 CELL Graph Description                                            | 49   |

|------------------------------------------------------------------------------|------|

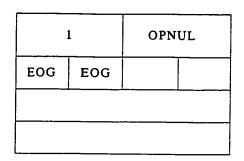

| Figure 4-3 Default value of Operator                                         | 53   |

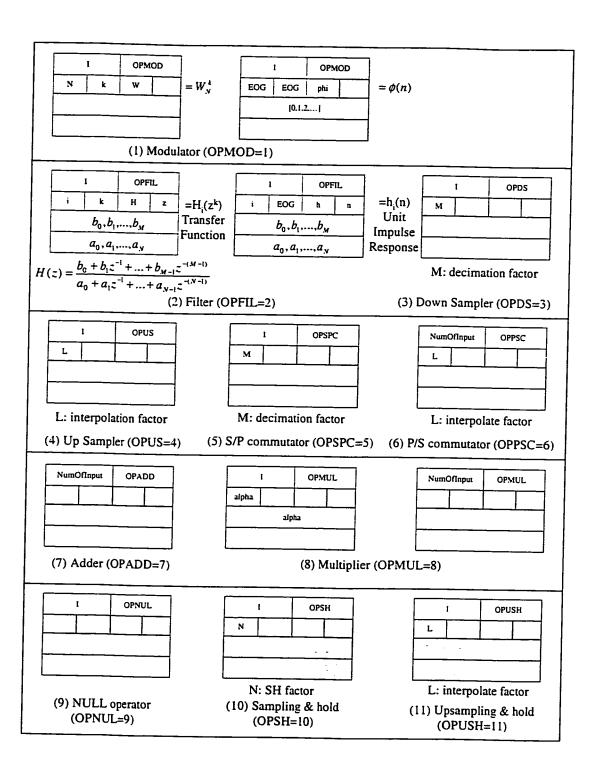

| Figure 4-4 Operators Description                                             | 59   |

| Figure 4-5 System Block Diagram                                              | 60   |

| Figure 4-6 Classes Model and Relationship                                    | 62   |

| Figure 4-7 Classes Model                                                     | 63   |

| Figure 4-8 Main Menu                                                         | 68   |

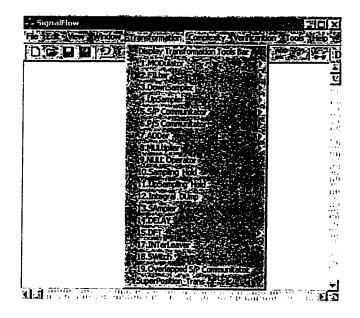

| Figure 4-9 MSFG Transformation Submenu                                       | 70   |

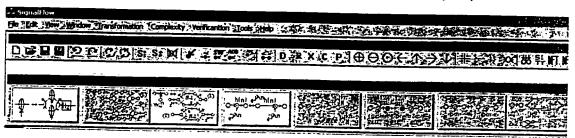

| Figure 4-10 MSFG Transformation Tools Bar (Figure Menu)                      | 70   |

| Figure 4-11 Some Dialog Windows                                              | 71   |

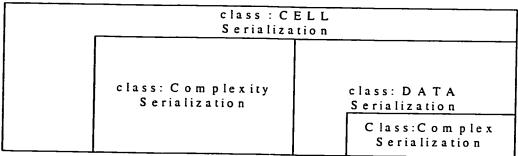

| Figure 4-12 Serialization                                                    | 72   |

| Figure 4-13 SFG file structure                                               | 72   |

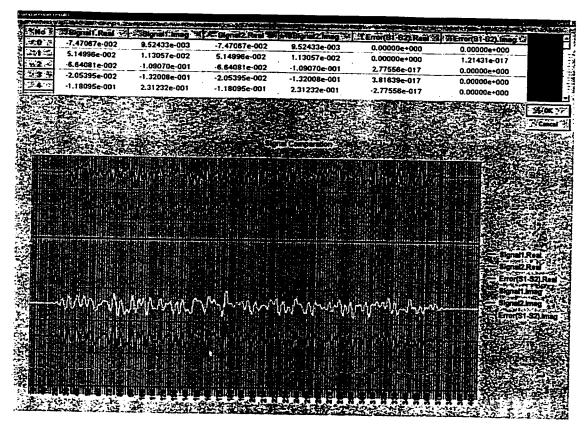

| Figure 4-14 Simulation and Verification Menu                                 | 74   |

| Figure 4-15 Simulation and Verification result figure                        | 75   |

| Figure 4-16 Complexity information of MSFG                                   | 76   |

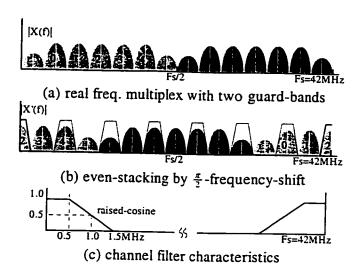

| Figure 5-1 Five-channel MF-TDMA signal and the demultiplexing channel filter | 78   |

| Figure 5-2 DEMUX function (lowpass model)                                    | 78   |

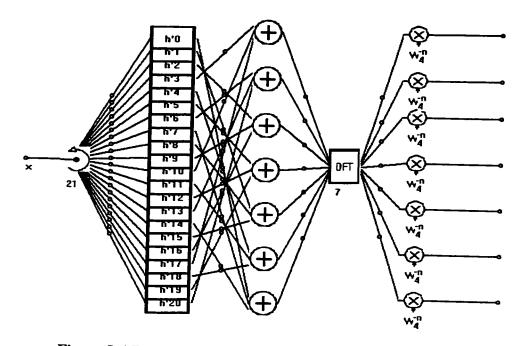

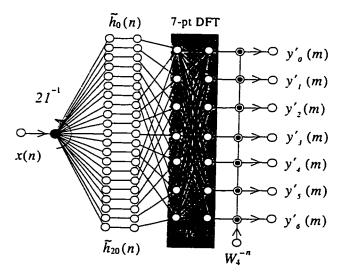

| Figure 5-3 Step-by-step simplification for demultiplexing the k-th channel   | 81   |

| Figure 5-4 Polyphase DFT structure for the 5-channel DEMUX                   | . 82 |

| Figure 5-5 DSP block diagram                                                 | . 82 |

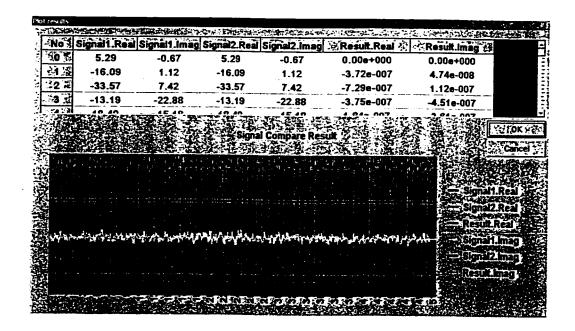

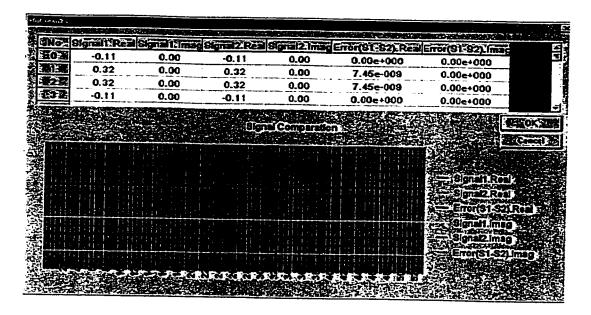

| Figure 5-6 Simulation and Verification of DEMUX                              | . 84 |

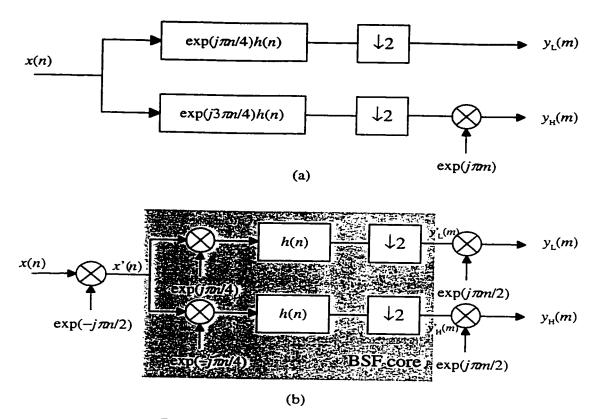

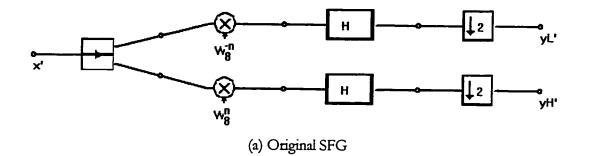

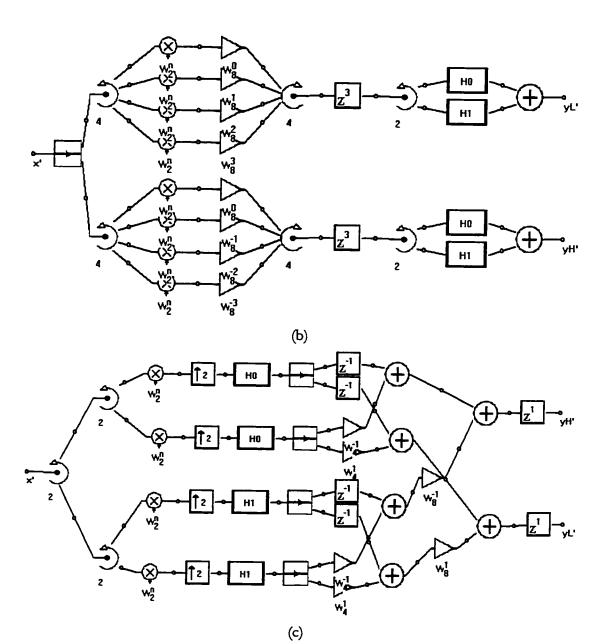

| Figure 5-7 Direct complex BSF structure                                      | . 85 |

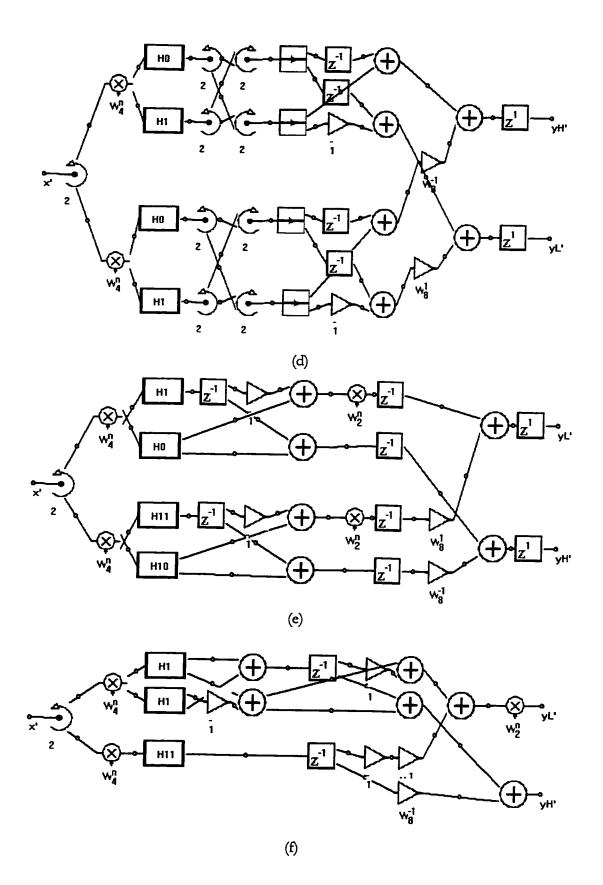

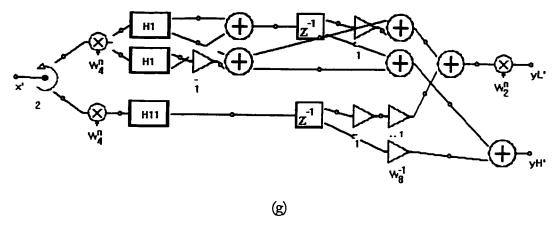

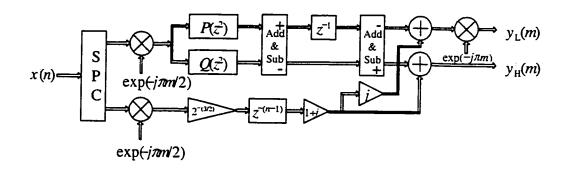

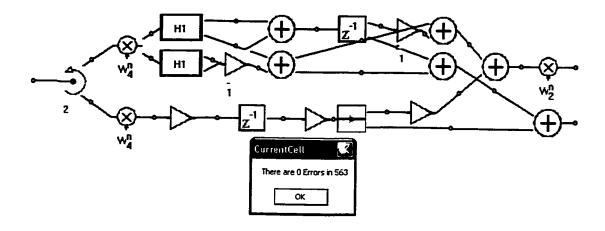

| Figure 5-8 Derivation for the optimal complex BSF                            |      |

| Figure 5-9 DSP block diagram                                                 | . 89 |

| Figure 5-10 Simulation and Verification result                               | 01   |

# **LIST OF TABLES**

| Table 3-1 Fundamental MSFG operators   | 23 |

|----------------------------------------|----|

| Table 3-2 Basic MSFG Operators         | 25 |

| Table 3-3 Extended MSFG Operators      | 27 |

| Table 4-1 CELL Class                   | 51 |

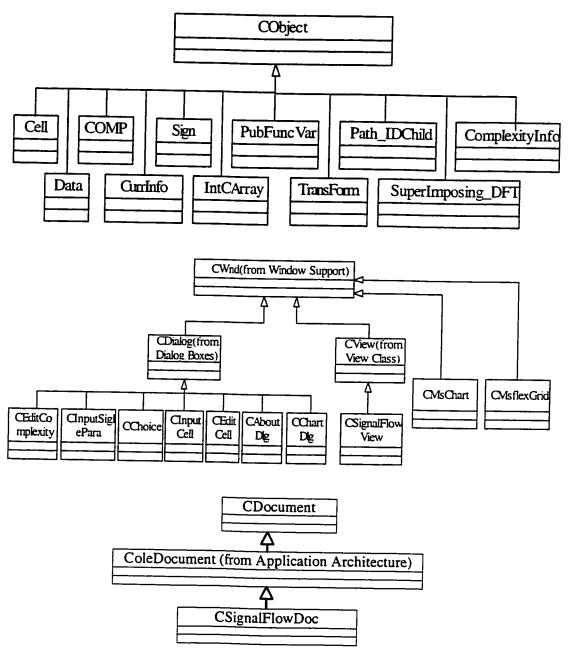

| Table 4-2 Classes derived from CObject | 64 |

| Table 4-3 Classes derived from CDialog | 65 |

| Table 4-4 Functions in CSignalFlowView | 65 |

| Table 4-5 Functions in CSignalFlowDoc  | 66 |

#### LIST OF ACRONYMS

ADD Adder

API Application Program Interface

ATM Asynchronous Transfer Mode

DDC Digital Down-Converter

DELAY Delay element

DEMUX Demultiplexer

DRFU Down-Real Filter-Up

DS Down Sampler

DSB/SC Double-SideBand Suppressed Carrier modulation

DSP Digital Signal Processing

FDM Frequency Division Multiple Access

FFT Fast Fourier Transform

FIL Filter

FIR Finite Impulse Response

GCD Great Common Divisor

GCD Great Common Divisor

GDFT Generalized Discrete Fourier Transform

GSM Global System for Mobile Communication

IDU Integral & Dump

INTL Interleave

LPTV Linear Periodically Time-Varying

LTI Linear Time Invariant

MAC Multiplication and Accumulation

MF-TDMA Multi-Frequency Time Division Multiple Access

MFC Microsoft Foundation Class Library

MIMO Multi-Input Multi-Output

MOD Modulator

MPDT Modulation Polyphase Decomposition Transform

MSDN Microsoft Develop Network

MSFG Multirate Signal Flow Graph

MUL Multiplier

NULL Null operator

OOP Object Oriented Programming

OSPC Overlap SPC Commutator

PSC Parallel-to-Serial Commutator

SA Sampler

SFG Signal Flow Graph

SH Sampling & Hold

SPC Serial-to-Parallel Commutator

SSB Single-SideBand modulation

SW Switch

US Up Sampler

USH Upsampling & hold

#### Chapter 1

# Introduction

#### 1.1 Background

Multirate Digital Signal Processing (DSP) technique is one of the most important techniques that have been widely used in designing and implementing digital communications systems. It is particularly useful when signal sampling rate is high or the required processing rate is close to or higher than the limits of given technology, for example, in some high speed digital receivers and digital modem applications. Multirate DSP techniques have been applied in a wide variety of areas, of signal processing including: communication systems [5], speech and audio processing systems [9], antenna systems [16], and Radar systems [12]. Its typical applications in communication system include sub-band coding [28], sampling rate conversion [3], transmultiplexing as in telephony systems [26] and frequency demultiplexing [8].

A major problem of multirate DSP is the high computational complexity when the information bandwidth is much smaller than signal sampling rate. An optimal multirate system has the processing bandwidth equal or close to the information bandwidth. In fact, one of the primary concerns in multirate DSP is how to reduce the processing bandwidth at different points of the system in order to minimize the overall computational complexity. A well-known and profound result in multirate DSP is the development of the critically decimated or interpolated polyphase filter banks [3,4], which are optimal in the sense that the computational complexity is minimized.

In practice, the frequently used approach to multirate system optimization is to directly apply such existing optimized multirate structures as polyphase filters and polyphase FFT (Fast Fourier Transform) filter banks to functional blocks in multirate

systems. Systems optimized in this way are often not globally optimal because the optimizations are performed locally.

Although multirate system optimization could be achieved by using mathematical representation and manipulations, this mathematical method is difficult to manifest structural information during the reduction process. Its another disadvantage is that it can be extremely tedious and error-prone.

Another method of multirate system optimization is use conventional Signal Flow Graph (SFG) representation and transformations [14,23] to simplify a multirate network. However, the conventional SFG, which is valid only for Linear Time Invariant (LTI) systems, provides little help to handle multirate operations, which are periodical time varying in nature. Generally speaking, this method can only be used to solve very simple problems.

With the above conventional approaches, it is very difficult to optimize even moderate complex systems such as the non-maximally decimated filter banks and filter banks with rational decimation factor, which are often encountered in frequency demultiplexer designs. Global optimization of multirate systems is very often unaddressed, largely due to lack of systematic methods for multirate system design and optimizations.

As a natural extension of the conventional SFG, MSFG has been proposed to represent and to optimize multirate systems [17,18]. Multirate system optimizations can be achieved by applying a series of MSFG identities and transformations to multirate networks to minimize the overall computations. This approach shows structural information explicitly throughout the reduction process. Using this method, a number of efficient filter bank structures have been successfully derived and some of them have been actually implemented in telecommunications industry [19].

However, MSFG approach also has its shortcomings. Manipulation of MSFGs is still a tedious and very error-prone task because manual manipulations of MSFGs are required throughout the process of the MSFG transformation. This has been the main

motivation for the development of a computer-aided design system for transformation and optimization of Multirate DSP systems. Having performed extensive search on this subject, we have found that, as far as we know, no one else has ever developed or attempted to develop such a system for optimization of multirate signal processing systems. Therefore, if such a system can be successfully developed, it could even evolve into a commercial product in the future. This has been our another motivation to develop such a system.

The work presented in this thesis is focused on the development of this computer aided design system. The system can be designed to facilitate the design and optimization of multirate signal processing systems through MSFG transformations. With this system, MSFG transformations and optimization can be performed interactively or automatically without manual manipulations of MSFGs. It can even automatically verify the transformation results. Hence, the design system can significantly simplify the process of MSFG transformations.

# 1.2 Classical Signal Flow Graph and Multirate Signal Flow Graph

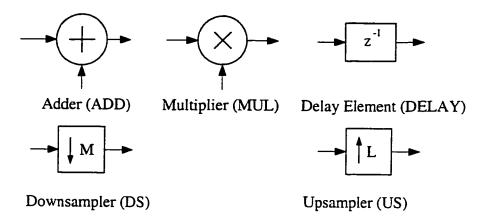

Classical SFG is a single rate SFG. It includes three basic operators: multiplier (MUL), adder (ADD) and delay element (DELAY).

MSFG is an extension of the conventional SFG. Besides the above three basic single rate SFG operators, there are two more basic operators in MSFG, the downsampler (DS) and the upsampler (US). These five basic operators in MSFG are shown in Figure 1-1.

Figure 1-1 Basic MSFG Operators

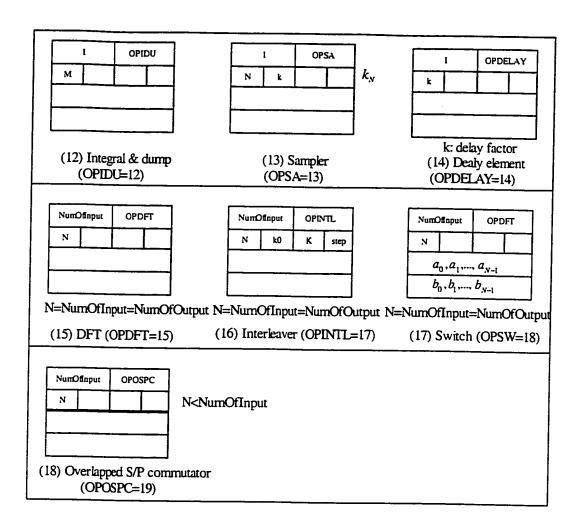

From these basic operators, we further define 13 composite MSFG operators. Therefore, we have defined a total of 18 different MSFG operators for various multirate signal processing operations in MSFG. These 18 operators are Modulator (MOD), Filter (FIL), Downsampler (DS), Upsampler (US), Serial-to-Parallel Commutator (SPC), Parallel-to-Serial Commutator (PSC), Adder (ADD), Multiplier (MUL), Null Operator (NULL), Sampling & Hold (SH), Upsampling & Hold (USH), Integral & Dump (IDU), Sampler (SA), Delay element (DELAY), Discrete Fourier Transform (DFT), Interleaver (INTL), Switch (SW) and Overlap SPC Commutator (OSPC).

#### 1.3 MSFG Transformation

A multirate DSP system can be transformed into its equivalencies with different structures via MSFG transformations. Some fundamental relationships between multirate operators have been given in the form of identity (noble identities, see section 3.5). These MSFG transformations are classified in four categories:

- The noble identities

- General identities

- Polyphase decomposition

- Cascade of operators

# 1.4 A Computer Aided Design System for Transformation and Optimization of Multirate DSP systems

The main objective of this study is to develop a software system, automatically or interactively, to perform MSFG transformations and get one or more optimized MSFG under given optimization constraints. It needs a friendly user interface to make the MSFG transformation and optimization an easy task.

With this design system, one can represent a multirate system in the form of a MSFG and then optimize it by performing a series of MSFG transformations interactively. The system has the capability of calculating the output response at any CELL in the MSFG. It therefore can verify the correctness of the derived network by comparing the response of the derived with that of the original MSFG.

To perform the MSFG transformation automatically or interactively, the following foundational functions have been implemented in the system.

- MSFG transformation and identities

- Simulation of MSFG response

- Verification of the transformed MSFG

- Complexity information of MSFG

C++ is an object oriented programming (OOP) language. In OOP, the structure and its functions are combined into a single entity called Class. The objects are created from Classes. OOP has the following advantages: simplicity, modularity, modifiability, extensibility, flexibility, maintainability and reusability.

MFC (Microsoft Foundation Class) Library is a large and extensive C++ class hierarchy that makes the development of Windows applications significantly easier. MFC is compatible across the entire Windows family. MFC class hierarchy encapsulates the user interface portion of the Windows Application Program Interface (API), and makes it significantly easier to create Windows applications in an object oriented way. This

hierarchy is available for and compatible with all versions of Windows. Consequently, the code created in MFC is portable.

This computer aided design system is based on MSFG representation and transformations. It is developed using Visual C++ language on the Microsoft Windows operation system. An OOP method based on MFC (Microsoft Foundation Class Library) has been used in the development of the system. The design system has a user-friendly GUI interface, and is easy to use. It allows users to perform MSFG transformations, optimization and verification of multirate signal processing systems in a visual operation mode.

# Theory of Multirate Digital Signal Processing

Signals that exist in the real world are always band-limited. Digital signal processing for bandpass signals requires sampling rate alteration in order to reduce computations. A system like this is called a multirate system. To deal with multirate DSP systems efficiently, multirate DSP techniques have evolved [4,27]. Multirate DSP techniques are useful in digital telecommunication systems for handling multiple data transmission rates. This chapter will briefly introduce multirate digital signal processing fundamentals.

## 2.1 Band-limited signals

# 2.1.1 Lowpass signals and bandpass signals

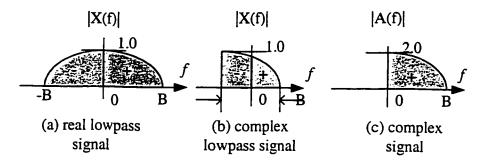

Signals in transmission systems are always band-limited with finite bandwidth. A signal is *lowpass* if its significant spectral content is centered around zero frequency (f=0), which is shown in Figure 2-1(a) and Figure 2-1(b). For real lowpass signal, its magnitude spectrum must be even symmetric and the phase must be odd symmetric about f=0 as shown in Figure 2-1 (a). For complex signals (also referred as complex envelopes) shown in Figure 2-1(b) and 2.1(c), symmetry properties of spectrum are destroyed. *Bandpass* signals in the real world can be interpreted as being translated from their equivalent lowpass signals, which are often referred as *baseband* signals. Efficient signal processing tends to move the bulk of the processing load to baseband.

Figure 2-1 Lowpass signals

# 2.1.2 Analytic signals and Hilbert transform

A signal is **analytic** if, and only if its Fourier transform is zero for negative frequencies (f<0), as for those illustrated in Figure 2-2(c) and Figure 2-2(d). Given a real signal x(t) with Fourier transform  $\mathcal{F}\{x(t)\}=x(\omega)$ , its analytic signal  $a_x(t)$  is defined, in frequency domain, by

$$A_{x}(\omega) = 2X(\omega)u(\omega)$$

$$= X(\omega)[1 + \operatorname{sgn}(\omega)]$$

$$= X(\omega) + X(\omega)\operatorname{sgn}(\omega)$$

$$= \begin{cases} 2X^{+}(\omega), & \text{for } \omega \ge 0 \\ 0, & \text{for } \omega < 0 \end{cases}$$

(2.1)

where  $u(\omega)$  is the unit step function and  $X^+(\omega)$  is the right (positive) sideband of  $X(\omega)$ . The non-symmetric property of  $A_x(\omega)$  determines that an analytic signal must be complex.

Signals shown in Figure 2-1(c) and Figure 2-2(d) are analytic with a single sideband while the complex signal of Figure 2-2(c) can be considered as double-sideband analytic with respect to the real bandpass signal of Figure 2-2(a).

Figure 2-2 Bandpass signals

Eq. (2.1) shows that the analytic signal  $A_x(\omega)$  of a real signal  $X(\omega)$  is obtained by adding signal

$$\widehat{X}(\omega) = X(\omega)\operatorname{sgn}(\omega) \tag{2.2}$$

to the original real signal  $X(\omega)$ . Eq. (2.2) is known as the Hilbert transform of x(t) and it is denoted by

$$\mathcal{X}\left\{x(t)\right\} = \hat{x}(t) \tag{2.3}$$

Hence the analytic signal  $a_{\mathbf{r}}(t)$  and the real signal x(t) are related by Hilbert transform:

$$a_x(t) = x(t) + j\widehat{x}(t) \tag{2.4}$$

We sometimes refer to the real and complex lowpass signals respectively as the real baseband and the complex baseband signals with respect to their modulated (frequency shifted) bandpass associate as shown in Figure 2-2.

# 2.1.3 Frequency translations and bandpass signals

Frequency translation shifts the signal spectrum from one frequency band to the other without changing the shape. Frequency shift in the continuous time domain is simply a multiplication by a continuous sinusoid either real or complex. For an arbitrary complex

signal  $x(t) = x_r(t) + jx_i(t)$  with Fourier transform  $X(\omega)$ , the following three types of frequency translations are defined:

$$x(t)e^{j\omega_{c}t}\longleftrightarrow X(\omega-\omega_{c}) \tag{2.5}$$

$$x(t)\cos(\omega_c t)\longleftrightarrow \frac{1}{2}X(\omega+\omega_c)+\frac{1}{2}X(\omega-\omega_c)$$

(2.6)

$$\Re\left\{x(t)e^{j\omega_{c}t}\right\}\longleftrightarrow \frac{1}{2}X^{\bullet}(-\omega-\omega_{c})+\frac{1}{2}X(\omega-\omega_{c})$$

(2.7)

The transform pair of Eq. (2.5) is called *one-sided frequency translation* as the signal spectrum is moved only in one direction. The complex bandpass signal of Figure 2-2(c) is the direct result of a one-sided translation of the real lowpass signal of Figure 2-1(a). Generally, signals after one-sided translations become complex.

Eq. (2.6) is a two-sided frequency translation since the signal spectrum is moved in both positive and negative frequency directions. The signal shown in Figure 2-2(a) is the result of a two-sided translation of the signal in Fig. 2.1(a). The two-sided frequency shift of Eq. (2.6) belongs to the class of double-sideband suppressed carrier modulation (DSB/SC).

Quadrature modulation as described by Eq. (2.7) can be considered as another kind of two-sided frequency translation. Unlike the double-sideband suppressed carrier modulation where the spectrum at the negative frequency side is exactly the same as that at the positive frequency side except the difference in the center frequencies, the negative sideband of a quadrature modulated signal is the complex conjugate of the positive sideband due to the real nature of quadrature modulation in time domain. The two two-sided frequency shifts become equivalent when dealing with real signals.

A bandpass signal can be regarded as one that is frequency translated with carrier frequency  $\omega_c=2\pi f_c$  from its lowpass equivalent, as shown in Figure 2-2 for  $f_c>B$  where B is the one-sided signal bandwidth. The bandpass signal is said narrow band if  $f_c>>B$  (as often encountered in RF/IF systems).

Another kind of real bandpass signals is single-sideband (SSB) modulated signals defined by

$$x_{SSB}(t) = x(t)\cos(\omega_c t) \mp \hat{x}(t)\sin(\omega_c t)$$

(2.8)

where x(t) is the baseband real (lowpass) signal (Figure 2-1(a)) and  $\hat{x}(t)$  is the Hilbert transform of x(t). When the sign in Eq. (2.8) is '-', the transmitted SSB signal is the upper sideband (Figure 2-2(b)); otherwise, it is the lower sideband (Figure 2-2(e)).

# 2.2 Multirate systems and signal processing

Multirate digital signal processing technique provides a very efficient means for bandpass signal processing and multirate system optimizations. It minimizes computations in a multirate system by using the most appropriate sampling rate that is commensurate with the signal bandwidth [3]. This technique is particularly relevant to narrow band signal processing, e.g., in transmultiplexing/demultiplexing problems.

#### 2.2.1 Discrete signal representations

#### 2.2.1.1 Polyphase representation

Given an integer M, exactly M discrete signals can be obtained from a signal x(n), each of which is down sampled from x(n) with a different phase offset and is given as

$$x_{\lambda}^{(p)}(n) = x(nM + \lambda), \lambda = 0,1,\cdots M-1,$$

(2.9)

where  $x_{\lambda}^{(p)}(n)$ s are known as polyphase components of x(n). Consequently, the signal can be represented by the polyphase components in the following form:

$$x(n) = \sum_{\lambda=0}^{M-1} x_{\lambda}^{(p)} \left(\frac{n-\lambda}{M}\right) w_{M} (n-\lambda)$$

$$= \sum_{\lambda=0}^{M-1} x(n) w_{M} (n-\lambda)$$

(2.10)

where  $w_M(n)$  is the discrete sampling function, which is defined as

$$w_{M}(n) = \frac{1}{M} \sum_{k=0}^{M-1} W_{M}^{kn} = \begin{cases} 1 & \text{for } n = mM, m \text{ integer} \\ 0 & \text{otherwise} \end{cases}$$

(2.11)

It is easy to show that the polyphase representation of discrete signal in the z-domain is:

$$X(z) = \sum_{\lambda=0}^{M-1} z^{-\lambda} X_{\lambda}^{(p)}(z^{M})$$

(2.12)

where the z-transform of polyphase components is given as

$$X_{\lambda}^{(p)}(z) = \sum_{n=-\infty}^{\infty} x_{\lambda}^{(p)}(n)z^{-n}$$

(2.13)

#### 2.2.1.2 Modulation representation

A set of complex exponential modulated signals  $x_{k \mid M}^{(m)}(n), k = 0, 1, \dots, M-1$  is defined as

$$x_{k/M}^{(m)}(n) = x(n)e^{j\frac{2\pi}{M}n} = x(n)W_M^{-kn}$$

(2.14)

Their z-transforms are

$$X_{k/M}^{(m)}(z) = X(zW_M^k) \tag{2.15}$$

It is also simple to show, by considering Equations (2.10) and (2.11), that the z-transform of x(n) can be represented by its modulated signals, i.e.,

$$X(z) = \sum_{\lambda=0}^{M-1} \left( \frac{1}{M} \sum_{k=0}^{M-1} X_{k/M}^{(m)}(z) W_{M}^{\lambda k} \right)$$

(2.16)

Comparing with Eq. (2.12), we have the following relationship between the polyphase components and the modulation components:

$$z^{-\lambda} X_{\lambda}^{(p)} \left( z^{M} \right) = \frac{1}{M} \sum_{k=0}^{M-1} X_{k/M}^{(m)} \left( z \right) W_{M}^{\lambda k} \tag{2.17}$$

That is, the polyphase components can be obtained by performing an IDFT (Inverse DFT) to the modulation components.

# 2.2.2 Sampling rate alteration

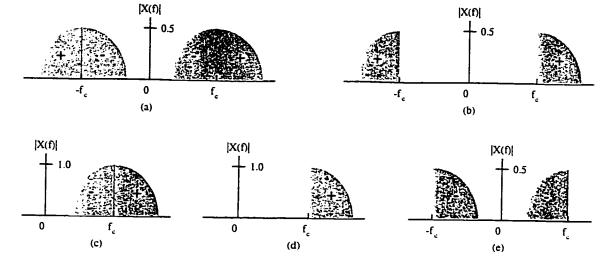

#### 2.2.2.1 Downsampling and decimation

Wherever sampling rates are considerably higher than the signal's Nyquist rate, there might be possibilities to reduce the sampling rate hence reducing the computation load. The process of downsampling is also called *sampling rate decimation*. In most cases, it consists of two stages: anti-aliasing filter followed by a downsampler, as shown in Figure 2-3(a). The purpose of the anti-aliasing filter (h(n)) is to remove spectral fold-over

(aliasing) into the band of interest after downsampling. For decimation by M, the downsampler simply takes every M-th samples and discards the rest from the input sequence. Hence, for the decimated signal depicted in Figure 2-3 (a),

$$y(m) = \sum_{k=-\infty}^{\infty} h(k)x(mM - k)$$

(2.18)

A prominent property of downsampling is that the spectrum of the downsampled signal is the sum of equally spaced shifted copy of the original signal spectrum. This property can be seen in the z-transform of the downsampled signal,

$$Y(z^{M}) = \frac{1}{M} \sum_{k=0}^{M-1} V(zW_{M}^{k})$$

(2.19)

With the substitutions of  $z = e^{j\omega}$  and V(z) = H(z)X(z), the Fourier relation between the decimated signal and the original signal is,

$$Y(M\omega) = \frac{1}{M} \sum_{k=0}^{M-1} X\left(\omega - \frac{2\pi k}{M}\right) \cdot H\left(\omega - \frac{2\pi k}{M}\right)$$

(2.20a)

or, in terms of new frequency  $\omega' = M\omega$

$$Y(\omega') = \frac{1}{M} \sum_{k=0}^{M-1} X\left(\frac{\omega' - 2\pi k}{M}\right) \cdot H\left(\frac{\omega' - 2\pi k}{M}\right)$$

(2.20b)

The spectral relation (ignoring scaling factors for the amplitudes) is shown in Figure 2-3(b) to Figure 2-3(e)

## 2.2.2.2 Upsampling and interpolation

If several narrow-band signals are to be combined to form a wide-band signal (as in FDM signal generation), their sampling rates must be increased before combining them together. The process of sampling rate increase is called *interpolation*. The sampling rate interpolation performs the upsampling followed by an anti-imaging filtering as shown in Figure 2-3(f). The latter is necessary because the up sampled sequence v(m) contains L-1 images of the baseband spectrum at harmonics of the original sampling frequency  $2\pi k/L$ ,  $k=1,2,\cdots L-1$ .

Figure 2-3 Spectra relation for integer rate alteration: (a) to (e) for integer rate decimation (M=3); (f) to (j) for integer rate interpolation (L=3)

The interpolated signal of Figure 2-3(f) can be represented as

$$y(m) = \sum_{k=-\infty}^{\infty} h(k) v(m-k)$$

(2.21)

where

$$v(m) = \begin{cases} x(m/L) & \text{for } m = nL, n \text{ integer,} \\ 0 & \text{otherwise.} \end{cases}$$

(2.22)

The z-transform of the up sampled signal is

$$V(z) = X(z^{L}) \tag{2.23}$$

Therefore, its Fourier transform is

$$V(\omega) = X(L\omega) = X(\omega') \tag{2.24}$$

These relations are illustrated in Figure 2-3(g) through Figure 2-3(j).

# 2.2.3 Rational sampling rate conversion

Sampling rate decimation or interpolation is the increase or decrease of sampling rate by an integer factor. In many cases, rational sampling rate conversions are required as in frequency demultiplexing filter banks. In this section, it will be shown that rational sampling conversion can be realized by a linear periodically time-varying (LPTV) filter. Alternatively, the LPTV filter can be replaced by a polyphase network in which all the subfilters are linear time invariant (LTI) and the LPTV operations are decoupled from the filtering by the use of SPC and PSC commutators.

#### 2.2.3.1 Rational sampling rate conversion

It has been shown that rational sampling rate conversion of a LTI discrete system leads to a LPTV system with input-to-output relation given as [19],

$$y(m) = \sum_{n = -\infty}^{\infty} g_m(n) x \left( \left( \frac{mM}{L} \right) - n \right)$$

(2.25)

where the time-varying impulse response  $g_m(n)$  is defined as

$$g_{m}(n) = h\left(\left(nL + \left\langle mM \right\rangle_{L}\right)T^{n}\right) \tag{2.26}$$

where h(t) is the impulse response of the corresponding continuous LTI system and 1/T'' is the sampling frequency for h(t).

The time-varying nature of Eq. (2.25) is apparent. Since  $g_m(n)$  is periodic in L, the system is linear periodically time-varying. Therefore, sampling rate alteration of a LTI system leads to a LPTV system if the rate change is rational. As the multirate filter bank theory is under the assumption of rational rate conversion, multirate filter banks thus belong to the class of LPTV systems.

For non-rational sampling rate alteration, the rate ratio could be expressed by a ratio of two very large integers which approach infinity, then the periodic nature of  $g_m(n)$  no longer exists due to infinite L. Therefore, for non-rational sampling alteration, the LTI system becomes in general linear time-varying. Figure 2-4 shows the rational sampling rate conversion using LPTV filter.

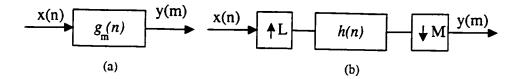

Figure 2-4 Rational sampling rate conversion:

(a) using a LPTV filter; (b) using a LTI filter

An alternative structure to Figure 2-4(a) is to use interpolation and decimation filters in tandem. As a result, the impulse responses of the anti-aliasing filter in the decimator and the anti-imaging filter in the interpolator can be combined into a single LTI filter h(n). The resultant rational sampling converter is shown in Figure 2-4(b). Ideally, for lowpass signals, the combined filter should have the frequency response as

$$H(\omega) = \begin{cases} L & \text{for } |\omega| \le \min\left\{\frac{\pi}{L}, \frac{\pi}{M}\right\} \\ 0 & \text{otherwise} \end{cases}$$

(2.27)

Compared to the LPTV filter approach, the symmetry property of the LTI filter can be exploited in this method, saving complexity by approximately a factor of two. Despite the advantages of avoiding time-varying filtering and being able to exploit symmetry property, the structure suffers poor computational efficiency since the filtering is performed at the highest sampling rate of the system. As will be shown later, a polyphase decimator and interpolator can greatly improve the computational efficiency by using a set of LTI sub-filters operating at a low sampling rate. They, however, lose symmetry due to the decomposition of the filter.

# 2.2.3.2 Polyphase analysis and polyphase synthesis of signals

Before introducing the concept of polyphase decomposition of decimation/interpolation filters, let us first look at two basic multirate operations, the polyphase analysis and polyphase synthesis of signals.

Polyphase components of signal:

For a discrete signal x(n) (real or complex), its N polyphase components are defined as

$$x_i(m) = x(mN+i), i = 0,1,\dots, N-1 \text{ and } m \in \mathbb{Z}$$

(2.28)

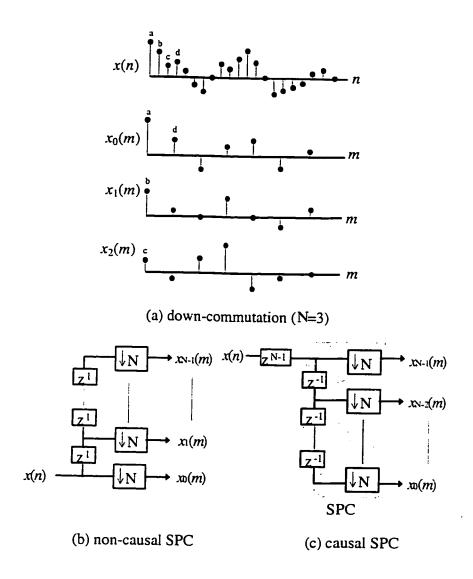

where N is an arbitrary integer. Clearly, a polyphase signal is a decimated signal with a time shift as illustrated in Figure 2-5(a). Though polyphase signals can also be defined as  $x_i(m) = x(mN - i)$ , as appeared in some literature, Eq. (2.28) will be solely used as the definition for polyphase signals hereafter to avoid confusion.

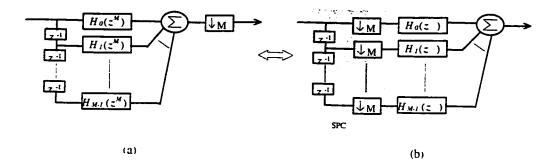

#### Polyphase analysis:

From the polyphase definition of Eq. (2.28), the polyphase components can be obtained through the structure shown in Figure 2-5(b). The commutation process in the structure is known as *polyphase analysis* and the structure is called *serial-to-parallel commutator* (converter) (SPC). Because time advances are used in the structure, it is non-causal and not realizable in practice. The time advances can be abstracted from the structure transforming the non-causal SPC structure into an equivalent structure consisting of a time advance and a causal SPC (shaded area) as shown in Figure 2-5(c).

#### Polyphase synthesis:

The dual process of polyphase analysis is called *polyphase synthesis* of a signal, which interleaves (combines) the polyphase components back into the original signal. The process is also governed by the relations of Eq. (2.28). The structure that synthesizes the original signal from the polyphase components should be the dual of Figure 2-5(b), which can be obtained by taking the generalized transposition to the figure-giving rise to Figure 2-6. The structure is called *parallel-to-serial commutator* (converter) (PSC).

Figure 2-5 Polyphase analysis of signal

Figure 2-6 Polyphase synthesis of signal

# 2.2.3.3 Polyphase decomposition of decimation and interpolation filters

Polyphase structures are extremely important in multirate systems and filter banks. They provide opportunities for moving filtering (computations) from high sampling rates to lower ones and enables hardware sharing amongst different channels in filter banks, leading to both computationally efficient and low-complexity structures.

Consider the direct structure of the sampling rate decimator in Figure 2-3(a). Since the impulse response of the LTI anti-aliasing filter can be regarded as a signal (it is indeed from system point of view), it can be polyphase decomposed according to Eq. (2.12). Hence, we have in z-domain,

$$H(z) = \sum_{\lambda=0}^{M-1} z^{-\lambda} H_{\lambda}^{(p)}(z^{M})$$

(2.29)

which represents a LTI polyphase network as shown in Figure 2-7(a). Replacing the antialiasing filter h(n) in Figure 2-3(a) with the polyphase network results in an equivalent structure shown in Figure 2-8(a). It follows that the downsampler can be moved across the polyphase network by applying noble identities (see section 3.5), giving rise to the computational efficient structure of Figure 2-8(b) in which LTI sub-filters are at the lower sampling rate.

Figure 2-7 Transposition of LTI polyphase network

Figure 2-8 Polyphase decimation filter

Figure 2-9 Polyphase interpolation filter

For the polyphase interpolator structure, the concept of transposition of LTI network can be used transforming the LTI polyphase network of Figure 2-7(a) into an equivalent transposed polyphase structure of Figure 2-7(b) (for M=L). Again, replacing the antiimaging filter in Figure 2-3(e) with the transposed polyphase filter of Figure 2-7(b), results in Figure 2-9(a). Applying noble identities to the structure, the upsamplers are moved across the polyphase network leaving the polyphase filters at the lower sampling rate. The resulting computationally efficient polyphase interpolator structure is shown in Figure 2-9(b).

## Theory of Multirate Signal Flow Graph Transformation

In this chapter we will briefly introduce the foundation of Multirate SFG (MSFG) and MSFG transformation. In addition, 18 MSFG operators as well as a number of MSFG transformations and identities in four categories will also be introduced.

#### **3.1 MSFG**

The signal graph representation renders explicit structural information making it suitable for hardware structure mapping. Nevertheless, the conventional signal flow graph (SFG) representation, which suits linear time invariant systems only [14,15], proves inadequate in multirate environment due to the linear periodically time varying nature of linear multirate systems [3].

For multirate systems, we introduce the multirate SFG representation as a complement to conventional design approaches and an extension to the SFG. A MSFG provides more direct and clearer link to the hardware structure and the parallelism of filter banks than does the pure mathematical representation. Being extended from the conventional SFG, the MSFG preserves most of the properties of the former. In multirate environment, identities and MSFG transformations are defined. With the introduction of a set of shorthand notation for MSFG, the flow graph manipulation and transformation problems can be considerably simplified.

Signal Flow Graph is traditionally defined by a set of branches and nodes in which the former define the signal operations and the latter define the connection points of these branches in the structure [3,14]. Similarly, a MSFG also consists of branches and nodes. However, branches in MSFG are restricted to be LTI (Linear Time Invariant), just as those in the conventional SFG, and all the non-linear and time-varying (modulation, down-sampling, up-sampling, for examples) operations are defined by node functions. The reason that we attribute the non-linear and multirate operations to node functions is because all the "irregularities" of the MSFG, with respect to the conventional SFG, can be approached by identities and transforms associated with nonlinear/time-varying nodes. Thus, special care is only needed when those nonlinear/time-varying nodes are involved.

From the point of view of signal processing, branches or node functions perform specified processing for input signal, so these branches and node functions can be represented as MSFG operators in my study.

#### 3.2 MSFG Operators

#### 3.2.1 Elementary MSFG operators

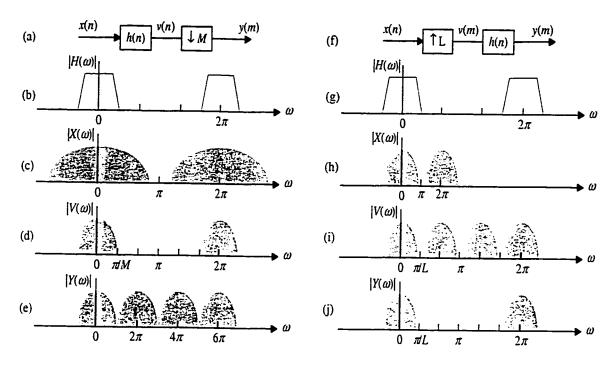

In multirate signal flow graph approach, five elementary operators, namely, adder (ADD), multiplier (MUL), delay element (DELAY), downsampler (DS) and upsampler (US) are defined.

Conceptually, the fundamental difference between classical DSP and multirate DSP lies in the sampling rate alteration, which is not allowed in the former.

The most fundamental single-rate operators are adder (ADD), which adds a group of input signals, multiplier (MUL), which multiplies the input signal with a real or complex constant, and delay element (DELAY), which delays the input signal by an integer number k of samples.

The most fundamental multirate operators are downsampler (DS) and upsampler (US), which respectively decrease or increase the sampling rate in multirate DSP.

These elementary MSFG operators are described detailedly in Table 3-1.

**Table 3-1 Elementary MSFG operators**

|   |                             | 71                        |                            | <del></del>                                                                                      |

|---|-----------------------------|---------------------------|----------------------------|--------------------------------------------------------------------------------------------------|

| N | Operator Name               | Block diagram<br>Notation | Short-hand notation        | Output<br>waveform                                                                               |

| 1 | ADD (adder)                 | <b>*</b>                  | 0000                       |                                                                                                  |

| 2 | MUL<br>(multiplier)         | <b>→</b>                  | $0 \xrightarrow{\alpha} 0$ |                                                                                                  |

| 3 | DELAY<br>(delay<br>element) | D                         | $0 \xrightarrow{z^{-1}} 0$ | S <sub>0</sub> S <sub>1</sub> S <sub>2</sub> S <sub>3</sub> S <sub>4</sub> S <sub>5</sub><br>N=2 |

| 4 | DS<br>(down-<br>sampler)    | <b>→   M →</b>            | $0 \longrightarrow M^{-1}$ | S0 S1 S2 S3 S4 S5<br>N=3                                                                         |

| 5 | US<br>(upsampler)           | → PL                      | ○ → L                      | S0 S1 S2 S3 S4 S5<br>N=3                                                                         |

#### 3.2.2 Basic MSFG operators

From these fundamental single-rate and multirate operators, we can define some composite MSFG operators, they are Modulator (MOD), Filter (FIL), S/P commutator (SPC), Overlapped S/P commutator (OSPC), P/S commutator (PSC), Null Operator (NULL), Sampling & Hold (SH), Upsampling & Hold (USH), Integral & Dump (IDU), and Sampler (SA).

From DS and US, three important rate-changing operators are defined. They are serial-to-parallel commutator (SPC), which decreases the sampling rate by decomposing the incoming signal into a group of sub-signals, parallel-to-serial commutator (PSC), which increases the sampling rate by combining a group of signals and overlapped serial-to-parallel commutator (OSPC), which is similar to the SPC except that the number of parallel branches N is larger than the decimation factor M.

There are some other multirate operators frequently encountered in digital networks. A sampling & hold (SH) does not actually change the sampling rate of a signal. It retains (holds) the signal value at the sampling point N (SH factor) times. An upsampling & hold (USH), on the other hand, does increase the sampling rate of a signal by repeating (holding) every signal element of the input signal L (USH factor) times. Similar to the upsampler that has the dual operation of downsampler, the USH also has a dual operation, which is the integral & dump (IDU). The IDU operator is defined by the transposition of USH. An IDU with decimation factor M integrates (accumulates) every M signal elements and dumps the integral to output reducing the sampling rate by a factor of M. Unlike the SH operator, a sampling (SA) operator samples the incoming sequence without holding the sampled signal elements, where  $k_n$  denotes the sampling instance n that satisfied  $n - k_n = 0$ , where n = 0, where n = 0, where n = 0 performs modulo N operation.

Apart from the above eight multirate operators, i.e., US, DS, SH, USH, SPC, PSC, IDU, and SA, three single-rate operators are also defined in MSFG. The output of a *null* operator (NULL) is exactly the same as its input. A modulation operator (MOD) performs signal modulation (multiply the input signal with modulation signal  $\phi(n)$  or  $W_N^n$ ). A filter (FIL) performs linear filtering whose impulse response is defined by

$$H(z) = \frac{Y(z)}{X(z)} = \frac{b_0 + b_1 z^{-1} + \dots + b_{M-1} z^{-(M-1)}}{a_0 + a_1 z^{-1} + \dots + a_{N-1} z^{-(N-1)}} = \frac{\sum_{k=0}^{M-1} b_k z^{-k}}{\sum_{k=0}^{N-1} a_k z^{-k}}.$$

(3.1)

These basic MSFG operators are described detailedly in Table 3-2.

**Table 3-2 Basic MSFG Operators**

|    | Table 3-2 Basic MSFG Operators      |                                                                                                                                                   |                                                   |                                                                                           |  |

|----|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------|--|

| No | Operator Name                       | Block diagram<br>Notation                                                                                                                         | Short-hand notation                               | Output<br>waveform                                                                        |  |

| 6  | MOD<br>(modulator)                  | →×→                                                                                                                                               | $0 \rightarrow 0 \rightarrow 0$ $0 \phi(n)$       |                                                                                           |  |

| 7  | FIL<br>(filter)                     | H(z)                                                                                                                                              | H(z)                                              |                                                                                           |  |

| 8  | SPC<br>(S/P<br>commutator)          | $ \begin{array}{c c} \hline Z^{-1} & \hline \hline M & c \\ \hline Z^{-1} & \hline M & b \\ \hline Z & \hline M & a \end{array} $                 | $0 \xrightarrow{M^{1}} 0 \xrightarrow{c} b$       | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                    |  |

| 9  | OSPC<br>(overlap S/P<br>commutator) | $ \begin{array}{c c} \hline z^{-1} & & \downarrow M & c \\ \hline z^{-1} & & \downarrow M & b \\ \hline z^{-1} & & \downarrow M & a \end{array} $ | $0 \xrightarrow{M^{-1}} 0 \xrightarrow{c} b$      | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                    |  |

| 10 | PSC<br>(P/S<br>commutator)          | $ \begin{array}{c c} c & AL & Z^{-1} \\ b & AL & Z^{-1} \\ \hline a & AL & Z \end{array} $                                                        | $b \stackrel{c}{\underset{a}{\longrightarrow}} 0$ |                                                                                           |  |

| 11 | NULL<br>(null operator)             |                                                                                                                                                   | oo                                                | S <sub>0</sub> S <sub>1</sub> S <sub>2</sub> S <sub>3</sub> S <sub>4</sub> S <sub>5</sub> |  |

| 12 | SH<br>(sampling<br>&hold)           | → <b>‡</b> n                                                                                                                                      | <b>○</b>                                          | S <sub>0</sub> S <sub>0</sub> S <sub>0</sub> S <sub>3</sub> S <sub>3</sub> S <sub>3</sub> |  |

| 13 | USH<br>(upsampling<br>&hold)        | → FL                                                                                                                                              | ○L                                                | S <sub>0</sub> S <sub>1</sub> S <sub>2</sub> S <sub>3</sub> S <sub>4</sub> S <sub>5</sub> |  |

| 14 | IDU<br>(integral<br>&dump)          | <b>→</b> <u>↓</u> M                                                                                                                               | O                                                 | S <sub>0</sub> +S <sub>1</sub> +S <sub>2</sub>                                            |  |

| 15 | SA<br>(sampler)                     | N=iN+k, I integer                                                                                                                                 | $\overset{k_{N}}{\longrightarrow}$                | S <sub>2</sub> <sup>N=3,k=2</sup> S <sub>5</sub>                                          |  |

#### 3.2.3 MIMO MSFG operators

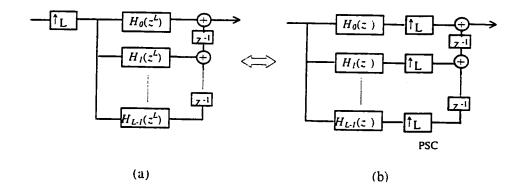

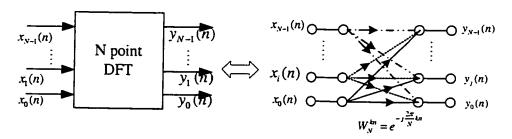

In addition, we define some useful MIMO (Multi-Input Multi-Output) MSFG operators, i.e., Discrete Fourier Transform (DFT), Interleaver (INTL), and Switch (SW).

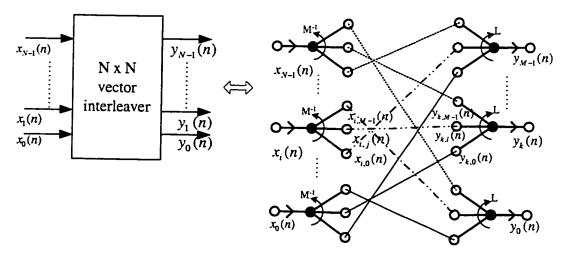

A Digital Fourier Transform (DFT), shown in Figure 3-1, performs

$$X[k] = \sum_{n=0}^{N-1} x[n] \cdot e^{-j\frac{2\pi}{N}kn} = \sum_{n=0}^{N-1} x[n] \cdot W_N^{kn}.$$

(3.2)

Figure 3-1 DFT

A switch (SW) interconnects an array of parallel input signals to an array of output ports. An interleaver (INTL), as shown Figure 3-2, writes an array of parallel signals into a memory in an order and reads them out in another order.

Figure 3-2 Interleaver

These MIMO MSFG operators are described in Table 3-3.

**Table 3-3 MIMO MSFG Operators**

| No | Operator Name                            | Block diagram<br>Notation           | Short-hand<br>notation | Output<br>waveform |

|----|------------------------------------------|-------------------------------------|------------------------|--------------------|

| 16 | DFT<br>(Digital<br>Fourial<br>Transform) | $W_N^{in} = e^{-i\frac{2\pi}{N}in}$ | DFT                    |                    |

| 17 | INTL<br>(inter-leaver)                   | # A(n)                              | IL.                    |                    |

| 18 | SW<br>(switch)                           |                                     | S W                    |                    |

#### 3.3 MSFG transformation

A multirate DSP system can be transformed into its equivalencies with different structures via flow graph transformations to be given in the follow sections. The fundamental relationships between multirate operators have been given in the form of identity (noble identities shown in Figure 3-4).

The most fundamental and important result in multirate DSP theory is, perhaps, the concept of polyphase decomposition of signals and networks. Polyphase filter transform can lead to computationally efficient filter bank structures. The polyphase decomposition concept can be extended to modulation leading to the Modulation Polyphase Decomposition Transform (MPDT) and its variations.

Since the upsampling and downsampling processes are often realized via PSC and SPC (as in polyphase decomposition of filters and modulators) in multirate DSP networks, one will inevitably deal with various combinations of commutators and other signal processing components in multirate networks. A set of identities associated with

the cascades of commutators with filters, modulators, and single up/down-samplers have been identified. They are very useful in multirate DSP network transformations.

#### 3.4 Superposition theorem

For a linear multirate system H(z), if it has more than one independent signal sources  $S_i$ , i=1, ..., N, and the transfer functions from  $S_i(n)$  to the output are  $H_i(z)$ , i=1, ..., N, then the response of the system is the sum of the partial responses  $D_i(z)=S_i(z)\bullet H_i(z)$ , i.e.,

$$D(z) = \sum_{i=1}^{N} S_i(z) \bullet H_i(z)$$

(3.3)

This theorem can be expressed graphically by Figure 3-3.

Figure 3-3 Superposition theorem

In the following sections, we will summarize various MSFG transformations in different categories.

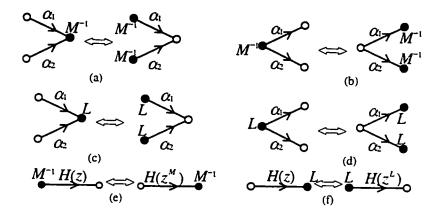

#### 3.5 The noble identities

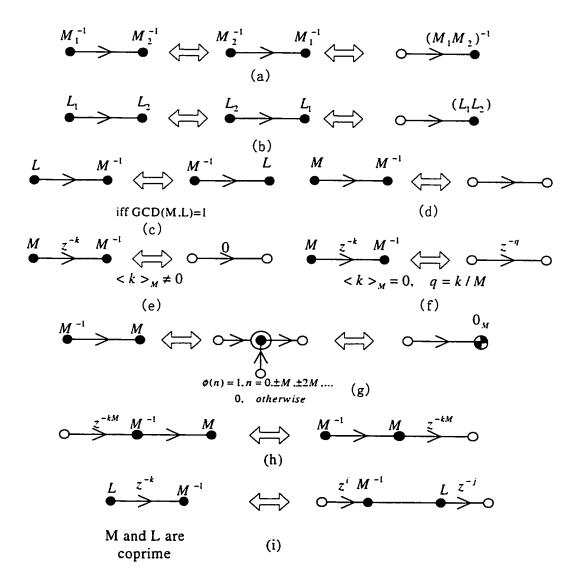

The noble identities are considered the most fundamental characteristics of multirate systems, with which most MSFG identities and transforms can be derived. Some noble identities are shown in Figure 3-4.

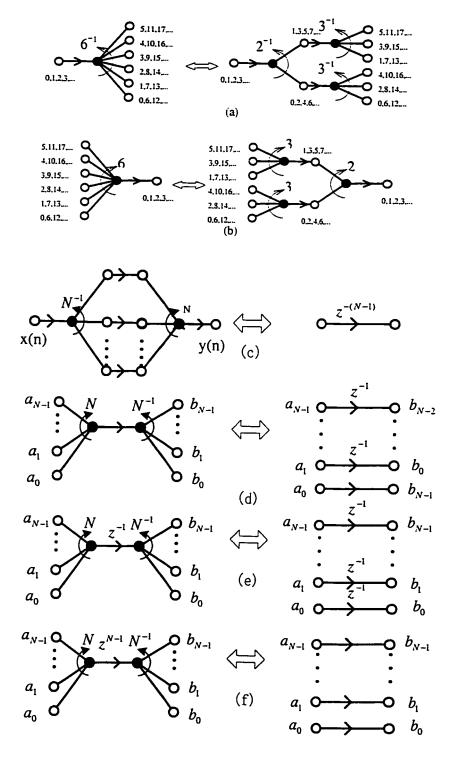

Figure 3-4 Noble identities

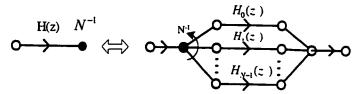

The identities (a) to (d) are obvious because of the linear assumption of MSFG. The noble identity (e) shows that the downsampler (with factor M) can be moved forward across any LTI system and it can be moved backward across a LTI system if, and only if, the system is divisible by  $z^{-M}$  to avoid non-realizable fractional delays. Similarly, the noble identity (f) suggests that an upsampler (with factor L) can move backward freely across any LTI system and move forward across a LTI system only when it is divisible by  $z^{-L}$ .

#### 3.6 General identities

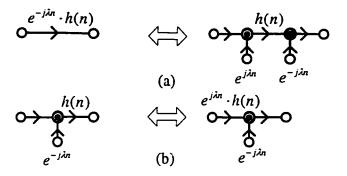

#### 3.6.1 Complex filter identities

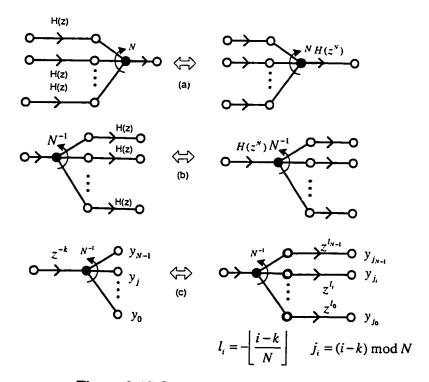

Figure 3-5 show that complex filter identities. Identity Figure 3-5(a) shows that a complex filter can be realized using the DRFU (Down-Real Filter-Up) structure. Identity Figure 3-5(b) shows that if a signal is firstly modulated by a complex exponential and then filtered by a real filter, the process is equivalent to firstly filtering with an inverse modulated filter (complex) and then modulating with the complex exponential.

Figure 3-5 Complex filtering identities

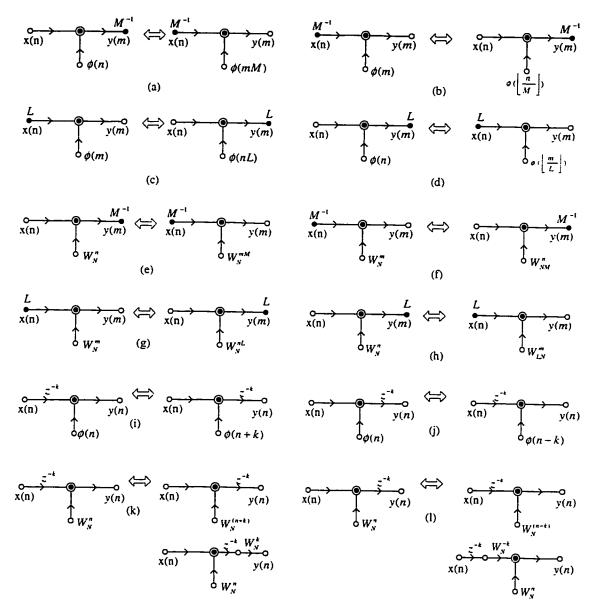

#### **3.6.2** Modulation identities

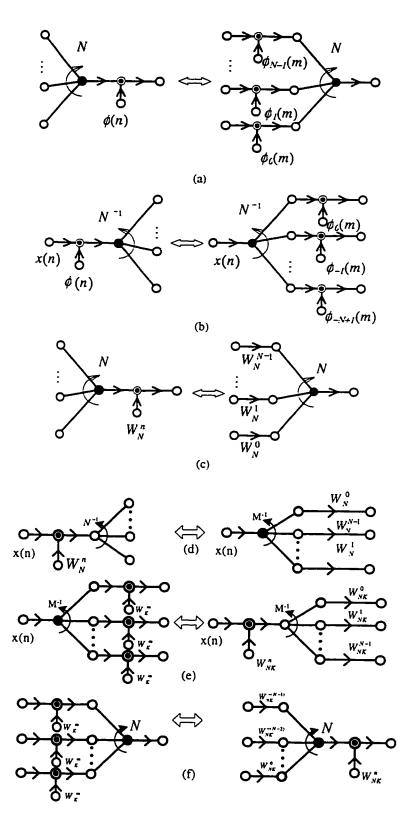

Some important equivalent structures associated with modulation operators, which are frequently used in multirate filter bank design, are summarized into identities shown in Figure 3-6. The identities shown in Figure 3-6(a) to Figure 3-6(d) holds for arbitrary modulating sequence  $\phi(n)$ , periodic or non-periodic. The modulating sequences  $\phi(n)$  in Figure 3-6(b) are up-sampled (hold or without hold) versions for  $\phi(n)$ ; and  $\phi(n)$  in Figure 3-6(d) are for  $\phi(n)$ .

Since most often the modulating sequences are complex exponentials, the identities shown in Figure 3-6(a) to Figure 3-6(d) are equivalent to those of Figure 3-6 (e) to Figure 3-6 (h).

We often have to deal with cascades of modulator and delay/advance in MSFG networks. Assuming that the modulation sequence extends infinitives in both time directions, it is easy to show that the delay can be moved across the modulator if the origin of the modulating sequence changes accordingly as shown in Figure 3-6 (i) and Figure 3-6 (j). The identities shown in Figure 3-6 (k) and Figure 3-6 (l) are the equivalent to those of Figure 3-6(i) to Figure 3-6(j) when complex exponentials are used.

Figure 3-6 Modulation identities

#### 3.6.3 Identities associated with composite rate-changing operators

According to the definition of USH operator, it is equivalent to a PSC that has all its parallel inputs connecting to an ordinary operator as shown in Figure 3-7(a). The IDU function, as the dual to USH, is equivalent to the transposition of USH and is shown in Figure 3-7 (b). Another way of realizing the IDU function is to perform an M tap comb filtering first and then down sample the sequence by M as shown in the Figure 3-7(b). Having defined the USH function, the SH function can be realized by the simple cascade

of a down sampler and an USH as shown in Figure 3-7(c). Figure 3-7(d) shows this relation, which includes the identity shown in Figure 3-12(g), as special case with k=0.

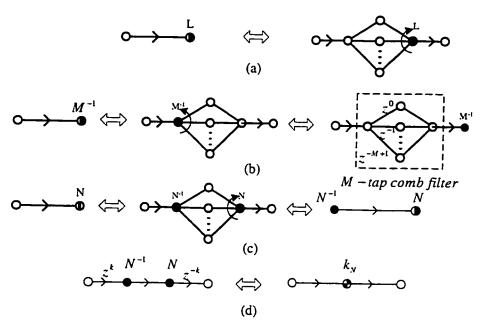

Figure 3-7 Identities associated with composite rate-changing operators

#### 3.7 Polyphase decomposition

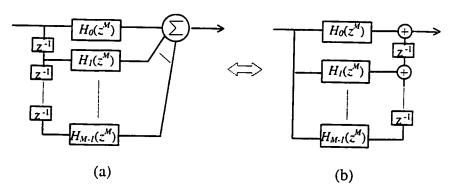

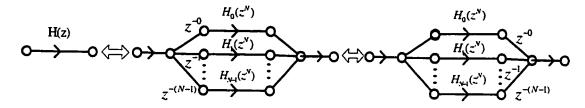

#### 3.7.1 Filter Polyphase decomposition

Polyphase structures are extremely important in multirate systems and filter banks, which are shown as Figure 3-8. They provide opportunities for moving filtering from high sampling rates to lower sampling rates and enables hardware sharing amongst different channels in filter banks, leading to both computationally efficient and low-complexity structures.  $H_i(z)$ 's are the z-transforms of polyphase filters  $h_i(m)$ 's which are defined as

$$h_i(m) = h(mN + i), i = 0,1,...,N-1$$

(3.4)

(a) polyphase decomposition for LTI filter

(b) polyphase decomposition for decimation filter

(c) polyphase decomposition for interpolation filter

Figure 3-8 Polyphase decomposition transforms (PDT)

#### 3.7.2 Modulation polyphase decomposition

Consider the modulation of signal x(n) with a sequence  $\phi(n)$ , the result signal y(n) is:  $y(n)=x(n)\phi(n)$ . Similar to the FIR filter polyphase decomposition, the signal y(n) can be represented by its N polyphase components:

$$y_i(m) = y(mN + i) = x_i(m)\phi_i(m)$$

(3.5)

where

$$x_i(m) = x(mN + i)$$

$$\phi_i(m) = \phi(mN + i)$$

(3.6)

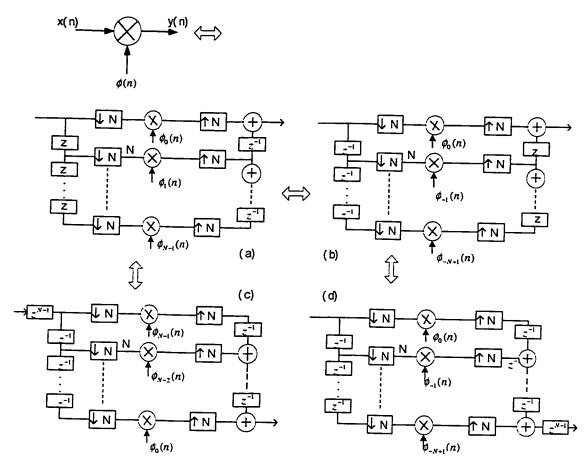

i=0,1,...,N-1, m is integer.  $x_i(m)$  and  $\phi_i(m)$  are polyphase components of x(n) and  $\phi(n)$  respectively. With the SPC and PSC structures of Figure 2-5(b) and Figure 2-6, the Eq. 3.7 can be described as a polyphase network shown in Figure 3-9(a). It is called *type 1 MPDT* (Modulation Polyphase Decomposition Transform). Alternatively, the modulation can be expressed with a different set of polyphase components by:

$$y_{i}(m) = y_{-i}(m) = y(mN - i)$$

$$= x(mN - i)\phi(mN - i)$$

$$= x_{-i}(m)\phi_{-i}(m)$$

(3.7)

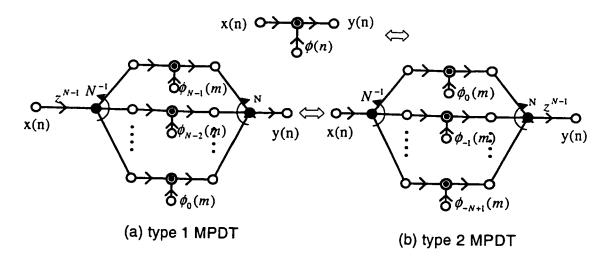

In this case, the SPC will be causal but the PSC will not be causal. The embedded poly-phase network is shown in Figure 3-9(b), which is equivalent to Figure 3-9(a) and is called *type 2 MPDT*. In the above polyphase networks, the serial-to-parallel commutator (SPC) in Figure 3-9(a) and the parallel-to-serial commutator (PSC) in Figure 3-9(b) are non-causal hence unrealizable. In section 2.2.3.2, it has been shown that non-causal SPC can be replaced by a time advance of  $z^{N-1}$  followed by a causal SPC. Similarly, a non-causal PSC can be substituted by a causal PSC followed by a time advance  $z^{N-1}$ . Therefore, the type 1 and type 2 MPDT have the equivalent structures shown in Figure 3-9(c) and Figure 3-9(d) respectively. The corresponding MSFGs are shown in Figure 3-10(a) and Figure 3-10(b) respectively.

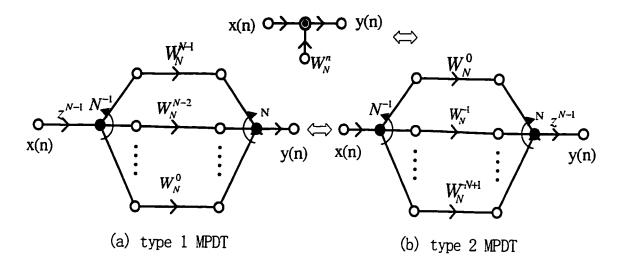

If the modulating sequence is a complex exponential with period N,

$$\phi(n) = e^{-j\frac{2\pi}{N}n} = W_N^n$$

(3.8)

then its components become complex constants  $\phi_i(m) = \phi(mN + i) = W_N^i$ , which leads to simple MPDT structure in which the modulation is replaced by simple scalar, as shown as Figure 3-11(a) and Figure 3-11 (b).

Figure 3-9 Two types of MPDT structures in conventional SFG

Figure 3-10 MSFGs of type 1 and type 2 MPDT

Figure 3-11 MPDT for complex modulation

#### 3.8 Cascade of operators

#### 3.8.1 Cascade of samplers

Cascade of samplers are shown in Figure 3-12. The identities of Figure 3-12(a) and (b) show that down-sampling and up-sampling can be performed in stages if the factors are composite. It's evident from the definitions of down-sampling and up-sampling. Identity Figure 3-12(c) shows that for a upsampler-downsampler, or downsamplerupsampler, cascade to be commutable the necessary and sufficient condition is that the two rate converting factors L and M must be co-prime, i.e., GCD(L,M)=1. When the upsampler and the downsampler have the same factor M, the order cannot be changed. Identity Figure 3-12(d) show that if up-sampler is preceding down-sampler and two rate factors are all M, the inserted M-1 zeros to each signal sample by up-sampler will be discarded by down-sampler, result the output are exactly the same as input. Figure 3-12(e) and (f) shown that if k=qM, noble identity (e) or (f) can be applied, the delay can be moved across the samplers and become to  $z^{-q}$  from  $z^{-qM}$ ; otherwise the output samples will be constant zero because at the sampling points of the downsampler the signal elements are all zeros. In contrast, if down-sampler is performed first shown in Figure 3-12(g), the following upsampler will insert M-1 zeros after each sample retained by the downsampler, hence the process is equivalent to the modulation of the signal with a sampling sequence as shown in Figure 3-12(g) and is also equivalent to the sampler (SA)

with offset equal to zero. In identity Figure 3-12(h), it is very clear that when this sampling process is cascaded with a delay which k=qM on any side of the network, the delay can move across the downsampler-upsampler cascade freely. This property can be proved by simply applying the noble identity (e) or (f). Figure 3-12(i) shows that if M and L are co-prime, we can find i and j which satisfy iL-jM = -k, then  $z^{iL}$  and  $z^{-jm}$  can exchange with upsampler and downsampler, applying noble identities (e) and (f).

Figure 3-12 Cascade of samplers

#### 3.8.2 Cascade of commutators

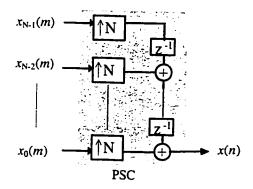

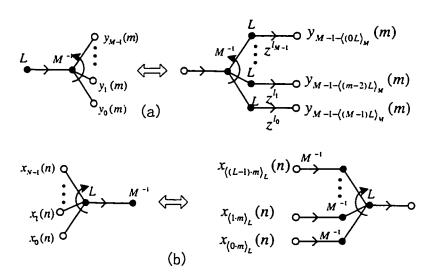

Serial-to-parallel (SPC) and parallel-to-serial (PSC) commutations can be performed in multi-stage if the commutation factors are composite. That is, for N-fold commutation, if  $N = \prod_{i=0}^{m-1} N_i$ , an M-stage commutation tree can be constructed, Figure 3-13 (a) and (b) demonstrates how a SPC and a PSC (N=6 for both cases) are decomposed into commutation trees. The numbers in the figure are the sample indices of signal elements. This property is frequently used in MSFG simplification.

From time to time, we have to deal with SPC-PSC and PSC-SPC cascades in MSFG manipulation. Since SPC and PSC are dual and perform operations complementary to each other, it is intuitive to foresee that cascading of the two would cancel the effects of the two types of commutations. Therefore, it can be expected that the cascades should be equivalent to simple networks connecting the input(s) and the output(s) with, perhaps, some pure delays as a consequence of the use of causal PSC. It is simple to verify (e.g., graphically) that an SPC-PSC cascade with commutation factor of N is equivalent to a pure delay of N-1 (shown in Figure 3-13(c)). Similarly, a PSC-SPC cascade is equivalent to a part delayed connection (except  $a_0$  and  $b_0$  no delay, others delayed with a unit delay) as shown in Figure 3-13 (d). In particular, when a unit delay is inserted between the PSC and SPC, the network can be transformed into a full delayed connection (with a unit delay) between corresponding ports of PSC and SPC (Figure 3-13 (e)). The simplest case is the direct connections between the corresponding PSC and SPC ports, which occurs when a time advance of  $z^{N-1}$  is in sandwich between the commutators, as shown in Figure 3-13(f).

**Figure 3-13 Cascades of Commutators**

#### 3.8.3 Commutator-modulator cascades

When modulators are cascaded with commutators, MPDTs introduced in section 3.7.2 can be used to move polyphase components of modulating sequences into polyphase branches of commutators. For a PSC-modulator cascade, by using the type 1 MPDT to the modulator and then applying the identity of Figure 3-13(f), the modulator is polyphase decomposed and moved into the PSC branches as shown in Figure 3-14(a). Similarly, for a modulator-SPC cascade, it can be transformed into an equivalent structure shown in Figure 3-14 (b) by applying the type 2 MPDT and the identity of Figure 3-13(f). If the modulation sequence in the above cascades is periodic with period N of  $\phi(n) = W_N^n$  being equal to the commutation factor N, then the modulators in the commutator branches become scalar multipliers as shown in Figure 3-14(c) and 3.14(d).

If branches of a SPC are modulated with the same periodic sequence, say a complex exponential of  $\phi(n) = W_N^n$ , then a common modulator can be used for all the branches and each branch is phase shifted by a constant phase as shown in Figure 3-14(e). This identity can be proved by applying the identities of Figure 3-6(f) and Figure 3-6(i). Similarly, when branches of a PSC are modulated with the same complex exponential, a common modulator can be used and each branch has to be phase shifted accordingly as shown in Figure 3-14(f).

Figure 3-14 Commutator-SPC and SPC-commutator identities

#### 3.8.4 Commutator-filter cascades

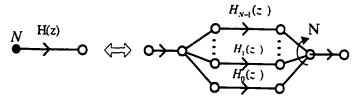

Some times, it is necessary to identify equivalent structures for commutators whose branches connect to identical filters as shown in Figure 3-15 (a) and (b). In these cases, applying with noble identities, we can move the filters to the other side of the commutators resulting in a cascade of commutator with an interpolated filter. If filter H(z) is replaced with a pure delay  $z^{-k}$ , the situation will change, the delay can across the SPC-commutator, but the delay for each branches will be  $z^{l_i}$ , and the output sequence will change also to  $y_{j_i}$ , where  $l_i = -\left\lfloor \frac{i-k}{N} \right\rfloor$  and  $j_i = (i-k) \mod N$ . It is shown at Figure 3-15(c).

The notation  $\lfloor x \rfloor$  indicates the floor function, which is the greatest integer less than or equal to x.

Figure 3-15 Commutator-filter identities

#### 3.8.5 Commutator-sampler commutability

In MSFG transformation, it is often needed to move samplers across commutators, e.g., in upsampler-SPC and PSC-downsampler cascades. It can be shown that the commutation is allowed only when the sampler factor L of the sampler and the commutation factor M are co-prime (i.e., GCD (L, M)=1). Here, GCD-Great Common Divisor, is the greatest common divisor of two positive integers L and M, for example, GCD(3,5)=1. Also, the move of the sampler will lead to reordering of the commutator branches and time advance to the branch signals shown as Figure 3-16.

For an upsampler-SPC cascade (Figure 3-16(a)), if L and M are co-prime, the upsampler can be moved to the output of the SPC. The time advance introduced to the i-th branch of the SPC will be

$$l_i = \left\lfloor \frac{(M-1-i)l}{m} \right\rfloor \tag{3.9}$$

where l and m are any solution of

$$mL - lM = 1 (3.10)$$

The original output poly phase signals will be reordered as a result of the transform by delivering k-th polyphase component  $y_k(m)$ , instead  $y_i(m)$  at the i-th branch of the transformed structure. Where k is given by

$$k = M - 1 - \langle (M - 1 - i)L \rangle_{M}$$

(3.11)

Similarly, when the downsampler moves across the PSC in a PSC-downsampler cascade as shown in Figure 3-16 (b), the time advance introduced to the i-th branch of the PSC is

$$m_i = \left\lfloor \frac{im}{l} \right\rfloor \tag{3.12}$$

where l and m are any solution of

$$mL - lM = -1 \tag{3.13}$$

Again, as shown in Figure 3-16(b), the input poly-phase signal are reordered in the transformed network with  $x_k(m)$  instead of  $x_i(n)$ , as the input signal to i-th channel, where k is determined by

$$k = \langle iM \rangle_L \tag{3.14}$$

The notation  $\langle \bullet \rangle_{\bullet}$  indicates modulo operation, that is,  $\langle n \rangle_{N} \equiv n \mod N$ .

Figure 3-16 Sampler-commutator identities

#### Chapter 4

# A Computer Aided Design System for Transformation and Optimization of Multirate DSP systems

Instead of manipulating the MSFG manually, this computer aided design system can perform the MSFG transformations and optimization of multirate networks in an automatic or interactive manner.

In this chapter, we will introduce in detail the data structure, system block diagram, MSFG transformation, simulation, verification and optimization of this computer aided design system [11].

### 4.1 Objectives and requirements of the computer aided design systems