**INFORMATION TO USERS**

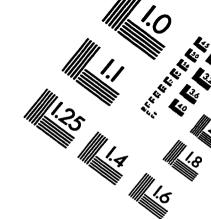

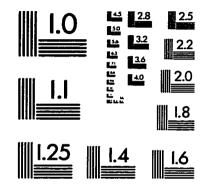

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

UMI

A Bell & Howell Information Company

300 North Zeeb Road, Ann Arbor MI 48106-1346 USA

313/761-4700 800/521-0600

## SINGLE PHASE TRAPEZOIDAL AC POWER SUPPLIES FOR HYBRID FIBER/COAX NETWORKS

## Neeraj Kaushik

A Thesis

in

The Department

of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at Concordia University Montreal, Quebec, Canada

> February 1997 © Neeraj Kaushik, 1997

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre rélérance

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-26005-4

## **ABSTRACT**

## Single Phase Trapezoidal AC Power Supplies for Hybrid Fiber/ Coax Networks

## Neeraj Kaushik

Single phase ac power supplies are used to power hybrid fiber/coax (HFC) networks. These power supplies are required to produce a trapezoidal-shaped voltage waveform. Conventional power supplies having a front-end diode bridge rectifier and a large dc bus capacitor are an unacceptable approach for this application as they draw a highly distorted current waveform resulting in a poor power factor. An intermediate boost stage is used to waveshape the input current thus providing power factor correction. Owing to the additional power conversion stage, this topology results in reduced efficiency. In this thesis a novel power supply topology is proposed which eliminates the use of the boost stage and the large dc bus capacitor while maintaining high efficiency and good power factor. Three voltage controlled PWM pattern generators namely, Hysteresis, Triangular-carrier and One-cycle technique are identified and implemented for the power supply based on the proposed topology. Performance comparison of the power supply using the three techniques is done based on criteria such as input power factor, input current total harmonic distortion and efficiency. Experimental results on a laboratory prototype confirm the feasibility of the proposed power supply.

## **ACKNOWLEDGEMENTS**

I wish to express my gratitude to Dr. G. Joós and Dr. P. Jain for their valuable advice and support during the course of this study.

I like to thank all my friends and research colleagues, especially Donato Vincenti and Jose Espinoza for their technical support and help.

I wish to acknowledge the financial support received from the Natural Sciences and Engineering Research Council (Canada) and the Fonds FCAR (Province of Quebec).

## **TABLE OF CONTENTS**

| List of Figuresvii                                                               |

|----------------------------------------------------------------------------------|

| List of Tablesxiv                                                                |

| List of Acronymsxv                                                               |

| List of Principle Symbolsxvi                                                     |

|                                                                                  |

| CHAPTER 1. INTRODUCTION                                                          |

| 1.1 General1                                                                     |

| 1.2 Problem definition4                                                          |

| 1.2.1 Conventional regulated ac/ac power supply without power factor correction6 |

| 1.2.2 Conventional regulated ac/ac power supply with power factor correction8    |

| 1.3 Proposed topology9                                                           |

| 1.4 Scope and contribution of the thesis                                         |

| 1.5 Outline of the thesis                                                        |

|                                                                                  |

| CHAPTER 2. PWM PATTERN GENERATOR AND CONTROL TECHNIQUES                          |

| FOR THE POWER SUPPLY                                                             |

| 2.1 Introduction                                                                 |

| 2.2 Hysteresis Integral PWM Control Technique                                    |

| 2.2.1 Principle of operation                                                     |

| 2.2.2 Implementation aspects                                                     |

|                   | 2.2.3 Modes of operation                                | 16                             |

|-------------------|---------------------------------------------------------|--------------------------------|

| 2.3               | Triangular-carrier Integral PWM Control Technique1      | 7                              |

|                   | 2.3.1 Principle of operation                            | 8                              |

|                   | 2.3.2 Implementation aspects                            | 9                              |

|                   | 2.3.3 Modes of operation                                | 20                             |

| 2.4               | One-cycle Integral PWM Control Technique                | 22                             |

|                   | 2.4.1 Principle of operation                            | 22                             |

|                   | 2.4.2 Implementation aspects                            | 23                             |

|                   | 2.4.3 Modes of operation                                | 25                             |

| 2.5               | Conclusion2                                             | 27                             |

|                   |                                                         |                                |

|                   |                                                         |                                |

| CH                | APTER 3. CONTROL LOOP DESIGN                            |                                |

|                   | Introduction                                            | 28                             |

| 3.1               |                                                         |                                |

| 3.1               | Introduction                                            | 29                             |

| 3.1               | Introduction                                            | 29<br>29                       |

| 3.1               | Introduction  Hysteresis Integral PWM Control Technique | 29<br>29<br>32                 |

| 3.1               | Introduction                                            | 29<br>29<br>32<br>2            |

| 3.1               | Introduction                                            | 29<br>29<br>32<br>2            |

| 3.1<br>3.2<br>3.3 | Introduction                                            | 29<br>29<br>32<br>2<br>4       |

| 3.1<br>3.2<br>3.3 | Introduction                                            | 29<br>29<br>32<br>2<br>4<br>35 |

| 3.6 Conclusions40                                                           |

|-----------------------------------------------------------------------------|

| CHAPTER 4. ANALYSIS AND PERFORMANCE COMPARISON OF THE THREE CONTROL SCHEMES |

| 4.1 Introduction41                                                          |

| 4.2 Average switching function analysis42                                   |

| 4.3 Experimental results53                                                  |

| 4.4 Performance evaluation and comparison53                                 |

| 4.5 Conclusions                                                             |

|                                                                             |

| CHAPTER 5. POWER CIRCUIT DESIGN                                             |

| 5.1 Introduction                                                            |

| 5.2 Circuit description                                                     |

| 5.3 Design considerations for power circuit70                               |

| 5.4 Design example79                                                        |

| 5.5 Conclusions80                                                           |

|                                                                             |

| CHAPTER 6. SUMMARY AND CONCLUSIONS                                          |

| 6.1 Summary82                                                               |

| 6.2 Conclusions83                                                           |

| 6.3 Suggestions for future research work                                    |

| REFERENCES 84 APPENDICES 89                                                 |

## **LIST OF FIGURES**

| Fig. 1 Hybrid fiber/coax network2                                                         |

|-------------------------------------------------------------------------------------------|

| Fig. 2 Utility interface                                                                  |

| Fig. 3 Conventional regulated ac/ac power supply without power factor correction6         |

| Fig. 4 Conventional regulated ac/ac power supply with power factor correction9            |

| Fig. 5 Proposed power supply topology                                                     |

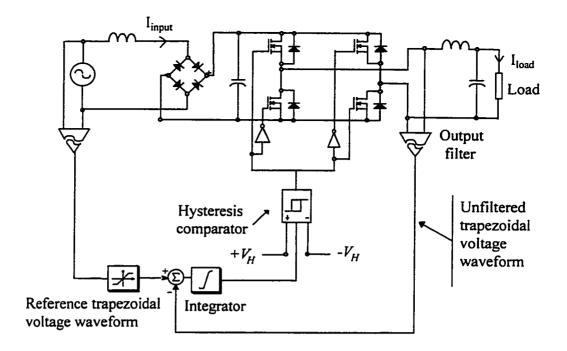

| Fig 2.2 Pattern generator based on Hysteresis integral PWM control                        |

| Fig. 2.3 Hysteresis-based PWM controller                                                  |

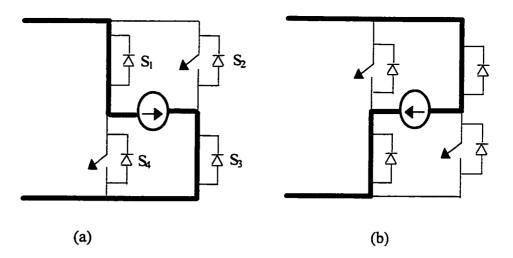

| Fig. 2.4 Modes of Operation of the PWM inverter based on the hysteresis integral17        |

| PWM control. (a) operation of the inverter for positive half-cycle of the trape-          |

| zoidal reference. (b) operation of the inverter for negative half-cycle of the trape-     |

| zoidal reference.                                                                         |

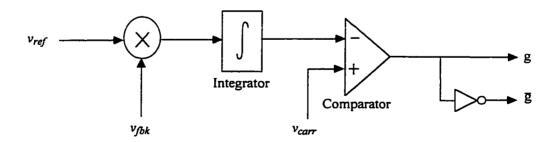

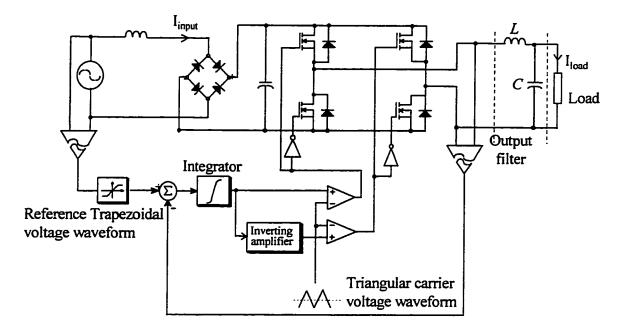

| Fig. 2.5 Pattern generator based on Triangular-carrier integral PWM control               |

| Fig. 2.6 Triangular-carrier based PWM integral control                                    |

| Fig. 2.7 Modes of Operation of the PWM inverter based on the Triangular21                 |

| carrier integral control. (a) and (b) represent operation of the inverter for positive    |

| half-cycle of the trapezoidal reference. (c) and (d) depict the operation of the inverter |

| for negative half-cycle of the trapezoidal reference.                                     |

| Fig. 2.8 Pattern generator based on One-cycle reser integral PWM control                  |

| Fig. 2.9 One-cycle Reset Integral F wivi controller                                      |

|------------------------------------------------------------------------------------------|

| Fig. 2.10 Modes of Operation of the PWM inverter based on the reset integral2            |

| control. (a) and (b) represent operation of the inverter for positive half-cycle of      |

| the trapezoidal reference. (c) and (d) depict the operation of the inverter for negative |

| half-cycle of the trapezoidal reference.                                                 |

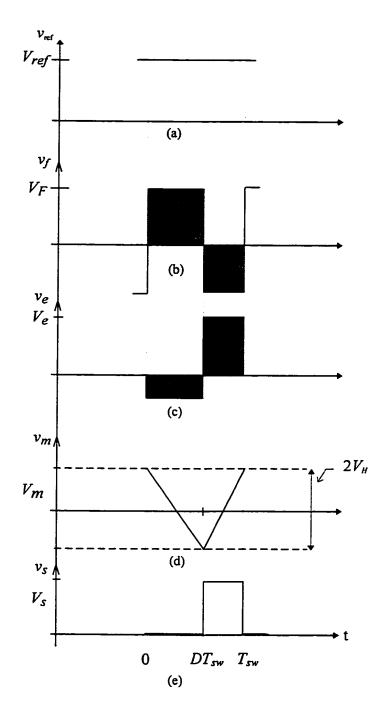

| Fig. 3.1 Waveforms representing a specific period of operation of the converter30        |

| based on hysteresis based controller. (a) reference trapezoidal waveform.                |

| (b) feedback voltage signal. (c) error voltage signal. (d) integrated error waveform.    |

| (e) gating signal generated at the output of the comparator.                             |

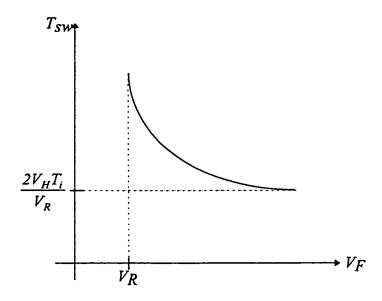

| Fig. 3.2 Variation of feedback voltage with the switching period                         |

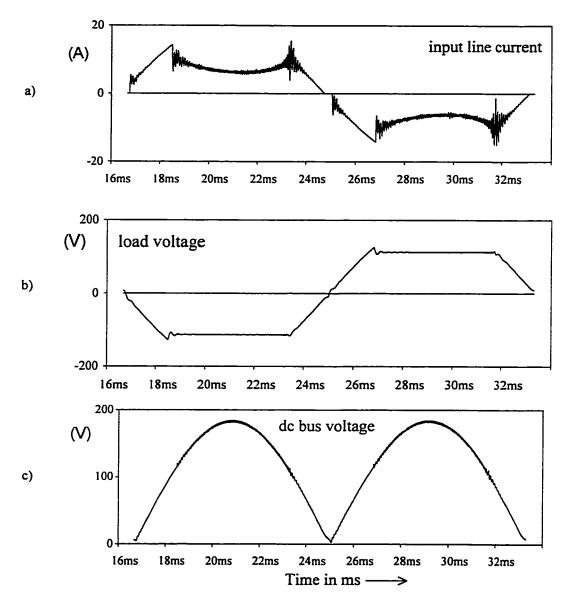

| Fig. 3.3 Operation of the hysteresis based PWM controller (simulated results)33          |

| (a) Input current. (b) Load voltage (filtered). (c) Dc bus voltage.                      |

| (Hysteresis window $\Delta V_H = 5$ % peak of reference,                                 |

| average switching frequency $f_{SW}$ = 40 kHz, input voltage = 120 V,                    |

| output voltage = 90 V rms, rated output current = 10 A, resistive load).                 |

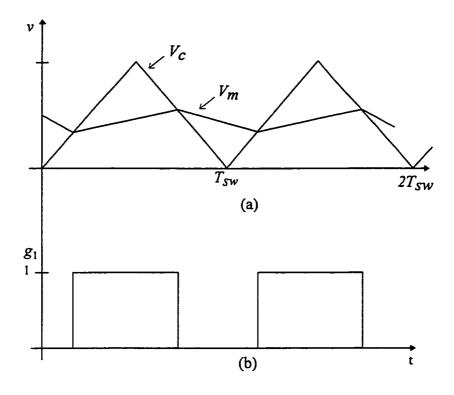

| Fig. 3.4 Control waveforms for triangular-carrier integral control technique34           |

| Fig. 3.5 Operation of the Triangular Carrier-based integral PWM controller36             |

| (simulated results). (a) Input current. (b) Load voltage (filtered) (c) DC bus voltage.  |

| (Magnitude of the carrier = 20 V (peak to peak), average switching frequency             |

| $f_{SW}$ = 40 kHz, input voltage = 120 V rms, output voltage = 90 V rms rated output     |

| Fig. 3.6 Control waveforms for one-cycle reset PWM integral control technique37             |

|---------------------------------------------------------------------------------------------|

| Fig. 3.7 Operation of the Reset Integral PWM Controller (simulated results)39               |

| (a) Input current (c) output voltage (filtered) (c) DC bus voltage.                         |

| (Integrator gain = 20 $\mu$ s, switching (clock) frequency $f_{SW}$ = 40 kHz, input voltage |

| = 120 V, output voltage = 90 V, rated output current = 10 A, resistive load).               |

| Fig. 4.1 (a) Rectified dc bus voltage and rectified trapezoidal reference                   |

| (b) Inverter average switching function. (c) Input line current (rated voltage, 130 V,      |

| rated load, 10 A.                                                                           |

| Fig. 4.2 Output rectified waveform of the bridge rectifier                                  |

| Fig. 4.3 Harmonic spectrum of the output voltage of the bridge rectifier47                  |

| Fig. 4.4 Output trapezoidal waveform of the full-bridge inverter                            |

| Fig. 4.5 Harmonic spectrum of the output trapezoidal waveform of the                        |

| full-bridge inverter                                                                        |

| Fig. 4.6 Switching function curve of the full-bridge inverter                               |

| Fig. 4.7 Waveform of the dc bus current                                                     |

| Fig. 4.8 Waveshape of the input current drawn from the utility by the supply51              |

| Fig. 4.9 Harmonic spectrum of the input current drawn by the power supply51                 |

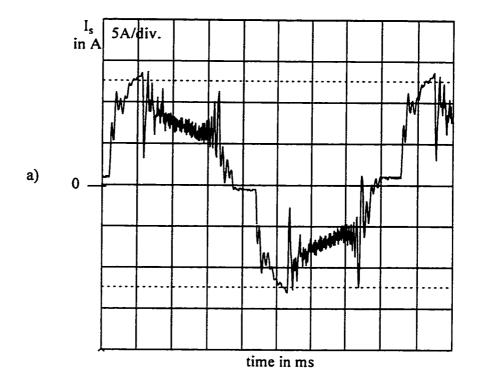

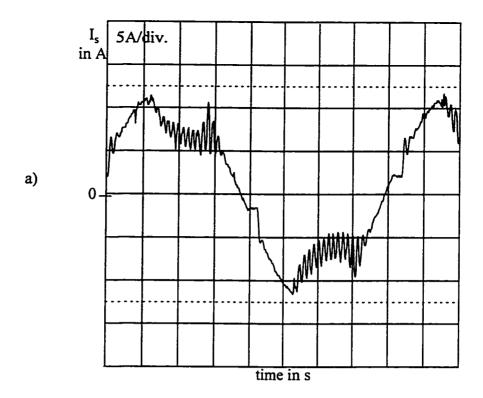

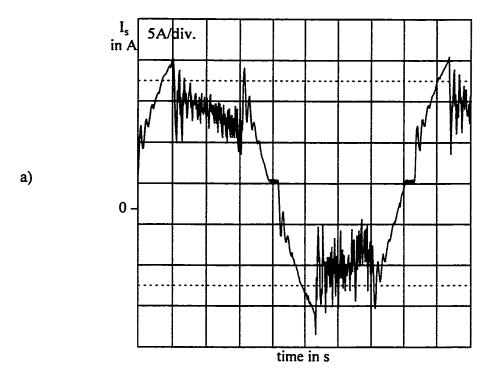

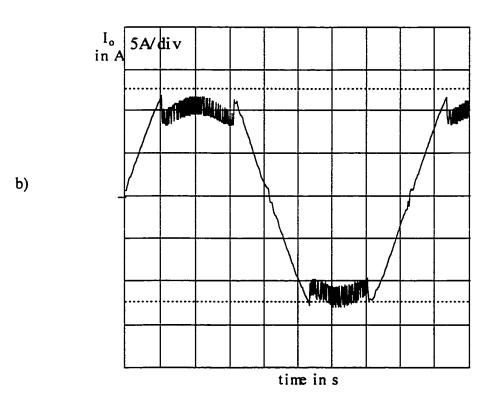

| Fig. 4.10 Operation of the hysteresis controller (experimental results)55                   |

| (a) Input current. (b) Load current (filtered). (c) Dc bus voltage. (d) Unfiltered          |

| inverter output voltage. (Hysteresis window $\Delta V_H = 5\%$ peak of reference,           |

| average switching frequency $f_{SW} = 40$ kHz, input voltage = 120 V, output voltage =  |

|-----------------------------------------------------------------------------------------|

| 90 V rms, rated output current = 10 A, resistive load.                                  |

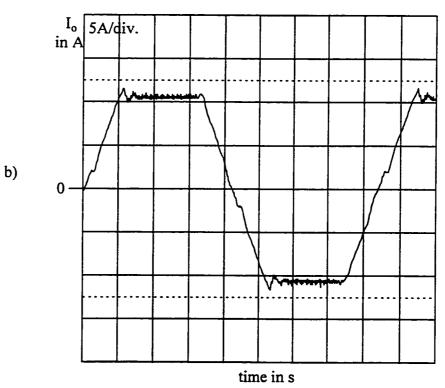

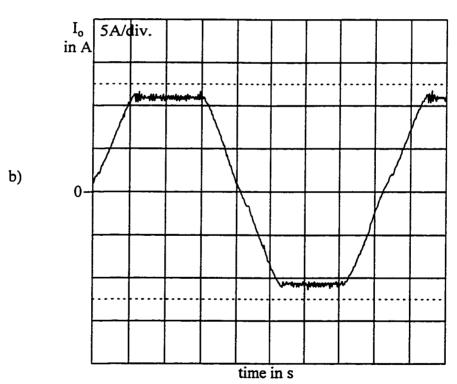

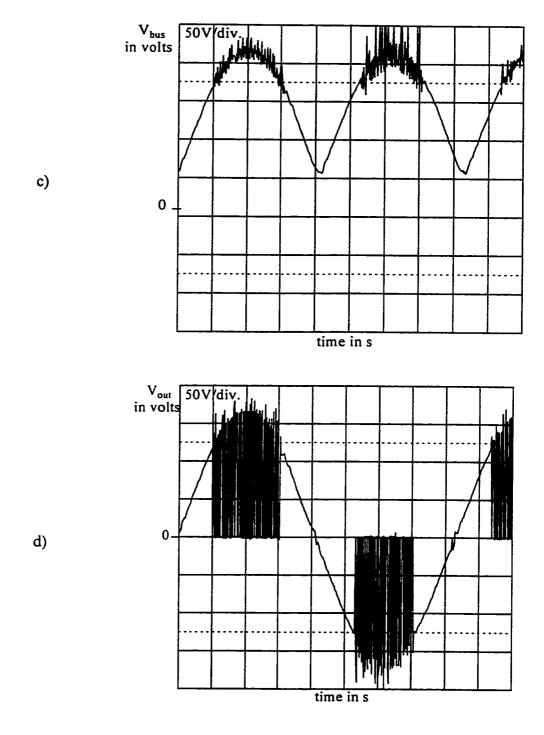

| Fig.4.11Operation of the Triangular Carrier -based integral PWM                         |

| controller (experimental results). (a) Input current. (b) Load current (filtered).      |

| (c) DC bus voltage. (d) Unfiltered inverter output voltage . ( Magnitude of the         |

| carrier = 20 V(peak to peak), average switching frequency $f_{SW}$ = 40 kHz, input      |

| voltage = 120 V rms, output voltage = 90 V rms rated output current = 10 amps,          |

| resistive load.                                                                         |

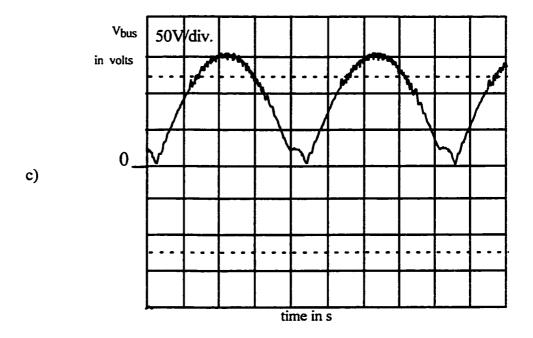

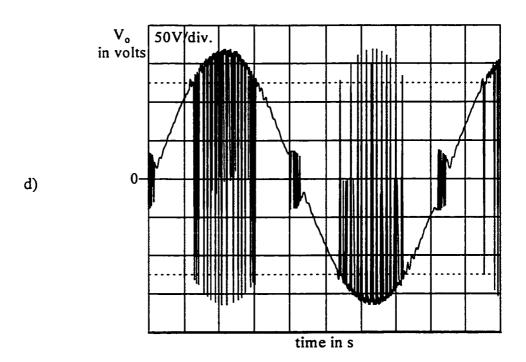

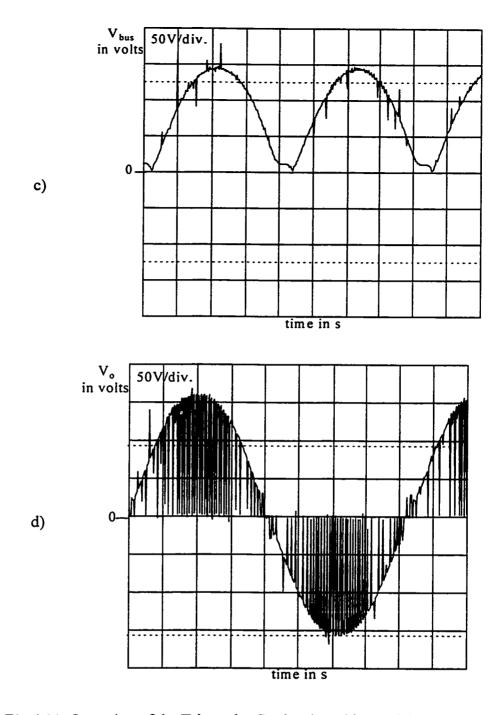

| Fig. 4.12 Operation of the Reset Integral PWM Controller (experimental results)59       |

| (a) Input current. (b) Dc bus voltage. (c) Inverter output voltage (unfiltered).        |

| (d) Output voltage (filtered). (Integrator gain = 25 $\mu$ s, average switching (clock) |

| frequency $f_{SW}$ = 40 kHz, input voltage = 120 V, output voltage = 90 V rated output  |

| current = 10 amps, resistive load).                                                     |

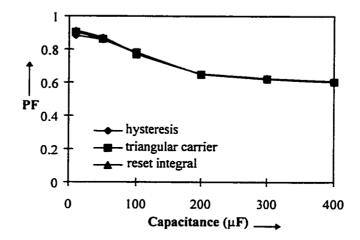

| Fig. 4.13 Effect of different capacitor values on input power factor for proposed61     |

| control techniques                                                                      |

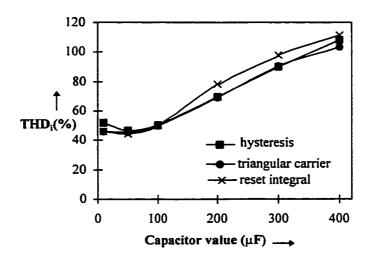

| Fig. 4.14 Effect of different capacitor values on total harmonic distortion for62       |

| proposed control techniques.                                                            |

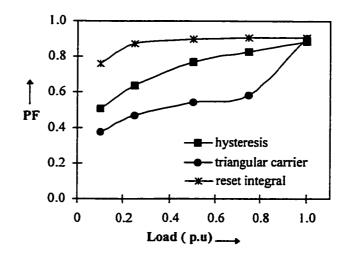

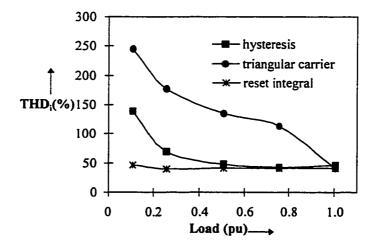

| Fig. 4.15 Effect of varying load on input power factor for proposed control63           |

| techniques.                                                                             |

| Fig. 4.16 Effect of varying load on input total harmonic distortion for proposed63      |

| control techniques.                                                                     |

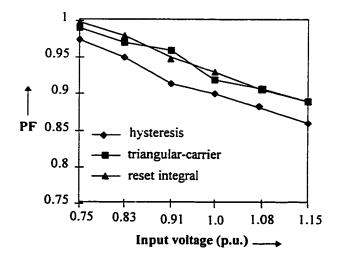

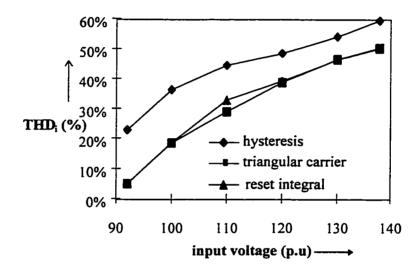

| Fig 4.17 Performance as a function of input voltage variation 64                        |

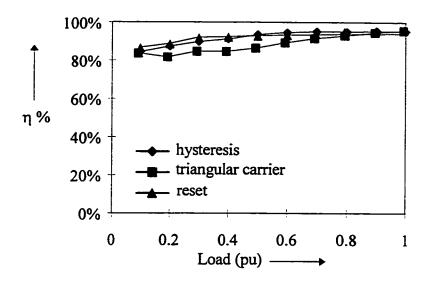

| supply65                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------|

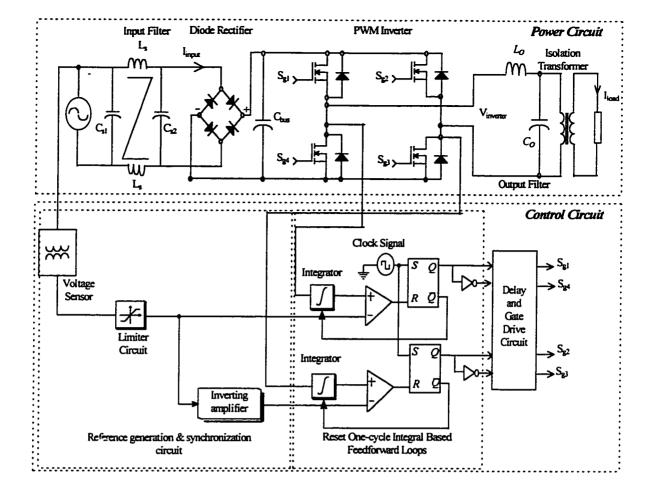

| Fig. 5.1 One-cycle Reset Integral PWM Controlled Sine Wave ac to Trapezoidal69                                          |

| Wave ac Power Supply.                                                                                                   |

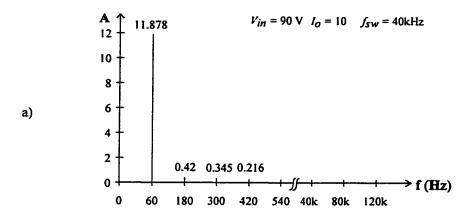

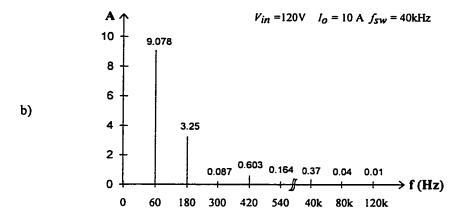

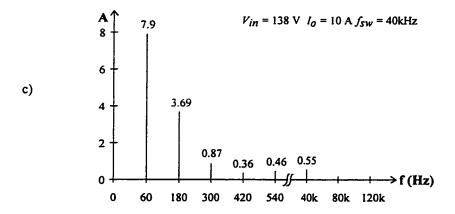

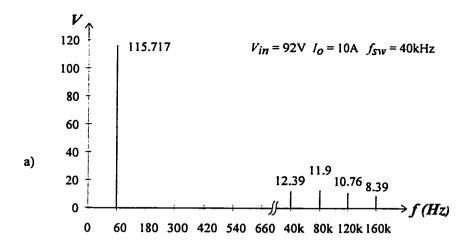

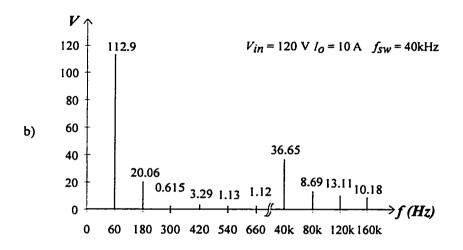

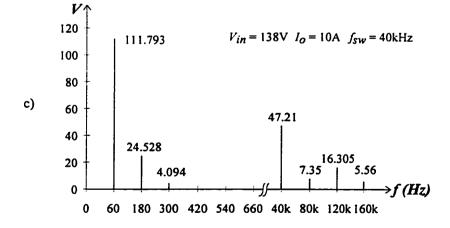

| Fig. 5.2 The harmonic spectrum of the input current at rated load for various72                                         |

| operating conditions at $f_{SW}$ = 40 kHz, $I_0$ =10 amps at (a) $V_i$ = 90 V (b) $V_i$ = 120 V                         |

| (c) $V_i = 138 \text{ V}.$                                                                                              |

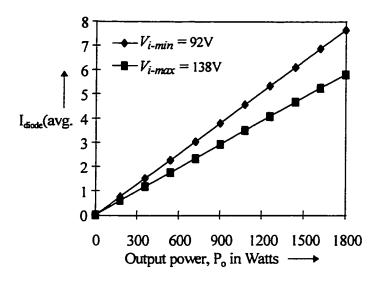

| Fig. 5.3 Variation of average current through the rectifier diodes as a function of73                                   |

| output power for minimum and maximum operating voltages ( $f_{SW} = 40 \text{ kHz}$ ,                                   |

| output voltage = 90 V, resistive load).                                                                                 |

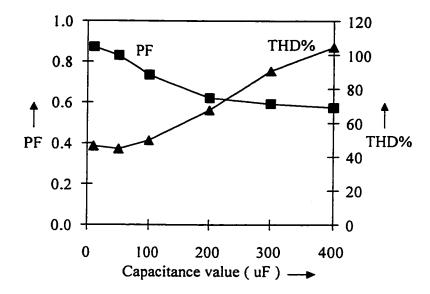

| Fig. 5.4 Performance of the proposed power supply as a function of dc capacitor74                                       |

| size (experimental results). (a) Power factor and Input current THD. ( $f_{SW} = 40 \text{ kHz}$ ,                      |

| input voltage = 120 V, output voltage = 90 V, output voltage = 90 V, resistive load).                                   |

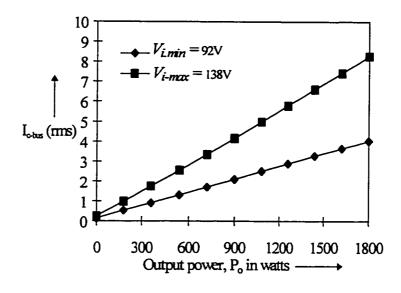

| Fig. 5.5 Variation of rms current through the dc bus capacitance as a function of75                                     |

| output power for minimum and maximum operating voltages. ( $f_{SW}$ = 40 kHz,                                           |

| output voltage = 90 V, resistive load).                                                                                 |

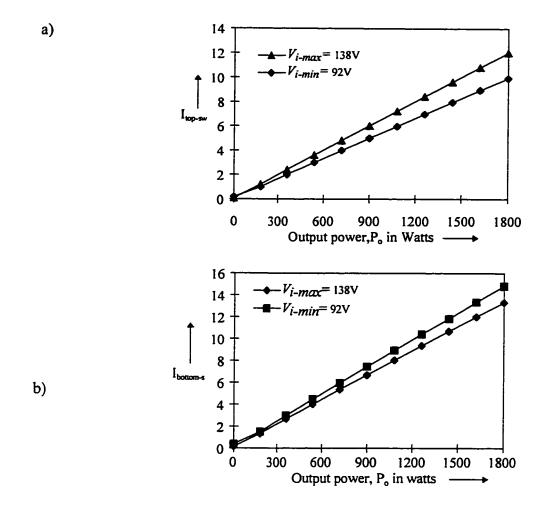

| Fig. 5.6 Variation of rms current through the MOSFETs of the full-bridge inverter77                                     |

| as a function of output power for minimum and maximum supply voltages.                                                  |

| $(f_{SW} = 40 \text{ kHz}, \text{ output voltage} = 90 \text{ V}, \text{ resistive load}).$ (a) current through the top |

| switches (b) current through the bottom switches.                                                                       |

Fig. 4.18 Effect of input voltage variation on the performance of the proposed power

Fig. 5.7 The harmonic spectrum of the output voltage at rated load for various.....78 operating conditions at  $f_{SW} = 40$  kHz,  $I_0=10$  amps at (a)  $V_i = 90$  V (b)  $V_i = 120$  V (c)  $V_i = 138$  V.

## **LIST OF TABLES**

| Table 1 Relative sizes of the input current harmonics in a typical ac/ac power sup  | pply |

|-------------------------------------------------------------------------------------|------|

| without power factor correction                                                     | 7    |

| Table II Theoretical limit - Input THD and power factor                             | 45   |

| (Switching function analysis, Average model, PWM switching neglected, resistive loa | d).  |

| Table III Harmonic contents of the output voltage of the bridge rectifier           | .47  |

| Table IV Harmonic contents of the output trapezoidal waveform of the full-bri       | idge |

| inverter                                                                            | .49  |

| Table V Harmonic contents of the input current drawn by the power supply            | .52  |

## **LIST OF ACRONYMS**

CATV cable television

DPF displacement power factor

EMI electromagnetic interference

mH milli Henry

MOSFET metal-oxide semiconductor field-effect transistor

P proportional

PF power factor

PI proportional integral

PWM pulse width modulation

rms root mean square

SW switch

THD total harmonic distortion

kW kilo watts

$\mu F$  micro farad

pu per unit

## LIST OF PRINCIPAL SYMBOLS

$\boldsymbol{C}$ capacitor, capacitance de bus capacitance  $C_{dc}$ output filter capacitor  $C_{\alpha}$  $C_{S_1}$ ,  $C_{S_2}$ high frequency capacitor Dduty cycle  $D_1$  to  $D_4$ diodes of the bridge rectifier maximum switching frequency fsw(max) dominant frequency  $f_{\rm r}$ input current drawn by the power supply  $i_i$  $I_1$ rms value of fundamental frequency current component  $I_{\varsigma}$ rms value of the total current  $I_{o}$ output load current diode current  $I_{diode}$  $k_{S}$ voltage sensor gain  $k_{r}$ measure of harmonic content of the input at dominant frequency Linductor, inductance LCsecond-order output filter  $L_o$ output filter inductor  $L_{S_1}$ input high frequency inductor input source inductance  $L_{\mathcal{S}}$  $P_o$ output power

$R_s$  input source resistance

$S_1$ ,  $S_2$ ,  $S_3$ ,  $S_4$  switches of the full-bridge inverter

$SW_{rect}$  switching function of the rectifier

$SW_{inv}$  switching function of the inverter

ton on-time of the switch

$T_{sw}$  switching time period

$T_i$  integrator time constant

$V_H$  hysteresis boundary voltage level

v<sub>int</sub> output voltage of the integrator

*v<sub>ref</sub>* reference voltage

$v_m$  modulated voltage

v<sub>e</sub> error voltage

V<sub>F</sub> feedback voltage

*v<sub>carr</sub>* carrier voltage waveform

v<sub>inv</sub> inverter output voltage

v<sub>i-min</sub> minimum input voltage

$v_{i-max}$  maximum input voltage

## **CHAPTER 1**

## INTRODUCTION

### 1.1 General

The cable-TV (CATV), consumer electronics and telecommunication industries are now entering the age of technology and business innovation to achieve new digital infrastructures. These infrastructures currently known as 'Information Superhighway', will be capable of providing a platform for a wide range of broadband, multimedia, entertainment, communication and information services. Power electronics is an integral part of these infrastructures and has been challenged to provide cost effective and reliable end-to-end power solutions.

In recent years, hybrid fiber/coax networks have emerged as a preferred approach for distributing multimedia services to the customer [1-2]. An attractive feature of these networks is in the use of coaxial cable for distributing reliable power to the customer [3].

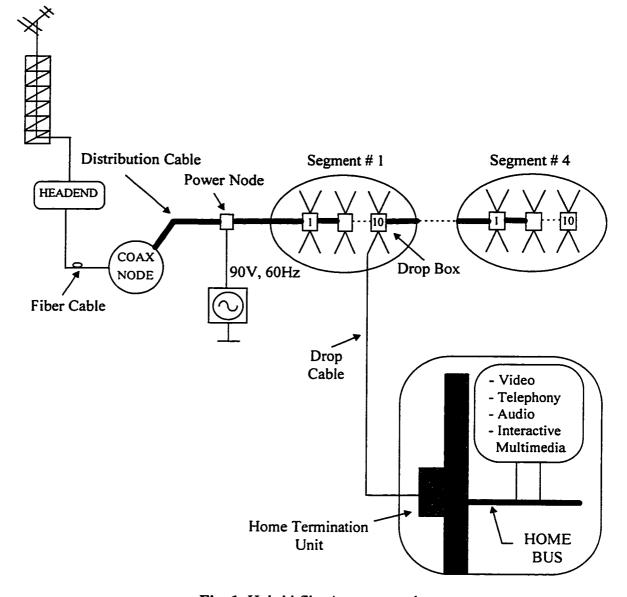

Fig. 1 shows a simplified diagram of a hybrid fiber/coax network. The headend typically serves a large area or a city. Bringing fiber optic line to home to provide broadband services is not economical. In the current architecture, video, telephony, audio and broadband signals are brought into a coax node over a fiber optic line. The optical signals are converted into electrical signals in the coax node, and are distributed to the homes using coax cable.

Fig. 1 Hybrid fiber/coax network.

Each headend in the network requires dc power which is obtained locally using ac/dc rectifiers. Powering the residential broadband (hybrid fiber/coax) network requires uninterrupted power to provide reliable telecommunication services [4,5].

Therefore, the requirements imposed for powering the hybrid fiber/coax system are [5]:

- (i) Uninterrupted power supply to all network elements

- (ii) Safe voltage distribution at the consumer end

- (iii) Low installation and maintenance cost

- (iv) High efficiency for minimum energy cost

- (v) Compatibility with existing network equipments.

Single phase ac power supplies are used to power hybrid fiber/coax networks. Unlike conventional ac/ac power supplies which generate sinusoidal shaped ac output waveform, the power supplies for hybrid fiber/coax networks are required to produce a trapezoidal-shaped waveform. This is based upon the fact that in order to transfer the maximum power to the network equipments at a given peak voltage and to have a low EMI, a trapezoidal waveform is better than a sinusoidal waveform [5].

The voltage level and frequency of network power distribution depends primarily on the following two factors:

- (1) Electrical safety of the people, and

- (2) Corrosion of distribution cables and connectors.

A good compromise which allows high enough safe voltage and frequency for low distribution power loss and corrosion is 90V at 60Hz [4-7].

Additional requirements of the power supplies include small size, high power factor (ideally 1), low total harmonic distortion (ideally 0) and high efficiency (ideally 100%) [8-10].

#### 1.2 Problem Definition

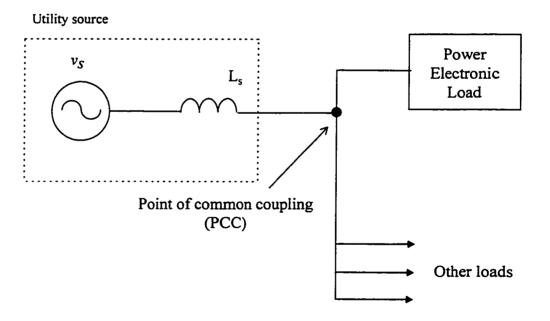

Conventional single phase ac/ac power supplies distort the utility waveform due to harmonic currents injected into the utility grid and produce electromagnetic interference. Fig. 2 illustrates the problems due to current harmonics in the input current drawn by a power electronic load from the utility source. Due to the finite internal impedance of the utility source, the distortion in the current waveform would result in the distortion of the voltage waveform at the point of common coupling to the other loads. This will cause the other loads to malfunction [8].

The power factor (PF) at which a power electronic load or an equipment such as a power supply operates is the product of the current ratio  $I_1/I_S$  and the displacement power factor (DPF):

$$PF = \frac{\text{real power}}{\text{apparent power}} = \frac{I_1}{I_s} \cdot DPF \tag{1}$$

In (1), the displacement power factor equals the cosine of the angle  $\phi_1$  by which the fundamental frequency component in the current waveform is displaced with respect to the input voltage waveform. The current ratio  $I_1/I_S$  in (1) is the ratio of the rms value of the fundamental frequency current component to the rms value of the total current [9].

It is observed from (1) that the power factor degradation is caused by current waveform distortion and/or phase displacement of the fundamental component of the

current with respect to the voltage. For the case when  $I_1/I_S = 1$  (i.e no distortion in the input current), and DPF < 1, only the component of current in phase with the input voltage contributes to the useful power delivered to the load but the total rms current determines the amount of line losses. Also, when the input current waveform is distorted, harmonic currents will be injected in the utility line. These injected harmonics contribute to the total rms current in the line which determines the amount of losses, but do not contribute to the useful power delivered to the load. Thus, both factors causing PF degradation, result in reduced efficiency and poor utilization of the utility source and line capacity [8-9].

Fig. 2 Utility interface

## 1.2.1 Conventional regulated ac/ac power supply without power factor correction

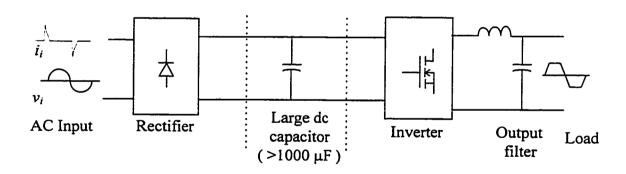

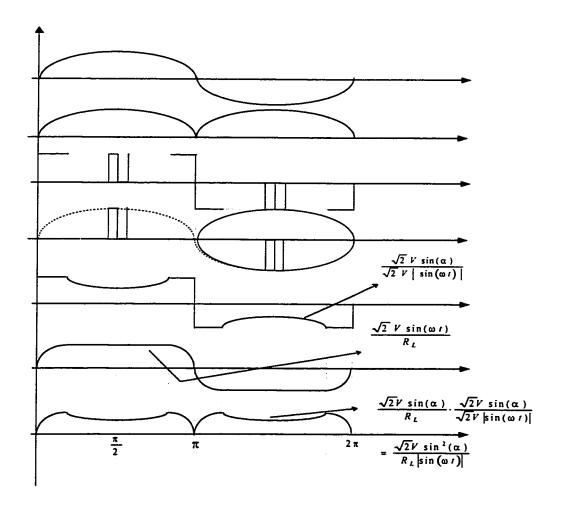

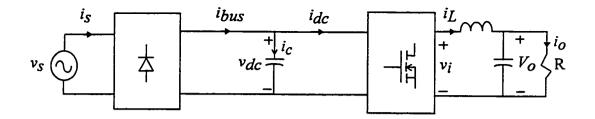

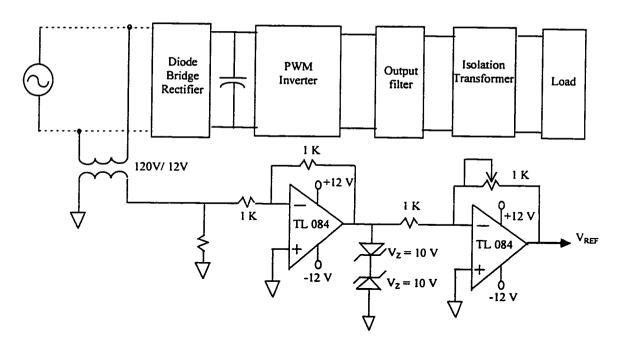

A conventional ac power supply structure for such applications, Fig. 3, consists of a front-end diode bridge rectifier, a large dc bus capacitor and a full-bridge PWM inverter. A front end diode bridge rectifier is utilized since it is rugged in nature, requires no external control and thereby reduces the cost in low and medium power applications. In operation, unregulated ripple free dc voltage is applied across the input of the PWM inverter. The PWM inverter converts this unregulated dc voltage into a regulated ac output voltage waveform of the desired shape [12].

In the simplest implementations, conventional open loop feedforward PWM techniques are utilized to control the duty-cycle of the inverter switches and produce the required output voltage [11].

Fig. 3 Conventional regulated ac/ac power supply without power factor correction

Although the conventional topology of Fig. 3 is simple, it has a severe drawback that the current drawn from the utility source is highly distorted and discontinuous, owing to the large capacitor connected at the output of the diode bridge rectifier. This results in very high current harmonics (>100% of the fundamental) in the input current and thus, a poor power factor (typically 0.5-0.6).

High input current distortion results in voltage distortion at the point of common coupling, which may affect other loads. Therefore regulations on power supply distortion have either been introduced, as in the case of IEC 1000-3-2 or recommended, as with the IEEE 519 standard. Power supplies such as the conventional one of Fig. 3 may therefore not meet the new requirements.

Table I shows the relative sizes of the input current harmonics in a typical ac/ac power supply without power factor correction (input voltage = 115 V rms, supply frequency = 60 Hz, having a dc bus capacitor greater than 1500 uF)

TABLE I

Relative sizes of the input current harmonics in a typical ac/ac power supply without power factor correction

| Harmonic number     | 3    | 5    | 7   | 9   | 11  | 13  | 15  | 17  |

|---------------------|------|------|-----|-----|-----|-----|-----|-----|

| $\frac{I_h}{I_l}$ % | 73.2 | 36.6 | 8.1 | 5.7 | 4.1 | 2.9 | 0.8 | 0.4 |

There are two different approaches to obtain a high input power factor at the input of these power supplies having a front end diode bridge rectifier [8]. One is by filtering harmonic currents at the interface with the utility. Passive input current waveshaping

methods use this approach. Passive methods have the obvious advantage of simplicity and reliability, but they cannot keep the current waveform independent of the load i.e., the input power factor can be optimized for only a narrow range of operating points [17]. The second approach is by preventing harmonic currents from being generated (or minimizing them). This approach is taken in active input current waveshaping techniques. Active methods provide possibility of using advanced control methods and can make the current waveform independent of the load [18-23].

## 1.2.2 Conventional regulated ac/ac power supply with power factor correction

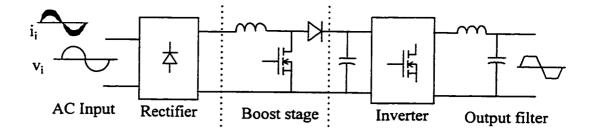

The common active method is to place a boost stage between the diode bridge rectifier and the PWM inverter. In this case, Fig. 4, the filtering capacitor is an integral part of the converter and is placed directly across the load.

To make the input power factor equal to unity, the input ac source should see a pure resistance when looking into the input terminals of the diode rectifier. This resistance is emulated by controlling the switch of the boost stage. The converter is so controlled that a sinusoidal current in phase with the input voltage is drawn by the rectifier.

Although power factor correction can be performed by using the buck and buck-boost converter, the most widely used topology for this purpose is the boost converter. A boost regulator is an excellent choice for the power stage of an active power factor corrector because the input current is continuous and this produces the lowest level of conducted noise and the improved input current waveform [9].

Fig. 4 Conventional regulated ac/ac power supply with power factor correction.

The boost regulator input current must be forced or programmed to be proportional to the input voltage waveform for power factor correction [10].

Fig. 4 shows an acceptable approach to waveshaping the input current. The boost stage forces the dc bus current to follow the waveshape of a full wave rectifier. This results in a sinusoidal input current with low THD (< 3%), with close to unity power factor (> 0.98).

The disadvantages of this type of power factor corrector are: (i) reduced conversion efficiency due to the additional power conversion stage and (ii) increased cost.

## 1.3 Proposed topology

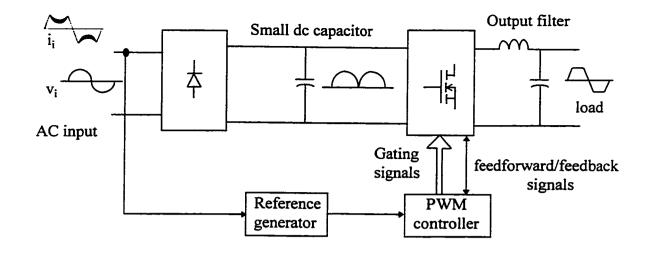

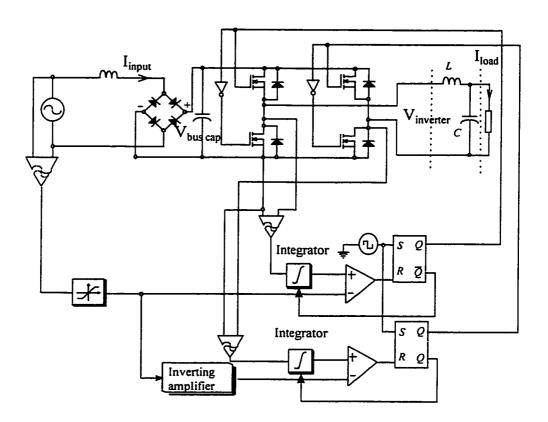

This thesis presents and analyzes a 60 Hz ac to 60 Hz trapezoidal ac converter topology that requires neither a boost stage nor a large dc capacitor [24-27].

The main features of the proposed topology include: (a) a small dc bus capacitor, the presence of the 120 Hz ripple being exploited in the control scheme; this choice reduces both overall weight and cost; (b) an on-line instantaneous voltage controlled

Fig. 5 Proposed power supply topology.

pattern generator synchronized with the dc ripple; this yields an increased dc bus utilization; (c) the input current drawn from the ac source is continuous and the fundamental component is in phase with the voltage; the THD of the input current is low (< 50%) and the resulting power factor is high (>0.9).

## 1.4 Scope and contribution of this thesis

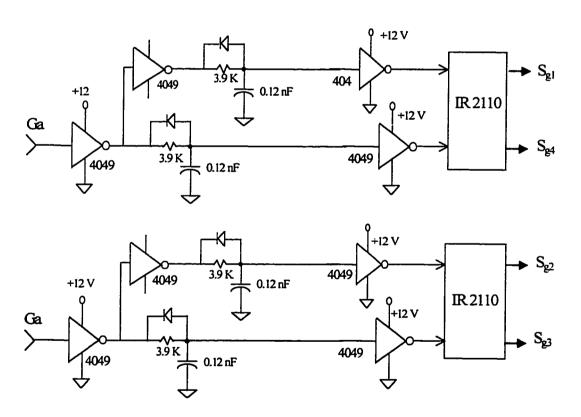

Single phase sinusoidal ac to trapezoidal ac power supply based on a novel single stage topology is implemented using the three PWM pattern generation and control schemes, namely (a) Hysteresis integral control (b) Triangular-carrier integral control, and (c) One-cycle integral control [25]. The focus of this thesis is on the PWM pattern generation and control schemes required to produce a trapezoidal output voltage for the proposed topology of Fig. 5 and their effect on input power factor and harmonic

distortion. A performance based comparison of these PWM techniques is done on a 900 VA laboratory prototype in terms of power factor (PF), Total Harmonic Distortion (THD) and efficiency  $(\eta)$ .

Average switching function analysis [39], which utilizes the concept of transfer function, is used to provide quantitative explanation of power supply waveforms. Furthermore, this analysis also establishes the theoretical limits to power factor and input harmonic distortion of each technique.

Also detailed design procedure for selecting and rating the components of the power supply based on One cycle or Reset integral control technique [38] is described.

The feasibility of the proposed power supply is exhibited and quantified through computer simulation on the PECAN software package [41-42]. Experimental results are obtained on laboratory prototypes comprising of MOSFET-based full bridge PWM inverter topology. The control circuits are designed using state-of-the-art analog and digital devices.

#### 1.5 Outline of the thesis

The contents of the thesis have been organized as follows:

Chapter 2 identifies an output voltage integral duty-cycle control based on which three modified feedforward/ feedback PWM pattern generation and control techniques-Hysteresis integral control, Triangular-carrier integral control and One-cycle integral control are derived. Different modes of the PWM inverter controlled by various techniques are identified.

In Chapter 3 the implementation aspects of the three schemes are discussed. Procedure for selection of parameters is given. A design example illustrates the selection of various power and control circuit components. Key simulation results are shown.

Chapter 4 presents generalized average switching function analysis. It further compares the performance of the three schemes in terms of the effect on input power factor and THD as a function of load, input dc bus capacitor and input line voltage. Experimental results are presented.

Chapter 5 presents design guidelines for the power circuit components of the proposed power supply based on Reset integral PWM control scheme.

Chapter 6 concludes the thesis and identifies some areas for future research work.

## **CHAPTER 2**

# PWM PATTERN GENERATOR AND CONTROL TECHNIQUES FOR THE POWER SUPPLY

## 2.1 Introduction

As discussed in the last chapter, single phase ac power supplies are used to power hybrid/coax cable networks. These power supplies are required to generate 90 V, 60 Hz trapezoidal shaped voltage waveform. An ideal trapezoidal shaped voltage waveform would have sharp rising and falling edges resulting in substantial amount of EMI generation [8]. Alternatively, 60 Hz trapezoidal shaped voltage waveform can be obtained without generating excessive EMI by simply flattening the top and bottom of the curved peaks of a 60 Hz pure sinusoidal waveform. That is, the flatting operation is performed only on the peaks of an otherwise sinusoidal voltage waveform. This type of shaping of the pattern is done using pulse-width-modulation (PWM) [12]. Besides the operation as a voltage controlled PWM pattern generator, these power supplies have to maintain 90 V rms, 60 Hz trapezoidal shaped voltage against all the source voltage and load power variations. Therefore control techniques for these voltage controlled PWM pattern generators have to be developed for the proposed power supply.

The objective of this chapter is to develop the voltage controlled PWM pattern generators and control techniques based on the integral duty cycle control. In this chapter three PWM pattern generators and control techniques- Hysteresis integral PWM control, Triangular-carrier integral PWM control and One-Cycle or Reset integral PWM control are derived and their hardware implementation is presented. Principle of operation of each scheme is explained. Modes of operation of the converter based on the proposed schemes are illustrated. Design details of the control loop and power circuit are discussed in subsequent chapters of the thesis.

## 2.2 Hysteresis Integral PWM Control Technique

Hysteresis, also known as bang-bang technique, is a widely used control method. This technique is based on the integral duty cycle control. The principle of operation of this PWM generation and control technique is illustrated. The hardware implementation of single phase trapezoidal ac/ac power supply based on this technique is described. Modes of operation of the converter based on this technique are also discussed.

## 2.2.1 Principle of operation

Hysteresis control is a well known and rugged technique [28-32]. It provides tight regulation of the control variable with a simple comparator circuit. Dynamic response is fast, however switching frequency varies over one cycle as well as with operating conditions [30].

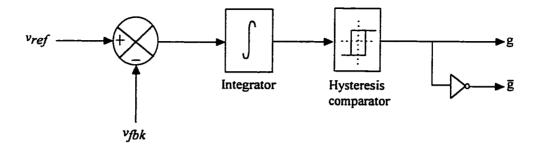

Fig 2.2 Pattern generator based on Hysteresis integral PWM control

In Fig. 2.2, the generalized pattern generator based on hysteresis integral control technique is shown. The output voltage of the converter before the LC filter stage is sensed with a voltage sensor and is fedback. This fedback voltage (vfbk) is compared with the reference voltage signal by an error amplifier. The output of the error amplifier i.e. the error is integrated using a real-time integrator. The integrated error is fed to the comparator circuit which is based on the principle of hysteresis.

### 2.2.2 Implementation aspects

The implementation of hysteresis control for the proposed topology is illustrated in Fig. 2.3. The purpose of the PWM generator and control circuit is to maintain the average volt-sec of the output voltage over one switching cycle equal to the trapezoidal reference. Therefore the unfiltered instantaneous inverter output voltage pattern is sensed and fedback to be compared to the trapezoidal reference. The error generated due to this comparision is fed to an integrator which improves the tracking of the feedback signal with the reference signal. The controlled voltage (i.e. the average integrated error)

Fig. 2.3 Hysteresis-based PWM controller.

remains within a window, whose size is a design parameter and fixes the maximum ripple of output voltage. Whenever the average error voltage hits one of the top or bottom boundaries, the inverter changes the mode of operation.

## 2.2.3 Modes of operation

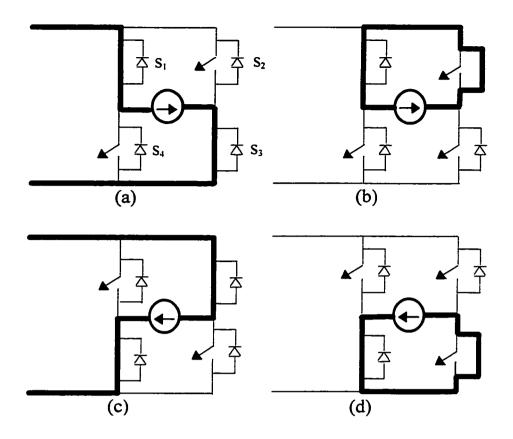

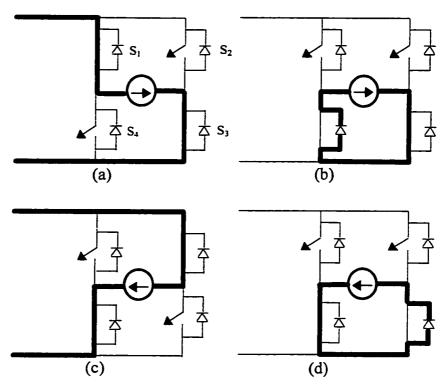

The modes of operation of the PWM inverter illustrated in Fig. 2.4 display the sequence of gating of switches of the inverter controlled by hystersis control. During the positive half of the trapezoidal reference, the switches S<sub>1</sub> and S<sub>3</sub> are gated simultaneously forcing the current to flow in positive direction through the load.

**Fig. 2.4** Modes of Operation of the PWM inverter based on the hysteresis integral PWM control. (a) operation of the inverter for positive half-cycle of the trapezoidal reference. (b) operation of the inverter for negative half-cycle of the trapezoidal reference.

During the negative half of the trapezoidal reference, switches  $S_2$  and  $S_4$  are gated simultaneously, forcing the current through the load in opposite direction as shown in Fig. 2.4(b). As it can be observed, all the four switches carry the same rms current.

## 2.3 Triangular-Carrier Integral Control

This technique [31-35] is also based on the output voltage integral duty cycle control. The principle of operation of this PWM pattern generation and control technique is illustrated. The hardware implementation of single phase trapezoidal ac/ac power supply based on this technique is described. Modes of operation of the converter based on this control technique are also discussed.

#### 2.3.1 Principle of operation

The basic loop is identical to the hysteresis controller, Fig.2.6. However, the switching frequency is stabilized by means of triangular carrier [35]; the integrated error is intersected with the carrier and the intersections define switching instants of the converter. Inverter switching frequency is constant and equal to the carrier frequency. Since this is the case, design is simpler than that of the hysteresis controller.

In Fig. 2.6, the generalized pattern generator based on triangular-carrier integral control technique is shown. The reference voltage is compared with the feedback voltage by an error amplifier. The error generated is integrated using a real-time integrator.

This integrated error or the modulating waveform is superimposed or compared with a triangular carrier waveform. When the modulating waveform is equal to the carrier waveform, switching occurs i.e. the intersections of the two waveforms generates the gating signals. The frequency of the carrier decides the switching frequency of the inverter.

Fig. 2.5 Pattern generator based on Triangular-carrier integral PWM control.

#### 2.3.2 Implementation aspects

The implementation of triangular-carrier integral control for the proposed topology is illustrated in Fig. 2.5. The purpose of the PWM generator and control circuit is to maintain the average volt-sec of the output voltage over one switching cycle to the trapezoidal reference. Therefore the instantaneous inverter output voltage pattern (unfiltered) is sensed and fedback. This fedback signal is compared to the trapezoidal reference. The error generated is fed to an integrator which improves the tracking of the feedback signal with the reference signal. This integrated error or the modulated waveform is further stabilized with a triangular carrier waveform. The output of the comparator i.e. the gating signals are fed to the top and the bottom switches of the left leg of the PWM inverter. The intregrated error is inverted and then compared with the carrier waveform, the gating signals generated in such a way are fed to the top and bottom switches of the right leg of the inverter.

#### 2.3.3 Modes of operation

The modes of operation of the PWM inverter illustrated in Fig. 2.7 display the sequence of gating of switches of the inverter controlled by the proposed control technique. During the positive half of the trapezoidal reference, the switches  $S_1$  and  $S_3$  are gated simultaneously forcing the current to flow in positive direction through the load, Fig. 2.7(a), this is followed in the next interval by turn-off of  $S_3$  and simultaneously turn-on of  $S_2$ . During this interval, Fig. 2.7(b), the current follows the same direction through the load but now  $S_3$  and the integral diode of switch  $S_4$  starts to conduct.

Fig. 2.6 Triangular-carrier based PWM integral control.

These modes of operation are sequentially repeated throughout the positive half cycle of trapezoidal reference.

During the negative half of the trapezoidal reference, switches  $S_2$  and  $S_4$  are gated simultaneously, forcing the current through the load in opposite direction as shown in Fig. 2.7(c). In the next interval,  $S_2$  turns-off and integral diode of  $S_3$  starts to freewheel to maintain the current in the same direction as displayed in Fig. 2.7(d). These two intervals are repeated throughout the negative half of trapezoidal reference.

As it can be observed, the lower switches  $S_3$  and  $S_4$  carry higher rms current as compared to the upper switches  $S_1$  and  $S_2$ , of the two legs of the PWM inverter.

Fig. 2.7 Modes of Operation of the PWM inverter based on the Triangular-carrier integral control. (a) and (b) represent operation of the inverter for positive half-cycle of the trapezoidal reference. (c) and (d) depict the operation of the inverter for negative half-cycle of the trapezoidal reference.

## 2.4 One Cycle or Reset Integral Control Technique

Reset integral control also known as the one-cycle control [34][35][38], forces the average value of the switched variable to follow a dynamic reference within one cycle. The duty-ratio of the switch is controlled such that in each cycle the average value of the switched variable of the switching circuit is exactly equal to or proportional to the control reference, both in the steady and the transient state. It rejects power source perturbations

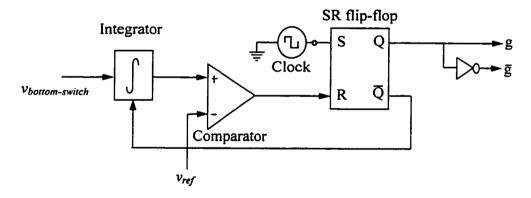

#### 2.4.1 Principle of operation

Fig. 2.8 shows the generalized pattern generator based on One-cycle Integral PWM control. The dc bus voltage is sensed across the bottom switch and is integrated by a resettable integrator. The integrated output voltage  $(v_{int})$  is compared with the reference voltage signal  $(v_{ref})$  by the comparator. When integrated voltage  $v_{int}$  hits the reference voltage  $v_{ref}$ , the integrator is reset (goes low) and the switch across which the voltage is sensed, turns ON hence applying zero voltage across the integrator. When the clock sets the flip-flop (Q goes high), the switch is turned OFF and the sensed voltage is applied to the integrator. The clock fixes the switching frequency of the pattern generator.

Fig. 2.8 Pattern generator based on One-cycle integral PWM control

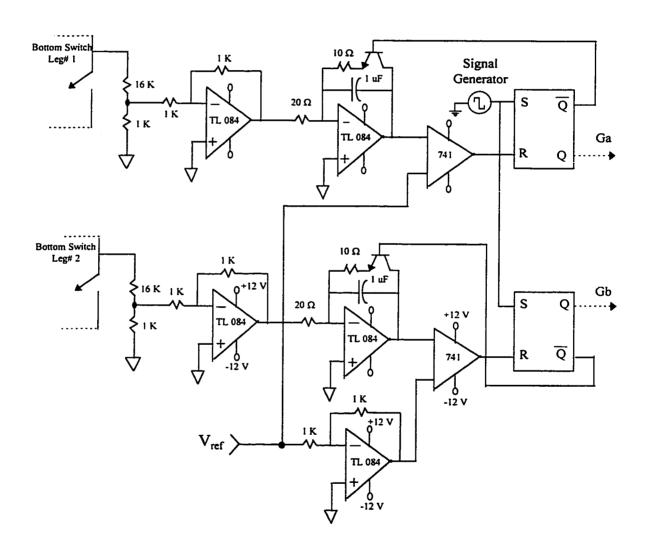

### 2.4.2 Implementation aspects

The implementation of One cycle integral PWM control for the proposed topology is illustrated in Fig. 2.9. The ac mains voltage is directly sensed from the single-phase ac

mains supply and passed through a limiter circuit to generate a trapezoidal-shaped reference signal. By generating the reference signal in such a manner, the trapezoidal-shaped reference is in phase and synchronized with the 120 Hz dc bus ripple. That is the zero-crossing of this reference signal corresponds to the zero-crossing of the dc bus ripple voltage.

The control circuit further consists of two feedforward loops based on One cycle Reset integral control principle. Each consists of a Reset Integral PWM control block which further consists of a real-time resettable integrator, a comparator, a clock, and S-R flip-flop. The output of the clock signal is tied to the SET option of the two flip-flops. The PWM gating signals generated by the upper controller block is complementary fed to the two switches of the left leg of the full-bridge inverter whereas the output of the lower PWM controller is fed to the two switches of the right leg of the full-bridge inverter.

The proposed simple on-line pattern generator based on cycle by cycle control of output voltage has a closed loop structure and requires sensing of the instantaneous value of the voltage across the bottom switches. This voltage is applied to a resettable real-time integrator. The integrated output is compared to a trapezoidal-shaped reference. As it reaches the reference during a cycle, the integrator is reset and the bottom switch is turned on. Similar operation is exhibited by the lower loop, the only difference is that the integrator output is compared with a trapezoidal reference which is inverted (180 degrees phase shift).

With this type of implementation, the upper loop (with a trapezoidal-shaped reference) controls the duty-cycle of the left leg of the full-bridge inverter during the first

half period and the lower loop (with an inverted trapezoidal-shaped reference) controls the duty-cycle of the right leg of the full bridge inverter during the remaining half period of the trapezoidal reference.

Fig. 2.9 One-cycle Reset Integral PWM controller.

## 2.4.3 Modes of operation

The modes of operation of the PWM inverter illustrated in Fig. 2.10 displays the sequence of gating of switches of the inverter controlled by the proposed topology. During the positive half of the trapezoidal reference, the switches  $S_1$  and  $S_3$  are gated

simultaneously forcing the current to flow in positive direction through the load, Fig. 2.10(a), this is followed in the next interval by turn-off of  $S_1$  and simultaneously turn-on of  $S_4$ . During this interval, Fig. 2.10(b), the current follows the same direction through the load but now  $S_3$  and the integral diode of switch  $S_4$  starts to conduct. These modes of

Fig. 2.10 Modes of Operation of the PWM inverter based on the reset integral control.

(a) and (b) represent operation of the inverter for positive half-cycle of the trapezoidal reference. (c) and (d) depict the operation of the inverter for negative half-cycle of the trapezoidal reference.

operation are sequentially repeated throughout the positive half cycle of trapezoidal reference.

During the negative half of the trapezoidal reference, switches  $S_2$  and  $S_4$  are gated simultaneously, forcing the current through the load in opposite direction as shown in Fig. 2.10(c). In the next interval,  $S_2$  turns-off and integral diode of  $S_3$  starts to freewheel maintain the current in the same direction as displayed in Fig. 2.10(d). These two intervals are repeated throughout the negative half of trapezoidal reference. As it can be observed, the lower switches  $S_3$  and  $S_4$  carry higher rms current as compared to the upper switches  $S_1$  and  $S_2$ , of the two legs of the PWM inverter.

#### 2.5 Conclusions

In this chapter three PWM pattern generation and control strategies based on voltage integral control with their block diagram implementation are presented for a single phase trapezoidal ac power supply. The principle of operation of each control scheme is explained. Modes of operation of the PWM inverter based on various PWM pattern generation and control strategies is illustrated.

## **CHAPTER 3**

# **CONTROL LOOP DESIGN**

#### 3.1 Introduction

In the previous Chapter, the principle of operation of the three PWM pattern generation and control techniques have been presented. In hysteresis based control technique, the error generated due to the comparison of reference and feedback voltages is averaged using a real-time integrator and then limited within a boundary by controlling the duty-cycle of the switches of the inverter. In triangular-carrier based control technique, the generated error is averaged using a real-time integrator and then limited within a boundary established by a triangular-carrier waveform. The switching frequency is stabilized by the carrier. In reset control technique, the integrated sensed voltage is compared with the trapezoidal reference in each cycle and error generated controls the gating signals applied to the switch.

Therefore in all three PWM pattern generation and control techniques, the heart of control loop is the real-time integrator as it provides better tracking of output voltage with the reference waveform. Therefore the selection of the proper time constant of the integrator is a crucial design parameter.

In this Chapter, design guidelines for the selection of integrator time constant are presented for all the three control techniques. Further, the key simulation waveforms are also presented.

#### 3.2 Hysteresis PWM integral control technique

Hysteresis control is a well known and rugged technique [29]. It provides tight regulation of the control variable with a simple comparator circuit. Dynamic response is fast, however switching frequency varies over one cycle as well as with operating conditions [30].

The implementation of hysteresis control for the present application had been illustrated in Fig. 2.3. The purpose of the PWM pattern generator and control circuit is to maintain the average volt-sec of the output voltage over one switching cycle equal to the trapezoidal reference. Therefore, the instantaneous inverter output voltage is measured, compared to the trapezoidal reference and the integrated error, or average error is maintained within a hysteresis band by switching upper and lower switches. The two legs of the inverter are operated in a complementary fashion (diagonal switches are gated simultaneously).

## 3.2.1 Design guidelines for the control loop

Design of the controller involves the choice of hysteresis band and integrator time constant. However, the accuracy of the output voltage tracking is essentially dependent upon the switching frequency. Therefore, hysteresis band and integrator time constant can

Fig. 3.1 Waveforms representing a specific period of operation of the converter based on hysteresis based controller. (a) reference trapezoidal waveform. (b) feedback voltage signal. (c) error voltage signal. (d) integrated error waveform. (e) gating signal generated at the output of the comparator.

be used to control the switching frequency.

From the Fig. 3.1, it can be observed that,

$$\frac{1}{T_i} \int_{0}^{DT_{SW}} (V_R - V_F) dt = -2V_H$$

(3.1)

And,

$$\frac{1}{T_i} (V_R - V_F) DT_{sw} = -2V_H \tag{3.2}$$

the duty cycle can be defined as,

$$D = \begin{cases} = \frac{V_R}{V_F} & V_F > V_R \\ 1 & V_F < V_R \end{cases}$$

(3.3)

Further from the waveform of  $V_e$ , it can be observed that when the feedback voltage is less than the reference voltage, the switch is always ON ie. D=1. When the feedback voltage is greater than the reference voltage, the duty cycle is equal to  $\frac{V_R}{V_F}$ .

$$\frac{1}{T}(V_R - V_F) \frac{V_R}{V_F} T_{sw} = -2V_H$$

(3.4)

Therefore,

$$T_{sw} = \frac{2V_H T_i V_F}{\left(-V_R + V_F\right) V_R} \tag{3.5}$$

Maximum switching frequency,

$$f_{sw(max)} = \frac{V_R}{2V_H T_i}$$

(3.6)

Maximum switching frequency for  $V_{fmax}$ ,

$$\frac{V_R(V_{F\max} - V_R)}{2V_H T_i V_{F\max}} = f_{sw(\max)}$$

(3.7)

Fig. 3.2 Variation of feedback voltage with the switching period.

It was found that given an average switching frequency, a hysteresis band of 5% of the peak of the trapezoidal waveform, together with an integrator time constant equal to 0.5 of the average switching period, resulted in good tracking.

## 3.2.2 Simulated results

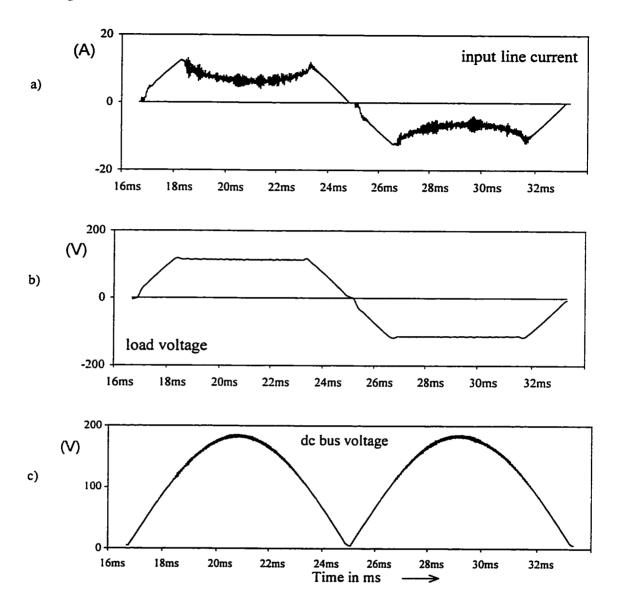

Simulated waveforms for input line current, load voltage and dc bus voltage for the proposed power supply based on Hysteresis integral PWM control are shown in the Fig. 3.2.

## 3.3 Triangular-Carrier Integral Control

The basic loop is identical to the hysteresis controller [33]. However, the switching frequency is stabilized by means of triangular carrier; the integrated error is

Fig. 3.3 Operation of the hysteresis based PWM controller (simulated results). (a) Input current. (b) Load voltage (filtered). (c) Dc bus voltage. (Hysteresis window  $\Delta V_H = 5\%$  peak of reference, average switching frequency  $f_{SW} = 40$  kHz, input voltage = 120 V, output voltage = 90 V rms, rated output current = 10 A, resistive load).

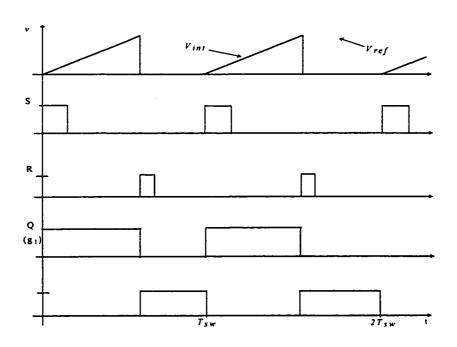

intersected with the carrier and intersections define switching instants, Fig. 3.4. Inverter switching frequency is constant and equal to the carrier frequency. design is simpler than

Fig. 3.4 Control waveforms for triangular-carrier integral control technique

that of the hysteresis controller [35].

## 3.3.1 Design guidelines for the control loop

The key design parameter of the control loop is the integrator time constant  $T_i$ . The time constant should be small enough to achieve a fast response, but large enough to maintain proper PWM operation [29]. The constraint is that the slopes of the modulation waveform  $v_m$  should be smaller than those of the carrier waveform  $v_{carr}$ . The maximum

falling slope of  $v_m$  occurs when the reference voltage  $v_{ref}$  is at the maximum and the inverter voltage  $v_{inv}$  is zero, i.e.

$$S_f = \frac{V_{ref,\text{max}}}{T_i} \tag{3.8}$$

The maximum rising slope of  $V_m$  occurs when the difference between  $v_{int}$  and  $v_{ref}$  at the maximum. This corresponds to the peak of the sine wave, i.e.

$$S_r = \frac{V_{fbk,peak} - V_{ref,max}}{T_i} \tag{3.9}$$

On the other hand, the rising and falling slopes of the carrier waveform are equal to  $4V_c/T_{sw}$  where  $V_c$  is the peak amplitude of the carrier and  $T_{sw}$  is the switching period.

The slope constraints are:

$$\frac{V_{ref.max}}{T_i} < \frac{4 V_c}{T_{sw}} \tag{3.10}$$

and

$$\frac{V_{fbk,peak} - V_{ref.max}}{T_i} < \frac{4 V_c}{T_{min}}$$

(3.11)

According to (3.10) and (3.11), and assuming  $V_c = 1$  and a voltage sensor gain of 1.0, the integrator time constant is 110  $\mu$ s. To provide a safety margin, particularly in view of the dc bus fluctuations, a value of 150  $\mu$ s is chosen for  $T_i$ .

#### 3.3.2 Simulated results

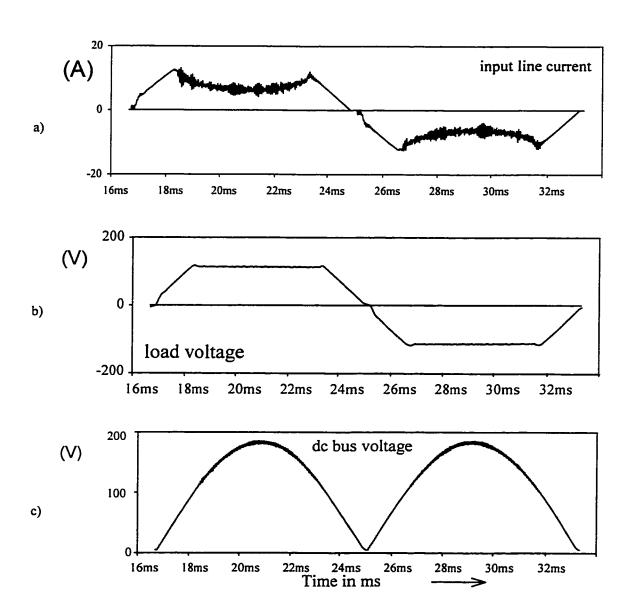

Simulated waveforms for input line current, load voltage and dc bus voltage for the proposed power supply based on triangular-carrier integral PWM control are shown in the Fig. 3.5.

Fig. 3.5 Operation of the Triangular Carrier-based integral PWM controller (simulated results). (a) Input current. (b) Load voltage (filtered) (c) DC bus voltage. (Magnitude of the carrier = 20 V (peak to peak), average switching frequency  $f_{SW} = 40$  kHz, input voltage = 120 V rms, output voltage = 90 V rms rated output current = 10 amps, resistive load).

The error triangulation method provides instantaneous waveshaping resulting in very fast response and has the advantage of constant switching frequency. This simplifies input filter design.

## 3.4 Reset Integral control

Reset integral control, Fig.2.9, also known as the One-cycle control, forces the average value of the switched variable to follow the reference within one cycle. The technique rejects power source perturbations and corrects switching delays if the dc bus voltage is measured at the inverter output [38].

## 3.4.1 Design guidelines for the control loop

The on time of the switch is controlled by the rate of integration, dependent on the input voltage and integrator time constant and the control voltage  $V_{ref}$ . It can be

Fig. 3.6 Control waveforms for one-cycle reset PWM integral control technique.

computed from the following equation:

$$\frac{1}{T_i} \int_0^{t_{on}} v_{sw} = v_{ref} \tag{3.12}$$

where,  $v_{sw}$  the voltage across the switch, the  $v_{ref}$  control reference voltage and  $T_i$  the integrator time constant.

The switch voltage  $v_{sw}$  can be represented by

$$v_{sw} = v_{dc} + k_r \cdot v_{dc} \sin(2\pi f_r t)$$

(3.13)

where  $k_r$  is the measure of the harmonic content of the input at the dominant frequency  $f_r$ .

The integrator output is given by:

$$v_{int} = \frac{k_s v_{sw} t}{T_i} \tag{3.14}$$

where  $k_s$  is voltage sensor gain.

The design procedure involves choosing the integrator to integrate the switch voltage to the value of the reference voltage, corresponding to the duty cycle D=1 in one switching period. Constraints are satisfied for a given integrator time constant when:

$$\frac{k_s v_{dc} (1 - k_r) T_{sw}}{T_i} = v_{ref}$$

(3.15)

Rearranging the above equation, we have

$$(1-k_r) v_{ref,max} = v_{ref} (3.16)$$

From the equations above, with  $v_{sw} = 120\sqrt{2}$  volts,  $v_{ref} = 90$  V rms and switching frequency = 40 kHz, the integrator time constant is derived equal to 20  $\mu$ s.

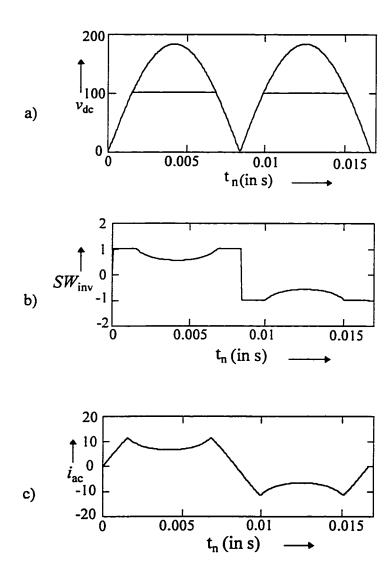

#### 3.4.2 Simulated results

Simulated waveforms for input line current, load voltage and dc bus voltage for the proposed power supply based on reset integral PWM control are shown in the Fig. 3.7.

Fig. 3.7 Operation of the Reset Integral PWM Controller (simulated results) (a) Input current (c) output voltage (filtered) (c) DC bus voltage. (Integrator gain =  $20 \mu s$ , switching (clock) frequency  $f_{SW} = 40 \text{ kHz}$ , input voltage = 120 V, output voltage = 90 V, rated output current = 10 A, resistive load).

# 3.5 Conclusions

In this chapter, the design of the control loop for all the three control techniques has been illustrated. The design equations have been derived to select a proper time constant of the integrator which is a crucial design parameter of the control loop for the three control techniques. Key simulation waveforms obtained validate the selection of the appropriate value of the integrator time constant.

## **CHAPTER 4**

# ANALYSIS AND PERFORMANCE COMPARISON OF THE THREE CONTROL SCHEMES

#### 4.1 Introduction

As discussed, the selection of the size of the dc bus capacitor for the power supply is based on a trade-off between two conflicting requirements. One being the input current distortion as a function of dc bus capacitor value and the other is the filtering provided by this capacitor to the reflected high frequency current harmonics, generated due to the PWM inverter. Since the dc capacitor is small, it does not provide a buffer between ac and dc sides, therefore, the shape of the output voltage and current affect the ac input current drawn by the power supply.

In order to examine this interaction, an analysis based on the average switching function is proposed, the switching frequency components being neglected. The analysis uses the concept of transfer characteristics. In addition to giving a quantitative explanation of the power supply waveforms, the switching function analysis also establishes the theoretical limits to power factor and input harmonic distortion, assuming the inverter switching frequency is high and can be eliminated by means of a small low-pass filter. Further in this chapter, a performance comparison of three PWM pattern

generation and control techniques is presented. The performance features are compared based on the indices such as input current Total Harmonic Distortion and input power factor.

#### 4.2 Average switching function analysis

In this Chapter, the transfer characteristics of the PWM inverter are first established quantitatively by considering the available input and expected output. Next, the analytical expressions (i.e. transfer function) for this transfer characteristics are derived as the ratio of expression representing relevant converter input and output [13].

The waveform to be modulated is considered the independent variable (input voltage/current in the converter). The resulting modulated waveform is the dependent variable (output voltage/current out of the converter). Therefore, the relationship between modulated and unmodulated waveforms can be analytically described by the following transfer function;

$$TF = \frac{\text{converter dependent electrical variable}}{\text{converter independent electrical variable}}$$

(4.1)

The transfer characteristics of the rectifier and PWM inverter are derived, for example, the rectifier switching function is a bipolar square wave with a frequency equal to the line frequency: the rectified dc bus voltage (Fig. 4.1(a)) is the product of this switching function and the ac voltage:

$$v_{dc} = SW_{rect} \cdot v_{ac} \tag{4.2}$$

Similarly, the trapezoidal output voltage is obtained from the dc bus voltage through the inverter switching function

$$v_o = SW_{inv}.v_{dc} \tag{4.3}$$

Fig. 4.1 (a) Rectified dc bus voltage and rectified trapezoidal reference. (b) Inverter average switching function. (c) Input line current (rated voltage, 130 V, rated load, 10 A).

The trapezoidal reference voltage is shown in Fig. 4.1(a) and it is assumed the output  $v_0$  tracks the reference if a suitable pattern generator is used, as described in Section II. The inverter switching function is shown in Fig. 4.1(b).

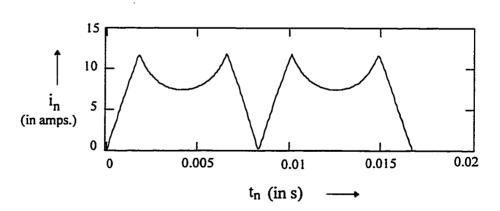

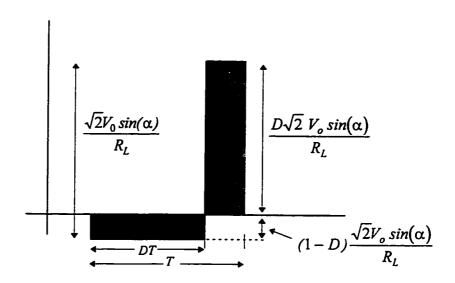

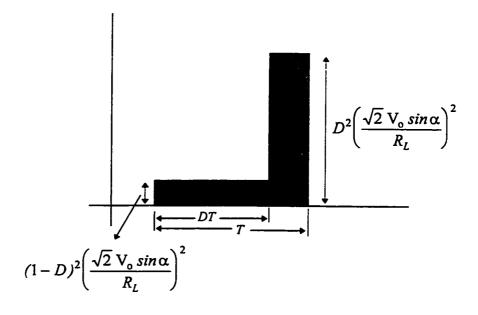

Assuming the load is resistive, the load current  $i_0$  is also trapezoidal. The dc bus current  $i_{dc}$  is given by:

$$i_{dc} = SW_{inv} \cdot i_{o} \tag{4.4}$$

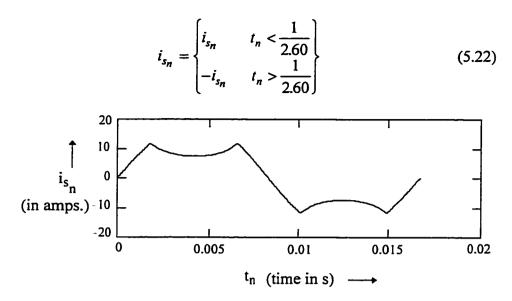

and the ac input current:

$$i_{ac} = SW_{rect} \cdot i_{dc} \tag{4.5}$$

This current is shown in Fig. 4.1(c).

In addition to giving a quantitative explanation of the power supply waveforms, the switching function analysis also establishes the theoretical limits to power factor and input harmonic distortion, assuming the inverter switching frequency is high and switching frequency is high and switching frequency harmonics are eliminated by means of a small low pass filter.

The maximum input power factor and minimum input THD (caused by low frequency components only) are given in Table I as a function of input voltage. Since the trapezoidal reference is generated by clipping the ac input voltage, input current distortion will increase as the ac line voltage increases, thus lowering power factor to 0.89.

Conversely, for the lowest input voltage, 92 V, the trapezoidal output voltage waveform is nearly sinusoidal, accounting for a higher power factor of 0.99. For rated

input voltage, 120 V, the power factor has a high value of 0.94. Note also that as the input voltage increases, the input current decreases, as expected.

TABLE II

Theoretical limit - Input THD and power factor

(Switching function analysis, Average model, PWM switching neglected, resistive load)

| Input voltage | Input rms current | Input THD | Input Power Factor |  |

|---------------|-------------------|-----------|--------------------|--|

| 92 V          | 9.82 A            | 5.05 %    | 0.99               |  |

| 100 V         | 9.17 A            | 17.39 %   | 0.98               |  |

| 110 V         | 8.52 A            | 28.03 %   | 0.96               |  |

| 120 V         | 8.00 A            | 36.43 %   | 0.94               |  |

| 130 V         | 7.57 A            | 43.58 %   | 0.91               |  |

| 138 V         | 7.28 A            | 48.67 %   | 0.89               |  |

## 4.3 Example

The input power factor and input current total harmonic distortion have been calculated for a nominal sinusoidal source voltage of 120 V rms, 60 Hz while generating a trapezoidal shaped output voltage having rms value of 90 V, 60 Hz using average switching function analysis. In this analysis, the higher order switching frequency harmonics have also been neglected.

As already shown, the switching function of the rectifier and inverter are first derived. Then, the load current is reflected using the switching function to obtain the waveshape of the current drawn by the power supply.

Similarly the value of power factor and total harmonic distortion can be derived for various input voltages.

$$V = 120\sqrt{2} \quad V \quad \omega = 2 \cdot \pi \cdot 60 \text{ rad/s}$$

$$k = 2^8$$

$$n = 0...k - 1 \tag{4.6}$$

$$t_n = \frac{1}{60} \cdot \frac{n}{k-1} \text{ in seconds.} \tag{4.7}$$

The output of the full bridge rectifier is given as:

$$V_{dc_n} = |V.\sin(\omega \cdot t_n)| \tag{4.8}$$

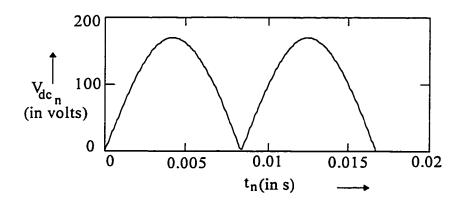

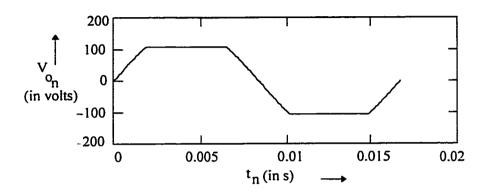

Fig. 4.2 Output rectified waveform of the bridge rectifier.

The Fourier transform of the output rectified waveform of the full-bridge rectifier can be obtained as following:

$$c = \frac{ffl(V_{dc})}{\sqrt{k}} \cdot 2; \quad c_o = \frac{c_o}{2}$$

(4.9)

$$j=0...N$$

(4.11)

Fig. 4.3 Harmonic spectrum of the output voltage of the bridge rectifier.

TABLE III

Harmonic contents of the output voltage of the bridge rectifier

|           | dc comp. | 2nd    | 4th    | 6th   | 8th   | 10th  |

|-----------|----------|--------|--------|-------|-------|-------|

| Magnitude | 107.6 V  | 72.5 V | 14.4 V | 6.2 V | 3.4 V | 2.2 V |

| of the    |          |        |        |       |       |       |

| harmonics |          |        |        |       |       |       |

The trapezoidal shaped output voltage waveform across the load as a function of  $\boldsymbol{\lambda}$  is given by ;

$$V_{o_n} = V \sin(\omega t_n)$$

$$\lambda = 0.625$$

(4.12)

where  $\lambda$  is the multiplication factor required to make a trapezoidal output voltage equal to 90 V.

$$V_{o_n} = \begin{cases} \lambda.V & \text{if } V_{o_n} > \lambda.V \\ V_{o_n} & \text{if } V_{o_n} < \lambda.V \end{cases}$$

$$(4.13)$$

$$V_{o_n} = \begin{cases} V_{o_n} & \text{if } V_{o_n} > -\lambda, V \\ -\lambda, V_{o_n} & \text{if } V_{o_n} < -\lambda, V \end{cases}$$

$$(4.14)$$

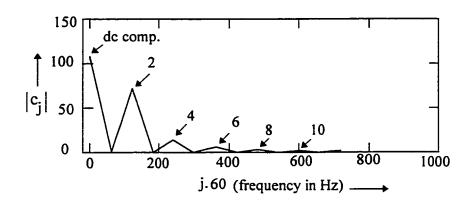

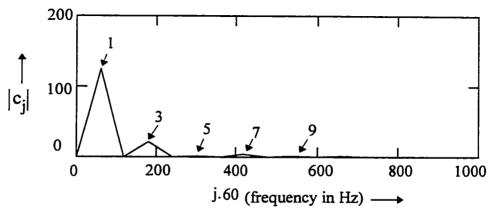

Fig. 4.4 Output trapezoidal waveform of the full-bridge inverter.

Obtaining the Fourier transform of the output voltage waveform of the full bridge inverter, we have:

$$c = \frac{fft(V_o)}{\sqrt{k}} \cdot 2, c_o = \frac{c_o}{2}$$

(4.15)

$$N=last(c) N=128$$

(4.16)

$$j=0...N$$

(4.17)

Fig. 4.5 Harmonic spectrum of the output trapezoidal waveform of the full-bridge inverter.

TABLE IV

Harmonic contents of the output trapezoidal waveform of the full-bridge inverter

|                                  | fund.   | 3rd    | 5th    | 7th    | 9th    |

|----------------------------------|---------|--------|--------|--------|--------|

| magnitude of<br>the<br>harmonics | 125.5 V | 21.0 V | 0.96 V | 3.73 V | 0.69 V |

The rms value of the output trapezoidal waveform is given by:

$$\frac{\sqrt{\sum_{j=1}^{N} (|c_j|)^2}}{\sqrt{2}} = 90 \tag{4.18}$$

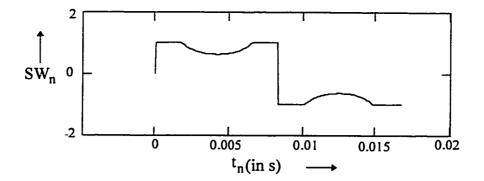

The switching function of the full bridge inverter is given as:

$$SW_n = \frac{V_{o_n}}{V_{dc_n}} \tag{4.19}$$

In Fig. 4.6, the switching fuction for the full-bridge inverter is given as

Fig. 4.6 Switching function curve of the full-bridge inverter.

The current through the load is obtained as:

$$i_{L_n} = \frac{V_{o_n}}{R} \tag{4.20}$$

Since the high switching order harmonics are neglected, the output filter can be neglected for low order harmonics. Further the dc bus current can be obtained by reflecting the load current to input of the full bridge inverter.

$$i_{L_n} = i_{L_n}.SW_n \tag{4.21}$$

Fig. 4.7 Waveform of the dc bus current.

The input current drawn by the power supply is given by:

Fig. 4.8 Waveshape of the input current drawn from the utility by the supply.

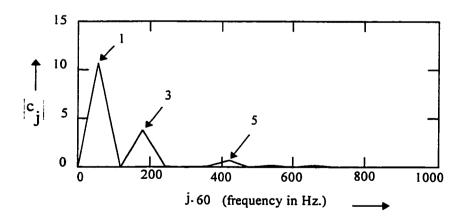

Obtaining the Fourier transform of the input current drawn by the power supply, we get:

$$c = \frac{fft(i_s)}{\sqrt{k}} \cdot 2, c_o = \frac{c_o}{2}$$

(4.23)

$$N=last(c) N=128$$

(4.24)

$$j=0....N$$

(4.25)

Fig. 4.9 Harmonic spectrum of the input current drawn by the power supply.

TABLE V

Harmonic contents of the input current drawn by the power supply

|                            | fundam<br>-ental | 3rd    | 5th    | 7th    | 9th    | 11th   | 13th   |

|----------------------------|------------------|--------|--------|--------|--------|--------|--------|

| Magnitude of the harmonics | 10.6 A           | 3.78 A | 0.04 A | 0.73 A | 0.17 A | 0.24 A | 0.13 A |

The rms value of the input current is given by:

$$\frac{\sqrt{\sum_{j=1}^{N} (|c_j|)^2}}{\sqrt{2}} = 8.01 \tag{4.26}$$

Input harmonic total harmonic distortion is given by:

$$\mathbf{THD} = \frac{\sqrt{\sum_{j=2}^{N} (|c_{j}|)^{2}}}{|c_{1}|} \cdot 100 \tag{4.27}$$

Input power factor of the supply is given by:

$$\mathbf{PF} = \frac{\left|c_1\right|}{\sqrt{\sum_{j=1}^{N} \left(\left|c_j\right|\right)^2}} \tag{4.28}$$

$$PF = 0.94$$

#### 4.4 Experimental Results

## 4.4.1 Conditions

The power supply is implemented with the 3 pattern generators and control circuits.

All the results are measured under the following conditions:

- Input voltage: 120 V rms, 60 Hz.

- Output voltage: 90 V rms, 60 Hz, 10 A rms ( 9  $\Omega$  resistive load).

- System parameters : line resistance  $R_S = 0.09 \ \Omega$ , line inductance  $L_S = 10 \ \mu\text{H}$ , dc bus capacitor  $C_d = 10 \ \mu\text{F}$ .

- Switching frequency: 40 Hz.

- Controller design parameters : as calculated in this chapter.

## 4.4.2 Current and voltage waveforms

Input current, output current (or output voltage), dc bus voltage and PWM (unfiltered) output voltage are given in Figs. 4.5, 4.6 and 4.7 for the hysteresis, triangular-carrier and reset integral techniques respectively.

#### 4.5 Performance evaluation and comparison

To evaluate the performance of the proposed power supply implemented with three PWM pattern generators and control techniques, the following system is designed and studied:

Fig. 4.10 Operation of the hysteresis controller (experimental results). (a) Input current. (b) Load current (filtered). (c) Dc bus voltage. (d) Unfiltered inverter output voltage. (Hysteresis window  $\Delta V_H = 5$  % peak of reference, average switching frequency  $f_{SW} = 40$  kHz, input voltage = 120 V, output voltage = 90 V rms, rated output current = 10 A, resistive load).

Fig.4.11 Operation of the Triangular Carrier -based integral PWM controller (experimental results). (a) Input current. (b) Load current (filtered). (c) DC bus voltage. (d) Unfiltered inverter output voltage. (Magnitude of the carrier = 20 V(peak to peak), average switching frequency  $f_{SW}$  = 40 kHz, input voltage = 120 V rms, output voltage = 90 V rms rated output current = 10 amps, resistive load.

Fig. 4.12 Operation of the Reset Integral PWM Controller (experimental results).(a) Input current. (b) Dc bus voltage. (c) Inverter output voltage (unfiltered). (d) Output voltage (filtered). (Integrator gain = 25  $\mu$ s, average switching (clock) frequency  $f_{SW}$  = 40 kHz, input voltage = 120 V, output voltage = 90 V rated output current = 10 amps, resistive load).

The performance of such a power supply is studied under the following conditions; (i) varying load; (ii) different dc bus capacitor values, and (iii) varying input voltage levels. The power factor and input current THD are used as the criteria for comparative evaluation of the performance features.

### 4.5.1 Rated Operation

Fig.4.12 shows the rectified output voltage  $v_s$ , input current  $i_s$  and load current  $i_L$ . These figures illustrate that input current has a waveform much closer to the sinusoidal waveshape as compared to the pulse-like waveform of the conventional ac power supplies. In addition the current is in phase with the voltage, which gives a high input power factor. Since the dc link capacitor is small, the dc bus is almost the same as the rectifier waveform of the ac source voltage.

# 4.5.2 Change of the DC link Capacitor C<sub>dc</sub>