# MULTI-CHANNEL PROCESSING OF TURBO CODES

# Pouriya Sadeghi

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements

for the Degree of Master of Applied Science at

Concordia University

Montreal, Quebec, Canada

August 2003

© Pouriya Sadeghi, 2003

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisisitons et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-612-83875-7 Our file Notre référence ISBN: 0-612-83875-7

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou aturement reproduits sans son autorisation.

### **ABSTRACT**

# MULTI-CHANNEL PROCESSING OF

### **TURBO CODES**

### Pouriya Sadeghi

A turbo decoder uses an iterative procedure and its performance is dependent on the number of iterations it performs. In a turbo decoder, the number of iterations required to achieve a certain FER is a function of the channel SNR. An example of this is a base station in a mobile communication system, where turbo decoder receives data frames from different users each with a given level of fading and as a result, with different SNR. If a fixed number of iterations is allocated to each frame, it is possible that certain frames remain erroneous while decoder is idle part of the time for other frames. In this thesis the idea of sharing the processing power among different frames, possibly belonging to different channels, is used. This time-sharing approach can increase the processing throughput and/or the performance of the turbo decoding scheme. We present two schemes and give their performance for the 3GPP and DVB-RCS codes. The first one is serial processing algorithm, which decodes the input frames one by one and the other one is parallel processing scheme that tries to decode all of those received channels simultaneously.

We investigated the implementation of these schemes using a Digital Signal Processor (DSP) chip (TI TMS320C6416 DSP CPU). We have developed an efficient implementation algorithm by combining those two multi-channel processing schemes. All the presented schemes can also be used for a single-channel communication system.

### **ACKNOWLEDGMENTS**

Firstly, I would like to express my sincere gratitude and thanks to my supervisor Dr. Mohammad Reza Soleymani and my co-supervisor Dr. Asim J. Al-Khalili for their generous help and constant support. I appreciate the way Dr. Soleymani devoted his precious time to discuss with me the details of my research, which was both encouraging and inspiring. His goal has always been in place to keep the research environment friendly and stress free.

My heartfelt thanks to my dearest mother, sister and brother, who supported me with their love and understanding. Special thanks to my beloved wife who has been involved in every aspect of this research, without her support none of this would have been possible.

I would like to thank Mr. Mohsen Ghotbi, Ms. Yingzi Gao, Ms. Shirin Esfandiari and all of my friends at Wireless and Communication Laboratory for their valuable advice and suggestions.

I also extend my thanks to the faculty and staff of Electrical and Computer Engineering department, and to my defense committee Dr. Shayan, Dr. Ghrayeb and Dr. Ganesan.

# TABLE OF CONTENTS

| Li | st of fig | gures                                                  | viii |

|----|-----------|--------------------------------------------------------|------|

| Li | st of ta  | bles                                                   | x    |

| 1  | Intro     | duction                                                | 1    |

| 2  |           | o Decoding                                             | 8    |

|    | 2.1       | BCJR Algorithm                                         | 9    |

|    |           | 2.1.1 Maximum A Posteriori Probability (MAP) Algorithm | 9    |

|    |           | 2.1.2 Max-Log-MAP Algorithm                            | 16   |

|    |           | 2.1.3 Max*-Log-MAP Algorithm                           | 18   |

|    | 2.2       | Interleaver (Permuter)                                 | 19   |

|    | 2.3       | Iterative Decoding of Turbo Codes                      | 19   |

|    | 2.4       | Iterative Nature of Turbo Decoder                      | 23   |

|    |           | Early Stopping Criteria                                |      |

|    | 2.6       | Summary                                                | 27   |

| 3  | Multi     | -Channel Processing                                    | 28   |

|    | 3.1       | Ideal Scheme                                           | 29   |

|    | 3.2       | Fixed-Iteration Scheme                                 | 30   |

|    | 3.3       | Serial Processing Scheme                               | 31   |

|    | 3.4       | Parallel Processing Scheme                             | 33   |

|    | 3.5       | Multi-Channel Schemes for Single Channel Systems       | 35   |

|    | 3.6       | Summary                                                | 36   |

| 4 | Comp  | uter Si | mulations                                   | 37 |

|---|-------|---------|---------------------------------------------|----|

|   | 4.1   | 3GPP    | Standard                                    | 37 |

|   |       | 4.1.1   | 3GPP Channel Coding                         | 39 |

|   |       | 4.1.2   | Turbo Coding Option of 3GPP                 | 40 |

|   |       | 4.1.3   | Trellis Termination for 3GPP Turbo Codes    | 42 |

|   |       | 4.1.4   | 3GPP Turbo Code Interleaver                 | 42 |

|   |       |         | 3GPP Simulation Results                     |    |

|   | 4.2   | DVB/F   | RCS Standard                                | 44 |

|   |       | 4.2.1   | Turbo Coding Option of DVB/RCS              | 45 |

|   |       | 4.2.2   | Determination of DVB/RCS Circulation States | 47 |

|   |       | 4.2.3   | DVB/RCS Code Rates                          | 48 |

|   |       | 4.2.4   | DVB/RCS Simulation Results                  | 49 |

|   | 4.3   |         | ation algorithms                            |    |

|   |       | 4.3.1   | Fixed-Iteration Scheme                      | 52 |

|   |       | 4.3.2   | Ideal Processing Scheme                     | 52 |

|   |       | 4.3.3   | Serial Processing Scheme without MIPCH      | 55 |

|   |       | 4.3.4   | Serial Processing Scheme with MIPCH         | 56 |

|   | **    | 4.3.5   | Parallel Processing Scheme                  | 58 |

|   | 4.4   | Multi-0 | Channel Processing Simulation Results       | 59 |

|   | 4.5   | Summa   | ary                                         | 66 |

|   |       |         |                                             |    |

| 5 | DSP I | •       | entation                                    | 67 |

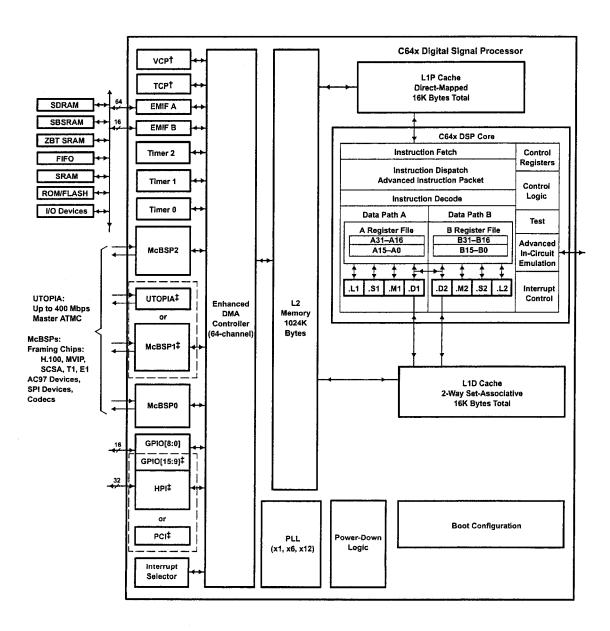

|   | 5.1   | TMS32   | 20C6416 Architecture                        | 68 |

|   |       |         | Central Processing Unit (CPU)               |    |

|   |       | 5.1.2   | Memory                                      | 70 |

|   |       | 5.13    | Peripheral Options                          | 71 |

|              | 5.2   | Turbo  | Decoder Coprocessor (TCP)             | 72 |

|--------------|-------|--------|---------------------------------------|----|

|              |       | 5.2.1  | Interleaving/De-interleaving          | 72 |

|              |       | 5.2.2  | Stopping Criterion                    | 73 |

|              |       | 5.2.3  | Data Format                           | 73 |

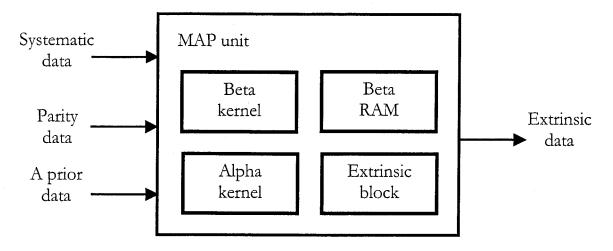

|              |       | 5.2.4  | MAP Processing Unit                   | 73 |

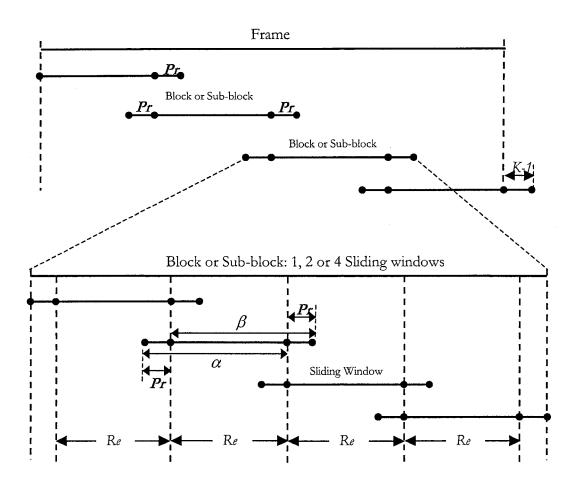

|              |       | 5.2.5  | Sliding Windows Decoding              | 74 |

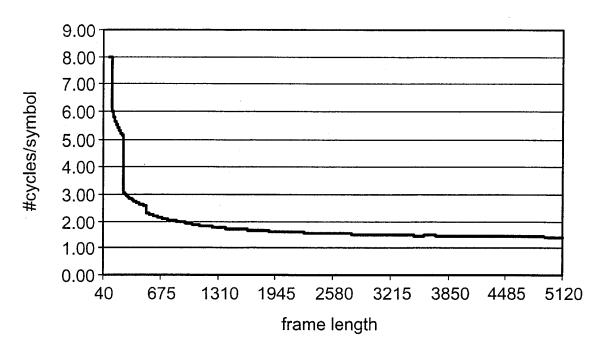

|              |       | 5.2.6  | TCP Processing Delay                  | 76 |

|              | 5.3   | TCP P  | rocessing Modes                       | 79 |

|              |       | 5.3.1  | TCP Standalone Mode (SA Mode)         | 79 |

|              |       | 5.3.2  | TCP Shared-Processing Mode (SP Mode)  | 80 |

|              | 5.4   | Apply  | ying Multi-Channel Processing Schemes | 82 |

|              |       | 5.4.1  | Fixed-Iteration Scheme                | 82 |

|              |       | 5.4.2  | Serial Processing Scheme              | 84 |

|              |       | 5.3.4  | Parallel Processing Scheme            | 85 |

|              | 5.5   | TMS32  | 20C6416 Hardware Modification         | 88 |

|              | 5.6   | The Ne | ew Implementation Scheme              | 89 |

|              | 5.7   | Summa  | ary                                   | 92 |

| 6            | Concl | usion  |                                       | 93 |

| Bibliography |       |        | 95                                    |    |

# LIST OF FIGURES

| Fig. 1.1: Typical turbo encoder.                                                         | 3   |

|------------------------------------------------------------------------------------------|-----|

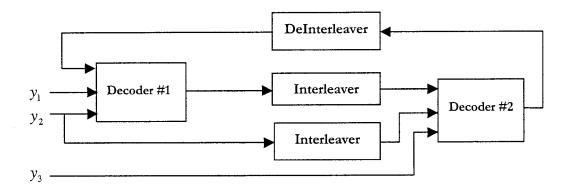

| Fig. 1.2: Typical turbo decoder.                                                         | 5   |

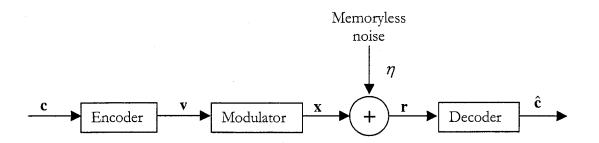

| Fig. 2.1: Model of the communication system                                              | 10  |

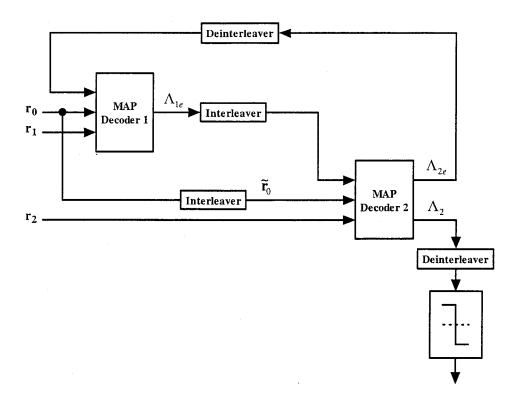

| Fig. 2.2: An iterative turbo decoding system using MAP decoder                           | 20  |

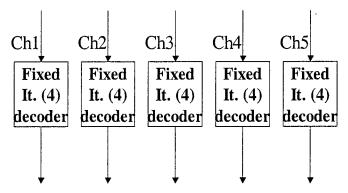

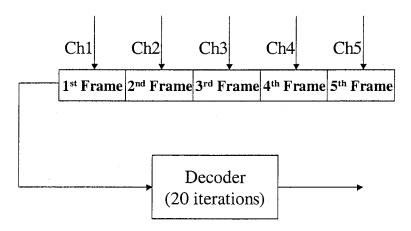

| Fig. 3.1: An example of the fixed-iteration method of multi-channel decoding,            |     |

| consisting of 5 fixed-iteration turbo decoders with 4 iterations per channel             |     |

| $(n_f = 4)$ , i.e., there is a total of 20 iterations for all channels $(n_u = 20)$      | 30  |

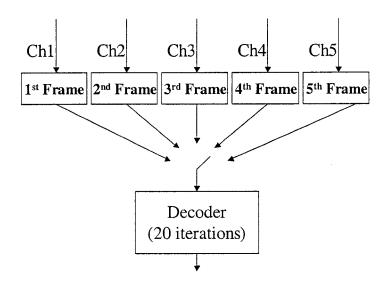

| Fig. 3.2: An example of the serial processing scheme of multi-channel decoding,          |     |

| consisting of a single turbo decoder                                                     | 32  |

| Fig. 3.3: An example of the parallel processing scheme for multi-channel decoding,       |     |

| consisting of a single turbo decoder                                                     | .34 |

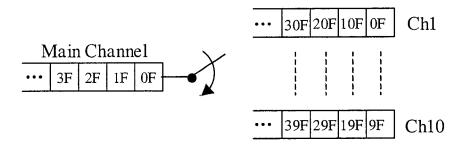

| Fig. 3.4: An example of converting a one-channel system to a multi-channel one by        |     |

| using 10 buffers                                                                         | .35 |

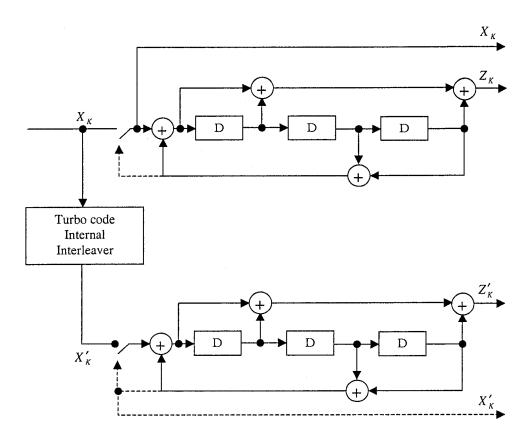

| Fig. 4.1: Structure of rate 1/3 Turbo coder (dotted lines apply for trellis termination  |     |

| only)                                                                                    | .41 |

| Fig. 4.2: 3GPP frame error rate (FER) vs. number of iterations per frame for several     |     |

| SNRs on an AWGN channel (k=1440, r=1/3).                                                 | .44 |

| Fig. 4.3: DVB/RCS turbo encoder block diagram.                                           | .46 |

| Fig. 4.4: DVB/RCS frame error rate (FER) vs. number of iterations per frame for several  |     |

| SNRs on an AWGN channel (k=212, r=1/2)                                                   | .51 |

| Fig. 4.5: Tree of $n_{ch}$ level of branches, used for spanning all of the possibilities | .53 |

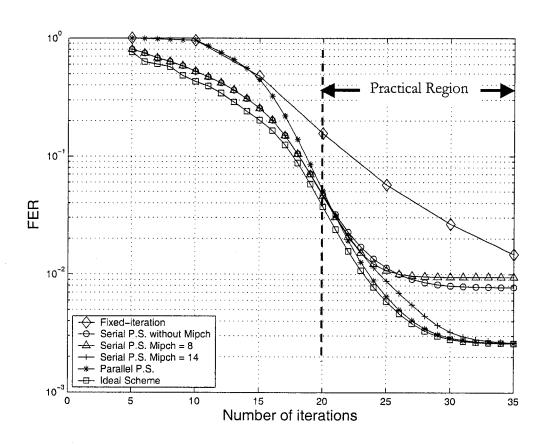

| Fig. 4.6: | FER performance of all multi-channel processing schemes for 3GPP turbo      |    |

|-----------|-----------------------------------------------------------------------------|----|

|           | codes at SNR=1.0 dB, Frame length=1440. (Mipch=Maximum number of            |    |

|           | iterations per channel)                                                     | 61 |

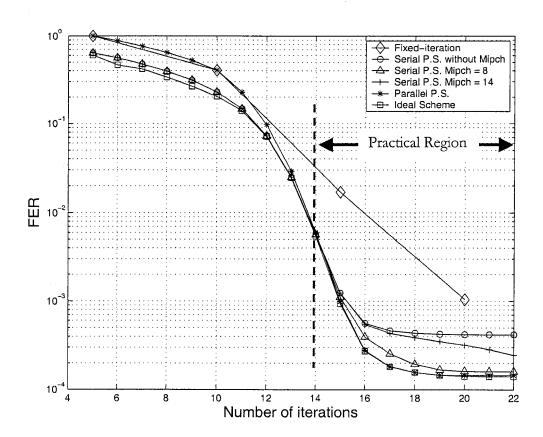

| Fig. 4.7: | FER performance of all multi-channel processing schemes for 3GPP turbo      |    |

|           | codes at SNR=1.5 dB, Frame length=1440. (Mipch=Maximum number of            |    |

|           | iterations per channel)                                                     | 62 |

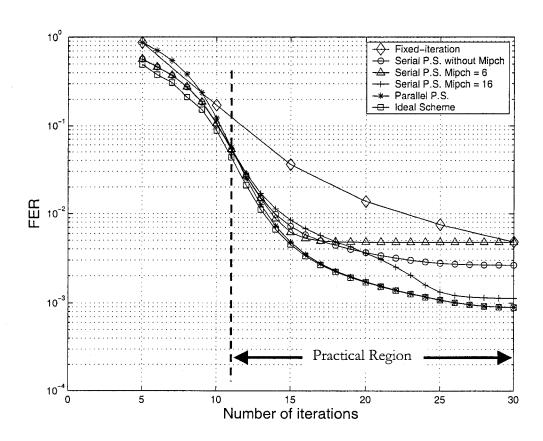

| Fig. 4.8: | FER of all multi-channel processing schemes for DVB-RCS turbo codes at      |    |

|           | SNR=2.0 dB (R=1/2), Frame length=212.                                       | 63 |

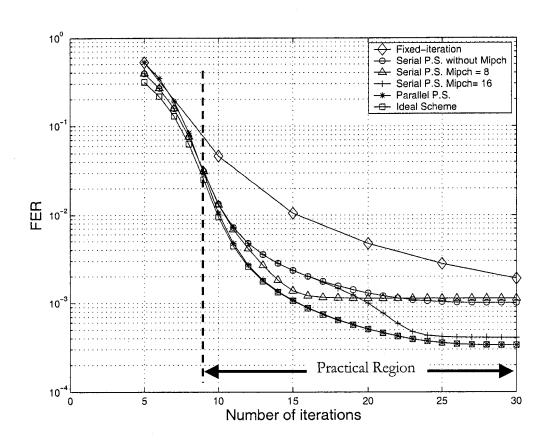

| Fig. 4.9: | FER of all multi-channel processing schemes for DVB-RCS turbo codes at      |    |

|           | SNR=3.0 dB (R=2/3), Frame length=212                                        | 64 |

| Fig. 5.1: | Block diagram of TMS320C6416 DSP                                            | 69 |

| Fig. 5.2: | MAP processing unit block diagram                                           | 74 |

| Fig. 5.3: | Sub-blocks and sliding windows segmentation                                 | 75 |

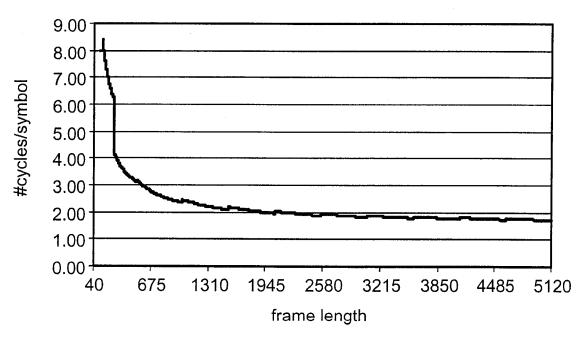

| Fig. 5.4: | Processing unit performance for Pro=24 (with 4 sliding windows in each sub- |    |

|           | block).                                                                     | 78 |

| Fig. 5.5: | Processing unit performance for Pro=48 (with 4 sliding windows in each sub- |    |

|           | block)                                                                      | 78 |

| Fig. 5.6: | TCP standalone mode block diagram.                                          | 80 |

# LIST OF TABLES

| Table 2.1: Probabilities (%) of correction of a 3GPP frame vs. number of iterations for | ,  |

|-----------------------------------------------------------------------------------------|----|

| several SNRs on an AWGN channel (k=1440, r=1/3).                                        | 24 |

| Table 4.1: UMTS key parameters                                                          | 38 |

| Table 4.2: Usage of channel coding scheme and coding rate.                              | 40 |

| Table 4.3: Circulation state correspondence table                                       | 48 |

| Table 5.1: Number of sliding windows per sub-block.                                     | 76 |

| Table 5.2: Example of a multi-channel processing system by using the new                |    |

| implementation scheme                                                                   | 91 |

### **INTRODUCTION**

More than fifty years ago Shannon discovered the limits on transmission rates in digital communication systems. In "A Mathematical Theory of Communication" [1], he defined the capacity of the Adaptive White Gaussian Noise (AWGN) channel as:

$$C = W \log_2 \left( 1 + \frac{S}{N} \right) \tag{1.1}$$

where W is the bandwidth of the channel in Hertz, S is the signal power and  $N = WN_0$  is the variance of the Gaussian noise.

Shannon's channel coding theorems indicate that for an Additive White Gaussian Noise (AWGN) channel with capacity C, there exist codes that using them the information

can be sent across the channel at a rate less than C, with an arbitrarily low bit error rate [2] (for a proof refer to [3]).

For example, for a Binary Phase Shift Keying (BPSK) modulation system, which has a spectral efficiency of 1 bps/Hz, over an AWGN channel, the lower limit for Signal to Noise Ratio (SNR) to have an arbitrarily small Bit Error Rate (BER), is 0.0 dB. However, an uncoded BPSK system requires 9.5 dB [4] for a BER of  $1 \times 10^{-5}$ . So the maximum possible coding gain over an uncoded BPSK modulation scheme is (9.5-0.0) = 9.5 dB.

The Consultative Committee for Space Data Systems (CCSDS) issued the NASA/ESA standard in 1983, which has a coding gain of 7.4 dB for BER of  $1\times10^{-5}$  [5]. This standard is still 2.1 dB away from the theoretical Shannon limit. There were too many efforts in 1980's and early 1990's to narrow this gap. There were just a few improvements of a few tenths of dB by utilizing serial concatenated systems, Reed Solomon code [6] and extremely complex Viterbi decoders [7].

In 1993 turbo coding was introduced. It provided a performance that was only a few tenths of dB away from the Shannon limit. Turbo codes used decoders much less complex than those used in NASA/ESA standard. The effect of this 2 dB extra coding gain, is even stronger in the wireless communication systems, where the bandwidth demand is growing very fast.

Turbo coding has two principle parts: parallel concatenated encoders and iterative decoding system. Parallel concatenated encoder, which can be designed for convolutional codes or block codes, works as follow: assume that there are two convolutional encoders (it is also possible to have more than two encoders). The first encoder encodes the data sequence (m) as  $(c_1)$  (Fig. 1.1). Next, the original data sequence (m) is interleaved by the

interleaver resulting in  $\tilde{m}$  that is used as the input data sequence for the second encoder. The output of the second encoder  $(c_2)$ , the output of the first encoder  $(c_1)$  and the original data sequence (m) are multiplexed, punctured and sent through an AWGN channel (the channel model that has been used in this thesis) to the turbo decoder receiver.

Fig. 1.1: Typical turbo encoder.

The excellent performance of turbo code is achieved at moderate decoding complexity. A turbo decoding system consists of two iterative Soft-Input/Soft-Output (SISO) decoders. The Soft-Input/Soft-Output property makes turbo coding perfect for iterative decoding. These two decoders are serially concatenated trough an interleaver identical to that used in the encoder side. In turbo coding system, the interleaver is one of the most important components: producing good weight codewords and decrease the correlation between the outputs of those two encoders. Producing good (high weight) codewords reduces the probability that the turbo decoder decodes the received sequence to a wrong codeword instead of the original one. Having less correlation between two output parity sequences is the main concept of the iterative decoding. It causes the soft outputs of the turbo decoder be relatively independent of each other, so the soft output of one component decoder can be used as the soft input of the other and vice versa. This means that for decoding a frame, the turbo decoder performs several iterations. For the first

iteration, it assumes that the probabilities of 0 and 1 are equal and based on the channel information, produces a soft decision output for each data bit. For other iterations, the decoder will use the soft output of the other decoder as a priori probability to perform the next iteration.

The performance of the turbo decoder is directly related to the number of the iterations that it performs to decode a received frame. If the turbo decoder can perform more iterations to decode each input frame, it can achieve a better BER. The number of iterations required to decode each input sequence can be assumed to be a random variable dependent on the variance of the AWGN. In traditional turbo coding schemes, the number of iterations is usually set to a fixed value, and the turbo decoder performs this fixed number of iterations to decode each input frame. Another option for the turbo decoder is to perform different number of iterations for each frame. In this case, to stop the decoding procedure on each frame, it is possible to use some rules and conditions to check whether the uncoded sequence is corrected or not. These rules and conditions are called "stopping criteria". There are several proposed stopping criteria so far. In [8], it has been shown that using some stopping criteria, will add, on the average, less than one iteration to the number of required iterations to correct each input channel (in comparison with the ideal case where the decoder knows when it has to stop).

In several parts of a communication system, we need to decode more than one channel simultaneously. These include the hub in a non-regenerative satellite communication system, the on-board processor in a regenerative satellite payload and the mobile base station where several channels are received from different terminals and the base station has to decode all of them at the same time. The ideal situation for the decoder is to have all information about all channels and the knowledge that how many iterations each frame needs to be corrected. So the decoder decodes first the channel that needs less

iteration than others, and so on. This ideal method is optimum, but in the practice, the turbo decoder does not know the original data sequence at the transmitter so it is not possible to determine whether decoded sequence is erroneous or not .So this is not a practical method and it is only for comparison and measuring the performance of other schemes.

In a traditional scheme, for each channel there is one decoder, and the procedure of decoding each channel is exactly the same as the decoding of a one-channel system (Fig. 1.2). For implementing a turbo code system, this traditional method is inefficient in practice, because in this method, each decoder has a fixed number of iterations, and if a frame needs more iterations than this limit to be decoded correctly, the decoder is not capable of correcting it. On the other hand, there are some other decoders that have decoded their assigned frames in less number of iterations than this limit, so they are idle at the same time. The basic idea in this thesis is to share these idle times for other sequences and have an efficient turbo decoder with a good throughput and performance.

In this thesis, we investigate mainly two multi-channel processing turbo decoding schemes in order to increase the performance and/or capacity of the turbo decoders. The presented schemes can be applied to any other kind of iterative decoder.

Fig. 1.2: Typical turbo decoder.

Chapter 2 deals with the subject of turbo decoding schemes and among these schemes; Bahl-Coke-Jelinek-Raviv (BCJR) algorithm is mentioned in more detail. The BCJR algorithm is being used widely in the iterative decoding systems. BCJR algorithm is an optimal algorithm over an AWGN channel and it has the minimum symbol error rate (or bit error rate). Next, two practical variants of this algorithm are described in detail (Log-MAP, Max-Log-MAP). Interleaver (permuter), which is one of the basic components of the turbo decoding, is also explained in Chapter 2. After that, the principles of iterative decoding are discussed. Then, the iterative nature of turbo decoder that is one of the main factors in performance of the turbo decoder is explained by means of some computer-based simulation examples. Chapter 2 ends with the introduction of the stopping criterion and describing several stopping criteria for turbo decoding.

Chapter 3 provides a detailed investigation of multi-channel turbo coding systems and proposes several multi-channel processing schemes for these systems. And at the end, it describes how to use these multi-channel processing schemes for a single-channel turbo decoding systems with some restrictions.

Chapter 4 begins with introducing Third Generation Partnership Project (3GPP) and Digital Video Broadcasting for Return Channel via Satellite (DVB/RCS) turbo coding standards. Then the results of computer-based simulations of 3GPP and DVB/RCS using AWGN channel and BCJR algorithm for several SNRs are presented. Based on the simulation results, the performance of each of the proposed parallel processing schemes in Chapter 3 are analyzed. It is shown that the performance of the proposed parallel processing scheme is close enough to the ideal case where prior to the decoding process, the turbo decoder knows how many iterations each input frame requires to be corrected, and it decodes the input frame that needs smaller number of iterations first.

In Chapter 5, implementation issues of the multi-channel processing schemes proposed in Chapter 3 on a Digital Signal Processing (DSP) chip, "TMS320C6416", for 3GPP turbo coding standard are investigated. This chip is one of the highest-performance DSP CPU so far, and has also two embedded coprocessor; Viterbi coprocessor and turbo decoder coprocessor (designed for 3GPP and CDMA2000 coding standards). The chapter closes with introducing an efficient multi-channel processing implementation algorithm, which can be considered as a combination of those proposed multi-channel processing schemes. This efficient multi-channel processing algorithm is not restricted to only this DSP CPU and can be used in any other hardware implementation of turbo codes.

### **TURBO DECODING**

A turbo decoder consists of two soft-input/soft-output (SISO) decoders concatenated serially via an interleaver (permuter) identical to the one used in turbo encoder [4]. BCJR (or MAP) decoder is an appropriate choice for those two decoders; because it is SISO compatible and also an optimal algorithm in terms of Symbol Error Rate (SER) or BER [9].

In this chapter, first, three different versions of BCJR algorithm are described in detail. Then, turbo code interleaver is discussed. Next, the structure of turbo decoder is explained and its most important property, the iterative nature, is mentioned in more detail. At the end of this chapter, some issues concerning parallel processing and early stopping criteria are described.

### 2.1 BCJR Algorithm

The Bahl, Cocke, Jelinek, and Raviv (BCJR) algorithm [10] which is also called forward-backward or *maximum a posteriori* (MAP) algorithm, is one of the turbo decoding algorithms that minimizes the SER or BER based on the information sequence received from an AWGN channel [11]. This algorithm is an optimal algorithm in terms of the SER (or BER).

Large number of calculations, complicated and non-linear mathematical functions and huge amount of memory requirement, make the implementation of the MAP algorithm in hardware or even in computer-based simulations tedious and time consuming. As a result, some variants of this algorithm such as Log-MAP algorithm and Max-Log-MAP algorithm are used in practice. The performance of the Log-MAP algorithm is the same as original MAP algorithm. Although Max-Log-MAP algorithm is a sub optimal algorithm, in most cases its performances is close enough to the original MAP algorithm, and it can be utilized instead of MAP decoder [12].

### 2.1.1 Maximum A Posteriori Probability (MAP) Algorithm

In this section, we use a  $(n,1,\nu)$  binary convolutional code whose encoder has one bit input, n bits output and a  $\nu$ -bit shift register ( $\nu$  bits of memory). Therefore, the encoder has  $M_{\nu} = 2^{\nu}$  different states. The state sequence from time 0 to t will be presented by:

$$\mathbf{S}_{0}^{t} = (S_{0}, S_{1}, ..., S_{t}) \tag{2.1}$$

It is seen that the next state is only dependent on current state and the next input bit. So, the state transition is a Markov process. The system block diagram is shown in Fig. 2.1.

Fig. 2.1: Model of the communication system

In the following, each data sequence is defined in detail. The input binary message sequence is denoted by:

$$\mathbf{c} = (c_1, c_2, ..., c_t, ..., c_N) \tag{2.2}$$

where N is the length of the input sequence. The output sequence of the encoder is represented by:

$$\mathbf{v}_{1}^{N} = (\mathbf{v}_{1}, \mathbf{v}_{2}, ..., \mathbf{v}_{N})$$

,  $\mathbf{v}_{t} = (v_{t,0}, v_{t,1}, ..., v_{t,n-1})$  (2.3)

$\mathbf{v}_{i}^{N}$  is modulated by a BPSK modulator and the output sequence of it, is defined by:

$$\mathbf{x}_{1}^{N} = (\mathbf{x}_{1}, \mathbf{x}_{2}, ..., \mathbf{x}_{N}) , \quad \mathbf{x}_{t} = (x_{t,0}, x_{t,1}, ..., x_{t,n-1})$$

$$x_{t,i} = 2v_{t,i} - 1 , \quad i = 0,1, ..., n-1$$

(2.4)

The output of the noisy channel is represented by:

$$\mathbf{r}_{1}^{N} = (\mathbf{r}_{1}, \mathbf{r}_{2}, ..., \mathbf{r}_{N}) , \quad \mathbf{r}_{t} = (r_{t,0}, r_{t,1}, ..., r_{t,n-1})$$

$$(2.5)$$

$$r_{t,i} = x_{t,i} + \eta_{i} , \quad i = 0,1,...,n-1$$

where  $\eta_i$  is a zero-mean Gaussian random variable with variance  $\sigma^2$ . The channel is assumed to be an AWGN channel so each noise sample is independent from other noise samples.

The output of the decoder (estimated message sequence) is denoted by (we use "^" for representing the estimated variables):

$$\hat{\mathbf{c}} = (\hat{c}_1, \hat{c}_2, ..., \hat{c}_t, ..., \hat{c}_N)$$

(2.6)

In the ideal case  $\hat{\mathbf{c}}$  must be identical to  $\mathbf{c}$ .

As a general rule, the output of the MAP decoder is in log-likelihood ratio format defined as:

$$\Lambda(c_t) = \log \frac{\Pr\{c_t = 1 \mid \mathbf{r} \}}{\Pr\{c_t = 0 \mid \mathbf{r} \}}$$

(2.7)

The above soft output can be converted into a hard decision output by using the following criterion:

$$c_{t} = \begin{cases} 1 & \text{if } \Lambda(c_{t}) \ge 0 \\ 0 & \text{otherwise} \end{cases}$$

(2.8)

The MAP decoder starts decoding process from  $S_0 = 0$  producing output sequence  $\mathbf{x}_1^{\tau}$  and it ends in  $S_{\tau} = 0$  by using trellis termination technique. It is obvious that  $\tau$  must be equal to N + v.

The output sequence of the noisy channel is:

$$\mathbf{r}_{1}^{\tau} = (\mathbf{r}_{1}, \mathbf{r}_{2}, \dots, \mathbf{r}_{\tau}) \tag{2.9}$$

For each received sequence  $(\mathbf{r}_1^{\tau})$  using an AWGN we have:

$$\Pr\{ \mathbf{r}_{1}^{\tau} \mid \mathbf{x}_{1}^{\tau} \} = \prod_{j=1}^{\tau} R (\mathbf{r}_{j} \mid \mathbf{x}_{j})$$

(2.10)

where

$$R \left( \mathbf{r}_{j} \mid \mathbf{x}_{j} \right) = \prod_{i=0}^{n-1} \operatorname{Pr} \left\{ r_{j,i} \mid x_{j,i} \right\}$$

and

$$\Pr\{ r_{j,i} \mid x_{j,i} = -1 \} = \frac{1}{\sqrt{2\pi\sigma}} e^{-\frac{(r_{j,i}+1)^2}{2\sigma^2}}$$

(2.11)

$$\Pr\{ r_{j,i} \mid x_{j,i} = +1 \} = \frac{1}{\sqrt{2\pi}\sigma} e^{\frac{-(r_{j,i}-1)^2}{2\sigma^2}}$$

(2.12)

Let  $c_t$  be the information bit input to the encoder at time t, associated to transition from  $S_{t-1}$  to  $S_t$  producing  $\mathbf{v}_t$ . The MAP decoder estimates  $c_t$  based on the received sequence  $(\mathbf{r}_1^{\tau})$  as a soft output  $(\Lambda(c_t))$ :

$$\Pr\left\{ c_{t} = 0 \mid \mathbf{r}_{1}^{\tau} \right\} = \sum_{(l',l) \in B_{t}^{0}} \Pr\left\{ S_{t-1} = l', S_{t} = l \mid \mathbf{r}_{1}^{\tau} \right\}$$

$$= \sum_{(l',l) \in B_{t}^{0}} \frac{\Pr\left\{ S_{t-1} = l', S_{t} = l, \mathbf{r}_{1}^{\tau} \right\}}{\Pr\left\{ \mathbf{r}_{1}^{\tau} \right\}}$$

(2.13)

where  $B_i^0$  is the set of all possible transitions form  $S_{i-1}$  to  $S_i$  for which  $c_i$  is equal to 0.

$$\Pr\left\{ c_{t} = 1 \mid \mathbf{r}_{1}^{\tau} \right\} = \sum_{(l',l) \in B_{t}^{1}} \Pr\left\{ S_{t-1} = l', S_{t} = l \mid \mathbf{r}_{1}^{\tau} \right\}$$

$$= \sum_{(l',l) \in B_{t}^{1}} \frac{\Pr\left\{ S_{t-1} = l', S_{t} = l, \mathbf{r}_{1}^{\tau} \right\}}{\Pr\left\{ \mathbf{r}_{1}^{\tau} \right\}}$$

(2.14)

where  $B_t^1$  is the set of all possible transitions form  $S_{t-1}$  to  $S_t$  with  $c_t = 1$ .

It is possible to define the log-likelihood ratio based on the following joint probability function:

$$\rho_{t}(l',l) = \Pr\{S_{t-1} = l', S_{t} = l, \mathbf{r}_{1}^{\tau}\}, l', l = 0,1,...,(M,-1)$$

(2.15)

$$\Pr\left\{ c_{t} = 0 \mid \mathbf{r}_{1}^{\tau} \right\} = \sum_{(l',l) \in \mathcal{B}^{0}} \frac{\rho_{t}(l',l)}{\Pr\left\{ \mathbf{r}_{1}^{\tau} \right\}}$$

$$(2.16)$$

$$\Pr\left\{ c_{t} = 1 \mid \mathbf{r}_{1}^{\tau} \right\} = \sum_{(l',l) \in \mathcal{B}_{1}^{l}} \frac{\rho_{t}(l',l)}{\Pr\left\{ \mathbf{r}_{1}^{\tau} \right\}}$$

$$(2.17)$$

and

$$\Lambda(c_t) = \log \frac{\sum_{(l',l) \in B_t^1} \rho_t(l',l)}{\sum_{(l',l) \in B_t^0} \rho_t(l',l)}$$

(2.18)

In order to calculate the joint probability function ( $\rho_t(l',l)$ ), it is useful to define it as a function of 3 other probability functions as follows:

$$\alpha_{t}(l) = \Pr\left\{ S_{t} = l, \mathbf{r}_{1}^{t} \right\} , \quad \beta_{t}(l) = \Pr\left\{ \mathbf{r}_{t+1}^{\tau} \mid S_{t} = l \right\}$$

(2.19)

$$\gamma_t^i(l',l) = \Pr\{c_t = i, S_t = l \mid S_{t-1} = l'\}$$

,  $i = 0,1$  (2.20)

The joint probability can be rewritten as:

$$\rho_{t}(l',l) = \Pr\{S_{t-1} = l', S_{t} = l, \mathbf{r}_{1}^{\tau}\}

= \Pr\{\mathbf{r}_{t+1}^{\tau}, \mathbf{r}_{t}, \mathbf{r}_{1}^{t-1}, S_{t-1} = l', S_{t} = l\}

= \Pr\{\mathbf{r}_{t+1}^{\tau} \mid \mathbf{r}_{t}, \mathbf{r}_{1}^{t-1}, S_{t-1} = l', S_{t} = l\} \cdot \Pr\{\mathbf{r}_{t}, \mathbf{r}_{1}^{t-1}, S_{t-1} = l', S_{t} = l\}

= \Pr\{\mathbf{r}_{t+1}^{\tau} \mid S_{t} = l\} \cdot \Pr\{\mathbf{r}_{t}, \mathbf{r}_{1}^{t-1}, S_{t-1} = l', S_{t} = l\}

= \beta_{t}(l) \cdot \Pr\{\mathbf{r}_{t}, \mathbf{r}_{1}^{t-1}, S_{t-1} = l', S_{t} = l\}

= \beta_{t}(l) \cdot \Pr\{S_{t} = l, \mathbf{r}_{t} \mid \mathbf{r}_{1}^{t-1}, S_{t-1} = l'\} \cdot \Pr\{\mathbf{r}_{1}^{t-1}, S_{t-1} = l'\}

= \Pr\{\mathbf{r}_{1}^{t-1}, S_{t-1} = l'\} \cdot \beta_{t}(l) \cdot \Pr\{S_{t} = l, \mathbf{r}_{t} \mid S_{t-1} = l'\}

= \alpha_{t-1}(l') \cdot \beta_{t}(l) \cdot \sum_{i \in (0,1)} \gamma_{t}^{i}(l', l)$$

(2.21)

so

$$\Lambda(c_t) = \log \frac{\sum_{(l',l) \in B_t^1} \alpha_{t-1}(l') . \beta_t(l) . \gamma_t^1(l',l)}{\sum_{(l',l) \in B_t^0} \alpha_{t-1}(l') . \beta_t(l) . \gamma_t^0(l',l)}$$

(2.22)

$\alpha_{l}(l)$  can be calculated recursively using boundary conditions  $\alpha_{0}(0)=1$  and  $\alpha_{0}(l)=0$  for  $l \neq 0$ .

$$\alpha_{t}(l) = \Pr\{S_{t} = l, \mathbf{r}_{1}^{t}\}\$$

$$= \sum_{l'=0}^{M_{t}-1} \Pr\{S_{t-1} = l', S_{t} = l, \mathbf{r}_{1}^{t}\}\$$

$$= \sum_{l'=0}^{M_{s}-1} \Pr\{S_{t-1} = l', S_{t} = l, \mathbf{r}_{1}^{t-1}, \mathbf{r}_{t}\}\$$

$$= \sum_{l'=0}^{M_{s}-1} \Pr\{S_{t-1} = l', \mathbf{r}_{1}^{t-1}\} \cdot \Pr\{\mathbf{r}_{t}, S_{t} = l \mid S_{t-1} = l', \mathbf{r}_{1}^{t-1}\}\$$

$$= \sum_{l'=0}^{M_{t}-1} \alpha_{t-1}(l') \cdot \Pr\{\mathbf{r}_{t}, S_{t} = l \mid S_{t-1} = l'\}\$$

$$= \sum_{l'=0}^{M_{s}-1} \alpha_{t-1}(l') \cdot \sum_{i \in (0,1)} \Pr\{\mathbf{r}_{t}, c_{t} = i, S_{t} = l \mid S_{t-1} = l'\}\$$

$$= \sum_{l'=0}^{M_{s}-1} \alpha_{t-1}(l') \cdot \sum_{i \in (0,1)} \gamma_{t}^{i}(l', l)$$

$\beta_{\tau}(l)$  can be calculated recursively using boundary conditions of  $\beta_{\tau}(0) = 1$  and  $\beta_{\tau}(l) = 0$  for  $l \neq 0$ .

$$\beta_{t}(l) = \Pr\{\mathbf{r}_{t+1}^{r} \mid S_{t} = l\}$$

$$= \sum_{l'=0}^{M_{t}-1} \Pr\{S_{t+1} = l', \mathbf{r}_{t+1}^{r} \mid S_{t} = l\}$$

$$= \sum_{l'=0}^{M_{t}-1} \frac{\Pr\{S_{t+1} = l', \mathbf{r}_{t+1}^{r}, S_{t} = l\}}{\Pr\{S_{t} = l\}}$$

$$= \sum_{l'=0}^{M_{t}-1} \frac{\Pr\{S_{t+1} = l', \mathbf{r}_{t+1}^{r}, \mathbf{r}_{t+2}^{r}, S_{t} = l\}}{\Pr\{S_{t} = l\}}$$

$$= \sum_{l'=0}^{M_{t}-1} \frac{\Pr\{\mathbf{r}_{t+1} \mid S_{t+1} = l', \mathbf{r}_{t+2}^{r}, S_{t} = l\} \cdot \Pr\{S_{t+1} = l', \mathbf{r}_{t+1}, S_{t} = l\}}{\Pr\{S_{t} = l\}}$$

$$= \sum_{l'=0}^{M_{t}-1} \frac{\Pr\{\mathbf{r}_{t+1} \mid S_{t+1} = l'\} \cdot \Pr\{S_{t+1} = l', \mathbf{r}_{t+1}, S_{t} = l\}}{\Pr\{S_{t} = l\}}$$

$$= \sum_{l'=0}^{M_{t}-1} \frac{\beta_{t+1}(l') \cdot \Pr\{S_{t+1} = l', \mathbf{r}_{t+1} \mid S_{t} = l\} \cdot \Pr\{S_{t} = l\}}{\Pr\{S_{t} = l\}}$$

$$= \sum_{l'=0}^{M_{t}-1} \frac{\beta_{t+1}(l') \cdot \Pr\{S_{t+1} = l', \mathbf{r}_{t+1} \mid S_{t} = l\}}{\Pr\{S_{t} = l\}}$$

$$= \sum_{l'=0}^{M_{t}-1} \beta_{t+1}(l') \cdot \Pr\{S_{t+1} = l', \mathbf{r}_{t+1} \mid S_{t} = l\}$$

$$= \sum_{l'=0}^{M_{t}-1} \beta_{t+1}(l') \cdot \sum_{i \in (0,1)} \Pr\{c_{t+1} = i, S_{t+1} = l', \mathbf{r}_{t+1} \mid S_{t} = l\}$$

$$= \sum_{l'=0}^{M_{t}-1} \beta_{t+1}(l') \cdot \sum_{i \in (0,1)} \gamma_{t+1}^{i}(l', l)$$

also  $\gamma_t^i(l',l)$  can be calculated as follows:

$$\gamma_{t}^{i}(l',l) = \Pr\{S_{t} = l, \mathbf{r}_{t}, c_{t} = i \mid S_{t-1} = l'\}

= \frac{\Pr\{S_{t} = l, \mathbf{r}_{t}, c_{t} = i, S_{t-1} = l'\}}{\Pr\{S_{t-1} = l'\}}

= \frac{\Pr\{\mathbf{r}_{t} \mid S_{t} = l, c_{t} = i, S_{t-1} = l'\} \cdot \Pr\{S_{t} = l, c_{t} = i, S_{t-1} = l'\}}{\Pr\{S_{t-1} = l'\}}$$

(2.25)

$$= \frac{\Pr\{\mathbf{r}_{t} \mid \mathbf{x}_{t}\}.\Pr\{S_{t} = l, c_{t} = i, S_{t-1} = l'\}}{\Pr\{S_{t-1} = l'\}}$$

$$= \frac{\Pr\{\mathbf{r}_{t} \mid \mathbf{x}_{t}\}.\Pr\{c_{t} = i \mid S_{t} = l, S_{t-1} = l'\}.\Pr\{S_{t} = l, S_{t-1} = l'\}}{\Pr\{S_{t-1} = l'\}}$$

$$= \Pr\{\mathbf{r}_{t} \mid \mathbf{x}_{t}\}.\Pr\{\mathbf{x}_{t} \mid S_{t} = l, S_{t-1} = l'\}.\Pr\{S_{t} = l \mid S_{t-1} = l'\}$$

$$\Pr\{\mathbf{r}_{t} \mid \mathbf{x}_{t}\} = \frac{1}{\sqrt{2\pi}\sigma} \exp\left(-\frac{\sum_{j=0}^{1} \left(r_{t,j}^{i} - x_{t,j}^{i}(l)\right)^{2}}{2\sigma^{2}}\right)$$

(2.26)

With further expression:

$$\gamma_{t}^{i}(l',l) = \begin{cases} p_{t}(i) \exp\left(-\frac{\sum_{j=0}^{1} \left(r_{t,j}^{i} - x_{t,j}^{i}(l)\right)^{2}}{2\sigma^{2}}\right) & for (l,l') \in B_{t}^{i} \\ 0 & otherwise \end{cases}$$

$$(2.27)$$

where  $p_t(i)$  is a priori probability of  $c_t = i$ ,  $B_t^i$  is a set of all transitions from  $S_{t-1} = l'$  to  $S_t = l$  with  $c_t = i$  and  $x_{t,j}^i(l)$  is the encoder output associated with transitions of  $B_t^i$ .

### 2.1.2 Max-Log-MAP Algorithm

The standard MAP algorithm needs huge amount of memory and also uses too many non-linear mathematical operations and multiplications. Max-Log-MAP algorithm is an approximation of MAP algorithm that is easier in implementation. However, this algorithm

is not an optimal algorithm as MAP algorithm (about 0.2dB difference in the performance for 3GPP turbo codes).

Max-Log-MAP Algorithm utilizes logarithm format of  $\alpha_t(l)$ ,  $\beta_t(l)$  and  $\gamma_t^i(l',l)$  which are denoted as  $\overline{\alpha}_t(l)$ ,  $\overline{\beta}_t(l)$  and  $\overline{\gamma}_t^i(l',l)$  respectively.

$$\overline{\gamma}_{t}^{i}(l',l) = \log \gamma_{t}^{i}(l',l) \tag{2.28}$$

$$\overline{\alpha}_{t}(l) = \log \alpha_{t}(l)$$

$$= \log \sum_{l'=0}^{M_{s}-1} \sum_{i \in (0,1)} e^{\overline{\alpha}_{t-1}(l') + \overline{\gamma}_{t}^{i}(l',l)}$$

$$(2.29)$$

$$\overline{\beta}_{t}(l) = \log \beta_{t}(l)$$

$$= \log \sum_{l'=0}^{M_{s}-1} \sum_{i \in (0,1)} e^{\overline{\beta}_{t+1}(l') + \overline{\gamma}_{t+1}^{i}(l',l)}$$

(2.30)

and boundary conditions become:

$$\overline{\alpha}_0(0) = 0$$

and  $\overline{\alpha}_0(l) = -\infty$  for  $l \neq 0$  (2.31)

$$\overline{\beta}_{\tau}(0) = 0$$

and  $\overline{\beta}_{\tau}(l) = -\infty$  for  $l \neq 0$  (2.32)

Using these new definitions, the log-likelihood ratio (LRR) can be rewritten as follows:

$$\Lambda(c_t) = \log \frac{\sum_{l=0}^{M_s-1} e^{\overline{\alpha}_{t-1}(l') + \overline{\gamma}_t^1(l',l) + \overline{\beta}_t(l)}}{\sum_{l=0}^{M_s-1} e^{\overline{\alpha}_{t-1}(l') + \overline{\gamma}_t^0(l',l) + \overline{\beta}_t(l)}}$$

(2.33)

This log-likelihood ratio can be simplified by using the following approximation:

$$\log(e^{\delta_1} + e^{\delta_2} + \dots + e^{\delta_n}) \approx \max_{i \in \{1, 2, \dots, n\}} \delta_i$$

(2.34)

This maximum value can be calculated by applying (n-1) max(x,y) function recursively over each two values. So the LLR can be written as:

$$\Lambda(c_{t}) \approx \max_{l} \left[ \overline{\alpha}_{t-1}(l') + \overline{\gamma}_{t}^{1}(l',l) + \overline{\beta}_{t}(l) \right] - \max_{l} \left[ \overline{\alpha}_{t-1}(l') + \overline{\gamma}_{t}^{0}(l',l) + \overline{\beta}_{t}(l) \right]$$

(2.35)

where,

$$\overline{\alpha}_{t}(l') \approx \max_{l} \left\{ \overline{\alpha}_{t-1}(l') + \overline{\gamma}_{t}^{i}(l',l) \right\} \text{ for } 0 \le l' \le M_{s} - 1 , \quad i = 0,1$$

(2.36)

and

$$\overline{\beta}_{t}(l) \approx \max_{i} \left\{ \overline{\beta}_{t+1}(l') + \overline{\gamma}_{t+1}^{i}(l',l) \right\} \text{ for } 0 \le l' \le M_{s} - 1 \quad , \quad i = 0,1$$

(2.37)

### 2.1.3 Max\*-Log-MAP Algorithm

Because of using the max(x,y) approximation in calculating the maximum-likelihood ratio in the previous section, Max-Log-MAP algorithm is a sub optimal algorithm. It is possible to improve the performance of the decoder by using the Jacobian algorithm [13]:

$$\log(e^{\delta_{1}} + e^{\delta_{2}}) = \max(\delta_{1}, \delta_{2}) + \log(1 + e^{-|\delta_{1} - \delta_{2}|})$$

$$= \max(\delta_{1}, \delta_{2}) + f_{c}(|\delta_{1} - \delta_{2}|)$$

(2.38)

where  $f_c(.)$  is correction function that can be implemented as a simple look-up table. The performance of this Log-MAP algorithm is dependent on the number of the levels of the look-up table, but on the other hand multi-level look-up table can reduce the speed of the decoder. In most cases using a 3-level or 4-level look-up table, the performance of the Log-Max\*-MAP algorithm can be identical to the performance of the optimum MAP algorithm.

### 2.2 Interleaver (Permuter)

The function of the interleaver is to receive the N-bit sequence and rearrange it to construct a new N-bit sequence, which is applied to the input of the second encoder. Since the interleaver decorrelates the inputs of the two encoders [14], at the receiver side, after correcting some of the errors by means of parity bits of first encoder, we will be able to correct some remaining errors by using parity bits of the second encoder. There are two major points in choosing the interleaver; choosing an interleaver to obtain an output as uncorrelated as possible (with consideration of decoding constraints), and choosing the length of the output block code, N.

### 2.3 Iterative Decoding of Turbo Codes

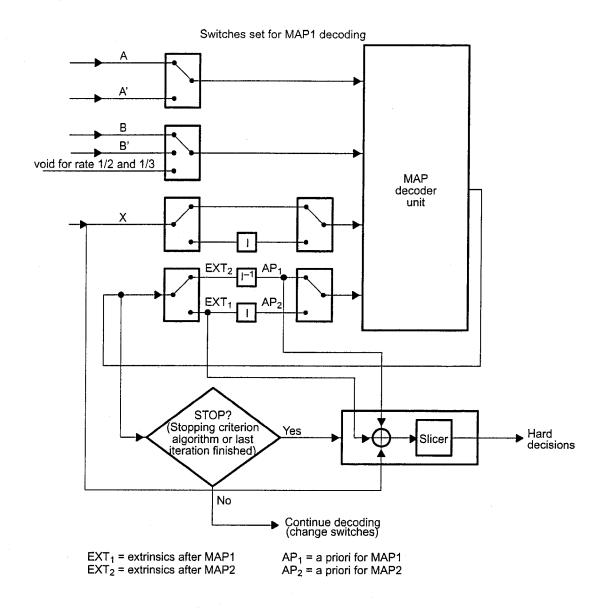

Iterative decoding consists of two serially concatenated MAP-based decoders, separated by an interleaver identical to that one at the encoder (Fig. 2.2). The inputs of the first MAP decoder are the received noisy information sequence  $\mathbf{r}_0$  and the parity sequence produced by the first encoder from the AWGN channel. The second MAP decoder uses the soft output sequence of the first MAP decoder as one of its inputs. Other inputs of the second decoder are an interleaved version of the received information sequence ( $\tilde{\mathbf{r}}_0$ ) and the received encoded sequence produced by the second encoder. The second decoder also produces a soft output that will be used as one of the inputs of the first decoder, and so on. This feedback-loop is the distinguishing feature of turbo decoding algorithm. The name of "Turbo Code" is derived from the principle of the turbo engine that is using some kind of feedback of the engine output at its input.

Fig. 2.2: An iterative turbo decoding system using MAP decoder

After performing a certain number of iterations, there will be no further improvement in decoding performance, so the turbo decoder stops the decoding process and makes a hard decision on the information bits based on the last iteration soft output sequence [15,16].

It is possible to write the soft output of each of those MAP decoders as follows:

$$\Lambda_{1}(c_{t}) = \log \frac{\sum_{l',l=0}^{M_{s}-1} \alpha_{t-1}(l') \cdot \beta_{t}(l) \cdot p_{t}^{1}(1) e^{\left(-\sum_{j=1}^{L} \left(r_{t,j} - x_{t,j}^{1}(l)\right)^{2} / 2\sigma^{2}\right)}}{\sum_{l',l=0}^{M_{s}-1} \alpha_{t-1}(l') \cdot \beta_{t}(l) \cdot p_{t}^{1}(0) e^{\left(-\sum_{j=1}^{L} \left(r_{t,j} - x_{t,j}^{0}(l)\right)^{2} / 2\sigma^{2}\right)}}$$

(2.39)

where  $p_t^1(i)$  is the a priori probability for  $c_t = i$ . In the first iteration of the first decoder, it is reasonable to assume that  $p_t^1(0) = p_t^1(1) = 1/2$ .  $\Lambda_1(c_t)$  can be written as:

$$\Lambda_{1}(c_{t}) = \log \frac{p_{t}^{1}(1)}{p_{t}^{1}(0)} + \log \frac{\sum_{l',l=0}^{M_{s}-1} \alpha_{t-1}(l').\beta_{t}(l).e^{\left(-\left(\left(r_{t,0}-x_{t,0}^{1}(l)\right)^{2}+\sum\limits_{j=1}^{L}\left(r_{t,j}-x_{t,j}^{1}(l)\right)^{2}\right)/2\sigma^{2}}\right)}$$

$$\sum_{l',l=0}^{M_{s}-1} \alpha_{t-1}(l').\beta_{t}(l).e^{\left(-\left(\left(r_{t,0}-x_{t,0}^{0}(l)\right)^{2}+\sum\limits_{j=1}^{L}\left(r_{t,j}-x_{t,j}^{0}(l)\right)^{2}\right)/2\sigma^{2}}\right)}$$

(2.40)

Since this code is systematic,  $x_{t,0}^i$  is independent of trellis diagram and state (l). Using BPSK modulation  $x_{t,0}^0$  is equal to -1 and  $x_{t,0}^1$  is equal to +1. LLR becomes:

$$\Lambda_1(c_t) = \log \frac{p_t^1(1)}{p_t^1(0)} + \frac{2}{\sigma^2} r_{t,0} + \Lambda_{1e}(c_t)$$

(2.41)

where

$$\Lambda_{1e}(c_{t}) = \log \frac{\sum_{l',l=0}^{M_{s}-1} \alpha_{t-1}(l').\beta_{t}(l).e^{\left(-\sum_{j=1}^{l} (r_{t,j} - x_{t,j}^{1}(l))^{2} / 2\sigma^{2}\right)}}{\sum_{l',l=0}^{M_{s}-1} \alpha_{t-1}(l').\beta_{t}(l).e^{\left(-\sum_{j=1}^{l} (r_{t,j} - x_{t,j}^{0}(l))^{2} / 2\sigma^{2}\right)}}$$

(2.42)

$\Lambda_{1e}(c_t)$  is called *extrinsic information*. This value does not contain the information of the received data bit at time  $t(r_{t,0})$ . This is the information that is produced by one MAP decoder constituent and is used by the other one as the input.

The interleaved version of the first decoder's extrinsic information  $(\tilde{\Lambda}_{1e}(c_t))$  is used as the a priori probability for the second decoder. The  $p_t^2(i)$  is the a priori probability for  $c_t = i$  of the input information bits for the second decoder

$$\tilde{\Lambda}_{1e}(c_t) = \log \frac{p_t^2(1)}{p_t^2(0)}$$

,  $p_t^2(1) = 1 - p_t^2(0)$  (2.43)

It is straight forward to write:

$$p_{t}^{2}(1) = \frac{e^{\tilde{\Lambda}_{1e}(c_{t})}}{1 + e^{\tilde{\Lambda}_{1e}(c_{t})}}$$

(2.44)

$$p_t^2(0) = \frac{1}{1 + e^{\tilde{\Lambda}_{1e}(c_t)}}$$

(2.45)

and for the second decoder, the LLR can be written:

$$\Lambda_2(c_t) = \log \frac{p_t^2(1)}{p_t^2(0)} + \frac{2}{\sigma^2} \tilde{r}_{t,0} + \Lambda_{2e}(c_t)$$

(2.46)

$$\Lambda_{2}(c_{t}) = \tilde{\Lambda}_{1e}(c_{t}) + \frac{2}{\sigma^{2}}\tilde{r}_{t,0} + \Lambda_{2e}(c_{t})$$

(2.47)

The extrinsic information of the second MAP decoder is interleaved and used as the a priori probability for the first MAP decoder. By initializing  $\Lambda_{2e}^{(0)}(c_t) = 0$  in the first iteration, and performing a definite maximum number of iterations, turbo decoder stops the decoding process and makes a hard decision based on the last iteration's soft output.

### 2.4 Iterative Nature of Turbo Decoder

The most important property of the turbo decoder is its iterative nature [16,17]. This means that for decoding a frame, the turbo decoder performs several iterations. For the first iteration, it assumes that the probabilities of 0 and 1 are equal and based on the channel information bits it produces a soft decision output for each data bit. For other iterations, the decoder will use the soft output of the other decoder as the a priori probability.

In each iteration, the turbo decoder improves the SER or BER performance in comparison with the previous iterations, and it can correct more number of erroneous bits. As a result, the more number of iterations the turbo decoder can perform for each frame, the better BER it can achieve. But the number of required iterations per each frame is a random variable, and it is not possible to set the turbo decoder to perform a fixed number of iterations per each frame and have an optimum receiver in terms of SER or BER.

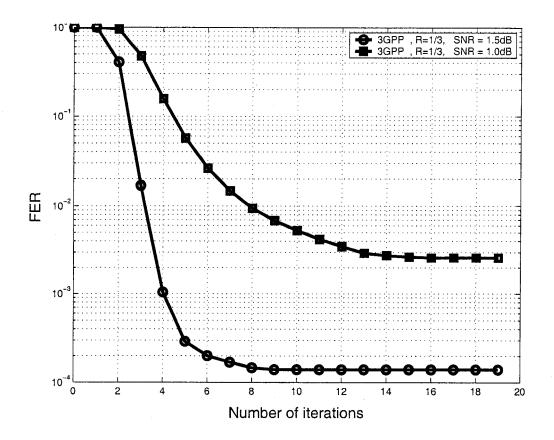

As mentioned before, the performance of these kinds of iterative decoders is directly related to the number of iterations that they perform to decode a frame. Here, we have simulated the 3GPP turbo code for several values of signal-to-noise ratio (SNR) [18], in order to use them as practical examples in the next chapters (the details of these computer-based simulations will be given later). Table 1 shows the percentage of the 3GPP packets being corrected at any given iteration.

For instance, for SNR = 1.5 dB in Table 1, if there is a turbo decoder capable of performing a maximum of 3 iterations per frame, it will be able to correct 98.308% (0.004+59.453+38.851) of the frames. As a result, the FER is equal to 0.01692, but if this decoder was capable of performing a maximum of 4 iterations per frame (one more iteration), the FER would be improved more than 10 times (0.00104).

Table 2.1: Probabilities (%) of correction of a 3GPP frame vs. number of iterations for several SNRs on an AWGN channel (k=1440, r=1/3).

| Number of iterations | SNR = 1.0 dB | SNR = 1.5 dB | SNR = 2.0 dB |

|----------------------|--------------|--------------|--------------|

| 1                    | 0.000        | 0.004        | 1.467408     |

| 2                    | 4.615        | 59.453       | 95.48462     |

| 3                    | 47.825       | 38.851       | 3.028626     |

| 4                    | 31.920       | 1.588        | 0.016247     |

| 5                    | 9.946        | 0.077        | 0.001644     |

| 6                    | 3.059        | 0.007        | 0.000483     |

| 7                    | 1.162        | 0.002        | 0.000000     |

| 8                    | 0.528        | 0.002        | 0.000000     |

| 9                    | 0.258        | 0.002        | 0.000000     |

| 10                   | 0.159        | 0.000        | 0.000000     |

| 11                   | 0.094        | 0.000        | 0.000000     |

| 12                   | 0.085        | 0.000        | 0.000000     |

| 13                   | 0.056        | 0.000        | 0.000000     |

| 14                   | 0.034        | 0.000        | 0.000000     |

| Not-correctable      | 0.259        | 0.014        | 0.000967     |

From Table 2.1, it can be seen that for SNR of 1.5 dB, there is no frame that can be corrected in 10, 11, 12, 13 and 14 iterations. As a result, setting the maximum number of iterations to more than 9 (this parameter will be described in detail in Chapter 3) for this value of SNR, will not change the performance of the turbo decoder, and also in multichannel decoding systems, it will make it worse.

### 2.5 Early Stopping Criteria

Some of the turbo decoders are capable of performing various number of decoding iterations for different input frames in order to achieve the desired performance (BER or FER), while others only perform a fixed number of iterations for each frame. As indicated in the previous sections, the required number of iterations for each frame is a random

variable with a specific distribution function based on the channel characteristic, coding specifications, etc.

The ideal case for the turbo decoder is that the decoder has the source information and can compare it with the decoded sequence in order to determine if there is any symbols (bits) in error or not. In this case, if the sequence is decoded correctly, the turbo decoder stops decoding process and makes a hard decision based on the last soft output. However, since the source information is not accessible to the receiver (had it been available, the whole communication process would have been futile), this is not a realizable method.

One of the techniques that can give the turbo decoder an estimation of how correct a frame is, is stopping criterion. At the end of each iteration for each frame, the decoder checks the condition of the stopping criterion; if the condition is satisfied the turbo decoder stops decoding and assumes that the output of the last iteration is reliable enough to make a hard decision based on it and there will not exist any improvement in SER or BER by performing more iterations on the current frame; otherwise the turbo decoder continues decoding process and performs another iteration on the current frame. To prevent an endless loop of performing iterations (when the stopping criterion is never satisfied or the input frame is not a decodable one), it is possible to define a maximum number of iterations per frame. After performing this number of iterations for each frame, if the stopping criterion is not yet satisfied, the turbo decoder stops decoding process and makes a hard decision based on the output of the last iteration, or in some cases turbo decoder assumes that this frame is in error and it is not possible to make a decision based on this frame (this depends on the application).

There are several proposed stopping criteria so far [19,8] such as soft-decision rules, hard-decision rules and Cyclic Redundancy Check (CRC) rule. Besides all of the realizable

stopping criteria, there is an unrealizable stopping rule that can be used as a limit for the performance of other stopping criteria. We call this unrealizable stopping criterion "Genie rule". Theoretically, it is assumed that genie rule can recognize whether the decoded sequence is corrected or not based on the knowledge of the original transmitted sequence, and it can immediately stop the decoding process as soon as that specific frame becomes corrected. In the following, some of the realizable stopping criteria are described in detail.

In one of the soft-decision rules, at the end of each iteration, the average value of the extrinsic information of the second decoder component  $(\tilde{\Lambda}_{2e}(c_i))$  is compared to a given threshold  $(\theta)$ . This stopping rule is satisfied at the earliest iteration that:

$$\frac{1}{N} \sum_{i=1}^{N} |\tilde{\Lambda}_{2e}(c_i)| \ge \theta \tag{2.48}$$

In [8], it has been shown that using the above stopping criterion, will add on the average less than one iteration to the number of required iterations to correct each input channel (in comparison with the genie rule).

In another soft-decision rule, the minimum of the extrinsic value of the second constituent decoder  $(\tilde{\Lambda}_{2e}(c_i))$  for all of the symbols (bits) is compared to a threshold  $(\theta)$ . The decoding procedure will stop at the moment that the following condition is satisfied:

$$\min_{1 \le i \le N} \left[ |\tilde{\Lambda}_{2e}(c_i)| \right] \ge \theta \tag{2.49}$$

In one of the hard-decision rules, the decoder stops the decoding process as soon as the hard decision at the end of the current iteration is identical to the hard decision of the previous iteration.

$$\hat{c}_i^n = \hat{c}_i^{n-1} \quad , \quad 1 \le i \le N \tag{2.50}$$

In CRC stopping criterion, a specific number of CRC bits is appended to the end of each information sequence at the input of the turbo encoder. At the decoder, after performing each iteration, the decoder makes hard decision of the sequence and checks the CRC bits for error. If decoder detects no error in those CRC bits, it assumes that the output of the last iteration is reliable enough to make the final decision and it stops the decoding process.

# 2.6 Summary

In this chapter, BCJR algorithm was presented and three versions of this algorithm were described. Then, the turbo interleaver and turbo code structure were discussed. After that, the iterative nature of turbo decoder was explained using some computer-based simulations. And finally, the concept of stopping criteria and some of those rules were presented in detail.

#### **MULTI-CHANNEL PROCESSING**

In some communication systems, the turbo decoder receives several input frames at the same time, either from one transmitter (like another mobile base station) or from several transmitters (like mobile handset terminals). These input frames are usually different and have to be decoded separately. To obtain a better performance in these kinds of systems, multi-channel processing techniques are being used widely.

In order to process all of the frames in real time, the maximum turbo decoding delay for each frame is set equal to the period of each frame (T), so there is no need for data buffering in the receiver. As it was mentioned in the previous chapter, each frame needs a specific number of iterations to be decoded correctly. This number of iterations is different from one frame to another.

If the turbo decoder takes ( $\tau$ ) seconds to perform one iteration, so the total number of iterations that the turbo decoder can perform to decode all of ( $n_{ch}$ ) frames in one time slot (T) will be:

$$n_{ii} = |T/\tau| \tag{3.1}$$

### 3.1 Ideal Scheme

When using one decoder to decode all the channels, the ideal situation is that the decoder has the information about all frames (channels) and knows how many iterations each frame needs to be decoded correctly. So, the decoder first decodes the frame that needs less number of iterations, and after decoding it, it decodes the frame that needs also less number of iterations among all of the remaining frames and so on. This ideal method is optimum.

But, the main problem is that the decoder neither has the capability to determine that a specific channel has been corrected nor knows how many iterations a frame needs to be corrected. As explained in the previous chapter, early stopping criteria can approximate these parameters, but still to use the stopping criteria the turbo decoder has to perform a few iterations for each frame, and it does not have access to this information prior to the decoding process. This pre-decoding process will decrease the number of available iterations for the rest of the process.

No other schemes can have better performance than this ideal (unrealizable) scheme. In this thesis, this scheme will be used as the theoretical limit for analyzing the performance of other schemes.

### 3.2 Fixed-Iteration Scheme

Fixed-Iteration scheme is the traditional turbo processing scheme. It is designed based on the decoding algorithm for a single input channel (single frame processing) system. In this method, for each input channel, there is one turbo decoder capable of performing a definite number of iterations  $(n_f)$ . So, for an  $n_{ch}$ -channel system, there will be  $n_{ch}$  completely independent turbo decoders (Fig. 3.1).

Fig. 3.1: An example of the fixed-iteration method of multi-channel decoding, consisting of 5 fixed-iteration turbo decoders with 4 iterations per channel ( $n_f$  =4), i.e., there is a total of 20 iterations for all channels ( $n_u$  =20).

This decoding scheme is exactly equivalent to the scheme using a single turbo decoder capable of performing a total of  $n_{ii}$  iterations in each time slot (frame period). The  $n_{ii}$  is determined as follows:

$$n_f = \lfloor n_{it} / n_{ch} \rfloor \tag{3.2}$$

This single turbo decoder performs a fixed number of iterations  $(n_f)$  for decoding each frame.

The implementation of this scheme is very simple and straightforward. The main disadvantage of this scheme is its performance. This disadvantage can be explained by means of an example; assume that  $n_f$  is equal to 4. There will be some input frames that need less number of iterations to be decoded. For instance, if a frame needs 2 iterations to be decoded, the turbo decoder decodes it in 2 iterations and spends the remaining 2 iterations on this frame without any gain or improvement. On the other hand, there may exist some other frames that need more than  $n_f$  iterations (e.g., 5 iterations) to be decoded. So, the decoder performs 4 iterations on them and leaves these frames in error. In summary, the turbo decoder is idle for early-decoded frames while it does not have enough iterations to perform for the late decodable frames.

# 3.3 Serial Processing Scheme

The multi-channel processing algorithm that we call *serial processing scheme* is based on the decoding method for a single-channel system using the stopping criteria technique explained in Chapter 2. The decoding procedure is as follows: the decoder starts decoding the first input frame and performs some iterations on this frame until the stopping criterion is satisfied; at this point the decoder assumes that the frame has been decoded correctly and it makes the hard estimation on the frame. After decoding the first channel, the decoder repeats the same procedure for the second frame and other frames one after the other (Fig. 3.2).

On the average, the decoder is supposed to decode each channel in  $n_f$  iterations and if some of the channels are corrected in less than  $n_f$  iterations, the decoder can save these extra iterations and use them for decoding other frames that need more than  $n_f$  iterations.

This method is much better than the fixed-iteration scheme, because the decoder can use the idle time left after decoding the easier frames to correct the remaining frames. As a result, with the same total number of iterations as the fixed-iteration scheme, we can achieve a better BER or with the same performance, the decoder can decode more channels (increasing the throughput of the decoder).

Fig. 3.2: An example of the serial processing scheme of multichannel decoding, consisting of a single turbo decoder.

In this method, there are some cases where the decoder cannot perform even a single iteration on some of the channels. As the worst-case scenario, assume that the first frame is not correctable in less than  $n_u$  iterations (the total number of available iterations for one time slot), so the decoder will spend all its time to decode this frame, and cannot do any iterations on other frames. Therefore all of the frames will be in error. To avoid this problem, we define Mipch as the maximum number of iterations per channel (Mipch must be less than  $n_u$ ). It means that if the decoder cannot decode a frame after Mipch iterations, it will stop processing current frame and will go to the next frame. This Mipch is one of the design parameters, which has to be set by the designer. In the next chapter, several

computer-based simulations results are presented with different values of *Mipch* for different SNRs.

Since this scheme -even when using the maximum number of iterations per channelis a serial processing technique, there are some cases where the turbo decoder cannot

decode the frames in the best way. We will explain these situations using an example:

assume that there are 5 input channels  $(n_{ch}=5)$  and the turbo decoder is capable of

performing 20 iterations  $(n_{it}=20)$  and the maximum number of iterations has been set to 7. (Mipch=7). Suppose that the input frames need 7, 6, 8, 4 and 2 iterations to be corrected.

Using the described scheme, the turbo decoder performs the maximum number of iterations (Mipch=7) to correct the first frame, after that, it performs 6 iterations to decode the

second frame, and next, it performs the maximum number of iterations (Mipch=7) to

decode the third frame but this frame cannot be corrected with 7 iterations, and at the end

there is not any iterations left to decode the forth and fifth frames. As a result, the turbo

decoder corrects only 2 frames out of 5. If the decoder could decode the forth and fifth

frame prior to third frame, 4 frames instead of 2, would be corrected. But since this is a

serial processing technique, it always starts decoding process from the first received frame

to the last and it is not possible to change the order of the frames in the decoding process.

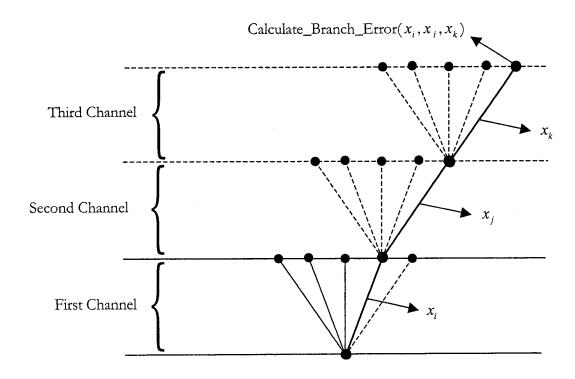

### 3.4 Parallel Processing Scheme

In the previous method, the decoder decodes the channels serially (it decodes the first one completely, and goes to the next one and so on.), but in this new method, the decoder decodes channels in parallel. This means that the decoder performs one iteration for each frame, and checks whether that frame satisfies the stopping criterion or not. For the first

round, it performs one iteration for each frame, and for the second and other rounds it will do exactly the same procedure but only for the uncorrected frames (Fig. 3.3).

In the serial processing scheme, despite the introduction of a maximum number of iterations per channel, there are some cases where the first frames need more than the average number of iterations as explained before. So probably, the decoder cannot decode the last frames (which may be correctable even in one or two iterations), due to the lack of required iterations. In this new scheme the turbo decoder decodes the frame that needs least number of iterations first.

Although the performance of this scheme is much better than the serial processing algorithm (it will be discussed in detail in the next chapter), in the DSP implementation chapter a new algorithm based on a combination of these two schemes will be suggested which is optimum in terms of number of memory accesses.

Fig. 3.3: An example of the parallel processing scheme for multichannel decoding, consisting of a single turbo decoder.

# 3.5 Multi-Channel Schemes for Single Channel Systems

The above parallel processing schemes not only can improve the performance and/or throughput of the multi-channel systems, but also can be very useful for single channel turbo decoding systems with the same benefits.

With a very simple buffering technique, it is possible to convert a single channel system to a multi-channel one and apply all of the discussed schemes to it. For example, a channel with a data rate of 2 Mbps can be assumed as a 10-channel system with the data rates of 200 Kbps for each channel (Fig. 3.4). As a result, one turbo decoder can be utilized to decode all of the 10 channels at the same time. The serial to parallel converter part consists of 10 buffers each capable of storing a given number of frames (for example two) at a time. The input frames will be placed in order from the first buffer to the last. This process will be repeated at each time slot. When the frame at the top of a specific buffer unit is processed, this frame will be erased and the frames in that buffer will be shifted one place up and one empty place will be add to the end of the buffer. Each of these buffers is considered as one channel and a multi-channel processing scheme will be applied to these simulated channels.

Fig. 3.4: An example of converting a one-channel system to a multi-channel one by using 10 buffers.

The only critical issue in this case, is the latency of the decoder, because the first input frame (frame 0F in Fig. 3.4) should be buffered until other 9 frames (1F...9F in Fig. 3.4) are received in order to start the decoding process. So the maximum acceptable latency of the system determines the maximum number of channels that can be assumed:

Maximum Number of channels =

$$\frac{Maximum\ Latency}{The\ Frame\ Period}$$

(3.3)

# 3.6 Summary

At the beginning of this chapter, the multi-channel turbo decoding system was described, and then in order to improve the performance and/or throughput of this system some multi-channel processing schemes were introduced. At the end, it was explained how to use these schemes even for a single channel system.

# Chapter 4

#### **COMPUTER SIMULATIONS**

In this chapter, we will talk about two different turbo coding standards; 3GPP and DVB/RCS. Next, we will simulate a simple turbo decoder for each of these standards for several SNRs and code rates in order to obtain their FER. We will describe the computer algorithms that we use to simulate the proposed multi-channel processing schemes. At the end, we will simulate all those multi-channel processing schemes and will discuss their performance in detail.

#### 4.1 3GPP Standard

Second Generation (2G) mobile communication systems, which have been designed for mobile digital telephony, have a very low data capacity [20]. For example, GSM supports only data rates up to 9.6 Kbps. In order to transmit video and image on a mobile

communication system, third generation (3G) standard has been proposed, which is capable of transmitting data rates up to 2 Mbps.

The most important step in utilizing this new technology was its standardization process between various regional and global operators. International Telecommunication Union (ITU), which is the final organization responsible for adopting standards in telecommunication area, set December 1998 as the deadline for submitting the 3G standard proposals for all of organizations and countries around the world. The family of 3G standards, which was approved later by ITU, is called IMT-2000 (International Mobile Telecommunications for the year of 2000).

European Telecommunication Standards Institute (ETSI) is the organization responsible for developing telecommunication standards (e.g. GSM) in Europe. ETSI proposed UMTS (Universal Mobile Telecommunications System) standard as the 3G candidate for the IMT-2000 (Table 4.1). UMTS is an evolutionary path form the old 2G (e.g. GSM) to the new 3G and allows the 2G operators to keep their infrastructures and investments during the upgrade process from 2G to 3G systems.

Table 4.1: UMTS key parameters

| UMTS parameters        | FDD                                   | TDD     |  |  |  |

|------------------------|---------------------------------------|---------|--|--|--|

| Multiple access scheme | W-CDMA                                | TD-CDMA |  |  |  |

| Crrier spacing         | 4.4-5.2 MHz                           | 5 MHz   |  |  |  |

| Chip rate              | 3.84 Mchip/s (Mcps)                   |         |  |  |  |

| Spreading factor range | 4 – 512                               | 1 – 16  |  |  |  |

| Modulation             | QPSK                                  |         |  |  |  |

| Pulse shaping          | Root raised cosine, roll-off = $0.22$ |         |  |  |  |

| Frame length           | 10 ms                                 |         |  |  |  |

| Timeslots per frame    | 15                                    |         |  |  |  |

Unlike Japan and Europe, there is not any nation-wide 2G standard in USA. In the USA there are three main 2G standards; TDMA-based standard (IS-136), CDMA-based standard (IS-91) and GSM derivative standard (PSC1900). CDMA2000 (Code Division Multiple Access for the year of 2000) and UWC-136 were U.S. proposals to the ITU as the evolutions of IS-95 and IS-136, respectively.

In 1998, 3<sup>rd</sup> Generation Partnership Project (3GPP) was established to harmonize the various 3G W-CDMA proposals based on the GSM core network. This organization was founded by almost all of the major countries in the telecommunication field (Japan, Europe, USA, ...). In order to merge Japanese 3G and UMTS standards into a single standard, this organization proposed 3GPP and since that time, it has been developing and refining this standard. The 3GPP2 organization was established around the CDMA2000 and it proposed 3GPP2 standard. In 1999, Operator Harmonization Groupe (OHG) proposed a harmonization between 3GPP and 3GPP2, called G3G, in order to let CDMA2000 and UMTS, work together.

# 4.1.1 3GPP Channel Coding

Information blocks, sent as the input data to the channel encoder, are denoted by  $O_{ir1}, O_{ir2}, ..., O_{irK_i}$ ; where i is the transport channel number, r is the code block number, and  $K_i$  is the number of information bits in each code block and the number of code blocks on transport channel i, is denoted by  $C_i$  [18]. After encoding, the bits are denoted by  $y_{ir1}, y_{ir2}, ..., y_{irY_i}$ , where  $Y_i$  is the number of encoded bits. The relationship between  $O_{irk}$  and  $y_{irk}$  and between  $K_i$  and  $Y_i$  is dependent on the channel coding scheme. The following channel coding schemes can be applied to transport channels; convolutional

coding, turbo coding and no coding. Use of coding scheme and coding rate for different types of transport channel is shown in Table 4.2. The value of  $Y_i$  for each coding scheme is:

- $\Box$  Convolutional coding with rate 1/2:  $Y_i = 2 \times K_i + 16$ ; rate 1/3  $Y_i = 3 \times K_i + 24$ ;

- □ Turbo coding with rate 1/3:  $Y_i = 3 \times K_i + 12$ ;

- $\square$  No coding  $Y_i = K_i$ .

Table 4.2: Usage of channel coding scheme and coding rate.

| Type of transport channel | Coding scheme        | Coding rate |  |  |  |

|---------------------------|----------------------|-------------|--|--|--|

| Broadcat channel          |                      | 1/2         |  |  |  |

| Paging channel            | Convolutional coding |             |  |  |  |

| Random Access channel     | Convolutional coding |             |  |  |  |

| Dedicated Channel,        |                      | 1/3, 1/2    |  |  |  |

| Downlink Shared Channel,  | Turbo coding         | 1/3         |  |  |  |

| Forward Access Channel    | No Coding            |             |  |  |  |

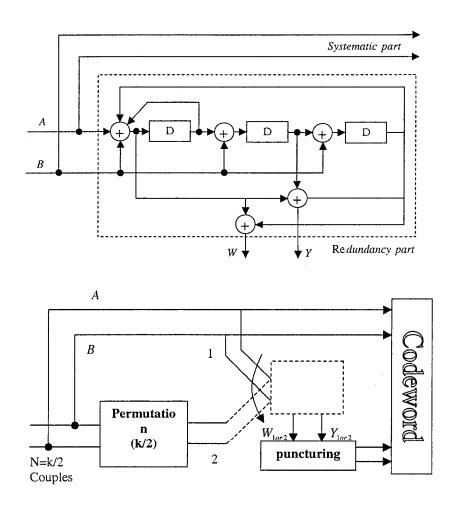

# 4.1.2 Turbo Coding Option of 3GPP

The turbo decoding scheme uses a Parallel Concatenated Convolutional Code (PCCC) with two 8-state constituent encoders and one turbo code internal interleaver. The coding rate of the turbo encoder is 1/3. The structure of turbo coder is illustrated in Fig. 4.1. the generating function is,

$$G(D) = \left[1, \frac{g_1(D)}{g_0(D)}\right]$$

(4.1)

$$g_0(D) = 1 + D^2 + D^3$$

,  $g_1(D) = 1 + D + D^3$

the initial value of the shift registers of the 8-state constituent encoders shall be all zeros when starting to encode the input bits.

Fig. 4.1: Structure of rate 1/3 Turbo coder (dotted lines apply for trellis termination only)

The turbo encoder output sequence is:

$$x_1, z_1, z'_1, x_2, z_2, z'_2, \dots, x_K, z_K, z'_K$$

(4.2)

where  $x_1, x_2, ..., x_K$  are the input bits to the first constituent encoder and the interleaver, K is the number of bits, and  $z_1, z_2, ..., z_K$  and  $z_1', z_2', ..., z_K'$  are the output bits from the first and the second 8-state constituent encoders, respectively.

The output bits from the interleaver are denoted by  $x'_1, x'_2, ..., x'_K$ , and these bits are applied to the second 8-state constituent encoder.

The 3GPP turbo decoder consists of two MAP decoders as described in Chapter 2.

#### 4.1.3 Trellis Termination for 3GPP Turbo Codes

In order to have a better performance, trellis termination can be used in 3GPP turbo coding. Trellis termination is performed by taking the tail bits from the shift registers feedback after all information bits are encoded. Tail bits are padded after the encoding of information bits. The first three tail bits shall be used to terminate the first constituent encoder (upper switch of Fig. 4.1. in lower position) while the second constituent encoder is disabled. The last three tail bits shall be used to terminate the second constituent encoder (lower switch of Fig. 4.1. in lower position) while the first constituent encoder is disabled. So the transmitted bits for trellis termination shall be:

$$x_{K+1}, z_{K+1}, x_{K+2}, z_{K+2}, x_{K+3}, z_{K+3}, x'_{K+1}, z'_{K+1}, x'_{K+2}, z'_{K+2}, x'_{K+3}, z'_{K+3}$$

$$(4.3)$$

### 4.1.4 3GPP Turbo Code Interleaver

The 3GPP turbo code internal interleaver functions as follows: applying input bits to a rectangular matrix with padding, performing intra-row and inter-row permutations of the rectangular matrix, and producing the output bits from the rectangular matrix with pruning.

The input bits to the turbo code internal interleaver are denoted by  $x_1, x_2, x_3, ..., x_K$ , where K is the number of information bits and takes a value between 40 and 5114. The relationship between the input bits to the turbo code internal interleaver and the input bits to the encoder is defined by  $x_K = o_{irk}$  and  $K = K_i$  [18].

#### 4.1.5 3GPP Simulation Results

These simulation results are based on the 3GPP turbo codes using a simple 3GPP decoder. These simulations were run on a "Sun-Blade-1000 (dual-processor)" with a "SUNOS 5.8" operating system and "GCC 2.95" C++ compiler.

In Fig. 4.2, the performance (FER) of 3GPP turbo code versus the number of iterations per frame has been shown. The frame length is equal to 1440, code rate is 1/3 and we have chosen an AWGN channel model. We will use the results of these simulations as the inputs of the multi-channel processing simulations.

Fig. 4.2: 3GPP frame error rate (FER) vs. number of iterations per frame for several SNRs on an AWGN channel (k=1440, r=1/3).

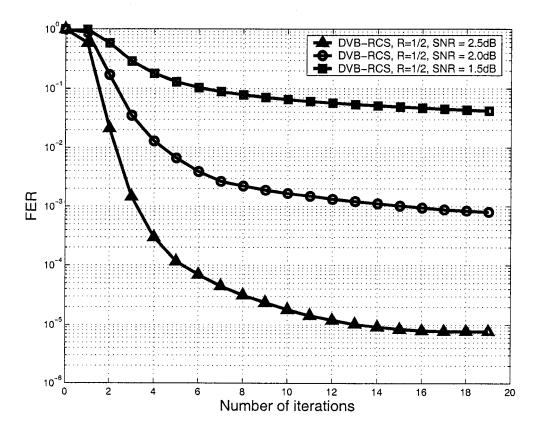

## 4.2 DVB/RCS Standard

Digital Video Broadcasting for Return Channel via Satellite (DVB/RSC) has been proposed by the DVB Committee for the satellite communication systems [21]. ETSI (European Telecommunication Standards Institute) has also a DVB/RCS standard [22] to provide two-way, full-IP and asymmetric communications via satellite in order to be used in the countries where Asymmetric Digital Subscriber Line (ADSL) and cable modem are not economically capable of covering more than 25% of the demands. By using this standard, a large number of small terminals will be capable of sending *return* signals to a

central gateway and at the same time, receiving IP data from that gateway on the *forward* link in the DVB/MPEG2 (Digital Video Broadcasting/Moving Picture Expert Group-2) format. In DVB/RCS systems, the quality of service and the cost of terminals are almost independent of the distance of the central gateway and terminals. This advantage puts satellites in a favorable position. The speed of the return channel for DVB/RCS standard can range from 144 Kbps to 2 Mbps and it is shared between all terminals sending small packets using MF-TDMA (Multi-Frequency - Time Division Multiple Access)/DAMA (Demand-assigned Multiple Access) techniques. Use of Turbo Codes is also an option in DVB/RCS.

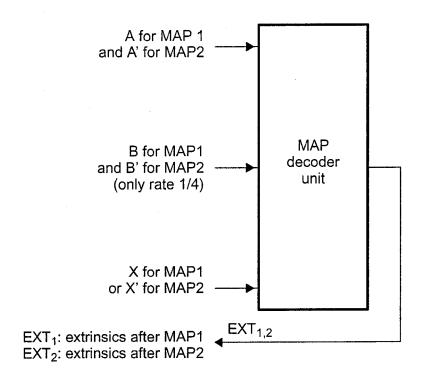

# 4.2.1 Turbo Coding Option of DVB/RCS

The DVB/RCS turbo encoder is depicted in Fig. 4.3. It uses double binary Circular Recursive Systematic Convolutional (CRSC) codes. The most significant bit (MSB) of the first byte, after the burst preamble, is assigned to A, the next bit to B and so on for the remaining of the burst content.