#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

**UMI**°

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, Mi 48106-1346 USA 800-521-0600

#### STATIC ANALYZER - A DESIGN TOOL FOR TROM

#### HONGJING TAO

A THESIS

IN

THE DEPARTMENT

OF

COMPUTER SCIENCE

# Presented in Partial Fulfillment of the Requirements For the Degree of Master of Computer Science Concordia University Montréal, Québec, Canada

AUGUST 1996 © HONGJING TAO, 1996

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre reférence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-44886-X

#### **Abstract**

#### Static Analyzer - A Design Tool for TROM

#### Hongjing Tao

Real-Time Reactive Systems are large complex systems. Many reserchers have been studying this field and have developed specification methods to reason about the behavior and attributes of real time reactive systems from different perspectives. This thesis contributes to the development of one part of a tool that will provide an environment to specify, design, debug and simulate real-time reactive systems built on TROMs, Timed Reactive Object Models. The tool consists of three major parts: Editor, Interpreter(including Axiom Generator) and Simulator. The Interpreter which is fundamental to the tool is the subject of study in this thesis. The Interpreter will do syntax and semantic analysis for user specification and generate internal data representation to perform the simulation. The Axiom Generator will generate axioms for each particular TROM to be used by formal verification during system simulation.

## Acknowledgments

I am greatly indebted to my supervisor Professor V. S. Alagar for his valubale advice to complete this work. I would like to thank him for his continuous guidance and moral support.

I would like to thank my husband Xiaohui for his great support and encouragement.

I would also like to thank my parents for their continuous love and help.

Finally, I would like to dedicate this thesis to my lovely daughter Elizabeth.

## **Contents**

| Li | st of | Figur  | es                                    | viii |

|----|-------|--------|---------------------------------------|------|

| Li | st of | Table  | s                                     | ×    |

| 1  | Intr  | oduct  | ion                                   | 1    |

|    | 1.1   | Large  | Complex System                        | 1    |

|    | 1.2   | Scope  | e of the thesis                       | 3    |

|    | 1.3   | Thesi  | is Outline                            | 4    |

| 2  | Re    | active | System Design - A brief Outline       | 5    |

|    | 2.1   | Modu   | ılar Design                           | 5    |

|    | 2.2   | TRO    | M Methodology                         | 6    |

|    |       | 2.2.1  | Tier 1 - Data Abstraction             | 7    |

|    |       | 2.2.2  | Tier 2 - TROM Methodology             | 12   |

|    |       | 2.2.3  | Tier 3 – Subsystem Specification      | 14   |

|    | 2.3   | Train- | Gate-Controller Example               | 15   |

|    |       | 2.3.1  | An Informal Description               | 15   |

|    |       | 2.3.2  | A Formal Model                        | 16   |

| 3  | Arc   | hitect | ure Design for Interpreter            | 22   |

| 4  | Syı   | ntax A | nalysis for TROM class and Subsystems | 25   |

|    | 4.1   | A For  | mal Grammar for <b>TROM</b> class     | 25   |

|    |       | 4.1.1  | TROM class member – Class             | 26   |

|    |       | 4.1.2  | TROM class member - Event             | 26   |

|    |       | 4.1.3  | TROM class member - State             | 27   |

|    |       | 4.1.4  | TROM class member - Attribute         | 27   |

|   |      | 4.1.5          | TROM class member - Trait                                       | 28 |

|---|------|----------------|-----------------------------------------------------------------|----|

|   |      | 4.1.6          | <b>TROM</b> class member - Attribute-function                   | 29 |

|   |      | 4.1.7          | TROM class member - Transition-Spec                             | 30 |

|   |      | 4.1.8          | <b>TROM</b> class member – Timε-Constraint                      | 32 |

|   | 4.2  | A Form         | mal Grammar for Subsystem                                       | 34 |

|   |      | 4.2.1          | Subsystem member - SCS-name                                     | 35 |

|   |      | 4.2.2          | Subsystem member – Include                                      | 35 |

|   |      | 4.2.3          | Subsystem member - Instantiate                                  | 35 |

|   |      | 4.2.4          | Subsystem member - Configure                                    | 36 |

|   | 4.3  | A Form         | mal Grammar for Simulation Event                                | 37 |

| 5 | Inte | ernal <b>R</b> | Lepresentation - Abstract Syntax Tree                           | 39 |

|   | 5.1  | The T          | FROM Abstract Syntax Tree Data Structure                        | 39 |

|   |      | 5.1.1          | General Description for <b>TROM</b> AST class member containers | 41 |

|   |      | 5.1.2          | Class name                                                      | 42 |

|   |      | 5.1.3          | Port-type-name                                                  | 42 |

|   |      | 5.1.4          | Event                                                           | 43 |

|   |      | 5.1.5          | State                                                           | 43 |

|   |      | 5.1.6          | Attribute                                                       | 43 |

|   |      | 5.1.7          | Trait                                                           | 44 |

|   |      | 5.1.8          | Attribute-function                                              | 44 |

|   |      | 5.1.9          | Assertion Tree Data Structure                                   | 45 |

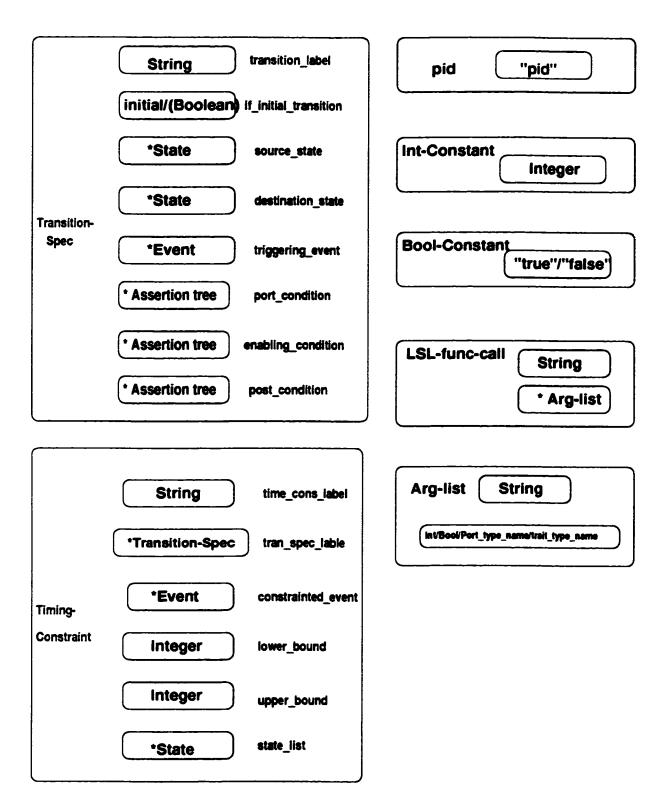

|   |      | 5.1.10         | Transition-Spec                                                 | 47 |

|   |      | 5.1.11         | Time-Constraint                                                 | 49 |

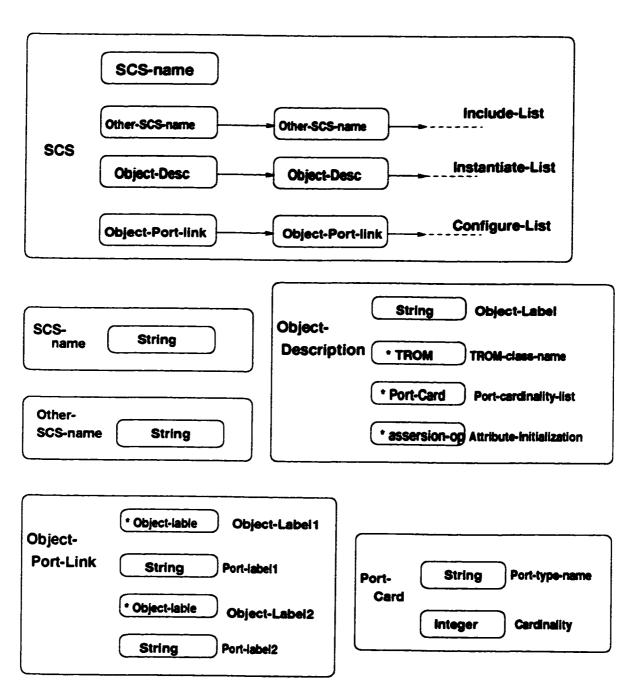

|   | 5.2  | The S          | SCS Abstract Syntax Tree Data Structure                         | 50 |

|   |      | 5.2.1          | General Description for SCS AST class member containers .       | 50 |

|   |      | 5.2.2          | SCS name                                                        | 52 |

|   |      | 5.2.3          | Include                                                         | 52 |

|   |      | 5.2.4          | Instantiate                                                     | 52 |

|   |      | 5.2.5          | Configure                                                       | 53 |

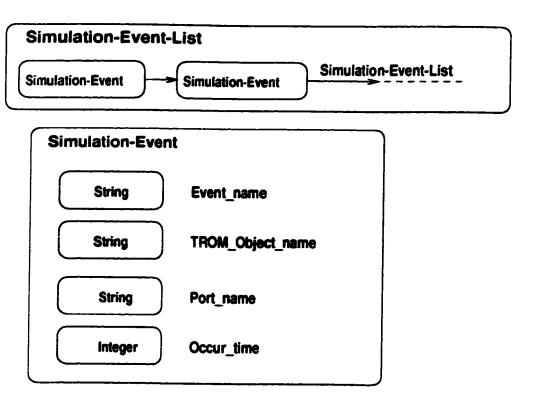

|   | 5.3  | The S          | Simulation Event List Abstract Syntax Tree Data Structure       | 53 |

|   |      | 5.3.1          | Simulation-Event                                                | 54 |

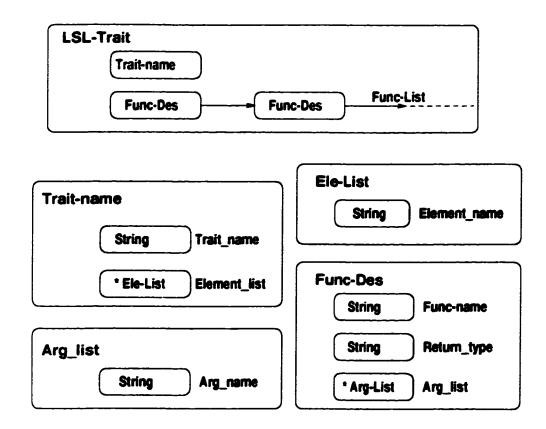

|   | 5 1  | The 1          | ISI Trait Abstract Suntay Tree Data Structure                   | 55 |

|   |                                                    | 5.4.1    | General Description for LSL Trait AST class member contain- |     |

|---|----------------------------------------------------|----------|-------------------------------------------------------------|-----|

|   |                                                    |          | ers                                                         | 56  |

|   |                                                    | 5.4.2    | Trait name                                                  | 56  |

|   |                                                    | 5.4.3    | Func-Decs                                                   | 56  |

|   | 5.5                                                | Larch    | $/\mathrm{C}++$ specification                               | 57  |

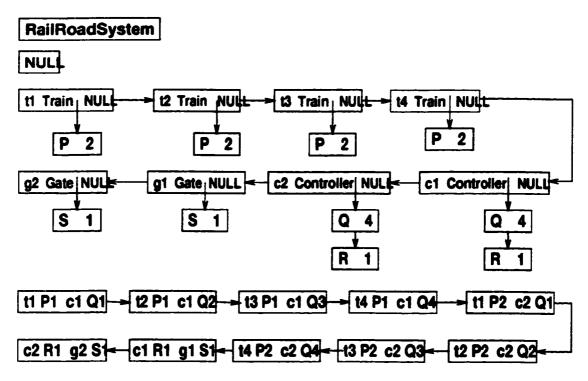

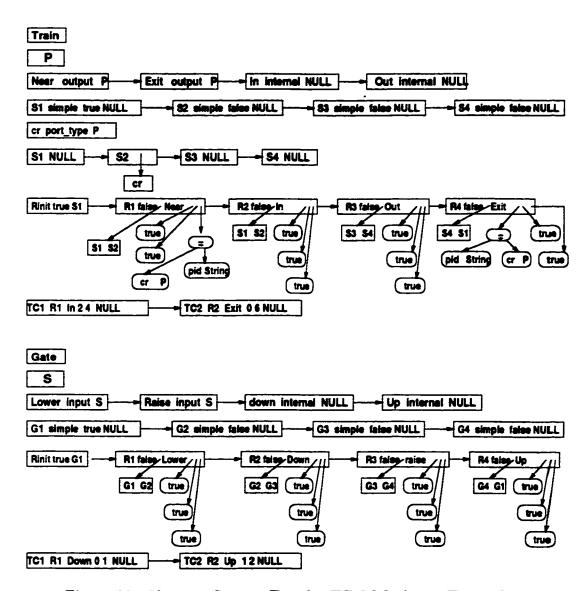

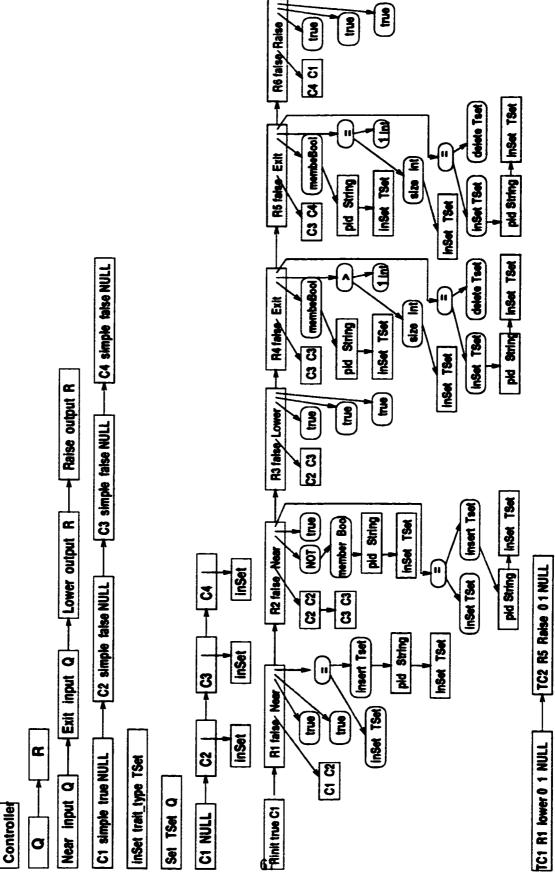

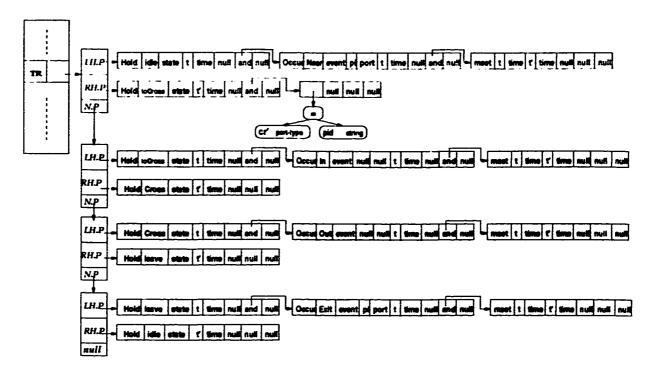

|   | 5.6                                                | Abstra   | act Syntax Tree for Train-Gate-Controller Example           | 65  |

| 6 | Sen                                                | nantic   | Analysis for TROM and Subsystems                            | 68  |

|   | 6.1                                                | What     | properties need to be checked?                              | 68  |

|   |                                                    | 6.1.1    | TROM class semantic analysis                                | 68  |

|   |                                                    | 6.1.2    | Subsystem semantic analysis                                 | 70  |

|   | 6.2                                                | Imple    | mentation of the Interpreter                                | 71  |

|   | 6.3                                                | How A    | AST is used in Semantic Analysis?                           | 72  |

|   | 6.4                                                | Seman    | ntic Analysis Report Example                                | 78  |

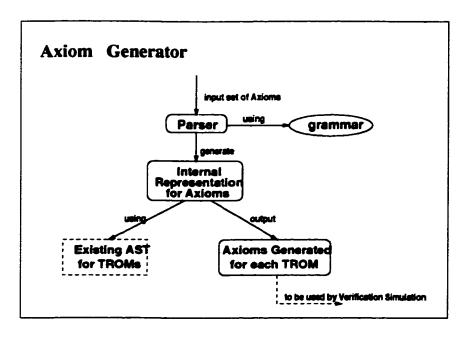

| 7 | Axi                                                | om Ge    | enerator                                                    | 83  |

|   | 7.1                                                | TRO      | M Axiom System                                              | 83  |

|   | 7.2                                                | Axion    | Generation                                                  | 88  |

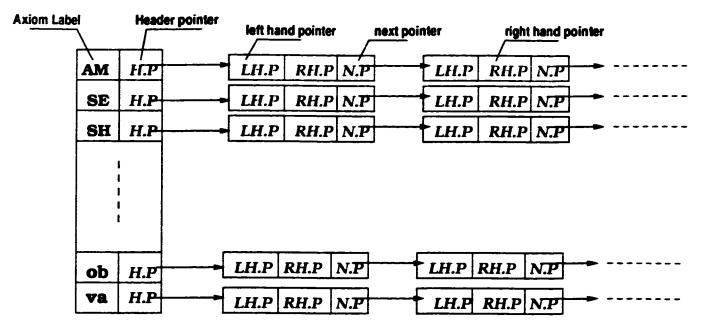

|   | 7.3                                                | Intern   | al Representation for Axioms                                | 94  |

|   | 7.4                                                | How t    | he axioms are used for verification                         | 95  |

|   | 7.5                                                | Case S   | Study - Axioms for Train-Gate-Controller Example            | 97  |

|   |                                                    | 7.5.1    | Axioms for Train <b>TROM</b>                                | 97  |

|   |                                                    | 7.5.2    | Axioms for Gate <b>TROM</b>                                 | 100 |

|   |                                                    | 7.5.3    | Axioms for Controller <b>TROM</b>                           | 102 |

| 8 | Cor                                                | clusio   | n                                                           | 106 |

| A | Syntax Grammar implementation using Flex and Bison |          |                                                             | 110 |

| B | Ahs                                                | stract ! | Syntax Tree Definition                                      | 120 |

# List of Figures

| 1  | An overview of the methodology.                                 | 7  |

|----|-----------------------------------------------------------------|----|

| 2  | LSL Trait - Set                                                 | g  |

| 3  | The Well-formed <b>TROM</b> Class Definition                    | 14 |

| 4  | Class interaction diagram - RailRoad system                     | 17 |

| 5  | Class specifications for Train, Gate                            | 18 |

| 6  | Class specifications for Controller                             | 19 |

| 7  | Subsystem specifications for RailRoadSystem                     | 20 |

| 8  | The Architecture of Overall System                              | 23 |

| 9  | The Architecture for Abstract Syntax Tree                       | 23 |

| 10 | TROM Abstract Syntax Tree Structure                             | 40 |

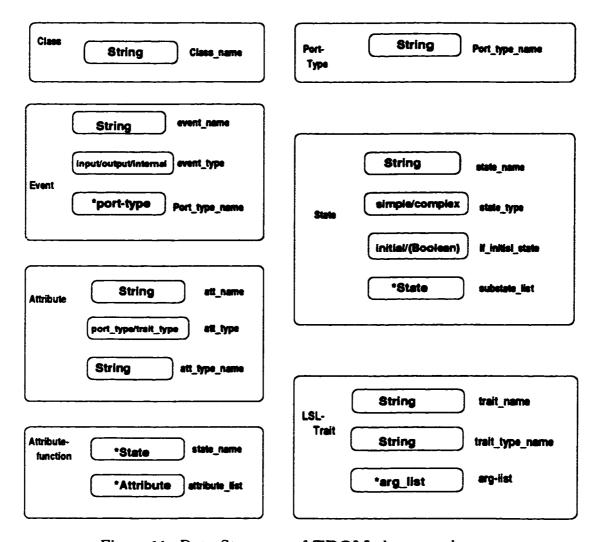

| 11 | Data Structure of <b>TROM</b> class members                     | 41 |

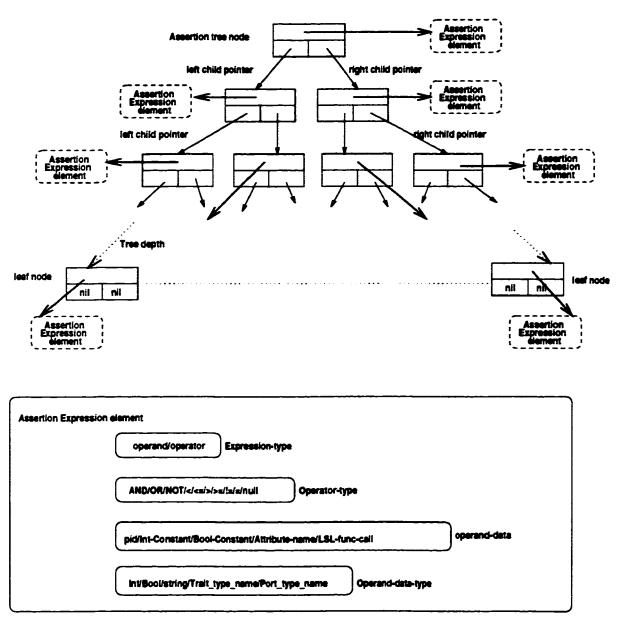

| 12 | Data Structure of an Assertion tree                             | 46 |

| 13 | Data Structure of <b>TROM</b> class members                     | 48 |

| 14 | SCS Abstract Syntax Tree Structure                              | 51 |

| 15 | Simulation Event List Abstract Syntax Tree Structure            | 54 |

| 16 | LSL Trait Abstract Syntax Tree Structure                        | 55 |

| 17 | Larch/C++ Specification for Set                                 | 58 |

| 18 | Larch/C++ Specification for Bag                                 | 61 |

| 19 | Larch/C++ Specification for BagIterator                         | 62 |

| 20 | Larch/C++ Specification for BinaryTree                          | 63 |

| 21 | Larch/C++ Specification for BinaryTreeIterator                  | 64 |

| 22 | AST for Subsystem - Trait-Gate-Controller System                | 65 |

| 23 | Abstract Syntax Tree for <b>TROM</b> class - Train, Gate        | 66 |

| 24 | Abstract Syntax Tree for <b>TROM</b> class - Controller         | 67 |

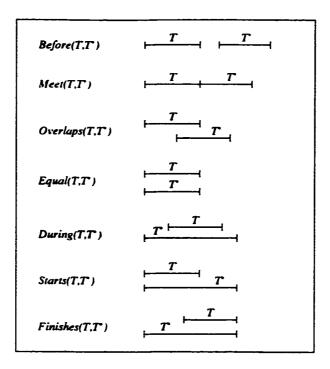

| 25 | The predicates defining temporal relationship between intervals | 84 |

| 26 | The Architecture for Axiom Generator                            | 89 |

| 27 | The Top Level Representation of <b>TROM</b> Axioms | 94 |

|----|----------------------------------------------------|----|

| 28 | The LHS and RHS nodes structure                    | 95 |

| 29 | Transition Axiom for Train TROM                    | 96 |

## List of Tables

| 1  | TROM class Description                                             | 2          |

|----|--------------------------------------------------------------------|------------|

| 2  | A grammar for <b>TROM</b> class member – Class                     | 26         |

| 3  | A grammar for <b>TROM</b> class member – Events                    | 27         |

| 4  | A grammar for <b>TROM</b> class member – States                    | 27         |

| 5  | A grammar for <b>TROM</b> class member – Attributes                | 28         |

| 6  | A grammar for <b>TROM</b> class member –Traits                     | 29         |

| 7  | A grammar for <b>TROM</b> class member – Attribute-functions       | 30         |

| 8  | A grammar for <b>TROM</b> class member – Transition Specifications | 33         |

| 9  | A grammar for <b>TROM</b> class member – Time-Constraints          | <b>3</b> 4 |

| 10 | SCS Description                                                    | <b>3</b> 4 |

| 11 | A grammar for SCS member – SCS-name                                | 35         |

| 12 | A grammar for SCS member – Include                                 | 35         |

| 13 | A grammar for SCS member – Instantiate                             | 36         |

| 14 | A grammar for SCS member - Configure                               | 37         |

| 15 | A grammar for Simulation Event List                                | 37         |

| 16 | A grammar for Axiom Generator                                      | 90         |

| 17 | Predicates for Axiom Generator                                     | 90         |

## Chapter 1

### Introduction

According to Parnas[12], a system can be considered complex if its shortest useful description is relatively long. The length of the shortest description indicates the amount of information required to understand the product. As systems become more and more sophisticated in the different domains of applications, a clean and comprehensive specification of overall system organization and behavior become critical aspects of system design. Many reserchers in this field are developing tools to deal with system complexity in different perspectives. Because the complexity in modern systems is due to software construction, it follows that we need to distinguish those attributes of software that contributes to the complexity from the physical system that they govern. Since we have to work with very complex systems in the real world, we must understand the sources of complexity and the method with which we can fight complexity.

#### 1.1 Large Complex System

According to general system theory, an entity called "system" is a complex organization of elements or parts "in interaction"[2]. In other words, a large and complex software system contains a variety of entities(objects) and a complex system(transformation function) controlling the interaction of objects[16]. There are two types of complexities in designing a large system: complex requirements, and complexity due to bad design. In general, there are three important factors contributing

to those two types of complexities[2].

- "Largeness" in numbers: such as size(lines of code), control and distribution of operations, long life cycles and evolutionary changes, persistance of information and protection of long-term investments make the system large in space and in time.

- Heterogeneity of concepts and procedures: such as heterogeneity of equipment, operating systems heterogeneity, heterogeneity of authority, applications heterogeneity, where it is desired to integrate otherwise separate applications to perform a single task.

- Complex organization and scalability: focus on examining the relationships between the components constituting the system and identifying types of system organizations.

We should keep in mind that although the world is not simple and the system requirements become very complicated, our goal must focus on building simple systems that perform complex tasks rather than developing large complex computer systems. Since the system requirements can not be changed, the complex requirements must be understood through the use of browser, cross-references and other computerized support. The significant challenge lies in designing a system which reduces, if not totally eliminates, complexity.

There are several ways to deal with complexity. An important design principle is to reduce the complexity of interconnectedness of system components. By applying the principles of abstraction, information hiding, separation of concerns and object-orientation, system design can be simplified. For example, by structuring the system hierarchy and by providing abstract interfaces, we can enhance the understandability and usability of the system. In order to achieve this goal, a modular and hierarchical design is highly recommended since it is suitable to use above mentioned method to reduce system complexity.

Recently, an Object-Oreinted methodology combining real time has been put forth to formally develop large reactive systems. The formal Object Oriented methodology introduced by Achuthan[1] includes the principles of abstraction, object orientation, separation of concerns, hierarchical design and moduler composition. The basic building block in this method is a **TROM**, Timed Reactive Object Model. Consequently, this methodology is excellent in reducing design complexity. This work provides formal foundation and rigorous methodology enabling formal verification and validation. However, in order to apply this methodology in practice, we need an environment for easy user interaction towards a better understanding of the system features, system interaction and system behavior. Our task is to build an environment for a reactive system development so that user can create a correct system specification and simulate the system behaviour. The animation tool consists of three major parts – an User Interface, an Interpreter and a Simulator. This thesis is a contribution to the development of the interpreter.

#### 1.2 Scope of the thesis

The goal of the thesis is to develop an interpreter for syntatic and semantic checking of user defined **TROM**s and subsystems modeling a reactive system. After defining a grammar for **TROM**, we explain how it is used for syntax checking of user defined **TROM**s. Simple semantic analysis such as the correctness of event name and port-type name can be done during syntax analysis. However, issues ralated to system behavior are to be dealt with during semantic analysis. An abstract internal representation called AST, Abstract Syntax Tree, is generated for syntacticly and semanticly correct **TROM**s and Subsystems.

In Achuthan[1], an axiomatization of **TROM** is given. Based on this set of axioms, we can develop an axiom generator and provide a methodology for generating axioms for specific **TROM** models. Those axioms are exported to, a verification system, for formal verification of system properties.

#### 1.3 Thesis Outline

A brief outline of the thesis is as follows: Chapter 2 gives a brief discussion on reactive system design: Chapter 3 discusses the architecture of the Interpreter; Chapter 4 gives grammars for TROMs and Subsystems. It also gives the definition of well-formed TROMs and subsystems and explains the syntactic analysis of user input system components; The structure of abstract syntax tree is explained and is illustrated for train-gate-controller example in Chapter 5. Chapter 6 discusses the semantic analysis and Larch/C++ specifications; axiom generator is discussed in Chapter 7. This thesis concludes in Chapter 8 with discussion on how this work fits with the overall goal of building an environment in which reactive systems based upon TROMs Achuthan[1] can be developed.

## Chapter 2

## Reactive System Design - A brief Outline

#### 2.1 Modular Design

Real-time reactive systems are large and complex systems. Some aspects of such a system are fundamental, while others are arbitrary and are likely to change. By decomposing system functionalities into self-contained and independent modules, we can tackle the complexity arising due to system changes. Some of the advantages are the following:

- Data and functionalities can be encapsulated.

- Abstract interfaces can be provided.

- It can reduce the strength of inter-module connections. Strength of connection is consistent with an information theoretic point of view.

- Each module can be documented independent of other modules. This allows the user to focus on the small components of the system.

- Modules can be tested independently for correctness and completeness.

- Modular verification reduces the complexity of the system verification.

Hierarchical Design is another modular design concept which restructures the system and simplifies the description and analysis of the system. Module containment hierarchy, program uses hierarchy, resource control hierarchies and process work allocation hierarchies are used in designing system hierarchies. Due to hierarchical design, the overall system architecture becomes easy to comprehend, thus reducing the complexity arising in the description of systems. The OO methodology introduced by Achuthan[1] includes these principles and in addition deals with real-time reactive objects.

#### 2.2 TROM Methodology

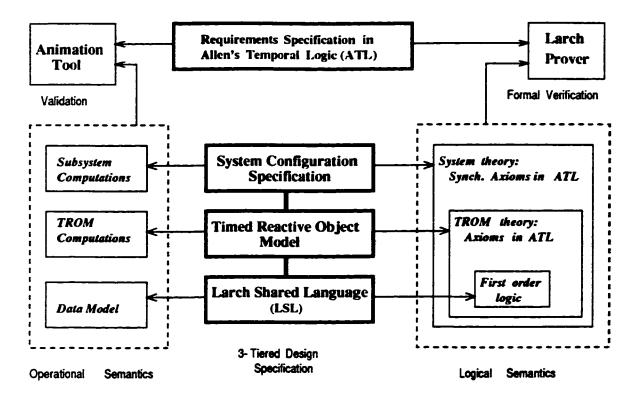

Reactive systems[4] are systems that continually interact with their environment. Typical requirements of such systems are that they satisfy certain timing constraints and avoid unsafe execution paths during their interaction with the environment. The methodology introduced by Achuthan[1] provides a formal Object-Oriented framework for the specification and reasoning of reactive systems. In this methodology, a system requirement is specified in temporal logic[11] and a system design is modeled as a collection of synchronously communicating objects using a 3-tiered design language. See Figure 1

The middle tier gives the detailed specification of the objects used in the upper tier by means of class definitions described in **TROM** terminology. In other words, each reactive object is formally modeled using a **TROM**. A **TROM** is a finite state machine augmented with ports, attributes, timing constraints and logical assertions. The state can be hierarchical in nature. The transitions are labled by events, which describe interactions of the object with its environment. The attributes in each state, defined by the attribute function, model the computations on data associated with transitions. The behaviors of attributes are abstractly specified in the **LSL** traits included in lower tier. With each transition, three assertions are associated: 1) precondition, stating the conditions to be satisfied for enabling the transition; 2) postcondition, specifying the status of the attributes due to data computations associated

Figure 1: An overview of the methodology.

with the transition; and 3) port-condition, specifying the port at which an interaction happens.

#### 2.2.1 Tier 1 – Data Abstraction

This level specifies the data abstraction used in the class definition of the middle tier by means of one of the languages of Larch, the Larch Shared Language(LSL)[10]. Larch languages are formal specification languages geared towards the specification of the observable effects of program modules, particularly modules which implement abstract data types. Larch provides a two-tiered approach to specification:

In one tier, a Larch Interface language(LIL) is used to describe the semantics of a program module written in a particular programming language. LIL specifications provide the information needed to understand and use a module interface. LIL doesn't refer to a single specification language but to a family of specification languages. Each specification language in the LIL family is designed for a specific programming language. The LIL for C++ is called Larch/C++.

LIL specifications are used to specify the abstract state transformations resulting from the invocation of the operations of a module. These specification are written in a predicative language using pre- and post-conditions.

• In the other tier, the Larch Shared Language(LSL) is used to specify state-independent, mathematical abstractions which can be referred to in LIL specifications. These underlying abstractions, called *Traits*, are written in the style of an equational algebraic specification.

LSL is programming language independent and is shared by all LILs.

The unit of encapsulation in **LSL** is the trait. Figure 2 shows an **LSL** trait which specifies the properties of a set. This example is similar to a conventional algebraic specification in the style of [10]. A trait contains a set of operator declarations, or signatures, which follows the keyword introduces. A set of equational axioms follows the keyword assert. A signature consists of the sorts and the domain and range of an operator. The equational axioms specifies the behavior and constraints on the defined operators.

There are a few notable differences between Larch traits and conventional algebraic specifications:

- ☐ The name of a trait (e.g. SetTrait) is distinct from the name of all sort and operator identifiers defined in the trait (e.g. Set).

- ☐ The names of sorts are not explicitly declared. They are implicitly declared by appearing in a signature.

- □ Larch makes use of the clauses partitioned by and generated by to increase the expressive power of traits.

- □ The semantics of = and == are exactly the same in **LSL**; only their syntactic precedence differs to ensure that expressions parse in an expected manner without having to use parentheses. The operator = binds more tightly than the operator ==.

```

Set(E,C): trait

includes Integer

introduces

\{\}: \rightarrow C

insert: E, C \rightarrow C

member: E, C \rightarrow Bool

delete: E, C \rightarrow C

size: C \rightarrow Int

isEmpty: C \rightarrow Bool

asserts

C generated by {}, insert

C partitioned by member

\forall s: C, e, e_1, e_2: E

\neg (member(e, \{\}))

member(e_1, insert(e_2, s)) == e_1 = e_2 \lor member(e_1, s)

size(\{\}) == 0

size(insert(e, s)) == if member(e, s) then <math>size(s) else size(s) + 1

delete(e_1, insert(e_2, s)) == if e_1 = e_2 then s else insert(e_2, delete(e_1, s))

isEmpty(\{\})

isEmpty(s) == size(s) = 0

\neg isEmpty(insert(e, s))

implies

\forall e, e_1, e_2 : E, s : C

insert(e, s) \neq \{\}

insert(e, insert(e, s)) == insert(e, s)

insert(e_1, insert(e_2, s)) ==

insert(e_2, insert(e_1, s))

converts delete, member, size, is Empty

exempting

\forall \ e : E

delete(e, {})

```

Figure 2: LSL Trait - Set

- $\square$  Equations of the form term == true can be abbreviated to term; thus the first equation in Figure 2 is an abbreviation for  $\neg (e \in \{\}) == true$  and the third equation is an abbreviation for  $isEmpty(\{\}) == true$ .

- The semantics of Larch traits is based on multisorted first order logic with equality rather than on an initial, final or loose algebra semantics used by other algebraic specification languages. Each trait denotes a theory in multisorted first-order logic with equality. The theory contains each of the trait's equations, the conventional axioms of first order logic with equality, everything which follows from them, and nothing else. This means that the formulas in the theory follow only from the presence of assertions in the trait never from their absence. The theory of a trait can also be strengthened by adding a generated by or a partitioned by clause.

- □ A trait definition need not correspond to an abstract data type (ADT) definition since an LSL trait can define any arbitrary theory of multisorted first-order equational logic. For example, a trait can be used to define the first order theory of mathematical abstractions such as equivalence relations which do not correspond to abstract data types.

- □ LSL traits can be augmented with checkable redundancies in order to verify whether intended consequences actually follow from the axioms of a trait. These checkable redundancies are specified in the form of assertions which are included in the implies clause of a trait and can be verified using Larch Prover.

In the trait of Figure 2, the generated by clause states that all values of the sort Set can be represented by terms composed solely of the two operator symblos {} and insert. In other words, saying that sort C is generated by a set of operators, Ops, asserts that each term of sort C is equal to a term whose outermost operators is in Ops. The operators in the set Ops are referred to as the generators of the sort C. A generated by clause strengthens the theory of a trait by adding an inductive rule of inference which can be used to prove properties which hold for all Set values.

<sup>&</sup>lt;sup>1</sup>A theory is a set of logic formulas having no free variables.

For LSL traits which define an ADT, there is a sort referred to as the distinguished sort, sometimes also called the *principal sort* or data sort. For example, for the trait of Figure 2 the distinguished sort is Set, which is the sort corresponding to the set ADT.

The partitioned by clause provides additional equivalences between terms. Intutively, it states that two terms are equal if they cannot be distinguished by any of the functions listed in the clause. For the Set example, this property could be used to show that order of insertion in the set is commutative. That is, it could be shown that the terms insert(e1, insert(e2, s)) and insert(e2, insert(e1, s)) are equal for all values of e1, e2: Int and s: int.

The exempting clause documents the absence of right-hand sides of equations for delete(e,  $\{\}$ ); this incompleteness is dealt with in the interface specification. The converts and exempting clauses together provide a way to state that this algebraic specification is sufficiently complete. Intutively, what the converts and exempting clauses are saying is the following: the specification of the operators delete, is Empty is complete in the sense that any term involving these operators can be reduced to terms not involving these operators. The only exception to this rule is for terms which involve a subterm of the form  $delete(e, \{\})$ .

LSL also provides a way of putting traits together, one of which is through an includes clause. A trait that includes another trait is textually expanded to contain all operator declarations, constraints clauses, generated by clauses, and axioms of the included trait. The meaning of the including trait is the meaning of the textually expanded trait. In the Set example, the signature and meaning of the '+' operator comes from the Integer trait. Boolean operators (true, false,  $\neg$  (not),  $\land$ ,  $\lor$ ,  $\rightarrow$ , and  $\leftrightarrow$ ) as well as some heavily overloaded operators (if-then-else,  $\Rightarrow$ ) are built into the language; that is, traits defining these operators are implicitly included in every trait.

We discuss Larch/C++ in Chapter 5, in the content of specifying Abstract Syntax Tree structures.

#### 2.2.2 Tier 2 – TROM Methodology

In this level, reactive objects are modeled using TROMs. Communications between TROMs occur at the ports linking the TROMs. A port has an unique port type, which dictates the set of messages and the message sequences allowed at that port. A TROM can have ports of different types and several ports of one type. When an event E occurs at a port P at time T, an activity is initiated which may take a finite amount of time to complete. Due to the occurence of an event at the port, the TROM may undergo a state change, triggers or outputs several time-constraint events.

A formal definition of **TROM**, as given by [1], is the following: Definition 2.2.2.1 A **TROM** is an 8-tuple  $(\mathcal{P}, \mathcal{E}, \Theta, \mathcal{X}, \mathcal{L}, \Phi, \Lambda, \Upsilon)$  such that:

- $\mathcal{P}$  is a finite set of port-types with a finite set of ports associated with each port-type. A distinguished port-type is the null-type  $P_0$  whose only port is the null port o.

- $\mathcal{E}$  is a finite set of events and includes the silent-event tick. The set  $\mathcal{E}$ -tick is partitioned into three disjoint subsets:  $\mathcal{E}_{in}$  is the set of input events,  $\mathcal{E}_{out}$  is the set of output events,  $\mathcal{E}_{int}$  is the set of internal events. Each  $e \in (\mathcal{E}_{in} \cup \mathcal{E}_{out})$ , is associated with a unique port-type  $P \in \mathcal{P}$ - $P_0$ .

- $\Theta$  is a finite set of states.  $\theta_0 \in \Theta$ , is the initial state.

- X is a finite set of typed attributes. The attributes can be of one of the following two types: i) an abstract data type supporting a data model; ii) a port reference type.

- ullet L is a finite set of LSL traits introducing the abstract data types used in  ${\mathcal X}$ .

- $\Phi$  is a function-vector  $(\Phi_s, \Phi_{at})$  where,

- Φ<sub>s</sub>: Θ → 2<sup>θ</sup> associates with each state θ a set of states, possibly empty, called substates. A state θ is called atomic, if Φ<sub>s</sub>(θ) = Ø. By definition, the initial state θ<sub>0</sub> is atomic. For each non-atomic state θ, there exists a unique atomic state θ<sup>\*</sup> ∈ Φ<sub>s</sub>(θ), called the entry-state.

- $\Phi_{at}$ :  $\Theta \to 2^{\mathcal{X}}$  associates with each state  $\theta$  a set of attributes, possibly empty. called active attribute set. At each state  $\theta$ , the set  $\overline{\Phi}_{at}(\theta) = \mathcal{X} \Phi_{at}(\theta)$  is called the dormant attribute set of  $\theta$ .

- $\Lambda$  is a finite set of transition specifications including  $\lambda_{init}$ . A transition specification  $\lambda \in \Lambda$   $\lambda_{init}$ , is represented as  $\lambda : \langle \theta, \theta \rangle$ ;  $e(\varphi_{port})$ ;  $\varphi_{en} \Longrightarrow \varphi_{post}$ ; where:

- $\langle \theta, \theta' \rangle$ , where  $\theta$ ,  $\theta' \in \Theta$  are the source and destination states of the transition, respectively.

- e(φ<sub>port</sub>)where e ∈ E lables the transition; φ<sub>post</sub> is an assertion on the attributes

in X and a reserved variable pid. pid signifies the identifier of the port at

which an interaction associated with the transition can occur. If e ∈ E<sub>int</sub>

∪ tick, then the assertion φ<sub>port</sub> is absent and e is assumed to occur at the

null-port o.

- $\varphi_{en} \Longrightarrow \varphi_{post}$ , where  $\varphi_{en}$  is the enabling condition and  $\varphi_{post}$  is the post-condition of the transition.  $\varphi_{en}$  is an assertion on the attributes in X, primed attributes in  $\Phi_{at}(\theta')$  and the variable pid specifying the data computation associated with the transition.

For each  $\theta \in \Theta$ , the silent-transition  $\lambda_{so} \in \Lambda$  is such that,

$\lambda_{so}$ :  $\langle \theta, \theta \rangle$ ; tick;  $true \Longrightarrow \forall x \in \Phi_{at}(\theta)$ : x=x';

The initial-transition  $\lambda_{init}$  is such that  $\lambda_{init}$ :  $\langle \theta \rangle$ ; Create();  $\varphi_{init}$  where  $\varphi_{init}$  is an assertion on active-attributes of  $\theta_o$ .

- $\Upsilon$  is a finite set of time-constraints. A timing constraint  $v_i \in \Upsilon$  is a tuple  $(\lambda_i, e'_i, [l, u], \Theta_i)$  where,

- $\lambda_i \neq \lambda_s$  is a transition specification.

- $e'_i \in (\mathcal{E}_{int} \cup \mathcal{E}_{out})$  is the constrainted event.

- [l,u] defines the minimum and maximum response times.

- $\Theta_i \subseteq \Theta$  is the set of states where in the timing constraint  $v_i$  will be ignored.

```

Class < classname > < [@port-types] >

Events: < event list >

State: < initial-state, list-of-states >

Attributes: list of < {att: att-type} >

Traits: list of < {traitname [port-type, att-type]} >

Attribyte-function: list of < {set of states -> set of atts} >

Transition Spec: < init-lable: <init-state>; Create(); >

list of < trans-lable: <source, destination>;

event(assertion); assertion -> assertion; >

Time-Constraints:

list of < lable: (trans-lable, event,[min, max], set of state) >

end

```

Figure 3: The Well-formed **TROM** Class Definition.

The grammar given in Chapter 4 is based on this formal definition.

To apply this formalism in defining a **TROM** class. We give a template, shown in Figure 3. A user will write a **TROM** class specification based on this grammar.

#### 2.2.3 Tier 3 – Subsystem Specification

This level is the topmost tier which constitutes subsystem configuration specifications(SCS), describing the system architecture by succinctly specifying the interaction relationship that can exist between the objects in a system. It also defines the inheritance and subtyping by aggregating instantiated objects to form subsystems and systems. Subsystems are components in a system architecture. Each subsystem encapsulates the association, interaction, and concurrent evolution of a collection of TROMs. Hence a subsystem specification includes one or more SCS definitions.

The template for a subsystem configuration specification is shown below.

```

SCS: < name >

Include: list of < other_SCS_name>

Instantiate: list of < object_instantiation>

```

Configure: list of < object\_port\_aggregation>

This 3-tiered design specification forms the main component in the framework. Due to this approach, the design specification framework not only provides an architectural specification of a system, but also forms a means for formally specifying detailed design of the system component. One of the main advantages of this methodology is the conciseness in specification when object-oriented structuring principles such as instantiation, inheritance and subtyping are used as part of the design. Through a case study, we illustrate the specification in the second and the third tiers. We also use the example to bring out the features of our tool.

#### 2.3 Train-Gate-Controller Example

Consider a generalized version of a railroad crossing system introduced in [5]. We emphasize on its real-time reactive behavior and generalized version of the object-oriented design point of view. We will use this case study throughout the thesis.

#### 2.3.1 An Informal Description

A railroad crossing system consists of a collection of trains and gates servicing the roads crossing the train tracks. The gate should remain closed whenever a train goes past the crossing. In order to control the gates there exists a collection of controllers such that one controller controls each gate. A controller closes its associated gate when it gets a "nearing signal" from a train and opens the gate once all the trains crossing the gate have left. A controller does this by receiving signals from the trains and transmitting necessary control signals to its associated gate. Thus the problem is more general than the one studied before in the following sense: more than one train can cross a gate simultaneously, probably through multiple parallel tracks; a train can independently choose the gate it is going to cross, probably based on its direction and zone of travel. A safety requirement for the system is that whenever a train is inside a gate, the gate should remain closed.

When a train is approaching a gate, the train starts sending a Near message to the

controller associated with the gate. While leaving the gate, the train informs the controller by an Exit message. A typical time constraint on the train is that there is a minimum delay of at least 2 units of time before the train gets into the gate after it sends the message Near. Furthermore, after the message Near, there is a maximum delay of 5 units before which the train should exit the crossing.

A controller, upon receiving a Near message from a train, sends the signal Lower to its associated gate to lower the gate. Similarly, following the receipt of an Exit message from the last train to leave the gate, the controller sends a Raise message to the gate. There are two time constraints associated with the controller. The controller should respond by sending: i) a Lower message to the gate within 1 unit of time after receiving the Near message; ii) a Raise message to the gate within 1 unit of time after receiving the Exit message from the last train to leave the gate.

A gate responds to a *Lower* message and a *Raise* message by closing and opening the gate, respectively. There is a minimum delay constraint of 1 unit for closing the gate and a minimum of 1 unit and maximum delay constraint of 2 units, for opening the gate.

We discuss a formal specification of the system using our model in the following paragraphs.

#### 2.3.2 A Formal Model

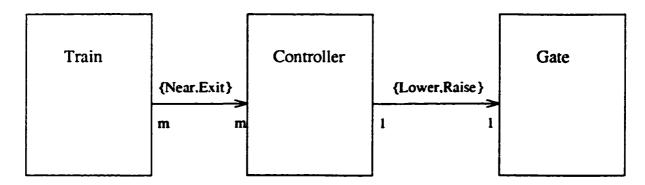

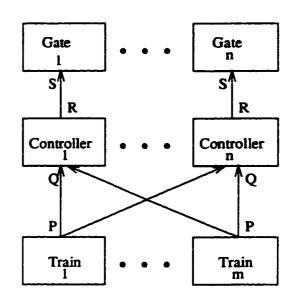

There are three types of interacting components: Train, Gate and Controller. The instantiation relationship in object-orientation helps to specify the system using three class specifications one for each of the above component types. The class interaction diagram for the system is shown in Figure 4.

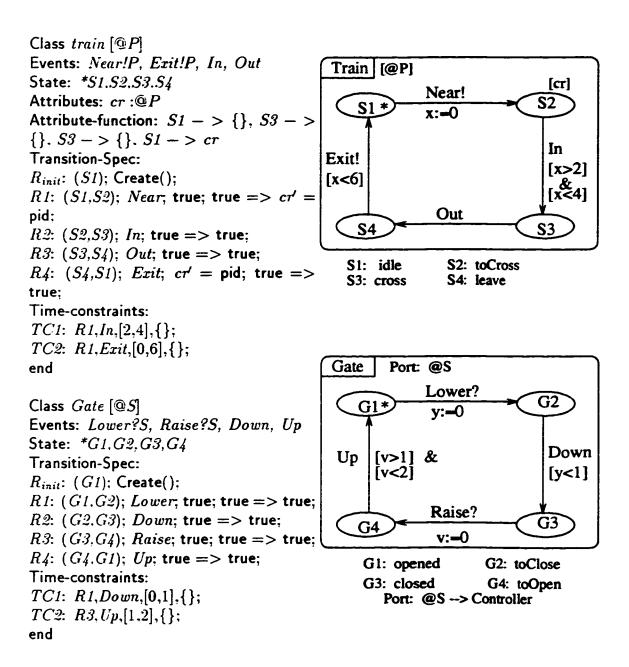

The class specifications of the three components together with their state diagrams are shown in Figures 5 and 6.

Each class specification describes the behavior of a component individually. The RailRoad system is modeled as a SCS by instantiating the objects from the three classes and linking them.

Figure 4: Class interaction diagram - RailRoad system

The train class supports a port-type, @P. A train starts in state S1. The port condition of the Near event in a train specifies that the train can non-deterministically select one of its ports of type @P for an interaction. A train class object models its intention to cross a specific gate(i.e., the gate associated with the controller which may be linked to the port selected). The attribute cr of states S2, S3 and S4 denotes that the further interaction of the train should be at the port it chose, until it exits the gate. The internal events In and Out signifies the start and end, respectively of the action of crossing a gate by the train. The two time constraints associated with a train are specified by the two tuples. The trigger event for both the time constraints is the event Near.

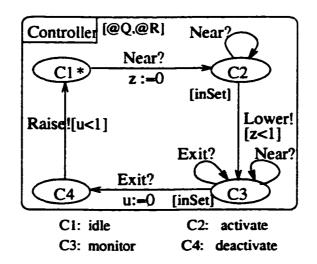

Initially the controller is in state C1. A controller supports ports of two types, @Q and @R. Implicitly, the ports of type @Q are used for interactions with train class objects and the ports of type @R are used for interactions with gate class objects. When in state C1, the controller responds to the input event Near at a port of type @Q by sending the event Lower at a port of type @R, within 1 unit of time. This corresponds to the signal from the first approaching train to enter the crossing after the gate was last opened. Subsequent Near events at other ports of type @Q mark the approaching signal from other trains, probably in parallel tracks. The attribute inSet associated with the states C2 and C3 denotes the set of ports at which an interaction involving Near has occurred, and implicitly underscores those train class objects crossing the gate at that instant. It is obvious from the post conditions that, an insertion into the inSet and a deletion from it is done by the transitions Near

Figure 5: Class specifications for Train, Gate

```

Class Controller [@Q, @R]

Events: Near?Q, Exit?Q, Lower!R, Raise!R

State: *C1, C2, C3, C4

Attributes: inSet: TSet

Traits: Set[@Q, TSet]

Attribute-function: C1 - > \{\}; C2 - > inSet; C3 - > inSet; C4 - > inSet\}

Transition-Spec:

R_{init}: (C1); Create();

R1: (C1,C2); Near; true; true => inSet' = insert(pid, inSet);

R2: (C2, C2), (C3, C3); Near, NOT( member(pid, inSet)); true => inSet' = insert(pid,

inSet);

R3: (C2.C3); Lower; true; true => true;

R4: (C3,C3); Exit; member(pid, inSet); size(inSet) > 1 => inSet' = delete(pid, in-

R5: (C3,C4); Exit; member(pid, inSet); size(inSet) = 1 => inSet' = delete(pid, in-

Set);

R6: (C4,C1); Raise; true; true => true;

Time-constraints:

TC1: R1, Lower, [0,1], \{\};

TC2: R5, Raise.[0,1], \{\};

end

```

Figure 6: Class specifications for Controller

```

SCS RailRoadSystem Instantiate:

```

```

t1 :: Train[@P:2];

t2 :: Train[@P:2];

t3:: Train[@P:2]:

t4 :: Train[@P:2];

c1:: Controller@Q:4,@R:1;

c2 :: Controller[@Q: 4, @R: 1];

g1 :: Gate[@S:1];

g2 :: Gate[@S:1];

Configure:

t1.@P1 < -> c1.@Q1;

t2.@P1 < -> c1.@Q2;

t3.@P1 < -> c1.@Q3;

t4.@P1 < - > c1.@Q4;

t1.@P2 < -> c2.@Q1;

t2.@P2 < -> c2.@Q2;

t3.@P2 < -> c2.@Q3;

t4.@P2 < - > c2.@Q4:

c1.@R1 < -> g1.@S1;

c2.@R1 < - > g2.@S1;

end

```

Figure 7: Subsystem specifications for RailRoadSystem

and Exit. respectively. Once the controller receives the event Exit at all the ports in the inSet (i.e., implicitly from all the trains which were crossing), the controller will send the event Ruise at a port of type @R within 1 time unit as specified by the time-constraint. The port specification for the events Near and Exit, indicates that for each train instance any Exit event should be preceded by a Near event and every consecutive Near event should be interleaved by an Exit event.

The gate supports a port-type @S. A gate is open in start state G1 and closed in state G3. Interaction of the gate with its controllers is through its port involving events Lower and Raise. The events Down and Up are internal events and denote the end of the action, closing and opening, of the gate respectively. The reactions associated with the two time constraints of the gate are triggered by the events Lower and Raise, respectively.

The RailRoad subsystem is formed by composing objects instantiated from the above classes. A subsystem configuration specification is shown in Figure 7. The ability to specify objects independently and to configure a system/subsystem independently using the instantiated objects makes **TROM** suitable for specifying large systems.

## Chapter 3

# Architecture Design for Interpreter

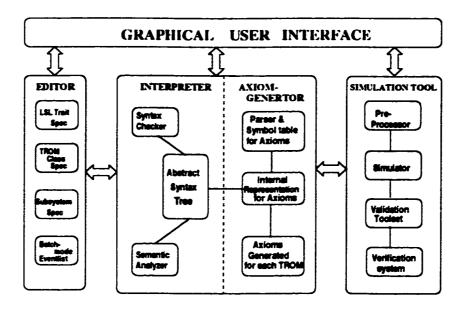

To apply **TROM** methodology in practice, we need to develop a system enviornment – a tool, for user to write the **TROM** classes and Subsystem specifications and to be able to trace the interactive object behavior at run time. This tool consists of three major parts: User Interface, Interpreter and Simulator. The overall structure of the tool is shown in Figure 8.

This thesis focuses on developing an Interpreter which takes user's **TROM** class and Subsystem specifications and generates an internal representation (i.e., AST - abstract syntax tree) to be used by the Simulation Tool. It also focuses on designing an Axiom Generator which is used by the verification system and it is discussed in Chapter 7.

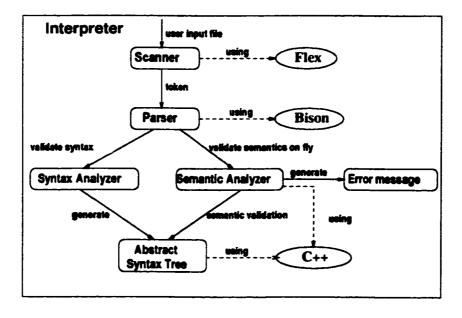

The architecture design for the Interpreter is shown in Figure 9.

The Interpreter will take the user input file and generate an internal data representation which is used during simulation. It also generates axioms which are used to verify system properties. The components of the Interpreter are the following:

- Scanner used to identify input file and to generate tokens. It also does basic lexical analysis using Flex.

- Parser clarifies tokens from scanner in order to check syntactic correctness by using **Bison**.

Figure 8: The Architecture of Overall System

Figure 9: The Architecture for Abstract Syntax Tree

- Syntax Analyzer uses a pre-defined grammar for **TROM** and SCS in order to validate syntactically correct tokens. Any error will terminate the program and is directly reported to the user by **Bison**.

- Abstract Syntax Tree a data structure to represent the useful information from user input file (the detailed structure of the AST will be discussed in Chapter 5).

- Semantic Analyzer a program written in C++ and used to do semantic checking. There are two types of semantic checking.

- i) On the fly validation does simple semantic check at the same time with syntax checking. For example, duplicate names can be checked during on fly validation.

- ii) AST validation does complex semantic checking after building up an AST. For example, type checking, linking to LSL traits,.., must be done at this stage.

- Error Message generated by semantic analyzer in order to help user correct the input file. Every detected error will be kept in a file until the end of the analysis.

### Chapter 4

# Syntax Analysis for TROM class and Subsystems

The templates for **TROM** and Subsystem are given in Chapter 2. In this chapter, we focus only on the syntax and discuss the grammar for well-defined **TROM** classes and Subsystems.

#### 4.1 A Formal Grammar for TROM class

The TROM class is composed of several members, shown in Table 1.

We will give a grammar for each of the **TROM** class member. Words shown in "sans serif type" font are keywords and case sensitive. CHAR(10) in the grammar means that at most 10 characters are allowed.

The specification of *Train-TROM*, *Gate-TROM* and *Controller-TROM* as given in Chapter 1 are consistant with the grammar given bellow. From Definition 2.2.2.1 and class specifications shown in Figure 3, we abstract a formal grammar for **TROM**:

TROM ::= <class> <events> <states> <attributes> <traits> <att\_funcs> <tran\_specs> <time\_constraints> end

Table 1: TROM class Description

```

class ::= Class < class_name > [<port_types>] NL

port_types ::= @<port_type_name > | @<port_type_name>, <port_types>

class_name ::= CHAR(10)

port_type_name ::= CHAR(10)

```

Table 2: A grammar for TROM class member - Class

#### 4.1.1 TROM class member – Class

Class is a header which describes the name and the port types of a **TROM**. The format is:

- The keyword Class followed by class name and Port types.

- Port types are preceded by the symbol @, within square brackets, and separated by commas.

The grammar for class is shown in Table 2.

#### 4.1.2 TROM class member - Event

Event enumerates the set of events associated with the class. The format is:

- The keyword Events followed by a colon and list of events.

- Events are separated by commas and must belong to one of the three types:

- Input event: an event name followed by the symbol? and a port type for the event.

- Output event: an event name followed by the symbol! and a port type for the event.

- Internal event is not marked.

The grammar for *Event* is shown in Table 3.

```

::= Events: < event_list> NL

events

event_list

::=

<event> | <event>, <event_list>

<inputevent> | <outputerent> | <interevent>

event

::=

::= \langle event\_name \rangle ? \langle port\_type\_name \rangle

inputevent

outputevent

::= <event_name>! <port_type_name>

interevent

::= \langle \epsilon vent\_name \rangle

::= CHAR(10)

event_name

port_type_name ::= CHAR(10)

```

Table 3: A grammar for TROM class member - Events

```

states ::= States: <state_set> NL

state_set ::= *<state>, <state_list>

state_list ::= <state> | <state_list>

state ::= <state_name> | <state_name> (<state_set>)

state_name ::= CHAR(10)

```

Table 4: A grammar for TROM class member - States

#### 4.1.3 TROM class member – State

State enumerates the abstract states of the class. The format is:

- The keyword State followed by a colon and a list of states.

- States are separated by commas and contains three special types:

- Initial state: state name preceded by the symbol \*.

- Substates: list of state lables separated by commas within parentheses. The states should follow their parent state.

- Initial substate: substate name preceded by the symbol \*.

The grammar for State is shown in Table 4.

#### 4.1.4 TROM class member – Attribute

Attribute describes the set of attributes belonging to the class together with their

```

attributes ::= Attributes: <att_list> NL | \varepsilon att_list ::= <attribute> | <attribute> :: <att_list> attribute ::= <att_name> : <crait_type_name> :: <trait_type_name ::= CHAR(10) port_type_name ::= CHAR(10)

```

Table 5: A grammar for TROM class member - Attributes

types. The format is:

- The keyword Attributes followed by a colon and a list of attributes.

- Attributes are separated by semi-colon.

- An attribute is represented by its name, followed by a colon and a type of the attribute.

- The type of an attribute is either a port type or an abstract data type associated with a LSL trait.

- The Attribute description is optional.

The grammar for Attribute is shown in Table 5.

#### 4.1.5 TROM class member – Trait

Trait imports the behavior of a specified data model which belongs to the corresponding trait defined in the LSL tier. Any trait reference type specified in Attribute section must match one of the parameters listed in a trait in this section. This defines the link between two tiers i.e., the data abstraction and the class definition. The format is:

• The keyword Traits followed by colon and list of traits together with their parameters.

```

traits

::= Traits: \langle trait\_list \rangle NL | \varepsilon

trait_list

::= <trail> | <trail > : <trail_list >

trait

::= \langle trait\_name \rangle [\langle arg\_list \rangle, \langle trait\_type\_name \rangle]

arg_list

:= \langle arg \rangle | \langle arq \rangle . \langle arq\_list \rangle

::= <trait_typc_name> | @<port_type_name >

arg

trait_name

::= CHAR(10)

trait_type_name

::= CHAR(10)

::= CHAR(10)

port_type_name

```

Table 6: A grammar for **TROM** class member -Traits

- Traits are separated by commas.

- A trait is represented by its name followed by its parameters.

- The parameters for a trait are enumerated within square brackets and are separated by commas.

- The *Trait* section is optional.

The grammar for *Trait* is shown in the Table 6.

#### 4.1.6 TROM class member - Attribute-function

Attribute-function defines the association of attributes to states, thus partitioning the domain of attributes into active and dormant parts at each state. The format is:

- The keyword Attribute-function followed by colon and list of attribute-functions.

- Attribute-functions are separated by semi-colons.

- An attribute-function is presented as follows:

- A state name followed by the symbol ->

- One or more names of attributes separated by commas and enumerated within brackets (the symbol {} representing an empty set).

```

att_funcs ::= Attribute_function: \langle att\_func\_list \rangle \mid \varepsilon

att_func_list ::= \langle att\_func \rangle: \mid \langle att\_func \rangle; \langle att\_func\_list \rangle

att_func ::= \langle stat\epsilon\_nam\epsilon \rangle - \rangle \{\langle att\_list \rangle\} NL

att_list ::= \langle att\_nam\epsilon \rangle \mid \langle att\_nam\epsilon \rangle, \langle att\_list \rangle \mid \varepsilon

att_name ::= CHAR(10)

state_name ::= CHAR(10)

```

Table 7: A grammar for TROM class member - Attribute-functions

• The Attribute-function section is optional.

The grammar for Attribute-functions is shown in Table 7.

#### 4.1.7 TROM class member – Transition-Spec

Transition-Spec describes the transition specification for each transition in the state machine. The format is:

- The keyword Transition Spec is followed by a colon and the list of transitions which start with initial transition followed by other transitions.

- Each transition starts at a new line with its name and finishes with a semi-colon.

- An initial transition is specified as follows:

- The initial transition name followed by a colon

- The symbol < followed by a name of starting state, the symbol > followed by a semi-colon

- Create();

- One or more assertions separated by AND or OR within parentheses. An assertion which is an expression in one of the following format:

- \* The constant true.

- \* An attribute name defined in the Attributes section plus a superscript' which means the post condition of the attribute followed by the operater = and either a function as defined in the LSL trait with the corresponding arguments enclosed within parentheses, the reserved pid or the same attribute name without superscript'.

- A semi-colon.

- The initial transition specification is optional

- Other transitions have the following format:

- The transition name followed by a colon

- List of state pairs are separated by commas. Each state pair is specified as (S1, S2), where S1, S2 are state names.

- A semi-colon followed by an event name

- A semi-colon followed by a port condition

- The port condition syntax is: One or more assertions separated by AND or OR within parantheses. An assertion is a *Boolean* expression which is in one of the following formats:

- \* The constant true.

- \* A Boolean function as defined in **LSL** traits with the corresponding arguments enclosed within parenthesis. An argument can be an attribute defined in Attributes section or the reserved **pid**. The Boolean function can be preceded by the keyword NOT.

- \* An Integer expression followed by a *Boolean* operator and another Integer expression. An Integer expression can be an *Integer* or a function returning an *Integer* as defined in the **LSL** trait with the corresponding arguments enclosed within parentheses. *Boolean* operators are =, ! =, <, >, <=, >=.

- A semi-colon followed by an enabling condition which has the same syntax as port condition described above.

- The symbol=> followed by a post condition.

- The post condition syntax is: One or more assertions separated by AND or OR within parantheses. An assertion is a *Boolean* expression which is in one of the following format:

- \* The constant true.

- \* An attribute name defined in the Attributes section plus a superscript' which means the post condition of the attribute followed by the operater = and either a function as defined in the LSL trait with the corresponding arguments enclosed within parentheses, the reserved pid or an attribute name without superscript'.

- A semi-colon.

The grammar for Transition Specification is shown in Table 8.

#### 4.1.8 TROM class member – Time-Constraint

Time-constraints describe the timing constraints associated with the transitions. The timing constraints ensure that the class will not keep the resource unallocated indefinitely. The syntax is according to the following format.

- The keyword Time-Constraints followed by a colon and a list of Time-constraints which are separated by semi-colons.

- Each specific Time-constraint starts at a new line, and has the following format:

- A Time-constraint name followed by a colon

- A transition specification name followed by a comma

- An event name followed by a comma

- A left square bracket

- An integer for the minimum response time followed by a comma

- An integer for the maximum response time

```

NL

tran_specs

::= Transition

Spec:

<tran_spec_init>

NL

<tran_spec_list> NL

tran_spec_init

< tran_spec_name>:

<state_name>;

Create();

\langle assertion\_op \rangle; \mid \varepsilon

tran_spec_list

<tran_spec> NL | <tran_spec> NL <tran_spec_list>

::=

tran_spec

<tran_spec_name>:

<state_pairs>

<trig_event>

::=

\langle assertion \rangle = \langle assertion \rangle;

<state_pair>; | <state_pair>; <state_pairs>;

state_pairs

state_pair

:=

(<state_name>,<state_name>)

triq_event

<event_name> (<assertion>) | <event_name>

assertion

<simple_exp> | <simple_exp> < b_op> < simple_exp>

::=

b_{-}op

::= = | <> | < | <= | > | >=

simple\_exp

::= \langle term \rangle | \langle term \rangle OR \langle term \rangle

term

::= <factor> | <factor> AND <factor>

factor

::= NOT < factor > | pid | < att_name' > | < att_name > | true

| false | \langle LSL\_term \rangle | (\langle assertion \rangle)

LSL_term

::= \langle LSL\_func\_name \rangle (\langle arg\_list \rangle)

arq_list

::= \langle arg \rangle \mid \langle arg \rangle, \langle arg\_list \rangle

arg

pid | <att_name> | <LSL_term>

::=

att_name'

::= CHAR(10)

att_name

:= CHAR(10)

state_name

::=

CHAR(10)

event_name

CHAR(10)

LSL_func_name

::=

CHAR(10)

```

Table 8: A grammar for **TROM** class member - Transition Specifications

```

Time_Constriants ::= Time_Constraints: NL < constriants>

constriants

<constriant> NL | <constriant> NL <constriants>

constriant

::=

<time_cons_name>:

(< tran_spec_name>,

\langle \epsilon v \epsilon n t_n a m \epsilon \rangle, [\langle m i n \rangle, \langle m a x \rangle], \{\langle s t a t \epsilon s \rangle\}

states

\langle state\_name \rangle \mid \langle state\_name \rangle, \langle states \rangle \mid \varepsilon

state_name

::= CHAR(10)

time_cons_name

::= CHAR(10)

tran_spec_name

::= CHAR(10)

event_name

::= CHAR(10)

min

:= NAT

::= NAT

max

```

Table 9: A grammar for TROM class member - Time-Constraints

```

SCS ::= <scs> <include> <instantiate> <configure> end

```

Table 10: SCS Description

- A right square bracket followed by a comma

- Ignoring-states: list of states separated by commas and enumerated within brackets. The symbol {} representing an empty set.

The grammar for Time-Constraint is defined in the Table 9.

#### 4.2 A Formal Grammar for Subsystem

A Subsystem Configuration Specification (SCS) is used to specify a system/subsystem by aggregating instantiated objects. It can also be used to build large systems by composing subsystems. The syntax for a SCS is given in Table 10.

As shown in Table 10, a SCS is composed of several members. We will give a grammar for each of the SCS member.

The subsystem configuration specification for *Train*, *Gate* and *Contorller* as given in chapter 1 is consistant with the grammar given bellow.

```

scs ::= SCS < scs_name > NL

scs_name ::= CHAR(10)

```

Table 11: A grammar for SCS member – SCS-name

```

\begin{array}{lll} include & ::= & lnclude: & <scs\_name\_list > NL \mid \varepsilon \\ scs\_name\_list & ::= & <scs\_name>; \mid <scs\_name\_list> \\ scs\_name & ::= & CHAR(10) \end{array}

```

Table 12: A grammar for SCS member - Include

#### 4.2.1 Subsystem member -SCS-name

SCS-name is a header which describes the name of the SCS. The format is:

• The keyword SCS followed by scs name

The grammar for SCS-name is shown in Table 11.

#### 4.2.2 Subsystem member – Include

Include is used for importing subsystem definitions from other subsystem configuration specification. This provides modularity and makes it easier to reuse pieces of specification. The format is:

- The keyword Include followed by a colon and a list of other SCS names which are separated by commas.

- The *Include* is optional.

The grammar for *Include* is shown in Table 12.

#### 4.2.3 Subsystem member – Instantiate

Instantiat $\epsilon$  is used to define instantiation relationship between objects and their classes. The format is:

```

instantiates

Instantiate: \langle inst\_list \rangle NL | \varepsilon

::=

inst_list

<instantiate> | <instantiate>: <inst_list>

::=

instantiate

\langle obj\_name \rangle :: \langle trom\_name \rangle [\langle port\_card\_list \rangle]

::=

<port_card> | <port_card>, <port_card_list>

port_card_list

::=

::= < port_type_name > : < cardinality >

port_card

obj_name

::= CIIAR(10)

port_type_name

::= CHAR(10)

trom_name

::= CHAR(10)

cardinality

NAT

::=

```

Table 13: A grammar for SCS member – Instantiate

- The keyword Instantiate followed by a colon and list of instantiated objects which are separated by semi-colon.

- object name followed by the symbol ::

- A TROM class name followed by a left square bracket.

- A port type, followed by a colon, and the cardinality of ports for that port type.

If there are more than one port type, a comma separates the tuples of port type and cardinality.

- A right square bracket, followed by a point.

- The Instantiate is optional.

The grammar for *Instantiate* is shown in Table 13.

#### 4.2.4 Subsystem member - Configure

Configure is used to define a system/subsystem using objects specified in the Instantiate clause and subsystem specifications imported through the Include clause. It also links the ports of various interacting objects/subsystems using compositions. The format is:

• The keyword Configure followed by a colon and list of object-port links which are separated by semi-colon. Object-port link has the following syntax:

Table 14: A grammar for SCS member - Configure

- A pair of an instantiated object name followed by a symbol . and a symbol @ followed by a port name associated with the object.

- The symbol < ->

- Another pair of an instantiated object name followed by a symbol . and a symbol @ followed by a port name associated with the object.

The grammar for Configure is shown in Table 14.

#### 4.3 A Formal Grammar for Simulation Event

```

sel ::= SEL: <s_event_list>

s_event_list ::= <s_event> | <s_event>; <s_event_list>

s_event ::= <event_name>, <obj_name>, <port_name> <occur_time>

event_name ::= CHAR(10)

obj_name ::= CHAR(10)

port_name ::= CHAR(10) | NULL

occur_time ::= NAT

```

Table 15: A grammar for Simulation Event List

A Simulation Event is used to stimulate the user defined system and to trace the system behaviour. The Simulation Events are accepted as tuples, each appearing on a line. The format is:

• The keyword SEL followed by a colon and a list of simulation events which are separated by semi-colons. Each simulation event has the following syntax:

- An event name, followed by a comma.

- A TROM class object name, followed by a comma.

- A port name, followed by a comma. If the event is an internal event, the null port is specified by the reserved word NULL.

- A natural number specifying the time at which the event occurs, relative to the start time.

The grammar for Simulation Event List is shown in Table 15.

### Chapter 5

# Internal Representation – Abstract Syntax Tree

The Abstract Syntax Tree is an object-based data structure which contains objects that can be accessed during simulation. The animation system has four kinds of input: **LSL** traits, **TROM**, SCS, and Simulation Event List. Therefore, four kinds of Abstract Syntax Trees are constructed. The data structure of each AST might be different, depending on its usage. This section will focus on the detailed data structure design for each AST and also discuss the formal software specification using Larch/C++ specification language.

### 5.1 The TROM Abstract Syntax Tree Data Structure

As we mentioned in the previous chapter, a **TROM** input may contain one or several **TROM** classes. We should construct an AST for each **TROM** class.

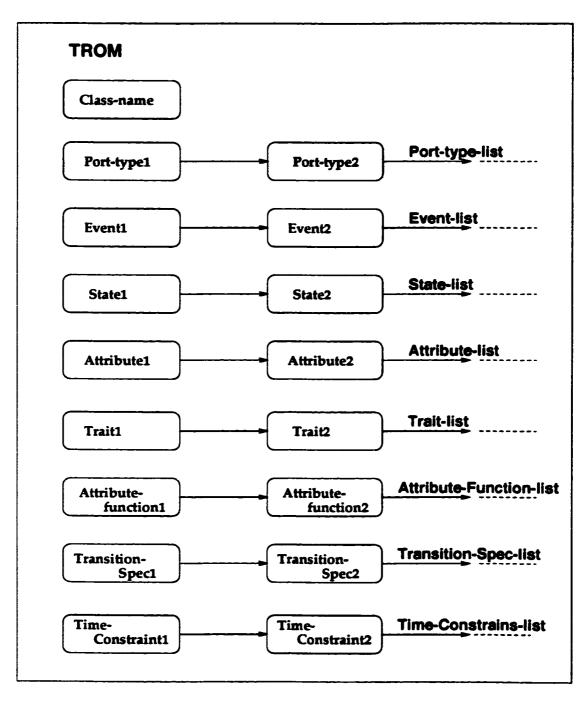

The TROM AST data structure is shown in Figure 10.

As shown in Figure 10, the **TROM** AST is a data construct which is a collection of **TROM** class member objects. There is a container for each type of class member object which can be implemented by a linked list. The **TROM** AST is unique and it can be identified by its class-name attribute. Some of the **TROM** class members

Figure 10: TROM Abstract Syntax Tree Structure.

Figure 11: Data Structure of TROM class members.

such as class-name, port-type list, event list are mandatory. So, their corresponding containers must contain at least one element. Others such as traits, attribute-function are optional. So, their containers can be empty.

The data structure of **TROM** class members are described in detail in the following subsections (see Figure 11, Figure 12 and Figure 13).

# 5.1.1 General Description for TROM AST class member containers

Except the Class\_name. all the **TROM** AST class members are represented by a container data type, which we said can be implemented by a linked-list. We named

them following the convention: X\_list is a container of elements of type X. It can be implemented by a list (linked-list) of X-type data.

For example, **Event\_list** is a container of elements of type Event. To apply the Object-Oriented system design principles, the container is an abstract data type which encapsulates the implementation details. We design the container class which supports the following standard access functions:

- create: Create an empty data container

- is Empty: Return a boolean value to assert if the container is empty

- remove: Remove a specific element from the container

- insert: Insert an element into the container at a specific location

- append: Add an element into the container at the end

- find: Find out a specific element from the container

- getFirst: Retrieve the first element from the container

- getNext: Retrieve an element from the container next to the current location

- destroy: Destroy the container and all its elements

The set of container management and navigational functions allow the fellow researchers to use the **TROM** AST without knowing the implementation details of their data structures.

#### 5.1.2 Class name

The class name is represented by a string variable which contains an unique **TROM** class identifier. The class name is mandatory in **TROM** class AST.

#### 5.1.3 Port-type-name

The port-type-name is represented by a string variable which is not duplicable in the port-type-list. The port-type-list is mandatory in **TROM** class AST.

#### **5.1.4** Event

The event is represented by a data structure in the event\_list. The data structure contains the following data members:

- event\_name: a string variable which is not duplicable in the event\_list.

- event\_type: an enumerated variable with the values input, output, internal.

- port\_type\_name: a reference to the existing port\_type\_name in the port-type\_list or null if the event\_type is internal.

The Event\_list is mandatory in TROM class AST.

#### 5.1.5 State

The State is represented by a data structure in the State\_list. The data structure contains the following data members:

- state\_name: a string variable which is not duplicable in the State\_list.

- state\_type: an enumerated variable with the values simple, complex. The complex state type means the state has a set of substates.

- if\_initiaLstate: a boolean variable to indicate if it is the initial state.

- Substate\_list: a container of substates of the **State\_list** type. It must be empty for simple state type and it must contain at least two different states for complex state types.

The State\_list is mandatory in TROM class AST.

#### 5.1.6 Attribute

The Attribute is represented by a data structure in the Attribute\_list. The data structure contains the following data members:

• att\_name: represents an attribute name and is a string variable, which is not duplicable in the Attribute\_list.

- att\_type: represents an attribute type and is an enumerated variable with the values { port\_type}, or { trait\_type}. The trait\_type is defined in the Trait\_list and port\_type is defined in Port-type\_list

- att\_typε\_name: represents an attribute type name and is a reference to an existing Port-type-list or Trait-list.

The Attribute\_list is mandatory in TROM class AST.

#### 5.1.7 Trait

The *Trait* is represented by a data structure in the **Trait\_list**. The data structure contains the following data members:

- trait\_name: represents a trait name and is a string variable, which is not duplicable in the **Trait\_list**.

- trait\_type\_name: represents a trait type name and is a string variable, which is not duplicable in the **Trait\_list**.

- arg\_list: a container of arguments set associated with the trait. It can be a reference to an existing port\_type\_name or trait\_type\_name and at least contains one argument.

The **Trait\_list** is optional in **TROM** class AST.

#### 5.1.8 Attribute-function

The Attribute-function is represented by a data structure in the Attribute-function\_list. The data structure contains the following information:

- state\_name: a reference to an existing state in State\_list.

- attribute\_name\_list: a reference container to the existing Attribute\_list associated with the state. attribute\_name\_list associated with a state can be empty.

The Attribute-function\_list is optional in TROM class AST.

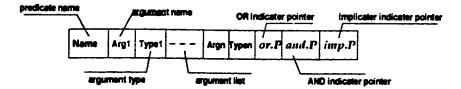

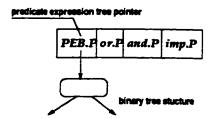

#### 5.1.9 Assertion Tree Data Structure

We have seen that in the grammar for Transition Specification, the port\_conditions, enabling\_conditions and post\_conditions are all instances of a generic type, an assertion expression. The assertion expression can be represented by and stored in a specific container type – a binary tree. It can be evaluated by traversing the binary tree in inorder.

We can name the various Transition\_Spec assertions by the following convention:

X\_tree is a binary tree container of elementary assertions for representing the conditions of type X.