## **NOTE TO USERS**

Page(s) not included in the original manuscript and are unavailable from the author or university. The manuscript was scanned as received.

40,43,88

This reproduction is the best copy available.

# Wideband Multi-Level QAM MODEM with Programmable Bit Rate and Programmable Intermediate Carrier Frequency

Qi Wang

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements

For the Degree of Master of Applied Science at

Concordia University

Montreal, Quebec, Canada

August 2003

© Qi Wang, 2003

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisisitons et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-612-91134-9 Our file Notre référence ISBN: 0-612-91134-9

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats. L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou aturement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this dissertation.

While these forms may be included in the document page count, their removal does not represent any loss of content from the dissertation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de ce manuscrit.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

# Canadä

#### ABSTRACT

# Wideband Multi-Level QAM MODEM with Programmable Bit Rate and Programmable Intermediate Carrier Frequency

#### Qi Wang

Quadrature Amplitude Modulation (QAM) has been predominant in current wireless digital communications, such as satellite and microwave radio communications. Due to diverse wireless communication applications, a digital QAM modem with diverse bit rates (R) and intermediate carry frequency (IF) is of great interest. The main objective of this thesis is to design, analyze and implement a multi-level QAM modem with programmable bit rates and programmable IF, thus not only meeting different requirements, but also dramatically reducing the complexity of the following analog Radio Frequency (RF) block.

In the thesis, the digital QAM modem is built based on the fundamentals of Digital Communication Systems (DCS) and Digital Signal Processing (DSP). The underlying relationship between signal resampling and its filter impulse response is studied and analyzed. A new signed-array structure for 2's complement multiplication is introduced in order to improve the regularity and flexibility of hardware design. The modem analysis and comparisons are shown in terms of performances and structures. Hardware design techniques are developed in-depth. The modem model is coded in VHDL (VHSIC Hardware Description Language) and synthesized using Synopsys tools, and its performance is evaluated. The regular structure and portable VHDL coding of the modem can satisfy diverse applications implemented in different FPGAs or ASICs.

#### Acknowledgment

The subject Wideband Proprammable Modem that my supervisor Prof. Yousef Shayan particularly chose for me is immensely challenging and inspiring. The experience of doing this research could never have been more rewarding and fruitful to me. Particularly at the beginning, I would like to sincerely thank Prof. Yousef Shayan, my thesis supervisor, for his valuable guidance and priceless advice in carrying out this research from its start to its end. He introduced me to this exciting area of Wideband Multi-Level QAM Modem, which is market-oriented and of great importance in modern digital communications, and was a constant source of inspiration. Without his encouragement and precious advice all the time, this research would have been impossible to be done.

I would also like to extend my heart-felt appreciation to Dr. Kort and Mr. Obuchowicz for their help and valuable suggestions whenever I needed it.

My wife has always been a stimulus of my research. I would not smoothly have been through this hard time without her long-time encouragement and support.

I would like to express my honest gratitude to my colleagues and friends namely Haiqing Zhang, Wei Wu, Yanjie Wang, Yang Xiao and other colleagues from the Graduate Student Office. These individuals have provided boundless energy and selfless assistance during my graduate work and have seen me through this most important moment of my life as a student of Concordia University. Without their support, this would not have been a smooth, memorable ride.

# **Table of Contents**

| Chapter 1 Introduction                             | 1  |

|----------------------------------------------------|----|

| 1.1 Literature Survey for QAM Modem Implementation | 2  |

| 1.2 Thesis Preview                                 | 5  |

| 1.3 Thesis Organization                            | 6  |

| Chapter 2 Modem Fundamentals                       | 8  |

| 2.1 Review of Basic DSP Fundamentals               | 9  |

| 2.1.1 Signal Sampling                              | 9  |

| 2.1.2 Binary Number Representations                | 11 |

| 2.2 Pulse-Shaping and Matched Filter Concept       | 12 |

| 2.2.1 Pulse-Shaping                                | 12 |

| 2.2.2 Matched Filter Detection                     | 14 |

| 2.2.3 Signal Re-sampling                           | 16 |

| 2.3 Digital IF $f_c$ and Symbol Rate $R_s$         | 17 |

| 2.4 Interpolation and Decimation                   | 19 |

| 2.5 Finite-Precision Numerical Effects             | 21 |

| 2.5.1 Signal Scaling                               | 21 |

| 2.5.2 Truncation and Rounding                      | 22 |

| Chapter 3 Modem Simulations                         | 24   |

|-----------------------------------------------------|------|

| 3.1 Why FIR Filter                                  | 25   |

| 3.2 Pulse-Shaping Filter & Matched Filter Order     | 25   |

| 3.3 Interpolation Filter & Decimation Filter Order  | 29   |

| 3.4 Finite Word Length                              | 31   |

| 3.4.1 Signal Scaling                                | 31   |

| 3.4.2 System Quantizaiton                           | . 33 |

| 3.5 Coefficients and 2's Complement Representations | . 36 |

| Chapter 4 Hardware Design Techniques                | 44   |

| 4.1 Quadrature Signal Constellation                 | . 44 |

| 4.2 FIR Filter Design                               | . 46 |

| 4.2.1 Transversal Structure                         | . 46 |

| 4.2.2 Poly-Phase Structure                          | . 49 |

| 4.3 Adders and Mulitpliers                          | . 53 |

| 4.3.1 High-Speed CLA-CSA Adder                      | . 54 |

| 4.3.2 New Structure for Signed Array Multiplier     | . 55 |

| 4.4 Carry Frequency, Baud rate and Memory Size      | . 63 |

| Chapter 5 Modem Hardware Implementation             | 69   |

| 5.1 Pipelining & Parallel Processing                | . 70 |

| 5.2 VHDL Implementation                             | 71   |

| 5.2.1 VHDL Design Strategies                        | . 71 |

| 5.2.2 Primitives, Components and Top-Level System   | 71   |

| 5.3 Clock Distribution and System Throughputs       | 76 |

|-----------------------------------------------------|----|

| 5.4 System Verification                             | 77 |

| 5. 5 Illustrative Example Based on Xilinx Virtex II | 78 |

| 5. 5.1 Effects Caused by Structures or Hardware     | 78 |

| 5. 5.2 System Parameters and Features               | 79 |

| 5. 5.3 Tradeoffs to Enhance System Performances     | 80 |

| 5. 6 Commercial Applications Using ASICs            | 82 |

| 5. 7 System Schematic and Pin Descriptions          | 84 |

| Chapter 6 Conclusions                               | 86 |

| Bibliography                                        | 88 |

| Appendix A                                          | 92 |

# **List of Figures**

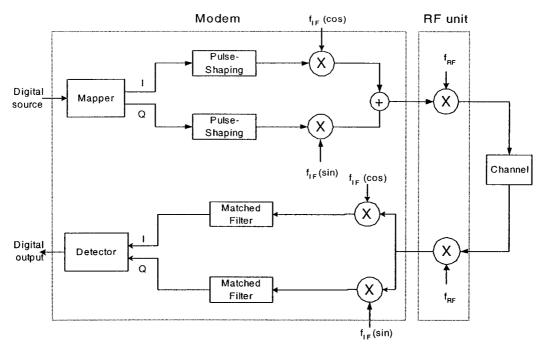

| Fig 1-1 | Typical QAM transmitter/receiver diagram                             | . 2 |

|---------|----------------------------------------------------------------------|-----|

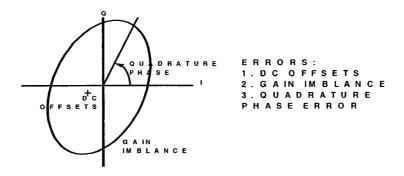

| Fig 1-2 | Errors in analog quadrature demodulation                             | . 3 |

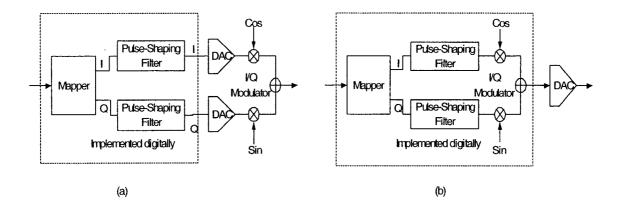

| Fig 1-3 | Digital implementations of a transmitter                             | . 4 |

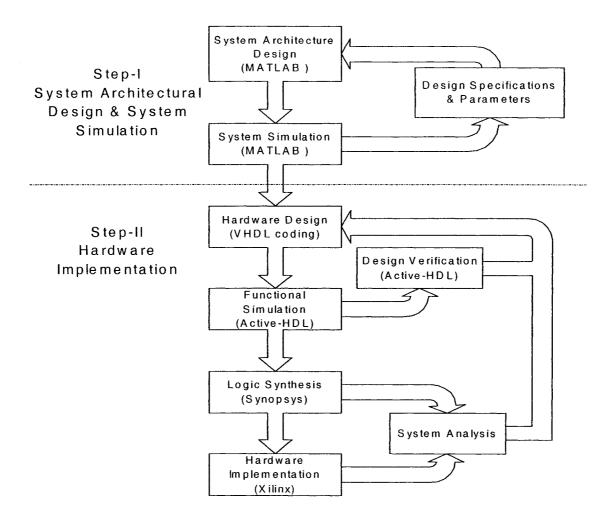

| Fig 1-4 | Design & implementation flow of WDM                                  | . 6 |

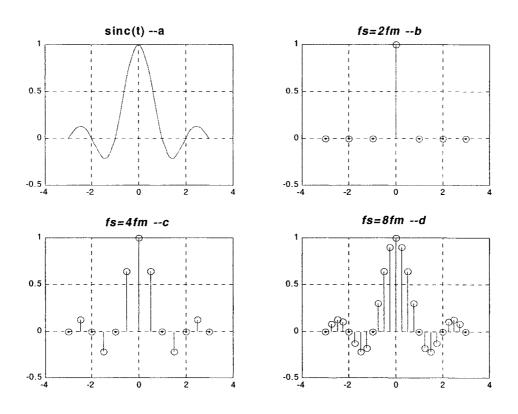

| Fig 2-1 | Impulse response of LPF with different up sampling rates             | 10  |

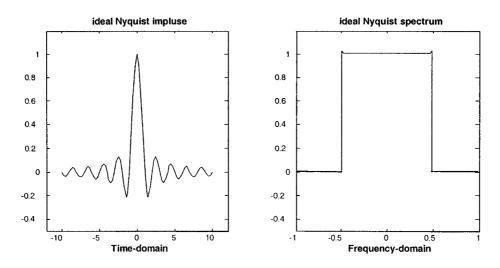

| Fig 2-2 | Ideal Nyquist Filter                                                 | 13  |

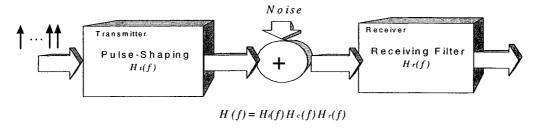

| Fig 2-3 | Typical baseband digital system                                      | 14  |

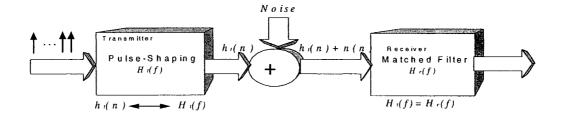

| Fig 2-4 | Typical matched detection system                                     | 15  |

| Fig 2-5 | Pulse-shaping filter                                                 | 16  |

| Fig 2-6 | Modulator's sampling rate at each stage                              | 18  |

| Fig 2-7 | Filter with rational factor L/M                                      | 19  |

| Fig 2-8 | Modem and its symbol rates                                           | 20  |

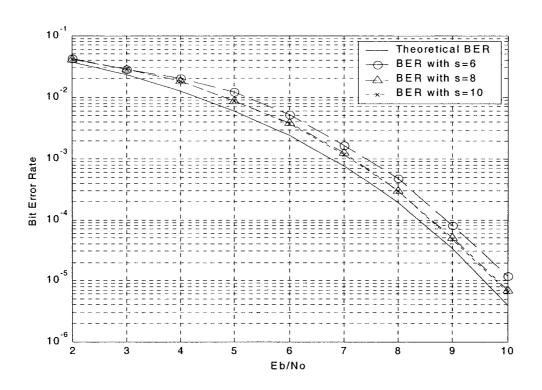

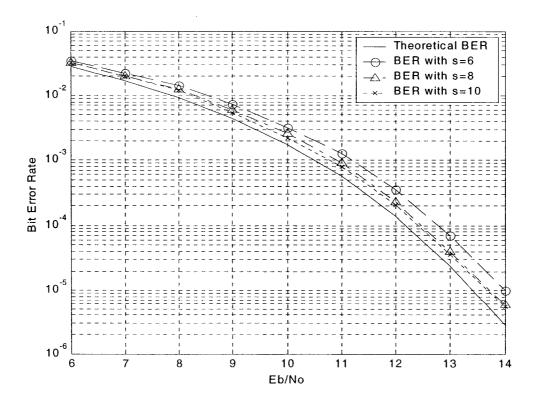

| Fig 3-1 | QPSK error performances with different symbol spans                  | 27  |

| Fig 3-2 | 2 16-QAM error performances with different symbol spans              | 27  |

| Fig 3-3 | Frequency response of Square-Root Raised Cosine filter               | 28  |

| Fig 3-4 | Impulse response of Square-Root Raised Cosine filter                 | 29  |

| Fig 3-5 | Frequency response of interpolator with different factors            | 30  |

| Fig 3-6 | 5 16-QAM BERs with different word lengths                            | 34  |

| Fia 3-7 | Frequency response of the quantized square-root raised cosine filter | 35  |

| Fig 3-8 Quantized frequency response of interpolator/decimator              | 36       |

|-----------------------------------------------------------------------------|----------|

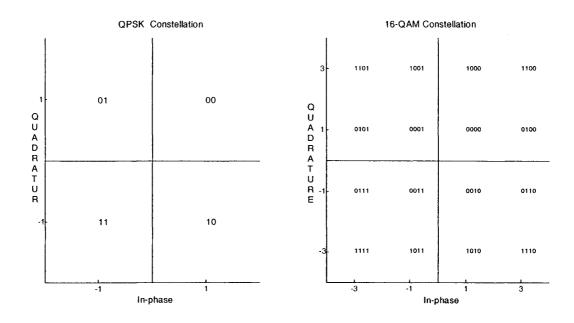

| Fig 4-1 Rectangular QPSK/16-QAM signal constellations                       | 45       |

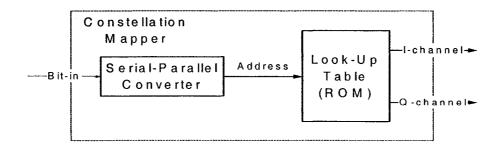

| Fig 4-2 Lookup table for QAM mapping                                        | 45       |

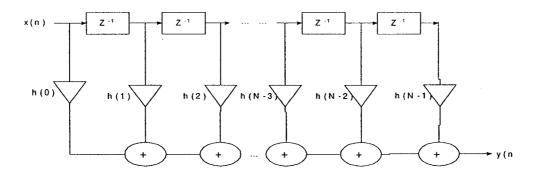

| Fig 4-3 Transversal structure of a FIR filter                               | 46       |

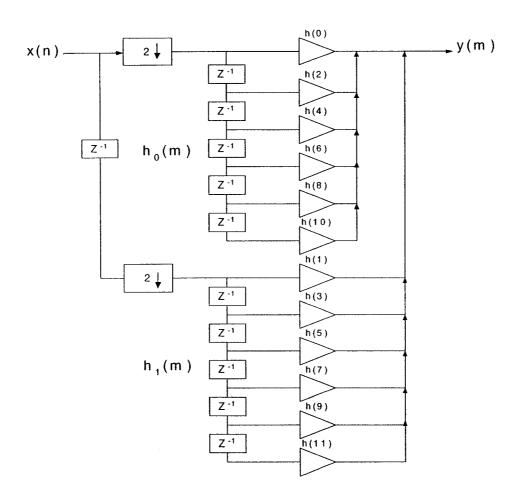

| Fig 4-4 Decimator model (N=12, M=2)                                         | 48       |

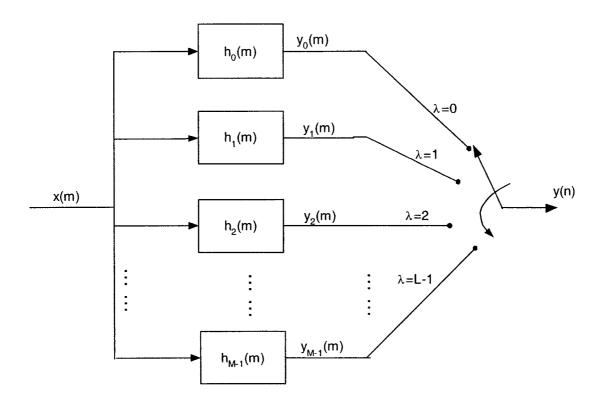

| Fig 4-5 Poly-phase decimation structure (N=12, M=2)                         | 49       |

| Fig 4-6 Poly-phase decimator with an input commutator rotating countcle     | ockwise  |

|                                                                             | 50       |

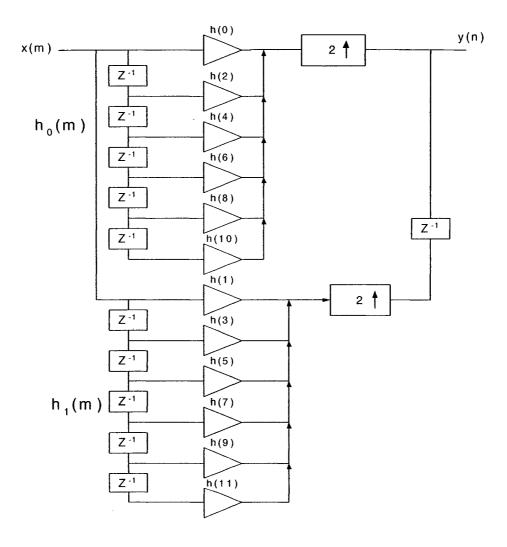

| Fig 4-7 Poly-phase interpolation filter ( <i>N</i> =12, <i>L</i> =2)        | 51       |

| Fig 4-8 Interpolator Model                                                  | 52       |

| Fig 4-9 Poly-phase interpolator with an output commutator                   | rotating |

| countclockwise                                                              | 53       |

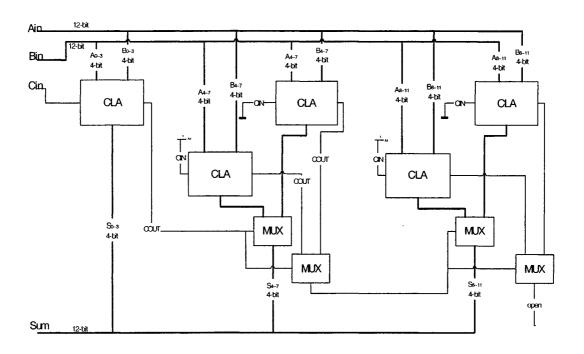

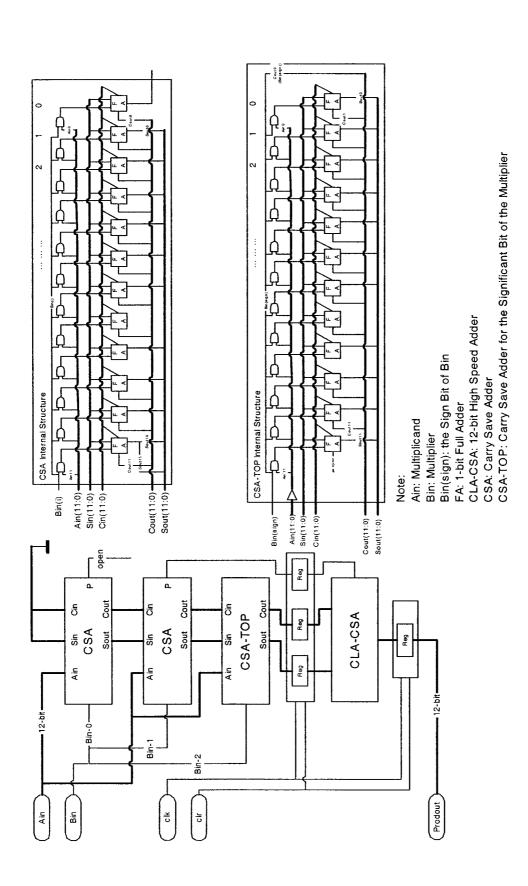

| Fig 4-10 12-bit high-speed CSA-CLA adder                                    | 55       |

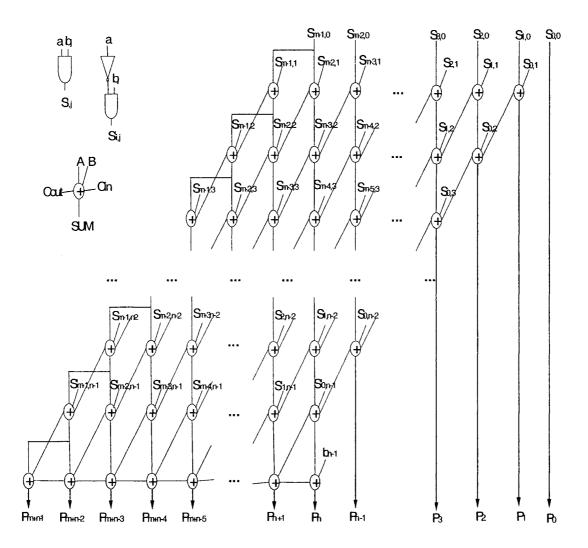

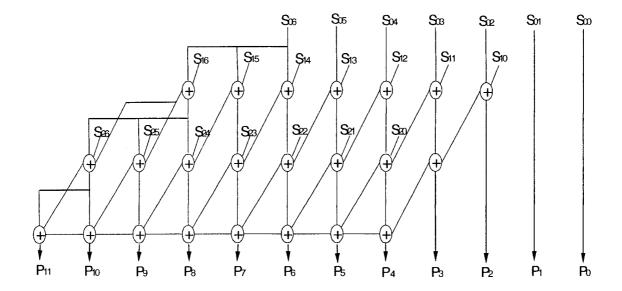

| Fig 4-11 The new structure for 2's complement multipication                 | 60       |

| Fig 4-12 6-bit by 6-bit signed-array multiplier with 7-bit roundoff product | 61       |

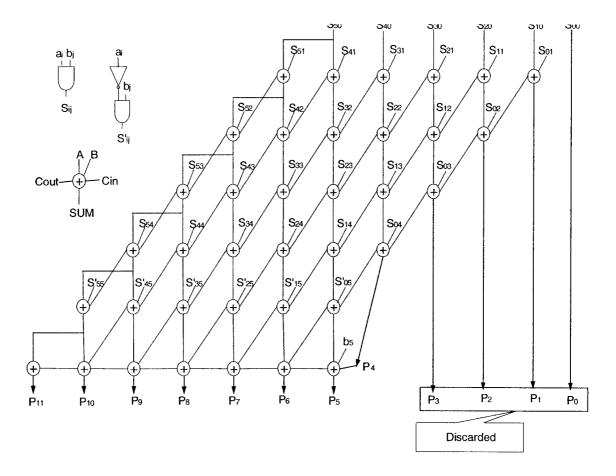

| Fig 4-13 The new structure for radix-4 booth-encoded partial products       | 62       |

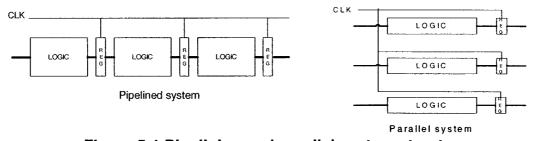

| Fig 5-1 Pipelining and parallel system structure                            | 70       |

| Fig 5-2 12-bit by 3-bit roundoff multiplier                                 | 73       |

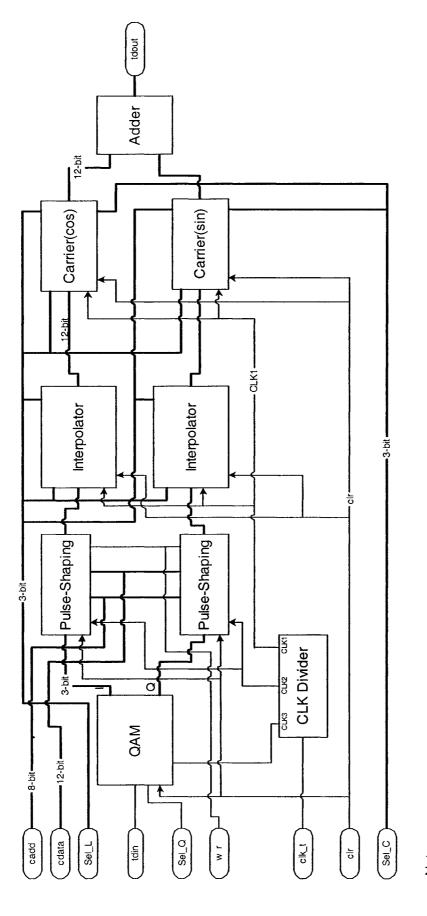

| Fig 5-3 Modulator diagram                                                   | 74       |

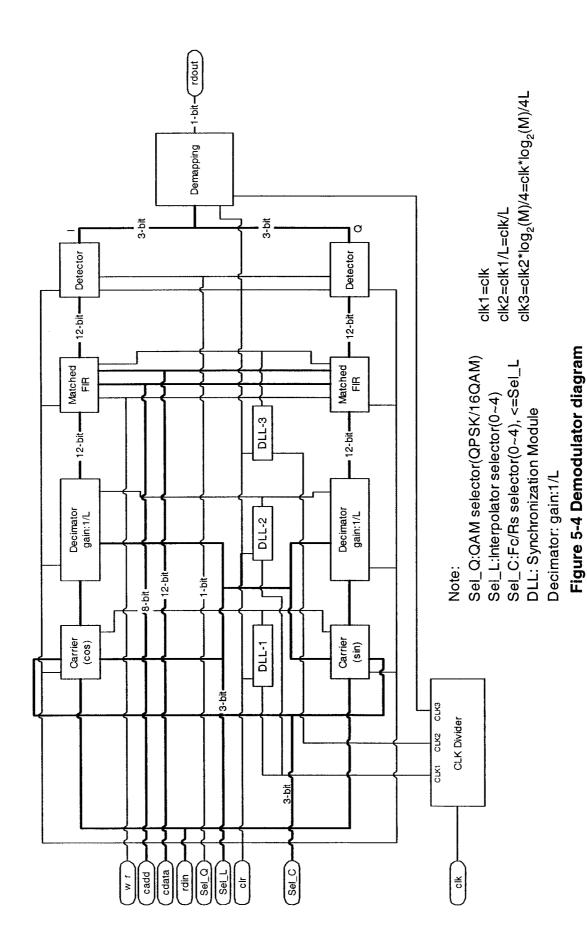

| Fig 5-4 Demodulator diagram                                                 | 75       |

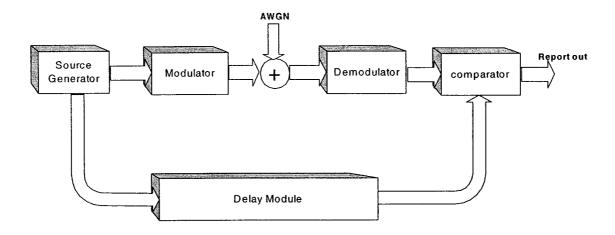

| Fig 5-5 Modem Testbench                                                     | 78       |

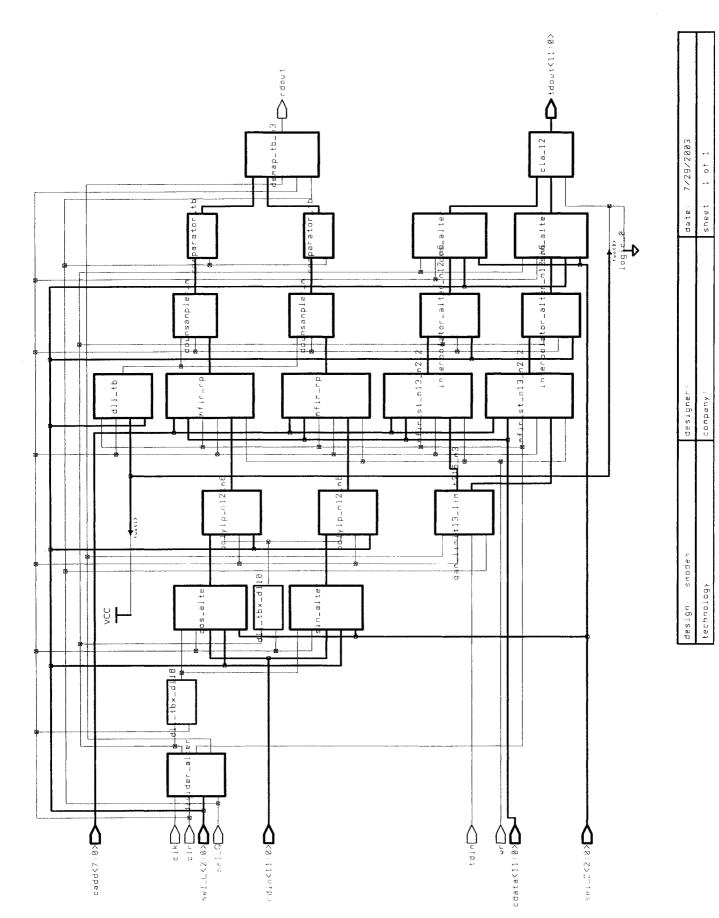

| Fig 5-6 Modem schematic                                                     | 85       |

## **List of Tables**

| Table 3-1 16-QAM error performances through interpolation/decimation       | 30 |

|----------------------------------------------------------------------------|----|

| Table 3-2 Word lengths for each block of the transmitter                   | 34 |

| Table 3-3 Word lengths for each block of the receiver                      | 35 |

| Table 3-4 QPSK/16-QAM constellation mapping                                | 37 |

| Table 3-5 Pulse-shaping/ Matched filter coefficients                       | 38 |

| Table 3-6 Interpolator coefficients                                        | 39 |

| Table 3-7 Decimator coefficients                                           | 41 |

| Table 3-8 IF modulator (cosine) coefficients                               | 42 |

| Table 4-1 Memory Size ( $MS$ ) effect on IF $f_c$ precision                | 64 |

| Table 4-2 Baud rate $R_s$ effect on IF $f_c$ precision                     | 65 |

| Table 4-3 Baud rate $R_s$ precision effect on IF $f_c$ precision           | 66 |

| Table 4-4 $R_s$ & $MS$ effect on IF $f_c$ precision                        | 67 |

| Table 5-1 The modem sampling rate at each stage                            | 76 |

| Table 5-2 Timing analysis for different FPGAs                              | 79 |

| Table 5-3 Area & Power analysis for different structures of matched filter | 79 |

| Table 5-4 The modem system parameters                                      | 80 |

| Table 5-5 Data rates for T-carrier system transmission                     | 82 |

| Table 5-6 Estimations for memory size and IF frequency accuracy            | 82 |

| Table 5-7 The modem pin descriptions                                       | 84 |

# **List of Acronyms**

## (Alphabetical Order)

| Acronym Meaning                             |

|---------------------------------------------|

| ASICApplication Specific Integrated Circuit |

| AWGN Additive White Guassian Noise          |

| BER Bit Error Rate                          |

| CPACarry-Propagation-Adder                  |

| CSACarry-Save-Adder                         |

| CSACarry-Select-Adder                       |

| DACDigital-Analog Converter                 |

| DCSDigital Communication System             |

| DSPDigital Signal Processing                |

| FIRFinite Impulse Response                  |

| FPGAField Programmable Gate Array           |

| IF                                          |

| IIRInfinite Impulse Response                |

| ISIIntersymbol Interference                 |

| KCMConstant Coefficient Multiplier          |

| LPFLow Pass Filter                          |

| LUTLook-Up Table                            |

| MFMatched Filter                            |

| M-QAMM-ary Quadrature Amplitude Modulation  |

| MS   | Memory Size                         |

|------|-------------------------------------|

| PSTN | Public Service Telephone Network    |

| QPSK | Quadrature Phase Shift Keying       |

| RF   | Radio Frequency                     |

| RCA  | Ripple-Carry-Adder                  |

| RAM  |                                     |

| VHDL | VHSIC Hardware Description language |

| VLSI | Very Large Scale Integration        |

| WDM  | Wideband Digital Modem              |

# **Chapter 1 Introduction**

Based on different applications, in modern communication systems, diverse modulation techniques, such as Phase Shift Keying (PSK), Frequency Shift Keying (FSK) and Quadrature Amplitude Modulation (QAM), are well developed and widely deployed. However, with the ever-growing market demands, the development of communication systems is now facing more and more rigorous constraints:

- Available bandwidth

- Permissible power

- Reliable error performance

Due to its bandwidth & power efficiency, QAM technology captures more attention and is extensively applied to high-speed digital communication systems. Currently, the commercial applications of QAM technology cover many applications such as satellite and microwave radio communications.

A typical functional transmitter/receiver diagram for Quadrature Amplitude Modulation is shown in Fig 1-1which consists of a QAM modem and a Radio Frequency (RF) unit. The RF unit is usually implemented by analog technology since its high radio frequency cannot be generated by current digital hardware technology.

Fig 1-1 Typical QAM transmitter/receiver diagram

# 1.1 Literature Survey for QAM Transmitter/Receiver Implementation

Currently, there are mainly 2 implementation approaches for a digital QAM modem: analog and digital. In analog implementation, there exist the following inevitable drawbacks due to analog circuit inaccuracies:

- 1. In-phase & Quadrature (I & Q) imbalance from magnitude and phase point of view.

- 2. In-phase & Quadrature (I & Q) imbalance from Direct Current (DC) offset and drift point of view.

The errors associated with these drawbacks are illustrated in Fig 1-2. An ideal quadrature demodulator will have a perfect circle with its center at the origin (0,0) on I/Q plane. DC offsets in the analog demodulator circuit cause the center to move from the origin.

Elliptical characteristics on I/Q plane are due to gain imbalance and quadrature phase error.

Fig 1-2 Errors in analog quadrature demodulation

To avoid the above disadvantages caused by analog hardware, there is a clear trend toward implementing part of the system digitally. The section of the system designed digitally can vary from radio to radio. Therefore, the location of the Digital-to-Analog Converter (DAC) varies. For example, Fig 1-3 [1] shows 2 different approaches to implement a digital transmitter. In Fig 1-3 (a), the transmitter is implemented by digital baseband filters and analog I/Q modulators. Two DACs are located prior to I/Q modulators in this case. However, to implement I/Q modulators digitally, as shown in Fig 1-3 (b), leads to less expensive cost, more stable results and better system peerformance. In this case, a DAC is applied right after digital I/Q modulators. The dash-lined sections in Fig 1-3 are digitally implemented.

Fig 1-3 Digital implementations of a transmitter:

#### (a) Analog IF; (b) Digital IF

In fully digital modems, many designers have developed a simple approach with  $f_c = R_s$  ( $R_s$ : baud rate,  $f_c$ : IF carrier frequency) [2, 3, 4]. This approach has taken advantage of the inherent relationship between pulse-shaping filters and IF modulators; thus hardware for the transmitter implementation could be significantly reduced. This approach is typically used in some specific applications where the baud rate  $R_s$  is fixed. However, the above method is not suitable for general-purpose commercial modems since they may be used for different applications. In this thesis, we will design and implement such a general-purpose modem considering the following requirements:

- Variable input data rates (R) for a wide variety of customer applications

- Fixed and selectable IF carrier frequency so as to reduce the complexity of analog RF

- Low bit error rate  $(P_B)$  for high quality communications

#### 1.2 Thesis Preview

The objective of this thesis is to design and implement a wideband digital modem based on QAM modulation, which features:

- Fully digitized

- Multi-level QAM modulation (QPSK/16-QAM)

- Variable and high-speed input bit rates

- Fixed but selectable IF

- Single chip modem (ASIC or FPGA)

In the course of the design, considerable success is achieved. An approach is explained for having selectable and fixed carrier frequency. A new array-based structure for 2's complement multiplication is proposed and employed in hardware implementation. Pipelining and parallel processing is widely used for high-speed implementation of a pure digital QAM modem system.

The design and implementation of the modem consists of 2 steps. The first step focuses on the system architectural design and the system-level simulation by using MATLAB simulation software. The design specifications and parameters are determined and optimized at this step. The second step concentrates on the hardware design by using VHDL (VHSIC Hardware Description Language). At this step, the hardware structure of the system is optimized and the test-bench for design verification is built. Finally, as an example, the hardware implementation based on Xilinx virtex II FPGA is illustrated. Fig 1-4 shows the design and implementation flow of the modem.

Figure 1-4 Design & implementation flow of the modem

## 1.3 Thesis Organization

The thesis is organized as follows:

a. In Chapter 2, a thorough introduction is given to Digital Communication Systems (DCS) and Digital Signal Processing (DSP) fundamentals and corresponding algorithms as to the modem. Subjects include discrete sampling and 2's complement representation, digital signal processing and its applications, interpolation and decimation, finite precision and quantization effects.

- b. In Chapter 3, the modem fundamental architectures will be built using MATLAB simulation tools. At this stage, the system structure and functionality is simulated and verified, and the corresponding parameters such as filter orders and word length are optimized and determined.

- c. In Chapter 4, hardware design techniques for the modem, such as constellation mapping, high-speed adder, poly-phase filters are developed. Furthermore, a new signed-array structure for 2's complement multiplication is introduced and detailed. Also, pipelining & parallel processing are discussed.

- d. In Chapter 5, the detailed structure of each block is built using VHDL. Some optimizations are adopted to improve the performance. The functional verification is made using ALDEC Active-HDL. Design analysis and logic synthesis is done by Snopsys Design Compiler and Synopsys Analyzer. The system hardware implementation targeted to Xilinx virtex II FPGA is accomplished by using Xilinx Design Manager. At this stage, the overall system specifications will be given.

- e. Chapter 6 summarizes the whole work and main contributions of the thesis.

## **Chapter 2 Modem Fundamentals**

As discussed in Chapter 1, a purely digitally implemented QAM modem has the advantages in terms of cost and performance; thus it would be more preferable in modern communication system designs. However, unlike analog signals, digital signals are processed in a different way, called Digital Signal Processing (DSP), which is concerned with the representation, transformation and manipulation of signals and the information they contain. In this chapter, some basic but important DSP fundamentals including signal sampling and binary number representation are first introduced. Particular attention is paid to pulse-shaping and matched filter (MF) concepts. Nyquist filters and zero inter-symbol interference (ISI) are discussed in this section. The signal re-sampling section clearly manifests the inherent relationship between the digital filter and its input signal. The relation of the symbol rate and digital intermediate frequency (IF) is also discussed. Furthermore, the concept of interpolation and decimation are introduced for pure digital modems with fixed IF. At the end, the quantization effects in digital systems are explained.

#### 2.1 Review of Basic DSP Fundamentals

Compared to analog systems, digital signals feature two characteristics: time-discrete and amplitude-discrete (a set of finite values). In this section, we give a brief discussion to these 2 major aspects that arise in processing and implementing digital systems. A more detailed analysis for signal re-sampling and finite-precision effects is given in section 2.2 and 2.5.

## 2.1.1 Signal Sampling

A discrete-time system takes an input of numbers and produces an output sequence of numbers. These number sequences x(n) are often samples of a continuous function of time, where  $x(n) = x_a(nT)$ , which represents the value of an analog signal  $x_a(t)$  at equally spaced times  $t_n = nT$ , and n is an integer. To simplify the discussion, T is usually set to 1 unless otherwise specified.

It is well known that a continuous signal with maximum frequency  $f_m$  can be restored without information loss if it is sampled by the sampling rate  $f_s$  larger than or equal to  $2 f_m$  (Nyquist Sampling Theorem). The impulse response of an ideal Nyquist low-pass filter (LPF) in time domain and its frequency spectrum can be expressed as:

$$h(t) = W \cdot \sin c(Wt) \tag{2.1}$$

$$H(f) = \begin{cases} 1 & |f| \le \frac{W}{2} \\ 0 & elsewhere \end{cases}$$

(2.2)

where  $\frac{W}{2}$  is the bandwidth of LPF.

For a digital filter, we often use h(n) and  $H(e^{jw})$  to represent the filter impulse response and frequency spectrum, respectively. Hence, the digital filter response h(n), sampled from its analog impulse response function h(t), should comply with *Nyquist Sampling Theorem*. In real systems, the sampling rate that is used to obtain h(n) from h(t) is usually performed at a rate that exceeds the *Nyquist minimum bandwidth* by a factor of 4 or more.

By using MATLAB, Fig 2-1 shows different h(n) sequences that can be obtained from the same analog impulse function h(t). This has been achieved by up sampling at rates of 2, 4, and 8, where  $f_m$  is the cutoff frequency of  $\sin c(t)$ .

Figure 2-1 Impulse response of LPF with different up sampling rates a. analog function h(t)=sinc(t); b. h(n) with sampling rate  $f_s=2f_m$ ; c. h(n) with sampling rate  $f_s=4f_m$ ; d. h(n) with sampling rate  $f_s=8f_c$

#### 2.1.2 Binary Number Representations

Generally, we assume that signal values and system coefficient have infinite precision in theoretical analyses of discrete-time systems. However, when implementing digital systems, the signal values and system coefficients should be represented with finite precision since they need to be stored in finite-length registers. The digital hardware implementation is based on the binary-number representation. Currently, 3 number representation formats, which are signed magnitude, 1's complement and 2's complement, are available. But 2's complement representation is the most common for digital system designs because its subtraction can be performed with addition circuitry. In 2's complement, a real number with infinite-precision can be represented as [5]:

$$x = X_{m} \left( -b_{m-1} + \sum_{i=0}^{m-2} b_{i} 2^{i-(m-1)} \right)$$

(2.3)

Where  $X_m$  is an arbitrary scale factor and the  $b_i$  is either 0 or 1.  $b_{m-l}$  is referred to as the sign bit and m is an integer. In Eq (2.3),  $0 \le x \le X_m$  when  $b_{m-l}=0$ ; otherwise,  $-X_m \le x \le 0$ . In hardware implementation, this arbitrary number x must be represented with finite-precision using a finite bit length (say l bits, l < m). So Eq. (2.3) can be modified to:

$$\hat{x} = Q_{l}[x] = X_{m}(-b_{l-1} + \sum_{i=0}^{l-2} b_{i} 2^{i-(l-1)}) = X_{m} \hat{x}_{l}$$

(2.4)

In this case, the fractional part of the quantized number can be represented as:

$$\hat{x}_{L} = b_{l-1}b_{l-2} \dots b_{0} \tag{2.5}$$

Obviously,  $\hat{x}$  in Eq (2.4) is the quantized result of x. This leads to a quantization error that can be expressed as:

$$\varepsilon = x - Q_{t}[x] \tag{2.6}$$

More detailed analysis for quantization effects is given in section 2.5.

## 2.2 Pulse Shaping and MF Concept

In wireless communication systems, the frequency bandwidth is always limited because of signal transmission channel bandwidth constraint and government regulations. However, a non-processed digital signal stream is a bit stream whose spectral content usually extends from DC up to infinity. It must be converted to a waveform that is compatible with the government requirements and transmission channel. Pulse-shaping is such a process that can transmit a binary representation (rectangular pulse) to a baseband waveform (Nyquist pulse) whose bandwidth can meet the above requirements. And matched filtering is its paired process in the demodulator side used to provide the maximum signal-to-noise power ratio at the output for a given transmitted signal waveform.

#### 2.2.1 Pulse-Shaping

The more compact the signaling spectrum is made, the greater is the number of users that can simultaneously be served. For wireless communication systems, it is essential to reduce the required system bandwidth as much as possible since it means the greatest profit to communication service providers. However, there is a basic limitation to such bandwidth reduction. Once a system operates at smaller bandwidths, the pulses would spread in time domain and result in interference among adjacent symbols. This effect refers as to *Intersymbol Interference* (ISI). Hence, a pulse-shaping filter should be:

- with the bandwidth as small as possible

- with zero ISI

According to Nyquist [7], the theoretical minimum system bandwidth needed in order to detect  $R_s$  symbols/s, with zero ISI, is R/2 Hz. This is called *Nyquist Bandwidth Constraint*. The impulse response and frequency spectrum of an ideal Nyquist filter is shown in Fig 2-2. In hardware implementation, a Nyquist filter with ideal rectangular-shaped frequency transfer function is not realizable since its corresponding time-domain pulse is with infinite length.

Figure 2-2 Ideal Nyquist Filter

Since ideal Nyquist filters are not realizable, a prudent decision should be made by which the requirement of zero ISI is met and the system bandwidth is reasonably small but greater than *Nyquist bandwidth constraint*. Raised cosine filter is one of Nyquist filters that can meet the above requirements. Its frequency transfer function can be expressed as follows:

$$H(f) = \begin{cases} \cos^{2}\left(\frac{\pi}{4} \frac{|f| + W - 2W_{0}}{W - W_{0}}\right) & |f| < 2W_{0} - W \\ 0 & |f| > W \end{cases}$$

(2.7)

where W is absolute bandwidth and  $W_0 = 1/2T$  represents the minimum Nyquist bandwidth. The roll off factor is defined as  $r=(W-W_0)/W_0$ ,  $0 \le r \le 1$ . The difference of  $W-W_0$  is termed "excess bandwidth".

A convenient model for a typical baseband digital system and its frequency transfer function H(f) can be illustrated as Fig 2-3, where,  $H_t(f)$ ,  $H_c(f)$ ,  $H_r(f)$  are transfer functions for the transmitter, channel, and receiver, respectively.

Figure 2-3 Typical baseband digital system

Without noise appearance, the transfer function for the channel is set  $H_c(f)=1$ . Thus, the system transfer function H(f) can be rewritten as:  $H(f)=H_t(f)H_r(f)$ . The receiving filter is often configured to compensate the distortion by both the transmitter and the channel. The signal-to-noise ratio (SNR) could be optimized if  $H_t(f)=H_r(f)=H(f)^{1/2}$  [5] which is called "square-root raised cosine filter". In such a system, the transmitting filter and receiving filter are identical. Although the impulse response of the square-root raised cosine filter, called "square-root Nyquist pulse", doesn't exhibit zero ISI, the product of their transfer functions will give rise to zero ISI if a square-root raised cosine filter is used both at the transmitter and at the receiver [10].

#### 2.2.2 Matched Filter Detection

The maximum signal-to-noise ratio could be obtained when the impulse response of the receiving filter is the mirror image of the transmitted signal s(t), delayed by the symbol duration T [10]. This kind of the receiving filter is then called "matched filter". Its impulse response can be expressed as:

$$h_r(t) = \begin{cases} ks(T-t) & 0 \le t \le T \\ 0 & elsewhere \end{cases}$$

(2.8)

where k is constant.

For digital systems, the above matched filter is called "sampled matched filter". Its function can also be expressed as:

$$h_{r}(n) = \begin{cases} ks(M-n) & 0 \le n \le M \\ 0 & elsewhere \end{cases}$$

(2.9)

where M is an integer.

In digital communication systems, MF detection is always required since the maximum SNR should be obtained. Meanwhile, zero ISI is essential for the whole system as well. Fortunately, the square-root raised cosine filter meets these 2 requirements if a root-square raised cosine filter is used both at the transmitter and the receiver.

Figure 2-4 Typical matched detection system

As shown in Fig 2-4, the input of the transmitting filter is processed as an impulse sequence, so the transmitted signal s(n) is exactly  $h_t(n)$ . And the impulse response of the square-root raised cosine filter is even symmetrical; thus  $h_t(n) = h_t(-n)$ . Clearly, since the transmitting filter and the receiving filter are identical, the following equation can be established:

$$h_r(n) = h_r(n) = h_r(-n) = s(-n)$$

(2.10)

In Eq(2.9), integer M means time delay; it doesn't affect any other characteristics. Hence, it is obvious that using square-root raised cosine filter at both transmitter and receiver could satisfy zero ISI and MF detection.

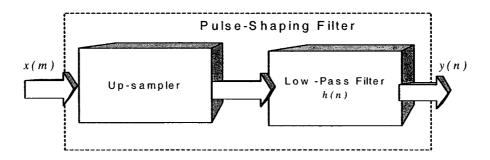

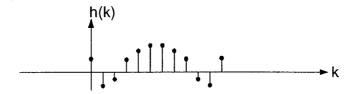

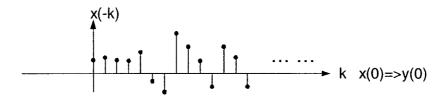

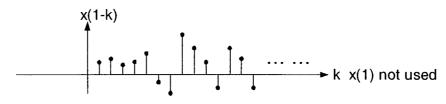

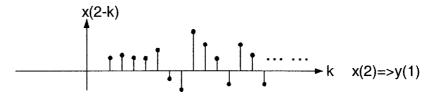

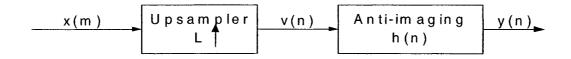

#### 2.2.3 Signal Re-sampling

In digital communication system design, digital filter coefficient h(n) is pre-defined and stored in memory. If the transversal structure is used, the pulse-shaping filter consists of 2 parts: an up-sampler and a low-pass filter (LPF) shown as Figure 2-5. In poly-phase structure (refer to section 3.4), the up-sampler and the low-pass filter are combined. In the following, the underlying relationship between input x(n) and the digital filter impulse response h(n) will be discussed.

Figure 2-5 Pulse-shaping filter

Assume that the input x(n) with symbol rate  $R_s$  goes through a filter. According to Nyquist, the theoretical minimum filter bandwidth is  $R_s/2$  for detecting  $R_s$  symbols/s without ISI. The following equation could be obtained:

$$f_m = \frac{R_s}{2} \tag{2.11}$$

where  $f_m$  is the filter bandwidth.

The above filter can be implemented using digital techniques and sampled waveforms. If such a digital filter has N sampled waveforms per symbol duration, then the filter needs to process N times in one symbol duration  $T(1/R_s)$ . Since x(n) inputs only one symbol in one symbol duration, the processing match between input x(n) and the filter coefficients h(n) must be made. Up-sampling, sometimes called "zero-padding", is such a process which stuffs corresponding zeros in input sequence x(n).

If the sampling frequency of the filter is  $f_s$ , the number of zeros stuffed between 2 input symbols yields:

$$N - 1 = f_{\rm s} / R_{\rm s} - 1 \tag{2.12}$$

For example, if a digital filter has 4 sampled waveforms per symbol duration, the zero-stuffed number is N-1=3. And then the input sequence  $x_0, x_1, x_2, \dots$  is pre-processed by the up-sampler as:  $x_0, 0, 0, 0, x_1, 0, 0, 0, x_2, 0, 0, \dots$  before going through the following LPF.

## 2.3 Digital IF $f_c$ and Symbol Rate $R_s$

So-called quadrature modulation is a method of combining two signals into a single channel by modulating a cosine wave on I channel and a sinusoid wave on Q channel,

thereby doubling the effective bandwidth. For the digital IF modulator, its IF waveform is pre-defined and stored in the memory.

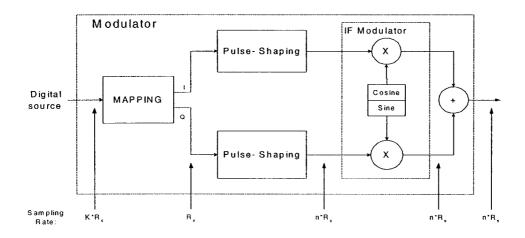

Once the digital QAM modem is designed, the sampling rate at each stage is determined. In Fig 2-6, the sampling rate at each stage of the modulator is shown, where  $k=\log_2(M)$  (M: QAM symbol set size), n is the up-sampling rate of the pulse-shaping filter.

Figure 2-6 Modulator sampling rates at each stage

Carrier wave (sine and cosine) coefficients are pre-defined and stored in memory. If the carrier frequency is  $f_c$ , its coefficients could be obtained by up-sampling with sampling rate  $f_s \ge 2f_c$ . In real systems, such sampling rate usually reaches a factor of 4 or more. Assuming that m carrier samples are taken every carrier period ( $m = f_s/f_c$ ), and Fig 2-6 reveals that  $f_s = n \cdot R_s$ ; therefore, the carrier frequency  $f_c$  could be obtained as follows:

$$\frac{R_s}{f_c} = \frac{m}{n} \tag{2.13}$$

Usually, n=4 and  $m\geq4$  are taken in real systems. Clearly, if  $m\geq n$ ,  $R_s\geq f_c$ , the carrier frequency  $f_c$  will never be higher than the symbol rate  $R_s$ . However, in most of communication systems, the carrier frequency is to be fixed at a much higher frequency than the symbol rate. Therefore, the interpolation and the decimation are then introduced to make it possible.

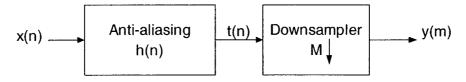

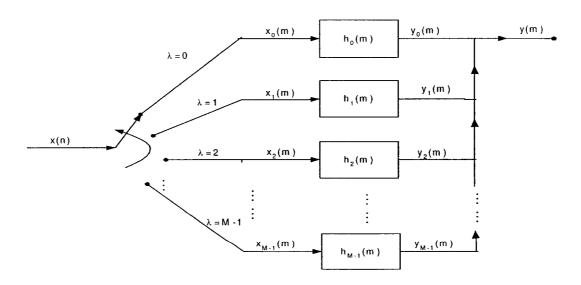

### 2.4 Interpolation and Decimation

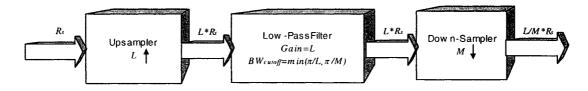

A common use of interpolation and decimation in DSP is for sampling-rate conversion. Suppose a digital signal x(n) is sampled at an interval  $T_1$ , and we wish to obtain a signal y(n) sampled at an interval  $T_2$ . Then the techniques of decimation and interpolation enable this operation, providing the ratio  $T_1/T_2$  is a rational number i.e. L/M. Sampling-rate conversion can be accomplished by L-fold expansion, followed by low-pass filtering and then M-fold decimation. It is important to emphasize that the interpolation should be performed first and decimation second to preserve the desired spectral characteristics of x(n). Furthermore by cascading the two in this manner, both of the filters can be combined into one single low-pass filter shown in Figure 2-7 [5]. Furthermore, if the ratio  $T_1/T_2$  is an integer, only an interpolator or decimator is needed.

Figure 2-7 Filter with rational factor L/M

Actually, the pulse-shaping filter discussed above is an interpolator whose up-sampling rate is an integer. The low pass filter in Fig 2-7 is set with Gain of L and Cutoff Bandwidth of  $min(\pi/L,\pi/M)$ . Cutoff Bandwidth is required to achieve anti-aliasing and

anti-imaging [6, 7]. Gain of L is used to keep interpolation key values unchanged after filtering.

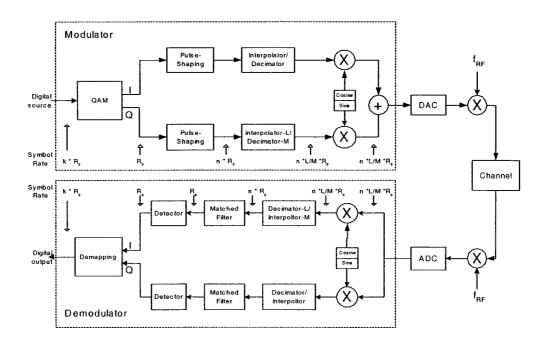

With interpolators and decimators added, a real pure digital modem for general-purpose and its symbol rate at each stage are shown in Fig 2-8. Where L and M are the interpolation and decimation factors. The focus of this thesis will be on the dash-lined sections in Fig 2-8.

Figure 2-8 Modem and its sampling rates

With interpolation and decimation, the relationship between symbol rate  $R_s$  and the carrier frequency  $f_c$  in the transmitter side could be expressed as follows:

$$f_c = \frac{L}{M} \frac{n}{m} R_s \tag{2.14}$$

where L and M are interpolation and decimation factors, respectively; n is pulse-shaping filter up-sampling rate and m is the number of carrier samples per carrier period. Since L

and M could be changed as required, the carrier frequency  $f_c$  can be set fixed and much higher than the symbol rate  $R_s$ .

#### 2.5 Finite-Precision Numerical Effects

In hardware implementation, digital system inputs, coefficients, and results are always stored in finite-length registers. Consequently, either overflows or quantization errors could be introduced in digital binary number representation. In the following sections, some techniques are discussed to help designers choose appropriate methods to meet both system and hardware implementation requirements.

#### 2.5.1 Signal Scaling

If the amplitude of a signal in a fixed-point implementation exceeds the dynamic range, overflows will arise and the output signal could be extremely distorted. Meanwhile, if this amplitude is set very low when being processed through a digital filter, the filter will be inefficiently operating and the signal-to-noise ratio will be very poor. Hence, a suitable signal scaling needs to be used to optimize signal levels.

There are several ways to estimate signal levels. One is to use test signals obtained from a real target. Scaling is based on maximum sample values at each node. This method is seldom used if the system is large and thus calculation is complicated.

Another method, that is widely used, is to calculate the most maximum sample values based on the system transfer function and impulse response. There are 2 norms used for the estimation [13, 14,16]:

• Safe scaling: to choose appropriate  $\lambda$  to make  $v(n) \le M$ .

$$v(n) \leq M \sum_{k=0}^{\infty} |\lambda f(k)| \qquad (2.15)$$

where  $\lambda$  is the scaling constant; v(n) is variable at node k; f(k) is the transfer function from the input to node k; and the input amplitude is bounded by M.

• L<sub>p</sub> norm:

$$|F_{k}(z)|_{p} = \left[\frac{1}{2\pi}\int_{-\pi}^{\pi} |F_{k}(e^{-jw})|^{p} dw\right]^{\frac{1}{p}}$$

(2.16)

where p is positive integer, and  $F_k(z)$  is the transfer function from the input to node k.

### 2.5.2 Truncation and Rounding

Once the register length is assigned, the set of machine representable numbers is determined. Assume that the assigned word length is l bits. Then, any number of m bits long (m>l) should be quantized before being processed. There are 2 approaches normally used for quantization: truncation and rounding. Truncation is to truncate all the least significant bits of n-bit long number that can't be accommodated in l-bit long registers. Rounding is to round to the nearest machine-representable number by adding 1 at the position l+1 and then truncating the m-bit long number to l bits.

Obviously, if a number x is quantized, an error  $\varepsilon$  is then introduced given by [11]:

$$\varepsilon = x - Q[x] \tag{2.17}$$

where Q[x] denotes the quantized value of x. For 2's complement number, quantization error  $\varepsilon_T$  of truncation could be expressed as:

$$0 < \varepsilon_{\scriptscriptstyle T} < q \tag{2.18}$$

where q is quantile interval.

And quantization error  $\varepsilon_R$  of rounding could be expressed as:

$$-\frac{q}{2} < \varepsilon_R < \frac{q}{2} \tag{2.19}$$

In hardware implementation, quantization has to be done, but quantization error acts as noise that degrades the system performance. Hence, word length of system registers should be chosen very carefully.

# **Chapter 3 The Modem Simulations**

A typical QAM modem simulation model is constructed using MATLAB software based on Fig 2-8 block diagram [8, 9]. The system performance is evaluated based on modem Bit Error Rate (BER). This chapter mainly discusses evaluation of different parameters in the design of digital filters since they play the most important role in the system. The modem employs four filters which are pulse shaping, matched filter, interpolator and decimator. Advantages of FIR filters in communication systems are first briefed. Section 3.2 and 3.3 analyze the effects of filter orders (the pulse-shaping & matched filter, interpolation & decimation filter) on error performance. Finite word length is discussed in section 3.4. The main design parameters are finally given based on appropriate compromises between hardware complexity and error performance.

### 3.1 Why FIR Filters

There are 2 types of digital filters: Infinite Impulse Response (IIR) filters and Finite Impulse Response (FIR) filters. Currently, FIR filters are widely used in most of real-time communication systems. Compared to IIR filters, FIR filters are:

- easily designed to be "linear phase" to avoid signal distortion

- simple to implement using fractional arithmetic.

- computationally more efficient when doing multi-rate applications (interpolation &decimation).

Accordingly, FIR filters have been chosen for our system. Performance of an FIR filter is mainly determined by its filter order and the coefficient word length. The order of an FIR filter and the coefficient word length should be as large as possible if a designer wants to build up a filter as precise as possible. On the other hand, a larger FIR filter order or its coefficient word length requires more resources in hardware implementation, such as chip area, power consumption, etc. Thus, it is important to make the filter order or coefficients word length as low as possible. Hence, necessary trade-offs have to be made on both sides.

# 3.2 Pulse-Shaping Filter & Matched Filter Order

The impulse response of the square-root raised cosine filter is:

As mentioned in Chapter 2, in our design, a square-root raised cosine filter is used as the pulse-shaping filter on the transmitter side and the matched filter on the receiver side.

$$h(t) = 4r \cdot \frac{\cos((1+r)\pi t/T) + \frac{\sin((1-r)\pi t/T)}{4rt/T}}{\pi\sqrt{T}((4rt/T)^2 - 1)}$$

(3.1)

where r ( $1 \ge r \ge 0$ ) is roll-off factor, T is symbol period. In our design, the roll-off factor r is set 0.5 for the square-root raised cosine filters.

The impulse response of an ideal, causal LPF filter extends from 0 to  $\infty$ . An FIR filter is an approximation of an ideal filter. Its length is determined by examining its error performance. The order of an FIR filter is affected by the filter symbol span and the upsampling rate. The order can be expressed as:

$$N - 1 = 4 \cdot s \tag{3.2}$$

where N is the number of filter coefficients, N-1 is the filter order, s is the symbol span. For the square-root raised cosine filter, the up-sampling rate is set to 4.

By bypassing the interpolator/decimator, all the square-root raised cosine filter parameters could be examined and optimally chosen based on BER. For *M*-ary QAM modulation, there is an approximate equation expressed as follows [11]:

$$P_{B} \approx \frac{2(1 - L^{-1})}{\log_{2} L} Q\left(\sqrt{\left(\frac{3\log_{2} L}{L^{2} - 1}\right) \frac{2E_{b}}{N_{0}}}\right)$$

(3.3)

where  $Q(\cdot)$  is Q function [11], and L represents the number of amplitude levels in one dimension ( $L=M^{1/2}$ ). Fig 3-1 and 3-2 show QPSK and 16-QAM error performances with pulse-shaping and matched filter symbol span s=6, 8, 10, in presence of *Additive*, *Gaussian White Noise* (AGWN) channel.

Figure 3-1 QPSK error bit rates with different symbol spans

Figure 3-2 16-QAM error bit rates with different symbol spans

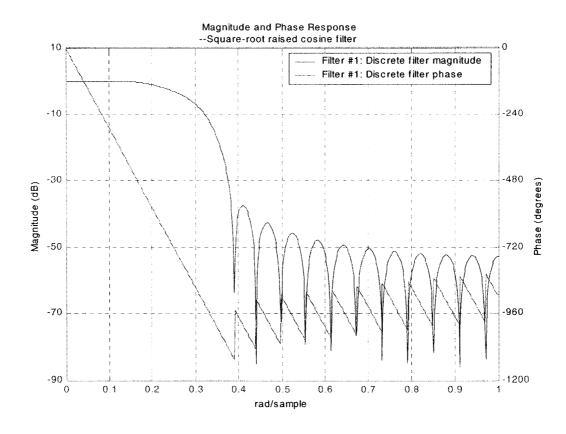

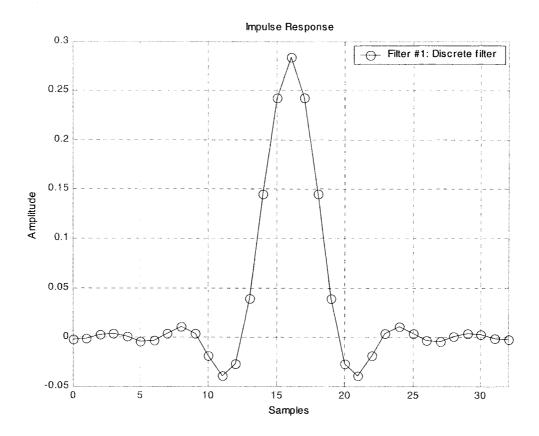

Fig 3-1 and 3-2 reveal that a symbol span larger than 8 doesn't help much on the improvement of QPSK/16-QAM error performance but increases hardware. So the symbol span of the square-root raised cosine filter is set to 8. Thus the filter order is 4s=32. Figure 3-3 and 3-4 are frequency and impulse response of the pulse-shaping/matched filters, respectively. The filter parameters are as follows.

- Number of filter coefficients: *N*=33 (filter order: 32)

- Up-sampling rate: 4;

- Roll-off factor: r=0.5

Figure 3-3 Frequency response of Square-Root Raised Cosine filter

Figure 3-4 Impulse response of Square-Root Raised Cosine filter

# 3.3 Interpolation Filter & Decimation Filter Order

In chapter 2, we have discussed interpolation with rational factor. To simplify hardware implementation, an integer interpolation is employed in our design.

The interpolator with factor L on the transmitter side makes the filter up-sampling rate changeable in order to make the sampling match between the pulse-shaping filter and the complex mixer. On the receiver side, a decimator with the same frequency spectrum needs to be inserted between IF recovery block and the matched filter. Table 3-1 shows the system BERs with different interpolation factors L and different symbol spans s at  $E_B/N_0$ =14 dB for 16-QAM modulation.

Table 3-1 16-QAM error bit rates through interpolation/decimation

$(E_B/N_o=14dB)$

|          |    | S=4                  |    | S=6                   |     | S=8                   |

|----------|----|----------------------|----|-----------------------|-----|-----------------------|

| L        | N  | P <sub>B</sub>       | N  | P <sub>8</sub>        | N   | P <sub>B</sub>        |

| bypassed |    | 5.8*10 <sup>-6</sup> |    | 5.8*10 <sup>-6</sup>  |     | 5.8*10 <sup>-6</sup>  |

| 2        | 9  | 1.1*10 <sup>-5</sup> | 13 | 6.12*10 <sup>-6</sup> | 17  | 6.05*10 <sup>-6</sup> |

| 4        | 17 | 1.0*10 <sup>-5</sup> | 25 | 5.9*10 <sup>-6</sup>  | 33  | 5.8*10 <sup>-6</sup>  |

| 8        | 33 | 1.0*10 <sup>-5</sup> | 49 | 5.8*10 <sup>-6</sup>  | 65  | 5.8*10 <sup>-6</sup>  |

| 16       | 65 | 1.0*10 <sup>-5</sup> | 97 | 5.8*10 <sup>-6</sup>  | 129 | 5.8*10 <sup>-6</sup>  |

where the number of coefficients N = s\*L+1;  $P_B$  is Bit Error Rate.

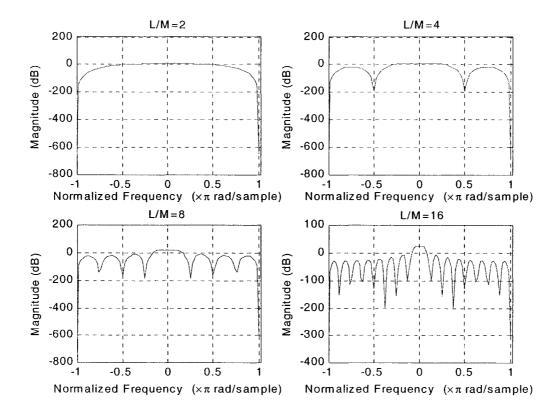

As seen in Table 3-1, the symbol span of 6 is the best tradeoff from error performance and hardware implementation point of view. This result is also verified at other values of  $E_B/N_0$ . Once the symbol span for the interpolator/decimator is determined, the frequency spectrums with different interpolation/decimation factor L/M could be plotted in Fig 3-5.

Figure 3-5 Frequency response of interpolator with different factors

### 3.4 Finite Word Length

The previous discussion regarding filters is based on infinite precision. However, all hardware implementation numbers such as filter coefficients, products, and sums are stored in finite-length registers. Hence, necessary quantization and signal scaling are required. In section 2.1.2, we have discussed that an arbitrary number can be represented with a scale factor  $X_m$  ( $X_m > 1$ ) and a binary fractional part. In fixed-point computations, the scale factor is assumed  $X_m = 2^k$ . A value k implies that the binary point is located between  $b_{L-l-k}$  and  $b_{L-l-(k+l)}$  for an L-bit number  $b_{L-l}b_{L-2}$  ... $b_0$  where  $b_{L-l}$  is the sign bit. Signal scaling helps to determine parameter k; quantizing technique helps to determine appropriate word length L.

To simplify hardware design and reduce design time, the system is simulated under the following assumptions:

1. Number representation: 2's complement

2. Quantization mode: rounding

3. Signal scaling mode: safe scaling

### 3.4.1 Signal Scaling

When processing digital filter, either signal amplitude or filter coefficient values can be scaled to avoid overflows. Since QPSK and 16QAM are employed in our design, the dynamic range of signal amplitude on I/Q channel is set from -3 to 3, which is obtained from the worst case (16QAM-constellation mapping).

On the transmitter side, the input of the pulse-shaping filter upper bounded by 3 is represented by 3 bits in 2's complement. To find the optimal filter coefficients without overflows, according to Eq (2.15), we need to make:

$$\sum_{k=0}^{n-1} |f(k)| \le 1 \tag{3.1}$$

However, for the pulse-shaping filter and the interpolation filter, there is an efficient way to choose coefficients big enough without overflows. As we know, an interpolation filter input is stuffed with L-1 zeros before filter processing. This means that only 1/L filter coefficients (one out of L sub-filters) are in computation each time. Hence, Eq (3.1) could be modified as:

$$\sum_{k=0}^{\frac{n-1}{L}} |f(Lk + m)| \le 1$$

(3.2)

where L is the interpolation factor, and m is a positive integer less than L. For instance, the pulse-shaping filter with 33 coefficients stuffs 3 zeros in its input before processing. To optimize its coefficients with no overflows at the filter output, we only need to guarantee the following condition:

$$Max\left(\sum_{k=0}^{8} \left| f(4k) \right|, \sum_{k=0}^{7} \left| f(4k+1) \right|, \sum_{k=0}^{7} \left| f(4k+2) \right|, \sum_{k=0}^{7} \left| f(4k+3) \right| \right) \le 1$$

(3.3)

Based on Eq (3.3), the pulse-shaping coefficients can be chosen. The maximum sub-filter sum for pulse-shaping filter coefficients is upper-bounded by 0.73. For the interpolation filter, the same rule can be applied. Meanwhile, we need the interpolation filter with gain equal to L in order to remain key values unchanged.

The boundary of each block in the transmitter side can be shown as follows:

• Magnitude of QAM mapping output:  $M_Q \le 3$

- Magnitude of pulse-shaping filter output:  $M_P \le M_Q$  \*0.73 = 2.19 (0.73: the maximum sub-filter sum for the pulse-shaping filter)

- Magnitude of interpolation filter:  $M_I \le M_P * 1.39 = 3.04$  (1.39: the maximum sub-filter sum for the interpolator)

- Magnitude of IF modulator:  $M_C \le M_I *1$  (1: the maximum sine or cosine values)

- Magnitude of adder:  $M_A \le M_C$  \*1.414 = 4.3 (1.414: the maximum (sinx+cosx) value) In the receiver side, the received signal needs to be converted to digital signal via ADC. Since the input signal amplitude is known, the decimation filter coefficients are chosen based on Eq (2.15). For the matched filter, the same coefficients as the pulse-shaping filter are selected. The boundary of each block can also be shown as follows:

- Magnitude of IF recovery block:  $M_R \le 4.3$  (after ADC)

- Magnitude of decimation filter:  $M_D \le M_R * 0.5 * 1.25 = 2.69$  (1.25:  $1/L * \Sigma |f(k)|$ ; 0.5: caused by LPF)

- Magnitude of matched filter:  $M_M \le M_D^* 2.76 = 7.42 (2.76: \Sigma |f(k)|)$

### 3.4.2 System Quantization

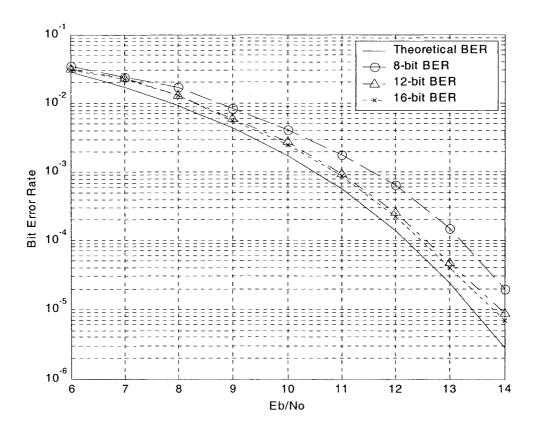

An L-bit number's precision depends on its fractional part. If the scale factor of the number is determined, the only way to make the number more precise is to extend L until the requirements are met. Generally, coefficients, products and sums can have different word lengths based on design requirements. In our design, the word length L is set identical. It is examined using MATLAB simulation model and determined based on the system performance. In Fig 3-6, 3 BER comparisons with the word length L equal to 8,

12 and 16 bits are plotted. Note that all simulations are made for 16-QAM modulation scheme since it is more vulnerable than QPSK.

Figure 3-6 16-QAM BERs with different word lengths

By changing the interpolation factor, almost the same results are obtained. Therefore, the word length L of 12 bits is chosen for future hardware design. Hence, the word length of each block for the transmitter and receiver is given as Table 3-2 and 3-3:

Table 3-2 Word lengths for each block of the transmitter

|             | Mapper | Pulse-shaping filter | Interpolator | IF modulator | Adder  |

|-------------|--------|----------------------|--------------|--------------|--------|

| Coefficient | [3 0]  | [12 11]              | [12 11]      | [12 11]      |        |

| Input       | bit-in | [3 0]                | [12 9]       | [12 9]       | [12 9] |

| Output      | [3 0]  | [12 9]               | [12 9]       | [12 9]       | [12 8] |

In term [a b], a stands for the total word length, b stands for the fraction length.

Table 3-3 Word lengths for each block of the receiver

|             | IF recovery | Decimator | Matched filter | Detector | Demapper |

|-------------|-------------|-----------|----------------|----------|----------|

| Coefficient | [12 11]     | [12 11]   | [12 11]        |          |          |

| Input       | [12 8]      | [12 8]    | [12 9]         | [12 7]   | [3 0]    |

| Output      | [12 8]      | [12 9]    | [12 7]         | [3 0]    | bit-out  |

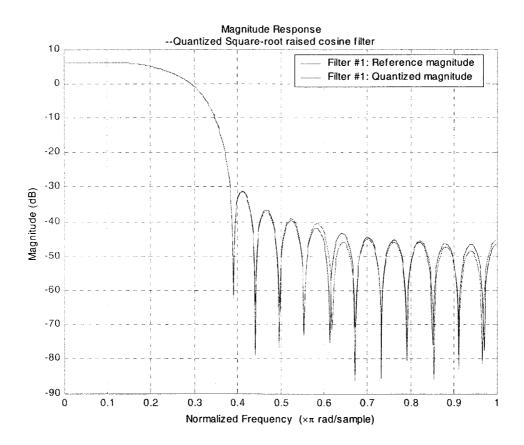

In order to make a comparison, the quantized and non-quantized frequency spectrums of the square-root raised cosine filter are plotted in Fig 3-7.

Figure 3-7 Frequency response of the quantized square-root raised cosine filter

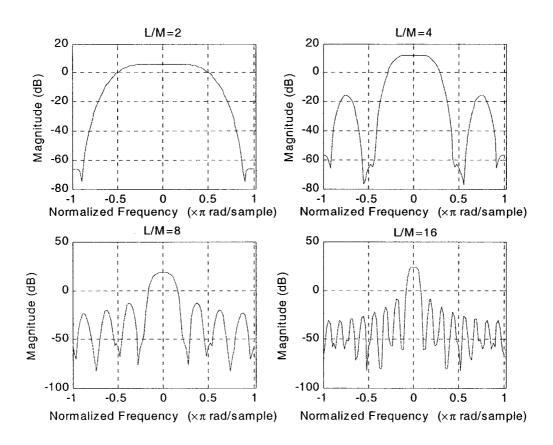

As well, the quantized frequency spectrums of the interpolation filters with different interpolation factor are plotted in Fig 3-8.

Figure 3-8 Quantized frequency response of interpolator/decimator

# 3.5 Coefficients and 2's Complement Representations

In our design, the blocks that are Constellation mapper, Pulse-shaping filter/Matched filter, Interpolator/Decimator and IF modualtor need coefficients pre-defined and prestored. The quantized coefficient values and their 2's complement representation (based on Eq (2.4)) can be listed as follows.

- In Table 3-4, the mapping output of QPSK scheme I/Q is extended 1 bit to make the same word length as that of 16QAM. This is to simplify hardware implementation.

- Table 3-5 shows Pulse-shaping/ Matched filter coefficients.

- Table 3-6 and 3-7 show the interpolator (gain=L) and decimator (gain=1) coefficients, where L=2, 4, 8, 16, respectively.

- Table 3-8 shows Cosine waveform coefficients. Since Cosine and Sinusoid have 90° offset, only Cosine waveform coefficients are tabulated.

Table 3-4 QPSK/16-QAM constellation mapping

|       |         | QPSK (I/Q: 2-  | -1-BIT) |                |       |         | 16-QAM (I/Q:   | 3- <b>BIT</b> ) |                |

|-------|---------|----------------|---------|----------------|-------|---------|----------------|-----------------|----------------|

| INPUT |         | ı              |         | Q              | INPUT |         | l              |                 | Q              |

|       | Decimal | 2's complement | Decimal | 2's complement |       | Decimal | 2's complement | Decimal         | 2's complement |

| 00    | 1       | 001            | 1       | 001            | 0000  | 1       | 001            | 1               | 001            |

| 01    | -1      | 111            | 1       | 001            | 0001  | -1      | 111            | 1               | 001            |

| 10    | 1       | 001            | -1      | 111            | 0010  | 1       | 001            | -1              | 111            |

| 11    | -1      | 111            | -1      | 111            | 0011  | -1      | 111            | -1              | 111            |

|       |         |                |         |                | 0100  | 3       | 011            | 1               | 001            |

|       |         |                |         |                | 0101  | -3      | 101            | 1               | 001            |

|       |         |                |         |                | 0110  | 3       | 011            | -1              | 111            |

|       |         |                |         |                | 0111  | -3      | 101            | -1              | 111            |

|       |         |                |         |                | 1000  | 1       | 001            | 3               | 011            |

|       |         |                |         |                | 1001  | -1      | 111            | 3               | 011            |

|       |         |                |         |                | 1010  | 1       | 001            | -3              | 101            |

|       |         |                |         |                | 1011  | -1      | 111            | -3              | 101            |

|       |         |                |         |                | 1100  | 3       | 011            | 3               | 011            |

|       |         |                |         |                | 1101  | -3      | 101            | 3               | 011            |

| 1     |         |                |         |                | 1110  | 3       | 011            | -3              | 101            |

|       |         |                |         |                | 1111  | -3      | 101            | -3              | 101            |

Table 3-5 Pulse-shaping/ Matched filter coefficients

| No.         | Coefficients in decimal | Coeficients in 2's complement (12-bit) |

|-------------|-------------------------|----------------------------------------|

| h(0)/h(32)  | -0.0049                 | 111111110110                           |

| h(1)h(31)   | -0.002                  | 11111111100                            |

| h(2)h(30)   | 0.0054                  | 00000001011                            |

| h(3)/h(29)  | 0.0083                  | 00000010001                            |

| h(4)/h(28)  | 0.0015                  | 0000000011                             |

| h(5)/h(27)  | -0.0083                 | 111111101111                           |

| h(6)/h(26)  | -0.0073                 | 111111110001                           |

| h(7)/h(25)  | 0.0078                  | 00000010000                            |

| h(8)/h(24)  | 0.021                   | 000000101011                           |

| h(9)/h(23)  | 0.0078                  | 00000010000                            |

| h(10)/h(22) | -0.0376                 | 111110110011                           |

| h(11)/h(21) | -0.0786                 | 111101011111                           |

| h(12)/h(20) | -0.0532                 | 111110010011                           |

| h(13)/h(19) | 0.0786                  | 000010100001                           |

| h(14)/h(18) | 0.2896                  | 001001010001                           |

| h(15)/h(17) | 0.4873                  | 001111100110                           |

| h(16)       | 0.5684                  | 010010001100                           |

# Table 3-6 Interpolator coefficients

|                                |              |              | ,             |              |              |              |              | _            | _            | ī             | _            | _            | _            | ,            |              |              |              |             | _           | _                                       | -,           | -            | -            |               |              |              |              | _             |               |              | _            | -            |              |              |              |              |              | . ,          |              |              |              |              | _            |              |              |               | -            |

|--------------------------------|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|-------------|-------------|-----------------------------------------|--------------|--------------|--------------|---------------|--------------|--------------|--------------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|--------------|

| Coefficients in 2's complement | 01111111111  | 011111001100 | 011110000100  | 011100101100 | 011011000101 | 011001001111 | 010111001110 | 010101000011 | 010010110000 | 010000011000  | 00111111100  | 00101101110  | 001000100010 | 000110101000 | 000100010011 | 000000000000 | 111111000101 | 11111000101 | 10101011111 | 111101101111                            | 111010101011 | 000000101111 | 101011001111 | 111100110011  | 111100111000 | 111101000011 | 101010101111 | 111101101010  | 1111101000100 | 111111000000 | 111111100000 | 000000000000 | 000000000110 | 000000001011 | 0000100000   | 000000010011 | 000000010110 | 000000010111 | 00001100000  | 000011000    | 000000010111 | 000000010101 | 000000010011 | 000000010000 | 000000001100 | 0000000001000 | 000000000100 |

| Coefficients in decimal        | 0.9995       | 0.9746       | 0.9395        | 0.8965       | 0.8462       | 0.7886       | 0.7256       | 0.6577       | 0.5859       | 0.5117        | 0.4355       | 0.3584       | 0.2822       | 0.207        | 0.1343       | 0.0649       | 0000         | -0.0200     | 20.034      | -0.0708                                 | -0.0845      | -0.0938      | 1660.0-      | -0.1001       | -0.0977      | -0.0923      | -0.0835      | -0.0732       | -0.0005       | -0.0313      | -0.0156      | 0            | 0.0029       | 0.0054       | 0.0078       | 0.0093       | 0.0107       | 0.0112       | 0.0117       | 0.0117       | 0.0112       | 0.0103       | 0.0093       | 0.0078       | 0.0059       | 0.0039        | 0.002        |

| L=16<br>N=96<br>No.            | 48           | 49           | 50            | 51           | 25           | 53           | 54           | 22           | 99           | 57            | 58           | 69           | 09           | 61           | 85           | 3            | 40           | 8 8         | 8 5         | à                                       | 3 8          | 200          | ?   i        | 7             | 72           | 23           | 4 ;          | ς)<br>1       | 9/2           | 78           | 79           | 80           | 81           | 82           | 83           | 8            | 85           | 8            | 87           | 88           | 88           | 8            | 91           | 95           | 93           | 98            | 92           |

| Coefficients in 2's complement | 00000000000  | 000000000100 | 000000001000  | 000000001100 | 000000010000 | 000000010011 | 000000010101 | 000000010111 | 000000011000 | 000000011000  | 000000010111 | 000000010110 | 000000010011 | 0000100000   | 000000001011 | 011000000000 | 0000000000   | 11111100000 | 0000000     | 111110100001                            | 111110001100 | 01010101111  | 101010101111 | 111101000011  | 111100111000 | 111100110011 | 101011001111 | 11110100000   | 111101101111  | 111110010101 | 111111000101 | 000000000000 | 000010000101 | 000100010011 | 000110101000 | 00100100010  | 001011011110 | 001101111100 | 010000011000 | 010010110000 | 010101000011 | 010111001110 | 011001001111 | 011011000101 | 011100101100 | 011110000100  | 011111001100 |

| Coefficients in decimal        | 0            | 0.002        | 0.0039        | 0.0059       | 0.0078       | 0.0093       | 0.0103       | 0.0112       | 0.0117       | 0.0117        | 0.0112       | 0.0107       | 0.0093       | 0.0078       | 0.0054       | 0.0029       | 0 00         | -0.0130     | -0.0013     | -0.0464                                 | chan.o-      | 0.0732       | -0.0835      | -0.0923       | -0.0977      | -0.1001      | -0.0991      | -0.0938       | -0.0845       | -0.0522      | -0.0288      | 0            | 0.0649       | 0.1343       | 0.207        | 0.2822       | 0.3584       | 0.4355       | 0.5117       | 0.5859       | 0.6577       | 0.7256       | 0.7886       | 0.8462       | 0.8965       | 0.9395        | 0.9746       |

| L=16N<br>=96<br>No.            | 0            | -            | 2             | 3            | 4            | 2            | 9            | 2            | 8            | 6             | 10           | F            | 12           | 13           | 7            | <u> </u>     | 2 [          | -   9       | ٩           | 2 2                                     | ₹ 2          | 2/2          | 3            | 33            | 24           | 52           | 8 2          | 7 8           | ş ç           | 3 8          | 3            | 32           | 33           | 34           | 35           | 8            | 37           | 8            | စ္တ          | 9            | 4            | 4            | 43           | 4            | 42           | 46            | 47           |

| ٥                              | 000000000000 | 000100000000 | 0000100000    | 000000010101 | 000000011000 | 000000010111 | 000000010011 | 000000001011 | 000000000000 | 111111000000  | 111110000100 | 111101010101 | 111100111000 | 111100110101 | 111101010111 | 101010011111 | 00010001000  | 0010010011  | 00100100010 | 00111111100                             | 0,0011010010 | 0110011101   | 011011000101 | 011110000100  | 011111111111 | 011110000100 | 101000110110 | 0100111001110 | 00110111100   | 00100100010  | 000100010011 | 000000000000 | 111110010101 | 111101010111 | 111100110101 | 111100111000 | 111101010101 | 111110000100 | 111111000000 | 000000000000 | 000000001011 | 000000010011 | 000000010111 | 000000011000 | 000000010101 | 000000010000  | 000000001000 |

| Coefficients in decimal        | 0            | 0.0039       | 0.0078        | 0.0103       | 0.0117       | 0.0112       | 0.0093       | 0.0054       | 0            | -0.0313       | -0.0605      | -0.0835      | -0.0977      | -0.0991      | -0.0845      | -0.0522      | 0 1343       | 0.1343      | 0.2022      | 0.4355                                  | 0.0809       | 0.7256       | 0.8462       | 0.9395        | 0.9995       | 0.9395       | 0.8462       | 0.7250        | 0.355         | 0.2822       | 0.1343       | 0            | -0.0522      | -0.0845      | -0.0991      | -0.0977      | -0.0835      | -0.0605      | -0.0313      | 0            | 0.0054       | 0.0093       | 0.0112       | 0.0117       | 0.0103       | 0.0078        | 0.0039       |

| L=8<br>N=48<br>No.             | 0            | -            | 2             | 3            | 4            | 5            | 9            | 2            |              | 6             | 10           | F            | 12           | 13           | 4            | ٤ ز          | 1 2          | ٩           | ٩           | 2                                       | 3 2          | 2 6          | 7            | 23            | 24           | 52           | 878          | /7 8          | 000           | 8            | 3            | 32           | 33           | 뚕            | 35           | ဗ္က          | 37           | 8            | 88           | \$           | 4            | 45           | 43           | 4            | 45           | 46            | 47           |

| -                              | 000000000000 | 0000100000   | 0000000011000 | 000000010011 | 000000000000 | 111110000100 | 111100111000 | 111101010111 | 000000000000 | 001001000010  | 010010110000 | 011011000101 | 01111111111  | 011011000101 | 010010110000 | 010000100100 | 111101010000 | 11101010011 | 00111001111 | 000000000000000000000000000000000000000 | 00000000000  | 11001000000  | 000000011000 | 0000000010000 |              |              |              |               |               |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |               |              |

| Coefficients in decimal        | 0            | 0.0078       | 0.0117        | 0.0093       | 0            | -0.0605      | -0.0977      | -0.0845      | 0            | 0.2822        | 0.5859       | 0.8462       | 0.9995       | 0.8462       | 0.5859       | 0.2822       | 0 00 0       | -0.0843     | -0.0977     | -0.0605                                 | 0000         | 0.0093       | 0.011/       | 0.0078        |              |              |              |               |               |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |               |              |

| L=4<br>N=24<br>No.             | 0            | -            | 2             | 3            | 4            | 2            | 9            | 7            | 8            | 6             | 10           | =            | 12           | 13           | 14           | 12           | 9 ;          | - ;         | 0 9         | S S                                     | 2            | 17           | 77           | 23            |              |              |              |               |               |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |               |              |

| Coefficients in 2's complement | 000000000000 | 000000011000 | 000000000000  | 111100111000 | 000000000000 | 010010110000 | 0111111111   | 010010110000 | 000000000000 | 1111001111000 | 000000000000 | 000000011000 |              |              |              |              |              |             |             |                                         |              |              |              |               |              |              |              |               |               |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |               |              |

| Coefficients in decimal        | 0            | 0.0117       | 0             | -0.0977      | 0            | 0.5859       | 0.9995       | 0.5859       | 0            | -0.0977       | 0            | 0.0117       |              |              |              |              |              |             |             |                                         |              |              |              |               |              |              |              |               |               |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |               |              |

| L=2<br>N=12<br>No.             | 0            | -            | 2             | 3            | 4            | 2            | ဖ            | 7            | ∞            | 6             | 2            | Ξ            |              |              |              |              |              |             |             |                                         |              |              |              |               |              |              |              |               |               |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |               |              |

# Table 3-7 Decimator coefficients

| Coefficients in 2's<br>complement | 00001000000  | 000001111101 | 000001111000 | 000001110011 | 000001101100 | 00000101101                             | 000001010100 | 000000000000000000000000000000000000000 | 110100100000 | 000001000001 | 000000111000 | 000000101110 | 000000100100   | 000000011010  | 0000000010001 | 0000000001000 | 000000000000 | 11111111100  | 11111111001   | 111111111111 | 111111110101 | 111111110100 | 111111110011 | 111111110011 | 111111110100 | 111111110100 | 111111110101 | 111111111111 | 11111111000  | 111111111010 | 11111111100  | 11111111110  | 000000000000 | 000000000000 | 00000000001  | 00000000001  | 00000000001   | 00000000001  | 100000000000 | 00000000000  | 00000000010  | 1000000000001 | 00000000001  | 00000000000  | 00000000001  | 00000000000  | 00000000001  | 000000000000 |

|-----------------------------------|--------------|--------------|--------------|--------------|--------------|-----------------------------------------|--------------|-----------------------------------------|--------------|--------------|--------------|--------------|----------------|---------------|---------------|---------------|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|--------------|--------------|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Coefficients in decimal           | 0.0625       | 0.061        | 0.0586       | 0.0562       | 0.0527       | 0.0454                                  | 0.041        | 10.0                                    | 0.0366       | 0.0317       | 0.0273       | 0.0225       | 0.0176         | 0.0127        | 0.0083        | 0.0039        | 0            | -0.002       | -0.0034       | -0.0044      | -0.0054      | -0.0059      | -0.0063      | -0.0063      | -0.0059      | -0.0059      | -0.0054      | -0.0044      | -0.0039      | -0.0029      | -0.002       | -0.001       | 0            | 0            | 0.0005       | 0.0005       | 0.0005        | 0.0005       | 0.0005       | 0.001        | 0.001        | 0.0005        | 0.0005       | 0.0005       | 0.0005       | 0.0005       | 0.0005       | 0            |

| L=16<br>N=96<br>No.               | 48           | 49           | 20           | 20           | 7 5          | 3 2                                     | t 12         | 3 8                                     | 95           | 27           | 28           | 59           | 90             | 61            | 62            | ន             | 8            | 65           | 99            | 67           | 89           | 69           | 70           | 71           | 72           | 73           | 74           | 75           | 76           | 77           | 78           | 79           | 80           | 81           | 82           | 83           | 84            | 85           | 98           | 87           | 88           | 88            | 90           | 91           | 92           | 93           | 8            | 95           |