# Quantitative Evaluation of the Impact of Floating Point Arithmetic Units on the Performance of DSP Structures

### **Wassim Tout**

A Thesis

in

The Department

of

Electrical And Computer Engineering

Presented in Partial Fulfilment of The Requirements for The Degree of Master of Applied Science at Concordia University Montreal, Quebec, Canada

August 2003

© Wassim Tout, 2003

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisisitons et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-612-91126-8 Our file Notre référence ISBN: 0-612-91126-8

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

exclusive permettant à la

Bibliothèque nationale du Canada de

reproduire, prêter, distribuer ou

vendre des copies de cette thèse sous

la forme de microfiche/film, de

reproduction sur papier ou sur format

électronique.

L'auteur a accordé une licence non

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou aturement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this dissertation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de ce manuscrit.

While these forms may be included in the document page count, their removal does not represent any loss of content from the dissertation.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

# Canadä

### **Abstract**

Quantitative Evaluation of the Impact of Floating Point Arithmetic Units on the Performance of DSP Structures

#### **Wassim Tout**

Arithmetic operations traditionally used fixed-point processing because it makes them less expensive. In integer and fixed-point arithmetic, multipliers are larger, slower and consume much more power than adders, which are often neglected in performance evaluation of DSP systems. In floating-point arithmetic that is not true and in this thesis we show that multipliers and adders are equally important. The thesis also emphasizes low power design. For that reason, some of the basic digital filter network structures, built with FP arithmetic units, are revisited to map their performance with different filtering functions. This thesis presents digital filter network structures' performance with different filtering functions. It presents filter network structures transformed from their original form to accommodate pipe-lined arithmetic units. These filter structures can also be implemented with fixed-point arithmetic units because of the speed advantage they provide. Several experiments, through hardware synthesis of the structures, show that FIR filter Direct form structure using an adder tree consumes less power than Direct form structure using a chain of adders and its Transposed form. They also show that for IIR filters, Direct form II using standard floatingpoint arithmetic units is power optimal. This research work is intended to provide designers with information on the performance of these structures with different applications in an effort to help reduce the "design gap".

## Acknowledgment

I am grateful to Dr. Asim J. Al-Khalili for his supervision and his support, without which this work would not have been accomplished. I wish to thank Rajan V.K. Pillai for providing the audio data samples, Syed Y.A. Shah for providing the VHDL code of the FP arithmetic units and Ted Obuchowicz for his technical assistance with the different CAD tools used to perform the experiments. I am also grateful to my family whose help and support made it all possible.

# **Table of Content**

| List of Figuresix                            |

|----------------------------------------------|

| List of Tables xiii                          |

| Chapter 1: Introduction                      |

| 1.1 Introduction                             |

| 1.2 Low Power Design                         |

| 1.3 Motivation                               |

| 1.4 Design and Experimentation Methodology   |

| 1.5 Design Implementation                    |

| 1.6 Contributions 8                          |

| 1.7 Thesis Organisation 8                    |

| 1.8 Summary9                                 |

| Chapter 2: Digital Filters                   |

| 2.1 Introduction                             |

| 2.2 Filter Basics                            |

| 2.3 FIR Systems                              |

| 2.4 Basic Network Structures for FIR Systems |

| 2.4.1 Direct Form                            |

| 2.4.2 Transposed Form                        |

| 2.5 IIR Systems                              |

| 2.6 Basic Network Structures for IIR Systems |

| 2.6.1 Direct Forms                           |

| 2.6.2 Transposed Direct Forms                |  |

|----------------------------------------------|--|

| 2.6.3 Cascade Forms                          |  |

| 2.7 Summary                                  |  |

| Chapter 3: Arithmetic Units                  |  |

| 3.1 Introduction                             |  |

| 3.2 Experimental Approach                    |  |

| 3.2.1 Input Data Samples                     |  |

| 3.2.2 SDP Configurations                     |  |

| 3.2.3 MDP Configurations                     |  |

| 3.3 Results                                  |  |

| 3.3.1 Single Data Path FP Arithmetic Units   |  |

| 3.3.2 Multiple Data Path FP Arithmetic Units |  |

| 3.4 Floating-Point vs. Fixed-Point           |  |

| 3.5 Conclusion                               |  |

| 3.6 Summary                                  |  |

| Chapter 4: Finite Impulse Response Filters   |  |

| 4.1 Introduction                             |  |

| 4.2 Standard FIR Filter Network Structures   |  |

| 4.2.1 Experimental Approach - Experiment 2   |  |

| 4.2.2 Results (non pipe-lined)               |  |

| 4.3 Pipe-lined FIR Network Structures        |  |

| 4.3.1 Problem Definition                     |  |

| 4.3.2 Problem Solving (Re-timing)            |  |

| 4.3.2.1 First Approach                                          | 50 |

|-----------------------------------------------------------------|----|

| 4.3.2.2 Second Approach                                         | 52 |

| 4.3.3 Experimental Approach                                     | 56 |

| 4.3.4 Results (pipe-lined)                                      | 57 |

| 4.3.4.1 Single Data Path Arithmetic Units                       | 57 |

| 4.3.4.2 Pipe-lined vs. Combinational                            | 64 |

| 4.3.4.3 Multiple Data Path Arithmetic Units                     | 66 |

| 4.3.4.4 Multiple Data Path vs. Single Data Path                 | 71 |

| 4.4 Floating-Point vs. Fixed-Point                              | 73 |

| 4.5 Conclusion                                                  | 75 |

| 4.6 Summary                                                     | 76 |

| Chapter 5: Infinite Impulse Response Filters                    | 77 |

| 5.1 Introduction                                                | 77 |

| 5.2 Hardware Implementation of IIR Systems                      | 78 |

| 5.3 Experimental Approach                                       | 80 |

| 5.4 Results                                                     | 81 |

| 5.4.1 Single Data Path Arithmetic Units                         | 81 |

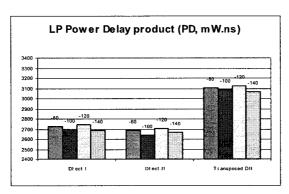

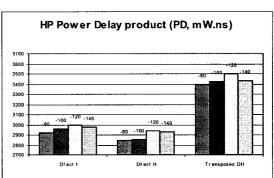

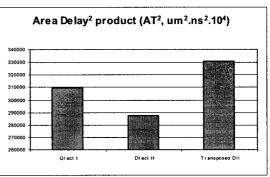

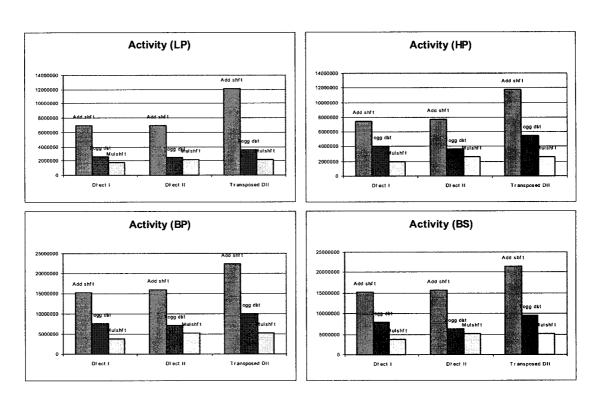

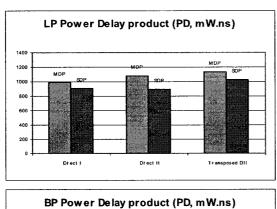

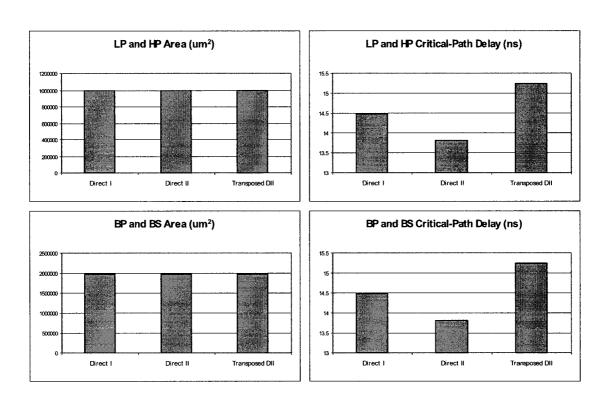

| 5.4.1.1 Low Pass and High Pass Filters                          | 81 |

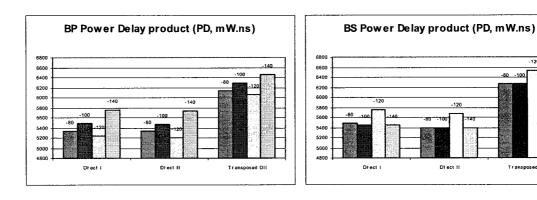

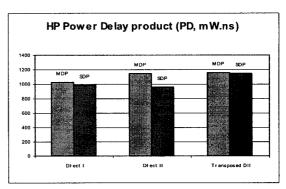

| 5.4.1.2 Band Pass and Band Stop Filters                         | 83 |

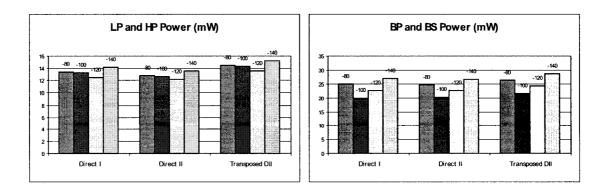

| 5.4.2 Multiple Data Path Arithmetic Units                       | 87 |

| 5.4.2.1 Low Pass and High Pass Filters                          | 87 |

| 5.4.2.2 Band Pass and Band Stop Filters                         | 89 |

| 5.4.3 Correlation Between Power Behaviour and Internal Activity | 92 |

| 5.4.4 Multiple Data Path vs. Single Data Path    | 99  |

|--------------------------------------------------|-----|

| 5.4.5 Second-Order-Section vs. Nth-Order-Section | 100 |

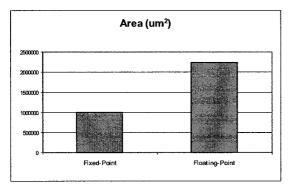

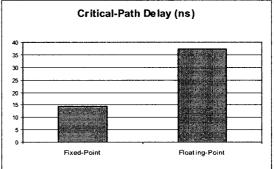

| 5.5 Floating-Point vs. Fixed-Point               | 101 |

| 5.6 Conclusion                                   | 103 |

| 5.7 Summary                                      | 104 |

| Chapter 6: Contribution and Future Works         | 105 |

| 6.1 Contribution                                 | 105 |

| 6.2 Feasibility Evaluation                       | 105 |

| 6.3 Future Related Works                         | 106 |

| References                                       | 108 |

| Appendix                                         | 113 |

# **List of Figures**

| 1.1 Power Optimization Flow                                                                | . 5 |

|--------------------------------------------------------------------------------------------|-----|

| 2.1 Direct Form of a FIR system                                                            | 15  |

| 2.2 Transposed Form of a FIR system                                                        | 16  |

| 2.3 Direct Form I of an IIR system                                                         | 18  |

| 2.4 Direct Form II of an IIR system                                                        | 19  |

| 2.5 Transposed Direct Form II of an IIR system                                             | 19  |

| 2.6 Cascade structure of a sixth-order system with Direct Form I realisation               | 21  |

| 2.7 Cascade structure of a sixth-order system with Direct Form II realisation              | 21  |

| 2.8 Cascade structure of a sixth-order system with Transposed Direct Form II realisation 2 | 21  |

| 3.1 Block diagram of the Single Data Path FP multiplier                                    | 25  |

| 3.2 Block diagram of the Single Data Path FP adder                                         | 26  |

| 3.3 Simple Adder and Multiplier Configurations                                             | 27  |

| 3.4 General Purpose Multiplier-Accumulator (MAC) configurations                            | 28  |

| 3.5 Transversal Filter Multiplier-Accumulator (F-MAC) configurations                       | 28  |

| 3.6 Block diagram of the Multiple Data Path FP multiplier                                  | 29  |

| 3.7 Block diagram of the Multiple Data Path FP adder                                       | 30  |

| 3.8 Simple Adder and Multiplier Configurations                                             | 31  |

| 3.9 General Purpose Multiplier-Accumulator (MAC) configurations                            | 32  |

| 3.10 Transversal Filter Multiplier-Accumulator (F-MAC) configurations                      | 32  |

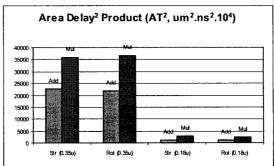

| 3.11 Average values of AT and AT2 products for the SDP units                               | 35  |

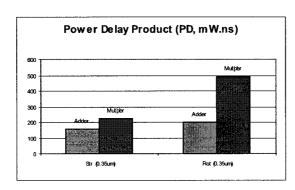

| 3.12 Average values of PD product for the SDP units                                        | 36  |

| 3.13 Average values of AT and AT2 products for the MDP units                         |  |

|--------------------------------------------------------------------------------------|--|

| 3.14 Average values of PD product for the MDP units                                  |  |

| 3.15 Area Performance Figures of the Arithmetic Units                                |  |

| 3.16 Power Performance Figures of the Arithmetic Units                               |  |

| 3.17 Delay Performance Figures of the Arithmetic Units                               |  |

| 3.18 Average values of PD product for the FP units                                   |  |

| 3.19Average values of AT product for the FP units                                    |  |

| 3.20 Average values of AT2 product for the FP units                                  |  |

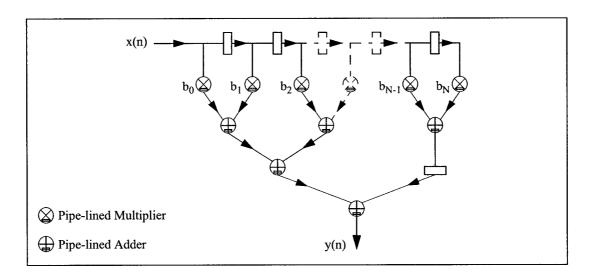

| 4.1 Standard Direct Tree Form                                                        |  |

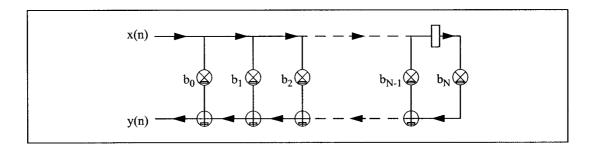

| 4.2 Standard Direct Form                                                             |  |

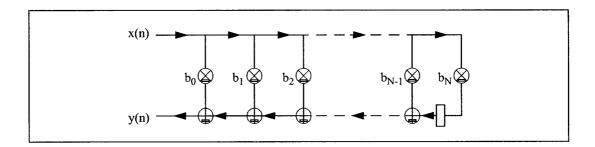

| 4.3 Standard Transposed Form                                                         |  |

| 4.4 Standard Direct Form of a FIR system with simulated pipe-lined components 49     |  |

| 4.5 Standard Transposed Form of a FIR system with simulated pipe-lined components 49 |  |

| 4.6 Approach 1 re-timed FIR Direct Form with simulated pipe-lined components 50      |  |

| 4.7 Approach 1 re-timed FIR Transposed Form with simulated pipe-lined components 50  |  |

| 4.8 Approach 1 re-timed FIR Direct Form with actual pipe-lined components 51         |  |

| 4.9 Approach 1 re-timed FIR Transposed Form with actual pipe-lined components 51     |  |

| 4.10 Modified Direct Tree Form with simulated pipe-lined components                  |  |

| 4.11 Modified Direct Form with simulated pipe-lined components                       |  |

| 4.12 Modified Transposed Form with simulated pipe-lined components 53                |  |

| 4.13 Direct Tree Form using pipe-lined components                                    |  |

| 4.14 Direct Form using pipe-lined components                                         |  |

| 4.15 Transposed Form using pipe-lined components                                     |  |

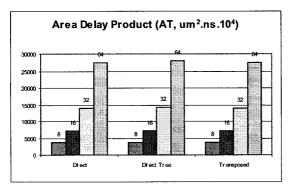

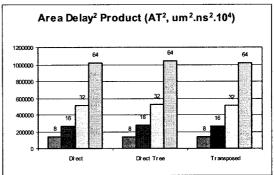

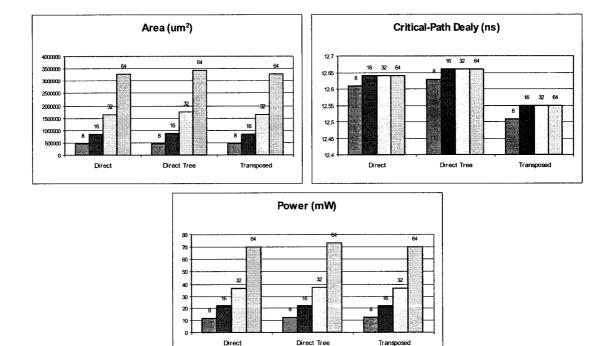

| 4.16 Area delay products for the FIR filter realisations using SDP units (pipe-lined) | 61 |

|---------------------------------------------------------------------------------------|----|

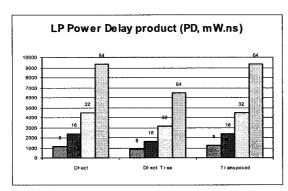

| 4.17 Power delay product for the FIR filter realisations using SDP units (pipe-lined) | 61 |

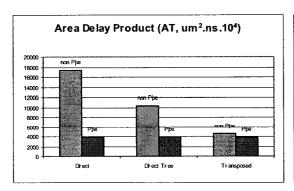

| 4.18 Area delay products for the FIR filter realisations using SDP units              | 64 |

| 4.19 Power delay product for the FIR filter realisations using SDP units              | 65 |

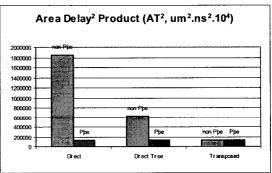

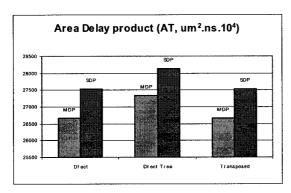

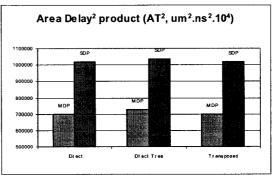

| 4.20 Area delay products for the FIR filter realisations with MDP units (pipe-lined)  | 69 |

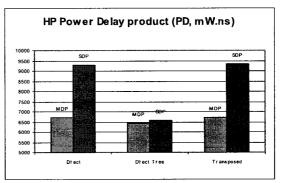

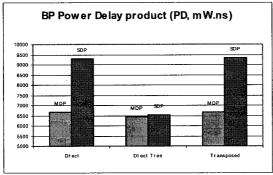

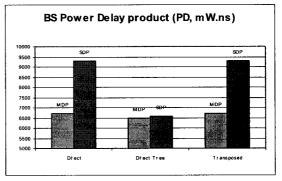

| 4.21 Power delay product for the FIR filter realisations with MDP units (pipe-lined)  | 70 |

| 4.22 Power delay product for order 64 FIR filter realisations (pipe-lined)            | 72 |

| 4.23 Area delay products for order 64 FIR filter realisations (pipe-lined)            | 72 |

| 4.24 Area, Delay and Power Performance of the Fixed-Point FIR filters                 | 73 |

| 4.25 Comparison of Performance of the Fixed and Floating-Point FIR filters            | 74 |

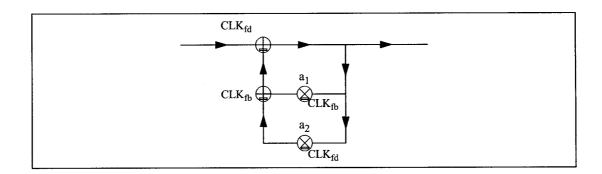

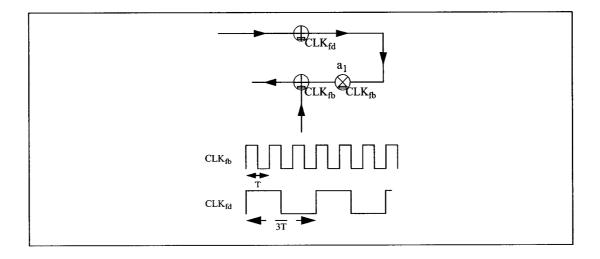

| 5.1 Feedback loop of Direct form I illustrating the clocking scheme of the structures | 78 |

| 5.2 Broken feedback loop and waveforms of the clock signals                           | 78 |

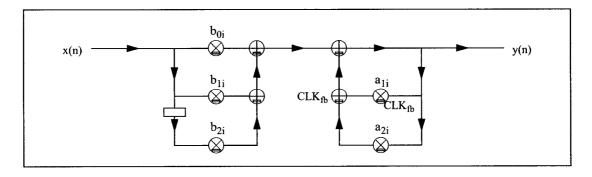

| 5.3 Ith Second-order section of a Direct form I IIR filter structure                  | 79 |

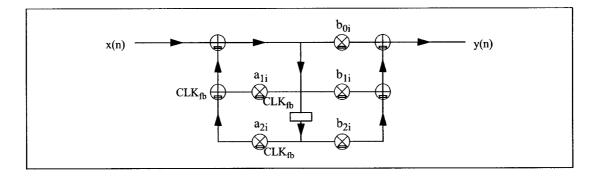

| 5.4 Ith Second-order section of a Direct form II IIR filter structure                 | 80 |

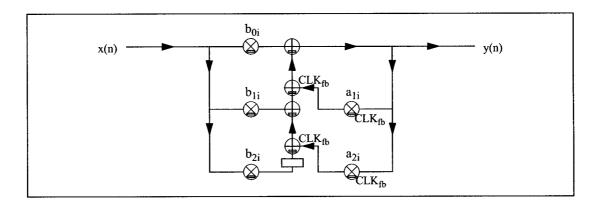

| 5.5 Ith Second-order section of a Transposed Direct form II IIR filter structure      | 80 |

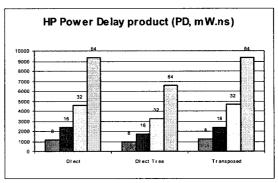

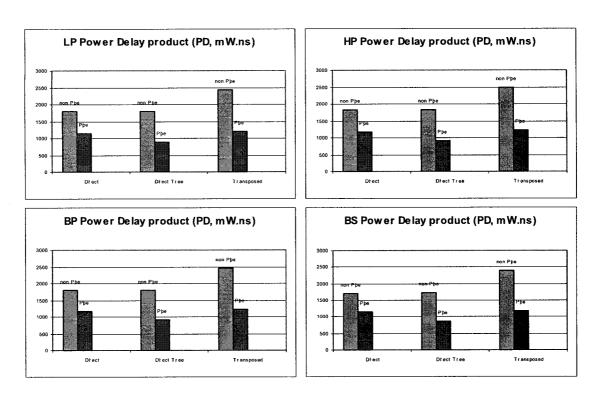

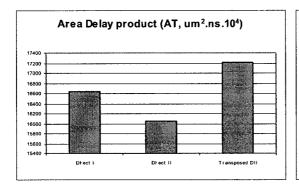

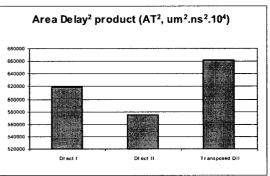

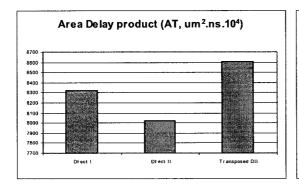

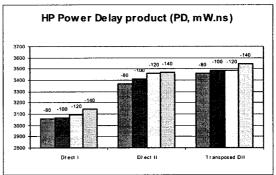

| 5.6 Area delay products for low pass and high pass filters using SDP units            | 83 |

| 5.7 Power delay product for low pass and high pass filters using SDP units            | 83 |

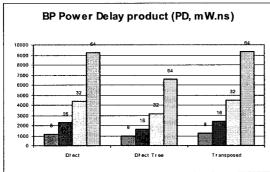

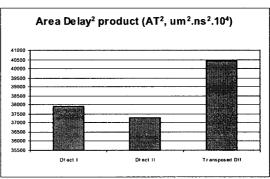

| 5.8 Area delay products for band pass and band stop filters using SDP units           | 85 |

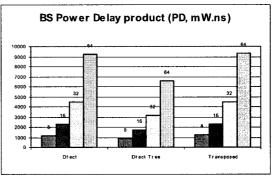

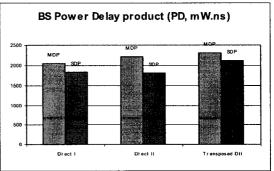

| 5.9 Power delay product for band pass and band stop filters using SDP units           | 86 |

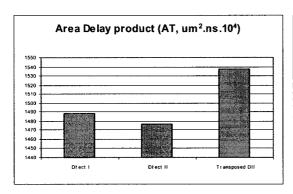

| 5.10 Area delay products for low pass and high pass filters using MDP units           | 88 |

| 5.11 Power delay product for low pass and high pass filters using MDP units           | 89 |

| 5.12 Area delay products for band pass and band stop filters using MDP units          | 91 |

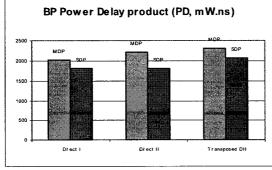

| 5.13 Power delay product for band pass and band stop filters using MDP units          | 92 |

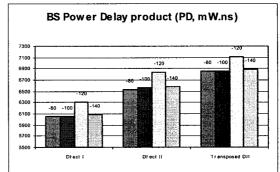

| 5.14 Break-down of activity for the IIR filters                                    | . 96 |

|------------------------------------------------------------------------------------|------|

| 5.15 Average Power delay product for the IIR filter realisations                   | . 99 |

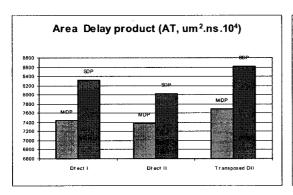

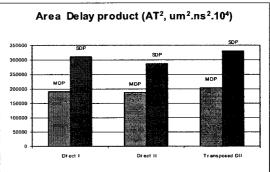

| 5.16 Average Area delay products for the IIR filter realisations                   | 100  |

| 5.17 Area, Delay and Power Performance of the Fixed-Point IIR filters              | 102  |

| 5.18 Power Performance of the Fixed-Point IIR filters                              | 102  |

| 5.19 Area, Delay and Power Performance of the Fixed and Floating-Point IIR filters | 103  |

# **List of Tables**

| 3.1 A, T and P figures in simple configurations                              | 33 |

|------------------------------------------------------------------------------|----|

| 3.2 A, T and P figures in MAC configuration                                  | 34 |

| 3.3 A, T and P figures in F-MAC configuration                                | 34 |

| 3.4 A, T and P figures in simple configurations                              | 36 |

| 3.5 A, T and P figures in MAC configuration                                  | 37 |

| 3.6 A, T and P figures in F-MAC configuration                                | 37 |

| 4.1 A, T and P figures for order 8 low pass and high pass filters            | 47 |

| 4.2 A, T and P figures for order 8 band pass and band stop filters           | 48 |

| 4.3 A, T and P figures for order 8 and 16 low pass filters with SDP units    | 57 |

| 4.4 A, T and P figures for order 32 and 64 low pass filters with SDP units   | 58 |

| 4.5 A, T and P figures for order 8 and 16 high pass filters with SDP units   | 58 |

| 4.6 A, T and P figures for order 32 and 64 high pass filters with SDP units  | 58 |

| 4.7 A, T and P figures for order 8 and 16 band pass filters with SDP units   | 59 |

| 4.8 A, T and P figures for order 32 and 64 band pass filters with SDP units  | 59 |

| 4.9 A, T and P figures for order 8 and 16 band stop filters with SDP units   | 59 |

| 4.10 A, T and P figures for order 32 and 64 band stop filters with SDP units | 60 |

| 4.11 Order 64 low pass filters activity                                      | 62 |

| 4.12 Order 64 high pass filters activity                                     | 62 |

| 4.13 Order 64 band pass filters activity                                     | 63 |

| 4.14 Order 64 band stop filters activity                                     | 63 |

| 4.15 A, T and P figures for order 8 and 16 low pass filters with MDP units   | 66 |

| 4.16 A, T and P figures for order 32 and 64 low pass filters with MDP units                  |

|----------------------------------------------------------------------------------------------|

| 4.17 A, T and P figures for order 8 and 16 high pass filters with MDP units                  |

| 4.18 A, T and P figures for order 32 and 64 high pass filters with MDP units                 |

| 4.19 A, T and P figures for order 8 and 16 band pass filters with MDP units                  |

| 4.20 A, T and P figures for order 32 and 64 band pass filters with MDP units                 |

| 4.21 A, T and P figures for order 8 and 16 band stop filters with MDP units                  |

| 4.22 A, T and P figures for order 32 and 64 band stop filters with MDP units                 |

| 5.1 A, T and P results for low pass filters with stop band ripple -80db and -100db using SDP |

| units                                                                                        |

| 5.2 A, T and P results for low pass filters with stop band ripple -120db and -140db using    |

| SDP units                                                                                    |

| 5.3 A, T and P results for high pass filters with stop band ripple -80db and -100db using    |

| SDP units                                                                                    |

| 5.4 A, T and P results for high pass filters with stop band ripple -120db and -140db using   |

| SDP units                                                                                    |

| 5.5 A, T and P results for band pass filters with stop band ripple -80db and -100db using    |

| SDP units                                                                                    |

| 5.6 A, T and P results for band pass filters with stop band ripple -120db and -140db using   |

| SDP units                                                                                    |

| 5.7 A, T and P results for band stop filters with stop band ripple -80db and -100db using    |

| SDP units                                                                                    |

| 5.8 A, T and P results for band stop filters with stop band ripple -120db and -140db using   |

| SDP units                                                                                    |

| 5.9 A, T and P results for low pass filters with stop band ripple -80db and -100db using    |

|---------------------------------------------------------------------------------------------|

| MDP units87                                                                                 |

| 5.10 A, T and P results for low pass filters with stop band ripple -120dband -140db using   |

| MDP units                                                                                   |

| 5.11 A, T and P results for high pass filters with stop band ripple -80db and -100db using  |

| MDP units                                                                                   |

| 5.12 A, T and P results for high pass filters with stop band ripple -120db and -140db using |

| MDP units                                                                                   |

| 5.13 A, T and P results for band pass filters with stop band ripple -80db and -100db using  |

| MDP units                                                                                   |

| 5.14 A, T and P results for band pass filters with stop band ripple -120db and -140db using |

| MDP units                                                                                   |

| 5.15 A, T and P results for band stop filters with stop band ripple -80db and -100db using  |

| MDP units90                                                                                 |

| 5.16 A, T and P results for band stop filters with stop band ripple -120db and -140db using |

| MDP units91                                                                                 |

| 5.17 Low pass filters activity with -80db and -100db                                        |

| 5.18 Low pass filters activity with -120db and -140db93                                     |

| 5.19 High pass filters activity with -80db and -100db94                                     |

| 5.20 High Pass filters activity with -120db and -140db                                      |

| 5.21 Band Pass filters activity with -80db and -100db94                                     |

| 5.22 Band Pass filters activity with -120db and -140db                                      |

| 5.23 Band Stop filters activity with -80db and -100db                                       |

| 5.24 Band Stop filters activity with -120db and -140db            | . 95 |

|-------------------------------------------------------------------|------|

| 5.25 Contribution percentages to power dissipation with MDP units | 97   |

| 5.26 Contribution percentages to power dissipation with SDP units | 98   |

# Chapter 1

### Introduction

#### 1.1 Introduction

Until a few years ago, floating-point (FP) processing was only available in large work stations. Nowadays, FP arithmetic is available in the smallest of computers. The major advantage of FP arithmetic is the high computational accuracy, in the context of truncation necessary in integer arithmetic, it provides along with a significantly wider dynamic range than fixed-point arithmetic. However, FP arithmetic is far more complex than fixed-point arithmetic and using it results in increased chip area, higher power dissipation and reduction in speed. Low power design became crucial with the wide spread of portable information and communication terminals. High performance electronics, in addition, suffer from a permanent increase of the dissipated power per square millimetre of silicon, due to the increasing clock-rates. The increase in power dissipation limits the performance [1][2].

Full-custom implementation and technology-specific optimization strategies are viable choices for low power, high speed digital design. However, reuse of such low level techniques is not possible with technology migration, and their results fade rapidly. High level design optimization techniques survive through generations of technology migration because of their inherent low sensitivity to the implementation technology. In contrast, power reduction and speed enhancement attained with high level design strategies are very significant. The power savings at the algorithm level are orders of magnitude [3].

1

#### 1.2 Low Power Design

The increasing need for low power consuming systems stems, in large part, from the huge demand for mobile digital electronics. New digital applications such as digital mobile communication devices (phones and PDAs), which utilize complex speech compression algorithms, and sophisticated radio modems in a pocket-sized device require methodologies for low power design. Considerable research efforts are focusing on increasing the life of batteries for mobile devices [4]. Numerous low power design techniques exist for different levels of the design flow. They range from the highest levels like algorithm and architecture all the way down to the physical layers.

At highest levels, the literature presents techniques that deal with sorting the coefficients of FIR filters [5], techniques that exploit the low power capabilities of parallel architectures [6], techniques that try to optimize arithmetic units with one constant operand [7] and transition activity scaling techniques to reduce the switching activity within the design [3][8]. At lower levels, we find such techniques as logic minimization and state encoding [9], hazardous activity elimination by latch repositioning [10] and by gate sizing [11], clock-gating [12][13], output pre-computation [14], gate resizing [15], signal-to-pin assignment and I/O encoding and the use of networks "don't cares" [16]. Of course, optimizing the high-level DSP architecture to allow selection of the optimal low-power process does not imply that lower level optimization techniques are no longer useful. Several low-level optimization techniques reduce power beyond that of architectural extensions. Further optimization can be achieved through process enhancement [17][18][19]. It has been argued that the right algorithm gives the maximum amount of power saving, which can be orders of magnitude

in contrast to other alternatives [3][20][21]. Using the correct algorithm, the right architecture and the proper clocking scheme, a considerable amount of power can be saved without having to use circuit level technology-dependent techniques.

#### 1.3 Motivation

FP arithmetic is gaining in popularity and because of certain assumptions about FP arithmetic units' performance, we deemed necessary to investigate some digital signal processing applications using FP arithmetic units. The simple extension of conclusions from the fixed-point domain to that of the floating-point can lead to unpleasant surprises. An example case of such extensions is the obviously common belief that in the floating-point domain, as in the fixed-point domain, multipliers are more important than adders. Such assumptions can be detrimental to a design cycle.

Other information of critical importance is the performance of different structures with different applications. The transfer function of a digital filter can have different implementations without changing the input/output behaviour. Even if area and delay are the same for all the implementations, the power dissipation is likely to be different. That is due to the fact that different structures have different node capacitances and different switching activities. The designer would not need to investigate the performance of the different implementations if the information is already available. That results in reducing the design cycle time, thus increasing productivity [1]. This research effort is meant to help the designer make design trade-off decisions based on power, area and delay performances of a number of network structures before even starting the design process.

#### 1.4 Design and Experimentation Methodology

In total, three Finite Impulse Response (FIR) and three Infinite Impulse Response (IIR) filter network structures are examined in this work. A few basic configurations using FP adders and multipliers are also examined. Modelling of the different designs is done at Register Transfer Level (RTL) in VHDL. RTL code is technology independent and can be translated into hardware with available technology libraries. Functional verification of the different designs is performed at both register transfer and Gate levels. As the power consumption of controlled data path architectures is highly dependent on the utilisation of different data paths, the role of input data becomes very important. Simulation of all the designs is done using real data obtained through conversion of real audio signals to IEEE single precision floating-point format.

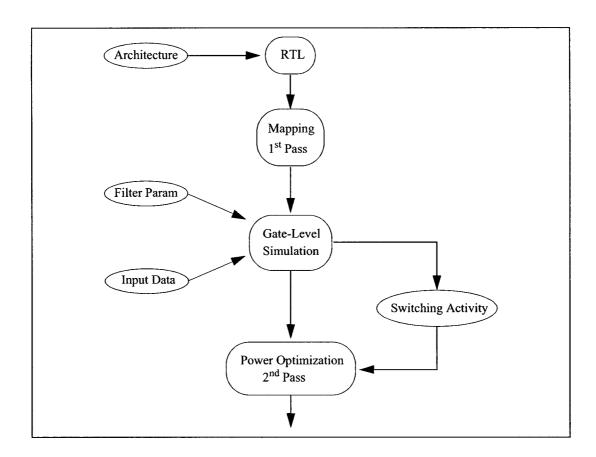

MATLAB is used to obtain the input data and to calculate the parameters for the different filters. It is also used to implement reference or "golden" models and to simulate them with the input data. Simulation results of the reference models are then stored into "golden" files and used to verify the results of the RTL and gate-level simulations. The VHDL System Simulator (VSS) is used to simulate RTL and gate-level netlists and to capture the switching activity. Design Compiler is used to synthesise the designs. Power Compiler, in conjunction with Design Compiler, uses the switching activity captured during simulation to optimize the designs simultaneously for area, delay and power and to analyse their power consumption. VSS, Design Compiler and Power Compiler are all products of Synopsys Inc. After generating the filter parameters and input data and RTL modelling of the architectures, the power optimization/estimation flow consists of several steps. We start with area

and delay optimization during the first pass mapping phase of the design. The design is then simulated at gate level to capture the switching activity, which is then back-annotated onto the gate-level design for simultaneous area and delay and power optimization during a second pass mapping phase. The flow is best illustrated in Figure 1.1. The switching activity of the different designs is captured during gate-level simulation and back-annotated onto the design nets for power optimization and power estimation. Power analysis using switching activity from gate-level simulation is very accurate. It can predict average power to within 10 to 25 percent of power analysis results, using a transistor-level simulator such as SPICE [22].

Figure 1.1 Power Optimization Flow

Although the floating-point arithmetic units used for this work are quite large circuits, the gate-level approach does not present any serious problem. The higher accuracy it provides makes it a more reliable approach than that of the RTL's. In fact, we found the results obtained with RTL approach to be inconclusive. It is better, actually, to skip that approach altogether, and work directly with gate-level. The time spent gathering results with the RTL approach should have been spent on the gate-level approach because it is more reliable. To reduce execution time, the building blocks are synthesised individually. Once that is done, they are connected together to form the larger designs. This saves us significant amount of time when synthesizing the large designs.

#### 1.5 Design Implementation

To prove that the findings of this work are not technology dependent, two target technology libraries are used during synthesis of the designs; 0.35 um and 0.18 um CMOS from TSMC provided by the Canadian Microelectronics Corporation (CMC). The operating voltage is 3 V for 0.35 um CMOS technology and 1.62 V for 0.18 um CMOS technology. During synthesis, the same set of constraints is used for the different designs. This ensures that only the difference in architecture is affecting the final results. The filter network structures used are basic common structures slightly modified, where necessary, to accommodate the pipelined floating-point arithmetic units. A detailed examination of these network structures can be found further in this thesis. While the main purpose of this work is to evaluate the power consumption of these different structures, each architecture can be further optimized for power by modifying the algorithm or by using circuit level optimization techniques or by customizing the synthesis constraints for each of the architectures.

Frequency distributions of pre-alignment and normalization shifts, their rate of change and the relevant bit level activities and other activity statistics have also been gathered [23]. This is made possible by carefully inserting counters and flags at particular locations within the designs. These "monitors" allowed for greater visibility of the type of operations being performed by the different components of the design. The extra code needed to implement the monitors is ignored during synthesis and only used to gather the statistics listed above during register transfer level simulation.

Simulation and synthesis of all the designs in this work require significant amount of runtime regardless of the type of platform they are running on. Taking a given design through the power optimization process presented in Figure 1.1 required anywhere between three to eight days of execution time on a six Ultra-SPARC 400 MHz CPU server with 6 GB of RAM, depending on the size of the design. The memory requirement often reached 1.8 GB of RAM with the largest designs. A particular family of designs required several weeks of execution time, mostly for gate level simulation. Experiments performed on this particular family of designs were limited to only the smallest of these designs. Because the experiments required significant amount of time and computing resources, a considerable amount of design automation scripts had to be developed to support this work. Simulation and verification flow scripts were written in addition to power optimization flow scripts to run these jobs in the background without having to rely on interactive shells. Additional scripts were developed for text editing and data extraction and status reporting at each phase of the different flows. Simple UNIX command files, Bourne shell, C shell and PERL were used to develop the design automation scripts.

#### 1.6 Contributions

The contributions of this thesis work can be summarised in the following few bullets:

- Contributions towards addressing assumptions about the performance of arithmetic

units in the floating-point domain. We evaluated the performance of a number of floating-point arithmetic units in three different applications. The results showed that multipliers and adders are equally important in the floating-point domain and the

performance of the adder cannot be neglected as it is the case in integer and fixed-point

arithmetic.

- We present a simple and easy way of pipe-lining digital filter structures by using pipelined arithmetic units.

- The evaluation of high level design decisions for performance optimal realisations of floating-point FIR and IIR filters. We compare the power/performance of several digital filter network structures with different filtering functions and classify them in accordance with their performance.

- We compare performance figures of different implementations of the filter structures and draw conclusions as to performance optimal conditions.

- The results of this work can help in the selection of the best suitable network structure for a given application, thus help reducing the "design gap".

#### 1.7 Thesis Organisation

The thesis is organised in the following manner: Chapter 2 introduces digital filter basics, types, common network structures and applications. Chapter 3 presents an in-depth investigation of area, delay and power performance of floating-point adders and multipliers [8].

Chapter 4 presents three common FIR network structures and how they were adapted to use pipe-lined floating-point arithmetic units in [8]. It also investigates the performance of these network structures with different filtering functions and with different arithmetic units in DSP applications. Chapter 5 presents the Second-order-Section (SOS) implementation of three common IIR network structures and their area, delay and power performance with different filtering functions and with the different floating-point adders and multipliers in DSP applications. Chapter 6 concludes this thesis and presents proposals for future related work.

#### 1.8 Summary

This chapter presented several aspects of the problem of digital design especially for low power. We started out by presenting arguments explaining why there is a need for new low power design methodologies. Next we presented a review of a number of low power design methodologies and approaches that are either being used in the industry or currently under development. The low power design methodologies discussed were divided into separate categories depending on which level of the design flow they are applied. Some approaches apply to physical level, gate-sizing for example, others apply to technology mapping or synthesis level as in the case of clock-gating. The most important approaches for this thesis work are those that apply to algorithmic level. The last part of this chapter discussed the motivation behind this research effort and presented the approach and tools used in the implementation.

### Chapter 2

### **Digital Filters**

#### 2.1 Introduction

In DSP applications, filtering of data samples is a very demanding operation. Given a set of filter specifications satisfying certain signal processing requirements, with the help of modern CAD tools, the designer can rapidly delineate an appropriate filter. While the filter transfer function obtained through the aforementioned exercise does remain the same, different implementations of the same transfer function are possible [24]. Digital Signal Processing (DSP) is one of the most powerful technologies that will shape science and engineering in the near future. Revolutionary changes have already been made in a broad range of fields: communications, medical imaging, radar & sonar, high fidelity music reproduction, and oil prospecting, to name just a few. Each of these areas has developed a deep DSP technology, with its own algorithms, mathematics, and specialised techniques. This combination of "breadth and depth" makes it impossible for any one individual to master all of the DSP technology that has been developed [25]. DSP education involves two tasks: learning general concepts that apply to the field as a whole, and learning specialised techniques for the particular area of interest. The rest of this chapter presents theoretical digital filter basics, usage, types and some of the common network structures.

#### 2.2 Filter Basics

In signal processing, the function of a filter is to remove unwanted parts of the signal (separation of signals), such as random noise, or to extract useful parts of the signal (restoration

of signals), such as the components lying within a certain frequency range. Analog, or electronic, filters can be used for these tasks; however, digital filters can achieve far superior results [25]. Digital filters are a very important part of DSP. In fact, their extraordinary performance is one of the key reasons that DSP has become so popular. Signal separation is needed when a signal has been contaminated with interference, noise, or other signals. For example, a device for measuring the electrical activity of a baby's heart (EKG) while still in the womb. The raw signal will likely be corrupted by the breathing and heartbeat of the mother. A filter might be used to separate these signals so that they can be individually analysed. Signal restoration is used when a signal has been distorted in some way. For example, an audio recording made with poor equipment may be filtered to better represent the sound as it actually occurred. Another example is the de-blurring of an image acquired with an improperly focused lens, or a shaky camera [25].

These problems can be approached with either analog or digital filters. Analog filters are cheap, fast, and have a large dynamic range in both amplitude and frequency. Digital filters, in comparison, are vastly superior in the level of performance that can be achieved. For example, a low-pass digital filter can have a gain of 1 +/- 0.0002 from DC to 1000 hertz, and a gain of less than 0.0002 for frequencies above 1001 Hertz. The entire transition occurs within only 1 hertz, which is not likely to be expected from an op-amp circuit. Digital filters can achieve thousands of times better performance than analog filters [25]. This affects dramatically the way filtering problems are approached. With analog filters, the emphasis is on handling limitations of the electronics, such as the accuracy and stability of the resistors and capacitors. In comparison, digital filters are so good that the performance of the filter

is frequently ignored. The emphasis shifts to the limitations of the signals, and the theoretical issues regarding their processing.

The most straightforward way to implement a digital filter is by convolving the input signal with the digital filter's impulse response. All possible linear filters can be made in this manner. When the impulse response is used in this way, it is called the filter kernel. Recursion is another way to implement digital filters. When a filter is implemented by convolution, each sample in the output is calculated by weighting the samples in the input, and adding them together. Recursive filters are an extension of this, using previously calculated values from the output, besides points from the input. Instead of using a filter kernel, recursive filters are defined by a set of recursion coefficients. All linear filters have an impulse response, even if it is not used to implement the filter. The impulse response of a filter is simply the output of the filter when the input is an impulse. The impulse responses of recursive filters are composed of sinusoids that exponentially decay in amplitude. In principle, this makes their impulse responses infinitely long. However, the amplitude eventually drops below the round-off noise of the system, and the remaining samples can be ignored. Because of this characteristic, recursive filters are also called **Infinite Impulse Response** or IIR filters [25]. In comparison, filters carried out by convolution are called Finite Impulse Response or FIR filters.

The following list gives some of the main advantages of digital over analog filters [25].

A digital filter is programmable, i.e. its operation is determined by a program stored in the processor's memory. This means that the digital filter can easily be changed without affecting the circuitry (hardware). An analog filter can only be changed by redesigning the filter circuit.

- Digital filters are easily designed, tested and implemented on a general-purpose computer or work-station. The characteristics of analog filter circuits (particularly those containing active components) are subject to drift and are dependent on temperature.

Digital filters do not suffer from these problems, and so are extremely stable with respect to both time and temperature.

- Unlike their analog counterparts, digital filters can handle low frequency signals accurately. As the speed of DSP technology continues to increase, digital filters are being applied to high frequency signals in the Radio Frequency (RF) domain, which in the past was the exclusive preserve of analog technology.

- Digital filters are very much more versatile in their ability to process signals in a variety of ways; this includes the ability of some types of digital filter to adapt to changes in the characteristics of the signal.

Fast DSP processors can handle complex combinations of filters in parallel or cascade (series), making the hardware requirements relatively simple and compact in comparison with the equivalent analog circuitry.

#### 2.3 FIR Systems

For causal FIR systems, the system function has only zeros (except for poles at z = 0) and is given by Eq (2.1):

$$y(n) = \sum_{k=0}^{M} b_k x(n-k)$$

Eq (2.1)

also known as the discrete convolution of x(n) with the impulse response:

$$h(n) = \begin{cases} b_n & n = 0, 1, ..., N \\ 0 & otherwise \end{cases}$$

Eq (2.2)

It is important to notice that a FIR filter uses memory to recall past inputs and integrate them with a specific weighting function (i.e. b terms). Thus, a FIR filter uses no feedback, is inherently stable and will not oscillate [24]. In some applications, such as speech processing, the zero phase (or linear phase) characteristic of a filter is not very critical. The human auditory system responds to short time spectral magnitude characteristics, so the shape of a speech waveform can sometimes change drastically without the human listener's being able to distinguish it from the original.

In image processing, the linear phase characteristic appears to be more important. Our visual world consists of lines, scratches, etc. A non-linear phase distorts the proper registration of different frequency components that make up the lines and scratches. This distorts the signal shape in various ways, including blurring. The zero-phase characteristic is quite useful in applications such as image processing. And zero-phase is very easy to achieve with FIR filters due to the symmetry with respect to the origin. In addition, design and implementation are often simplified if we require zero-phase [26].

Advantages of using FIR filters are [24]:

• FIR filters can easily be designed for constant phase delay and/or constant group delay.

- Stability is inherent and limit cycling is not a problem provided the user implements the filter with non-recursive techniques.

- Round off errors can be controlled in a straightforward fashion in order to keep their effects insignificant.

Drawbacks of using FIR filters are [27]:

- A FIR generally requires many stages to obtain sharp filter bands.

- Additional stages add to memory requirements and often slow processing speed.

#### 2.4 Basic Network Structures for FIR Systems

It will not be necessary for the purpose of this work to examine all known FIR structures. Instead, examining some of the basic and most common network structures will be sufficient for the scope of this thesis work.

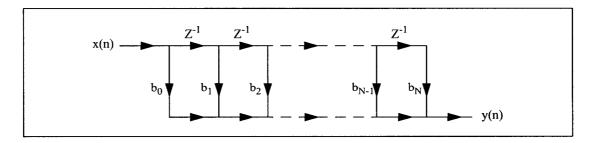

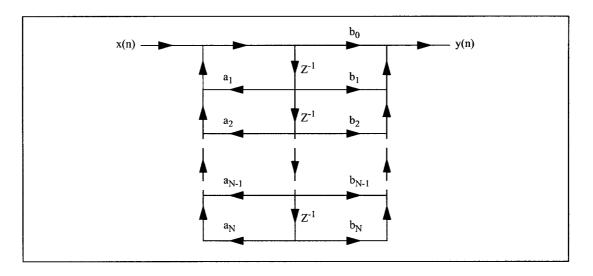

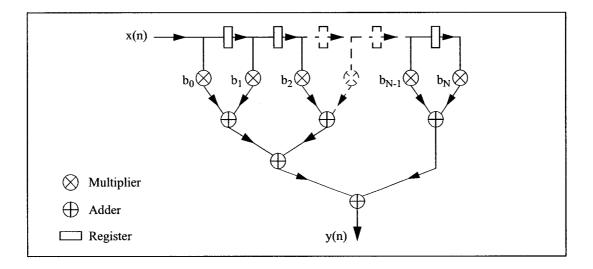

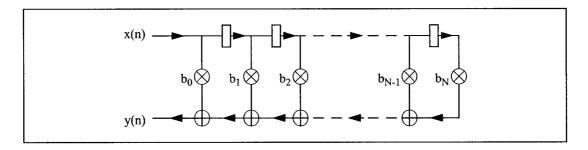

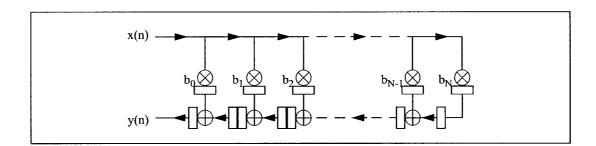

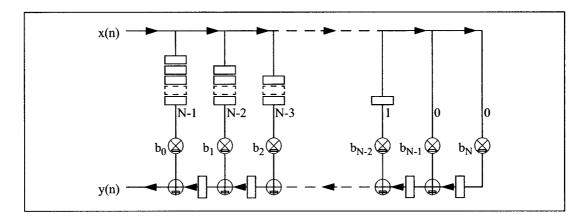

#### 2.4.1 Direct Form

Because of the chain of delay elements across the top of the diagram, this structure is also referred to as tapped delay line structure or a transversal filter structure [24].

Figure 2.1 Direct Form of a FIR system

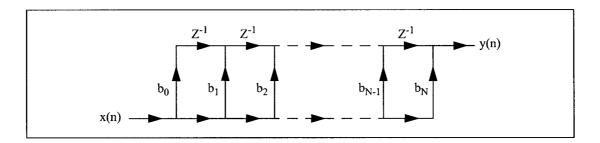

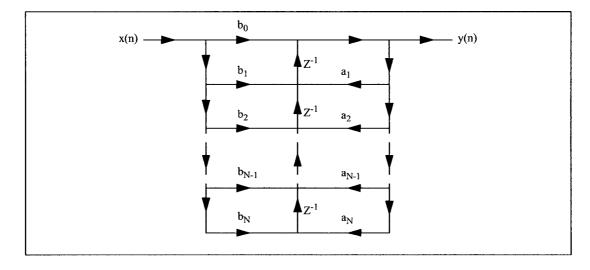

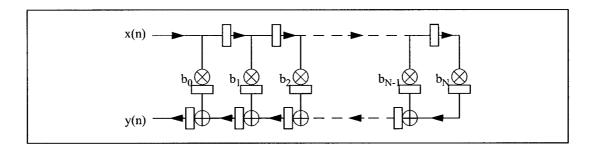

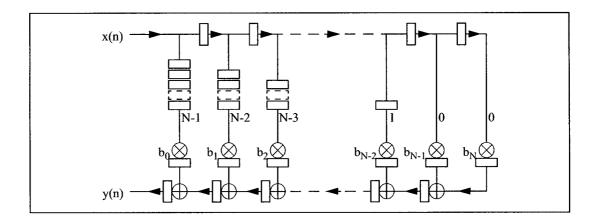

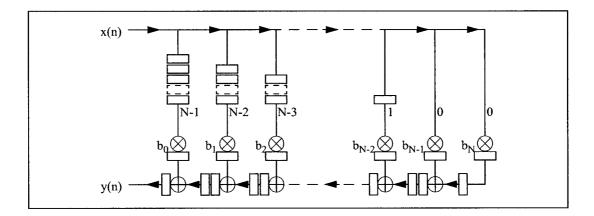

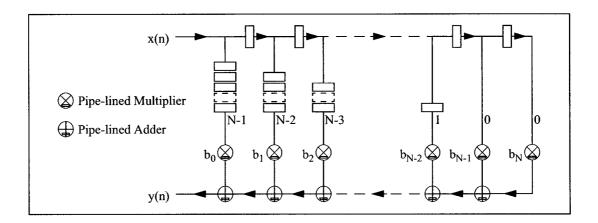

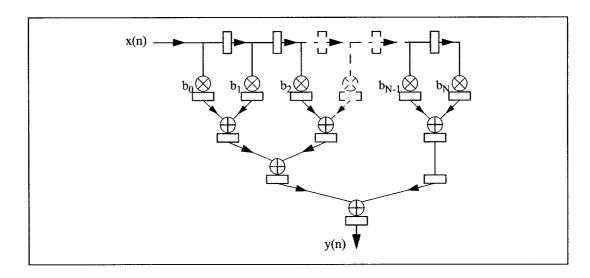

#### 2.4.2 Transposed Form

Transposition of a flow graph is accomplished by reversing the directions of all branches in the network while keeping the branch transmittances as they were and reversing the roles of the input and output so that the source nodes become sink nodes and vice versa. For single-input/single-output systems, the resulting flow graph has the same system function as the original graph if the input and output nodes are interchanged [24]. In the Direct form structure, the delay elements are across the input data path. In the Transposed form, the delay elements are across the computed data path. The Transposed structure is illustrated in Figure 2.2.

Figure 2.2 Transposed Form of a FIR system

#### 2.5 IIR Systems

An infinite impulse response (IIR) digital filter has an impulse response that is infinite in extent. A linear time-invariant IIR system has input and output that satisfy a difference equation of the form [24]:

$$y(n) - \sum_{k=1}^{N} a_k y(n-k) = \sum_{k=0}^{M} b_k x(n-k)$$

Eq (2.3)

Like FIR filters, IIR filters use memory to recall past inputs and integrate them with a specific weighting function (i.e. b terms). IIR filters, however, also recall past outputs and integrate them with specific weighting function (i.e. a terms). Recalling the past outputs is implemented by a feedback loop. With an IIR filter, controlling the phase characteristic is very difficult. It is impossible for a single recursively computable IIR filter to have zerophase. If zero-phase is necessary, two or more IIR filters are combined to obtain zero-phase for the overall filter [26].

The main advantage of using IIR filters is that they require smaller number of coefficients, i.e. arithmetic operations, to meet a particular magnitude specification than FIR filters [26]. However, the drawbacks of using IIR filters are [26]:

- Testing filter stability and stabilizing an unstable filter without affecting the magnitude response are very big tasks.

- Zero-phase is difficult to achieve.

- High sensitivity to filter coefficient quantization errors.

#### 2.6 Basic Network Structures for IIR Systems

An IIR filter with an arbitrary impulse response h(n) cannot be realised, since computing each output sample requires a large number of arithmetic operations. As a result, in addition to requiring h(n) to be real and stable, we require h(n) to have a rational z-transform corresponding to a recursively computable system [26]. It will not be necessary for the purpose of this work to examine all known IIR structures. Instead, examining some of the basic and most common network structures will be sufficient for the scope of this thesis work.

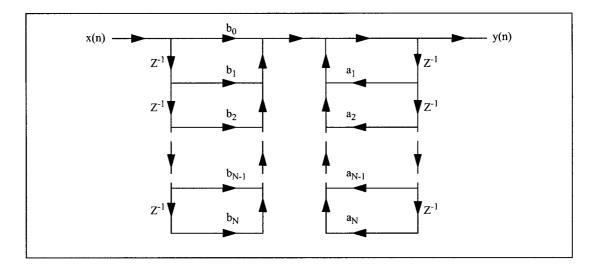

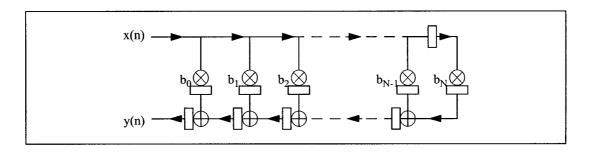

#### 2.6.1 Direct Forms

The coefficients in the Direct form structures correspond directly to the coefficients of the numerator and denominator polynomials. The corresponding rational system function to Eq (2.3) is given by Eq (2.4):

$$H(z) = \frac{\sum_{k=0}^{M} b_k z^{-k}}{\sum_{k=1}^{N} a_k z^{-k}}$$

$$1 - \sum_{k=1}^{M} a_k z^{-k}$$

Eq (2.4)

From Eq (2.4) we can draw two structures: Direct form I and Direct form II illustrated in Figure 2.3 and Figure 2.4 respectively.

Figure 2.3 Direct Form I of an IIR system

Figure 2.4 Direct Form II of an IIR system

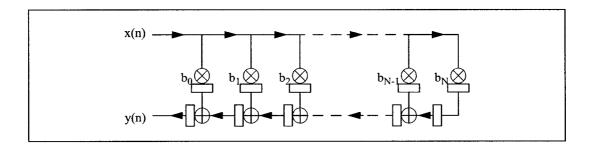

### 2.6.2 Transposed Direct Forms

Applying the transposition theorem, discussed in Section 2.4.2, to Direct form II, we end up with a new network structure: Transposed Direct Form II illustrated in Figure 2.5.

Figure 2.5 Transposed Direct Form II of an IIR system

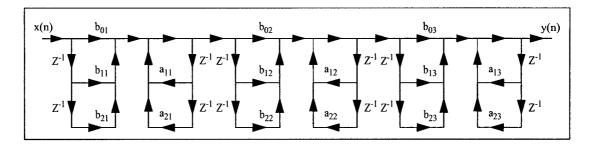

#### 2.6.3 Cascade Forms

If we factor the numerator and denominator polynomials in Eq (2.4), we can express H(z) in the following form [24], where  $M = M_1 + M_2$  and  $N = N_1 + N_2$ :

$$H(z) = A \frac{\left(\prod_{k=1}^{M_1} (1 - g_k z^{-1})\right) \prod_{k=1}^{M_2} (1 - h_k z^{-1})(1 - h^*_k z^{-1})}{\left(\prod_{k=1}^{N_1} (1 - c_k z^{-1})\right) \prod_{k=1}^{N_2} (1 - d_k z^{-1})(1 - d^*_k z^{-1})}$$

Eq (2.5)

In this expression, the first-order factors represent real zeros at  $g_k$  and real poles at  $c_k$ , and the second-order factors represent complex conjugate pairs of zeros at  $h_k$  and  $h_k^*$  and complex conjugate pairs of poles at  $d_k$  and  $d_k^*$ . This represents the most general distribution of poles and zeros when all the coefficients in Eq (2.4) are real. Eq (2.5) suggests a class of structures consisting of a cascade of first- and second-order systems. In practice, however, it is often desirable to implement the cascade realisation using a minimum of storage and computation. A modular structure that is advantageous for many types of implementation is obtained by combining pairs of real factors and complex conjugate pairs into second-order factors so that Eq (2.5) can be expressed by Eq (2.6) [24], where  $N_s$  is the largest integer contained in (N+1)/2:

$$H(z) = \prod_{k=1}^{N_s} \frac{b_{0k} + b_{1k}z^{-1} + b_{2k}z^{-2}}{1 - a_{1k}z^{-1} - a_{2k}z^{-2}}$$

Eq (2.6)

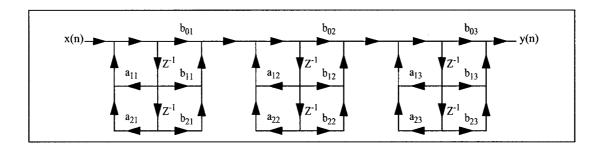

The individual second-order sections (SOS) can be implemented using any of the Direct form structures in Figure 2.3, Figure 2.4 and Figure 2.5. The resulting network structures are illustrated in Figure 2.6, Figure 2.7 and Figure 2.8 respectively.

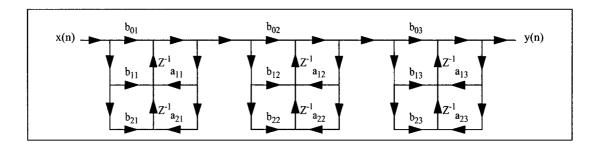

Figure 2.6 Cascade structure of a sixth-order system with Direct Form I realisation

Figure 2.7 Cascade structure of a sixth-order system with Direct Form II realisation

Figure 2.8 Cascade structure of a sixth-order system with Transposed Direct Form II realisation

# 2.7 Summary

In this chapter we have presented the basic concepts of digital filtering. We began with a brief review of the different types of digital filters and their applications. We followed by discussing the advantages and disadvantages of each type of digital filters and reviewing some of their basic common network structures. The digital filter network structures pre-

sented in this chapter are the basis for the work discussed in Chapter 4 and Chapter 5. Since these two chapters contain numerous references to the network structures discussed in this chapter, it became necessary to familiarise the reader with these structures to better understand the implications of the results reported in this thesis.

# Chapter 3

# **Arithmetic Units**

#### 3.1 Introduction

The wide dynamic range of floating point arithmetic is attracting more and more signal processing applications to the floating point domain. This trend has become noticeable in recent years, with the advent of high speed floating point DSP integrated circuits. Advances in VLSI technology made it possible for even small computers to perform sophisticated floating point computations. In integer and fixed-point arithmetic and for the same bit width, addition takes a back seat to multiplication whether for area or for delay or for power consumption.

The objective of the present chapter is to show that in floating point arithmetic, both multiplication and addition operations are on an equal footage of importance. A secondary objective is to show that Transition Activity Scaling Algorithm [3] based floating-point arithmetic units [8] consume less power than their standard counterparts [28] [29]. Both goals are technology independent and that is demonstrated through the use of two different CMOS process technologies, 0.35 um and 0.18 um from TSMC. For all the designs, the same set of constraints is used during synthesis to ensure that it is only the difference in architecture that is affecting the final results. The rest of this chapter is organized in the following manner. Section 3.2 presents the experimental approach used to simulate and synthesize the different designs. Section 3.3 presents the results of the different experiments along with analyses of those results. Section 3.5 concludes this chapter.

#### 3.2 Experimental Approach

Different experiments are performed to realise the aforementioned objectives. All the designs are implemented with VHDL coding and synthesised using "Design Compiler" and "Power Compiler" from Synopsys. The adder and multiplier [8] are IEEE 754 floating-point standard (single precision) compliant floating-point arithmetic units. This means that the data buses in the designs are 32-bit wide. The floating-point multiplier and adder are treated as separate entities. Rounding is performed after each operation, addition or multiplication, which complies with IEEE standard. Two sets of FP arithmetic units are evaluated, Single Data Path (SDP) units [8][28][29] and Multiple Data Path (MDP) units [3][8][22].

#### 3.2.1 Input Data Samples

An assorted collection of audio signal samples in "wav" and "au" formats are listed in [22]. Due to the excessive amount of time required to execute each experiment, we had to limit ourselves to processing only three randomly chosen audio samples out of the batch of samples listed in [22]. The audio signal samples used are namely: Graphon.au, Quichits.wav and Danube.au. Also used is X-files.wav, a 606 KB wav-format sample of the X-files theme that was down-loaded off the world-wide-web. Moreover, to reduce the execution time of the simulation and synthesis procedures, only 64k data input vectors in floating-point format are used. All data samples are converted to IEEE 754 floating-point standard (single precision) format to be compatible with the VHDL coded designs. Converting to floating point format is performed with especially written MATLAB routines.

# 3.2.2 SDP Configurations

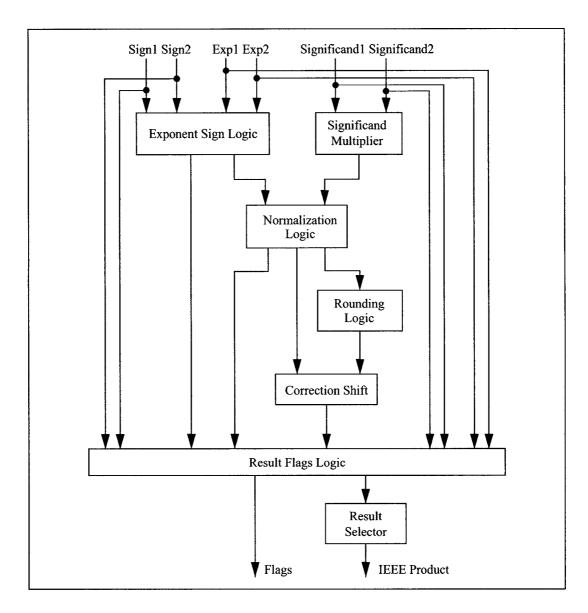

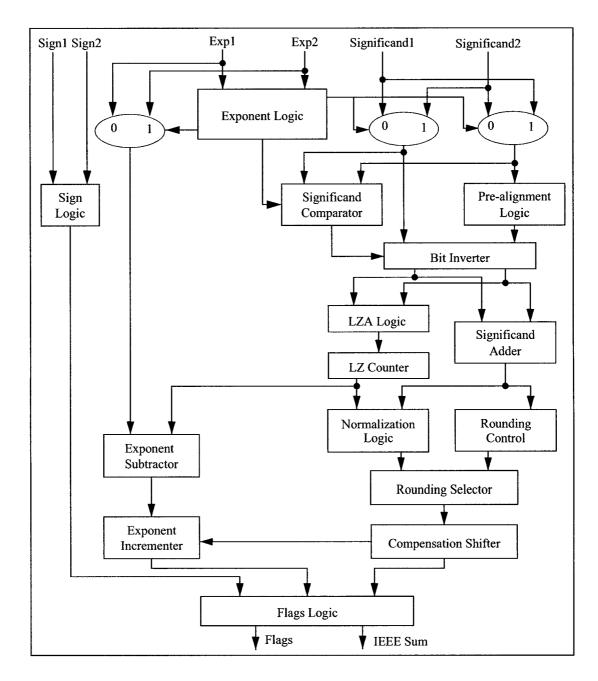

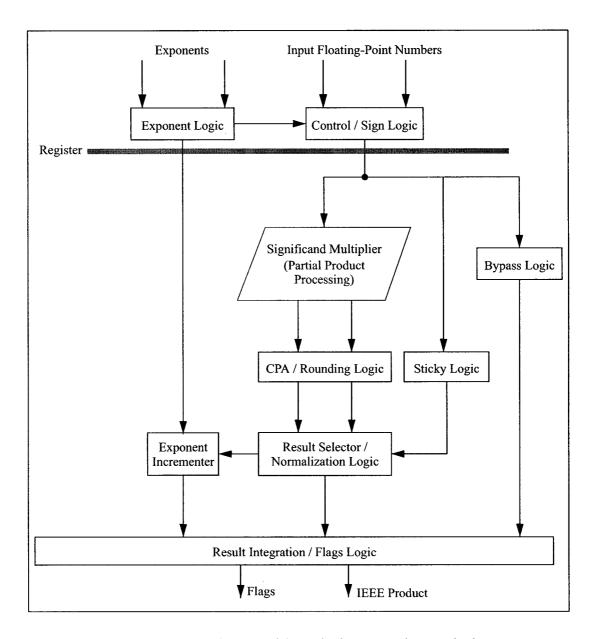

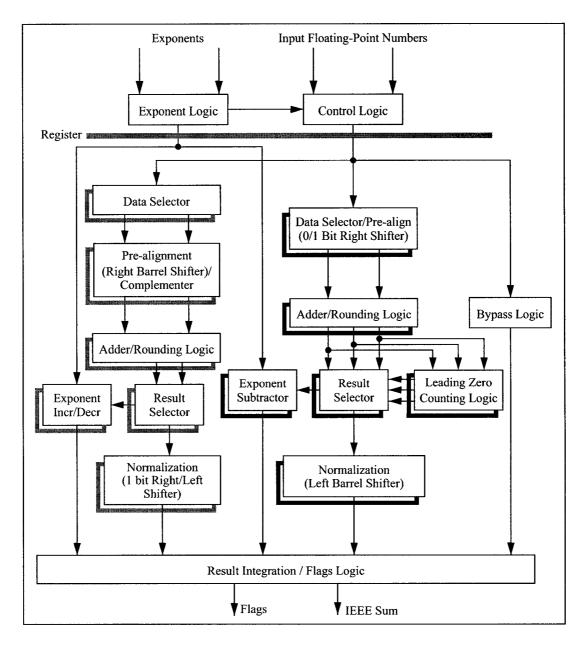

The block diagrams of the SDP FP arithmetic units are shown in Figure 3.1 and Figure 3.2.

Please note that these are non pipe-lined arithmetic units.

Figure 3.1 Block diagram of the Single Data Path FP multiplier

Figure 3.2 Block diagram of the Single Data Path FP adder

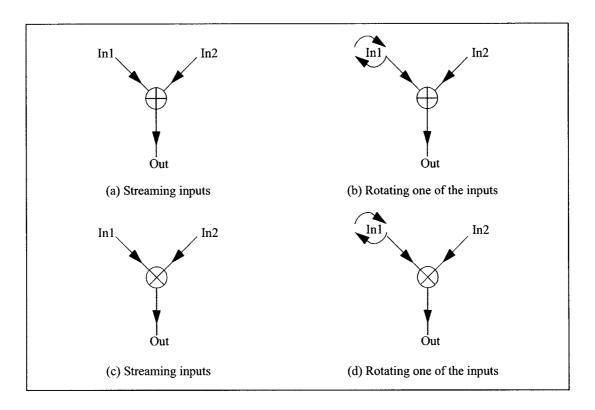

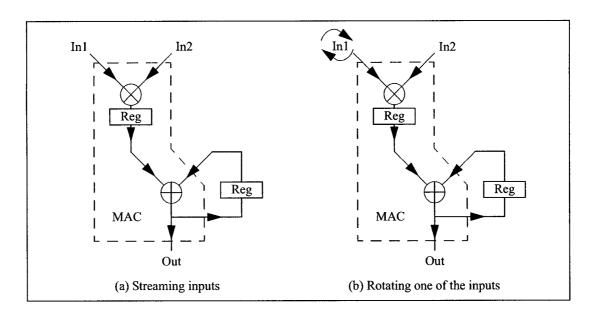

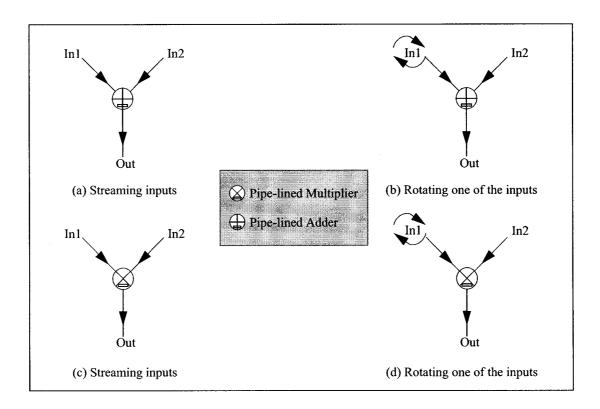

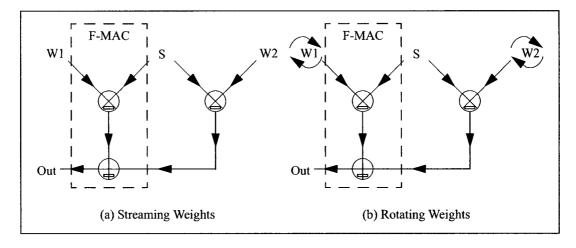

The arithmetic units [8] are simulated and synthesized in three different configurations. The first configuration consists of a simple component, adder [Figure 3.3, (a) & (b)] or multiplier [Figure 3.3, (c) & (d)]. The second consists of a general purpose Multiplier-Accumu-

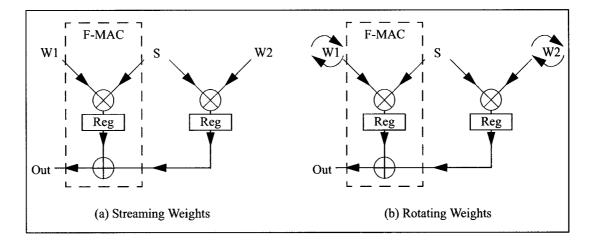

lator (MAC) [Figure 3.4]. And the third consists of a Multiplier-Accumulator (F-MAC) having the same function we see in a transversal filter structure [Figure 3.5].

Figure 3.3 Simple Adder and Multiplier Configurations

Two simulation environments are used to capture the switching activity for the adder, the multiplier and the general purpose MAC. The first simply connects two data streams to the input [Figure 3.3 (a) & (c) and Figure 3.4 (a)]. The purpose of the second is to influence the switching activity throughout the design and to reduce the amount of occurrences of special numbers (0, denormal,  $\pm \infty$  and NaN [3]). A simple and sufficient way of doing just that is to rotate a set of non-special data numbers at one of the inputs [Figure 3.3 (b) & (d)][Figure 3.4 (b)]. The other input is the same as in the first simulation environment.

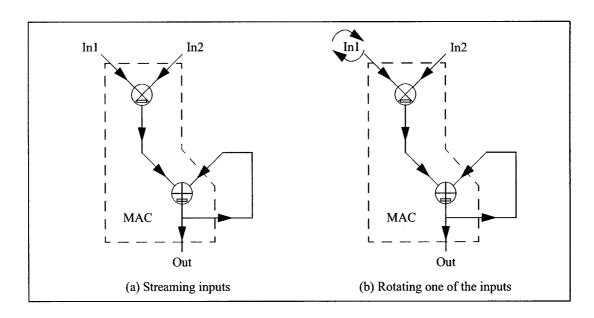

Figure 3.4 General Purpose Multiplier-Accumulator (MAC) configurations

Figure 3.5 Transversal Filter Multiplier-Accumulator (F-MAC) configurations

The third configuration has two simulation environments also, slightly different from each other. One has constant multiplication weights [Figure 3.5 (a)] while the other rotates a set of weights [Figure 3.5 (b)]. For the three configurations, the rotated weights are those of an order 8 low pass FIR filter with a cut-off frequency of 0.2.

# 3.2.3 MDP Configurations

The block diagrams of the MDP FP arithmetic units are shown in Figure 3.6 and Figure 3.7. Please note that these are pipe-lined arithmetic units and the pipe-line register is an integral part of the design and cannot be removed without compromising the functionality of these units.

Figure 3.6 Block diagram of the Multiple Data Path FP multiplier

Figure 3.7 Block diagram of the Multiple Data Path FP adder

For the above reason, the design configurations seen in the previous section had to be modified to accommodate these pipe-lined units. Figure 3.8, Figure 3.9 and Figure 3.10 present the modified configurations. Please note that the registers used in the SDP design configurations.

rations are now internal components of the MDP arithmetic units. The simulation environments used are the same as in Section 3.2.2.

Figure 3.8 Simple Adder and Multiplier Configurations

With these configurations too, two simulation environments are used to capture the switching activity for the adder, the multiplier and the general purpose MAC. The first simply connects two data streams to the input [Figure 3.8 (a) & (c) and Figure 3.9 (a)]. The purpose of the second is to influence the switching activity throughout the design and to reduce the amount of occurrences of special numbers by rotating a set of non-special data numbers at one of the inputs [Figure 3.8 (b) & (d)][Figure 3.9 (b)]. The other input is the same as in the first simulation environment.

Figure 3.9 General Purpose Multiplier-Accumulator (MAC) configurations

Figure 3.10 Transversal Filter Multiplier-Accumulator (F-MAC) configurations

The third configuration has two simulation environments also. One has constant multiplication weights [Figure 3.10 (a)] while the other rotates a set of weights [Figure 3.10 (b)]. Here too, the rotated weights are those of an order 8 low pass FIR filter with a cut-off frequency of 0.2.

#### 3.3 Results

The reported measurements are those of the area (A), the critical-path delay (T) and the dynamic power (P). Also presented are the calculated values of the AT, AT<sup>2</sup> and PD products in Figure 3.11 and Figure 3.12. Since the leakage power is negligible to the dynamic power, its contribution to the total power consumption has no effect on the results of the comparison work. For that reason, it is not included when considering the power performance of the designs. Please note that for the same design we can have slightly different values, less than 2%, for area and delay if the input is changed. That is due to fine tuning the design during the power optimization procedure [22]. Also, please note that power dissipated by both adder and multiplier is data dependent and the variation of power dissipation with different input data is very high.

# 3.3.1 Single Data Path FP Arithmetic Units

The block diagrams of the multiplier and the adder are shown in Figure 3.1 and Figure 3.2. The simulation results show the highest critical path delay for the adder and the multiplier to be 59.29 ns in 0.35 um technology. For power comparison, the operating frequency of all the designs and in both technologies is set to 16.67 MHz, corresponding to a clock signal period of 60 ns. The power performance figures are measured at the above frequency.

Table 3.1 A, T and P figures in simple configurations

| Simple Config |       | Adder           |       |      | Multiplier      |       |      |  |

|---------------|-------|-----------------|-------|------|-----------------|-------|------|--|

| Data          | Tech. | Α               | Т     | P    | Α               | Т     | P    |  |

|               | um    | um <sup>2</sup> | ns    | mW   | um <sup>2</sup> | ns    | mW   |  |

| Str           | 0.35  | 174195          | 59.15 | 3.17 | 441735          | 59.15 | 3.73 |  |

Table 3.1 A, T and P figures in simple configurations

| Simple Config |       | Adder           |       |      | Multiplier      |       |       |  |

|---------------|-------|-----------------|-------|------|-----------------|-------|-------|--|

| Data          | Tech. | Α               | Т     | P    | Α               | Т     | P     |  |

|               | um    | um <sup>2</sup> | ns    | mW   | um <sup>2</sup> | ns    | mW    |  |

| Rot           | 0.35  | 169855          | 59.07 | 5.81 | 420096          | 59.15 | 14.13 |  |

| Str           | 0.18  | 33681           | 30.57 | 0.62 | 78309           | 34.33 | 1.40  |  |

| Rot           | 0.18  | 32486           | 31.16 | 0.75 | 78833           | 32.31 | 1.77  |  |

Table 3.2 A, T and P figures in MAC configuration

| MAC  |       | Adder           |       |      | Multiplier      |       |       |  |

|------|-------|-----------------|-------|------|-----------------|-------|-------|--|

|      | Tech. | A               | Т     | Р    | A               | Т     | P     |  |

| Data | um    | um <sup>2</sup> | ns    | mW   | um <sup>2</sup> | ns    | mW    |  |

| Str  | 0.35  | 170406          | 57.97 | 3.83 | 391833          | 59.29 | 7.90  |  |

| Rot  | 0.35  | 166923          | 58.00 | 5.18 | 395246          | 59.22 | 23.25 |  |

| Str  | 0.18  | 32689           | 30.98 | 0.52 | 77949           | 34.34 | 1.36  |  |

| Rot  | 0.18  | 32297           | 31.88 | 0.57 | 78561           | 32.82 | 1.65  |  |

Table 3.3 A, T and P figures in F-MAC configuration

| F-MAC |       | Adder           |       |      | Multiplier      |       |       |  |

|-------|-------|-----------------|-------|------|-----------------|-------|-------|--|

|       | Tech. | A               | Т     | P    | Α               | Т     | P     |  |

| Data  | um    | um <sup>2</sup> | ns    | mW   | um <sup>2</sup> | ns    | mW    |  |

| Str   | 0.35  | 168875          | 58.12 | 5.56 | 408502          | 59.19 | 13.94 |  |

| Rot   | 0.35  | 166932          | 58.09 | 6.21 | 395263          | 59.23 | 23.23 |  |

| Str   | 0.18  | 32526           | 31.73 | 0.57 | 77998           | 33.22 | 1.59  |  |

| Rot   | 0.18  | 32252           | 31.43 | 0.62 | 78565           | 32.76 | 1.65  |  |

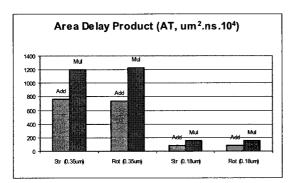

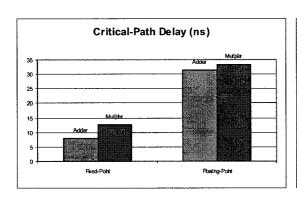

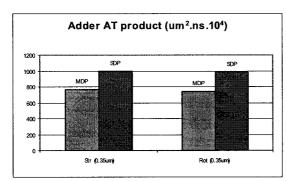

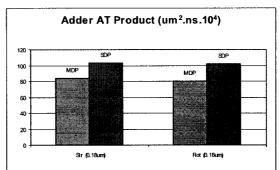

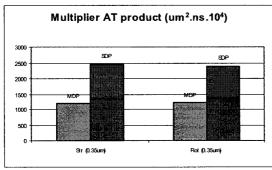

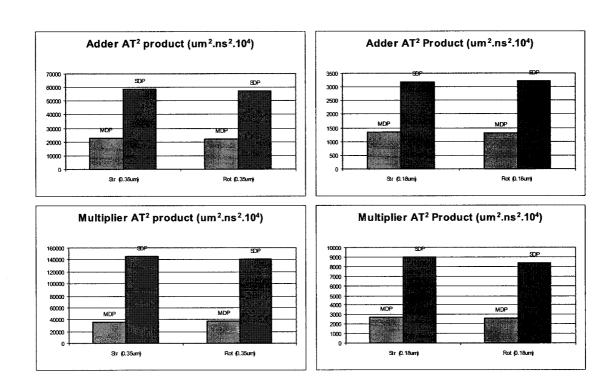

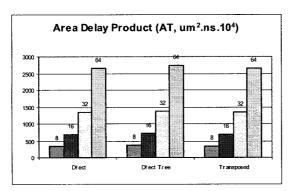

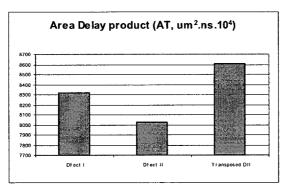

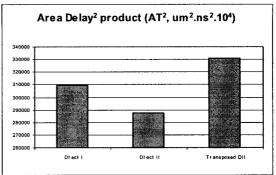

Examining the results of Table 3.1 through Table 3.3 for both adder and multiplier, in the configurations illustrated in Figure 3.3, Figure 3.4 and Figure 3.5, we clearly see that the adder cannot be considered negligible compared to the multiplier in terms of performance. It is obvious that the adder has a smaller area than the multiplier, but it is only by around 60% in both technologies. Comparing the critical-path delays, we find that they differ by a maximum of only 10%. The Area Delay and Area Delay<sup>2</sup> products presented in Figure 3.11 show a clearer image of the above discussion.

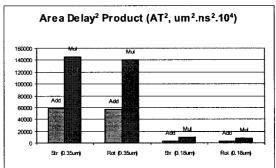

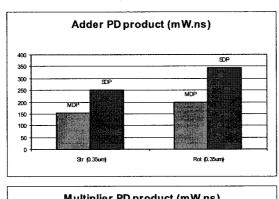

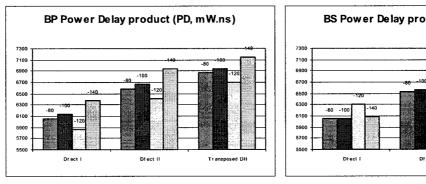

Figure 3.11 Average values of AT and AT<sup>2</sup> products for the SDP units

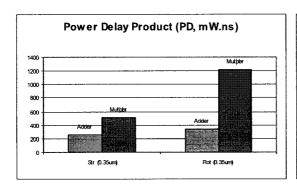

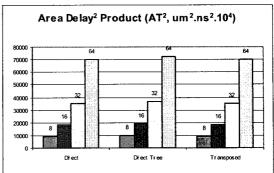

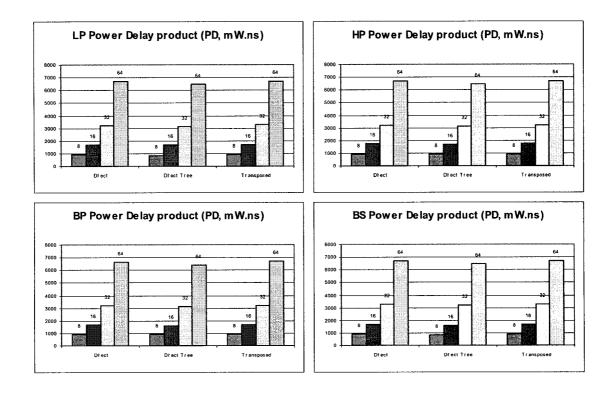

Comparing the power performance, we find the adder to be consuming less than the multiplier by an average reaching 67% in 0.35 um technology and 64% in 0.18 um technology. That is clearly reflected in the Power Delay product presented in Figure 3.12. Here too, we find the effect of the adder to be non negligible in comparison to that of the multiplier. This is due to the high level of complexity of the FP addition compared to that of the FP multiplication. The added complexity of the addition algorithm narrows the performance gap between adders and multipliers in the FP domain.

Figure 3.12 Average values of PD product for the SDP units

# 3.3.2 Multiple Data Path FP Arithmetic Units

The block diagrams of the multiplier and the adder are shown in Figure 3.6 and Figure 3.7. Here too, the power consumption is measured at an operating frequency of 16.67 MHz, corresponding to a clock signal period of 60 ns. Examining the results of Table 3.4 through Table 3.6 for both, adder and multiplier, in the configurations illustrated in Figure 3.3, Figure 3.4 and Figure 3.5, we see once again that the adder cannot be considered negligible compared to the multiplier.

Table 3.4 A, T and P figures in simple configurations

| Simp | le Config | Adder           |       |      | Multiplier      |       |      |

|------|-----------|-----------------|-------|------|-----------------|-------|------|

|      | Tech.     | Α               | Т     | P    | Α               | Т     | P    |

| Data | um        | um <sup>2</sup> | ns    | mW   | um <sup>2</sup> | ns    | mW   |

| Str  | 0.35      | 271329          | 30.15 | 2.78 | 396314          | 30.35 | 3.34 |

| Rot  | 0.35      | 259691          | 29.44 | 3.85 | 407479          | 30.09 | 8.49 |

| Str  | 0.18      | 53227           | 16.23 | 0.46 | 95174           | 16.96 | 0.50 |

| Rot  | 0.18      | 49771           | 15.91 | 0.59 | 94017           | 16.74 | 0.96 |

Table 3.5 A, T and P figures in MAC configuration

| N    | МАС   | Adder           |       |      | Multiplier      |       |      |

|------|-------|-----------------|-------|------|-----------------|-------|------|

|      | Tech. | A               | Т     | P    | Α               | Т     | P    |

| Data | um    | um <sup>2</sup> | ns    | mW   | um <sup>2</sup> | ns    | mW   |

| Str  | 0.35  | 255579          | 29.99 | 2.36 | 394424          | 29.53 | 3.04 |

| Rot  | 0.35  | 249008          | 30.53 | 2.92 | 405283          | 30.03 | 8.06 |

| Str  | 0.18  | 53725           | 15.78 | 0.33 | 95578           | 16.69 | 0.45 |

| Rot  | 0.18  | 51143           | 16.06 | 0.41 | 94263           | 16.67 | 0.45 |

Table 3.6 A, T and P figures in F-MAC configuration

| F-MAC |       | Adder           |       |      | Multiplier      |       |      |

|-------|-------|-----------------|-------|------|-----------------|-------|------|

| D .   | Tech. | A               | Т     | P    | A               | Т     | P    |

| Data  | um    | um <sup>2</sup> | ns    | mW   | um <sup>2</sup> | ns    | mW   |

| Str   | 0.35  | 244519          | 28.35 | 2.62 | 407313          | 29.91 | 4.84 |

| Rot   | 0.35  | 238070          | 28.77 | 3.20 | 405554          | 30.25 | 8.01 |

| Str   | 0.18  | 49600           | 16.25 | 0.46 | 95548           | 17.41 | 0.60 |

| Rot   | 0.18  | 49310           | 16.26 | 0.51 | 93741           | 16.62 | 0.45 |

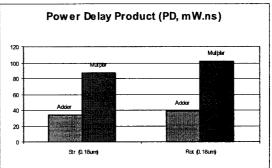

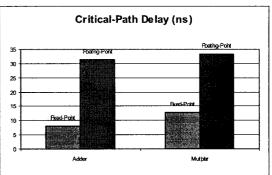

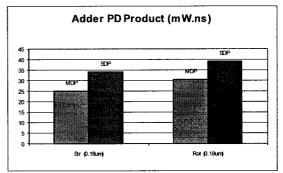

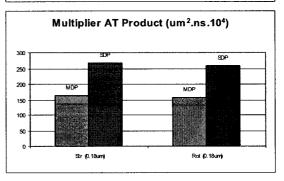

The adder, here, has a smaller area than the multiplier, but it is only by around 45% in both technologies. Comparing the critical-path delays, we find that they differ by a maximum of only 4%. The Area Delay and Area Delay<sup>2</sup> products presented in Figure 3.13 reflect the above discussion. Comparing the power performance, we find the adder to be consuming less than the multiplier by an average reaching 64% in 0.35 um technology and 40% in 0.18 um technology. That is clearly reflected in the Power Delay product presented in Figure

3.14. Here too, we find the effect of the adder to be non negligible in comparison to that of the multiplier. In fact, in some cases we find the adder to have a 13% higher power consumption than the multiplier. This is due to the high level of complexity of the FP addition compared to that of the FP multiplication. The higher complexity of the transition activity scaling algorithms, especially the addition's, narrows the performance gap between adders and multipliers in the FP domain. In fact, that gap is considerably diminished to the point where it is possible for adders to dissipate more power than multipliers [Table 3.6].

Figure 3.13 Average values of AT and AT<sup>2</sup> products for the MDP units

Figure 3.14 Average values of PD product for the MDP units

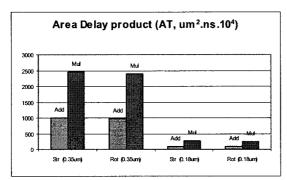

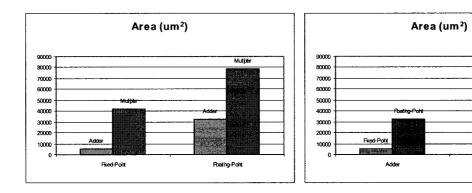

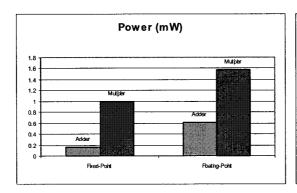

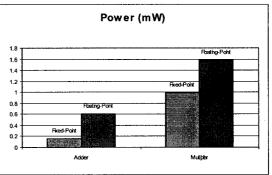

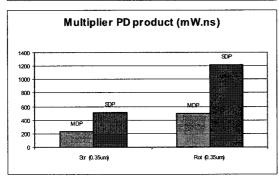

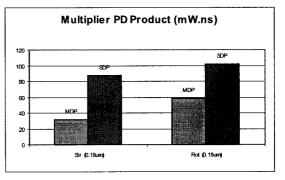

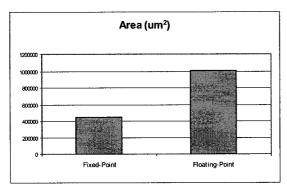

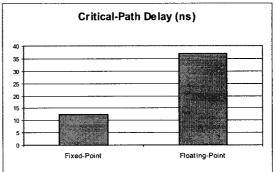

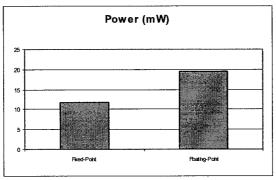

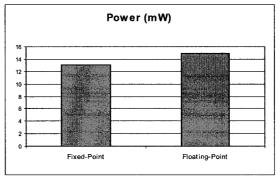

# 3.4 Floating-Point vs. Fixed-Point

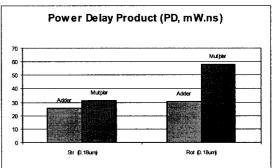

As we mentioned at the beginning of this chapter, the importance of the performance of multipliers outweigh significantly that of adders in the fixed-point domain. Under the same operating conditions, fixed-point and floating-point units have widely different performances. A typical fixed-point adder has an area around 13% that of a typical fixed-point multiplier while in the floating-point domain it is around 40% [Figure 3.15]. That is mainly due to the increased algorithm complexity of the floating-point addition.

The power performance sees a similar change when migrating from fixed-point to floating-point. In fixed-point, the power dissipation of the adder is around 16% that of the multiplier while in floating-point it is around 40% [Figure 3.16]. In fixed-point, the critical path delay of the adder is around 65% that of the multiplier while it is around 95% in floating-point [Figure 3.17].

Figure 3.15 Area Performance Figures of the Arithmetic Units

Multiple

Although migrating from fixed-point to floating-point arithmetic is generally accompanied by an increase in area, delay and power dissipation, the percentage increase differ significantly between adders and multipliers. The fixed-point adder is around 17% the floating-point's, has a critical path delay that is around 75% smaller and dissipates around 74% less power. The fixed-point multiplier, on the other hand, is more than half the size of the floating-point's. Its critical path delay is around 60% smaller but it dissipates only around 37% less power. The above is clearly illustrated in Figure 3.15, Figure 3.16 and Figure 3.17.

Figure 3.16 Power Performance Figures of the Arithmetic Units

Figure 3.17 Delay Performance Figures of the Arithmetic Units

#### 3.5 Conclusion

From the experiments performed on the floating-point arithmetic units, we can conclude that both, adder and multiplier, units are equally important in the floating-point domain. That is more visible for the MDP designs, where the adder is around 45% smaller in size than the multiplier and consumes less power by at most 64%. For SDP units the adder is 60% smaller than the multiplier and consumes less power by an average reaching 67% in 0.35 um technology and 64% in 0.18 um technology. Critical-path delays for the adder and the multiplier are very close for both MDP and SDP designs. The difference does not exceed 4% for MDP units and 10% for SDP units. Of interest is the fact that in some cases the MDP adder has a larger delay than the multiplier.

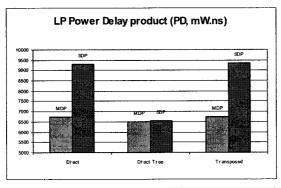

Another conclusion we can draw from the experiments performed on the floating-point arithmetic units. We can conclude that the multiple data path units have a definite advantage over their single data path counterparts. We see, from the results we have gathered, that the MDP units consume less power than the SDP units, and require less time to perform their function. They suffer, however, from increased area, especially in the case of the adder, which is around 1.5 times the size of its SDP counterpart. When considering the performance products (AT, AT<sup>2</sup> and PD) presented in Figure 3.18, Figure 3.19 and Figure 3.20, we find the MDP units to have a significant advantage over their SDP counterparts by a large percentage. This is true with both, 0.35 um and 0.18 um CMOS technologies. The result of the work presented in this section justifies revisiting some of the basic digital FIR and IIR filter architectures and reporting on their performance.

Figure 3.18 Average values of PD product for the FP units

Figure 3.19 Average values of AT product for the FP units

Figure 3.20 Average values of AT<sup>2</sup> product for the FP units

### 3.6 Summary

This chapter considered the difference in performance between adders and multipliers in the floating-point domain. We presented the different configurations in which the arithmetic units were evaluated. The data samples are also listed to avoid any future ambiguity. The results obtained for each of the configurations are presented in the form of tables and analysed. The conclusion of this chapter presents two points. First, both adders and multipliers are equally important in terms of power consumption, delay and area in the floating-point domain. The second point is that arithmetic units using transition activity scaling algorithm consume less power than other floating-point arithmetic units under the same operating conditions.

# Chapter 4

# Finite Impulse Response Filters

#### 4.1 Introduction

In DSP applications, filtering of data samples is a very demanding operation. With the help of widely available CAD tools and with a given set of filter specifications, an appropriate filter can rapidly be obtained. The wide dynamic range and higher accuracy of floating point arithmetic is attracting more and more signal processing applications to the floating point domain. This trend has become noticeable in recent years, with the advent of high speed floating point DSP integrated circuits. Advances in VLSI technology made it possible for even small computers to perform sophisticated floating point computations.

A filter transfer function can have different implementations without modifying the filter characteristics. In Chapter 2, we have seen that FIR filters can be implemented in Direct and Transposed forms while the filter transfer function remained the same. The memory requirement for the different realisations is not necessarily the same. In general, differences in realisations imply differences in performance as well. In this chapter we will consider the different FIR filters realisations discussed in Chapter 2. We will show how the different FIR filters network structures presented in Chapter 2 were modified to accommodate the pipe-lined floating-point arithmetic units. A comparative study of area, delay and power consumption performance of the different realisations is discussed in this chapter. In this chapter, we attempt to realise several implementations of the same filter and quantify their performance with the objective of classifying them in accordance with their performance.

The rest of this chapter is organized in the following manner. Section 4.2 presents an area, delay and power performance evaluation of three standard FIR filter network structures. Section 4.3 presents an area, delay and power performance evaluation of three pipe-lined FIR filter realisations and shows how they were derived from the structures presented in Section 4.2. Section 4.3 also presents the experimental approach used to simulate and synthesize the different designs along with analyses of the results. Section 4.5 draws conclusions from the results while Section 4.6 presents a summary for this chapter.

#### 4.2 Standard FIR Filter Network Structures