## AN OPERATING SYSTEM FOR COMPUTER CONTROLLED LOGIC PRINTED CIRCUIT BOARD TESTING

PETER H. TRAU, Eng.

A THESIS

in

The Faculty

of

Engineering

Presented in Partial Fulfillment of the Requirements for

the Degree of Master of Engineering at

Sir George Williams University

Montreal, Canada

March, 1972

#### ACKNOWLEDGMENTS

The author wishes to thank the following individuals for their invaluable help:

- Dr. W. M. Jaworski of Sir George Williams University consented to act as the author's advisor and provided many helpful suggestions on the scope and subjectmatter of this thesis.

- Mr. R. E. Enos, Eng., is the author's department manager at the Northern Electric Co., and gave the author a task which ultimately resulted in this paper. He also provided valuable guidance.

- Mr. F. Benedetti, Eng., of the Northern Electric Co., designed the interface and testset of the logic test system, and offered much help on hardware considerations.

- Mr. E. Beneteau of the Northern Electric Co. is the author of the translator program and cooperated closely with the author in implementing the software system.

## CONTENTS

| ACKNOWLEDGMENTS                                      | ii |

|------------------------------------------------------|----|

| FIGURES v                                            | ii |

| FLOWCHARTS vi                                        | ii |

| CHARTS                                               | ix |

| TABLES                                               | ix |

| 1. INTRODUCTION                                      | 1  |

| 2. TESTING LOGIC CIRCUITS                            | 4  |

| 2.1 LOGIC DEVICES                                    | 4  |

| 2.1.1 Example: SN7407 HEX BUFFER/DRIVERS with open   |    |

| collector high-voltage outputs                       | 5  |

| 2.1.2 Example: SL-6-4025 MTNS QUAD 25-BIT STATIC     |    |

| SHIFT REGISTER                                       | 6  |

| 2.1.3 Testing TTL Integrated Circuits                | 8  |

| 2.2 LOGIC CIRCUIT BOARDS                             | 9  |

| 2.2.1 Physical Characteristics                       | 9  |

| 2.2.2 Possible Failures on a Printed Circuit Board . | 10 |

| 2.3 LOGIC CIRCUIT ANALYSIS                           | 12 |

| 2.3.1 Analysis From a Logic Function Point of View . | 12 |

| 2.3.2 Analysis From a Logic Device Point of View     | 13 |

| 2.3.3 Analysis From a Random Error Point of View     | 13 |

| 2.4 TRUTHTABLE GENERATION                            | 14 |

| 2.5 SOFTWARE IMPLEMENTATION                          | 16 |

| 2.6 ERROR DETECTION AND CORRECTION                   | 17 |

| 3. TEST SYSTEM HARDWARE                              | 19 |

| 3.1 THE PDP-15/20 COMPUTER                           | 19 |

| 3.1.1 Central Processor Description                  | 20 |

| 3.1.2 Memory Organization                            | 23 |

|     | 3.1.3 The Input/Output Processor                     |

|-----|------------------------------------------------------|

|     | 3.2 THE INTERFACE 25                                 |

|     | 3.3 THE TEST STATION 26                              |

| 4.  | TEST SYSTEM SOFTWARE 29                              |

|     | 4.1 THE SOURCE TEST PROGRAM                          |

|     | 4.2 THE TRANSLATOR 30                                |

| . • | 4.3 THE OPERATING SYSTEM 30                          |

|     | 4.4 THE UTILITY PROGRAMS                             |

| 5.  | OPERATING SYSTEM SOFTWARE 33                         |

|     | 5.1 OPERATING SYSTEM ORGANIZATION 34                 |

|     | 5.2 OPERATING SYSTEM INITIALIZATION AND START 36     |

|     | 5.3 KEYBOARD MONITOR AND COMMAND REPERTOIRE 39       |

|     | 5.3.1 Keyboard Wait Loop 40                          |

|     | 5.3.2 Data Mode Commands 42                          |

|     | 5.3.3 Biasing Mode Command 43                        |

|     | 5.3.4 Testing Modes 44                               |

|     | 5.3.5 Test Initiation Command "Start" 45             |

|     | 5.3.6 Test Initiation Command "Continue" 47          |

|     | 5.3.7 "Partial Test" and "Looping" 47                |

|     | 5.3.8 "Repeat Current Line" and "Repeat Sequence" 50 |

|     | 5.3.9 The Step Mode 50                               |

|     | 5.3.10 Test Program Verification 52                  |

|     | 5.3.11 Housekeeping Commands 57                      |

|     | 5.4 ELEMENTARY FUNCTIONS AND FUNCTIONAL TEST         |

|     | ROUTINES 57                                          |

|     | 5.4.1 FTR 4: Full Address Word 59                    |

|     | 5.4.2 FTR 5: Partial Address Word                    |

|     |                                                      |

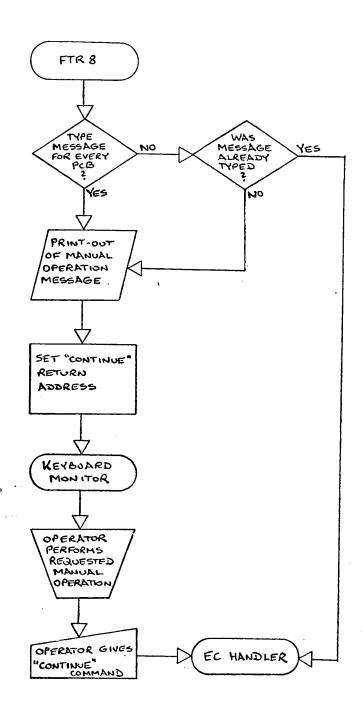

|    | 5.4.3 FTR 8: Manual Operation 64                        |

|----|---------------------------------------------------------|

|    | 5.4.4 FTR 9: Wait                                       |

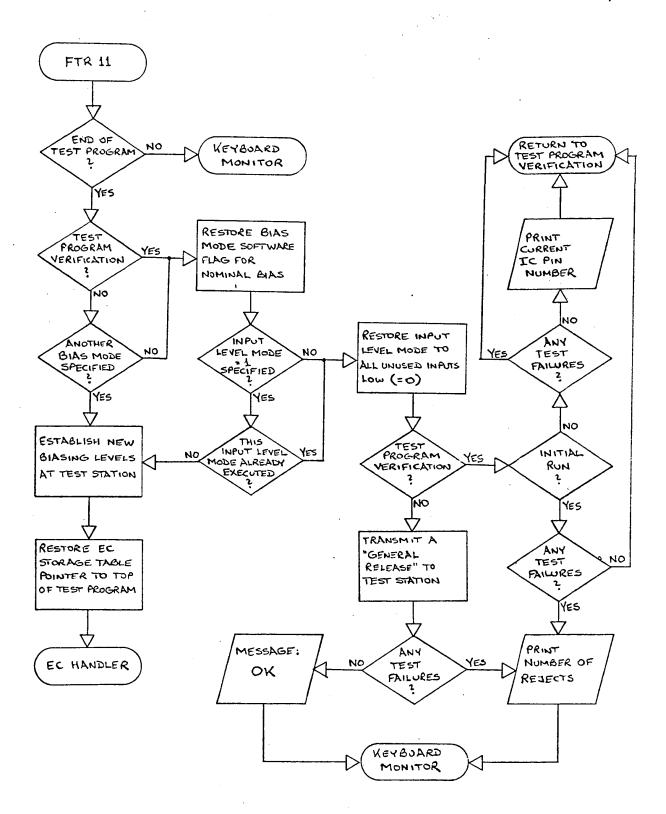

|    | 5.4.5 FTR 11: General Release; End                      |

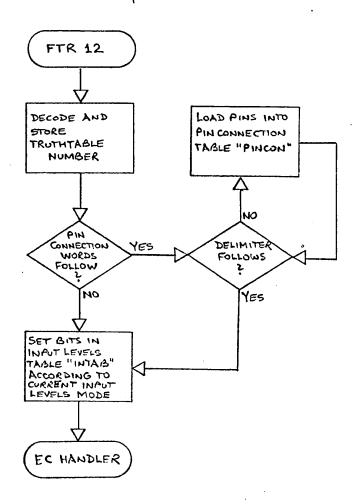

|    | 5.4.6 FTR 12: Pin Connection Table; Truthtable          |

|    | Number 71                                               |

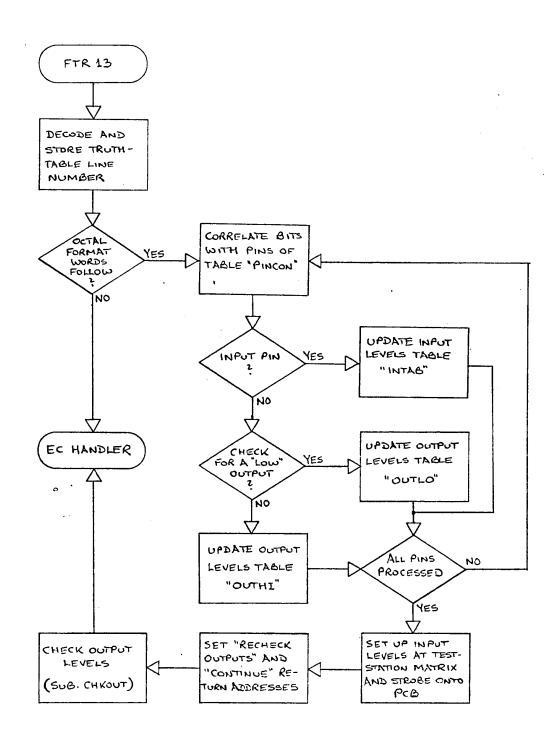

|    | 5.4.7 FTR 13: Octal Format; Truthtable Line Number . 74 |

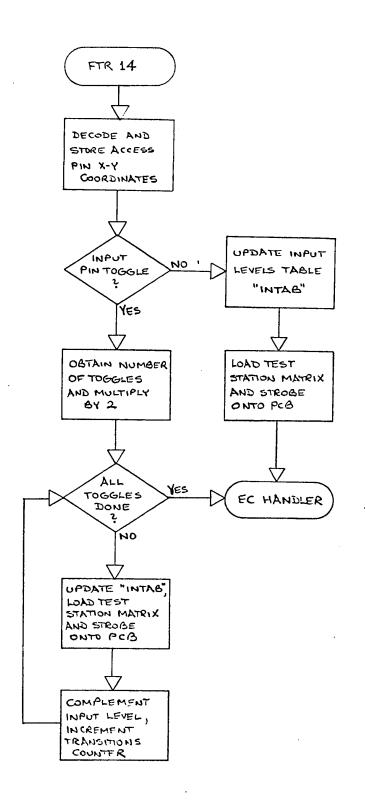

| •  | 5.4.8 FTR 14: Input Pin Toggle; Sequential Input        |

|    | Setting 74                                              |

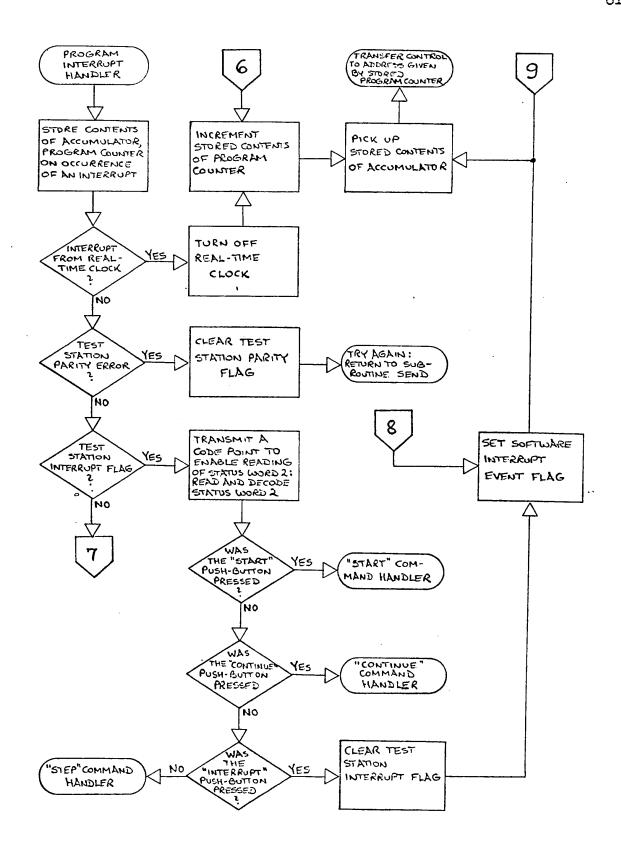

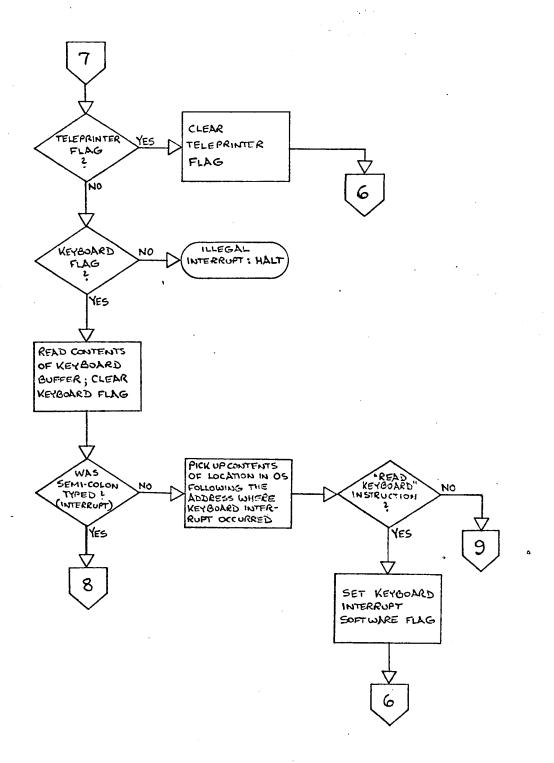

|    | 5.5 PROGRAM INTERRUPT HANDLER 79                        |

|    | 5.6 UTILITY SUBROUTINES 83                              |

|    | 5.6.1 Biasing Group Subroutines 84                      |

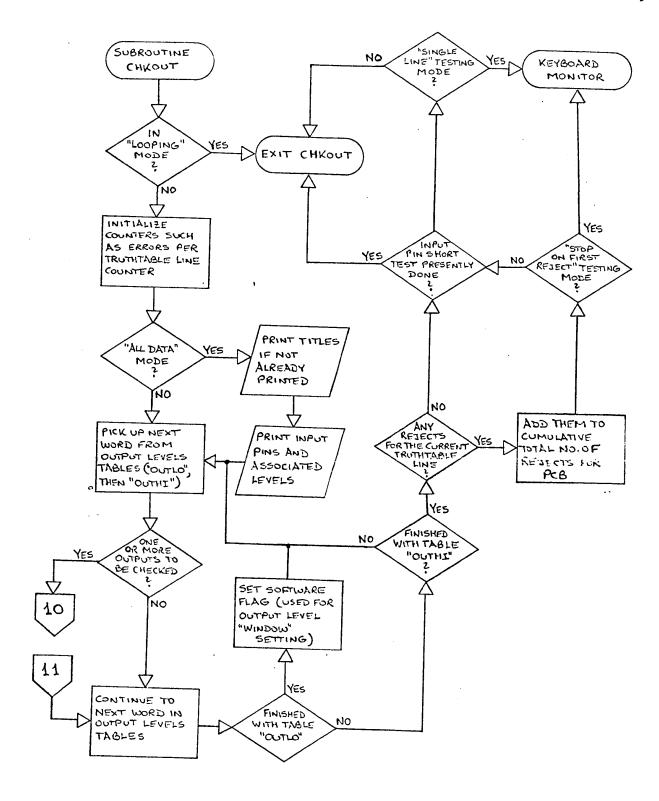

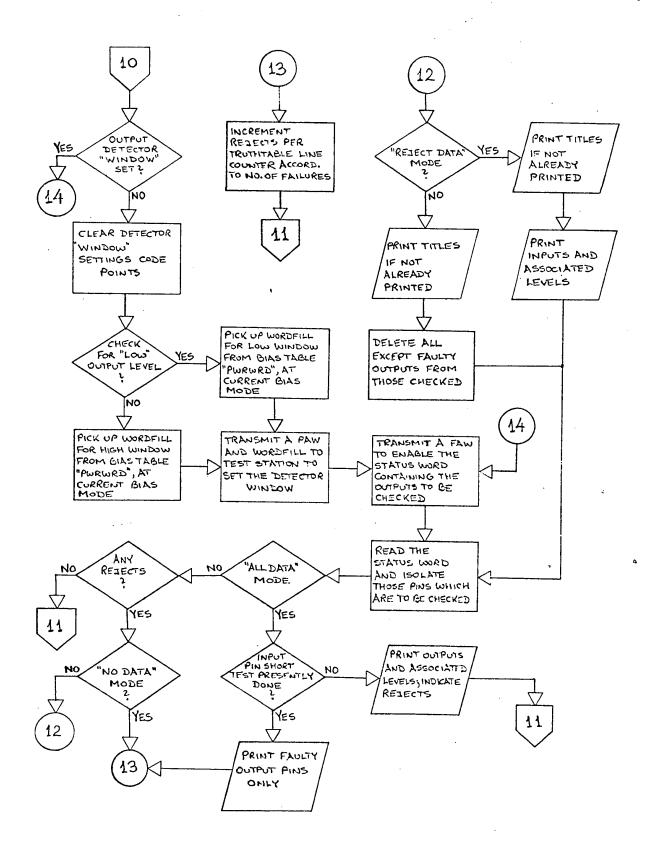

|    | 5.6.2 Output Levels Checking 87                         |

|    | 5.6.3 Input Levels Modifications 91                     |

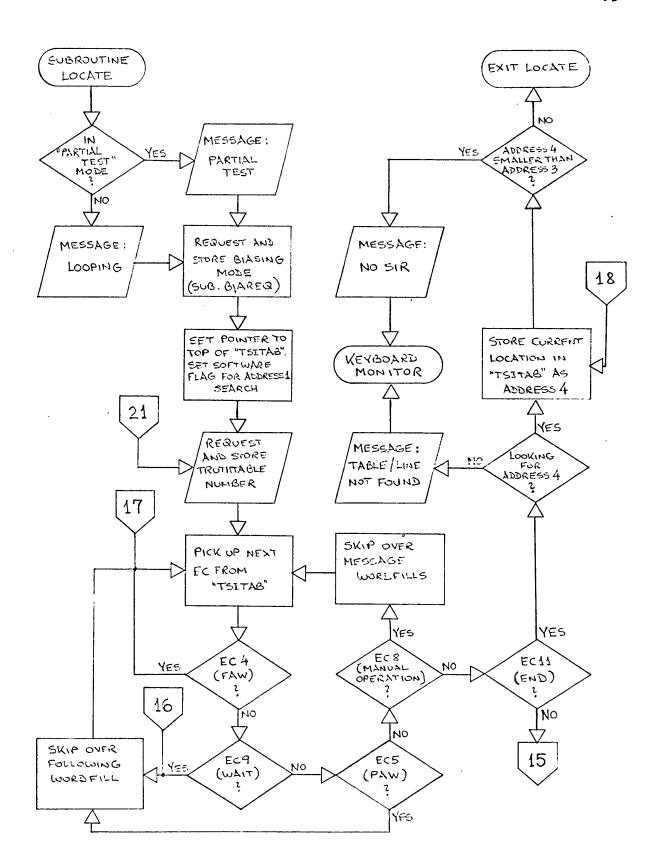

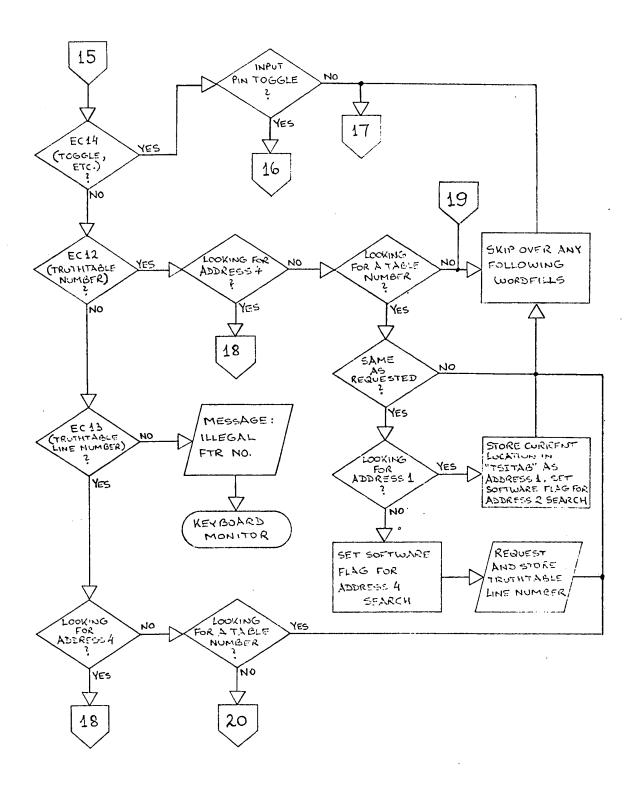

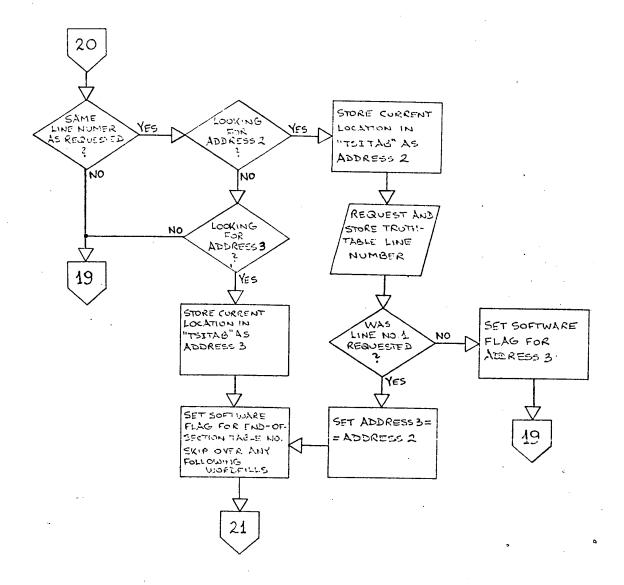

|    | 5.6.4 Partial Testing Boundaries Location 92            |

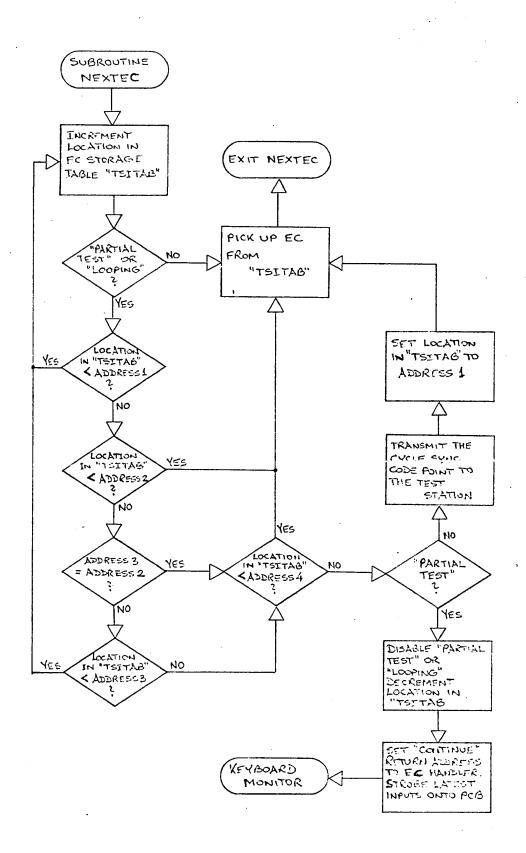

|    | 5.6.5 Next EC                                           |

|    | 5.6.6 Keyboard Reading and Character Packing Group . 96 |

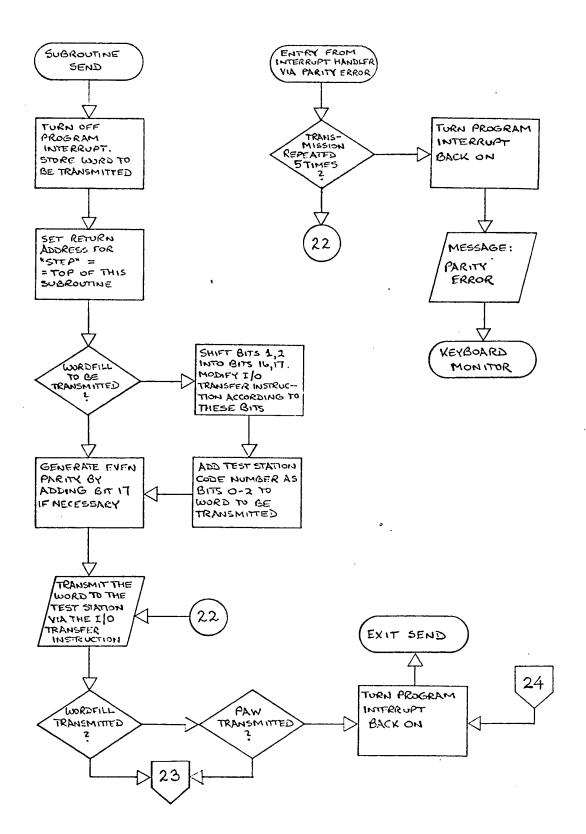

|    | 5.6.7 Transmission to Test Station 98                   |

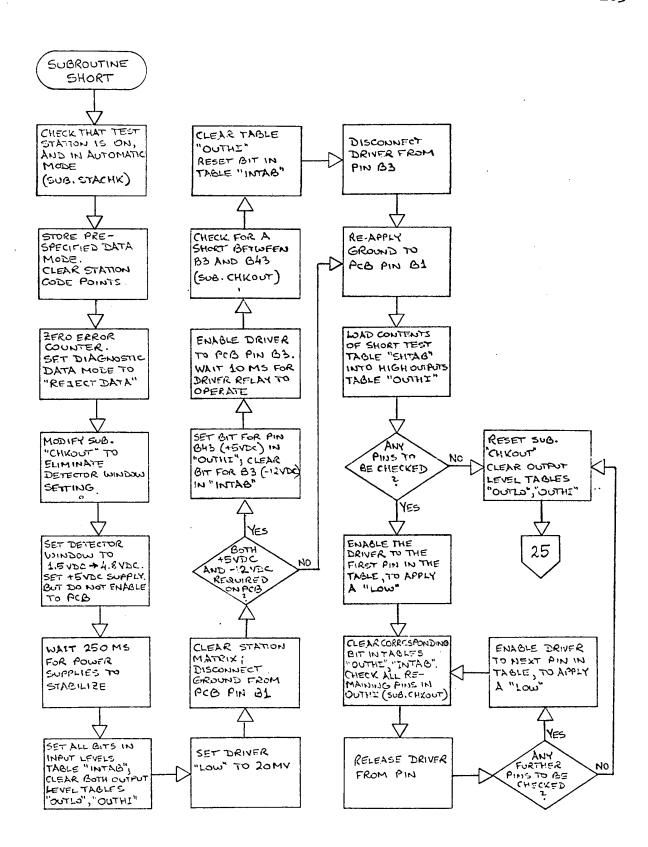

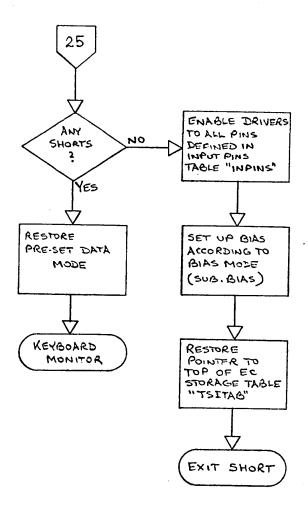

|    | 5.6.8 Input Pin Short Test                              |

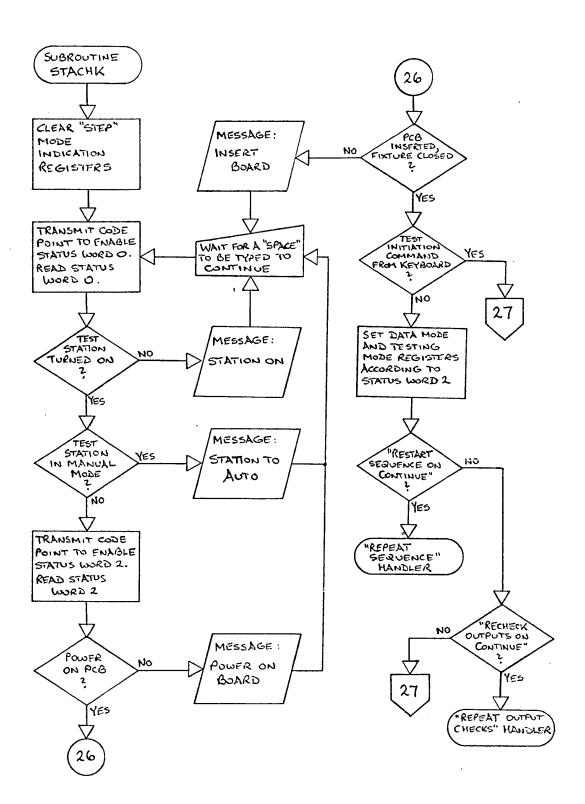

|    | 5.6.9 Station Status Check 105                          |

|    | 5.6.10 Type-out Group                                   |

| 6. | OPERATOR'S MANUAL                                       |

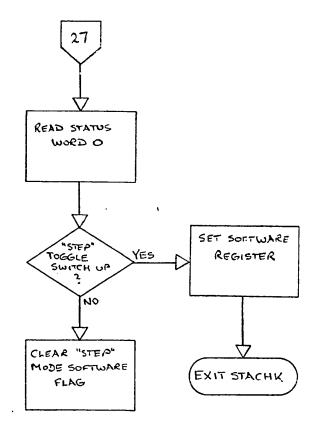

|    | 6.1 OPERATING SYSTEM INITIALIZATION AND START 112       |

|    | 6.2 AVAILABLE OPERATOR COMMANDS                         |

|    | 6.2.1 Mode Commands                                     |

|    | 6.2.2 Test Initiation Commands                          |

|    | 6.2.3 Miscellaneous Commands 128                        |

|    | 6.2.4 Command Combinations                              |

•••

| 6.3 TESTING AND TROUBLESHOOTING TECHNIQUES 130             |

|------------------------------------------------------------|

| 6.3.1 Test Program Prove-in                                |

| 6.3.2 Sorting of PCB's                                     |

| 6.3.3 Troubleshooting                                      |

| 7. A SAMPLE TEST PROGRAM                                   |

| 7.1 CIRCUIT UNDER TEST 133                                 |

| 7.2 TESTING TRUTHTABLES 136                                |

| 7.3 SOURCE TEST PROGRAM 138                                |

| 7.4 TRANSLATOR OUTPUT 142                                  |

| 7.5 TEST RESULTS 146                                       |

| 7.5.1 Translation; Initial Run 146                         |

| 7.5.2 Diagnostic Output Listings 148                       |

| 7.5.3 Partial Testing                                      |

| 7.5.4 Short Test and Miscellaneous Error                   |

| Diagnostics 154                                            |

| 7.5.5 Test Program Verification                            |

| 8. CONCLUSIONS                                             |

| APPENDIX A: OPERATING SYSTEM SOURCE PROGRAM LISTINGS . 160 |

| APPENDIX B: 8-BIT AND TRIMMED 6-BIT ASCII CODES 209        |

| LIST OF ABBREVIATIONS 212                                  |

| REFERENCES 213                                             |

## FIGURES

| 2.1 SN7407 Circuit Schematic (each buffer/driver   | r) 5    |

|----------------------------------------------------|---------|

| 2.2 SN7407 Dual-In-Line package (Top View)         | 6       |

| 2.3 SL-6-4025 Logic Diagram and Input/Output       |         |

| Relationship                                       | 7       |

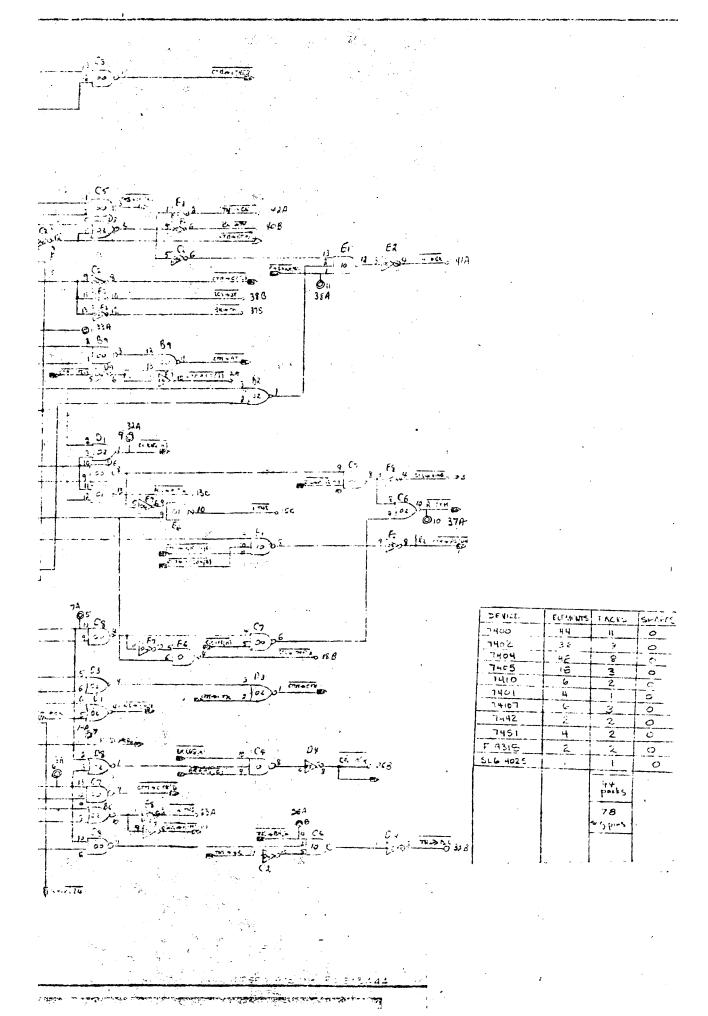

| 3.1 Simplified Block Diagram of PDP- 15 CPU        | 22      |

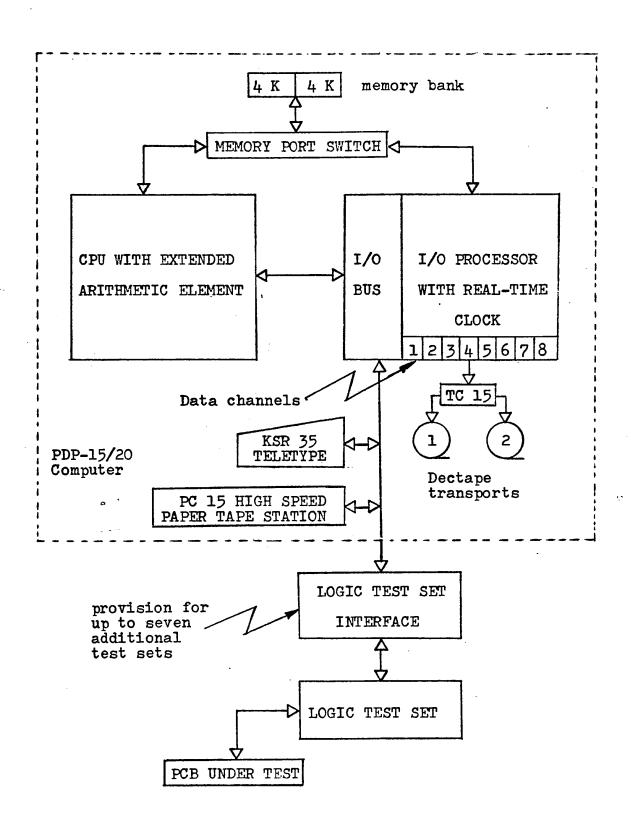

| 3.2 Block Diagram of the Logic Test System         | 28      |

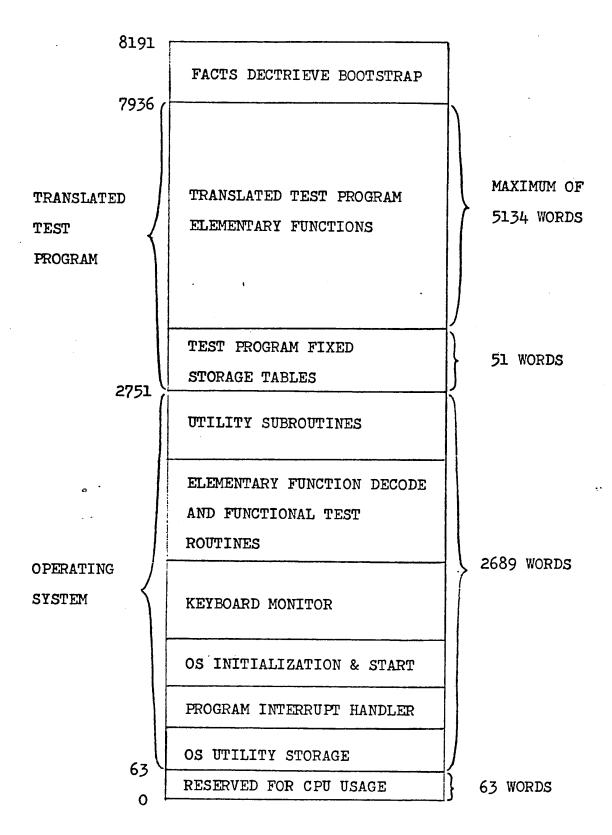

| 5.1 Operating System Core Allocation               | 35      |

| 5.2 EC 4 and FAW Bit Assignments                   | 60      |

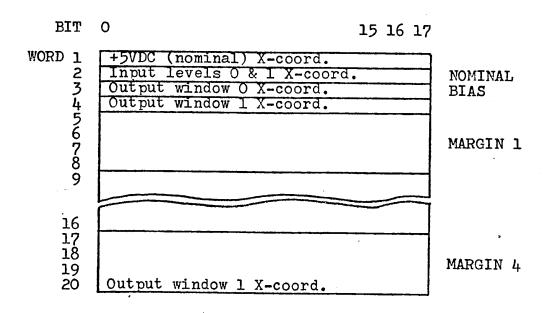

| 5.3 Input and Output Levels Tables                 | 63      |

| 5.4 EC 5, Wordfill and PAW Bit Assignments         | 65      |

| 5.5 EC 8 and Wordfills Bit Assignments             | 66      |

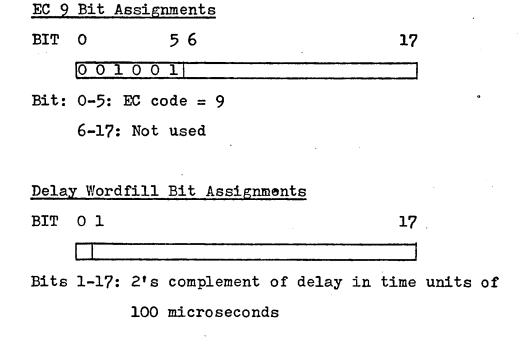

| 5.6 EC 9 and Delay Wordfill Bit Assignments        | 68      |

| 5.7 EC 11 Bit Assignments                          | 69      |

| 5.8 EC 12, Pin Connection Table and Definition V   | Vord 73 |

| 5.9 EC 13 and Octal Format Word Bit Assignments    | ••• 75  |

| 5.10 EC 14 and Toggles Word Bit Assignments        | 77      |

| 5.11 Biasing Table "PWRWRD"                        | 86      |

| 5.12 Status Word O (Station Status) Bit Assignment | ents 87 |

| 5.13 Input Format to Subroutine SEND               | •••• 99 |

| 5.14 Input Pins Table "INPINS" and Input Pin Sho   | ort     |

| Test Table "SHTAB" Bit Assignments                 | 105     |

| 5.15 Status Word 2 Bit Assignments                 | 108     |

| 6.1 IC Pin Definition for Test Program Verificat   | ion 124 |

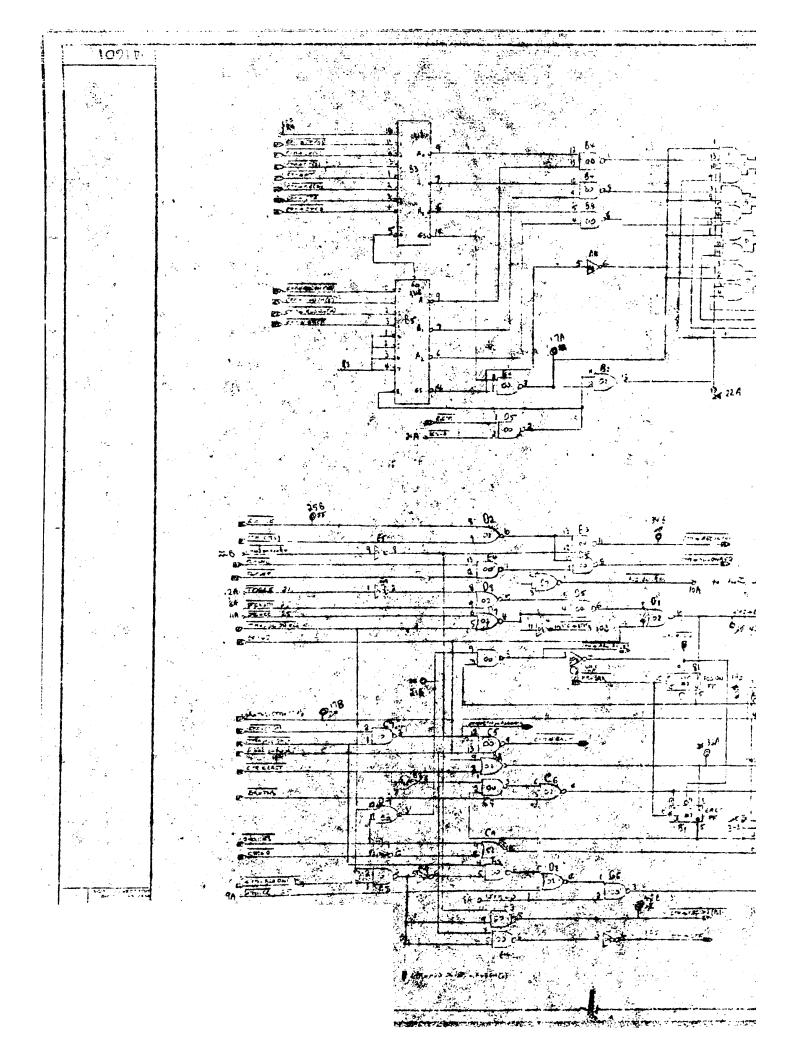

| Circuit Under Test Schematic                       | 134     |

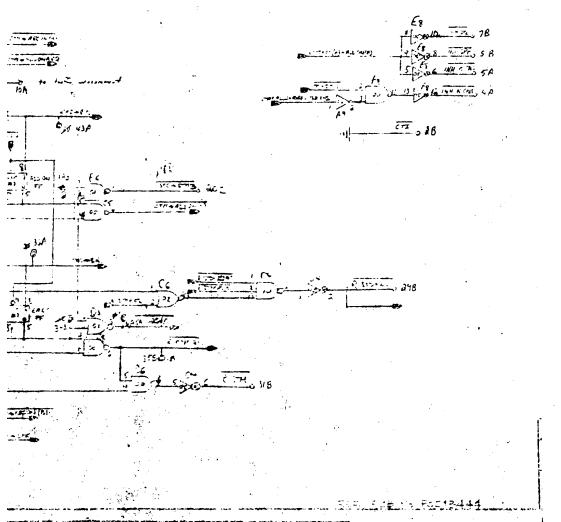

| Testing Truthtable                                 | 137     |

## FLOWCHARTS

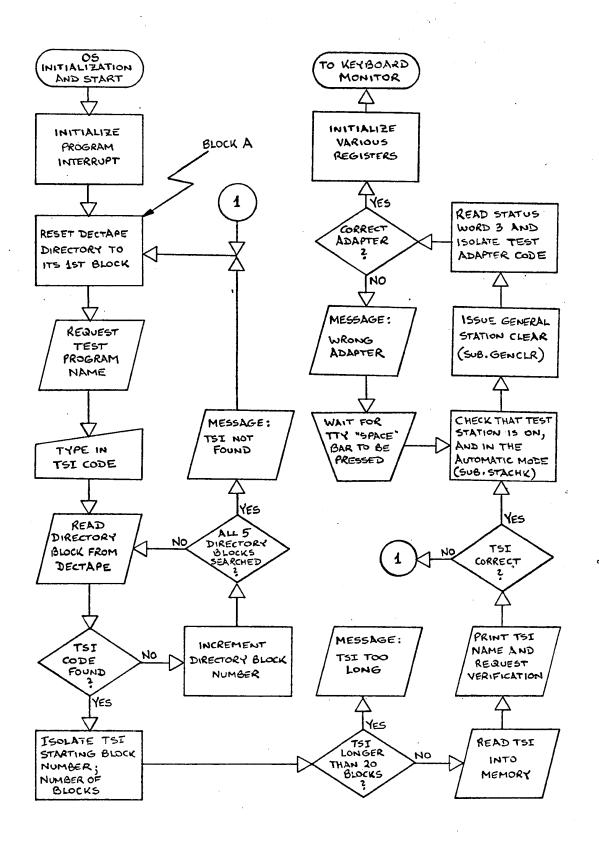

| 5.1          | OS Initialization and Start 38                      |

|--------------|-----------------------------------------------------|

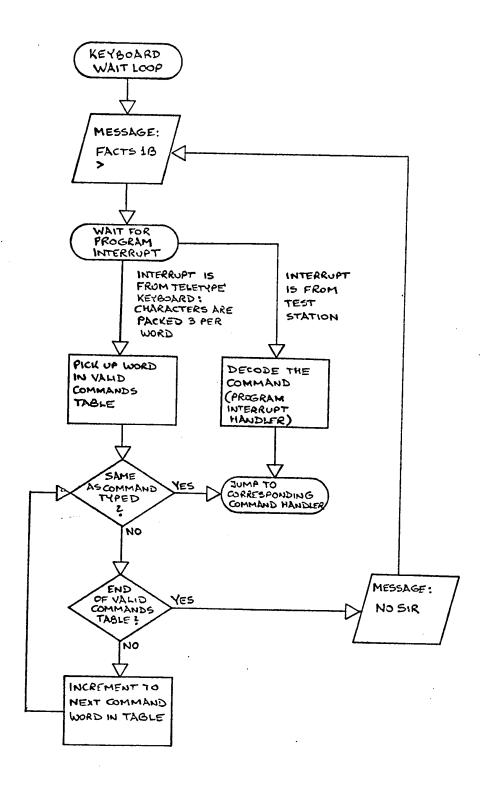

| 5.2          | Keyboard Wait Loop 41                               |

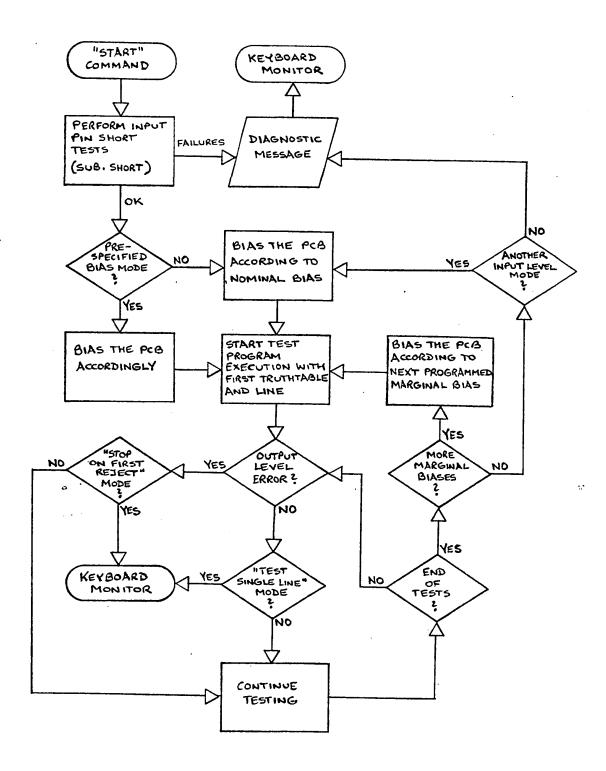

| 5 <b>.</b> 3 | Testing Under The "Start" Command 46                |

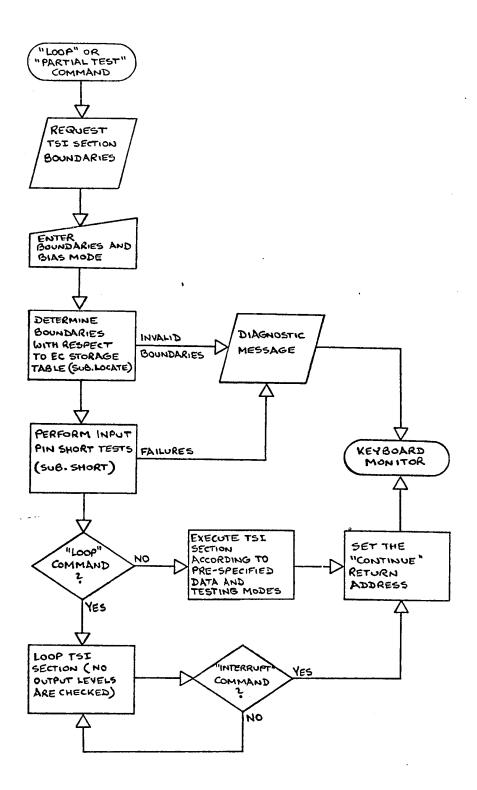

| 5.4          | Testing Under "Loop" or "Partial Test" 49           |

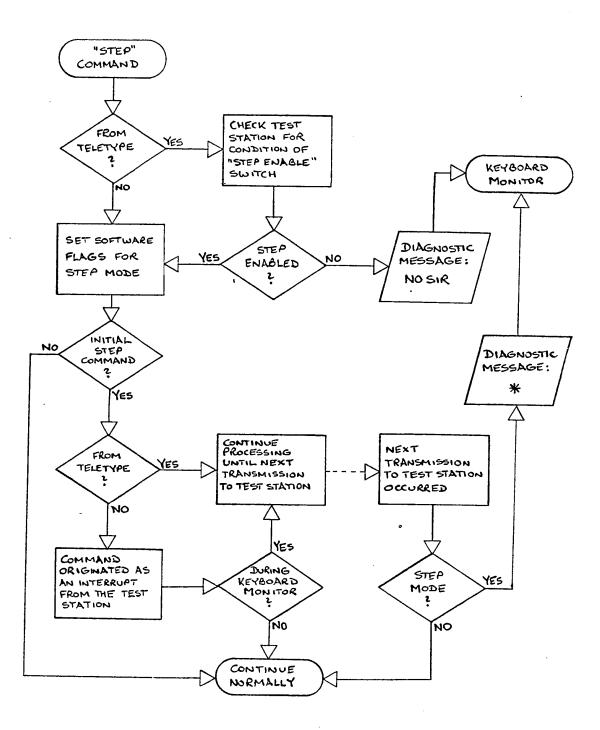

| 5.5          | Step Mode 51                                        |

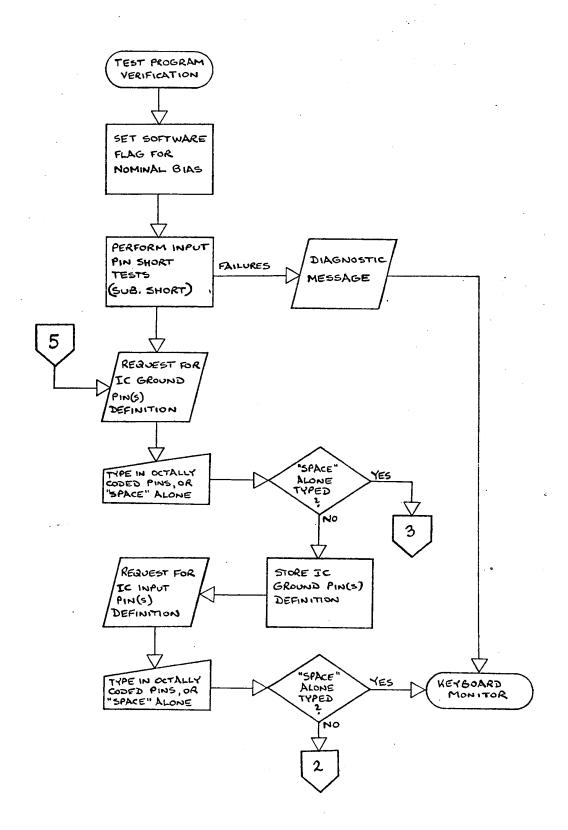

| 5.6          | Test Program Verification 54                        |

| 5.7          | EC Handler 58                                       |

| 5.8          | FTR 4 (Full Address Word)                           |

| 5.9          | FTR 8 (Manual Operation) 67                         |

| 5.10         | FTR 11 (General Release; End) 70                    |

| 5.11         | FTR 12 (Pin Connection Table; Truthtable Number) 72 |

| 5.12         | 76                                                  |

| 5.13         | FTR 14 (Input Pin Toggle; Sequential Input          |

|              | Setting) 78                                         |

| -5.14        |                                                     |

| 5.15         | 80                                                  |

| 5.16         | 07                                                  |

| 5.17         | Subroutine "NEXTEC" 97                              |

| 5.18         | 100                                                 |

| 5.19         | 107                                                 |

| 5.20         | 106                                                 |

## CHARTS

| 6.1 | Loading the Operating System                | 114 |

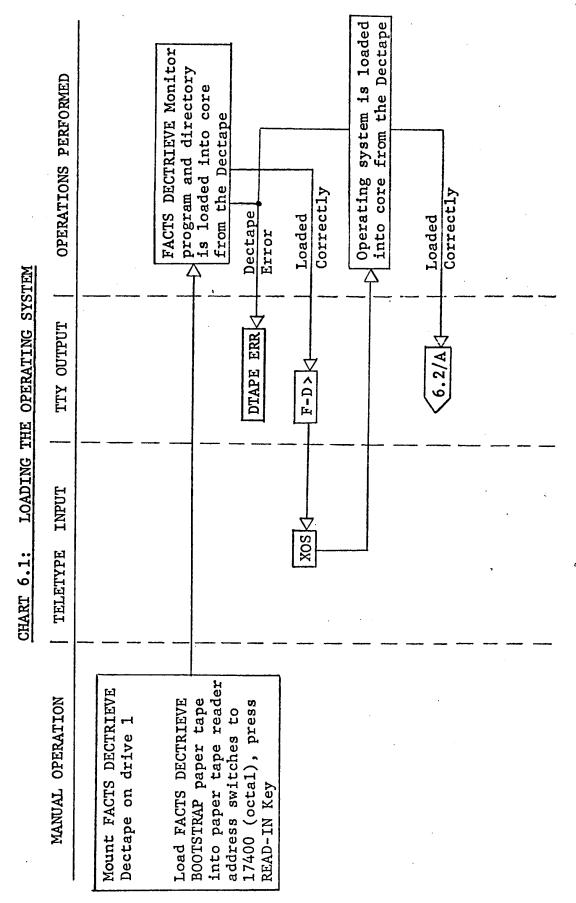

|-----|---------------------------------------------|-----|

| 6.2 | OS Start; Test Program Loading              | 115 |

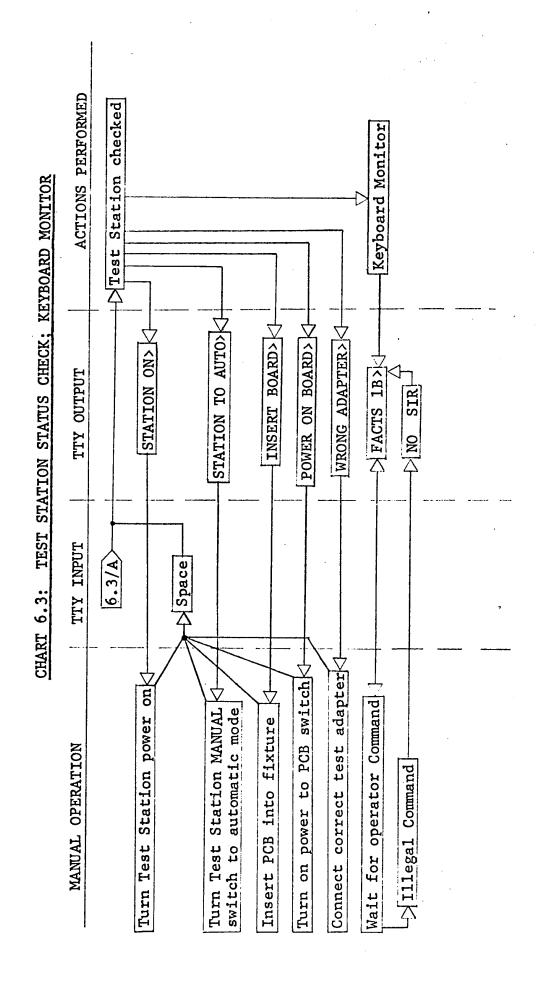

| 6.3 | Test Station Status Check; Keyboard Monitor | 116 |

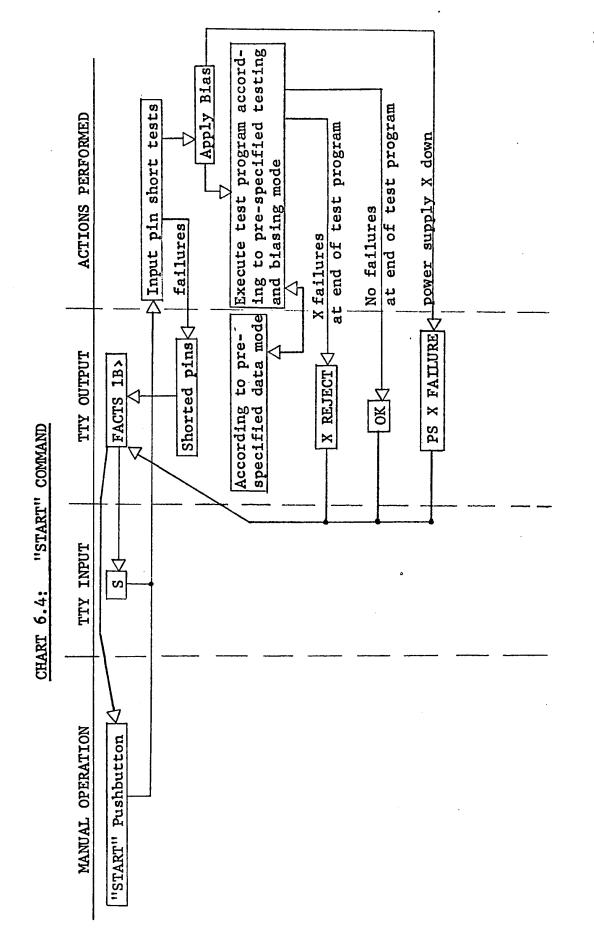

| 6.4 | "Start" Command                             | 125 |

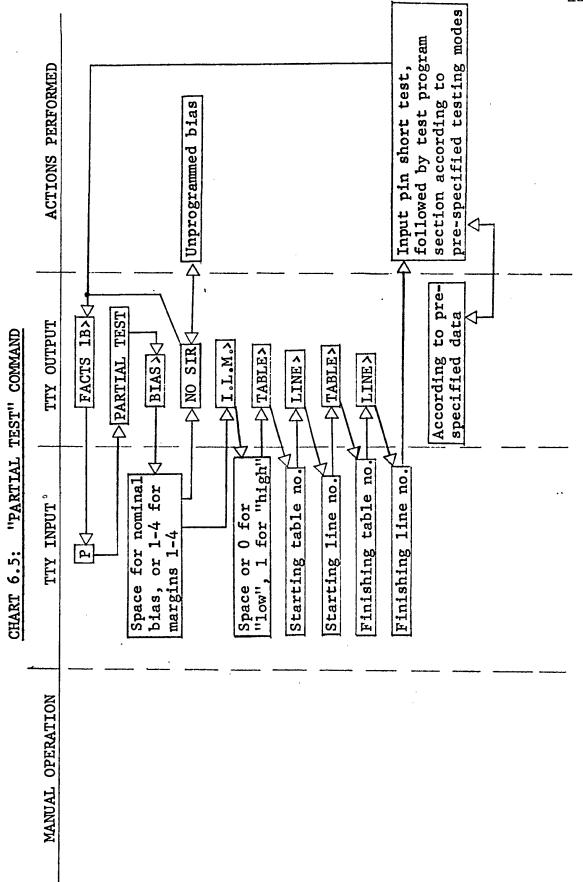

| 6.5 | "Partial Test" Command                      | 126 |

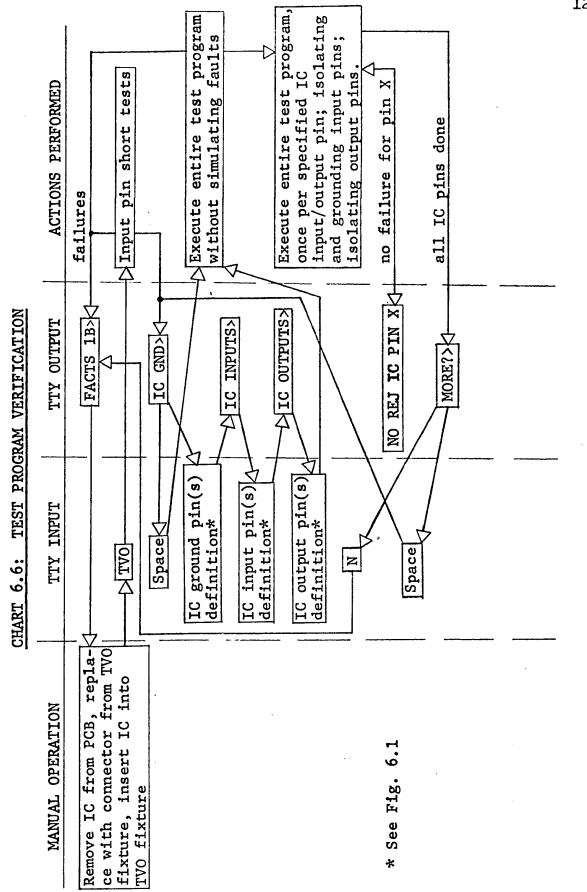

| 6.6 | Test Program Verification                   | 127 |

|     |                                             |     |

|     |                                             |     |

|     |                                             |     |

|     | <u>TABLES</u>                               |     |

|     | •                                           |     |

| 6.1 | Data Mode Commands                          | 119 |

| 6.2 | Testing Mode Commands                       | 120 |

| 6.3 | Test Initiation Commands                    | 122 |

| 6.4 | Miscellaneous Commands                      | 128 |

| 6.5 | Summary of Commands and their Combinations  | 129 |

# SIR GEORGE WILLIAMS UNIVERSITY FACULTY OF ENGINEERING GRADUATE STUDIES RESEARCH THESIS

by

PETER H. TRAU, Eng.

entitled

AN OPERATING SYSTEM FOR COMPUTER CONTROLLED

LOGIC PRINTED CIRCUIT BOARD TESTING

#### ABSTRACT

An Operating System for a computer controlled logic printed circuit board test system is presented. This Assembler language program was developed by the author for a Northern Electric Co. designed manufacturing test facility, consisting of a Digital Equipment Corporation PDP-15/20 computer, and an interface and testset built by the Northern Electric Co. It tests logic printed circuit boards containing up to 45 integrated circuits, according to stored test programs. The Operating System decodes the test programs and controls the testset. An extensive command repertoire is provided to facilitate error location and correction. This test system has been successfully used to test over 25 different logic printed circuit board codes.

#### CHAPTER 1

#### INTRODUCTION

Northern Electric Co. Ltd., the author's employer, conducts a significant part of its business in the design and manufacture of electronic switching systems. All recent designs employ DTL and TTL Integrated Circuits, currently up to medium scale integration on devices such as encoders, decoders, converters and shift registers.

The logic devices and associated circuit components are mounted on printed circuit boards, of double-sided design, with 86 access terminals (43 to a side) on one edge of the board, and containing up to 45 IC's. This quantity allows for major logic functions, or multiple identical functions, to appear on a single circuit board. It also results in high printed circuit path densities with minimum path-to-path seperations of one ten-thousands of an inch.

It is of course necessary to test such logic circuit boards. Whereas binary logic is simpler to check than an analog electronic circuit of similar device density - that is if one omits rise, fall, and delay time measurements for the logic circuit - the aforementioned logic device densities result in extremely large numbers of tests. Hence arises the need for automatic testing facilities. Furthermore, since there exist a large number of different circuits, the best solution to the testing problem lies in a digital computer controlled automatic test system. This can operate under stored-program control, and can thus check different circuits according to different test programs.

Employing this philosophy the Northern Electric Co. designed such an automatic test system. It consists of a Digital Equipment Corporation PDP-15/20 Computer, which was purchased, and a logic testset connected to the computer via an interface, both of the latter designed and built by the Northern Electric Co. The author's task was to develop an Operating System for this facility. This Operating System should load and decode test programs, and control the testset accordingly. It should also facilitate the on-line debugging of faulty logic circuits.

The following chapters of this paper, which deals primarily with software, will include some hardware description of the test system. Due to confidentiality considerations these will necessarily be sketchy since the author was granted permission to publish only the Operating System. The philosophy employed in testing logic circuits will be discussed to give the reader more perspective over the requirements of the Operating System, but it should be stated that this philosophy was well established in the Company when this testing system was designed. Hence any of the Author's ingenuity was restricted to maximizing the versatility of the Operating System within the constraints expressed in the test system hardware.

While this Sytem was specifically designed to test logic circuits for SG-l EPBX, an electronic PBX (Private Branch Exchange) system newly developed by Bell-Northern Research, and the Northern Electric Co., as a stand-alone unit, its hardware was designed to be compatible with other

existing testsets. This was done with the intent of an eventual time-shared test system, capable of operating concurrently up to seven seperate testsets via one computer. This concept, which is now in the software design state, determined the overall software philosophy of the test system, adding further constraint on the Operating System. It will be possible, if so desired, to include this test system in a time-sharing configuration, without hardware changes, and with relatively minor software modifications.

Along with this introduction, chapters 2, 3, and 4 are meant essentially as preambles to the Operating System. Chapter 2 will deal with logic devices and circuit boards, and why they have to be tested. It presents the 'raison d'être' for the test system. Chapter 3 presents a brief description of the test system hardware, consisting of the computer, the interface, and the actual testset. Chapter 4 deals with the entire test system software, of which the Operating System is but a part. The Operating System software is finally discussed in Chapter 5. Chapter 6 is titled Operator's Manual and describes the Operating System usage from an operator's point of view. Part of an actual test program is presented in Chapter 7, along with a representative sample of computer input and output during the testing process.

## CHAPTER 2 TESTING LOGIC CIRCUITS

The test system described in this paper was designed to test and trouble-shoot logic circuit boards. The following sections will describe the logic devices and circuit boards, give some of the reasons for testing them, and detail the steps necessary to generate an automatic testing procedure for a logic circuit.

#### 2.1 LOGIC DEVICES

We are dealing here exclusively with binary logic devices existing, as the name implies, in one or the other of two possible states. Furthermore these devices operate in a positive Pogic mode. Hence their "level O", "low", or "off" state is characterized by an output voltage near ground (O VDC), whereas their "level 1", "high", or "on" state results in an output voltage typically above +2 VDC.

While this test system is capable of testing any positive logic device or circuit, given certain restrictions explained in the following chapters, it was specifically designed for logic circuits comprised of TTL (transistor-transistor logic) or TTL-compatible IC's, of which two examples follow. These IC's require a +5 VDC positive bias and in certain cases an additional -12 VDC negative bias. One IC pin supplies a return to ground. The devices have 14 or 16 access pins generally in a dual-in-line package.

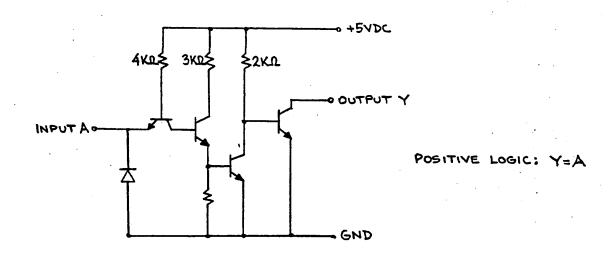

## 2.1.1 Example: SN7407 HEX BUFFER/DRIVERS with open-collector high-voltage outputs (1)

### FIGURE 2.1: SN7407 Circuit Schematic (each buffer/driver)

These monolithic TTL hex buffers/drivers feature high voltage open collector outputs for interfacing with high-level circuits (such as MOS), or for driving high-current loads (such as lamps or relays), and are also characterized for use as buffers for driving TTL inputs. For increased fanout, several buffers in a single package may be paralleled.

Some of the electrical characteristics of this device are:

Supply voltage Vcc: +15 VDC max.

Low level output voltage Vol: 0.4 - 0.7 VDC according to load.

Low level sinking current Iol: 40 mA max.

Propagation delay time, low-to-high level output, at

nominal bias, 110 onm load: 17 - 26 ns (Turn-off time). Similarily, turn-on time: 10 - 15 ns.

FIGURE 2.2: SN7407 Dual-In-Line Package (Top View)

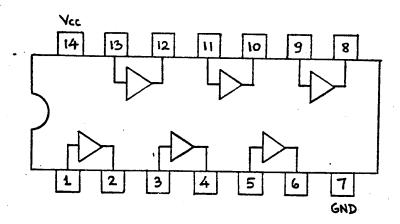

## 2.1.2 Example: SL-6-4025 MTNS QUAD 25-BIT STATIC SHIFT REGISTER (2)

This is a static shift register belonging to a standard family of DTL/TTL/MOS compatible registers which are constructed using low threshold silicon nitride passivated P-channel enhancement mode Field Effect Transistors.

Each register has one serial input and one serial output, and the clock input is common to the four registers. all inputs, including clock, can be driven directly from DTL/TTL logic levels, and each output can directly drive DTL/TTL without external interfacing components.

Data is read into each register when the clock input is at a logic O and is read out following the positive going (O - 1) clock transition. Data can be stored indefinitely

in the register with the clock held in either logic state.

Since this device is TTL compatible from a "black box" point of view, its biasing and input/output level characteristics are similar to the TTL device described in the previous section. The only major difference with TTL logic is the additional requirement of a -12 VDC bias, necessitated by the Metal Thick Oxide Nitride Silicon (MTNS) process employed in the device's manufacture.

FIGURE 2.3: SL-6-4025 Logic Diagram and Input/Output

Relationship

#### 2.1.3 Testing TTL Integrated Circuits

A manufacturer selling TTL IC's provides his customers with specification sheets detailing the device's parameters which should be met under specific test set-ups. Broadly speaking, these are:

- (a) Switching speeds

- (b) Noise immunity

- (c) Steady-state input/output characteristics as affected by temperature and DC-bias variations, and loading variations.

The manufacturer then guarantees a certain maximum percentage of faulty devices, say 1%.

To guarantee perfectly functioning components before inserting them into printed circuit boards would, because of large volume, require an automatic test set-up for IC's to measure the above parameters. This would necessitate a large capital expense due to the sophisticated hardware required to automatically check switching speeds and noise immunity. Furthermore, since assembled printed circuit boards will have to be tested also, due to reasons which will be outlined in section 2.2.2, and since it is impractical to test switching speeds and noise immunity on a circuit board basis, two different and expensive testsets are required. Considering then the IC manufacturer's guarantee of 1% rejects, it is sufficient to concentrate on testing circuit boards, and only check IC's on a sample basis which can make do with manually operated facilities.

When checked as part of a logic function on a circuit board individual IC's are checked for correct steady-state input/output characteristics under fixed loads, current ambient temperature, but, if required, under varying DC-bias and input level conditions. This corresponds to the margin testing feature which will be described in the following chapters.

#### 2.2 LOGIC CIRCUIT BOARDS

The term "logic circuit boards" describes printed circuit boards containing logic devices (although there may also be some devices performing analog functions), which form part of, or entire, logic functions. As a logic system is partitioned onto individual circuit boards it may not always be possible to include entire discrete logic functions on a single board. Hence such boards contain incomplete parts of logic functions which may or may not result in seperate identifiable functions. Also, as was already stated, there may be analog circuit components on part of the circuit board, resulting in hybrid circuits. The varied portions may feed each other, resulting in logic inputs and analog outputs, or vice-versa.

## 2.2.1 Physical Characteristics

The type of printed circuit board (PCB) employed in the SG-1 EPBX system is double-sided, with printed circuit paths running north-south on one side, and east-west on the other

side of the board. There are 86 access pins on one edge,

43 to a side. Circuit components are mounted on only one side,

the component or "A" side. The other side is denoted the

wiring or "B" side. Certain access pins are identically defined on most of these logic boards - Bl is ground, B3 and

B43 carry the -12 VDC and +5 VDC bias respectively.

There is provision for up to 45 IC's plus certain load resistors, filter capacitors, etc. on a board. This can result in high printed circuit path densities, with minimum path-to-path spacings of one ten-thousands of an inch. Circuit connections to devices may be made on either side, at device pins inserted into plated-through holes. These also serve to connect circuit paths on the A and B sides.

## 2.2.2 Possible Failures on a Printed Circuit Board

To give a better idea of the reasons for spending large sums in designing or purchasing automated test equipment for logic PCB's, the following list of failure types is presented.

(a) Component failure - This may be caused by defective or marginal components, components improperly inserted, or incorrect component types or values. As was already stated, the manufacturer may guarantee less than 1% failures in IC's. With up to 45 IC's per PCB this fact alone could result in one failure per two or three boards. While dropout due to this cause is happily much less, errors made during PCB assembly, which accounts for the other types of errors of component failure, largely offsets any gains made here.

- (b) Solder bridges between circuit paths This results from poor wave soldering of closely spaced circuit paths and may cause failures on 10% of the PCB's tested. Visual inspection after wave soldering and before testing catches a large percentage of this error type.

- (c) Matrix errors This includes printed circuit path routing errors, improper etching resulting in hair-thin bridges between adjacent paths, improperly plated-through holes which causes open circuits, or hairline cracks on circuit paths, which has the same result. Circuit paths routing errors are usually caused by improper checking of artwork when a new circuit is laid out, or when an old design is changed. This type of error will be picked up when the corresponding PCB test program is being proved in, and will thus seldom enter into manufacturing testing. All of the other types of matrix errors mentioned above may occur during manufacturing testing.

- (d) Poor connector contacts Grease or dirt on the gold-plated PCB access pins can result in an open-circuit condition between the PCB and the test set connector. This is enhanced by non-wiping connectors which make contact by being clamped down onto the goldfingers, and thus do not wipe them clean before contact is made as is the case when the PCB is plugged into an ordinary wiping connector. Non-wiping connectors are used during testing to insure that the PCB goldfinger contacts are not scratched (they might other-wise corrode).

These failures may each result in a single test failing,

or a catastrophic failure were devices are destroyed when power is applied to the PCB. Considering also that thousands of individual tests may be necessary to completely check a logic PCB, it becomes clear that automatic test facilities are necessary to insure proper PCB performance.

### 2.3 LOGIC CIRCUIT ANALYSIS

As was already mentioned in section 2.2 individual PCB's do not necessarily contain entire logic functions from a system point of view. Rather they may contain a seemingly random collection of interconnected logic devices with no apparent identifiable function. The system designer, when partitioning his circuits onto individual PCB's, rarely bothers to rewrite his logic equations to fit the bits and pieces of circuitry ending up on a particular board.

All logic circuit analysis as far as this test system is concerned is done from a steady-state DC level point of view. Switching speeds and possible hazards caused by critical races are considered only so far as to avoid simultaneous changes to several direct inputs to sequential circuits.

## 2.3.1 Analysis From a Logic Function Point of View

Whenever an identifiable logic function appears on a PCB all of its design-required input/output relationships should be checked. If they are all correct, and one assumes that don't cares are indeed meaningless, nothing else need be tested for this particular circuit. This is strictly a

functional test as far as the steady-state input/output conditions are concerned. It must be remembered that switching speeds and associated hazards are not checked. This is based on the assumption that the designer has taken care of this. The function of the PCB tester is not to verify a design, but rather to make certain that all required devices are functioning correctly, and are mounted and interconnected as specified. In the case of an identifiable logic function this purpose is achieved also by checking the function.

## 2.3.2 Analysis From a Logic Device Point of View

Some PCB's contain odds and ends in logic devices which are mounted with their input/output pins wired directly to the PCB access terminals. Or the devices may be interconnected in small groups. These must be analyzed from a device point of view - that is each device must be checked for its particular function.

## 2.3.3 Analysis From a Random Error Point of View

Random errors are those caused by solder bridges or matrix errors resulting in open and short circuits. Certain PCB's contain multiple identical logic circuits and functions. Whereas these circuits are seperate as far as their inputs and outputs are concerned, a solder bridge for example could short part of one circuit to part of another. This may not be detected when these circuits are checked individually and seperately. It may result in faults when both circuits operate concurrently.

It is extremely difficult - if not impossible - to try and analyze a circuit from the point of view of including sufficient additional tests to try and pick up every conceivable short and open circuit that might occur between it and other seperate circuits. There are certain procedures followed to minimize the possibility of overlooking such an error. These include exercising seperate circuits concurrently and checking all outputs all of the time, testing twice - once with all unused inputs set low, once set high, and employing Test Program Verification (described in subsequent chapters) which assures that the specified tests will pick up any open or short circuit condition at any IC access pin.

### 2.4 TRUTHTABLE GENERATION

Truthtables, or tables of combination, describe the steady-state relationship between the input and output levels of a logic circuit. Complete truthtables consist of 2<sup>n</sup> lines of input/output relationships, where n is the number of discrete inputs to the circuit. Testing truthtables are usually subsets of complete truthtables since it is often unnecessary to subject a logic circuit to 2<sup>n</sup> tests in order to check it.

Some work has been done to computerize the generation of testing truthtables for PCB's. This usually involves entering a device interconnection map into memory, along with the device codes. Each device code corresponds to a subroutine. The analysis program then tries to determine PCB input pin setups so as to exercise each device input and output pin at

least once per logic level. It then gives the expected output levels at the PCB access terminals. As the number of seperate devices grows, so must the number of defining subroutines. Such analysis programs require large computer memories because of their large size. Their greatest disadvantage lies in their inability to generate trouble-shooting information. If certain ones of hundreds of thousands of tests fail it becomes imperative to provide exact information as to the input/output conditions of the PCB at the time of failure, as well as the actual circuits currently under test.

In any case, the first step in generating a logic PCB test program is to analyze the logic circuits and write testing truthtables. These must include sufficient tests to exercise each logic device enough to insure correct functioning. In the case of combinational circuits it is sufficient to set each device input pin at least once low, and include any additional tests necessary to have the output change state at least once. In the case of sequential circuits the capability of memory must also be checked. Furthermore, additional tests may have to be added to check for possible interaction between seperate circuits. The testing truthtables will clearly state PCB input and output terminal numbers and possible intermediate testpoints exercised and checked at any time. Coordinate information must be provided to the test program to indicate the exact location within any truthtable as a test is performed. These truthtables are then used to both encode the testprogram, and to provide trouble-shooting information.

#### 2.5 SOFTWARE IMPLEMENTATION

As the name implies this is the encoding of a testing truthtable into some form of computer language to permit the computer to test the PCB via a logic testset.

There are of course several computerized logic PCB testsets manufactured by various companies, and each has its

unique accompanying software package. Most of these are

"high level" to facilitate the encoding of testing truthtables without requiring much knowledge of computer programming. There is little to choose in this respect between

Hewlett-Packard's 2060A Logic Test System, Computer Automation Inc. Capable Tester, or General Radio's 1790 Logic

Circuit Analyzer. This is of course understandable when one

considers that there are only so many things one can do with

logic circuits, given the constraints of steady-state level

testing only. What seperates the men from the boys in this

business is the power of the error detection and correction

tools provided by the tester's operating software and hardware.

If a "high level" language is used to encode testing truthtables in readable "English" statements, this must then be translated into an input acceptable to the operating system which communicates with the testset. This can be either a one or two pass affair. In a one pass system translator and operating system are part of the same program and hence co-resident in memory as the test program is being executed. This has the advantage of usually permitting tests to be modified,

or additional tests to be entered when a PCB is under test.

(This corresponds to on-line editing). Its disadvantages are large core requirements for the software system and hence less available storage for test programs, and increased test execution times as each statement must be translated before being executed each time the test is to be performed.

A two-pass system seperates the translating and execution functions. Here the "English" test program is converted by a translator program into a format usable as direct input to an operating system. When a PCB is to be tested this translated test program is then loaded by the operating system and executed. Here the advantages are lesser core requirements for the operating system which can hence be more sophisticated, increased test program storage availability for more tests as the test program statements are "condensed" by the translator, and improved execution speeds. The disadvantages are the usual lack of direct translation capability by the operating system, although some manufacturers have provided some translation capability for their operating system either directly, or as a seperate translator-editor-operating system package. Also, the translator output has to be stored in addition to the original source test program.

## 2.6 ERROR DETECTION AND CORRECTION

The purpose of a computer controlled logic testset is not only to sort out faulty circuits but also to provide on-line debugging facilities. Considering the complexity of logic circuits such debugging facilities are a combination of hardware and software devices intended to minimize the time required to locate and correct a failure.

Hardware devices include manual measuring instruments such as logic probes and volt-chmmeters, or automatic checking of testpoints within a circuit under test. Software devices comprise extensive command repertoires for an operator to initiate partial or modified testing in order to zero in on the fault. There is also the possibility of including error directories which store fault sequences for single errors and can hence identify and locate them. This becomes impractical for multiple errors.

#### CHAPTER 3

#### TEST SYSTEM HARDWARE

This chapter gives a general description of the test system hardware. This comprises the computer, the logic PCB testset, and the interface linking the two. Both of the latter were designed and built by the Northern Electric Co.

Since this dissertation concentrates on software, the following is intended only to place the Operating System into the context of its hardware constraints. It should be noted that once it has been decided which computer to purchase as a controller, certain limitations are placed on peripheral hardware design. Similarly the testing hardware of necessity governs the design and function of the software. For optimum efficiency the various hardware items as well as the software must be matched to exclude any inconsistencies.

## 3.1 THE PDP-15/20 COMPUTER

The computer is a Digital Equipment Corporation PDP-15 data processor with 8192 18-bit words of memory and an 800 ns cycle time. Its input/output devices comprise a KSR-35 Teletype (keyboard and printer only), a high-speed paper tape reader (300 characters/second) and punch (50 characters per second), as well as two Dectape (Digital Equipment Corp. magnetic tape) drives, each of which can store 150,000 words per reel.

For purposes of comparison, the General Radio 1790

Logic Circuit Analyzer standard system<sup>(3)</sup> employs a computer with 4096 12-bit words of 1.6 micro-second cycle core memory. It includes a Teletype including paper tape reader and punch, and a high-speed photoelectric paper tape reader.

Computer Automation Inc. Capable Test System<sup>(4)</sup> in its standard configuration includes its 208 minicomputer, which has a memory of 8192 16-bit words. Its input/output equipment includes an ASR-33 Teletype with paper tape reader and punch, and a high-speed (300 characters/second) photoelectric paper tape reader.

The basic Hewlett-Packard 2060 Digital Logic Module Test System<sup>(5)</sup> is furnished with an HP 2116B computer with 8192 16-bit words, a modified ASR-35 Teletype with paper tape reader and punch, as well as a high-speed paper tape reader.

None of the three systems include mass storage devices such as magnetic tape in their basic configurations. All have expandable memories. There is no attempt to make value judgements on the relative merits of one system over another, since the author was not part of the decision-making process in the test system hardware configuration. The following sections give brief descriptions of the PDP-15 organization.

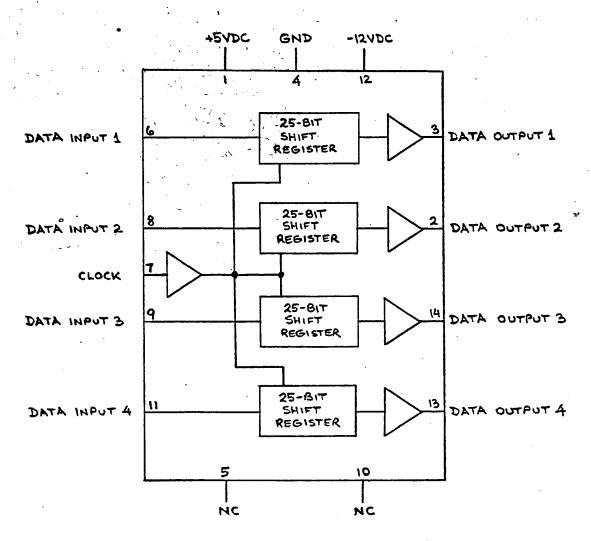

## 3.1.1 Central Processor Description

The Central Processor (CPU) is the nerve centre for control and execution of stored programs. By coordinating its own operation with that of other subsystems, it provides supervisory control over the PDP-15 System. (6) It contains arithmetic and control logic hardware, several registers

for processor-memory communications, a program counter, instruction register, accumulator (as well as index and limit registers not used in the Bank mode operation).

The CPU performs calculations and data processing in a parallel binary mode through step-by-step execution of individual instructions. Both the instructions and the data on which the instructions work are stored in the core memory of the PDP-15. The arithmetic and logical operations necessary for the execution of all instructions are performed by the arithmetic unit operating in conjunction with the central processor registers. Figure 3.1 gives a simplified block diagram of the CPU. Some of its registers are briefly described below.

- Arithmetic unit: Handles all Boolean functions and contains an 18-bit, 85 ns adder. It acts as the transfer path for inter-register transfers and shift operations.

- Instruction register: It accepts the six most significant bits of each instruction word fetched from memory, which include the operation code, indirect addressing, and indexing.

- Accumulator: This 18-bit register retains the result of arithmetic-logical operations for the interim between instructions. For all program-controlled input/output transfers, information is transferred between core memory and an external device through the accumulator. Its contents can be manipulated, and can be added to from memory.

- Link: This 1-bit register is used to extend the arithmetic capability of the accumulator. In 1's complement arith-

FIGURE 3.1: SIMPLIFIED BLOCK DIAGRAM OF PDP-15 CPU (6)

metic it is an overflow indicator, while in 2's complement arithmetic it logically extends the accumulator to 19 bits and functions as a carry register. The contents of the link can be checked and manipulated.

- Program counter: It determines the order in which instructions are performed. It contains the address from which the next instruction is to be taken.

#### 3.1.2 Memory Organization

The primary storage facility for the PDP-15 is an 8192 word magnetic core memory. It provides rapid (400 ns) random access data instruction storage for both the CPU and the input/output processor. The basic subsystem of memory is the bank, which contains 2 pages of 4096 words each for a total of 8192 words per bank. Every bank contains a data buffer, an address buffer, and all the necessary read/write control and timing circuitry to make it an autonomous unit.

Memory communicates directly with the CPU and the input/output processor through the memory bus and the memory data buffer. A 13-bit memory address register allows direct addressing of 8192 words in each bank.

Reading from and writing into memory are performed by read and write memory half cycles requiring 400 ns each for an effective cycle time of 800 ns.

## 3.1.3 The Input/Output Processor

The I/O Processor contains 2 sub-units, the data channel controller and the addressable I/O bus. It contains the control

logic and registers necessary to transfer up to 18 bits of parallel data on a common bi-directional I/O bus. Data may be transferred directly between the I/O Processor and the accumulator of the CPU. While transfers are being made between memory and the I/O Processor the CPU is free to operate independently.

Peripheral devices may transfer data in any one of three modes: single-cycle block transfers, multi-cycle block transfers, and program-controlled transfers. The first two are implemented by the data channel controller, to which the TC15 Dectape controller is connected. The addressable I/O bus implements the program-controlled transfers. It also contains the program interrupt.

Program-controlled transfers, implemented by input/output transfer (IOT) instructions can move up to 18 bits of

data between a selected device and the accumulator of the

CPU. The microcoding of the IOT instruction includes the

issuing of both a unique device selection code and the appropriate processor-generated input/output pulses to initiate

a specific operation. For an "out" transfer the program reads

a data word from memory into the accumulator. A subsequent

IOT instruction places the data on the I/O bus, selects the

device, and transfers the data to the device. For an "in"

transfer the IOT instruction selects the device and transfers

data into the accumulator.

The program interrupt (PI) facility, when enabled, allows the ready status of I/O device flags to automatically cause a program interrupt. At that time the contents of the

program counter and other information is stored in location O, and the instruction in location l is then executed, transferring control to an I/O service routine for IOT instructions to identify and service the interrupt. When completed, the routine restores the system to the status prior to the interrupt via a single instruction, allowing the interrupted program segment to continue.

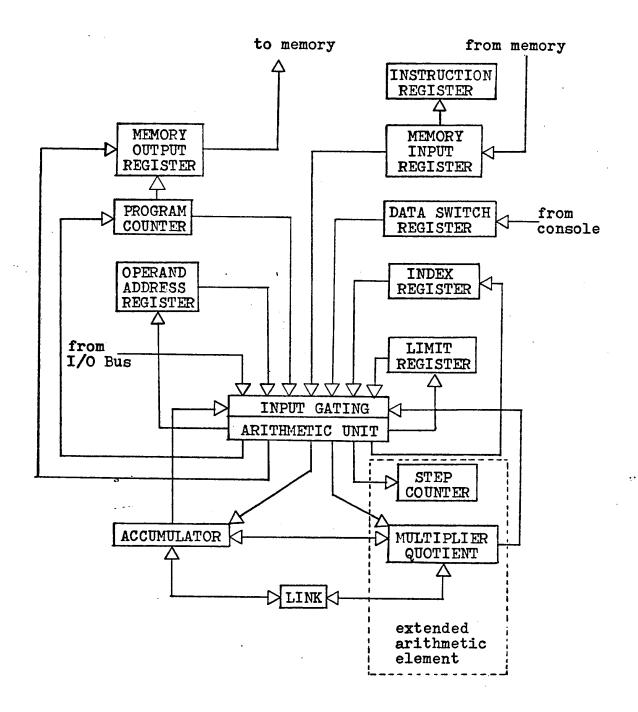

#### 3.2 THE INTERFACE

Entirely designed and built by the Northern Electric Co. this device is connected to the PDP-15 I/O bus as an interface to up to seven seperate testsets. Since the physical length of the I/O bus is limited by timing considerations, and since test stations are not necessarily or practically placed in close proximity to the computer, an interface becomes necessary. In this case the interface communicates with the test stations via balanced transmission lines independent of the timing requirements of the computer's I/O bus. All communication between computer and interface are IOT initiated. The interface decodes the IOT's and transmits a corresponding command to the test stations. Whereas all test stations see the instruction, only the actually addressed station will decode it and take action. Output from the test stations is requested via an IOT from the computer. The interface receives 18 status bits from the station, which are then strobed into the accumulator via the I/O bus.

The interface was designed to handle up to seven seperate

test stations with a view towards future expansion in a time-sharing testing environment. The only hardware modifications necessary will be the addition of the Automatic Priority Interrupt option to the computer, to handle interrupts on a priority basis rather than via a skip-chain as is the case in the current program interrupt system. An additional 8K of memory will also be necessary. It is then possible to operate up to seven test stations concurrently, with a corresponding vast increase in tested PCB output. The test stations need not be of similar intent - a mix of logic and analog testsets is possible - as long as they correspond to the general hardware philosophy employed in the current system.

## 3.3 THE TEST STATION

The test station applies all programmed inputs to the PCB under test, and checks requested output levels. It contains all the necessary hardware to test a logic PCB. This includes programmable bias power supplies, stimuli and detectors for 86 PCB access pins and an additional 10 active testpoints (where stimuli may be applied) and 48 passive testpoints containing detectors only. The DC voltage levels of the stimuli are variable for both logic 0 and 1 so as to permit marginal testing of logic devices. Output levels are checked via programmable detector "windows".

The test station console contains switches to select desired testing and output data modes, and to permit manual modifications of stimuli application to the PCB under test. It also displays the current input/output levels on the PCB, the latest command received via the interface, and the current status of either test station or PCB according to which status display has been pre-selected.

A seperate connectable unit contains the test program verification hardware. It consists essentially of programmable relays through which IC access pins may be isolated from the rest of the circuit on the PCB, and grounded. Hence open circuits and shorts to ground may be simulated to check if the test program will pick them up.

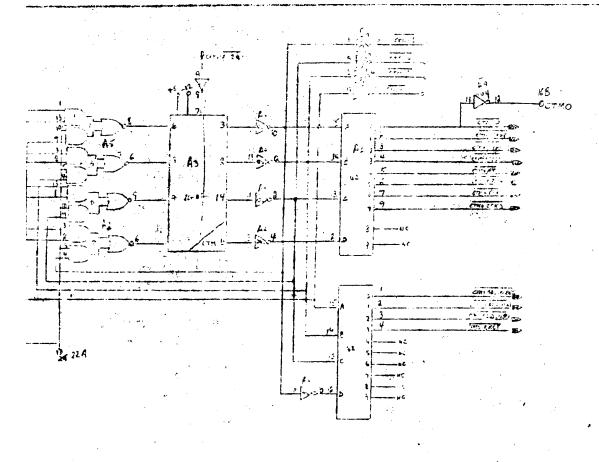

FIGURE 3.2: BLOCK DIAGRAM OF THE LOGIC TEST SYSTEM

#### CHAPTER 4

#### TEST SYSTEM SOFTWARE

The test system software is an integrated package of programs necessary for the efficient utilization of the logic test system. It consists of source test programs for the PCB's and a translator to convert them into Operating System input, and utility programs to perform storing, editing, swapping and debugging operations. Again, as in chapter 3 the following descriptions of the various programs are mainly intended to place the Operating System in context. All software, unless otherwise noted, was written by the Northern Electric Co.

#### 4.1 THE SOURCE TEST PROGRAM

This consists of the encoded testing truthtables and other necessary information in "English" statements. This type of coding permits easy interpretation of the source program listings and does not require skilled programmers for the encoding of the testing instructions. For an example of a source test program listing see chapter 7.

The source test program is listed and an 8-level ASCII paper tape is punched offline on a KSR-35 Teletype. The paper tape becomes the original input medium for either an editing or translating operation.

#### 4.2 THE TRANSLATOR

The Operating System cannot decode the source test program statements directly. They must be translated (or compiled) into series of command bit-strings (18-bit words) which can be recognized and implemented by the various handlers of the Operating System. This is done by the translator program.

The translator accepts its source program input either directly from paper tape, or from a directory-oriented Dectape (Digital Equipment Corp. magnetic tape). It outputs the translated test program onto another directory-oriented Dectape. The translator includes diagnostics for test program encoding errors. These must be corrected before a translation is completed.

#### 4.3 THE OPERATING SYSTEM

The Operating System exercises the test station according to the instructions in the translated test program.

The various PCB testing and output data modes are under operator control and may be initiated either from the test system Teletype or directly from the test station control switches.

The Operating System loads the entire translated test program from Dectape into core following the area occupied by itself. The maximum size of a translated test program is roughly 5.5K words. Considering the encoding format of the

translator output, which will be detailed in the following chapter, this could be from 5K to upwards of 50K individual tests per test program.

### 4.4 THE UTILITY PROGRAMS

These comprise the various programs performing editing, debugging, storage, loading, listing, etc. functions.

A group of programs called the FACTS DECTRIEVE SYSTEM was written by the author to store source programs, assembled binary programs, and translated test programs on Dectape under a directory system. It can also swap programs from one tape to another, list them, punch them on paper tape, etc. Using this system all necessary software for the operation of the test system is stored on a single Dectape in the following order:

- (a) FACTS DECTRIEVE SYSTEM programs

- (b) Operating System

- (c) Translator

- (d) Translated test programs

By loading a bootstrap paper tape the FACTS DECTRIEVE SYSTEM keyboard monitor program is loaded from the Dectape. The Operating System or the translator may then be requested and loaded into memory. Control is then transferred to the loaded program.

Editing and debugging operations are performed using the Digital Equipment Corporation's Advanced Editor and Dynamic Debugging Technique programs. The Editor operates

on source programs only and is used to correct errors in the source test program before translation. Editing is done from Dectape to Dectape, although initial paper tape input is possible. The translator obtains its input from the same Dectape containing the edited source test program. Hence the entire editing-translating-testing process is mass-storage oriented with resulting advantages in speed and versatility.

The Dynamic Debugging Technique is a co-resident program in upper core that allows the operation of an assembled binary program in lower core to be examined and controlled via the debugging program's command repertoire. It was used to prove in the Operating System.

#### CHAPTER 5

## OPERATING SYSTEM SOFTWARE

This chapter deals with the actual Operating System (hereafter abbreviated by OS) software. The OS is an assembled binary program. Its source program was written in the assembler language of the PDP-7,-9, -15 family of computers, using mnemonics. The source program was then assembled using the Digital Equipment Corp. Basic Assembler for the PDP-7,-9 series of computers. The resulting object program was stored on Dectape for subsequent loading into memory and execution.

The question will probably arise from those familiar with PDP-9,-15 machines as to why the program was written in basic assembler language rather than using the more sophisticated Macro language and Assembler of the PDP-15 Advanced Software System. The reason for this was the desire to minimize core requirements by writing our own I/O device handlers, rather than using the device handlers of the Advanced Software System. It was also desireable to retain absolute control of the disposition in core of the various parts of the program. Lastly, this OS is one of a family of more or less compatible operating systems controlling various digital and analog test stations. These will all eventually be incorporated in a time-shared test system which of necessity will have all its controlling software written in the basic assembler language for purposes of control.

There are several basic differences between the PDP-7, PDP-9, and PDP-15 computers. This OS includes several instruction types which may only be executed on a PDP-15. Otherwise the program could be run on a PDP-9, which was actually used to prove in much of the software. The program could be executed on a PDP-7 only if the machine has been hardware updated to a PDP-9 level, but again only if several aforementioned instruction types are changed.

It should also be mentioned that the PDP-15 must be in the PDP-9/15 (bank) mode which allows the direct addressing of 8192 words of memory.

#### 5.1 OPERATING SYSTEM ORGANIZATION

The OS software can be divided into six sections for ease of analysis. These are:

- (a) OS initialization and start

- (b) Keyboard monitor and command repertoire

- (c) Elementary function decode and functional test routines

- (d) Program interrupt handler

- (e) Utility subroutines

- (f) OS tables, variables and elementary function storage The following sections of this chapter will deal with these parts in detail.

The OS is normally stored on Dectape and is loaded into memory via the FACTS DECTRIEVE bootstrap paper tape and a keyboard command. It then occupies lower core as shown

FIGURE 5.1: OPERATING SYSTEM CORE ALLOCATION

in Figure 5.1. Various registers are then reset to their initial state and the OS requests the name of a test program, which is subsequently loaded into memory. Test program execution occurs as specified by various commands given through the OS keyboard monitor. This execution involves the decoding of the test program's elementary functions via the functional test routines, sending appropriate instructions to the test station, and receiving output via the status lines.

I/O operations are usually performed through the program interrupt handler which functions in a skip-chain mode. Common subroutines are stored among the OS utility subroutines. Tables and variables which are modified by the OS during execution are stored at the beginning of the OS. Various tables of constants and fixed parameters of a test program are loaded into an area immediately following the OS, along with the test program's elementary functions.

#### 5.2 OPERATING SYSTEM INITIALIZATION AND START

OS execution commences at this program section. Its first action is to initialize the program interrupt handling to enable the interrupt skip chain. The Dectape directory is reset to its first directory block. There are a total of five directory blocks per Dectape, each block containing a maximum of 63 discrete program names, for a total of up to 315 programs per Dectape.

The OS now requests a test program (abbreviated by TSI

which stands for testset instructions) name, and waits for characters to be typed on the Teletype keyboard. The endof-message is indicated by striking the space bar. Up to

8 characters may be entered as the TSI code. When entered,

the code is checked against all directory entries and a diagnostic message is typed if no match occurs. Otherwise the

TSI's tables and elementary functions are read into memory

providing the total length of the TSI does not exceed 20

Dectape blocks (5120 words). Otherwise the permissible TSI

storage of 5134 words for the elementary functions plus 51

words for the storage tables would be exceeded.

One of these storage tables contains the full TSI name in packed 6-bit ASCII. This is now typed to make sure that the correct TSI has been loaded. Upon verification via the Teletype keyboard a first transmission is initiated to the test station to check that it is turned on, and in the automatic mode of operation. If not, appropriate diagnostic messages are typed. A general clear is then issued to reset the station. A status word is next requested and read to check that the correct external adapter (if any) is plugged in. Various additional software registers are then initialized before the OS enters the keyboard monitor to wait for a testing initiation command.

FLOWCHART 5.1: OS INITIALIZATION & START

### 5.3 KEYBOARD MONITOR AND COMMAND REPERTOIRE

The entire testing process is under operator control and is performed according to his commands. These may be entered from either the Teletype keyboard or various pushbuttons and switches on the test station console. The keyboard monitor section of the OS consists essentially of a wait-loop when commands are accepted, and corresponding decoding and action initiating routines.

This is one of the key sections of the OS. It was the intention of the author to provide a sufficiently powerful and versatile command library to allow rapid trouble shooting of faulty logic circuits. This was attempted by permitting the operator to control the extent and sequence of test program execution, and provide him with various types of printed output data. This will become more evident in the following sections.

The command repertoire may be divided into six classes of commands:

- (a) Data mode commands

- (b) Biasing mode command

- (c) Testing modes

- (d) Test initiation commands

- (e) Test program verification

- (f) Housekeeping commands

The first three types are preconditioners or qualifiers for the test initiation commands which specify the extent and sequence of test program execution. The test program verification command is used to check on the ability of a new or modified TSI to pick up simulated faults on the PCB. The last type groups commands of miscellaneous intent, not included in the other classes.

### 5.3.1 Keyboard Wait Loop

Whenever a command is required to initiate or continue test program execution the OS enters the keyboard wait loop. This is indicated by the message FACTS 1B appearing on the teleprinter. The OS then waits for an interrupt to occur from either the Teletype keyboard or the test station. In the first case the typed characters are trimmed to 6-bit ASCII and packed 3 per word. The first word is then compared to the entries in a table of valid keyboard command character combinations. If a match occurs a "jump" is executed to the corresponding command handler. If the character sequence was invalid, this fact is indicated to the operator.

If the command was initiated from the test station it is decoded by the program interrupt handler which also transfers control to the appropriate command handler. When a test initiation command was given from the test station, the data mode is set according to the test station's data mode switch setting. Conversely, if such a command was given via the Teletype keyboard, the data mode must also be specified from the Teletype. Otherwise the last data mode used remains enabled. In other words, qualifying commands and test initiation commands must be issued from the same device — either all from the Teletype, or all from the test station.

FLOWCHART 5.2: KEYBOARD WAIT LOOP

This was done to avoid confusion as to which data mode or testing mode etc. is enabled for the current test run.

The operation of the keyboard wait loop can be summarized via Flowchart 5.2.

### 5.3.2 Data Mode Commands

These specify the format of the output data on the teleprinter. Four seperate commands allow the operator to specify from a minimum of print-out in the case of the "No Data" command, where only the total number of test failures is printed, to a maximum in the case of the "All Data" command, where all input and output pins and associated levels on the PCB are printed for each test performed. The two intermediate stages comprise the "Reject Data" and the "Reject Coordinates" commands. The first results in the same output as the "All Data" command but only for those truthtable lines containing one or more failures. The second causes only those PCB access pins that had incorrect output levels to be printed, along with the corresponding truthtable numbers and truthtable line numbers.

The handlers for this type of command set a software switch and then return control to the keyboard wait loop to enable a test initiation command to be typed. The data mode remains unchanged until either another data mode command is recognized, or the reset command "Normal Run" is given.

## 5.3.3 Biasing Mode Command

This command allows the setting of a specific biasing mode before a subsequent test initiation command. A test program may specify up to five groups of biasing conditions. Each group consists of a setting for the +5 VDC PCB bias supply, the logic level O and 1 input voltage level specifications, and the voltage ranges (windows) for the output level detectors for logic levels O and 1. The first biasing group is called "Nominal Bias", and the other groups are denoted "Margin 1" to "Margin 4". The biasing mode command may specify any of these groups as long as they were included in the TSI. This command cannot create a new biasing group since this would involve translating operations in decoding voltage levels into wordfills for transmission to the test station.

This command may also be used to specify the input level mode for the current test. This refers to the logic level which is applied to those PCB input pins which are not exercised in a current truthtable. Normally, at the first pass of a test program, these pins are set low. If so specified in the TSI, a second pass will repeat all specified tests with these pins set high. This provides another level of assurance of picking up possible shorts between printed circuit paths.

The biasing mode command is intended as a trouble-shooting tool only in that it permits the partial execution of a

test program - say only for that biasing condition where

failures occurred. It is obviously of no use if only nominal

biasing was specified. Marginal biasing levels are intended to check if a circuit performs within the maximum and minimum voltage levels specified for the logic devices. They can also be used to detect marginally operating devices which cause intermittent failures under nominal biasing conditions.

This command may only be specified via the Teletype keyboard since it causes questions to be printed, the answers being the required bias and input level modes respectively.

### 5.3.4 Testing Modes

These specify the sequence and extent of test program execution upon a subsequent test initiation command. The "Stop First Reject" command causes testing to halt at the end of the next truthtable line containing one or more incorrect output levels. The "Test Single Line" instruction will result in an unconditional halt at the end of the next truthtable line. In both cases all current input levels remain applied to the PCB under test at the time of the halt. When these commands are given, specific software flags are set and the OS returns to the keyboard wait loop to await further commands. They are intended as troubleshooting tools. Once specified they remain in force unless cancelled either by resetting their respective toggle switches on the test station and initiating testing from there, or by specifying the "Normal Run" command on the Teletype. The latter also resets the data and biasing modes to "No Data" and nominal bias respectively.

## 5.3.5 Test Initiation Command "Start"

This command causes the execution of test program instructions to take place. It first performs an input pin short test on the PCB under test. This is explained in section 5.6.8. If there were no failures during the input pin short test, the PCB is biased according to either a preceeding "Bias Mode" command, or according to the nominal bias mode specified in the TSI. The tests are then executed from the beginning of the test program, according to any pre-specified testing mode, with output data being printed according to any pre-specified data mode. Testing will normally continue until all truthtables have been executed once per programmed biasing mode with all unused inputs set low, and again once per biasing mode with all unused inputs set high, if so specified. It is thus possible to have the programmed truthtables executed ten times per PCB if all five biasing modes and both input level modes were specified in the TSI.

If the "Start" command was given via a push-button on the test station, an interrupt is generated which, when decoded, will cause data and testing modes to be assumed according to switch settings at the test station.

Flowchart 5.3 indicates test program execution under the "Start" command. It does not include data modes since these govern print-out only and do not influence the testing sequence.

FLOWCHART 5.3: TESTING UNDER THE "START" COMMAND

### 5.3.6 Test Initiation Command "Continue"

As the name implies this is intended to continue test program execution after a valid intermediate halt. Valid intermediate halts are those which are either programmed in the TSI, such as a manual operation request (see section 5.4.3), those which occur due to preset testing modes, or a halt caused by the operator requesting an interrupt via the Teletype keyboard (typing a semi-colon) or the test station push-button. In such cases a return address is generated by the OS to allow subsequent program continuation.

The "Continue" command may be given from either the Teletype or the test station. When issued, the test station is first interrogated to check that it is turned on, whether this command originated there, and, if so, its switches are scanned for testing and data modes. The command handler then checks if a return address has been set, and control is transferred to that address. Otherwise a diagnostic message is printed and control is returned to the keyboard monitor.

## 5.3.7 "Partial Test" and "Looping"

These testing initiation commands are trouble-shooting tools only. They allow a specified section of a test program to be executed, singly in the case of "Partial Test", and continuously in the case of "Looping". Since the operator must specify the boundaries of the sectional test in terms of truthtable and truthtable line numbers, as well as the

desired biasing mode, these commands can only be entered via the Teletype.

In both cases the handler first tries to locate the boundaries of the specified section in the elemental commands storage. If any of the specified table or line numbers cannot be found an appropriate diagnostic message is printed. Otherwise test execution commences with an input pin short test, followed by the test program section.

For "Partial Test" any of the available data and testing modes may be pre-specified. Testing normally halts at the end of the specified section. Test program execution can then be completed via the "Continue" command.

The "Looping" command causes the execution of the specified test program section in a continuous loop. Outputs are not checked, so that testing and data modes now have no meaning. This is intended to allow waveform monitoring with an oscilloscope by the rapid repetition (at computer speed) of programmed input level changes. The loop can only be stopped with the "Interrupt" command, at which time the keyboard monitor is re-entered. The loop can be restarted via a subsequent "Continue" command.

Flowchart 5.4 shows the testing sequence under the "Loop" and "Partial Test" commands. The action of the testing modes during "Partial Test" is identical to that shown for the "Start" command.

FLOWCHART 5.4: TESTING UNDER "LOOP" OR "PARTIAL TEST"

### 5.3.8 "Repeat Current Line" and "Repeat Sequence"

These further two test initiation commands are useful in re-testing after having performed some manual operation on the PCB - such as the replacing of a faulty device. The "Repeat" command will repeat the current truthtable line's output level checks. Testing will then continue according to the preset testing modes. The "Repeat" command does not change any input conditions.

The "Repeat Sequence" command restarts a pre-defined "Partial Test" within the same pre-specified boundaries.

Again, testing occurs according to pre-specified testing modes.

Both these commands may be implemented from either the Teletype or the test station.

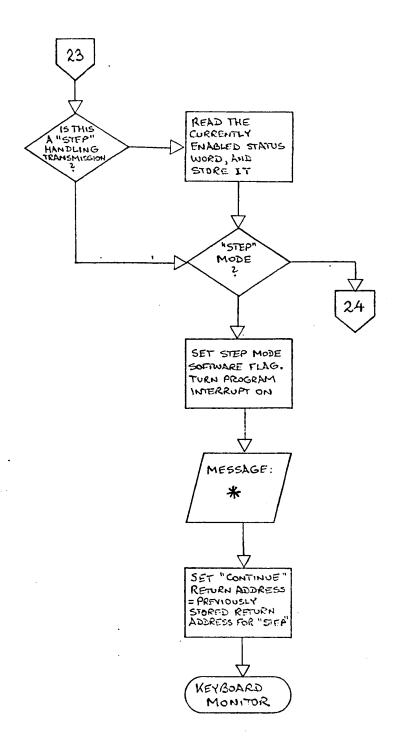

## 5.3.9 The Step Mode

Under this mode the OS halts after each complete transmission to the test station (except for those transmissions which are necessary for step mode implementation). This allows a check on OS software operation by examining the sequence of communications with the testset. It is also useful in hardware maintenance by placing the speed of hardware updating via OS commands under the control of the operator.

The "Step" command may be implemented either from the Teletype or the test station, but in either case a switch must be set on the testset to enable this mode. This is a precautionary measure as well as a means of disabling the step mode to continue normal processing.

FLOWCHART 5.5: STEP MODE

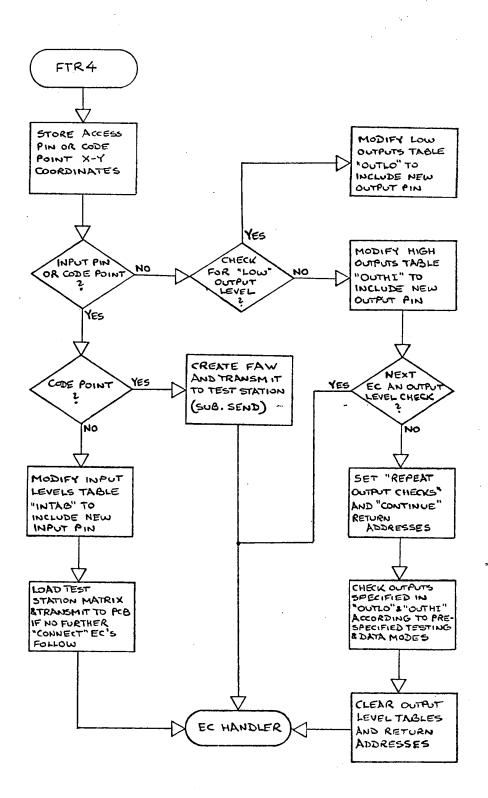

## 5.3.10 Test Program Verification

Since testing truthtables are generated manually through the analysis of logic circuits, it is very likely that individual logic devices may not be actually tested. This is due to the complexity of the logic circuits and the fact that only a relatively small number of possible input level combinations are exercised. Otherwise a PCB with only ten inputs would require 1024 individual tests. The actual PCB's tested generally have many more input pins.

Test Program Verification simulates faults on each IC access pin. If the entire test program is then executed, and no error is detected, the test program is hence incomplete in that it does obviously not exercise that particular IC pin. The necessary hardware consists of a copy of the PCB having all its IC's mounted removably in sockets, and a set of programmable relays which isolate the pins of an IC socket on a testset fixture from corresponding pins on a cable-mounted connector. This connector is inserted into a vacated IC socket on the PCB, whose corresponding IC is inserted into the socket on the fixture. By exercising the aforementioned relays open-circuits and shorts to ground can be simulated on each IC input and output pin. Faults are introduced one IC pin at a time, with the other pins remaining connected to the circuit on the PCB via the cablemounted connector.

The software implementation of the "Test Program Verification" command is as follows:

After an IC has been selected and transplanted, its

ground pin number, input and output pin numbers are defined via the Teletype. The testprogram is then executed with all fixture relays in their normal state such that the IC appears in the circuit as normal. This is to prevent misleading failures due to poor contacts. For this and subsequent runs of the test program only the nominal biasing mode is assumed, but both input level modes are used, if so specified in the TSI. After the successful completion of the first run, the first IC input pin is isolated from the PCB, and grounded. The entire test program is executed. If there were no failures a diagnostic is printed, identifying the current IC pin. In any case, this input pin is reconnected to the PCB. and the process is repeated for all subsequent IC input pins. The output pins are handled next, but are only isolated from the PCB, and not grounded, as otherwise certain types of IC's could be destroyed.

With the diagnostic output from the Test Program Verification the programmer can then add sufficient truthtables to test the previously missed devices. It is of course possible in certain circuit configurations that "don't care" conditions sourround a device such that no externally applied input level configurations will change its output level. In such cases this command must be used judiciously to avoid needless frustration in trying to create impossible test setups. Flowchart 5.6 shows the logic of this command.

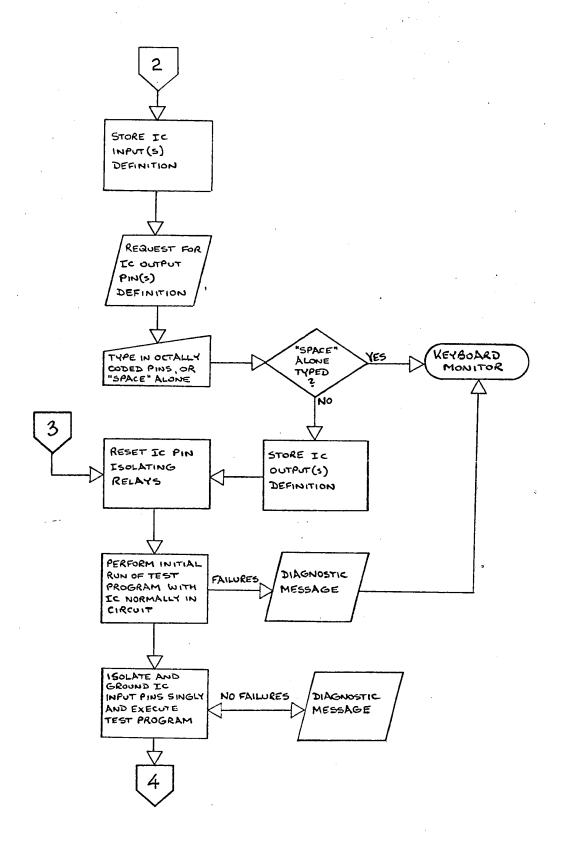

FLOWCHART 5.6: TEST PROGRAM VERIFICATION (page 1 of 3)

FLOWCHART 5.6: TEST PROGRAM VERIFICATION (page 2 of 3)

FLOWCHART 5.6: TEST PROGRAM VERIFICATION (page 3 of 3)

### 5.3.11 Housekeeping Commands

These miscellaneous commands serve to load a new test program in the case of the "New" instruction, clear all operated conditions on the test station in the case of "General Release", and return to the FACTS DECTRIEVE bootstrap. All of these commands can only be entered from the Teletype.

The "New" command transfers control to the OS initialization and start routine (section 5.2), specifically to block A in Flowchart 5.1.

The "General Release" command clears the test station by resetting all logic, relays, power supplies, etc., and then returns control to the OS keyboard monitor.

The "Return to FACTS DECTRIEVE" command transfers control to the starting address 7936 of the FACTS DECTRIEVE bootstrap (see Figure 5.1), which in turn enables the usage of the FACTS DECTRIEVE system.

#### 5.4 ELEMENTARY FUNCTIONS AND FUNCTIONAL TEST ROUTINES

The translator output of a test program's truthtables is in the form of 18-bit words which, when decoded by the OS, result in manipulation of the test station in order to test a logic PCB. There are eight discrete types of these words, which are called elementary functions or commands. The OS decodes them with eight corresponding functional test routines.

These elementary commands may be considered to be the basic building blocks of the testing system's performance repertoire insofar as they define exclusively all possible functions that the test system may be required to perform by the TSI.

The following sections will define the eight elementary functions. It should be noted that the reason for their code numbers not being in numerical order from 1 to 8 is due to other existing test stations having already used certain code numbers. To avoid decoding ambiguities in a future time-shared system, the code numbers for this OS had to be unique.

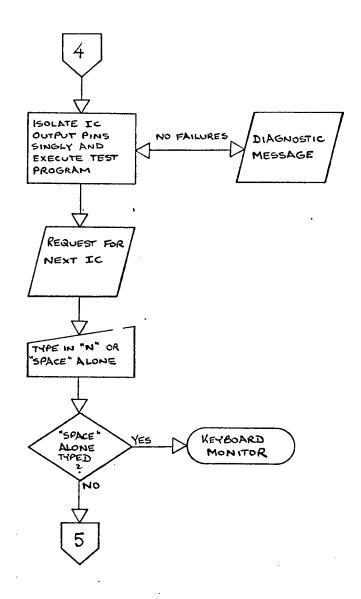

The correct functional test routine (FTR) is selected by a dispatch routine denoted the EC (elementary command) handler, which operates as shown in Flowchart 5.7.

FLOWCHART 5.7: EC HANDLER

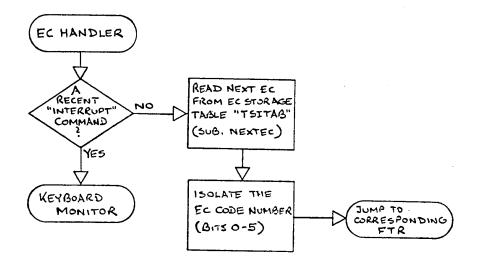

## 5.4.1 FTR 4: Full Address Word

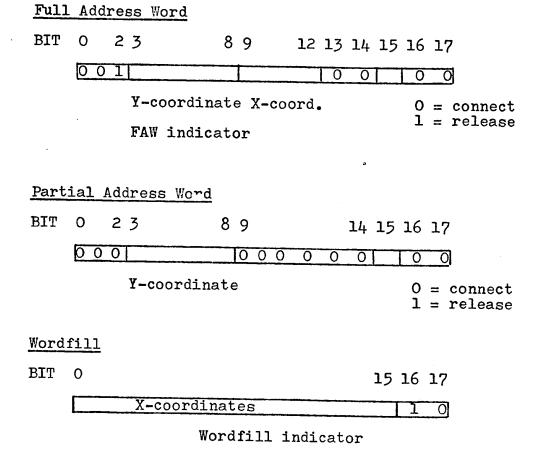

Instructions from the OS to the test station may be transmitted in two seperate formats. One of these is the Full Address Word (FAW) which uniquely defines the X and Y coordinates of an individual code point in the test station. Every action that can be performed by the test station is controlled through one or more of these code points. The other format is that of the Partial Address Word (PAW) and accompanying Wordfill, which will be discussed in section 5.4.2.

The EC 4 is created by the translator whenever it is desired to change the level of a single PCB input pin, to check the output level of a single PCB output, or to exercise a single code point in the test station, say to modify a power supply setting. The FTR 4 then creates a corresponding FAW for transmission to the testset. The individual bit assignements for both the EC 4 and a FAW are shown in Figure 5.2.

The actions of the FTR 4 are depicted in Flowchart 5.8. The following explanation will aid in understanding it. The differentiation between PCB input pins or ordinary test station code points is made from the fact that input pins must fall within Y-coordinate levels 0 to 5. Each Y-level has 16 X-coordinates. This results in a total of 96 random accessible input pins. Since a logic PCB has 86 access terminals, the additional 10 points are utilized as active test-points which may be externally connected to the PCB.

# EC 4 Bit Assignments BIT O 5678 13 14 17 000100 Bit: 0-5: EC code = 4 6: 0 = Input pin or code point 1 = Output check 7: 0 = Release or logic 0 l = Connect or logic 1 8-13: Y-coordinate of matrix point 14-17: X-coordinate of matrix point FAW Bit Assignments BIT 0 23 8 9 12 15 17 Bit: 0-2: Test station code 3-8: Y-coordinate of matrix point 9-12: X-coordinate of matrix point 15: 0 = connect1 = release

### FIGURE 5.2: EC 4 AND FAW BIT ASSIGNMENTS

17: Parity (even)

FLOWCHART 5.8: FTR 4 (FULL ADDRESS WORD)