## ASPECTS OF PROGRAMMING LANGUAGE DESIGN

Peter Grogono

A Thesis in the

Department of Computer Science

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Computer Science at Concordia University Montreal, Quebec, Canada

October, 1979

© Peter Grogono, 1979

#### ABSTRACT

## ASPECTS OF PROGRAMMING LANGUAGE DESIGN

Peter Grogono

This thesis starts by surveying the relationship between contemporary programming languages and contemporary computer architecture, using as a reference point the von Neumann machine. It demonstrates that the complexity and unreliability of modern software is in part due to the different design goals of architects and programmers. This thesis argues in favour of a more unified approach to computer system design, and presents a simple language that supports some of the claims made.

### Preface

The original goal of the research that led to this thesis was the design of a programming language suitable for the interactive manipulation of dynamic data structures.

Early investigation revealed that the tradition of designing a procedural language by abstracting from machine language is a major obstacle to the designer who wishes to make a significant extension to the power of a typical contemporary language.

This thesis consists of two parts. The first part, sections 1 through 3, contains an analysis of the factors that have led to complexity and unreliability in system software, especially in compilers, and makes some suggestions as to how these problems might be solved by programming language designers. The second part, section 4, presents a simple language, the design of which employs some of the ideas developed in the first part.

I have received much help and encouragement during the preparation of this thesis. I wish to thank those with whom I have discussed the ideas presented herein. My deepest debt, however, is to V.S. Alagar, who patiently allowed my research to meander in strange and unexpected directions, but was able to guide me at the critical corners. Professor Alagar also read and criticized many versions of this thesis. The final version owes much to him; the mistakes are my own.

# Contents

| 0     | Introduction 8.                                |

|-------|------------------------------------------------|

| 1 .   | x Survey 11                                    |

| 1.1   | Contemporary Machines 11                       |

| 1.1.1 | The von Neumann Machine 12                     |

| 1,1.2 | Extensions to the von Neumann Machine 14       |

| 1.2 ° | Contemporary Programming Languages 18          |

| 1.2.1 | Pascal as a von Neumann Language 19            |

| 1.2.2 | Inadequacies of the von Neumann Machine 20     |

| 1.2.3 | Other von Neumann Languages 24                 |

| 1.2.4 | Other Kinds of Language 25                     |

| 1.3   | Recent Developments in Programming Languages 2 |

| 1.3.1 | Verification 29                                |

| 1.3.2 | Abstract Data Typés 32                         |

| 1.3.3 | Concurrent Programming 34                      |

| 2     | The Semantic Gap 38                            |

| 2.1   | Narrowing the Semantic Gap 39                  |

| 2.2   | Extensions to von Neumann Architecture 42      |

| 2.2.1 | Procedure Invocation 42                        |

| 2.2.2 | Addressing Mechanisms 43                       |

| 2.2.3 | Evaluation Stacks 45                           |

| 2.2.4 | Variable Size Memory Cells 46                  |

| 2.2.5 | Tagged Data 47                                 |

| 2:2.6 | * Associative Memory 48                        |

| 2.3   | Microprogramming 49                            |

| 2.4    | Conclusion 51                               |

|--------|---------------------------------------------|

| 3      | Multiprocessor Architecture 53              |

| 3.i 6. | . Motivations for Multiprocessor Systems 53 |

| 3.1.1  | Limitations of Uniprocessors 53             |

| 3.1.2  | Very Large Scale Integration 54             |

| 3.2    | Aspects of Multiprocessor Design 56         |

| 3.2.1  | Common Clock 57                             |

| 3.2.2  | Shared Memory 58                            |

| 3.2.3  | Connections Between Processors 59           |

| 3.2.4  | Instructing the Processors 61               |

| 3.3    | Languages for Multiprocessors 62            |

| 3.3.1  | Static Program Architecture 63              |

| 3.3.2  | Dynamic Program Structure, 65               |

| 3.3.3  | Granularity 69                              |

| 3.3.4  | Dataflow Languages 70                       |

| 3.4    | Conclusion 73                               |

| 4.     | A Case Study 74                             |

| 4.1    | Description of CSP 74                       |

| 4.1.1  | Syntax and Informal Semantics 75            |

| 4.1.2  | Standard Processes 86°                      |

| 4.2    | Example Programs 88                         |

| 4.3    | An Implementation of CSP 100                |

| 4.3.1  | CSP System Architecture 101                 |

| 4.3.2  | CSP Processor Architecture 102              |

| 4.3.3  | - Compiling CSP 113                         |

| 4.3.4  | Loading CSP 115                             |

/•

| 4.4   | Evaluation of the CSP System 115     |

|-------|--------------------------------------|

| 4.4.1 | Evaluation of the Language 115       |

| 4.4.2 | Evaluation of the Implementation 120 |

| 4.4.3 | Directions for Further Research 122  |

| 4.5   | Conclusion 123                       |

Appendix 1: A Notation for the Productions of a Grammar 1/17

Appendix 2: The Grammar of CSP 129

References 132

# Diagrams

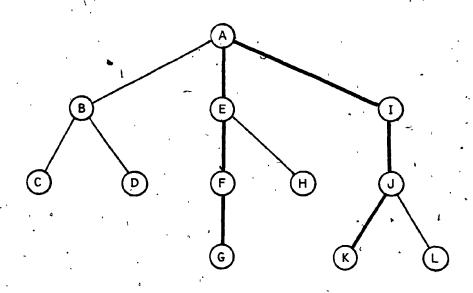

Fig. 3.1 A Program with Tree Structure 64

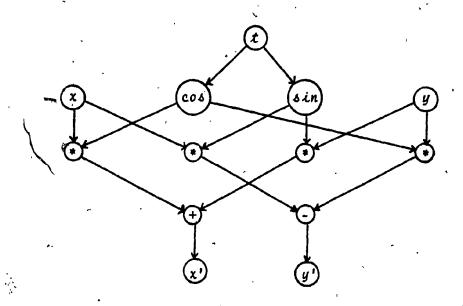

Fig. 3.2 A Dataflow Diagram 71

### 0 Introduction

The object of this thesis is to demonstrate that there is a widening gap between processor design and programming language design, and that this gap has harmful consequences for software development.

The boundary between hardware and software design is the machine language. The problem of the hardware designer is to construct a machine, or perhaps a range of machines, that will interpret the machine language as rapidly as possible, subject to constraints of hardware technology and economics. The problem of the software designer is to construct operating systems, interpreters, and compilers that will enable users of the computer system to worker efficiently at a higher, less machine dependend, level; the software designer is subject to the restraints of software technology and economics.

Section 1 is a critical survey of the consequences of this division of design at the arbitrary level of the machine language. It demonstrates that the independent development of hardware and software has lead to unecessarily increased complexity in both, but not to comparable increases in efficiency and performance. The limiting factor is always the machine language interface, which has changed little during the last twenty years.

If substantial progress is to be achieved in computer

design, machine languages must be radically changed.

Proposals for change at the machine language level should come from software designers, because software designers have (or, at least, ought to have) a deeper understanding of the problems which must be solved by the machine language.

Although a unified top-down approach is ostensibly desirable, it is not without dangers. Section 2 discusses ways in which machine languages can be modified to make high-level languages easier to implement. This approach cannot be expected to lead to radical innovations, because most high-level languages are merely abstractions of contemporary machine languages.

The traditional computer is designed around a single processing unit executing a single stream of sequential instructions. The computing power of a single processor is limited, and it is therefore inevitable that in the future large computers will have many processors. The recently developed techniques of very large scale integration, and in particular the introduction of cheap, mass-produced microprocessors, will hasten this trend. Section 3 discusses some of the issues raised for language designers by these developments.

Sections 1, 2, and 3 take a broad view of the future of computer design. Taken together, they point to the need for a greater unification between hardware and software design. Section 4 shows the form which such a unification might

assume. A simple language, based on Hoare's [1978] language CSP, is described, together with an implementation.

#### 1 Survey

This section surveys the current scene in terms of both hardware and software. It is not an unprejudiced survey; it is intended to demonstrate that, despite much activity, there have been few fundamental advances during the last ten years. This stagnation is shown to be due to the paucity of communication between architects of hardware and designers of software.

### 1.1 Contemporary Machines

The designer of a programming language which is to be widely used can assume only very general properties of the machines on which it is to be implemented. In principle, a language designer will follow Dijkstra's [1976] dictum, that the processor should be regarded as a slave that executes programs written in a programming language according to predefined semantics, rather than regarding the semantics of the language as being defined by an implementation on a particular processor. Despite this, most languages have been designed for contemporary processors, and to this extent processor technology can be perceived as a limiting factor in language design. The general properties of contemporary processors are those of a von Neumann machine. The basic von Neumann machine is described in section 1.1.1 below. The von Neumann machine has been extended in a number of ways that do not affect this argument; these

extensions are discussed in section 1.1.2. There are other extensions to the basic von Neumann machine which are more significant but which cannot yet be called 'general properties'; these are discussed in section 2.1.1.

## 1.1.1 The von Neumann machine

The term von Neumann machine is used to denote a computer with the following general properties [von Neumann, 1946]:

- 1. The machine consists of a processor P and a memory M.

- 2. The unit of memory is a string of binary digits called a word. The memory stores the values of a number of words. Each word has the same number of bits.

- The processor can read from or write to the memory.

During a single transfer, the value of one word is moved from M to P (read) or from P to M (write).

- 4. Having read a word from memory, the processor can interpret it as an instruction or as data. It is not in general possible to determine whether a word is destined to be used as an instruction or as data by examining its value.

The instructions executed by the processor are of two main kinds: one kind alters the flow of control, and the

other does not. Instructions of the first kind are typically called conditional jumps: the processor evaluates a simple boolean expression, using data in memory as operands, and executes either the next instruction in sequence or another one depending on the result of the evaluation. The unconditional jump is merely the special case in which the expression evaluated is the constant true. Instructions of the second kind are either computational or motional. A computation instruction applies an operator to one or more operands, and produces one or more results. The operators may be arithmetic or boolean, or special operators such as shift, mask, or extract. A motional instruction moves data from one place to another; in particular, input and output instructions may be regarded as motional.

The implementation of these instructions varies considerably from one actual computer to another. For example, a conditional jump instruction may be implemented by simpler instructions, such as test and jump, or test and skip. Sometimes a single instruction may perform several logical tasks: for example, decrement and jump if zero. The underlying principles, however, are always the same.

The von Neumann machine is important for three reasons. First, almost all of the computers currently in use are, in essential respects, von Neumann machines. Second, many contemporary programming languages were designed to be implemented efficiently on von Neumann machines, and were

therefore strongly influenced by von Neumann machine characteristics. Third, even those languages that were not designed to be implemented on von Neumann machines are in practice executed by von Neumann machines, because these are in most instances the only machines available.

# 1.1.2 Extensions to the von Neumann Machine

More than thirty years have elapsed since the first von Neumann machines were built. The purpose of this section is to show that, although many improvements have been made to the initial design during that period, modern computers still have the basic characteristics of von Neumann machines.

The earliest computers had a register, sometimes called the <u>accumulator</u> (AC), which had the same number of bits as a word of memory. Later a second register of the same size, the <u>multiplier/quotient</u> (MQ) was provided to store the other half of the double length quantities that arose during multiplication and division of integers. Later still, <u>index registers</u> were added to remove some of the burdens of address calculations from the accumulator. Eventually, several general purpose registers were provided instead of an accumulator and index registers.

Registers are considered to be part of the processor.

They provide short-term storage, thereby reducing the number of data transfers between the processor and the memory.

- The simplest form of memory controller allows only one memory access to be in progress at a particular time. A memory which is divided into banks allows concurrent access to several locations, provided that no two locations are in the same bank. The addresses within a bank are usually not contiguous, and so memories of this type are called interleaved memories.

- 3. The processor can use an interleaved memory effectively by executing several instructions concurrently, provided that the instructions do not interact with each other. A processor that executes several instructions concurrently is usually designed in such a way that the programmer is not aware of instruction overlap.

- The processor does not in general access the memory randomly. The distribution of access within a short time will often be confined to a small interval in the address space. This fact can be exploited by constructing the memory in two parts, one of small capacity and high speed, and the other of large capacity and lower speed. The smaller memory is called a cache.

- 5. The principle of the cache is extended in <u>virtual</u>

<u>memory</u> machines which provide a large virtual address

space by using disks to back-up a solid-state memory.

- 6. Input and output operations are usually much slower than processor operations. Input and output may proceed in parallel with processing if the processor can respond to an interrupt sent by a peripheral device which is ready for more data. Greater efficiency can be obtained if the peripheral is allowed direct memory access.

- 7. Input and output functions were originally performed by the processor, but additional processors can be added to perform input and output. The processor is sometimes called the <u>central</u> processor to distinguish it from ancillary processors.

There are three things to note about these extensions to the von Neumann machine:

1. Although some of them have not been widely implemented until recently, they are all old ideas. Index registers were used in the MUI (1949) and general purpose registers in the Ferranti Pegasus (1956).

Interrupts and asynchronous input and output date from the Univac 1103 (1954) and the Remington Rand LARC (1956). The IBM 360/87 (1966) used a cache memory, and

the Ferranti Atlas (1958) had virtual memory.

- 2. The machine language of a computer possessing these extensions is essentially the same as the machine language of the earliest von Neumann machines. The power of individual instructions has increased only slightly, and the improvements that have occurred help the assembly language programmer more than the compiler The reason for this is often that computer manufacturers want to provide their customers with 'upward compatibility'. They will therefore go to great lengths to enhance the hardware in a manner that is transparent to the programmer. The cache memory of the IBM 360/91 and the pipelined instructions of the CDC 6600 are examples of this philosophy. The result is that programming language development suffers, and attempts to enhance performance are made at the wrong level of abstraction.

- All of the extensions described are intended to reduce the number of accesses to the memory. This suggests that a fundamental limitation of the von Neumann machine is the single path between the processor and the memory. Backus [1978] calls this the von Neumann bottleneck.

## 1.2 Contemporary Programming Languages

We can associate with the von Neumann machine a class of programming languages called von Neumann languages. A program in a von Neumann language has the following properties:

- Two kinds of language construction are used; one describes <u>data</u> and the other describes <u>actions</u>.

- 2. The actions described by the program are those that can easily be carried out by a von Neumann machine: expressions are evaluated, data is moved about, and the flow of control is influenced by values of the data.

The class of widely used von Neumann languages includes COBOL, FORTRAN, ALGOL-60, PL/I, ALGOL-68, and Pascal. Languages such as LISP, SNOBOL, and APL are not von Neumann languages in the sense defined here, although they may be, and in fact usually are, implemented on a von Neumann machine.

It is an important part of this thesis that, despite the advances in hardware technology described in section 2.1.3 below, modern computers do not adequately support von Neumann languages. In order to establish this point, it is necessary to examine in more detail the sense in which the languages mentioned above are von Neumann languages. We consider Pascal, because it is a reasonably modern, general

purpose, and cleanly designed language. The argument developed in the two sections below could be made almost as easily in terms of Algol, Fortran, Basic, Cobol, or any other von Neumann language.

## 1.2.1 Pascal as a von Neumann Language

The programming language Pascal was defined about 10 years ago, although its first published description dates from 1971 [Wirth, 1971]. It was originally intended to be a language for teaching programming principles, and—consequently it is a relatively 'sparse' language, in which elaborate data and control structures are built from simpler units. One specific objective of Pascal was that it should be possible to compile and execute Pascal programs efficiently on typical computers of the late 1960's. As these computers are essentially von Neumann machines with the superficial enhancement described above, Pascal may be called a von Neumann language.

1. The primitive types of Pascal, integer, real, boolean, and char correspond to the types of data that are usually stored as logical units in memory. The methods for constructing arrays and records are abstracted from the indexed and offset addressing techniques of assembly language programming. Sets are simply strings in an abstract form.

- 2. Pascal expressions consist of operands and operators.

The operands are data with the types described above, and the operators correspond to the machine language instructions for performing computations. Pascal assignment statements map to instructions that alter the content of the memory of the von Neumann machine.

- 3. Pascal has a relatively small number of control structures. The sequence (a series of statements separated by semicolons) corresponds to the convention of the von Neumann machine that instructions are executed sequentially unless they are jumps. The selection statements (if, case) and looping statements (while, repeat, for) are abstractions of machine instructions that control the flow of execution.

### 1.2.2 Inadequacies of the von Neumann Machine

Although the preceding section demonstrates that Pascal is a von Neumann language in the sense defined at the beginning of section 1.2, there are many features of Pascal that have no counterpart in the von Neumann machine. These inadequacies of the von Neumann machine are reflected in the complexity of the compiler, object code, loader, and run-time system that are needed to support Pascal programs in a typical environment.

- Code and data in a Pascal program are separated; code cannot be accessed or altered, and data cannot be executed. The von Neumann machine, on the other hand, does not distinguish code and data.

- determined from its declaration in the program text.

The function of an operator is determined by its operands. For example, the operator '\*' may denote integer multiplication, real multiplication, or set intersection. In the von Neumann machine, the situation is reversed: the type of a variable cannot be determined from its representation in memory, and different operations are implemented by different instructions. The compiler therefore carries a twofold burden: it must maintain an elaborate symbol table containing the types of variables, and its code generator must emit instructions appropriate to the types of their operands.

- Arrays and records are natural ways of structuring data in a von Neumann machine, but the machine provides very little assistance in accessing or altering them. The index registers and the instructions that use them help, but it is rare that an array or record component is accessed by a single instruction in the machine code. Furthermore, the machine provides no assistance

at all in checking the legality of access to an array or record component. Bounds checking for arrays and type checking for record components must be performed by additional code emitted by the compiler. This inadequacy of the machine leads to overhead during both compilation and execution.

The control structures of Pascal can be implemented using the conditional jump instruction, but the von-Neumann machine provides no further assistance. It does not, for example, recognize nested statements or block structure. The raw code emitted by the compiler will contain many jump instructions, and often the targets of these jumps will themselves be jumps. implementor has the choice of accepting the inefficiency of the object code, or of increasing the complexity of the compiler by adding 'optimizing' features. Moreover, modern operating systems require the compiler to generate code that is at least relocatable, and ideally position independent. Structured source languages tend to generate code with many jumps, thereby placing an extra burden on the relocating loader. Machines which use 'short' and 'long' addresses for jump operands place an additional burden on the compiler, since it must determine when a 'short' branch can safely be used. The high degree of structuring present in the source program does not help these low-level 'optimizations' algorithms.

- The principal abstraction mechanism of Pascal is the procedure. Most computers provide no help at all in the implementation of procedure calls and exits. At most, there is a 'subroutine call' instruction, which is often not usable because it leaves the link in the wrong place.

- In many implementations of Pascal, a stack is used to store local variables, parameters, and links. Although this use of stacks has been known since ALGOL was first implemented in 1958, very few modern computers have instructions suited to the manipulation of stacks.

Some computers have 'increment address and store' and 'load and decrement address' instructions, or their equivalent, and these may be helpful in evaluating expressions which the compiler has translated into reverse polish. They do not help the ALGOL or Pascal implementor, however, because he needs an efficient means of creating a stack frame, and of addressing variables with respect to the base of the current stack frame.

# 1.2.3 Other von Neumann Languages

Although Pascal was chosen to demonstrate that contemporary von Neumann machines do not adequately support contemporary von Neumann languages, similar arguments can be applied to other languages. In fact, to the extent that Pascal was designed for efficient implementation on contemporary processors, it is actually a poor choice for demonstrating the inadequacy of these processors. PL/I and Algol-68 both have many features which cannot be implemented efficiently on a von Neumann machine.

- 1. PL/I and ALGOL-68 both allow programs to define structures whose size may change during execution of the program. This is a common requirement of string processing algorithms, for example. The task of storing dynamically varying structures, and of checking the legality of access to them, must be performed by code emitted by the compiler and the run-time system, because the machine certainly does not help.

- 2. PL/I provides many data representations, in particular, binary and decimal fixed point. Operations on fixed a point data must be simulated on a host machine that does not possess instructions that operate on data in these formats.

- 3. PL/I has an on statement that defines a response to an

interrupt caused by a program error, such as an overflow or a range error. Some of these errors may be detected by the machine, but others are not. The PL/T run-time system must detect all of the exception conditions, with or without help from the machine and operating system, and provide the appropriate response.

# 1.2.4 Other Kinds of Language

There are a number of languages which are in widespread use, but which cannot be called von Neumann languages. These languages are usually implemented on von Neumann machines for the simple reason that other kinds of machine are for the most part unavailable. The implementation usually requires an interpreter, or a compiler supported by an elaborate run-time system.

One of the essential components of the von Neumann machine is the memory. The value of a datum stored in the memory of a von Neumann machine may subsequently be retrieved from the memory. The hardware concept of storage is associated with the linguistic concept of assignment. In applicative languages, there is no assignment operation, and in principle memory is not required. A program in an applicative language is an expression composed of operands, operators, and function invocations. Execution of the program consists of applying operators and function

definitions until the expression achieves an irreducible form.

If the functions RPLACA and RPLACD, and the functions that depend on them, are removed from LISP, the resulting language is applicative. Operators and functions have no side-effects; the only consequence of their application is a result; and the value of the result depends only on the value of the operands. A LISP machine accepts as input an expression satisfying the rules of LISP syntax (a symbolic expression or S-expr), evaluates it, and displays the During the evaluation, structures binding variable names to values, and formal parameters to actual parameters, Some of these are part of the final result, are created. others are not. When the LISP machine is simulated by a von Neumann machine, the structures will occupy space in memory. Since the amount of memory available is finite, the space occupied by structures that are no longer required must be reclaimed. The machine has no way of deciding whether a memory cell is active or inactive, and consequently garbage collection must be performed by the interpreter. The garbage collector is an expensive piece of machinery which is required by the implementation, not the language: this is a strong indication that LISP is not a von Neumann language.

A LISP implementation is, nonetheless, usually supported by a von Neumann machine, and the language is usually extended in ways that reflect the von Neumann

machine. Typically, assignment and goto statements are added (as part of the <u>prog</u> feature); more recent LISP systems provide higher level control structures. These extensions are symptoms both of the capabilities of the host processor and the programmers' preference for sequential execution.

The memory of a von Neumann machine consists of a number of addressable cells of uniform size. A data object whose size changes during its lifetime cannot be stored in a simple way. Similarly, the operations provided by the von Neumann machine have fixed length operands. Languages such as SNOBOL, in which operands are strings, or APL, in which operands are vectors, are not von Neumann languages, although, like LISP, they can be simulated by an interpreter running on a von Neumann machine.

The language LUCID [Ashcroft and Wadge, 1975, 1977, 1978] is a language in which statements, as opposed to commands, are written. The designers of LUCID have demonstrated that a language amenable to conventional mathematical techniques of proof can nonetheless incorporate control structures, such as iteration, that are normally associated with command languages.

Backus [1978] proposes a functional style of programming which is a kind of high-level LISP. He perceives the von Neumann bottleneck as a limitation of von Neumann architecture, and suggests that it is the excessive

detail required in contemporary programming languages that leads to the inefficiency of their implementation.

The language SASL [Turner, 1975] is also akin to LISP.

Turner [1979] has demonstrated a novel implementation technique for applicative languages in which the source program is mapped into a tree structure, and the tree is then transformed into a canonical form which is equivalent to the result that would be obtained by executing the program. An interesting feature of the technique is that local variables disappear during the transformation.

# 1.3 Recent Developments in Program Language Design

Although many people are interested in programming language design, radical innovations have been few and far between. The field of programming language design is, in fact, stagnant. This stagnation is due to intrinsic incompatibilities between the principal areas of active interest -- program verification, abstract data structures, and concurrent programming -- and von Neumann architecture.

## 1.3.1 Program Verification

The idea of formally demonstrating that a program is correct, instead of relying on tests, is not new. Although program verification has been the subject of intensive research, there are at present few non-trivial programs that have been convincingly proved correct. There are several reasons for this.

First, the early proponents of formal programming methodology recommended that correctness be achieved by the strict application of a formal program development technique. The proof should be developed in parallel with the program, so that when the program is complete, so is the proof. As Dijkstra [1976, page 216] says: '... therefore, instead of first designing the program and then trying to prove its correctness, we develop correctness proof and program hand in hand'. The alternative approach is to start with the text of a complete program, and prove that it does what it is supposed to do; this is a much more difficult task. 2

Second, a traditional mathematical proof is a set of assertions that are simultaneously true. A program in a von Neumann language describes a process. The proof of a program must take as its starting point the text of the program, and yet it must recognize the changes of state that occur as the program is executed. Thus a statement as innocuous as

with informal semantics 'increase the value of  $\underline{x}$  by 1' leads to problem's in formalizing the meaning of the program text using traditional mathematical techniques. A further difficulty in this area is that computer manufacturers of aim that their processors can 'add', 'multiply', and so on. In fact, the operations that a typical processor performs bear only a slight resemblance to the operations known to mathematicians as 'addition' and 'multiplication'. Thus the axioms for a programming language describe the implementation on an idealized machine whose performance is not even approached in practice.

Exploring the techniques of program verification more deeply, we find that two problems recur: the difficulty of capturing the essential properties of assignment, and the difficulty of dealing with arrays. Both of these problems can be traced back to the architecture of the von Neumann machine, the memory of which is essentially an array to which assignments are made.

The third reason for the lack of success of verification techniques is the complexity of the proofs. Although a proof is often considered to be a chain of logical deductions whose truth depends only on axioms, premises, and rules of inference, in practice a proof is successful only to the extent that it is convincing. Unfortunately, the proofs of programs are often less

convincing than the programs that they claim to prove. There is no more justification for believing a proof to be free of errors than believing a program to be free of errors. In fact, we should probably be more suspicious of the proof, because it is both longer and more difficult to construct [DeMillo et al, 1977].

The fourth difficulty with program verification stems from the dual nature of useful computer programs. The correctness of a program depends on two things: the correct representation of the external world within the program, and the internal logic of the program itself. Floyd [1967b] demonstrated the connection between theorem proving and the correctness of a program: we can specify correctness in terms of theorems about programs. Given a suitable axiomatic system, for example, Hoare's [1969], we can prove these theorems rigorously. Moreover, we can devise programs that construct the proofs, and hence automatic program verifiers.

An automatic program verifier constructs a proof that is <u>formal</u> in the sense of Lakatos [1976, ppl24-5]. The validity of the proof does not depend on the meaning of the specific (problem dependent) terms. In other words, the proof can say nothing about the correctness of the representation within the program of facts from the external world. This is what Pratt [1977] means when he says:

Proofs are just computations for convincing mere machines

limited by Church's Thesis of the truth of propositions'.

Proofs of programs will perhaps become manageable when these two aspects of programming (external facts and internal logic) can be separated. Pratt [1977] calls this the 'fact/heuristic dichotomy' (the term is derived from Chomsky's 'competence/performance dichotomy'), and he has demonstrated that in a language in which fact and heuristic are separated, correctness proofs are empty, and the program is automatically correct if the facts on which it is based are true. An application of the fact/heuristic principle to code generation in a compiler is given by Johnson [1978].

# 1.3.2 Abstract Data Types

The second area of active research concerns abstract data types. The type of a variable determines both the set of values that it may assume, and the set of operators which accept it as an operand.

For simple types, these two properties are usually built into the language. For example, the declaration

· VAR flag : boolean

determines the values that <u>flag</u> may assume (<u>true</u> and <u>false</u>), and the operators which accept it as an operand (<u>AND</u>, <u>OR</u>, and <u>NOT</u>). These concepts extend naturally to structured types: for example, the properties of an array can be

derived from the properties of each of its components. An operation on an entire array is either illegal (as in Pascal for all operations other than assignment), or is interpreted as the application of the specified (scalar) operation to each component of the array in turn (as in PL/I).

This concept of type, which already goes far beyond the von Neumann machine (as shown in Section 1.2.2), is inadequate for the higher levels of abstraction found in recent programming languages such as Alphard [Shaw et al, 1977] and CLU [Liskov et al, 1977]. These languages provide mechanisms not only for implementing more elaborate data types, but also for encapsulating them. Data abstraction in this sense requires three features not provided by earlier languages:

- the compiler must detect and reject attempts to employ knowledge of the implementation of an abstract data type. This is what is meant by encapsulation: only those operators that are meaningful for the type may be performed upon it. The operations permitted on a variable of type stack might be: procedures push and pop; and boolean valued functions empty and full.

- The instantiation of a variable may involve appropriate initialization. For example, a stack should be initially empty.

3. The data types must be parameterized. For example, once the type stack and the associated operations have been defined, it must be possible to instantiate a 'stack of 10 integers' or a 'stack of 100 reals'.

The first two of these features are more important than the third. We can make statements about variables of a given type which are true when the variable is initialized, and whose truth is preserved by the permitted operations. These statements are then <u>invariant properties</u> of the variables of the type, and this invariance can be deduced from the defining capsule of the type only.

The von Neumann machine does not provide any support for abstract data types. Substantial checking is required during both compilation and execution. The cost of implementing abstract data types is high, because of the complexity of the compiler and the run-time support system.

### 1.3.3 Concurrent Programming

The third area of active research considered here is concurrent programming. The art of writing code that supports concurrent programs and responds to asynchronous events has been perceived as difficult, and this perception has been substantiated by unreliable software. Most techniques of concurrent programming are based on the

assumption that sequential programs are easier to understand than parallel programs, and that parallel programs should therefore consist mostly of sequential code, with the addition of a small number of synchronizing primitives. The synchronizing primitives that have been proposed include semaphores [Dijkstra, 1968], monitors [Hoare, 1974], and mailboxes [Atwood et al, 1972].

A process consists of a sequential program (body of code), which can be shared with other processes, and a state vector which is unique to the process. From time to time a processor is allocated to a process, and steps in the process are executed. Processors are regarded as resources, and, like most resources, are limited in number. A layer of software, consisting of an interrupt handler, synchronizing and communication primitives, and a scheduler, is required to maintain the illusion of concurrent sequential processes. Processes therefore run on virtual machines.

The earliest machines did not have hardware interrupts. Interrupts were introduced to provide a means of overlapping processing and peripheral operations. This solution, conceived and executed at the engineering level, resulted in a machine that had undesirable properties for the programmer, such as non-determinacy. The task of disguising these undesirable properties was left, as usual, to the programmer.

Ployd [1979] has introduced the phrase paradigms of

programming, in which the word 'paradigm' is used in the sense of Kuhn [1970]. The dominant paradigm of programming at the present time is probably 'top-down design with step-wise refinement', or perhaps, more loosely, 'structured programming'. Floyd comments on his own introduction of a programming paradigm: the use of non-deterministic algorithms, originally intended for parsing, and later adopted by the artificial intelligence community [Floyd, 1967a].

The contemporary paradigm for concurrent programming is something like this: 'do as much as you can sequentially, and, when you have no alternative, use one of the currently. fashionable devices for communicating or synchronizing'. The purpose of this paradigm is to ensure that the confidence that we have in the correct, deterministic behaviour of sequential programs can be extended to concurrent programs. The methodology arose from two \ considerations: first, sequential programs were better understood; and, second, most concurrent programs were actually executed by one, or perhaps two, processors. the concept of concurrent processes was introduced to disguise the existence of non-deterministic events, such as interrupts, rather than as an abstraction of a machine with many processors. The need for concurrency was recognized, but the object was to minimize its impact on the practice of programming.

It is a central argument of this thesis that this paradigm of concurrent programming is obsolete. It must be replaced by a paradigm that leads to programs with much more parallelism. Such a paradigm has been proposed by Hewitt and Atkinson [1977]. Section 4 presents a simple programming language for which a paradigm of this kind is appropriate.

### 2 The Semantic Gap

The 'distance' between the concepts underlying computer architecture and the concepts underlying high level languages has been called the <u>semantic gap</u> [Gagliardi, 1973]. It has been demonstrated in the preceding sections that the semantic gap is wide. Although many programming languages are based on von Neumann principles, and most computers have a von Neumann architecture, in practice the machines only provide rudimentary support for the languages. The width of the semantic gap is responsible for the complexity of modern compilers and operating systems, and this complexity is in turn responsible for the expense and unreliability of software.

Some people perceive the semantic gap as a serious problem. For example, Myers [1978] finds that modern processors are quite inadequate for the support of modern programming languages. He considers the problem of implementing PL/I on the IBM 360, and so his concern is perhaps not surprising. On the other hand, there are those who are not worried by the semantic gap, and are even proposing that it should be allowed to widen. Feldman [1979] works from the premise that compilers as complex as the best contemporary artificial intelligence programs will be constructed in the near future.

The point of view adopted in this thesis is that the semantic gap should be narrowed. As it is unlikely that

programmers will accept a drastic reduction in the power of programming languages, this can be achieved only by designing machines that come closer to providing the features required by high level languages.

## 2.1 Narrowing the Semantic Gap

There have been many reports of computers designed for the efficient execution of high level languages. These projects can be graded according to how close the machine is to a particular language.

At one extreme, there are machines that interpret a program written in a high level language directly from its source text. An APL machine has been described by Thurber and Myna [1970], and an ALGOL-60 machine has been described by Bloom [1975]. Machines of this type, which perform no encoding of the program at all, are unlikely to be efficient. These systems might be well-suited to educational environments, where programs are short and source-level debugging aids are essential.

A less radical solution is to tailor the instruction set of the machine to the high level language that it is intended to implement. Then it is only necessary to provide an 'assembler' to translate the source text into the machine language. The assembler may be implemented in hardware or software. Machines incorporating hardware assemblers also

include an APL machine [Robinet, 1975], and an ALGOL machine [Haynes, 1977]. The SYMBOL machine [Chesley and Smith, 1971; Rice and Smith, 1971; Cowart, Rice, and Lundstrom, 1971] is of particular interest.

The SYMBOL computer was built by Fairchild Inc for Iowa State University. The SYMBOL programming language is typeless, has a syntax and block structure similar to that of to PL/I, and provides data structures in the form of lists. There is no software; one part of the processor reads and translates the source program, and another part executes the compiled code. The translator is very fast: the existing version compiles 1250 statements per second, and a proposed (but not implemented) version could compile 5000 statements per second. (Note also that the SYMBOL machine was built in 1970, and these performance figures are based on a 4 microsecond memory cycle time.) The speed of execution of the compiled code is comparable to that of more orthodox processors, although the high level architecture allows certain complex operations to be performed very rapidly.

Machines with software interpreters include an Algol-like machine [de la Guardia and Field, 1976] and an ISPL machine [Balzer, 1973].

Obvious limitations of computers which implement a specific language are that they cannot easily be adapted when the language changes, and that they cannot be used at

all for languages other than the one for which they were designed. McKeeman [1967] introduced the term <u>language</u> oriented architecture to denote an architecture that is not designed specifically for a particular high level language but which provides instructions and hardware which facilitate the implementation of a language or a family of languages.

Examples of language directed architectures include the English Electric KDF9, directed towards ALGOL, and various computers marketed by Burroughs Corporation, directed towards ALGOL (B5500, B6500, B6700, B7600) and COBOL (B3500).

Tanenbaum [1978] has described a computer architecture suitable for languages of the ALGOL family, such as ALGOL-60, ALGOL-68, Pascal, XPL, BCPL, and SAL. Tanenbaum's architecture is strongly influenced by the stack-based implementation of these languages. Addressing modes, procedure calls, expression evaluation, and array component address calculation are all designed in terms of a hardware stack.

# 2.2 Extensions to the von Neumann Architecture

In this section, we consider some extensions to the von Neumann machine. The von Neumann architecture -- a single processor and a randomly addressable memory -- remains unchanged? These extensions allow von Neumann machines to support contemporary programming languages more efficiently, both by reducing the complexity of the compiler and by simplifying the object code.

### 2.2.1 Procedure Invocation

The following is a fairly general schema for invoking a procedure in a high level sequential programming language:

- 1. Create an environment in which the procedure will execute;

- Compute the addresses or values of parameters which are to be passed to the procedure;

- 3. Save the status of the caller in its own local environment;

- Transfer control to the procedure;

- Execute the procedure;

- 6. Return values of parameters to the caller;

- Destroy the local environment;

#### 8. Return to the caller.

Some languages do not require all of these steps; for example, FORTRAN environments are static, and so steps 1 and 7 may be omitted.

The only contribution that a typical processor makes to this operation is a save-link-and-jump instruction of some kind, that may suffice (but often does not) for steps 3 and 4. More powerful instructions can be envisioned: ideally, a CALL instruction with an appropriate operand would implement steps 1 through 4, and a RETURN instruction would implement steps 6 through 8.

## 2.2.2 Addressing Mechanisms

The addressing modes provided by most processors are machine oriented rather than language oriented. Some instructions address part of the instruction itself, some address registers, and some address memory. These are the simple addressing modes: it is usually possible to compute an address which is the sum of the contents of a register and part of the instuction.

These addressing mechanisms are usually adequate in the sense that there is usually an instruction, or a small group of instructions, that will access the required operand. A compiler, however, will usually employ only a few of the

available addressing modes, and there may be no efficient ways of accomplishing the most common tasks. Many machines have general purpose registers which may be used to store an operand or an address. The optimal use of these registers is beyond the ability of most compilers. In fact, the intelligent use of registers is one of the factors that distinguishes code produced by a good assembly language programmer from code produced by a compiler.

The following objects must be addressed in a typical high level language:

- 1. Constants (note that constants are often stored in the instruction space rather than in the data space);

- Local variables;

- Non-local variables;

- 4. Array components (indexed addressing);

- Record components (offset addressing).

As stated above, it is always possible to realize these addressing modes in terms of an instruction set.

Nevertheless, a machine that provided the addressing modes listed would simplify both compiler design and object code.

A large proportion of the assignment statements in high level language programs have very simple right hand sides

[Knuth, 1971; Tanenbaum, 1978]. This suggests that it is more useful to provide instructions that can move data around in memory and perform simple operations on data in memory, than it is to provide only instructions to load and store registers. The provision of instructions of this type probably accounts for some of the success of the DEC PDP11 architecture.

## 2.2.3 Evaluation Stacks

It is much easier to generate code for a stack machine than for a multi-register machine. This is because expression evaluation is inefficient for a one-register machine, and requires register optimization on a multi-register machine. Stack machines may also be able to evaluate expressions faster than machines with a small number of hardware registers, because fewer memory accesses are required. (This argument is not applicable to machines such as the DEC PDP11 which use memory for the stack; it is, however, applicable to machines such as the English-Electric KDF9 and the Burroughs 6500, in which high-speed registers are used for the stack.)

The advantages of stack machines are most fully realized when the expressions to be evaluated have several operators. The studies of Knuth and Tanenbaum cited above show that such expressions are comparatively rare. The stack code for

x := y

is

PUSH y POP x

and the stack code for

n := n +

is.

PUSH n PUSH 1 ADD POP n

Both of these statements can be implemented in one instruction by a machine that has memory to memory move and memory increment instructions. Stack evaluation is desirable, but it must be supported by additional instructions for special cases such as these.

# 2.2.4 Variable Size Memory Cells

The memory of a von Neumann machine is used to store objects of many different types. Some of the more common types are instructions, integers, characters, booleans, reals, and structured combinations of these. Early computers could only address a word of memory at a time, and all operations involving more than one word, or a part-word, had to be simulated by software. More recent computers can

address units of several lengths, such as 8, 16, 32, and 64 bits in the case of the larger IBM 370 computers. The word length of the Burroughs B1700 computer is determined by the microprogram.

## 2.2.5 Tagged Data

One of the more striking differences between a high level language and the von Neumann machine on which it is implemented is the way in which operators and operands are treated. In the source text, the effect of an operator is determined by its operands. In the machine, the effect of an operator is determined by the instruction chosen.

There is no reason, however, why an item of data in memory should not be tagged with its type. Myers [1978] points out several advantages of this approach:

1. Fewer operation codes are required, and so instructions can be shorter. It might seem that this advantage would be offset by the extra storage required for the data, but this is not necessarily so. Usually, a datum will be stored once only and accessed more than once, and so storing type information in the datum rather than in the instruction may lead to a net saving of space. This is especially true of arrays, because only one type descriptor is needed for an entire array.

The processor can perform type compatibility checks

during execution. This is not in fact a particularly significant advantage, since type compatibility errors should probably be detected during compilation anyway.

3. The processor can perform automatic type conversion.

For example, an integer may be converted to a real

before being added to another real.

The concept of tagged data can be extended to structures: an array tag specifies the number of components and their type, and a record tag specifies the type of each component. The processor can then perform bounds checking for arrays and type checking for record components.

# 2.2.6 Associative Memory

A von Neumann machine has a memory that is accessed by address. A large part of the complexity of von Neumann systems is due to the address translations performed during compilation, linking, and execution. In certain circumstances, address translation can be eliminated, or at least reduced, by the use of associative memory.

An <u>associative</u> memory is capable of retrieving a datum of which the value (or part of the value) is known. The retrieval of an entry from a symbol table, which requires an algorithm in a von Neumann machine, is a basic operation in an associative processor. Although the idea of associative memory is not new, it is only recently that the technology

to produce it economically has become available. A detailed discussion of associative memory is beyond the scope of this thesis. Yau and Fung [1977] have surveyed recent work in this field.

### 2.3 Microprogramming

Hardware is petrified software. The advantage of software is that it can be easily and cheaply altered; the advantage of hardware is that it can be cheaply mass-produced.

The boundary between hardware and software used to be fixed at the level of the conventional machine language. We can now 'lower' this boundary by writing a program, at a lower level of abstraction, that interprets the instructions of the machine language. Such a program is called a microprogram [Wilkes and Stringer, 1953]. We can also 'raise' the boundary by executing a program that is stored in read-only memory in machine language form;

Microprogramming has already been exploited in a number of different ways:

The machine language may be implemented by a microprogram to reduce the cost of the processor. In this case, the microprogram cannot be altered by the user. The ICL 1907, and DEC PDP11/45 computers are microprogrammed in this way.

- 2. Microprogramming may be used to provide compatibility of machine language instructions over a wide range of processor architectures. This is the approach used by IBM in the 360 and 370 series of computers.

- of the computer by microprogramming. The

Hewlett-Packard 2100 computer is microprogrammed; the

manufacturer provides the microprogram for the basic

instruction set, and also for certain standard

extensions, such as floating-point instructions. The

user may add to the microprogram, extend the

instruction repertoire by adding to the microprogram,

or create his own instruction set.

- 4. Different microprograms may be used to implement different languages. The Burroughs B1700 computer provides instruction sets tailored for different languages: the switch from one instruction set to another is achieved by a jump in the microprogram.

The application of microprogramming can be extended from programming languages to the programs themselves. The declaration of an abstract data type, for example, could be compiled into a microprogram that provides the instructions necessary for operating on the defined data type.

## 2.4 Conclusion

The preceding sections have demonstrated stagnation in the development of both hardware and software concepts, and have identified von Neumann architecture as a principal cause of this stagnation. This situation is due not to weaknesses in von Neumann's work; rather, it is due to the phenomenal brilliance of his original design.

the available technology was not adequate for a digital processor of reasonable power. EDVAC had 30,000 tubes, and each time it was switched on, several of them burned out. By the early 1950's, the von Neumann design was well matched to the available technology. The processor was constructed with complex, high-speed switching circuits, and the memory consisted of delay lines, storage tubes, and magnetic cores. The processor contained a few expensive devices, the memory contained many cheap devices, and costs were balanced.

The von Neumann architecture was so successful that it is still the most common architecture in use after 33 years of research and development. During this time the speed and complexity of electronic devices has increased by several orders of magnitude, and the cost and size of these devices has diminished by several orders of magnitude. No other design has survived such a radical change in the underlying technology.

The technological background against which a computer should be designed today is utterly different from what it was in 1946. The most important change is the size of the basic component. For about 20 years the logical component from which a computer was built was the gate, a simple electronic switch. Gates were realized physically by relays, tubes, transistors, and eventually by integrated circuits. The unit of fabrication of computers constructed in the future will be a chip constructed by LSI (large scale integration) techniques. A typical unit might contain a processor, 8K bits of ROM, and 32K bits of RAM. The cost per chip decreases rapidly with the volume manufactured, and so there will be a strong incentive to restrict the variety of LSI chips, and to match them to specific functions by programming them.

Manufacturers are currently producing microprocessors in large quantities. These microprocessors have von Neumann architectures, and most of the undesirable features of mainframe computers designed in the early 1960's. There is a serious danger that the proliferation of microprocessors will be a fatal blow to the ailing science of software theory.

### 3 Multiprocessor Architecture

There are a number of indications that the use of Multiprocessor systems will increase rapidly during the next few years. This section examines the reasons for these increases; the forms that multiprocessor systems may take; and the implications for programming language design.

#### 3.1 Motivations for Multiprocessor Systems

Several processors are better than one: this is the first and most important explanation for the interest in multiprocessor configurations. A second explanation is provided by the technological developments of the last few years.

# 3.1.1 Limitations of Uniprocessors

A single processor is limited, as we have seen, by the von Neumann bottleneck: the bandwidth of the channel between the processor and the memory. This bandwidth can be increased by enlarging the word size; by interleaving memory banks; by providing cache memory; or by providing more registers. All of these procedures add to the complexity of the processor, and hence to its cost. Moreover, measures such as providing more registers may increase the complexity, and hence the cost, of software.

## 3.1.2 Very Large Scale Integration

The logical unit of processor design is the gate; the physical unit is the manufactured component. In the early days of computers, using tubes, and later transistors, the ratio of logical to physical units was of the order of 1:10. The introduction of integrated circuits in the 'third generation' of computers, starting with the IBM 360 series, increased this ratio to about 10:1. This change did not lead to a revolution in processor design because processors were still conseived as a collection of gates, although it did lead to an increase in the use of modular design concepts. More recently, the development of VLSI (very large scale integration) technology has increased the logical/physical ratio to  $10^4$ :1 or even  $10^5$ :1. The design units of the future will therefore be of much greater complexity than single gates: they will be processors, peripheral controllers, memory access controllers, memory blocks, and so on.

The design of a VLSI module is expensive (typically hundreds of thousands of dollars), but the circuits can be manufactured very cheaply (often for less than a dollar per unit), provided that production runs are large. It is therefore economical to use VLSI techniques only if a very large number of units can be sold. This implies that general purpose devices are more amenable to VLSI techniques than special purpose devices.

Once a VLSI circuit has been designed and put into production, it cannot easily be altered. Moreover, the complexity of the circuits is such that the logical design cannot be adequately evaluated until the device has been extensively tested.

These two considerations -- the need for large production runs and the complexity of individual devices -- point to the same conclusion: VLSI circuits should be programmable. In fact, of course, the programmable microprocessor is already the most common example of VLSI technology.

Although microprocessors are not yet as powerful as mainframe processors, their potential is much greater. A CDC 7600 mainframe costs about \$5,000,000; for the same cost, using today's prices, it would be possible to construct a machine containing 10<sup>4</sup> microprocessors and 10<sup>9</sup> bytes of memory. Such a project is not feasible at present because the software necessary to make such a machine usable does not exist. The example, however, serves as an indication of the need for such software.

### 3.2 Aspects of Multiprocessor Design

43

Most contemporary multiprocessor systems fall into one of two categories: identical processors sharing a common memory; and distributed systems consisting of autonomous computers exchanging messages. In this section we consider an intermediate architecture, in which the coupling between processors is tight enough to allow a simple computational task to be shared between them, but at the same time loose enough to allow extensive concurrency.

It should be noted that the multiprocessor architecture proposed here, and developed in more detail in section 4, is not a multiprocessor in the sense in which the term is often used in the literature. For example, Enslow [1977] states the following criteria for a multiprocessor:

- A multiprocessor contains two or more processors of approximately comparable capabilities.

- 2. All processors share access to common memory.

- All processors share access to input/output channels, control units, and devices.

- 4. The entire system is controlled by one operating system providing interactions between processors and their programs at the job, task, step, data set, and data element level.

The multiprocessor systems discussed in this thesis do not satisfy any of these requirements. In Enslow's terminology, the systems described here are multicomputer systems.

## 3.2.1 Common Clock

Most electronic logic systems are controlled by one or more clocks. A <u>clock</u>, in this context, is a logic signal that alternates between <u>false</u> and <u>true</u>; the oscillation is regular and is usually between 106 and 108 cycles per second. All state transitions in the system take place at the same time as clock transitions; between clock transitions the system is quiescent.

It is a premise of logic design that state transitions are instantaneous, and that propagation and recovery times are infinitesimal. In practice, of course, this is not so, and it is a problem of logic engineering to construct a system that will run fast and reliably. Reliability depends on many factors, but a necessary condition for reliability is that the interval between clock transitions is long compared with the propagation and recovery times within the system. In a large system, the clock rate is limited by the complexity or even the physical size of the system.

This is one reason for abandoning the concept of a common clock in a computer with several processors. Another reason is that in a large multiprocessing network,

processors will have specialized functions. A clock rate suitable for a peripheral controller might be quite unsuitable for a floating-point processor.

#### 3.2.2 Shared Memory

It is possible to connect several processors to a single memory. The obvious advantage of such a configuration is that very little new software is needed. Application programs can run in one processor of a multiprocessor environment just as they ran in a single processor environment, and the operating system software needs to be changed only slightly so that it can schedule several processors. For this reason, many commercial computer systems are offered with two or more processors sharing memory: computer manufacturers must usually make a commitment to existing software. The disadvantages of this approach are described in section 1.1.2 above.

For the same reason, a configuration of this kind is not of great interest to researchers; it offers little potential for interesting software development. Processes running in different processors communicate by altering shared data structures, and secure ways of accessing shared data structures have been described by Hoare [1974] and Brinch Hansen [1975].

A more serious objection to systems of this type is

that the performance of the processors may be degraded because they are competing for memory. Since memory response time is a limiting factor in some single processor systems, this is an important problem.

### 3.2.3 Connections Between Processors

There are a number of ways in which the processors of a multiprocessor system may be interconnected:

- 1. Each processor is connected to a common bus.

- 2. Each processor is connected to every other processor.

- 3. Processors are at the nodes of a rooted tree whose edges define the connections.

- 4. Processors are placed at the  $2^N$  vertices of an N-dimensional hypercube whose edges define the connections.

- 5. Processors are placed at the nodes of an arbitrary graph whose edges define the connections.

Note that configuration 5 includes configurations 2, 3, and 4. Configuration 1 is a special case: any processor can communicate directly with any other processor, but only one communication can take place at a time.

Configuration 2 requires N(N-1) connections between N

processors; it is too expensive to implement unless N is very small. Configuration 3 is an elegant implementation of a hierarchical system; the processor at the root of the tree handles the most abstract features of the task, and delegates subtasks to its subtrees. The DDM1 machine [Davis, 1979] has a tree structure in which any processor that is not a leaf of the tree may delegate tasks to a processor immediately below it in the tree. It is unlikely that efficient processor utilization will be achieved with a fixed tree structure.

The hypercube (configuration 3) is a generalized tree in which every processor can be regarded as a root. If there are  $N=2^k$  processors, the longest path between any two processors has  $k=\log_2 N$  edges and  $N.\log_2 N$  connections are required altogether. IMS Associates manufacture computers with processors connected in this way: configurations with 16 and 256 processors are available.

The configuration may change dynamically. The first configuration is actually a dynamic configuration because at a given time, any two processors may be connected. Tree and hypercube configurations usually have a fixed structure, and this may limit the degree of parallelism that can be obtained with them. The general graph (configuration 5) is not very useful unless either the system is used for solving one problem only or the topology can be altered to suit the problem. In systems of this type some processors may be

dedicated to communications; many edges would emanate from them, but only a few edges would emanate from a processing node.

## 3.2.4 Instructing the Processors

Regardless of the way in which the processors are connected, they must be told what to do. There are two possibilities: either a processor may be provided with code for all of the actions that it will ever be required to perform, or it may be loaded prior to each task. In the first case, the messages passed between processors will consist of pure data, and in the second case they will consist of a mixture of instructions and data. distinction may be blurred in some cases: if a processor contains a LISP interpreter, and is sent LISP programs, it can be placed in either of the above categories according as to whether LISP programs are considered to be instructions or data. In dataflow systems, a message consists of an operator and operands; a processor may apply some operations and pass others to a lower level processor. At the other extreme, an operating system loads a large program, such as a compiler, into a processor before activating it.

The important point is that loading time should be small compared to processing time; otherwise the processors will be utilized inefficiently.

In a procedural language, code and data are distinct, and code may be re-entrant. Re-entrant code is useful for a single processor supporting several processes which require the same code. (Recursion is a special case of this.) The concept of re-entrant code and multiple activation records seems to be less useful in an environment in which the number of processors is comparable to the number of processes.

### 3.3 Languages for Multiprocessors

It is possible to implement a von Neumann language on a multiprocessor system. If the language is not adapted for multiprocessing, the programmer has gained nothing and the semantic gap has been widened. If the language is extended by the addition of a few synchronization and communication facilities, it will still not be closely matched to the system architecture, and the problems of inefficiency, unreliablility, and complex compiler design will not have been solved. It follows that new languages will be required for multiprocessor systems.

## 3.3.1 Static Program Architecture

The structure of all but the most simple systems is hierarchical. In computer science, the hierarchy is usually represented by a tree: the root of the tree denotes an abstract concept, and the leaves of the tree denote concrete instantiations. The intermediate nodes of the tree are abstractions of the subtrees below them, and concretizations of the nodes above them. (This tree, like most trees in computer science, has its root at the top.)

The hierarchical nature of complex systems has long been recognized by programmers and designers of programming languages. Almost all programming languages have some form of procedure, and in a program, procedures are the nodes of the hierarchical tree. We use the term <u>arborization</u> to denote the extent to which a program has a tree-like structure.

In a fully arborized program, the only channels of communication are the edges of the graph describing the tree. For example, the procedures G and K of the program depicted in the Fig. 3.1 can only communicate along the darkened edges GFEAIJK. In a practical situation, this path is so indirect that G and K are effectively isolated from one another. In many instances, this is a desirable situation: G and K can be coded by different programmers working in different places, and subsequently one can be altered without reference to the other. Furthermore,

provided that G and K do what is expected of them by F and J respectively, they need have no knowledge of the rest of the program.

Fig. 3.1: A Program with Tree Structure

Although this property of a fully arborized program is attractive in principle, it is unworkable in practice. This is evident from the fact that there is no widely used programming language in widespread use which lacks a mechanism for subverting the arboreal structure. FORTRAN has COMMON, and in BASIC and COBOL control may move freely at any level of the tree and data is global. Languages of the ALGOL family use nested scopes: in terms of the diagram, procedures G and H can only communicate by means of variables declared in or above procedure F. In practice,

most programs written in these languages employ global data, declared in the root, A. This is widely recognized to be too restrictive: there are times when G should be allowed to communicate with H without F knowing about it.

It is therefore necessary to provide a means of converting the tree into a network without destroying its basically tree-like nature. We use the term reticulation to denote the degree to which a program possesses a network structure.

The contribution of structured programming has been to emphasize the arboreal nature of programs. The need for reticulation has been realized more recently, and has lead to increased interest in abstract data types. Languages of the future must enable both arboreal and reticular structures to be implemented.

#### 3.3.2 Dynamic Program Structure

A program written in a language of the ÅLGOL family consists of a 'main program' and procedures. The main program may be considered as a procedure with a special privilege — it is called by, and returns to, the operating system. Call the main program  $P_0$  and the procedures  $P_1, P_2, \ldots, P_n$ , and write down all these names. If  $P_i$  calls  $P_k$ , draw the line  $P_i P_k$ . If both  $P_i$  and  $P_j$  call  $P_k$ , then create a new node  $P_k$ , and

join P<sub>i</sub>P<sub>k</sub> and P<sub>j</sub>P<sub>k</sub>. The diagram is now a tree of which P<sub>0</sub> is the root. Select a node and label it 'A.'. Label all the nodes on the path between the selected node and the root, including the root, 'S' (there will not be any if the selected node was P<sub>0</sub>). Label all other nodes 'I'. Suppose that each node represents a process and that the only active process is the one labelled 'A' and that the others are either suspended at a procedure call ('S') or are inactive ('I'). This is a model for a possible, though unusual, execution of an ALGOL program: the active node moves about the tree; all processes on the path to the root are suspended; and all processes not on the path to the root are inactive. This suggests a question: why are all processes except one suspended or inactive?

We are accustomed to writing programs that do one thing at a time because we use processors that can only do one thing at a time. Yet this is an unnecessary and arbitrary limitation. There are many programming situations in which a multiprocessing model is more natural than a tree-structured sequential model.

Consider this sequential program:

repeat

read

do something

write

until end of file

This is a common abstraction for many problems. It is

satisfactory if each 'read' produces exactly the right amount of data for each 'do something', but it breaks down if this is not so. We then have to choose one component of the program and use it to 'drive' the other two. It is much more natural to define the abstract solution to a problem of this kind as three communicating processes:

read ---> do something ---> write

In this model, each unit is a process, receiving data from a process or file on its left, and sending data to a process or file on its right. No process dominates, controls, or drives.

In many compilers, the parser is a procedure which, when called, returns part of the parse tree. The parser, in turn, calls the scanner, which returns a token. It is simpler to think of the parser as a process which receives tokens from the scanning process and sends subtrees to the code-generation process. Multi-pass compilers are often written in this way, but the 'passes' are executed sequentially rather than concurrently. The intermediate files used to convey the partially-compiled program from one pass to the next can be eliminated by parallel processing.

In ALGOL-type languages, it is considered undesirable to allow functions to have side-effects. Sometimes side-effects cannot be avoided, however; consider, for example, the case of a function which is required to return

a pseudo-random number. It is more consistent to think of a pseudo-random number generator as a process emitting random numbers as they are required, rather than as a function.

These arguments, considered in conjunction with the arguments developed in section 3.1 in favour of a multiprocessor architecture, suggest that a language should be developed that embodies parallel processing in its fundamental design. Some of the obvious advantages of such a language are: