**INFORMATION TO USERS**

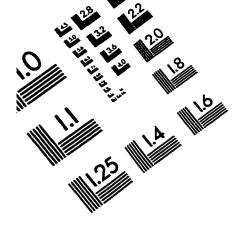

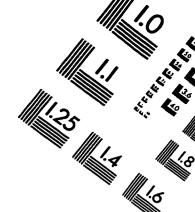

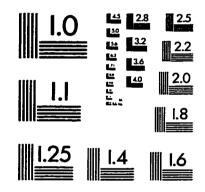

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

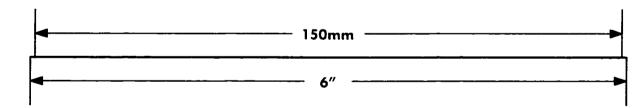

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

UMI

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor MI 48106-1346 USA 313/761-4700 800/521-0600

# DESIGN AND IMPLEMENTATION OF THREE-PHASE FOUR-WIRE ACTIVE FILTERS

#### Kévork Haddad

A Thesis

in

The Department

of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the requirements

for the Degree of Master of Applied Science at

Concordia University

Montreal, Quebec, Canada.

November 1996 © Kévork Haddad, 1996

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-26002-X

#### ABSTRACT

# DESIGN AND IMPLEMENTATION OF THREE-PHASE FOUR-WIRE ACTIVE FILTERS

Kévork Haddad

Concordia University, 1996.

The widespread use of power electronics in all types of industrial, commercial and even residential electrical equipment is causing the deterioration of the quality of the electric supply through distortion of the supply voltage. This has led to the development of more stringent requirements regarding harmonic current generation, as are found in standards such IEEE-519. Passive filters have been used to limit the flow of harmonic currents in distribution systems. However, these tend to be bulky and the design is complex, particularly if the number of harmonic components to be reduced increases. With improvements in power electronic devices and conversion techniques, an innovative concept, the active power filter, has recently been proposed and investigated. Voltage source structures in particular present excellent performance characteristics in three phase configurations. However, in a number of installations, four-wire systems are used. Furthermore, if the three phase load is unbalanced, neutral currents flow and the three phase three-wire active filter cannot adequately eliminate harmonics. This thesis deals with active filters for the general case of three phase four-wire systems. The proposed filter uses three independent current controllers acting on half-bridge inverters. The PWM pattern is generated using a constant frequency ramp comparison technique. A detailed analytical study is presented to design the power circuit in order to ensure operation in single phase and unbalanced load conditions. The quality of the supply current, the magnitude and components of the neutral current and the filter bandwidth are investigated. The theoretical considerations are verified by simulation and by experiments on a industrial prototype. Results demonstrate that the active filter is a viable and a potentially economical solution to mitigating harmonics in distribution power systems.

#### **ACKNOWLEDGMENTS**

I wish to express my sincere gratitude to my supervisor, Dr. Géza Jóos, for his valuable support, advice and guidance throughout the course of my research.

I am also grateful to Professor Alain Jaafari and Mr. Thierry Thomas, from the Laboratoire d'Electronique Industrielle, E.I.V.L., Blois, France, for sharing their practical experience.

Thanks are extended to my friends in the Power Electronics Lab, who made the period of my research more pleasant and fruitful. Special thanks to Mr. José Espinoza and Mr. Ali Reza Bakhshai for many helpful discussions we shared.

Financial support from Québec Ministry of Education (FCAR) is gratefully acknowledged, particularly for financing a three month stay at the Laboratoire d'Electronique Industrielle (summer 1995) and the National Sciences and Engineering Research Council (NSERC).

To my father, Hagop.

#### TABLE OF CONTENTS

| List  | of Figu  | res                                      | ••••       |

|-------|----------|------------------------------------------|------------|

| List  | of Table | es                                       | xiv        |

| List  | of Princ | ipal Symbols                             | .xv        |

| List  | of Acro  | nyms                                     | χiχ        |

|       |          |                                          |            |

|       |          |                                          |            |

| СНА   | PTER     | 1                                        |            |

| INTE  | RODUC    | CTION                                    |            |

| 1.1   | Gene     | ral                                      | 1          |

| 1.2   | Disto    | rtions in Power Networks                 | 3          |

| 1.3   | Harm     | onic Standards and Recommended Practices | 4          |

| 1.4   | Powe     | r in Distorted AC Networks               | 6          |

| 1.5   | Metho    | ods of Dealing with Harmonics            | .8         |

| 1.5.1 | Passiv   | e Filters                                | .9         |

| 1.5.2 | Active   | Filtering                                | l <b>0</b> |

|       | 1.6      | Literature Review                        | 1          |

|       | 1.6.1    | Shunt Active Filters.                    | 1          |

|       |          | 1.6.2 Series Active Filters              | 2          |

|       |          | 1.6.3 Hybrid Active Filters1             | .3         |

|      | 1.6.4 Active Filter Topologies15                                  |

|------|-------------------------------------------------------------------|

|      | 1.6.6 Control Aspects16                                           |

|      | 1.7 Problem Statement16                                           |

| 1.8  | Scope and Contribution of This Thesis                             |

| 1.9  | Outline of This Thesis18                                          |

|      |                                                                   |

| СНА  | PTER 2                                                            |

| THR  | EE PHASE SHUNT CONNECTED VOLTAGE SOURCE ACTIVE FILTERS            |

| 2.1  | Introduction20                                                    |

| 2.2  | Active Filter Configuration21                                     |

| 2.3  | Three Phase Active Filter                                         |

| 2.4  | Four Wire Half-Bridge Topology24                                  |

| 2.5  | Power Circuit Design                                              |

|      | 2.5.1 Current Ripple Generated by the Half-Bridge Active Filter28 |

|      | 2.5.3 Reactor and DC Bus Voltage Selection30                      |

| 2.6  | Conclusions38                                                     |

|      |                                                                   |

| СНА  | TER 3                                                             |

| RATI | NG ISSUES AND DC BUS CAPACITOR SELECTION                          |

| 3.1  | Introduction                                                      |

| 3.2  | Design of the Capacitors40                                        |

| 3.3  | Dc Capacitor Voltage for Step Changing Load                       |

| 3.4  | Activ  | ve Filter Current Compensation Capacity44                |

|------|--------|----------------------------------------------------------|

|      |        |                                                          |

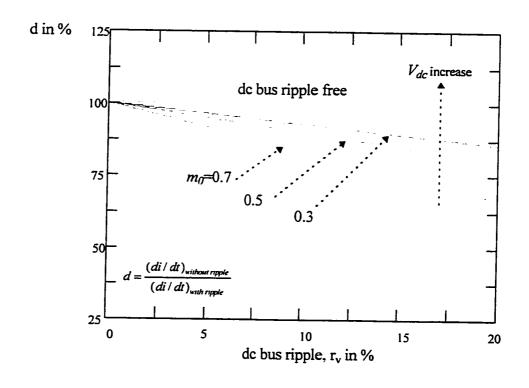

| 3.5  | Effec  | et of the Dc Bus Ripple on the Compensation Capability46 |

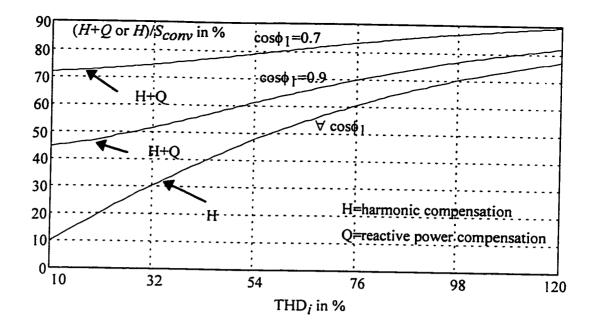

| 3.6  | Requ   | ired Harmonic Power by the Active Filter48               |

| 3.7  | Ratin  | g of the Synchronous Link Reactor49                      |

| 3.8  | Capa   | citor and Inverter Rating50                              |

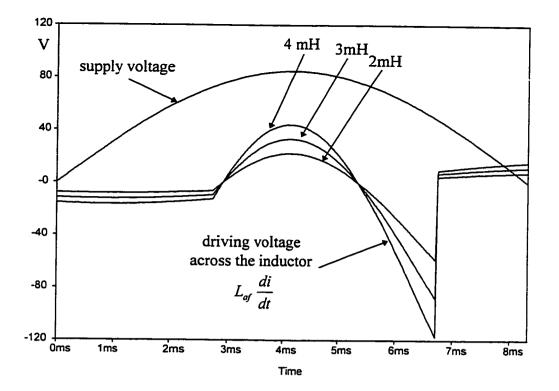

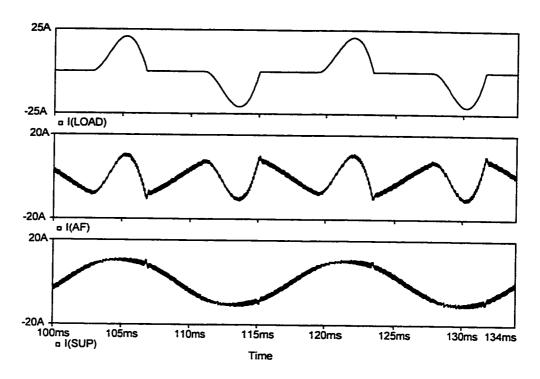

| 3.9  | Desig  | gn Example51                                             |

| 3.10 | Conc   | lusions55                                                |

|      |        |                                                          |

| СНА  | PTER   | 4                                                        |

| CON  | TROL   | SYSTEM DESIGN                                            |

| 4.1  | Introd | luction56                                                |

| 4.2  | Contr  | ol Circuits Description56                                |

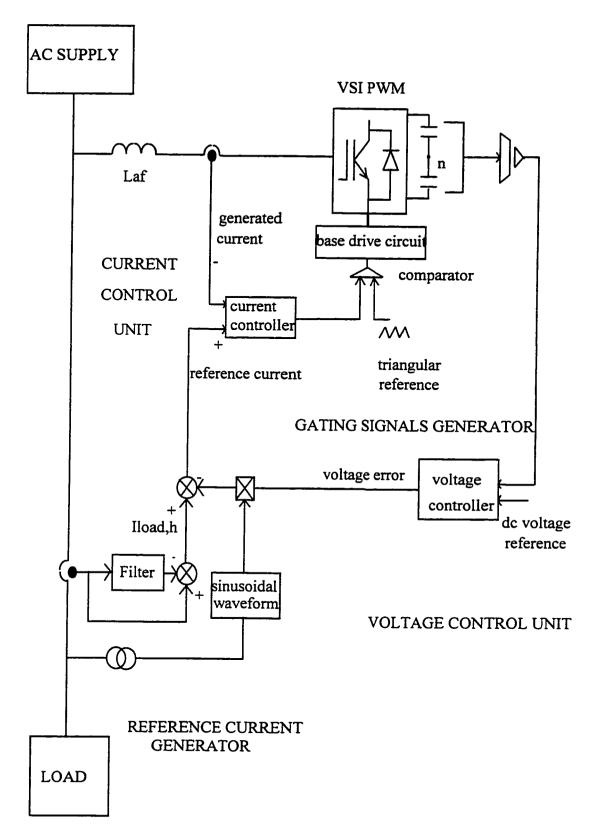

|      | 4.2.1  | Reference Current Generator58                            |

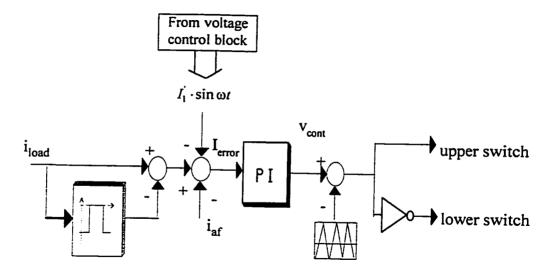

|      | 4.2.2  | Current Control Unit59                                   |

|      | 4.2.3  | Gating Signals Generator59                               |

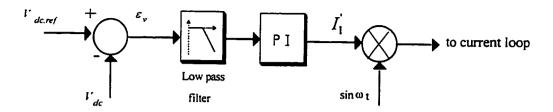

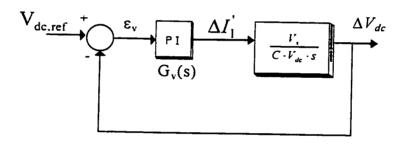

|      | 4.2.4  | Voltage Control Unit60                                   |

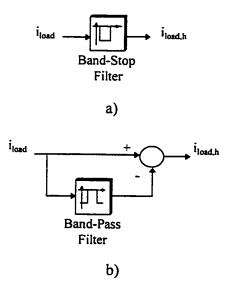

| 4.3  | Design | n of the Extraction Circuit60                            |

| 4.4  | Design | n of Control Loops63                                     |

|      | 4.4.1  | Design of the Current Loop63                             |

|      | 4.4.2  | Voltage Loop Design70                                    |

|      | 4.5    | Conclusions76                                            |

#### **CHAPTER 5**

### SIMULATION AND EXPERIMENTAL RESULTS

| 5.1  | Introduction                                                     | 7          |

|------|------------------------------------------------------------------|------------|

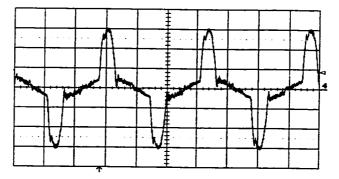

| 5.2  | Single Phase Operation-Experimental Results                      | 77         |

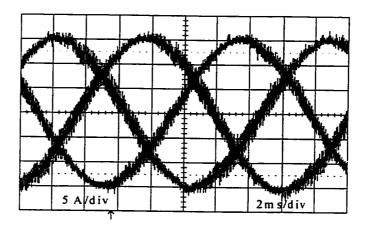

| 5.3  | Unbalanced Load Operation                                        | 80         |

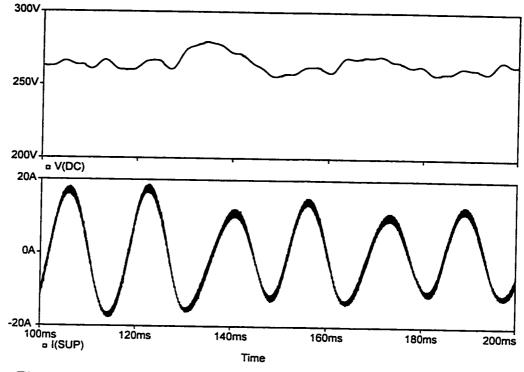

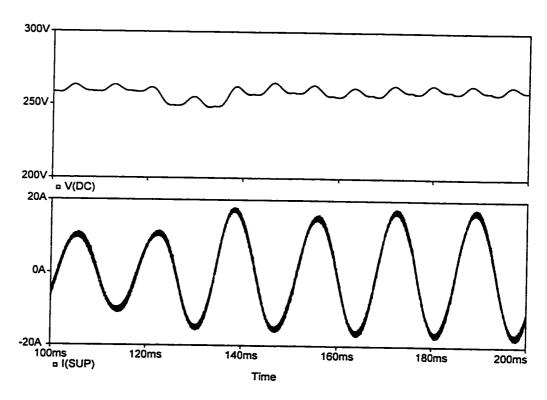

|      | 5.3.1 Simulation Results-Four Wire Active Filter                 | <b>8</b> 1 |

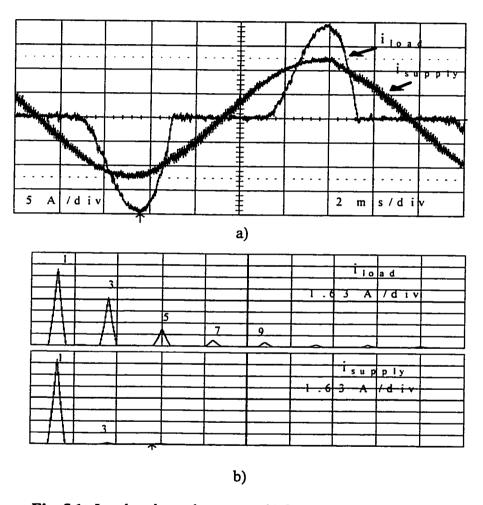

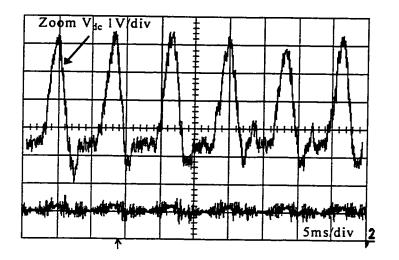

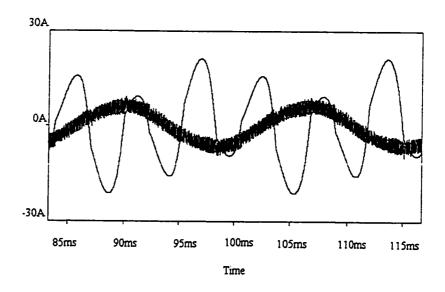

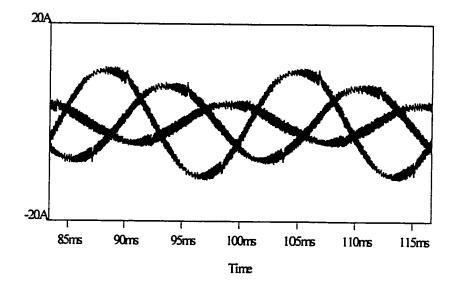

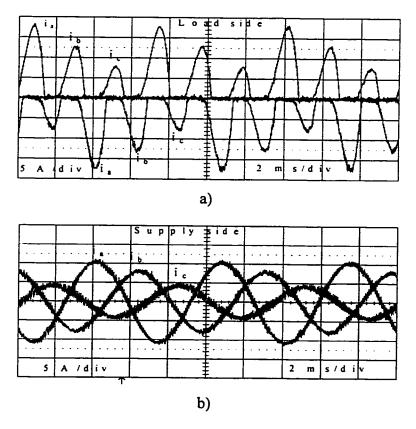

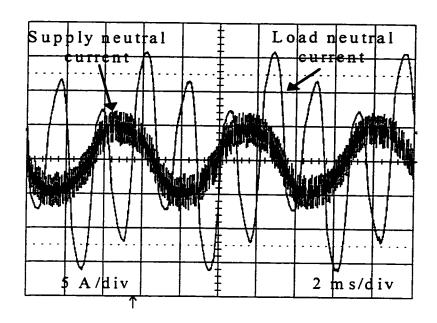

|      | 5.3.2 Experimental Results-Four Wire Active Filter               | 82         |

| 5.4  | Unbalanced Mains-Experimental Results                            | 86         |

| 5.4  | Balanced Single Phase Loads Operation-Experimental Investigation | 88         |

| 5.5  | Performance Comparisons.                                         | 90         |

| 5.5  | Conclusions                                                      | 91         |

|      |                                                                  |            |

| CHA  | APTER 6                                                          |            |

| SUM  | IMARY AND CONCLUSIONS                                            |            |

| 6.1  | Summary                                                          | 92         |

| 6.2  | Conclusions                                                      | 93         |

| 6.3  | Suggestions for Future Work                                      | 94         |

|      |                                                                  |            |

| REFI | ERENCES                                                          | 95         |

| APPE | ENDIX A                                                          | 103        |

| APPE | ENDIX B                                                          | 106        |

#### LIST OF FIGURES

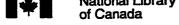

| Fig. 1.1  | Harmonic distortion at PCC.                                                          | 2   |

|-----------|--------------------------------------------------------------------------------------|-----|

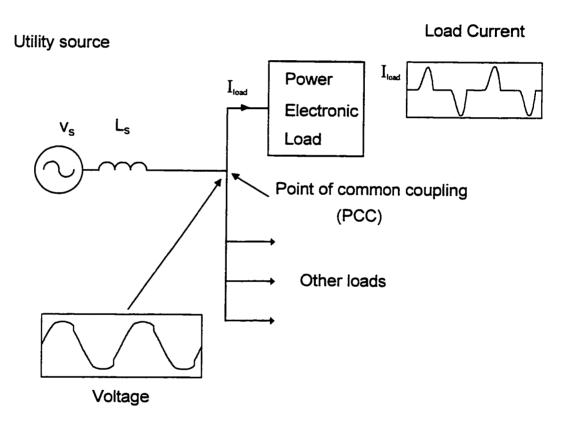

| Fig. 1.2  | Classification of distortion types in power networks.                                | 4   |

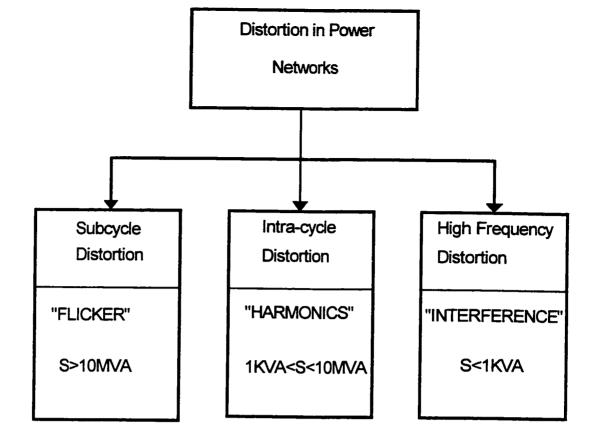

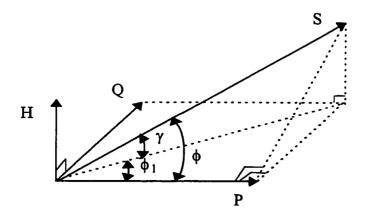

| Fig. 1.3  | Components of electric power                                                         |     |

| Fig. 1.4  | Power tetrahedron.                                                                   | 7   |

| Fig. 1.5  | Passive filters. (a) single tuned filter (b) first order high-pass filter (c) second |     |

|           | order high-pass filter.                                                              | 9   |

| Fig. 1.6  | Principle of shunt connected active filters                                          | .12 |

| Fig. 1.7  | Series connected active filter.                                                      | .13 |

| Fig. 1.8  | Hybrid series active filter.                                                         | .14 |

| Fig. 1.9  | Hybrid shunt active filter                                                           | .14 |

| Fig. 1.10 | Main topologies of active filters. (a) voltage-type (b) current-type.                | 15  |

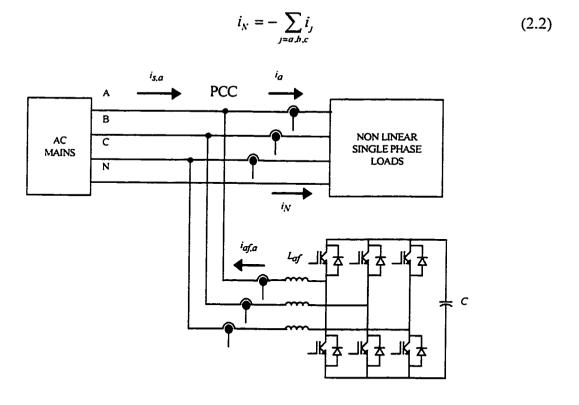

| Fig. 2.1  | Four wire half-bridge active filter                                                  | 21  |

| Fig. 2.2  | Three phase active filter                                                            | 22  |

| Fig. 2.3  | Single phase diode rectifier.                                                        | 26  |

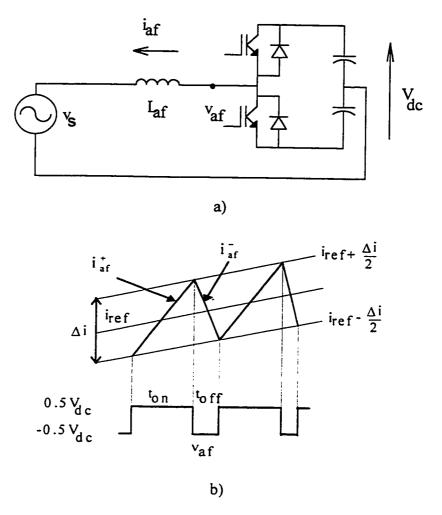

| Fig. 2.4  | (a) half-bridge active filter (b) output voltage and current                         | 29  |

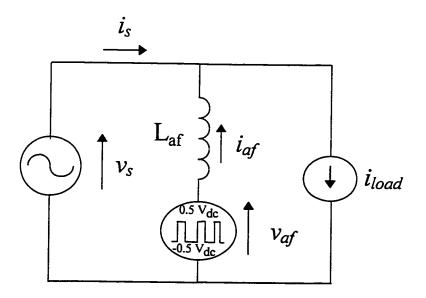

| Fig. 2.5  | Per phase equivalent circuit of the system                                           | 30  |

| Fig. 2.6  | Equivalent circuit of the system at high frequencies                                 | 32  |

| Fig. 2.7 | 7 Minimum active filter inductance in function of normalized switching               |

|----------|--------------------------------------------------------------------------------------|

|          | frequency and dc bus voltage as parameter34                                          |

| Fig. 2.8 | Flowchart showing selection procedure of the power circuit parameters37              |

| Fig. 3.1 | Peak current compensation capability of the active filter in function of the         |

|          | frequency with dc bus voltage as parameter45                                         |

| Fig. 3.2 | Effect of the dc bus ripple on the di/dt capability of the active filter with dc bus |

|          | voltage as parameter47                                                               |

| Fig. 3.3 | Required harmonic and reactive power from the active filter in function of load      |

|          | THDi49                                                                               |

| Fig. 3.4 | Supply voltage and the driving voltage across the inductor in function of time.52    |

| Fig. 3.5 | Simulation results. a) load current b) injected current c) supply current after      |

|          | compensation54                                                                       |

| Fig. 3.6 | Simulation results. Load and supply currents spectrum54                              |

| Fig. 4.1 | Active filter control block diagram57                                                |

| Fig. 4.2 | Harmonic current extraction options58                                                |

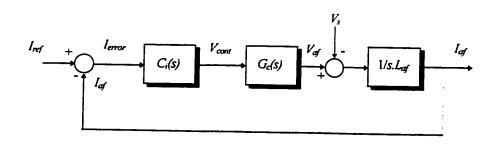

| Fig. 4.3 | Per phase current control                                                            |

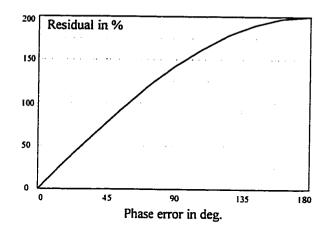

| Fig. 4.4 | The effect of phase error on residual current                                        |

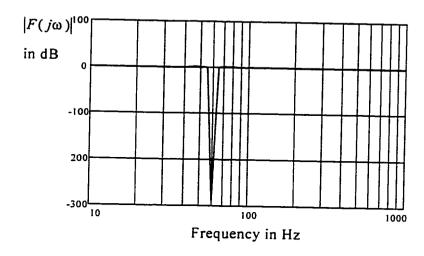

| Fig. 4.5 | Gain of the extraction circuit in function of frequency                              |

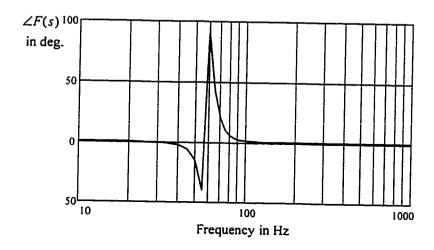

| Fig. 4.6 | Phase angle of the extraction circuit in function of frequency62                     |

| Fig. 4.7 | Current loop model64                                                                 |

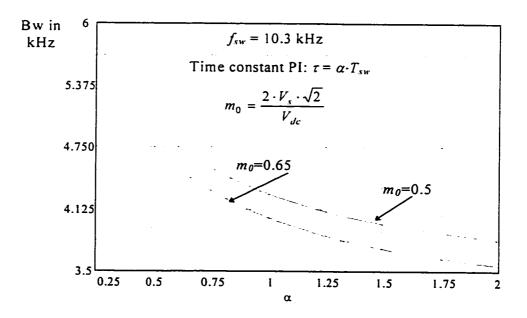

| Fig. 4.8 | Bandwidth of the active filter in function of time constant of the PI controller.66  |

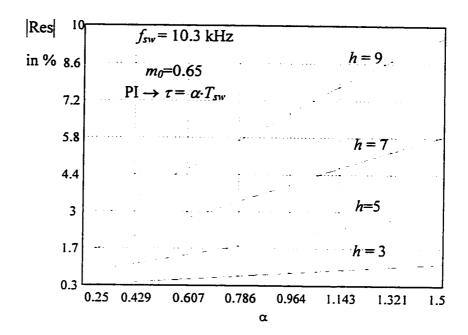

| Fig. 4.9  | Residual current introduced by the current loop in function of the PI controlle    | er  |

|-----------|------------------------------------------------------------------------------------|-----|

|           | time constant.                                                                     | 68  |

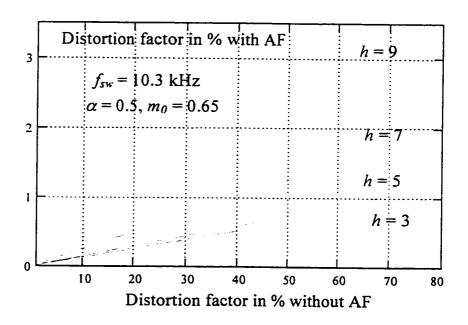

| Fig. 4.1  | 0 Individual distortion factor after compensation in function of distortion factor | r   |

|           | before compensation                                                                | 68  |

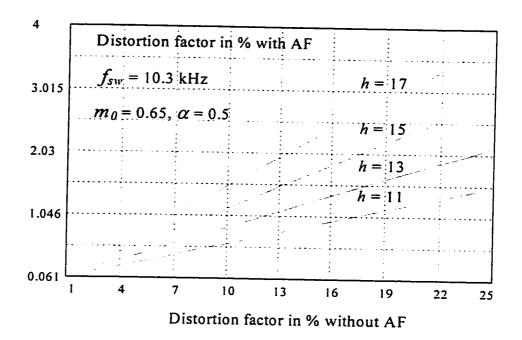

| Fig. 4.1  | 1 Individual distortion factor after compensation in function of distortion factor | r   |

|           | before compensation for high order harmonics.                                      | 69  |

| Fig. 4.12 | 2 Response of the current loop for a step change in load                           | 69  |

| Fig. 4.1  | 3 Voltage control block                                                            | 70  |

| Fig. 4. 1 | 4 Model of the voltage loop at no load                                             | 72  |

| Fig. 4.1: | 5 Dc bus behavior for a step change in reference.                                  | .73 |

| Fig. 4.10 | 6 Dynamic performance of the active filter for a sudden decrease in load a) dc     |     |

|           | bus voltage b) supply current.                                                     | .75 |

| Fig. 4.17 | 7 Dynamic performance of the active filter for a sudden increase of load a) dc     |     |

|           | voltage b) supply current.                                                         | .75 |

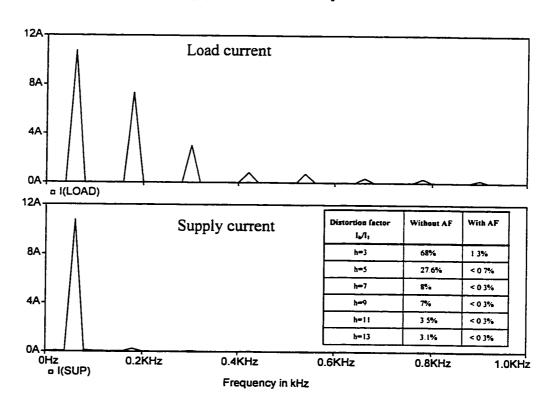

| Fig. 5.1  | Load and supply currents b) Spectrum of line and load currents.                    | .78 |

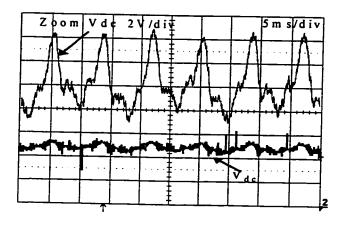

| Fig. 5.2  | Dc bus voltage                                                                     | .79 |

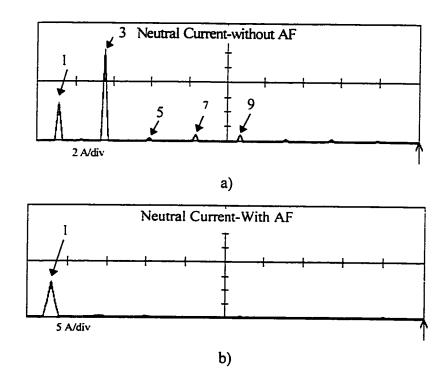

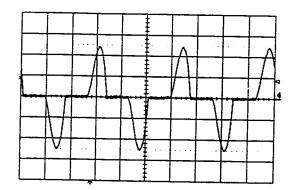

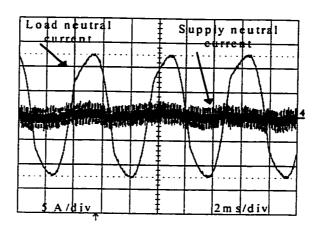

| Fig. 5.3  | Neutral current before and after compensation.                                     | .81 |

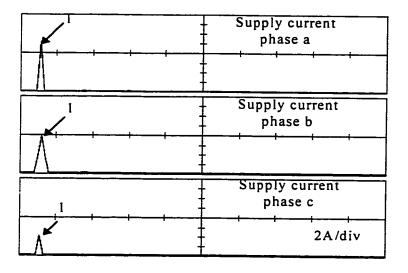

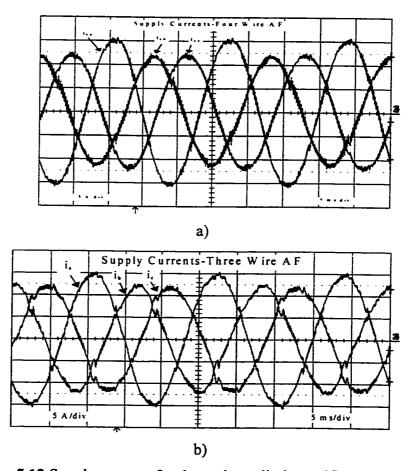

| Fig. 5.4  | Supply currents after compensation.                                                | .82 |

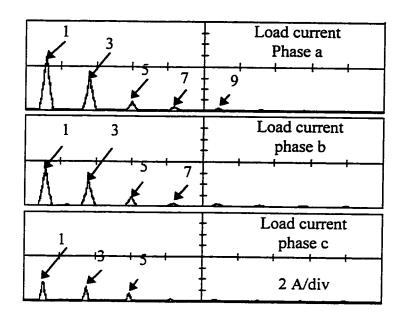

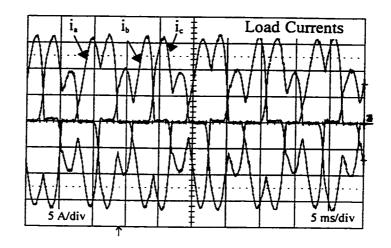

| Fig. 5.5  | a) Load currents b) supply currents.                                               | .82 |

| Fig. 5.6  | Neutral current with and without active filter                                     | .83 |

| Fig. 5.7  | Spectrum of the neutral current. a) load side b) supply side.                      | .83 |

| Fig. 5.8  | Spectrum of load currents.                                                         | .84 |

| Fig. 5.9  | Spectrum of supply side currents after compensation.                        | .84 |

|-----------|-----------------------------------------------------------------------------|-----|

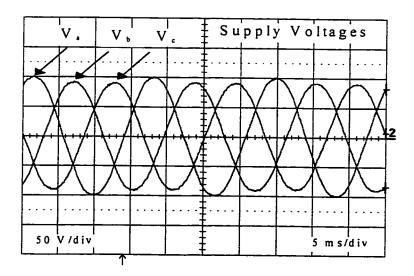

| Fig. 5.10 | Unbalanced ac mains (+10%). Line to neutral voltages.                       | .86 |

| Fig. 5.11 | Load currents before compensation.                                          | .87 |

| Fig. 5.12 | Supply currents for three phase diode rectifier load under unbalanced mains |     |

|           | (+10%). a) Four wire active filter b) Three wire active filter              | .87 |

| Fig. 5.13 | Dc bus voltage in four wire active filter.                                  | .88 |

| Fig. 5.14 | Load current.                                                               | .88 |

| Fig. 5.15 | Supply and load neutral currents with four wire active filter.              | .89 |

| Fig. 5.16 | Supply currents after compensation with four wire active filter.            | .89 |

| Fig. 5.17 | Supply current after compensation with three wire active filter             | 89  |

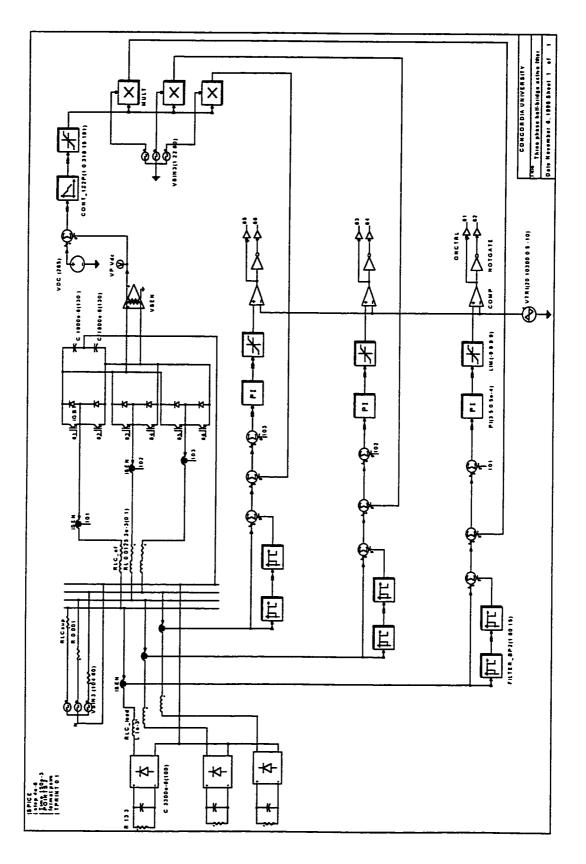

| Fig. B.1  | Complete simulation file1                                                   | 07  |

|           |                                                                             |     |

IV

#### LIST OF TABLES

- Table 1.1 IEEE-519 Maximum odd-harmonic current distortion.

- Table 1.2 IEEE-519 Voltage distortions limits

- Table 2.1 Typical neutral current amplitudes.

- Table 2.2 High frequency components of the inverter voltage for modulation index 0.9

- Table 3.1 Active filter design values

- Table 4.1 Power circuit and control system design values

- Table 5.1 Single phase diode bridge data

- Table 5.2 Active filter performance for different load conditions.

- Table 5.3 Three single phase diode bridges.

- Table 5.4 Four wire active filter (fsw = 10.3 kHz)

- Table 5.5 Active filter performance under unbalanced operation

- Table 5.6 Three single phase diode bridges

- Table 5.7 Performance of half bridge and three phase active filters.

## LIST OF PRINCIPAL SYMBOLS

| $A_r$             | Amphitude of the ripple component          |

|-------------------|--------------------------------------------|

| BW                | Current loop bandwidth                     |

| С                 | Active filter capacitor                    |

| $C_i$             | Current controller transfer function       |

| d                 | Ratio of rate of rise currents             |

| Ε                 | Energy stored in the capacitor             |

| f                 | Fundamental frequency                      |

| f <sub>b</sub>    | Frequency width of the filter passing band |

| f <sub>c</sub>    | Cut-off frequency                          |

| f <sub>jn</sub>   | High order frequency                       |

| f <sub>h</sub>    | Low order frequency                        |

| f <sub>sn</sub> . | Switching frequency                        |

| F                 | Extraction circuit transfer function       |

| $F_b$             | Band pass filter transfer function         |

| $G_c$             | Modulator transfer function                |

| 'n                | Harmonic order                             |

| Ч                 | Harmonic or distording power               |

- HD<sub>v</sub> Individual harmonic voltage distortion

- $H_{\nu}$  Voltage open loop transfer function

- I<sub>1</sub> Fundamental load current

- $\vec{I_1}$  Active filter fundamental current

- $i_j$  Load current in line j (j = a, b and c)

- $i_{j,1}$  Load fundamental current in line j (j = a, b and c)

- $i_{j,h}$  Load distording current in line j (j = a, b and c)

- $i_{af}$  Active filter current

- $i_{afj}$  Active filter current in line j (j = a, b and c)

- iaf.N Active filter current in the fourth wire

- $i_{dc1}$  Upper capacitor dc current

- $i_{dc2}$  Lower capacitor dc current

- *i*<sub>load</sub> Load current

- $i_N$  Load side neutral current

- $i_s$  Supply current

- $i_{s,j}$  Supply current in line j (j = a, b, and c)

- Isc Short circuit current at PCC

- $i_{s,N}$  Supply side neutral current

- k Current controller proportional term

- $k_v$  Voltage controller proportional term

- $L_{af}$  Active filter inductor

- $L_{\rm s}$  Supply impedance

| $m_0$                 | No load modulation index            |

|-----------------------|-------------------------------------|

| m                     | Modulation index at full load       |

| P                     | Real power                          |

| Q                     | Reactive power                      |

| Riosses               | Losses of the active filter         |

| $r_{\rm v}$           | Dc voltage regulation ratio         |

| s                     | Laplace operator                    |

| S                     | Apparent Power                      |

| t <sub>off</sub>      | Off time of a swich                 |

| ton                   | On time of a switch                 |

| $T_{sw}$              | switching period                    |

| V <sub>af</sub>       | Active filter output voltage        |

| V <sub>cont</sub>     | Modulating signal                   |

| $V_{dc}$              | Dc bus voltage                      |

| $\widetilde{V}_{dc}$  | Dc bus fluctuating voltage          |

| $V_{dc1}$             | Upper capacitor dc voltage          |

| $V_{dc2}$             | Lower capacitor dc voltage          |

| $\widetilde{V}_{dc1}$ | Upper capacitor fluctuating voltage |

| $\widetilde{V}_{dc2}$ | Lower capacitor fluctuating voltage |

| $V_s$                 | Supply voltage (line to neutral)    |

| $V_{tri}$             | Triangular wave amplitude           |

VAIII

| ω                 | Fundamental angular frequency                         |

|-------------------|-------------------------------------------------------|

| $\omega_0$        | Natural undamped frequency                            |

| $\omega_r$        | Angular frequency of the ripple component             |

| ΔΕ                | Energy variation across the capacitor                 |

| ∆i                | Peak to peak ripple current                           |

| $\Delta V_{dc}$   | Peak to peak dc bus ripple voltage                    |

| $\psi_{jn}$       | Active filter current phase angle at high frequencies |

| $\phi_h$          | Load current phase angle at low frequencies           |

| $arphi_r$         | Ripple component phase angle                          |

| τ                 | Current controller time constant                      |

| $	au_f$           | Low pass filter time constant                         |

| $	au_v$           | Voltage controller time constant                      |

| 5                 | Damping ratio                                         |

| $\mathcal{E}_{v}$ | Dc voltage error                                      |

#### LIST OF ACRONYMS

BJT Bipolar Junction Transistor

EPRI Electric Power Research Institute

GTO Gate Turn-Off Thyristor

IEEE Institute of Electrical and Electronic Engineers

IEC International Electrical Commission

IGBT Insulated Gate Bipolar Transistor

PCC Point of Common Coupling

PI Proportional-Integral

PWM Pulse Width Modulated

PSIM Power Electronic Circuit Simulator

rms Root Mean Square

THD Total harmonic distortion

VSI Voltage Source Inverter

#### Chapter 1

#### INTRODUCTION

#### 1.1 General

Electric power generated by the utilities is distributed to the consumer in the form of 60 Hz ac voltage. The utilities have a tight control on the design and operation of the equipment used for transmission and distribution, and can therefore keep frequency and voltage delivered to their customers within close limits. Unfortunately, an increasing portion of loads connected to the power system are comprise of power electronic converters. These loads are non linear and inject distorted currents in the network and consequently, through line drops, they generate harmonic voltage waveforms. Power converters such as rectifiers, power supplies and at a higher power level, arc furnaces are all sources of distortion. According to the Electric Power Research Institute (EPRI), in 1995, 35-40% of all electric power flows through electronic converters. This is expected to increase to 60% by the year 2000 [1].

The distortion, whether it is produced by a large single source or by the cumulative effect of many small loads, often propagates for miles along distribution feeders.

As the use of non linear power equipment is spreading, the degradation of the power quality in the utility networks is increasing and is becoming a major problem. Limiting the voltage distortion is therefore a concern for both utilities and consumers. For these reasons international agencies like IEEE and IEC are proposing or enforcing distortion limits [2] [3].

The simple block diagram of Fig. 1.1 illustrates the distortion problem due to harmonic at low and medium power levels.

Fig. 1.1 Harmonic distortion at PCC.

The utility is represented by an ideal ac voltage source in series with a lumped impedance representing lines and transformers. The voltage waveform at the point of common coupling is distorted due to harmonic current generated by the power electronic load or the non-linear load. This results in the following effects on the power system components:

- (i) Malfunction of harmonic sensitive loads;

- (ii) Increased losses in parallel connected capacitors, transformers, and motors;

- (iii) Improper operation of protection relays and circuit breakers.

# 1.2 Distortions in Power Networks

As shown in Fig. 1.2, the different sources of distortion in power networks conveniently can be divided into three classes according to the power level of the equipment and frequency range [4]: (a) sub-cycle distortion give rise to flicker and occur generally at the highest power level, they are caused by dynamic loads, such as arc furnaces, mill drives, mine winders, (b) high frequency distortion is caused by modern power electronic equipment, due to high rate of rise of current and voltage, and (c) intracycle distortion which covers a very wide range of power, and results from the power processing technique. The distortion generated by these last sources is usually termed "harmonics".

This work focuses on distortion caused by harmonics.

Fig. 1.2 Classification of distortion types in power networks.

#### 1.3 Harmonic Standards and Recommended Practices.

In view of the proliferation of the power electronic equipment connected to the utility distribution system, various international agencies have proposed limits on the magnitude of harmonic current injected into the supply to maintain acceptable power quality. The resulting guidelines and standards specify limits on the magnitudes of harmonic currents and harmonic voltage distortion at various harmonic frequencies. The most widely known are the IEEE-519 guidelines [2] in North America and the IEC-1000

Standard (formerly IEC 555) [3] prepared by the International Electrical Commission (in effect since 1996). However, the approach taken in these documents is drastically different. The IEC Standard imposes limits on individual equipment (up to 15 A, 220 V) connected to the supply, whereas the IEEE Recommended Practice addresses the issue of harmonic distortion at the point of common of coupling (PCC). Complying with the IEC Standard usually requires special design of the equipment itself [5] [6] [7]. However, meeting the IEEE guidelines can be achieved by means of filters, particularly active filters. Therefore, reference in this work will only be made to the IEEE guideline.

IEEE 519 proposes to designers of industrial plants harmonic limits as given in Table 1.1 and 1.2. For existing installations, harmonic mitigation techniques may have to be used to reduce distortion to the specified limits.

Table 1.1 IEEE-519 Maximum odd-harmonic current distortion.

% Limits of Harmonic Currents (Bus voltage @ PCC<69 KV)

| $I_{SC}/I_1$ | h<11 | 11 <h<17< th=""><th>17<h<23< th=""><th>23<h<35< th=""><th>35<h< th=""><th>THD</th></h<></th></h<35<></th></h<23<></th></h<17<> | 17 <h<23< th=""><th>23<h<35< th=""><th>35<h< th=""><th>THD</th></h<></th></h<35<></th></h<23<> | 23 <h<35< th=""><th>35<h< th=""><th>THD</th></h<></th></h<35<> | 35 <h< th=""><th>THD</th></h<> | THD  |

|--------------|------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------|------|

| <20          | 4.0  | 2.0                                                                                                                            | 1.5                                                                                            | 0.3                                                            | 0.3                            | 5.0  |

| 20-50        | 7.0  | 3.5                                                                                                                            | 2.5                                                                                            | 1.0                                                            | 0.5                            | 8.0  |

| 50-100       | 10.0 | 4.5                                                                                                                            | 4.0                                                                                            | 1.5                                                            | 0.7                            | 12.0 |

| 100-1000     | 12.0 | 5.5                                                                                                                            | 5.0                                                                                            | 2.0                                                            | 1.0                            | 15.0 |

| >1000        | 15.0 | 7.0                                                                                                                            | 6.0                                                                                            | 2.5                                                            | 1.4                            | 20.0 |

Notes: 1 I<sub>SC</sub> is the maximum short-circuit current @PCC.

2 I<sub>1</sub> is the maximum fundamental frequency load current@PCC.

Table 1.2 IEEE-519 Voltage distortions limits

| Bus Voltage @PCC | HDv(%) | THDv(%) |

|------------------|--------|---------|

| 69 KV and below  | 3.0    | 5.0     |

HDv=Individual harmonic voltage distortion.

#### 1.4 Power in Distorted AC Networks.

The active and reactive power components for electric circuits with sinusoidal and linear loads are well established. In the case of non-linear loads, however the use of the reactive and the harmonic power is an actual necessity for accomplishing reactive power compensation and/or harmonic filtering. The components of the electric power are shown in Fig. 1.3 assuming a sinusoidal voltage supply and a non-linear load [8]. In this case, the power factor  $(cos\phi)$  is the product of the distortion factor  $(II/I=cos\gamma)$  by displacement factor  $(cos\phi)$ :

Power Factor = Distortion factor × Displacement Factor

The displacement factor corresponds to the power factor of systems without harmonics. This factor may be called fundamental power factor, as it depends only on the current fundamental component. On the other hand, the power factor, as defined above, may be called total power factor, as it depends on fundamental and all harmonic components. Hence, harmonics cause lower power factor. The power components in distorted networks are represented in power tetrahedron, instead of the triangle as in the linear case, is shown in Fig. 1.4.

Fig. 1.3 Components of electric power

Fig. 1.4 Power tetrahedron.

From Fig. 1.3 and 1.4, various important factors are determined on the use of reactive power and harmonic compensation:

- (i) The reactive component is dependent only on the current component at fundamental frequency. The reactive component can be eliminated by using a conveniently chosen capacitor or inductor. The connection of an inductor or a capacitor component in parallel with load allows the generation of a current at fundamental frequency that absorbs or generates the reactive power required by the load;

- (ii) The distorting power is dependent on the current components with frequencies different from fundamental frequency (harmonics) and can not be eliminated by a single capacitor or inductor. The elimination of harmonic power depends on filters that work as a short-circuit for the harmonic current generated by the load.

#### 1.5 Methods of Dealing with Harmonics.

As an alternative to harmonic reduction, it has been suggested to derate transformers and oversize cables [9]. This could be an adequate solution in some cases. but since system configurations change, and thereby the harmonic profile of the system, the required amount of derating or oversizing could be difficult to predict. Also, this option does not prevent harmonics from entering the supply system. Therefore, a more appropriate method for harmonic mitigation is the use of filters.

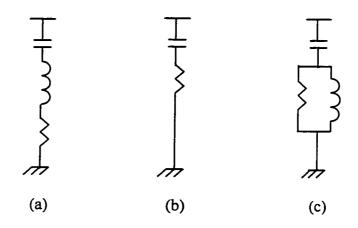

#### 1.5.1 Passive Filters

Passive filters in power systems as shown in Fig. 1.5, are usually shunt connected, the accepted practice being to connect a number of separate shunt branches across the terminals of the load or the plant. Each of these branches is tuned to one of the dominant harmonics, with a low pass branch added that exhibits low impedance for the remaining higher order harmonics [10].

Fig. 1.5 Passive filters. (a) single tuned filter (b) first order high-pass filter (c) second order high-pass filter.

Passive filters can prevent harmonics from entering a supply system, and are also useful in increasing power factor, but there are a number of considerations that are critical in this approach [10] [11]. For instance parallel and series resonance with ac line impedance may produce amplification in the harmonic current and voltage of the line at certain frequencies. Also, the effectiveness in attenuating harmonics are not dictated only by the passive filter itself, but depend on the source impedance. Moreover, it is difficult to decouple the effects of one load from those of other loads connected to the line and

compensate only for harmonic currents produced by this one load. Thus, it is often necessary to oversize passive filters in order to avoid overheating.

The classic solution of tuned passive filters therefore has serious limitations. Furthermore, with the widespread use of variable distorting electronic loads, harmonic tracking is not adequately achieved. Also the probability of encountering resonant conditions increases with the number of installed filtering units.

Active filtering techniques have therefore been proposed to overcome the problems associated with passive filters.

#### 1.5.2 Active Filtering

The first attempts to reduce harmonics without the use of conventional passive filters, were made by B. Bird, et al. [12]. Their design proposed changing the waveform of the current drawn by the load by injecting a third harmonic current, displaced in phase, into the converter itself. With this method however it is impossible to fully eliminate more than one harmonic.

It was Ametani's idea to expand the current injection method by proposing a technique to eliminate multiple harmonics [13] [14]. According to this theory, an active control circuit could be used to precisely shape the injected current. Ideally, this current would contain harmonic components of opposing phase, thus the harmonics would be neutralized, and only the fundamental component would remain. Despite the promising theoretical concept, Ametani was not successful in producing a practical circuit capable

of creating a precise current. The total harmonic distortion was reduced, but single harmonics were not completely eliminated.

On the other hand, Sasaki and Machida theorized that harmonics could be eliminated by using the principle of magnetic flux compensation [15]. This in principle, is the use of current to produce a flux to counteract the flux produced by the harmonics. Once again, theoretically, any number of harmonics could be directly eliminated. The current that would be required to eliminate waveform distortion caused by harmonics was calculated mathematically, but again, a practical control circuit was not realized.

Over the last ten to twelve years the remarkable progress in capacity and switching performance of devices such as bipolar transistors (BJT), gate turn-off thyristors (GTO) and insulated gate bipolar transistors (IGBT), has spurred in the study of active power filters for harmonic compensation. In addition, advances in topologies and controls schemes for static PWM converters have enabled active power filter using these converters to generate specified harmonic currents, such as created by non linear loads.

#### 1.6 Literature Review

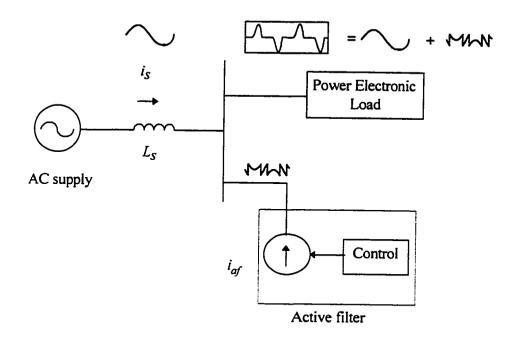

#### 1.6.1 Shunt Active Filters.

The shunt active filter approach [16] [17] [18] is based on the principle of injection of harmonic currents into the ac system, of the same amplitude but opposite in phase to that of the load harmonic currents. Fig. 1.5 shows the active power filter

compensation principle, which is controlled in a closed loop manner to actively shape the source current into sinusoid.

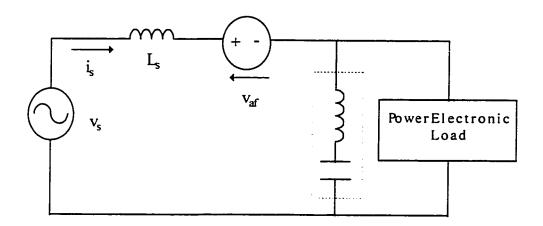

Fig. 1.6 Principle of shunt connected active filters.

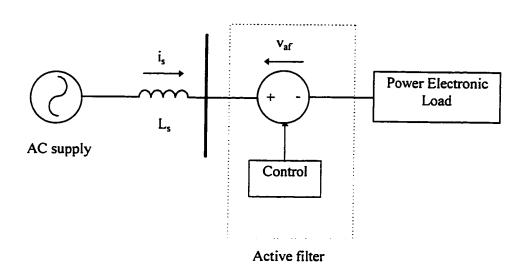

#### 1.6.2 Series Active Filters

In series active filter configuration [10], a voltage source,  $v_{af}$ , is constructed in such a way that when its voltage is added to the load voltage, the distorted voltage is canceled, thus resulting of a sinusoidal voltage at the PCC. Fig. 1.7 shows the series active filter compensation principle.

Fig. 1.7 Series connected active filter.

For harmonic compensation, both shunt and series active filter have much smaller ratings than the apparent power of the load. The shunt active filter is rated for supply voltage, but a reduced current. In the case of series dynamic filters, the rated load current passes through the filter but the rated voltage is again lower. Therefore, harmonic minimization can be implemented with converters having a reduced power rating.

#### 1.6.3 Hybrid Active Filters.

Hybrid structures were proposed for harmonic compensation of large rated loads in high voltage networks. Hybrid active filters configurations, combines passive and active filters [20]. These filters improve the compensation characteristics of the passive filters and thus realize a reduction in the rating of the active filter. They are particularly suited in installations where L-C tuned passive filters already exist.

In the hybrid series configuration, the series voltage injection is to be regarded as an isolator, either determining the harmonic currents to be supplied to the non-linear load or the harmonic currents that will be absorbed by the tuned LC-filters. Fig. 1.7 and Fig. 1.8 show two hybrid active filter configurations, series [21] [22] [23] [24] and shunt [25] [26] [27] [28] [29] [30]. In the first case, the injected voltage is in series, Fig. 1.7, and in the second case it is in series with the shunt passive filter Fig. 1.8.

Fig. 1.8 Hybrid series active filter.

Fig. 1.9 Hybrid shunt active filter.

### 1.6.4 Active Filter Topologies.

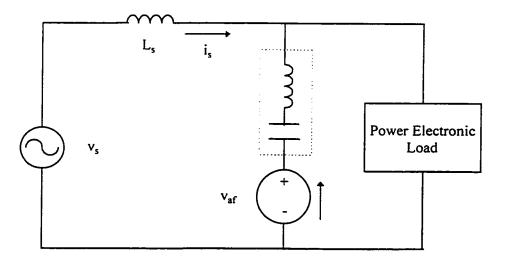

There are two types of power circuits [31] for the active filters as shown in Fig. 1.9, current and voltage source types. The voltage-type inverter uses a capacitor with a regulated dc voltage [32] [33], Fig. 1.9 (a), while the current-type approach uses a reactor supplied with a regulated dc current [34] [35] [36], Fig. 1.9 (b). One of the main advantage of voltage type converters is that they are easily expandable and are less expensive than current-type converters.

Fig. 1.10 Main topologies of active filters. (a) voltage-type (b) current-type.

### 1.6.6 Control Aspects.

Compensation of harmonics can be accomplished in time-domain or frequency domain [17]. First approach is based upon "on line" computation of an instantaneous error function, while the second case uses the principle of Fourier analysis and periodicity of the distorted waveform to be corrected. The error-function in time-domain could be computed in the following ways: a) extraction of the fundamental component from the distorted waveform through a notch filter [17], b) instantaneous reactive power compensation, which uses an instantaneous orthogonal power transformation on both the actual and the fundamental components of voltage and current to produce a power function [37][38]. The difference between these two transformations is the error, and c) synchronous reference frame approach [21] [39]. Many PWM strategies exist (for compensation in the time-domain) to generate the gating signals to the switches and thereby to reconstruct the distorted current. The most widely used PWM strategies are [17] [40]: a) triangular wave or ramp comparison, b) hysteresis, and c) deadbeat.

### 1.7 Problem Statement.

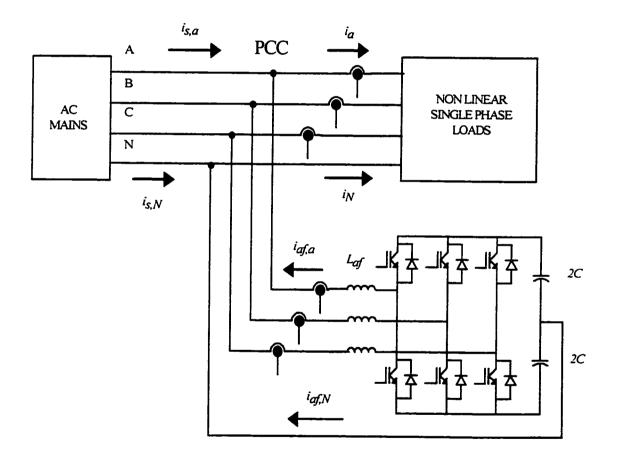

The conventional three phase active filter, in a bridge configuration is well suited for three phase balanced loads, supplied from a three wire ac mains [31] [35] [36] [41] [42] [43] [37]. Nevertheless, in a number of industrial and commercial applications, power is distributed through three phase, four wire systems. Furthermore, if non-linear single-phase loads are present, or the three phase load is unbalanced, the line currents,

both in terms of fundamental and harmonic components, are unbalanced and neutral currents flow. In unbalanced load condition, the sum of the instantaneous harmonic currents is not equal to zero. As a result, phase interactions between the lines appear and the three-phase three-wire active filter cannot adequately reduce or eliminate line harmonics in this situation. The problem points to the necessity of having per phase based current controllers and converters so that:

- i) independent harmonic reduction is achieved in each phase:

- ii) reduction of the neutral current is achieved without disturbing the operation of the active filter.

To eliminate the neutral current in three phase four wire systems, [44] has proposed an additional active filter, while [45] [46] [47] [48] [49] proposed an eight switch active filter topology, which is complicated to implement. Also [45] [46] reported a three phase half-bridge topology, which uses variable hysteresis current mode controller. Other suggested methods include the use of complicated zigzag transformer connections as reported in [50].

### 1.8 Scope and Contribution of This Thesis

This thesis is a contribution to the design and implementation of a three phase four wire active filter. An industrial-type experimental unit rated 208V/15A, was developed and used for testing and validation purposes. Features of the system include:

(i) The power circuit is a force-commutated pulse-width modulated voltage source

inverter (PWM-VSI), based on half-bridge configuration, using three single phase modules with a center tap capacitor, (ii) Per phase based current controllers and power converters are implemented to allow control of individual phase currents. The proposed implementation uses the ramp comparison technique that allows operation under constant switching frequency achieving better switching pattern than hysteresis control [51].

Specific contributions include:

- (i) A detailed analytical treatment and a systematic approach to design the power circuit for various modes of operation is presented [52] [53]. The treatment is general and valid for other type of voltage source configurations;

- (ii) The residual currents and individual harmonic distortion factors after compensation are determined theoretically [54]. The feasibility is tested through computer simulation on PSIM [55] software package;

- (iii) Thorough testing and validation is carried out on the experimental unit to verify the theoretical results.

### 1.9 Outline of This Thesis

The thesis is organized as follows:

Chapter 2 analyzes the three phase three wire and three phase four wire voltage source active filters. Working constraints are derived. Design guidelines showing the selection of various power components such as the synchronous link reactor, dc bus voltage and the switching frequency are included.

Chapter 3 quantifies the required harmonic power and discusses rating issues of the active filter and power components. A design procedure is presented to select the dc bus capacitor that covers all modes of operation. The effect of dc bus ripple on the compensation capacity is analyzed. A typical example is included to illustrate the design approach followed by simulation results showing the static performance of the active filter.

Chapter 4 covers modeling of the voltage and current blocks, and control system design, quantifies the residual harmonic components, and gives simulation results showing the dynamic performance of the active filter.

Chapter 5 validates the theoretical concepts by simulation and experimentally. Performance of the active filter is investigated under different modes of operation: (a) single phase load, (b) balanced load (c) unbalanced load, and (d) mains voltage unbalance. The active filter in the three phase full bridge configuration is tested under the same modes and its performance is compared to the proposed topology.

Chapter 6 concludes the thesis and identifies some areas for future research work.

### Chapter 2

# THREE PHASE SHUNT CONNECTED VOLTAGE SOURCE ACTIVE FILTERS

### 2.1 Introduction

With improvements in power and control circuits, active filters are becoming a viable alternative to passive filters for meeting harmonic distortion limits. The superior performance of active filters as compared to conventional passive L-C filters, is in fact due to their filtering characteristics which is independent of the source impedance [10]. This chapter describes the operation of three-phase four wire active filters for the general case. The active filter under study is connected in shunt with the load and its structure is based on a self commutated pulse-width modulated voltage source inverter connected to a self controlled dc bus. The chapter also investigated the neutral current for unbalanced load conditions when the half-bridge topology is used. Design issues such as switching frequency, dc bus voltage and line inductor values are detailed. The quality of the supply current, the magnitude and components of the neutral currents are also investigated.

### 2.2 Active Filter Configuration

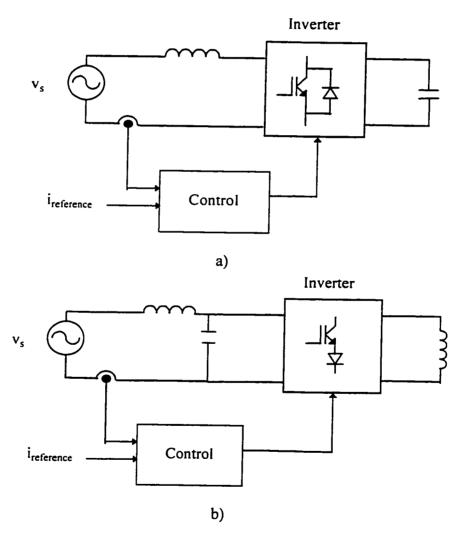

The general topology for the four wire active filter is given in Fig. 2.1. The dc bus uses a common capacitor, with the center-tap connected to the line neutral, thus providing a return path for the neutral current. The PWM pattern is generated using a constant frequency ramp comparison technique [40] [56]. The ac side of the converter is connected to the mains via a synchronous link reactor,  $L_{af}$ , Fig. 2.1, which also serves as a first order low-pass filter.

Fig. 2.1 Four wire half-bridge active filter.

### 2.3 Three Phase Active Filter

The operation of the conventional three phase active filter, Fig. 2.2, is investigated for the general case. It is assumed that the supply feeds three different single phase non-linear loads, connected between the lines and the neutral. The currents drawn by the loads are non sinusoidal and have all the odd harmonics including the triplen.

The load currents are expressed as:

$$i_i = i_{i,1} + i_{i,h} \tag{2.1}$$

Where j = phase a, b and c.  $i_{j,1}$  is the fundamental component of the load current, and  $i_{j,h}$  is the distorting current for phase j.

Neutral current before compensation is the sum of phase currents:

Fig. 2.2 Three phase active filter.

For the general case, each three phase system of harmonic order h, is an unbalanced system. By the symmetrical components theory each unbalanced system can be decomposed in several balanced harmonic systems of the same harmonic order and of positive,  $i_{j,h}^+$ , negative,  $i_{j,h}^-$ , and zero sequence,  $i_{j,h}^0$ .

$$i_{j,h} = i_{j,h}^+ + i_{j,h}^- + i_{j,h}^0 (2.3)$$

The absence of fourth wire in the active filter makes the zero sequence current nil.

$$i_{af}^0 = 0 (2.4)$$

The active filter currents are given by :

$$i_{af,j} = i_{j,h}^+ + i_{j,h}^- \tag{2.5}$$

Supply side currents are given by:

$$i_{s,i} = i_i - i_{af,i} (2.6)$$

Combining (2.1), (2.5) and (2.6) gives:

$$i_{s,j} = i_{j,1} + i_{j,h}^0 (2.7)$$

The neutral current is given by:

$$i_N = -\left\{i_{a,1}^0 + i_{a,h}^0\right\} = -i_a^0 \tag{2.8}$$

The theoretical analysis shows that with a three wire three phase active filter:

- i) the line current harmonics remain partially uncompensated, (2.7).

- ii) the amplitude of the harmonic currents in the neutral wire is not reduced.

Moreover, the equations (2.7) and (2.8) show that the active filter cannot compensate the line currents even when balanced non linear single phase loads are present, since triplen components cannot be supplied.

### 2.4 Four Wire Half-Bridge Topology

### A. Operation

The connection of the capacitor midpoint to the neutral wire allows implementation of per-phase based current regulators, hence the phases are totally decoupled.

The currents generated by the active filter are given by:

$$i_{af,J} = i_{J,h} \tag{2.9}$$

Supply side currents are obtained from (2.7) and (2.9):

$$i_{s,j} = i_{j,1} \tag{2.10}$$

Current in the neutral wire at the supply side is given by:

$$i_{s,N} = -\sum_{j=a,b,c} i_{s,j} \tag{2.11}$$

Combining (2.10) and (2.11) yields:

$$i_{s,N} = -\sum_{j=a,b,c} i_{j,1} \tag{2.12}$$

Comparing equations (2.2) and (2.12) one see that only the fundamental component remains in the neutral wire. Comparing the magnitude of the neutral current before and after compensation yields:

$$\frac{I_{s,N}}{I_N} < 1 \tag{2.13}$$

The theoretical analysis shows that in the general case:

- i) the line currents are compensated, equation (2.10);

- ii) the amplitude of the neutral current is reduced for unbalanced loads, equation (2.13).

### B. Neutral Current

The current in the neutral wire before compensation contains all the odd harmonics including the triplen, its expression is given by:

$$i_{N} = \sum_{h=1}^{\infty} I_{N,2n-1} \cdot \sqrt{2} \cdot \sin[(2h-1)\omega t + \phi_{h}]$$

(2.14)

The rms value of  $i_N$  is given by:

$$I_N = \sqrt{\sum_{h=1}^{\infty} I_{N,2h-1}^2}$$

(2.15)

The current in the fourth wire of the active filter supplies all the odd harmonics including the triplen, but excluding the fundamental component. After compensation the current in the neutral wire has a 60 Hz component which is the contribution of unbalanced line currents. The rms value of the current in the neutral wire at the supply side is given by [9]:

$$I_{s,N} = \sqrt{I_{a,1}^2 + I_{b,1}^2 + I_{c,1}^2 - (I_{a,1} \cdot I_{b,1}) - (I_{a,1} \cdot I_{c,1}) - (I_{b,1} \cdot I_{c,1})}$$

(2.16)

Usually, when the loads are balanced, the neutral current contains only triplen harmonics. It follows that after compensation, the neutral wire is exempt of low frequency components. On the other hand, the return wire of the active filter carries the current present in the neutral wire of the load. To illustrate the problems associated with typical single phase non-linear loads, diode rectifiers with capacitive output are considered, as shown in Fig. 2.3.

With rectifier conduction angles of 60°, the magnitude of the neutral current could reach 1.73 times the phase current for balanced loads [9]. Table 2.1 gives the magnitude of the neutral current for two cases. The magnitude of the neutral current is 127 % of the line current when the loads are unbalanced. The worst case occurs when the load are balanced, since its magnitude reaches a value of 165 % of the line current.

Fig. 2.3 Single phase diode rectifier.

Table 2.1 Typical neutral current amplitudes.

| Harmonic<br>h         | Single<br>Phase load | Balanced Loads<br>(3×1φ)<br>Neutral Current | Typical<br>Unbalanced Loads<br>Neutral Current |

|-----------------------|----------------------|---------------------------------------------|------------------------------------------------|

| 1                     | 1.0                  |                                             | 0.57                                           |

| 3                     | 0.68                 | 2.04                                        | 1.46                                           |

| 5                     | 0.287                |                                             | 0.11                                           |

| 7                     | 0.083                |                                             | 0.11                                           |

| 9                     | 0.073                | 0.0219                                      | 0.127                                          |

| 11                    | 0.036                |                                             | 0.032                                          |

| $I_a$                 | 1.25                 |                                             |                                                |

| $I_N$                 |                      | 2.06                                        | 1.58                                           |

| $I_{\rm N}/I_{\rm a}$ |                      | 1.65                                        | 1.264                                          |

### 2.5 Power Circuit Design

The selection of the ac link reactor and the dc capacitor value affects directly the performance of the active filter. The design criteria is based upon specifying the filter inductor such that it keeps the high frequency ripple of the inverter ac output current small, and at the same time ensuring sufficient driving voltage to generate the rate of rise of the distorting current.

The following assumptions are made when the power circuit is analyzed:

- i) the converter switching elements are ideal;

- ii) the passive elements are ideal;

- iii) the dc bus voltage is ripple free.

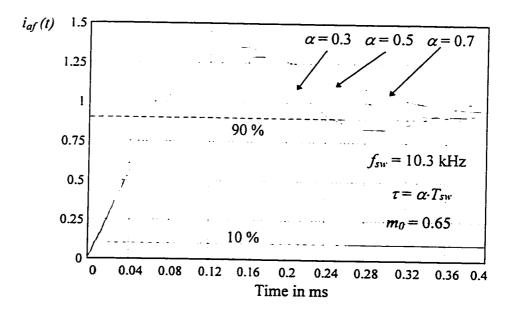

## 2.5.1 Current Ripple Generated by the Half-Bridge Active Filter

The switches of one leg of the inverter are gated in a complementary fashion, yielding a bipolar output voltage as shown in Fig 2.4 a). The output current and voltage of the inverter are shown in Fig. 2.4 b).

When upper switch is gated.

$$\frac{di_{af}^{+}}{dt} = \frac{0.5 \cdot V_{dc} - v_{s}(t)}{L_{af}}$$

(2.17)

When lower switch is gated

$$\frac{di_{af}^{-}}{dt} = \frac{-0.5 \cdot V_{dc} - v_{s}(t)}{L_{af}}$$

(2.18)

From Fig. 2.4 we have:

$$\frac{d}{dt}(i_{af}^+ - i_{ref}) = \frac{\Delta i}{t_{out}}$$

(2.19)

$$\frac{d}{dt}(i_{af}^{-}-i_{ref}) = \frac{\Delta i}{t_{off}}$$

(2.20)

Using the fact that:

$$f_{SW} = \frac{1}{T_{sw}} = \frac{1}{t_{on} + t_{off}}$$

(2.21)

Combining equations (2.14), (2.15), (2.16) and (2.17) gives:

$$\Delta i = \frac{V_{dc}}{4 \cdot f_{sw} \cdot L_{af}} \left[ 1 - \frac{4}{V_{dc}^2} (v_s + L_{af} \cdot \frac{di_{ref}}{dt})^2 \right]$$

(2.22)

Fig. 2.4 (a) half-bridge active filter (b) output voltage and current.

Maximum ripple is expressed as:

$$\Delta i_{\text{max}} = \frac{V_{dc}}{4 \cdot L_{af} \cdot f_{SW}} \tag{2.23}$$

The above expression shows that the current ripple increases when the switching frequency and/or the reactor value decreases. Also, the current ripple increases when the dc bus voltage increases.

### 2.5.3 Reactor and DC Bus Voltage Selection

The ripple generated by the converter must be limited to an acceptable level in order to achieve a low total harmonic distortion current in the mains. With the ramp comparison technique, the spectrum of the output current is well defined, hence its rms value may be obtained by simply calculating the value of the individual harmonic at specified frequencies. The equivalent circuit of the system is shown in Fig. 2.5.

The output voltage generated by the converter is the sum of the voltage,  $G_c \cdot V_{cont}$ , that produces the required injected current and the high frequency components. The output voltage,  $v_{af}$  can be written as:

$$v_{af}(t) = G_c \cdot v_{con}(t) + \sum_{j+n=odd} V_{af,f_{jn}} \cdot \sqrt{2} \cdot sin(2 \cdot \pi \cdot f_{jn} \cdot t + \psi_{jn})$$

(2.24)

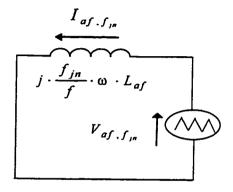

Fig. 2.5 Per phase equivalent circuit of the system.

Where  $G_c$  is the gain of the converter and is defined as the ratio of half the dc bus voltage to the amplitude of the triangular waveform,  $v_{cont}$  is the control voltage or the modulating signal,  $V_{af,f_m}$  is the rms value of the active filter output voltage at high frequencies,  $f_{jn}$ . The high frequency harmonics are generated as a consequence of switching action of the converter.

The high frequency harmonic orders  $f_{in}$  are given by :

$$f_{in} = j \cdot f_{sw} \pm n \cdot f \tag{2.25}$$

It is assumed that the active filter cancels the harmonic component of the load completely, hence the high frequency harmonic currents are reflected back to the supply side.

The supply side current is given:

$$i_{s}(t) = I_{1} \cdot \sqrt{2} \cdot \sin(\omega t + \phi_{1})$$

$$+ \sum_{j+n=odd} I_{af \cdot f_{jn}} \cdot \sqrt{2} \cdot \sin(2 \cdot \pi \cdot f_{jn} \cdot t + \psi_{jn})$$

(2.26)

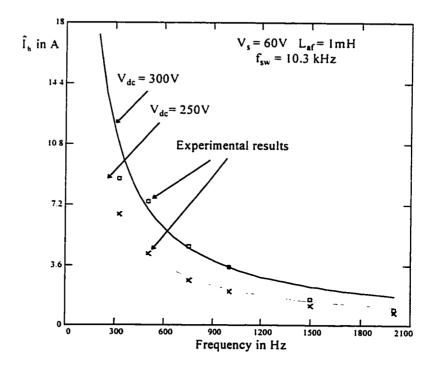

Using the equivalent circuit of the active filter as shown in Fig. 2.6. The rms value of individual harmonic currents at frequencies  $f_{in}$  is expressed as:

$$I_{af,f_{pr}} = \frac{V_{af,f_{pr}}}{2 \cdot \pi \cdot f_{pr} \cdot L_{af}} \tag{2.27}$$

Rearranging equation (2.27) gives:

$$\frac{I_{af, f_{jn}}}{I_{1}} = \frac{1}{m_{0}} \cdot \frac{V_{af, f_{jn}}}{V_{dc} / 2} \cdot \frac{f}{f_{jn}} \cdot \sqrt{2} \cdot \frac{1}{\frac{\omega \cdot L_{af}}{V_{x} / I_{1}}}$$

(2.28)

Fig. 2.6 Equivalent circuit of the system at high frequencies.

$m_0$  is the modulation index at no load, and is defined as the ratio of peak output voltage to half the dc bus voltage.

$$m_0 = \frac{2 \cdot V_s \cdot \sqrt{2}}{V_{ds}} < 1 \tag{2.29}$$

The value of the synchronous link reactor in pu in function of the ripple current becomes:

$$\frac{\omega L_{af}}{V_{c}/I_{1}} = \frac{1}{m_{0}} \cdot \frac{\sqrt{\sum_{j+n=odd} \left[\frac{f}{f_{jn}} \cdot \left(\frac{\hat{V}_{af,f_{jn}}}{V_{dc}/2}\right)\right]^{2}}}{\left(I_{af,ripple}\right)_{rms}/I_{1}}$$

(2.30)

Where  $(I_{af,ripple})_{rms}$  is defined as:

$$(I_{af,ripple})_{rms} = \sqrt{\sum_{j+n=odd}^{\infty} I_{af,f_{ph}}^{2}}$$

(2.31)

Equation (2.30), shows that the value of the reactor depends on the dc bus voltage and the harmonic content of the converter voltage which in turn depends on the modulation index. Table 2.2 gives the value of these harmonics for a modulation index 0.9. The largest component of the ripple current in the active filter is contributed by the harmonic at the switching frequency,  $f_{sw}$ , as shown in Table 2.2.

Table 2.2 High frequency components of the inverter voltage for modulation index 0.9

| $f_{jn}=jf_{sw}\pm nf$         | $\hat{V}_{af.f_m} / V_{dc}/2$ |

|--------------------------------|-------------------------------|

| $f_{sw}$                       | 0.71                          |

| $f_{sw} \pm 2f$                | 0.269                         |

| $2 \cdot f_{sw} \pm f$         | 0.248                         |

| $2 \cdot f_{sw} \pm 3 \cdot f$ | 0.176                         |

| $2f_{sw} \pm 5f$               | 0.023                         |

| $3f_{sw}$                      | 0.142                         |

| $3 \cdot f_{sw} \pm 2 \cdot f$ | 0.119                         |

| $3 \cdot f_{sw} \pm 4 \cdot f$ | 0.13                          |

| $3 \cdot f_{sw} \pm 6 \cdot f$ | 0.03                          |

| $4 \cdot f_{sw} \pm 1 \cdot f$ | 0.173                         |

| $4 \cdot f_{sw} \pm 3 \cdot f$ | 0.062                         |

| $4 \cdot f_{sw} \pm 5 \cdot f$ | 0.101                         |

| $4 \cdot f_{sw} \pm 7 \cdot f$ | 0.033                         |

|                                |                               |

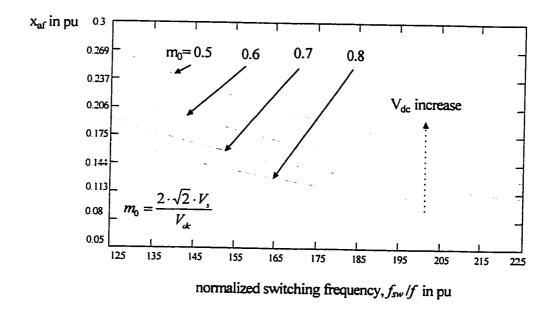

The minimum value of the synchronous link reactor can be found by forcing the ripple,  $\left(I_{af,ripple}\right)_{rms}/I_1$ , to less than 5% for the maximum load current,  $I_1$ , and by choosing a modulation index equal to 0.9 for the same load condition. For a given modulation frequency, increasing the dc bus voltage, will result in a higher value for the reactor. On the other hand, for a given dc bus voltage, increasing the modulation frequency, decreases the value of the inductor, as shown in Fig. 2.7. Equation (2.30) gave the first relation between the dc bus voltage and the reactor. An additional equation is required to compute both  $L_{af}$  and  $V_{dc}$  values. The second relation is obtained by using the fact that the modulation is less than one at maximum load condition (in our case 0.9).

Fig. 2.7 Minimum active filter inductance in function of normalized switching frequency and dc bus voltage as parameter.

55

The modulation index is defined as the ratio between the inverter voltage and half the dc bus voltage.

$$m = \frac{\left(v_{af}(t)\right)_{\text{max}}}{V_{dc}/2} = \frac{\left(V_s \cdot \sqrt{2} \cdot \sin \omega t + L_{af} \cdot \frac{di_{load J_t}}{dt}\right)_{\text{max}}}{V_{dc}/2} \tag{2.32}$$

In the general case if the instant at which the maximum occurs in (2.32) is not known, then the worst case occurs when the reactor introduces a voltage drop that equals the supply voltage, hence the slope of the distorting current is at its maximum and has positive sign:

$$\left(\frac{di}{dt}\right)_{load.Ji} = \frac{0.5 \cdot V_{dc}.m - V_{s} \cdot \sqrt{2}}{L_{at}}$$

(2.33)

In other words, (2.33) shows that the di/dt generated by the inverter is finite and is greater than the di/dt generated by the harmonic component of the load current.

$$\left(\frac{di}{dt}\right)_{local h} < \left(\frac{di}{dt}\right)_{local h} \tag{2.34}$$

The design equations show that there are a compromise to make when choosing the reactor and the dc voltage values. Small reactor,  $L_{af}$ , is required to generate high di/dt, however decreasing the reactor increases the ripple current, which in turn is reflected to the mains. As a consequence the supply side exhibits higher total harmonic distortion. Also, a similar effect is observed with  $V_{dc}$ . A high dc voltage is required to obtain a sufficient driving voltage capable of producing a high di/dt, which has two immediate effects: i) the ripple current of the converter is increased, ii) the switches must be selected with higher blocking capability in terms of voltage.

- -

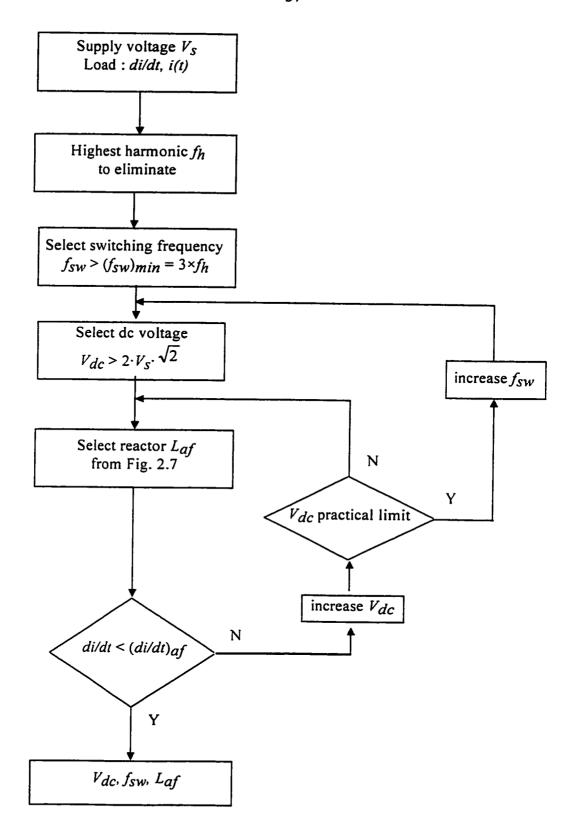

The flowchart of Fig. 2.8 shows the selection procedure of the switching frequency, the synchronous link reactor and the dc bus voltage values. These three parameters are determined knowing the supply voltage, the harmonic content of the load, and the rate of rise of the distorting current. On the other hand, the flowchart shows that an iteration is required to extract these values, and the dc voltage is not permitted to exceed the practical limit. The practical limit is the maximum blocking capability of the switches and is dependent on the technology available. For example, IGBT type switches have maximum blocking capability of twelve hundred volts, and if a fifty percent of safety margin is taken, then the practical limit as referred to flowchart becomes eight hundred volts.

The design procedure as presented in Fig. 2.8 requires an initial guess of the switching frequency, which is dependent from the highest harmonic to eliminate [16]. From Table 2.2, the high frequency components of the active filter current are mainly at.

$$f_{sw}, f_{sw} \pm 2f, 2f_{sw} \pm f, 2f_{sw} \pm 3f, 2f_{sw} \pm 5f, \dots$$

The lowest frequency is  $f_{sw}$ -2·f, and  $f_{sw}$  must be chosen so that this frequency becomes higher than the highest frequency of harmonics to be eliminated. Thus

$$f < f_{\text{vw}} - 2 \cdot f \tag{2.35}$$

Hence,  $f_{sw}$  should be chosen at least three times the highest frequency of harmonics to be suppressed. For example, if the highest frequency of harmonics is 1260 Hz (21<sup>st</sup> harmonic), the frequency of the triangular wave should be 3780 Hz or higher.

The design equations are general and are valid for any type of non-linear load and regardless of the combination, such as balanced and unbalanced loads.

Fig. 2.8 Flowchart showing selection procedure of the power circuit parameters.

### 2.6 Conclusions

The chapter has presented the power circuit configuration and the working principles for different modes of operation. Design equations for the power circuit were derived in the general case and for any type of load. The analysis demonstrates that with the proposed configuration the current in the neutral wire is substantially decreased. Moreover, the chapter shows that the switching frequency, the synchronous link reactor and the dc voltage are related to each other and that they depended upon the parameters of the load. Accordingly a systematic design procedure is presented to select the power circuit parameters in order to obtain the appropriate parameters of the active filter.

### Chapter 3

# RATING ISSUES AND DC BUS CAPACITOR SELECTION

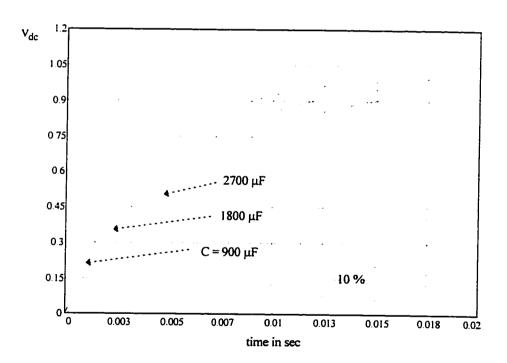

### 3.1 Introduction

The previous chapter has presented a general design procedure to select the power components. A constant dc bus voltage has been assumed. However, the force commutated voltage source inverter consists of a self controlled dc bus, and capacitors are used as a reservoir of energy to maintain constant the dc voltage and to reduce the voltage fluctuation under load variation. This chapter presents a design procedure to select the capacitor value in such a way as to ensure the proper operation of the harmonic compensator for various load environments. The impact of the ripple voltage on the active filter compensation capability is also investigated. Rating issues of the active filter and the power components are discussed in detail as a function of various system parameters. An example is detailed to illustrate the complete design process for the power circuit. Finally, simulation results are presented to show the static performance of the active filter and to confirm theoretical calculations.

### 3.2 Design of the Capacitors

Under steady state operating conditions the dc voltage control loop keeps the dc voltage constant. However, transient changes in the instantaneous power absorbed by the load generate voltage fluctuations across the dc capacitor. The amplitude of these voltage fluctuations can be controlled effectively with an appropriate dc capacitor value [57]:

When designing the capacitor the following assumptions are made:

- ii) in steady state, the fluctuating voltage of the capacitor is very small compared to the average voltage.

- ii) the converter is lossless.

The voltage fluctuation in the dc capacitor under steady state is due to the variation of the harmonic power flow [58] [57] and the energy stored in the inductor. The current in the inductor has two components, the distorted current and the ripple current superimposed on the reference due to the switching action of the converter. The first current is a periodic ac waveform, hence the energy variation is null. The second part consist of the energy that the inductor discharges in the capacitor within one switching period. During the on state, energy is accumulated across the inductor and this energy is absorbed by the capacitor during the off state. Because the switching frequency is high, the effect of this energy variation on the dc bus is neglected.

For the single phase case, by equalizing the instantaneous input power to the instantaneous output power we obtain.

$$v_{s} \cdot i_{af} = i_{dc1} \cdot v_{dc1} + i_{dc2} \cdot v_{dc2}$$

(3.1)

$$v_{dc1} = V_{dc1} + \tilde{V}_{dc1}$$

and  $v_{dc2} = V_{dc2} + \tilde{V}_{dc2}$  (3.2)

$$i_{dc1} = 2 \cdot C \cdot \frac{d\widetilde{V}_{dc1}}{dt}$$

and  $i_{dc2} = 2 \cdot C \cdot \frac{d\widetilde{V}_{dc2}}{dt}$  (3.3)

Using the fact that the average dc voltage of each capacitor are approximately equal, then (3.1) could be written as:

$$v_s \cdot i_{af} = C \cdot V_{dc} \cdot \frac{d\widetilde{V}_{dc}}{dt}$$

(3.4)

$$v_s = V_s \cdot \sqrt{2} \cdot \sin \omega t \tag{3.5}$$

$$i_{af} = \sum_{h=3.5}^{\infty} I_{af,h} \cdot \sqrt{2} \cdot \sin(h \cdot \omega \cdot t - \phi_h)$$

(3.6)

The voltage fluctuation,  $\Delta V_{dc}$  across the capacitor is :

$$\Delta V_{dc} = \left(\widetilde{V}_{dc}\right)_{\text{max}} - \left(\widetilde{V}_{dc}\right)_{\text{min}} \tag{3.7}$$

The energy variation,  $\Delta E$ , across the capacitor is:

$$\Delta E = E_{max} - E_{min} \tag{3.8}$$

Where

$$E = \int_{0}^{t} v_{s} \cdot i_{af} \cdot dt \tag{3.9}$$

$$\Delta V_{dc} = \frac{\Delta E}{C \cdot V dc} \tag{3.10}$$

It can be shown that using reasonably high switching frequency the instantaneous energy can be written as:

$$E = \int_{0}^{t} v_{s} \cdot i_{load,h} \cdot dt \tag{3.11}$$

Equation (3.10) shows that the voltage fluctuation across the capacitor is a function of the converter instantaneous energy fluctuation, the dc bus voltage and the size of the capacitor.

The dc voltage regulation ratio is defined as:

$$r_{v} = \frac{\Delta V_{dc}}{V_{dc}} \tag{3.12}$$

Finally the minimum capacitor value to meet the required voltage regulation is given by:

$$C_{\min} = \frac{1}{V_{dc}^2 \cdot r_v} \Delta E \tag{3.13}$$

For three phase case equation (3.13) is replaced by:

$$E = \int_{0}^{t} \left( \sum_{j=a,b,c} v_{s,j} \cdot i_{j,b} \right) \cdot dt$$

(3.14)

The capacitors are designed to limit the dc voltage ripple to a specified value, typically 1 to 2 %. In our case the capacitor should be designed for the worst case, since the active filter will operate in several modes (single phase or unbalanced load). It follows that the capacitor value is load dependent and simulation is one way of evaluating the worst possible case. It will be shown in section 3.6, that the worst case occurs when the active filter is compensating a single phase load. The harmonic frequencies of the dc bus voltage in the case of a single phase load, can be found by expanding (3.13).

$$E = \int_{0}^{t} \sum_{h=2,4}^{\infty} (V_s \cdot \sqrt{2} \cdot I_h \cdot \sqrt{2} \cdot \sin(\omega \cdot t) \cdot \sin(h \cdot \omega \cdot t - \phi_h)) dt$$

(3.15)

Transforming the product into summation yields:

$$E = \int_{0}^{t} \sum_{h=2,4}^{\infty} \left\{ 2 \cdot V_{s} \cdot I_{h} \left( \cos[(h-1)\omega t - \phi_{h}] - \cos((h+1)\omega t - \phi_{h}) \right) \right\}$$

(3.16)

Integrating (3.18) one obtains:

$$E = \sum_{h=2.4}^{\infty} \left\{ V_s \cdot I_h \left[ \frac{1}{(h-1)\omega} \sin[(h-1)\omega t - \phi_h] - \frac{1}{(h+1)\omega} \sin[(h+1)\omega t - \phi_h] \right] \right\} + cte \quad (3.17)$$

The above expression shows that the dc bus voltage has harmonic components at twice the mains frequency, resulting from the third harmonic of the load, a harmonic component at four times the mains frequency, which is the contribution of the third and fifth harmonic of the load, hence all the even harmonics are present in the spectrum of the dc bus voltage. A similar reasoning show that, under unbalanced load condition, the spectrum of the dc bus has similar harmonic distribution. However, under balanced load condition, the dc bus ripple components are located at multiples of six times the mains frequency.

### 3.3 Dc Capacitor Voltage for Step Changing Load

In some cases, a load has a sudden change, such as disconnection from the ac line or sudden connection to the ac line. When the load current is dropped, the active filter current has not yet changed until the next cycle. Hence this extra current,  $\Delta I_{af}$ , will charge the capacitor [38] [58]. Where  $\Delta I_{af}$  is the step drop of the peak value of the active

filter accompanied with the drop of the fundamental load current. From (3.1) we have:

$$\frac{C}{2} \cdot \left(\frac{dv_{dc}^2}{dt}\right) = v_s \cdot i_{af} \tag{3.18}$$

Let  $V_{dc}(\infty) = V_{dc} + \Delta V_{dc}$ , then equation (3.18) becomes:

$$\Delta V_{dc}^2 + 2 \cdot V_{dc} \cdot \Delta V_{dc} - \frac{4 \cdot V_s \cdot \sqrt{2} \cdot \Delta I_{ef}}{C \cdot \omega} = 0$$

(3.19)

The previous equation shows that the voltage rises when the load steps down. For the calculated value C, the voltage rise is obtained by solving the second order equation. If the voltage rise is not permissible, then the new value of the capacitor is obtained by imposing a permissible voltage range. It is found that the new value of the capacitor is greater than the first value obtained in Section 3.2.