# DESIGN OF HARDWARE INTERFACE FOR SBC 8085 INTEL-SINGLE BOARD COMPUTER

SAMÍR BAHY EL DIN

A Major Technical Reprot

in

The Faculty

of

Engineering

Presented in partial fulfillment of the Requirements

for the degree of Master of Engineering at

Concordia University

Montreal, Quebec, Canada

November 1979

C SAMIR BAHY EL DIN 1979

#### ABSTRACT.

# SAMIR BAHY EL DIN DESIGN OF HARDWARE INTERFACE FOR SBC 8085 INTEL-SINGLE BOARD COMPUTER

An Overall general description of up 8085 and IC 8279 are covered in this report.

The design of INTERFACE for keyboard type input device and the output device using INETL 8279 is the center of attention of this technical report.

The design deals with the assembly programming of 8279 which is needed in that design.

#### **ACKNOWLEDGEMENT**

I wish to express my sincere gratitude to Dr. S. Gracovetsky, for his helpful suggestions, counsel and encouragement.

Special thanks should go to Mrs. Monica Etwaroo - for typing this Major Technical Report.

٠.

#### TABLE OF CONTENTS

| ī            | • ;                          | ,                                       |                                         | PAGE         |

|--------------|------------------------------|-----------------------------------------|-----------------------------------------|--------------|

| •            |                              | , 9                                     | • •                                     |              |

| ABSTRACT     |                              |                                         |                                         | ٠            |

| ACKNOWLEDGE: | MENT                         |                                         |                                         |              |

|              | • •                          | .*                                      | ٠,                                      | ,            |

| INTRODUCTIO  | N                            |                                         | ••••                                    | ,            |

| TECHNICAL R  | EPORT                        |                                         |                                         | 1,           |

| 1. REQUIRE   | MENT                         |                                         | • • • • • • • • • • • • • • • • • • • • | ·\ \         |

| ,            | NT AVAILABLE FOR THE PROJECT |                                         |                                         | . 1          |

| ø            | EXPANSION                    |                                         |                                         | ٠ .          |

| 3. 3131EM    | EXPANSION                    |                                         | • • • • • • • • • • • • • • • • • • • • | τ .          |

| 4. DESCRIP   | TION FOR 80/05 SBC           |                                         | • • • • • • • • • • • • • • • • •       | . 2          |

| 5. DESCRIP   | TION OF INTEL 8085 UP        | •••••                                   | • • • • • • • • • • • • • • • •         | 3            |

| 5.1.1        | ARITHMETIC SECTION           |                                         |                                         | . 3          |

| 5.1.2        | INSTRUCTION DECODER          | * * * * * * * * * * * * * * * * * * * * |                                         | 4            |

| 5.1.3        | ARITHMETIC LOGIC UNIT        | •                                       | •••••                                   | 4.           |

| 5.1.4        | ACCUMULATOR                  |                                         | 1 1 1                                   | 5            |

| 5.1.5        | PROGRAM MEMORY               |                                         | · · · · · · · · · · · · · · · · · · ·   | 5            |

| -5.1.6       | BUS                          |                                         |                                         | · <b>*</b> 5 |

| 5.1.7        | TEST AND INT INPUTS          | 1,                                      | ••••••••                                | 7            |

| 5.1.8        | PROGRAM COUNTER AND STACK .  |                                         |                                         | 8            |

| 5.1.9        | PROGRAM STATUS WORD          |                                         | ••••••                                  | <u>,</u> 11  |

| 5.1.10       | CONDITIONAL BRANCH LOGIC     |                                         | 18                                      | , 12         |

| 5.1.12       | INTERRUPT                    |                                         |                                         | 12           |

| · • • • • • • • • • • • • • • • • • • • | •                                                         | rade |

|-----------------------------------------|-----------------------------------------------------------|------|

| 5.1.12                                  | INTERRUPT TIMING                                          | 13   |

|                                         | TIMER/COUNTER                                             | 14   |

| 5.1.14                                  | CLOCK AND TIMING CIRCUITS                                 | 17   |

|                                         | 5.1.14.1 CLOCK GENERATION                                 | 17   |

|                                         | 5.1.14.2 CYCLE COUNTER                                    | 17   |

| 5.1.15                                  | INITIALIZATION OR RESET                                   | 18   |

| 5.1.16                                  | PIN DESCRIPTION FOR 8085 UP                               | 19   |

| •                                       | 5.1.16.1 AD <sub>0</sub> -7 (INPUT/OUTPUT 3-STATE)        | 19   |

| ,                                       | 5.1.16.2 A <sub>8</sub> -A <sub>15</sub> (OUTPUT 3-STATE) | 19   |

|                                         | 5.1.16.3 S <sub>0</sub> , S <sub>1</sub> (OUTPUT)         | 21   |

|                                         | /5.1.16.4 RD (PUTPUT 3-STATE)                             | 21   |

| •                                       | 5.1.16.5 WR (OUTPUT 3-STATE)                              | 21   |

| ``\                                     | 5.1.16.6 ALE (OUTPUT)                                     | 21   |

|                                         | 5.1.16.7 READY (INPUT)                                    | 22   |

| 1 -                                     | 5,1.16.8 HOLD (INFUT)                                     | 22   |

| * t                                     | 5 <sub>6</sub> 1.16.9 HOLD A (OUTPUT)                     | 22   |

| •                                       | 5.1.16.10 INTR (INPUT)                                    | 23   |

| · '>                                    | 5.1.16.11 TRAP (INPUT)                                    | 23   |

|                                         | 5.1.16.12 INTA (OUTPUT)                                   | 23   |

|                                         | 5.1.16.13 RESET OUT (OUTPUT)                              | 24   |

|                                         | 5.1.16.14 RESET IN (INPUT)                                | 24   |

|                                         | 5.1.16.15 CLK (OUTPUT)                                    | 25   |

|                                         | 5.1.16.16 IO/M (OUTPUT)                                   | 25   |

|                                         | 5.1.16.17 X <sub>1</sub> , X <sub>2</sub> (INPUT)         | 25   |

| *                                       | 5.1.16.18 V <sub>CC</sub>                                 | 25   |

|                                         |                                                           |      |

|     | *       | •       |                     |             |               | <b>A</b>            | ,                                       | ) .                                     | PAGE |

|-----|---------|---------|---------------------|-------------|---------------|---------------------|-----------------------------------------|-----------------------------------------|------|

|     | . 5.1.1 | 6.19 S  | ID, (INPU           | T)          |               |                     |                                         | ••••••                                  | . 25 |

|     | 5.1.1   | 6.20 S  | OD (PUTP            | UT)         |               |                     | • • • • • • • •                         | ,,                                      | . 25 |

|     | 5.1.1   | 6.21 V  | ss ····             |             |               |                     | · · · · · · · · · ·                     | • • • • • • • •                         | 26   |

| 6.  | DESCR   | IPTION  | OF INTEL            | 8111-RAM    |               |                     | • • • • • • •                           |                                         | 27   |

| 7.  | DESCRI  | PTION O | F INTEL             | 8155 RAM/   | O/TIMER       |                     | • • • • • • •                           | • • • • • • •                           | 28   |

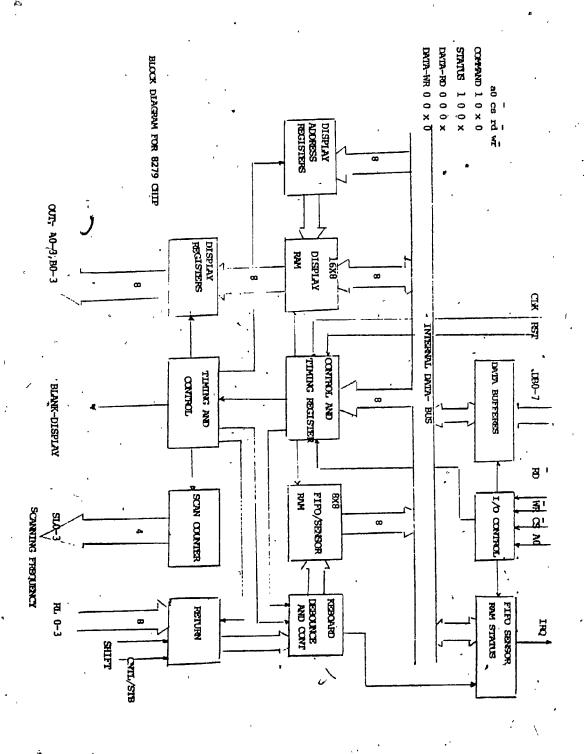

| 8.  | DESCRI  | PTION O | ,<br>F 8279 (       | PROGRAMMAE  | BLE KEYBO     | )ARD/DISPLA         | AY INTER                                | FACE)                                   | 30   |

| •   | 8.1     | "FUNCTI | ONAL DES            | CRIPTION.   |               |                     |                                         |                                         | 32   |

|     | , n     | 8.√.1   | INPUT M             | ODES        |               |                     | <u>.</u>                                |                                         | 32   |

|     | ,       | 8.1\2   | OUTPUT              | MODES       |               |                     | • • • • • • •                           |                                         | 32   |

|     | 8.2     | HARDWA  | RE DESCR            | IPTION      |               |                     | • • • • • • •                           |                                         | 34   |

|     | 8.3     | PRINCI  | PLES OF             | OPERATION   |               |                     | • • • • • • •                           |                                         | 37   |

| *   |         | 8.3.1   | I/O CON             | ITROL AND I | DATA BUFE     | FERS                | • • • • • • • •                         | • • • • • • • •                         | · 38 |

|     | •       | 8.3.2   | CONTROL             | AND TIMIT   | NG REGIŞT     | TERS AND T          | IMING CO                                | NTROL                                   | 38   |

|     |         | 8.3.3   | SCAN ÇO             | OUNTER      |               |                     | • • • • • • •                           | • • • • • • •                           | 39   |

|     |         | 8.3.4   | RETURN              | EUFFERS AN  | ND KEYBOA     | ARD DEBOUN          | CE AND C                                | ONTROL                                  | 40   |

|     | ,       | 8.3.5   | FIFO/SE             | NSGR RAM.   | AND STATU     | ıs                  | • • • • • • •                           | •••••                                   | . 40 |

| •   | ,       | 8.3.6   | DISPLAY             | ADDRESS F   | REGISTERS     | AND DISP            | LAY RAM                                 | • • • • • • • •                         | , 41 |

|     | 8.4     | KEYBOA  | RD/DISPL            | AY MODE SE  | ET            | , ,                 | • • • • • • • • • • • • • • • • • • • • |                                         | 42   |

|     | (       | 8.4.1   | 8 <sub>2</sub> 79 0 | OMMANDS .   | • • • • • • • | • • • • • • • • • • | • • • • • • •                           | • • • • • • • •                         | 42   |

| , ' | 5       | 8.4.2   | KEYBOA              | RD/DISPLAY  | Y MODE SE     | т                   | • • ,• • • • •                          | * * * * * * * * * * * * * * * * * * * * | 42   |

|     | t ·     | 8.4.3   | PROGRA              | M ÇLOCK .   |               |                     |                                         | •••••                                   | 43   |

|     |         | 8.4.4   | READ F              | IFO/SENSOR  | R RAM         |                     | • • • • • • • •                         | ••••                                    | 43   |

|     |         | 8.4.5   | READ [              | ISPLAY RAI  | ч             |                     | • • • • • • •                           |                                         | 44   |

| ,   |         | 8.4.6   | WRITE               | DISPLAY RA  | <b>,</b> м    | • • • • • • • •     | • • • • • •                             | • • • • • • •                           | 45   |

|     | •       | 2 4 7   | n TSDL Å            | V WRITE II  | NHTRIT/RI     | ANKING              | *                                       | *                                       | 45   |

ヷ

|    | s ",      |                                              | PAGE    |

|----|-----------|----------------------------------------------|---------|

|    |           | 8.4.8 CLEAR                                  | 46      |

|    |           | 8.4.9 END INTERRUPT/ERROR MODE SET           | 47      |

| ,  | •         | 8.4.10 STATUS WORD                           | 48      |

| ٠  |           | 8.4.11 DATA READ                             | 48      |

|    |           | 8.4.12 DATA WRITE                            | 48      |

|    | 8.5       | INTERFACE CONSIDERATIONS                     | 49      |

|    |           | 8.5.1 SCANNEC KEYBOARD MODE, 2-KEY LOCKOUT   | 49      |

|    |           | 8.5.2 SCANNED KEYBOARD MODE, N-KEY ROLLOVER  | 50<br>· |

| r  | <b>\$</b> | 8.5.3 SCANNED KEYBOARD - SPECIAL ERROR MODES | 50      |

|    | •         | 8.5.4 SENSGR MATRIX MODE                     | 51      |

|    | -         | 8.5.5 DATA FORMAT                            | 51      |

|    | `         | 8.5.6 DISPLAY                                | 53      |

| }. | DESCRI    | PTION OF THE HARDWARE DESIGN                 | 54      |

|    | 9.1       | COMMUNICATION BETWEEN CPU AND THE OTHER LSI  | 55      |

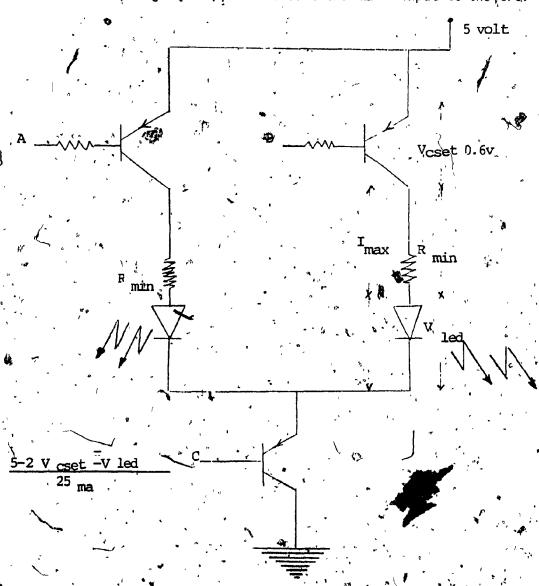

| •  | 9.2       | CIRCUIT ANALYSIS                             | 57      |

|    | 9.3       | INITIALIZATION                               | 58      |

|    | 9.4       | CLOCK CIRCUITS                               | 59      |

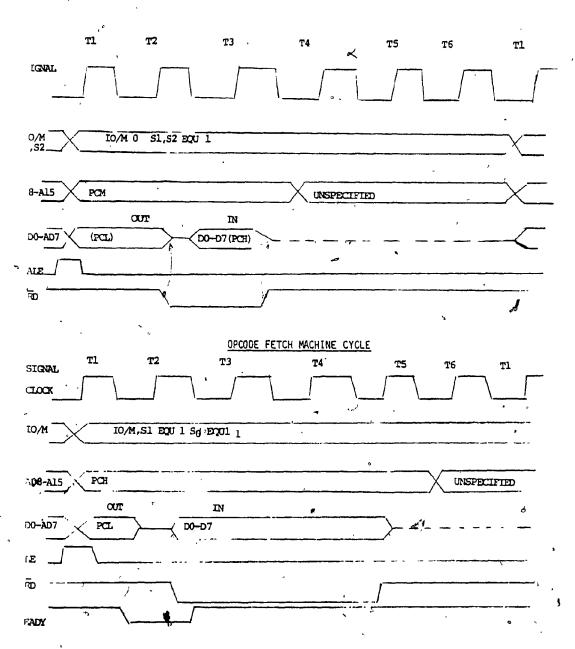

|    | 9.5       | INSTRUCTION TIMING                           | 62      |

|    | 9.6       | OPCODE FETCH TIMING                          | 67      |

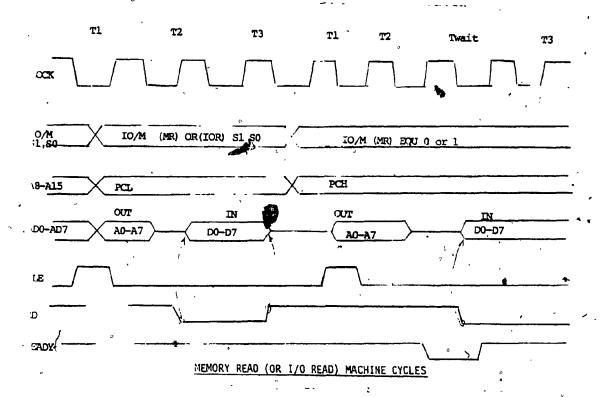

|    | 9.7       | MEMORY READ TIMING                           | 69      |

|    | 9.8       | 1/O READ TIMING                              | 70      |

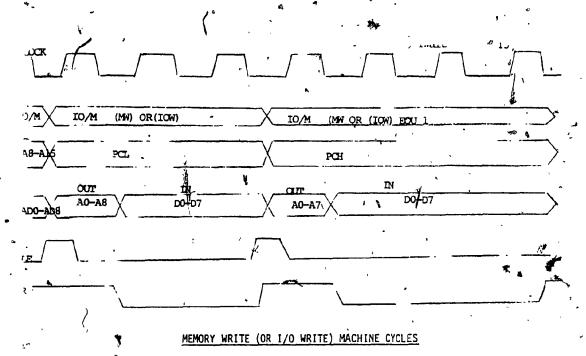

|    | 9.9.      | MEMORY WRITE TIMING                          | 71      |

|    | 9.10      | 1/0 WRITE TIMING                             | 74      |

|    | 9.11      | MULTIPLEXED ADDRESS/DATA BUS                 | 74      |

|    | 9.12      | MULTIBUS INTERFACE                           | 75      |

|                  |                                                       | PAGE |

|------------------|-------------------------------------------------------|------|

|                  |                                                       |      |

| 10. <sub>e</sub> | THE INTERFACE DESCRIPTION                             | ' 77 |

| 11.              | PROGRAMMING OF 8279                                   | 80   |

|                  | 11.1 I/O REGISTER ADDRESSING                          | 80   |

|                  | 11.2 PROGRAMMING THE COMMAND REGISTER                 | 80   |

| •                | 11.2.1 INSTRUCTION REQUIRED FOR COMMAND REGISTER      | 81   |

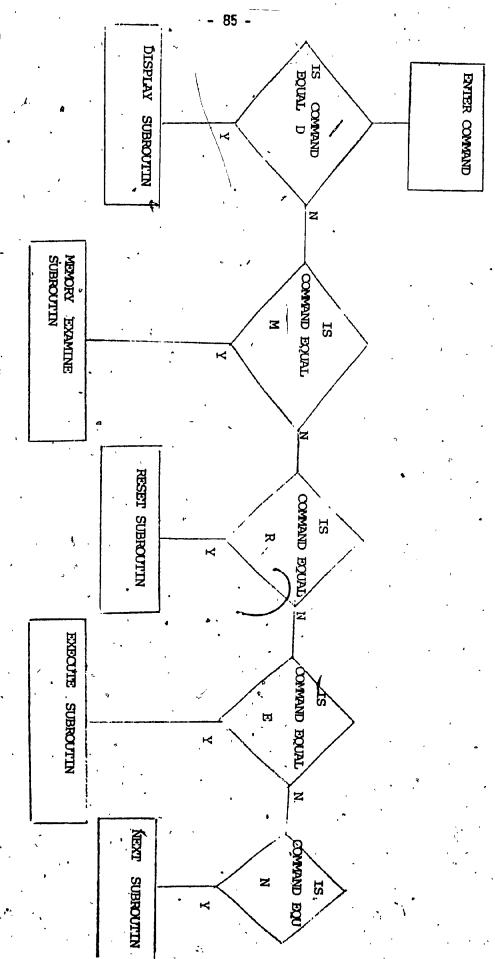

| 12.              | DESCRIPTION OF THE MONITOR ROUTINE USED IN THE SYSTEM | 83   |

| 13.              | DISCUSSION                                            | 86   |

| 14.              | REFERENCES                                            | 87   |

#### INTRODUCTION

THE INPUT/OUTPUT INTERFACE FOR SBC 80/05 WILL GIVE THE SBC THE CAPABILITY TO COMMUNICATE WITH OUTSIDE WORLD. THE FOLLOWING THREE PARAGRAPH EX-PLAINS THE RELATION DETWEEN INPUT DEVICE, OUTPUT DEVICE AND 8279 CHIP.

- i) THE MATRIX KEYBOARD WILL BE USED AS INPUT DEVICE WHICH WILL MAKE THE USER (FOR THIS SMALL SYSTEM) CAPABLE FOR PUTTING ANY KIND OF INFORMATION INSIDE THE RAM AND BY USING THE MONITOR OR (THE SOFTWARE DESIGNED FOR THIS SYSTEM). THE USER WILL BE ABLE TO PROCESS HIS INFORMATION AND GETTING THE FINAL RESULT IN THE OUTPUT DEVICE.

- ii) THE TIL 313 LIGHT EMMITTING DIOUS WILL BE USED AS OUTPUT DEVICE, AND WILL DISPLAY THE FINAL RESULT FOR THE PROCESSED DATA.

- iii) THIS TWO DEVICES COMMUNICATE WITH 8085 UP THROUGH INTEL 8279 CHIP (PROGRAMMABLE KEYBOARD / DISPLAY INTERFACE). THE PURPOSE OF THE PROJECT IS TO GET FAMILIAR WITH THE HARDWARE AND SOFTWARE OF THE 8085 UP AND 8279 PROGRAMMABLE KEYBOARD AND DISPLAY INTERFACE LSI.

HARDWARE INTERFACE DESIGN AND SOFTWARE

#### TECHNICAL REPORT

#### REQUIREMENT

It is required to design the HARDWARE INTERFACE for BC 80/85 single board computer which is a member of INTEL' complete line of SBC 80 computer.

The HARDWARE INTERFACE will give the capability for the Single Board Computer to use a keyboard as input device or TTY and light emmitting diodes led's as output device.

#### 2. EQUIPMENTS AVAILABLE FOR THE PROJECT

- a) SBC 80/05 Single Board Computer which contains:

- 1) INTEL 8085 CPU

- 2) INTEL 8111-RAM provide 256 bytes of static read and write memory

- 3) INTEL 8155 combination RAM/10/TIMER

- Two sockets are providing for installing up to

4k bytes of ROM (which stores the required operating system)

SBC 80/05 provides jumber-selectable interrupts to the four interrupt request inputs of the 8085 CPU.

- b) INTÈL 3279-PROGRAMMABLE KEYBOARD/DISPLAY INTERFACE

- c) 2 TTL DECODER 74LS156

- d) MATRIX KEYBOARD

- e) 4 TIL-313

- f) 16 TRANSISTOR (2N2907)

#### 3. SYSTÊM EXPANSION

Processing power, memory and I/O capacity may be increased in SBC 80/05 based system with single -5 $\nu$  power by adding standard INTEL expansion boards.

Memory may be expanded to 65,536 bytes by adding user-specified combinations of RAM boards, PROM boards or Combination boards. Input/Output capacity may also be increased by adding SBC 80 Analog I/O Boards.

#### 4. DESCRIPTION FOR 80/05 SBC

The SBC 80/05 Single Board Computer is controlled by an Intel 8085 cpu, which includes six 8 bit general purpose registers, may be addressed individually or in pairs, which allows both single-precision and double-precision operations. The minimum on board execution time is 2.03 usec.

The 8085 cpu has a 16 bit program counter which allows direct addressing of up to 65,536 bytes of memory and external stack located within any portion of Read/write memory, may be used

as a last-in/first-out storage area for the contents of the Program Counter. Flags, accumulator and all six general-purpose registers and 16 bit stack pointer registers which control the addressing of the external stack and, this will allows subroutine nesting. This is bounded only by the system memory size.

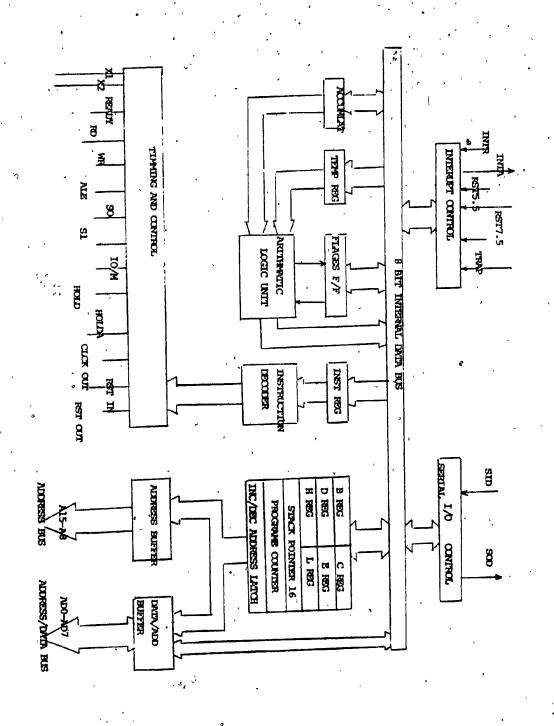

#### 5. DESCRIPTION OF INTEL 8085 UP

The following sections break the 8085 into functional blocks and describe each in detail.

#### 5.1.1. Arithmetic Section

The arithmetic section of the processor contains the basic data manipulation functions of the 8085 and can divided into the following blocks:

- a) Arithmetic Logic Unit (ALU)

- b) Accumulator

- c) Carry Flag

- d) Instruction Decoder .

In a typical operation data sorted in the accumulator is combined in the ALU with data from another source on the internal bus (such as a register or I/O port) and the result is sorted in the accumulator or another register. The following is a more detailed description of the function of each block.

#### 5.1.2. Instruction Decoder

r 4.

The operation code (op code) portion of each program instruction is stored in the Instruction Decoder and converted to output which control the function of each of the blocks of the Arithmetic Section. These lines control the source of data and the destination register as well as the function performed in the ALU.

#### 5.1.3. Arithmetic Logic Unit

The ALU accepts 8-bit data words from one or two sources and generates an 8-bit result under control of the Instruction Decoder. The ALU can perform the following functions:

- Add With or Nithout Carry

- And, OR, Exclusive OR

- Increment/Decrement

- Bit Complement

- Rotate Left, Right

- Swap Nibbles

- BCD Decimal Adjust

If the operation performed by the ALU results in a value represented by more than 8 bits (overflow of most significant bit) a Carry Flag is set in the Program Status Word.

#### 5.1.4. Accumulator

The accumulator is the single most important data register in the processor being one of the sources of input to the ALU and often the destination of the result of operations performed in the ALU. Data to and from I/O ports and memory also normally passes through the accumulator.

#### 5.1.5. Program Memory

Resident program memory consists of 1024 words eight bits wide which are addressed by the program counter. In the CPU, the memory is ROM which is mask programmable at the factory. Program code is completely interchangeable among the three versions.

#### 5.1.6. Bus

Bus is also 8-bit port which is true bidirectional port with associated input and output strobes. If the bidirectional feature is not needed, Bus can serve as either a statically latched output port or non-latching input port. Input and output lines on this port cannot be mixed however.

As a static port, data is written and latched using the OUTL instruction and inputted using the INS instruction. The INS and OUTL instructions generate pulses on the corresponding RD and WR output strobe lines; however, in the static port mode they are generally not used. As a bidirectional port the MOVX instructions are used to read and write the prot. A write to the port generates a pulse on the WR output line and output data is valid at the trailing edge of Wr. A read of the port generates a pulse on the RD output line and input data must be valid at the trailing edge of RD. When not being written or read, the BUS lines are in a high impedance state.

# 5.1.7. <u>Test and INT Inputs</u>

Three pins serve as inputs and are testable with the conditional jump instruction. These are TO, Tl, and INT. These pins allow inputs to cause program branches without the necessity to load an input port into the accumulator. The TO, Tl and INT pins have other possible functions as well.

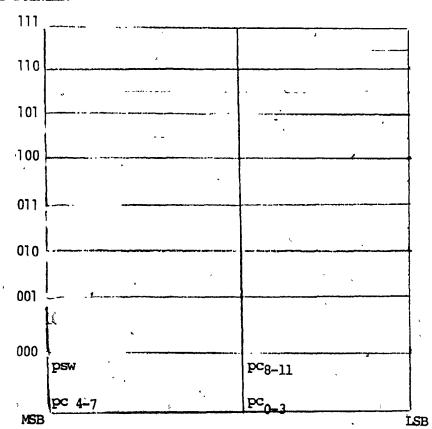

#### 5.1.8. Program Counter and Stack

The Program Counter is an independent counter while the Program Counter Stack is implemented using pairs of registers in the Data Memory Array. Only 10 bits of the Programm Counter are used to address the 1024 words of on-board program memory while the most significant two bits are used for external Program Memory fetches.

The Program Counter is initialized to zero by activating the Reset line.

An interrupt or CALL to a subroutine causes the contents of the program counter to be stored in one of the 8 register pairs of the Program Counter Stack. The pair to be used is determined by a 3-bit Stack Pointer which is a part of the Program Status Word (PSW). Data RAM locations 8 thru 23 are available as shown in the following figures.

The Stack Pointer when initialized to 000 points to RAM locations 8 and 9. The first subroutine jump or interrupt results in the program counter contents being transferred to locations 8 and 9 of the RAM array. The stack pointer is then incremented by one to point to locations 10 and 11 in anticipation of another CALL. Nesting of subroutines within subroutines can continue up to 8 times without overflowing the stack. If overflow does occur the deepest address stored (location 8 and 9) will be overwritten and lost since the stack pointer overflows from 111 to 000. It also underflows from 000 to 111 (look to the Program Counter Map).

The end of s subroutine, which is signalled by a return instruction (RET or RETR), causes the Stack Pointer to be decremented and the contents of the resulting register pair to be transferred to the Program Counter.

|     | FLAG SAVED IN STACK |    |      | NESTING LEVEL |         |                  |        |     |     |

|-----|---------------------|----|------|---------------|---------|------------------|--------|-----|-----|

| MSB | CX                  | AC | FO - | BS            | not use | ) S <sub>2</sub> | s<br>1 | S O | LSB |

# PROGRAM COUNTER MAP

|                                                    | <u> </u> |         |         |         |             | # <b>#</b> | ,                     |        |        |        |        |        |        |        |        |        |     |

|----------------------------------------------------|----------|---------|---------|---------|-------------|------------|-----------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----|

| MSB                                                | A<br>15  | A<br>14 | A<br>13 | A<br>12 | A<br>11     | A<br>10    | <b>A</b> <sub>9</sub> | A<br>8 | A<br>7 | A<br>6 | A<br>5 | A<br>4 | A<br>3 | A<br>2 | A<br>1 | A<br>0 | LSB |

| <pre>FLAG SAVED -&gt; STACK POINTER IN STACK</pre> |          |         |         |         |             |            |                       |        |        |        |        |        |        |        |        |        |     |

| •                                                  | ~        | PS      | W '4    | >       | <del></del> |            |                       | PR     | OGRAI  | v COÜN | TER    | 000-   | 7FFH_  | 2k By  | TE     | >      | -   |

# NESTING LEVEL OF POINTER

#### 5.1.9 Program Status Word

An 8-bit status word which can be loaded to and from the accumulator exists called the program Status Word (PSW). The accompanying figure shows the information available in the word. The Program Status Word is actually a collection of flip-flops throughout the machine which can be read or written as a whole. The ability to write to PSW allows for easy restoration of machine status after a power down sequence.

The upper four bits of PSW are stored in the Program

Counter Stack with every jump to subroutine or interrupt vector and are optionally restored upon return with the RETR instruction. The RET return instruction does not update PSW.

The PSW bit definitions are as follows:

Bits 0 - 2: Stack Pointer bits  $(S_0, S_1, S_2)$

Bit 3: Not used ("1" level when read)

Bit 4: Working Register Bank Switch Bit (BS)

0 Bank 0

1 Bank 1

Bit 5: Flag 0 bit (F0) user controlled flag which can be complemented or cleared, and tested with the conditional jump instruction JF0.

Bit 6:

Auxiliary Carry (AC) carry bit generated by an ADD instruction and used by the decimal adjust instruction DAA.

Bit 7:

Carry (CY) carry flag which indicates that the the previous operation has resusted in overflow of the accumulator.

#### 5.1.10 Conditional Branch Logic

The conditional branch logic within the processor enables several conditions internal and external to the processor to be tested by the users program. By using the conditional jump instruction the following conditions can effect a change in the sequence of the program execution.

#### 5.1.11 Interrupt

An interrupt sequence is initiated by applying a low "O" level input to INT pin. Interrupt is level triggered and active low to allow "WIRE ORing" of several interrupt sources at the input pin. The Interrupt line is sampled every machine cycle during ALE and when detected causes a "jump to subroutine" at location 3 in program memory as soon as all cycles of the current instruction are complete. As in any CALL to subroutine, the Program Counter and Program Status word are saved in the stack.

Program Memory location 3 usually contains and unconditional jump to an interrupt service subroutine elsewhere in program memory. The end of an interrupt service subroutine is signalled by the execution of a Return and Restore Status instruction RETR. The interrupt system in single level in that once an interrupt is detected all further interrupt requests are ignored until execution of an RETR re-enables the interrupt input logic. This occurs at the beginning of the second cycle of the RETR instruction. This sequence holds, true also for an internal interrupt generated by timer overflow. If an internal timer/counter. generated interrupt and an external interrupt are detected at the same time, the external source will be recognized. If needed, a second external interrupt can be created by enabling the timer/counter interrupt, loading FFH in the Counter (one less than terminal count), and enabling the event counter mode. A "1" to "0" transition on the T1 input will then cause an interrupt vector to location 7.

#### 5.1.12 Interrupt Timing

The interrupt input may be enabled or disabled under Program Control using the EN I and DIS I instructions. Interrupts are disabled by Reset and remain so until enabled by the users program.

An interrupt request must be removed before the RETR instruction is executed upon return from the service routine otherwise the processor will re-enter the service routine immediately. Many peripheral devices prevent this situation by resetting their interrupt request line whenever the processor accesses (Reads or Writes) the peripherals data buffer register. If the interupting device does not require access by the processor, one output line of the CPU may be designated as an "interrupt acknowledge" which is activated by the service subroutine to reset the interrupt request. The INT pin may also be tested using the conditional jump instruction JNI. This instruction may be used to detect the presence of a pending winterrupt before interrupts are enabled. If interrupt is left disables, INT may be used as another test input like TO and Tl.

#### 5.1.13 <u>Timer/Counter</u>

The CPU contains a counter to aid the user in counting external events and generating accurate time delays without placing a burden on the processor for these functions. In both modes the counter operation in the same, the only difference being the source of the input to the counter. It can work as a counter, an event counter and as a timer.

The 8-bit up binary counter is presettable and readable with two MOV instructions which transfer the contents of the accumulator to the counter and vice versa. The counter content is not affected by Reset and is initalized solely by the MOV T,A instruction. The counter is stopped by a START T instruction or as an event counter by a START CNT instruction. Once started the counter will increment to its maximum count (FF) and over flow to zero continuing its count until stopped by a STOP TCNT instruction or Reset.

The increment from maximum count to zero (overflow) results in the setting of an overflow flag flip-flop and in the generation of an interrupt request. The state of the overflow glag is testable with the conditional jump instruction JTF. The flag is reset by executing a JTF or by Reset. The interrupt request is stored in a latch and then ORed with the external interrupt input INT. The timer interrupt may be enabled or disabled independently of external interrupt by the EN TGNTI and DIS TGNTI instructions. If enabled, the counter overflow will cause a subroutine call to location 7 where the timer or counter service routine may be stored. If timer and external interrupts occur simultaneously, the external source will be recognized and the Call will be to location 3.

Since the timer interrupt is latched it will remain pending until the external device is serviced and immediately be recognized upon return for the service routine. The pending timer interrupt is reset by the Call to location 7 or may be removed by executing a DIS TGNTI instruction. Execution of a START CNT instruction connects the Tl input pin to the counter input and enables the counter.

Subsequent high to low transitions on Tl will cause the counter to increment. The maximum rate at which the counter may be incremented is once per three instruction cycles (every 7.5 usec when using a 6MHz crystal)—there is no minimum frequency. Tl input must remain high for at least 100ns after each transition.

As a timer, execution of a START T instruction connects an internal clock to the counter input and enables the counter. The internal clock is derived by passing the basis 400 KHz machine cycle clock ALE through a - 32 prescaler. The prescaler is reset during the START T instruction. The resulting 12.5 KHz clock increments the counter every 80 usec (assuming 6 MHz XTAL). Various delays between 80 usec and 20 msec (256 counts) can be obtained by presetting the counter and detection overflow. Times longer than 20 msec may be achived by accumulating multiple overflows in a register under software control.

For time resoulution less than 80 usec an external clock can be applied to the Tl input and counter operated in the event counter mode. Ale divided by 3 or more can serve as this external clock. Very small delays or "fine tuning" of larger delays can be easily accomplished by software delay loops.

#### 5.1.14 Clock and Timing Circuits

Timing generation for the CPU is completely self-contained with the execption of a frequency reference which can be XTAL, series RC, or external clock source. The Clock and Timing circuitry can be divided into the following functional blocks:

#### 5.1.14.1 Clock Generation

The output of the oscilator is divided by 3 in the State Counter to create a clock which defines the state times of the machine (CLK). CLK can be made available on the external pin TO by executing an ENTO CLK instruction. The output of CLK on TO is disables by Reset of the processor.

#### 5.1.14.2 Cycle Counter

CLK is then divided by 5 in the Cycle Counter to provide a clock which defines a machine cycle consisting of 5 machine states.

This Clock is called Address Latch Enable (ALE).

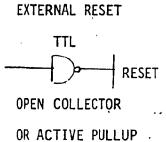

#### 5.1.15 Initialization or Reset

The reset input provides a means for initialization for the processor. This Schmitt-Trigger input has an internal pullup registor which in combination with an external l ufd capacitor provides an internal reset pulse of sufficient length to guarantee all circuitry is reset. If the reset pulse is generated externally the reset pin must be held at ground (.5V) for at least 50 milliseconds after the power supply is within tolerance.

POWER ON RESET

#### Reset performs the following functions:

- 1. Sets program counter to zero.

- 2. Sets stack pointer to zero.

- 3. Selects register bank 0:

- 4. Selects memory bank 0.

- 5. Sets BUS to high impedance state.

- 6. Sets Ports 1 and 2 to input mode.

- 7. Disables interrupts (timer and external)

- 8. Stops timer.

- 9. Clears timer flag.

- 10. Clears FO and Fl.

- 11. Disables clock output from TO.

#### 5.1.16 Pin Description For 8085 UP

The following describes the function of each pin:

#### 5.1.16.1 ADO-7 (Input/Output 3-state)

Multiplexed Address/Data Bus; Lower 8-bits of the memory address (or I/O address) appear on the bus during the first clock cycle of a machine state. It then becomes the data bus during the second and third clock cycles.

# 5.1.16.2 Ag-A<sub>15</sub> (Output 3-State)

Address Bus; The most significant 8-bits of the memory address or the 8-bits of the I/O address,

3-stated during Hold and Halt modes.

# 8085 PIN CONFIGURATION

| •                     |                |                 |                   |

|-----------------------|----------------|-----------------|-------------------|

| × 1 =                 |                | 40              | o v <sub>cc</sub> |

| x <sub>2</sub> $\Box$ | 2              | 39              | hold              |

|                       | UCRO-PROCESSER | 38              | ⊐hlda             |

| .sod 🗀                | 4              | 37              | Iclock out        |

| sid 🖰                 | <b>5</b>       | 36              | I reset in        |

| trap                  | 6 .            | 35              | ] ready           |

| rst-7.5               | 7.             | 34              | JIO/M             |

| rst-6.5               | 8 8085-A-INIEL | 33              | Dsl ,             |

| rst-5.5               | 9              | 32              | ⊃ <b>®</b> o      |

| INTR C                | 10             | 31              |                   |

| INTA                  | 11             | ,               | WR                |

| اسا                   |                | 30              | LALE              |

| ADO 💆                 | 12             | 29              | ⊃ <sup>S0</sup>   |

| AD1                   | 13,            | 28              | A 15              |

| · AD2 📺               | 14             | 27              | A 14              |

| ÀD3                   | <b>15</b> 1, . | 26              | A 13              |

|                       | 16             | 25              | A 12              |

| AD5                   | , ;<br>17      | 24              | JA 11             |

| AD6                   | 18             | 23              | A 10              |

| AD7                   | 19             | 22              | LIA 9             |

| V [                   | 20             | - <b>21</b> - , | A 8               |

#### 5.1.16.3. So, S1 (Output)

Data Bus Status. Encoded status of the bus cycle:

| $\frac{s_1}{}$ . | $\frac{s_0}{}$ | •     |

|------------------|----------------|-------|

| 0                | 0              | HALT  |

| 0                | 1              | WRITE |

| 1                | 0              | READ  |

| 1                | ]              | FETCH |

S1 can be used as an advancec R/W Status

# 5.1.16.4. RD (Output 3-state)

READ; indicates the selected memory of I/O device is to be read and that the Data Bus is available for the data transfer. 3-stated during Hold and Halt.

# 5.1.16.5. WR (Output 3-state)

WRITE; indicates the data on the Data Bus is to be written into the selected memory or I/O location. Data is set up at the trailing edge of WR. 3-stated during Hold and Halt modes.

# 5.1.16.6. <u>ALE (Output)</u>

Address Latch Enable: it occurs during the first clock cycle of a machine state and enables the address to get latched into the on-chip latch of peripherals.

The falling edge of ALE is set to guarantee setup and hold times for the address information. ALE can also be used to strobe the status information. ALE is never 3-stated.

#### 5.1.16.7. READY (Input)

If Ready is high during a read or write cycle, it indicates that the memory or peripheral is ready to send or receive data. If Ready is low, the CPU will wait for Ready to go high before completing the read or write cycle.

#### 5.1.16.8. <u>HOLD (Input)</u>

HOLD; indicates that another Master is requesting the use of the Address and Data Buses. The CPU, upon receiving the Hold request, will relinquish the use of buses as soon as the completion of the current machine cycle. Internal processing can continue. The processor can regain the buses only after the Hold is removed. When the Hold is acknowledged, the Address, Data, RE, WR, and IO/M lines are 3-stated.

# 5.1.16.9. <u>HLDA (Output)</u>

HOLD ACKNOWLEDGE; indicates that the CPU has received the Hold request and that it will relinquish the buses in the next clock cycle.

HLDA goes low after the Hold request is removed.

The CPU takes the buses one half clock after

HLDA goes low.

#### 5.1.16.10 <u>INTR (Input)</u>

INTERRUPT REQUEST; is used as a general purpose interrupt. It is sampled only during the next to the last clock cycle of the instruction. If it is active, the Program Counter (PC) will be inhibited from incrementing and an INTA will be instruction can be inserted to jump to the interrupt service routine. The INTR is enabled and disabled by software. It is disabled by Reset and immediately after an interrupt is accepted.

# 5.1.16.11 TRAP (Input)

Trap interrupt is nonmaskable restart interrupt.

It is recognized at the same time as INTR. It is unaffected by any mask or interrupt Enable. It has the highest priority of any interrupt.

# 5.1.16.12 INTA (Output)

INTERRUPT ACKNOWLEDGE; is used instead of (and has the same timing as) RD during the Instruction cycle after an INTR is accepted.

It can be used to activate the 8259 Interrupt chip or some other interrupt port.

RST 5.5

RST 6.5 (inputs)

RST 7.5

RESTART INTERRUPTS; These three inputs have the same timing as INTR except they cause an internal RESTART to be automatically inserted.

RST 7.5 Highest Priority

RST 6.5

RST 5.5 Lowest Priority

The priority of these interrupts is ordered as shown above. These interrupts have a higher priority that the INTR.

# 5.1.16.13 RESET OUT (Output)

Indicates CPU is being reset. Can be used as a system RESET. The signal is synchronized to the processor clock.

# 5.1.16.14 RESET IN (Input)

Reset sets the Program Counter to zero and resets the interrupt Enable and HLDA flip-flops. None of the other flags or registers (except the instruction register) are affected. The CPU is held in the reset condition as long as Reset is applied.

#### 5.1.16.15 CLK (Output)

Clock Output for use as a system clock when a crystal or R/C network is used as an input to the CPU. The period of CLK is twice the X<sub>1</sub> X<sub>2</sub> input period.

#### 5.1.16.16 10/M (Output) '

10/M indicates whether the Read/Write is to memory or I/o. Tristated during Hold and Halt modes.

#### 5.1.16.17 X<sub>1</sub>, X<sub>2</sub> (Input)

Crystal or R/C network connections to set the internal clock generator. X1 can also be an external clock input instead of a crystal. The input frequency is divided by 2 to give the internal operating frequency.

# 5.1.16.18 VCC

5 volt supply

# 5.1.16.19. <u>SID (Input)</u>

Serial input data line. The data on this line is loaded into accumulator bit 7 whenever a RIM instruction is executed.

# 5.1.16.20 <u>SOD</u> (Output)

Serial output data line. The output SOD is set

or reset as specified by the SIM instruction.

5.1.16.21 · VSS

Ground Reference.

#### 6. DESCRIPTION OF INTEL 8111-RAM

Two Intel 8111-A4 RAM chips provide 256 bytes of static read/write memory; an Intel 8155 combination RAM/IO/Timer provides an additional 256 bytes of static read/write memory. Two sockets are provided for installing up to 4k bytes of nonvolatile read-only memory (ROM), which may be added in 2k byte increments using Intel 2716 Ultraviolet Erasable and Reprogrammable ROM's (EPROM's) or 8316E Masked ROM's. Optionally, if only 2k bytes are required, ROM may be added in 1k byte increments using Intel 8708 EPROM's or 8308 Masked ROM's.

Twenty-two programmable parallel I/O lines are implemented using the I/O ports of the Intel 8155 RAM/IO/Timer. The system software is used to configure the I/O lines in any combination of unidirectional input or output ports. The I/O interface may be customized to meet specific peripheral requirements. In order to take full advantage of the large number of possible I/O configurations, sockets are provided for interchangeable I/O line drivers and terminators. Hence, the flexibility of the I/O interface is further enhanced by the capability of selecting the appropriate combination of optional line drivers and terminators to provide the required sink current, polarity, and drive/termination characteristics for each application. The 22 programmable I/O lines and single groung lines are brought to a 50-pin edge connector (J1).

## 7. DESCRIPTION OF INTEL 8155 RAM/IO/TIMER

The Intel 8155 RAM/IO/Timer includes a programmable 14-bit interval timer, which is configured by software to meet the system requirements. Whenever a given time delay is needed, software commands to the timer select the desired operating tode. The current contents (present count) of the timer counter and the timer mode bits may be read at any time during system operation. There are four timer operating modes:

- a. Timer Out goes low during the second half of count.

Therefore, the count loaded in the Count Length

Register should be twice the timeout desired.

- b. Timer Out remains high until the first half of the count has been completed, and goes low for the second half of the count. The count length is automatically reloaded when the terminal count is reached.

- c. A single low pulse is generated upon reaching the terminal count; this function is useful for generating real-time clocks.

- d. A Divide-by-N Counter generates a repetitive Timer Out low pulse; a new pulse train is initiated every time the terminal count is reached.

Serial I/O capability is provided through the Serial Input Data (SID) and Serial Output Data (SOD) functions of the CPU. These functions are controlled exclusively by software through the execution of RIM and SIM instructions. The baud rate for the serial interface is determined by the system time available for the execution of serial I/O support software. Hence, the maximum baud rate supported by the SBC 80/05 is solely dependent on the overall system real-time software requirements. Serial I/O signals are TTL compatible and sockets are provided on the board for optional installation of RS232C line drivers and receivers.

### 8. DESCRIPTION OF 8279 (PROGRAMMABLE KEYBOARD/DISPLAY INTERFACE)

The Intel 8279 is a general purpose programmable keyboard and display I/O interface device designed for use with Intel micro-processors. The keyboard portion can provide a scanned interface. to a 64-contact key matrix. The keyboard portion will also interface to an array of sensors or a strobed interface keyboard, such as the hall effect and ferrite variety. Key depressions can be 2-key lockout or N-key rollover. Keyboard entries set the interrupt output line to the CPU.

The display portion provides a scanned display interface for LED, incandescent, and other popular display technologies.

Both numeric and alphanumeric segment displays may be used as well as simple indicators. The 8279 has 16X8 display RAM which can be organized into dual 16X4. The RAM can be loaded or interrogated by the CPU. Both right entry, calculator and left entry typewriter display formats are possible. Both read and write of the display RAM can be done with auto-increment of the display RAM address.

# 8.1 FUNCTIONAL DESCRIPTION

Since data input and display are an integral part of many microprocessor designs, the system designer needs an interface that can control these functions without placing a large load on the CPU. The 8279 provides this function for 8-bit microprocessors.

The 8279 has two sections: keyboard and display. The keyboard section can interface to regular typewriter style keyboards or random toggle or thumb switches. The display section drives alphanumeric displays or a bank of indicator lights. Thus the CPU is relieved from scanning the keyboard or refreshing the display.

The 8279 is designed to directly connect to the microprocessor bus. The CPU can program all operating modes for the 8279. These modes include:

# 8.1.1 INPUT MODES

.Scanned Keyboard - with encoded (8 X 8 X 4 key key-board) or decoded (4 X 8 X 4 key keyboard) scan lines. A key depression generates a 6-bit encoding of key position. Position and shift and control status are stored in the FIFO. Keys are automatically debounced with 2-key lockout or N-key rollover.

.Scanned Sensor Matrix - with encoded (8 X 3 matrix switches) or decoded (4 X 8 matrix switches) scan lines. Key status (open or closed) stored in RAM addressable by CPU.

.Strobed Input - Data on return lines during control line strobe is transferred to FIFO.

#### 8:1.2 OUTPUT MODES

- .8 or 16 character multiplexed displays that can be organized as dual 4-bit or single 8-bit.

- .Right entry or left entry display formats.

- .Other features of the 8279 include:

- .Mode programming from the CPU.

- .Programmable clock to match the 8279 scan times to the CPU cycle time.

- .Interrupt output to signal CPU when there is keyboard or sensor data available.

- .An 8 byte FIFO to store keyboard information.

- .16 byte internal Display RAM for display refresh.

This RAM can also be read by the CPU.

# 8.2 HARDWARE DESCRIPTION

The 8279 is packaged in a 40 pin DIP. The following is a functional description of each pin.

| No. | 0f |

|-----|----|

|-----|----|

| Pins  | Designation    | <u>Function</u>                             |

|-------|----------------|---------------------------------------------|

| 8     | DBO-DB7        | Bi-directional data bus. All data and       |

| •     | :              | commands between the CPU and the 8279 are   |

|       |                | transmitted on these lines.                 |

| 1     | CLK .          | Clock from system used to generate internal |

|       |                | timing.                                     |

| 1 .   | RESET          | A high signal on this pin resets the 8279.  |

| 1     | CS ,           | Chip Select. A low on this pin enables the  |

| •     |                | interface functions to receive or transmit. |

| 1     | A <sub>0</sub> | Buffer Address. A high on this line indi-   |

| , , , |                | cates the signals in or out are interpreted |

|       |                | as a command or status. A low indicates     |

|       | y '            | that they are data.                         |

| 2     | RD, WR         | Imput/Output read and write. These signals  |

|       | •              | enable the data buffers to either send data |

|       |                | to the external bus or receive it from the  |

|       | ,              | external bus.                               |

| 1 ,   | IRQ            | Interrupt Request. In a keyboard mode, the  |

| •     |                | interrupt line is high when there is data   |

| ·     | •              | in the FIFO/Sensor RAM.                     |

No. Of

Pins Designation Function The interrupt line goes low with each FIFO/ Sensor RAM read and returns high if there is still information in the RAM. sensor mode, the interrupt line goes high whenever a change in a sensor is detected. 'Vss, Vcc Ground and power supply pins. SL0-SL3 Scan Lines which are used to scan the key switch or sensor matrix and the display digits. These lines can be either encoded (1 of 16) or decoded (1 of 4). RL0-RL7 Return line inputs which are connected to the scan lines through the keys or sensor switches. They have active internal pullups to keep them high until a switch closure pulls one low. They also serve as an 8bit input in the Strobed Input mode. SHIFT The shift input status is stored along with the key position on key closure in the Scanned Keyboard modes. It has an active internal pullup to keep it high until a switch closure pulls it-low.

| No. 01 | f             |                                              |

|--------|---------------|----------------------------------------------|

| Pins   | Designation   | Function                                     |

| 1      | CNTL/STB      | For Keyboard modes this line is used as a    |

|        | ₫•<br>        | control input and stored like status on a    |

| •      |               | key closure. The line is also the strobe     |

| •      |               | line that enters the data into the FIFO in   |

|        |               | the Strobed Input mode. (Rising Edge).       |

|        |               | It has an active internal pullup to keep     |

|        | •             | it high until a switch closure pulls it low. |

| 4      | OUT A0-OUT A3 | These two ports are the outputs fot the      |

| 4      | OUT B0-OUT B3 | 16 X 4 display refresh registers. The data   |

|        |               | from these outputs is synchronized to the    |

|        | ,             | scan lines (SLO-SL3) for multiplexed digit   |

|        | ,             | displays. The two 4 bit ports may be blank-  |

|        |               | ed independently. These two ports may also   |

| •      |               | be considered as one 8 bit port.             |

| 1      | BD .          | Blank Display. This output is used to        |

| 1      |               | blank the display during digit switching     |

# 8.3 PRINCIPLES OF OPERATION

The following is a description of the major elements of the 8279 Programmable Keyboard/Display interface device.

or by a display blanking command.

# 8.3.1. I/O CONTROL AND DATA BUFFERS

The I/O control section uses the CS, AO, RD and WR lines to control data flow to and from the various internal registers and buffers. All data flow to and from the 8279 is enabled by CS. The character of the information, given or desired by the CPU, is identified by AO. A logic one means the information is a command or status. A logic zero means the information is data. RD and WR determine the direction of data flow through the Data Buffers. The Data Buffers are bi-directional buffers that connect the internal bus to the external bus. When the chip is not selected (CS 1), the devices are in a high impedance state. The drivers input during WR.CS and output during RD.CS.

### 8.3.2. CONTROL AND TIMING REGISTERS AND TIMING CONTROL

These registers store the keyboard and display modes and other operating conditions programmed by the CPU. The modes are programmed by presenting the proper command on the data lines with AO=1 and then sending a WR. The command is latched on the rising edge or WR. The command is then decoded and the appropriate function is set.

The timing control contains the basic timing counter chain. The first counter is a N prescaler that can be programmed to match the CPU cycle time to the internal timing. The prescaler is software programmed to a value between 2 and 31. A value which yields an internal frequency of 100 kHz gives a 5.1 ms keyboard scan time and 10.3 ms debounce time. The other counters divide down the basic internal frequency to provide the proper key scan, row scan, keyboard matrix scan, and display scan times.

# 8.3.3. SCAN COUNTER

The scan counter has two modes. In the encoded mode, the counter provides a binary count that must be externally decoded to provide the scan lines for the keyboard and display. In the decoded mode, the scan counter decodes the least significant 2 bits and provides a decoded 1 of 4 scan. Note than when the keyboard is in decoded scan, so is the display. This means that only the first 4 characters in the Display RAM are displayed.

In the encoded mode, the scan lines are active high outputs. In the decoded mode, the scan lines are active low outputs.

# 8.3.4 RETURN BUFFERS AND KEYBOARD DEBOUNCE AND CONTROL

The 8 return lines are buffered and latched by the Return Buffers. In the keyboard mode, these lines are scanned, looking for key closures in that row. If the debounce circuit detects a closed switch, it waits about 10 msec to check if the switch remains closed. If it does, the address of the switch in the matrix plus the status of SHIFT and CONTROL are transferred to the FIFO. In the scanned Sensor Matrox modes, the contents of the return lines is directly transferred to the corresponding row of the Sensor RAM (FIFO) each key scan time. In Strobed Input mode, the contents of the return lines are transferred to the FIFO on the rising edge of the CNTL/STB line pulse.

# 8.3.5 FIFO/SENSOR RAM AND STATUS

This block is a dual function 8 X 8 RAM. In Key-board or Strobed Input modes, it is a FIFO. Each new entry is written into successive RAM positions and each is then read in order of entry. FIFO status keeps track of the number of characters in the FIFO and whether it is full or empty. Too many reads or writes will be recognized as an error.

The status can be read by an RE with CS low and AO high. The status logic also provides an IRQ signal when the FIFO is not empty. In scanned Sensor Matrix mode, the memory is Sensor RAM. Each row of the Sensor RAM is loaded with the status of the corresponding row of sensor in the sensor matrix. In this mode, IRQ is high if a change in a sensor is detected.

## 8.3.6 DISPLAY ADDRESS REGISTERS AND DISPLAY RAM

The Display Address Registers hold the address of the word currently being written or read by the CPU and the two 4-bit nibbles being displayed. The read/write addresses are programmed by CPU command. They also can be set to auto increment after each read or write. The Display RAM can be directly read by the CPU after the correct mode and address is set. The addresses for the A and B nibbles are automatically updated by the 8279 to match data entry by the CPU. The A and B nibbles can be entered independently or as one word, according to the mode that is set by the CPU. Data entry to the display can be set to either left or right entry. See interface Considerations for details.

# 8.4 SOFTWARE OPERATION

## 8.4.1 8279 COMMANDS

The following commands program the 8279 operating modes. The commands are sent on the Date Bus with CS low and AO high and are loaded to the 8279 on the rising edge of WR.

# 8.4.2 KEYBOARD/DISPLAY MODE SET

MSB

LSB

CODE: 0 0 0 D D K K K

Where DD is the Display Mode and KKK is the Keyboard Mode.

DD

- 0 0 8 8-bit character display Left entry

- 1 0 8 8-bit character display Right entry

- 1 1 16 8-bit character display Right entry

For description of right and left entry, see Interface

Considerations. Note that when decoded scan is set in

keyboard mode, the display is reduced to 4 characters

independent of display mode set.

KKK

0 0 0 Encoded Scan Keyboard - 2 Key Lockout

0 0 1 Decoded Scan Keyboard - 2-Key Lockout

0 1 0 Encoded Scan Keyboard - N-Key Rollover

0 1 1 Decoded Scan Keyboard - N-Key Rollover

1 0 0 Encoded Scan Keyboard - N-Key Rollover

1 0 0 Encoded Scan Sensor Matrix

1 0 1 Decoded Scan Sensor Matrix

1 1 0 Strobed Input, Encoded Display Scan

1 1 Strobed Input, Decoded Display Scan

# 8.4.3 PROGRAM CLOCK

# 8.4.4 READ FIFO/SENSOR RAM

CODE: 0 1 'O AI x A A A A  $-\hat{x}$  Don't Care Where AI is the Auto-Increment flag for the Sensor RAM and AAA is the row that is going to be read by the CPU. AI and AAA are used only if the mode-is set to Sensor Matrix. This command is used to specify that the source

of data reads (CS . Rd . Ao) by the CPU is the FIFO/

Sensor RAM. No additional commands are necessary as

long as data is desired from the FIFO/Sensor RAM.

Another command is necessary if reading is desired

from a different row than has been selected. If AI

is a one, the row select counter will be incremented

after each read so the next read will be from the next

Sensor Ram row.

In the Auto Increment mode for reading data from the FIFO/Sensor RAM, each read advances the address by one so that the next read is from the next character. This Auto Incrementing has no effect on the display.

#### 8.4.5 READ DISPLAY RAM

Where AI is the Auto-Increment flag for the Diaplay RAM and AAAA is the character that the CPU is going to read next. Since the CPU uses the same counter for reading and writing, this command also sets the next write location and Auto-Increment mode. This command is used to specify the display RAM as the data source for CPU data reads. If AI is set, the character address will be incremented after each read (or write) so that the next read (or write) will be from (to) the next

CA has the combined effect of CD and CF. CA uses the CD clearing code to determine how to clear the Display RAM. CA also resets the internal timing chain to resynchronize it.

## 8.4.6 WRITE DISPLAY RAM

Where AI is the Auto-Increment flag for the Display RAM and AAAA is the character that the CPU is going to write next. The addressing and Auto-Increment are indentical to Read Display RAM. The difference is that Write Display RAM does not affect the source of CPU reads. The CPU will read from whichever RAM (Display or FIFO/Sensor) was last epecified. This command will, however, change the location the next Display RAM read will be from if that source was specified.

### 8.4.7 DISPLAY WRITE INHIBIT/BLANKING

CODE: 1 0 1 X IW IW BL BL

Where IW is Inhibit Writing (nibble A or B) and BL is Blanking (nibble A or B). If the display is being used as a dual 4-bit display, then it is necessary to mask

character.

### 8.4.8 CLEAR

Where CD is Clear Display, CF is Clear FIFO Status (including interrupt), and CA is Clear All. CD is used to clear all positions of the Display RAM to a programmable code. All ones, all zeros and hexadecimal 20 are possible. The 2 least significant bits of CD are also used to specify the blanking code (see below).

CD CD CD

O X All Zerox (X Don't Care)

0 AB Hex 20 (0010 0000)

1 1 All Ones

Enable clear display when l(or by CA 1)

Clearing the display takes approximately 160 us. During this time the CPU cannot write to the Display RAM. The MSB of the FIFO status word will be set during this time. CF set the FIFO status to empty and resets the interrupt output line. After execution of a clear command with CF set, the Sensor Matrix mode RAM pointer will be set to row 0.

one of the 4-bit halves so that entries to the Display from the CPU do not affect the other half. The IW flags allow the programmer to do this. It is also useful to be able to blank either half when that half is not to be displayed. The BL flags blank the display. The next command sets the output code to be used as a "blank". Default after reset is all zeros. Note that to blank a display formatted as a single 8-bit output, it is necessary to set both BL flags to entirely blank the display. A "l" sets the flag. Reissuing the command with "O" resets the flag.

# 8.4.9 END INTERRUPT/ERROR MODE SET

CODE: 1 1 1 E X X X X - X Don't care For the sensor matrix modes this command lowers the IRQ line and enables further writing into RAM.

(The IRQ line would have been raised upon the detection of a change in a sensor value. This would have also inhibited further writing into the RAM until reset).

For the N-key rollover mode - if the E bit is \_\_\_\_\_ programmed to "1" the chip will operate in the special Error mode. (For further details, see Interface Considerations Section).

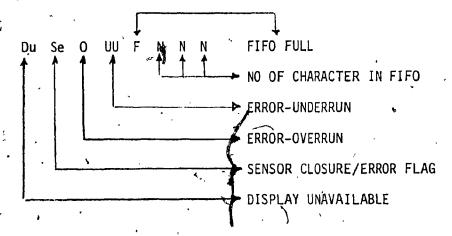

# 8.4.10 STATUS WORD

The status word contains the FIFO status, error, and display unavailable signals. This word is read by the CPU when  $A_{\rm O}$  is high and CS and RD are low. See Interface Considerations for more detail on status word.

## 8.4.11 DATA READ

Data is read when Ao, CS and Rd are all low. The source of the data is specified by the Read FIFO or Read Display commands. The trailing edge of R9 will cause the address of the RAM being read to be incremented if the Auto-Increment flag is set.

FIFO reads always increment (if no error occurs) independent of AI.

#### 8.4. 12 DATA WRITE

Data that is written with Ao, CS and WR low is always written to the Display RAM. The address is specified by the latest Read Display or Write Display command. Auto-Incrementing on the rising edge of WR occurs if AI set by the latest display command.

### 8.5 INTERFACE CONSIDERATIONS

# 8.5.1 SCANNED KEYBOARD MODE, 2-KEY LOCKOUT

There are three possible combinations of conditions that can occur during debounce scanning. When a key is depressed, the debounce logic is set. Other depressed keys are looked for during the next two scans. If none are encountered, it is a single key depression and the key position is entered into the FIFO along with the status of CNTL and SHIFT lines. If the FIFO was empty, IRQ will be set to signal the CPU that there is an entry in the FIFO. If the FIFO was full, the key will not be entered and the error flag will be set. If another closed switch is encountered, no entry to the FIFO can occur. If all other keys are released before this one, then it will be entered to the FIFO. If this key is released before any other, it will be entirely ignored. A key is entered to the FIFO only once per depression, no matter how many keys were pressed along with it or in what order they were released. If two keys are depressed within the debounce cycle, it is a simultaneous depression. Neither key will be recognized until one key remains depressed alone. The last key will be treated as a single key depression.

#### 8.5.2 SCANNED KEYBOARD MODE, N-KEY ROLLOVER

With N-Key Rollover each key depression is treated independently from all others. When a key is depressed, the debounce circuit waits 2 keyboard scans and then checks to see if the key is still down. If it is, the key is entered into the FOFO. Any number of keys can be depressed and another can be recognized and entered into the FIFO. If a simultaneous depression occurs, the keys are recognized and entered according to the order the keyboard scan found them.

## 8.5.3 SCANNED KEYBOARD - SPECIAL ERROR MODES

For N-key rollover mode the user can program a special error mode. This is done by the "End interrupt/Error Mode Set" command. The debounce cycle and key-validity check are as in normal N-key mode. If during a single debounce cycle, two keys are found depressed, this is considered a simultaneous multiple depression, and sets an error flag. This flag will prevent any further writing into the FIFO and will set interrupt (if not yet set). The error flag could be read in this mode by reading the FIFO STATUS word. The error flag is reset by sending the normal CLEAR command with CF = 1.

#### 8.5.4 SENSOR MATRIX MODE

In Sensor Matrix mode, the debounce logic is inhibited. The status of the sensor switch is inputted directly to the Sensor RAM. In this way the Sensor RAM keeps an image of the state of the switches in the sensor matrix. Although debouncing is not provided, this mode has the advantage that the CPU knows how long the sensor was closed and when it was released. A keyboard mode can only indicate a validated closure. To make the software easier, the designer should functionally group the sensors by row since this is the format in which the CPU will read them. The IRQ line goes high if any sensor value change is detected at the end of a sensor matrix scan. The IRQ line is cleared by the first data read operation if the Auto-Increment flag is set to zero, or by the End Interrupt Command if the Auto-Increment flag is set to one.

# 8.5.5 DATA FORMAT

In the Scanned Keyboard mode, the character entered into the FIFO corresponds to the position of the switch in the keyboard plus the status of the CNTL and SHIFT lines (non-inverted).

CNTL is the MSB of the character and SHIFT is the next most significant bit. The next three bits are from the scan counter and indicate the row the key was found in. The last three bits are from the column counter and indicate to which return line the key was connected.

MSB

LSB

CNTL SHIFT

SCAN

RETURN

SCANNED KEYBOARD DATA FORMAT

In Sensor Matrix mode, the data on the return lines is entered directly in the row of the Sensor RAM that corresponds to the row in the matrix being scanned. Therefore, each switch position maps directly to a Sensor RAM position. The SHIFT and CNTL inputs are ignored in this mode. Note that switches are not necessarily the only thing that can be connected to the return lines in this mode. Any logic that can be triggered by the scan lines can enter data to the return line inputs. Eight multiplexed inputs ports could be tied to the return lines and scanned by the 8279.

MSB

LSB

RL7 RL6 RL5 RL4 RL3 RL2 RL1 RL0

In Strobed Input mode, the data is also entered to the FIFO from the return lines.

The data is entered by the rising edge of a CNTL/STB line pulse. Data can come from another encoded keyboard or simple switch matrix. The return lines can also be used as a general purpose strobed input.

LSB MSB

RL3 RL2 RL1 RL5 RL4 RLO RL7 RL6

# 8.5.6 DISPLAY

# 8.5.6.1 Left Entry

Left Entry mode is the simplest display format in that each display position directly corresponds to a byte (or nibble) in the Display RAM. Address 0 in the RAM is the left-most display character and address 15 (or address 7 in 8 character display) is the right most display character. Entering characters from position zero causes the display to fill from the left. The 17th (9th) character is entered back in the left most position and filling again proceeds from there.

LEFT ENTRY MODE (AUTO INCREMENT)

Note that now the display position and register address do not correspond. Consecretly, entering a / character to an arbitrary position in the Auto Increment mode may habe unexpected results. Entry starting at Display RAM address 0 with sequential entry is recommended.

## DESCRIPTION OF THE HARDWARE DESIGN

The SBC 80/05 is composed of the following functional

# blocks:

- a) Clock Generator (inclusing power-up reset).

- b) CPU (including interrupt control).

- c) Bus Interface (address bus drivers, data bus drivers, and bus controllers).

- d) SRandom Access Memory (RAM).

- e) Read Only Memory (ROM/EPROM).

- f) Programmable Keyboard / Display Interfact

- g) Serial I/O Interface

- h) Parallel I/O Interface (including programmable timer).

## 9.1. COMMUNICATION BETWEEN CPU AND THE OTHER LSI

CPU, which is the heart of the system, performs all the system processing functions and generates the address and control signals required to access memory and I/O ports. The CPU multiplexes the 8 - bit data bus and the lower eight bits of the address bus. During the first part of the machine cycle, the lower eight bits on the address/data bus are latched into Demultiplexer U18 and RAM/IO/Timer U15. During the remainder of the machine cycle the bus is used for memory and I/O data transfers. The CPU responds to interrupt requests originating from jumper-selectable sources. As shown in block diagram, these interrupt requests may be generated by the on-board timer and parallel I/O ports, by one or more devices via the Multibus, or by an external source.

~ (\*\*\*\*)

SBC 80/05 BLOCK DIAGRAM WITH 8279 INCLUDED

The 8155 timer is a programmable 14-bit binary down-counter that counts the input pulses and outputs either a square wave or a pulse when the "terminal-count" is reached. The count length and timer output mode are loaded under program control. The four selectable timer modes are as follows:

- Timer Out goes low during the second half of count.

Therefore, the count loaded in the Count Length

Register should be twice the timeout desired.

- b) Timer Out remains high until the first half of the count has been completed and goes low for the second half of the count. The count length is automatically reloaded when the terminal count is reached.

- c) A single low pulse is generated upon reaching the terminal count; this function is useful for generating real-time clocks.

- d) A Divide-by-N Counter generates a repetitive Timer

Out low pulse; a new pulse train is initiated every

time the terminal count is reached.

# 9.2 CIRCUIT ANALYSIS

The schematic diagram for the SBC 80/05 is given. Both active-high and active-low signals are used. A signal mnemonic that ends with a virgule (e.g., DAT7/) denotes that the signal is active low (0.4V).

Conversely, a signal mnemonic without a virgule (e.g., ALE) denotes that the signal is active high (2.0V).

### 9.3 INITIALIZATION

When power is applied in a start-up sequence, the contents of the CPU program counter, instruction register and interrupt enable flip-floware subject to random factors and cannot be predicted. For this reason, a power-up sequence is used to set the CPU (as well as Bus Controller U19 and the I/O ports of U15) to a known internal state.

When power is initially applied to the SBC 80/05, capacitor C1 (1ZC7) begins to charge through resistor R4. The charge developed across C1 is sensed by a Schmitt trigger, which is internal to Clock Generator A3. The Schmitt trigger converts the slow transition appearing at pin 2 into a clear, fast-rising synchronized RESET output signal at pin 1. The RESET signal is inverted by open-collector gate U24-3 to produce Initialize signal INIT/, which is distributed as shown on block diagram. The INIT/ signal clears the CPU program counter, instruction register, and interrupt enable flip-flop; initializes the three I/O ports of U15 to the input mode; and sets Bus controller U19 to a known internal state.

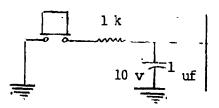

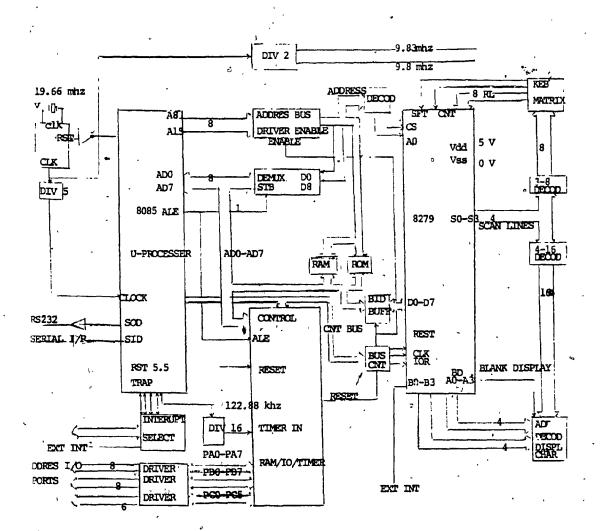

#### 9.4 CLOCK CIRCUITS

The time base for the SBC 80/05 is provided by Clock Generator U3 (1ZC7) and crystal Y1. The 19.6608-MHz output of U3 is divided by U12 (2ZC6) to produce a 9.8304-MHz signal, which is driven through gate U30 to produce Multibus clocks BCLK/ and CCLK/. Jumpers W7 and W8 are provided so that, when removed, some other master module can be used to generate one or both of these clocks if desired.

The 19.6608-MHz output of U3 is divided by U2 (1ZD6) to produce a 3.93216-MHz clock input to CPU U1, which internally divides this into a 1.96608-MHz clock output. This output is further divided by U14 (2ZB6) to produce the 122:88-kHz input to U15 (3ZD4).

The Bus Interface allows the SBC 80/05 to use a system bus that is common to other master devices (e.g., CPU's and DMA controllers), thus allowing system memory and I/O devices to be shared on a priority basis. The primary element of the Bus Interface is Bus Controller U19 which operates synchronously with the bus clock (BCLK/) and consists of the following functional sections:

- a) Bus arbitration logic to resolve bus contention in multiple master systems.

- to ensure adequate setup and hold times for the address and data placed on the Multibus;

also generates read/write control signals.

c) Output drive logic for driving the bus memory and I/O command (control) lines.

When the SBC 80/05 gains control of the Multibus to perform a write operation, the Bus Controller gates the device address and data onto the Multibus and issued a Write command. In performing a read operation, the Bus Controller gates the device address onto the Multibus and issues a Read command. Operations between the CPU and the on-board memory and I/O ports do not require the Multibus. Notice in block diagram that the data bus drivers are bidirectional and the address bus drivers are unidirectional. This allows the SBC 80/05 full control of the Multibus but prevents other modules from accessing the SBC 80/05 memory and I/O ports.

The SBC 80/05 provides eight-bit words of static Random Access Memory (RAM). Two Intel 8111-U4 devices provide 256 words in locations 3E00-3EFF. The Intel 8155 RAM/I0/Timer provices 256 eight-bit words of static RAM in locations 3F00-3FFF.

This 512 word RAM storage area requires neither refreshing nor clock inputs, thereby providing the CPU immediate access to the addressed location.

Two IC sockets are provided to allow to install either 2K or 4K bytes of Read Only Memory (ROM). We install two Intel 2716 (2K x 8) or 8708 (1K x 8) ultraviolet erasable and reprogrammable ROM's (EPROM's) for program development or install two Intel 8316E (2K x 8) or 8408 (1K x 8) masked ROM's containing a dedicated program. Depending on the type of ROM or EPROM installed, the address locations are 0000-07FF (two 1K x 8-bit chips) or 0000-0FFF (two 2K x 8-bit chips).

The Serial I/O Interface is accomplished via the Serial Input Data (SID) and Serial Output Data (SOD) pins on the CPU.

Data on the SID line is loaded into the CPU by a RIM instruction; data on the SOD line is set or cleared by a SIM instruction. Data buffers are provided for TTL level interface. Sockets are provided for the installation of level converters for FS232C interface.

purpose ports provided by the Intel 8155 RAM/IO/Timer. Each of the three ports can be programmed to be either an input port or an output port. One of the three ports (Port 03) can be programmed to be status pins, thus allowing the other two ports (Ports 01 and 02) to operate in a handshake mode. The I/O portion of the 8155 contains four internal registers - one register for command and status and one data register for each of the three ports. Sockets are provided for the installation of input terminators or output drivers as required by the user's configuration.

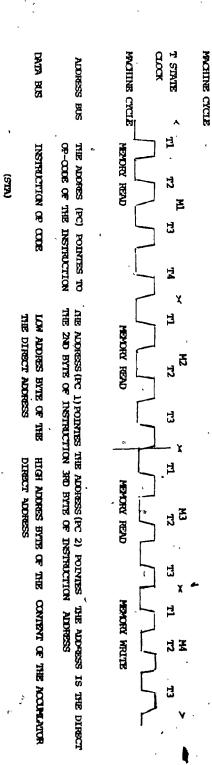

#### 9.5 INSTRUCTION TIMING

The execution of any program consists of read and write operations, where each operation transfers one byte of data between the CPU and a particular memory or I/O address. Although the CPU can vary the address, data, type, and sequence of operations, it is capable of performing only a basic read or write operation. With the execption of a few control lines, such as Address Latch Enable (ALE); these read and write operations are the only communication necessary between the processor and the other components to execute any instruction.