#### ABSTRACT

# HARDWARE IMPLEMENTATION OF DIGITAL FILTERS Saleem G. Zoughbi

This major technical report attempts to put together methods, approaches and techniques which can be used to implement recursive and non-recursive digital filters. In other words, it is the analysis and design of dedicated digital hardware that can be used to perform real-time filtering tasks like the many required in communication systems.

Chapter I introduces the digital filter, its operation and its realizations. It starts with basic definitions of the digital filter, its operation, then the different methods of realization are described.

In Chapter II, the different hardware implementations are described. These implementations include the conventional and combinatorial approaches. Other implementations that use counters, RAMs and residue number systems are described.

Chapter III describes problems, variations and other associated aspects of the approaches used in the hardware implementation of filters. Basic considerations of digital signal processor hardware architecture are described also.

Chapter IV, which concludes the report, gives a summary and an evaluation of the different hardware implementation approaches described in the report.

### ACKNOWLEDGEMENT

I wish to express my gratitude to Professor A.Antoniou for suggesting numerous improvements and guiding me through writing this report.

I wish to thank Miss Margaret Stredder for typing the final manuscript. I also wish to thank Miss Luna Shomali and Miss Amal Shomali for helping in typing the first draft.

Last, but not least, I wish to thank my wife Hiyam for helping and understanding.

## TABLE OF CONTENTS

|                                                  | PAGI              |

|--------------------------------------------------|-------------------|

| ABSTRACT                                         | . i               |

| ACKNOWLEDGEMENTS                                 | . iii             |

| LIST OF FIGURES                                  | :                 |

|                                                  | ·′ vi:            |

| LIST OF TABLES                                   |                   |

| NOTATIONS                                        | . x               |

|                                                  | ' "               |

| CHARMED I DIGITA CONCERNA                        |                   |

| CHAPTER I - BASIC CONCEPTS                       | 1                 |

| 1.1 Introduction                                 | 1                 |

| 1.2 Digital Filter As A System                   | <u>2</u> ~<br>5   |

| 1.3.1 Direct realization'                        | 7                 |

| 1.3.2 Direct canonic realization                 | 7                 |

| 1.3.3 Cascade realization                        | 12                |

| 1.3.4 Parallel realization                       | 14                |

| 1.4 Digital Filter Implementation                | 14,               |

|                                                  |                   |

| CHAPTER II - HARDWARE IMPLEMENTATIONS OF DIGITAL | •                 |

| FILTERS                                          | 1 <b>9</b>        |

| 2.1 Introduction                                 | . 19              |

| 2.2 Conventional Implementations                 | 19                |

|                                                  | 17                |

| 2.2.1 The arithmetic unit                        | . 20              |

| 2.2.2 Implementation of digital filters          | 25<br>28          |

| 2.2.3 Multiplexing                               |                   |

| 2.2.4 Multiplexed hardware structures            | 31                |

| 2.3 Combinatorial Implementations                | 40                |

| 2.3.1 Non-recursive digital filters              | 41                |

| 2.3.2 Memory optimization                        | 42                |

| 2.3.3 Recursive digital filters                  |                   |

| 2.3.4 Monkewich-Steenart implementation          | <u>49.</u><br>58. |

| 2.4.1 Non-recursive digital filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | ,            | •          |              | 0       |       | ***           |      | 11     | •     |     |      |     | PAGE       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------|------------|--------------|---------|-------|---------------|------|--------|-------|-----|------|-----|------------|

| 2.4.2 Extension to negative numbers 2.4.3 Recursive digital filter 2.4.4 Other variations  2.5 High Speed Implementations  2.5 High Speed Implementations  2.5.1 Non-recursive digital filters 2.5.2 Recursive digital filters 2.5.3 Extension to negative numbers  2.6 The RAM digital Filter 2.7 Residue Number System Implementation  2.7.1 The algebra of finite fields 2.7.2 Encoders and decoders 2.7.3 Implementation of digital filters  2.7.1 The algebra of finite fields 2.7.2 Encoders and decoders 2.7.3 Implementation of digital filters  3.1 Introduction 3.2 Techniques in RNS Implementation  3.2 Techniques in RNS Implementation  3.2.1 Scaling 3.2.2 Hardware structure 3.2.3 Other RNS considerations  3.3 Techniques in Direct Implementations  3.3.1 The cycling filter 3.3.2 The Heute filters  3.4 Implementation of Digital Signal Processors  3.4.1 Convolution  14 3.4.1.1 Number theoretic transform 14 3.4.1.2 The Cook-Toom algorithm 14 | ,     | 2.4          | Implementa | ation "      | Všing   | Cou   | nter          | s '  | •      |       |     | į    | . • | . 58       |

| 2.4.3 Recursive digital filter 2.4.4 Other variations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       | 2,4.1        |            |              |         |       |               |      |        |       |     | : [  | •   | 60         |

| 2.4.4 Other variations  2.5 High Speed Implementations  2.5.1 Non-recursive digital filters  2.5.2 Recursive digital filters  2.5.3 Extension to negative numbers  2.6 The RAM digital Filter  2.7 Residue Number System Implementation  2.7.1 The algebra of finite fields  2.7.2 Encoders and decoders  2.7.3 Implementation of digital filters  2.7.1 The algebra of finite fields  2.7.2 Encoders and decoders  2.7.3 Implementation of digital filters  3.1 Introduction  3.2 Techniques in RNS Implementation  3.2 Techniques in RNS Implementation  3.2.1 Scaling  3.2.2 Hardware structure  3.2.3 Other RNS considerations  3.3 Techniques in Direct Implementations  3.3.1 The cycling filter  3.3.2 The Heute filters  3.4 Implementation of Digital Signal  Processors  3.4.1 Convolution  14  3.4.1.1 Number theoretic transform  14  3.4.1.2 The Cook-Toom algorithm  14                                                                                    |       |              |            |              |         |       |               | ers  | 3      |       |     |      |     | 63         |

| 2.5 High Speed Implementations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |              |            |              |         | filt  | er            | •    | • •    | • •   | .•  | !    | •   | 69         |

| 2.5.1 Non-recursive digital filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | 2.4.4        | Other va   | irlati       | .ons    | • ~ • | • •           | •    | •      | • •   | •   | •    | •   | 76         |

| 2.5.2 Recursive digital filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       | 2.5          | High Speed | l'Impl       | .ement  | atio  | ns .          | .•   | •      |       | •   | •    |     | 85         |

| 2.5.2 Recursive digital filters 2.5.3 Extension to negative numbers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •     | 2.5.1        | Non-rect   | ırqive       | diai    | ta1   | fil+          | ATS  |        |       |     |      |     | 85         |

| 2.5.3 Extension to negative numbers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1     |              |            |              |         |       |               |      |        | • •   | •   | :    | •   | 90         |

| 2.7 Residue Number System Implementation . 102 2.7.1 The algebra of finite fields . 103 2.7.2 Encoders and decoders                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |              |            |              |         |       |               |      |        | ./.   | ٠   | •    | •   | 93         |

| 2.7 Residue Number System Implementation . 102 2.7.1 The algebra of finite fields . 103 2.7.2 Encoders and decoders                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | , ,   | 26           | The PAM    | diait        | ១1 គាត់ | 1+22  |               |      | , ge   | ¢.,   |     |      |     | 96         |

| 2.7.1 The algebra of finite fields                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |              |            |              |         |       |               | eni  | iat:   | ion   | •   | •    |     |            |

| 2.7.2 Encoders and decoders 2.7.3 Implementation of digital filters  112  CHAPTER III - FURTHER ASPECTS OF IMPLEMENTATIONS  3.1 Introduction 3.2 Techniques in RNS Implementation  113  3.2.1 Scaling 114  3.2.2 Hardware structure 125  3.3.2 Techniques in Direct Implementations 126  3.3.1 The cycling filter 3.3.2 The Heute filters 13  3.4 Implementation of Digital Signal Processors 13  3.4.1 Convolution 14  3.4.1.1 Number theoretic transform 15  3.4.1.2 The Cook-Toom algorithm 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -     |              | ٠.,        |              | _       |       | _             |      | •      |       | •   | •    | ٠.  | ₹          |

| 2.7.3 Implementation of digital filters 112  CHAPTER III - FURTHER ASPECTS OF IMPLEMENTATIONS 113  3.1 Introduction 114 3.2 Techniques in RNS Implementation 115  3.2.1 Scaling 115  3.2.2 Hardware structure 125  3.2.3 Other RNS considerations 125  3.3 Techniques in Direct Implementations 125  3.3.1 The cycling filter 125  3.3.2 The Heute filters 135  3.4 Implementation of Digital Signal Processors 135  3.4.1 Convolution 145  3.4.1.1 Number theoretic transform 145  3.4.1.1 Number theoretic transform 145  3.4.1.2 The Cook-Toom algorithm 145                                                                                                                                                                                                                                                                                                                                                                                                          |       |              |            |              |         |       | fiel          | .ds  | ,      |       | •   | •    |     | 105        |

| CHAPTER III - FURTHER ASPECTS OF IMPLEMENTATIONS . 118  3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •     |              |            |              |         |       | `• <b>,</b> • | ٠.,  | •      | • •   | •   | •    | •   | 108        |

| 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | 2.7.3        | Tubremen   | itatio       | n or    | algi  | tal           | Il.  | Lte:   | rs    |     | •    |     | 112        |

| 3.2 Techniques in RNS Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CHAP' | TER II       | I – FURI   | THÉR A       | SPECI   | S OF  | IMP           | LEN  | ÆN     | TAT   | IOŅ | 1S., | • • | , 118      |

| 3.2 Techniques in RNS Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       | ′3 <b>.1</b> | Introducti | lon          |         |       |               |      |        | •     |     |      |     | 119        |

| 3.2.1 Scaling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       | 3.2          | rechniques | in           | RNS     | Impl  | emen          | tat  | io     | n.    | •   | •    | •   |            |

| 3.2.2 Hardware structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       | 3 2 1        | Saalina    |              |         |       |               |      |        |       |     |      |     | 119        |

| 3.2.3 Other RNS considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |              |            |              | cture   |       | • •           | •    | •      | • •   | •   | •    | •   |            |

| 3.3.1 The cycling filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |              |            |              |         |       | ions          |      | :      | • •   | •   | :    | :   | 122        |

| 3.3.1 The cycling filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       | 3.3 7        |            |              | *       |       |               |      | ıt i.e | วทร   |     |      |     | 128        |

| 3.3.2 The Heute filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       | 3.5          |            | , 4 <i>2</i> |         |       |               |      |        |       | •   | •    | •   | 120        |

| 3.4 Implementation of Digital Signal Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | `     | ₹3.3.1       |            |              |         | •     |               |      |        | •′ ′• | •   |      | •   | 128        |

| Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | *     | 3.3.2        | The Heut   | e fil        | ters    | , • • |               | •    | •      | ٤.    | •   | •    |     | 131        |

| 3.4.1 Convolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |              |            |              | of Di   | gita  | l Si          | gna  | 1      | •     |     |      |     |            |

| 3.4.1.1 Number theoretic transform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       | I            | Processors |              | • • •   | • •   | • •           | •    | •      | • •   | •   | •    | •   | <b>137</b> |

| 3.4.1.2 The Cook-Toom algorithm 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •     | 3.4.1        | Convolut   | ion          |         |       |               | •    |        |       | •   | ••   | ·•  | 141        |

| 3.4.1.2 The Cook-Toom algorithm 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       | 3.4.1        | .1 Number  | then         | retio   | tra   | nsfo          | חדיב | _      |       | _   |      |     | 144        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |              |            |              |         |       |               |      | •      | • •   | •   | •    |     | 148        |

| I A / WWW 1Mm lamantations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       | 3 1 2        |            | laman        | +=+i>   | ne    |               |      |        |       |     |      | 1   | 152        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |              |            |              |         |       | • •           | :    |        |       | •   | •    | ·•• | 157        |

)

なきないです。

. 4. 0.4.

| ••         |     |   |     | 4   |     |    |    |   |   | 4- | ,   |   | •         |    |    |   | _ |   |     |    | 4 | PAGE | į |

|------------|-----|---|-----|-----|-----|----|----|---|---|----|-----|---|-----------|----|----|---|---|---|-----|----|---|------|---|

| CHAPTER IV | -   | ( | 201 | 1C1 | LUS | IC | NC |   |   | •  | . • |   |           | /• | •  | • | • |   | - • | •  |   | 159  |   |

|            | `   |   |     |     | ,   |    |    |   |   |    |     | • | 1         |    |    | • |   |   |     |    |   |      | , |

| REFERENCES | •   | • | •   | ٠   | •   | •  | •  | • | • | •  | •   | • | <b>/•</b> | •  | •  | • | • | • | -   | •  |   | 163  |   |

| ADDITIONAL | REI | E | REI | 4CI | ES  |    | •  | • | • | •  | ٠   | • |           | •  | ₩, | • | • | • | •   | ັ• | • | 166  |   |

\*

## LIST OF FIGURES

|        |                                                             | Ī        |

|--------|-------------------------------------------------------------|----------|

| FIGURE | PAG                                                         | Ε        |

| 1,1    | The digital filter as a system 3                            |          |

| 1.2    | Direct realization of H(z) 8                                | l        |

| 1.3    | The realization of $N(z)$                                   | ,        |

| 1.4    | Direct realization of a second-order filter                 | ,<br>)   |

| 1.5    | The Canonic realization of $H(z)$ 11                        |          |

| 1.6    | A canonic second-order section                              | }        |

| 1.7    | A cascade realization of H(z)                               | }.       |

| . 1.8  | Parallel realization of H(z)                                | ,<br>5   |

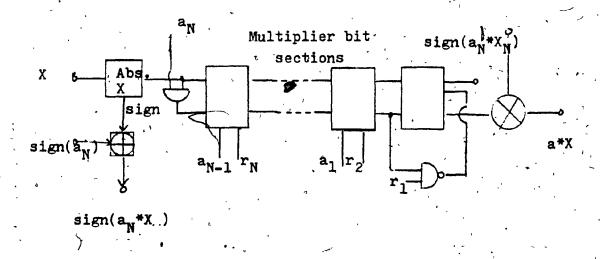

| 2.1(a) | Serial multiplier for signed magnitude 20                   | <b>,</b> |

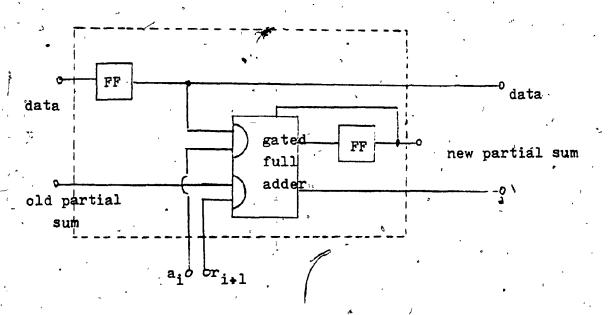

| 2.1(b) | A multiplier bit section                                    | 4        |

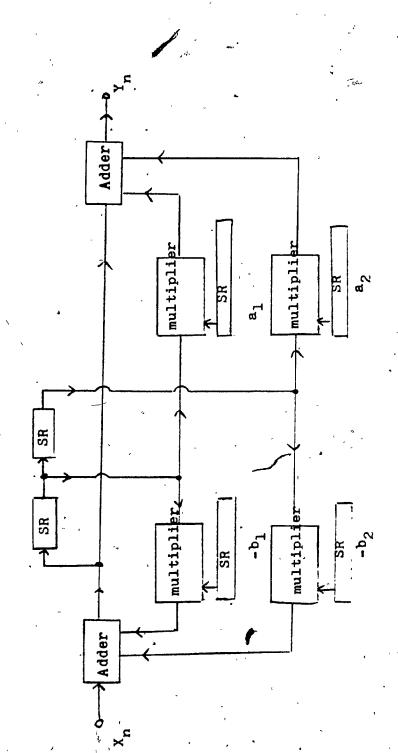

| 2.2    | The basic conventional second-order section . 29            | 3        |

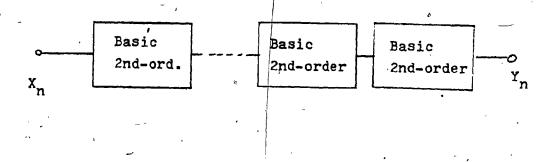

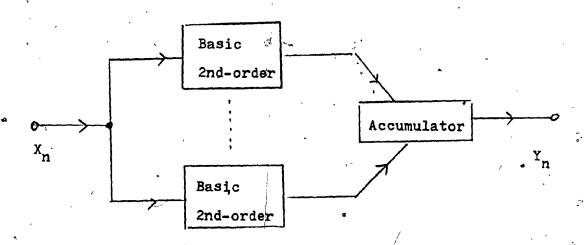

| 2.3    | Cascade implementation using second-order sections          | 0        |

| 2.4    | Parallel implementation using second-order sections         | 0        |

| 2.5    | Type I multiplexing in conventional implementation          | 2        |

| 2.6    | Type II multiplexing in conventional implementation         | 3        |

| 2.7    | A realization of a second-order section 3                   | 5        |

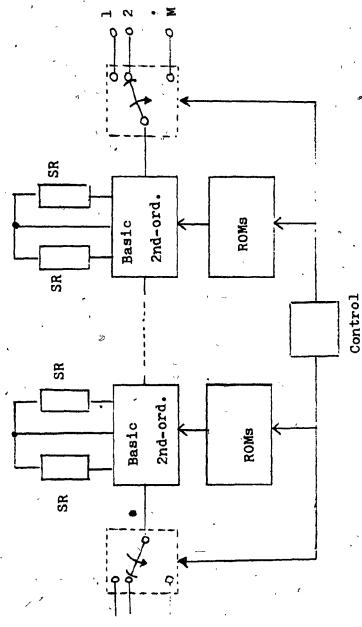

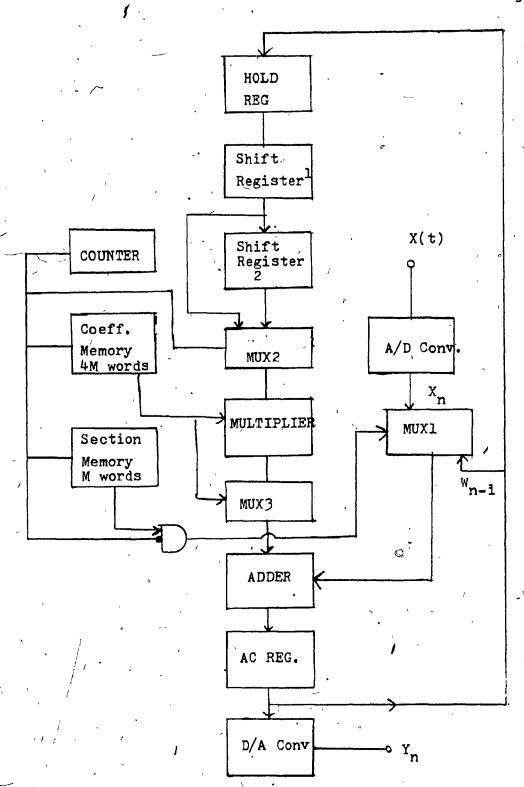

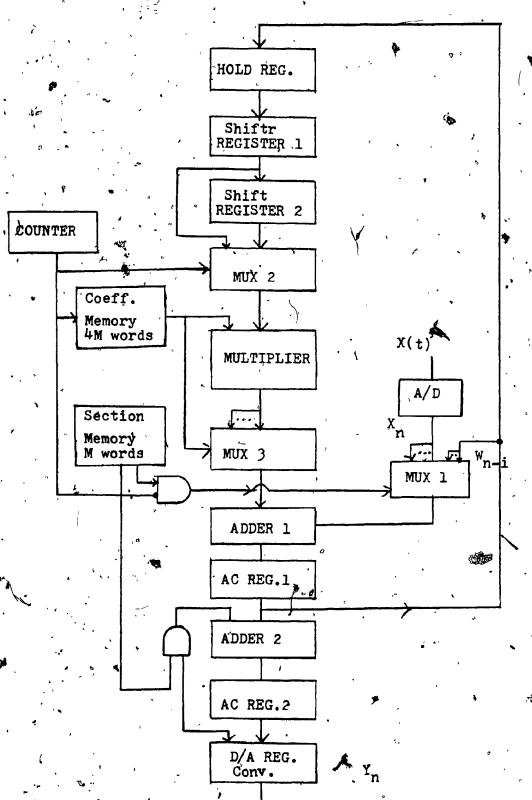

| 2.8    | Gabel's hardware structure for cascade sections             | 6        |

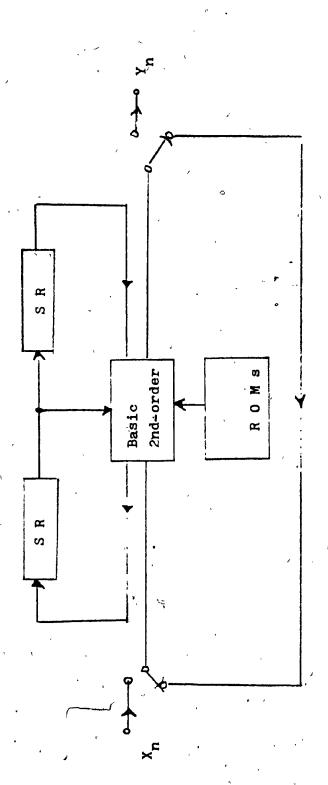

| 2.9    | Gabel's hardware structure for parallel or cascade sections | 9        |

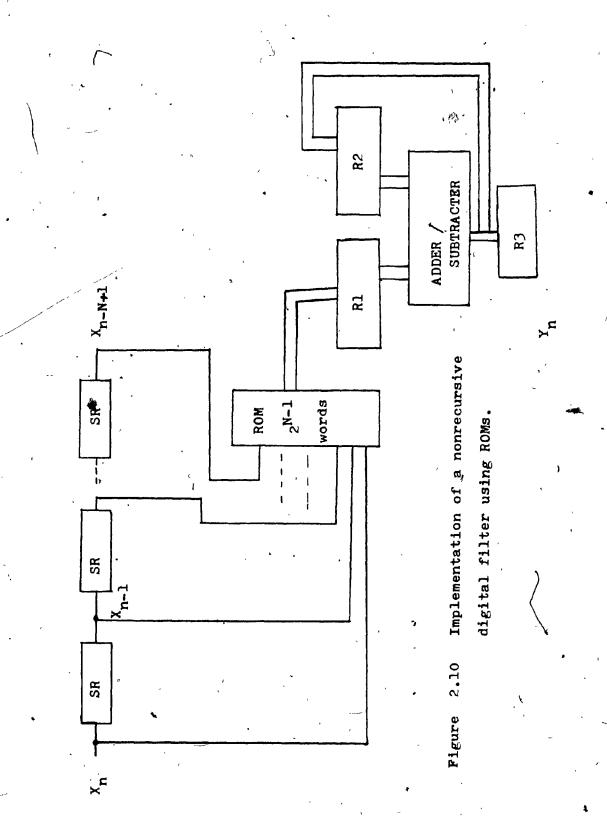

| 2.10   | Implementation of a nonrecursive digital filter using ROMs  | 2        |

| FIGURE |                                                                                                                                                                        | PAGE        |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

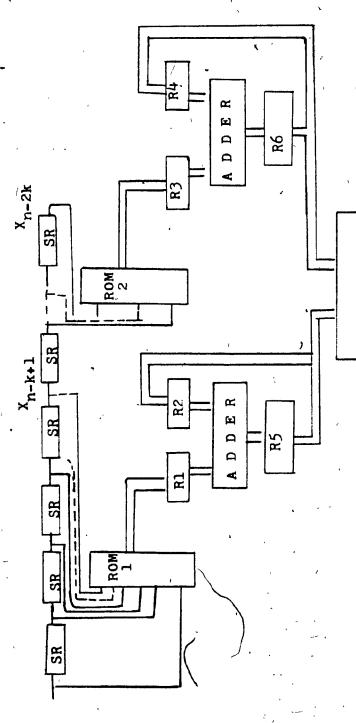

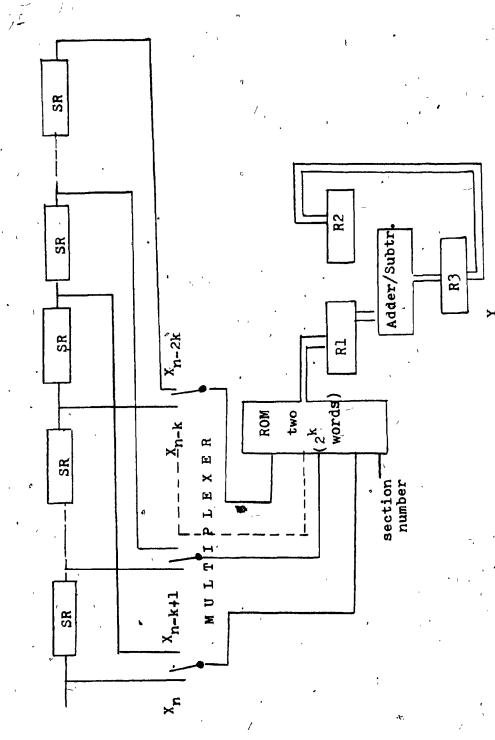

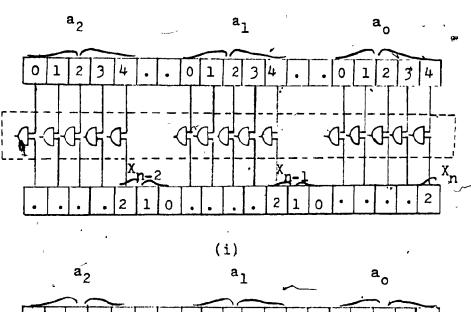

| 2.11   | The implementation of an Nth - order non-recursive filter by splitting it into two sections of kth - order, each, N=2k. For N=MK, M adders have to operate in parallel | . 46        |

| 2.12   | The nonrecursive filter of order N=2k in a serial fashion                                                                                                              | 48.         |

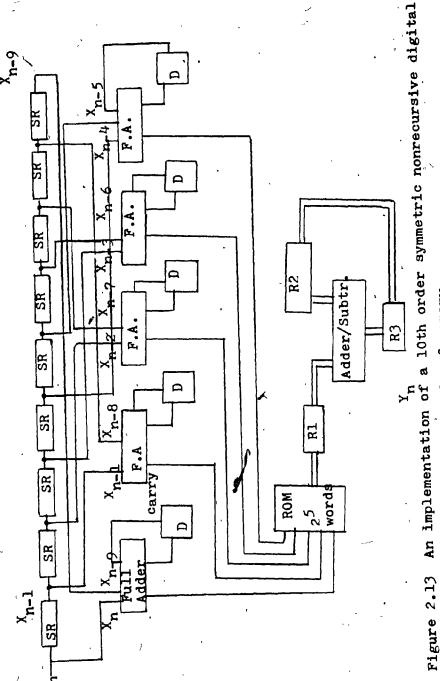

| 2.13   | An implementation of a $10\frac{\text{th}}{\text{-}}$ - order symmetric nonrecursive digital filter using 32 words of memory                                           | 50 <b>′</b> |

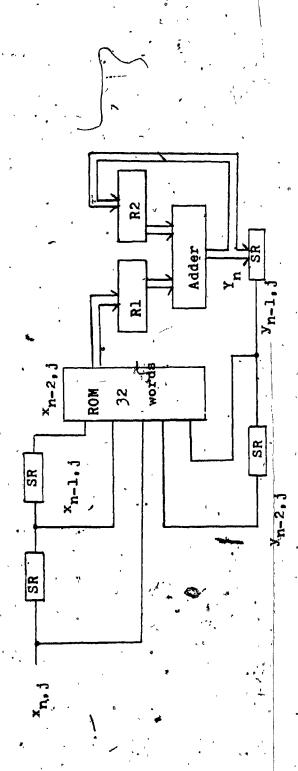

| 2.14   | A bit serial implementation using ROM for a recursive digital filter                                                                                                   | 53          |

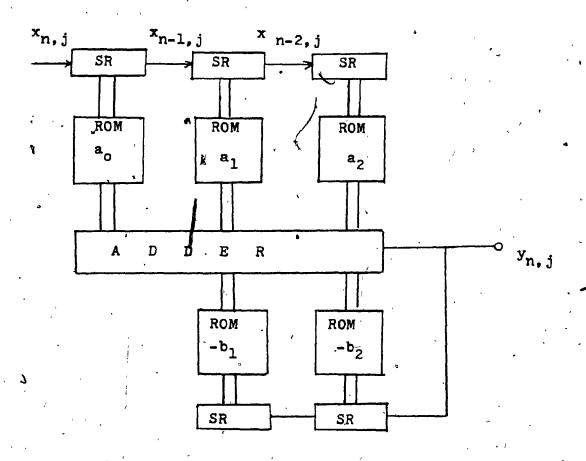

| 2.15(  | a) A second-order recursive filter using a ROM                                                                                                                         | 54          |

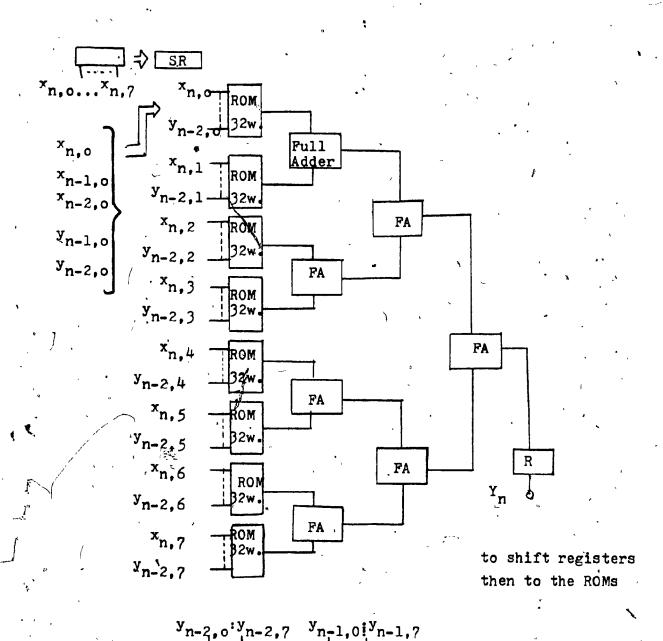

| 2.15(  | o) A fully parallel implementation of a second-order section using ROM's                                                                                               | 55          |

| 2.16   | A parallel 6th - order ROM implementation                                                                                                                              | 56          |

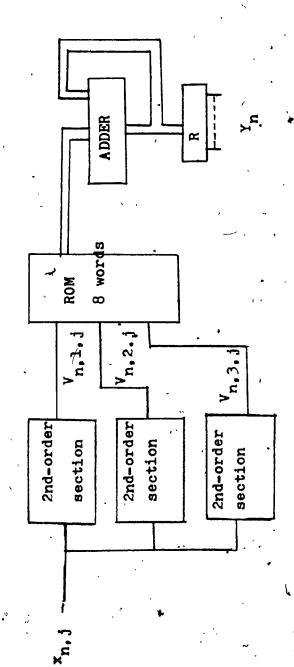

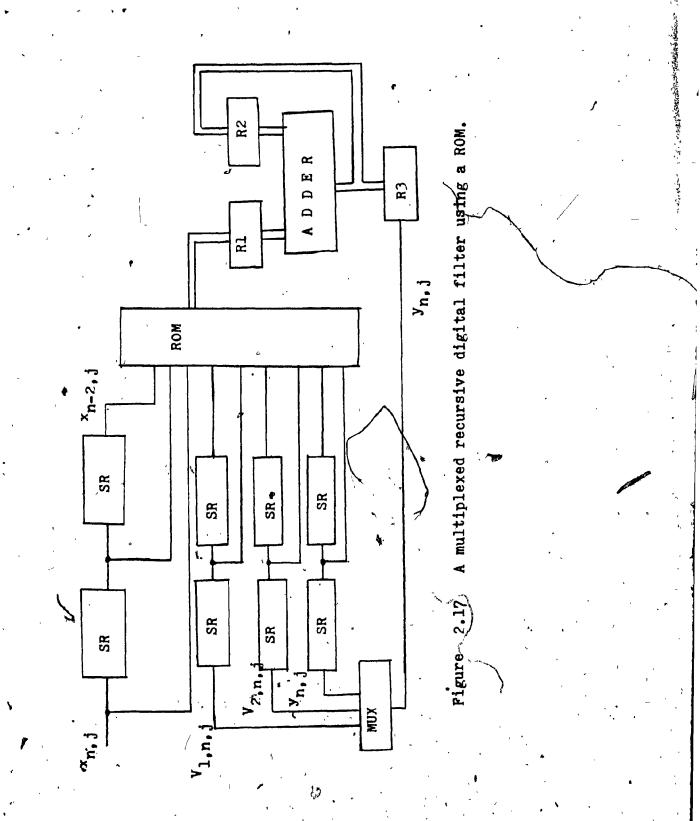

| 2.17   | A multiplexed recursive digital filter using an ROM                                                                                                                    | 57          |

| 2.18   | Steenart-Monkewich implementation of a second-order section                                                                                                            | . 59        |

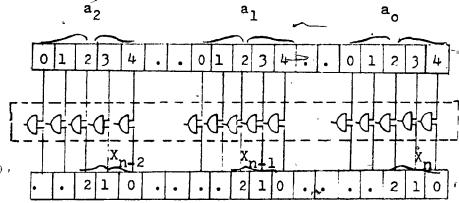

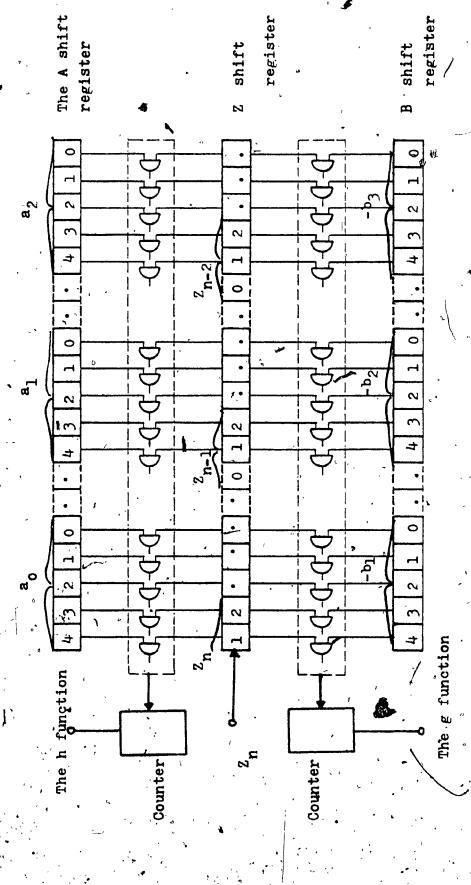

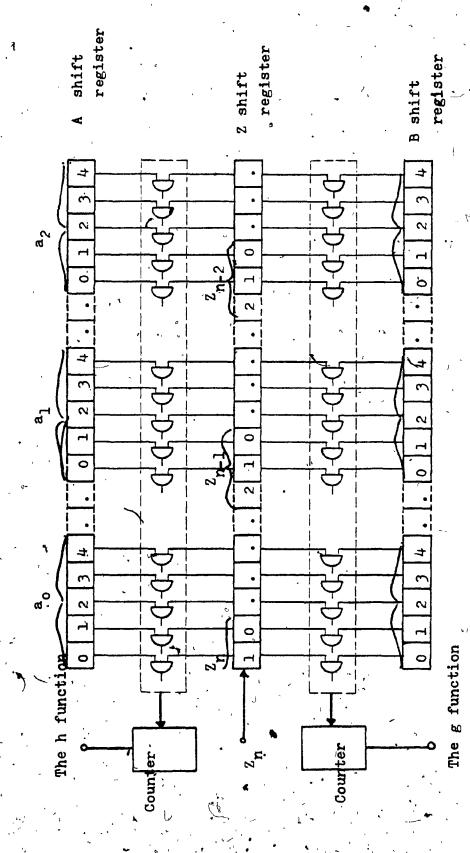

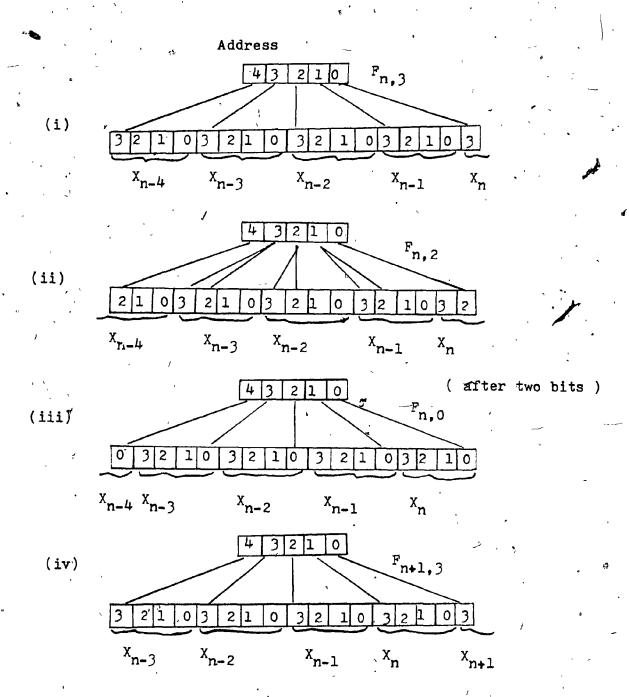

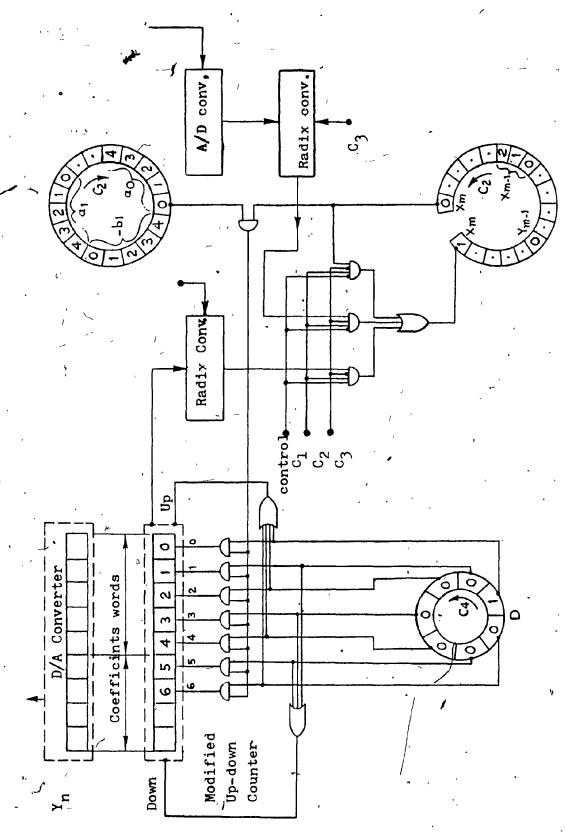

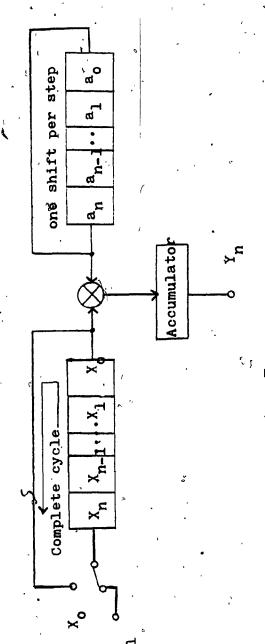

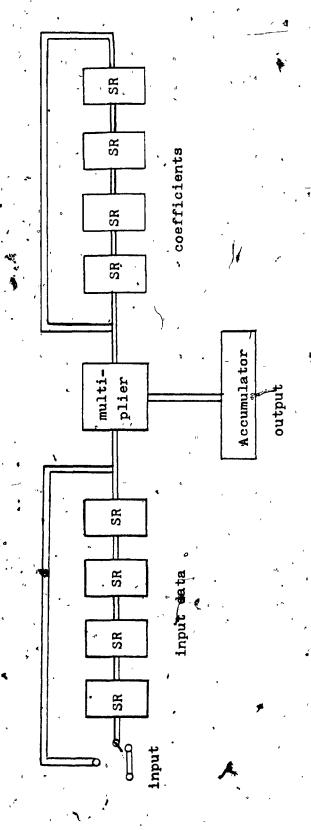

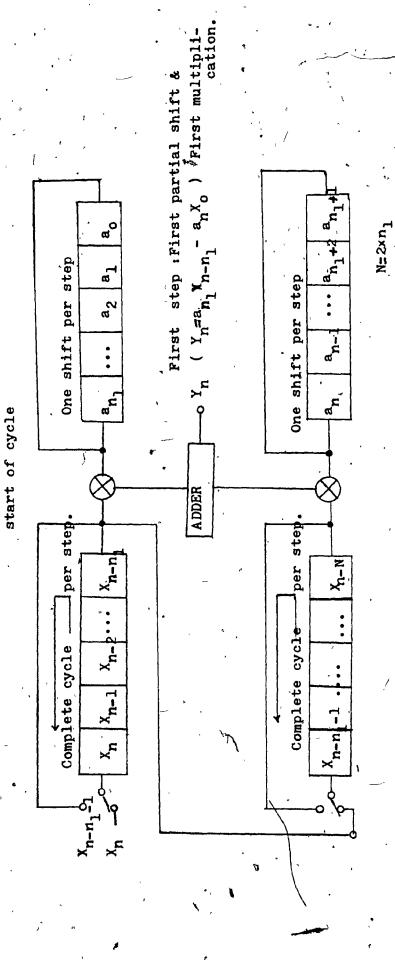

| 2.19   | The shifting and counting process                                                                                                                                      | 64          |

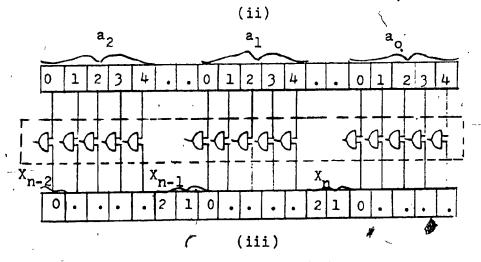

| 2.20   | The nonrecursive counting digital filter                                                                                                                               | 65          |

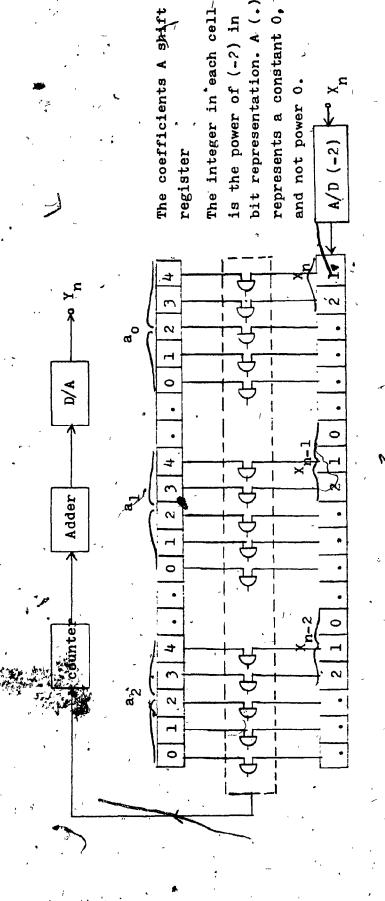

| 2.21   | The recursive filter implemented with counters                                                                                                                         | . 75        |

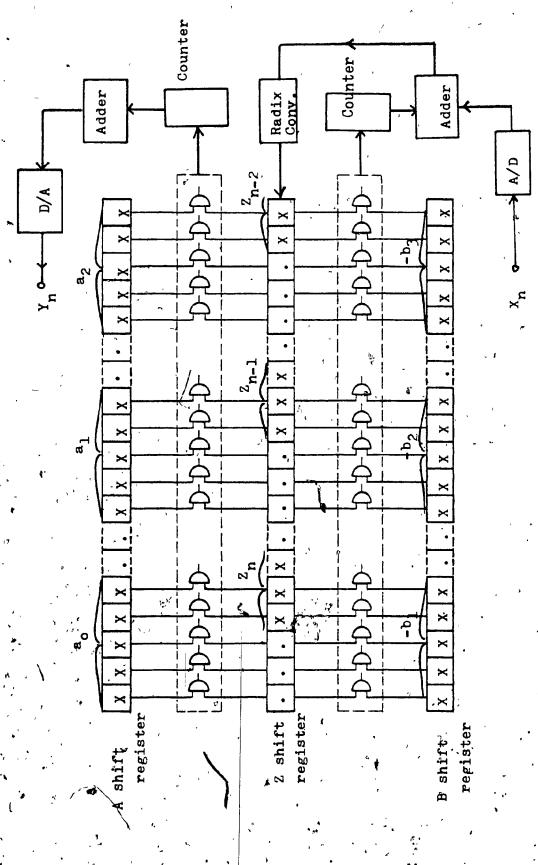

| `2.22  | Shifting in an increasing index (IIS) sequence                                                                                                                         | 77          |

| 2.23   | Shifting in a decreasing index (DIS) sequence                                                                                                                          | 78          |

| 2.24   | A recursive filter implemented using counters in direct realization                                                                                                    | 81          |

| 2.25   | Canonic variation of the counting recursive digital filter                                                                                                             | . 84        |

/ .

0

| FIGURE     |                                                                                                  | PAGE  |

|------------|--------------------------------------------------------------------------------------------------|-------|

| 2.26       | Nonrecursive filter implemented according to Little's algorithm                                  | . 91  |

| 2.27       | Recursive filter implemented according to Little's algorithm                                     | 94    |

| 2.28       | The RAM nonrecursive filter                                                                      | 100   |

| 2.29       | Shifting and generating a RAM address                                                            | 101   |

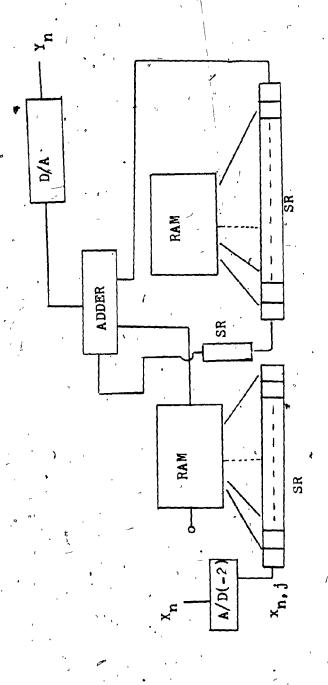

| 2.30       | A recursive RAM filter using two RAMs                                                            | 103   |

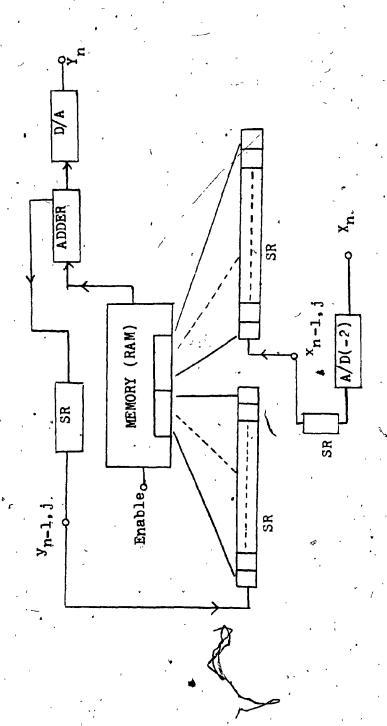

| 2.31       | A RAM recursive filter                                                                           | 104   |

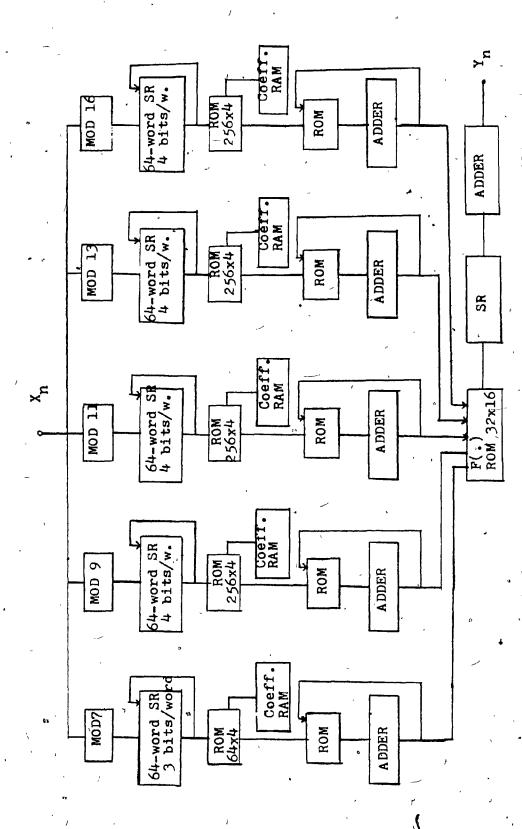

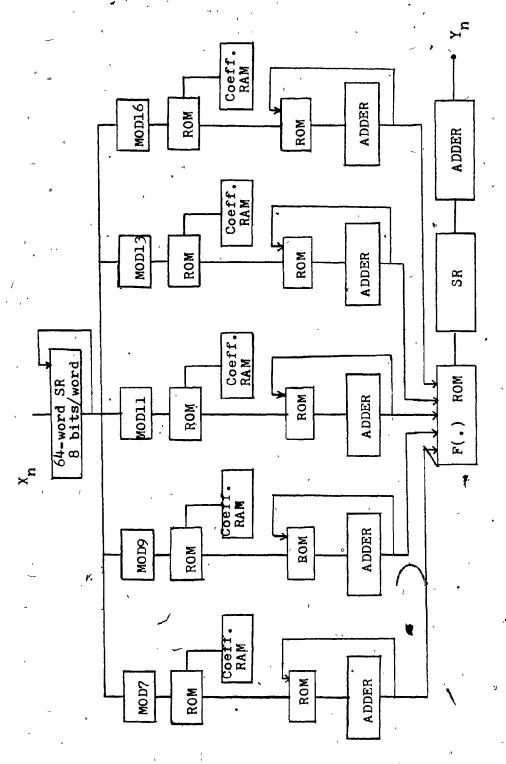

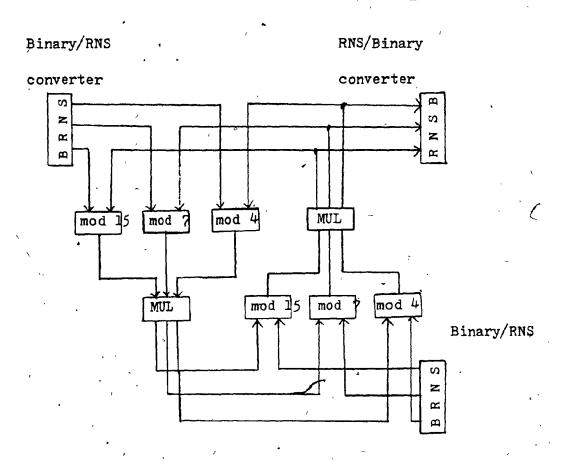

| 2.32       | A residue number implementation of digital filters. 5 moduli are used: 7,9,11,13,16              | 115   |

| 2.33       | Another RNS implementation of filters                                                            | , 117 |

| <b>5</b>   |                                                                                                  |       |

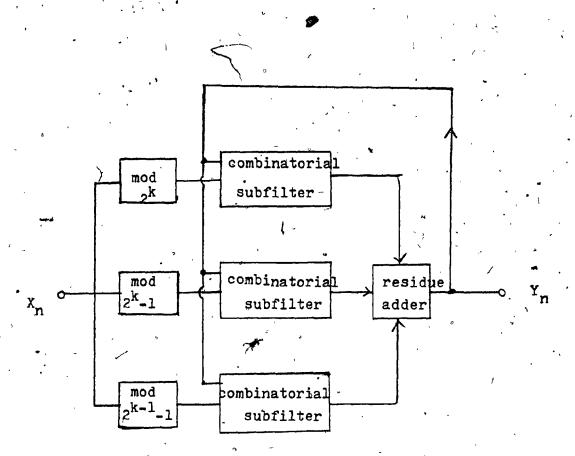

| 3.1        | Architecture for a combinatorial recursive filter in residue number system                       | 121   |

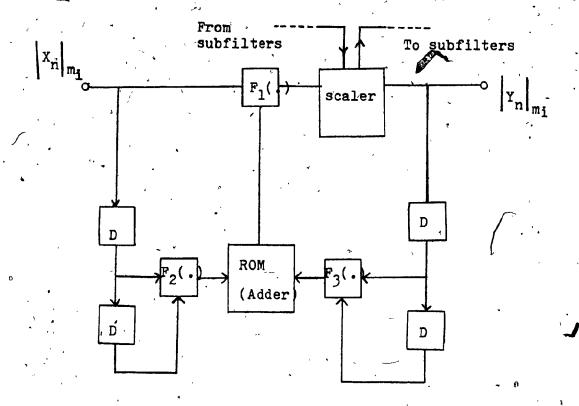

| 3.2        | Architecture for a high-speed combinatorial filter in a general residue system with 4-bit moduli | 123   |

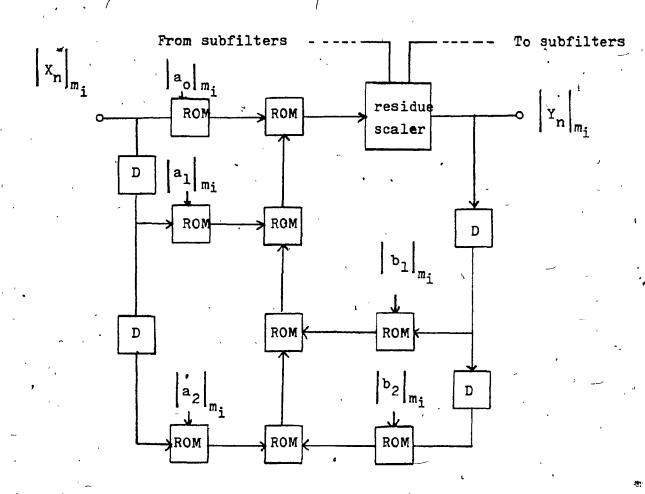

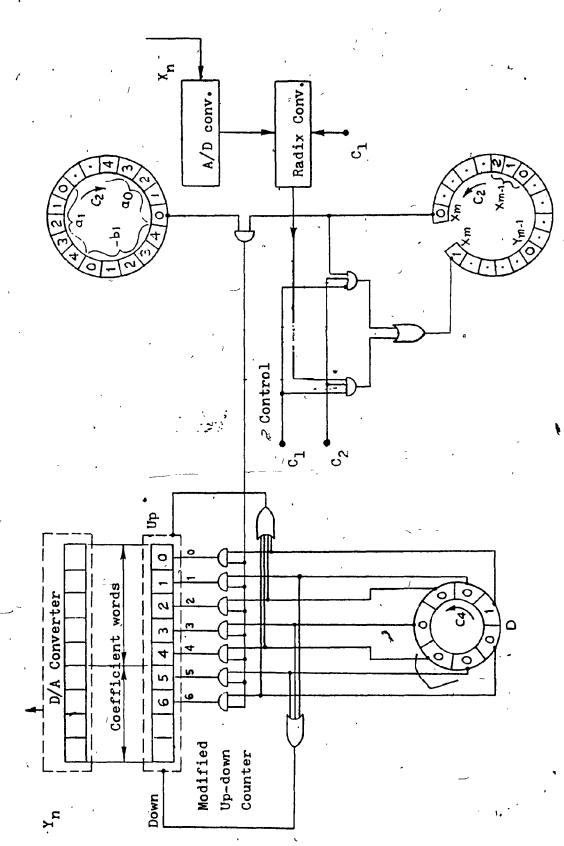

| 3.3        | Architecture with general ROM multipliers for an adaptive second-order section                   | 125   |

| 3.4        | A residue number system second-order section based on Soderstrand's approach                     | 126   |

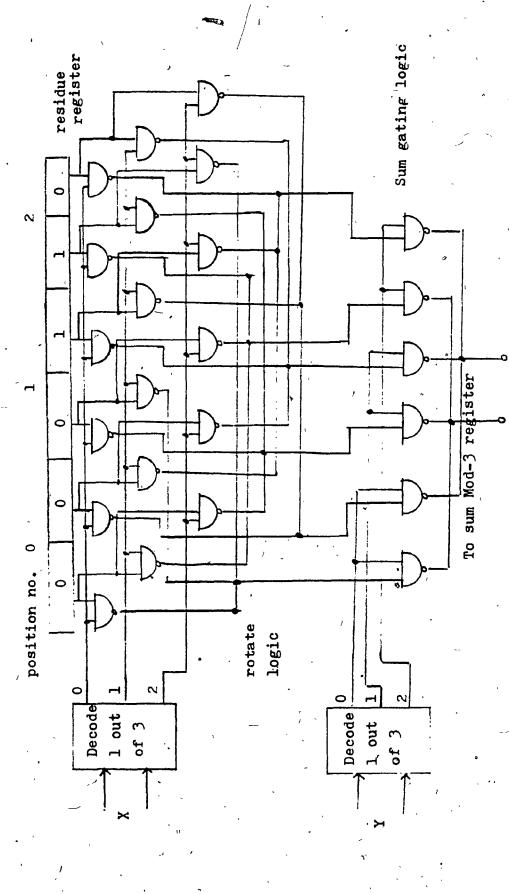

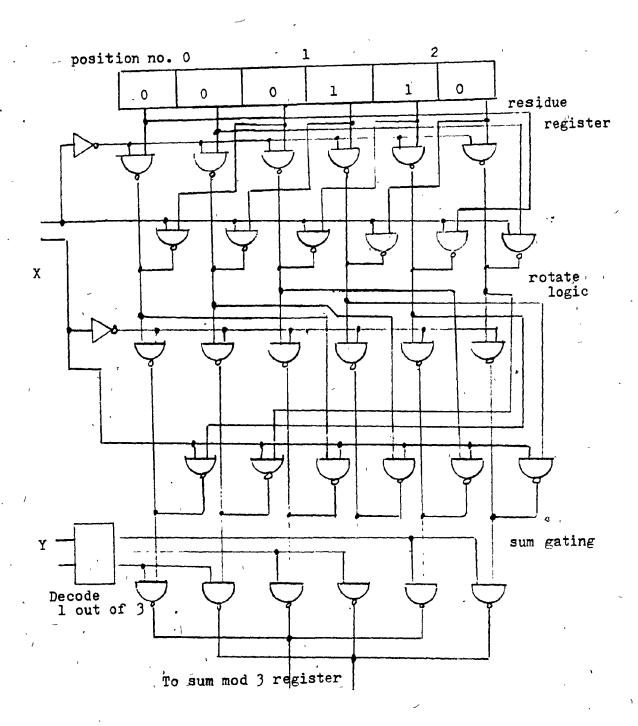

| 3.5        | Modulo 3 adder realization using rotate logic .                                                  | 129   |

| 3.6        | Alternative implementation of mod adder (mod-3) using rotation by power of 2                     | 130   |

| 3.7        | The cycling nonrecursive filter                                                                  | 132   |

| <b>3.8</b> | The cycling recursive filter                                                                     | 133   |

| 3.9.       | The Heute implementation using a multiplier                                                      | 135   |

| 3.10       | The pasic structure for the Heute filters                                                        | 136   |

| 3.11       | A parallel double section Heute filter                                                           | -138  |

| 3.12       | The Heute implementation using two multipliers                                                   | 139   |

,

| FIGURE |                                                                        | PAGE |

|--------|------------------------------------------------------------------------|------|

| 3.13   | Combined parallelism : two multipliers and two general shift registers | 140  |

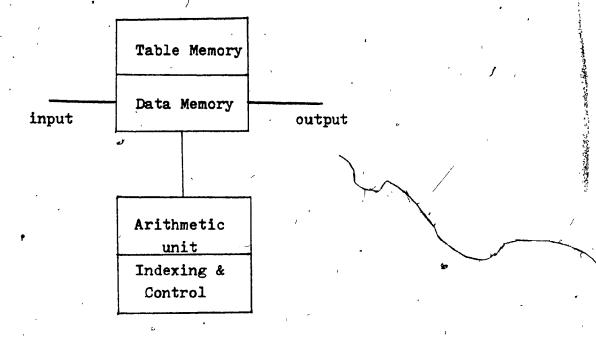

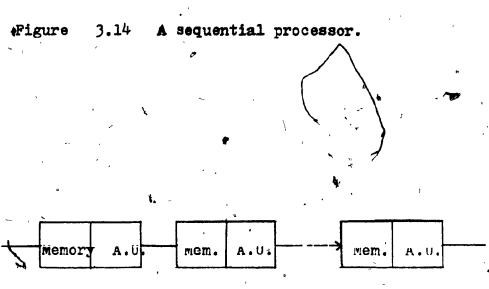

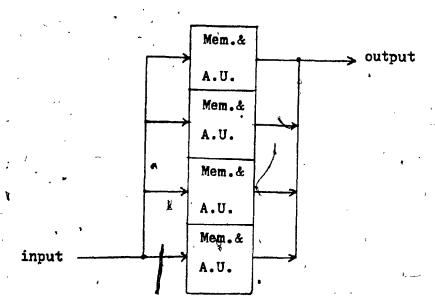

| 3.14   | A sequential processor                                                 | 154  |

| 3.15   | A cascade processor                                                    | 154  |

| 3.16   | Parallel iterative processor                                           | 156  |

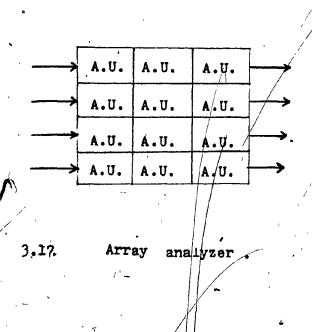

| 3.17   | Array analyzer                                                         | .156 |

| ,      |                                                                        | •    |

| •      |                                                                        | • '  |

| •      | LIST OF TABLES                                                         | t    |

| TABLE  | · · · · · · · · · · · · · · · · · · ·                                  | PAGE |

| 2.1    | Control and timing in Gabel's multiplexed filter                       | 37   |

#### NOTATIONS

| a                                                                    | The ith coefficient of a filter (for input data                                              |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| b <sub>i</sub>                                                       | The ith coefficient of a filter (for delayed output in a recursive filter)                   |

| В                                                                    | The word-length in bits                                                                      |

| · Ba                                                                 | The word-length of a                                                                         |

| B <sub>x</sub>                                                       | The word-length of the input data word                                                       |

| <sup>B</sup> t                                                       | The total word-length for a shift register in the counting implementation, = $B_a + B_x - 1$ |

| b <sub>jk</sub>                                                      | The $k \pm \frac{th}{t}$ bit of the $j \pm \frac{th}{t}$ coefficient                         |

| e <sub>i</sub> ,f <sub>i</sub> ,<br>j' <sup>g</sup> i,h <sub>i</sub> | Logic functions of i,j                                                                       |

| F <sub>t</sub>                                                       | The tth Fermat number                                                                        |

| F (p)                                                                | A Galois field of order p                                                                    |

| H(z)                                                                 | The transfer function in the z-domain                                                        |

| mi                                                                   | The ith modulo in a residue number system                                                    |

| m-1                                                                  | The multiplicative inverse of m                                                              |

| m <sub>i</sub> .                                                     | The dynamic range of the modulo $\mathbf{m}_{\mathbf{i}}$ in a residue number system         |

| m 1                                                                  | The multiplicative inverse of $\overline{m}_{i}$                                             |

| ,R                                                                   | The response of a filter                                                                     |

| Ť                                                                    | The sampling period                                                                          |

| X(nT)                                                                | The nth sample of input data                                                                 |

| $\overline{\mathbf{x}}$                                              | The Discrete Fourier transform                                                               |

|                                                                      |                                                                                              |

$\mathbf{X_i}(\mathbf{n})$  ,  $|\mathbf{X_n}|_{\hat{\mathbf{m}}_i}$  The input data modulo  $\mathbf{m}_i$  in a residue number system

- X(z) The Z-transform of the input

- $Y_{i}^{(n),|Y_{n}|_{m}}$  The output modulo  $m_{i}$  in a residue number system

- Y(z) The Z-transform of the output

- $Y_{i,n}$  The  $i\frac{th}{n}$  partial result of the  $n\frac{th}{n}$  output sample

- α ¸ij

- /)β ij

- Y<sub>ij</sub>

- $^{\delta}$ ij

- Binary bits for discrete numbers in binary representation

- "i

- ۷ij

- ρ<sub>ij</sub>

## CHAPTER I BASIC CONCEPTS

### 1.1 INTRODUCTION

of a signal can be reshaped, modified or manipulated according to some desired specification. It may include amplifying, attenuating, rejecting or isolating frequency components. Such a process can be used to eliminate signal contamination such as noise, to remove signal distortion. brought about by an imperfect transmission channel, to separate two or more distinct signals and many other applications.

The digital filter is a digital system that is used to filter discrete time signals. It is implemented by means of software (computer programs) or by means of dedicated hardware. The hardware implementation is very useful for real-time data, although real-time and non-real-time data can be filtered by both a hardware or a software-implemented digital filter.

Digital filters have tremendous applications in digital signal processing. These include digital communications, acoustics, biomedical engineering, radar systems, mov/ing-target indicators, and so forth. The development in digital-filter hardware is progressing rapidly. This will lead to

the production of efficient and low-cost digital filters that are suitable for a variety of applications.

## 1.2 THE DIGITAL FILTER AS A SYSTEM

A digital filter can be viewed as a system. The input is a discrete time quantized function which would excite the filter to produce a discrete time output. Figure 1.1 depicts such a representation. The response is related to the excitation by some rule of correspondence. If X(nT) and Y(nT) are the excitation and the response, respectively, then the filter can be characterized by

$$Y(nT) = R X(nT)$$

(1.1)

where

R is an operator.

If the internal parameters of the filter do not change with time, the digital filter is said to be time-invarient. Usually, the response of a filter depends on the current and some previous values of the excitation. Such filters are said to be causal. On the other hand, filters in which the response depends on future values of the excitation, are said to be noncausal.

If the response of a digital filter is a linear function of the excitation, the filter is linear. For example, a linear digital filter would have its response doubled if

Figure 1.1 The digital filter as a system.

ř

٠...

~J

its excitation is doubled. In addition, in a linear filter, the response to a sum of different excitations is the sum of the individual responses.

Digital filters are of two basic types: recursive and non-recursive. A non-recursive digital filter is one in which the response depends only on the values of the excitation, that is

$$Y(nT) = f\{..., X(nT-T), X(nT), X(nT+T) ...\}$$

Assuming the filter to be linear and time-invarient, Y(nT) can be expressed as

$$Y(nT) = \sum_{i=-\infty}^{\infty} a_i X(nT-iT)$$

where

a; represent constants.

Furthermore, if the filter is causal

$$a_{-1} = a_{-2} = \dots = a_{-\infty} = 0$$

Hence

$$Y(nT) = \sum_{i=0}^{\infty} a_i X(nT-iT)$$

If X(nT) = 0 for n < 0 and  $a_i = 0$  for i > N, then

$$Y(nT) = \sum_{i=0}^{N} a_i X(nT-iT)$$

(1.2)

Therefore, any linear, time-invarient, causal, non-recursive filter can be represented by an  $N^{\frac{th}{h}}$  - order difference equation. N is the order of the filter.

The recursive digital filter, on the other hand, has a response which depends on current and previous values of the excitation and the previous values of the responses. So, for a linear, time-invarient causal filter

$$Y(nT) = \sum_{i=0}^{N} a_i X(nT-iT) - \sum_{i=1}^{N} b_i Y(nT-iT) \qquad (1.3)$$

## 1.3 DIGITAL FILTER REALIZATIONS

There are three types of elements involved in the digital filter realization: the unit delay, the adder and the multiplier. The proper inter-connection of these elements would produce a network which would realize the digital filter.

It is convenient and useful to analyze the digital filter characteristics by examining the Z-transform of its response. Taking the one-sided Z-transform of Equation (1.3), we obtain

$$Z[Y(nT)] = Z[\sum_{i=0}^{N} a_i X(nT-iT)] - Z[\sum_{i=1}^{N} b_i Y(nT-iT)]$$

or

where

$$X(Z) = Z[Y(nT)]$$

$$X(Z) = Z[X(nT)]$$

Let us define N(z), D(z), D'(z), H(z) as follows:

$$N(z) = \sum_{i=0}^{N} a_i z^{-i}$$

(1.5)

$$D'(z) = \sum_{i=1}^{N} b_{i} z^{-i}$$

(1.6)

$$D(z) = 1 + D'(z)$$

(1.7)

$$H(z) = \frac{N(z)}{D(z)}$$

(1.8)

With these definitions, Eq. (1.4) reduces to

$$Y(z) = H(z) X(z)$$

where

H(z) is the transfer function of the filter.

There are many methods for realizing a digital filter. The basic and common principle to all of them, to break down the filter transfer function, H(Z), into blocks and to rearrange them into different configurations. Four configurations for realizing digital filters are described here [1].

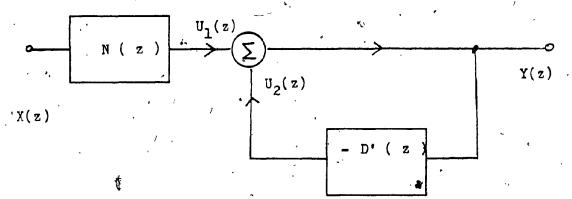

## 1.3.1 Direct Realization

With H(Z) defined as in Eq. (1.8), we can write Y(Z) as

$$Y(z) = U_1(z) + U_2(z)$$

(1.9)

7

where

$$U_1(Z) = N(\dot{Z}) \times (Z)$$

(1.10)

$$U_2(Z) = -D'(Z) Y(Z)$$

(1.11)

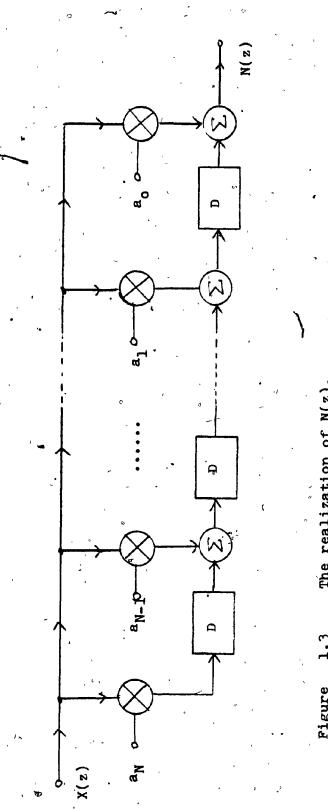

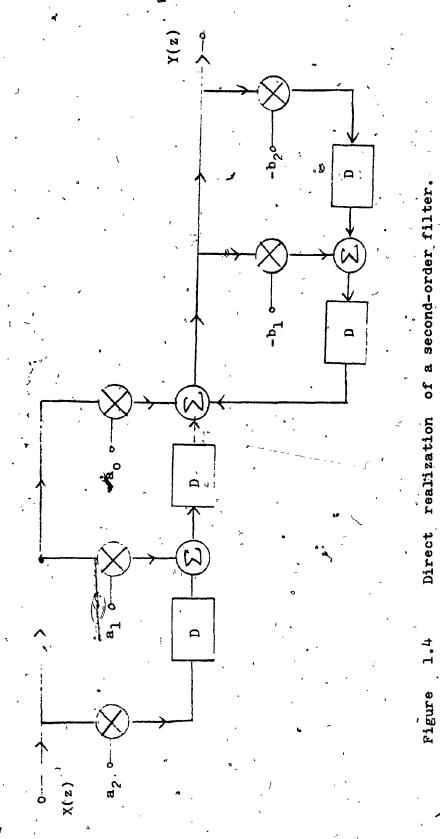

The realization can be obtained by realizing N(Z) and -D(Z) separately, and then connecting them, as shown in Fig. 1.2. The realization of polynomial N(Z) is easy and can be obtained in several ways. One possibility is depicted in Fig. 1.3. The same approach can be used to realize -D(Z). The direct realization of a second-order filter, N=2, is shown in Fig. 1.4.

## 1.3.2 Direct Canonic Realization

If Eq. (1.4) is rewritten as

$$Y(Z) = N(Z) Y'(Z)$$

(1.12)

where

$$Y'(Z) = X(Z) - D'(Z) Y'(Z)$$

(1.13)

we can deduce a direct realization which has the structure shown in Fig. 1.5. Notice that the number of unit delays is N, which is the order of the filter. Because of this property the realization is said to be canonic with respect

Direct realization of H(z)...

The realization of N(z) Figure

of a second-order filter. realization Direct

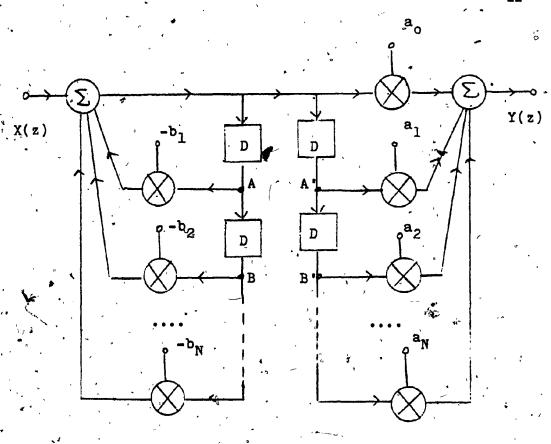

Figure 1.5 The Canonic realization of H(z).

Notice that points A & A' are the same point indeed. They can be combined together to eliminate the excess usage of delay units.

The same thing applies to points B & B',..etc.

to the number of unit delays.

## 1.3.3 Cascade Realization

The transfer function H(Z) defined in Equation (1.8) can be split into a product of second-order sections, i.e., we can rewrite Equation (1.8) as

$$/H(z) = \prod_{i=1}^{M} H_i(z)$$

(1.14)

where

$$H_{i}(Z) = \frac{a_{0i} + a_{1i}Z^{-1} + a_{2i}Z^{-2}}{1 + b_{1i}Z^{-1} + b_{2i}Z^{-2}}$$

(1.15)

Each  $H_1(Z)$  can be realized by using the  $2\frac{nd}{l}$  - Order canonic structure of Figure 1.6. The cascade realization can be obtained by cascading the realizations of  $H_1(Z)$  as in Figure 1.7.

## 1.3.4 Parallel Realization

In this approach, Equation (1.8) is rewritten as

$$H(Z) = \sum_{i=1}^{M} H_i(Z)$$

(1.16)

where .

$$H_{i}(z) = \frac{a_{0i} + a_{1i}z^{-1}}{1 + b_{1i}z^{-1} + b_{2i}z^{-2}}$$

(1.17)

Each H<sub>1</sub>(Z) is realized as a separate block, as in the cascade realization. The blocks obtained are then connected

Figure 1.6 A canonic second-order section.

Figure 1.7 A cascade realization of H(z).

in parallel as in Figure 1.8.

## 1.4 DIGITAL FILTER IMPLEMENTATION

Certain arithmetic operations are required very often in digital signal processing. This includes bit operations which are the elementary operations dealt with in implementation.

Recalling the characteristic equations of the non-recursive digital filter (Equation (1.2)), and that of the recursive one (Equation (1.3)), the filter operation involved is a "multiply-and-add" one. Sometimes, the initial input and final output of the filter are continuous time analog signals. Hence, to be able to use a digital filter in such a case, another process is required, namely, sampling to obtain discrete data, and smoothing to recover the continuous output.

The "multiplication-and-addition" process is the thing that identifies the different methods of implementation. There are many types of implementations because of the different ways one can multiply and add binary numbers. One possibility is to use a multiplier and an accumulator. One other way is to precompute all possible products of the coefficients of the filter and all possible inputs, and store them in a table, then use the input to look into this table and find the partial products and accumulate them.

Figure 1.8 Parallel realization of H(z).

Many other ways are suggested, and described in Chapter II.

However, these methods require one or more of the following digital operations:

- (a) Addition or accumulation: This is the process

of adding a computed value to a register. This

is done by an accumulator/register, using full

adders and combinational circuitry.

- (b) Multiplication by 2<sup>n</sup>: This is an easy operation realized by a shift register. To multiply a register value by 2<sup>n</sup>, we simply shift the n bits toward the most significant bit in the register. Similarly, to divide by 2<sup>n</sup> the bits are shifted towards the least significant bit in the register.

- (c) Multiplication of two binary numbers: There are many algorithms to multiply two binary numbers.

The most common one is the serial multiplication.

Let X<sub>1</sub>X<sub>2</sub> ... X<sub>N</sub> and Y<sub>1</sub>Y<sub>2</sub> ... Y<sub>N</sub> be two N-bit binary numbers, (i.e., X<sub>i</sub>, Y<sub>i</sub> ε [1,0] ), then

Z<sub>1</sub>Z<sub>2</sub> ... Z<sub>N</sub> can be obtained as follows [1]:

- (i) Initialize an accumulator (a shift register of  $2^n$  bits.)

- (ii) Form A<sub>ij</sub> by gating (AND) Y<sub>i</sub> and X<sub>i</sub> for j=1,2,..., N, and accumulate the result in the

## accumulator/shift register.

- (iii) Shift the contents of the shift register one bit towards the most significant bit (A<sub>il</sub>), i.e., multiplying by 2.

- (iv) Add the contents of the shift register to the accumulator.

- (v) Repeat steps (ii), (iii), (iv) for i=1,2, ..., N.

The final result in the accumulator is the product  $z_1 z_2 \dots z_{2N}$ . Another approach for the multiplication of two binary numbers is to use the serial magnitude multiplier. This multiplier receives the multiplicand bit by bit, serially, and the N bits of the multiplier in parallel and produces the product serially, bit by bit. It can be realized by delay flip-flops, gates and full adders.

Residue arithmetic encoding and decoding: Another pair of digital operations that is sometimes used in the implementation of digital filters, is residue arithmetic encoding and decoding. If, for example,  $X_1X_2 \ldots X_n$  is a binary number, the encoding process is to find M binary numbers, each represented by K bits as

$R = \{x_{11}x_{12} \dots x_{1K}, x_{21}x_{22} \dots x_{2K}, \dots; x_{2K}, \dots; x_{MK}\}$  (1.18)

where those M binary numbers are the original binary number  $x_1 x_2 \dots x_n^{n}$  modulo  $p_i$ , and

p<sub>i</sub>'s is a set of M relatively prime integers.

The decoding process is the reverse of this operation, i.e., given R as in Equation (1.18),  $X_1X_2 \ldots X_n$  is obtained.

(e) Counting: The "multiply-and-add" operation can be implemented by adding all the possible products of all the bits of the data and the coefficients.

These bit products are gated bits, hence by counting the number of 1's obtained at the gates, and shifting and accumulating, we achieve the filter operation. This requires binary counters which are implemented by using flip-flops and gates.

" Any implementation method uses two or more of the above operations. The choice of operations affects the efficiency, accuracy and speed of the implemented digital filter.

### CHAPTER II

## HARDWARE IMPLEMENTATION OF DIGITAL FILTERS

## 2.1 INTRODUCTION

Hardware implementations of digital filters have different characteristics. These characteristics are determined by the implementation approaches used. These approaches use mostly logic circuitry that are basically combinatorial and use shift registers, ROMs, RAMs, counters, encoders and decoders. The basic approaches discussed in this Chapter are widely different from each other, and hence their hardware characteristics differ with respect to speed, accuracy, reliability and other aspects. Six different approaches are discussed here, and the basic concepts are analyzed and compared.

## 2.2 CONVENTIONAL IMPLEMENTATIONS

One of the standard approaches towards the implementation of digital filters is to replace the multipliers and adders in the filter realization by arithmetic units that would multiply and add. A specific multiplier unit was proposed by Jackson, Kaiser and McDonald [2] as early as 1968. This multiplier implements the filter using serial arithmetic, and performs addition and subtraction, as well. The filter can be constructed from a small set of relatively

adders. This configuration is highly modular in form, and is well suited to large-scale integration. In fact, such a filter can be easily multiplexed to process a number of distinct signals.

## 2.2.1 The Arithmetic Unit

There are three operations involved in the filter operation: delay, addition and multiplication. Each one of these operations can be implemented by a simple digital circuit. A delay is achieved by a delay flip-flop, and the addition is done by using an accumulator of a set of full adders. The multiplication, on the other hand, is not easy to implement by a simple digital circuit. However, if the multiplication is examined on the bit level, it turns out to be a simple process of gating. This is because the product of two bits is the same as their gated value.

Consider the multiplication of two B-bit words,  $\boldsymbol{x}$  and a, such that

$$x = \sum_{i=0}^{B} x_{i}(2^{i}) = X_{B}X_{B-1} \dots X_{1}X_{0}$$

$$a = \sum_{i=0}^{B} a_{i}(2)^{i} = A_{B}A_{B-1} \dots A_{1}A_{0}$$

(2.1)

where

$$x_{i}$$

,  $A_{i} \in \{0,1\}$ .

If y is the product of x and a, then

$$y = xa = \sum_{i=0}^{B} x_i 2^{i} \sum_{i=0}^{B} A_i 2^{i}$$

$$= \sum_{i=0}^{B} 2^{i} (\sum_{j=0}^{B} X_{i} A_{j} 2^{j}) \qquad (2.2)$$

This can be rewritten as

$$y = (x_B x_{B-1}, ..., x_1 x_0) (A_B A_{B-1}, ..., A_1 A_0)$$

=  $s_{2B} s_{2B-1}, ..., s_1 s_0$  (2.3)

where  $S_i \in \{0,1\}$ . Bits  $S_i$ 's can be obtained from the following algorithm.

$$x_{B}x_{B-1} \dots x_{2}x_{1}x_{0}$$

$A_{B}A_{B-1} \dots A_{2}A_{1}A_{0}$

$q_{0,B} \dots q_{0}, q_{0,0}$

$q_{1,B} q_{1,B-1} \dots q_{1,1} q_{1,0}$

$q_{2,B} q_{2,B-1} \dots q_{2,0}$

$q_{3,B} q_{3,B-1} \dots q_{3,0}$

•••

•••

•••

$s_{2B}s_{2B-1}$  ......  $s_2 \cdot s_1 \cdot s_0$

Here, q<sub>ij</sub> is given by

$$q_{i,j} = A_i X_j \tag{2.4}$$

fór

The partial products are used to compute the final product bits

$$S_{i} = Z_{i} \mod 2 \qquad (2.5)$$

where

$$z_{i} = \sum_{j=0}^{i} q_{j,i-j} + c_{i-1}$$

and

$$C_i = Z_i - S_i$$

Notice that

$$c_0 = 0, s_0 = q_{0,0}$$

Notice that for every input,  $X_i$ , a process of gating takes place with every other bit of  $A_i$ . Adding these gated results, a partial sum is found. This partial sum would be controlled by a timing sequence that realizes the shifting process to account for the relative position of  $X_i$  and the  $i\frac{th}{t}$  partial sum. Therefore, a 2B bit multiplier can be implemented by using gates, full adders and delay Flip-Flop. Figure 2.1 shows a serial multiplier. It is composed of multiplier bit sections which are gated full-adders.  $X_j$  is fed in to be gated with  $A_i$ , then the result is accumulated, i.e., added to a partial sum which was calculated in the previous step. This partial sum is gated with a timing sequence,  $r_{i+1}$  so as to be sure that the proper bit gating is added to the old partial sum, starting at the proper bit in this sum.

Negative numbers can be represented in the two's complement form or the signed magnitude form. A sign bit can be fed to a sign detector or multiplier. In fact, an exclusive-OR gate is what is needed. It takes two signs as input and produces their product sign. Timing is required to prevent the sign bit from being taken as a magnitude bit, thus resulting in an erroneous output. After the sign multiplication is done, and the final output is computed, the sign adjustment is trivial. The timing will cause the sign bit to be taken to the sign detector (the exclusive-OR gate). The timing sequence ensures that there is synchronization of this shift-

Figure 2.1(b) A multiplier bit section.

ing process, and the addition of this product to the old partial sum. Finally, there are two things to do: change the product sign, as mentioned earlier, and secondly, to truncate or round the final product to a word of the required number of bits.

## 2.2.2 Implementation of Digital Filters

Equations (1.2) - (1.3) can be expressed as

$$y_n = \sum_{i=0}^{N} a_i X_{n-i}$$

(2.6)

and

$$\mathbf{Y}_{n} = \sum_{i=0}^{N} \mathbf{a}_{i} \mathbf{X}_{n-i} - \sum_{i=1}^{N} \mathbf{b}_{i} \mathbf{Y}_{n-i}, \qquad (2.7)$$

whore

for non-recursive filters.

The z-transform gives

$$Y(z) = \sum_{i=0}^{N} a_i z^{-i} X(z)$$

(2.8)

and proper scaling, Y(z) can be expressed as.

$$Y(z) = K_0 (1+a_1^{'}z^{-1}+a_2^{'}z^{-2} + ... + a_n^{'}z^{-N}) X(z)$$

that is

$$Y'(z) = X(z) (1 + \sum_{i=1}^{N} a_i^i z^{-i})$$

(2.9)

Alternatively, by factorizing the polynomial  $(1+\sum_{i=1}^{N}a_{i}^{i}z^{-i})$  we obtain

$$Y'(z) = \sum_{i=1}^{N_0} (1+\alpha_{1i} z^{-1}+\alpha_{2i} z^{-2}) X(z) (2.10)$$

where

$$N_{o} = \begin{cases} N/2 & \text{N:even} \\ \\ (N+1)/2 & \text{N:odd} \end{cases}$$

Each second-order polynomial in Equation (2.10) can be realized by a second-order filter section. By proper scaling again the input data can be scaled so as to satisfy the following condition:

$$-1 < x_n < 1$$

(2.11)

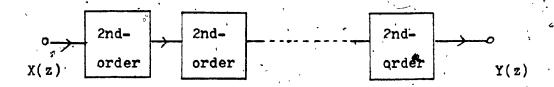

The complete filter can be realized by using  $N_o$  second-order sections in cascade.

Likewise, for the recursive filter, Equation (2.7) gives

$$Y(z) = \frac{\sum_{i=0}^{N} a_{i}^{i} z^{-i}}{\sum_{i=1}^{N} b_{i}^{i} z^{-i}} X(z)$$

(2.12)

This equation can be written as

$$Y'(z) = \prod_{i=1}^{N_0} \frac{(1 + \alpha_{1i}z^{-1} + \alpha_{2i}z^{-2})}{(1 + \beta_{1i}z^{-1} + \beta_{2i}z^{-2})} X(z) \quad (2.13)$$

and hence, a recursive filter can be realized in cascaded form of second-order sections. Equation (1.12) can also be rewritten as

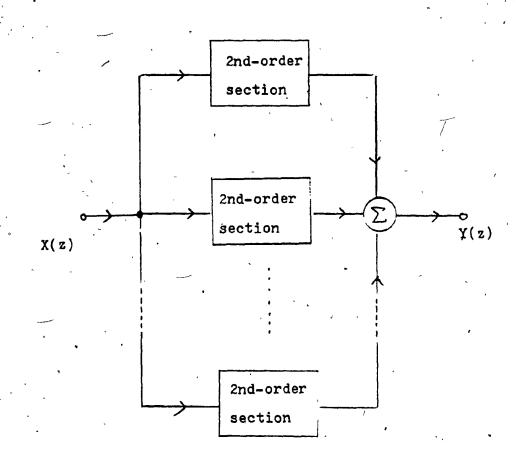

$$Y'(z) = G_0 + \sum_{i=1}^{N_0} \frac{\gamma_{0i} + \gamma_{1i} z^{-1}}{(1 + \beta_{1i} z^{-1} + \beta_{2i} z^{-2})} \qquad (2.14)$$

This equation results in a parallel realization of second-order sections.

The implementation of the filter therefore can be accomplished by cascade or parallel connection of second-order simple filters characterized by

$$Y_{i}(z) = \frac{(1 + \alpha_{1i}z^{-1} + \alpha_{2i}z^{-2})}{(1 + \beta_{1i}z^{-1} + \beta_{2i}z^{-2})} X(z)^{2}$$

(2.15)

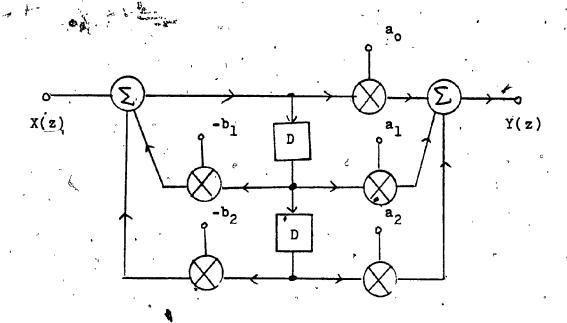

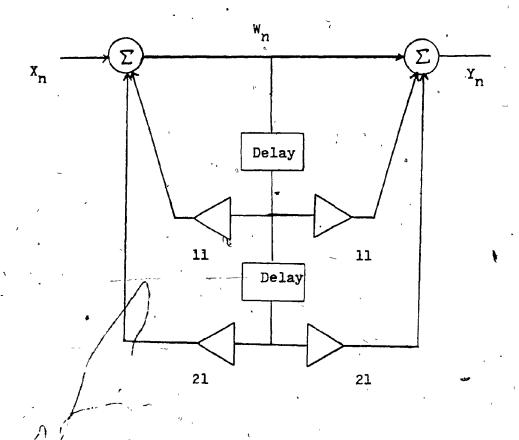

To implement a simple section, we require four multipliers, two delay flip flops, three intermediate accumulators, and another accumulator to hold the final output. The implementation of Equation (2.15) is depicted in Fig. 2.2. The cascade implementation of Equation (2.13) is slower than the parallel one of Equation (2.14). These implementations are shown in Figures 2.3 and 2.4, respectively.

The multiplier, itself, causes a delay of B bits in going through to compute the product serially. This delay has to be deducted from the unit delay that is provided by the delay flip-flops. Also, on addition, the operation of checking the sign bit, a delay of B bits occurs which is the time needed to pass the absolute value of the input data and the arrival of the input sign bit. This has to be considered, too, in determining the delay time of the input data.

# 2.2.3 Multiplexing

If the input rate bit is far below the speed capability of the digital circuit, the digital filter can be multiplexed to utilize the circuit more efficiently. The filter can be multiplexed to operate on several input signals simultaneously, or to affect a number of different filters for a single input signal.

The basic conventiumal second-order section. Figure

Figure 2.3 Cascade implementation using 2nd-order sections.

Pigure 2.4 Parallel implementation using 2nd-order sections.

If there are M input signals, a multiplexer would cause the M input signals to be interleaved and fed serially into the arithmetic unit. The use of multiplexing is illustrated in Figure 2.5. The bit rate in this scheme is increased by a factor of M. This means that the filter is operating M times faster.

The other possibility, is to use the same unit to compute, or participate in computing the outputs of several filters for given inputs. This implies that the filter section has different coefficients to use for every distinct input signal. These coefficients can be stored in ROMs. It is also possible to multiplex one arithmetic unit, so as to implement a higher order filter. This can be achieved by routing the output back to the input of the unit, and at the same time, changing the coefficients in the unit by reading a new set from the ROMs. Figure (2.6) illustrates this multiplexing scheme.

## 2.2.4 Multiplexed Hardware Structures

A more elaborate hardware structure for recursive digital filters was suggested by Gabel [3]. High speed operation and low hardware cost are achieved in this structure. Its operation is based upon a multiplier and a set of ROMs that store the coefficients. However, the control and the timing circuitry are different from that of the implementation discussed, so far.

Type I multiplexing in conventional implementation. 2.5 Figure

Type II multiplexing in conventional implementation. Figure

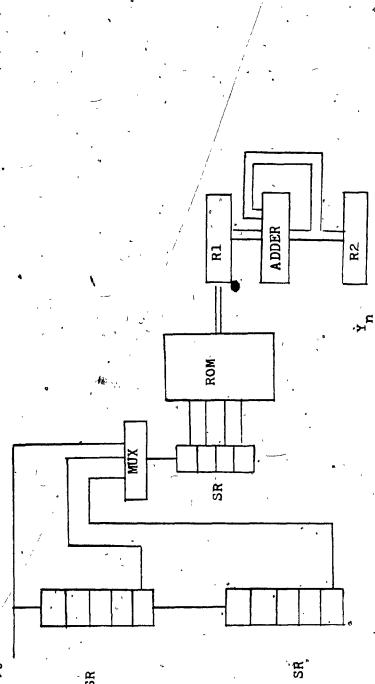

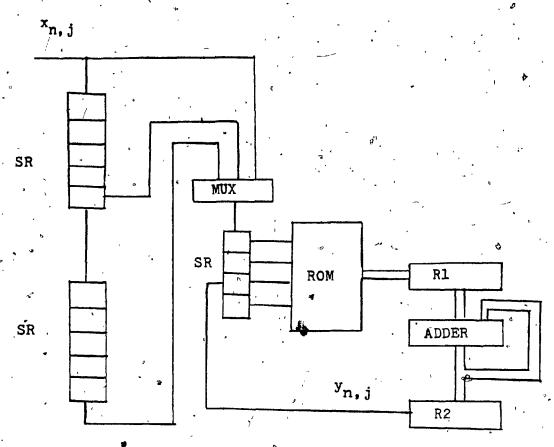

Cascade or parallel implementation is possible. cascade structure is shown in Figures (2.7) and (2.8). The input x(t) is digitized and fed to the multiplexer MUX1, together with the previous values of the input,  $X_{n-1}$ , where  $i=1,2,\ldots,N.$   $X_n$  will be passed to the adder which accumulates in the AC register. This partial output is fed back to a hold register for the next Nyquist interval, then shifted to the shift register REG1 and then to REG2. Both of these registers are used to generate the old or delayed values of the partial outputs. Meanwhile, the counter would control the ROMs to provide the proper coefficients which are fed to the multiplier. The product is transmitted to the adder through a regulating multiplexer and the new partial output is accumulated, again, in the AC register. Feeding the output back to MUX1 the cycle can be repeated over and over. The counter is all the control circuitry needed. It controls the data flow. Each count triggers a certain event in the system to happen. For example, an 8th - order filter is to be implemented. The control and the timing of the circuit must be of the form described in Table 2.1.