National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

# NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R S C  $\,$  1970, c  $\,$  C-30, and subsequent amendments

# **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous à lait parvenir une photocopie de qualité intérieure

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c C-30, et ses amendements subséquents

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-56078-9

# HIGH PERFORMANCE MEDIUM POWER UNINTERRUPTIBLE POWER SUPPLY

Mike Boost

A Thesis

in

The Department

of

Electrical & Computer

Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy at Concordia University

Montréal, Québec, Canada

January 1990

Mike Boost, 1990

# **ABSTRACT**

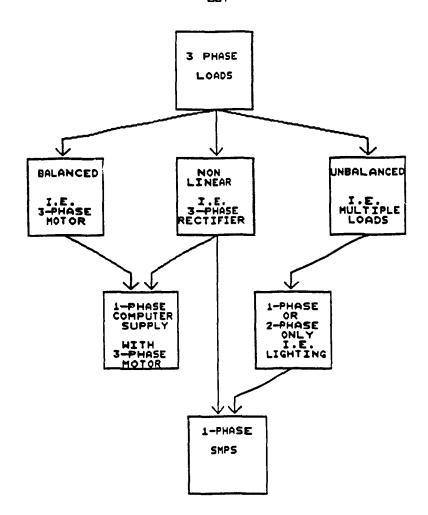

The concept of an ideal uninterruptible power supply (UPS) has evolved within the last ten years. In the past, solid state UPS carried performance specifications slightly better than those for an equivalent motor generator set. Todays medium power UPS is expected to power a wider variety of critical loads rendering it virtually as sophisticated as the equipment it powers. Traditional UPS balanced, linear loads such as motors and transformers are being displaced by unbalanced and nonlinear loads such as computers. Furthermore, UPS are now expected to operate within the human working environment in densely populated areas where the minimization of space and weight is increasingly important. Unfortunately the widening UPS operating environment and load spectrum often handicaps the current generation of UPS. In view of this, this thesis is directed towards the theoretical design and experimental verification of a UPS power train more compatible to modern loads and environments with streamlined space and weight requirements.

In order to achieve the high performance UPS a new topology is proposed that includes a fully controlled rectification stage, high frequency link isolation stage and a low output impedance inverter stage

Advanced pulse width modulation (PWM) techniques are critically evaluated allowing application of the most suitable technique for both the controlled rectification stage and the inverter stage. The results yield filter components of reduced size and weight.

The proposed high frequency link stage is used to provide isolation and

regulate the inverter input voltage. Evaluation of several feasible topologies yields a suitable power conversion stage that allows a dramatic reduction of transformer size and weight.

私以及於我們不可以學學的問題以及

The low output impedance inverter stage contains a strategically selected output filter and a novel PWM technique to allow clean power delivery to most single and three phase nonlinear loads as well as unbalanced loads.

The thesis includes the evaluation of the switch and drive as well as the controller design for each of the three stages. The Evaluation of several suitable semiconductors yields a single common switching device and drive for the UPS. Further, three different controllers are used respectively for each stage. In particular a new, completely digital controller without a microprocessor is developed for the rectification stage allowing for increased ruggedness.

Two sophisticated software programs are developed to aid the analysis. A worst case ratings program to quickly solve converter ratings based on load and applied PWM technique and a simulation program to quickly analyze power electronic circuits which employ PWM are presented.

Finally in order to establish the feasibility of the new UPS topology, and to validate the analytical techniques predicted, key results are simulated and experimentally verified on a 10kVA laboratory prototype. Details of practical importance not typically found in the literature, such as lead inductance limitations, electromagnetic interference (EMI), snubbers, layout requirements, switching deadtimes/overlaps and transformer saturation are included.

# TABLE OF CONTENTS

| ABSTRACT                                          | • | • |   | iii   |

|---------------------------------------------------|---|---|---|-------|

| TABLE OF CONTENTS                                 |   |   |   | v     |

| LIST OF FIGURES                                   |   |   | • | x     |

| LIST OF TABLES                                    | • | • | • | xvi   |

| LIST OF ACRONYMS                                  | • | • |   | xvii  |

| LIST OF SYMBOLS                                   | • |   |   | xviii |

|                                                   |   |   |   |       |

| 1.0 INTRODUCTION                                  | • | • |   | 1     |

| 1.1 General                                       |   |   |   | 1     |

| 1.2 Evolving UPS Requirements                     |   | • |   | 4     |

| 1 2.1 Physical UPS Requirements                   |   |   |   | 4     |

| 1 2 2 Electrical UPS Requirements                 |   |   |   | 5     |

| 1.3 Scope of this Thesis                          |   | • |   | 6     |

|                                                   |   |   |   |       |

| 2 0 UPS DESIGN CRITERIA                           |   |   |   | 9     |

| 2 1 Introduction .                                |   |   |   | 9     |

| 2.2 Modern Medium Power UPS Specifications        |   |   |   | 11    |

| 2.2.1 Input Specifications                        |   | • |   | 11    |

| 2.2.2 Output Specifications .                     |   |   |   | 12    |

| 2.2.3 Physical Specifications                     |   |   |   | 13    |

| 2.3 UPS Topology Evaluation                       |   |   |   | 16    |

| 2.3.1 Proposed UPS Topology                       |   |   |   | 21    |

| 2.4 PWM For Improving Power Converter Performance |   |   |   | 24    |

| 2 4 1 Carrier PWM Techniques                      |   |   |   | 28    |

| 2.4.1.1 The Original Sine PWM Technique          |     | • | • | 29        |

|--------------------------------------------------|-----|---|---|-----------|

| 2.4.1.2 The Modified Sine PWM Technique          |     |   |   | 31        |

| 2.4.1.3 The Third Harmonic Injection PWM Techniq | ļue | • | • | 33        |

| 2.4.1.4 The Harmonic Injection PWM Technique     |     |   |   | 35        |

| 2.4.1.5 Waveform Quality Under Variable          |     |   |   |           |

| Modulation Index Conditions                      |     |   | • | <b>37</b> |

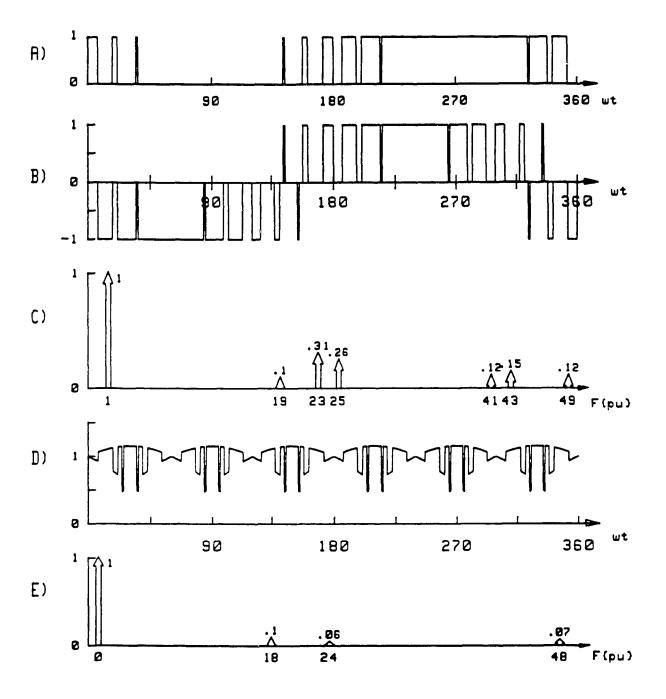

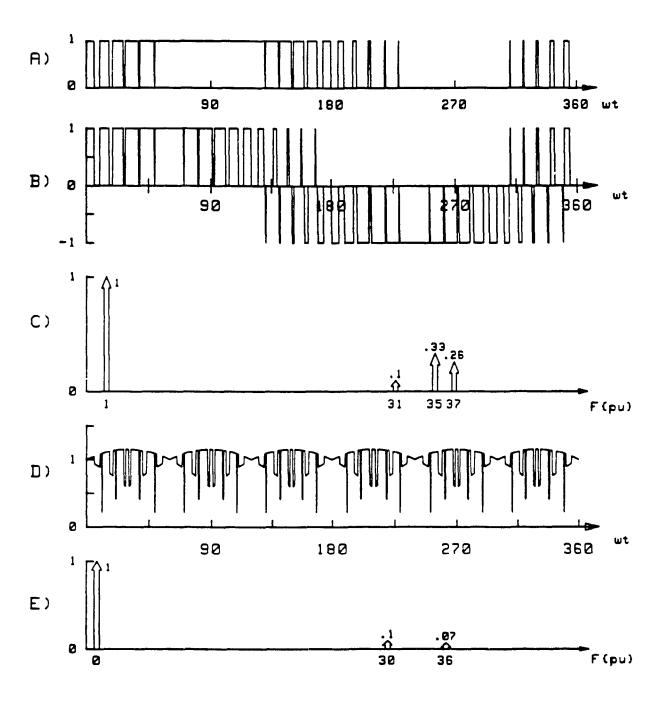

| 2.4.2 Programmed PWM Techniques                  |     |   |   | 43        |

| 2.4.2.1 Selective Harmonic Elimination (SHE)     |     |   | • | 45        |

| 2.4.2.1.1 SHE with Regulated Converter Input     |     | • |   | 46        |

| 2.4.2.1.2 SHE with Unregulated Converter Input   | t   |   |   | 49        |

| 2.4.3 PWM Classification and Selection           |     |   |   | 52        |

| 2.4.3.1 AC TERM and DC TERM Gains                |     |   |   | 52        |

| 2.4.3.2 Quality Factors                          |     |   |   | 53        |

| 2.4.3.3 UPS Controlled Rectifier PWM Selection   |     | • | • | 53        |

| 2.4.3.4 Voltage Source Inverter PWM Selection .  |     | • | • | 54        |

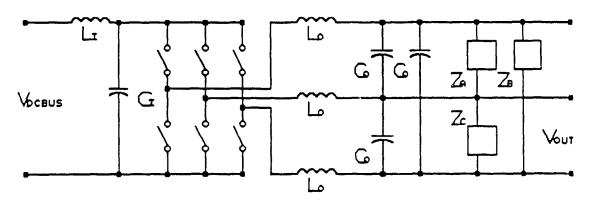

| 2.5 Software Development                         |     | • |   | 54        |

| 2.5.1 UPS Inverter Worst Case Ratings Program .  |     |   |   | 54        |

| 2.5.1.1 Program Methodology                      |     | • |   | 55        |

| 2.5.1.2 Derivation of Worst Case Per Unit        |     |   |   |           |

| Component Ratings                                |     |   |   | 56        |

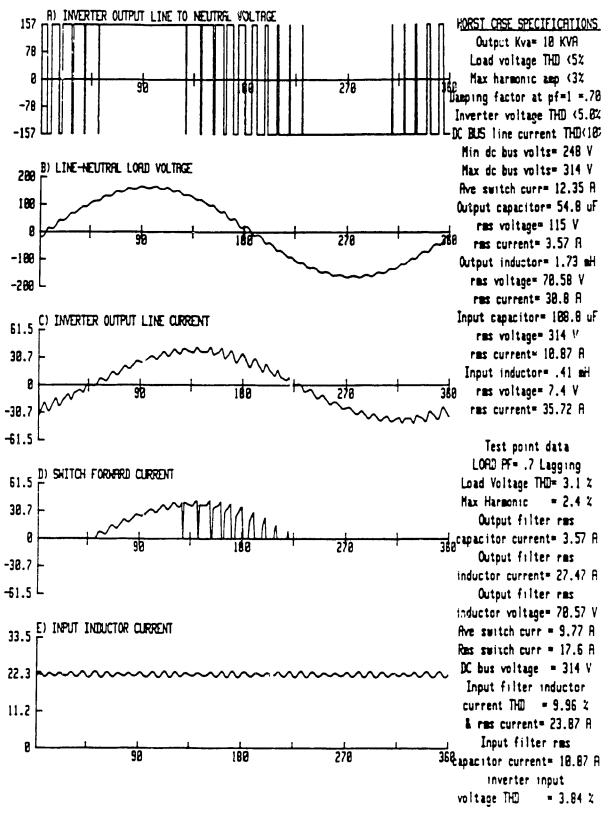

| 2.5.1.3 Actual Component Ratings                 |     |   |   | 60        |

| 2.5.1.4 Test Point Data and Waveforms            |     | • |   | 60        |

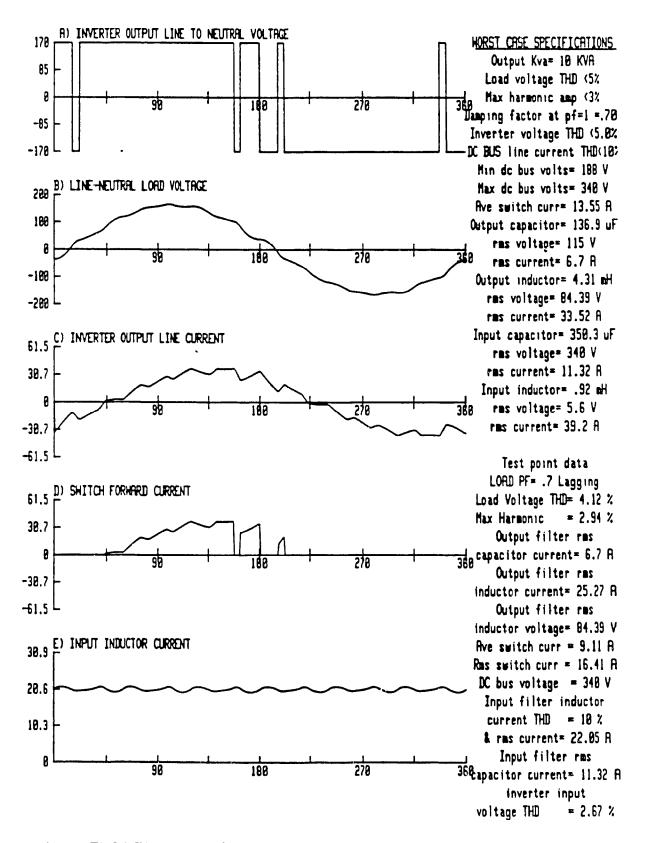

| 2.5.1.5 Example Operation                        |     | • | ė | 60        |

| 2.5.2 An Analysis/Simulation Program for         |     |   |   |           |

| Power Electronics Circuits                       |     | • |   | 63        |

| 2.5.2.1 Program Methodology                      |     | • |   | 64        |

| 2.6 Conclusion                                   |     | ٠ |   | 75        |

|                                                  |     |   |   |           |

| 3.0 O Design for 60 HZ UPS Applications  | •      | • | • | • | • | 77  |

|------------------------------------------|--------|---|---|---|---|-----|

| 3.1 Balanced Load Worst Case Inverter Ra | atings | • | • | • | • | 79  |

| 3.1.1 Output Filter Ratings              | •      | • | • | • | • | 84  |

| 3.1.2 Inverter Switch Ratings .          | •      | • | • |   |   | 93  |

| 31.3 Input Filter Ratings                | •      | • | • | • |   | 97  |

| 3.2 3-¢ Controlled Rectifier Ratings .   | •      | • | • |   | • | 110 |

| 3.2.1 Output Filter Ratings              |        | • | • |   |   | 115 |

| 3.2.2 Rectifier Switch Ratings .         | •      |   |   |   |   | 122 |

| 3.2.3 Input Filter Ratings               | •      |   |   |   |   | 123 |

| 3 3 High Frequency Link Evaluation .     | •      |   |   | • |   | 133 |

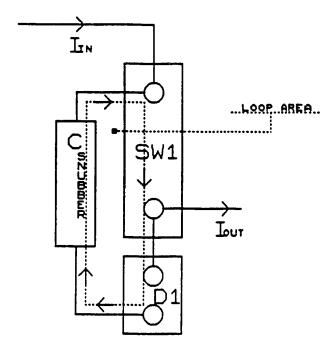

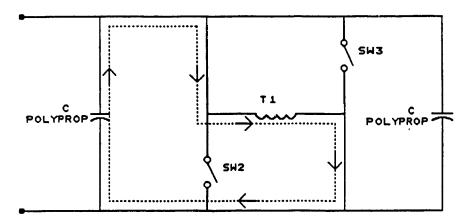

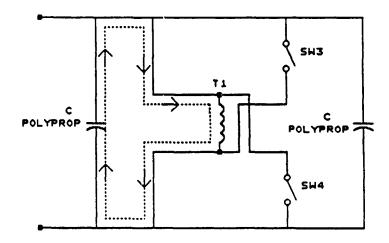

| 3 3 1 Single Switch Evaluation .         |        |   |   |   |   | 134 |

| 3.3.2 Half Bridge Evaluation             |        |   |   | • |   | 150 |

| 3 3 3 Full Bridge Evaluation             |        |   |   |   |   | 162 |

| 334 High Frequency Link Selection        |        |   |   |   |   | 171 |

| 3 4 Design Example                       |        |   |   |   |   | 173 |

| 3 4.1 Circuit Values                     |        | ٠ | • | • |   | 174 |

| 3.4 1 1 Inverter Stage                   |        |   |   |   |   | 175 |

| 3 4.1 2 Rectifier Stage                  | •      |   |   |   |   | 176 |

| 3 4 1 3 High Frequency Link Stage        |        |   |   |   |   | 177 |

| 3.4.2 Simulation Results                 |        |   |   |   |   | 178 |

| 3.4.2 1 Inverter Simulation              |        |   |   |   |   | 178 |

| 3 4.2.2 Rectifier Simulation .           |        |   |   |   |   | 185 |

| 3 4 2.3 HF Link Simulation               |        |   |   |   |   | 188 |

| 3.4.3 Switch and Drive Selection         |        |   |   |   |   | 189 |

| 3.4.4 Controller Circuits                |        |   |   |   |   | 190 |

| 2.4.4.1 Investor Controller              |        |   |   |   |   | 101 |

|     | 3.4.4.2 Rectifier Controller       | •        | •  |   |   | • | • | 192 |

|-----|------------------------------------|----------|----|---|---|---|---|-----|

|     | 3.4.4.3 High Frequency Link (      | Controll | er |   |   |   |   | 197 |

|     | 3.4.5 Practical Limitations .      | •        | ě  |   |   | • | ě | 199 |

|     | 3.4.5.1 Snubbers                   |          |    |   |   |   |   | 199 |

|     | 3.4.5.2 Layout Requirements        | •        |    |   |   |   | • | 204 |

|     | 3.4.5.3 Switching Deadtimes/       | Overlap  | 5  |   | • | • | ě | 206 |

|     | 3.4.5.4 Transformer Saturation     | on .     | •  |   |   | • | • | 207 |

|     | 3.4.6 Experimental results .       |          |    |   | • | • | ٠ | 208 |

|     | 3.4.6.1 Inverter Stage .           | •        | •  |   |   |   | • | 208 |

|     | 3.4.6.2 High Frequency Link S      | Stage    |    | • |   |   | • | 212 |

|     | 3.4.6.3 Rectifier Stage .          | •        |    |   |   |   |   | 217 |

|     | 3.5 Conclusion                     |          |    | • |   |   |   | 217 |

|     |                                    |          |    |   |   |   |   |     |

| 4.0 | SPECIAL LOAD CONSIDERATIONS.       |          |    |   |   |   |   | 221 |

|     | 4.1 Categorization of Loads .      |          |    |   |   |   |   | 222 |

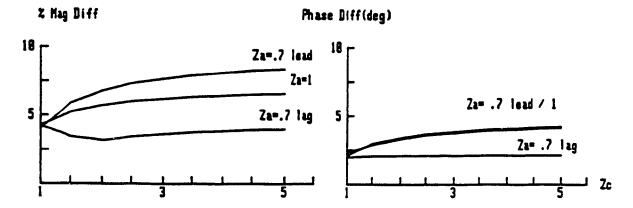

|     | 4.1.1 Unbalanced Load Application  | n.       |    |   |   |   |   | 226 |

|     | 4.1.2 Nonlinear Load Application   |          |    |   |   |   |   | 228 |

|     | 4.2 Existing Alternatives          |          |    | • |   |   |   | 230 |

|     | 4.2.1 Combining 1-φ Inverters      |          |    | • |   |   |   | 231 |

|     | 4.2.2 Harmonic Traps               |          |    |   |   |   | • | 232 |

|     | 4.2.3 Unbalanced Switching Func    | tion     |    |   |   | ٠ | • | 233 |

|     | 4.3 UPS System Modifications .     |          |    | • |   | • |   | 234 |

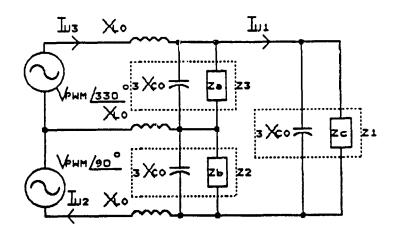

|     | 4.3.1 UPS Output Filter Derivation | on       |    |   |   |   |   | 234 |

|     | 4.3.2 Special PWM                  | •        |    |   |   | • |   | 236 |

|     | 4.4 Topology Performance           |          |    |   |   |   |   | 241 |

|     | 4.4.1 Predicted Topology Perform   | nance    |    |   |   |   |   | 241 |

|     | 4.4.1.1 Balanced Linear Load       | •        | •  |   |   | • |   | 241 |

|       | 4.4.1.2       | Unbalanc   | ed Lo    | oad le  | st            | •      | • | • | • | • | • | 244 |

|-------|---------------|------------|----------|---------|---------------|--------|---|---|---|---|---|-----|

|       | 4.4.1.3       | Nonlinear  | r Loa    | d App   | licati        | on     | • | • |   |   | • | 246 |

|       | 4.4.1.4       | 1-ø Nonli  | inear    | Load    | <b>A</b> ppli | cation | า | • |   | • | • | 247 |

|       | 4.4.2 Expe    | rimental   | Resu     | lts     | •             | •      | • | • | • | • | • | 248 |

| 4     | .5 Conclusion | n.         |          |         |               | •      | • | • | • | • |   | 256 |

|       |               |            |          |         |               |        |   |   |   |   |   |     |

| 5 0 0 | CONCLUSION    | SUMMARY    | <i>.</i> |         | •             |        | • |   |   |   | • | 257 |

| 5     | .1 Further W  | Vork .     |          |         |               |        |   |   | • |   | • | 262 |

|       |               |            |          |         |               |        |   |   |   |   |   |     |

| 6 O F | RFFERENCES    |            |          |         | •             |        |   |   |   |   | • | 263 |

|       |               |            |          |         |               |        |   |   |   |   |   |     |

| APPE  | ENDIX         |            |          |         |               |        |   |   |   |   |   |     |

|       | Al Worst C    | Case Inver | ter R    | atings  | s Prog        | gram   |   |   |   |   |   | 272 |

|       | A2 Power S    | Switch an  | d Dri    | ive F v | aluati        | ion    |   |   |   |   |   | 297 |

|       | A. Rectifie   | r Control  | ler S    | chema   | tic           |        |   |   |   |   |   | 307 |

# LIST OF FIGURES

|              |                                                   |   | page       |

|--------------|---------------------------------------------------|---|------------|

| Figure F2.1  | Typical SMPS equivalent circuit C=2.8µF/W 1/R=8.7 |   |            |

|              | μmhos/W                                           | • | 13         |

| Figure F2.2  | 4th generation UPS power train topology           |   | 16         |

| Figure F2.3  | Phase controlled rectifier/battery charger stage  | • | 17         |

| Figure F2.4  | 3-φ UPS inverter stage                            |   | 20         |

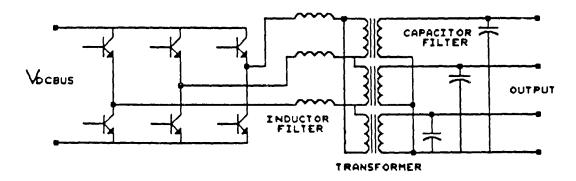

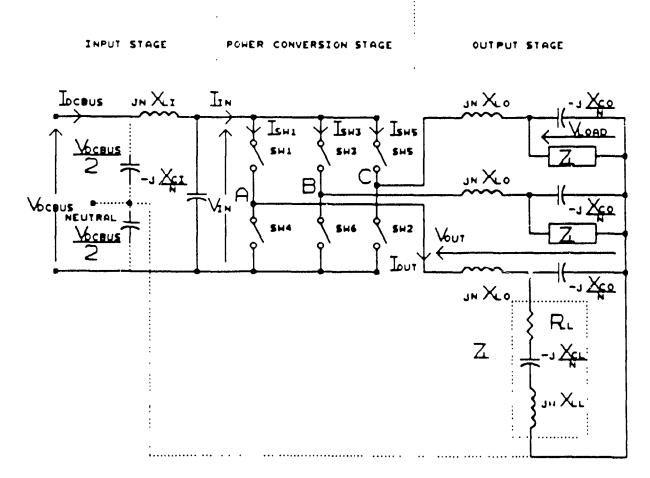

| Figure F2.5  | Proposed 60hz UPS topology                        |   | 22         |

| Figure F2.6  | Inverter voltage and current waveforms with six   |   |            |

|              | step and sinusoidal (SPWM) operation              |   | 26         |

| Figure F2.7  | Generalized bridge configuration                  | • | 28         |

| Figure F2.8  | Sinusoidal PWM (SPWM)                             |   | 30         |

| Figure F2.9  | Modified Sinusoidal PWM (MSPWM)                   |   | 32         |

| Figure F2.10 | Harmonic Injection PWM (HIPWM) (1st & 3rd) .      | • | 34         |

| Figure F2.11 | Harmonic Injection PWM (HIPWM) (1st & 3rd & 9th)  | • | 36         |

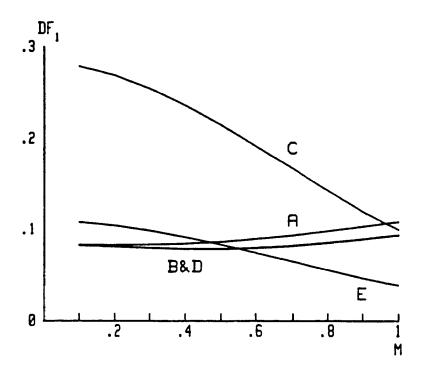

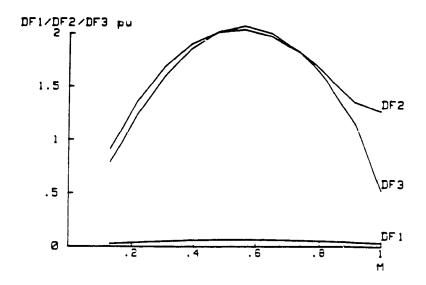

| Figure F2.12 | 2nd order filter distortion factor (AC TERM) .    | • | 38         |

| Figure F2.13 | 1st order filter distortion factor (AC TERM)      |   | 39         |

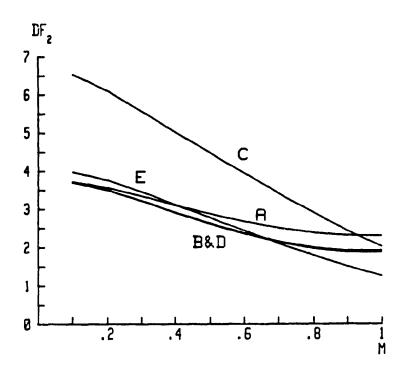

| Figure F2.14 | 1st order filter distortion factor (DC TERM) .    |   | 40         |

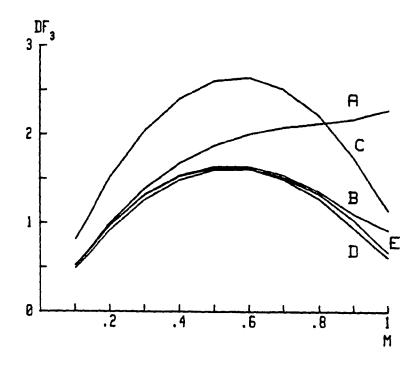

| Figure F2.15 | Inverter dc terminal rms ripple                   |   | 42         |

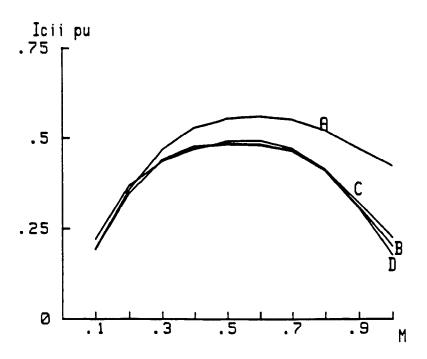

| Figure F2.16 | Rectifier input capacitor rms ripple current .    |   | 42         |

| Figure F2.17 | Programmed PWM sensitive to angle distortion .    |   | 44         |

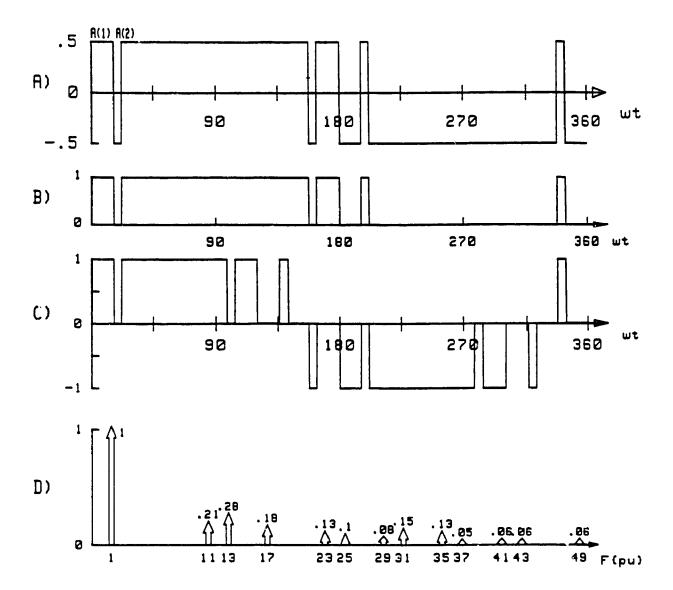

| Figure F2.18 | SHE PWM                                           |   | 48         |

| Figure F2.19 | SHE characteristics                               |   | <b>5</b> 0 |

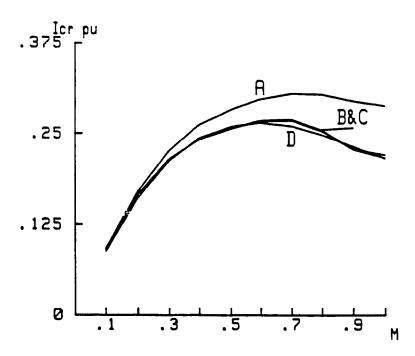

| Figure F2.20 | SHE distortion factor indices                     |   | 51         |

| Figure F2.21 | SHE input current quality factors                 |   | 51         |

| Figure F2.22 | Worst case ratings inverter stage generalized    |            |

|--------------|--------------------------------------------------|------------|

|              | structure                                        | 55         |

| Figure F2.23 | Worst case per unit ratings flowchart            | <b>5</b> 8 |

| Figure F2.24 | Worst case inverter ratings waveforms            |            |

|              | for SHE example                                  | 62         |

| Figure F2.25 | Typical screen display of entered circuit        | 65         |

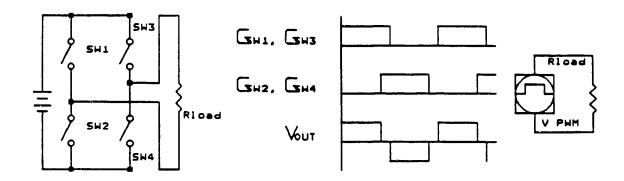

| Figure F2.26 | Modeling of a Single Phase PWM Inverter          | 66         |

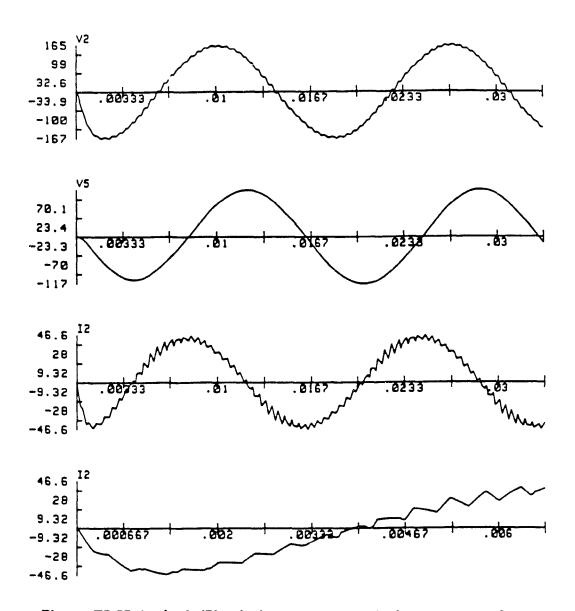

| Figure F2.27 | Analysis/Simulation program typical output       |            |

|              | waveforms                                        | 75         |

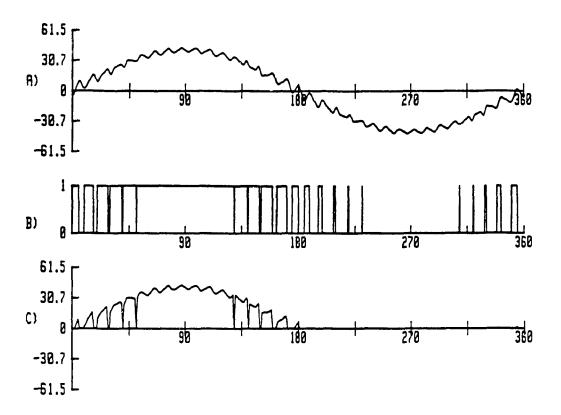

| Figure F3.1  | UPS inverter stage power train schematic         | 79         |

| Figure F3.2  | Inverter switch#1 (SWI) gating signal (GSWI)     | 80         |

| Figure F3.3  | Theoretical switch waveforms                     | 96         |

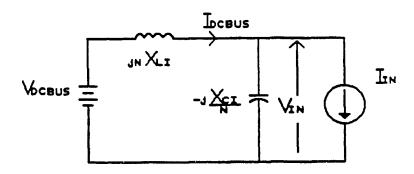

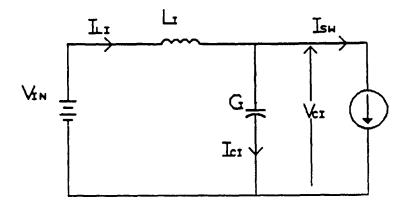

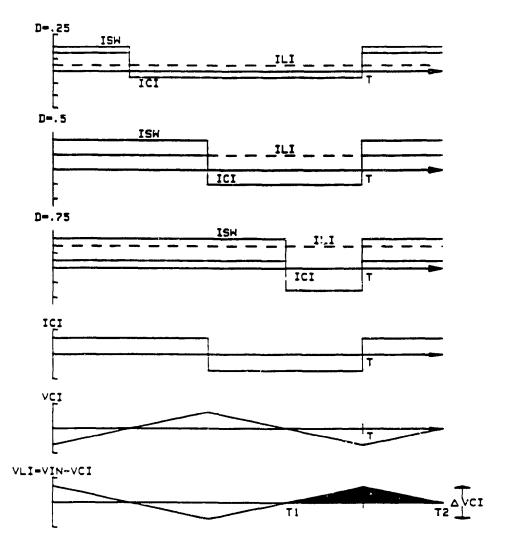

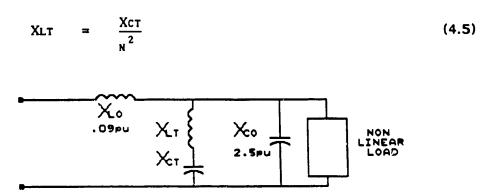

| Figure F3 4  | Input stage analysis model                       | 98         |

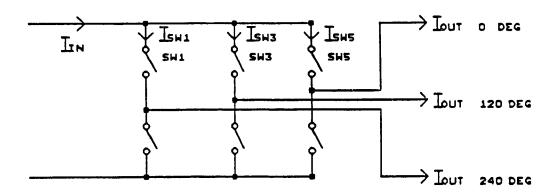

| Figure F3 5  | Summation of switch currents                     | 100        |

| Figure F3 6  | Phasor diagram of input current                  | 101        |

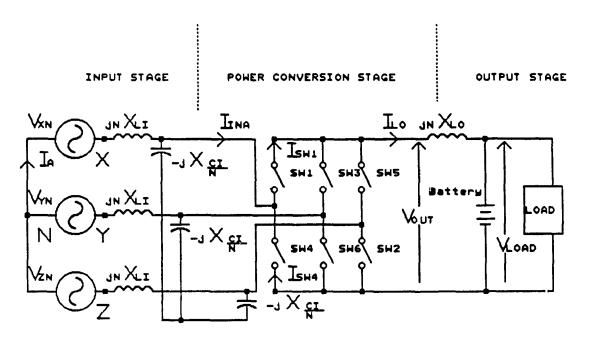

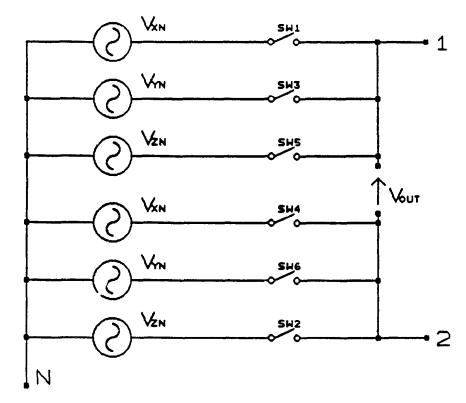

| Figure F3.7  | Controlled rectifier power train topology        | 111        |

| Figure F3 8  | Simplified model for transfer function           |            |

|              | realization                                      | 112        |

| Figure F3.9  | Controlled rectifier gating signal derivation .  | 113        |

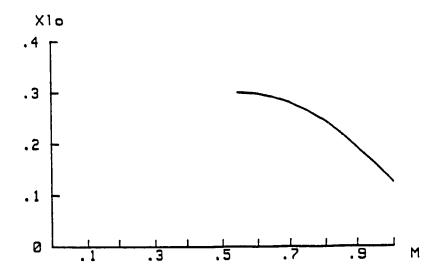

| Figure F3 10 | Controlled rectifier harmonic gains as a         |            |

|              | function of M                                    | 120        |

| Figure F3 11 | Output inductor impedance required vs modulation |            |

|              | index M                                          | 121        |

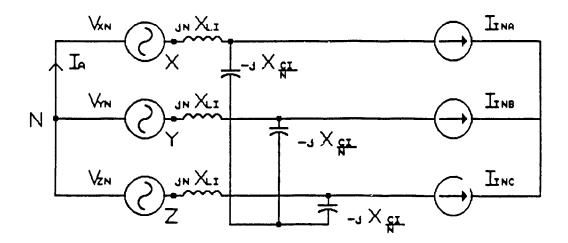

| Figure F3 12 | Simplifies input stage for controlled rectifier  | 124        |

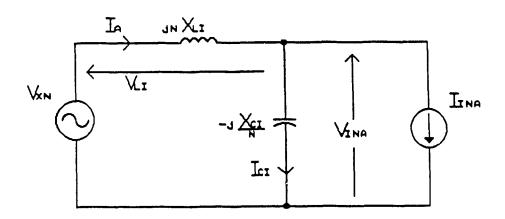

| Figure F3 13 | Single phase equivalent input circuit            | 125        |

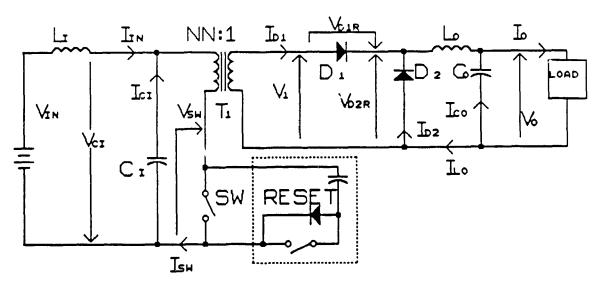

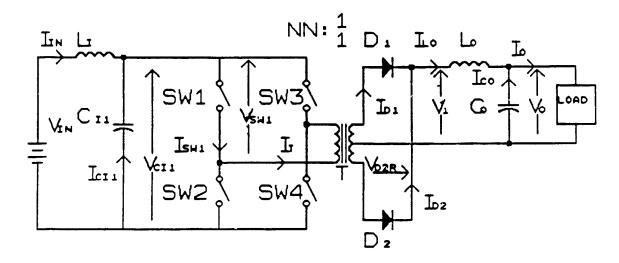

| Figure F3 14 | Single switch forward converter                  | 134        |

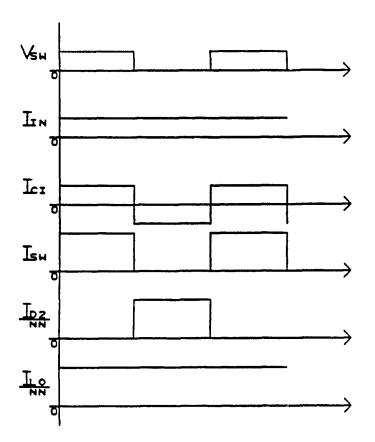

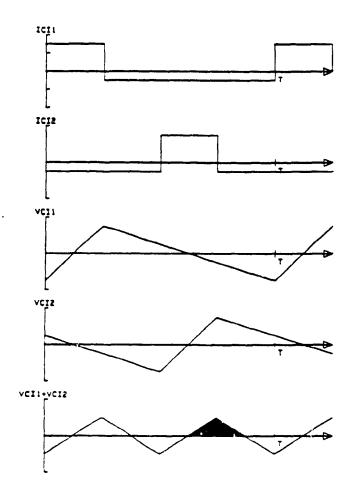

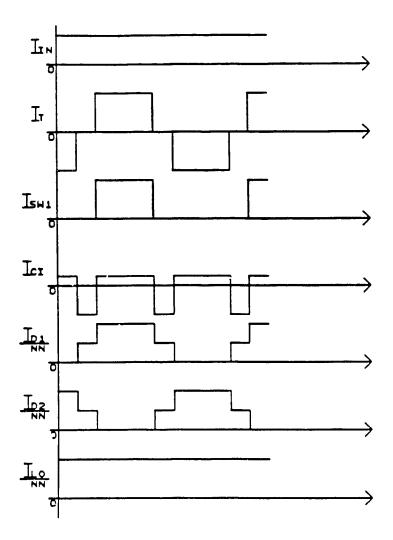

| Figure F3 15 | Forward converter typical waveforms              | 136        |

| Figure F3.16 | Forward converter typical output waveforms     | •  | • | 143 |

|--------------|------------------------------------------------|----|---|-----|

| Figure F3.17 | HF link equivalent input circuit               |    | • | 146 |

| Figure F3.18 | HF link equivalent input circuit waveforms     |    | • | 147 |

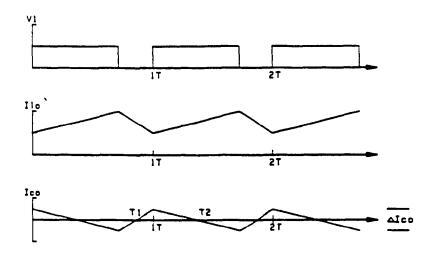

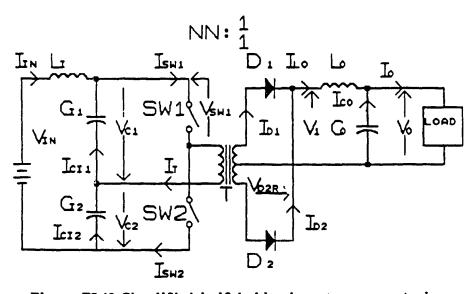

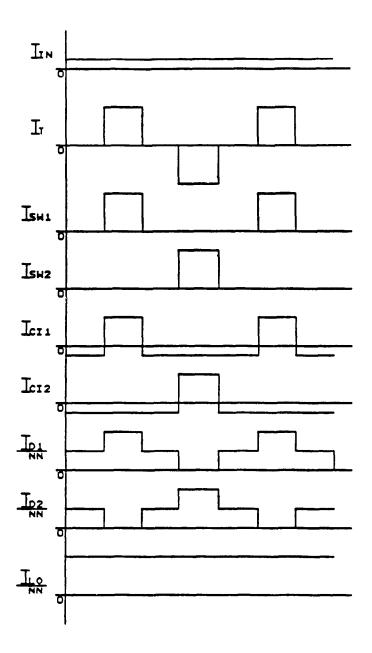

| Figure F3.19 | Simplified half bridge inverter power train    |    | • | 150 |

| Figure F3.20 | Waveforms for the half bridge inverter .       |    |   | 152 |

| Figure F3.21 | Half bridge inverter output inductor charging  |    | • | 157 |

| Figure F3.22 | Half bridge inverter input waveforms .         | •  | • | 160 |

| Figure F3.23 | Full bridge inverter power train topology      | •  | • | 162 |

| Figure F3.24 | Full bridge inverter topology waveforms .      |    | • | 163 |

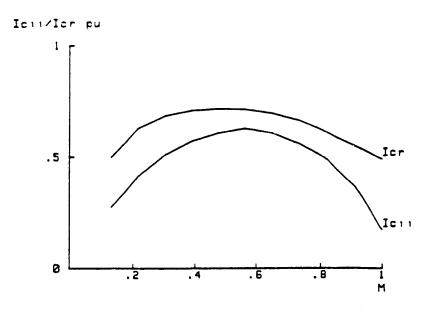

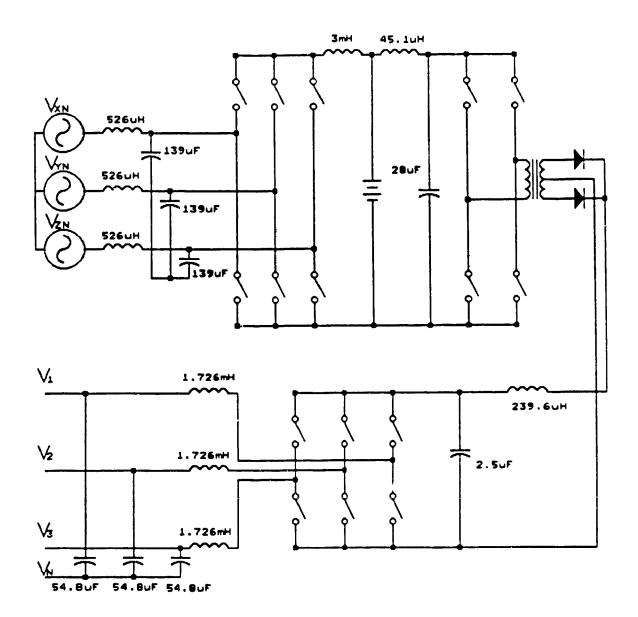

| Figure F3.25 | UPS power train with components                | •  |   | 175 |

| Figure F3.26 | Worst case inverter ratings program waveform   | ì  |   |     |

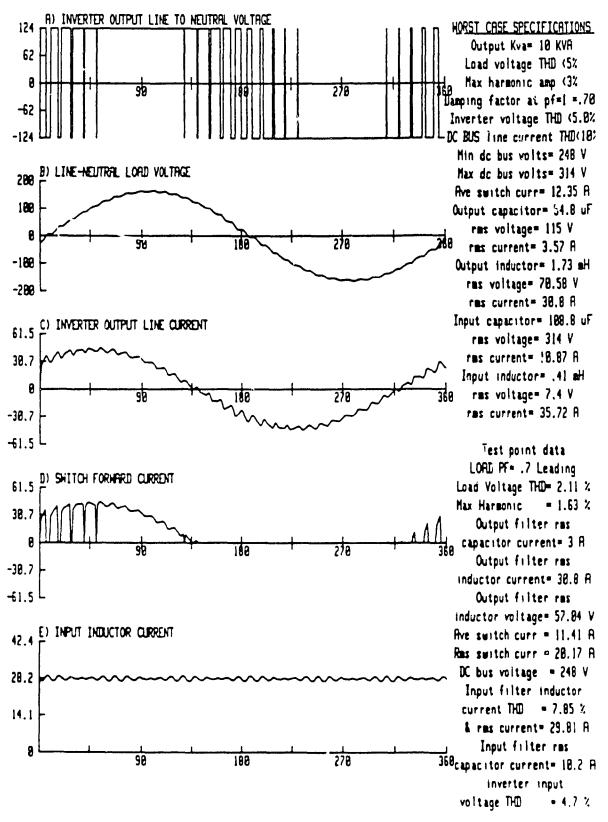

|              | results with lagging PF                        |    | • | 179 |

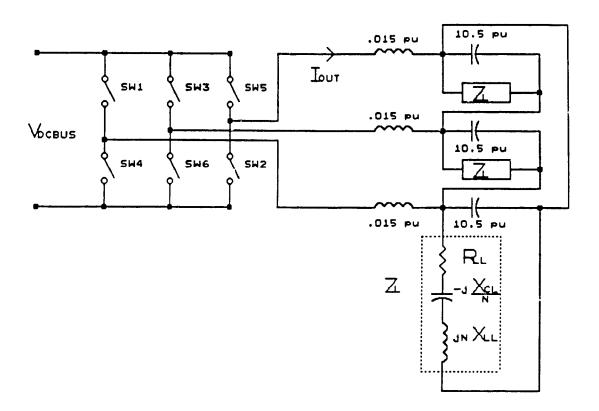

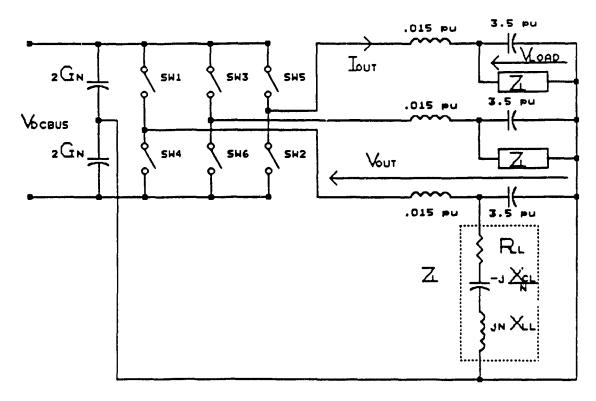

| Figure F3.27 | Simulated inverter circuit topology .          | •  |   | 180 |

| Figure F3.28 | Inverter lagging PF simulation results .       | •  | • | 181 |

| Figure F3.29 | Worst case inverter ratings program waveform   | ıs |   |     |

|              | results with leading PF                        | •  | • | 182 |

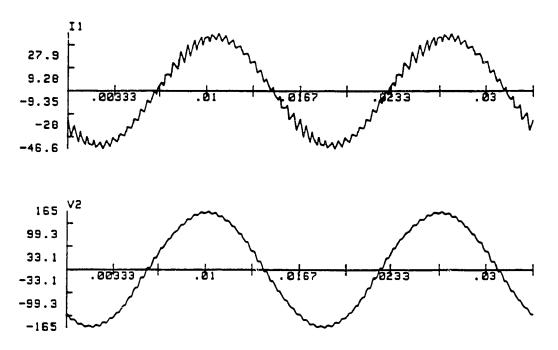

| Figure F3.30 | Inverter leading PF simulation results .       | •  | • | 183 |

| Figure F3.31 | Worst case inverter ratings program results    |    |   |     |

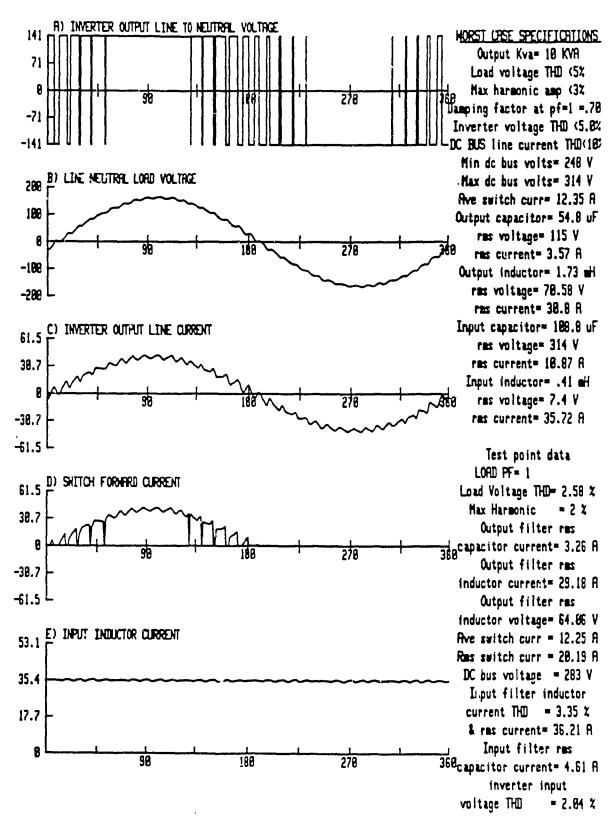

|              | with unity power factor                        | •  | • | 184 |

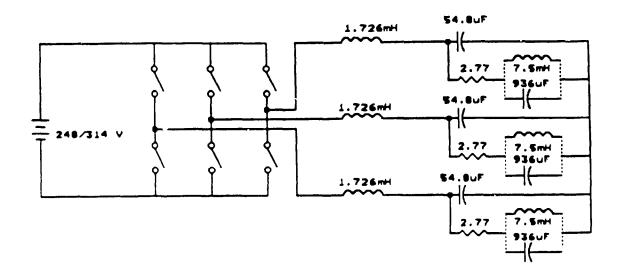

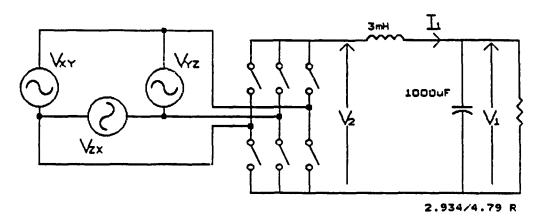

| Figure F3.32 | Rectifier simulation topology                  | •  | • | 185 |

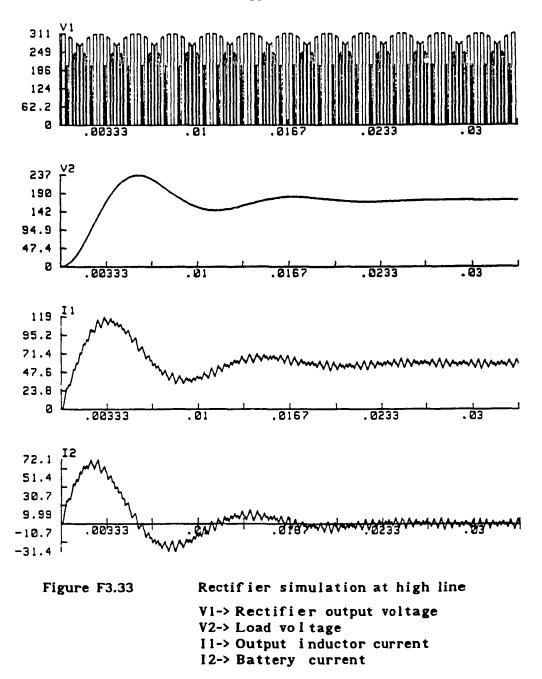

| Figure F3.33 | Rectifier simulation at high line              | •  | • | 186 |

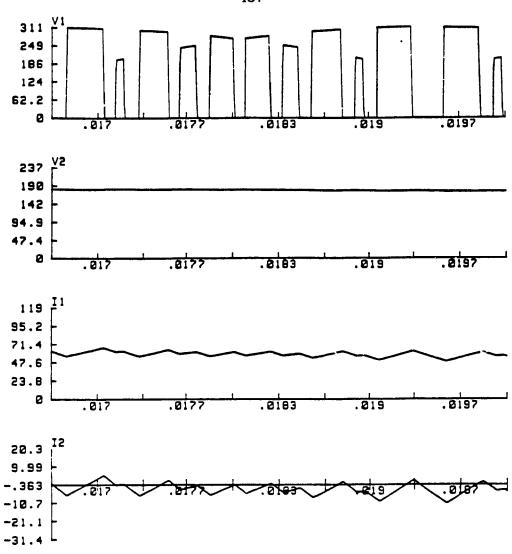

| Figure F3.34 | Rectifier simulation at high line              |    |   |     |

|              | (expanded time)                                | •  | • | 187 |

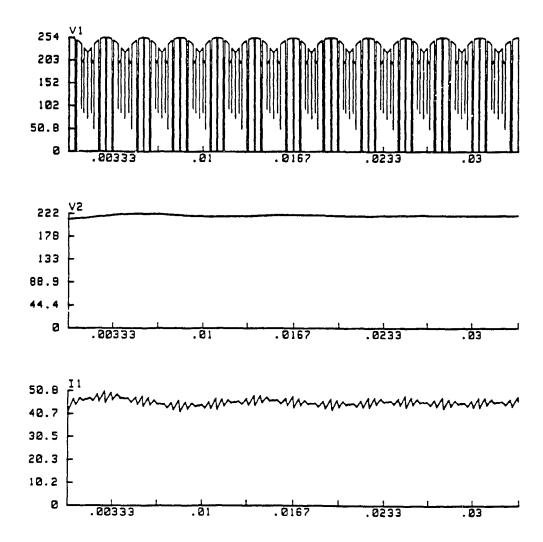

| Figure F3.35 | Rectifier simulation (expanded time at low lin | e) | • | 188 |

| Figure F3.36 | Inverter gating signal derivation              |    | • | 191 |

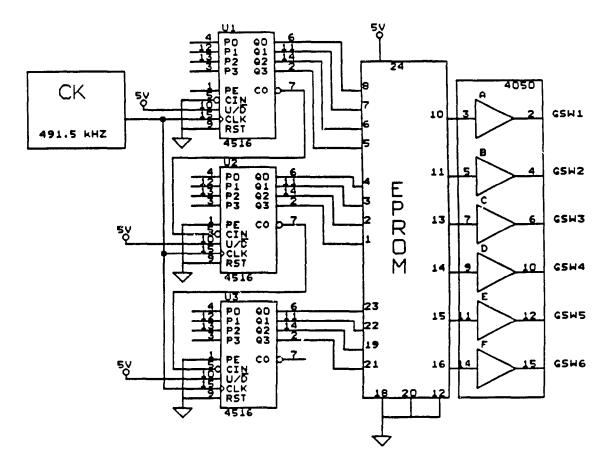

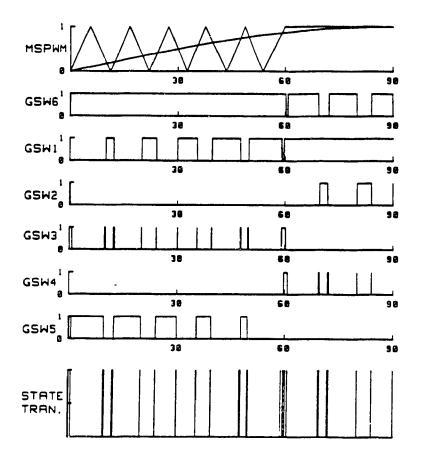

| Figure F3.37 | Inverter gating signa' hardware                | •  | • | 192 |

| Figure F3.38  | Expanded MSPWM gating signals for control             |     |

|---------------|-------------------------------------------------------|-----|

|               | derivation                                            | 193 |

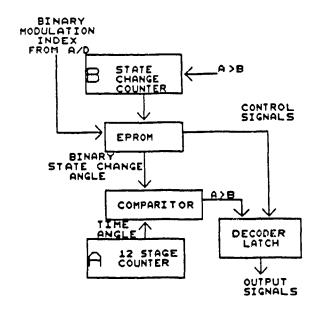

| Figure F3.39  | Control block diagram                                 | 194 |

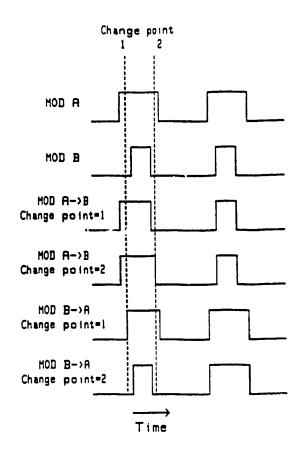

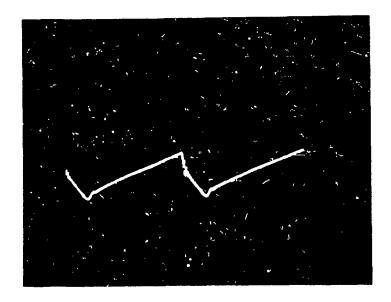

| Figure F3.40  | Digital modulation change                             | 196 |

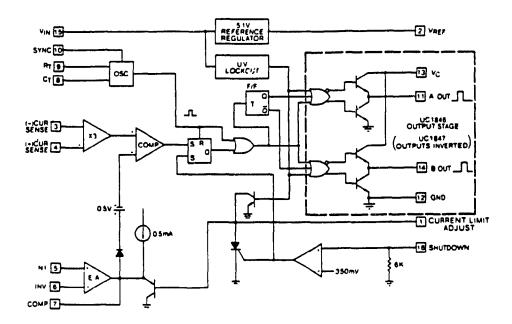

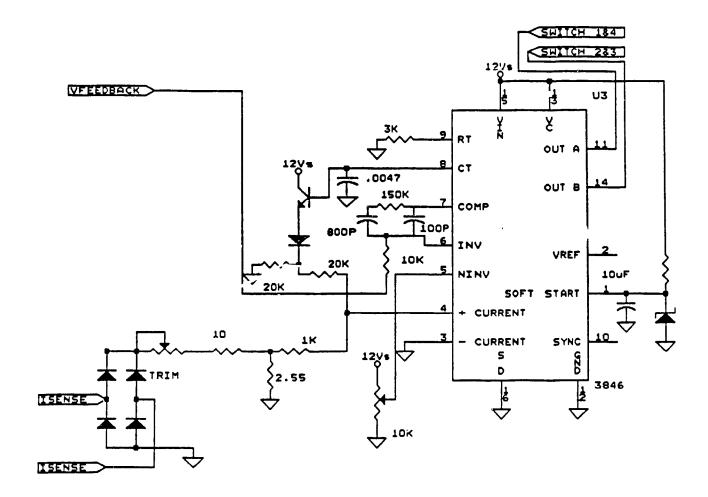

| Figure F3.41  | Current mode control chip 3846                        | 198 |

| Figure F3.42  | HF link control using the 3846                        | 199 |

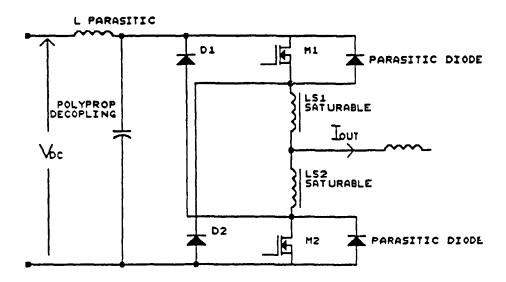

| Figure F3.43  | HF link and inverter MOSFET snubber                   | 200 |

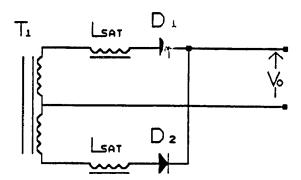

| Figure F3.44  | Output diode reverse recovery snubbing                | 201 |

| Figure F3.45  | Rectifier MOSFET snubber                              | 202 |

| Figure F3.46  | Critical current loop of MOSFET semiconductors .      | 205 |

| Figure F3.47  | Typical inverter pulsed current loop area             | 205 |

| Figure F3.48  | Improved inverter pulsed current loop area            | 206 |

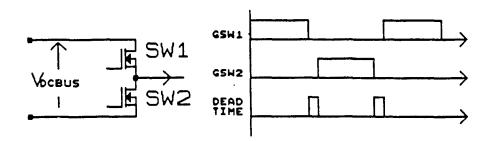

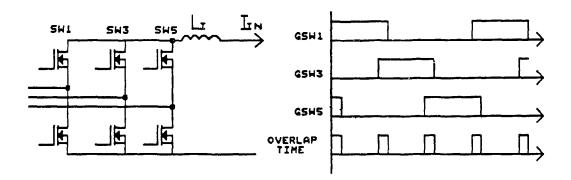

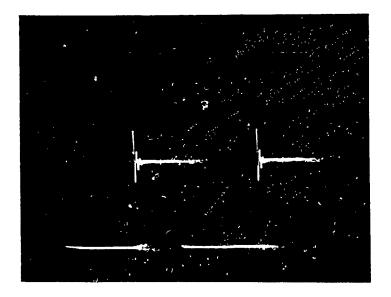

| Figure F3.49  | HF link and Inverter switch deadtime                  | 206 |

| Figu. e F3.50 | Rectifier switch overlap                              | 207 |

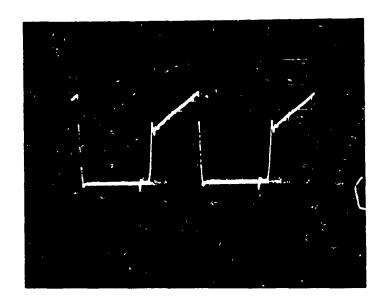

| Figure F3.51  | Experimental inverter line to line voltage            |     |

|               | J00V/div                                              | 209 |

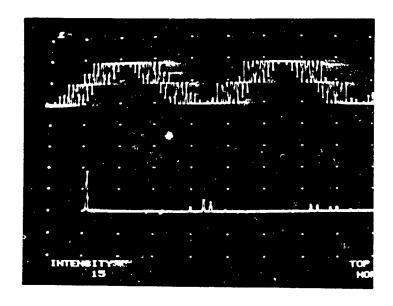

| Figure F3.52  | Experimental inverter line to line spectrum           | 209 |

| Figure F3.53  | Inverter switch and output line current               | 210 |

| Figure F3.54  | Experimental inverter load voltage                    | 211 |

| Figure F3.55  | Experimental inverter output voltage spectrum .       | 212 |

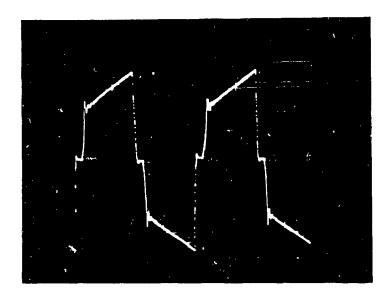

| Figure F3.56  | HF link MOSFET drain source voltage 100V/div 10μs/Giv | 213 |

| Figure F3.57  | HF link MOSFET current 20A/div 10μs/div               | 214 |

| Figure F3.58  | HF link transformer primary current 20A/div 10μs/div  | 215 |

| Figure F3.59  | HF link output diode reverse voltage 200V/div 10μ/div | 216 |

| Figure F3.60  | HF link output inductor current 10A/div 5μs/div .     | 217 |

| Figure F4.1   | $3-\phi$ load tree with examples                      | 22  |

| Figure F4.2   | Typical UPS inverter configuration                    | 22  |

| Figure F4.3   | Simplifier inverter circuit                                   | 225 |

|---------------|---------------------------------------------------------------|-----|

| Figure F4.4   | Resulting NEMA %voltage and phase unbalance (Zb=.7 lag)       | 227 |

| Figure F4.5   | DC link current during 1- $\phi$ operation of 3- $\phi$ UPS . | 228 |

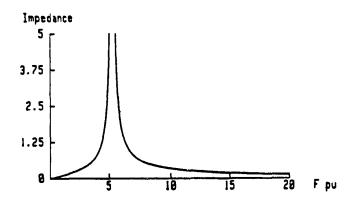

| Figure F4.6   | Typical LC filter impedance                                   | 229 |

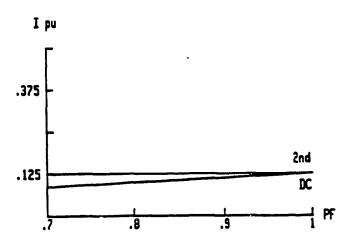

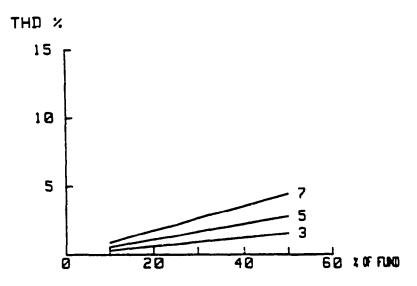

| Figure F4.7   | THD under nonlinear load with various harmonics .             | 230 |

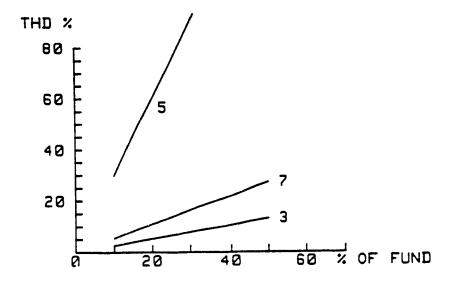

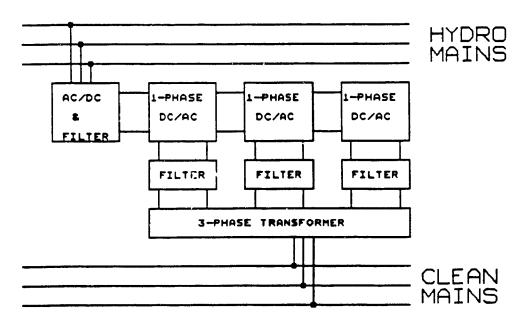

| Figure F4.8   | Unbalanced solution with three single phase bridges           | 231 |

| Figure F4.9   | Single harmonic trap                                          | 232 |

| Figure F4.10  | Unbalanced effect as XLO is varied (ZA=.7 lag,                |     |

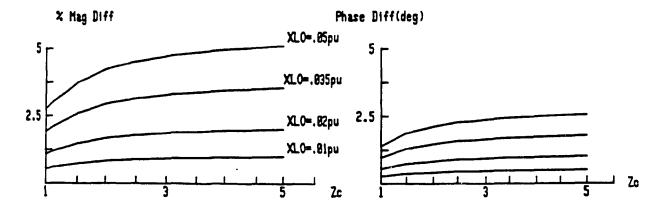

|               | Z <sub>B</sub> =.7 lead)                                      | 235 |

| Figure F4.11  | Advanced Harmonic Injection PWM                               | 238 |

| Figure F4.12A | Proposed UPS inverter topology                                | 239 |

| Figure F4.12  | UPS inverter topology proposed for special                    |     |

|               | case 1- $\phi$ line to neutral loads                          | 240 |

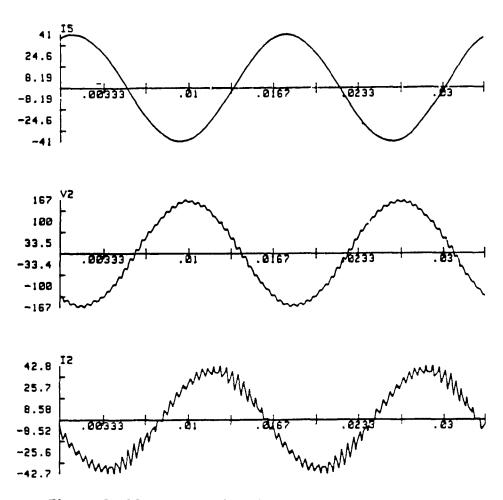

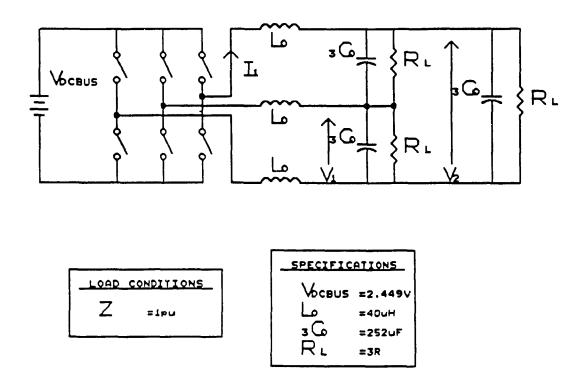

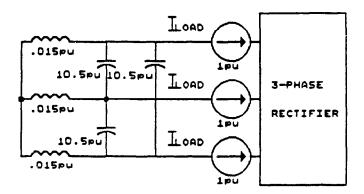

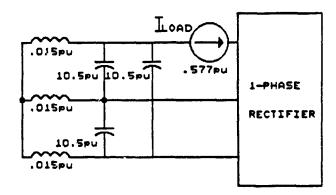

| Figure F4.13A | Simulation test circuit                                       | 242 |

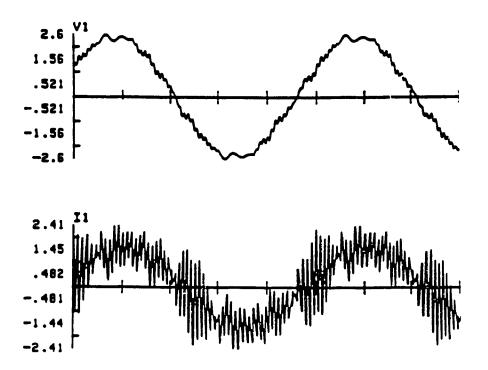

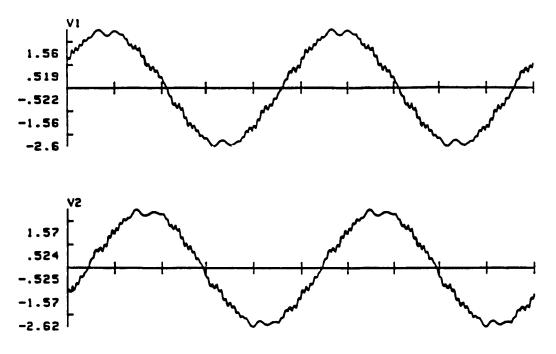

| Figure F4.13B | Simulated waveforms under balanced load conditions            | 243 |

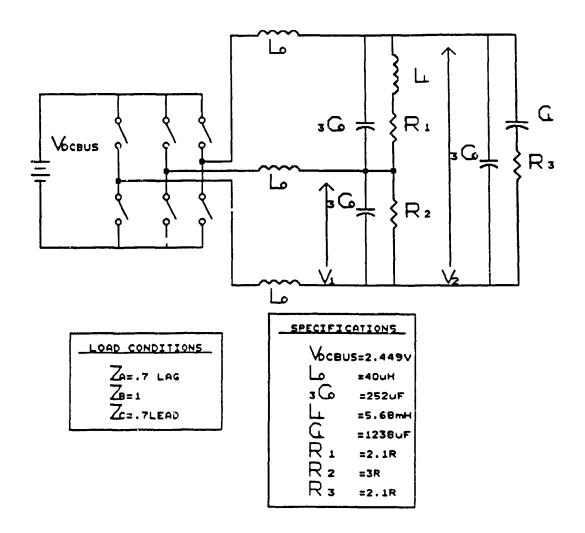

| Figure F4.14A | Unbalanced simulation test circuit                            | 245 |

| Figure F4.14B | Simulated waveforms under unbalanced load conditions          | 246 |

| Figure F4.15  | Equivalent circuit of load induced harmonics                  | 247 |

| Figure F4.16  | Equivalent circuit of single phase load                       |     |

|               | induced harmonics                                             | 248 |

| Figure F4.17  | THD under adverse load condition                              | 248 |

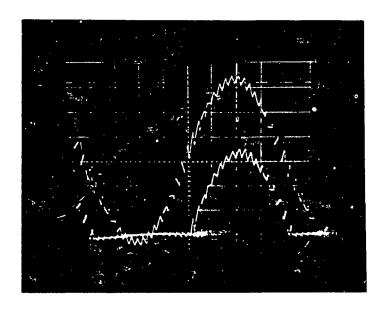

| Figure F4.18  | Waveforms under balanced load conditions                      |     |

|               | Power Factor=1, R=8.42 $\Omega$ (L-N)/phase                   | 250 |

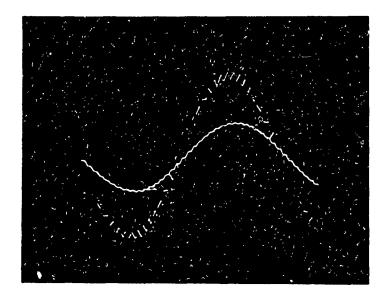

| Figure F4.19  | Waveforms under unbalanced load conditions                    | 252 |

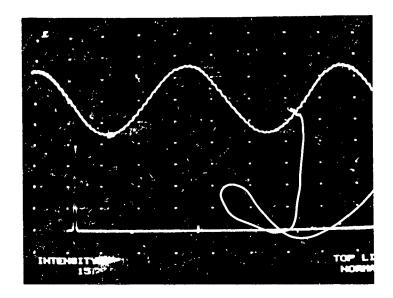

| Figure F4.20  | Waveforms under $3-\phi$ nonlinear load conditions .          | 254 |

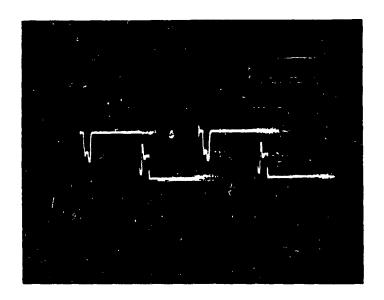

| Figure F4.21  | Waveforms under $1-\phi$ nonlinear load conditions .          | 255 |

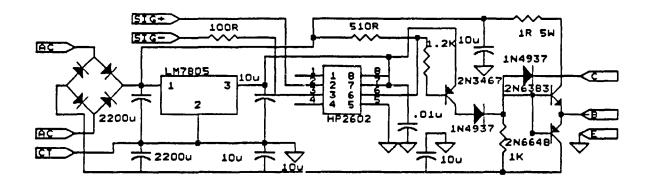

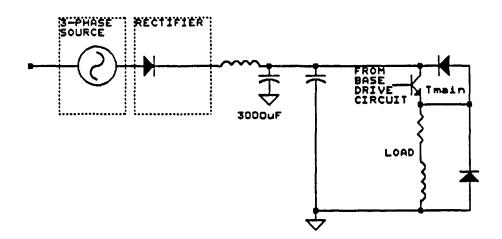

| Figure FA2.1  | The darlington base drive circuit                             | 298 |

| rigure raz.z | Storage time test circuit       | •     | •     | •     | •     | •      | 299 |

|--------------|---------------------------------|-------|-------|-------|-------|--------|-----|

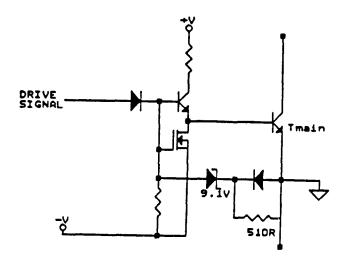

| Figure FA2.3 | Base drive modification accomm  | odati | ng a  | -20   |       |        |     |

|              | reverse potential voltage       | •     | •     | •     | •     | •      | 300 |

| Figure FA2.4 | The MOSFET base drive circuit   | •     | •     | •     | •     | •      | 301 |

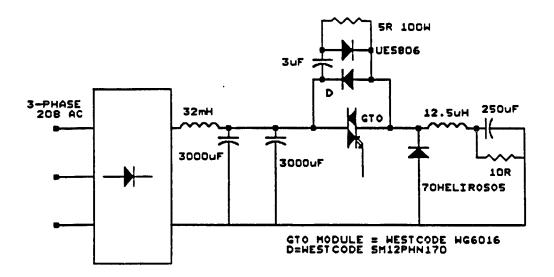

| Figure FA2.5 | GTO test circuit                | •     | •     | •     | •     | •      | 303 |

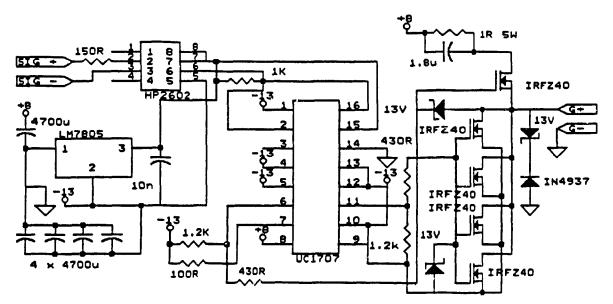

| Figure FA2.6 | The GTO drive circuit .         |       |       |       | •     | •      | 304 |

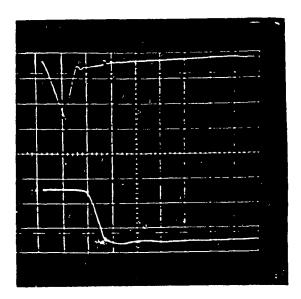

| Figure FA2.7 | Experimental GTO turn off base  | e and | anod  | e cur | rent  | •      | 305 |

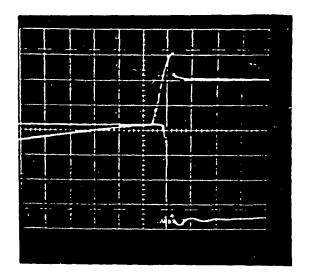

| Figure FA2.8 | Experimental GTO turn off ano   | de cu | rrent | curr  | ent a | nd Vak | 305 |

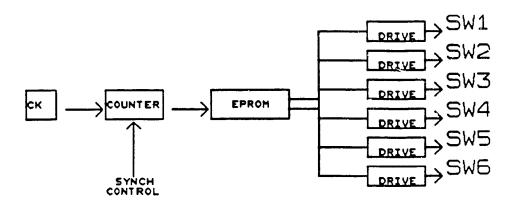

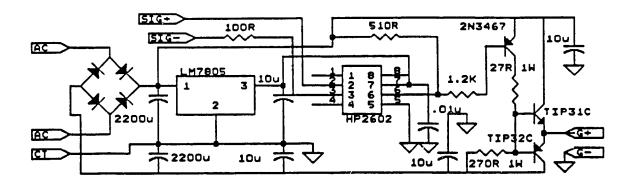

| Figure FA3.1 | The UPS rectifier logic circuit | contr | rol   |       | •     | •      | 307 |

# LIST OF TABLES

| Table T2.1  | Modern UPS Specifications                              | • | 15         |

|-------------|--------------------------------------------------------|---|------------|

| Table T2.2  | Harmonic spectrum with 20µsec deadtimes                | • | 45         |

| Table T2.3  | Five harmonic elimination SHE Angles                   | • | 49         |

| Table T2.4  | Maximum AC and DC TERM gain values (M =1)              | • | <b>5</b> 2 |

| Table T2.5  | Worst case inverter per unit ratings for SHE example   | • | 61         |

| Table T3.1  | Inverter PWM transition angles                         | • | 83         |

| Table T3.2  | Load voltage harmonics with .7 lagging power factor    | • | 90         |

| Table T3.3  | Output line current harmonic content for .7 leading pf |   | 92         |

| Table T3.4  | Inverter input current spectrum at .7 pf leading       |   | 105        |

| Table T3.5  | Inverter input current spectrum at .7 pf lagging       |   | 106        |

| Table T3.6  | Input current harmonic content as a function of M      |   | 119        |

| Table T3.7  | Rectifier input current spectrum for worst case input  |   |            |

|             | filter calculations                                    | • | 130        |

| Table T3.8  | Summary of high frequency link ratings                 |   | 171        |

| Table T3.9  | Switch evaluation criteria table summary               | • | 190        |

| Table T3.10 | UPS volume summary                                     | • | 218        |

| Table T3.11 | UPS weight summary                                     | • | 219        |

| Table T4.1  | Per unit rectifier current harmonics                   |   | 229        |

| Table T4.2  | Unbalanced output voltages                             |   | 244        |

| Table T4.3  | Expected voltage harmonics                             |   | 247        |

| Table T4.4  | Experimental component values                          |   | 249        |

| Table T4.5  | Unbalanced load line to line voltages                  |   | 251        |

| Гable TA2.1 | Storage time switching characteristics of QM 100DY-H   |   | 298        |

| Table TA2.2 | Storage time switching characteristics of QM 300HA-24  |   | 299        |

# LIST OF ACRONYMS

THD Total Harmonic Distortion

NEMA National Electric Manufacturers Association

UTS Uninterruptible Power Supply

PWM Pulse Width Modulation

HF High Frequency

CR Controlled Rectifier

VSI Voltage Sourced Inverter

CSI Current Sourced Inverter

SHE Selective Harmonic Elimination

SPWM Sinusoidal Pulse Width Modulation

MSPWM Modified Sinusoidal Pulse Width Modulation

HIPWM Harmonic Injection Pulse Width Modulation

PF/pf Power Factor

MTBF Mean Time Between Failures

EMI Electromagnetic Interference

TIPF Total Input Power Factor

EPROM Erasable Programmable Read Only Memory

SMPS Switch Mode Power Supply

IC Integrated Circuit

ZTO Zero turn off thyristor

# LIST OF SYMBOLS

VRMS Rectifier input rms voltage

VDC Rectifier output dc voltage

Controlled rectifier phase delay firing angle

VDROP Rectifier combined line and source impedance drop

VDCFLOAT Battery Float Voltage

Bd Battery discharge ratio

amin Minimum phase delay firing angle

$HAR_{LL}$  Amplitude of harmonic N

N Harmonic order

HARA. Fourier series odd harmonic frequency term amplitude

HARB Fourier series even harmonic frequency term amplitude

Vin Input converter voltage

FBK Filter Break Frequency

FBASE Rectifier input voltage frequency

RK Harmonic reduction factor

HAR<sub>FIRM</sub> Fundamental harmonic amplitude

HAR DOM Dominant harmonic amplitude

Fo Filter order

ORDER Dominant Harmonic Order

IIN Converter input current amplitude of harmonic N

IODC Rectifier output dc current

GAC Converter ac gain

GDC Converter dc gain

DF<sub>1</sub>, DF<sub>2</sub>, DF<sub>3</sub> Distortion factor quality index

GACMAX Maximum converter ac gain

GDCMAX Maximum converter dc gain

Icii Inverter dc link capacitor rms current quality factor

ICR CR rms input capacitor current quality factor

SW<sub>r</sub> Converter SHE switching frequency

M Converter modulation index

CII, CI2, LI, CI, Lo, Co Converter filter component values

XLI, XCI, XLO, XCO Converter filter component impedance values

ILIRMS, ICIRMS Converter filter component rms current rating

ILORMS, ICORMS Converter filter component rms current rating

VLIRMS, VCIRMS Converter filter component rms voltage rating

VLORMS, VCORMS Converter filter component rms voltage rating

Liva, Civa, Lova, Cova Converter filter component power rating

Iswave Converter average switch current rating

Iswrms Converter rms switch current rating

ISWPK, ISWIPK Converter peak switch current rating

ISW2PK, ISW3PK Converter peak switch current rating

ISWAPK Converter peak switch current rating

Vswpk Converter peak switch voltage

VDCBUSMAX Inverter maximum dc bus voltage

VDCCBUSMIN Inverter minimum dc bus voltage

VL-N Inverter output line to neutral fundamental voltage

ZL-N Inverter output line to neutral load

PTOTAL Total inverter output apparent power

ISCALE, VSCALE, Worst case inverter ratings program current voltage

ZSCALE and impedance scaling factors

QL Fundamental cut set matrix

QEC, QER, QEL, QES, QCC Sub divisional cut set matrices

QCR, QCL, QCJ, QRR Sub divisional cut set matrices

QRL, QRJ, QLL, QLJ Sub divisional cut set matrices

Ct Capacitor twig diagonal matrix

Cı Capacitor link diagonal matrix

Lt Inductor twig matrix

Li Inductor link matrix

Gt Conductance twig diagonal matrix

Gı Conductance link diagonal matrix

Rt Resistive twig diagonal matrix

Rı Resistive link diagonal n.atrix

VDCBUS Inverter input supply voltage

KMAX Total # of intersections below 90°

INTER(X) Converter transition or voltage swing angle

φN Phase shift of harmonic N

ZL Inverter load impedance

RL Inverter load impedance, resistive portion

XCL Inverter load impedance, capacitive portion

XLL Inverter load impedance, inductive portion

IDCBUS\_RIP Inverter input inductor current ripple

VIN\_RIP Inverter input capacitor voltage ripple

Inverter input supply current

RX... Normalized rectifier output voltage amplitude of

harmonic N and modulation index M

55 Converter transfer function

**TFM** Converter transfer function at modulation index M

TYMAX Maximum converter transfer function

79min Minimum converter transfer function

VBATMIN Minimum battery voltage

VBATMAX Maximum battery voltage

X State space analysis state vector

U State space analysis supply vector

Gsw1, Gsw2, Gsw3 Inverter switch gating signals

Gsw4, Gsw5, Gsw6 Inverter switch gating signals

VAN, VBN, VCN Inverter leg center point to fictitious neutral voltage

Vout Converter output voltage

VLOAD Converter load line to neutral voltage

IOUT Inverter output line current

Isw1, Isw2, Isw3 Converter switch current

Isw4, Isw5, Isw6 Converter switch current

Isw Converter switch current

IOUT\_TD(ωτ) Time domain representation of Iout

IOUT\_TDP(ωτ) Positive section of IOUT\_TD(ωτ) X Gswl\_TD(ωτ)

Gswl\_TD( $\omega \tau$ ) Time domain representation of Gswl

Pout Converter output power

Pin Converter input power

ILOAD Inverter load current

Vxn, Vyn, Vzn Rectifier input source line - neutral voltage

IINA Rectifier input bridge current

F1, F2 PWM control signals for rectifier gating derivation

VBA? Battery voltage

V Input rectifier peak source voltage

VMAX Input rectifier peak source voltage at high line

VMIN Input rectifier peak source voltage at low line

IDCMAX Maximum rectifier output dc current level

ILO Converter output inductor current

ILO, Rectifier output inductor current amplitude of

harmonic N at modulation index M

ILOMAX Maximum dc output current of rectifier

ILORIP Rectifier output current ripple factor

VLO Rectifier output inductor voltage amplitude of

harmonic N at modulation index M

IA Rectifier source line current

Ici Rectifier input filter capacitor current (single phase)

VLI Rectifier input filter inductor voltage

Displacement angle between Vxn and Inn

IINA Rectifier bridge input current

Olsplacement angle of IA

eVxn, Displacement angle of Vxn,

VINATHD Rectifier input voltage THD

Ici, Icii, Icii Converter input capacitor filter current

Ico Converter output capacitor filter current

ILI Converter input inductor filter current

VDIR, VD2R, VDR Reverse diode voltages

Vo HF link output load voltage

Io HF link output load current

NN Transformer turns ratio

D Duty cycle

DMAX Maximum duty cycle

DMIN Minimum duty cycle

VINMIN Minimum HF link input voltage

VINMAX Maximum HF link input voltage

VOMAX Maximum HF link output voltage

VOMIN Minimum HF link output voltage

ID1, ID2, ID HF link diode current

IDIAVE, ID2AVE HF link diode ave current

AP Transformer area product

Aw Transformer core window area

AE Transformer magnetic core cross section area

Ku, Kt, Kp, KB Transformer sizing factors

Fsw HF link switching frequency

ΔB Transformer core flux swing

Ap Relative transformer area product

VLO Output inductor voltage

Vci, Vci, Vc2 Input capacitor voltage

IT Transformer current

Fck Clock frequency

Lsi, Ls2 Saturable reactors

I, I, I, I Inverter output line currents

Z1, Z2, Z3 Inverter output leg impedances including filter

capacitor and load

VPWM Inverter output line to line PWM waveform

Iui, Iu2, Iu3 Inverter mesh analysis loop currents

Za, Zb, Zc Inverter unbalanced load impedances

ZFILTER Equivalent LC filter impedance

VLOADLL, Inverter output line to line voltage amplitude

of harmonic N

kVA Kilo volt-amp

# 1.0 INTRODUCTION

#### 1.1 General

Electric power utilities have strived to keep ac power at high availability. However, by virtue of its complex network structure (exceeding on occasion thousands of miles) power distribution equipment is prone to abnormalities and failure. Although numerous power line disturbance phenomena may occur, power blackouts are typically considered the prime problem. The mean time between failures (MTRF) of a high quality power utility is roughly 200 hours [6]. If uncompensated, outages may lead to a life threatening situation in medical facilities and air traffic control centers.

This problem gave rise to the concept of utilizing an intermediate or auxiliary energy stage between the ac mains and the critical load which could process and provide power during a utility failure. The uninterruptible power supply [UPS] is such an intermediate stage providing variable amounts of battery powered, auxiliary energy. Its use is now virtually standard practice in the traditional life threatening, critical power environments.

The history of the UPS reveals several distinct evolutionary phases leading to the present generation termed "4th generation UPS" characterized by PWM control. Recent developments include a thrust towards the production of a UPS, with more extensive applications beyond those of the traditional life threatening type. New installations in close proximity to manpower as well as in expanded industrial environments have led to the imposition of stricter UPS specifications which have handicapped the present "4th generation". Two of the main factors contributing to the increasing use of UPS systems were the introduction of modern sophisticated electronics equipment into virtually

every facet of engineering, and the optimization of manufacturing flow concepts. Each of these two factors are are discussed in more detail.

Modern office complexes and many manufacturing divisions now 1) utilize high technology equipment in the form of telecommunications apparatus, robotics, data acquisition tools, main frames and personal computers. On a broader scale, many small business outfits are also stepping up their employment of similar technologically intensive yet less complex equipment [7]. The majority of equipment in this category contain microprocessors which have branched out from their computer roots into many diverse applications such as cash register control, telephone operation, security systems supervision, process control and instrumentation. Such equipment may provide the industrial leading edge and/or enhanced competitiveness at levels, yet are often highly sensitive to mains disturbances. A power outage in the millisecond range can cause excessive costs and delays due to loss of services and/or data. Moreover, of equal importance, a substantial part of equipment damage or inexplicable shut downs are due to ac mains over voltages and high voltage spikes which typically occur at a rate of 5/month [6]. Reasonable hydro specifications guarantee a steady state window of +/-10% nominal voltage. However, a portion of modern technology based equipment significant computers) are only guaranteed to operate properly up to and including 6% above nominal line voltage [8]. Consequently the MTBF of the system is influenced to a greater extent by the ac mains quality rather than the MTBF of the actual equipment. As more institutions demand higher amounts of ac energy in many areas a negative quality factor is created. Some experts insist that in certain areas the

escalating demand for ac power has highly burdened hydro facilities leading to an actual diminishing of quality [9]. This leads to a higher risk of ac line abnormalities. In an effort to alleviate the quality problem many businesses are beginning to accept the need for a UPS system.

2) Secondly, going industrial trend towards reduced maintenance and increased quality has led to flow manufacturing concepts such as the Can Ban Line and push methods. These involve strict interaction between machines and operators in a production line format that are highly vulnerable to interruptions. Reinstating flow may involve resetting machinery, electronic robots or re-booting software control. This often results in costly setbacks. With the expanding awareness of these new manufacturing techniques many industries are becoming more heavily dependant on the quality of ac power supplied to them. A detailed study revealing the magnitude of operating losses attributed to ac failures dictates that on the average day an average sized Canadian industrial facility will lose \$3000.00 due to a power outage of less than one minute [10]. An Inco representative recently reported at a conference that a power outage of 100ms forced the reprocessing of \$250,000 worth of nickel [7]. It is clear that the effect of ac shutdown must today be considered more damaging and costly to businesses and industries than in previous years. Consequently to reduce expenses, an increasing demand for medium power UPS has been generated by manufacturing departments to reduce costly, unexpected shutdowns.

## 1.2 Evolving UPS Requirements

The widening spectrum of applications for medium power UPS has necessitated the establishment of a new set of power supply requirements both physically and electrically.

# 1.2.1 Physical UPS Requirements

Physical requirements stem from the office environment where floor space prices are at a premium and consequently raise concerns about supply power density. Most present medium power UPS have power densities in the range of .1->.4 w/in<sup>3</sup> [11],[12],[13],[14],[15],[16] without batteries. Combining this 'ow power density with added space (approximately 25 inches for rear access leads to the typical floor space requirement of 21 ft<sup>2</sup> for a 10kVA UPS. This renders it expensive to utilize especially in down town locations where floor space rental is in the order of \$30.00/ft<sup>2</sup> to \$190.00/ft<sup>2</sup> per month.

Secondly, from the standpoint of floor loading, many office structures can handle approximately 70kg/ft<sup>2</sup>. With a typical weight of.06->.1 kg/w (without batteries) a medium power UPS could weigh 1000kg [14],[16]. This is often too heavy for non concrete floors consequently the range of application may be limited by weight constraints.

Finally, many UPS utilize Pulse Width Modulation (PWM) techniques in order to improve the waveforms and benefit from the resulting components size, weight and cost reduction. For medium power semiconductors, the maximum switching frequency is relatively low creating in many instances unbearable audible noise in the range of 1 to 18 Khz. This often forces added consideration and expense for the utilization of such a converter in the office or working environment.

In summary, the three major physical challenges are weight reduction,

size reduction and audible noise reduction.

## 1.2.2 Electrical UPS Requirements

Traditionally UPS are designed to deliver power to linear and balanced loads which in the past were in the majority. However, modern high technology equipment is not necessarily balanced or linear. In fact, by the \_ ur 2000 it is estimated that over 50% of the utility's power grid will consist of computers or similar equipment [18]. UPS loads are expected to dramatically increase accordingly. These loads can create conditions where the typical UPS inverter stage can no longer guarantee clean power nor abide by the specifications for the output waveform. This may lead to load failure as well as a reduction of UPS MTBF and battery life.

Secondly, with expensive shutdown costs, system reliability requirements are escalating. Surveys have shown that large (32%) UPS downtime is attributed directly to failures initiated at the control components level primarily due to IC failure [17]. Consequently the need has arisen to alleviate this condition in order to improve reliability and general ruggedness of the supply.

Finally, most UPS are equipped to handle loads of limited power factor typically in the range of .8 lagging to unity [11]. Limiting the power factor range typically reduces the voltage transfer function window of the UPS inverter stage allowing for a more efficient design. This is no longer sufficient as many nonlinear loads exhibit capacitive characteristics in the leading range and many inductive linear loads have power factors less than .8. In summary, the main electrical challenges include the capability to deliver quality power to nonlinear and unbalanced loads, increased power factor range and improvement in supply ruggedness.

### 1.3 Scope of this Thesis

Todays modern UPS are static, employing semiconductors combined with battery backed power. Although various configurations are now available the UPS structure most commonly encountered is termed "4th generation UPS" [11],[16].

Being geared essentially for traditional applications the typical UPS cannot meet many of the new challenges in modern industrial and office complex applications without added expense and/or complexity. In an attempt to compensate for this, many UPS manufacturers have invested heavily in adapters which when combined with the present generation UPS provide partial solutions in limited areas. However some physical requirements are often impossible to meet with the present system. Consequently, a significant amount of research is being directed towards medium power UPS to complete the present "5th Generation" evolutionary stage and thus eliminating the need for various acapters, reducing space and weight requirements and permitting less expensive operation in the widening spectrum of office and industrial applications.

This thesis contributes to this research trend by presenting the theory and design of a UPS tailored to new applications meeting many of the challenges required by todays typical UPS customers. Solutions to the major setbacks presently encountered are derived, implemented and tested leading to a high performance UPS.

Chapter two initially outlines a framework of specifications for a UPS which is expected to complement the new, more specification stringent environment. Since focus is given on overcoming the modern electrical and physical challenges previously presented, attention is focused primarily on the power train. A number of secondary items (which are clearly important

during actual design) have virtually no significance on the results presented. For this reason items such as the transfer switch, transient response, battery storage facilities, low voltage disconnects, overload conditions, electromagnetic interference, loop compensation and circuitry surveillance are given little consideration.

The chapter then presents an improved topology which is expected to satisfy the needs of the modern requirements by reducing weight and size. The topology highlights a high frequency link stage to provide electrical isolation.

Thirdly a critical evaluation of pulse width modulation techniques is presented leading to the selection of the most compatible ones for the UPS topology selected. This leads to further size and weight reduction.

Finally, chapter two presents developed software tools essential to accurate UPS design and evaluation. The software routines include a worst case inverter ratings program and an analysis/simulation program.

Chapter three focuses on the UPS power systematic power train design. The power train is segregated into three stages; the rectifier stage, the high frequency link stage and the inverter stage. Each is analyzed and optimized separately, worst case component ratings are evaluated and selected sections are simulated and/or experimentally proven. Three possible options for a high frequency link stage are evaluated. The most appropriate one is selected based on practical limitations. However, not to exclude future improved component availability, all component stresses and ratings are done in a per unit system thus simplifying future pro rating. Attention is also focused on items which are of practical importance such as semiconductor drive and switch evaluation, controllers for each stage, snubbers. gating requirements such delays/overlaps, transformer saturation and cost considerations. This ensures

that practical limitations are not simply ignored during the design and evaluation process.

Chapter four focuses on special UPS load considerations which are not typically addressed in present UPS designs. The load effects are evaluated and utilized to make design and strategy adjustments to the UPS topology. After optimally designing the output filter and applying a novel high performance PWM technique the improved inverter stage is simulated and experimentally verified under various harsh loading conditions.

Chapter five summarizes all conclusions and extrapolates the extent to which the design goals were achieved. Moreover further areas of continuing research are presented.

# 2.0 UPS DESIGN CRITERIA

#### 2.1 Introduction

An overview of a wide variety of UPS manufactures data sheets will reveal that specifications can be subdivided into two classes. The first class encompasses a majority of requirements which have been developed and accepted over decades rendering them as virtual industry wide standards. These include specifications such as

-Total Harmonic Distortion (THD) < 5%

-Maximum harmonic amplitude < 3%

-Input power factor at rated load > .9

In contrast, the second class contains several specifications which have not solidified and remain relatively inconsistent. Although many manufacturers of UPS now list their respective specifications, a uniform standard is often lacking. Specifications in this category typically include

- -Allowable unbalanced load

- -Output Power Factor

- -Power Density

- -Allowable Nonlinear Load

Using typical applications, publications and surveys, a modern specifications table is constructed encompassing both classes. A comparison between present typical UPS specifications and the modern specifications table reveals critical performance characteristics which are in need of being upgrading to meet the requirements of modern consumer applications.

Given incomplete specifications, the presently existing popular 4th generation UPS topology is segregated into smaller sections in order to

evaluate areas where alterations or restructuring would enhance performance. In order to meet the stringent requirements the overall power train topology is modified. This includes the application of a high frequency link stage yielding a high performance type UPS.

Accompanying the high performance topology is the requirement for an equally high performance PWM technique. The selection of an advanced PWM technique is not a simplistic procedure. With the wide acceptance of gate turn off power devices (eg bipolars, power FETs, GTOs etc) significant research effort has recently been focused on improving converter performance by improved PWM techniques. With still higher performance power semiconductors on the horizon (ie ZTO), PWM is envisioned to carry even greater significance. In response to this a number of "improved" PWM schemes have been proposed to increase converter gain and/or reduce output distortion. However little or conflicting data is available about their merits relative to each other. Further, most PWM schemes are judged by their output voltage spectrum when applied to an inverter stage while numerous other criteria as well as applications should be considered. Since UPS typically contain a controlled rectifier stage as well as an inverter stage it may be erroneous to select the rectifier PWM scheme based on its application to an inverter stage. Consequently, selection of the best PWM technique for UPS applications is accompanied by uncertainty which can lead to less than optimum results. Recognizing this problem, this chapter compares the most prominent PWM schemes, providing the framework for selection of the most compatible PWM technique for the rectifier as well as inverter stages of the proposed high performance UPS power train.

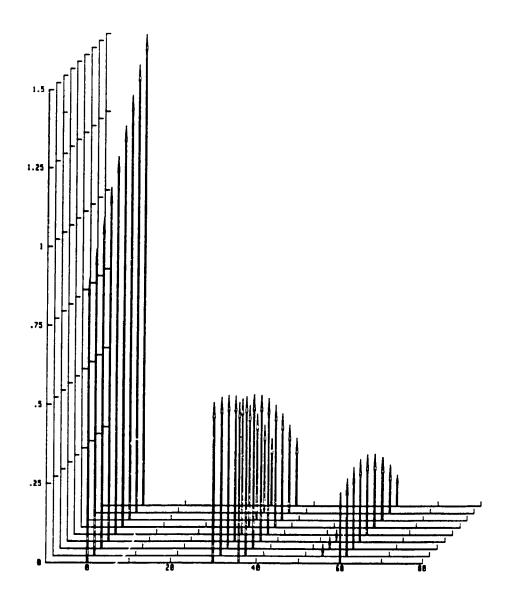

Finally, the void in available software directed towards power electronics necessitates the development of preliminary analysis and design

software tools specially tailored to three phase power converters. This chapter develops two programs capable of evaluating UPS performance characteristics leading to correct component selection. The developed programs include an Analysis/Simulation routine [3] and A Worst Case Components ratings routine.

# 2.2 Modern Medium Power UPS Specifications

# 2.2.1 Input Specifications

Medium power, when referred to UPS driven critical loads typically falls within the 10-20 kVA range. At this power level three phase 208 volt nominal lines are by, far the most widely used supply rails in North America. Hydro systems offer a typical window of +6%,-10% of nominal voltage [8] and although some power supplies offer brownout handling capabilities until -15% [16], this is often considered to be too conservative since such occurrences are rare. Moreover, batteries make such a step unnecessary and costly.

Frequency variation by hydro is typically +/-1% [8] indicating that the UPS should be conservatively rated at +/-3% to ensure problem free input operation when a heavy load steps on line transiently slowing down hydrogenerators.

Input power factor is often given little weight by UPS manufacturers yet since total input apparent power is used by electrical utilities as a pricing parameter, a poor power factor becomes costly. Moreover, since most UPS are used at 64% of rated load [6], power factor should be relatively high even at half load. This translates into a modern input power factor requirement of pf >.9 for 50% to 100% load. Other input criteria such as surge protection, electromagnetic interference (EMI) and walk-in are important parameters yet

have no influence within the scope of this thesis and are thus neglected. A summary of the input specifications are given in table T2.1

## 2.2.2 Output Specifications

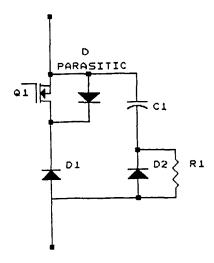

The vast majority of linear and nonlinear loads are capable of operating properly with a steady state supply voltage of up to 5% total harmonic distortion (THD) as long as no individual harmonic exceeds 3% in amplitude. The typical modern UPS is designed to deliver these specifications while accommodating balanced and linear loads, which in the past were the majority. However, newer types of loads are not necessarily balanced or linear and can create conditions where the typical UPS inverter stage can no longer maintain waveform specifications possibly leading to load failures. In fact many consumers are now requiring that UPS manufacturers give specifications under nonlinear load conditions as well as linear in order to guarantee performance Further. purchase [8]. many manufacturers are outlining testing standards for nonlinear applications such as three to one crest to rms single phase load current waveforms at 70% to 85% rated power [8]. This is in anticipation of nonlinear switch mode power supply (SMPS) current demands which are now found in a wide variety of equipment. A second standard often used is a test circuit simulating computer power supplies shown in figure F2.1 [19]. In order to accommodate such loads, the UPS THD requirement should be held to <5% for linear as well as nonlinear loads.

Figure F2.1 Typical SMPS equivalent circuit C=2.8μF/W 1/R=8.7μmhos/W

Unbalanced loads often induce unbalanced load voltages. For some types of loads connected to the same voltage lines the existence of unbalanced voltage may be damaging. Ac motors for instance, may experience dramatic overheating and life reduction due to short circuit, negative sequence rotor currents. The National Electric Manufacturers Association (NEMA) has recommended heavy motor deratings for unbalanced supply voltages greater than 2.5% while operation of motors with greater than 5% supply unbalance is not recommended [20]. By unbalancing loads on the three phase inverter this limit is easily exceeded. Since modern loads are not expected to be balanced, the UPS should keep voltage unbalance to less than 1.5% even under worst case unbalanced load.

Although no standard for acceptable load power factor range has been widely adopted, many manufacturers design to meet loads with limited range of .8 lagging to unity [11]. This avoids larger inverter modulation range and trims down UPS design requirements. However many modern loads such as computers and SMPS do not fall into this range. This dictates that modern UPS should be able to deliver power to a wider range of loads typically varying from .7 lagging to .7 leading.

### 2.2.3 Physical Specifications

Traditionally size and weight of the UPS has not been a critical

parameter since battery backup size and weight dominated. However many industries and office complexes are reducing battery reserve requirements to the level where only an orderly shutdown procedure need be powered from backup. This has re-focused attention towards UPS physical specifications. Typical medium power 4th generation UPS have a power to weight ratio of roughly (10-15) w/kg without batteries [11],[12],[15]. Modern UPS in the same power range should approach weights that virtually permit wall mounting eliminating the requirement for occupied floor space. This translates into a weight ratio of better than 25w/kg.

In general, size is proportional to weight. A typical UPS has a density of .1-.5w/in<sup>3</sup>. This should be increased to lw/in<sup>3</sup> resulting in office volume cost savings. Further size reduction in the order of 40% can be realized by exploiting forced air cooling with little cost impact. Moreover, MTBF figures of 800,000 hours for fans will not effect the overall UPS system MTBF. Since UPS are now expected to operate in human working environments where normal conversations are to be held, power supply audible noise is a concern. Todays typical 4th generation UPS utilize relatively high semiconductor switching speeds when implementing PWM strategies. For medium power semiconductors the maximum switching frequency is relatively low creating in many instances unbearable noise in the range of 1 to 18Khz. This often forces added considerations and expense for utilization of such a converter in the working environment. Further, the use of forced cooling rather than convection will create additional noise. Summing all elements contributing to noise, the modern office environment will have audible noise of less than 55 - 65dba at 1 meter distance with a 45dba ambient noise [21].

Operating temperature in controlled environments seldom exceeds 30°C, however the UPS is expected to operate when environmental control is

temperature and the allowable components temperature rise. The UPS should be fully operational in a 40° ambient. This gives a baseline for heatsink size. Efficiency of the power supply is also a critical parameter influencing cost directly and MTBF indirectly. Todays UPS efficiency ratings fall in the 72% to 85% range depending on operating conditions. Design of a modern UPS should allow for no lower than 80% efficiency at nominal load to keep user costs low and MTBF high.

A summary of the specifications is listed in table T2.1

INPUT: Voltage  $3-\phi$  208 +10% -10%

Freq 60 ±3hz

Power Factor >.9 from 50% to 100% load

OUTPUT: Voltage 208

Power 5-15Kva

THD <5%

Maximum harmonic <3%

100% nonlinear load capacity

typical 120° pulse for 3-φ

typical 3-1 peak to rms ratio for 1-\$\phi\$

Full unbalanced load capabilities

Including open loads

100% combination of unbalanced and nonlinear loads

Power factor: .7 lag to .7 lead

PHYSICAL: Temperature operation 0°-40°

Forced air cooling Weight ratio >25W/kg

Density >1W/in

Audible noise <65 dba

Efficiency: >80%

Table T2.1 Modern UPS Specifications

## 2.3 UPS Topology Evaluation

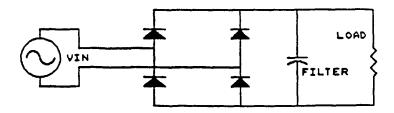

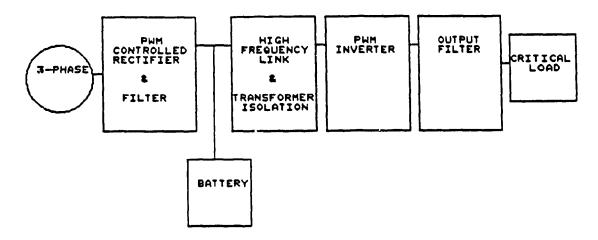

Numerous UPS topologies exist for medium power applications with respective advantages and drawbacks. Included in the list of topologies is the Ferroresonant version which is either "on line" and inefficient, or "off line" increasing risk of unavailability. The triport UPS which has the battery charger and inverter stages merged also has handicaps since during its standby stage the complex inverter design delivers charging power to the batteries. Should supply failure occur, the inverter must reverse the power flow to supply the starved load. The low voltage transfer time interval may be to severe for some loads. Square wave UPS,s have limited application as they do not produce a sine wave output. The most common UPS structure available today and possibly the most reliable one is shown in block form in figure F2.2. Classified as a 4th generation UPS, this configuration will be referred to throughout this thesis as the benchmark topology.

Figure F2.2 4th generation UPS power train topology

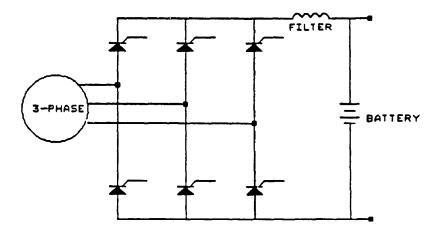

The phase controlled rectifier typically consists of thyristor semiconductors and a single order inductive filter. This stage is shown in

expanded form in figure F2.3. The rectifier output voltage swing is given by

$$VDC = \sqrt{2} \frac{3 \cdot (VRMS - VDROP)}{\Pi} \cdot COS(\alpha)$$

(2.1)

where V<sub>drop</sub> = typical combined line and thyristor drop at at medium power levels

Figure F2.3 Phase controlled rectifier/battery charger stage

The batteries must be kept at "float" voltage potential continuously in anticipation of a power failure. This voltage is roughly 2.25 volts per battery cell. During a power failure the battery terminal voltage is permitted to diminish to 1.75 volts per cell before permanent damage due to deep discharge will occur. At low ac line

$$V_{RMS} = 183V$$

At this voltage the rectifier will be at full conduction angle (ie  $\alpha=0^{\circ}$  = diode bridge action) giving the rated "float" voltage of the batteries as

$$V_{DCFLOAT} = \sqrt{2} X \frac{3(183-5)}{\pi} COS(0^{\circ}) = 240V$$

(2.2)

The maximum firing angle corresponds to maximum input line voltage

capabilities after an ac failure at which point in time the battery pack voltage has depleted to virtual low voltage disconnect point. The angle can be determined from the ratio of minimum to maximum battery voltage given by

$$Bd = \frac{1.75}{2.25} = .78$$

Therefore at high ac line

$$V_{RMS} = 229V$$

$V_{DROP} = OV$

and the minimum battery voltage firing angle is given by

$$\alpha = ARCCOS \left[ \frac{VDCFLOAT \cdot Bd \cdot \Pi}{2 \cdot 3(V_{RMS} - V_{DROP})} \right]$$

or

$$\alpha_{\min} = ARCCOS \left[ \frac{240 \cdot .78 \cdot \Pi}{\sqrt{2} \cdot 3(229 - 0)} \right] = 52^{\circ}$$

The harmonic voltages present at the rectifier output terminals are derived using fourier series and are given by

$$HAR_{N} = \sqrt{HARA_{N}^{2} + HARB_{N}^{2}}$$

(2.4)

where

$$HARA_{N} = \frac{6}{\Pi} \int_{\alpha+(\pi/3)}^{\alpha+(2\pi/3)} Vin \sin(n \cdot \omega \tau) d\omega \tau$$

HARB<sub>N</sub> =

$$\frac{6}{\Pi} \int_{\alpha + (\pi/3)}^{\alpha + (2\pi/3)} V_{\text{IN}} \cos(N \cdot \omega \tau) d\omega \tau$$

$$V_{IN} = \int_{2}^{2} V_{RMS} \sin(N \cdot \omega \tau) \qquad (2.5)$$

$$N = 6, 12, 18, \dots, \infty$$

The dominant harmonic to be filtered will be the sixth for which at

$$\alpha = 52^{\circ}$$

results in

$$HAR_N = 84V$$

or 44% of the dc level voltage. Since battery manufacturers recommend less than <5% ripple for full battery life span [22], this harmonic would have to be reduced to roughly 2% indicating a bulky filter requirement. The filter would typically be at a break frequency of

$$FBK = \left[\frac{HAR_{FUND} \cdot RK}{HAR_{DOM}}\right]^{1/FO} \cdot ORDER \cdot FBASE \qquad (2.6)$$

Where FBK = Filter break frequency required to reduce the dominant harmonic to RK times the fundamental

RK = Reduction factor=.02

$HaR_{FUND} = 186V$

$HaR_{DOM} = 84$

FBASE = Input supply frequency=60hz

Fo = Filter order=1 (choke only)

ORDER = dominant harmonic order =6

Evaluation of equation 2.6 gives

FBK =16hz

These result translates into the requirement of a large output filter reactor going against the desired weight and size reduction. Moreover, reflected back on the input ac side, the power converter contributes to a poor power factor and an input line current with low order harmonics. The input line current harmonic ratios at full conduction are given by

$$\left| \frac{\prod_{N} n}{\prod_{N}} \right| = \frac{1}{N}$$

$$= 1,5,7,11,13,...,00$$

(2.7)

A 20% fifth, 14% seventh, etc. as equation 2.7 indicates, may lead not only to poor power factor, but input voltage distortion and power line overheating. To overcome these problems, and the ongoing expense of poor power factor, shunt capacitors are often used [23]. These components are also large and bulky once again going against the weight and size reduction requirements.

The battery stage is generally independent of the power electronics design. Weight and size are directly related to charge required and battery type. The cells are considered to be external to the UPS electronics and may not necessarily be located in its vicinity.

The PWM inverter stage generally employs gate controlled semiconductors such as GTO's or darlingtons. An expanded version of the inverter stage represented in figure F2.2 is shown in figure F2.4.

Figure F2.4 3- $\phi$  UPS inverter stage

By increasing switching frequency the output filter is generally reduced in

size. However, typical PWM inverters in the medium power class have limited switching speed due to associated switching stresses. The required filter design to reduce the harmonic content typically contains poles in low frequency ranges which pose a high risk of increasing THD when the UPS is supplying power to a nonlinear load. Further, the relatively high impedance of the filter causes unbalanced voltages when power is supplied to unbalanced loads which may cause undesirable effects. Finally, PWM reduces the inverter voltage gain. This implies higher component currents, higher temperature operation and lower reliability.

The isolation transformer is used for voltage matching, isolation and to create a ground reference for single phase loads (delta-wye windings). At 60hz rated frequency, the three phase transformer may weigh hundreds of pounds. The transformer stage is generally the largest and heaviest item (excluding batteries) in the UPS. Therefore a major concern of an improved design is the reduction in the size and weight of the output transformer.

### 2.3.1 Proposed UPS Topology

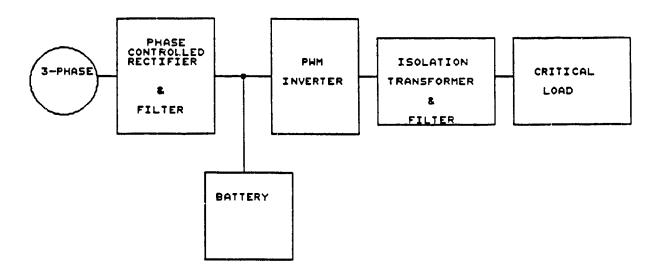

The new topology shown in figure F2.5 would address the requirements associated with the specifications outlined earlier.

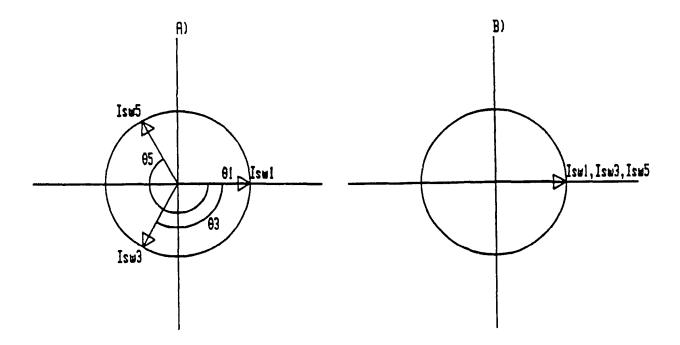

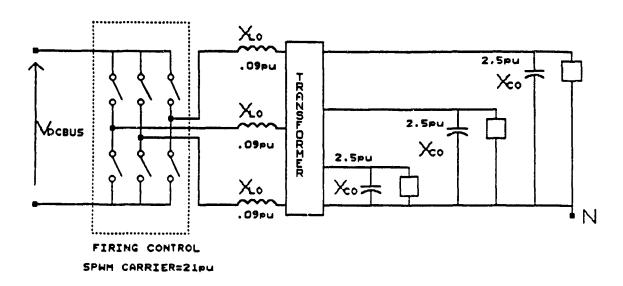

Figure F2.5 Proposed 60hz UPS topology

The novelties of this topology can be categorized as follows:

## 1) Input stage;

A PWM controlled rectifier replaces the previous 4th generation style phase controlled bridge. The associated advantages are;

- -A reduction of input and output harmonic distortion.

This implies reduction of filter size, weight and cost.

- -Linear modulation control rather than "COS( $\alpha$ )" control previously encountered in the phase controlled rectifier. This should simplify control.

- -Improved input power factor which further reduces required filtering and user ongoing cost penalties.

- -Improved dynamic response. A line or battery transient could be compensated with higher speed resulting in a larger bandwidth.

# 2) Inverter stage;

The PWM inverter and transformer are replaced with a

high frequency link stage (HF link) and a regulated input PWM inverter. The associated advantages are;

-Isolation is now provided by a 2 Kg high frequency transformer rather than 300 Kg low frequency version. This dramatically reduces weight and size.

-Since the inverter input is regulated, high performance fixed pattern PWM techniques can now be applied to the inverter. This results in higher voltage gain and lower switching frequencies thus reducing switching stresses and improving the input and output harmonic distortion. This translates into further filter size and weight reduction.

-The gating and control of the 3- $\phi$  inverter is simplified thus improving its reliability.

#### 3) Output filter stage;

The output filter stage is strategically designed to permit passive compensation for the application of a wide range of modern loads. The associated advantages are:

- -Ability to supply power to fully nonlinear loads.

- -Ability to supply power to fully unbalanced loads.

- -Ability to supply full rated power to single phase loads.

- -Improved dynamic response for accommodation of special switch mode power supply loads.

- -Lower filter cost, size and weight.

#### 4) General topology advantages;

Further indirect topology advantages include;

-The use of forced air cooling to further shrink heatsink size and weight. The fans provide for little reliability downgrade or maintenance increase. Fan filters are not required because air flow is solely through the confined heat sink apparatus.

-Common power semiconductors throughout the power stages and as a result a single style of base drive. This drives cost down because of increased quantities. It also tends to increase quality due to increased simplicity.

The overall objective of the UPS topology is to substantially reduce size and weight over the present 4th generation UPS while at the same time exceeding previous performance capabilities to reach the high performance specifications outlined in chapter 2.2.1.

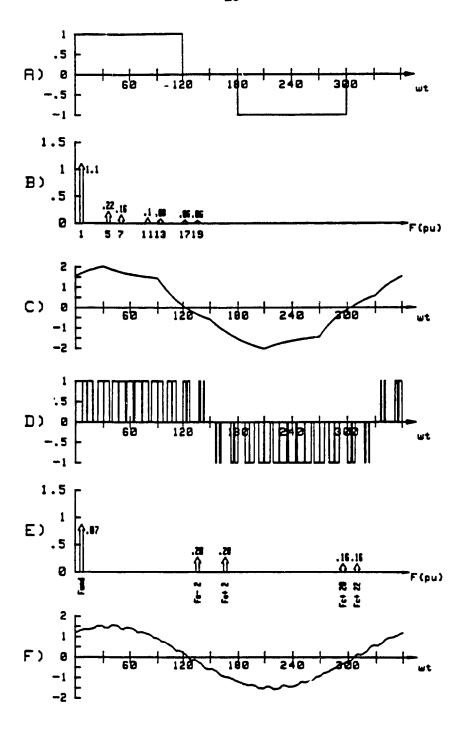

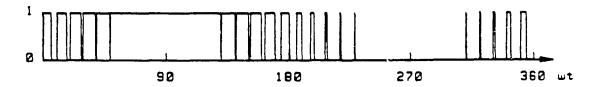

### 2.4 PWM For Improving Power Converter Performance

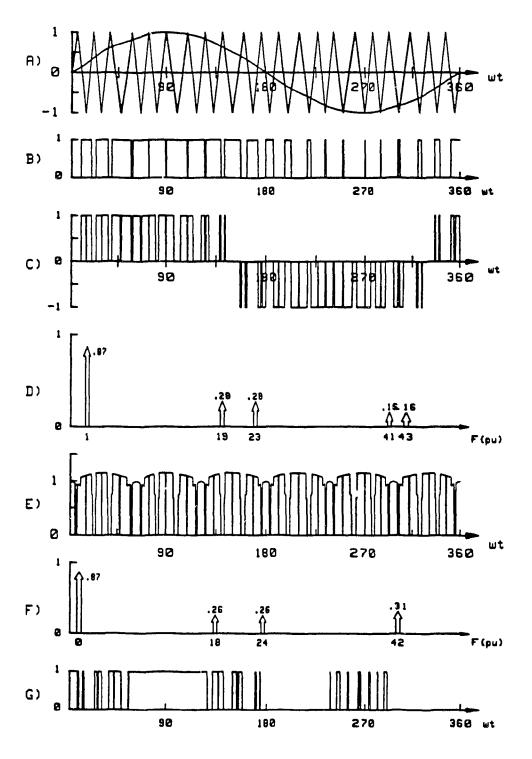

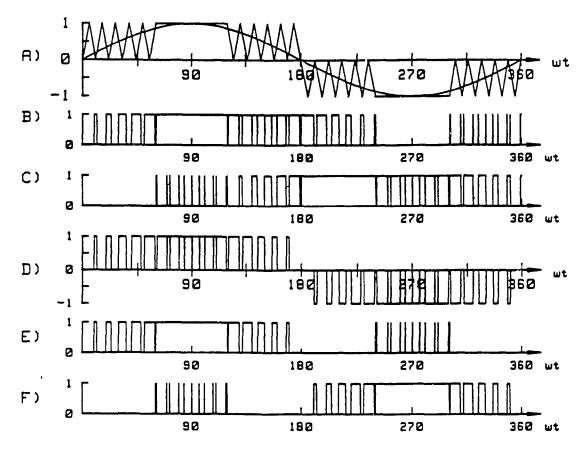

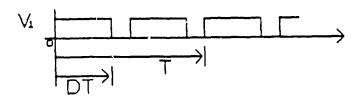

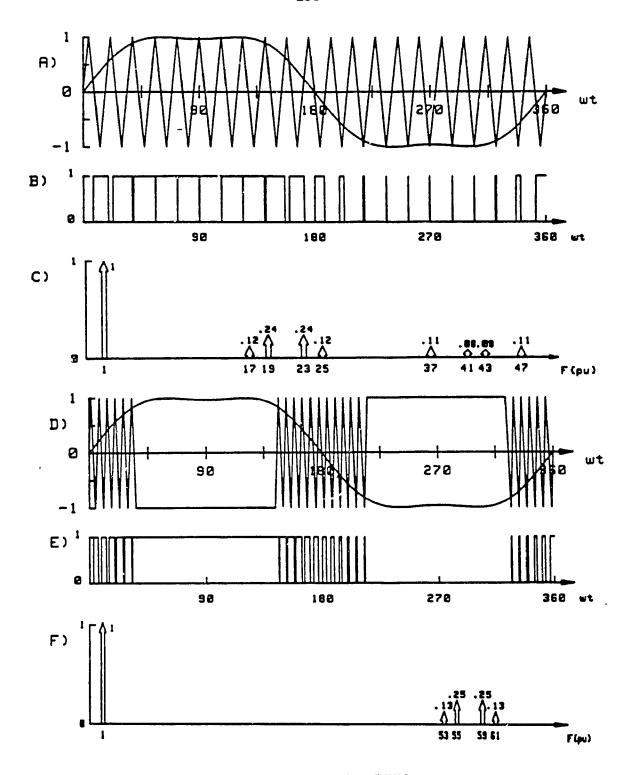

In power electronics, (PWM) is an operation performed on "raw" voltage and current waveforms to shape their spectra in a way beneficial to the application under consideration. Spectra shaping typically means the creation of a 'deadband' between wanted and unwanted spectral components to ease post PWM filtering requirements. For a given switching frequency it is desirable that the deadband be as wide as possible. To illustrate this point figures F2.6A,B,D and E show a typical inverter line to line output voltage before and after it has been pulse width modulated. Figure F2.6C and F show the resulting line current waveforms obtained with a load power factor of .8 lagging. In particular, figure F2.6F shows that PWM allows static inverters to generate close to ideal output waveforms while providing variable voltage and variable frequency operation. In addition to the importance of spectral shaping, the

main advantage of PWM is that it allows linear amplitude control of the output voltages/currents by varying a linear signal.

Further investigation of the results shown in figure F2.6 also reveals that PWM has several disadvantages, which include:

- 1-Attenuation of the wanted fundamental component, in this case from 1.1pu to .866pu.

- 2-Drastically increased switching frequencies (in this case from 1pu to 21pu). This means greater stresses on the associated switching devices and therefore derating of those devices.

- 3-Generation of high frequency harmonic components not previously present.

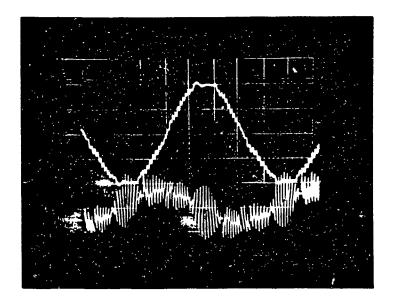

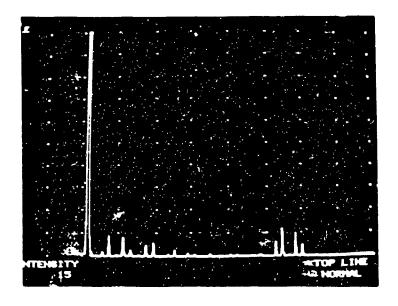

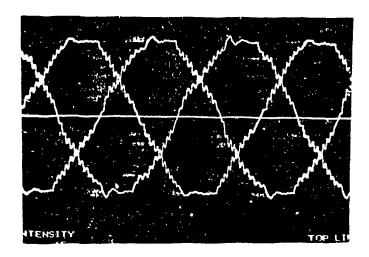

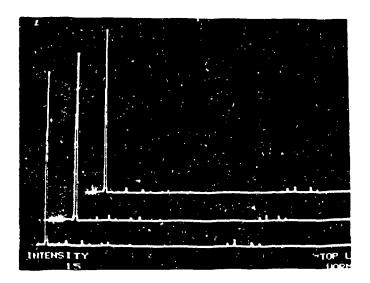

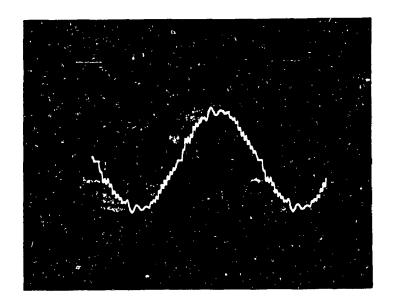

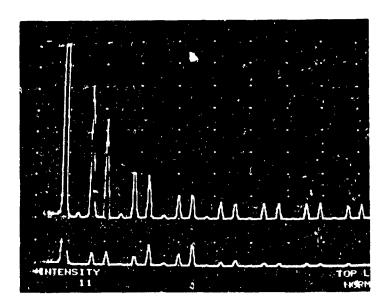

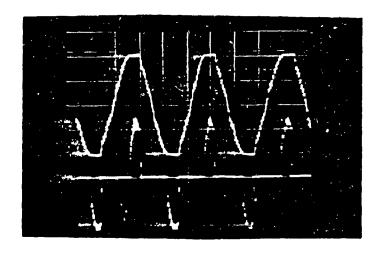

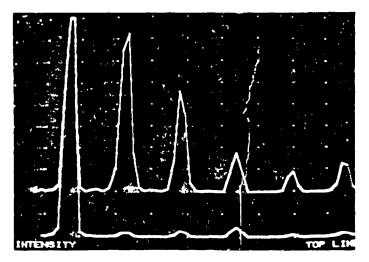

Figure F2.6 Inverter voltage and current waveforms with six step and sinusoidal (SPWM) operation.

A) Square wave output line to line voltage

B) Line to line voltage spectrum (square wave)

- C) Output line current (square wave)

- D) SPWM output line to line voltage

- E) Line to line voltage spectrum (SPWM)

- F) Output line current (SPWM)

Since the advantages of PWM outweigh the respective disadvantages, a considerable research effort has gone into minimizing the PWM disadvantages mentioned earlier. As a result numerous PWM schemes have been introduced over the past decade offering specific advantages in specific applications. Since dramatic UPS improvements can be obtained with PWM it is imperative to select the appropriate technique for both the controlled rectifier stage and the inverter stage. To date only a handful of techniques have proven to be widely used and are so called 'improved' PWM techniques [25],[26],[27],[28],[29]. However, previous work related to these improved techniques has been focused on converter output spectra neglecting other important criteria such as input spectra, input/output distortion factor, switching frequencies and hardware implementation considerations. Furthermore, another focus of previous work has been inverter applications neglecting in the process some other equally important areas such as controlled rectifiers. Consequently a clearer picture should be developed before selecting a PWM technique for UPS avoiding less than optimum results.

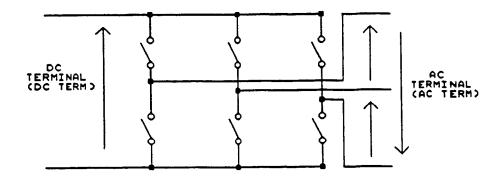

Since there are several PWM techniques and two types of converters involved in this evaluation, care must be taken to present relevant results with clarity. For this purpose, a generalized bridge converter (figure F2.7 comprised of six ideal four quadrant switches has been employed. The main advantage of this converter is that because of the nature of its switches it can function either as an inverter (voltage or current sourced) or as a rectifier by simply applying the proper gating signals. The generalized convertor thus permits the ac terminal waveforms (AC TERM) to represent either;

A) The line to line voltage of a voltage source inverter(VSI),

- B) The input line current of a controlled rectifier(CR), and the dc terminal waveforms (DC TERM) to represent;

- A) The input current of a VSI,

- B) The output voltage of a CR.

Also in the evaluation that follows, the switching frequency of the bridge is kept constant to provide a common basis for comparison of each technique under rectifying and inverting operation.

Figure F2.7 Generalized bridge configuration

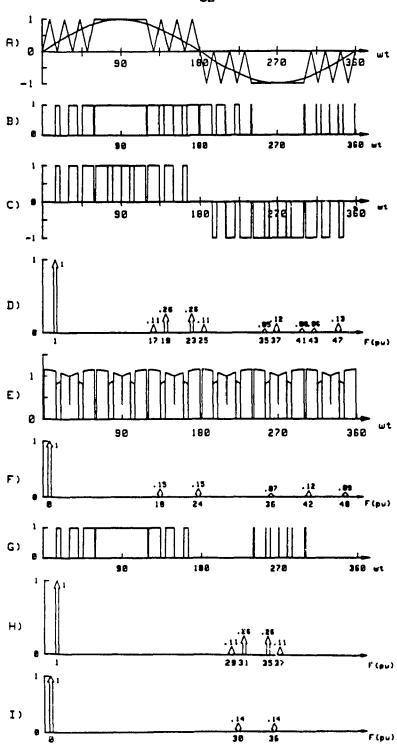

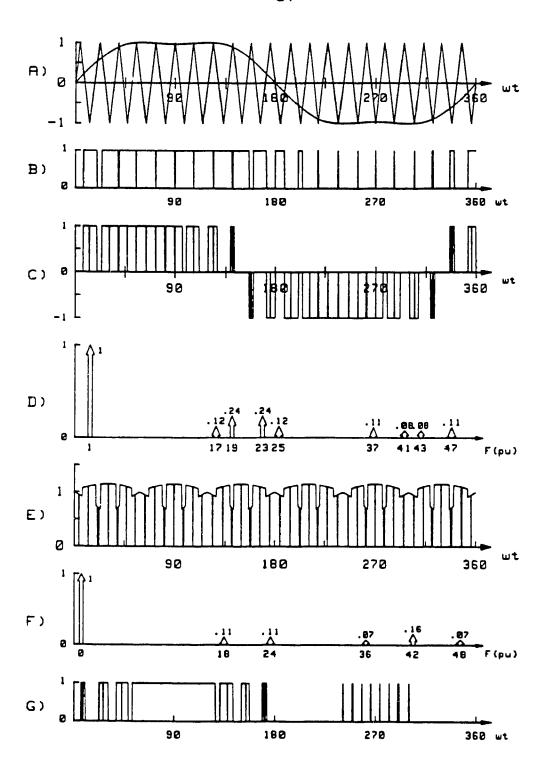

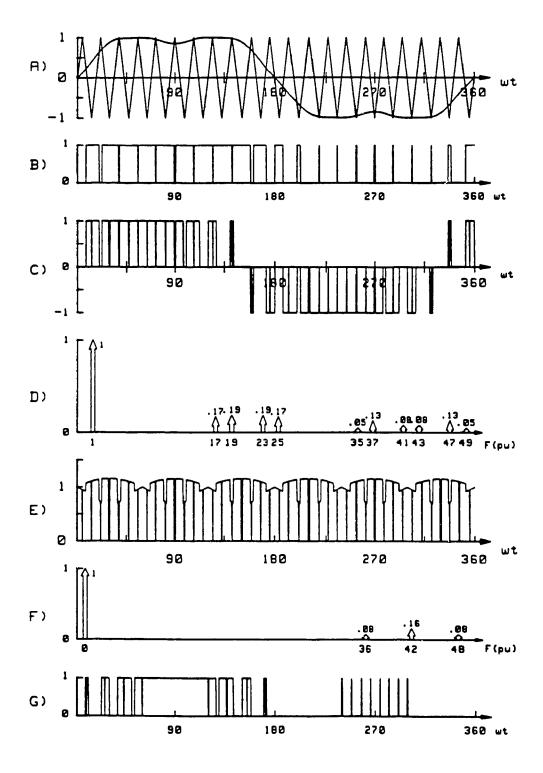

# 2.4.1 Carrier PWM Techniques

Carrier PWM techniques represent any firing pattern whose angles are derived by the intersection of two waveforms namely the carrier and reference.