National Library of Canada

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395 rue Wellington Ottawa (Ontario) K1A 0N4

Your tile A otto reterence

Our file. Notic reference

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# Performance Analysis and Design of Optimized Static Random Access Memory (SRAM)

Dewan Jahangir

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at

Concordia University

Montreal, Quebec, Canada

June 1992

© Dewan J., 1992

National Library of Canada

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file. Votte reference

Our file. None référence

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence et non exclusive irrévocable Bibliothèque permettant à la nationale du Canada reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette à la disposition personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-80997-3

#### Abstract

## Performance Analysis and Design of Optimized Static Random Access Memory (SRAM)

#### Dewan Jahangir

High speed, low power & area, and reliability are important design goals in high-performance Static RAM. The SRAM design varies in multi-dimensions (block, row, column) and type of implementation of other peripheral circuits. Therefore, in general, the performance analysis of the whole structure is particularly difficult. A more comprehensive model rather than the general RC delay model is required in order to achieve realistic designs.

In this thesis, a new Precharge circuit called Power Down Y-controlled PMOS (PDYCP) load precharge circuit is designed. Our PDYCP precharge circuit reduces power consumption by a factor of three over that of a conventional Y-controlled load (YCL). A design methodology of SRAM with an analytical model such as area, delay and power consumption suitable for module generator is developed. The performance of the SRAM is analyzed using Elmore's delay model which is confirmed with SPICE results. An optimized design of SRAM using Khun-Tucker optimization criteria is presented. Furthermore, a design aid tool for optimized design of SRAM is developed which is written in 'C'. Some optimization results are tabulated under various array sizes and load conditions.

#### Acknowledgments

I would like to express my sincerest gratitude to my thesis supervisors, Dr. A.J. Al-Khalili and Dr. B. Haroun, for their constant encouragement and knowledgeable guidance during the course of this work. They have always been available to direct and advise whenever the occasion arose. It was a really enjoyable experience working with people who are so enthusiastic and insightful. Their constructive criticisms and keen ability to pinpoint important issues and weaknesses have been a major part in the shaping of this thesis.

I would like to acknowledge the United Nations Educational Scientific & Cultural Organization (UNESCO), Paris and the United Nations Development Project (UNDP), Dhaka, Bangladesh for their Fellowship Award to me in the period from May 1989 to December 1991. Also, I would like to thank the Bangladesh Institute of Technology (BIT), Dhaka for granting me a study leave and thereby enabling me an opportunity to pursue higher studies.

I would also like to acknowledge the VLSI lab personnels Mr. G. Patel and Mr. D. Hargreaves for their great contribution & commitment to the lab which made a really pleasant environment for work.

Finally, I wish to express my deepest appreciation to my family for their patience and moral support. Without their generous support and encouragement this work would not have been possible.

Dedicated to my Family and Friends

## Table of Contents

| 1 | Int | rodu   | ction to SRAM Design: An overview                     | 1  |

|---|-----|--------|-------------------------------------------------------|----|

|   | 1.0 | Introd | uction                                                | 1  |

|   | 1.1 | Motiv  | ation                                                 | 1  |

|   | 1.2 | Organ  | ization of the Thesis                                 | 3  |

|   | 1.3 | Basic  | SRAM Architecture                                     | 4  |

|   | 1.4 | Static | Random Access Memory (SRAM) cells                     | 6  |

|   |     | 1.4.1  | Organization and Operation of a SRAM                  | 8  |

|   |     | 1.4.2  | A 6T SRAM Cell Design                                 | 14 |

|   | 1.5 | Decoc  | fing Scheme                                           | 19 |

|   |     | 1.5.1  | Dynamic Double-word line (DDWL) structure             | 19 |

|   |     | 1.5.2  | Divided Word-line (DWL) structure                     | 22 |

|   | 1.6 | Circui | it techniques for Decoder                             | 24 |

|   |     | 1.6.1  | PMOS-Load Decoder                                     | 24 |

|   |     | 1.6.2  | Transfer Word Drive (TWD) Decoder                     | 28 |

|   | 1.7 | Prech  | arge Scheme                                           | 27 |

|   |     | 1.7.1  | Different Precharge Techniques                        | 30 |

|   |     | 1.7.2  | Power Down Y-Controlled PMOS (PDYCP) Load bit line    |    |

|   |     |        | Precharge Technique                                   | 35 |

|   | 1.8 | Sensu  | ng Scheme                                             | 40 |

|   |     | 1.8.1  | Operation of a Current- Mirror Sense Amplifier (CMSA) | 40 |

|   |     | 1.8.2  | Various SA Circuit Techniques                         | 42 |

|   |     | 183    | Hierarchical Sonse Applifier Architecture             | 45 |

| 2 | Modeling and Analysis of SRAM |                                                           | 49 |

|---|-------------------------------|-----------------------------------------------------------|----|

|   | 2.0                           | Introduction                                              | 49 |

|   | 2.1                           | Capacitance Model of Word and Bit Line                    | 49 |

|   |                               | 2.1.1 Word Line Capacitance Model                         | 49 |

|   |                               | 2.1.2 Word line driver I/O Capacitance                    | 51 |

|   |                               | 2.1.3 Bit line Capacitance                                | 53 |

|   | 2.2                           | Word line Delay Analysis                                  | 54 |

|   |                               | 2.2.1 Word line delay modeling using Elmore's Delay Model | 54 |

|   |                               | 2.2.2 Approximate form of Word line                       | 57 |

|   | 2.3                           | Precharge Delay Analysis                                  | 62 |

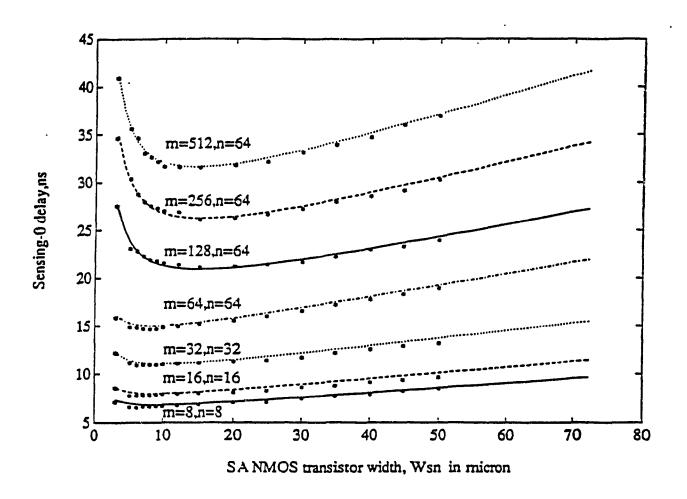

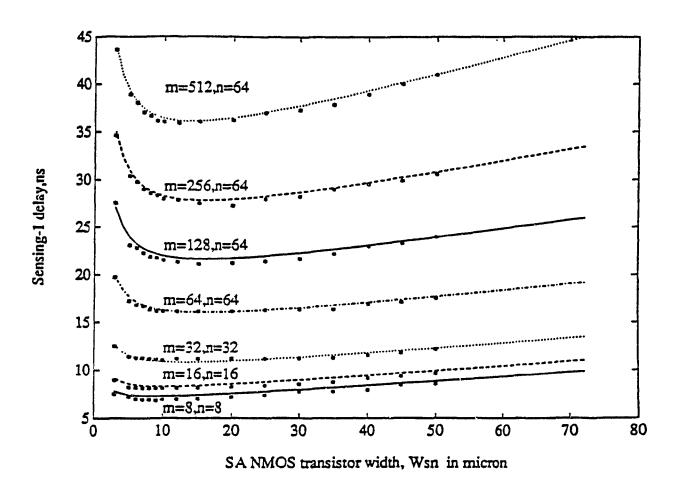

|   | 2.4                           | Sensing Delay                                             | 68 |

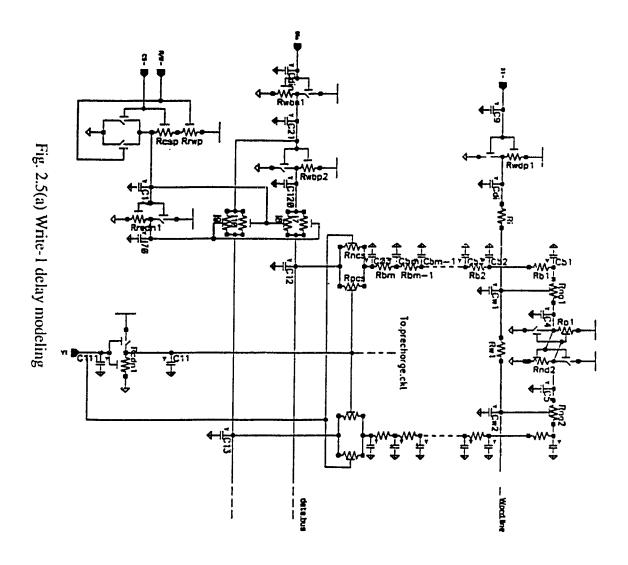

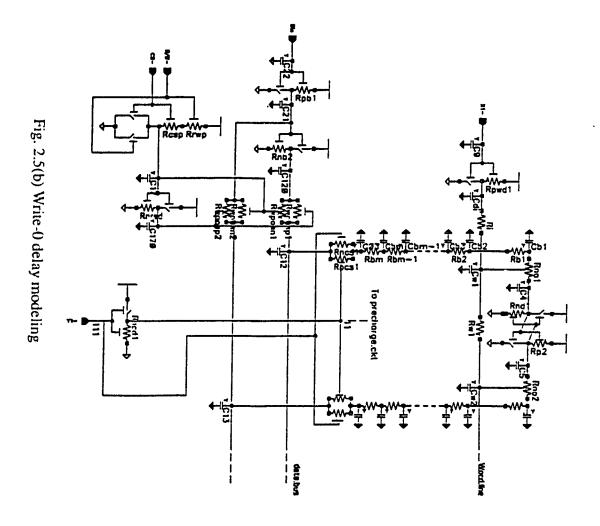

|   | 2.5                           | Write Access Delay                                        | 76 |

|   |                               |                                                           |    |

| 3 | Ar                            | ea Model of SRAM                                          | 82 |

|   | 3.()                          | SRAM Area                                                 | 82 |

|   | 3.1                           | SRAM cell Area                                            | 83 |

|   | 3.2                           | Decoder Area                                              | 86 |

|   | 3.3                           | Sense Amplifier Area                                      | 86 |

|   | 3.4                           | Precharge circuit Area                                    | 87 |

|   | 3.5                           | Column select T-gate Area                                 | 88 |

|   | 3.6                           | I/O peripheral Area                                       | 89 |

|   |                               |                                                           |    |

| 4 | Po                            | wer consumption in SRAM                                   | 92 |

|   | 4.0                           | Introduction                                              | 92 |

|   | 4.1                           | Standby power                                             | 92 |

|   | 4.2                           | Read power                                                | 92 |

|             | 4.3 Write power                                                      | 94  |

|-------------|----------------------------------------------------------------------|-----|

|             | 1.4 Standby Mode power dissipation                                   | 95  |

| 5           | SRAM Design Optimization                                             | 98  |

|             | i.1 Introduction                                                     | 98  |

|             | 5.2 Kuhn-Tucker Equations                                            | 98  |

|             | 5.3 Sizing and Optimization of Area, Delay and Power in Logic Blocks | 99  |

|             | 5.3.1 Optimum Sizing Algorithm of Transistors in a SRAM              | 101 |

|             | 5.4.1 Optimum Word Driver Design                                     | 103 |

|             | 5.4.2 Optimum Precharge Circuit Design                               | 107 |

|             | 5.4.3 Optimum Sense Amplifier Design                                 | 110 |

| 6           | Design and Layout Implementation of a SRAM                           | 114 |

| 6.0         | Example: Optimized SRAM Design                                       | 114 |

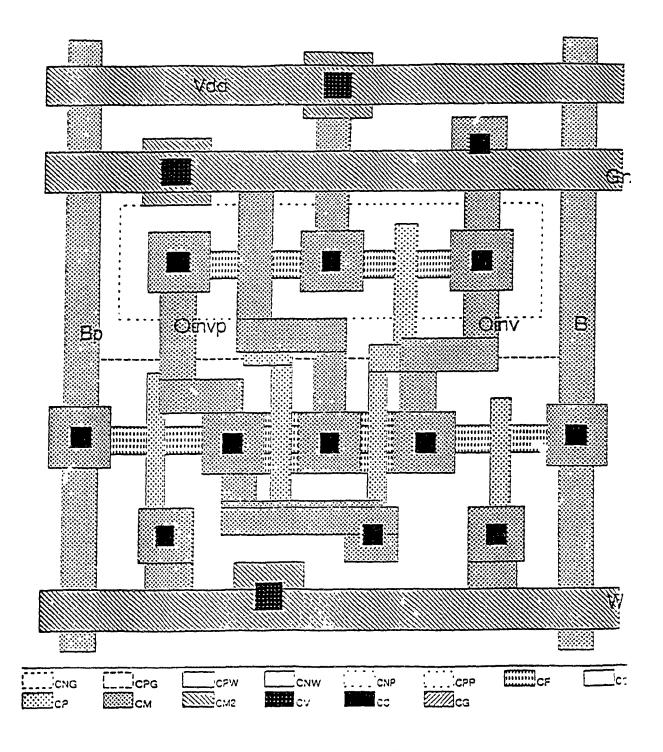

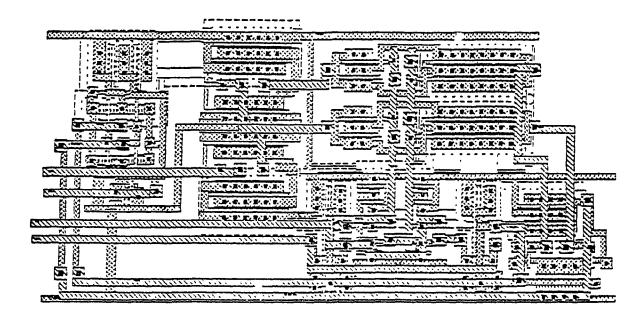

| 6.1         | Layout Implementation                                                | 118 |

| 7           | Conclusion                                                           | 133 |

|             | Appendix A SRAM Modeling                                             | 136 |

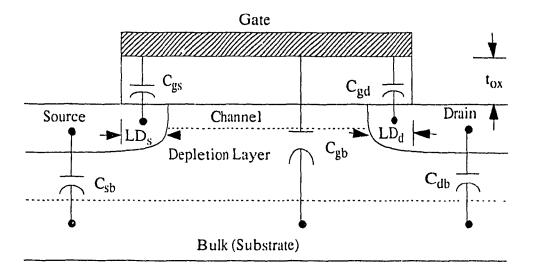

| <b>A.</b> 1 | Capacitance and Resistance calculation of a MOS Transistor           | 136 |

| A.2         | SRAM Node Capacitances                                               | 140 |

|             | Appendix B Optimized SRAM Design                                     | 141 |

| B 1.1       | Optimized Word Driver Design                                         | 141 |

| B1.2        | Optimized Precharge Circuit Design                                   | 142 |

| B.1.3       | Optimized Sense Amplifier Circuit Design                             | 143 |

| B,2         | Regression Results for SRAM Modeling                                 | 148 |

## List of Figures

| 1.1  | A typical SRAM Architecture                                        | 5  |

|------|--------------------------------------------------------------------|----|

| 1.2  | (a) A 4-transistor SRAM cell                                       | 7  |

| 1.2  | (b) A 6-transistor SRAM cell                                       | 7  |

| 1.3  | (a) Organization of a SRAM                                         | 9  |

| 1.3  | (b) SRAM with peripheral circuits                                  | 10 |

| 1.3  | (c) Read-0 operation of a SRAM                                     | 13 |

| 1.3  | (d)Write-1 operation of a SRAM                                     | 13 |

| 1.4  | (a) Graphical representation of Static Noise Margin                | 16 |

| 1.4  | (b) Stability margin as a function of r                            | 16 |

| 1.5  | (a) Dynamic Double-word line (DDWL) structure                      | 20 |

| 1.5  | Trade-off (b) Word line delay, (c) area and power as a function of |    |

|      | number of sections or blocks in a DDWL structure                   | 21 |

| 1.6  | (a) Conventional Divided-word line structure                       | 23 |

| 1.6  | (b) Hierarchical word decoding Architecture                        | 23 |

| 1.6  | (c) Comparison of DWL and HWD                                      | 23 |

| 1.7  | (a) PMOS load decoder and (b) Conventional CMOS decoder            | 25 |

| 1.7  | (c) 1-Mbit SRAM word decoding scheme                               | 25 |

| 1.7  | (d) Circuit schematic of word decoder using PMOS load              | 25 |

| 1.7  | (e) Delay time of two types of decoders                            | 27 |

| 1.7  | (f) Current of word decoder                                        | 27 |

| 1.7  | (g) Word-decoder circuit (for four memory subarray)                | 27 |

| 1.8  | (a) Transfer word drive decoder, (b) Conventional decoder          | 29 |

| 1.9  | (a) and (b) Continuous precharge circuits                          | 31 |

| 1.10 | (a) and (b) Controlled precharge circuits                          | 31 |

| 1 11 | Bit line load and ATD controlled precharge circuit                 | 32 |

| 1.12  | ATD controlled conventional precharge scheme                         | 32 |

|-------|----------------------------------------------------------------------|----|

| 1.13  | Y-controlled bit-line load (YCL) precharge circuit                   | 34 |

| 1.14  | Power Down Y-controlled PMOS (PDYCP) load precharge circuit          | 36 |

| 1.15  | SPICE simulation plots using PDYCP precharge technique               |    |

|       | for consecutive READ/WRITE operation                                 | 37 |

| 1.16  | (a) A CMOS Current Mirror Sense Amplifier (CMSA)                     | 41 |

| 1.16  | (b) Operation of a CMSA for a read-0                                 | 41 |

| 1.17  | (a) Conventional CMSA                                                | 43 |

| 1.17  | (b) Input controlled PMOS-load (ICPL) sense amplifier                | 43 |

| 1.18  | Dynamic Gain Control Double end Amplifier                            | 44 |

| 1.19  | Modified two stage CMSA                                              | 44 |

| 1.20  | Double line sensing structure                                        | 46 |

| 1.21  | (a) Sense Amplifier Circuit for fig. 1.21 (b)                        | 47 |

| 1.21  | (b) Two-stage local amplification and triple-sense-line structure    | 47 |

| 1.22  | Four-stage Sensing Scheme                                            | 48 |

| 2.1.1 | Word line Capacitance Modeling                                       | 50 |

| 2.1.2 | Word driver I/O Capacitance Modeling                                 | 51 |

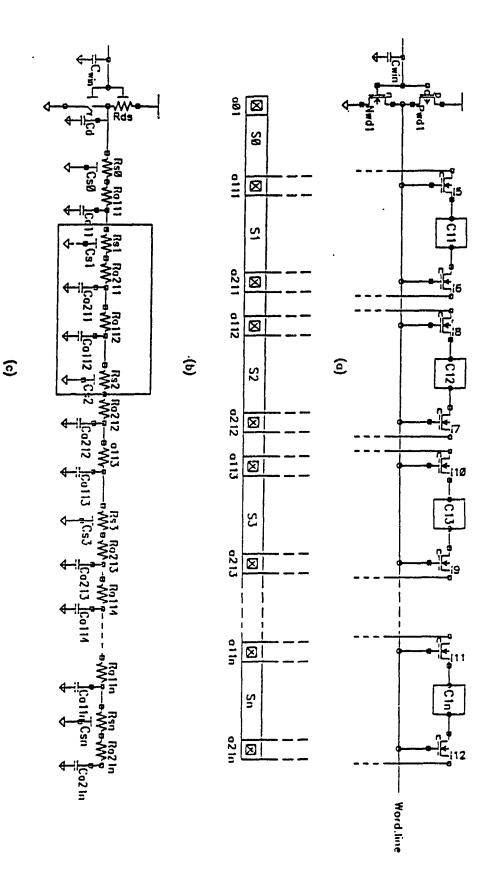

| 2.2.1 | (a) Word driver driving a row of a SRAM, (b) Physical representation |    |

|       | of an word line, (c) R, C delay model of a Word line                 | 55 |

| 2.2.2 | (a) $\pi$ - approximate model of a word line in a cell segment,      |    |

|       | (b) Approximate π- R C model of a word line                          | 58 |

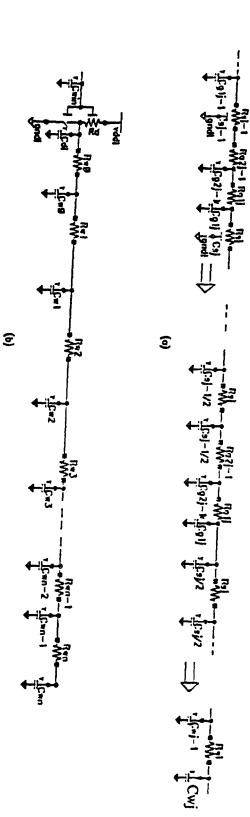

| 2 2 2 | (c) Comparison of analytical and SPICE simulation results            |    |

|       | for different word sizes                                             | 61 |

| 2.3   | (a) Precharge delay modeling                                         | 63 |

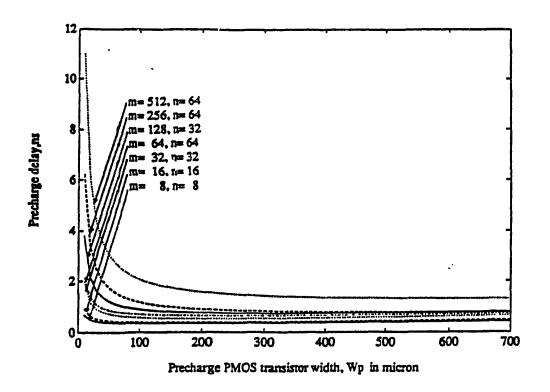

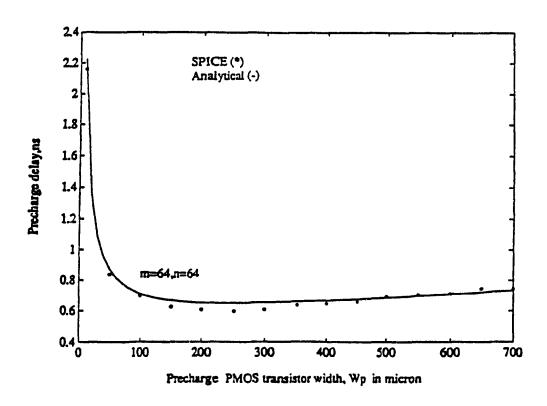

| 2.3   | (c) Precharge Delay Analytical results                               | 67 |

| 2.3   | (d) Comparison of analytical and SPICE simulation results            |    |

|       | for precharge delay                                                  | 67 |

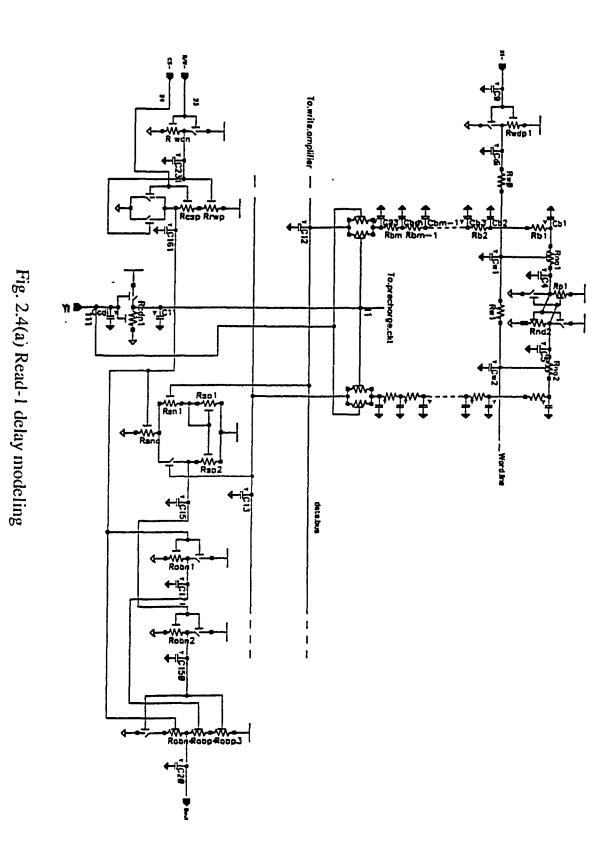

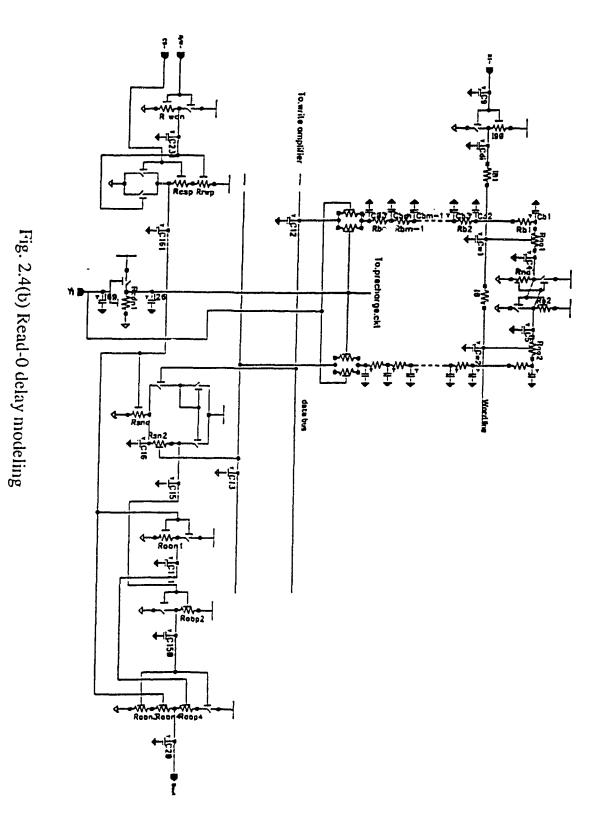

| 2.4  | (a) Read-1 delay modeling                                                     | 69  |

|------|-------------------------------------------------------------------------------|-----|

| 2.4  | (b) Read-0 delay modeling                                                     | 70  |

| 2.4  | (c) Read-0: Comparison of analytical and SPICE simulation results             | 74  |

| 2.4  | (d) Read-1: Comparison of analytical and SPICE simulation results             | 75  |

| 2.5  | (a) Write-1 delay modeling                                                    | 77  |

| 2.5  | (b) Write-0 delay modeling                                                    | 78  |

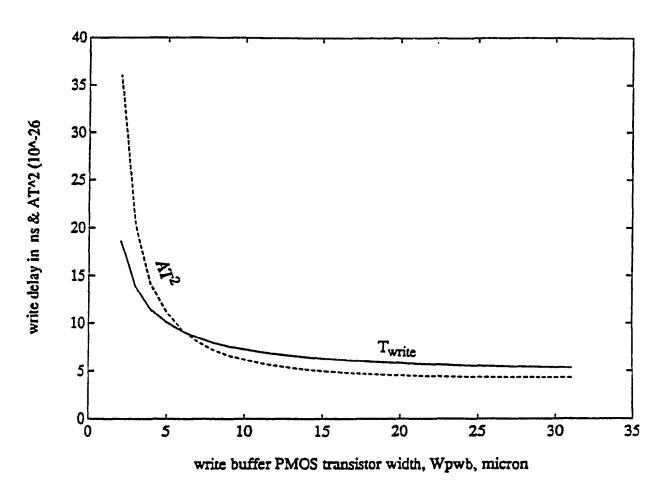

| 2.5  | (c) Write-1 access delay & AT <sup>2</sup> as a function of write buffer size | 81  |

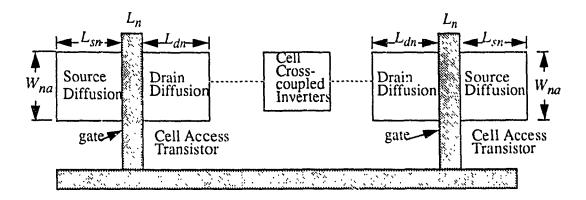

| 3.1  | (a) Top view of a SRAM cell access transistors                                | 84  |

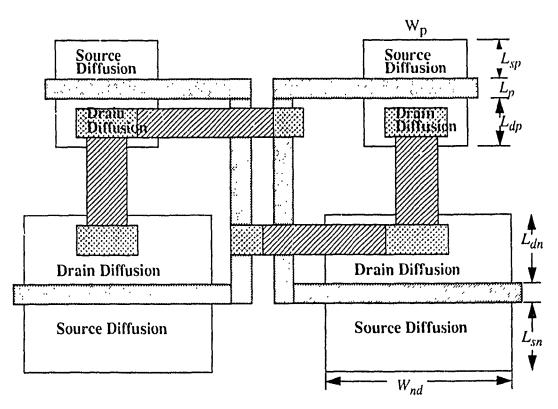

| 3.1  | (b) Top view of a cross-coupled inverter in a SRAM cell                       | 84  |

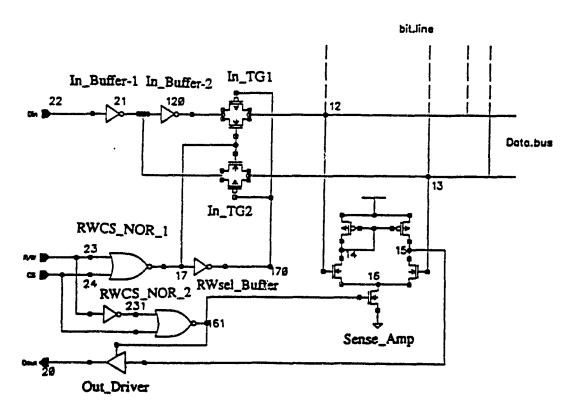

| 3.6  | I/O Peripheral circuits of a SRAM                                             | 91  |

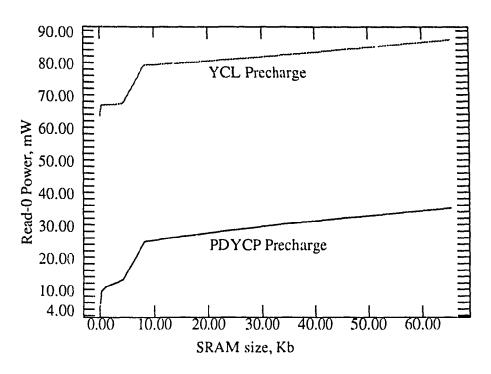

| 4.   | (a) SPICE Comparison of Read Power dissipation                                |     |

|      | using PDYCP and YCL Precharge circuit                                         | 96  |

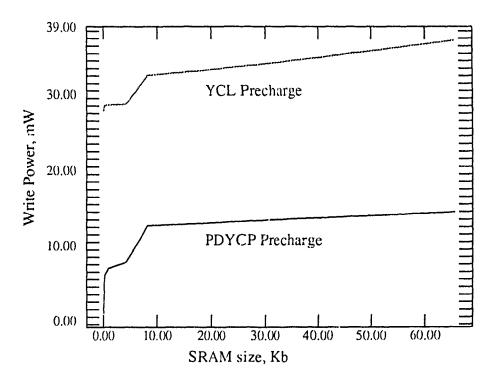

| 4.   | (b) SPICE Comparison of Write Power dissipation                               |     |

|      | using PDYCP and YCL Precharge circuit                                         | 96  |

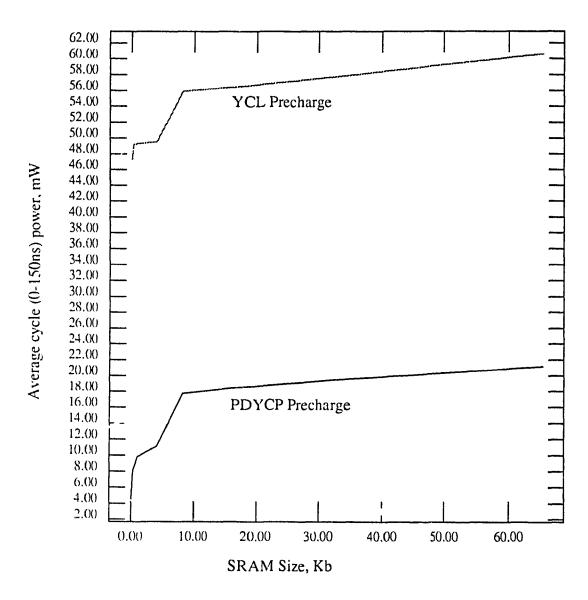

| 4.   | (c) SPICE Comparison of average cycle Power                                   | 97  |

| 6.1  | Layout of a SRAM cell                                                         | 121 |

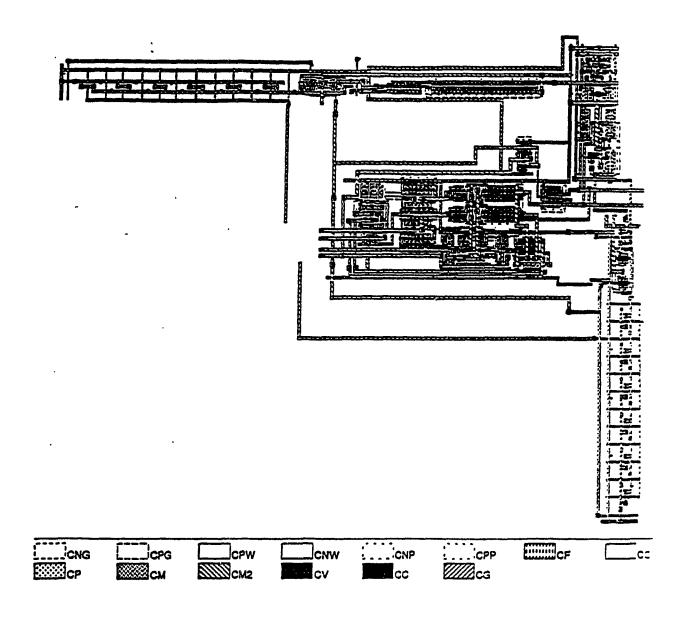

| 6.2  | (a) Test circuit of a SRAM cell (includes cell, decoder & peripherals)        | 122 |

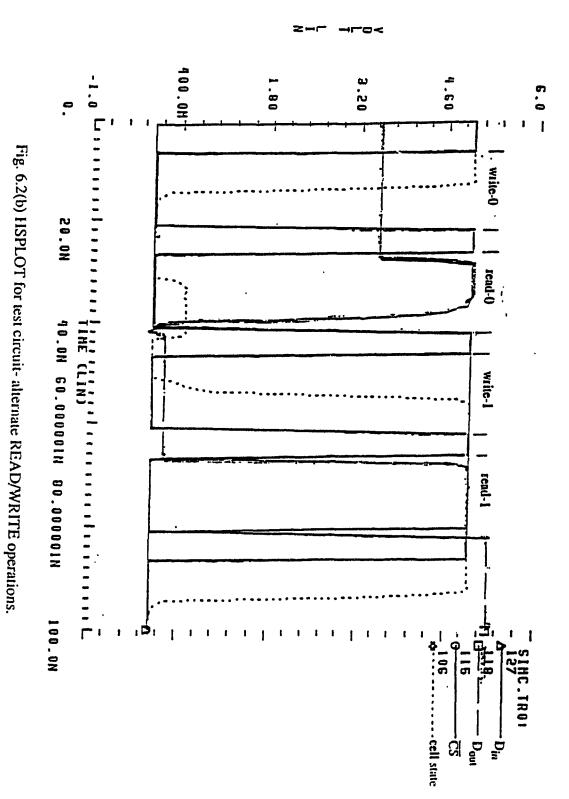

| 6.2  | (b) HSPLOT for test circuit- alternate READ/WRITE operations                  | 123 |

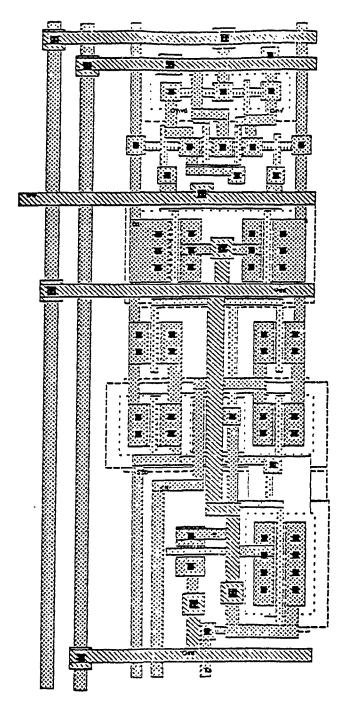

| 6.3  | A SRAM cell with precharge and column select circuit layout                   | 124 |

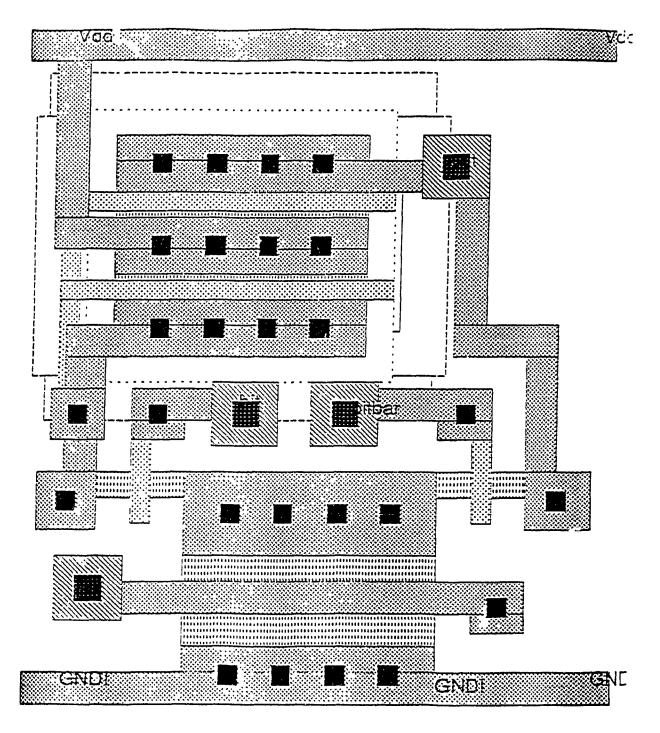

| 6.4  | A Current Mirror Sense Amplifier (CMSA) layout                                | 125 |

| 6.5  | I/O peripheral circuit layout of a SRAM layout                                | 126 |

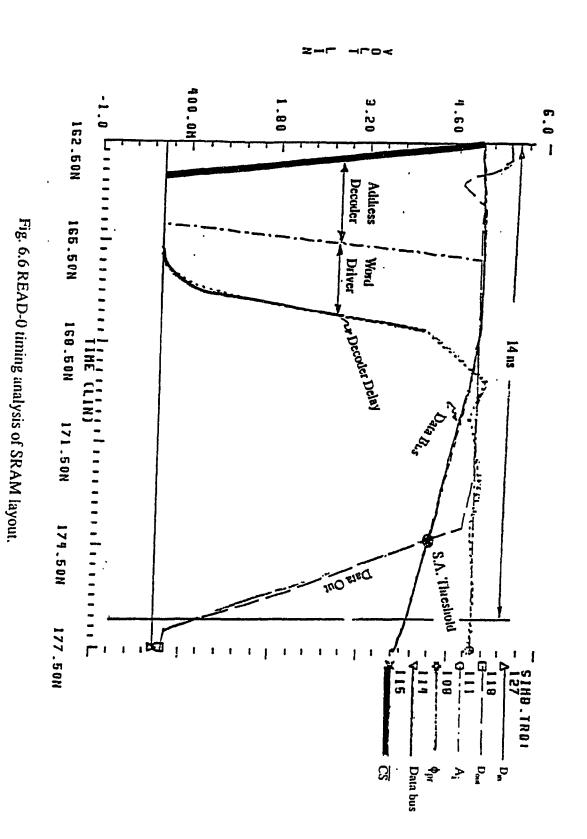

| 6.6  | A READ-0 timing analysis of SRAM layout                                       | 127 |

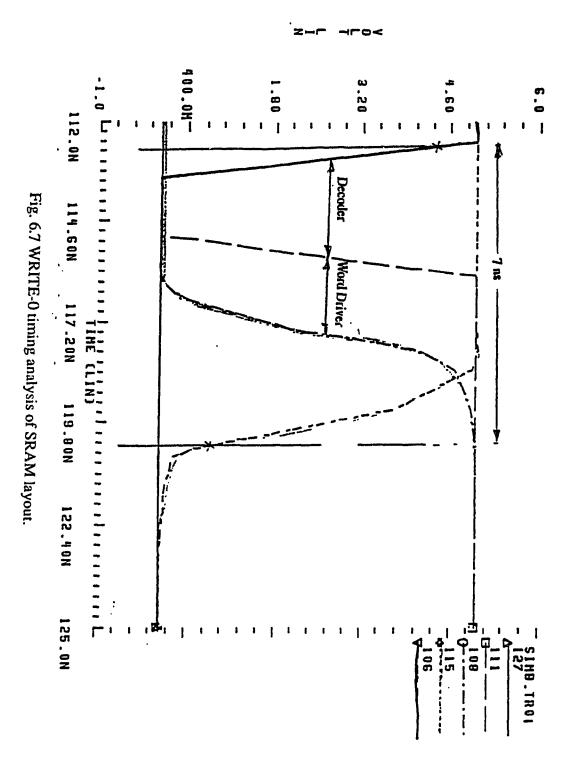

| 6.7  | WRITE-0 timing analysis of SRAM layout                                        | 128 |

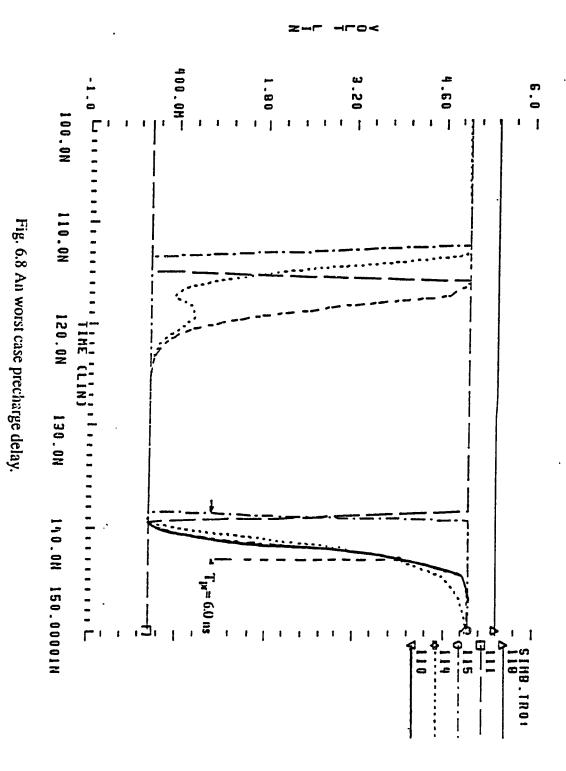

| 6.8  | An worst case precharge delay                                                 | 129 |

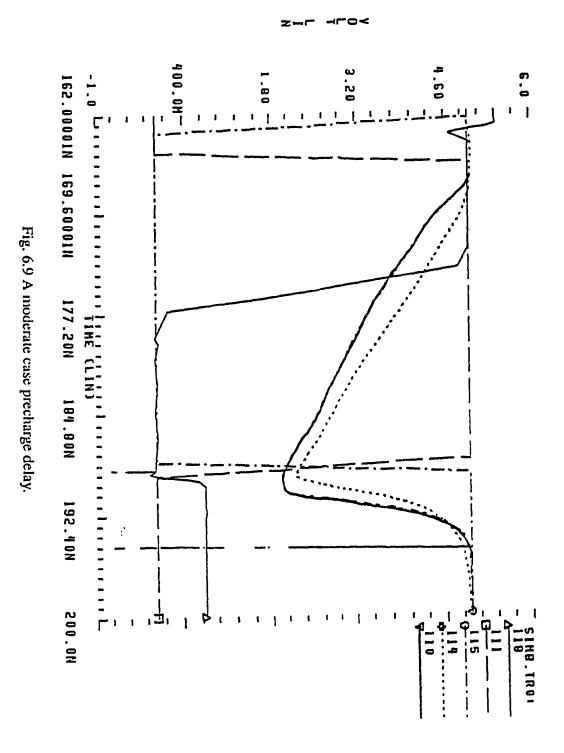

| 6.9  | A moderate case precharge delay                                               | 130 |

| 6.10 | A WRITE-1 timing analysis of the layout                                       | 131 |

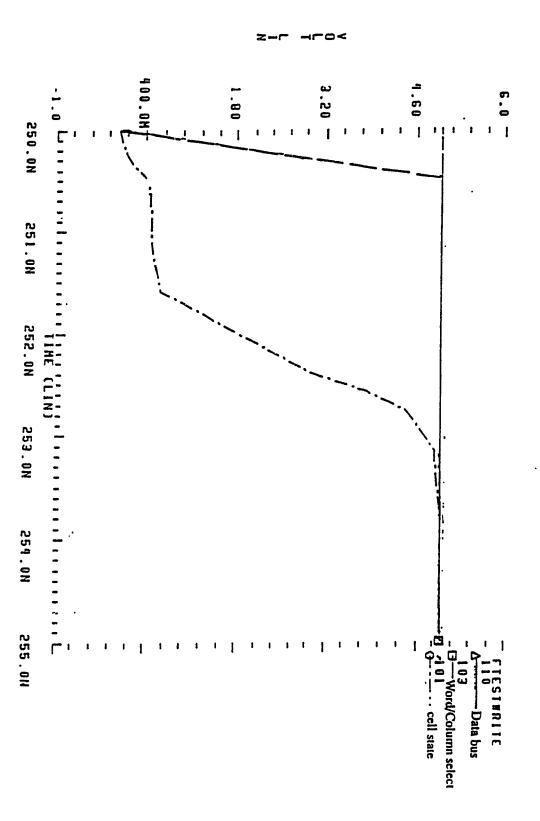

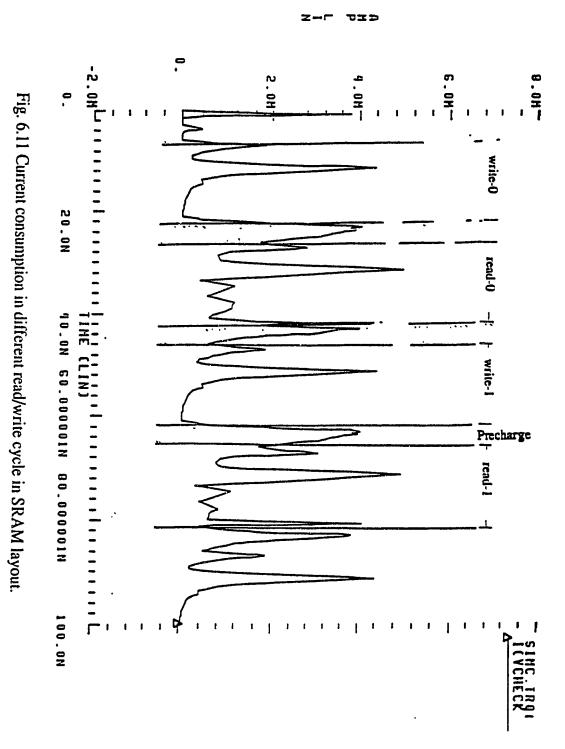

| 6.11 | Current consumption in different read/write cycles in SRAM layout             | 132 |

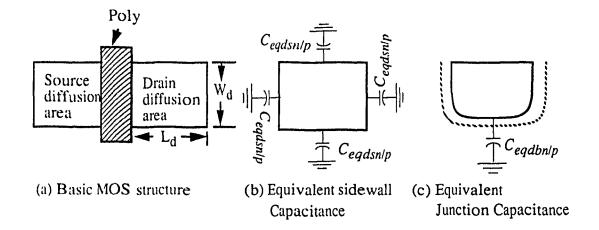

| A. 1.1 | Parasitic Capacitance of a MOS Transistor               | 136 |

|--------|---------------------------------------------------------|-----|

| Λ. 1.2 | Area and peripheral components of diffusion capacitance | 137 |

|        |                                                         |     |

|        |                                                         |     |

| List   | of Tables                                               |     |

|        |                                                         |     |

| 1      | Comparison of PDYCP & YCL precharge performance         | 39  |

| 2      | Example of Optimized design of a word driver            |     |

|        | under variable load conditions                          | 106 |

| 3      | Example of Optimized design of a precharge circuit      |     |

|        | under variable load conditions                          | 109 |

| 4      | Example of Optimized design of a sense amplifier        |     |

|        | under variable load conditions                          | 112 |

| B.1    | Word delay fit constants                                | 148 |

| B.2    | Precharge delay fit constants                           | 149 |

| B.3    | Sensing delay fit constants                             | 149 |

## Chapter 1

### INTRODUCTION TO

SRAM DESIGN: An overview

#### 1.0 Introduction

Memories are devices which can store information. There are two kinds of memory in general, such as volatile (data is erased when power is turned off) and non-volatile (retains data even if power is turned off). Semiconductor RAMs are volatile. Semiconductor RAMs are of two types: static (SRAM) and dynamic (DRAM). The SRAM capacity has quadrupled every two or three years in circuit and process technology[7]. The fastest access speed reported is 15ns with 4-Mb CMOS SRAM [1]. In SRAM, information is stored in the static structure of a cross-coupled inverter (latch-storage), while in DRAM information is stored in a capacitor. SRAM does not need to be refreshed but DRAM must be refreshed in a regular interval otherwise data will be corrupted. The advantages of a SRAM over a DRAM are its high speed, low power dissipation and high reliability. SRAMs are used in high speed applications such as in main and cache memory for computers, or test pattern memory in VLSI testing applications. They are also used for low power applications for holding data with battery backup in portable computers, memory cards and data terminals.

#### 1.1 Motivation

Optimization in SRAM design is essential in many applications such as Embedded RAM, Cache Memory, Module Generators where the designer has to match the specific design goal. The optimization problem is related to the design requirements, circuit topology and modeling technique. Area, delay and power consumption are three

imperative factors for performance trade-off in VLSI. Accurate modeling of the signal path delays in the circuit is important for high performance integrated circuit design. Although a device level simulator like SPICE can provide detailed and accurate delay information and optimization for small circuits, the analysis becomes more complicated and the computation time increases rapidly for large circuits specially for SRAM. Therefore, analytical delay model is required in general to solve the optimization problem in SRAM.

There have been two methods of general delay models, macromodeling [27] and transistor level models using RC tree modeling [18]. In macromodeling the whole circuit is partitioned into different sub-circuits instead of individual devices. The use of macromodeling is limited to circuits with regular logic gates (i.e. NAND's, NOR's, XOR's, etc.). The RC tree delay model is most successfully used for circuits with arbitrary resistances and capacitances. In the RC approach, a nonlinear MOSFET is modeled in terms of linear RC element. In general, the RC delay model suffers from accuracy and deviates far from SPICE simulation results. Inaccuracies in RC delay model results from neglecting the nonlinearities of the MOS transistors and from difficulties in including input waveform effects [26]. The solution to these problems can be offered by incorporating fit constants and including the effect of ramp input into the model.

Developing an efficient analytical model and goal directed optimization algorithm for automatic generation of transistor sizes in SRAM with low computational complexity is one of the aims of this thesis. As regards to computation time (for both man and machine) we decided to use RC tree delay model to develop a tool for optimized design of SRAM. As far as the accuracy of the model is concern we regression fitted our RC delay model with numerous SPICE simulation results for various SRAM array sizes and finally obtained a comprehensive RC delay model with fair agreement with SPICE. Moreover, we include in the model the analytical expression for the effect of ramp input to the signal delay. The maximum deviation of our model from SPICE simulation is 10 percent. The

important characteristics of our modeling and optimization tool are its accuracy, robustness and modularity.

#### 1.2 Organization of the Thesis

As stated earlier, the primary objective of this research is to develop a design aid tool for optimized design of SRAM to fulfill design criteria specially for embedded class of RAM. The circuits of interest for optimization are word driver, precharge and sense amplifier which has significant contribution on the access speed, overall chip area and power dissipation. However, the optimized design of other peripheral circuits are obtained from numerous SPICE simulation experience.

In chapter1, we investigated the design of SRAM cell and other peripheral circuits. Organization and operation of SRAM is briefly described. The design criteria for SRAM cell is also studied. Different types of decoding, precharge and sensing techniques are also depicted. We discussed our designed Power Down Y-controlled PMOS (PDYCP) load precharge circuit and also compared the performance using PDYCP and conventional Y-controlled load (YCL) precharge. The comparison reveals the excellent amount of power saving using PDYCP precharge.

Chapter 2 is devoted to modeling and analysis of SRAM using Elmore's RC delay modeling approach. The delay models specially for word, precharge, read and write are obtained. The RC delay models are regression fitted with numerous SPICE simulations and thus comprehensive delay models are obtained which confirms to SPICE simulation results with very little error (less than 10%). Comparison of our analytical models with SPICE for different SRAM array structure are depicted.

In chapter 3 we describe the area model of SRAM which is used by our optimization algorithm.

In chapter 4, power consumption in SRAM using PDYCP and YCL precharge are studied in terms of analysis and SPICE simulation. We compare power consumption using

both the precharge circuit techniques for any SRAM array size for read, write and standby time. Our results show that using PDYCP precharge technique power consumption in SRAM is reduced by a factor of three in comparison to YCL precharge.

Chapter 5 deals with optimization in SRAM design. We assume area is linearly related to power. Using the delay and area models in chapter 2 and 3 respectively we developed optimized design parameters for different circuits in SRAM. Since the unconstrained based optimization is insufficient to solve the optimization problem in general, we followed constrained based optimization. We used the well known Kuhn-Tucker optimization criteria to solve the problem. An algorithm for optimized design of SRAM is also discussed. Various results are tabulated using our approach which shows that with a little compromise in delay a significant amount of area can be saved.

Using our modeling and optimization formulas we developed a design aid tool for optimized design of SRAM. Chapter 6 presents a design example for a 4 k x1 bit (64x64) SRAM using our tool. We also present a layout for the 4 k x 1 bit SRAM using our results.

Finally, in chapter 7 we summarize our works in this thesis and identify future research problems that can be derived from this thesis.

#### 1.3 Basic SRAM Architecture

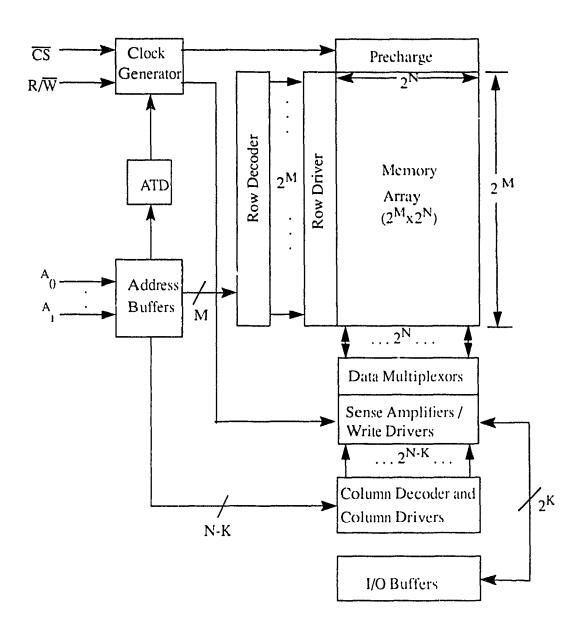

A typical SRAM architecture is illustrated in Fig. 1.1. The chip is organized with densely packed cell arrays in the form of a matrix. Each memory cell can store one bit of data. Around the cell array are the row decoder, column decoder, precharge circuit, data multiplexors, read/write circuits, control circuit and I/O buffers. The memory array consists of  $2^{M}x2^{N}$  bits of storage, where M and N are the number of address bits. The purpose of row and column decoders is to determine which cell to address for read/write. The row decoder addresses one row (word) of  $2^{N}$  bits out of  $2^{M}$  words. The column decoder addresses  $2^{K}$  of  $2^{N}$  bits of the accessed row, where K is the number of output bits. The purpose of a precharge circuit is to precharge bit lines and the data bus and thereby improve

Fig. 1.1 A typical SRAM Architecture

the cell stability and expedite the read operation. The data multiplexors or column selectors select the column of the cell that is being addressed for read/write. The sense amplifiers are used to speed up the access (read) time of the memory. The clock generator generates the internal timing control signals for the precharge circuit and the sense amplifier. The address transition detection (ATD) technique is used to enhance the control of the chip. The ATD pulse generator triggers the clock generator to provide internal synchronization. The function of the I/O drivers is to buffer the data to or from the external world.

In Fig. 1.1 we assumed a single block SRAM. However, in a chip there may be single or multiple blocks of cell arrays with other peripherals. The total number of blocks in a chip depends on the word size, total memory capacity, performance measure (access speed, power consumption) and layout issues. A number of different architectures and floor plans can be found in the literature (see for instance, [1-12, 28-30]).

#### 1.4 Static Random Access Memory (SRAM) cells

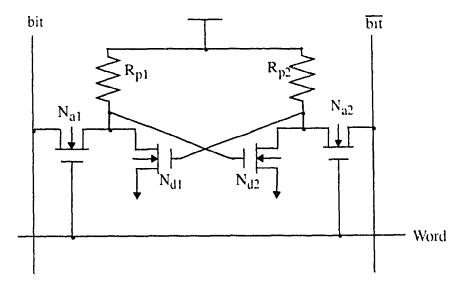

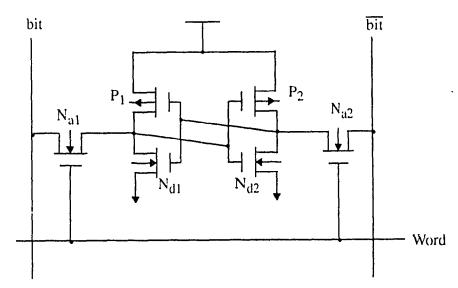

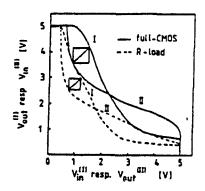

A SRAM cell in general may be of a four-transistor (4T) or a six-transistor (6T or full CMOS) type as shown in figure 1.2.(a) & 1.2.(b) respectively. The selection of any of the 4T or 6T configurations mainly depends upon two aspects such as, cell area and stability of the cell. Those two aspects are inter-related, to ensure the stability of the cell it is required to increase area. The total cell area in a SRAM occupies at least 50% of the overall chip area. The cell stability determines the Soft-error Rate[15] for the case of R-load cell and Static-Noise Margin.

The 4T (R-load) cells are used in some high density SRAM design. As in Fig. 1.2(a) the pull-up resistance is made with a special process requiring low area. But as reported in [9, 13] the Static-Noise Margin (SNM) of the R-load cell becomes much lower than the full CMOS one at low supply voltage. So, to have sufficient noise margin the R-load cell has to be made larger. Also, for a high density SRAM the resistance of the cell R-load must increase in order to maintain a constant SRAM standby current. As a result, it becomes

Fig. 1.2(a) A 4-transistor SRAM cell

Fig. 1.2(b) A 6-transistor SRAM cell

more and more difficult for a R-load cell to retain cell data. This is because the resistance of the R-load becomes so high that the R-load can not supply enough current to hold the high-level voltage of the memory cell node.

Comparatively, the 6T cell is more robust and stable because of the presence of a PMOS load transistor which supplies sufficient leakage current to hold a stable cell state. The following are the advantages of a 6T SRAM over a 4T SRAM:

- 1. Higher noise margin.

- Excellent data retention capability because of the active pull-up PMOS transistors.

- 3. No D.C. path exists in the cell, thus very low standby current can be obtained.

- 4. Since the cell stability can be achieved easily, the speed optimization can be achieved by increasing access transistor width.

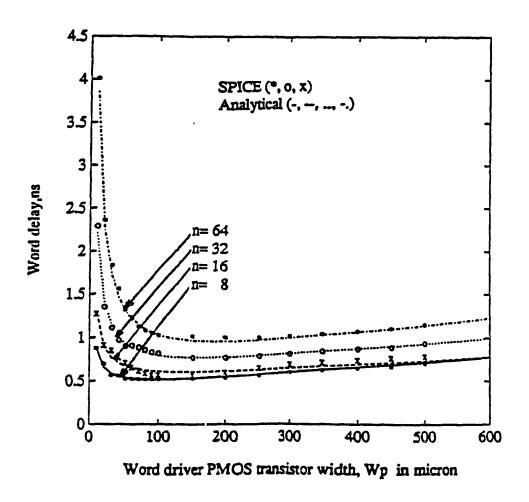

#### 1.4.1 Organization and Operation of a SRAM

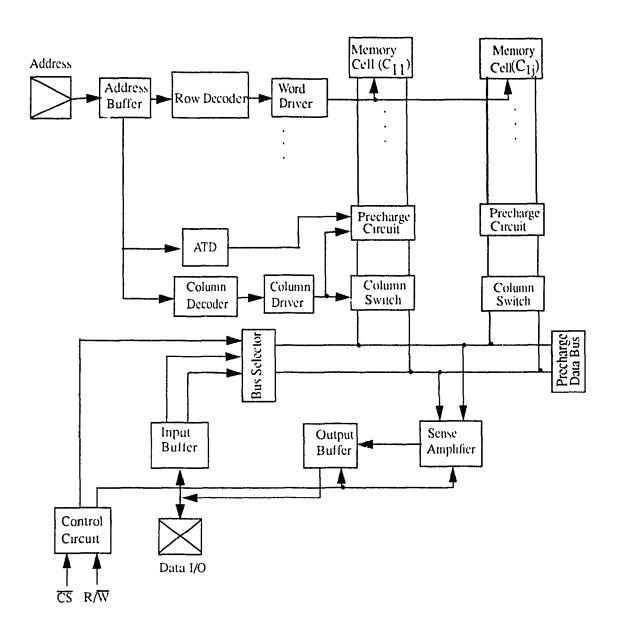

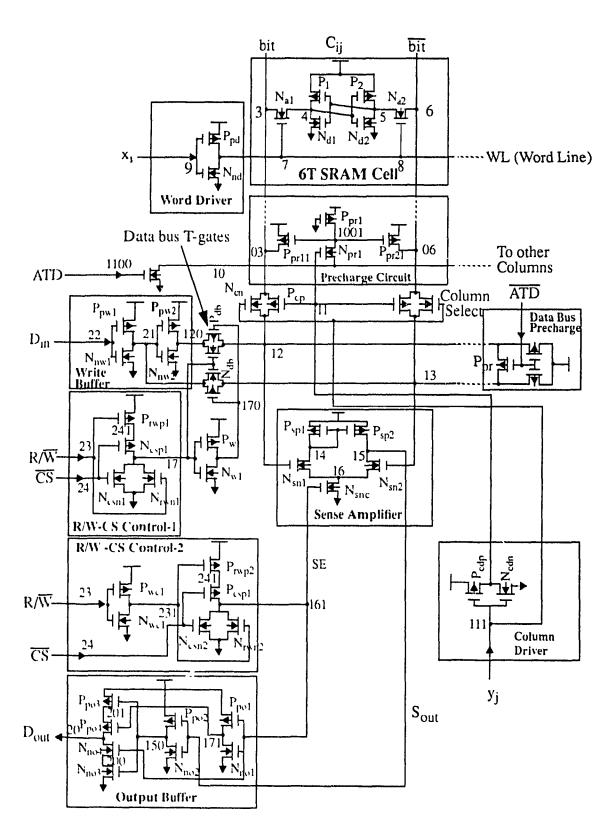

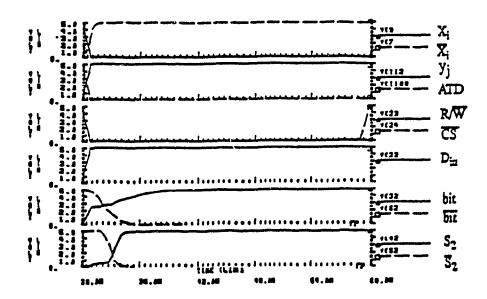

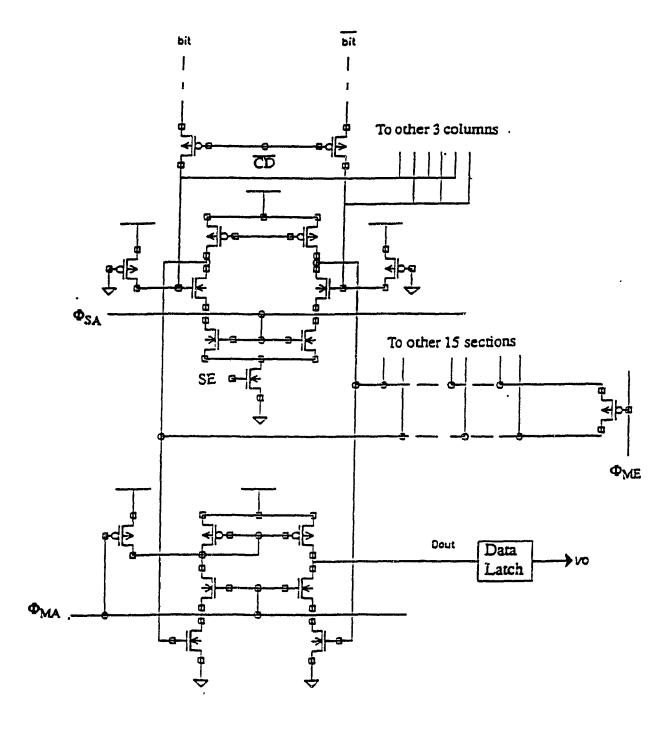

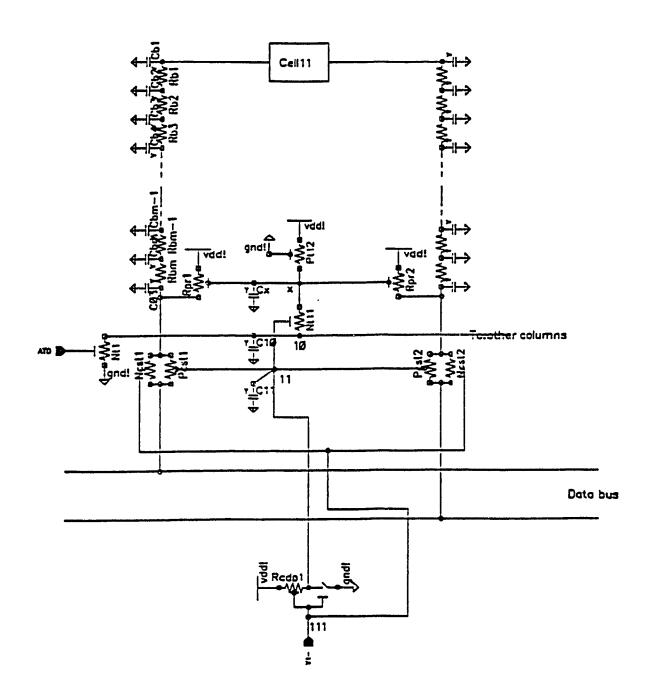

A functional description of the memory operation is depicted in Fig. 1.3(a), showing the general organization of a SRAM. Fig. 1.3(b) illustrates a simplified circuit diagram for read and write operation of a SRAM. The bit and bus lines are precharged and equalized by the precharge circuit. The read operation is initiated by the precharge cycle. During precharge the row and column decoders and sense amplifiers are disabled. As shown in Fig. 1.3(b) we used our newly designed Power Down Y-controlled PMOS (PDYCP) load precharge circuit which is explained in Section 1.7.2. Here, the operation of the PDYCP circuit is controlled by address transition detection (ATD) and a column decoder. When ATD=1 and  $Y_1$ =0, the bit and bus lines are precharged to  $V_{\rm dd}$ =5 volts. The address is decoded by two address decoders: row (X) and column (Y) decoder to select a cell for read/write. The word line is locally connected to all the cells which belong to the same row. The bit lines are laid into columns and connect all the cells which belong to the same column. The timing cycle starts with the chip select signal ( $\overline{CS}$ ) as active low. The read/write control

Fig. 1.3(a) Organization of a SRAM

Fig. 1.3(b) SRAM with peripheral circuits

signal (R/W) determines a read/write operation. For the sensing scheme we used a differential current mirror sense amplifier (CMSA) because of its high differential mode gain, low common mode gain and good common mode noise-rejection ratio (CMNRR). As soon as a small difference in potential between a pair of bit lines happens, it is amplified by the sense amplifier in a full swing and fed to the output buffer. An important issue here is the position of the column selectors. If the column selectors were placed after the sense amplifiers, more amplifiers would be required which increases power dissipation and area. As shown in Fig. 1.3(b), multiple bit lines are connected to the common data bus and feed to a single sense amplifier which is connected to the data bus. In high speed SRAM there is usually one or a few columns dedicated to a sense amplifier. Finally, data output is fed to the output pin by an output buffer. Input data comes through the same pin and goes through the input buffer. The sense amplifier is bypassed during a write operation, and the write buffer directly feeds the memory cell selected by the column and row decoders.

#### **SRAM cell operation:**

The key element in SRAM is the SRAM cell which can store information in its static structure as long as power is available in the chip. As in Fig. 1.2(b), the cell, being a cross-coupled inverter, with node 4 ( $S_1$ ) containing a '0' or '1' the complementary value will be stored at node 5 ( $\overline{S}_1$ ). Here, the transistors  $N_{a1}$  and  $N_{a2}$  are called access transistors,  $N_{d1}$  and  $N_{d2}$  are called driving transistors. The operation of the cell is as follows: when the word line is selected then the access transistors  $N_{a1}$  and  $N_{a2}$  conduct. The cell can be in one of the two stable states, either '0' or '1'. For state '0', the transistors  $N_{d1}$  and  $P_2$  are in conduction but  $N_{d2}$  and  $P_1$  are in non-conduction. In this case the voltage at nodes 4 and 5 will be '0' and '1' respectively. On the other hand, for state '1', transistors  $P_1$  and  $N_{d2}$  will be conducting and  $P_2$  and  $N_{d1}$  will be non-conducting which will ensure an '1' and a '0' at nodes 4 and 5 respectively.

#### Reading Data:

The read operation consists of two steps. First, the bit lines are precharged high keeping the word line disabled. As soon as the precharge time is over the word line and the column select line is enabled to address the desired cell to be read. Consequently, the CS=0 and  $R/\overline{W}=1$  signals are also set. The charge on one of the bit lines of the selected bit line pairs will be discharged through the enabled memory cell, representing the state of the cell. For instance, assume the cell Cii as shown in Fig. 1.3(b) is selected to read. The word line signal at node 7 and the column select signal at node 111 goes high which makes transistors Na1, Na2 and column select transmission gates conduct. If a logic '0' is stored in the cell (meaning node 4 = 0 and node 5 = 1) then the current flows through  $N_{a1}$  which will pull down the 'bit' line. If a logic '1' is stored in the cell (meaning node 4='1' and node 5='0') then the current would flow through  $N_{a2}$  and thereby pulling down the 'bit' line. Since, at the beginning of the cycle,  $\overline{CS}=0$  and  $R/\overline{W}=1$  which makes 'SE' line high and selects the sense amplifier. The sense amplifier is connected to the data bus, for a '0' read as the 'bit' line will be pulled down towards the ground then the differential voltage at the bit line pair will pull down sense amplifier's node 15 towards ground and thereby sensing a '0' which will be buffered at the output driver. For a read '1', the 'bit' line will stay high and the 'bit' line will be pulled down towards the ground which will result in pulling up node 15 towards  $V_{\rm dd}$  ( $V_{\rm dd}$ =5 volts: logic '1'). Fig. 1.3(c) illustrates a read-0 operation. Detailed operation of a CMSA is referred to Section 1.8.1.

#### Writing Data:

The write cycle starts by setting ATD=0,  $\overline{CS}$ =0, R/ $\overline{W}$ =0, WL=1, and Y<sub>j</sub>=1. Now, to write a '0' in the cell, D<sub>in</sub> should be set to '0'. Therefore, data '0' and '1' will be placed to the 'bit' and 'bit' lines respectively. Since the cell is already selected to write, the data placed in the bit lines will be written to the cell with nodes 4 and 5 at states '0' and '1' respectively. If the cell had a '1' stored in it then the new data will overwrite on it to '0'. In

Fig. 1.3(c) Read-0 operation of a SRAM

Fig. 1.3(d) Write-1 operation cf a SRAM.

this case transistors  $N_{d2}$  and  $P_1$  will be switched off and  $N_{d1}$  and  $P_2$  will be switched on. If the cell had a'O' stored in it then with 'bit'=0, it will keep the storage node 4 at 'O' and thus the state of the memory will remain unaltered. If an '1' is to be written in the cell, regardless of what is stored in the cell, the  $D_{in}$  (data input) is required to provide '1' which will set 'bit'=1 and ' $\overline{bit}$ '=0. Since the cell is selected to write, transistors  $N_{a1}$  and  $N_{a2}$  will be switched on through word selection and logic '1' and 'O' will be stored at nodes 4 and 5 respectively which confirms a write '1' into the cell. In this case, cell transistors  $N_{d2}$  and  $P_1$  will be switched on and  $N_{d1}$  and  $P_2$  will be switched off. If the cell originally had an '1' stored in it then the state of the cell will remain unchanged. Fig. 1.3(d) illustrates a write-1 operation. Where  $S_2$  and  $\overline{S}_2$  are the cell storage and complementary storage nodes respectively.

#### 1.4.2 A 6T SRAM Cell Design

Optimum design of the SRAM cell has a significant effect on the performance of a SRAM As discussed in Section 1.4 the cell area and stability of the cell are considered to be two important aspects in designing a SRAM cell. The cell area of a SRAM is determined by the minimum feature and the noise margin [16]. The noise margin of the cell depends on the conductance ratio of the cell driver and the access transistor. The conductance ratio also partly determines the speed performance and power dissipation. Therefore, optimization of the memory cell in terms of device dimensions is important to obtain high-density SRAMs.

Cell stability is influenced by the channel width mismatches or threshold mismatches in all paired devices [16]. In the typical SRAM cell as in Fig. 1.2(b) the PMOS pull-up transistors can be minimum sized since its only function is to offset the effects of leakage. Therefore, the design of the cell depends on the sizes of access and driver transistors. Their size ratio will affect the read/write speed. The size of the cell access transistor directly affects the load on the word and bit line. In order to design a high speed, low power and highly reliable

SRAM the following design criterion as proposed in [16] should be taken into account:

- 1. Nondestructive Read condition

- 2. Write condition

- 3. Data retention condition

- 4. Power dissipation condition.

#### **Nondestructive Read Condition:**

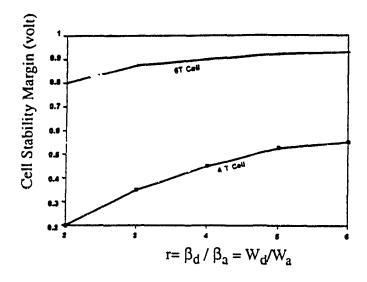

During a READ operation bit lines are precharged high to a voltage  $\leq V_{dd}=5$  volts. Fig. 1.4(a) shows the graphical representation of Static Noise Margin (SNM) which is obtained by drawing and mirroring inverter the characteristic [13]. As in Fig. 1.3(b) assume nodes 3 and 6 are precharged high. Node 4 contains data with complementary data at node 5. Now, after precharge, when the word line is selected to READ the cell, a transient disturbance at soft nodes 4 and 5 may occur which can corrupt stored data. The term nondestructive read refers to the SNM of the cell. The SNM of the cell should be high enough to cope with the transient READ disturbance. The SNM of a cross-coupled inverter is defined as the maximum noise voltage V<sub>n</sub> that can be tolerated by it before changing states [13]. A SRAM should be designed such that under all conditions some SNM is reserved to cope with dynamic disturbance caused by α particle, cross-talk, voltage supply ripple and thermal noise [13]. The static noise margin of the cell is determined by the  $\beta$ (transistor gain factor) ratio, r=  $\beta_d$  /  $\beta_a$  of the driver and access transistor respectively. Where,  $\beta = \mu C_{OX}W/L$ ,  $\mu$  is the mobility,  $C_{OX}$  is the gate oxide capacitance and W and L are the transistor channel width and length respectively. SNM is also related to the stability of the cell. Higher noise margin ensures better stability of the cell. The stability margin  $\Delta$  is defined as the difference between the minimum voltage applied on the bit line to WRITE into the cell and the maximum voltage delivered on the bit lines by the cell during READ operation [9].  $\Delta$  must be positive to guarantee the functionality of the RAM [9]. Fig. 1.4(b) shows the stability of a cell as a function of r. It is seen that the stability margin of a 6T cell

Fig. 1.4(a) Graphical representation of Static Noise Margin [13].

Fig. 1.4(b) Stability margin as a function of r [9].

is almost uniform and higher than a 4T cell because of the presence of the PMOS pull-up structure. According to our SPICE simulation and Fig. 1.4(b) an optimized design of a 6T cell can be done for a value of r=2 to 3.

#### Write condition:

During write operation the bit line pair and the word selecting the cell are enabled. Write data is placed on the 'bit' line and a complementary value is placed in the 'bit' line. The critical situation happens for the cells which belong to the same row of the cell under 'WRITE' but in other columns. To avoid miswrite to those unselected cells the ratio r becomes crucial. Nevertheless, it is observed that write condition does not affect stability of the unselected cells because of PMOS pull-up in 6T cell. In a conventional Y-controlled bit line precharge SRAM the bit lines of the unselected column are precharged high. Due to precharging of all unselected columns the write power dissipation increases. In our design, we propose a precharge technique which will avoid precharging of the unselected columns and thereby a significant reduction of power can be achieved and the cell will become more reliable.

#### **Data Retention Condition:**

The data retention in a memory cell means that the cell remains undisturbed by the bit line voltage set in the preceding read cycle. At the preceding read cycle one of the memory cells in a column is selected by a word line. As a result, the bit line is driven by the memory cell and one of a pair of the bit lines is set to a low voltage. In the unselected columns the bit line load precharge transistors act as a pull-up device. Since the column select transistors in the unselected bit lines are off, then the high-impedance pull-up results in a large voltage swing in those bit lines. The low level of the bit line in this period is lower than that of the column selected for read operation. The low level varies according to the channel width of MOS transistors of the memory cells in column. The lowest level of the bit line has to be set higher than the largest V<sub>FL</sub> of memory cells in the column to retain the data. Where,

V<sub>FL</sub> is defined as the bit line voltage at which the data changes from a high state to a low state when the voltage of a bit line is set under static condition.

#### Power dissipation condition:

In each column DC current flows into the memory cell connected to the selected word line. The power dissipation of the memory cell mainly depends on the size of the access transistors. As the bit line and input/output bus line are discharged by the current of these transistors, they determine the access time. Therefore, power dissipation is also a limiting factor in the design of the cell.

The optimum sizes of the access transistor and the inverter transistors are determined by the four conditions mentioned above and by design rules. As we have investigated, the above conditions mostly depend upon the cell ratio r and the precharge technique. The optimum value of r and our newly designed precharge technique will provide excellent results. In our design, the cell PMOS and access transistors are considered to be minimum sizea according to the technology and design rule with an optimum value of r=2.5 because of the following reasons:

- 1. The function of the PMOS transistor is to supply little leakage current.

- 2. Since r is fixed, an increase in  $W_a$  also increases  $W_d$  as r times of  $W_a$ . So, the overall SRAM array area increases as an O(mn). Where m and n are the number of rows and columns respectively in the SRAM array.

- Increased W<sub>a</sub> may reduce cell intrinsic access delay but word delay will be increased as an O(n).

- 4. Increased  $W_a$  will increase bit line capacitance which will increase bit line delay as an O(m).

#### 1.5 Decoding Scheme

The word decoding delay time can be defined as the delay time between the address setup time and word line selection time. The implementation of a decoding scheme is relative to the density of the RAM. For low density SRAM the simple conventional decoder [5] is sufficient. But as the memory density increases the word delay affects the total access time. For medium and high density SRAM's to have faster word selection time, dynamic double-word line (DDWL), and divided word line (DWL) structures are proposed in [10] and [11] respectively.

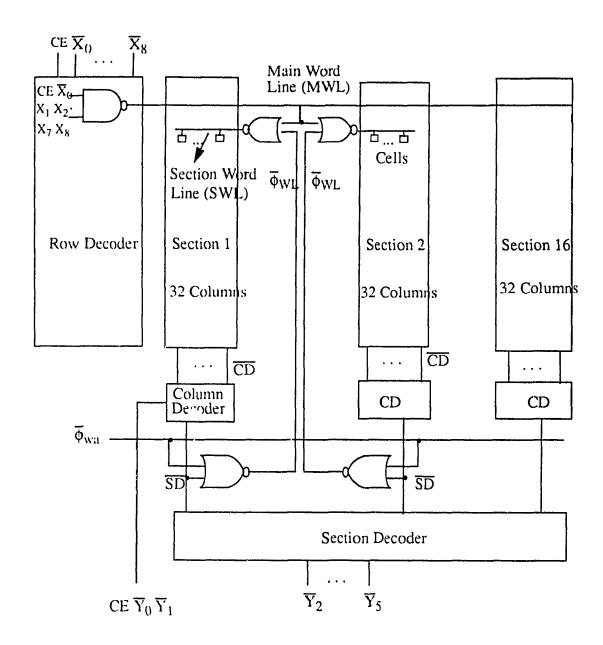

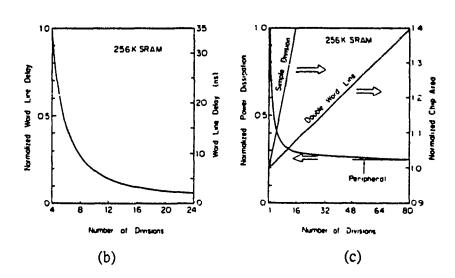

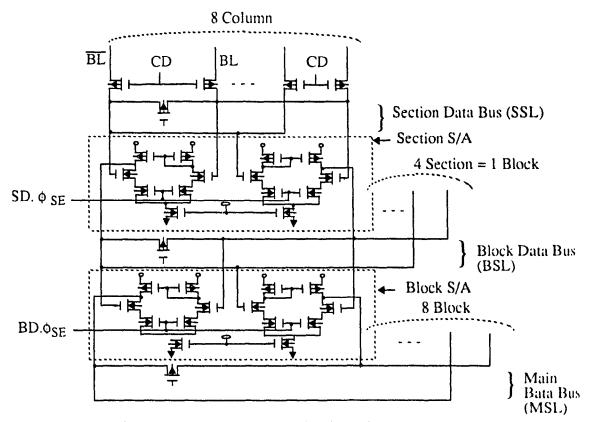

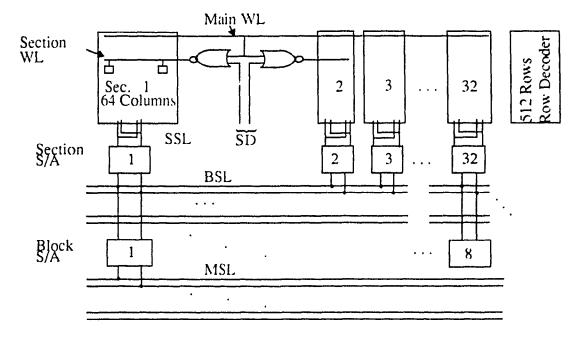

#### 1.5.1 Dynamic Double-word line (DDWL) structure

The basic architecture of DDWL is shown in Fig.1.5(a). Word lines are doubly placed, namely Main Word Lines (MWL) and Section Word Lines (SWL) [10]. Due to the global arrangements of MWL, the capacitance of the MWL is relatively small, which reduces overall word line RC delay. Moreover, the power dissipation is reduced because only one SWL is selected at a time and consequently only a small number of memory cells are activated. From the view point of delay time and power dissipation better performance can be achieved with an increased number of sections/ blocks. But with the increase of sections the number of local decoders required is increased which increases the overall chip area linearly. Fig.1.5(b) and (c) shows the trade-off of delay, power and area as a function of the number of sections or blocks. A 16 or 32 blocks can be a reasonable choice of better trade-off. The clock-controlled word lines are one of the main features of the DDWL scheme [10]. In this scheme, the activation signal,  $\phi_{wa}$  is created by address transition detectors (ATD). The pulse width of  $\phi_{wa}$  is made greater than the access time and is used to cut all the D.C. path in the SRAM after a read operation is over. Consequently, a low D.C. active power dissipation has been achieved with no power consumption after access time. This is known as automatic power down (APD) technique.

Fig. 1.5(a) Dynamic Double-word line (DDWL) structure [10]

Fig. 1.5 Trade-off (b) Word line delay, (c) area and power as function of number of sections or blocks in a DDWL structure [10].

#### 1.5.2 Divided Word-line (DWL) structure

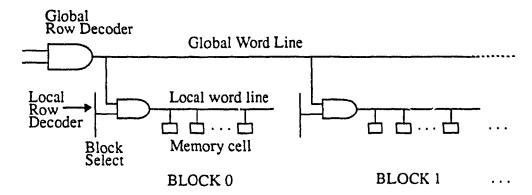

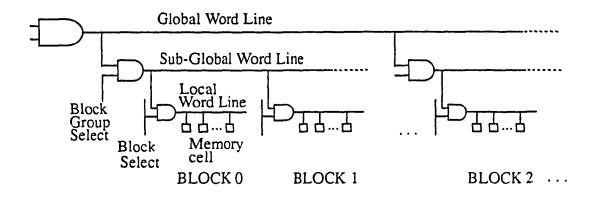

The concept of conventional divided word line architecture as proposed in [11] is illustrated in Fig. 1.6(a). The architecture is similar to that of the DDWL except that it is not clock controlled. In this scheme each block contains N (N= $n_c$  /  $n_b$ , where  $n_c$ = total number of cells in the memory, and  $n_b$ = number of blocks) number of cells. A local word line is placed in each block, is activated by a global word line and block select line. Since only one block is activated to READ/WRITE the DWL structure reduces both word-line delay, and power consumption.

For a high density SRAM with a capacity of 4MBit or more, the number of multidivided blocks will have to be increased. In this case, the DWL structure suffers from increased load capacitance of the global word line and causes a significant increase of both delay time and power consumption. Newly, hierarchical word decoding (HWD) architecture has been proposed in [3]. In this architecture, the word select line is divided into more than 3 levels as shown in Fig.1.6(b). The number of hierarchies, in other words, the level of word-line division, is determined by the total load capacitance of the word decoding path.

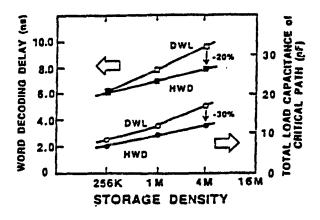

With HWD, the load capacitance of the word decoding path is efficiently distributed [3]. Therefore, the HWD architecture realizes a significant reduction in both delay and power consumption. Fig.1.6(c) shows the simulation results as in [3] of word decoding delay and total load capacitance of the word decoding path as a function of storage density. The conventional DWL and the proposed HWD are compared with each other at the optimum point of 256- Kb, 1- Mb, and 4- Mb SRAMs.

In a smaller density, like a 256-Kb SRAM, there is no significant difference. As the density becomes larger, although the HWD needs an extra decoding stage compared to the DWL, it shows better performance than that of the DWL. In a 4-Mb SRAM, for example, the HWD architecture can reduce the delay time 20% and the total load capacitance 30%

Fig. 1.6(a) Conventional Divided-word line structure [3]

Fig. 1.6(b) Hierarchical word decoding architecture [3].

Fig. 1.6(c) Comparison of DWL and HWD [3].

compared to the conventional DWL [3]. The estimation predicts that the proposed HWD architecture will be very effective for future high-density SRAM.

The advantages of the above two schemes are as follows:

- Elimination of wasted column current. The column currents flows only in a selected block which reduces total active power.

- 2. Reduced delay time. Due to 2 or 3 levels of hierarchy of the decoding technique the capacitance of the row select line is much smaller than that of a conventional word line, because it includes gate capacitance of every access transistor in the memory cells.

The drawback of DWL/HWL is that the column current in the selected block flows during the whole read and write cycle which increases active power. This can be overcome by using a block isolating circuit. The purpose of the block isolating circuit will be to disable the block when the sense amplifier senses the differential voltage. The signal produced by ATD circuit can also be used for this purpose.

### 1.6 Circuit techniques for Decoder

As we see in the above DDWL & DWL structures, an increase in the number of blocks and / or hierarchy increases the requirement of the number of decoder circuit linearly. Therefore, an optimized decoder circuit technique is very effective to reduce overall chip area. Two possible optimized decoder circuits namely, PMOS-load decoder [2],[5] and Transfer Word Decoder (TWD) [1] can be noted for high density SRAM applications in comparison to a conventional CMOS AND / OR decoder.

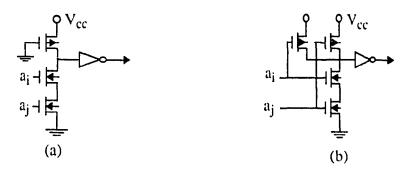

#### 1.6.1 PMOS-Load Decoder

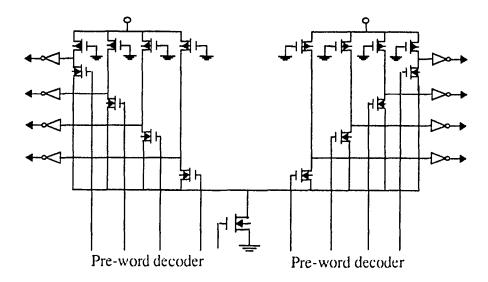

Figs. 1.7(a) & (b) show a PMOS-Load decoder [5] and a conventional CMOS

Fig. 1.7(a) PMOS load decoder and,

### (b) Conventional CMOS decoder [5]

Fig. 1.7(c) 1-Mbit SRAM word decoding scheme [5]

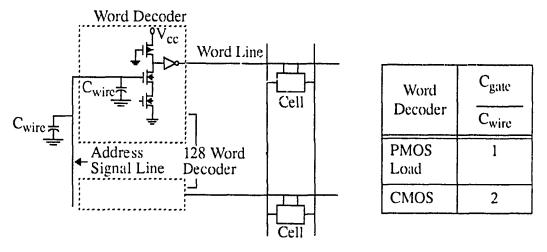

Fig. 1.7(d) Circuit schematic of word decoder using PMOS load [5].

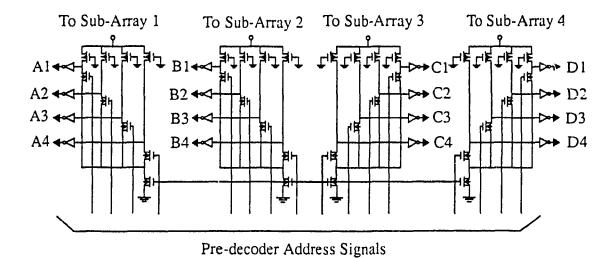

decoder respectively. The address signal line is connected only with the NMOS in a PMOS load decoder, while it is connected with both the PMOS and the NMOS in a CMOS decoder. Therefore, the address load capacitance caused by the gates in PMOS-load is almost half of that in a CMOS decoder. This implies that a smaller delay time can be obtained by using a PMOS-Load decoder. Fig. 1.7(c) shows a simplified 1- Mbit SRAM word decoder scheme which has typical PMOS load circuitry. A word decoder is the final decoder to select a word line, which is connected with 64 cells. An address signal is connected with 128 word decoders. As those 128 word decoders are densely packed in one cell array block, gate capacitance makes up a large portion of the total capacitance of the address signal line. In the 1- Mbit SRAM [5] the ratio of Cgate to Cwire is about 1 for a PMOS-load word decoder and about 2 for a CMOS word decoder. A circuit schematic of a word decoder used in a 1- Mbit SRAM [5] is shown in Fig. 1.7(d). Eight NAND gates are designed by using PMOS-load circuits. The bottom NMOS is used common to the eight NAND gates to reduce the word decoder area.

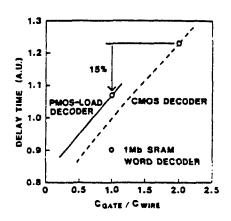

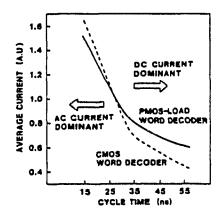

Fig. 1.7(e) shows the dependence of the delay times on the ratio of  $C_{\rm gate}$  to  $C_{\rm wire}$  for the two types of decoders. Apparently, the PMOS-load decoder produces more delay time than the CMOS decoder for the same capacitance ratio. However, in actual circuitry, because of the difference of the capacitance ratios between the two types of decoders, the PMOS-load decoder yields a smaller delay time in most cases. As shown in Fig. 1.7(e), a 15% decrease in the delay time is reported in [5].

The PMOS-load decoder has a D.C. current due to the normally ON PMOS transistors, while the CMOS decoder has no D.C. current. This fact might discourage us from employing the PMOS-load decoder. However, we have to remember that the CMOS decoder circuitry has more ac current than the PMOS-load decoder because of its large capacitance [5]. Fig. 1.7(f) shows the dependence of the average current upon cycle times for the two types of word decoders. With a cycle time of more than 25ns, a PMOS-load word decoder has more current because the D.C. current of the PMOS-load decoder is

Fig. 1.7(e) Delay time of two types of decoders [5]

Fig. 1.7(f) Current of word decoder [5]

Fig. 1.7(g) Word-decoder circuit (for four memory subarrays) [2].

dominant. However, with a cycle time of less than 25ns, a CMOS word decoder has more current because the ac current charging and discharging the capacitance becomes dominant.

A similar PMOS-load decoder circuit is also implemented in [2], where the word decoder for a four memory sub-array are laid in one region as shown in Fig. 1.7(g). This architecture reduces 40% word decoder layout area by sharing a common diffusion region [2].

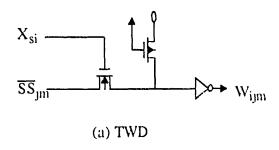

### 1.6.2 Transfer Word Drive (TWD) Decoder

As described before a conventional NAND decoder is not suited for high-speed high-density SRAM because of its high gate capacitance. A sophisticated decoder circuit called Transfer Word Drive (TWD) is proposed in [1]. Here, the conventional two input NAND gate is modified as in Fig.1.8. The principle of operation of the TWD decoder is such that when the main word line signal  $X_{si}$  is high and the selection signal  $\overline{SS}_{jm}$  is low, the word line  $W_{ijm}$  is selected. This circuit is very simple and has a similar function to the AND gate.

By using TWD, the load capacitance of the selected signal can be reduced by around 30% [1]. The advantages of the TWD decoder are, its simplicity, reduced layout area and faster delay time. For an optimized decoder design, a TWD decoder or a similar type will be highly preferable.

(b) Conventional

Fig. 1.8 (a) Transfer word drive decoder (b) Conventional decoder [1].

# 1.7 Precharge Scheme

In this Section, we describe various precharge techniques for a SRAM. Some typical precharge circuits have been presented with their merits and demerits. We also present a Power Down Y-Controlled PMOS (PDYCP) load precharge circuit. The performance of PDYCP precharge technique is compared with a Y-Controlled bit line load (YCL) precharge. Our results show that the PDYCP precharge technique performs superior to any other technique.

### 1.7.1 Different Precharge Techniques

Faster precharge of the bit lines for faster read operation is an important issue. Various circuit techniques have been reported in the past ten years for the precharge technique of a SRAM. Accordingly, precharge circuits can be classified into two categories:

- 1. Continuous precharge of bit / bus line,

- 2. Controlled precharge of bit / bus line.

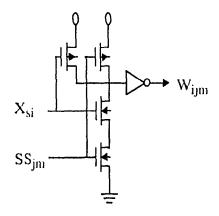

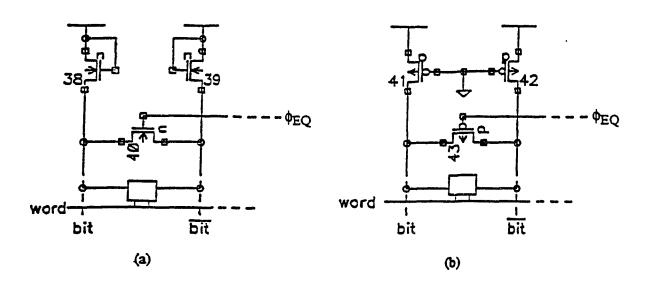

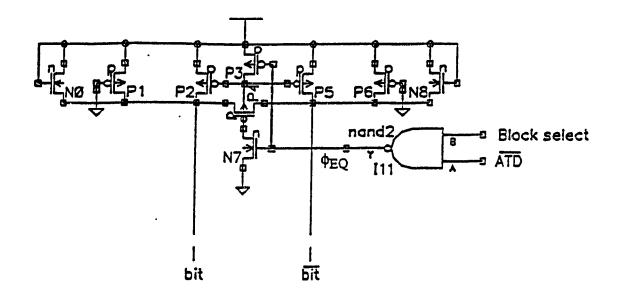

Fig. 1.9 & 1.10 shows some common form of precharge schemes. The continuous precharge scheme has the advantage of high current driveability which enables quick precharge. But, the serious disadvantage of it is that it increases total standby power due to continuous precharging of every column. For high density SRAM application, continuous precharge bit / bus line technique is impractical because of high power consumption. Instead, controlled bit / bus line precharge technique is preferred. A combination of both approaches can be used for better performance as in [3]. A bit line load with an Address Transition Detection (ATD) controlled precharge circuit [3] is shown in Fig. 1.11. Here, the bit line load consists of PMOS and NMOS transistors in parallel. The advantages of this type of structure are quick precharging and its voltage bump free characteristic. The Block Select and ATD signals generate a bit line equalize  $(\phi_{EO})$  signal to logically

Fig. 1.9(a) and (b) Continuous precharge circuits.

Fig. 1.10(a) and (b) Controlled precharge circuits.

Fig. 1.11 Bit line load and ATD controlled precharge circuit [3].

Fig.  $1.12 \overline{ATD}$  controlled conventional precharge scheme.

precharge and equalize the bit lines of the addressed block. The main difficulty with this method is that the unaddressed blocks are continuously precharged since transistors P1, P6, N0 and N8 as in Fig. 1.11 are always ON which results in high power dissipation. Fig. 1.12 shows a conventional fast precharge circuit scheme used in high density SRAM design. In this scheme, the precharge and equalize NAND gate experiences a very large precharge circuit gate capacitance because of precharging every column in the selected block which increases precharge delay.

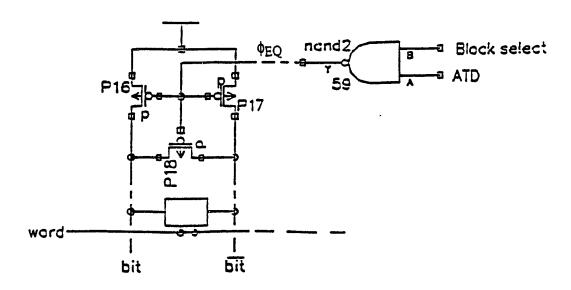

A technique known as YCL (Y- Controlled bit line load) as shown in Fig. 1.13 is used in [1]. In this approach, precharge is controlled by the Y-select (Column driver) signal. When the bit line is unselected, PMOS transistors  $M_{np1}$  &  $M_{np2}$  turn on, precharging the bit lines. The precharge gate capacitance in this case is just only for a single precharge circuit. Now, when the column address is valid, PMOS transistors  $M_{np1}$  &  $M_{np2}$  turn off. However, the bit lines are still precharged and equalized by the data bus line precharge circuit.

Therefore, the precharge and equalize operation of the YCL circuit is the same as that of the conventional circuit without sacrificing any precharge capability. Moreover, the load capacitance of the precharge clock line  $\phi_{EQ}$  generated by the row and column address transient detector has been reduced largely [1] because in this case the load consists of only the gate capacitances of the data bus precharge circuit.

The main advantage of YCL precharge is that faster precharge can be achieved. But, the problem with the unselected columns is still crucial. The unnecessary precharge of those columns increases power dissipation and in some cases may affect cell stability.

Fig. 1.13 Y -controlled bit-line load (YCL) precharge circuit [ S.AIZAKI '90 [1]]

# 1.7.2 Power Down Y-Controlled PMOS (PDYCP) Load bit line Precharge Technique

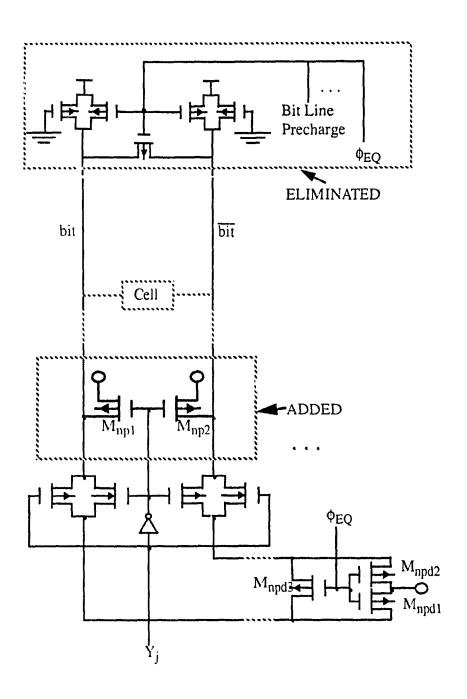

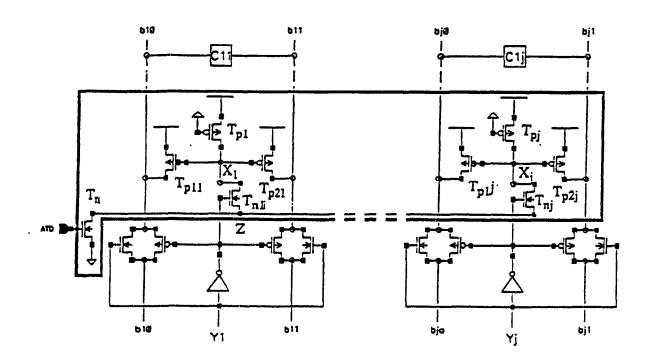

The primary purpose of the precharge circuit in a SRAM is to accelerate the reading process. It is observed that most of the previous precharge techniques suffer from drawbacks in terms of speed and power consumption. The most recently reported YCL[1] (Y-Controlled bit line load) induces faster precharge but experiences huge amount of power dissipation due to the D.C. current in every unselected column under read/write or standby mode because of unwanted precharge. Considering the above situations we developed a modified form of YCL circuit called PDYCP (Power Down Y-Controlled PMOS) load precharge which is shown in Fig. 1.14. Here, we added a power down circuit (inside heavy line area) which is able to prevent unnecessary precharge of the column. The precharge is controlled by an Address Transition Detection (ATD) signal. The ATD signal will go high at the beginning of the precharge cycle. As soon as the precharge is over the ATD signal will go down. During precharge all the column addressing signals  $Y_1$ ,  $Y_2$ ,  $Y_3$ , ...,  $Y_j$  will be low and as a result transistors  $T_n$ ,  $T_{n1}$ ,  $T_{n2}$ , ...,  $T_{np}$  will be ON. Therefore, with ATD high, nodes  $X_1$  to  $X_j$  will be pulled down to the ground. The formal READ operation starts when the column is addressed with Y high and at the same time ATD will go down meaning that address is in transition. When ATD=0, the 'Deselect' line (Z) will be pulled-up through  $T_{pl}$ ,  $T_{nl}$ . Assume that  $Y_1 = 1$ ,  $Y_2 = Y_3 = \dots = Y_1 = 0$ , so as a result transistor  $T_{nl}$  will be OFF and  $T_{n2}$ ,  $T_{n3}$ , ...  $T_{nj}$  will be ON. Now, the high voltage at Z and the grounded gate PMOS transistors will turn OFF the precharge PMOS transistors in every unselected column and the selected column. During standby mode all  $Y_1 = Y_2 = Y_3 =$ ...  $=Y_j=0$ , with ATD=0 which will disable the precharge PMOS transistors and thereby avoid unnecessary precharge.

The PDYCP circuit with other peripheral circuits in SRAM is given by Fig. 1.3(b). Fig. 1.15 depicts the SPICE simulation plot for the PDYCP precharge, READ and WRITE

Fig. 1.14 Power Down Y-controlled PMOS (PDYCP) load precharge circuit.

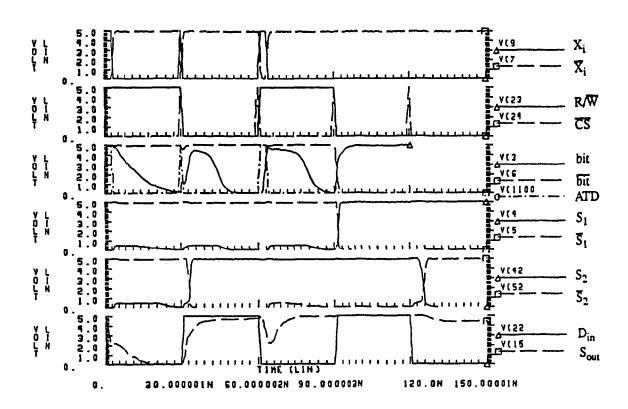

Fig. 1.15 SPICE simulation plots using PDYCP precharge technique for consecutive READ/WRITE operation.

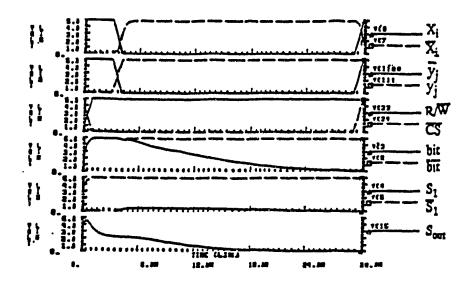

operation. Here, we considered two cells lying in two different columns for READ/WRITE operation. The functionality of the circuit is tested for any READ followed by READ/WRITE or vice versa. It is assumed that the READ cycle consists of precharge time plus the sensing time. As shown in Fig. 1.15 the READ/WRITE timing cycles are as follows:

0- 30 ns: READ-0, cell 11 30- 60 ns: WRITE-1, cell 12

60- 90 ns: READ-1, cell 12 90- 120 ns: WRITE-1, cell 11

120- 150 ns: WRITE-0, cell 12.

Where cell 11 is the cell at row 1 of column 1.

cell 12 is the cell at row 1 of column 2.

The symbols used for the SPICE plots in Fig. 1.15 are referred in Fig. 1.3(b). Moreover, we define,

$S_1$  = cell 11 storage node which corresponds to node 4 of Fig. 1.3(b).

$\overline{S}_1$  = cell 11 complementary storage node which corresponds to node 5 of Fig. 1.3(b).

$S_2$ = cell 12 storage node which corresponds to node 42 of Fig. 1.3(b) (not shown).

$\overline{S}_2$ = cell 12 complementary storage node which corresponds to node 52 of Fig. 1.3(b) (not shown).

In our PDYCP precharge scheme each precharge circuit contains two additional transistors over that of the conventional YCL precharge circuit. The PDYCP layout may look as it will take more area than that of the YCL, but in reality the wasted column area of YCL layout can efficiently be used in PDYCP implementation since the column width is fixed for a 6T SRAM. Our results show that with little or no layout area overhead the

PDYCP precharge scheme will be a best choice.

Table-I compares the performance of a PDYCP precharge with a conventional YCL precharge. It is clear that our PDYCP precharge technique will give very low power dissipation with faster precharge speed and will be very suitable for HDHSLP (High Density, High Speed, Lower Power dissipation) SRAM design. Further analytical and experimental comparisons are also available in Chapter-4.

| mxn   | cct type | T <sub>pr</sub><br>(ns) | T <sub>sa()</sub><br>(ns) | T <sub>sal</sub><br>(ns) | T <sub>w()</sub><br>(ns) | T <sub>w1</sub> (ns) | $P_r$ $(mw)$ | P <sub>w</sub> (mw) |

|-------|----------|-------------------------|---------------------------|--------------------------|--------------------------|----------------------|--------------|---------------------|

| 64x64 | YCL      | 1.53                    | 13.09                     | 14.93                    | 6.21                     | 4.69                 | 69.28        | 29.25               |

| 64x64 | PDYCP    | 1.06                    | 14.13                     | 15.43                    | 5.86                     | 4.49                 | 15.01        | 8.27                |

Table 1: Comparison of PDYCP & YCL precharge performance

As in Table 1 where,

m= number of rows, n= number of columns.

$T_{pr}$  = Precharge delay.

$T_{saO}$  = Sensing 'O' delay.

$T_{sal}$  = Sensing '1' delay.

$T_{w0}$  = Write '0' delay.

$T_{wl}$  = Write '1' delay.

$P_r$  = Read cycle power.

$P_w$  = Write cycle power.

# 1.8 Sensing Scheme

The sense Amplifier (SA) is the key circuit in the RAM to have a fast read access time. Plenty of research has been done by the RAM designers in the past decade ['80-'92] on sensing schemes. The implementation of a SA varies with the SRAM density. For a small scale SRAM a single stage SA is used. For medium and large scale SRAMs, a multistage SA with hierarchical architecture is used, which will be described later.

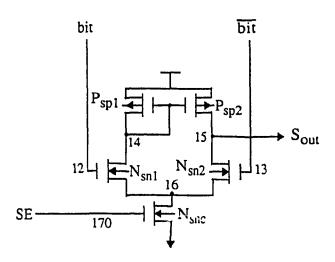

### 1.8.1 Operation of a Current - Mirror Sense Amplifier (CMSA)

The most commonly used of the SA circuits is the Current-mirror (CM) amplifier as shown in Fig.1.16(a). The advantage of this circuit is its fast sensing speed, large voltage gain and good output voltage stability. The SA circuit as shown is basically a differential amplifier. The transistor, N<sub>snc</sub>, is a long channel device and acts as a current source. The sensing delay mainly depends upon the sizes of the NMOS transistors ( $W_{sn1}$ ,  $W_{sn2}$  and W<sub>snc</sub>). During the precharge condition both the bits lines are pulled up while the Sense Enable (SE) signal is low which ensures the current transistor N<sub>snc</sub> is OFF. In this situation, transistors N<sub>sn1</sub> & N<sub>sn2</sub> are ON. Consequently, node 16 is pulled up because of capacitive coupling and as a result the output node 15 goes high as well. Now, depending on the cell content ('0' or '1') one of the bit lines will be pushed down with a high SE signal. The differential mode gain of the differential CMSA is such that a small differential input voltage (Say, 0.1 v) will be sensed at the output. If the cell contains an "1", the voltage at node 13 will start to drop through the RAM cell pass transistor and thereby turn N<sub>sn2</sub> OFF. Since, node 12 stays high which keeps N<sub>sn1</sub> ON and node 14 follows ground, then node 15 stays high and will imply a read '1'. If a '0' is stored in the memory cell then node 12 would be pulled down. In this case, transistors  $N_{sn1},\,P_{sp1}$  &  $P_{sp2}$  would be OFF and  $N_{sn2}$  &  $N_{snc}$  would be ON which would pull down node 15 towards the ground representing a READ '0'. The operation of a CMSA is depicted by

Fig. 1.16(a) A CMOS Current Mirror Sense Amplifier (CMSA)

Fig. 1.16(b) Operation of a CMSA for a read-0.

Fig. 1.16(b) for a read-0 case. Here, V(3) and V(6) are the voltages at bit and  $\overline{\text{bit}}$  nodes respectively. V(15) and V(170) are the sense amplifier output node and sense select (SE) node voltages respectively. The sense amplifier is selected with V(170) high. Since the cell contains a zero so, V(3) goes down and V(6) stays high. As a result, V(15) goes down towards the ground voltage ( $V_{SS}$ ) meaning that the cell contains a zero.

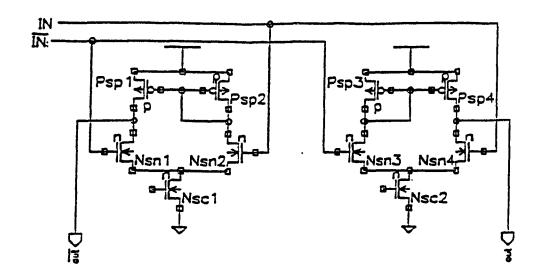

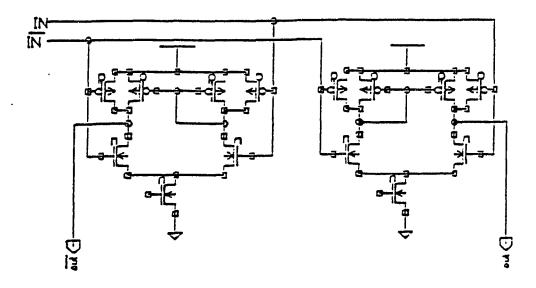

### 1.8.2 Various SA Circuit Techniques

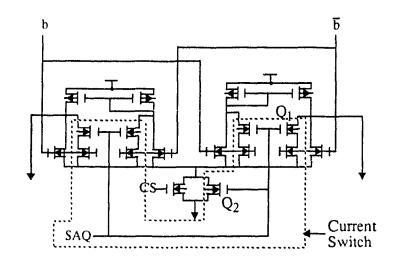

Various high speed SA circuits have been observed in the recent past. Some of them with their salient features will be presented in this Section. Fig. 1.17(a) and (b) show the conventional CMSA and Input Controlled PMOS load (ICPL) [1] sense amplifier, respectively. As realized in [1],[2] the conventional SA is not suited for high-speed highdensity SRAM applications because its gain is not enough for the high sensitivity needed for very fast access time. The ICPL sense amplifier as proposed in [1] includes two PMOS transistors as load in the conventional circuit which is shown in Fig.1.17(a). The four PMOS transistors act as active load and increase sensing gain [1]. It is reported in [1] that the ICPL sense amplifier has around 20% higher gain than the conventional sense amplifier. Another high speed and low power sense amplifier called Dynamic Gain Control Double end Amplifier [5] for a 1Mbit SRAM with 15ns access time which is shown in Fig.1.18. In this case a sensing delay (cell to data bus delay) of 4.5ns has been reported. The circuits within the dotted area are added to the conventional double-end currents-mirror (CM) amplifier. These additional circuits are used to vary the NMOS loading of the sense amplifier. A control signal, SAQ with a short pulse is used during the sensing operation, a fast sensing speed and low power dissipation is achieved simultaneously. A faster sense amplifier circuit so far has been reported in [29]. The circuit configuration is shown in Fig. 1.19. This is a modified form of a two stage CMSA, first stage is connected to the input of the second stage. A voltage difference of 0.1v can be amplified and the sensing delay of approximately 1ns is reported.

Fig. 1.17(a) Conventional CMSA [1]

Fig. 1.17(b) Input-controlled PMOS load (ICPL) sense amplifier [1].

Fig. 1.18 Dynamic Gain Control Double end Amplifier [5]

Fig. 1.19 Modified two stage CMSA [29]

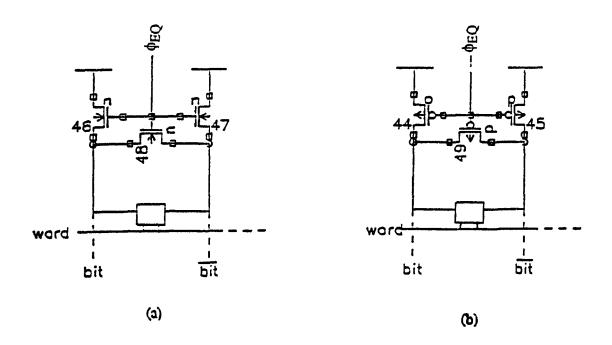

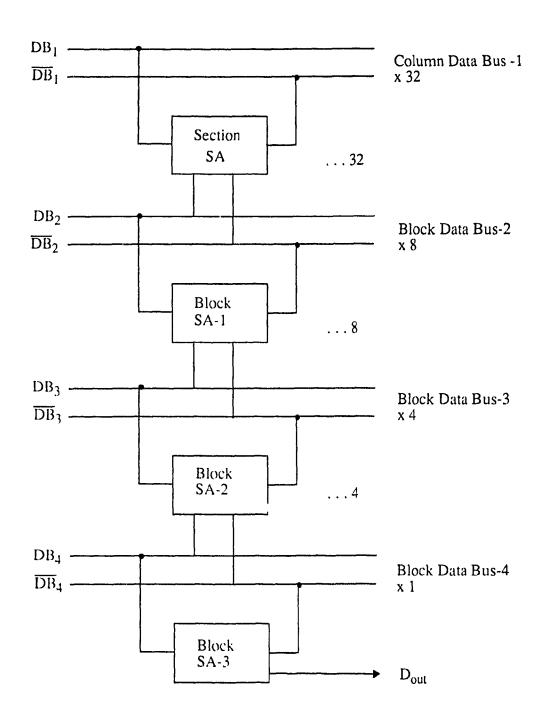

### 1.8.3 Hierarchical Sense Amplifier Architecture

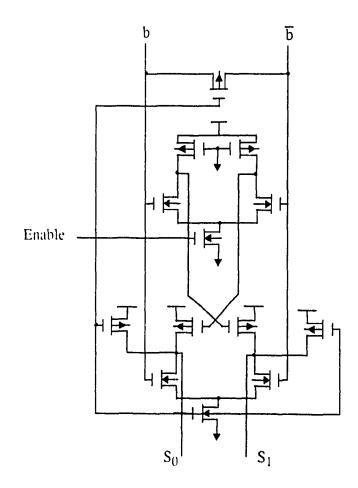

In a high density SRAM as the number of columns and blocks or divisions increase the sense amplifier input data bus line capacitance increases tremendously. So, it is necessary to partition the data-line in different hierarchical structures which will distribute the total capacitance in different hierarchical levels so optimum sensing delay can be achieved. The double line SA structure as reported in [10] is shown in Fig.1.20. This structure implements a local sense amplifier in each column section and a main sense amplifier as a master or global sense amplifier. In this configuration all the bit lines in a particular Section are connected to the local bus line which is input to the Section sense amplifier. Each Section sense amplifier output is connected to the global (main) sense amplifier input bus. Final sense output is carried out from the main SA. Sense clocks  $\phi_{SA}$ and  $\phi_{MA}$  handle the sense operation. This sense amplifier architecture can be suited for a medium density SRAM. In a high density SRAM as the number of column per block increases or the total number of blocks increases, for example in a 1Mbit SRAM, there may be a total of 32 blocks with 64 columns per block. In this case, the double sense line structure is not adequate because of the increased local as well as global data-line capacitance. To overcome this problem a two - stage local sense amplification with a triple - sense - line structure [6] and a four stage SA (four sense lines) [4] is proposed which is depicted in Fig.1.21(a) and 1.22 respectively. In these schemes a Section sense amplifier and block sense amplifier is selected by a hierarchical column decoding system. It can be realized that the circuit in Fig. 1.22 might need double the layout area of that in Fig.1.21(a).

For our 'Sensing Scheme' design we would prefer an optimized design of a CMOS CMSA. As far as high-density high-speed (HDHS) SRAMs are concerned we use a multistage SA structure with a hierarchical sense enabled architecture.

Fig. 1.20 Double line sensing structure [10].

Fig. 1.21(a) Sense Amplifier circuit for Fig. 1.21(b) [6]

Fig. 1.21(b) Two-stage local amplification and triple-sense-line structure [6].

Fig. 1.22 Four-stage Sensing Scheme [4].

# Chapter 2

# Modeling and Analysis of SRAM

### 2.0 Introduction

In this Chapter, we first developed the approximate generalized capacitance model of a SRAM specially for bit line and word line. The SPICE device parameters are used for analysis. Furthermore, the capacitance model is used to develop the RC delay model for a SRAM. In our delay model we assume that the RC time constant is linearly related to the actual delay. Therefore, we will use time constant as an absolute measure of delay and hereafter regression fit it with the actual delay obtained by SPICE simulation. The regression fit consists of two steps. First, the initial fit constants are obtained from regression analysis of the mathematical modeling results and SPICE simulation. Then the second or final regression fit is done between the initial fit constants and m (number of rows), n (number of columns) in order to generalize the model.

# 2.1 Capacitance Model of Word and Bit Line

A very good capacitance model is imperative to have a better delay model. The gate capacitance of the CMOS transistor is assumed to be linearly dependent on the transistor width. Furthermore, in our present analysis we assume the MOS device capacitance as a lumped element and the interconnect capacitance as an uniformly distributed parameter. It can be noted that in our analysis the subscript 'n' & 'p' will be used for NMOS and PMOS transistors respectively.

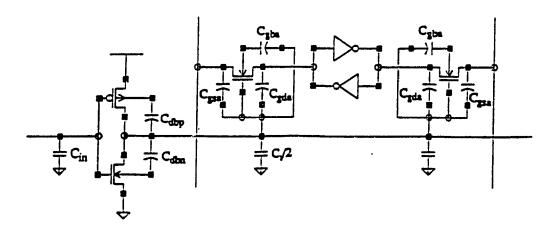

# 2.1.1 Word Line Capacitance Model

The word line capacitance consists of the cell access transistor gate capacitance plus the distributed capacitance of the word line interconnect metal/poly which is depicted in

Fig. 2.1.1. The SRAM cell access transistor gate capacitance  $C_{\rm g}$  can be determined as,

$$C_g = C_{gba} + C_{gsa} + C_{gda} \tag{2.1}$$

$$= C_{oxn} W_a L_a + C_{oxn} W_a LD_{sa} + C_{oxn} W_a LD_{da}$$

(22)

Where  $C_{gba}$ ,  $C_{gsa}$  &  $C_{gda}$  are gate to bulk, gate to source, gate to drain capacitance respectively of the cell access transistor.

$C_{oxn}$  is the NMOS transistor gate oxide capacitance per unit area.

$L_a$ ,  $W_a$  are the Length and width of the NMOS cell access transistor.

$LD_{sa}$ ,  $LD_{da}$  are the source and drain lateral diffusion length respectively of the cell access transistor.

Fig. 2.1.1 Word line Capacitance Modeling

Assuming the word line is connected to n cells, there might be n word segments in a row. The word line interconnect capacitance  $C_i$  per segment can be determined as,

$$C_i = c_o w_w l_w (2.3)$$

where  $c_o$  is the Word line inter-connect capacitance per unit area.

$w_w & l_w$  are the width and length respectively of each word segment.

Since there are two access transistors per cell in SRAM therefore, the capacitance per segment of word line can be written as,

$$C_{w} = 2 C_{g} + C_{i}. (2.4)$$

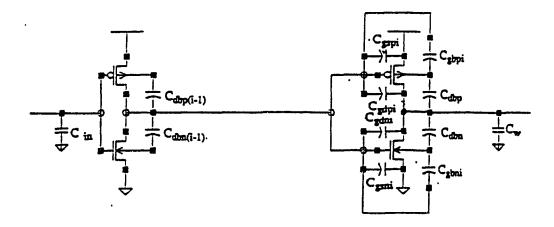

### 2.1.2 Word line driver I/O capacitance

The input capacitance of a driver,  $C_{din}$  consist of input gate capacitance  $C_{gi}$  of driver PMOS & NMOS transistors and the output capacitance  $C_{d(i-1)}$  of the driver driving it which is depicted in Fig. 2.1.2.

Fig. 2.1.2 Word driver I/O Capacitance Modeling

Now,  $C_{din}$  can be written as,

$$C_{din} = C_{d(i-1)} + C_{gi} = (C_{dbn} + C_{dbp})_{i-1} + (C_{gn} + C_{gp})_{i}$$

$$= (C_{dbn} + C_{dbp})_{i-1} + (C_{gbn} + C_{gsn} + C_{gdn} + C_{gbp} + C_{gsp} + C_{gdp})_{i}$$

$$= K_{eq} (CJ_{n} Ad_{n} + CJSW_{n} Pd_{n} + CJ_{p} Ad_{p} + CJSW_{p} Pd_{p})_{i-1}$$

$$+ (C_{oxn} W_{n} L_{n} + C_{oxn} W_{n} LD_{sn} + C_{oxn} W_{n} LD_{dn}$$

$$+ C_{oxp} W_{p} L_{p} + C_{oxp} W_{p} LD_{sp} + C_{oxp} W_{p} LD_{dp})_{i}$$

(2.5)