Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file. Votre reference

Our file. Notice reference.

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents

# RISC Architecture Enhancement for Data Communications Applications

Ali M. Elkateeb

A Thesis

in

The Department of Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy at Concordia University

Montreal, Quebec, Canada

May 1992

© Ali Elkateeb, 1992

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Noar file - Notre rete er ce Och tre - Notre rete er ce

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive permettant à Bibliothèque la nationale Canada dυ de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à disposition la des personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISAN 0-3:5 80019 1

#### **ABSTRACT**

# RISC Architecture Enhancement for Data Communications Applications

Ali Elkateeb, Ph.D. Concordia University, 1991

Efficient RISC architecture for real-time multi-tasking applications in a data communication environment has not been yet rigorously investigated. The aim of our work is to study the suitability of RISC architectures in a data communication environment, such as Integrated Service Digital Network (ISDN), and techniques to improve their performance. Since a register set structure has a big role in the RISC performance enhancement, the RISC register set structure will be the main focus of our research.

At first, a dynamic scanning approach is used to examine the software characteristics of ISDN protocols and their effect on the RISC performance. Then, a new approach is proposed to evaluate the state-swapping processing overhead under different load conditions in an ISDN environment. This approach offers a simple and yet accurate mean to estimate the state-swapping overhead. It is found that the state-swapping overhead is significant in ISDN processing. A RISC architecture using the Multiple Register Set (MRS) structure is introduced to reduce this overhead. The performance of the MRS-based RISC architecture is evaluated in terms of the size of the MRS, the number of tasks resident on the external memory, and the frequency of their execution. A priority strategy for distributing tasks' states among the MRS is proposed, and its implementation complexity is investigated. It is found that even if the number of tasks existing in the external memory increases, the proposed priority strategy can still maintain adequate performance improvement. Finally, the implementation of the priority strategy in conjunction with MRS structure for ISDN applications is discussed.

#### **ACKNOWLEDGEMENTS**

I wish to express my sincerest gratitude to my thesis supervisor, Dr. Tho Le-Ngoc, for his caring guidance, encouragement and patience throughout my research. He was always available to direct and to advise whenever the occasion arose. He has given me unlimited support towards refining my research ideas and developing a broad knowledge in all the related areas to my research. I would like also to acknowledge the financial support provided by Canada NSERC Grants and Quebec FCAP. Grant to Dr. T. Le-Ngoc.

I am grateful for Dr. A. Al-Khalili for advising me during my course work. His encouragement and continuous support has helped my progress in the Ph.D program during the beginning of studies at Concordia University. Special thanks for Dr. Hamidreza Jamali, Faouzi Kamoun, Allan Dubeau and Ajas Hussein for their sincere assistance in reviewing of the thesis.

Special thanks are for my wife Shatha and my daughter Israa for their moral support and patience for not seeing me as often as they should.

# **Table of Contents**

| LIST OF FIGURES                                                        | vii    |

|------------------------------------------------------------------------|--------|

| LIST OF TABLES                                                         | . viii |

| CHAPTER 1: Introduction                                                | 1      |

| 1.1 Background                                                         |        |

| 1.2 Thesis Organization                                                |        |

|                                                                        | . •    |

| CHAPTER 2: Processing in Communication Network Nodes                   | 6      |

| 2.1 Processing Features                                                |        |

| 2.1.1 Layer Structure                                                  |        |

| 2.1.2 The Instruction Set                                              |        |

| 2.1.3 Software Organization                                            |        |

| 2.1.3.1 System Software                                                | 13     |

| 2.1.3.2 Applications Software                                          | 15     |

| 2.1.4 Some Concluding Remarks                                          |        |

| 2.2 implementation of Network Node Functions Using Existing Technology |        |

| 2.2.1 Implementation of Hardware Functions                             | 22     |

| 2.2.2 Implementing Software Functions                                  |        |

| 2.2.2.1 Existing Host Processors                                       | 24     |

| 2.2.2.2 Multiprocessor Configurations                                  |        |

| 2.3 Reduced Instruction Set Computers (RISC)                           | 28     |

| 2.4 Motivations of This Research                                       | 30     |

| 2.5 Work Directions in This Research                                   |        |

| 2.€ The General Approach                                               | 34     |

| CHAPTER 3: ISDN Software Characteristics                               | 35     |

| 3.1 The Software Characteristics: Background                           |        |

| 3.2 Impact of Software Characteristics on RISC Architecture            |        |

| 3.3 Factors to be Measured From ISDN Software                          | 39     |

| 3.4 Measurement Method                                                 |        |

| 3.5 Simulated Models of ISDN Functions                                 |        |

| 3.5.1 Q.931 Basic Call Control Model                                   |        |

| 3.5.2 TEI Assignment Model                                             |        |

| 3.6 Results and Discussions                                            |        |

| 5.0 Headita and Discussions                                            | ,,,,   |

| CHAPTER 4: Processing Overhead of RISC State-Swapping                  |        |

| Operations in ISDN Software Processing                                 |        |

| 4.1 Structure of Tasks in ISDN Network Node Processing                 |        |

| 4.2 Processing Overhead for State-Swapping Operations with RISC        | 60     |

| 4.2.1 Size of Register Set                                             | 62     |

| 4.2.2 Optimizing Compiler                                              | 62     |

| 4.3 An Approach to Measuring State-Swapping Overhead                  | . 65  |

|-----------------------------------------------------------------------|-------|

| 4.4 Measuring State-Swapping Overhead                                 |       |

| 4.5 Discussions                                                       |       |

| Chapter 5: Multiple Register Sets in RISC_Based Architecture          |       |

| Used for ISDN Processing                                              | . 81  |

| 5.1 Multiple Register Set Structure                                   |       |

| 5.2 Allocation of Tasks' States to MRS                                | . 83  |

| 5.3 Characteristics of An Approach for Assigning Tasks' States to MRS |       |

| 5.4 The Priority-Based Approach                                       |       |

| 5.4.1 Strategy of Placing High Priority Tasks of Operating Systems    |       |

| 5.4.1.1 Dynamic System                                                | . 89  |

| 5.4.1.2 Static System                                                 | 91    |

| 5.4.2 Strategy of Placing the High Priority Application Tasks         | . 96  |

| 5.5 Performance Evaluation                                            | . 96  |

| 5.5.1 Effect of MRS Size                                              | 97    |

| 5.5.2 Effect of the Priority Strategy                                 | .103  |

| 5.6 Using MRS Structure for ISDN Processing                           | . 105 |

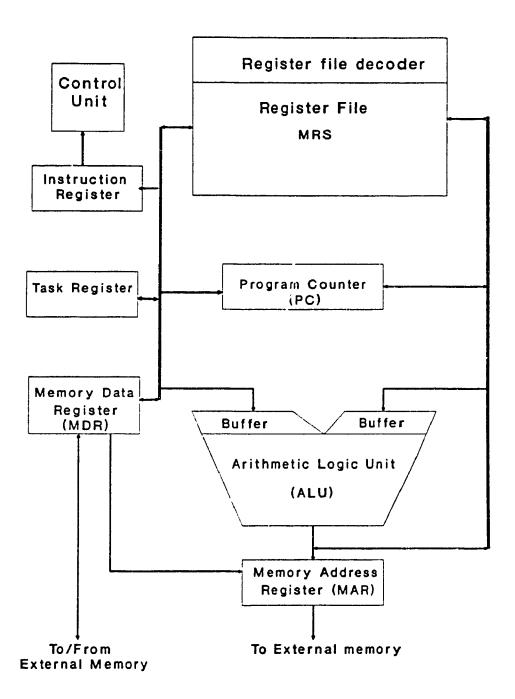

| 5.7 Incorporating MRS in RISC-Based Architecture                      | . 108 |

| 5.8 Discussions                                                       | . 114 |

| Chapter 6: Conclusion and Further Work                                | 119   |

| Reference                                                             | 123   |

| Appendix A: Listing of Q.931 Basic Call Control Program               | 131   |

| Appendix B: Listing of TEI Assignment Program                         | 166   |

# List of Figures

| 2.1  | ISO Open System Interconnection Reference Model                            | 8   |

|------|----------------------------------------------------------------------------|-----|

| 2.2  | Possible Task Distribution in a Low-Capacity Network Node                  | 17  |

| 2.3  | Distribution of Layer 2 and 3 Tasks                                        | 19  |

| 2.4  | Distributed Processing in a Communication Node                             | 21  |

| 3.1  | RISC Overlapped Register Set Organization                                  | 38  |

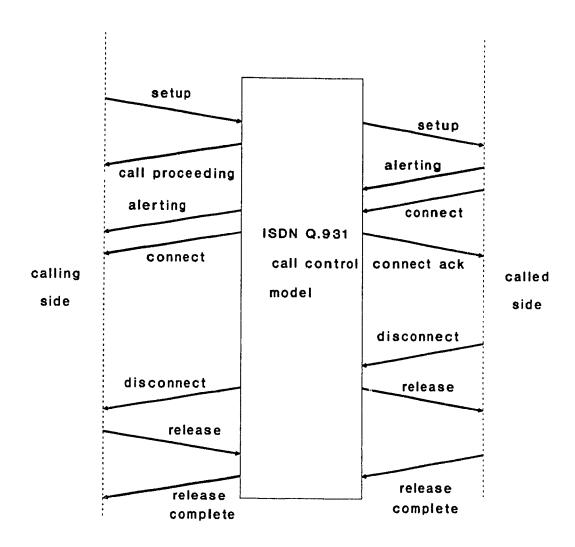

| 3.2  | Q.931 Task Operation                                                       | 43  |

| 3.3  | ISDN Mescages Used in Q.931 Model                                          | 45  |

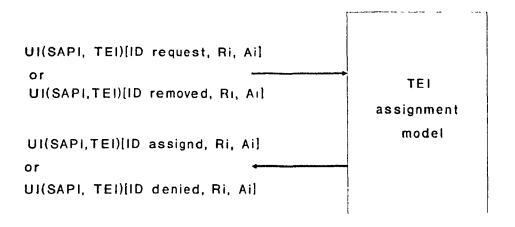

| 3.4  | Automatic TEI Assignment Task                                              | 47  |

| 3.5  | TEI Assignment Messages Format                                             | 48  |

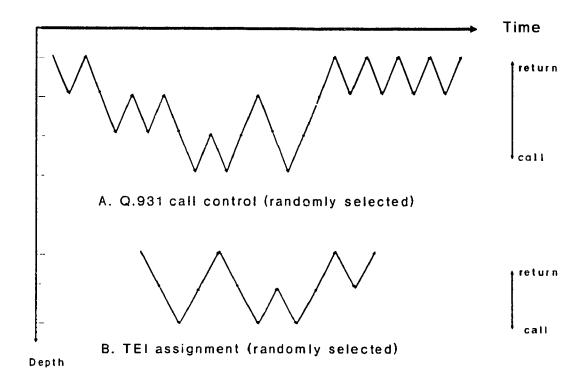

| 3.6  | Nested Procedures Behaviour                                                | 53  |

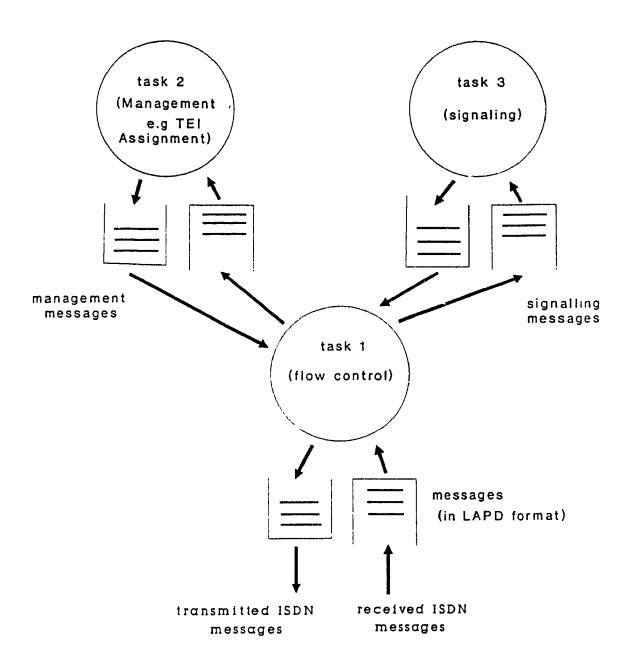

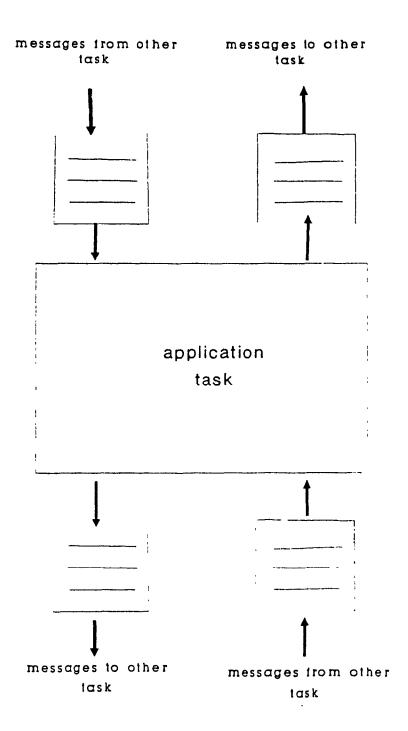

| 4.1  | Tasks Distribution and Messages Transfer                                   | 59  |

| 4.2  |                                                                            | 61  |

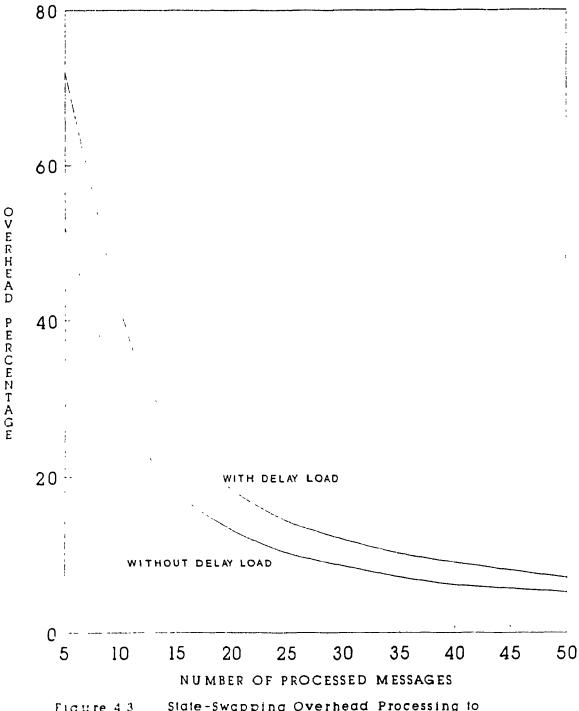

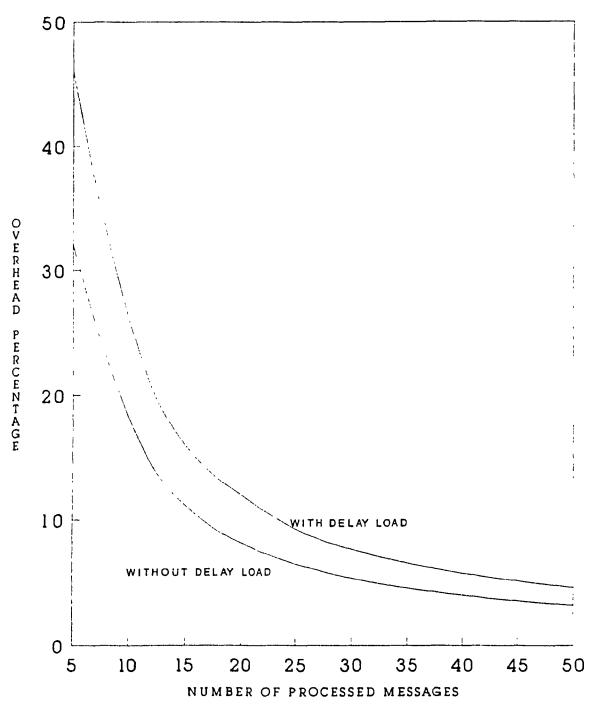

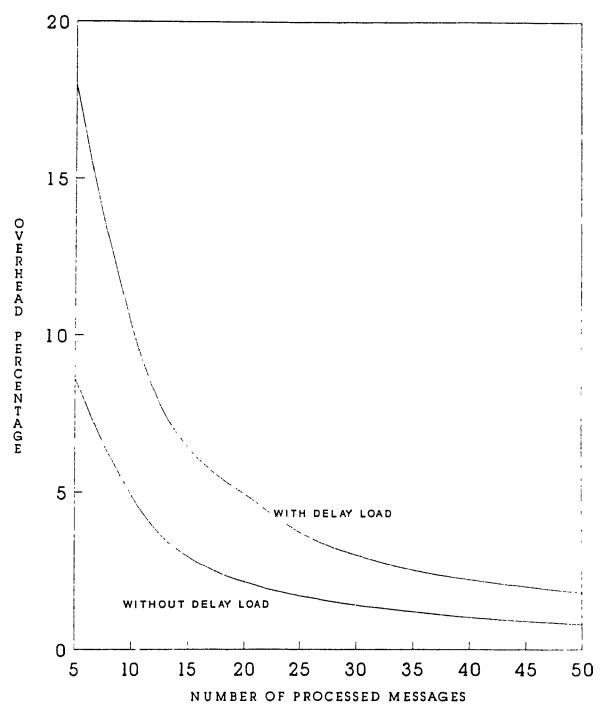

| 4.3  | State-Swapping Overhead Processing to Total Memory References (Q.931 Task) | 74  |

| 4.4  | state-Swapping Overhead Processing to Total                                |     |

|      | Machine Instructions (Q.931 Task)                                          | 75  |

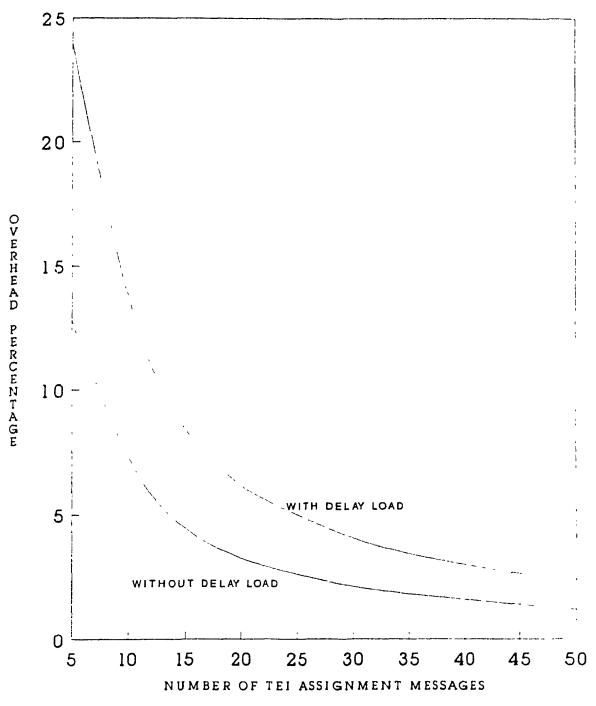

| 4.5  | State-Swapping Overhead Processing to Total Memory Reference               |     |

|      | (TEI Task)                                                                 | 76  |

| 4.6  | State-Swapping Overhead Processing to Total Machine                        |     |

|      | Instruction (TEI Task)                                                     | 77  |

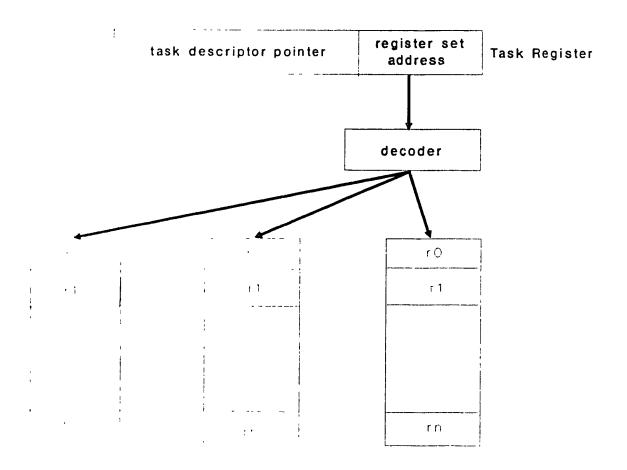

| 5.1  |                                                                            | 82  |

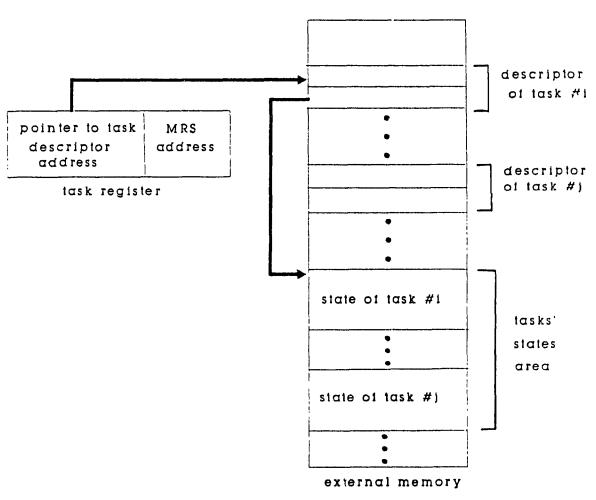

| 5.2  | Tasks Descriptor Organization                                              | 85  |

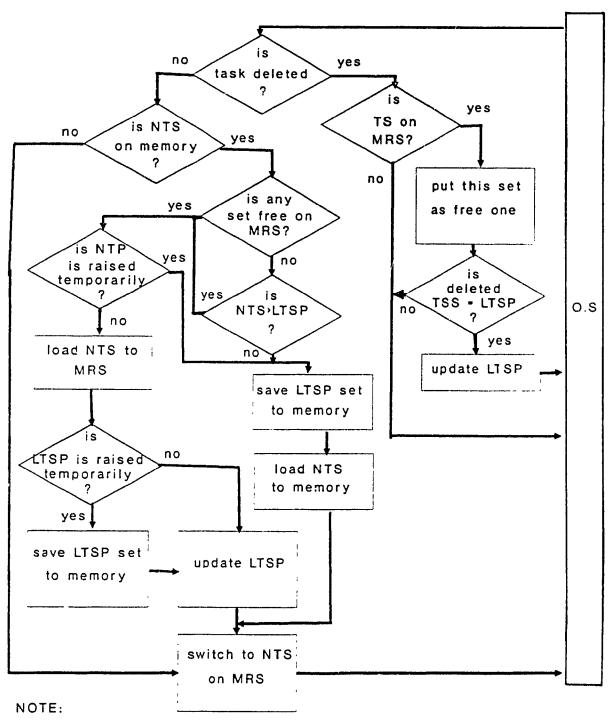

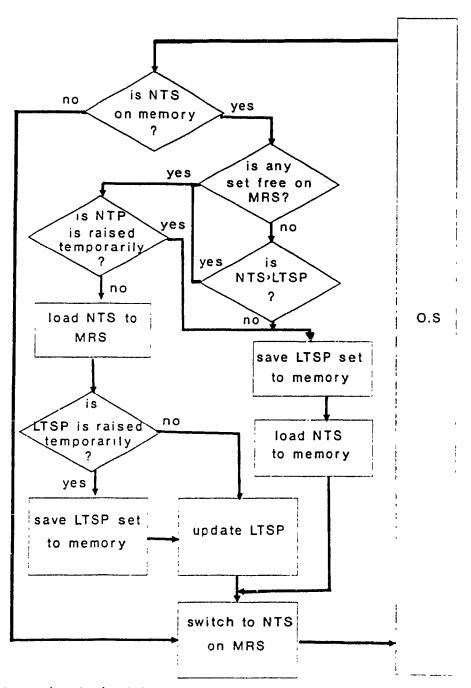

| 5.3  | Priority Strategy for Dynamic Systems                                      | 92  |

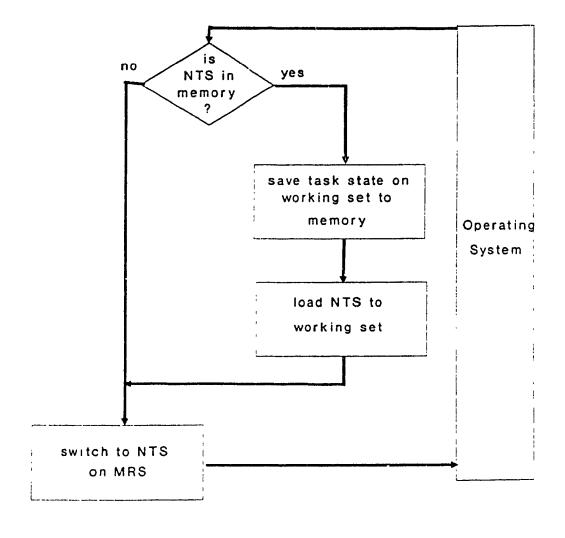

| 5.4  | Priority Strategy for Static Systems                                       | 94  |

| 5.5  | Priority Strategy for Static System                                        |     |

|      | (Assigning Task States in System Initialization)                           | 95  |

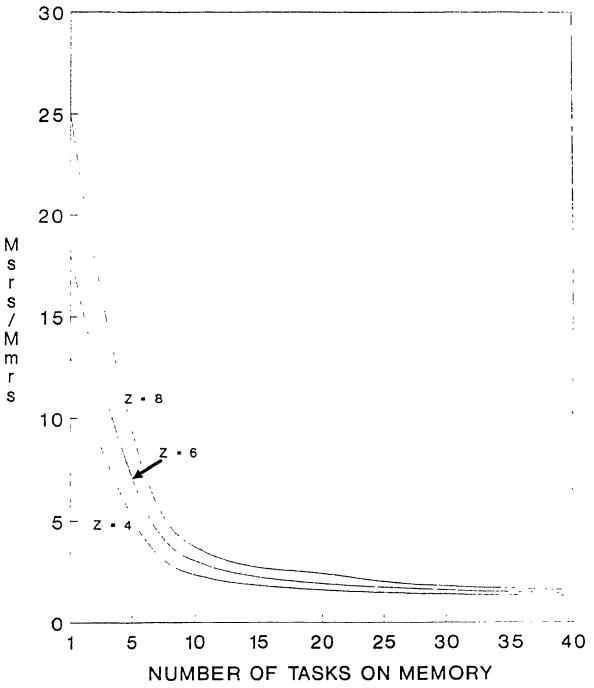

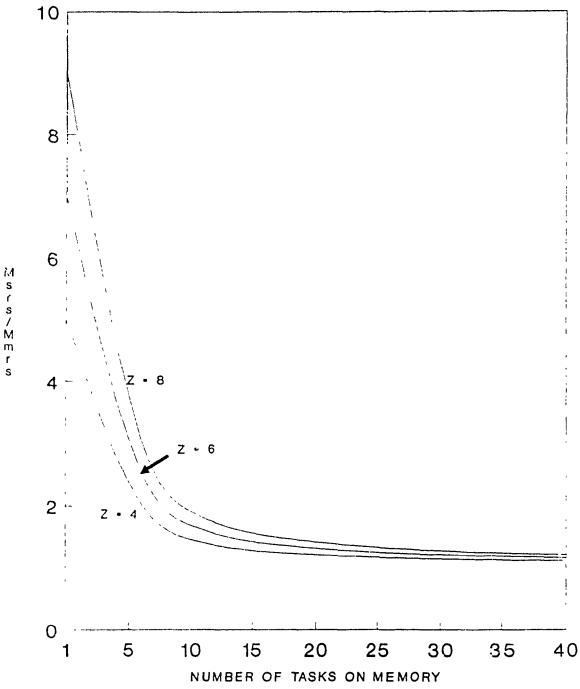

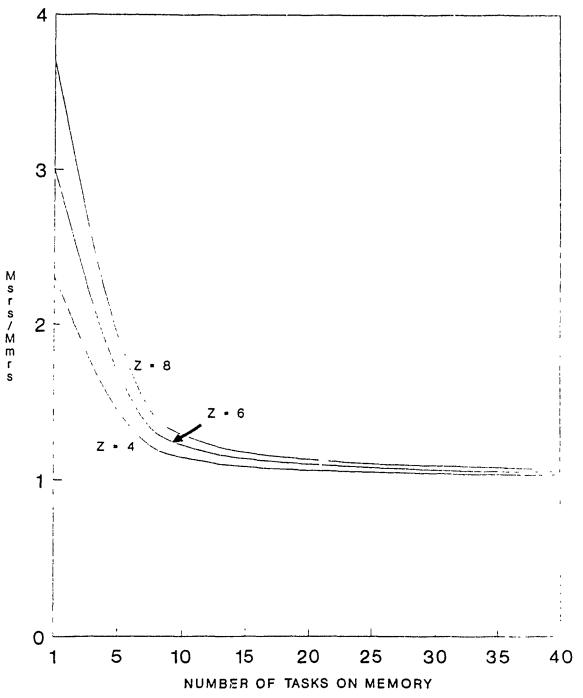

| 5.6a | a Comparing Performance of Mmrs with Msrs When P=0.25                      | 100 |

| 5.6t | Comparing Performance of Mmrs with Msrs When P=0.5                         | 101 |

| 5.60 | Comparing Performance of Mmrs with Msrs When P=0.75                        | 102 |

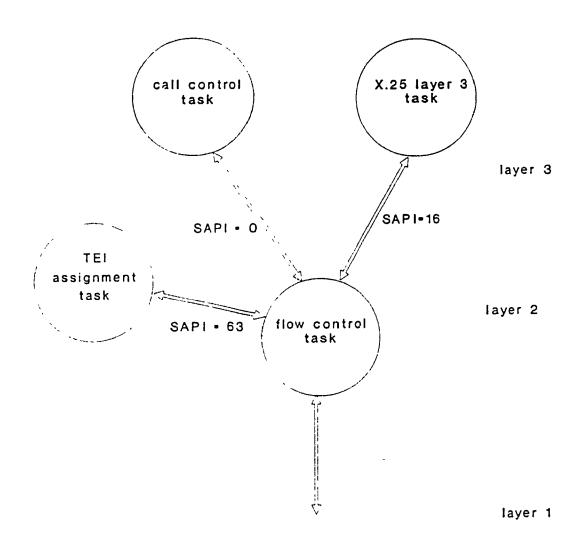

| 5.7  | ISDN User-Network Interface Processing Tasks                               | 107 |

|      | MRS-Based Processor Core                                                   | 110 |

| 5.9  | Listing of Simulated MRS Organization                                      | 112 |

| 5.10 | Listing of the Testing Vector for the Simulated MRS Organization           | 113 |

# viii

# List of Tables

| 3.1 | Relative Dynamic Frequency of HLL for Basic Call Control    | 51  |

|-----|-------------------------------------------------------------|-----|

| 3.2 | Relative Dynamic Frequency of HLL for ISDN TEI Assignment   | 52  |

|     | Number of Parameters Passed Between Procedures              | 55  |

| 4.1 | Processing Ratio of the State-Swapping Operation to the     |     |

|     | Q.931 Messages in Terms of Total Memory Reference           | 68  |

| 4.2 | Processing Ratios of the State-Swapping Operation to        |     |

|     | the Q.931 Messages in terms of Total Machine Instructions   | 69  |

| 4.3 | Processing Ratio of the State-Swapping Operation to the     |     |

|     | TEI Assignment Messages in terms of Total Memory references | 70  |

| 4.4 | Processing Ratios of the State-Swapping Operation to        |     |

|     | the TEI assignment Messages in terms of Total Machine       |     |

|     | Instructions                                                | 71  |

| 4.5 | Processing Ratios of the State-Swapping Operation to        |     |

|     | Average ISDN Messages in terms of Total Memory References   | 73  |

| 4.6 | Processing Ratios of the State-Swapping Operation to        |     |

|     | Average ISDN Messages in Terms of Total Machine             |     |

|     | Instructions3                                               | 73  |

| 4.7 | Average Overhead Processing for State-Swapping Operations   |     |

|     | in Terms of Total Machine Instructions                      | 78  |

| 5.1 | ISDN Processor Instruction Set                              | 115 |

#### CHAPTER I

#### INTRODUCTION

#### 1.1. Background

The trend towards digital communications has an impact on each type of transmission media and each type of switch used in communication networks. Transmissions over communications links are already heavily digital and will be totally so in the future. These communications links are intended for carrying the user information such as video, voice and data. The processors used within the nodes of these networks are to handle the received digital information and to perform the required communication nodes functions efficiently. The processed information will then passed to the required destination.

Optical fibers in today communications networks have provided a tremendously increased transmission bandwidth. This large transmission bandwidth has encouraged the support of more services and more users. Clearly, the increase in services and the number of users in a network has led to an increase in traffic volume. Consequently, the functions processed by the nodes would have to be performed at a faster rate and hence place a greater load on the processor within each node. For example, the Integrated Service Digital Network (ISDN), which has been proposed in last few years, allows more than one service to be processed simultaneously by the network. The terminals connected to ISDN switches will permit the subscribers to access various communication services through the use of a set of layered protocols that are defined by the I and Q series of the CCITT recommendations [1-4].

The Open System Interconnection (OSI) [20-24] model which was proposed in 1977 by the International Standards Organization (ISO), provides a solution to the problems of compatibility between computers from different manufacturers used in the same communication

network [25,26]. This model eliminates the problems found in information representation, communication techniques, and operating systems between computers used in the communication nodes [27]. Although the OSI model is comprised of a hierarchical seven-layered structure, only the first three layers are required for processing by the network nodes, i.e., physical, data link, and network layers. The ISDN user-network interface, Signalling System number 7 (SS7), X.25 are some examples of such protocols based on OSI model.

In general, the implementation of the first three layers functions can be done in both hardware and software. Layer 1 is always implemented by using hardware, part of the layer 2 functions can be implemented by hardware and the other part by software, while layer 3 is implemented by software. There are many VLSI chips which are used to perform the processing required by the hardware functions inside these layers [37,40,41,44]. Many general purpose processors have been used to support the processing required by the software functions of these three layers [47,54,57]. Designing a specialized processor to enhance the processing of these software functions has also been reported in small scale [49]. However, the specialized processors are not used widely because of their design complexity and high cost.

The latest development in the computer architecture has introduced a new approach in designing processors called the Reduced Instruction Set Computer (RISC) [69]. The reported success of RISCs as a high performance architecture has resulted in intensive research to investigate their performance, complexity, etc. However, the simple hardware design, the short development time and the high performance of the RISC-based processors would make the RISC architecture a promising one not only for general purpose computations but also for special purpose applications.

The work on RISCs has focused on the aspects related to RISC as a counterpart architecture to CISCs in general purpose computations. These researches examined the

instruction set from different directions, such as the justification of the choice of a certain instruction set; statistical programs measurements and evaluations; how the simple instructions were more utilized than the other complex instructions; and what their impact was on the code size; etc. Moreover, these researches also focused on the evaluation of register set organization and the number of these registers as well as their impact on the performance of this architecture. The performance measurements were evaluated by employing conventional benchmarks and by using simulation techniques. So far most of these studies have concentrated on the general purpose computations and have omitted studying this architecture for processing in specialized applications, such as for communications applications and specifically for the processing at the network nodes. The limited researches and studies for RISCs role in data communications network nodes processing along with the need for high efficient processors to cope with the demands to support the requirements speed of these applications, has directed this research towards investigating current RISC architectures with respect to their suitability and possible enhancements to supporting these requirements.

#### 1.2. Thesis organization

The material presented in this thesis is organized into two parts. In the first part, data communications processing is investigated and emphasis is given to the network nodes processing. This part has two major objectives: first is to study the frequently used general operations in such processing, and the second is to highlight the current architecture of communications network nodes in different perspectives. These perspectives can comprise of node hardware structures, the processors used as well as their types, and the multiprocessor supports. Moreover, the investigation to the candidate processor architecture to be used in such processing is done by analyzing and comparing the available architectures, namely CISC

or RISC. The merits and drawbacks of the current RISC architecture are studied. It also focuses on the motivations in using the RISC concept to build high performance data communications processing architectures. Following this, we will also highlight the possible work directions to be investigated in this research.

The second part focuses on the selection of suitable RISC architectures, and to investigate their drawbacks in supporting data communications applications in which task switching operations occur frequently. In chapter 3 attention is focused on the characteristics of the data communications software, by using a RISC-based computer system. Examples of these characteristics are, High Level Language (HLL) statements frequencies, processor-memory traffic, and procedures nested depths. The results shown in this chapter are used in the following chapters to clarify the RISC architecture type which is more appropriate to this application. Chapter 4 investigates the impact of RISC architecture on increasing the task switching overhead by increasing the state-swapping cost. This has been studied from two perspectives: the register set used in RISC, and the use of optimizing compilers. The stateswapping cost is also measured for different data communications processing workloads. In chapter 5, the enhanced RISC architecture for this application is considered by adding Multiple Register Sets' (MRS) organization, viewing the impact of MRS on the performance enhancement of RISC, and by supporting MRS with a strategy to distribute tasks states to these register sets. The effect of this organization on RISC architecture is investigated along with the possible changes that we would include with RISC to incorporate this organization. Also derived and evaluated the numerical method used to measure the performance improvements, which can be achieved in comparison to the RISC architecture with a Single Register Set (SRS). The priority strategy is derived and investigated in order to determine if such a strategy could further increase the performance by using it with MRS and estimate its enhancements. Finally, RISC-based architecture using MRS is highlighted with the necessary instruction set.

This work is concluded in chapter 6. Some final recommendations for the further work are also presented.

#### **CHAPTER 2**

#### PROCESSING IN COMMUNICATION NETWORK NODES

It is the intent of this chapter to develop background material related to the main aspects of computer architectures for data communications processing. This chapter attempts to investigate the following topics:

- I. The processing features of a network node in data communications: This will help us to understand the nature and structure of both hardware and software implemented in these nodes.

- ii. The technologies currently used to implement such applications in presently existing systems: This will review the status and possible drawbacks of the actual implementations using currently available technologies.

The outcome from the study of the above topics will derive the motivation for this work.

It is also used to set the direction of our work and the general approach to reach our goal.

#### 2.1. Processing Features

To find appropriate support to improve the processing performance in the network nodes, it is important to investigate the processing features. This section will study and analyze the processing features of data communications from three angles: their layer structure, instruction set, and software organization.

#### 2.1.1. Layer Structure

The OSI model distributes the functions of the data communications processing in

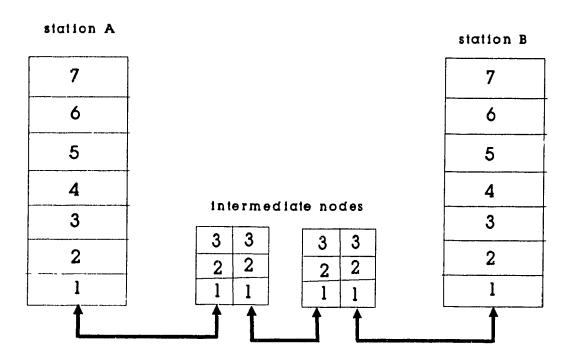

seven layers: Physical, Data Link, Network, Transport, Session, Presentation, and Applications (Figure 2.1). A network node usually includes only the first three layers. Since in this work we emphasize on the network node processing, the attention will be only given to these first three layers.

Layer 1 (or Physical Layer) takes the responsibilities for the information transfer over the links. This includes the electrical requirements of a data communication channel, the physical interface between devices and the rules by which bits are passed from one to another. The data link layer (layer 2) attempts to make the physical link reliable and provides the means to activate, maintain and deactivate the link. The main service provided by the data link layer to the higher layers is that of error control and flow control. The network layer services are responsible for establishing, maintaining and terminating communications.

Many protocols based on OSI models have been developed. Although the general functions are similar, each protocol can include some variations. Thus, it is useful to consider one of these protocols as an example for clarify the discussions throughout this work. Since ISDN become very important in today's and future of data communications applications, the ISDN usernetwork interface protocol is chosen as an example in this thesis.

The ISDN protocols, which are specified by CCITT [1-4], has defined many procedures and capabilities within the first three layers. CCITT has recommended that the Basic Rate Interface (BRI), (25½-D), of layer 1 of the ISDN user-network run at 144 kbit/s, and the Primary Rate Interface (PRI) rate 1544 kbit/s (North America and Japan) and 2048 kbit/s (for Europe). Layers 2 and 3 support a wide range of service capabilities. The physical layer provides simultaneous, bidirectional transmission of information signals synchronized with the network. In the case of the basic access, the physical layer also enables orderly activation and deactivation and regulates simultaneous access by several terminals to the common D-channel. In PRI, this

Figure 2.1 ISO Open System Interconnection

Reference Model

layer supports the point-to-point configuration, while no activation/deactivation capability is supported. Since this layer is always implemented in hardware, we will focus our attention towards the software aspects of layers 2 and 3.

It was intended by CCITT, that their recommendations for layer 2 and 3 should be applied to a variety of interface structures, such as basic access and primary access [81]. Layer 2 recommendations describe the link access procedure on D-channel, called LAPD. LAPD is on the basis of balanced mode HDLC such as X.25 LAPB. LAPD provides information transfer capabilities via point-to-point data links and via broadcast links. In order to handle multiple terminal installations at the user network interfaces as well as multiple layer 3 entities such as signalling and packet communication, LAPD has the capability of supporting multiple data link connections simultaneously on a single D-channel. In order to identify a specific data link connection, layer 2 address field consists of two subfields, namely, the data link layer Service Access Point Identifier (SAPI) subfield and the Terminal Endpoint Identifier (TEI) subfield. Layer 2 also provides two forms of information transfer services, either the Unacknowledged Information (UI) or the Acknowledged Information (AI) with multiple frame operation only. Layer 2 supports the TEI assignment procedures to automatically assign a TEI value to newly connected user terminal equipment at a specific user-network interface point. In this case no manual setting of a TEI value is necessary every time terminal equipment is connected to a user-network interface point.

Layer 3 recommendations describe the procedures for establishing and clearing of network connections such as circuit-switched connections using B-channel, user-to-user signalling connections using D-channel, packet-switched connections using either D-channel or B-channel. The main feature of this layer is the handling of the wide variety of connections as mentioned above through the same user network interface. This user network interface includes the

procedures for terminals operating in a stimulus mode to facilitate functional expansion for such terminals. The message structure of layer 3 consists mandatory and optional information elements to be discussed in more details in Chapter 3.

#### 2.1.2. The Instruction Set

The use of suitable instructions for specific applications, such as data communications, will enhance the processing and make the processor more efficient than other processors designed for general purpose applications. In order to define the type and quantity of instructions within a set, it is necessary to study and analyze the software functions which are required to be executed by the processor. This study will help us to answer some important questions such as:

Are there general purpose or special purpose instructions required with this set? Should the instructions be simple or complex? Are all instruction groups (e.g., logic, arithmetic, etc.) necessary to be supported or could these groups be reduced by eliminating some of them?

The objective of this section is to answer these questions, and in order to do so it is important to first understand the nature of the processing functions that the processor should perform in order to provide the required services.

The software processing part in the communication nodes usually deals with layer 3 and part of layer 2, as layer 1 and lower part of layer 2 are often implemented in hardware. Thus, the instructions used for layer 2 and 3 processing are the ones which define the type of instruction set required for the node processor. The instruction set used for these layers depends on the type of functions required to be handled by these layers. Hence, the study of these functions is important in determining the kind of required instruction set.

The amount of services and the complexity of these two layers become very large due to the different services which are required by different users, and these services are continuously increasing. For example, the ISDN access nodes are required to support signalling, circuit-switched, packet-switched, and telemetry traffic. Software characteristics of the network node protocols can affect the instruction set in the following manners:

- i. Programs implementing these protocols are large and complex, due to the large variety of required functions. For example, the implementation of layer 3 of the ISDN user-network interface protocol (Q.931) is done with about 70K of assembly code [29]. Required functions are of general purpose type such as searching databases, scanning messages, checking service availability, etc. Since the processing of these functions of the general purpose nature needs a processor to support such processing, the general purpose instructions are necessary to be supported in the processor used to handle the data communications functions. Also, note that complex numerical computations are not required.

- repeatedly. These repeatedly used functions give the impression that there could be a need for special purpose instructions. The investigation of the nature and the processing of some of these repeatedly used functions will help to have a clear answer. Let us consider the following repeatedly used functions: scanning and wrapping / unwrapping messages. In scanning messages, all messages arriving at layer 2 or layer 3 were required to be scanned to determine the type of service required; identification of the called terminal; and to verify the correctness of the message fields [4]. These messages are partitioned into many fields, each of these fields is dedicated for a particular service. At the receiver, each field is tested, and this processing of message scanning can be realized by a sequence of Compare and Branch instructions. Thus, there is no need for special instructions and therefore the general purpose instructions can be used here. The

other special function, i.e., wrapping / unwrapping operation, is required when the messages pass between the layers, particularly between layers 2 and 3 (usually this is done in layer 1 by the hardware which strips and inserts the flags) in which layer 2 strips off the information which will not be used by layer 3. For instance, the message address part (consisting of two fields, Service Access Point Identifier or SAPI and Terminal Endpoint Identifier or TEI) and the control field within the LAPD frame format messages, in the ISDN user-network interface messages, are inserted back when a response message is received from layer 3. Similarly, this can occur when a signalling message in the ISDN user-network interface is passed on to layer 3 of the call control. If the destination user number is not in this local node, then the signalling message will be forwarded to another node via the Signalling System number 7 (SS7). In order for this operation to be carried out, the signalling message must be embedded within the SS7 message header format [30]. This wrapping/unwrapping operation can be processed by using general purpose instructions in which the wrapped information could be ORed with the original information, while the unwrapped could be handled by ANDing the unrequired information with logical zeros, i.e., masking operation.

It is clear from the above discussion that the instruction set to be supported by the node processor includes simple and basic general purpose instructions such as AND, OR, BRANCH, COMPARE, etc. Special instruction(s) can be useful for this application and enhance the processing performance. For instance, the NTT processor which is designed for data communications nodes processing is supported by some special instructions for the path scanning operation [49]. However, having some special instructions within the instruction set will not change the type of the instruction set from a general purpose one. Many processors with general

purpose instructions are used in such applications, e.g., Intel 80386, Motorola 68020, etc.

#### 2.1.3. Software Organization

#### 2.1.3.1. System Software

When different data communications services with different priorities are concurrently processed, it is important to have the means to process the high priority service first. For instance, if the processor executes functions of two different services such as packet data and telephone signalling, then the packet data processing can be interrupted when the voice service needs processing. Clearly, this happens because the voice service is considered to have a higher priority than the packet data service due to the delay-sensitive characteristics of the voice service. The processing of such services can be managed in different ways. In the first way, the processor can continuously look for the types of messages arriving at the node. This is a polling technique. Clearly, it will require to stop the current processing until the processor finishes the execution for the arrived message. Normally when a signalling message arrives during the processing of a data message, the processor will decide to momentarily stop the data message processing and serve the signalling message. However, if the processing of the data message is very short and does not seriously delay the processing of the signalling message, the processor will continue to serve the data message and store the signalling message in a buffer. When the node processes a signalling message and receives another signalling message, a buffer should also be used to store the arrived message until it reaches its turn for processing. The use of many services with different priorities and more messages types will make the software for managing the system operations very complex and reduce the processing efficiency.

The above mentioned polling technique is not efficient. Interrupt technique can be used to enhance the performance. Each of the services used can be implemented as an interrupt

service routine. However, it is still important to implement and manage the message buffers and to schedule the operation of such service routines based on their priorities. It is also important to give the services with low priority a chance to be processed when the high priority service has many messages in its buffer waiting to be processed. A possible synchronization technique can be implemented by allowing the process of one or few messages of low priority service from time to time when the high priority service processes certain number of messages. In addition, the processing of data communications protocols also requires responses and actions in real-time. For instance, if the signalling messages are sent to the other node and no response is received within a specific time interval, the transmitting node will be interrupted by the real-time clock and an appropriate action will be done by the node such as retransmitting the message.

In order to avoid the network node software designer from taking care of synchronization, scheduling, rr essages buffering, etc., a real-time multi-tasking operating system is normally used. This will simplify the task of developing software for the communication nodes and increase the processing performance. Such operating systems are designed to make the processor to be efficient and to give a quicker response to the tasks which require it most. Thus, the node software will be developed as a group of logically separated modules or tasks rather than a single program [27]. This Intel iRMX [36], Duplex Multi-Environment Real-Time Operating System (DMERT) [54], MCPOS [47], and CTRON [59, 56, 58] are few examples of such operating systems.

Generally, these operating systems suffer from two types of overhead: the messages passing and task switching. Practically, passing a long message between tasks is very time consuming and hence passing the pointers (or tokens) of these messages rather than passing the whole message itself greatly helps in reducing this overhead [35].

Task switching usually occurs due to the suspension of a running task, either deliberately

or voluntarily, to allow another task to run. Basically, tasks are switched during different events such as when an interrupt occurs and requests a task to be run, which preempts the currently running task if this next running task has a higher priority than the current one. Task switching also occurs when a high priority task which is in ready state waiting for an object and this object becomes available; then the task will run immediately if it has a higher priority than the currently running one. Moreover, a task is switched when its time slot or limit has expired, and the operating system will schedule the next task in the ready list to run. The processing overhead of this operation consumes some of the overall processing. Hence, reducing this overhead will improve the system performance.

Different possible ways can be used to reduce the task switching overhead. For instance, designing the tasks in an efficient manner, by keeping the number of tasks minimal and especially by binding the heavily related tasks which need a large amount of data exchange. However, this could have a negative impact on software being developed and modified by making it more complicated, time consuming and costly. In systems where tasks running time is short, it is possible to let every task run to the end, and hence no preemption scheduling is implemented [47]. Clearly, this will reduce the task switching frequency since a task will relinquish the processor only when it has completely finished, thereby not allowing any other task to preempt it. However, this is not applicable where different services are implemented with different priorities and the tasks durations are lor.g.

#### 2.1.3.2. Applications Software

Each of the protocol services can be processed as one or more tasks [27]. As the services provided by these protocols become larger in today's and future communications systems, the software represents the service within these layers will need to have more tasks

where each task will represent a service or some functions of a specific service. For example, in the present ISDN user-network interface protocol, layer 3 or Q.931 call control provides a basic and supplementary signalling service in addition to the User-to-User Information transfer (UUI) and the packet data services. Layer 2, on the other hand, includes the management functions which are called the "TEI assignment" in addition to other functions supported by this layer [31-34].

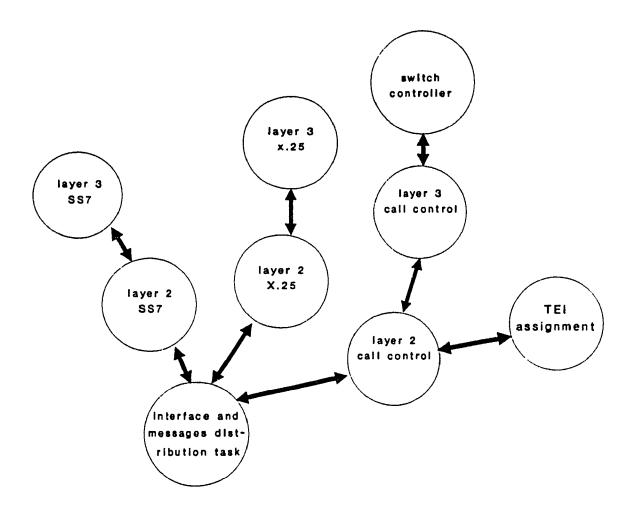

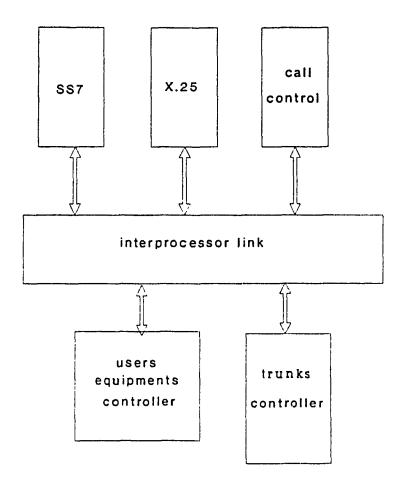

The distribution of the application tasks are basically dependent on the size of the nodes, i.e., the small size nodes have different task distributions than the medium and large size nodes. In small nodes where the traffic capacity is small, only one processor may be sufficient to manage the processing of the whole node software and to provide the users with the required service within a minimal processing time. The nodes software is basically organized in such a way that to improve the performance. Organized tasks differ from one node to another depending on the amount and type of services required. As the amount of these services increases, the tasks structure becomes more complex since each service might need more than one task. For example, in the ISDN access node with low traffic capacity, the distribution of the tasks can be managed as shown in Figure 2.2 (only the applications tasks are shown here). Depending on the supported services, some nodes might implement only a subset of that shown in Figure 2.2. For instance, in the ISDN point-to-multipoint subscriber radio system which organized as a star topology network the need for the SS7 support as an inter-signalling between the system nodes is not necessary, and can be substituted by a simple signalling system [5-10].

The concurrence nature of these asynchronous tasks have led to the use of mailboxes to transfer messages between each others. A task can be switched to get control of the processor when it is in ready state and has higher priority than other tasks. Otherwise, if tasks are organized in such a way that they have to be switched for each arriving message, the

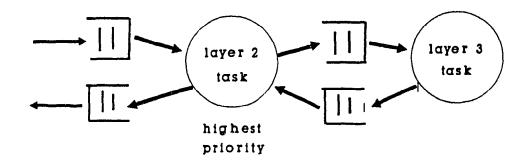

Figure 2.2 Possible Task Distribution in a Low-Capacity Network Node

communications processing overhead is increased and as a consequence the system throughput decreases. Thus, the communications and tasks processing should be balanced. Tasks switched with the arrival of each message makes the processing delay per message a minimum, however, the throughput of the processor will also be reduced due to the high task communication overhead. To illustrate the frequency of task switching in applications under heavy message passing between tasks, we can use a node with two application tasks representing layers 2 and 3 in two separate tasks respectively (Figure 2.3). When layer 2 has a higher priority than layer 3, layer 2 can process the messages in its input mailboxes until no more messages are left at which time task switching will occur allowing layer 3 to start processing (Figure 2.3a). Clearly, if the traffic to the node is high, then layer 3 will not be able to provide processing within an acceptable time limit unless the operating system intervenes to stop a layer 2 task and start a layer 3 task. In another possible tasks organization (Figure 2.3b) assuming that a layer 3 task has a higher priority than a layer 2 task, then each message received by the layer 2 task will be processed and passed to the mailbox of layer 3 task. The layer 3 task will then preempt the layer 2 task, process this message and return a response message (if necessary) to the layer 2 task mailbox. Therefore, with each incoming message to the node, there will be two tasks switched (one switched to layer 3 and one switched back to layer 2). This will increase the task switching overhead and reduce the processing throughput, but provide minimal message processing delay. Should the organization of these tasks be such as to process a few messages before they switch to another task, this will reduce the task switching cost at the expense of increasing the message processing delay. This will then allow each task to process a number of messages before task switching occurs.

In situations where the communication node becomes heavily loaded with traffic, it is not practical to keep all the communication node tasks to be processed confined to just one

A. Layer 2 with Highest Priority

B. Layer 3 with Highest Priority

Figure 2.3 Distribution of Layer 2 and 3 Tasks

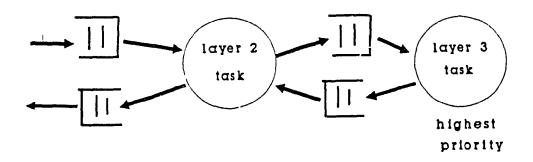

processor. Processor costs have dropped drastically in the last decade, making the use of multiprocessor in supporting nodes processing feasible. Node tasks can be partitioned to run in different processors based on the services each provide, i.e. the tasks providing the call control of layer 3 can be separated into one processor, while the tasks used to implement packet data are separated into another processor and so on (Figure 2.4). The distribution of tasks in this way accommodates the adaptation of new services in the future, hence making this a suitable solution for the most recent data communication nodes, i.e. such as ISDN nodes. Task switching overhead associated with the processing of such nodes is the same as the one discussed before for single processor systems. In addition the inter-processor message transferring introduces another overhead. Tasks distribution for multi-processor systems should be configured in such a way as to reduce this overhead. One such method of reducing this overhead is by allocating tasks of one service to the same processor [46]. This will minimize the message transfers between processors thereby reducing this overhead as well as a potential bus bottleneck. In such a configuration inter-processor message transfers only occur when a need arises to pass a message from one service processor to another.

#### 2.1.4 Some Concluding Remarks

The instruction set used in any general purpose processor is generally classified into different groups, as follows:

- General purpose instructions groups which are usually partitioned into different groups such as data movement, basic logic, arithmetic, branch, etc.

- ii. Special instructions to support the system operation, such as instructions for task switching and for virtual memory support.

The processing for data communication nodes is required to perform non numeric

Figure 2.4 Distributed Processing in a Communication Node

functions such as scanning messages, data base searching, etc. Since all of these functions are not numeric-intensive type, the processor used for data communications applications will be different from the processor used for other applications such as robotics and digital signalling processing, which are numeric-intensive applications. That is, the support for the floating point operations can be omitted from the processor support for this application. The support for this operation generally requires a large area of the chip which can be used to support other useful features. The other support for the operating system is still very important to be included within the processor used for this application because the software structure of the network node processing is usually implemented with different software tasks. The support for virtual memory is also very important in view of the large amount of data being used in these types of application.

#### 2.2 Implementation of Network Node Functions Using Existing Technology

Communication protocol processing has been strongly enhanced in the last few years. This enhancement has been achieved with VLSI chips known as protocol controllers [37]. Software functions in both layers 2 and 3 have been implemented by both general purpose processors and specialized processors. Processors used in communication nodes should be suited to multiprocessor configurations in order to enhance node performance for nodes with high traffic demands. This section will emphasize on the current implementations for these software and hardware functions and the type of processors used to enhance the performance.

# 2.2.1. Implementation of Hardware Functions

The functions which are performed by layer 1 and layer 2 such as bit rating, CRC, flag insertion and deletion, etc., can be implemented by hardware. Progress in VLSI technology has

made possible the realization of special protocol controllers. Processing layer 1 and part of layer 2 can be done by these protocol controllers to relieve the load of the host processor.

Many chips which are available today are designed for processing specific protocols. They cannot be used for different protocols and also become useless if the protocol has been modified. The latter case has led to the design of partially programmable controllers. This feature is very usefu! to cope with highly possible changes since typical protocol standards are usually imprecise and incomplete [37].

One common feature in the architecture of these protocol controllers is the incorporation of Direct Memory Access (DMA) and buffer management capabilities. The reason behind this is more feasible to store the user data in a common area of the host computer memory as opposed to storing it locally within the protocol controller itself. Moving data to and from the host memory requires a DMA interface. In addition, the protocol controller needs a simple method for accessing and referring to these buffers. This buffer management operation is a significant data management function.

Many chips are available today which are classified as communication controllers such as MC68605 X.25 protocol controller [39], MC68302 Integrated Multiple processor [38], and MC68824 Token Bus controller [40] from Motorola, 82586 Ethernet LAN controller chips from Intel [41], the VLSI implementation of the X.25 protocol from the Nippon Telephone and Telegraph Company (NTT) [42], etc. Some controllers are also available to sup, if the ISDN protocol processing, such as the support for the multiplexing of its D-channels [43], a complete chip set supporting the subscriber access protocol [44, 45]. Clearly, there are many chips available for processing of different data communications protocols and they can be used as peripheral devices of the node host processor(s) to achieve a higher performance.

#### 2.2.2. implementing Software Functions

The layer 2 and layer 3 functions such as the management, database processing, message scanning, etc., are generally implemented in software and executed by the node host processor. The host processors used in communication network nodes, in general, comprise of general purpose processors or special processors. The general purpose processors are always available and can be used immediately, whereas the special processors can only be used once they have been developed and produced. Clearly, the special processors designed for data communication processing provide higher performance than the general purpose processors, because their design is tailored to a particular application.

#### 2.2.2.1. Existing Host Processors

Basically, the design of the general purpose processors is intended to be used in different applications, and hence their structures are such that to provide a variety of features to satisfy different users. This makes their structures complex. Unfortunately, these processors cannot provide all possible features on the same chip because of certain limitations, such as the number of transistors which can be integrated on one chip, complexity of the designing chip, high costs, etc. These limitations have led to compromises, that is, keeping on chip the features which are believed to be more frequently used than others. For instance, in the Intel 80386 chip the memory management is kept on-chip while the floating point unit is integrated in a special floating point coprocessor. All of these type of processors have some type of supporting chips such as coprocessors to support them in applications that require some feature which is not directly available by these processors. For example, if the application requires many interrupt lines, an interrupt controller support chip can be used to enhance the host processor in dealing with this demand, likewise, a DMA controller can be used when there is a need for high speed data

transfers.

However, the comprehensive structure of these processors has two main drawbacks when using them in special applications:

- i. A high percentage of the chip resources will not be used. For instance, a processor with a virtual memory support on chip will not need to be used if the target application requires only a small memory size.

- ii. The complexity of their structure has an impact on their performance. Clearly, the use of larger hardware on chip will have an effect such as reducing its operation speed.

Moreover, having a large set of complex instructions will contribute to the difficulties of maintaining the streamline of the pipelining operations.

Despite the drawbacks of the general purpose processors, many of today's communication network node processing is achieved by using some of the available general purpose processors due to their low cost and their availability. The HDX10 distributed control digital switching [46], class-5 exchange [47], etc., are few examples for nodes used general purpose processors in their node design.

One of the key points in selecting a processor to be used in communication network nodes is the performance in terms of the processing speed. Therefore, it is crucial to have a host processor capable to achieve this objective. The limited performance of general purpose processors has led to the implementation of some specialized processors to provide the high performance processing requirements of these nodes. Specialized processors always incorporate within their architecture some special supports to enhance their performance when they work in a special environment. Generally, these specialized processors are designed to support specific applications (e.g. image processing, data communications, signal processing), others support the

specific programming languages, (e.g. C. Prolog, smalltalk, Lisp), and some support specific system configurations (e.g. data-flow machines, systolic array) [48].

In communication network nodes, a few special processors are used to enhance the processing. One example of these is the chip set designed by NTT [49]. One of their chips has been specifically designed for instruction execution which are required in such applications such as manipulating of bit-wise data. The processing of these instructions are implemented by a microprogram control unit within the chip. The reason behind having a processor with such instructions is to substitute using a general purpose processor by a more efficient specialized processor. The main objective of the other chips in this chip set is to reduce the amount of circuitry which usually used to interface between the host and the chips used for controlling the subscribers lines, i.e., the work like the controllers chips which mentioned before. This set of VLSI chips is designed to be configured in a multiprocessor environment, and hence can support a small to large network node processing need. The D70 digital switching system and the D51 packet switching system utilize this chip set [50, 51].

#### 2.2.2.2. Multiprocessor Configurations

Communication nodes are required to provide service over a broad range of traffic capacities, i.e. they should efficiently provide services for either small or large traffic capacities at each node with minimal delay. Hence, the processing system of each node should be flexible enough so as to accommodate different traffic capacities requirements. Moreover, with on going development in communication systems, extra services may be required. In order to integrate such services easily then the node required to handle them must be easily upgradeable. These nodes should also be high reliable in order to keep providing services without any interruptions. Such requirements will need to have a high degree of modularity and control distribution in the

communication node design.

To support these requirements, processors used in communication nodes should be able to provide the appropriate enhancement needed in order to easily modify a multiprocessor based node. There are two types of multiprocessor systems used for large and medium node processing: the "tightly coupled", where processors communicate through a shared main memory, and the "loosely coupled" in which each processor has a large local memory. Both types are used in present communication node processing [46]. The high performance achieved by using the loosely coupled structure has made it a more favourable one for these type of applications [52].

To facilitate functional expansion required by these nodes, the node functions should be shared between node processors. A suitable division of the switching program in a system is to dedicate each processor to a certain service; this division is also known as "function sharing" [51]. For instance, the line processor carries out subscriber signalling processing and line concentrator functions, while the call control processor carries out service analysis and call control tasks.

Clearly, sharing the node functions between processors can allow new equipment and services to be introduced without affecting the other processors which are not concerned. Moreover, function sharing reduces the communication between processors and therefore reduces the traffic congestion on the system bus while increasing the overall system performance. In spite of this reduction on the system bus, it is still important, with the large traffic and long message lengths in present communication nodes to reduce these effects even further. For instance, a Message Passing Coprocessor (MPC) can be used to move this overhead from the main processor and therefore increase the processing parallelism and enhance the systems performance, e.g. Intel 80389 MPC [53].

# 2.3. Reduced Instruction Set Computers (RISC)

The use of an efficient processor to perform functions of higher layers in the data communications is an important issue. The latest developments in computer architectures have made possible to design a high speed general purpose processor based on the new concept of the Reduced Instruction Set Computers (RISC) which can provide the performance higher than the CISC-based processor [69].

In 1975, IBM designed a minicomputer, called IBM 801, in order to achieve a better cost/performance ratio for High-Level-language (HLL) programs which endorsed the idea of simple hardwired control [61]. Although at that time the term RISC was not well defined, this IBM trial is considered to be the pioneer in the building of the RISC machine. At Berkeley, in 1980, Patterson and his research team investigated the RISC architecture and constructed the first RISC processor. By 1981 and 1983 respectively, the RISC I and RISC II processors were the outcomes of this intensive research [62]. Meanwhile, Hennesey's efforts at Stanford University resulted in the microprocessor without interlock pipeline (MIPS) RISC processor [63,64]. The success of RISC architecture have made many of such processors to be available in the last years, such as the CLIPPER [74], MC88000 [65], I860 [66], and R2000/3000 [67], etc.

The performance of the RISC-based processor has been evaluated in the first prototype RISC processor (RISC I). It was measured by comparing RISC I performance with some existing CISC microprocessors [69]. The research outcomes of these RISC prototype machines have shown that their performance is higher than that of existing CISC machines. There are many reasons behind the higher performance of RISCs. They are as follows:

i. Using complex instructions requires additional hardware components placed on the data path that may be part of a critical data path. Longer wires and extra circuitry results in slowing down the overall machine cycle, thus slowing down instruction execution.

- ii. Many complex instructions can be executed faster when they are replaced by a sequence of simple instructions. For example, substituting the use of the instruction LOAD MULTIPLE which is used in an IBM-370 with a sequence of simple LOAD instructions has been proven to execute twenty percent faster than its complex counterpart [61].

- iii. The simple instructions used with RISCs are typically executed in one cycle. This has a positive effect on pipeline operations by allowing them to operate at a maximum speed. Clearly, complex instructions will force the pipeline to freeze in certain circumstances, and hence the full advantages of using pipelining cannot be explored. The use of simple instructions helps to manage data dependencies easily and efficiently (as will be discussed in the next chapters).

- iv. Other reasons such as the use of large specially organized internal registers contribute to the high performance as is characteristics of RISCs. This topic will be discussed in the following chapters.

It is useful to mention here that the technology used in implementing a processor has a great effect on the processor's performance, e.g. implementing processors with ECL technology will provide faster processors than implementing them with CMOS technology. The latest developments with Gallium Arsenide (GaAs) has made it possible for processors to attain a much higher speed than those using ECL technology, have a lower power dissipation and can integrate about 30K transistor on-chip [70, 71]. This achievement is very important when considering the Stanford MIPS which was developed using around 24K transistors, i.e., it is possible to use GaAs to develop a RISC as such taking advantage of this very high speed technology [14]. However, the complexity of the CISC architecture requires a large number of transistors to implement such processors far too many than can be implemented with this technology.

The development of CISC processors is a very costly and time consuming process. The RISC processor design has minimized this to the lowest possible level. This minimization comes from the simplicity of the RISC architecture and the large degree of design regularity. This design regularity and effective utilization of the hardware resources are very important factors in VLSI design. The impact of these factors has reduced the developing cycle of these RISC-based implementations which in turn has reduced their productions cost. This was considered an important aspect in adopting RISCs to design a processor working in different applications, and more specifically the specialized ones.

## 2.4. Motivations of This Research

There is no doubt that using an efficient processing element in the data communications network nodes is a crucial factor in increasing the overall node performance. This is the main reason why in this research we have focused on searching for a way to improve the efficiency of these nodes through concentration at the processor level.

The research motivations can be summarized by the following points:

- As was mentioned in the previous part of this work, the RISC concept provides sultable and useful features, e.g., high performance RISC-based processors; a short development cycle at lower costs than CISCs; and very high performance processors with high-speed technologies such as GaAs. These have made the RISC architecture more favourable than the CISC architecture for use with data communications processing software at the network nodes. Moreover, the reported success of the developed RISC-based processors have also attracted our attention to participate in this new area of computer architecture.

- ii. Much work has been done in the evaluation of the RISC architecture in general purpose

computations. Unfortunately, few studies have been performed to investigate the suitability of this architecture for specialized applications. Hence this has increased further the importance of this work.

- iii. Investigation of data communications software behaviour is very important when searching for a realization of a processor architecture. The unavailability of such a study has added another reason to this research motivation.

- In data communications processing (as mentioned in the previous part of this work), there are some operations which are frequently processed (such as task switching and wrapping/unwrapping messages). This fact motivates investigating the adequacy of the present RISC concept to efficiently support such processing operations.

## 2.5. Work Directions in This Research

Two major issues have emerged in computer architecture designs since the introduction of Berkeley's RISC. One concerns the merits of using an instruction set consisting of simple but fast instructions as opposed to using complex and powerful instructions. A second issue is an organization scheme that keeps more data in fast internal memories, such as registers and caches. However, the study of developing a processor using the RISC architecture for data communications applications is required in order to investigate these two issues.

As mentioned previously, the processors used in the data communications node processing have to be capable of processing a variety of functions which require general purpose type of instructions. The processing of some frequently used operations in such applications does not prevent the use of simple and fast instructions which are recommended by RISC architectures. Using the simple instructions will not require more effort in the software developing for such applications since most of these software are usually written by High Level Languages

such as C.

Today there are many RISC-based processors which are available and they have very efficient instruction sets, e.g. the I860, R2000/3000, MC88000, etc. There is no doubt that a proposed processor for such applications will not require the support of one group of these instructions (the arithmetic instructions) because this application is a non-numeric type, and hence the floating point unit can be omitted from such a processor. This further simplifies the design of the hardwired control unit and provides more free space on the —) which can be used to support other architecture features.

Based on the above discussion, we have decided to investigate other major RISC issues which contribute to high performance, i.e., the use of an internal register set. Generally, the number of these registers used in RISCs are generally greater than those used in CISCs. Moreover, the organization of these registers, i.e., windows organization, as will be discussed in the next chapter, in the Berkeley RISC have contributed to an improve the RISC performance. All research and development which have been done relating to this area of RISCs focused on utilizing these registers to improve general purpose computations. Meanwhile, none of these studies have investigated the impact of using these registers on the network nodes applications where their processing is classified as a real-time multi-tasking. We believe that there are two reasons why these studies have not followed through such an investigation:

- i. In the early stages of research of developing the RISC, the main concern was given to general purpose computations and showing the superiority of this architecture in comparison with the CISC one. All efforts were concentrated into enhancing the architecture in this direction.

- ii. Real-time applications are basically control systems [73]. Support provided to enhance the RISC architecture to improve the performance of one real-time application will not

necessarily work for others.

Utilizing the available register set used in current RISC architectures could have an impact on the RISC performance adopted for this real-time multi-tasking application in two ways:

- i. The large number of these registers will increase the processor state and hence reduce processor performance when task switching operations occur frequently.

- ii. The register organization is also designed to support general purpose computations and more specifically to process intensive procedure calls with large nested depths. However, this is not the target of network node processing (as will be discussed in the next chapters).

In this research an emphasis is given to search for better ways to enhance the register set within these general purpose RISC architecture type and to improve the performance of such an architecture when it is applied to network node processing. The study of the register set within the RISC architecture, however, raises some issues:

- i. How does the present RISC register set perform when it is used for the network node software processing?

- ii. What type of register set organization and what number of registers used in current RISCs are appropriate for this application?

- iii. What is the impact of using other register set organizations which are not currently used in RISC architectures, i.e., such as non overlapping multiple register sets? Do they give any performance improvements and, if so, what are they?

The main objectives of this research are to answer the above questions.

## 2.6. The General Approach

To achieve the main objectives of this research, the general approach used in our work presented in the next chapters can be summarized as follows:

- i. The first part of this research is devoted to the study of the nature of the data communications software which runs inside the network nodes. This will be done by investigating some data communication software in order to understand their characteristics and to determine which one of the available RISC-based architectures is more appropriate for networks nodes processing.

- ii. In the second part, an emphasis will be given in enhancing the architecture through investigation of the register set organization. A special concern will be given to the study of the impact of RISC register set organization for the task switching overhead, which is not given enough study so far [64].

- iii. Based on the results of the above two points, a RISC structure for data communications using non-overlapping multiple register sets introduced and investigated. Performance improvement and hardware complexity of the introduced architecture are studied.

## **CHAPTER 3**

#### ISDN SOFTWARE CHARACTERISTICS

This chapter investigates the software characteristics of data communications and specifically ISDN. The main objective is to study parameters which could be used to design the RISC processor for data communications applications. In particular, we are interested in determining the appropriate structures of internal register sets of the processor. At first, the subject of measuring software characteristics is investigated and its objectives are highlighted. Then methods used for such measurements are outlined. To find the software characteristics of the ISDN processing, two ISDN processing models are proposed and simulated. The results of these simulations are also discussed.

# 3.1. Software Characteristics: Background

Software characteristic is a term used for investigating the internal structure of program and measuring its parameters, e.g., the type of the instructions used, the frequency of using each of these instructions, the amount of nested procedures depth, etc.. These measurements are very important to select an appropriate structure for the RISC processor suitable for special or general purpose applications. Taking these measurements will help to identify the necessary features that have to be incorporated within the processor in order to improve its performance. As it will be shown in next section, the use of register windows structure with Berkeley RISC is one of such examples.

Roughly speaking measurement could be classified as dynamic or static [75]. In dynamic measurement, we counts the number of times that each HLL statement is executed when the program is running. Conversely, static measurements are performed by counting the number

of occurrences of each HLL statement in the program. Dynamic measurement is preferred because it indicates the frequency of each statement during the real-time execution of the program.

Recently, a number of attempts been deployed in order to determine the characteristics of HLL programs [75]. The main objective of these studies was to identify the type of the HLL statements which occur most often in the program so that they could efficiently supported by the designed processor. Numerous collections of programs have been tested for measuring software characteristics. Knuth [91] has used a collection of FORTRAN programs used for students' exercises. Tanenbaum [63] studied Over 300 procedures, executed from operating system programs and written in a language which support structured programming (SAL). Huck [75] analyzed four programs representing a mix of general purpose scientific computing. The results of all these attempts confirmed the predomination of assignment statements in programs, and therefore suggest that the simple movement of data is of higher importance. Hence, these results were exploded for designing instruction set for computers. The main drawback of these studies, however, is that these results reveal which statements are frequently used but they do not show which statements are frequently invoked during the execution time of a typical program.

## 3.2. Impact of Software Characteristics on RISC Architecture

Berkeley researchers were the first to investigate the drawback associated with the previous studies [69]. This investigation performed through the study of a collection of different programs (which comprised of typesetting, CAD, Sorting, and file comparison), they found that the procedure call/return operation represented the most time consuming operation and required about  $45 \pm 19$ % of the total memory references executed by the processor [69]. Thus,

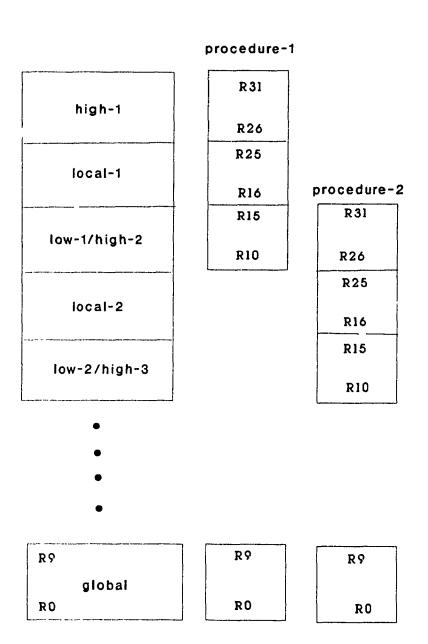

reducing the memory references generated by the intensive use of machine instructions, constituting the call/return operations within the HLL statements, has given a large effort towards the RISC architecture. There are two known schemes used to reduce memory references generated due to the call/return operation. In the first scheme, which is proposed by the Berkeley group for the RISC I, a large register set is used within the internal structure of RISC I to keep the operands on-chip and therefore reduce the memory access. This large register set is partitioned into a number of Overlapped Register Sets (ORS). Each set has three sections, where two of these sections are used to pass the procedure parameters between the next and previous procedures, while the third section is used to store the local variables. That is, in each set, the overlapped registers are used to pass parameters among procedures, and the nonoverlapped registers are reserved for local variables. Both overlapped and non-overlapped registers constitute one register set, called a window. In addition, there is also another set of registers which are used to store global variables (Figure 3.1). The global registers are not switched during the procedure call/return operations. Selecting the number of registers allocated for local variables and passing parameters, as well as the number of chosen windows is based on statistical results that have been generated from various studies [69]. One study, in particular, has found that with eight windows, a save or restore is needed only 1% of all calls or returns [77]. Other studies have shown that 98% of all procedure calls which were traced dynamically were passed with fewer than six arguments, and that 92% of these procedures used fewer than six local scalar variables [76]. Similar results were reported by the Berkeley RISC team [62]. The Berkeley RISC computers use 8 windows of 16 registers each (6 are overlapped registers and 10 are for local variables), while Pyramid computer employs 16 windows of 32 registers each [60].

The second scheme uses the optimizing compiler to allocate the most frequently used

Figure 3.1 RISC Overlapped Register Set Organization