A COMPREHENSIVE SUPPORT SYSTEM

FOR MICROCÓDE GENERATION

Juan Linares

. A. Thesis

ir

The Department

of.

Computer Science

Presented in Partial Fulfillment of the Requirements

for the degree of Master of Computer Science at

Concordia University

Montreal, Quebec, Canada

August 1982

🖒 Juan Lingres, 1982

#### ABSTRACT -

## A COMPREHENSIVE SUPPORT SYSTEM

### FOR MICROCODE GENERATION

#### Juan Linares

This, thesis examines the process of microcode production. A survey of current microprogramming techniques is presented to identify specific problems. The problem of microcode production is shown to have several interrelated components, namely: machine description, microprogram specification, microprogram verification, and microcode optimization.

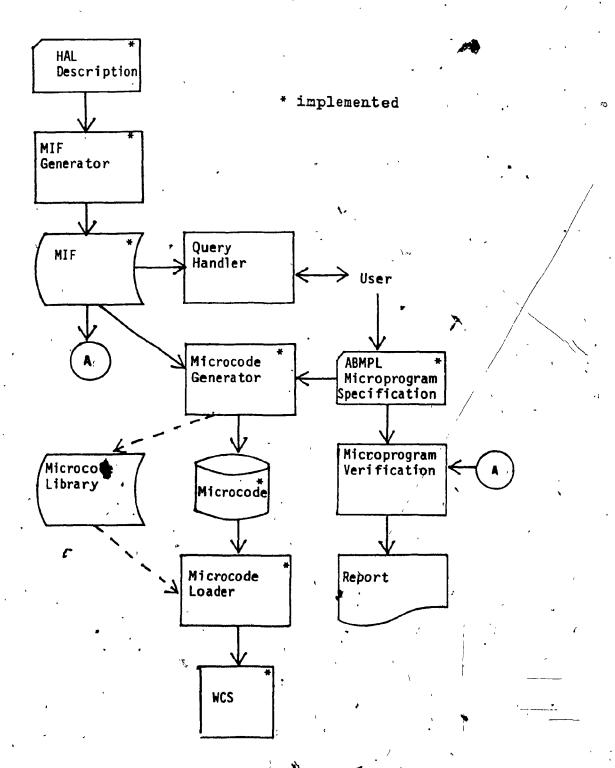

A comprehensive solution to this problem is proposed with the design of a Comprehensive Microprogramming System (CMPS). The system presents solutions to specific problems of microcode production while maintaining the relationships among the various phases of microcode production.

The two main components of the system are the Hardware Abstraction Language (HAL) and the Alternative Based Microprogramming Language (ABMPL). HAL is used to describe the microarchitecture of a computer and ABMPL is used to specify the microprograms. The features of both of this languages are discussed extensively throughout the thesis and some examples are provided. For both of this languages prototype compilers have been implemented and some practical experiences have been carried out in the SEL32/75.

#### **ACKNOWLEDGEMENTS**

I would like to express my sincerest thanks to my thesis supervisor Dr. Terrill Fancott, who enthusiastically guided me through this thesis. His numerous clarifications and suggestions have proven invaluable during the course of this project. I also would like to thank Dr. I. Greenshields, who as my initial supervisor stimulated my interest into microprogramming, and outlined the general direction of this research.

I also would like to express my gratitude to Dr. W. Jaworski for having taught me a new and fascinating way to create programs. His ideas on program development techniques have profoundly affected my ideas on software development. The concepts involved in his Alternative Based Language have contributed heavily towards the development of the microprogramming techniques presented in this thesis.

Mack, who at various times helped me with the implementation of microprograms for the SEL32/75 here at Concordia University. I also would like to thank my employer LAGOVEN S.A., of Caracas Venezuela, whose financial support of my studies here at Concordia University made the completion of this thesis possible.

I dedicate this thesis to my wife Lilian whose patience and moral support helped me through the completion of it.

## TABLÉ 'OF CONTENTS

| SIGNATURE PAGE                                     |

|----------------------------------------------------|

| ABSTRACT                                           |

| ACKNOWLEDGEMENTS                                   |

| TABLE OF CONTENTS                                  |

| LIST OF FIGURES                                    |

| 1) INTRODUCTIÓN8                                   |

| .1) BRIEF HISTORICAL SURVEY OF MICROPROGRAMMING8   |

| .2) A COMPREHENSIVE APPROACH TO MICROPROGRAMMING11 |

| .3) THE ORGANIZATION OF THIS THESIS14              |

| 2) CURRENT ASPECTS OF MICROPROGRAMMING16           |

| .1) CONTROL STORAGE ORGANIZATION16                 |

| .2) MICROINSTRUCTION FORMAT21                      |

| r.3) MICROINSTRUCTION SEQUENCING25                 |

| .4) PROBLEMS ASSOCIATED WITH MICROPROGRAMMING      |

| 3) DESCRIBING THE MICROARCHITECTURE                |

| .1) COMPUTERS AND ABSTRACT DATA TYPES39            |

| 2) THE NOTATION                                    |

| 4) SAMPLE MACHINE DESCRIPTIONS                     |

| 4.1) A DESCRIPTION OF THE SEL 32/7566              |

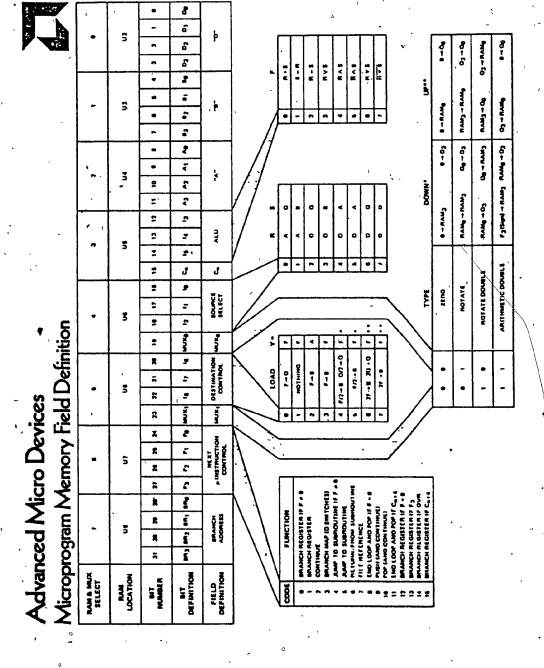

| 4.2) THE AM2900 FAMILY81                           |

| 5) THE PROCESS OF MICROPROGRAMMING89               |

| .1) THE MICROPROGRAMMING ENVIROMENT                |

| . 2) PRACTICAL EXAMPLES                       | 11j |

|-----------------------------------------------|-----|

| 6) THE FEASIBILITY OF CMPS                    | 120 |

| .1) MACHINE DEPENDENCE                        | 121 |

| .2) HIGH LEVEL MICROPROGRAMMING               | 122 |

| .3) OPTIMIZATION OF MICROCODE                 | 123 |

| .4) CONCLUSIONS                               | 124 |

| REFERENCES                                    |     |

| APPENDIX A - THE GRAMMAR OF ABMPL             |     |

| APPENDIX B - THE GRAMMAR OF HAL               |     |

| APPENDIX C - PARTIAL DESCRIPTION OF SEL 32/75 | •   |

| APPENDIX D - SAMPLE MICROPROGRAMS             | o   |

| APPENDIX E - MICROPROGRAM LOADER AND DRIVER   |     |

# LIST OF FIGURES

| 1.1 Wilkes' Matrix9                         |

|---------------------------------------------|

| 1.2 Baer's Microproprogramming System       |

| 2.1 Array Organization,17                   |

| 2.2 Block Organization18                    |

| 2.3 Split Organization19                    |

| 2.4 Nanoprogramming                         |

| 2.5 The SEL's Control Storage20             |

| 2.6 Direct Control                          |

| 2.7 Residual Control23                      |

| 2.8 Maximal Encoding24                      |

| 2.9 Minimal Encoding                        |

| 2.10 The SEL's Microword26                  |

| 2.11 The Serial-parallel Characteristics28  |

| 2.12 Sequencing in the SEL                  |

| 2.13 Microprogramming Productivity          |

| 4.1 The SEL's Data structure67              |

| 4.2 The Register File                       |

| 4.3 Typical AM2900-based Architecture82     |

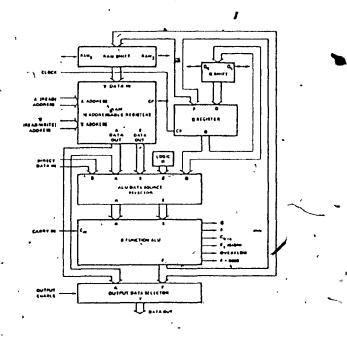

| 4.4 AM 2901 Architecture83                  |

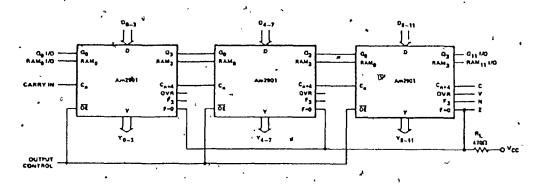

| 4.5 12-bit Cascaded AMD2901 ALU's84         |

| 4.6 AM 2909 Architecture86                  |

| 4.7 AM 2900 Microword Format                |

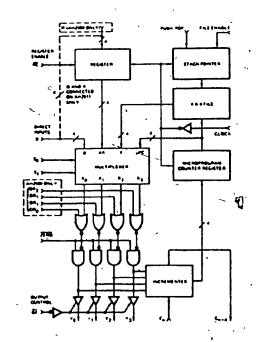

| 5.1 Comprehensive Microprogramming System94 |

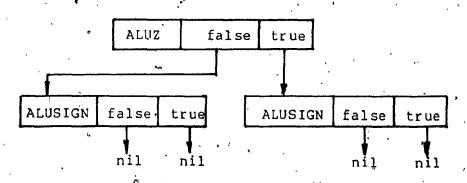

| 5.2 Maximal tree                            |

| 5.3 Testing Tree                            |

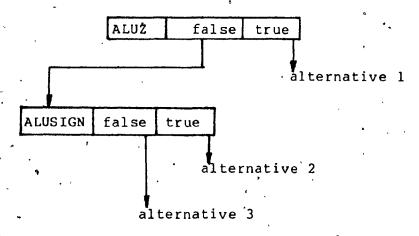

| 5.4 Connected Graph                         |

### CHAPTER 1: INTRODUCTION

Contemporary microprogramming research within the academic community is principally concerned with the design and implementation of reliable systems for the generation of compact and correct microcode. Shriver & Lewi's in a recent paper on microprogramming stated this succintly as follows: "contemporary microprogramming is concerned with firmware engineering, i.e., the reliable implementation of correctly functioning picroprograms" [SHRI81].

This interest has not yet, however, yielded good tools for the production of microcode. In some cases users have been concerned with applications of microprogramming, and have disregarded the development process [SHRI81]. In other cases researchers have attempted to borrow ideas from software engineering to solve problems in firmware engineering which "are not ordinarily encountered in the software domain" [DASG80].

## 1.1) BRIEF HISTORICAL SURVEY OF MICROPROGRAMMING

Microprogramming was originally proposed by M. V. Wilkes in 1951 as a systematic alternative to the ad hoc method of designing the control system of digital computers prevalent at the time. Besides being a more structured approach, it introduced a large degree of flexibility in the design, implementation, and maintenance of the instruction set of a computer [WILK69].

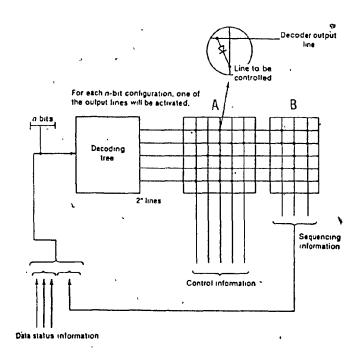

By now Wilkes' matrix model, shown in figure 1.1, become a classic in computer science. In this model at each clock pulse matrix 'A' would emit signals affecting the various gates in the CPU and matrix 'B.' would supply information to- determine the address ο£ the microinstruction. This scheme of logically dividing the information in microinstruction into functional information (microoperations with the hardware) sequencing information (addressing, tests, etc.) remained basically unchanged until now [MICK77].

Figure 1.1 Wilkes' Matrix (from FLYN80)

The next stage in the evolution of microprogramming was determined by the interest in microprogramming as a means of designing a range of computers of differing power but with

compatible instruction sets. The best example of this is IBM's 360 series in which all machines were at least upward-compatible. In this series all but the largest computer then announced (model 70) had microprogramming based on ROM [STEV64].

This contributed to the development οf hardware emulation as an important research topic. Tucker defined an emulator as a package that includes 'special hardware and a complementary set of software routines [TUCK65]. Emulation does not therefore imply the implementation of instruction set in a microprogram. An emulation package is' the result of a careful comparative analysis of the and host architectures. Particular implementation decisions are based on the study of the difficulties and advantages of a software versus microprogrammed implementation. A machine instruction may microprogrammed be if its software implementation is too difficult, or too inefficient. Another reason might be that a particular instruction is used so often as to be worth the effort of microprogramming it.

The latest phase in the evolution of microprogramming is characterized by the appearance of user-microprogramable machines which provide the tools to carry out research on the various aspects of microprogramming. Advances in integration technology have led to the appearance of powerful microprocessors which have given great impulse to

microprogramming, since these usually employ microprogrammed control units. Shriver & Lewis in a recent paper on microprogramming [SHRI81] write: "the LSI processor forced designers of multilevel interpreters to reevaluate microprogramming. Instead of reducing costs by simplifying the design and increasing flexibility, microprogramming became a way to increase the regularity of structure within an LSI chip".

To this day the goal of widespread user-microprogramming has remained elusive due to the lack of appropriate firmware tools. Their development will have profound effects on the field of computer science.

## 1.2) A COMPREHENSIVE APPROACH TO MICROPROGRAMMING

The problem of generating good microcode will not be solved simply by the introduction of high level languages and their compilers. This approach has been overemphasized the current microprogramming literature to the point of obscuring other issues in the problem midroprogramming. The specification of microprograms in a high-level notation should be consequence а comprehensive solution to the overall problem of user microprogramming. This solution must address the problems of machine description, optimality of microcode, microcode correctness, and user convenience. Shriver & Lewis, referring to the ideal microprogramming tool, wrote: "work toward this hypothetical microprogramming tool has been the thwarted by false starts and movement in tangential directions. One of the most obvious tangents has been the invention of new languages for microprogramming. These languages often incorporate ideas borrowed from software engineering. Data abstraction is the most frequently borrowed idea. At their worst, many high level languages incorporate low-level host machine features that we are attempting to hide by using a high level language in the first place" [SHRI81].

Microprograms are very intimately related to the microarchitecture in which they operate. Microarchitecture means all the hardware items which can be referred to or operated on by a microprogram. Dasgupta defines it as " the nature of the interface visible to the microprogrammer" [DASG80]. Given the above relationship any proposal to generate microcode must be concerned not, only with the structure of the language used to specify microprograms, but also with the microarchitecture in which these are executed.

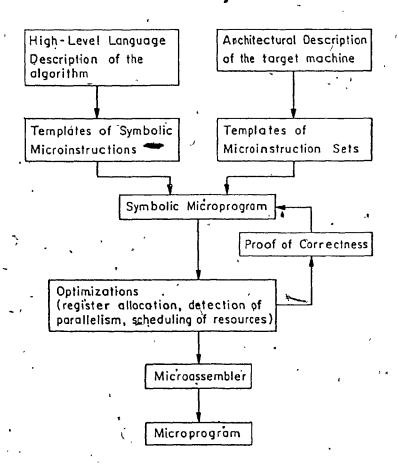

The central proposition of this thesis is the design of a comprehensive microprogramming system which addresses the various aspects of microcode generation, in particular those related to microprogram specification and microarchitecture description. Baer, when defining a microprogramming system writes: "the generation of a microprogram (microcode) is the result of a process which receives as input descriptions of

the algorithm to be executed and of the hardware resources needed to perform and sequence the operations" [BAER80].

Baer proposes the system of figure 1.2 and writes that "the automated translation of the microengine (microarchitecture) description into templates of microinstructions is a problem which is far from being solved" [BAER80].

Figure 1.2 Baer's Microprogramming System (from BAER80)

The system proposed in this thesis has a structure similar to Baer's but addresses the problem of machine description by introducing the concept of hardware

abstraction, analogous to the abstract data type concept. This abstraction constitutes a high-level language image of all user accessible storage structures, and operations available to the user. Microprograms will be specified in a high-level language which uses the operations and data items specified in the hardware abstraction data type. The logical structure of the language is based on the Alternative Based Language technique [JAW080] since it allows the abstraction of machines and programs, and is therefore in line with the overall strategy of this work.

## 1.3) THE ORGANIZATION OF THIS THESIS

Chapter two of this thesis examines the current state of microprogramming technology, in both hardware and software aspects, and the problems currently associated with microprogramming.

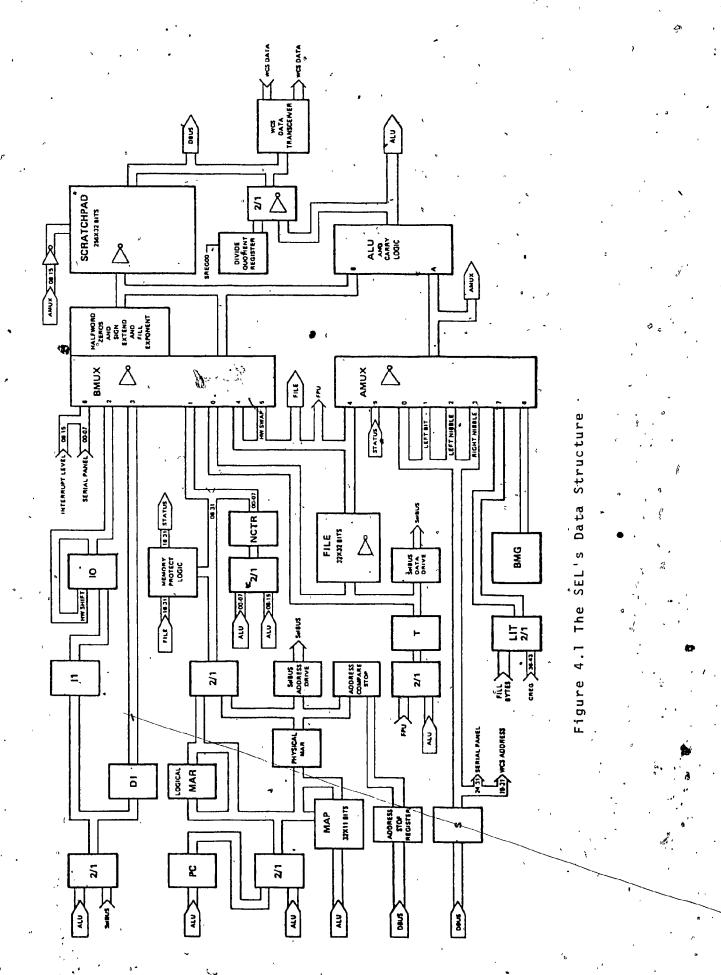

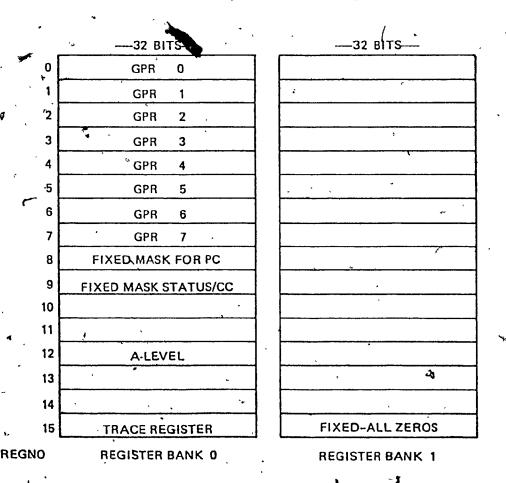

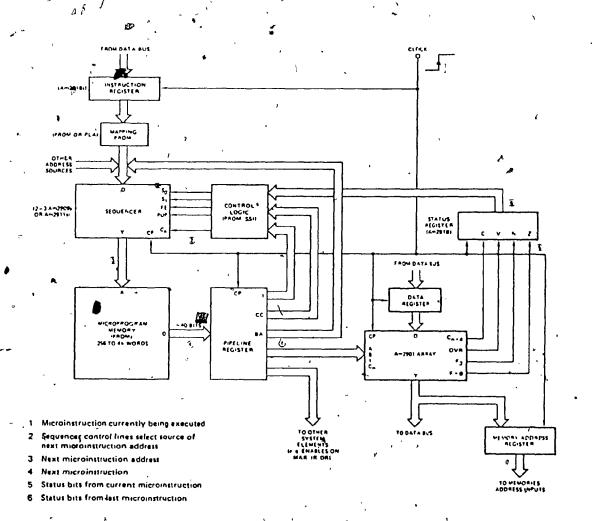

Chapters three, four, and five are used to develop the central proposition of this thesis. Chapter three deals with the description of computers in a way which is accessible and meaningful to application programmers. The concept of hardware abstraction is discussed and a hardware abstraction language to describe a computer is presented. In chapter four a practical example is given with the description of components and operations in the SEL 32/75 as hardware abstractions.

Chapter five is dedicated to microcode generation. The comprehensive microprogramming system is presented in its various aspects. The generation of microcode through an alternative based microprogramming language is discussed. Finally in chapter five some practical examples are presented with microprograms implemented through the system for the SEL 32/75.

It should be noted that the hardware abstraction language and the alternative based microprogramming language are complementary components of the system. One has no meaning without the other. In this thesis we have chosen to present the hardware abstraction language first, and then to introduce the alternative based microprogramming language. This order of presentation was chosen to emphasize the hardware aspects of microcode generation.

For those whose background is principally concerned with software it might seem more appropriate to approach the two system components in the reverse order. In such a case chapter five may be read before going to chapters three and four.

In chapter six the conclusions of the study are presented. The feasibility of the system is discussed as well as its ability to solve some of the problems currently associated with microprogramming.

## \*CHAPTER 2: CURRENT ASPECTS OF MICROPROGRAMMING

The aim of this chapter is to familiarize the reader the current status of microprogramming technology in its various aspects. Mick defines a microprogrammed a machine as "one in which a sequence of microinstructions is used to execute various commands required by the machine. If the machine is a computer, each sequence of microinstructions can be made to execute a machine instruction. tasks performed by the machine are called little elemental Microinstructions [MICK77]. microinstructions" further decomposed into microoperations which are hardware based and are the most primitive actions that can effected in the context of the microarchitecture.

The study of microprogramming hardware may be divided into three main areas which are related, but complex enough to deserve independent consideration. These are: control storage organization, microinstruction format and microinstruction sequencing.

## 2.1) CONTROL STORAGE ORGANIZATION

Control storage refers to a store from which microprograms are executed. This does not imply that control storage is distinct from main memory, although that is often the case. Most microprogrammed computers store microprograms in a smaller but faster memory, but there are some exceptions such as certain models of the IBM 360 series

and the Burroughs B17.00 in which microprograms are executed from an area of main memory [DASG79].

Dasgupta defines control storage as "a store in which microprograms reside, and whose organization and design is determined solely from the viewpoint of microprogramming" [DASG79].. One ο£ the' major disadvantages microprogramming compared to hardwired control, is the time involved in fetching microinstructions from control storage. This factor can be made insignificant implementations of control storage and microinstruction execution; hence the importance of control organization.

Figure 2.1 Array Organization (from RAUS80)

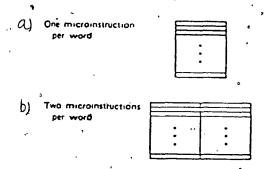

Control storage can be logically organized in several ways. The simplest and most common structure is the ordinary memory array with one microinstruction per world [fig. 2.la]. A variation of this form is to increase the size of the microword in order to accommodate two

microinstructions. The advantage of this is that fewer memory references are required since two microinstructions can be accessed simultaneously [fig. 2.1b].

Blocked

Figure 2.2 Block Organization (from 'RAUS80)

Another form of organization is in blocks [fig. 2.2]. In this scheme there are two types of addresses, one of microinstructions in the same block as the current microinstruction and the other of addresses of other blocks. As a result, addresses of microinstructions in the same block are shorter than in a non-blocked structure. This organization is efficient if the microprogram can be organized in branch-free blocks, each block processing a certain specific machine instruction. This is usually not an easy task, but with appropriate software it may be achieved.

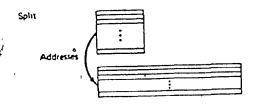

In the split structure [fig. 2.3] we have two different storage units with different word sizes. The unit with shorter word length contains microimstructions which utilize

very few resources or initiate the execution of a microinstruction in the other unit. The second storage unit has many more bits per word and therefore can exercise more control over machine resources. This organization can be very efficient if most microinstructions executed are of the short type or if many of them reference the same long microinstructions.

Figure 2.3 Split Organization (from RAUS80)

In a two-level organization the instructions in the lower level memory unit interpret those in the upper level [fig. 2.4]. This is called nanoprogramming and is conceptually similar to microprogramming, however this organization provides flexibility in the design of microinstructions as well as machine instructions. Machines with this organization are usually used for research into microprogramming. This organization of control storage is used in the QM-1 machine from Nanodata Corporation.

Figure 2.4 Nanoprogramming (from RAUS80)

For the purpose of this thesis, practical experiments will be carried out on the SEL32/75 computer available here at Concordia University. The SEL is a 32-bit user-microprogrammable computer oriented towards real time applications, but it can also handle general batch applications. It is therefore important to describe the particular microprogramming technologies which the SEL uses.

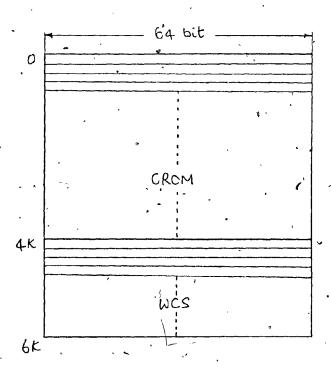

Figure 2.5 The SEL's Control Storage

The control storage of the SEL 32/75 [fig. 2.5] is of the single-word array type. It is organized as an array of 64-bit words, each word containing one microinstruction. The first 4K words consist of ROM which contains, among other things, the microprograms to interpret the basic instruction set of the SEL 32/75. The rest of the control

storage is used as a Writable Control Storage (WCS) which is installed in increments of 2K upto 8K. The WCS is made up of RAM and it is used for user-microprogramming. The WCS is viewed as an extension of the ROM control storage and therefore there is continuity in the range of addresses [SEL1].

## 2.2) MICROINSTRUCTION FORMAT

A microinstruction is merely a string of bits whose meaning (use) is determined by the decoding hardware. Of primary interest in the design of microinstructions is: the number of resources each microinstruction controls. In this respect microinstructions are classified as vertical or horizontal [RAUS80] although these appellations refer to the extremes of a broad spectrum.

Vertical microinstructions effect single operations such as LOAD, STORE BRANCH etc. They often resemble machine language instructions containing one or more operands.

Horizontal microinstructions, in contrast, control many resources which may operate in parallel. A microinstruction might control, for example, the simultaneous and independent operation of the ALU, input and output to main memory, conditional next address generation etc. Horizontal microinstructions have the potential advantage of efficient hardware utilization, but the optimization process is a difficult task.

For both vertical and horizontal formats, there are several ways to implement the executions of microoperations.

Figure 2.6 Direct Control (from RAUS80)

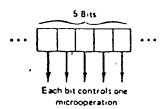

In DIRECT CONTROL, every bit in the microinstruction represents a microoperation and is converted into a control signal which inmediately and directly controls a certain machine resource [fig 2.6]. In the extreme horizontal case there would be one bit for every microoperation possible in the machine. This scheme provides flexibility, but results in large microwords and a waste of storage. It is of historical importance only since it corresponds to Wilkes' model and it is rarely used.

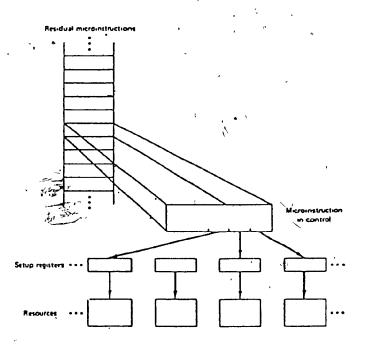

In RESIDUAL CONTROL a group of set up registers are used to control resources [fig. 2.7]. Each register controls a particular resource and microinstructions may then replace or alter the value in one or more registers. The set up registers may be manipulated by a sequence of vertical microinstructions, yet they simultaneously control several resources as do horizontal microinstructions. In situations where a certain resource performs the same operation repeatedly this scheme can provide substantial savings in

control storage use.

Figure 2.7 Residual Control (from RAUS80)

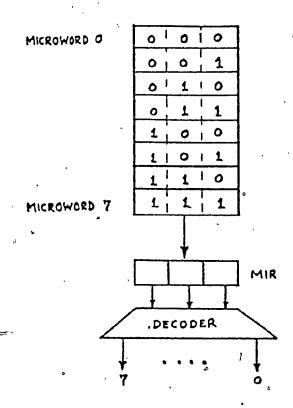

In 'MAXIMAL ENCODING each microinstruction is considered to be a unique state of a microword. If there are n possible states (microinstructions), then we can represent each microinstruction with a code using log2(n) bits. This scheme is most effective in minimizing microword length, but if the number of states (microinstructions) is large, a significant decoding delay may be introduced [fig. 2.8]. Furthermore this scheme lacks flexibility, because the addition of new microinstructions may result in hardware

modification.

Figure 2.8 Maximal Encoding (from DASG79)

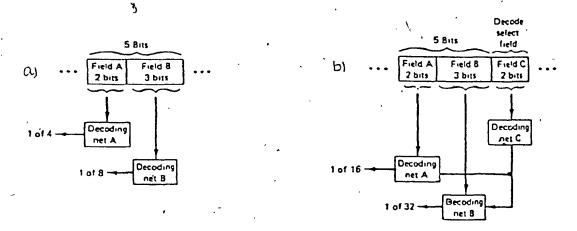

In MINIMAL ENCODING, microoperations on mutually exclusive resources are grouped into a sets represented by fields within the microinstruction. Its simplest form is called single level or direct encoding [fig. 2.9a]. In two-level encoding the meaning of a field is made to depend on the value of a control field within the microinstruction [fig. 2.9b]. This is sometimes referred to as bit steering. Another arrangement of two-level encoding is called format shifting, where the value of a field depends on the machine

state indicated by some status registers.

Figure 2.9 Minimal Encoding (from RAUS80)

The most widely used scheme is a combination of the various forms of minimal encoding. This the scheme used by the SEL 32/75. The format of the microword for the SEL is shown in figure 2.10. Certain fields such as the T field are used as control fields to determine the meaning (use) of other fields such as the M, X and P fields. Other fields such as the '+' field do not depend on any other field for the purpose of decoding.

## 2.3) MICROINSTRUCTION SEQUENCING

The microinstruction sequencing mechanism is a great source of variability among microprogrammable machines, since they all have different and often inconvenient addressing mechanism [PERS77]. Jones has studied the possibility of implementing high-level structured control constructs (REPLAT UNTIL, WHILE DO, etc.) using the available sequencing mechanisms and has found these lacking

|                                          | •                                        | ،<br>ا ر     |                   |                                              |              |                                             |                |                |                |                                       | ,                      |             |           | ĕ           | 1           | 1                                           |            | <del>;</del> |           |                       |            | 1         | 91           | SHAGHAD     | •        |           |             | 1       | ٦.         | 7       |             |             | 3           | •            |             |               |

|------------------------------------------|------------------------------------------|--------------|-------------------|----------------------------------------------|--------------|---------------------------------------------|----------------|----------------|----------------|---------------------------------------|------------------------|-------------|-----------|-------------|-------------|---------------------------------------------|------------|--------------|-----------|-----------------------|------------|-----------|--------------|-------------|----------|-----------|-------------|---------|------------|---------|-------------|-------------|-------------|--------------|-------------|---------------|

| ٠                                        |                                          | 8            | .*                | <u>.                                    </u> | -            | ٠                                           |                | •              | P.C.           | ÿ                                     | <u>.</u>               |             | ا٠        | Part 1 000  | <b>a</b>    | ا :                                         | 2          | 8            | .4        |                       | <u>۽</u>   |           | 5            | 4           | <u> </u> | 3         |             | 2       | <u> </u>   |         |             |             |             |              |             |               |

| ;                                        |                                          | AMCH         | 4 BIT BRANCH      | COMOST IONIAL<br>COMOST RS                   | I PÙ ORUCH I | ٥                                           |                |                |                |                                       | مرة                    | <b>N</b>    |           | •           | -           |                                             | CONDEN 4   | M 1004       | UMBLOCK   |                       | 3 CHBLACKP |           |              | PPE BLE     | TMCOUT   |           |             |         | innten.    | 1       | Trevia      | Free CB     | , i         | Nacional Co. | MAPPEVAL ID | * MANAGE      |

| 14   6   6                               | 12 BIT BRANCH                            | . BUT BRANCH | 11518             | ,                                            | SHAT COOL    | MON PAGE                                    | BUS TRANSS I R | ,,             |                | IS BET BRANCH                         |                        |             |           |             |             |                                             | COMOTR-S   | , Guarrau)   | -         | VARTOAV               | HAPMODE    | ENATOMI   |              |             | 71.48    |           | L           | i .     | TRACT      | -       | 1           | _           | ansilante a | COMMAN       | erro        | ADDASTOR      |

| 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1 |                                          | 2 nenz       | EXTENDED TESTS    | BBIT LITERAL                                 | £            | PLG MO                                      | ILPFICEI       | 111111003      | 110010030      | 2                                     | FORDER P               | •           | ,         |             | •:          |                                             | COMOLAN    | Djum         | EXFLAGAXE | ANA A                 | TRACTIF    |           | DINIMA       | T. Charact  | ENAMER   | Á.        |             |         | - ExtlAS   | ~       | 1111        | MOTIMEDUT   | mest mutour | TUD MINE DUT | 11.46       | , met ne tu.A |

| 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7  | 2 OF OK 115                              | WOADERS      | ,                 | W 118TS                                      | 8118118      |                                             |                |                | <b></b>        | Ц                                     |                        |             |           | •           | •           |                                             |            | •            |           | ,                     |            |           |              |             |          | ,         |             |         | PRIVAL     |         |             | *OCHUS*     | TONE        | , greugy     | 20117       | * 14.74       |

|                                          |                                          | H            | 10=0              |                                              | Ī            |                                             | Π              |                |                |                                       | П                      |             | Π         | Π           | П           | П                                           | Π          |              |           |                       |            |           |              |             |          |           |             | 2 X 12  | Burge      | MOSCALL | MAR SANDA   | ACHOMI SE   | METHOMESP.  | or thouse    | , audra,    | CA STORY      |

|                                          | 1.0001                                   |              | ST LITERAL HOPEL  | SE SECAR                                     | S WITHW      | es ACTEP                                    | A TURIL        | Jitalbe 30     | ANDIA M        | 11 PKW 109                            | n AMEG                 | 75          | N ASTACKE |             | 41          | 2 2<br>2<br>3<br>3<br>3<br>3<br>3<br>3<br>3 | -          |              | _         | 2 resrs               | 784        | Į,        | A listens    | MODE 75     | BOMEANTZ | CETTER    | ראונוווי    | ALV# 72 | AL LONG    | retus.  | Tanke LAG   | MCT.        | ****        | OH COM       | PCTV        | _             |

|                                          | 2                                        | PAPEG MOI    | 1 AEDAXI          | 1                                            | = }          | e nin                                       | ,              | 6 Arts         |                | , , , , , , , , , , , , , , , , , , , | 7 minos                | 175 511     | 300       |             |             |                                             | <i>:</i>   | ,            |           | W TESTS               | truce      | SIGHTAVE  | ALUMEON 2    | 19 70.00    | BEACHER  | WOM C     | †           | 1       | a distance | Ţ       | $\exists$   | 7           | CATT PROF.  | o owoma      | - amount    |               |

| <b>j</b>                                 | 0. 171   172   22<br>DESTIMATION         | 8            |                   | 2 pc                                         | , www        | 4 SCRATCH<br>LOCSTORE                       | <u>-</u>       | <b>,</b>       | MARIA          | ne conc                               | 7                      |             | FREREAD   | MUALLER ETT | PRIALLOS 1S | PULIMAN                                     |            |              |           | 8-11S13               | THE CUT I  | -         | -            | -           |          | •         | 1           | ╬       | UMBLOCK    | 7       | EMPLAID .   | +           | C MOOK 758  | •            |             | ,             |

| , -                                      | -                                        |              |                   |                                              | -            | ,                                           | -              | F              | ·_             |                                       | -                      |             |           | $\neg$      |             | -                                           |            |              |           | -                     | .3         |           | _            | _           | . ]      | .  .      | <u>. </u> . |         | <u>.</u>   |         | <u> </u>    | <u></u>     | ر ا         | ا            | _           | -             |

|                                          |                                          | r.           | -<br>-            | 2 Xons                                       | 3 4.8        | 1.V.                                        | B. V q dvis    | Milbain 6 A.1  | 1 NO Y         | , A 104                               | *                      | , A.OR.     | X AMO. B  | I am Y      | A AMP &     | •                                           | r Ovfricay | ı            |           | FPU DROERS<br>GROUP 2 | MO#1       | 1 MORT    | 2 CONFLICTOR | P CO        | 2007     | 26.57     | M.          | Prusone |            | 15. 121 |             |             | J           | 0            | 1           |               |

|                                          | 11 11 11 11                              | ٠            | 14.               | 3 10                                         | , D.         | Ë                                           | BEATUR 1 FILE  | <u>-</u>       | INTERAL PRICES |                                       |                        |             |           |             |             | •                                           |            |              |           | FPLORDERS<br>OROUPS   |            | 2         | CON Record   | 200         | ÓVFMONT? | ary Langs | 3           | 7       |            | ╅       |             |             |             |              |             | Ī             |

| _                                        | <del>-</del>                             | •            | 1 Ordatav 1 peter | Section 2                                    | DECOM.       | MODOL WILL                                  | <u>:</u> _     | - 1000 M       | <u> -</u> -    | ١                                     | Tark.                  | 201         | MIN'S     | K-VIII      |             | CONDITIONAL<br>ORDITIS                      | ğ          | M PCE        | 1 rower r |                       |            | ALTERY 73 | ALTERES 2    | 2 2         | 4        |           | # ·         | -       | No.        |         |             | ,           | SET NOTE C  | 0 2000       | ancepas .   | -             |

|                                          | 20 20 20 20 20 20 20 20 20 20 20 20 20 2 | F            | -                 | •                                            | -            | , j. i. | 3 5            | - Convector    |                | Г                                     | <u> </u>               | 43          | <b></b>   | <u>-1-</u>  |             | ٠.                                          | <u>.</u>   |              | •         | LOROTH                | •          | 1         | esse, T      | "           | PETPOOL  | †         | 3           | 20      | Dang       |         | могростоя   |             | υ           | Other name   | T E         | 1             |

| · -                                      | 0   m   m   m                            | 78           | 1 (XIIIVOLD       | 1_                                           | WIERTRAS .   | , sua                                       | WHEN PARE      | 4 2 TEST TRUCK | 1              | N/13 three o                          | LATINGED<br>TEST FALSE | A THE FALSE | ALVE      | o mature    | B tutter    | THEFT FALLS                                 | 14.8       |              | ,         | A GADGINS             | 9          | - Oracona | H            | S adriand t | BLECAME  | Tooler    | mot it      | 11000   | 210012     | -       | * morecanos | g get bei g | Mrt mar.    | OTHER BALFE  | -           | ŧ             |

Figure 2.10 The SEL's Microword Format

in capability. She writes: "the microinstruction sequencing capabilities (should) provide the basic mechanism implementing various forms of program logic.... Thus it is important that the microinstruction sequencing capabilities of machine the underlying organization support the implementation of the basic constructs of the appropriate program logic using context free (no embedded address) modules οf microcode. Review microinstruction sequencing - capabilities οf contemporary microprogrammed machines has shown that these sequencing capabilities generally fail to support modular implementation of the basic constructs of flowchartable program logic" [JONE75].

Microinstructions are executed in a general fetch-decode-execute sequence, but details of actual implementation can vary greatly. Generally a microprogram counter is used to indicate the address of the next microinstruction, and a certain field may be set aside within the microword to indicate a branch address. Unlike machine language programming, the effects of the sequencing scheme are not hidden from the microprogrammer and he must cope with them.

In sequencing microinstructions there are two aspects to be considered, one is the fetch-execute cycle of the microinstructions themselves and the other is the sequencing of microoperations within each microinstruction. The first

aspect covers the relationship between microoperations in different microinstructions. The second covers the relationship between microoperations within the same microinstruction.

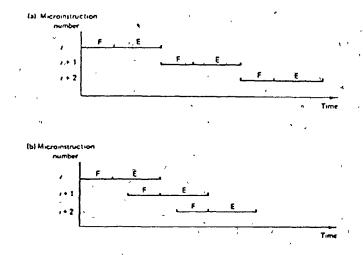

Figure 2.11 The Serial-parallel Characteristics (from RAUS80)

The first aspect is described by the serial-parallel characteristics of the sequencing scheme. In a serial implementation, fetching the next microinstruction does not begin until the execution of the current one terminates [fig. 2.11a]. In a parallel implementation, the fetch of the next microinstruction begins while the current one is being executed [fig. 2.11b]. The advantage of the serial approach is simplicity of realization, as the hardware does not have to control fetching and execution simultaneously and no special problems arise in conditional branching. The advantage of the parallel approach is the corresponding

saving of time.

The second aspect of sequencing is described by the monophase-polyphase characteristics of the sequencing scheme. These refer to the number of phases (minor cycles used to execute a microinstruction, which subcycles) usually requires one major clock cycle. In a monophase implementation there are no distinct control cycles and the microinstruction is executed by a single simultaneous issue of control signals. In a polyphase implementation each major clock cycle comprises multiple subcycles and hardware generates control signals at each subcycle. approach is sometimes considered a disguised form microprogramming. The advantage of monophase vertical operation are simplicity of realization (no special hardware needed) and speed (parallel operations), however it can only be used effectively in cases where there are no data conflicts among operations within a microinstruction. advantage of polyphase operation is that it' allows interaction the expense of among resources at complicated hardware.

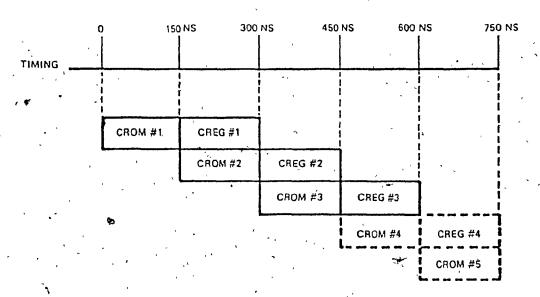

The SEL 32/75 uses a microprogram counter to point to the next microinstruction. This counter can be modified by the contents of certain fields within the microword, or by the the contents of certain registers or status indicators. Otherwise it is incremented by one by a special adder. Microinstructions are executed in two cycles each of 150

nanoseconds. During the first cycle (CROM) the basic tests and sequencing are accomplished. The second cycle executes all orders that the microinstruction directs. Although the microinstruction requires the full 300 nanoseconds to execute, one microinstruction can be handled every 150 nanoseconds, the second microinstruction going through the CROM cycle at the same time the first one is being executed in the CREG cycle [fig. 2.12].

Figure 2.12 Sequencing in the SEL (from SELl)

## 2.4) PROBLEMS ASSOCIATED WITH MICROPROGRAMMING

The production of microcode is usually a slow and difficult process in which familiarity with the hardware and efficiency of microcode are absolute requirements. The first is due to the level (hardware) at which microprogramming is done and the second because microprograms constitute the base of the entire software

system of a computer. Chaptal writes: "microprogramming introduces an articulation between the hardware and software" [CHAP75].

Most contemporary microprogramming is done by computer manufacturers to implement the basic instruction set of their computers. In this environment, familiarity with the architecture is a natural consequence of the manufacturing process.

More often than not the microprogrammer has an electrical or electronics engineering background rather than a computer science education, with solid experience in digital logic. It is a profound knowledge of architectural components and their organization that allows the microprogrammer to make use of the parallelism inherent in the architecture, thereby producing efficient microcode.

| Aids to Microprogramming    | instructions<br>per man-day | total time to<br>produce 10000<br>instructions<br>(man-years) |

|-----------------------------|-----------------------------|---------------------------------------------------------------|

| simulator                   | . 2                         | 18 years                                                      |

| microassemblers and loaders | - 5-10                      | 5-9 years                                                     |

| ∘high level language        | 10-25                       | 2-5 years                                                     |

Figure 2.13 Microprogramming Productivity (from CHAP75)

Chaptal has compiled the table of figure 2.13 to illustrate the low productivity of microprogrammers even

when working with short microinstructions (16 bits) [CHAP75]. Since long microinstructions are more desirable because of their potential for increased parallelism, it can be expected that the productivity of microprogrammers will diminish even further unless the obstacles to microprogram production are removed. These obstacles vary somewhat from machine to machine but they can be grouped into three main problem—areas: machine dependence, low level microprogramming software and microcode optimization.

## 2.4.1) MACHINE DEPENDENCE

problem of machine dependency of microprograms originates from their position in the programming hierarchy of a computer, i.e., at the lowest level just above the hardware. All other programming levels are implemented on a virtual interface. High level languages intermediate code for, a virtual machine which is separately transformed to machine language. Even assembler language is implemented on a virtual machine, since it uses subset of the hardware's storage resources and in some cases even virtual structures such as stacks certain Burroughs machines). / Assemblers can also invoke operations which are not directly implemented by hardware such as MOVE LONG instructions and in the case of stack machines the PUSH and POP operations.

Microprograms, on the other hand, are based on the hardware of the particular machine. They can only reference those structures which physically exist and can invoke only those operations which actually may be executed by the hardware. Dasgupta states the problem formally as: "the fact that microprograms by definition create some desired target architecture on a machine-specific (host) microarchitecture" [DASG80].

The problem machine dependence affects of systems implemented transportability οf microprogramming. Baba & Hagiwara write: "the desire for machine independent microprogramming systems has come from the fact that microprogramming languages are not compatible even between two adjacent models of the same architecturally compatible product line" [BABA81].

Machine dependence originates in three main areas of microarchitectural variability [DASG80]:

- 1) The semantics of microoperations, which refers to the various meanings that conceptually equal operations may take in different machines.

- 2) The timing of microinstructions, which refers to the sequencing of microinstructions as well as of the microoperations within a microinstruction.

- 3) The data path structure, which refers to the data transfer paths between hardware components.

### 2.4.2) LOW LEVEL SOFTWARE SUPPORT

The development of microprogramming languages has lagged behind that of macroprogramming languages. At a time when the construction of compilers for high level languages has become a mere routine, in the field of microprogramming this is still causing many problems [SINT80].

Most of the software available for microprogramming comes from the manufacturers in the form of microassemblers. very primitive in nature and are totally machine dependent. Their use requires familiarity with microarchitecture and leaves the user to deal on his own with the timing constraints of the sequencing mechanism. the case of the SEL 32/75, the microassembler composes one microinstruction at a time by mapping particular character strings to bit patterns in appropriate locations within the microword [SEL2]. . It provides pseudoinstructions and facilities to change the basic character strings to more meaningful ones, but no attempt whatsoever is made provide for global composition (merging of contiguous microinstructions) or to hide the effects of the sequencing mechanism.

There have been several attempts to develop high level microprogramming languages, but they have only partially succeeded. Some, like STRUM [PATT76], are successful in producing efficient microcode but are totally machine

and the microprograms are not transportable. oriented Others like SIMPL [RAMA74], were oriented towards implementation of a particular composition technique that excluded certain control and data structures. [DEWI76] tried to achieve machine independence by making the language extensible through the implementation by firmware of non-available hardware facilities, but this led to inefficient microcode. Baba & Hagiwara developed a machine independent microprogramming system [BABA81] that included a machine description and a microprogramming language, but the level of detail is so deep that it resembles a hardware description language and it is beyond the grasp of most application programmers.

### 2.4.3) MICROCODE OPTIMIZATION

The optimization of a microprogram is directed at reducing its execution time to a minimum and possibly its size as well. This process involves microcode compaction, i.e., the minimization of the number of microoperations, and consequently of microinstructions required to carry out a certain task. This is usually an arduous process because of the resource conflicts and data dependencies introduced by the bi-directional flow of control in microprogramming.

The problem can be stated formally as follows: "given a microprogram expressed as a sequence of microoperations, these must be placed into microinstructions so that the

execution time is minimized" [LAND80]. This topic has become a major research topic because of "the almost universal belief that only optimal microprograms are useful" [DASG80] and the pressure from the increasing number of applications for microprogramming.

problem is usually attacked by dividing The microprogram into branch free blocks and then trying to local compaction in each block. Once we have a achieve group of compacted blocks, then global optimization may be It. is this last step which has not been attempted. satisfactorily solved. Shriver & Lewis write: "Landskov al have shown that practical algorithms for the NP-hard optimizing straight-line segments problem microoperations are feasible, and give nearly optimal results. Indeed microcode compaction can be considered one the few solved problems of microprogramming. Global, optimization of microprograms is still a problem, however" [SHR181].

# . . . CHAPTER 3: DESCRIBING THE MICROARCHITECTURE

We have already established the intimate relationship between microprogramming and the microarchitecture.

'Familiarity with the microarchitecture is essential for the production of useful microcode. So far this familiarity has remained the domain of the hardware specialist and of a few brave application programmers who have the will to expend the time and effort necessary to acquire such familiarity.

Acquiring familiarity with a computer is an arduous process. It involves, among other things, the reading of countless technical manuals filled with hardware jargon, a trial-and-error approach to microprogramming with the consequent number of system crashes, manual optimization of microprograms, and plenty of time to do all of the above, most of it wasted on trivial problems whose solution is often found in a piece of information buried deep inside one of the manuals.

The problem of familiarizing an application programmer with a given machine is then a problem of transmitting information about the machine. The information must be easily accessible and must be meaningful in terms of concepts with which the programmer is already familiar.

Making the information accessible requires that it be organized in a storage medium that allows the user access at will and with user-defined search criteria. All of the

above suggest a computer-accessed database as the ideal storage medium.

Barbacci proposes a similar idea with the creation of a global database to contain machine information to be used by all types of computer applications: architecture evaluation, simulation, automatic programming etc. This machine database would be created by processing an ISPS (Instruction Set Processor Specification) description of the machine [BARB81].

Providing meaningful information requires the use of a notation with which the programmer is already familiar, i.e., concepts and constructs from the area of high level language programming. It must be noted however, that the environment of microprogramming is so distinct from that of high level programming, that there are certain structures and actions for which there are no appropriate language constructs. This situation appears in two forms:

- Structures and actions that are so specific .1) microprogramming that there are no language constructs sequencing describe them. For example, the οf microoperations, serially and in parallel, can not accurately described using the typical parallel programming constructs COBEGIN and COEND.

- 2) Structures and actions that may be described with known constructs, but the result is so complex as to make them less comprehensible. For example the shifting of bits in a

register may be described by a series of data transfers between the elements of an array. But then what is conceptually one operation, becomes many.

There is, therefore, a need for new language constructs especially suited for the microprogramming environment. These should, however, be kept to a minimum and should not require any major effort on the part of the programmer to understand them.

### 3.1) COMPUTERS AND ABSTRACT DATA TYPES

The abstract data type is a concept which permits a very clear and precise definition of data objects within a program. From the point of view of programming an abstract data type is defined as [GILO80]: "a homogeneous set of data objects and a set of operations applicable on the objects of the type".

A typical example of an abstract data type is a stack. It has a well defined structure (width and depth) and associated with it some well defined access procedures which act on the data structure (PUSH, POP etc.). Heinanen et al have used this concept to describe a special-purpose computer designed specifically towards the implementation of a programming hierarchy based on some primitive abstract data types which are implemented through microprogramming [HEIN80].

The microengine of a computer can be described as having a well defined data structure and a set of well defined operations which act on the data structure, however it can not be treated as an abstract data type because of the following:

- i) The microarchitecture of a computer is more like a collection of abstract data types. The data structure can not be considered a single storage item but rather a collection of storage items, some of which may be connected. Each item is usually acted upon by a subset of operations and often these subsets are not disjoint, i.e., a given operation can be performed on different storage items.

- ii) Abstract data types by definition provide a flexibility which is found in the context of microarchitecture. Among the àccess procedures associated with an abstract data type there procedures to create and delete objects of the type. the microarchitecture's environment there operations equivalent to such procedures. For example, if the microengine includes a counter we may describe its structure and the operations that can be performed on it, but we can not delete it or, create additional counters. We can only use whatever counters physically exist in the microengine.

While the concept of an abstract data type can not be applied strictly in the description of the microarchitecture of a computer, it can be used as a guide to provide a description in the form of hardware abstractions of the components of the microengine.

# 3.2) THE NOTATION: A HARDWARE ABSTRACTION LANGUAGE

The description of any structure or process requires the existence of a coherent notation that is understandable by those to whom we wish to communicate the description. In order to describe a microprogrammable computer, the notation must meet the the following requirements:

- 1) The machine must be described at the microarchitecture level. There are several levels of abstraction in a machine. These range from the purely functional level of the macroachitecture down to the level of the individual gates. The notation must therefore be tailored to the required level of abstraction.

- 2) The use of the notation must yield a functional description of the microarchitecture. The structure of storage components must be described with a few basic types. The semantics of operations must be described using a few well defined primitive operators. Both the basic types and primitive operators must be easily understood by the prospective microprogrammer.

To meet the above requirements this thesis proposes a Hardware Abstraction Language (HAL) for the functional description at the microarchitecture level, of the structures and operations physically occurring in the hardware.

The purpose of HAL is to describe the microarchitecture to the prospective microprogrammer in the form of a set of well defined storage structures and a list of well defined operations on them. HAL is intended to be applicable to description of a wide range of microarchitectures. However, its design has been influenced by its application to the SEL32/75 during the course of this research.

HAL not an executable language, but a hardware description language designed to yield functional description of the microarchitecture. This last point must be emphasized, since the syntax of HAL is flexible enough to allow the specifications of structures and operations for which a process of code generation would seem very complex. One must keep in mind, however, that the processing of a HAL description will not generate but code. machine information file. This file would be used by a microcode generator, and by the prospective microprogrammer to get acquainted with the microarchitecture. It could possibly be used by a microprogram verification (simulation) system.

Regardless of the complexity of the structures and operations described using HAL, one must remember that whatever is described must already be implemented in the hardware. The objective of HAL is to describe what physically occurs in the hardware, and not to implement new structures and operations based on existing hardware items, as is the case with most high level languages.

## 3.2.1) THE JUSTIFICATION FOR HAL

The first and most important justification for HAL is the need for a description of the microarchitecture. The problem then is to justify the choice of a particular notation to satisfy this need.

In choosing a particular notation we must take into account the following considerations:

- The guiding strategy in describing the microarchitecture is the concept of hardware abstraction, i.e., the microengine is to be described as having a set of well defined storage structures with a set of well defined operations on them.

- 2) The purpose of the microengine description is to provide information to the microprogrammer as well as to the microcode generator.

Upon considering the choice of a notation to describe the microarchitecture, one is inclined to use one of the existing hardware description languages. These have,

however, been found to be unsuitable due to the following reasons:

- 1) Computers are described at several levels, none of which exactly the description of the can accommodate Baer describes the following microengine. global system (PMS), the processor [Baer80]:. The description (ISP), the register transfer level, and the design and circuit level. The processor description Level encompasses the microengine description, but notations such as ISP are concerned with providing information for the assembler programmer. Bell & Newell state: The ISP descriptive system is meant to provide a uniform way of describing instruction sets, that is, of giving the information contained in a programmers manual" [BELL71]. The instruction set of a computer is however built upon the storage structures and functional capabilities of the microengine, these are more numerous and varied than what assembler 'programmer perceives.

- 2) Hardware description languages are not specifically concerned with microprogramming and their scope goes beyond the microengine. This usually creates an unnecessary degree of detail. The biggest defect of these languages is that they do not establish a link between the functional description of operations and the microinstructions that implement those operations. Dembinski & Budkowski state: "the specific feature of

microprogramming is the direct link between a functional specification of hardware units and microprogram instructions. A microprogram designer must be aware not only of how to express his algorithmic solution of a particular problem, but he also has to [take] care of the hardware realization of his algorithm [DEMB78].

- languages is usually beyond the grasp of most application programmers. Even in cases where the language is concerned with microprogramming as in the MPG system [BABA81], the objective is to provide information for the microprogram compiler and not for the prospective microprogrammer.

- 4) The sequencing of microoperations can not be adequately described by the timing primitives of existing languages. Sint writes [SINT81]; 'In most languages, one can only distinguish sequential and parallel execution of operations. For a description language that ..., describes microoperations as indivisible units this is insufficient, since their execution can overlap without being fully parallel'.

Given the unsuitability of existing hardware notation, HAL was designed with the following objectives in mind:

To describe the storage structures and functional capabilities of the microarchitecture in a form which application programmers could understand with minimal effort and at the same time be able to provide information to the microprogram generator.

- 2) To establish a direct link between the functional description of operations and the microinstructions that implement those operations.

- To be able to create a machine information file by processing the HAL description of the microarchitecture. This file is to be used both by the microprogrammer to get acquainted with the microarchitecture and by the microprogram generator to transform a microprogram specification into microcode.

#### 3.2.2) THE SYNTAX OF HAL

Freeman describes modern computers as having three types circuits: "storage, data transfer and manipulation, and control. Storage circuits are able to hold information over transfer and manipulation are the guts of a computer and provide the information processing power of a The essential third ingredient of a modern computer. stored-program computer, the control circuitry, provides the ability to evoke the operations of other circuits in many [FREE 75]. different sequences (i.e., different programs)." It is along the lines proposed by Freeman that HAL describes the microarchitecture. Since our purpose is to describe the physical circuitry through abstractions, we shall refer to Freeman's three types of circuits as: the data structure, the functional operations, and the control structure.

machine by listing its storage items, its functional operations and its control operations. It is similar to Pascal in the description of the data structure and in the basic functional statements. HAL was designed with the description of the SEL 32/75 in mind, but it is flexible enough to accommodate other machines and it could be easily extended. In BNF we write:

The data structure includes the description of the data types used as well as of the storage items available to the microprogrammer. The abstractions of existing storage items is done by using certain basic types to build more complex types. In BNF we have:

<data structure> ::= <data types> <storage>

<type declaration> ::◄

<type> ::= STACK(<positive constant>) OF <type> !

SEQ (<constant>..<constant>) OF <bit type> !

ARRAY [<index type>] OF <type> !

TUPLE <field list> END !

<simple type>

<bit type> ::= BIT ! ZERO ! ONE

The basic types used by HAL are BIT, ZERO, and ONE. These are defined as:

```

TYPE BIT= 0..1;

ZERO= 0..0;

ONE= 1..1;

```

These basic types accept the usual arithmetic operations +,-,\*,/ as well as the boolean operations OR,AND,XOR,NOT. A value of 1 stands for true and a value of 5 stands for false. Types ZERO and ONE are required because storage items sometimes have certain fields permanently set to 1 or 0. An item of type ZERO is always false and one of type ONE is always true.

The type SEQ is used to describe strings or sequences of bits. It is similar to the packed array of 1 dimension in Pascal, but with the difference that one can operate on individual bits as well as on the whole item. Bit labelling is established through a range of indices denoted by constants. The range of bit indices need not go from 10w to

high, it may go from high to low if it reflects the manufacturer's convention. The most typical example of a sequence structure is a register. Consider for example the following description of an X register in the CYBER:

TYPE XREG= SEQ (59..0) OF BIT;

in this case we chose 59..0 because it corresponds to CDC's convention of bit labelling. Whatever the choice, one must be consistent in order to have clarity. Allowing the use of high-low as well as low-high ranges seems to complicate implementation, but one must remember that HAL is not an executable language but a descriptive language from which no executable code will be generated.

The type STACK refers to the usual last-in-first-out structure with its associated PUSH and POP operations. In some machines such items are part of the hardware. The SEL32/75, for example, has a hardware stack which it uses to store return addresses during subprogram processing. The type STACK is not meant to describe stacks which may be perceived at the assembler level, but which do not exist in the hardware. The positive constant associated with the type STACK indicates the depth of the stack. For example in the SEL there is the JSTACK which can be described as follows:

STORE JSTACK: STACK[4] OF SEQ (0..12) OF BIT;

The type TUPLE is a structure which consists of a number of components or fields. It is similar to the Pascal RECORD, except that it has no variant part. An example would be the description of a floating point register type:

TYPE FPREG= TUPLE

SIGN: BIT;

EXPONENT: SEQ (1..11) OF BIT;

COEFFICIENT: SEQ (12..59) OF BIT

END;

If there is a register X of type FPREG then one can refer to one of its components, say EXPONENT, by coding X.EXPONENT.

The storage part of the data structure describes the storage items available in the microarchitecture. Every item described in this section must be based on the hardware, either the whole item or in case of a TUPLE its components. This allows for the logical grouping in a TUPLE of items which exist in the hardware but which are not physically grouped. In BNF the storage description is defined as follows:

<storage> ::= STORE <storage items>

<storage items> ::=

<identifiers declaration>; !

<identifiers declaration>; <storage items>

An example of storage declaration could be:

TYPE REG: SEQ (31..0) OF BIT;

STORE RØ, R1, R2, R3: REG;

STATUS: TUPLE

ALUPOS, ALUZERO, OVFLOW: BIT; PROGCTR: SEQ (12..0) OF BIT; KEY: SEQ (2..0) OF BIT

END;

The item STATUS may not necessarily exist as a whole in the hardware, but one may group several separate hardware items to establish a logical grouping.

The functional operations refer to the capabilities of the machine in data transfer and manipulation. The objectives of this section are:

- To establish the set of operations which the microprogrammer may invoke in the specification of a microprogram.

- 2) To establish the possible consequences of each operation.

- 3) To establish a direct link between the abstract description of the operations and the actual microword that carries out those operations.

The functional capabilities of the machine are described as a list of operations. In BNF we have:

<functional operations> ::= OPERATION <operation list>

<operation> ::=

EXP: <explicit operations> <underlying operations>

<compound statement> ::= COCYCLE <statement list> END

<statement list> ::=

<statement> !

<statement><sequence operator> <statement list>

<sequence operator> ::= , ! ;

Explicit operations are those that can be invoked directly by the microprogrammer. The operations are decribed statements which correspond to abstract descriptions of the physical actions occurring in the hardware. The compound used to describe the occurrence of multiple statement is operations within a single major clock cycle. understood that each microinstruction takes one major clock The originator of the COCYCLE cycle to be processed. Dasqupta (see DASG80). It is used here construct is s. describes parallelism of the it best the because Sequence operators are provided to indicate microengine. serial (;) or parallel (,) realization of operations. polyphasic machine, actions taken during different subcycles are separated by semicolons. Actions occurring during the same cycle or subcycle are separated by commas.

Underlying operations describe the operations that occur as a consequence of the explicit operations invoked. They also describe the microinstruction used to realize the explicit operations. In BNF we have:

<compound | statement>

<underlying operations> ::=

IMP: <implicit operations> MIW: <microword> !

MIW: <microword>

<implicit operations> ::=

<implicit operation> !

<implicit operation>; <implicit operation>;

<implicit operation> ::= <statement> !

Implicit operations usually describe data transfers or storage settings which result from the execution of the explicit operations, but which can not be directly invoked by the microprogrammer. The setting of condition codes after an arithmetic operation is a typical example of implicit operations. Implicit operations may be specified as a list of sequential operations because some explicit operations may take more than one major clock cycle to complete. For example in the SEL32/75 writing to a general register is initiated in one cycle and completed in the next.

Explicit operations are linked to a microinstruction by the description of a microword in the form of a string of bits. Each bit is described as having a fixed value (0,1), a variable value (letter), or as not being used (-). In BNF we have:

The microword description must be such that if processed by the microengine the storage items involved would be affected in the way described by the explicit and implicit operations.

Statements in HAL are Pascal-like except for the introduction of concatenation operators and some new

The keyword START is used to indicate that there is not a definite completion time associated with this operation, i.e., the microprogrammer may invoke the operation but he can not expect it to complete within a fixed predetermined time. Operations which are completely internal to the microengine always complete in fixed time, however in cases when the microengine has to communicate with external devices, the time elapsed until completion may vary depending on how busy the external device is. An example of this situation occurs during main memory access in which the elapsed time varies according to the traffic in the memory

The keyword NULL indicates that the result of the expression is not to be transmitted anywhere. Usually the purpose of such operations is to test the value of the expression, the result of the test being determined by the implicit operations.

and

Predefined procedures will be used to describe certain operations which are specific to the microengine and which are not easily expressed in high-level notation. These will be described in detail later.

The semantics of conditional statements are that if the expression is evaluated as true, then the operations specified as actions will be carried out. Conditional statements allow conditional interaction among resources in a polyphasic machine.

Variable concatenation describes the grouping of storage items for the purpose of receiving or providing information. The operations are similar to those of string concatenation in string-oriented languages. In BNF we have:

<variable concatenation> ::=

<variable reference> !

<variable reference>&<variable concatenation>

<variable> ::= <identifier><specifiers>

The bit index allows partial access to a storage item, i.e., to some of its bits only, while the specifiers allow access.

to specific components of a structured item, both ARRAY and TUPLE types.

Expressions in HAL are similar to Pascal except for the inclusion of some new operators, such as XOR which are commonly available at the microprogramming level. In BNF we have:

```

<expression> ::=

<simple expression> !

<simple expression> <relational op> <simple expression>

<relational op> ::= # ! = ! < ! > ! <= ! >=

<simple expression> ::=

<sign><term> !

<sign><term> <add op> <simpler expression>

<simpler expression> ::=

<term> !

<term> <add-op> <simpler expression>

<sign> :}= + ! -

<add op> ::= OR ! XOR ! +

<term> ::= <factor> !

<factor> <multiply op> <term>

<multiply op> :: = AND ! *

<factor> ::= <concatenation> !

cpredefined function reference> !

(<expression>) !

NOT <factor>

```

Predefined functions serve the same purpose as predefined procedures and will be discussed later. Concatenations are similar to variable concatenations except that they allow the introduction of, constants or literals in the concatenated item. In BNF we have:

<concatenation> ::= <element> !

# <element>&<concatenation>

<literal indicator> ::= \$<letter>

Literal indicators are used to indicate the position within a concatenation of a modifiable literal. These allow the introduction of constants by the microprogrammer in an operation. As an example, let us consider the description of register operations in a machine. Since registers usually have the same characteristics, it is not unusual to treat them as an array. Consider a machine with 8 general registers (0-7) and a shift register. They could be described as follows:

STORE GREG: ARRAY [0..7] OF SEQ (31..0) OF BIT; SREG: SEQ (31..0) OF BIT;

A typical operation in such a machine would be the transfer of data from a general register to the shift register.

Using a literal indicator, we could describe a general operation as:

The letter R would occupy the field within the microword which determines the bounds of the value which can be used. When the microprogrammer codes a microprogram he would then specify the the particular register by coding:

SREG:= GREG[\$R6]

The microcode generator updates the microword with the value required, 6 in this case.

The control structure section is used to describe the timing of tests and the control operations which can be performed in the machine. In BNF we have:

<control structure> ::=

<tests description> <control operations>

<tests description> ::= TEST <test list>

<test> ::= <expression> <timing operator> <time>

<timing operator> ::= AT ! AFTER

<time> ::= <sign> <phase>

The tests description establishes the testable conditions in the machine as described by an expression, and the timing constraints on the testing of those conditions. The keyword AT indicates that the condition is available for testing only during the given cycle or subcycle, and not before or after. The keyword AFTER indicates that the condition is available for testing, and remains so, after the given cycle has expired. These timing constraints usually originate in the scheme used to sequence microinstructions.

An example would help to illustrate the description of testable conditions. It is understood that conditions are set during the current clock cycle, i.e., cycle 0. Consider

two storage items ALUZ and COUNTZ. The first one is set to l if the result of an ALU operation is zero, otherwise it is set to zero. COUNTZ is set to 1 if the value of a counter becomes zero, otherwise it is set to zero. Assume there is pipelining of microinstructions, i.e., there overlapping οf the cycle times οf contiguous microinstructions. Under these timing constraints. description of these tests is as follows:

TEST ALUZ = 1 AT +1; COUNTZ = 1 AFTER 0;

The use of the keyword AT with ALUZ indicates that the ALU's bits can only be tested in the cycle inmediately following that in which they were set. In both of the above cases one cycle (cycle 0) has to elapse before the condition can be tested, but the first condition can be tested only during the second cycle, while the second condition can be tested anytime beginning with the second cycle.

The control operations section describes the ability of the machine to perform condition dependent non-sequential processing. The purpose of control operations is to be able to choose an address other than the next sequential address from which to fetch the next microinstruction. The operations are described using very primitive control constructs which express the different types of program flow modification. In BNF we have:

<control operations> ::= CONTROL <control list>

<control operation> ::=

EXP: <control description> <underlying operations>

<control description> ::=

<condition> <control operator> <concatenation>

<control operator> ::= GOTO ! GOSUB ! RETURN-

The control operators determine the kind of branching that may occur. They all have the ability to interrupt sequential processing but each has different implications. The operator GOTO achieves a simple branch at the same process level. The operator GOSUB is used to branch down to a lower process level, i.e., a subprogram, implying that provisions are made to eventually return to the same level. These provisions usually include saving the state of the machine for future restoration. The RETURN operator is used to branch up to a higher process level, implying a restoration of the original state of the machine. The implications of any of these operators will be described in the underlying operations.

The concatenation in the control operation provides the source of the branch address. This may be indicated by a constant, a storage item, a literal indicator, or a combination of them. The specification of a storage item indicate that its contents provide the branch address.