Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Onlario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# A modeling technique for specification and simulation of digital systems

Luc Morin

A Thesis

in

The Department

of

Computer Science

Presented in Partial Fulfillment of the Requirements

for the degree of Doctor of Philosophy at

Concordia University

Montréal, Québec, Canada

March 1993

©Luc Morin, 1993

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Oltawa (Ontario) K1A ON4

AND BE A TEMPENE

Children No eleter see

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive permettant la Bibliothèque à nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse disposition des personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-90925-0

#### **ABSTRACT**

# A modeling technique for specification and simulation of digital systems

Luc Morin, Ph. D.

Concordia University, 1993

In this thesis, a new logic modeling technique based on a mathematical abstraction of analog circuits into logic models is proposed. Many approaches have been used for the modeling of digital systems. They range from pure logic to real time models. Mixed circuit-logic models with switches and strength factors are the most popular in commercial simulators. All of these approaches are meant to provide simple and unambiguous descriptions of the logic devices. However, except in their specification of logic functions and simple timing specifications, they differ in other aspects such as the definition of an event, the number of logic levels, the strength factors, the modeling of wire capacitance and the processing of timing constraints and timing violations. The lack of a consensus is the source of many compatibility problems in modern integrated CAD systems where designers and customers need to share information processed by computers. The objective of this work is to lay down the foundations necessary for such a consensus.

The originality of the proposed approach lies in the mathematical formulation of the abstraction mechanism. Precise hypotheses are used to define the logic devices. Then strict construction rules are used to derive their logic models. Three aspects of the logic models are separately considered: the transmission of information over wires using logic events, the propagation delay and the transformation of continuous time to discrete time.

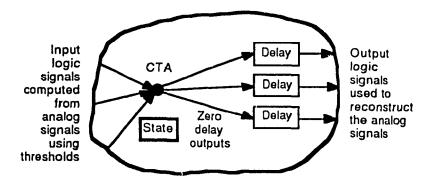

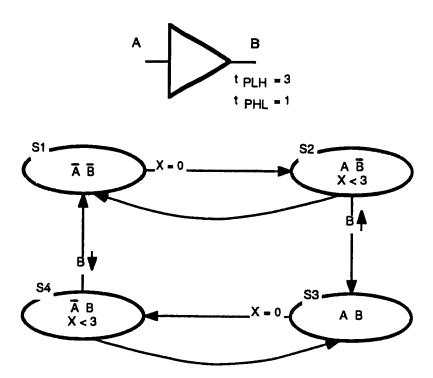

A new logic event definition called master-slave events and a new delay model preserving continuity in the modeled logic signal and causality (cause-effect relationship) in the scheduling of the logic events are proposed. Finally, a new graph based algorithm called a Continuous Time Automaton (CTA) is described to model logic devices and integrate the input timing constraints with the logic function. A CTA is a finite state machine that processes the sequence of input events and transforms the continuous change of state (continuous time) into a timed state sequence (discrete time).

A prototype simulator was developed and CTAs for clocks, pattern generators, gates, combinational circuits, flip-flops, tri-state devices and synchronous sequential circuits are proposed. Without optimization, the performance of the prototype simulator was comparable to many logic simulators for memory requirements, speed and timing accuracy. This modeling technique provides a more accurate logic signal representation, a better model for the physical phenomenon associated with propagation delay and a systematic method to specify and process input timing constraints. It is also easier to use than other logic modeling techniques and it closely matches the engineering approach. On the negative side, the modeling technique is limited to unidirectional signal. However it still permits the use of tri-state busses. Because it accepts and generates analog signals, the proposed model easily interfaces with other circuit models in mixed mode simulation.

This work should be useful to someone working on the specification, design, simulation, formal verification and testing of digital systems. For instance, the new modeling technique could be used for the development of primitives in VHDL.

#### Preface

This work was carried out over a period of five years. The ideas presented here have evolved all along from simple hints to, hopefully, an acceptable and applicable theory. The initial work was carried on metastability and was followed by a study of the logic models used in hardware description languages and simulators. In both cases, I was left with an odd feeling that something was incorrect. There were numerous approaches for the modeling of digital systems, but none seem to be able to justify its superiority on solid grounds. This was confirmed in a paper by M. R. Lightner where he stated that a formalism was yet to be developed for digital elements and their interconnections.

Trying to develop a new formalism for logic model proved to be a difficult task, chiefly because well established concepts had to be questioned and often rejected. The idea of using a finite state machine came early on, but it took quite some time to apply it to a simple buffer, to convince myself of the value of the approach and to refine the concept. These ideas further evolved and became the logic model consisting of classified interface ports, a timing specification, a continuous time automaton (CTA) and a continuity-preserving delay model. Finally, the master slave event concept was introduced to preserve the timing relationships, thus the causality, on the signal and at the input ports. In order to use and exercise the models in some sort of design environment, a hardware description language (HDIL), a data structure (HDIDS) and a logic simulator have been developed.

The core of this thesis consists of three chapters. The formal framework and the definitions are presented in chapter 2. The transmission of information over wires is studied in chapter 3, then the models for logic signals and for propagation delays are described. Finally, the concept of CTA is presented in chapter 4.

I would like to thank Dr. H. F. Li for his support and valuable criticism. This work was carried out at the computer science department of Concordia University, and

I would like to thank all the people who helped me in my work. This work was made possible by the financial support of Université du Québec à Chicoutimi through a three years scholarship. Finally, I would like to thank Michèle and Jacynthe for their personnal support.

## Table of content

| Abbreviations                                                | x                 |

|--------------------------------------------------------------|-------------------|

| Glossary                                                     | xi                |

| Chapter 1 Introduction                                       |                   |

| Chapter 1 Introduction                                       |                   |

| 1.1 Problem overview                                         |                   |

| 1.2 Basic definitions                                        |                   |

| 1.3 Design process                                           | 5                 |

| 1.4 Simulation and verification                              |                   |

| 1.5 The problem of modeling analog devices with logic models | 10                |

| 1.5.1 Time invariance and logic simulation                   | 12                |

| 1.5.2 Causality and logic simulation                         |                   |

| 1.5.3 Continuity and combinational devices                   |                   |

| 1.5.4 Continuity and sequential devices                      |                   |

| 1.5.5 Continuity and changes of state                        | 14                |

| 1.6 Problems with current modeling techniques                |                   |

| 1.6.1 Signal representation problems                         | 16                |

| 1.6.2 Propagation delay model problems                       |                   |

| 1.6.3 Changes of state problems                              |                   |

| 1.6.3.1 Device timing constraints                            |                   |

| 1.6.3.2 Signal timing constraints                            | 21                |

| 1.6.3.3 Real time systems                                    | 22                |

| 1.7 Proposed logic modeling technique                        |                   |

| 1.7.1 Step 1: What is a logic device?                        |                   |

| 1.7.2 Step 2: What is a logic model?                         | 27                |

| 1.7.3 Outline of step 3: Construction of logic models        |                   |

| 1.8 Summary                                                  | 30                |

|                                                              |                   |

| Chapter 2 Formal framework                                   |                   |

| 2.1 Mathematical premises                                    | 32                |

| 2.2 Signals and information                                  | 33                |

| 2.3 Signal transformation                                    |                   |

| 2.4 Logic event                                              |                   |

| 2.5 Logic signal                                             | 30<br>37          |

| 2.6 Logic devices and digital systems                        | <i>ጋ የ</i><br>2 ዩ |

| 2.7 Logic Simulator                                          |                   |

| 2.7.1 Purpose of simulation                                  | 43<br>12          |

| 2.7.1 Pulpose of simulation                                  |                   |

| 2.8 Conclusion                                               | 45<br>45          |

| Chapter 3  | Time model:             | logic signal       | and prop  | agation                                 | delay    |

|------------|-------------------------|--------------------|-----------|-----------------------------------------|----------|

| 3.1 Logic  | event set               |                    |           |                                         | 46       |

|            | Master output ever      |                    |           |                                         |          |

|            | lave input events       |                    |           |                                         |          |

|            | model                   |                    |           |                                         |          |

| 3.3 Simula | tion algorithms         |                    |           |                                         | 58       |

|            | specification usir      |                    |           |                                         |          |

| 3.4.1 H    | lardware linker and     | d Electrical Rule  | Checking  | (ERC)                                   | 61       |

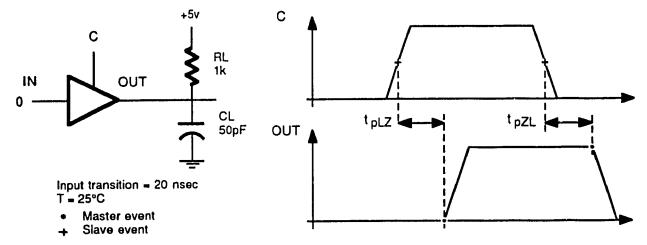

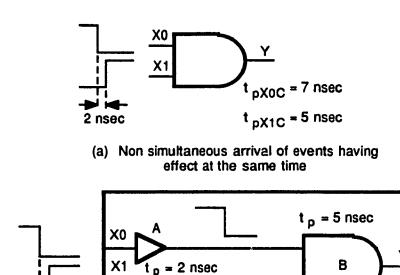

| 3.4.2 T    | iming specification     | of a gate          |           | • • • • • • • • • • • • • • • • • • • • | 61       |

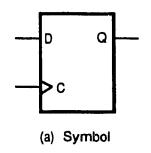

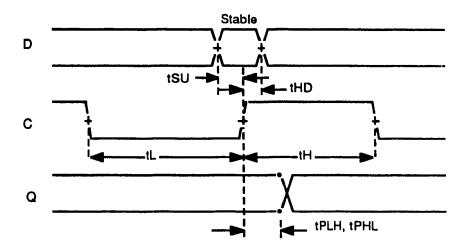

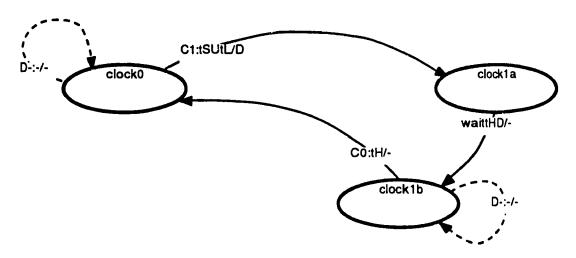

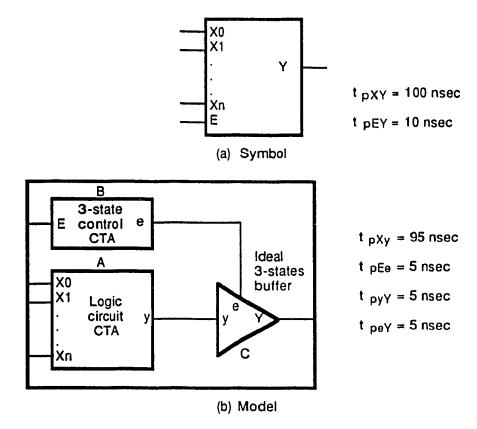

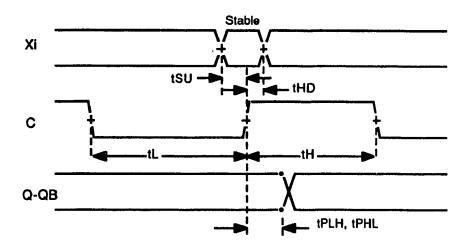

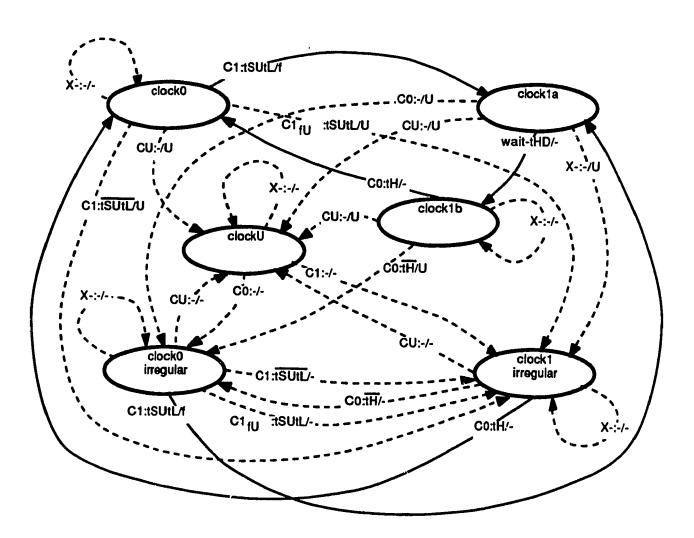

| 3.4.3 T    | iming specification     | of a flip-flop     | •••••     |                                         | 62       |

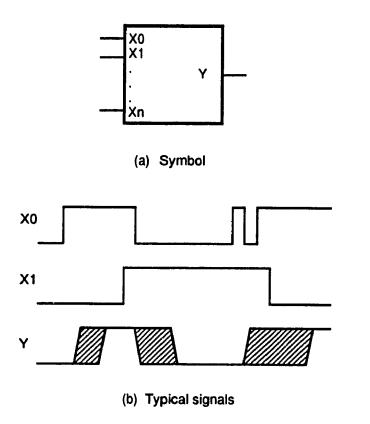

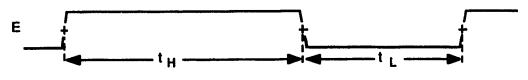

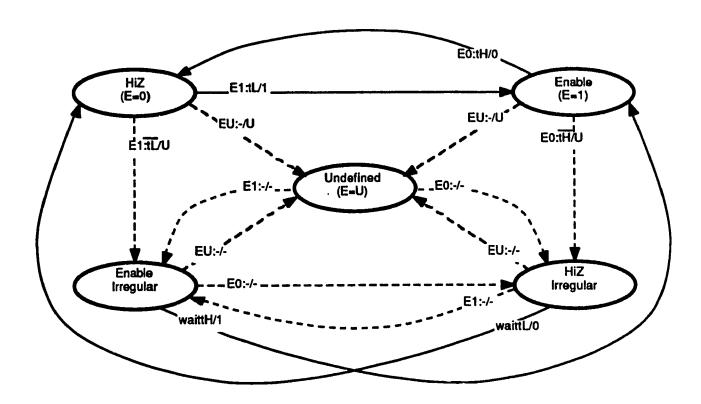

| 3.4.4 T    | iming specification     | n of a 3-state but | fer       |                                         | 64       |

| 3.5 Conclu | sion                    |                    | ••••••    | •••••                                   | 65       |

| Chapter 4  | State model:            | Continuous         | Time Au   | itomaton                                | (CTA)    |

|            | ction                   |                    |           |                                         |          |

|            | t logic modeling to     |                    |           |                                         |          |

|            | ew of a CTA             |                    |           |                                         |          |

|            | ions                    |                    |           |                                         |          |

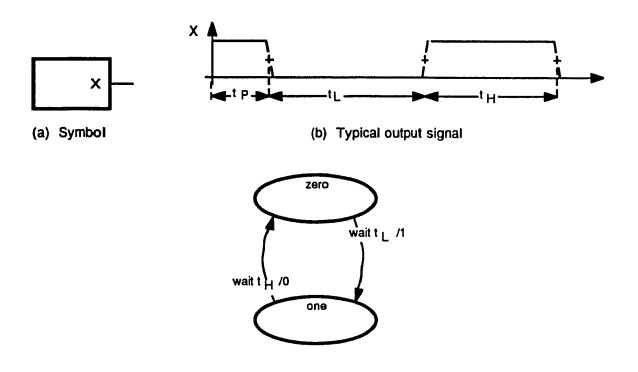

| 4.5 Examp  | oles of CTAs            |                    |           | •••••                                   | 80       |

|            | The wait state trans    |                    |           |                                         |          |

|            | he logic function       |                    |           |                                         |          |

|            | The state variables     |                    |           |                                         |          |

|            | The timing constra      |                    |           |                                         |          |

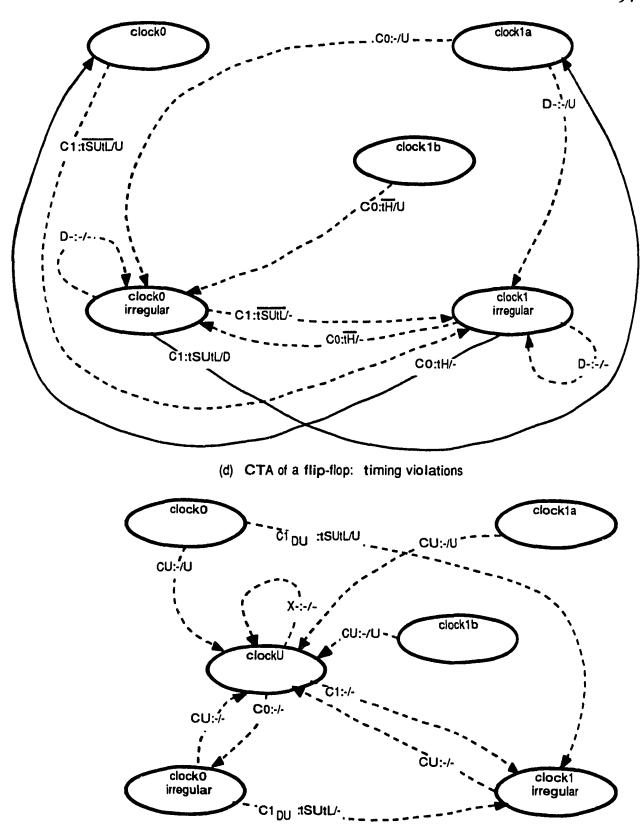

|            | Indefined input log     |                    |           |                                         |          |

|            | uction of a CTA fo      |                    |           |                                         |          |

|            | partitioning and e      |                    |           |                                         |          |

|            | Gates Tip-flops and SSC |                    |           |                                         |          |

|            | Combinational circ      |                    |           |                                         |          |

|            | ri-states devices       |                    |           |                                         |          |

|            | Flip-flops and SSC      |                    |           |                                         |          |

|            | More about SSC          |                    |           |                                         |          |

|            | ision                   |                    |           |                                         |          |

|            |                         |                    |           |                                         |          |

| Chapter 5  | -                       | ion, results a     | •         |                                         | -        |

|            | nentation               |                    |           |                                         |          |

|            | arameter extraction     |                    |           |                                         |          |

|            | inking algorithm a      |                    |           |                                         |          |

|            | nplementation of t      |                    |           |                                         |          |

|            | ation results and s     |                    |           |                                         |          |

| 5.3 Comp   | arative analysis        |                    |           |                                         | 113      |

| 5.3.1 C    | Comparing abstract      | ion mechanisms     | and conce | ptual mod                               | lels 113 |

|            | ignal representation    |                    |           |                                         |          |

|            | ropagation delay n      |                    |           |                                         |          |

|            | iming constraints       |                    |           |                                         |          |

|            | Comparison of the       |                    |           |                                         |          |

|            | dequacy with eng        |                    |           |                                         |          |

| 5.5 Conclu | ision                   |                    |           |                                         | 128      |

| Chapter 6    | Conclusion                      |     |

|--------------|---------------------------------|-----|

| 6.2 Results. | work                            | 133 |

| References   |                                 | 136 |

| Appendix A   | Binary Decision Theorem (BDT)   | 142 |

| Appendix B   | HDIL reference manual           | 165 |

| Appendix C   | HDIDS reference manual          | 191 |

| Appendix D   | CTA based logic models          | 198 |

| Appendix E   | Listings and simulation results | 220 |

#### **Abbreviations**

ASC Asynchronous Sequential Circuit

BDT Binary Decision Theorem

CIF Caltech Intermediate Form

CMOS Complementary Metal Oxide Semiconductor

CPU Central Processing Unit

CTA Continuous Time Automaton

DDMS Design Data Management System

DRC Design Rule Checking

DSP Digital Signal Processing

ERC Electrical Rule Checking

HDIDS Hardware Description and Integration Data Structure

HDIL Hardware Description and Integration Language

HDL Hardware Description Language

MITL Metric Interval Temporal Logic

PLA Programmable Logic Array

RAM Random Access Memory

ROM Read Only Memory

RTL Register Transfer Logic

SSC Synchronous Sequential Circuit

TA Timed Automaton

TL Temporal Logic

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

VLSI Very Large Scale Integration

#### Glossary

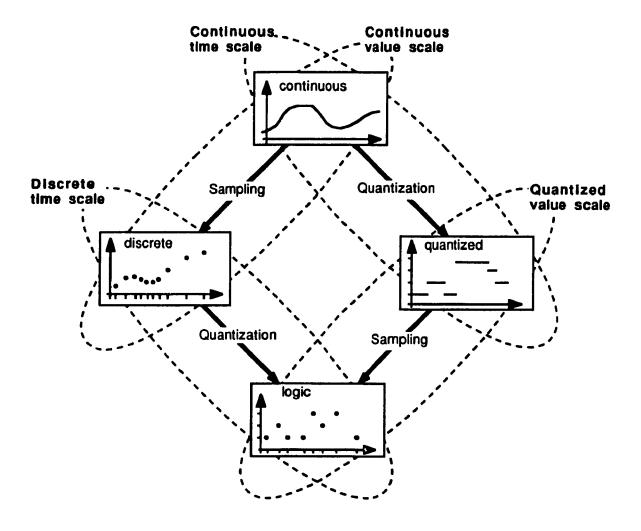

#### 1.0 Basic definitions

Function Unique mapping of a set called the domain onto another

set called the range.

Continuous Function mapping real onto real.

Discrete Function mapping natural onto real.

Quantized Function mapping real onto natural.

Digital Function mapping natural onto natural.

Sampling Transformation of the domain set from real to natural.

Quantization Transformation of the range set from real to natural.

Signal Abstraction used to represent the information contained

in a physical variable.

Analog An analog signal is a continuous function of time. All

signals are analog.

Point Element of an analog signal.

Discrete A signal is discrete if it is completely described by a

discrete function and an interpolation function.

Sample Element of a discrete signal.

Digital A signal is digital if it is completely described by a digital

function and an interpolation function. The digital function can map to a set like {0, 1} not necessarily related to

voltage thresholds.

Event Element of a digital function. An event describes the

assertion of a proposition, for example "crossing a

threshold,  $f(t)=V_{th}$ ".

Interpolation function Function that describes how the analog signal is

reconstructed from the samples or the events.

Synchronous signal Two digital signals are synchronized if any pair of events

taken from these signals are synchronized. Two events are synchronized if the relation between their occurrence

is explicitly known.

#### 2.0 Digital systems

Physical information Information related to the physical aspects, such as:

layout, mask, electrical parameters.

Layout Geometric description of the integrated circuit produced

by the IC designer and used for mask generation.

Mask Geometric description of the integrated circuit used for

the fabrication.

Wafer Unit for the production of ICs. There are many ICs

fabricated on one wafer.

Chip Portion of the wafer cut and installed in a package.

Package Mechanical support for the chip. The package with the

chip forms the integrated circuit.

Pad Metal area on the chip for bonding the external wire.

IOcircuit Refers to the interface circuit for the pad (protection

circuit for inputs and buffers for outputs).

Frame Refers to the element of the layout delimiting the

boundaries of the chip.

Cell Refers to a pre-designed function ready to be used within

a chip.

Electrical properties of the material

Refers to the surface resistivity or the normalized capacitance for the various materials or elements

fabricated on a chip.

Structural information Information about the organization of the digital circuit,

such as:

Circuit This is the basic abstraction in digital system, the

physical world is discretized into elements and wires

which form the circuit.

Element The element is either a part, like a 68000, or another

circuit allowing for hierarchical description.

Wire This is the abstraction of the conductor interconnecting

the elements in a circuit.

Port This is the abstraction of the point of connection on the

element. An element may have many ports.

Technology independence A piece of information defined such that technology does

not affect its definition. Physical information is technology dependent and structural and behavioral

information are technology independent. For example, the electrical model of a gate is technology dependent since it would be different for CMOS and TTL gates. On the other hand, the logic model is technology independent since it would be the same for both technology.

#### 3.0 Design process

Design

This is the first phase in problem solving, the specification is studied and a knowledge based model is constructed. When there is enough detail in the model, we assume a solution has been found. This part of the problem solving process is rarely automated. It consists in searching information in the design data base either manually or with the help of design assistant programs.

Specification

The initial description of the desired digital system or

component.

Solution

This is the result of the design phase. A solution is a knowledge based model, it is often imprecise even contains contradiction which will be resolved with design

verification cycles.

Technology based model

Class of information, such as the extracted model, normally processed with deterministic algorithm.

Knowledge based model

Class of information normally processed with nondeterministic algorithm, such as the information during

the early phase of the design.

Synthesis

Automated process that takes a specification and

produces a solution or directly a circuit.

<u>Implementation</u> This is the second phase of the problem solving process.

Often automated, the implementation takes a solution

and produces either a model or the actual hardware.

Model This is the result of the implementation. The verification

consists in the simulation or the analysis of the model.

Actual hardware This is the result of the implementation. The verification

consists in testing the actual hardware.

Custom design Technique of implementation where most of the cells are

designed individually and specifically for the digital

system.

Standard cell Technique of implementation where most of the individual

cells are common to many projects and are usually stored in a library. The implementation consists in placing the

cells and connecting them.

Gate array Technique of implementation where the cells are already

placed. The implementation consists in connecting them.

Placement Process, now automated, to find an optimum place for

each cell. The main criteria is the minimization of wire length. There are many algorithms, usually beginning with constructive placement followed by iterative

placement.

Constructive placement

Placement technique where the area is initially filled from

one end to the other.

Iterative placement

Placement technique using pair-wise interchange to

optimize the initial placement.

Routing Process of connecting the cells according to the netlist.

The routing consists in finding a channel(s) for each wire

and then assigning a track to the wire in the channel.

Route Sequence of channels used by a wire.

Channel Region of the layout reserved for wires.

Track Each channel is divided in tracks.

Global routing

Process of finding a route for a wire.

Channel routing

Process of assigning a track to a wire.

Silicon compilation Automated process to create the layout based on a user

description of the desired function. The compiler assembles the layout primitives or library cells to build

the desired circuit.

Structural compilation

Compilation based on the structural information, usually

the schematic diagram.

Behavioral compilation

Compilation based on the behavioral information.

Verification

This is the third phase of the problem solving process. Once a model or the actual hardware is available, it must be verified. Verification consists in simulation, analysis

or formal verification on the model or test on the

hardware.

Simulation Process of exercising the model under certain operating

conditions. No comparison is made to the specification.

Analysis The model is analyzed and specific aspects of the

specification are compared to the value obtained with the model. Timing analysis is a popular analysis technique, where propagation delays are computed and compared

with the specified ones.

Formal verification The model is formally compared with the specification.

All aspects of the specification are verified.

Test Process of exercising the actual hardware.

Result Describe the results obtained from the verification phase.

Evaluation This is the fourth phase of the problem solving process,

where the results are analyzed and compared with the specification and design decision or modification are

made.

Design/evaluation cycle Refers to the repetition of the design process. Many

cycles are usually required to obtain a system meeting

completely the specification.

Hierarchical design The design proceeds in step-wise refinement, from

system level down to circuit level or layout. At each level, the design/evaluation cycles are repeated as

required.

#### 4.0 Design environment

Design environment Computer based environment used by the digital system

designer. A design environment consists of a set of tools

and a design data base.

Design data base A generic term that refers to the information available to

the designer, including books, papers and colleagues.

Design assistant Since complete automation of the early phases of the

design is impossible, specific programs, called design assistant, can be used to help the designer search the

design data base and guide him in his decisions.

Tool A program specialized in solving a specific task, like a

PLA compiler or a placement and routing program. If the tool is used in the design phase it is called a design

assistant.

<u>Integration</u> The tools in the design environment need to share

information. A well integrated design environment allows the tools to share their information without human

intervention.

External integration Refers to the sharing of the information through files.

Internal integration Refers to the sharing of the information through active

memory.

#### 5.0 Model and simulation (behavioral information)

Model Mathematical representation of a system intended to

reproduce its response to input stimuli. There are many levels of models: circuit, switch, timing, logic, register

based.

Electrical model Model describing the elements by equations relating

voltages and currents at the ports.

Timing model Simplified electrical model allowing fast computation of

the timing. Switch models with capacitances are often

used.

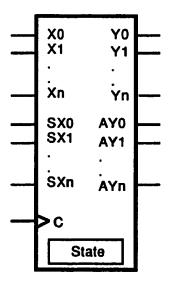

Logic model Model consisting of interface ports, a state, a state

transition function, an output function and a timing

specification.

Port class For the purpose of modeling, each port is classified as

either input, output, asynchronous input, synchronous

input, bidirectional, high voltage input, clock ...

State (Q) Whatever is required to allow the prediction of future

events without the knowledge of the past inputs.

Logic state Abstract state required to model the logic behavior (flip-

flop, registers ...).

Time related state variables

Set of state variables required to process accurately the timing specification of input and output events, often used

to store the occurrence of past events.

Continuous change of state Refers to a system whose model is characterized by an

infinite number of changes of state in a finite interval of

time.

Discrete change of state or timed state sequence

Refers to a system whose model is characterized by a finite number of changes of state in a finite interval of

time.

State transition function ( $\delta$ ) Describes the change of state based on the current state and the current inputs.

Output function  $(\lambda)$  Describes the output to be produced based on the current

state and the current inputs.

Time invariant load Characteristic of a load stating that it does not change

during the course of a simulation.

Event set A set of propositions describing properties of a signal

that occur at specific instant. Logic events are often

propositions describing the crossing of thresholds.

Threshold based events Describes an event set based on fixed threshold

crossing.

Signal based events Describes an event set based on certain properties of

the signal such as  $\frac{dx}{dt} = 0$ .

2-valued logic Algebra based on the Boolean values 0 and 1, often

augmented by U (undefined) and Z (high impedance) for

simulation purpose.

Multiple-valued logic Algebra based on more than two values. Values 0, X

and 1, augmented by U (undefined) and Z (high

impedance) are often used.

Model extraction Process of computing the model based on layout

information.

Hardware linking Process of computing the logic model parameters such as

the propagation delay based on the interconnection network characteristics such the wire capacitance. Linking rules (fan-in and fan-out) are also verified during

hardware linking.

Discrete event simulation Simulation based on the discretization of time and on the

causality of real systems.

Mixed-mode simulation Simulation using mixed models, like circuit and logic.

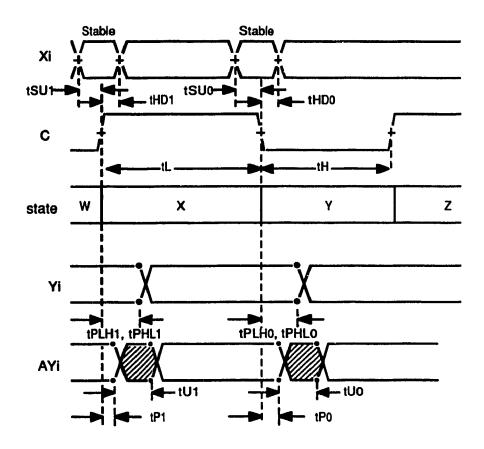

Timing specification Consist of:

Timing constraints Set of separation times between input slave events that

must be meet to insure proper operation of the logic

device.

Propagation delays Set of separation times between input slave events and

output master events that models the effect of RC

circuits.

Timing violation Pair of events whose separation does not meet a timing

constraint.

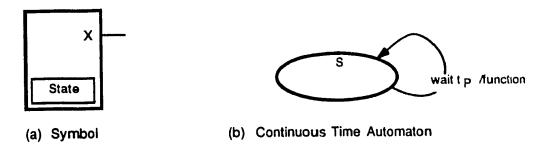

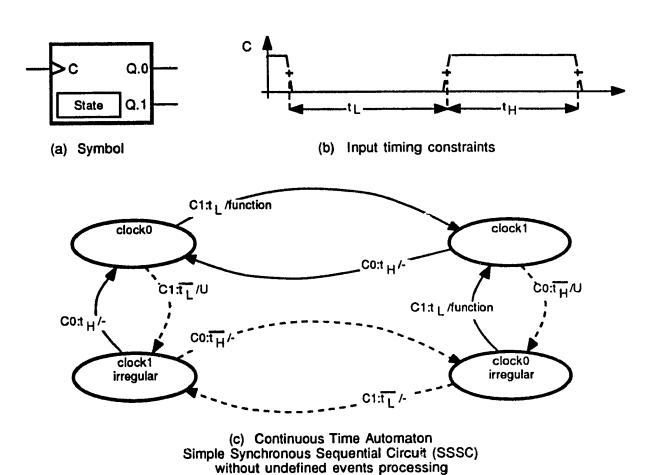

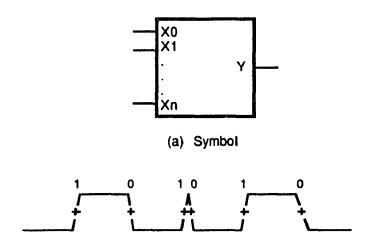

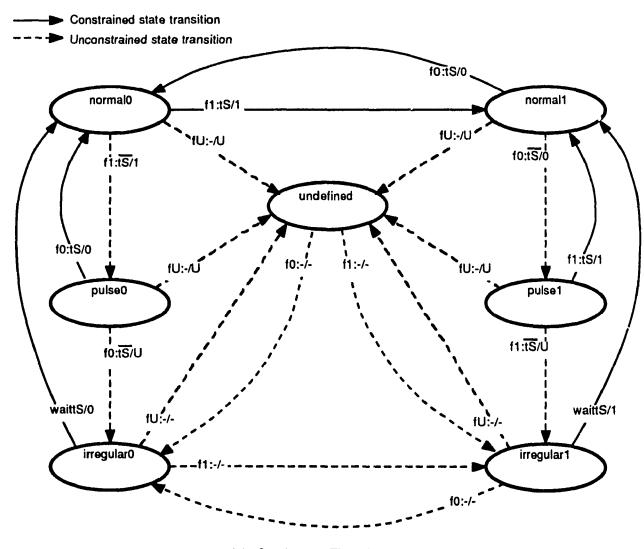

Continuous Time Automaton

State machine used to transform continuous change of state into timed state sequence.

#### Constrained state transition

State transition in a CTA that requires a finite amount of

simulation time.

Unconstrained state transition

State transition in a CTA that might require zero

simulation time.

Constrained cycle Cycle in a CTA made of at least one constrained state

transition.

Cycle in a CTA made only of unconstrained state Unconstrained cycle

transition.

Logic signal made of a finite number of event in any Constrained signal

interval of time.

Logic signal made of possibly an infinite number of events Unconstrained signal

in a given interval of time.

Timed sequence of events Sequence of events describing a constrained signal.

# Introduction

Since the early days of digital systems, designers have been modeling logic devices for various purposes. There was the simple approach using Boolean equations, then the engineering approach leading to data books and the more recent approach using logic models specified with hardware description languages like VHDL. Even if logic devices are simple to understand and use, modeling them is not so obvious because of:

- the complex relation between the logic function and the timing specification,

- the continuous nature of the analog circuits from which logic devices are built

- and indirectly, the need of unambiguous models for computer analysis and simulation.

The design of very high speed integrated circuits requiring highly optimized logic devices and the absence of simple but accurate models have placed a continuous demand for research in this area. The objective in this chapter is to describe the problem of constructing logic models for analog devices and to outline the proposed logic modeling technique.

#### 1.1 Problem overview

The object of this thesis is to study the abstraction mechanism involved in modeling an analog circuit at logic level. In particular, we wish to accurately model glitches and fine timing details as required by modern technology. An abstraction mechanism is comprised of:

- a set of axioms and hypotheses to define a level of abstraction (analog),

- a set of axioms and hypotheses to define another level of abstraction (logic),

• and a set of rules for the construction of a mathematical representation at one level based on the other level.

The general problem is the lack of a consensus on the axioms, the hypotheses and the construction rules for logic models leading to numerous and often incompatible logic modeling techniques [28]. For example, the following problems have been reported as sources of incompatibilities with VHDL models [32]:

- Logic level definition

- Signal strength definition

- Logic event definition

- Interpretation of timing specification

- Handling of unknown operating condition

In order to improve the logic model, each object used will be mathematically defined and each step of the process will be mathematically formulated. The process of finding a logic model for an analog circuit will be divided into three steps.

- Step 1: define the analog circuit properties that makes it a logic device.

- Step 2: define the characteristics of a logic model for that logic device.

- Step 3: construct the logic model.

The construction of a logic model is further divided into three parts:

- the transmission of information on wires,

- the propagation delays and

- the state.

In this chapter, current modeling techniques will be reviewed to illustrate the importance of following the above steps. Then, the definitions for logic devices (step 1) and logic models (step 2) will be given, followed by an outline of the proposed modeling technique (step 3).

#### 1.2 Basic definitions

It is necessary to begin our discussion about logic modeling with intuitive but carefully formulated definitions for the objects that will be used.

- Wire: A wire is a physical element carrying the continuous voltages and currents between the ports of analog devices or logic devices.

- Analog device: An analog device is characterized by a set of analog ports and

continuous functions. An analog port transfers the voltage and the current from

the inside to the outside of the device or vice versa. The device processes the

continuous voltages and currents at the ports according to some continuous

behavior specification.

- Analog circuit: An analog circuit is a network of analog devices connected with wires. The relation between the voltages and the currents at the ports of the analog devices and in the analog circuit are governed by Kirchhoff laws.

- Analog signal: An analog signal is a mathematical representation of the information carried by a wire. It consists of a continuous function of time modeling the voltage or the current.

- Analog model: An analog model is a mathematical representation of the behavior of an analog device. It consists of set of analog ports, a set of continuous state variables and a set of continuous equations describing how the state, the voltages and the currents are related.

- Logic device: A logic device is characterized by a set of logic ports and a logic function. A logic port is an analog port with the following restrictions: a logic input port is sensitive to threshold crossing and a logic output port produces a voltage compatible with the input ports. The device processes the continuous voltages and currents at the ports according to some logic behavior specification.

- Logic circuit: A logic circuit is a network of logic devices connected with wires. The

relation between the voltages and the currents at the ports of the logic devices

and in the logic circuit are governed by Kirchhoff laws.

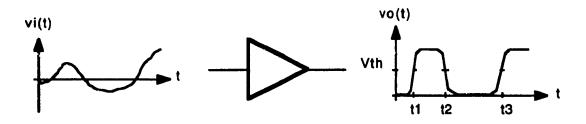

- Event set: An event set is a set of labelled predicates describing an instantaneous property on an analog signal. For example, the binary event set is often defined as:

{ label 0 :

$$(v(t) = V_{th} \text{ and } \frac{d \ v(t)}{dt} < 0)$$

, label 1 :  $(v(t) = V_{th} \text{ and } \frac{d \ v(t)}{dt} > 0)$ }

- Logic event: A logic event is a tuple consisting of a label describing the event and the time it happens.

- Logic signal: A logic signal is a time ordered sequence of logic events.

- Logic model: A logic model is a mathematical representation of the behavior of a logic device. It consists of set of logic ports, a set of discrete state variables and a set of discrete and logic equations describing how the state, the input events and the output events are related.

- Continuous time or continuous change of state: This is the characteristic of a model

whose state is a continuous function of time. This is also referred to as dense

time.

- Discrete time or discrete change of state: This is a characteristic of a model whose state is a discrete function of tim? In discrete time, there is a finite number of state changes in any interval of time.

- Timed state sequence: A timed state sequence is a sequence of state changes in discrete time.

- Timing constraints: The set of timing constraints is a set of real numbers used to

define an acceptable sequence of logic events that can drive a given logic device

(Ex: set-up time, hold time). Event separations are compared with timing

constraints to detect timing violations.

Propagation delays: The set of propagation delays is a set of real numbers used to

model the delay between an input event and an output event in a logic device.

The propagation delays are used in simulation by a propagation delay model.

#### 1.3 Design process

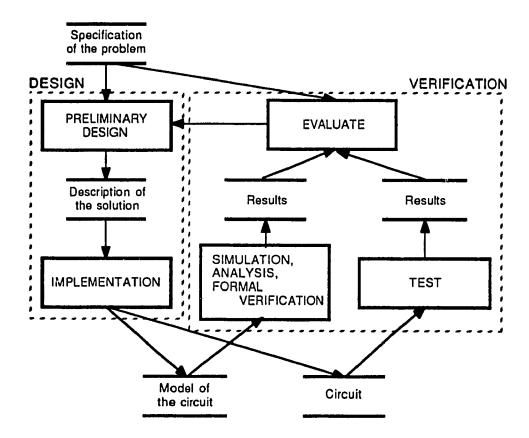

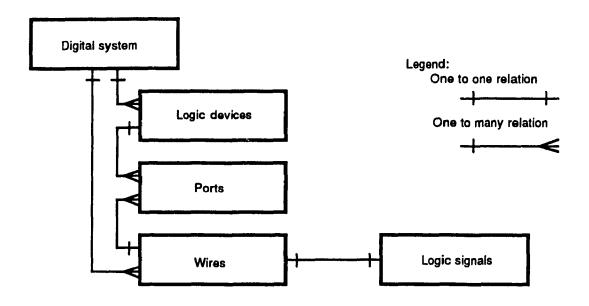

The objective of modeling in this thesis is to support the specification, the analysis and specially the simulation of digital systems at logic level. Since these constitute the major components in digital system design, it is therefore appropriate to spend some time to review the design process. As illustrated in Fig. 1.1, the design process is decomposed into two parts, design and verification. Design consists of transforming a specification into a circuit and verification insures that the proposed

Fig. 1.1 Digital system design process

circuit meets the specification. Design/verification cycles are repeated as many times as required until a correct circuit is obtained. Design generally begins with a preliminary design followed by an implementation. In the preliminary design phase, the specification is analyzed, a number of solutions are studied and one of them is selected. In the implementation phase, the selected solution is realized. The design checking then consists of an analysis, a formal verification or a simulation of the model. Verification terminates with an evaluation phase, where the results are analyzed and the design is modified as required. Design/verification cycles are carried out at different levels. From a general specification a system architecture can be derived, from a system architecture a register transfer model can be designed, and with more design cycles, detailed circuits are obtained. In this thesis, we are interested in the design and verification at logic level.

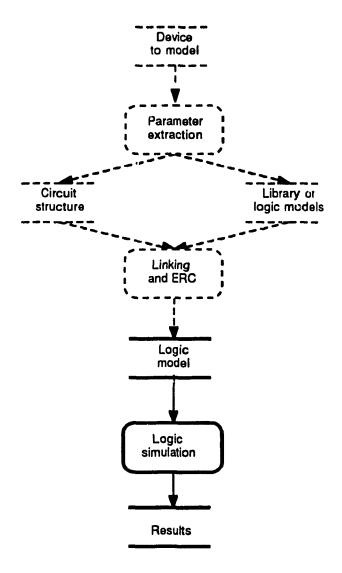

Until 1980, separate computer programs were used for solving specific problems in the design process [1]. For example, different tools were used for layout editing, physical rule checking, compaction, circuit extraction and simulation. Since then, design environments have greatly evolved and usually provide an integrated set of tools to support the designer in most phases of the design process [2]. The design of digital systems at logic level, consists in using manually designed elements or compiled modules (PLA, ROM, RAM, DSP, ...) and drawing the schematic diagram of the circuit. This is normally followed by automatic placement and routing, model extraction and simulation. In certain cases, the design might be reduced to writing a high level description and compiling it directly into a chip [3].

#### 1.4 Simulation and verification

Even though the trend in CAD systems is to automate synthesis [4], the need for effective verification tools is still strong. The tools are classified according to the completeness of checking of a design against its specification:

- Formal verification tools: The extracted or computed model of the composite

system is compared with the requirement specification. Both the model

and the specification are described using a special description language

and the model is proved to satisfy the specification mathematically.

This is quite complex and is practicable for smaller systems.

- Analysis tools: The model is partially compared with certain requirements in the specification. For example, timing analysis is often used to compare the computed timing parameters of the model with the specified timing.

- Simulation tools: The model is exercised for a restricted set of inputs and the simulation results are compared against the specification. The simulator does not make any comparison.

Each of these tools relies on a good model, one that faithfully captures the essential properties of the real system. Simulation tools are still the most popular. They are classified according to the level of abstraction: device, circuit or logic.

#### Device simulation

Device modeling uses discrete elements to model the physical structure (two or three dimensions) of a device and the simulation consists of predicting the current and voltage distributions in the device [5]. This type of simulation is useful to determine current concentration, to assert the circuit parameter values or to check the precision of a circuit model.

#### Circuit simulation

Circuit models assume that the 3-dimensional continuous physical world is discretized into elements and wires. The elements are modeled by a set of equations describing the relationships among the voltages and currents of the polics. A simulation of these elements involves in solving the set of network equations based on Kirchoff laws [6, 7]. Third generation circuit simulators have improved performance

by making use of space and time sparseness [8] and special circuit structure [9-11]. By using tabular models with adjustable precision, the simulation of a circuit can be further speeded up [12].

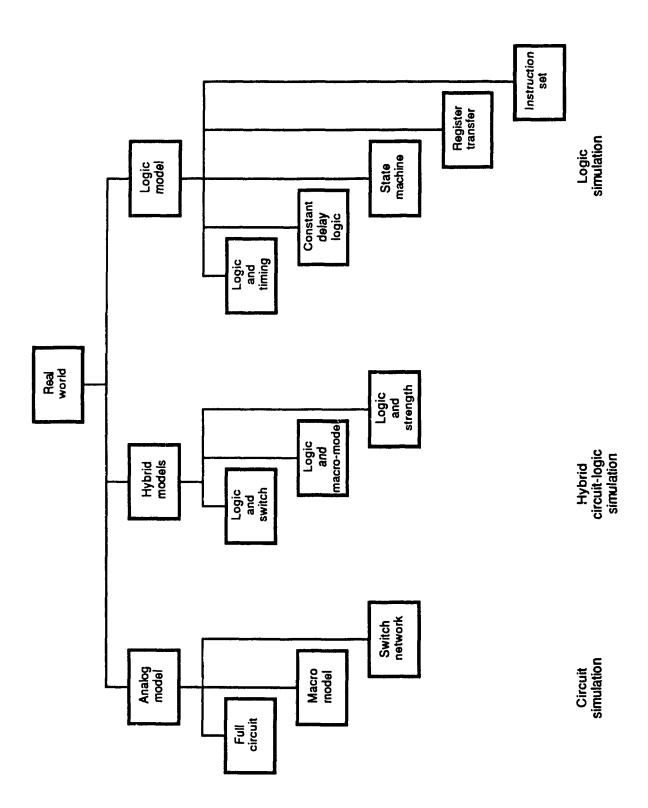

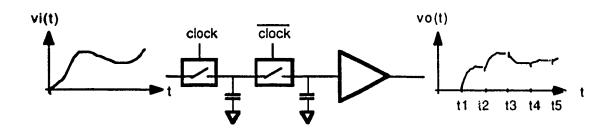

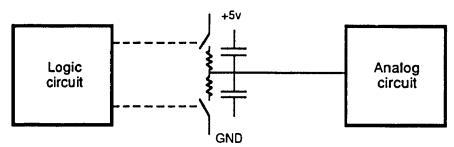

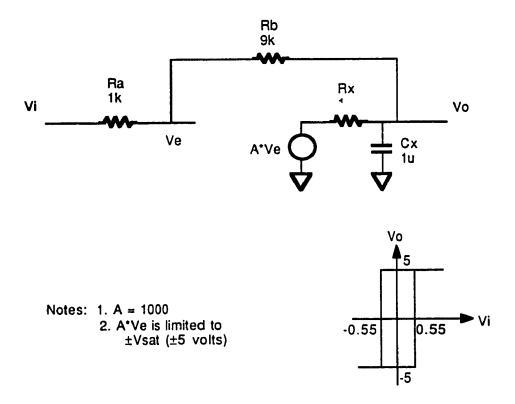

The large digital systems to simulate and the quest for speed have forced the designers to use simplified models. Since only timing specification need be determined, the simplified models were optimized to predict the propagation delays (see Fig 1.2). Two approaches have been used: macro-models and switches. A switch is a simplified model for a transistor and a switch based simulation often called timing simulation consists in predicting the waveshape of signals by assuming that the voltage at each port is the result of a network of resistors, capacitors and switches. In the case of MOS circuits, the switch model is easily extracted from the layout. Its interpretation is simple and the simulation results are reasonably accurate. This probably accounts for its popularity [13-20]. The switch-level modeling technique has also been applied to model bipolar logic circuits [21-23].

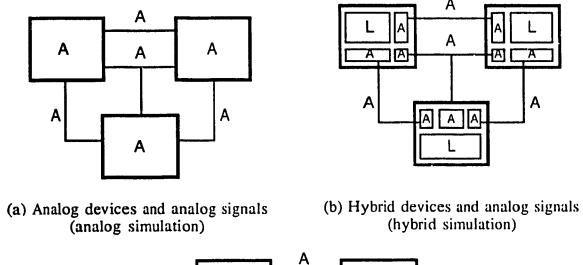

Macro-models are used to model a group of transistors performing a logic function. The electrical behavior of the output stage is modeled in detail using controlled sources, resistors and capacitors [24-26]. The objective is to be able to connect logic devices to analog circuit, perform a simulation and improve the accuracy compared with a simple logic model with only a propagation delay. As shown in Fig. 1.2, macro-models are also used in hybrid circuit-logic simulators [36-38]. The macro model of a logic device is similar to an operational amplifier which is modeled using Thevenin equivalent and transfer function instead of transistors. Switch and macro based simulations are useful to simulate circuit whose complexity would make an analog simulation too costly.

As shown in Fig. 1.2, hybrid models use macro-models, switch networks or strength factors or a combination of these. Hybrid models combine the speed of logic simulation for the internal operation of the devices with the accuracy of analog

Fig. 1.2 Classification of models

simulation for the interconnection network and the special devices. The major problem with hybrid simulation is that network equations based on Kirchoff laws need to be solved, but again this is a trade off between accuracy and speed.

#### Logic simulation

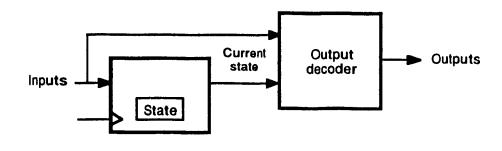

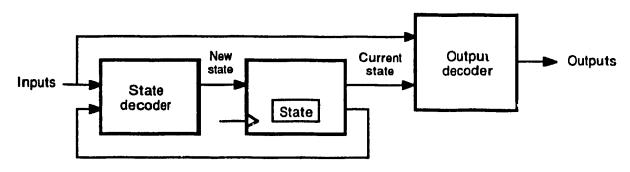

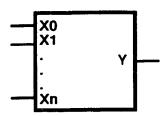

The next level up in the abstraction is the logic level. At analog level, the device state is a continuous function of time and at logic level, the device state is a discrete function of time. Basically, continuous time is discretized. The definition for logic models will be given in the next section, but we can safely say that a logic model consists of a logic function, a state and a timing specification. Since the subject of this thesis is logic simulation, we will review all of the related topics at the proper time.

### 1.5 The problem of modeling analog devices with logic models

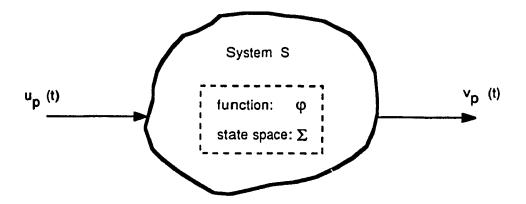

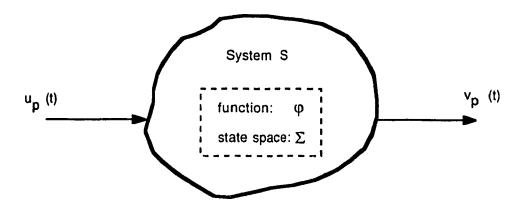

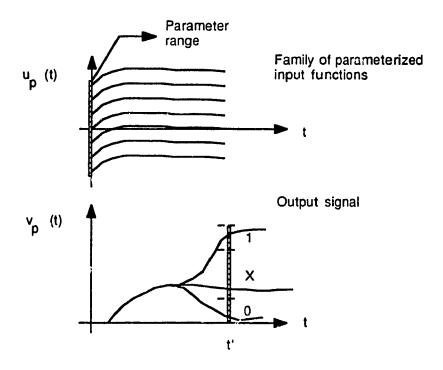

The construction of logic models begins with analog circuits. It is therefore essential to understand the behavior of analog devices and systems. The usual model taken from classical system theory will be used. The system S in Fig. 1.3 represents a logic device. For simplicity, imagine it is a logic buffer. It is driven by an input signal  $\mathbf{u}_{\mathbf{p}}(t)$  and produces an output signal  $\mathbf{v}_{\mathbf{p}}(t)$ . The input and output signals are parameterized using the continuous parameter p.

Assumptions: 1. S is a continuous, causal and time invariant system.

- up(t) is a function dependent on the continuous parameters p and t

(time). Varying p generates a family of parameterized input signals.

- 3.  $v_p(t)$  is the output of S for a given  $u_p(t)$ .

More formally, the system has a state  $s \in \Sigma$  and is modeled by a continuous function  $\phi$ :

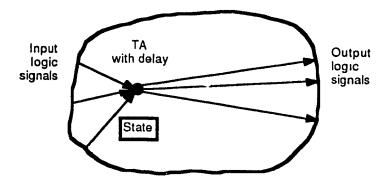

Fig. 1.3 Logic device

$$\Sigma$$

: { s | s is a state of S }  $\Sigma$  = R x R x R ... x R = R<sup>m</sup>

$\Sigma$  is the set of all state variables.

$$U_p = \{ u_p(t) \mid u_p(t) \text{ is a parameterized input function } \}$$

Each element of  $U_p$  is a function of the parameter p and the time t:

$$u_p(t): R \times R \rightarrow R$$

$$\phi\colon\thinspace\Sigma\:x\:U_p\:x\:R\:\to\:R$$

The function  $\phi$  maps a state,  $s \in \Sigma$ , at time t=0, an input function  $u_p(t) \in U_p$  on the interval [0, t], and the time,  $t \in R$ , into the value of  $v_p(t)$  at time t.

$$v_p(t) = \varphi (s, u_p, t)$$

The devices used in digital systems are continuous, causal and time invariant.

While constructing a logic model, it will be required to decide whether or not these

properties should be preserved. In the remaining of this section, these properties will be defined and studied with respect to logic devices and logic simulation.

#### 1.5.1 Time invariance and logic simulation

A system is time invariant if, given the initial state at  $t_0$  and the input signals beginning at  $t_0$ , the resulting changes of state and the output signals after  $t_0$  will always be the same for any  $t_0$ . More formally, since  $v_p(t) = \phi$  (s,  $u_p$ , t) is the response of the system S on the interval [0, t], then if the initial state at time T is also s and if the input signal is simply time shifted  $u_p(t-T)$ , then  $v_p(t-T)$  will be the response on the interval [T, t+T].

Time invariance is easily preserved in a logic simulator. Given any initial time, a logic simulator normally produces the same results for the same initial state and the same input signals.

#### 1.5.2 Causality and logic simulation

A system is causal if any changes at the inputs always precede its effect on the state and the outputs. More formally,  $v_p(t')$  may depend on  $u_p(t) \ \forall t < t'$  but does not depend on  $u_p(t) \ \forall t \ge t'$ . Causality is the essential justification for modeling propagation delay.

Whether it is analog or logic, a simulation always consists of predicting the future given the state of the model at current time and the inputs. Analog simulation is based on the sample-and-hold principle, the state and the outputs at the next time step are all evaluated simultaneously. The time step is very small and the prediction is based on the linearization of the set of differential equations that describe the circuit. Causality is always preserved since all voltages and all currents and therefore all changes of state are computed for the same time interval.

Logic simulation is event-driven and the simulation algorithms are based on the cause-effect principle: event X causes event Y. The new state and the outputs are evaluated sequentially, not simultaneously. Thus causality is crucial and establishing causality in the logic model and handling timing relationship and causal events efficiently and accurately are the key to satisfactory logic simulation. Since the event occurrences depend on the event definition, the selection of an event set will be critical to the success/effectiveness in logic simulation. Otherwise, management of time advancement poses an inefficiency problem in simulation.

Preserving causality in the logic model simply requires a strictly positive propagation delay model. With negative propagation delay, an input event X arriving at time  $t_X$  would produce an output event Y at time  $t_Y < t_X$ , meaning that the output signal for  $t > t_Y$ , depends on an input signal at time  $t_X > t$ . According to the definition, such a model does not preserve causality.

#### 1.5.3 Continuity and combinational devices

A system is continuous if a small change at the inputs produce a small change at the outputs. Mathematically, given a function f(a) and a limit  $a=\lim a_p$  where  $a_p$  describes any convergent sequence of values for a, f(a) is continuous at a if  $\lim f(a_p)=f(a)$  [27]. It is quite simple to verify if continuity is preserved in a logic model. Specifically, the model of the system in Fig. 1.3 is continuous in p, if for a small change in the parameter p, there is a small change in the output.

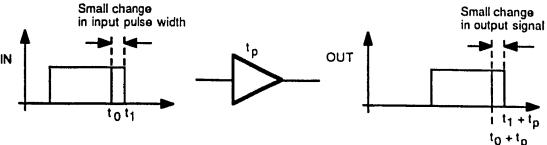

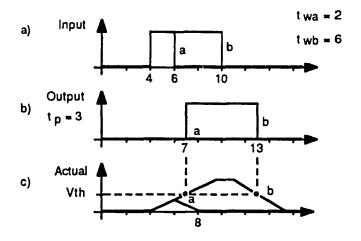

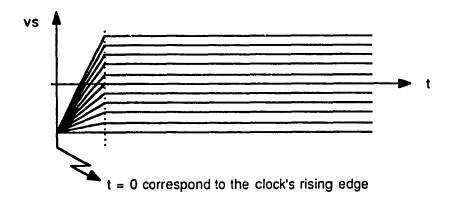

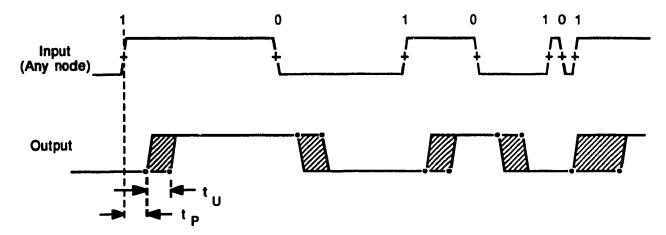

For example, assume the system S is a buffer and its model is a constant propagation delay with a single parameter  $(t_p)$ . Suppose now that a small pulse of width p is applied as the input  $u_p(t)$  and that transitions times are zero. As shown in Fig. 1.4, this delay model preserves continuity since for any small changes in the parameter p (pulse width) there is a small change in the output. In section 1.6, signal representations that do not preserve continuity will be examined.

Fig. 1.4 Preservation of continuity with a constant propagation delay model

#### 1.5.4 Continuity and sequential devices

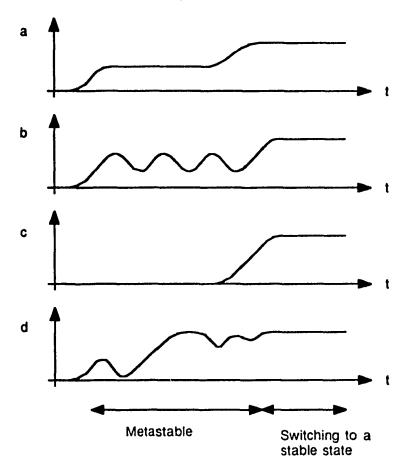

Many logic devices are modeled using logic states (flip-flop, register, random access memory). The binary state of each logic variables depends on some past input condition. For example, at the rising edge of the clock of a D flip-flop, the state variable and the output take the value of the input (0 or 1). Because of the continuous nature of the devices, all intermediate values are possible, perfect binary decision is not possible in continuous systems. The BDT (Binary Decision Theorem) is presented in Appendix A. This is also called the synchronization problem or the metastability problem.

The problem is solved by either allowing sufficient decision time so the probability of having an intermediate value is near zero or else by considering as unacceptable the input conditions that produce intermediate values. This has led to timing constraints like set-up and hold times. Either of these approaches should be used when modeling logic devices with logic state.

#### 1.5.5 Continuity and changes of state

In a continuous system, the state variables are continuous and they change continuously. When modeling a logic device, it is not desirable to keep track of continuously changing state variables. A logic model is characterized by discrete

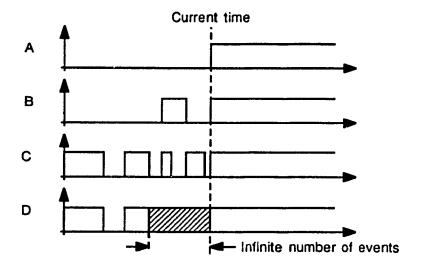

events and changes of state. Discrete changes of state are often referred to as a timed state sequence. In a timed state sequence, there is a finite number of changes of state in any time interval whereas in continuous change of state there is theoretically an infinite number of changes of state in any interval of time.

Modeling the continuous change of state with a timed state sequence effectively transforms continuous time into discrete time. This is a major issue in the modeling of logic devices and the solution is not simple. In simulation, a logic device can effectively be driven by arbitrary input signals that can change an infinite (very large) number of times in any interval. For example, a counter limited to 10 Mhz might be driven by a 100 Mhz clock in a given circuit. This causes a continuous change of state in the modeled device. The problem is to process the theoretically continuous stream of input events and generate a timed state sequence.

This summarizes the key points that must be considered when constructing the logic models for analog circuits.

### 1.6 Problems with current modeling techniques

In this section, the current modeling techniques will be reviewed to illustrate various problems. When possible, a probable cause related to some theoretical aspect of modeling causal, continuous and time invariant systems will be suggested. Problems are grouped into three areas:

- Signal representation problems

- Propagation delay model problems

- Changes of state problems

All of the problems described here are caused by the desire to preserve accuracy in modeling continuous signals and fine timing details using logic simulation. The complexity and the performance of modern digital designs require such accuracy and therefore these problems are quite real.

#### 1.6.1 Signal representation problems

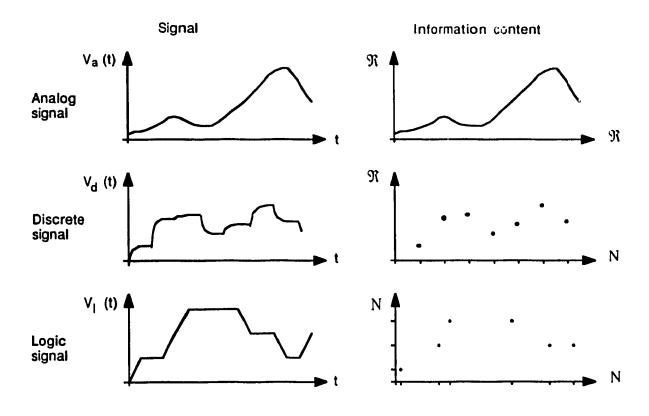

The objective in modeling the signal on a wire is to accurately describe the transmission of the information from one device to another. At analog level, this information is modeled with the node voltages and the branch currents. At logic level, the information is modeled with logic events describing logic signals. Various models for signal representation will be next examined.

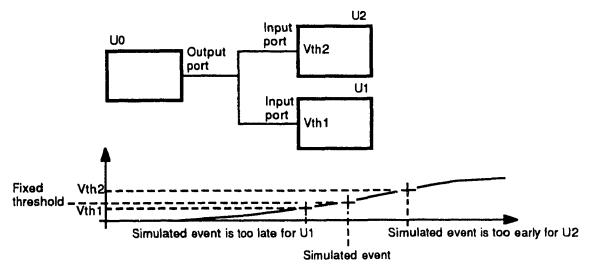

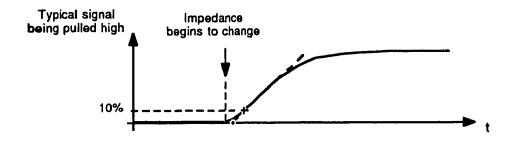

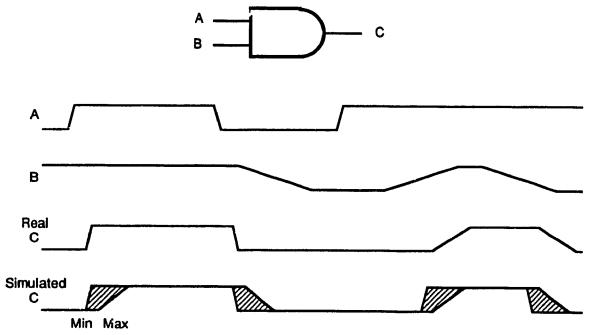

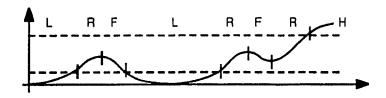

The simplest model consist in a list of logic events describing when the signal changes to zero or one based on the crossing of a fixed common threshold. This model is inadequate for modern designs where wiring capacitances have a non negligible impact on the speed performance. In MOS circuits, the transition times are significant and can not be neglected. As illustrated in Fig. 1.5, such an event definition introduces important timing errors. These errors may cause incorrect changes in the modeled logic state of the receiving circuits and may require negative propagation delays.

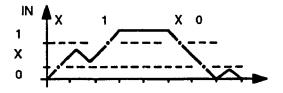

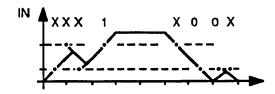

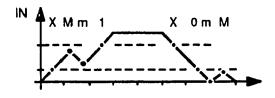

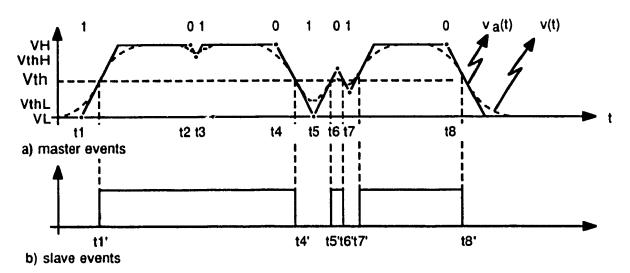

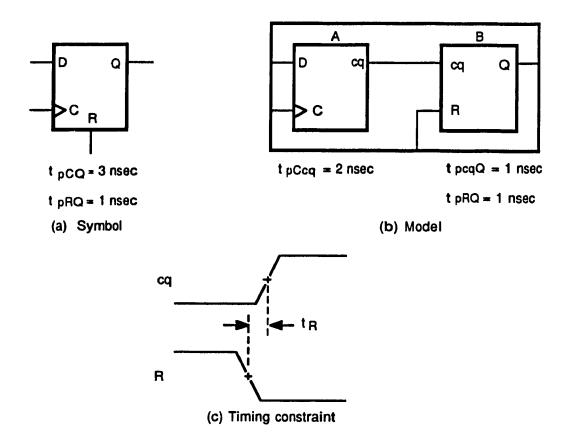

Threshold based logic events do not model the transfer of information accurately because the analog signal is not properly described. Using multiple thresholds is not sufficient either to properly model the analog signal. As shown in

Fig. 1.5 Timing errors with a common fixed threshold for input and output events

Fig. 1.6a, glitches in the X range or in the 0 range are not described by the sequence of threshold based events X1X0. Fictitious events as in Fig. 1.6b have been proposed [30] to simulate the crossing of the threshold for events within either ranges. The processing of such events is difficult since the chronological order is not maintainted. For example, the sequence of events for the signal in Fig. 1.6b is XXX1X00X and should have been XXX1X0X0 [30]. Minima and maxima have also been combined with threshold based events [30] as in Fig. 1.6c. Mixing minima and maxima with threshold based events in such manner is not necessary. In fact minima and maxima are the basis of the new event set proposed in chapter 3.

Each of the problems described above seems to be associated with a poor representation of the signal or some missing information about the signal. To solve

(a) Glitches and threshold based events

(b) Events simulating threshold crossing

(c) Using minimas and maximas

Fig. 1.6 Modeling analog signal with threshold based events

the problem we propose to use the analog signal in a detailed form to transmit the information between logic devices. In chapter 3, a logic event set will be defined to describe analog signals.

# 1.6.2 Propagation delay model problems

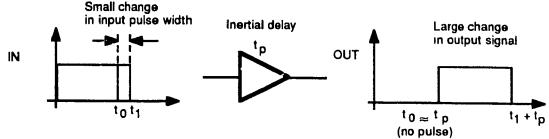

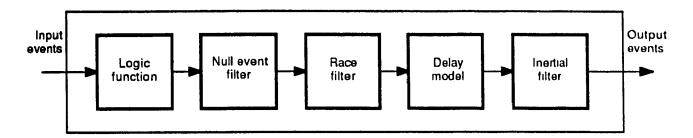

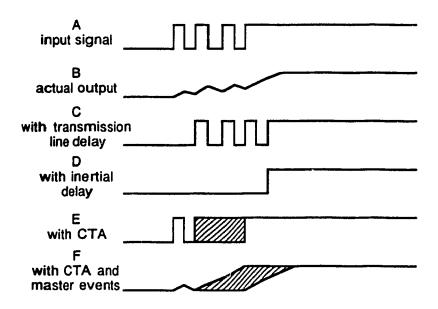

Propagation delays are used in logic simulators to model the passage of time. They are interpreted as the delay between the input events and the resulting output events. When using the constant delay model, the occurrence of an output event is computed by adding a value (tp) to the occurrence of the input event. Unfortunately, real devices rarely behave in a simple fashion. The propagation delay for low to high transitions are different from that for high to low transitions; the propagation delays depend on things such as which input is causing the event, if the receiver device ignores glitches and so on. Therefore, more elaborate delay models have been used and they include inertial delay [29-31, 47-50], transport delay [31, 48, 49] and spike delay [29] models. These models modify the output signal by replacing or removing events to model a specific behavior or to insure logical consistency in the produced signal. For example, a 1 event following another 1 event will be removed. The popular inertial delay model will be used to illustrate this.

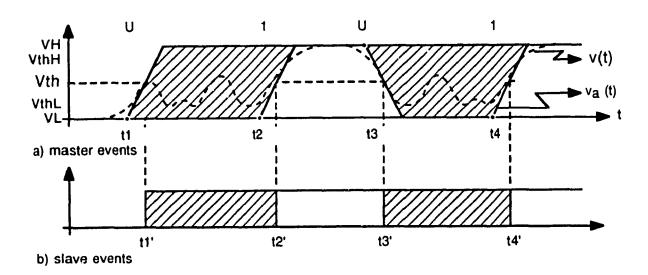

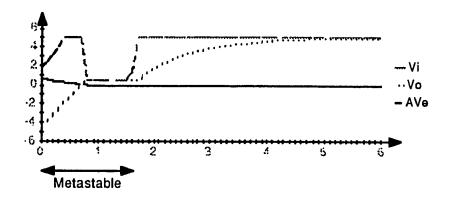

Inertial delays are often used to model the effect of either a large capacitive load or a large internal capacitor that filters out narrow pulses. As illustrated in Fig. 1.7a, pulse 'a' does not produce an output event since its width is smaller than the propagation delay. The problem with inertial delay is related to the transmission of information. Suppose that inertial delay is used to model a large load capacitance. Then the actual output signal might resemble the signal shown in Fig. 1.7c. The pulse a was removed but it could actually be seen by a receiving device with a lower threshold. Such problems have been described in section 1.6.1. In this case, the receiving circuit and not the transmitting circuit should decide on the removal of the

Fig. 1.7 Inertial delay model

event. This is clearly a failure to model the transmission of information between devices.

The fundamental problem is that these delay models are combining three aspects of the behavior that should be separately modeled: transmission of information (signal model), propagation delay and logic state. The modeling of a large wire capacitance is associated with the signal while an internal capacitance would be part of the device logic model. The internal capacitance might produce a pure propagation delay or a logic state. In this thesis we will demonstrate that modeling these aspects separately will improve the model for the transmission of information between logic devices and will result in simpler or at least more consistent logic models.

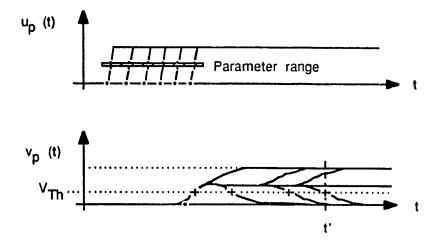

Another aspect that will be considered is the preservation of continuity. Even if it is not obvious how this will improve logic models, we believe that since all logic devices are continuous, it is wise to preserve this property. Unfortunately, inertial propagation delay models do not preserve continuity. This is demonstrated in Fig. 1.8 where a small change in the input pulse width produces a large change in the output waveform. In fact this is not possible in the real world, continuity commands that as

Fig. 1.8 Absence of continuity in the inertial delay model

$t_1 \rightarrow t_0$ , the difference between the output waveforms gets smaller. This model clearly fails to reproduce the correct behavior.

# 1.6.3 Changes of state problems

As discussed in section 1.5.5, a logic model must perform the transformation of continuous changes of state into a timed state sequence. This is accomplished by adding timing constraints, for example, by limiting the clock period of a counter or the width of a reset pulse. These constraints add to the constraints associated with binary decision described in section 1.5.4. In this section, we will analyze how the following modeling techniques have succeeded at doing the continuous time to discrete time transformation:

- device timing constraints

- signal timing constraints

- real time formalism

#### 1.6.3.1 Device timing constraints

The most popular logic modeling technique uses timing constraints such as set-up and hold times to define the acceptable sequences of input events. A typical simulator will compare the simulated event separation with the requirement and output a message in case of violation [29, 31, 48]. The transformation of continuous change of state into a timed state sequence is often not performed. For example, in

many logic models, the state of a flip-flop does not change to undefined in case of a timing violation. In the modified inertial delay model [29], some sort of transformation to a timed sequence of events is performed by replacing many close events by an undefined value.

Use of device timing constraints is basically correct for transforming continuous time into discrete time. The remaining problem is the absence of a systematic mechanism to construct a model that processes timing constraints and at the same time performs the transformation of continuous change of state into a timed state sequence. Since violation of timing constraints affects the state of the device they must be verified as part of the device model and not as an external check on the logic signal.

# 1.6.3.2 Signal timing constraints

In their quest for better logic models, designers have also used multiple thresholds to identify glitches directly on the signal. The signal voltage range is then divided into three (0, 1, X). It was demonstrated in section 1.6.1 that multiple thresholds events do not preserve continuity and do not easily model continuous signals. In addition, events defined using multiple thresholds require a more complex delay model and a more complex logic function and are therefore difficult to process.

For example, multiple thresholds lead to multiple-valued logic [42]. Table 1.1 shows the AND function using 2-valued logic while table 1.2 shows the same function using 6-valued logic. Each entry in table 1.2 is a sequence of three consecutive events based on two threshold dividing the signal range into three values (0, 1 and X).

| AND | 0 | 1 |  |

|-----|---|---|--|

| 0   | 0 | 0 |  |

| 1   | 0 | 1 |  |

Table 1.1 AND function using 2-valued logic

| AND       | (0,0,0) | (1,1,1) | (0,X,1)   | (1,X,0)          | (0, X, 0) | (1,X,1)   |

|-----------|---------|---------|-----------|------------------|-----------|-----------|

| (0,0,0)   | (0,0,0) | (0,0,0) | (0,0,0)   | (0,0,0)          | (0,0,0)   | (0,0,0)   |

| (1,1,1)   | (0,0,0) | (1,1,1) | (0,X,1)   | (1,X,0)          | (0,X,0)   | (1,X,1)   |

| (0, X, 1) | (0,0,0) | (0,X,1) | (0,X,1)   | (0, X, 0)        | (0,X,0)   | (0,X,1)   |

| (1, X, 0) | (0,0,0) | (1,X,0) | (0, X, 0) | (1, <b>X</b> ,0) | (0,X,0)   | (1,X,0)   |

| (0, X, 0) | (0,0,0) | (0,X,0) | (0, X, 0) | (0, X, 0)        | (0, X, 0) | (0, X, 0) |

| (1, X, 1) | (0,0,0) | (1,X,1) | (0,X,1)   | (1,X,0)          | (0, X, 0) | (1,X,1)   |

Table 1.2 AND function using 6-valued logic

Multiple-valued logic can be done for simple gates but then predicting the behavior of complex devices becomes quite complicated and no simple answer has been provided yet. Multiple-valued logic is the result of multiple-thresholds and significantly complicates the processing of events. It will be shown that 2-valued logic is sufficient even to process glitches.

Using multiple thresholds is probably the worst approach; the transformation of the continuous change of state into a timed state sequence is performed on the signal instead of the device state and the logic function gets very complex. Even with single threshold, use of signal timing constraints to identify glitches on the signal is not necessary.

#### 1.6.3.3 Real time systems

Computer scientists have studied the modeling of real time systems which should include logic systems and have attacked the problem in a more formal way. The basic approach consists of including time into first order logic with the objective of proving timing properties such as the safety of a control system. In temporal logic (TL) [53], the operator "eventually ( $\Diamond$ )" has been added to propositional logic to define real time properties. Time constrained version of temporal operator have been used to more accurately describe the system's behavior. For example, in metric interval temporal logic (MITL) [54], the operator  $\Diamond_{\{2,4\}}$  would indicate eventually

between 2 and 4 unit of time. Another approach called timed automata (TA) [55, 56] uses artificial variables called clocks to time the change of state. Whereas all of these techniques aimed at formal proofs, TA is also well suited for simulation, since a mechanism is implicitly used to increment time.

There are two aspects to discrete time abstraction: (1) is the model capable of processing continuous time? and (2) does it perform the transformation into a timed state sequence? TA is capable of processing continuous time and can perform the transformation if the designer does construct a correct automaton. Unfortunately, TA are general purpose and are difficult to use. For example, TA does not distinguish timing constraints from propagation delays. We believe they should be separately modeled and processed.

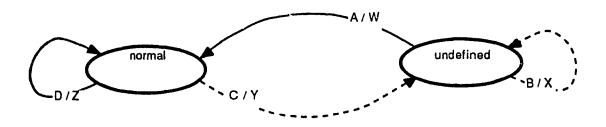

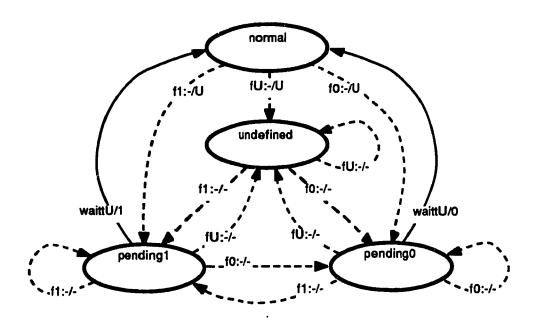

As such, there is no particular problem with TA. They are simply incomplete to deal with the whole modeling problem addressed here because the relation between TA and continuous systems is not clearly formulated. A modified TA will be proposed in chapter 6. The new TA, called Continuous Time Automaton (CTA), is specially designed to process timing constraints and transform continuous time into discrete time.

# 1.7 Proposed logic modeling technique

Basically, the discrete nature of logic signals and devices does not blend easily with the continuous analog world they have to capture. As mentioned by M. R. Lightner [33], important theoretical work is still required to formalize the hypotheses and axioms for the abstraction of analog circuits to logic models. Even if logic simulation with timing specification has been an active area of research [34-39], very little work has been done to define a better formalism [30, 40]. Most researchers are concerned with simulator efficiency (timing accuracy, speed and memory requirements). Our objective is to define such a formalism while maintaining timing

accuracy and simulation efficiency. Such a formalism will improve the accuracy in the signal representation and provide a more realistic delay model and a systematic technique to process timing constraints.

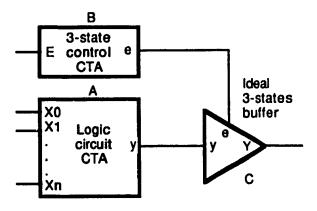

# 1.7.1 Step 1: What is a logic device?

In analog circuit simulation, the elements are described by a set of equations relating the voltages and the currents at the interface ports and the simulation consists of solving the network equations based on Kirchhoff laws. The abstraction of an analog circuit to a logic circuit consists of grouping the analog devices and partitioning the circuit into logic devices and wires. Even though Kirchhoff laws could be used to model part of the logic circuit as in hybrid simulation, it was decided not to use them in the logic model. Each group of analog devices must meet three hypotheses to be considered a logic device. Meeting these hypotheses also insures that Kirchhoff laws are not required. Therefore, a logic device is an analog circuit designed to meet certain criteria. The first hypothesis specifies the type of input port:

Input port hypothesis

Input ports are threshold sensitive or in general sensitive to certain events.

This corresponds to the usual assumption made by digital system designers.

A logic device will react only when a threshold is crossed. The effect might be a change of state or a change on the output signals. The second hypothesis specifies the type of output port:

# Output signal hypothesis

Output ports generate signals that do not normally linger around the threshold voltages of the input ports or in general that produce events compatibles with the input ports

The thresholds are simply crossed, otherwise, the signal is not considered an acceptable logic signal. Even if this might seem fuzzy for now, this hypothesis enforces the device hypothesis by further limiting the class of analog circuits that are considered logic devices. In general, these two hypotheses indicate that, for logic circuits to operate as specified, the output signals must be compatible with the thresholds of the input ports connected to it. In simpler term, since the logic devices are sensitive to threshold, the output signals must neatly traverse the thresholds. The third hypothesis specifies how output ports are connected to input ports:

# Network hypothesis

A wire always consists of a unique output port driving one or more input ports forming a time invariant load.

The output port might change with time.

This is the basic hypothesis that allows a designer to model a device without using Kirchhoff laws. This is restrictive, but it actually corresponds to the engineering practice. For example, devices specified in data books [43, 44] including standard cells for integrated circuit design [45] are all described assuming the network hypothesis. According to this hypothesis tristate devices are logic devices, but open collector devices and switches are not. Bus resolution function  $\rho$  (ed by VHDL [31] would be limited to tristate busses and signals. Obviously, our ective

is not to decide what can or can not be simulated. We merely describe what is theoretically considered a logic circuit.

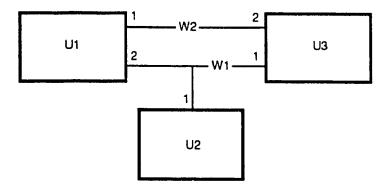

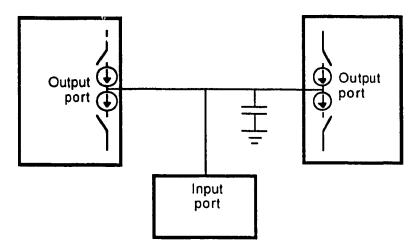

These hypotheses make no reference to the signal representation. In fact, logic devices also process analog signals. As shown in Fig. 1.9, an analog simulator uses differential equations for the devices to compute the analog signals. A hybrid simulator uses logic models for the internal operation of the device and differential equations for the interface part of the devices to compute the analog signals. A logic simulator uses a logic model for the devices and also computes the analog signal. In section 1.6.1, we have demonstrated that trying to define logic signals without

(c) Logic devices and analog signals (logic simulation)

Fig. 1.9 Classification of simulators

reference to analog signals leads to problems in the simulation. Allowing logic models to process analog signals is a key point in our approach and it will lead to logic events describing analog signals.

# 1.7.2 Step 2: What is a logic model?

The next step is to define a logic model for the logic device defined in step 1. The difference between an analog model and a logic model lies in the representation and the processing of the time and of the state changes. In an analog model, the time and the state changes are continuous whereas in logic models, they are assumed discrete.

During an analog simulation, multiple input events or waveforms are processed simultaneously, the time progresses continuously and the output events or waveforms are generated simultaneously. During a logic simulation, multiple input events are processed sequentially. State changes and output events are computed and predicted separately for each input event. Intuitively, a logic simulator processes the input signals as follow:

- The input events are derived from the analog input signals using the input event set definition.

- For each input event, the simulator waits some time corresponding to the input delay.

- Then the simulator processes each input event and produces a change of state if required. In general, a single input event may produce a sequence of state changes.

- Based on the input event and the new state, output events are generated after some time corresponding to the output delay.

In the general case, input and output delays are arbitrary, therefore the chronological order of the predicted state changes and output events might not be

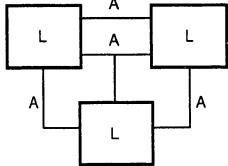

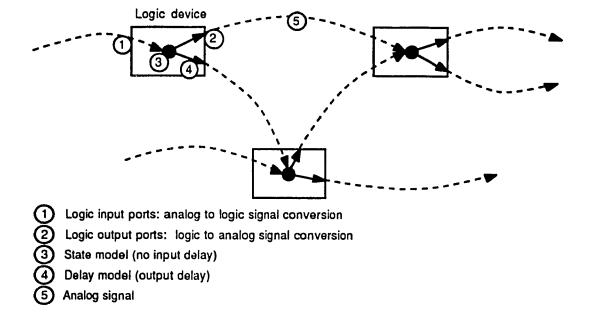

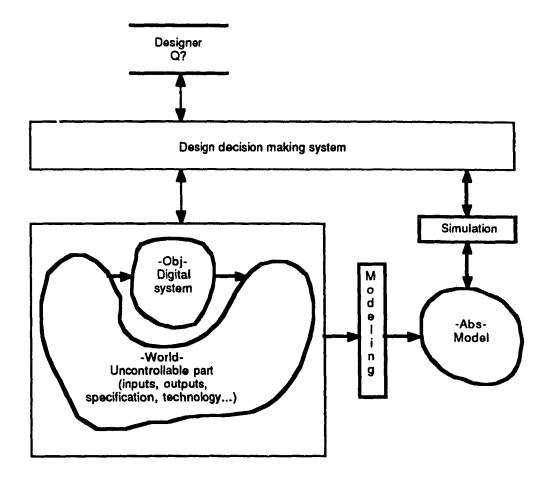

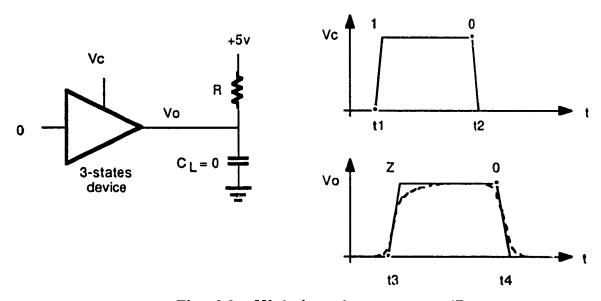

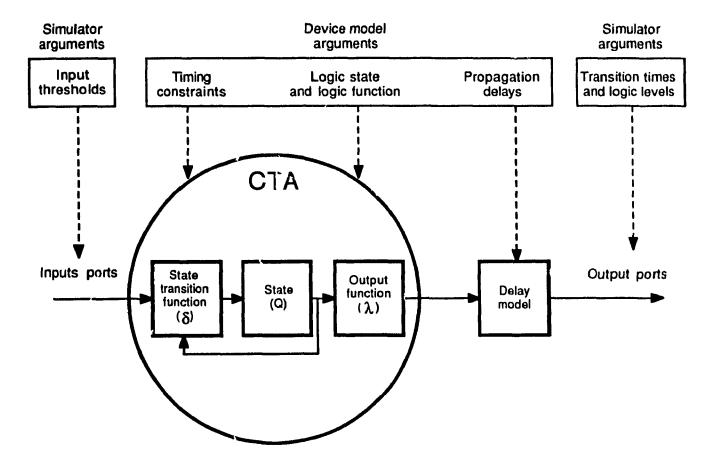

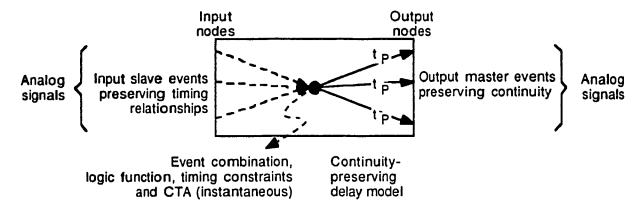

preserved and might become difficult to process. For example, assume a device X with a state S and two input ports A and B. If the input delay on port A is smaller than the input delay on port B, then the change of state S<sub>A</sub> might occur before the change of state S<sub>B</sub> even if the event on A occurs after that on B. With complex devices, not preserving the chronological order in the changes of state might be difficult to model. To simplify the construction of logic models, the analog circuits will be partitioned such that the input and output delays are grouped and associated with each output. As shown in Fig. 1.10, the input delays are reduced to zero and the delays are inserted at the output.

The conceptual model of Fig. 1.10 is based on two rules. The first rule indicates that the input delay is zero:

#### State model rule

In a logic model the change of state is simultaneous with the input event causing it.

Fig. 1.10 Conceptual model of a logic device

This rule insures that the chronological order of the changes of state is preserved with respect to the input sequence of events. This rule also indicates that delays must be associated with outputs. The second rule concerns the delay model:

#### Delay model rule

The propagation delay model for each output must preserve continuity

This is required to prevent problems such as those described in section 1.6.2. According to these rules, a logic circuit consists of logic devices connected as in Fig. 1.11. This conceptual model for logic circuits suggests how simulation will proceed. First, input events are computed using the analog signal and the input threshold. Second, the logic model is used and a change of state is computed. Then, if required, a continuity preserving delay model is used to compute the output events.

Fig. 1.11 Partitioning an analog circuit into logic devices

The output events which are defined differently from the input events, are then used to reconstruct the analog signal.

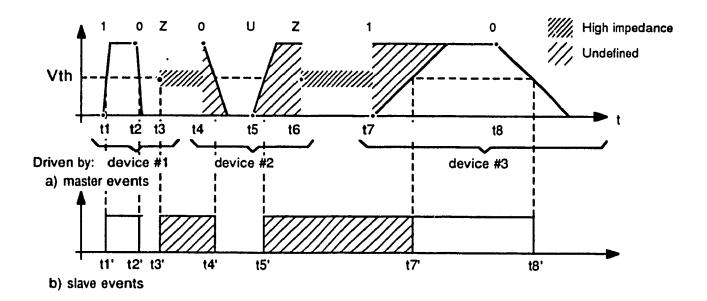

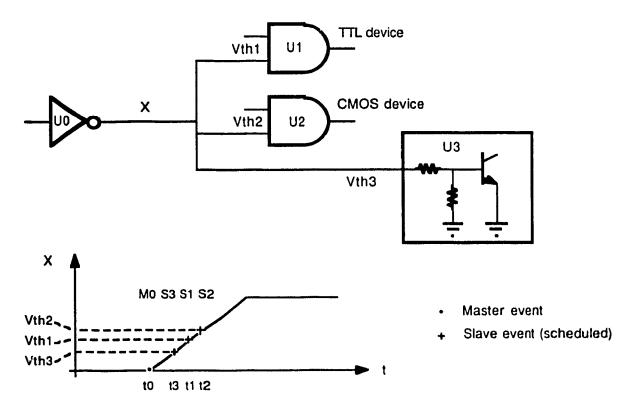

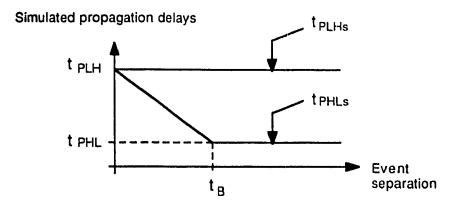

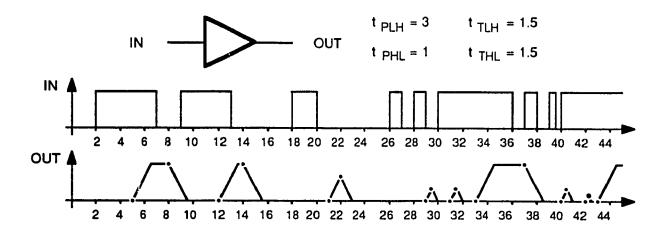

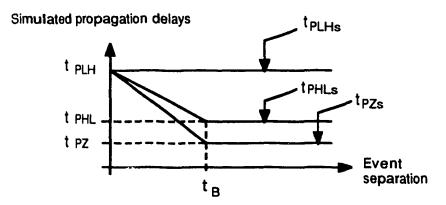

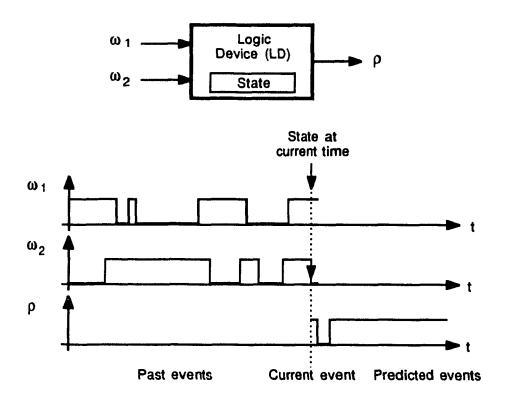

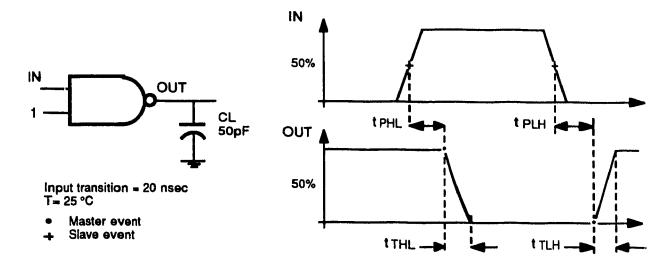

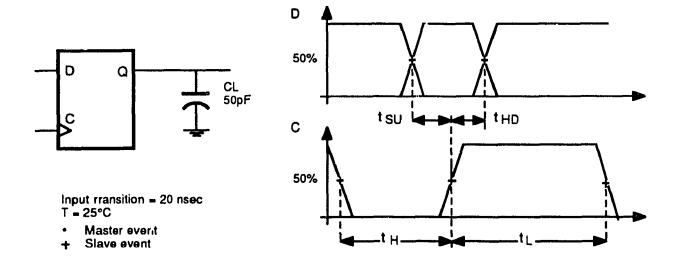

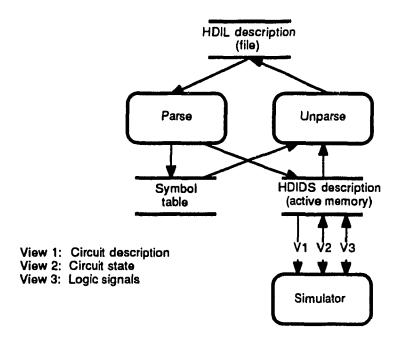

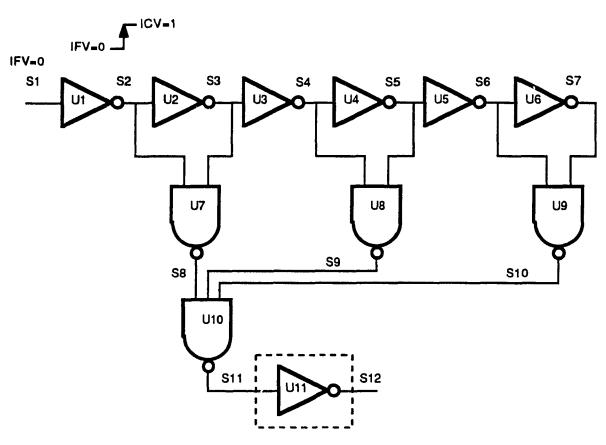

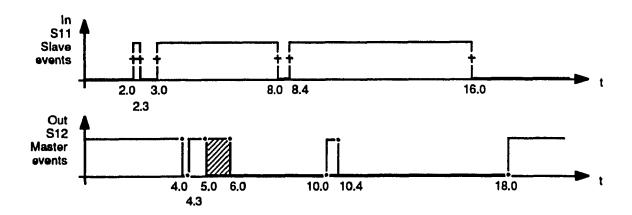

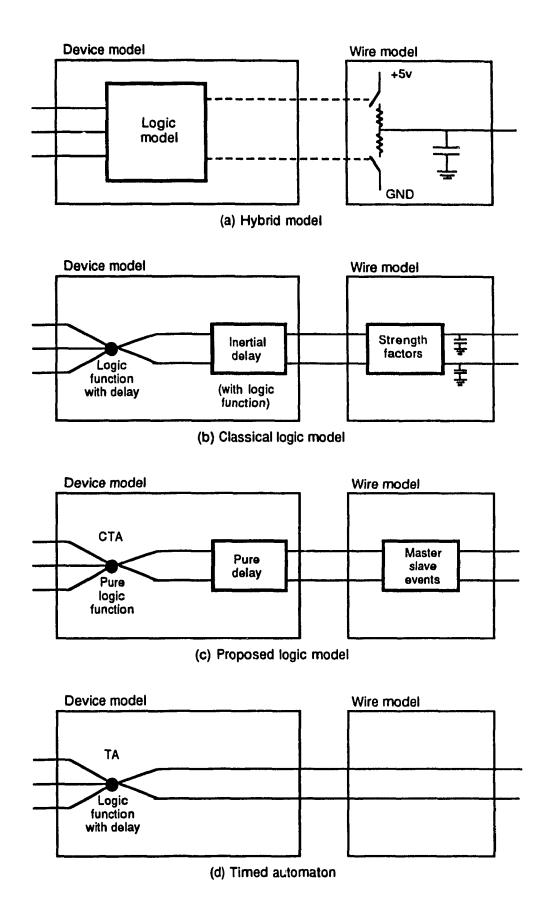

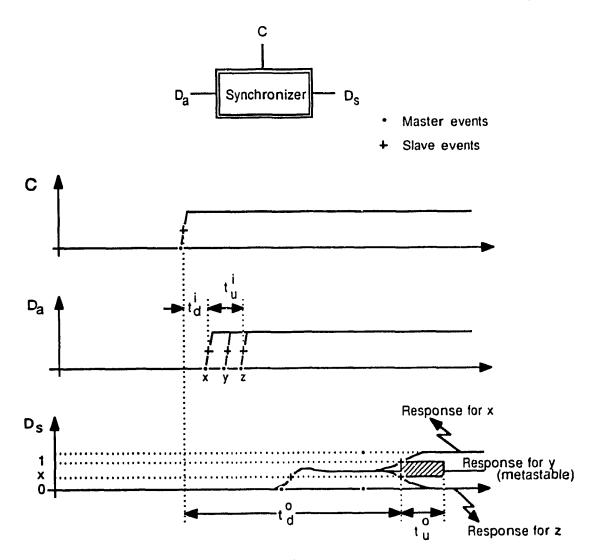

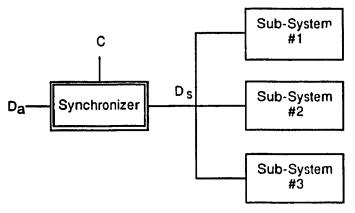

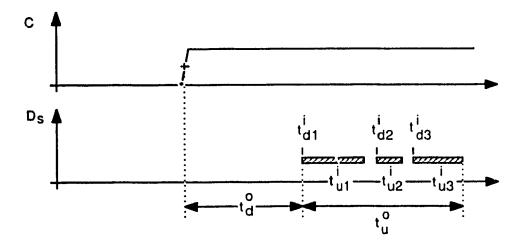

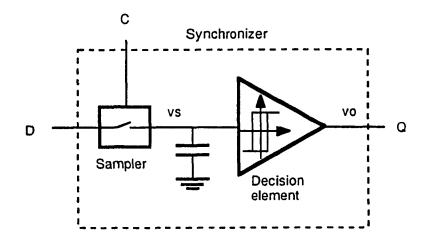

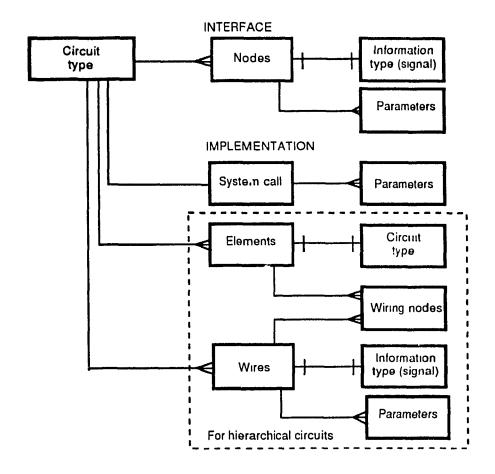

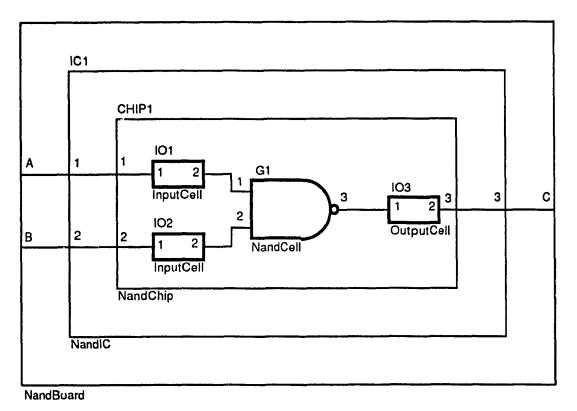

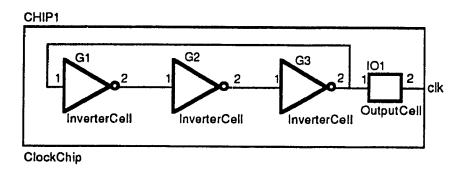

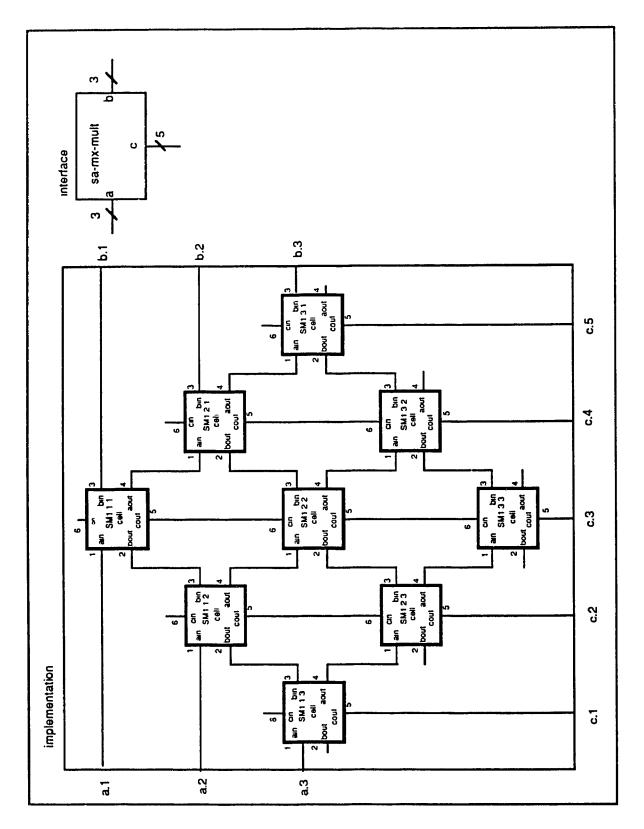

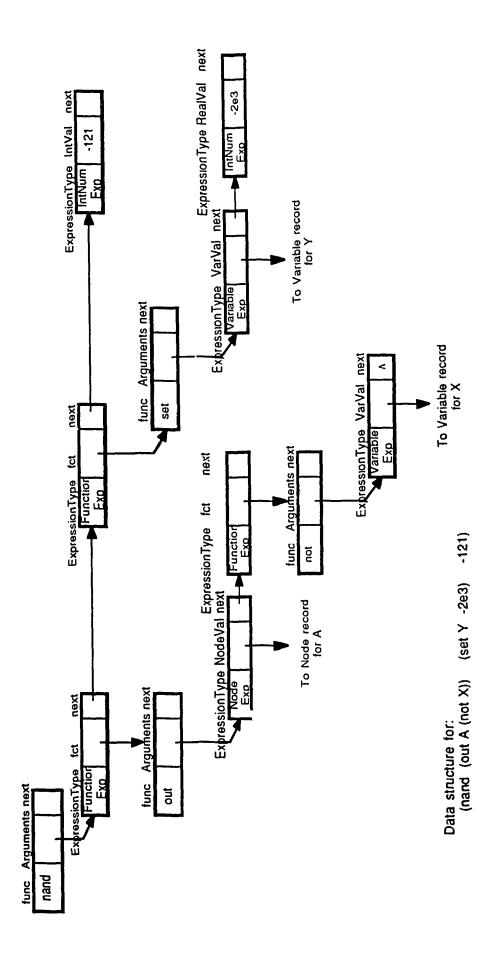

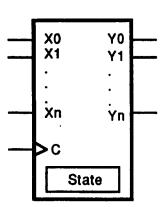

# 1.7.3 Outline of step 3: Construction of logic models