National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N<sup>A</sup>

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylogra phiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c C-30, et ses amendements subséquents

# A MODIFIED PULSEWIDTH MODULATED CURRENT SOURCE INVERTER

# **GERASIMOS MOSCHOPOULOS**

**A** Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements

for the Degree of Master of Applied Science at

Concordia University

Montreal, Quebec, Canada

December 1991

© GERASIMOS MOSCHPOULOS, 1991

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

> The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

> The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées

L'auteur conserve la propnété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-73682-8

#### ABSTRACT

# A MODIFIED PULSEWIDTH MODULATED CURRENT SOURCE INVERTER

#### **GERASIMOS MOSCHOPOULOS**

Current source inverters (CSIs) have several features that make them attractive in induction motor drives; however, they are not as widely used as voltage source inverters (VSIs) because of the drawbacks they have. These drawbacks include the appearance of overvoltage spikes on the inverter output voltage and the restriction of pulsewidth modulation techniques (PWM) that can be implemented. To overcome these drawbacks, it has been proposed to add additional components to the basic power circuit configuration; however, these modified topologies use a substantial number of additional components (thus increasing cost and complexity). Another proposed solution is to provide a short circuit path for the inductor current through the inverter itself but this results in the rise of the dc link current.

In this thesis, a modified pulsewidth modulated (PWM) CSI topology is proposed. This topology allows any PWM technique to be implemented no matter how low the modulation index or the fundamental frequency is, improves the dynamic response of the CSI, and allows the inverter output voltage spikes to be suppressed without the disadvantages of other previously proposed solutions. These benefits are obtained at the cost of only one additional switch connected in the de link and some additional input filtering. The operating principles of the proposed CSI are discussed and its characteristics under steady-state conditions are examined. The feasibility of the proposed converter is demonstrated with simulated results, and with experimental results obtained from a 5 kVA prototype unit.

#### **ACKNOWLEDGEMENTS**

I wish to express my gratiude to Dr. Geza Joos and to Dr. Phoivos D. Ziogas for their support and guidance throughout all stages of this study.

I wish to acknowledge the financial support provided by the National Science and Engineering Council of Canada (NSERC) and the Government of Quebec through FCAR grants.

I would like to thank Mr. Joseph Woods and Mr. Donato Vincenti for helping me with the experimental set-up and for being generous with their time and expertise.

Finally, I would like to thank my colleagues in the Power Electronics Lab at Concordia for helping to make my experience in the graduate program at Concordia a pleasant one.

#### **ACKNOWLEDGEMENTS**

I wish to express my gratiude to Dr. Geza Joos and to Dr. Phoivos D. Ziogas for their support and guidance throughout all stages of this study.

I wish to acknowledge the financial support provided by the National Science and Engineering Council of Canada (NSERC) and the Government of Quebec through FCAR grants. Financial support was also provided by the J. W. McConnell Fellowship given by Concordia University.

I would like to thank Mr. Joseph Woods and Mr. Donato Vincenti for helping me with the experimental set-up and for being very generous with their time and expertise.

Finally, I would like to thank my colleagues in the Power Electronics Lab at Concordia for helping to make my experience in the graduate program at Concordia more pleasant than it might have been.

## TABLE OF CONTENTS

|     |                                                                                 | Page |

|-----|---------------------------------------------------------------------------------|------|

| СНА | PTER 1. INTRODUCTION                                                            |      |

|     |                                                                                 | 1    |

| 1.1 | Introduction.                                                                   | 1    |

| 1.2 | Voltage source inverter                                                         | 2    |

| 1.3 | Current source inverter.                                                        | 2    |

| 1.4 | Voltage source inverter vs current source inverter.                             | 4    |

| 1.5 | Literature review.                                                              | 7    |

| 1.6 | Scope and contributions.                                                        | 10   |

| 1.7 | Summary of the thesis.                                                          | 11   |

| СНА | PTER 2. PULSEWIDTH MODULATION TECHNIQUES AND PATTE FOR CURRENT SOURCE INVERTERS | RNS  |

| 2.1 | Introduction.                                                                   | 13   |

| 2.2 | General rules for CSI patterns.                                                 | 13   |

| 2.3 | The autosequentially commutated inverter in the six-step mode                   |      |

|     | of operation.                                                                   | 14   |

| 2.4 | PWM techniques.                                                                 | 17   |

|     | 2.4.1 Introduction.                                                             | 17   |

|     | 2.4.2 Selective harmonic elimination.                                           | 18   |

|     | 2.4.3 Trapezoidal PWM.                                                          | 24   |

| 2.5 | Dc bus short-circuiting.                                                        | 26   |

|     | 2.5.1 Harmonic elimination.                                                     | 26   |

|     | 2.5.2 Amplitude control.                                                        | 29   |

| 2.6 | Selective harmonic elimination with PWM in the center 60° region.               | 31   |

| 2.7 | Sinusoidal PWM and its variations.                                              | 34   |

| 2.8 | Operation of CSI with an auxiliary switch.                                      | 38   |

| 2.9 | Conclusion.                                                                     | 40   |

# CHAPTER 3. PULSEWIDTH MODULATED CURRENT SOURCE INVERTER OPERATING CHARACTERISTICS

| 3.1 | Intro                                                   | Introduction.                                                           |    |  |

|-----|---------------------------------------------------------|-------------------------------------------------------------------------|----|--|

| 3.2 | Stead                                                   | y-state inverter relationships.                                         | 43 |  |

| 3.3 | CSI d                                                   | CSI dynamic response.                                                   |    |  |

| 3.4 | Inverter output overvoltage spikes.                     |                                                                         |    |  |

| 3.5 | Boost effect due to the short-circuiting of the dc bus. |                                                                         |    |  |

| 3.6 | Modifications based on short-circuiting considerations. |                                                                         |    |  |

| 3.7 | Conclusion.                                             |                                                                         |    |  |

| CHA | APTER 4                                                 | DC BUS & OUTPUT CHARACTERISTICS OF THE MODIFIED CURRENT SOURCE INVERTER |    |  |

| 4.1 | Intro                                                   | duction.                                                                | 60 |  |

| 4.2 | Princ                                                   | Principles of operation.                                                |    |  |

| 4.3 | Adva                                                    | ntages of the modified current source inverter.                         | 69 |  |

| 4.4 | Equa                                                    | Equations for steady-state operation and design guidelines.             |    |  |

|     | 4.4.1                                                   | Equations for steady-state operation.                                   | 70 |  |

|     | 4.4.2                                                   | Design of the output filter capacitor.                                  | 76 |  |

|     | 4.4.3.                                                  | Inverter system switch ratings.                                         | 78 |  |

|     | 4.4.4                                                   | Steady-state operation - design example.                                | 79 |  |

| 4.5 | Simulate                                                | ed and experimental results.                                            | 83 |  |

|     | 4.5.1                                                   | Motoring conditions.                                                    | 83 |  |

|     | 4.5.2                                                   | Regenerative conditions.                                                | 93 |  |

|     | 4.5.3                                                   | Transient conditions.                                                   | 95 |  |

| 4.6 | Conclus                                                 | ion.                                                                    | 97 |  |

# CHAPTER 5. THE INPUT CHARACTERISTICS OF THE MODIFIED CURRENT SOURCE INVERTER

| 5.1  | Introduction.                |              |                              | 98         |

|------|------------------------------|--------------|------------------------------|------------|

| 5.2  | The i                        | nput ac line | e currents.                  | 98         |

| 5.3  | <i>b</i> 1 ( )               |              |                              | 103<br>106 |

| 5.4  |                              |              |                              |            |

| 5.5  | Efficiency considerations.   |              | lerations.                   | 109        |

| 5.6  | Component design procedures. |              | 113                          |            |

|      | 5.6.1                        | Design of    | the dc link inductor.        | 113        |

|      | 5.6.2                        | Input filte  | er considerations.           | 115        |

|      |                              | 5.6.2.1      | Theoretical considerations.  | 115        |

|      |                              | 5.6.2.2      | Input filter design example. | 117        |

| 5.7  | Expe                         | rimental res | sults.                       | 118        |

| 5.8  | Concl                        | lusion.      |                              | 123        |

| СНА  | PTER                         | 6. CONCL     | LUSION                       |            |

| 6.1  | Sumn                         | nary of the  | thesis.                      | 124        |

| 6.2  | Concl                        | usions.      |                              | 125        |

| 6.3  | Sugge                        | stions for f | uture work.                  | 127        |

| REF  | ERENC                        | ES           |                              | 128        |

| APPI | ENDIX                        |              |                              | 133        |

# - viii -

# LIST OF FIGURES

|            |                                                             | Page |

|------------|-------------------------------------------------------------|------|

| Fig. 1.1:  | Voltage source inverter.                                    | 3    |

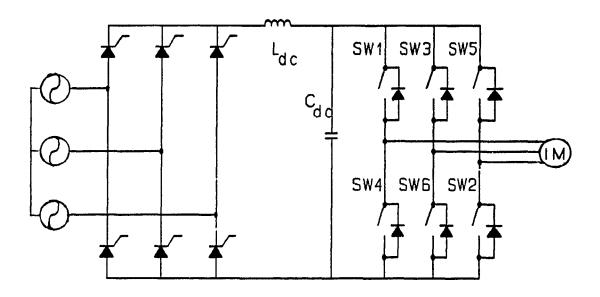

| Fig. 1.2:  | The autosequentially commutated inverter (ASCI).            | 5    |

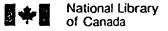

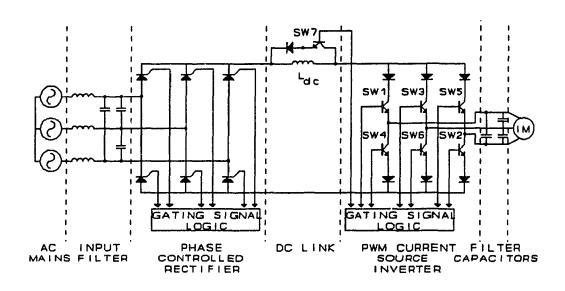

| Fig. 1.3:  | The PWM current source inverter.                            | 5    |

| Fig. 2.1:  | ASCI output line currents.                                  | 15   |

| Fig. 2.2:  | PWM output line current showing unwanted pulse problem.     | 19   |

| Fig. 2.3:  | A typical selective harmonic elimination pattern.           | 21   |

| Fig. 2.4:  | Trapezoidal PWM waveforms.                                  | 25   |

| Fig. 2.5:  | Sinusoidal PWM waveforms.                                   | 28   |

| Fig. 2.6:  | Notch control firing sequence and output line currents.     | 30   |

| Fig. 2.7:  |                                                             |      |

|            | cycle.                                                      | 32   |

| Fig. 2.8:  | PWM pattern for variable modulation index control.          | 32   |

| Fig. 2.9:  | Modified SPWM waveforms.                                    | 36   |

| Fig. 2.10: | Third harmonic injection SPWM waveforms                     | 37   |

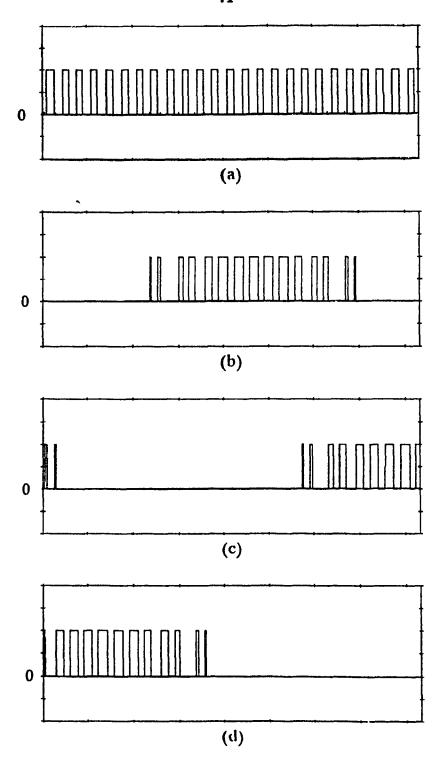

| Fig. 2.11: | Derivation of inverter switch gating signals when auxiliary |      |

|            | switch is present in dc link.                               | 39   |

| Fig. 2.12: | Typical gating signals for auxiliary switch and inverter    |      |

|            | switches.                                                   | 41   |

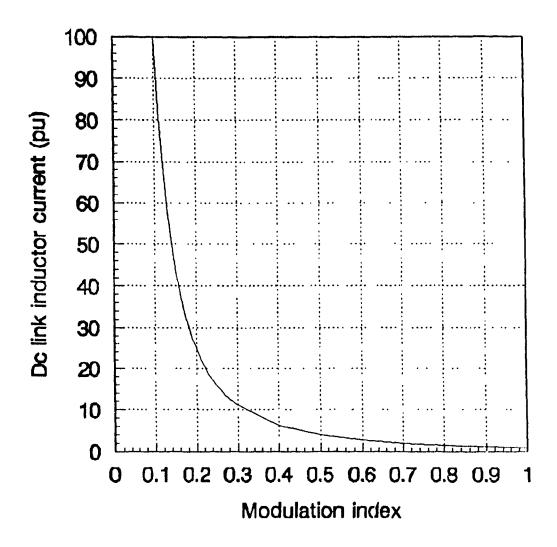

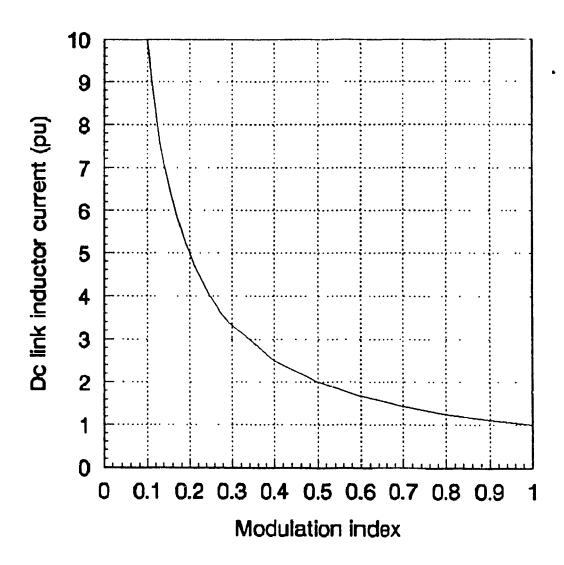

| Fig. 3.1:  | De link inductor current vs. modulation index for the       |      |

|            | conventional PWM CSI.                                       | 46   |

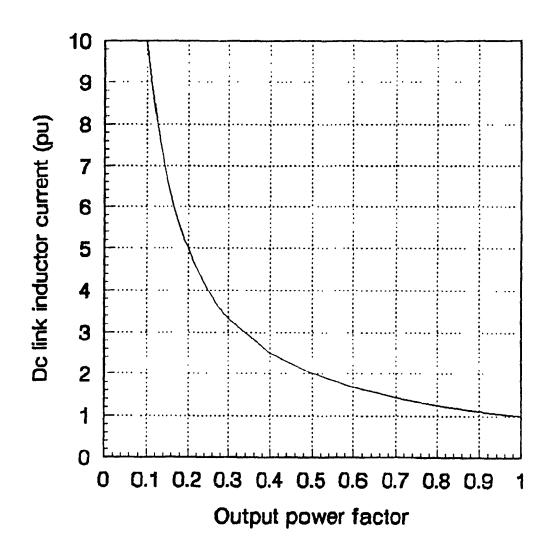

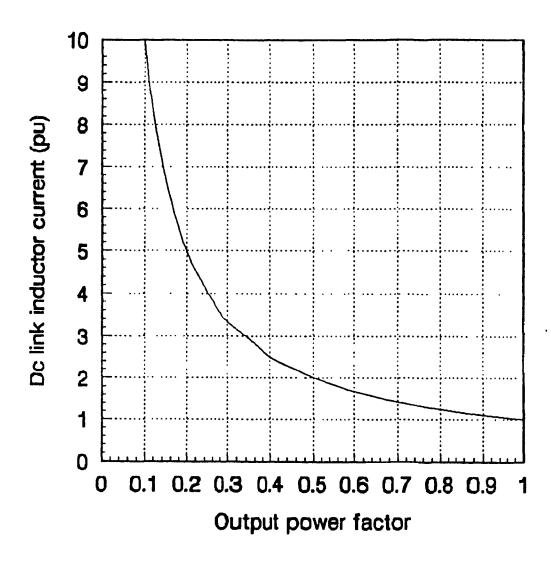

| Fig. 3.2:  | De link inductor current vs. output power factor for the    |      |

|            | conventional PWM CSI.                                       | 47   |

| Fig. 3.3:  | Equivalent circuits depicting overvoltage situations.       | 50   |

| Fig. 3.4:  | The modified PWM CSI topology proposed by Nonaka and        |      |

|            | Neba.                                                       | 55   |

| Fig. 3.5:  | Typical gating signals for the topology of Fig. 3.4.        | 57   |

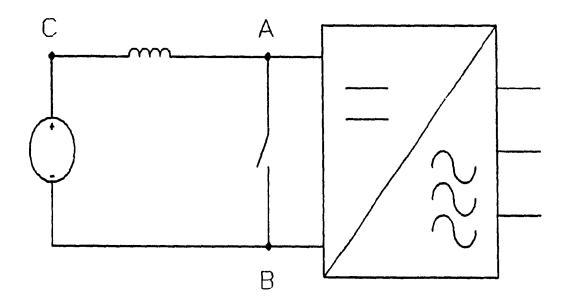

| Fig. 3.6:  | Equivalent de bus circuit.                                  | 58   |

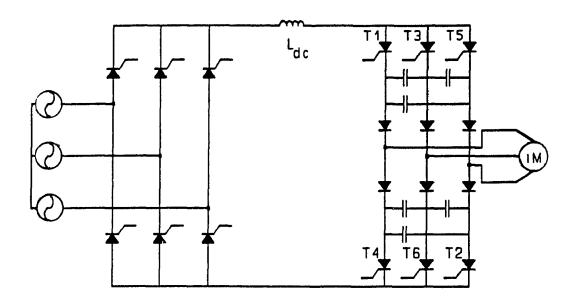

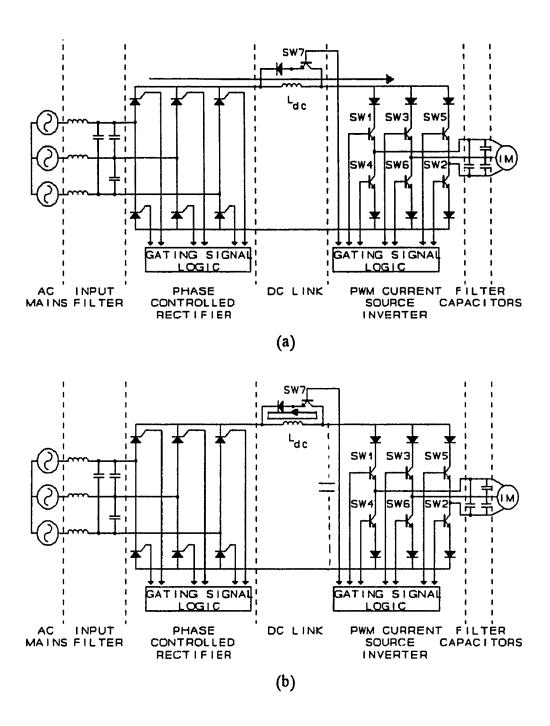

| Fig. 4.1:  | Modified current source inverter (MCSI) topology.           | 61   |

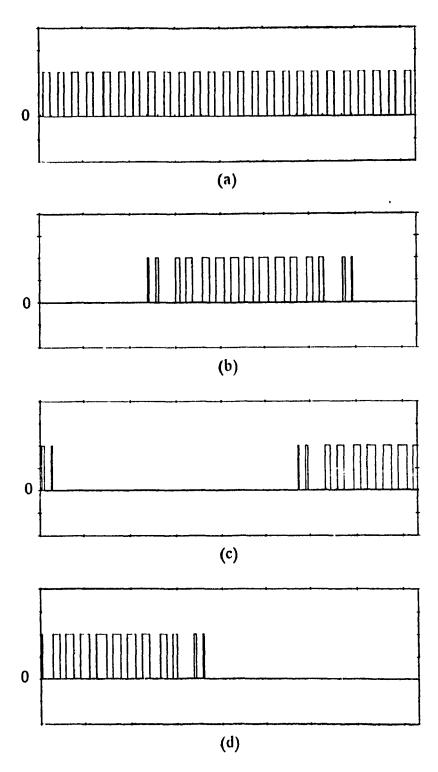

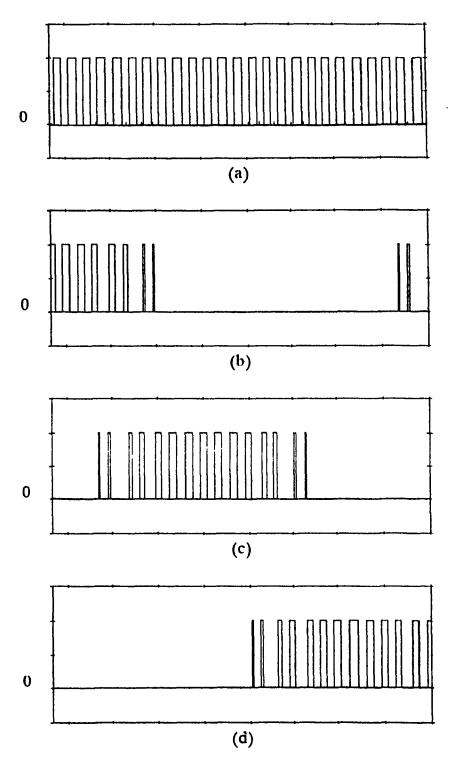

| Fig. 4.2:  | Gating signals for the auxiliary switch and the top three           |            |

|------------|---------------------------------------------------------------------|------------|

|            | inverter switches for a pattern with $M = 0.8$                      | 63         |

| Fig. 4.3:  | Gating signals for the auxiliary switch and the top three           |            |

|            | inverter switches for a pattern with $M = 0.4$                      | 64         |

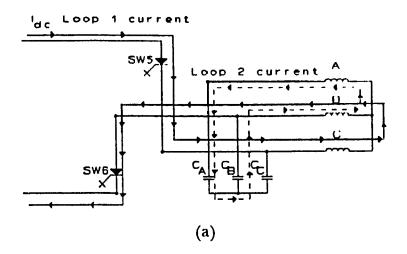

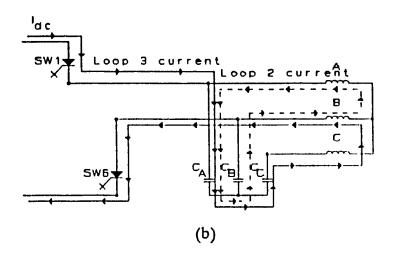

| Fig. 4.4:  | MCSI modes of operation.                                            | 66         |

| Fig. 4.5:  | MCSI dc bus characteristics.                                        | 67         |

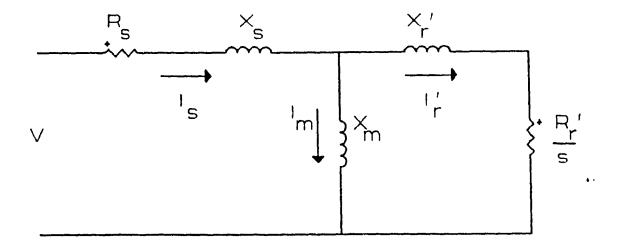

| Fig. 4.6:  | Per phase equivalent circuit of an induction mours.                 | 72         |

| Fig. 4.7:  | MCSI line diagram.                                                  | 72         |

| Fig. 4.8:  | De link inductor current vs. modulation index for the MCSI.         | 75         |

| Fig. 4.9:  | De link inductor current vs. output power factor for the            |            |

|            | MCSI.                                                               | <b>7</b> 7 |

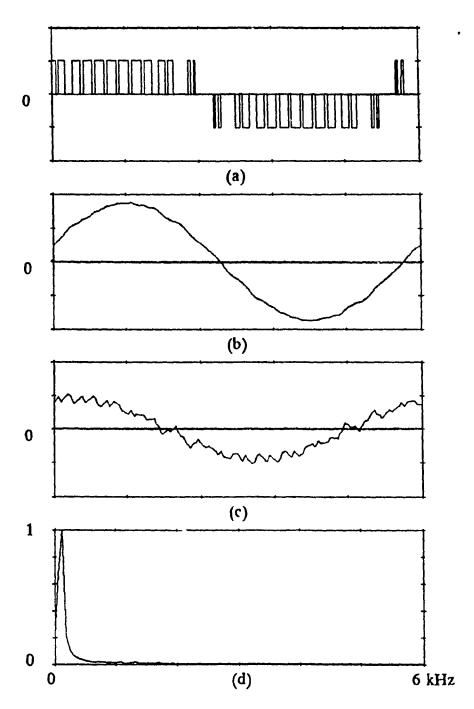

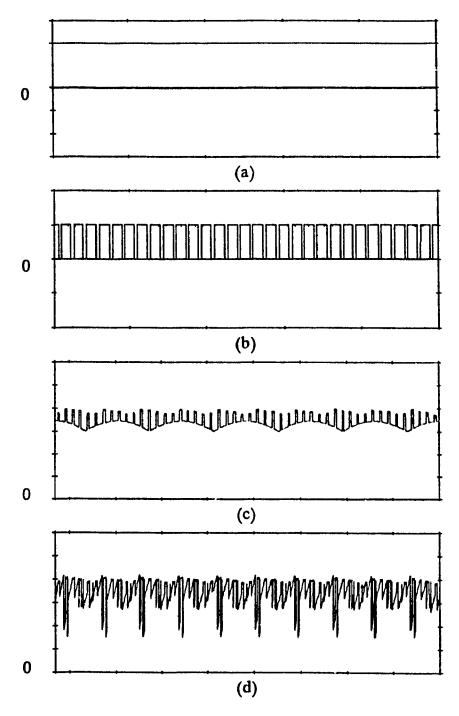

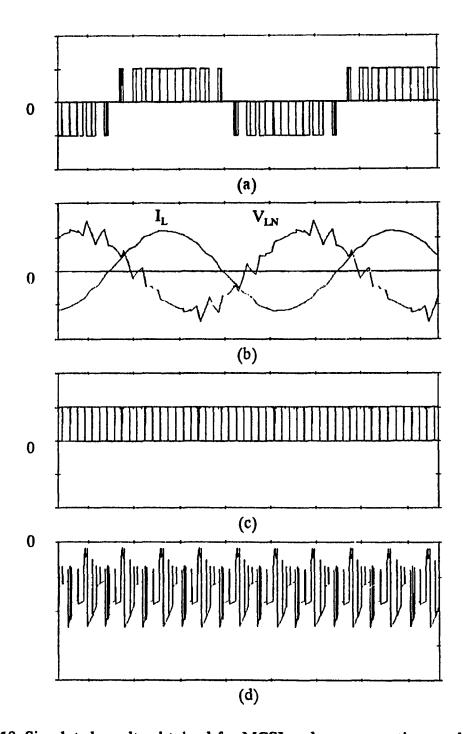

| Fig. 4.10: | Simulated output results for $M = 0.8$ , $f_o = 100$ Hz and load    |            |

|            | $R = 11 \Omega, L = 7 mH, C = 10 \mu F.$                            | 85         |

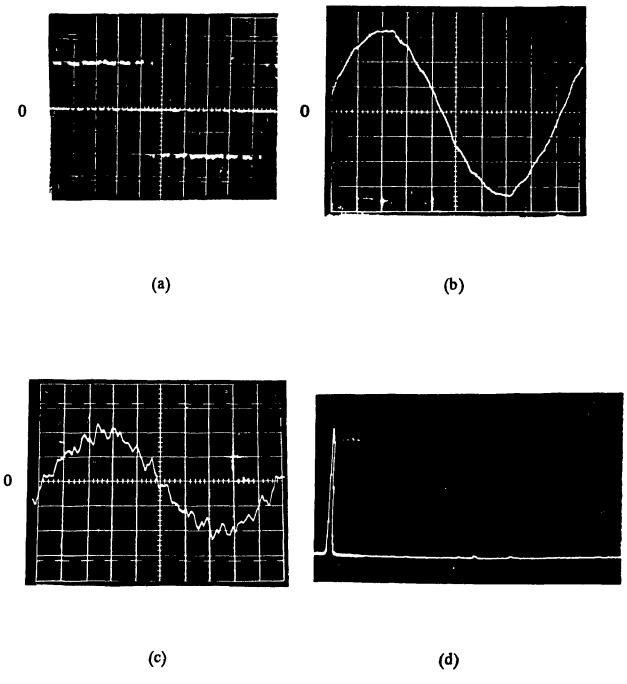

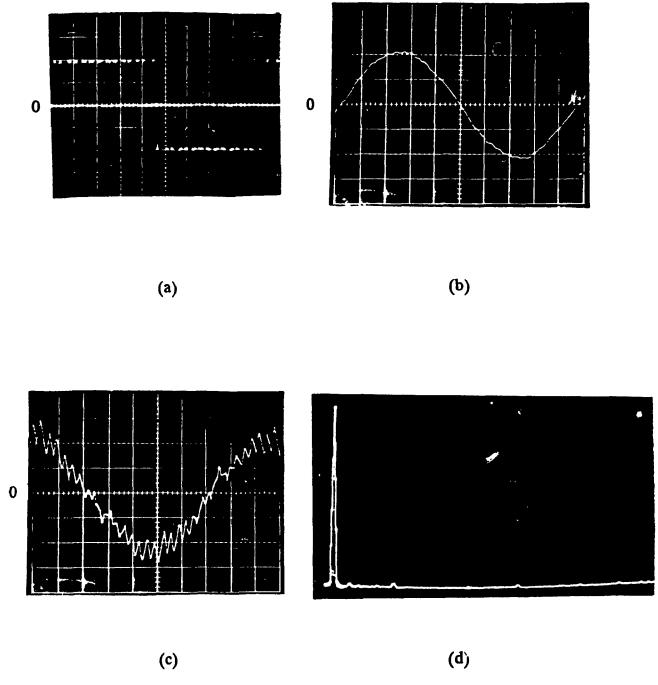

| Fig. 4.11: | Experimental output results for $M = 0.8$ , $f_o = 100$ Hz and load | d          |

|            | $R = 11 \Omega, L = 7 mH, C = 10 \mu F.$                            | 86         |

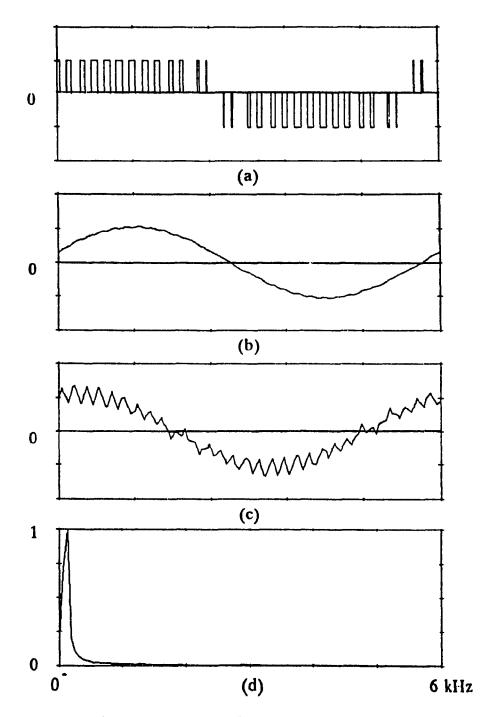

| Fig. 4.12: | Simulated output results for $M = 0.5$ , $f_o = 100$ Hz and load    |            |

|            | $R = 11 \Omega, L = 7 mH, C = 10 \mu F.$                            | 87         |

| Fig. 4.13: | Experimental output results for $M = 0.8$ , $f_o = 100$ Hz and load | d          |

|            | $R = 11 \Omega, L = 7 mH, C = 10 \mu F.$                            | 88         |

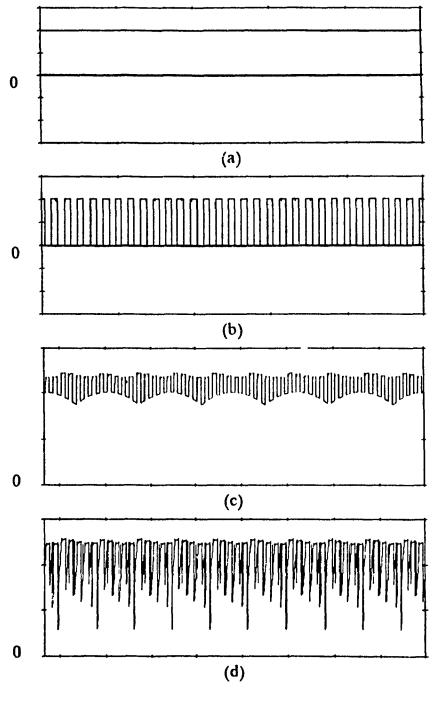

| Fig. 4.14: | Simulated dc bus results for $M = 0.8$ , $f_o = 100$ Hz and load    |            |

|            | $R = 11 \Omega, L = 7 mH, C = 10 \mu F.$                            | 89         |

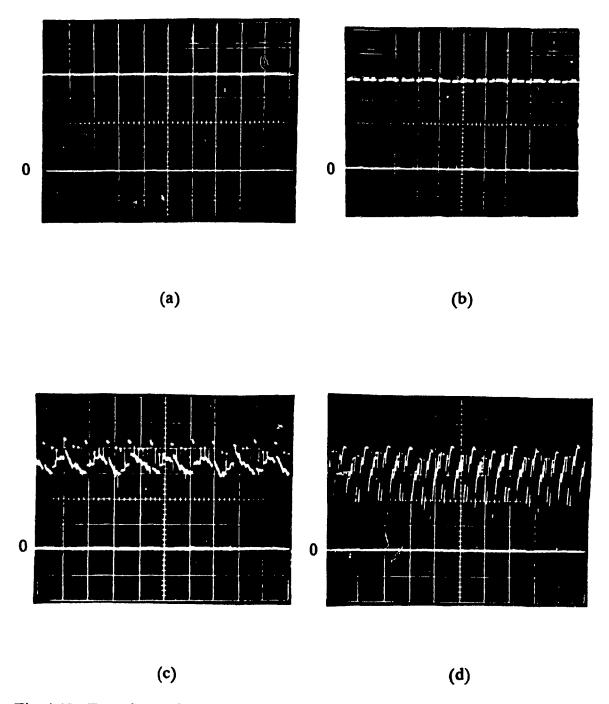

| Fig. 4.15: | Experimental dc bus results for $M = 0.8$ , $f_o = 100$ Hz and load | Ė          |

|            | $R = 11 \Omega, L = 7 mH, C = 10 \mu F.$                            | 90         |

| Fig. 4.16: | Simulated dc bus results for $M = 0.5$ , $f_o = 100$ Hz and load    |            |

|            | $R = 11 \Omega, L = 7 mH, C = 10 \mu F.$                            | 91         |

| Fig. 4.17: | Experimental dc bus results for $M = 0.5$ , $f_o = 100$ Hz and load | đ          |

|            | $R = 11 \Omega, L = 7 mH, C = 10 \mu F.$                            | 92         |

| Fig. 4.18: | Simulated results for the MCSI operating under                      |            |

|            | regenerative conditions.                                            | 94         |

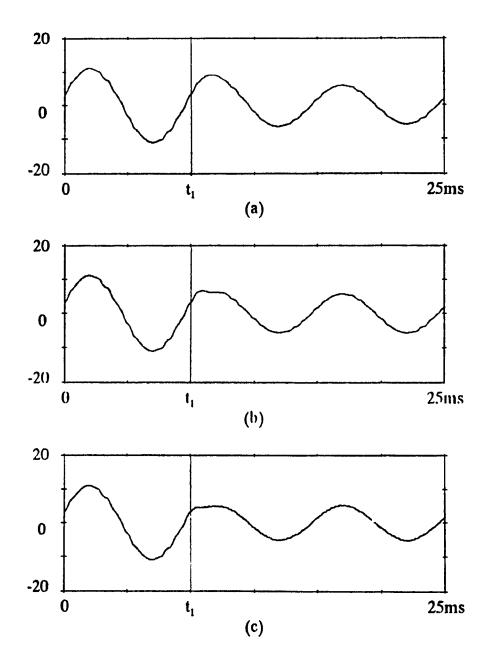

| Fig. 4.19: | Transient response of a load current for three CSIs                 | 96         |

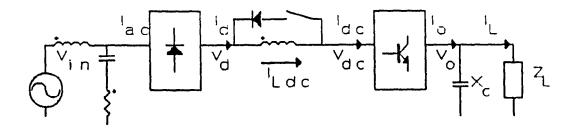

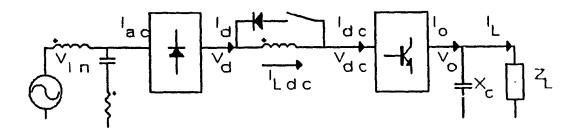

| Dc bus current and input line currents.                     | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCSI line diagram.                                          | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Relationship between dc bus current and input line current. | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

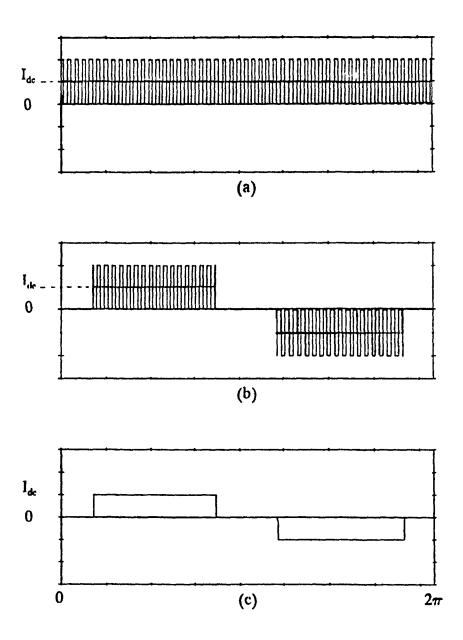

| D <sub>m</sub> vs M for third harmonic injection SPWM.      | 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

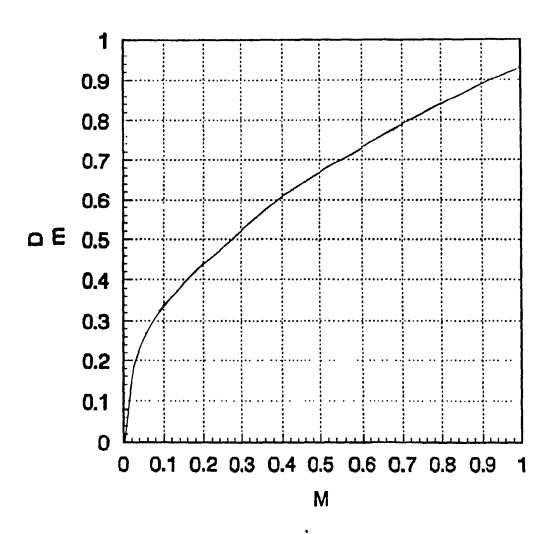

| Inverter output current for ASCI, SHE CSI, ICCC CSI,        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| and MCSI.                                                   | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

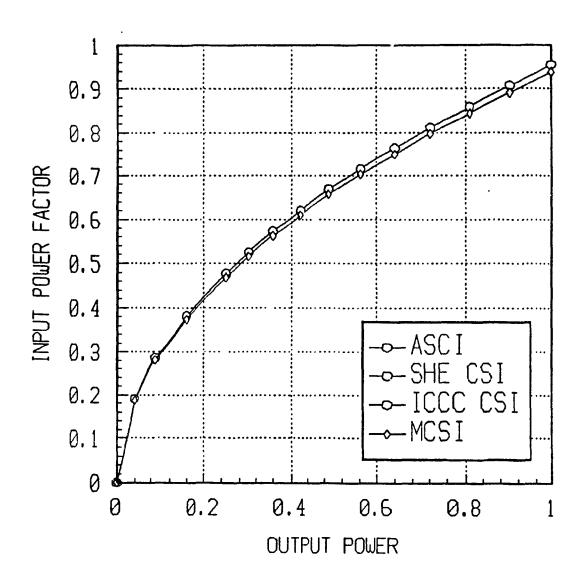

| Input power factor vs. output power when rectifier firing   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| control is used.                                            | 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Input power factor vs. output power when rectifier firing   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| angle control is used.                                      | 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

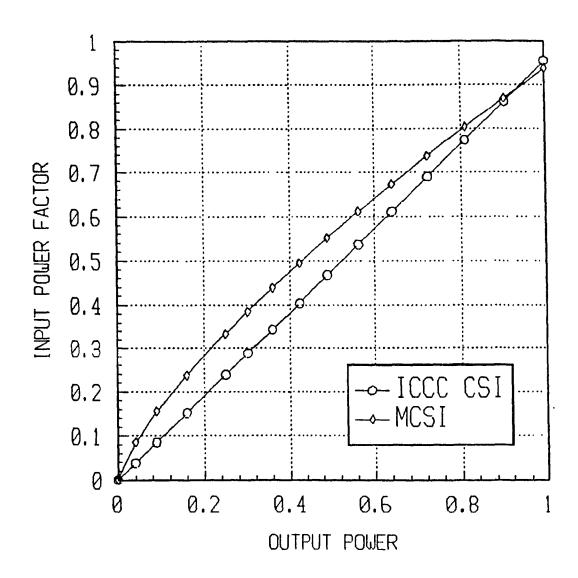

| Input power factor vs. output power for MCSI with and       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| without input filtering.                                    | 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

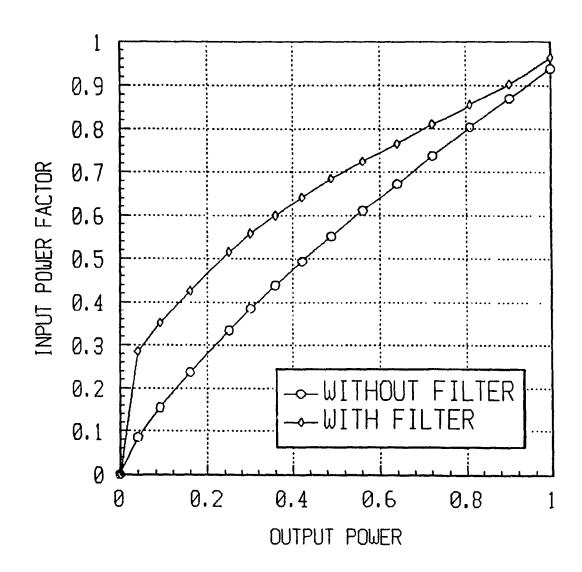

| Input current harmonic spectrum (simulated).                | 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

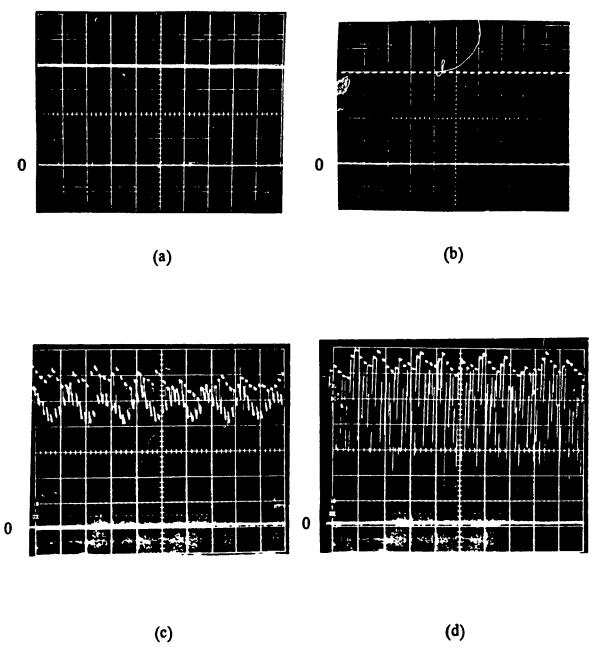

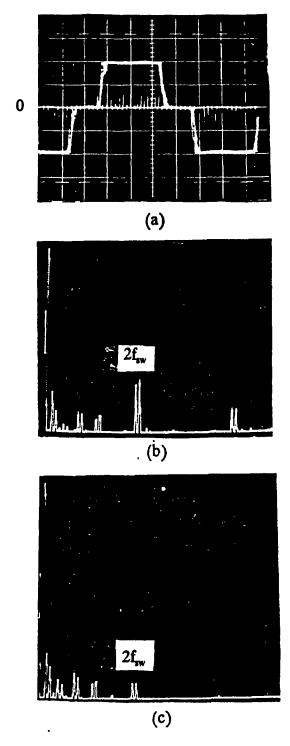

| Experimental input waveforms $(M = 0.8)$ .                  | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

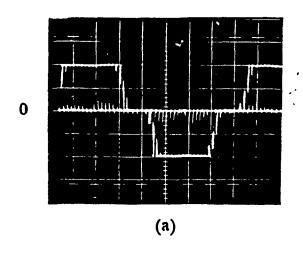

| Experimental input waveforms $(M = 0.5)$ .                  | 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

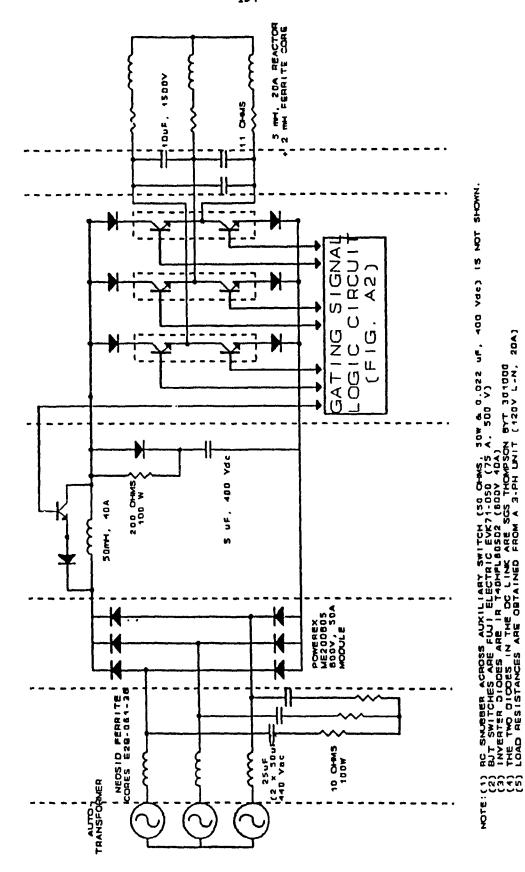

| 5 kVA experimental prototype unit.                          | 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

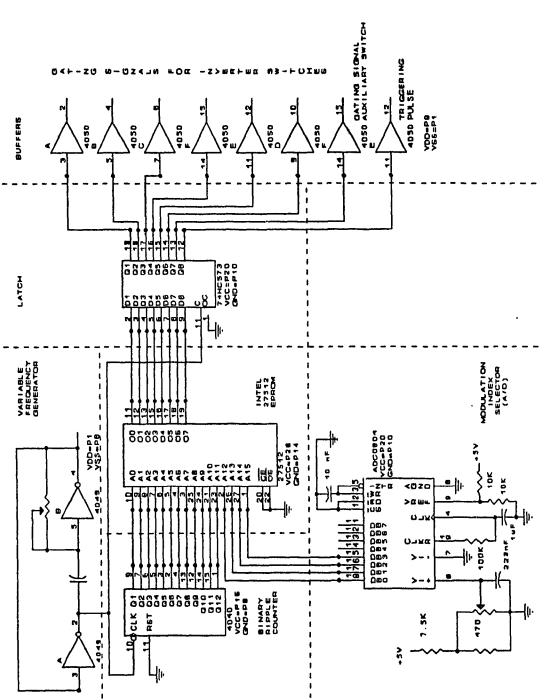

| Layout of gating signal logic circuit.                      | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                             | MCSI line diagram.  Relationship between dc bus current and input line current. $D_m$ vs M for third harmonic injection SPWM.  Inverter output current for ASCI, SHE CSI, ICCC CSI, and MCSI.  Input power factor vs. output power when rectifier firing control is used.  Input power factor vs. output power when rectifier firing angle control is used.  Input power factor vs. output power for MCSI with and without input filtering.  Input current harmonic spectrum (simulated).  Experimental input waveforms (M = 0.8).  Experimental input waveforms (M = 0.5).  5 kVA experimental prototype unit. |

#### LIST OF ACRONYMS

3HIPWM Third Harmonic Injection Pulsewidth Modulation

AC Alternating Current

ASCI Autosequentially Commutated Inverter

BJT Bipolar Junction Transistor

CSI Current Source Inverter

DC Direct Current

EPROM Erasable Programmable Read Only Memory

EPWM Equal Pulsewidth Modulation

GTO Gate Turn-Off Thyristor

HIPWM Harmonic Injection Pulse Width Modulation

ICCC Instantaneous Current Control Capability

kVA kilo Volt-Ampere

MCSI Modified Current Source Inverter

MSPWM Modified Sinusoidal Pulsewidth modulation

ms milli seconds

mH milli Henry

PWM Pulsewidth Modulation

RMS Root Mean Square

RPM Revolution Per Minute

SHE Selective Harmonic Elimination

SPWM Sinusoidal Pulsewidth modulation

TPWM Trapezoidal Pulsewidth Modulation

VSI Voltage Source Inverter

VA Volt-Ampere

μF micro Farad

# LIST OF PRINCIPAL SYMBOLS

| $A_{dc}$                   | attenuation factor for de link inductor design               |

|----------------------------|--------------------------------------------------------------|

| A <sub>o</sub>             | attenuation factor for output capacitor design               |

| $C_{f}$                    | value of the input filter capactors                          |

| $D_m$                      | ratio of I <sub>ac</sub> to I <sub>acr</sub>                 |

| f                          | frequency                                                    |

| $\mathbf{f}_{b}$           | break frequency                                              |

| $\mathbf{f_h}$             | harmonic frequency                                           |

| $\mathbf{f}_{\mathbf{m}}$  | input frequency                                              |

| f <sub>o</sub>             | inverter fundamental switching frequency                     |

| $\mathbf{f}_{\mathbf{r}}$  | frequency equal to six times the input frequency             |

| $\mathbf{f}_{\mathbf{sw}}$ | inverter switching frequency                                 |

| G                          | GTO                                                          |

| $I_{ac}$                   | fundamental rms component of input line current              |

| Iacl                       | output ac line current                                       |

| Iacr                       | total rms value of input line currents                       |

| $I_d$                      | rectifier output current                                     |

| $I_{dc}$                   | dc bus current or its average value                          |

| I <sub>dc,peak</sub>       | value of top part of de bus current                          |

| $I_h$                      | harmonic current                                             |

| $I_L$                      | load current                                                 |

| $I_{Lde}$                  | dc link inductor current                                     |

| I <sub>Ldc,rat</sub>       | rated dc link inductor current                               |

| $I_n$                      | nth current harmonic                                         |

| $I_o$                      | inverter output current                                      |

| k                          | number of switching angles                                   |

| K                          | PWM pattern constant                                         |

| K <sub>ac</sub>            | ratio of input line current fundamental rms component to the |

|                            | average value of the dc bus current                          |

|                            |                                                              |

ac gain factor of PWM pattern as a function of M  $K_i(M)$ duty cycle of auxiliary switch K, line-neutral L-N line-line L-L de link inductor  $L_{dc}$ value of the input filter inductors L M modulation index  $N_{p}$ number of pulses power factor pf per unit pu real power at input and output P quality factor for input filter Q input filter resistance  $\mathbf{R}_{\mathbf{f}}$ load or line resistance  $\mathbf{R}_{\mathbf{L}}$ R'r rotor resistance stator resistance R, slip S switch or switching function SW time instant  $\mathbf{t_1}$ Т thyristor  $V_{\mathbf{a}_{\mathbf{c}}}$ ac rms line-neutralinput voltage  $V_{d}$ rectifier output voltage inverter input voltage  $V_{dc}$ harmonic voltage  $V_{k}$ input voltage  $V_{in}$ V. fundamental rms component of the output line-neytral voltage V, voltage ripple on dc bus output filter capactor impedance for fo X<sub>c</sub> output filter capacitor impedance for any f<sub>b</sub>  $X_{ch}$

magnetizing reactance

$X_{m}$

| X'r            | rotor reactance        |

|----------------|------------------------|

| X <sub>s</sub> | stator reactance       |

| $Z_L$          | load impedance         |

| Z <sub>o</sub> | output impedance       |

| α              | rectifier firing angle |

| $\phi_{ m o}$  | output phase angle     |

#### **CHAPTER 1 - INTRODUCTION**

#### 1.1. Introduction

The induction motor - particularly the squirrel cage type - is rugged, reliable, efficient, and has low maintenance requirements; therefore it is the most widely used electric motor. This, however, was not always the case because the applications of the induction motor were limited to those requiring constant speed as methods of speed control were either expensive, inefficient, or limited. For example, one method of speed control was to connect the induction motor to a variable frequency source made up of a dc motor - ac generator set; this was impractical because of the cost and required maintenance of two machines in addition to the load.

The advent of power semiconductor devices in the 1950's and 60's, such as thyristors, has led to the widespread use of static power conversion as a means of constructing variable frequency sources for induction motors. Among the various power conversion circuits in existence, the inverter, which converts a dc source into a three-phase ac source, is the one that is generally used in induction motor drives. There are two types of inverters that are used today: the voltage source inverter (VSI) and the current source inverter (CSI); both of these are shown in this chapter and their characteristics are compared. Since the focus of this thesis is on CSIs, a review of previously proposed CSI topologies is given. Finally, the objective, scope, contributions and summary of the thesis are given.

### 1.2. Voltage source inverter

A voltage source inverter (Fig. 1.1) requires a dc voltage at its input. This voltage is generally obtained by converting the voltage from the ac mains into a dc voltage with a rectifier then eliminating the harmonics with an LC filter. The inverter converts the dc voltage at its input into three symmetrical ac voltages through the appropriate firing of its switches. The ac voltages that are fed to the motor are not sinusoidal but are made up of square pulses, and it is the motor leakage inductances that attenuate the harmonics. The diodes are added to permit reverse current flow during reactive power flow or during regeneration, to clamp the load voltage to that of the input level, and to use in the forced commutation (turnoff) of the switches when thyristors are used.

#### 1.3. Current source inverter

A current source inverter is fed from a current source which is made up of an inductor in series with a voltage source since an ideal current source does not exist. The inverter converts the dc input current into three symmetrical ac line currents that are then fed to the load.

The first CSI to be developed was the autosequentially commutated inverter (ASCI) [1]-[4]. This topology (Fig. 1.2) used thyristors as the main inverter switches

Fig. 1.1. Voltage source inverter.

.

and was the standard CSI topology of the 1970's. The topology got its name from the fact that if the thyristors were fired in sequence (T1-T6), then the firing of one switch would automatically commutate another. No additional circuitry was needed to commutate the thyristors because this was done by the diodes and capacitors in the inverter.

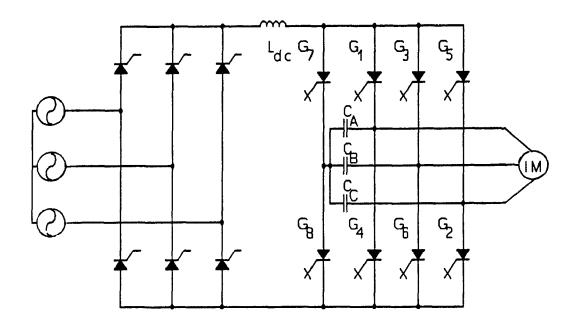

The advances in power semiconductor technology in the early 1980's such the development of gate turn-off thyristors (GTO) and bipolar junction transistors (BJT) led to the development of a new CSI topology as the ASCI was a thyristor based topology that could not take advantage of the new devices. The pulsewidth modulated CSI (PWM CSI) [5]-[6], shown in Fig. 1.3, has been gradually replacing the ASCI and is now the standard CSI topology [7] since it can produce almost sinusoidal line currents and has a higher range of operating frequencies. Since the inverter switches can be self-commutated, the commutating capacitors that were placed in the ASCI are removed. The PWM CSI, however, does have capacitors and they are used to filter out harmonics in the line currents and to provide current paths for the energy trapped in the leakage inductance of the motor whenever commutation takes place.

# 1.4. Voltage source inverter vs current source inverter

The relative advantages and disadvantages of VSI and CSI drives are given below. With these in mind, a designer can select the type of inverter best suited for

Fig. 1.2. The autosequentially commutated inverter (ASCI).

Fig. 1.3. The PWM current source inverter.

a particular application.

- 1) A CSI is more reliable than a VSI because it can tolerate a short-circuit in the inverter caused by the misfiring of the switches, by commutation failure, or by a fau.t in the load. Should any of the above occur, the resultant current can be regulated by controlling the rectifier output voltage.

- 2) A CSI has inherent four-quadrant operation capability and does not require any additional power circuitry for regeneration to occur. On the other hand, a VSI requires an additional converter connected anti-parallel to the frontend rectifier to provide a path for the current whenever regeneration occurs.

- 3) Multi-machine load on a single inverter or a multi-inverter load on a single rectifier is very difficult with CSIs; however this is not so for VSIs and they can be used wherever multi-machine or multi-inverter capability is required.

- A large leakage inductance lengthens the current transfer interval in a CSI thus limiting the range of inverter operating frequency and speed of operation. Also, the output filter capacitor and the motor inductance produce a resonance effect that amplifies the harmonics near the resonant frequency. These problems do not exist in a VSI.

#### 1.5. Literature review

Although the CSI has several advantages over the VSI, it is not as widely used because it has several drawbacks. In order to overcome some of these drawbacks, several researchers have proposed modifications to the standard ASCI and PWM CSI topologies. In this section, some of these drawbacks are examined along with a review of previously proposed modifications to the ACSI and the PWM CSI is given.

The problem that has sparked the most research into modified topologies is that the inverter output voltage contains large overvoltage spikes that can damage the inverter components and the load. These spikes are caused by the energy that is stored in the inverter capacitors and the motor leakage inductance, and appear whenever an inverter switch is commutated. This problem exists for both the ASCI and the PWM CSI, and is worse for the ASCI because the conduction interval for a switch is much longer thus the capacitors have more energy stored in them by the time commutation occurs. In order to reduce or suppress the output voltage spikes something must be done with the energy stored in the reactive elements.

One solution to the problem is to add a voltage clamping circuit to the inverter [8]-[9]. Voltage clamping circuits that have been proposed include zener diode circuits and transistor-capacitor-resistor circuits. The basic function of these circuits is to dissipate the reactive energy through a zener or a resistor whenever the inverter output voltage spikes reach a certain level. However, since energy is wasted

in the voltage clamping circuit, this method of reducing the inverter output spikes is not very efficient.

The overvoltage spike problem can also be solved by adding an energy rebound circuit to the inverter [10]-[12]. With this circuit, the energy stored in the motor leakage inductances is stored in a capacitor then fed back to the inverter whenever desired instead of being dissipated. Another advantage to having an energy rebound circuit has been shown by Matsuse and Kubota [13]. Since the storage capacitor acts as a dc voltage source at selected intervals, current does not have to always flow through the rectifier, and can be made zero whenever desired, thus allowing PWM techniques to be used with a standard thyristor rectifier. Although there are benefits to adding an energy rebound circuit to the inverter, one major disadvantage is that the circuit requires many additional components such as a diode rectifier and switches which increase the cost and complexity of the current source inverter.

Another drawback that the CSI has is that its dynamic response - the time it takes for the amplitude of the load currents to change after the command for change has been given is poor - especially when a phase-controlled rectifier is used as the front-end converter. The reason for the poor dynamic response is the size of the inductor in the dc link needed to ensure a stiff dc current; the current fed into the inverter cannot be quickly changed if the inductor is large. Several researchers have proposed solving this problem by firing the inverter switches in such a way so as to provide a short-circuit path for the inductor current through the

inverter itself [14]-[16]. This, however, results in a dc link current boost effect particularly at low operating frequencies and at low modulation indices.

A third drawb2ck that the CSI has is that the topology limits the way that the inverter switches can be fired. As a result, the output line currents that are produced by the CSI contain more low-frequency harmonics than do the output voltages of a voltage source inverter and this causes problems at the output including a decrease in the efficiency of the motor. In order to increase the gating techniques that can be implemented, thus reducing the problems caused by line current harmonics, several researchers have modified the CSI by adding additional switches external to the inverter [17]-[18].

When the ASCI was the standard topology, researchers tried to increase its range of operating frequency by adding additional components in the inverter circuit [15]. [19]-[20]. This range was limited to low frequencies because the commutation process needed to turn off the thyristors was slow as it took time for the charge on the capacitor to reverse. The additional circuitry enabled the charge on the capacitor to reverse quickly or to reduce the charge in a way similar to the voltage clamping circuits.

The range of operating frequency of the PWM CSI is much higher than that of the ASCI because it does not have any commutating circuits as self-commutated switches are used. At high operating frequencies, however, the switching losses of the PWM CSI become higher. In order to reduce these losses, Murai and Lipo [21] proposed adding a series - resonant circuit to the dc link and making the

current into positive half-sinusoidal pulses. The new topology allowed for zerocurrent switching of the inverter switches to occur since the dc link current had zero points at which the switches were fired.

#### 1.6. Scope and contributions

The objective of this thesis is to propose and analyze a modified PWM CSI topology that overcomes several of the drawbacks mentioned in the previous section, and to compare its performance to that of the conventional PWM CSI. The scope of this thesis is limited to an analysis of the characteristics of the proposed topology under steady-state conditions as the performance of the converter with an induction motor load under closed loop conditions is not considered. Emphasis is placed on demonstrating the operating principles, unique characteristics, and benefits of the proposed inverter topology.

The principal contributions of this thesis are as follows:

- 1) A modified current source inverter is proposed and analyzed. It is shown that the proposed inverter is simple and has several advantages over the conventional PWM CSI. The proposed topology allows any PWM technique to be used, has an excellent dynamic response, and does not have overvoltage spikes on the inverter output voltage.

- 2) The technique of variable modulation index control is examined in detail and its effect upon the operation of the conventional PWM CSI and the proposed

inverter is investigated and compared.

3) Since the inverter is an unconventional one, the standard design procedure for the conventional PWM CSI cannot be used; a design procedure to find steady-state operating points for the proposed CSI is presented.

### 1.7. Summary of the thesis

The contents of this thesis have been organized as follows:

In Chapter 2, the general rules for firing the CSI switches are given and several gating techniques for the inverter switches are examined. It is shown that the techniques that were originally proposed contain low-order harmonics and that the original gating rules were unnecessarily restrictive. PWM techniques that produce output line currents containing no low-frequency harmonics are presented. It is explained how the conventional PWM CSI does not allow certain techniques to be used and how this restriction can be removed by modifying the power circuit topology.

In Chapter 3, the operating characteristics of the conventional PWM CSI are examined. Equations relating the inverter operating parameters (i.e. the modulation index of the pattern) to the dc bus quantities are presented and are used to demonstrate the effect that a change in the parameters has on the dc bus. The dynamic response of the PWM CSI and the inverter output voltage spike problem are also considered. It is shown that the dynamic response cannot be improved and

the spike problem cannot be solved without some trade-offs, but that these tradeoffs are not necessary for the proposed CSI topology.

In Chapter 4, the proposed topology is introduced and its steady-state operating characteristics are shown and contrasted to those of a conventional PWM CSI. A design procedure to calculate operating points for the inverter and the load is presented along with a design procedure for the output filter capacitors and the ratings of the switches. An example is presented to show how the design procedure can be used to calculate the steady-state dc bus and inverter output values for two load operating points. Finally, the feasibility of the proposed topology is verified with simulated and experimental results.

In Chapter 5, the input characteristics of the proposed topology are examined. Equations relating the dc bus quantities to those at the input are presented, and are used in a design example and in a comparison of power factor with other CSIs. Efficiency considerations for the proposed topology, the ASCI and the conventional PWM CSI are also given. A design procedure for the input filter is presented and verified with simulated and experimental results.

In Chapter 6, the conclusions of this thesis are given along with suggestions for future work.

# CHAPTER 2 - PULSEWIDTH MODULATION TECHNIQUES AND PATTERNS FOR CURRENT SOURCE INVERTERS

#### 2.1. Introduction

An inverter pattern can be defined as the line current waveform produced when the inverter switches are fired in a particular way. The pattern is very important to the operation of a CSI because it determines the CSI's performance and operating characteristics. Patterns can be designed to meet the desired criteria (i.e. elimination of lower order harmonics) for a particular application. In this chapter, the general rules for CSI patterns are presented along with several patterns used in ASCIs and PWM CSIs. It is shown these patterns are limited in the number of low-order harmonics that they can eliminate, but that this limitation can be relaxed so that more PWM patterns can be implemented and the performance of the CSI can be improved. The benefits of adding an auxiliary switch to the CSI are also investigated.

## 2.2. General rules for CSI patterns

There are limits that must be placed on the inverter pattern that can be used because of the CSI six-switch configuration. In general, the pattern for a CSI must be such that only one top inverter switch and one bottom inverter switch are on at any moment. If there are less than two switches on, then there is no path for the

dc link inductor current to flow through the inverter and the energy stored in the dc link inductor would damage the switches by forcing a path to appear. If there are more than two switches on at the same time, then the output line current waveforms are not defined (since there are multiple paths for the current to flow) and thus contain undesired and uncharacteristic harmonics. The inverter pattern must ensure that there is always one and only one path for the dc link inductor current.

The pattern must also ensure that the output line currents have the same waveform and that each current has a phase difference of 120° with respect to the other two. Moreover, the pattern should contain half-wave and quarter-wave symmetry. Balanced and symmetrical line currents ensure that no even or triplen harmonics are fed to the load.

## 2.3. The autosequentially commutated inverter in the six step mode of operation

It was mentioned in Chapter 1 that the ASCI got its name from the fact that when the thyristors were fired in a certain sequence, then commutation took place automatically. In this sequence, each of the thyristors T1 to T6 was fired in order once in every period at 60° intervals, and kept on for 120°. This "six-step" method of operating the ASCI produced output currents that were made up of two pulses of 120° width - one positive and one negative. It can be seen in Fig. 2.1 that the line currents were symmetrical and well-defined, thus satisfying the general rules for CSI

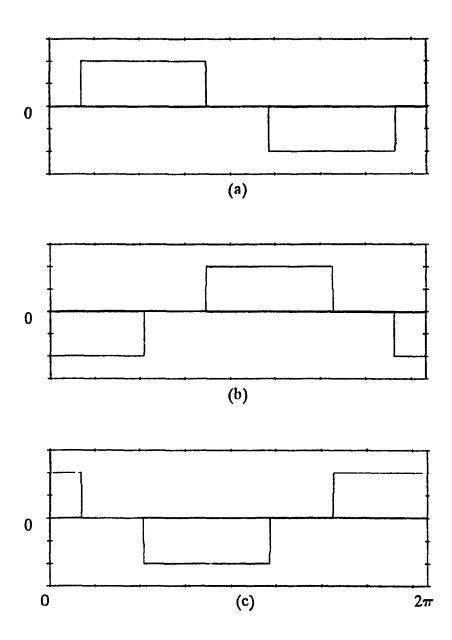

Fig. 2.1. ASCI output line currents (a) Phase A. (b) Phase B. (c) Phase C.

patterns.

The line current for each phase can be expressed as a Fourier series as

$$I(t) = \sum_{i=1}^{n} (a_n \cos n\omega t + b_n \sin n\omega t)$$

(2.1)

where

$$a_n = \frac{1}{\pi} \int_0^{2\pi} I(t) \cos n\omega t \ d\omega t \tag{2.2}$$

$$b_n = \frac{1}{\pi} \int_0^{2\pi} I(t) \sin n\omega t \ d\omega t$$

(2.3)

Since each line current has half-wave symmetry and quarter-wave symmetry, there are no even harmonics and

$$a_n = 0 ag{2.4}$$

$$b_n = \frac{1}{\pi} \int_0^{2\pi} I(t) \sin n\omega t \ d\omega t \tag{2.5}$$

The line current for phase A can be expressed as

$$b_n = \frac{4I_{dc}}{\pi} \int_{\frac{\pi}{c}}^{\frac{\pi}{2}} \sin n\omega t \ d\omega t \tag{2.6}$$

because of the symmetries, and this gives

$$b_n = \frac{2\sqrt{3}}{n\pi} I_{dc} \tag{2.7}$$

where n is odd. If the fundamental line current component  $I_1$  has an amplitude of then the amplitude of any harmonic  $I_n$  with respect to  $I_1$  is

$$I_1 = \frac{2\sqrt{3}}{\pi} I_{dc} \tag{2.8}$$

$$I_n = \frac{I_1}{n} \tag{2.9}$$

Although for many years the standard method of operation for an ASCI in induction motor drives was the six-step mode, there were several disadvantages to operating the ASCI in this manner. Most of these were due to the presence of large low-order harmonics in the line currents (i.e. the fifth harmonic was 20% of the fundamental component) which caused the following problems:

- The motor had severe torque pulsations at low speeds that caused the shaft to cog.

- 2) The motor had to be derated because of thermal loading.

- 3) The efficiency of the motor at light loads was poor. [22]

It was the need to reduce and eliminate the low frequency harmonics that led to the development of pulsewidth modulation (PWM) patterns for the ASCI and then for the PWM CSI.

#### 2.4. PWM techniques

#### 2.4.1. Introduction

When PWM techniques for CSIs were first developed in the late 1970's and early 1980's [23]-[26], this was done by cutting out pulses from the 120° wide line

current pulses and redistributing them to the other phases. This, however, meant that no PWM could be done in the center 60° of each half-cycle and the patterns that were implemented on the CSI had to be fixed since any attempt to modify them online could have violated the general inverter pattern rules. As a result, PWM patterns for CSIs were generally restricted to the following two which are examined in this section:

- 1) Selective harmonic elimination

- 2) Trapezoidal PWM

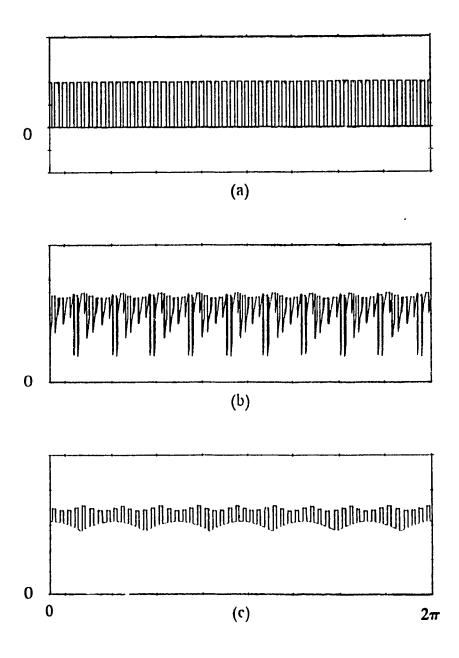

The result of allowing PWM within the center 60° of each half-cycle can be seen in Fig. 2.2. Fig. 2.2(a) shows an output line current having PWM in the center 60° regions while Fig. 2.2(b) and (c) show the appearance of unwanted (circled) pulses on the other two phases. These pulses must appear on the line currents because the pulses that have been cut out of the center 60° blocks of the current in (a) must be shifted to another phase to satisfy the constraint that there always be a path for current to flow through the inverter and the load. This causes the line currents to have more and larger harmonics than they would have if the pulses did not appear.

#### 2.4.2 Selective harmonic elimination

Selective harmonic elimination (SHE) was first proposed for voltage source

Fig. 2.2. PWM output line currents with unwanted pulse problem: (a) Phase A. (b) . Phase B. (c) Phase C.

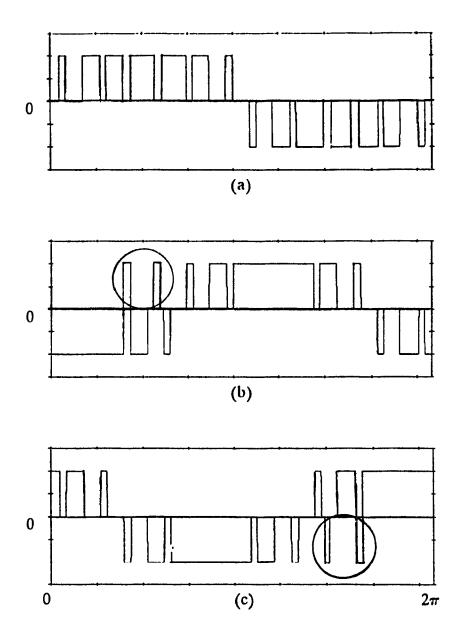

inverters by Patel and Hoft [27], then was later adapted for CSIs. The line current waveform produced with this technique (Fig. 2.3) has no PWM in the center 60° blocks and contains several symmetries - the 120° to 180° range is a mirror image of the 0° to 60° range, and the 30° to 60° range is an inverse mirror image of the 0° to 30° range. Using this technique, undesired harmonics can be eliminated from the line current by deriving its Fourier series and calculating the switching angles that set the magnitude of the undesired harmonics to zero. Once these angles are known, then the position and width of the pulses in the 0° to 30° range can be determined and the rest of the pattern can be constructed using the symmetries. The procedure to calculate the switching angles is as follows.

The line current waveform can be expressed as

$$I(t) = \sum_{i=1}^{n} (a_n \cos n\omega t + b_n \sin n\omega t)$$

(2.10)

where

$$a_n = 0 (2.11)$$

$$b_n = \frac{1}{\pi} \int_0^{2\pi} I(t) \sin n\omega t \ d\omega t \qquad (2.12)$$

because of half-wave and quarter wave symmetry. If k is defined as

$$k = \frac{N_p - 1}{2} \tag{2.13}$$

where  $N_p$  is the number of pulses per half-cycle, then equ. 2.12 can be expanded as

Fig. 2.3. A typical selective harmonic elimination pattern.

$$b_{n} = \frac{4I_{dc}}{\pi} \left( \int_{\alpha_{1}}^{\alpha_{2}} \sin n\omega t \ d\omega t + \dots \int_{\alpha_{k}}^{\frac{\pi}{6}} \sin n\omega t \ d\omega t + \int_{\frac{\pi}{3} - \alpha_{k}}^{\frac{\pi}{3} - \alpha_{k-1}} \sin n\omega t \ d\omega t + \dots \int_{\frac{\pi}{3} - \alpha_{1}}^{\frac{\pi}{2}} \sin n\omega t \ d\omega t \right)$$

$$(2.14)$$

when k is odd or

$$b_{n} = \frac{4I_{dc}}{\pi} \left( \int_{\alpha_{1}}^{\alpha_{2}} \sin n\omega t \ d\omega t + \dots \int_{\alpha_{k-1}}^{\alpha_{k}} \sin n\omega t \ d\omega t + \dots \int_{\frac{\pi}{6}}^{\frac{\pi}{3} - \alpha_{k}} \sin n\omega t \ d\omega t + \dots \int_{\frac{\pi}{3} - \alpha_{1}}^{\frac{\pi}{2}} \sin n\omega t \ d\omega t \right)$$

$$(2.15)$$

when k is even. If equ. 2.16

$$\int_{\theta_1}^{\theta_2} \sin n\omega t \ d\omega t = \frac{1}{n} \left( \cos n\theta_1 - \cos n\theta_2 \right) \tag{2.16}$$

is plugged into 2.14 and 2.15 then they can be written as

$$b_{n} = \frac{4I_{dc}}{\pi} \left( \cos(n\alpha_{1}) + \cos\left[n\left(\frac{\pi}{3} - \alpha_{1}\right)\right] - \cos(n\alpha_{2}) - \cos\left[n\left(\frac{\pi}{3} - \alpha_{2}\right)\right] + \dots + \cos(n\alpha_{k}) + \cos\left[n\left(\frac{\pi}{3} - \alpha_{k}\right)\right] - \cos\left(n\frac{\pi}{6}\right) \right)$$

(2.17)

when k is odd or

$$b_{n} = \frac{4I_{dc}}{\pi} \left( \cos(n\alpha_{1}) + \cos\left[n(\frac{\pi}{3} - \alpha_{1})\right] - \cos(n\alpha_{2}) - \cos\left[n(\frac{\pi}{3} - \alpha_{2})\right] + \dots - \cos(n\alpha_{k}) - \cos\left[n(\frac{\pi}{3} - \alpha_{k})\right] + \cos\left(n\frac{\pi}{6}\right) \right)$$

(2.18)

when k is even.

If k switching angles are derived for a pattern having  $N_p$  pulses per half-cycle using equ. 2.17 or 2.18, then k harmonics can be eliminated. For example, if a pattern has five pulses per half-cycle, then two switching angles can be calculated.

If the fifth and seventh harmonics are to be eliminated then the appropriate equations are

$$\cos (5\alpha_1) + \cos \left[5\left(\frac{\pi}{3} - \alpha_1\right)\right] - \cos (5\alpha_2) - \cos \left[5\left(\frac{\pi}{3} - \alpha_2\right)\right] + \cos \left(5\frac{\pi}{6}\right) = 0$$

(2.19)

$$\cos (7\alpha_1) + \cos \left[7\left(\frac{\pi}{3} - \alpha_1\right)\right] - \cos (7\alpha_2) - \cos \left[7\left(\frac{\pi}{3} - \alpha_2\right)\right] + \cos \left(7\frac{\pi}{6}\right) = 0$$

(2.20)

These transcendental equations can be solved by using a numerical method such as the Newton-Raphson method, and the switching angles  $\alpha_1$  and  $\alpha_2$  can be obtained.

Although SHE is an improvement over the ASCI six-step mode pattern, the number of harmonics that can actually be eliminated with this method are few. The reason for this is that the rigid symmetrical constraints placed on the pattern limit the switching angles that can actually be derived to the 0° to 30° range. If it was desired to eliminate many harmonics, then the pulses in this region - thus the pulses in the rest of the pattern - would be so thin that the inverter switches would not have enough time to switch on and off properly and the output line currents would be distorted. Therefore, SHE is generally used to eliminate up to four harmonics unless the frequency is very low; only then can more harmonics be eliminated as the pulses are wider. Since only four harmonics can be eliminated, these must be selected so that at least one corresponds to the resonance frequency, which is dependent on the value of the filter capacitors and the motor inductances. If the harmonic closest to the resonance frequency is not eliminated, then it will be

amplified thus worsening the harmonic content of the output currents.

### 2.4.3. Trapezoidal PWM

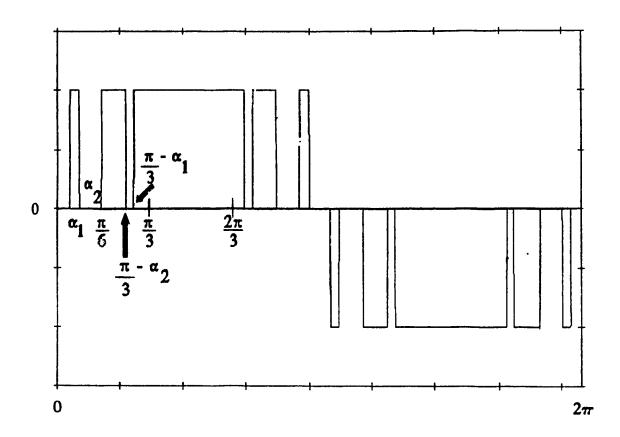

Trapezoidal PWM (TPWM) is a carrier PWM technique in which a trapezoidal modulating waveform is compared with a triangular carrier wave to produce a switching function from which the gating signals of an inverter leg are obtained (Fig. 2.4) [26],[28]. It can be seen that the triangular waveform is suppressed in the center 60° block of each half-cycle to avoid any PWM in this region.

The PWM pattern is dependent on two parameters, the modulation index, M and the number of pulses per half-cycle,  $N_p$ . M is the amplitude ratio of the modulating waveform, A, to the carrier waveform, B, and controls the width of the pulses.  $N_p$  is determined by the relationship between the frequency of the carrier to that of the modulating waveform. Since there is no PWM performed on the center  $60^{\circ}$  block of each half-cycle, the technique is extremely limited in the number of harmonics that can actually be eliminated; however, the magnitudes of selected harmonics can be minimized with the appropriate value of M and  $N_p$ . For example, if M = 0.82 and  $N_p = 7$  then the fifth harmonic is eliminated but there is a substantial seventh harmonic; if M is set to 1 then the seventh harmonic is reduced but the fifth becomes larger [26]. Although it can be calculated online with analog devices, the pattern that is used must be predetermined in some way because there

Fig. 2.4. (a) TPWM scheme. (b) TPWM pattern.

is no direct relationship between the harmonic content of the line currents and M and  $N_p$ . For TPWM, the switching angles of many switching functions - each with its own combination of M and  $N_p$  - must be derived first, then Fourier analysis must done so that the harmonic content of all the derived switching functions can be compared. This is in contrast to SHE where the desired harmonics to be eliminated are selected first, and then the pattern is constructed.

As with SHE, the harmonics near the resonant frequency should be the ones that are reduced. TPWM should be used whenever the inverter fundamental frequency is low since  $N_p$  can be high and more line current harmonics can be reduced or eliminated than with SHE. SHE, however, should be used when the inverter is operated at higher frequencies because it can eliminate more low-order harmonics as  $N_p$  for TPWM must be low.

## 2.5. Dc bus short-circuiting

# 2.5.1. Harmonic elimination

The two PWM techniques that have been presented so far are limited in the number of line current harmonics that they can eliminate because of the lack of PWM in the center 60° region of each half-cycle of the pattern. As was shown earlier, PWM in this region would result in the appearance of unwanted line current pulses. These pulses would not appear if it were possible to make all three line currents zero while providing a path for the dc link inductor current to flow through

the inverter whenever PWM in the center 60° region was required. This can be done if both switches of an inverter leg are made to be on at the same time so that the dc bus is short-circuited and the dc link current bypasses the load [29]-[30]. Inverter patterns that allow for the short-circuiting of the dc bus to take place while satisfying the constraint that there always be only one top switch and one bottom switch on at the same time can be designed.

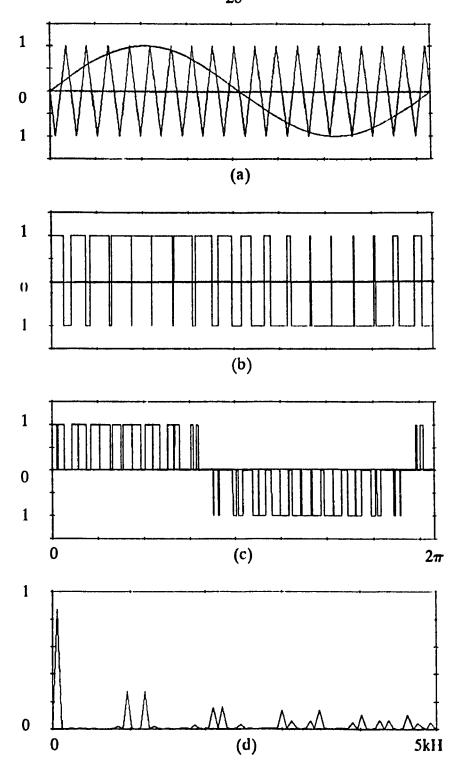

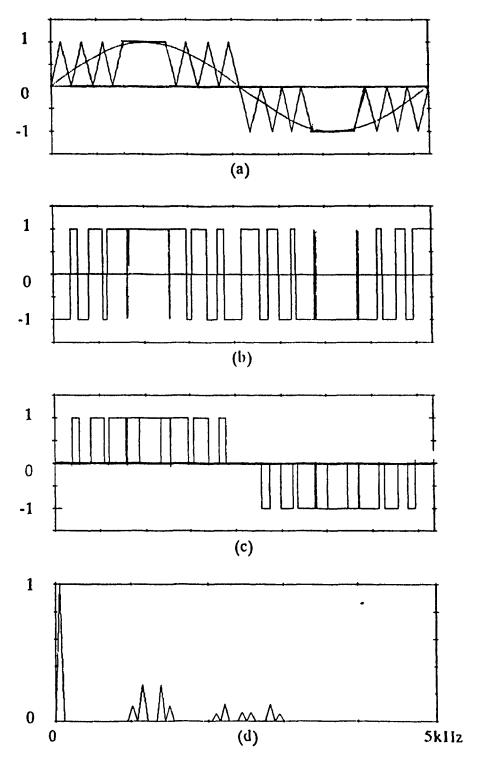

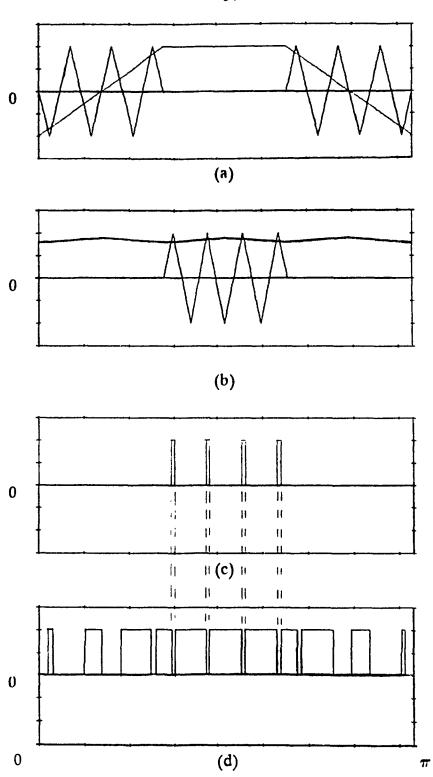

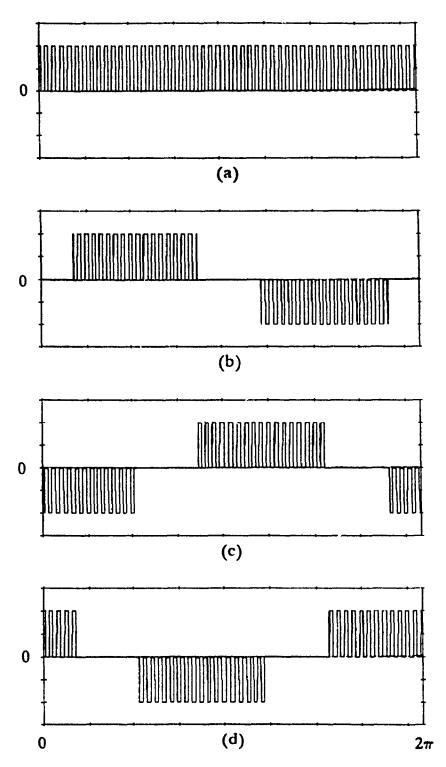

Since short-circuiting the dc bus allows PWM in the center 60° region to appear, the number of PWM techniques that can be used in a CSI are substantially increased. Moreover, techniques that have been used previously in VSIs can be adapted for use in CSIs. For example, sinusoidal PWM - a common VSI carrier PWM technique - can be converted to a CSI technique as shown in Fig. 2.5. In Fig. 2.5(a), a sinusoidal modulating wave is compared with a triangular carrier wave and the two-level switching function shown in Fig. 2.5(b) is produced; this function corresponds to the line-neutral output voltage and thus can be considered as a "lineneutral" function. If this procedure is done for each phase then three line-neutral switching functions will be produced, SWA, SWB, and SWC. If these switching functions are subtracted from one another then three three-level "line-line" switching functions will be produced,  $SW_{AB}$  (Fig. 2.5(c)),  $SW_{BC}$ , and  $SW_{CA}$ . Each switching function corresponds to a VSI line-line output voltage, but it can also correspond to a CSI line current since this too is a three-level waveform. Therefore, VSI PWM techniques, in general, can be adapted for use in CSIs if the two-level VSI switching functions are converted to three - level CSI switching functions from which the

Fig. 2.5. Sinusoidal PWM for 60 Hz fundamental. (a) SPWM scheme. (b) Line-neutral waveform. (c) Line-line waveform (CSI pattern). (d) Fourier spectrum of line-line pattern.

appropriate inverter switch gating signals can be obtained.

## 2.5.2. Amplitude control

Another benefit that can be gained by short-circuiting the dc bus at selected time intervals is an improvement in the dynamic response of the CSI (the time it takes for the load currents to change their amplitude once the command for change has been given) since it is possible to change the fundamental component of the output currents at the inverter. Although a discussion about dynamic response is postponed until Chapter 3, it will be shown here how the fundamental component can be controlled by the inverter pattern.

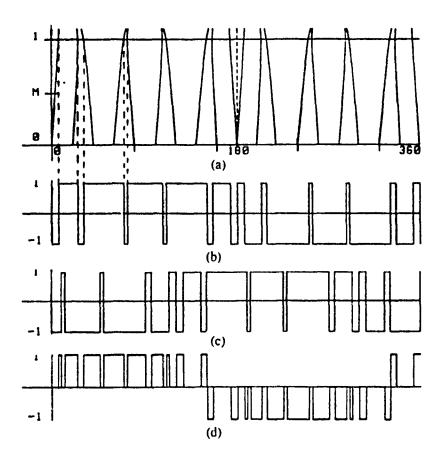

The basic principle of keeping the dc link inductor current constant while using short-circuiting or shoot-through pulses in the inverter pattern to change the fundamental component of the line currents was first proposed by Deng et al. and by Biswas et al. in [14] and [15] respectively. In [14], an ASCI was operated in the six-step mode and the amplitude of the fundamental component was controlled by placing notches in the output line currents then varying the width of the notches the wider the notches were, the more the amplitude of the fundamental line current component was reduced. The principle of "notch control" is shown in Fig. 2.6. where the inverter switch pairs are T1 and T4, T3 and T6, and T5 and T2. As can be seen, the position and width of the notches are determined by how the switches are fired - both switches of an inverter leg are on at the same time whenever it is

Fig. 2.6. (a) Notch control firing sequence. (b)-(d) Output line currents.

desired to place a notch in the line currents. The width of the notches is equal to the short-circuiting interval.

Although notch control made amplitude control possible, the technique had a drawback - since it was implemented on an ASCI operating in the six-step mode, the harmonic content of the line currents was poor. In [15], amplitude control was implemented on an ASCI using a technique that could have been called "equal PWM" (EPWM) as a PWM pattern with an odd number of equal width pulses per half-cycle was used. The fundamental component was controlled by varying the width of the pulses using short-circuiting as with notch control; however, a better harmonic content was obtained with EPWM although low-order harmonics were still present.

# 2.6. Selective harmonic elimination with PWM in the center 60° region

It was shown in section 2.4.2 that the number of harmonics that can be eliminated using SHE is limited because the symmetrical constraints placed on the pattern restrict the switching angles that can be calculated to the 0° to 30° range. A new, less restrictive pattern (Fig. 2.7) can be obtained by short-circuiting the dc bus and having PWM in the center 60° region [31]-[32]. Like the previous SHE pattern, the 120° to 180° is the mirror image of the 0° to 60°, however, the center 60° interval is obtained by folding the first and last 60° intervals around the 60° and 120° points respectively; this folding ensures that the shoot-through pulses do not affect

Fig. 2.7. SHE pattern with PWM in the center 60° region of each half-cycle.

Fig. 2.8. (a) PWM function for variable modulation index control. (b) Two-level switching function  $F_1(t)$ . (c) Two-level switching function  $F_2(t)$ . (d) PWM pattern for CSI.

the quarter-wave symmetry of the pattern. Unlike the pattern presented in section 2.4.2, the 30° to 60° range is not the mirror image of the 0° to 30° range thus the range of calculated switching angles is expanded to the 0° to 60° range. Therefore, the number of undesired harmonics that can be eliminated is increased (from 4 to about 20) because the pulses derived from the switching angles are wide enough so that the inverter switches have time to turn on and off properly. The switching angles can be calculated by using the same procedure as the one shown in section 2.4.2.

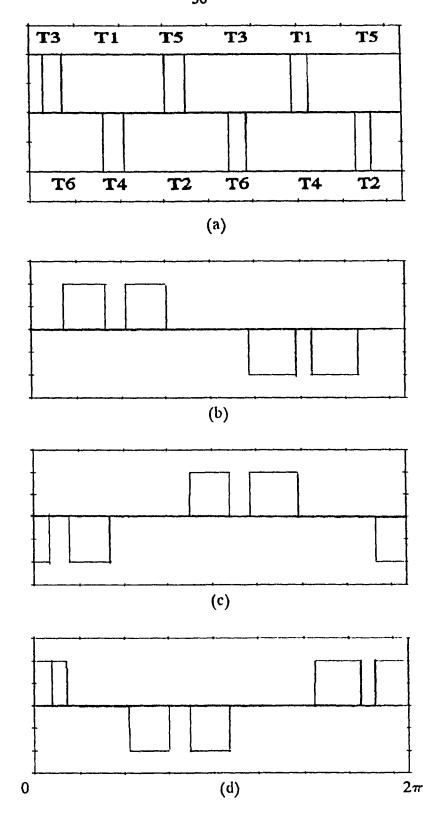

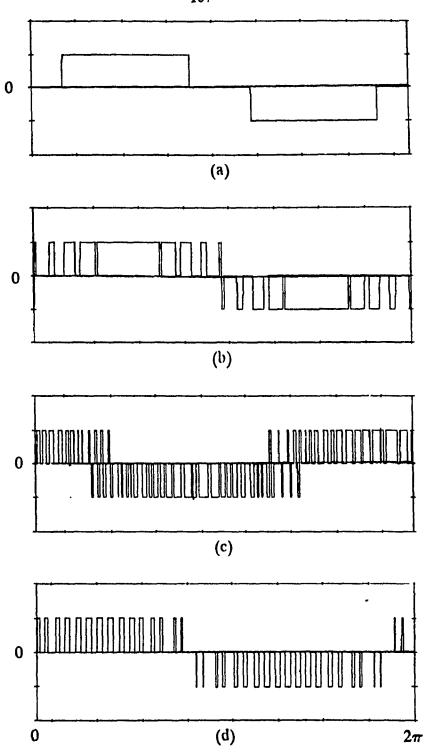

In [16], Enjeti et al presented a method of amplitude control that was implemented on a PWM CSI and used this SHE pattern. In this case, the appropriate switching angles were derived for various values of ac gain (the ratio of the peak value of the fundamental component to that of the unfiltered pulses) for the SHE pattern and the pattern shown in Fig. 2.8(a) was obtained. By comparing this function with a dc signal (whose value can be considered as the modulation index), a two-level function,  $F_1(t)$  (Fig. 2.8(b)) was produced. Fig. 2.8(c) shows another two-level function and Fig. 2.8(d) shows the PWM pattern for a CSI.

It can be seen in Fig. 2.8 that if the level of the dc signal in (a) is varied then this will affect the width and number of the pulses in (b) and (c) which in turn will affect the width and number of the pulses in (d) - similar to the way notch control affected the ASCI line currents. Since the amplitude of the fundamental component of the line current is controlled by the level of the dc signal or modulation index, this method of amplitude control can be called variable modulation index control.

## 2.7. Sinusoidal PWM and its variations

Sinusoidal PWM (SPWM) is a carrier PWM technique that has PWM in the center 60° region of each half-cycle unlike the other carrier PWM technique shown in this chapter, TPWM. The presence of PWM in this region gives SPWM the following advantages over TPWM:

(1) It is easier to control the harmonic content of the output line current when SPWM is used. Unlike TPWM, a suitable pattern - one with no low-order harmonics or harmonics near the resonance frequency - can be easily determined using SPWM because the location of the dominant (largest) harmonics is dependent on the frequency of the triangular carrier and this is easy to adjust. For example, the frequency of the carrier waveform in Fig. 2.5 is 21 times that of the modulating waveform, so that the harmonics that appear are the 19th and 23rd, which are sidebands of the 21st, and the 41st and 43rd, which are sidebands of the 42nd (2 x 21) harmonic. The 21st and the 42nd harmonics do not appear because triplen harmonics cannot appear on a balanced three-phase system. If, for some reason, it is desired to place the dominant harmonics around the 36th or xth harmonic, then all that needs to be done is to set the carrier frequency to 36 or x times that of the modulating waveform. Therefore, if the frequency of the carrier waveform is controlled independently from that of the modulating waveform (which it can be when the comparison between the two waveform is done with analog devices), then the position of the line current harmonics can be fully controlled.

(2) Amplitude control using TPWM is limited because of the unmodulated center 60° block. However, it is possible to control the amplitude of the fundamental component of the line current with SPWM using variable modulation index control as described in section 2.6.2. This amplitude is directly proportional to the modulation index so that if it is desired to reduced it to one-half or one-quarter of its original value, then it can be done by making M equal to 0.5 or 0.25.

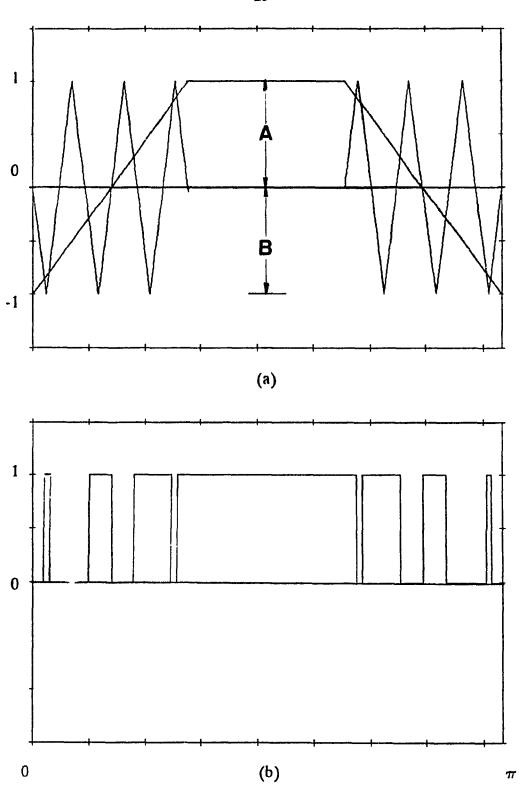

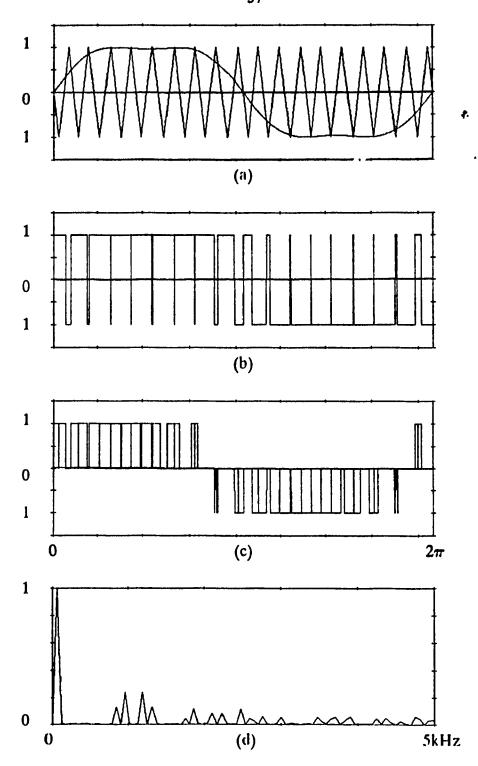

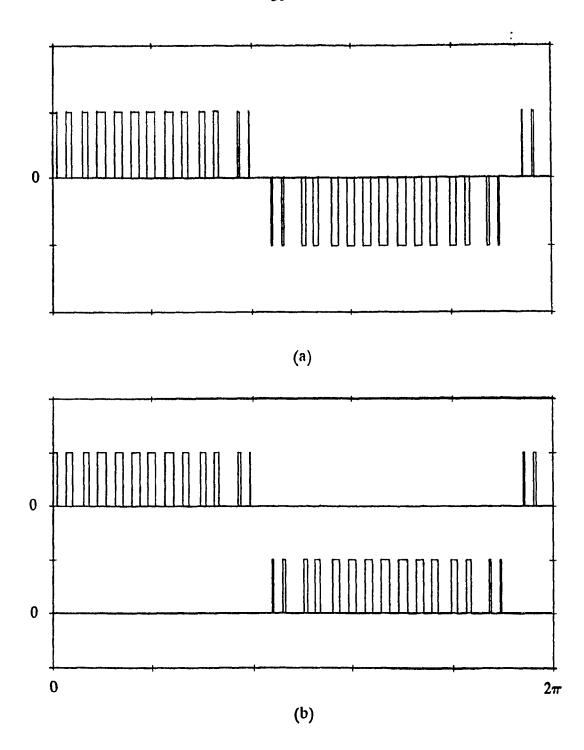

SPWM does have one disadvantage over TPWM and that is that its ac gain is lower, 0.866 vs. 1; therefore, more current must be fed to the inverter to get the same output with SPWM than with TPWM. Techniques such as the modified SPWM (MSPWM) and the third-harmonic injection techniques (3HIPWM) were derived to improve the ac gain of SPWM [33]. In the MSPWM technique (Fig. 2.9), only the first and last 60° intervals per half-cycle of the line-neutral switching functions are directly defined by the intersections of the modulating and carrier waveforms while the 60° to 120° range is obtained by folding the first and last 60° intervals around the 60° and 120° points respectively. This technique, however, is difficult to implement using analog devices and thus is rarely used. In the 3HIPWM technique (Fig. 2.10), the modulating waveform has been modified so that it is

$$y = 1.15 \sin \omega t + 0.19 \sin 3\omega t$$

(2.21)

and the pattern is obtained in the same manner as SPWM. It is important to note

Fig. 2.9. Modified SPWM for 60 Hz fundamental (a) MSPWM scheme. (b) Lineneutral waveform. (c) Line-line waveform (CSI pattern). (d) Fourier spectrum of line-line waveform.

Fig. 2.10. Third harmonic injection SPWM for 60 Hz fundamental (a) 3111PWM scheme. (b) Line-neutral waveform. (c) Line-line waveform (CSI pattern). (d) Fourier spectrum of line-line waveform.

that the ac gain of both of these techniques is increased to unity but at the cost of making the overall harmonic content worse.

## 2.8. Operation of CSI with an auxiliary switch

It is very difficult to implement carrier PWM patterns with shoot-through pulses using analog devices because the inverter switch gating signals cannot be obtained directly from the pattern without violating the general rules for CSI operation. Some procees must be carried out to construct the signals from the pattern. Since it is difficult to do this with analog devices, carrier PWM techniques can only be implemented by storing the gating signals in an EPROM as is done with SHE techniques. The use of an EPROM, however, takes away the benefits of using carrier PWM techniques because:

- (1) An EPROM can only store a limited number of PWM patterns.

- (2) If an EPROM is to be used then it is preferable to use SHE because it has a lower switching frequency. [31]

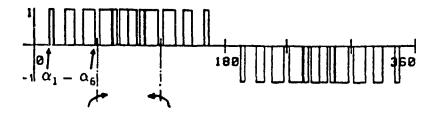

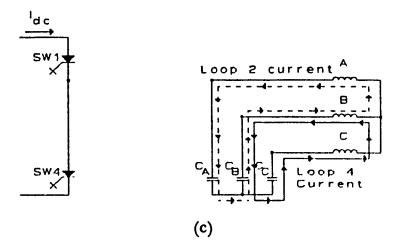

The benefits of carrier PWM techniques are best obtained when they are implemented using analog devices. In order to get these benefits, an auxiliary switch must be implemented in the dc link, external to the inverter because the gating signals of the switches can be easily derived from the pattern as is shown in Fig. 2.11 for typical CSI pattern. Fig. 2.11(a) shows the three-level switching function and Fig. 2.11(b) shows the gating signals for the top switch and bottom switch of an