National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

## NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser a désirer, surtout si les pages originales ont été dactylogra phiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

A Multichannel, Demand-Assignment Echo Canceller for Point-to-Multipoint Subscriber Radio Systems

Thanh-Son Nguyen

A Thesis

in

The Department

of

Electrical Engineering

Presented in Partial Fulfilment of the Requirements for the Degree of Master of Engineering at Concordia University

Montreal, Quebec, Canada

April, 1991

© Thanh-Son Nguyen, 1991

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-68746-0

#### ABSTRACT

A Multichannel, Demand-Assignment Echo Canceller for Point-to-Multipoint Subscriber Radio Systems

#### Thanh-Son Nguyen

Echo is a disturbing, but unavoidable phenomenon in any telephony network. Echo control devices are normally introduced at the subscriber interface points to reduce the round-trip delay. This arrangement requires M pairs of echo control devices where M, the number of subscribers, is much larger than N, the number of available trunks in Point-to-Multipoint (P-MP), Demand-Assignment Subscriber Radio systems. Also, due to dynamic trunk allocation of Demand-Assignment schemes, echo control devices need to adapt to different connected subscribers. Pursuing these objectives, various echo cancellation algorithms and structures are studied in this thesis.

The statistical approach based on the Block Least Mean Squares (BLMS), and the statistical behavior of trunks, is proposed. This approach is best suited to the dynamic trunk allocation of a P-MP system. Echo cancellation process is performed only on active trunks. The Multichannel, Demand-Assignment Echo Canceller (MCDAEC) is implemented, and its performances are evaluated.

#### **ACKNOWLEDGEMENT**

The author wishes to thank Dr. Tho Le-Ngoc for his guidance throughout the course of this research. His excellent characters, and his confidence in my fulfilling the project are grateful.

Special thanks also to the National Research Council for support in part this research work under the IRAP program. Thanks to my colleagues at SR Telecom Inc. for helping me at some critical moments, especially Mr. Djordje Konforti, who is now with BNR, for his Hardware design.

Lastly, I like to say thanks to my wife and my little boy, who share with me wonderful, sometimes frustrated moments. Thanks to my parents, brothers, and sisters for their supports in my early days.

## TABLE OF CONTENTS

| LIST OF FIGURES                                    |

|----------------------------------------------------|

| LIST OF TABLES                                     |

| CHAPTER 1. INTRODUCTION                            |

| CHAPTER 2. ECHO CONTROL TECHNIQUES & ALGORITHMS    |

| 2.1 Echo Control Methods                           |

| 2.1.1 Via Net Loss (VNL)                           |

| 2.1.2 Echo Suppressor                              |

| 2.1.3 Echo Cancellation                            |

| 2.2 Performance Criteria of an Echo Canceller1     |

| 2.3 Echo Cancellation Algorithms                   |

| 2.3.1 Least Mean Square (LMS) Algorithm            |

| 2.3.1.1 Derivation10                               |

| 2.3.1.2 Convergence20                              |

| 2.3.2 Least Squares (LS) Algorithm23               |

| 2.3.2.1 Derivation                                 |

| 2.3.2.2 Convergence29                              |

| 2.3.3 Modified Algorithms3                         |

| 2.3.3.1 Sign Algorithm (SA)3                       |

| 2.3.3.2 Block Least Mean Square (BLMS)3            |

| 2.3.3.3 Fast Recursive Least Square (FRLS)3        |

| 2.3.3.4 Fast Transversal Filters (FTF)3            |

| CHAPTER 3. ECHO CANCELLATION IN DA-, P-MP SYSTEMS3 |

| 3.1 System Description3                            |

| 3.2 Design Re quirements3                          |

| 3.2.1 System Requirements3                         |

| 3.2.2 Performance Requirements4                    |

| 3.3 Performance Evaluation of Echo Cancellation4   |

| 3.3.1 Least Mean Square (LMS) Algorithm4           |

| 3.3.1.1 General Algorithm4                         |

| 3.3.1.2 Complexity4                                |

| 3.3.1.3 Tracking Speed4                            |

|                                                    |

| vi                                                        |

|-----------------------------------------------------------|

| 3.3.2 The Block Least Mean Square (BLMS)45                |

| 3.3.2.1 Complexity45                                      |

| 3.3.2.2 Tracking Speed46                                  |

| 3.3.3 The Sign Algorithm46                                |

| 3.3.4 Least Squares (LS) Algorithm47                      |

| 3.3.4.1 General Algorithm47                               |

| 3.3.4.2 Complexity47                                      |

| 3.3.4.3 Tracking Speed48                                  |

| 3.3.5 Fast Recursive Least Square (FRLS)48                |

| 3.3.5.1 Complexity48                                      |

| 3.3.5.2 Tracking Speed49                                  |

| 3.4 Performance Evaluation of DSPs51                      |

| 3.4.1 The Oki Electric Family52                           |

| 3.4.2 The Nippon Electric Family54                        |

| 3.4.3 The AT & T Family55                                 |

| 3.4.4 The Texas Instrument TMS320 Family56                |

| 3.4.5 The Motorola DSP Family59                           |

| 3.5 A New Approach: The Statistical BLMS61                |

| 3.5.1 Simulation of the BLMS61                            |

| 3.5.2 The Statistical Approach67                          |

| CHAPTER 4. STRUCTURE OF THE MULTICHANNEL ECHO CANCELLER72 |

| 4.1 Hardware Configuration                                |

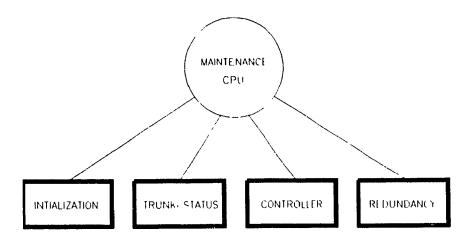

| 4.1.1 Maintenance CPU                                     |

| 4.1.1.1 Interfacing with the Controller74                 |

| 4.1.1.2 Interfacing with the DSPs76                       |

| 4.1.1.3 Initialization                                    |

| 4.1.1.4 Trunk Status Updating                             |

| 4.1.1.5 Controller Monitoring80                           |

| 4.1.1.6 Redundancy81                                      |

| 4.1.2 The Controller                                      |

| 4.1.2.1 Interfacing with the CPU81                        |

| 4.1.2.2 Interfacing with the DSPs82                       |

| 4.1.2.3 DSP Controller Maintenance83                      |

| vii                                         |

|---------------------------------------------|

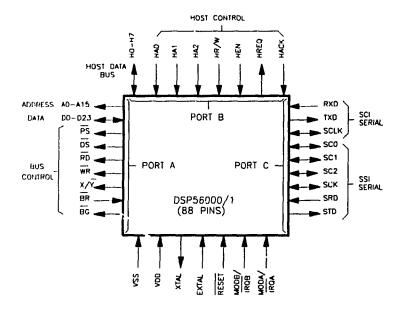

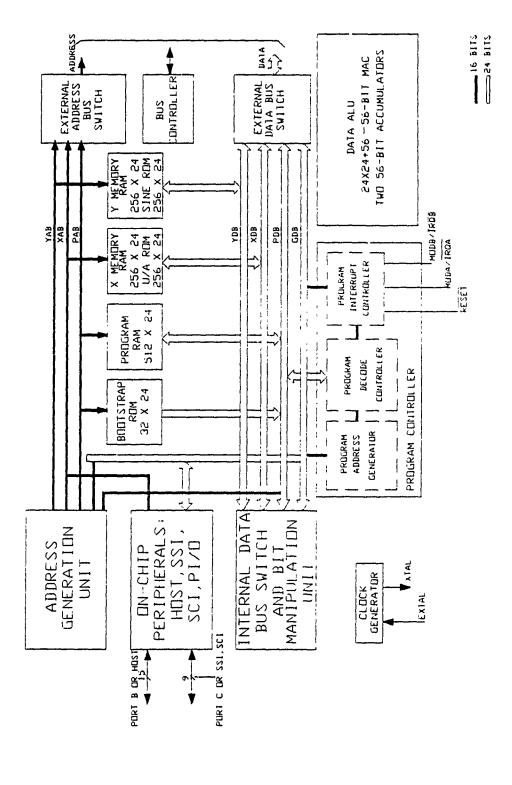

| 4.1.3 The DSPs84                            |

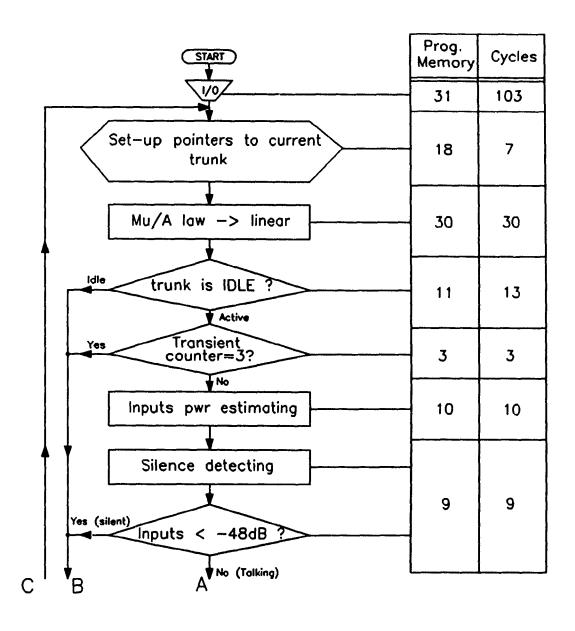

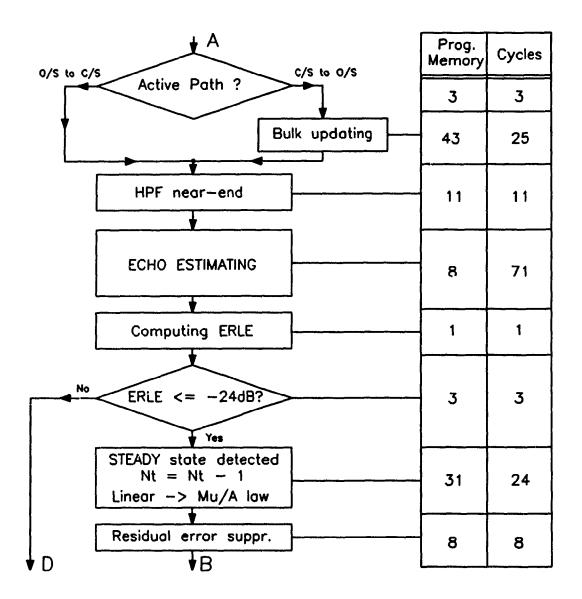

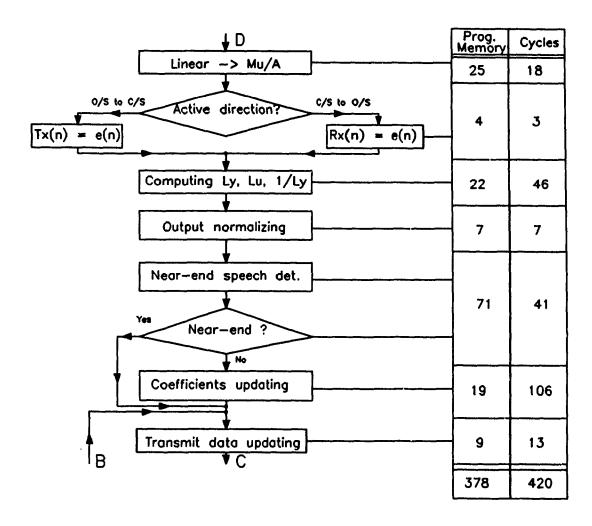

| 4.2 Software Configuration88                |

| 4.3 Performance Tests99                     |

| 4.3.1 Subjective Tests99                    |

| 4.3.2 Objective Tests101                    |

| CHAPTER 5. CONCLUSION106                    |

| REFERENCES108                               |

| APPENDIX A .A MEMORY MAP FOR ECHO CANCELLER |

| APPENDIX B .A FLOWCHART OF THE MCDAEC       |

| APPENDIX C .A PROGRAM LISTING OF THE MCDAEC |

## LIST OF FIGURES

| Figure                                             |

|----------------------------------------------------|

|                                                    |

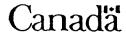

| 1. A typical Point-to-Multipoint system2           |

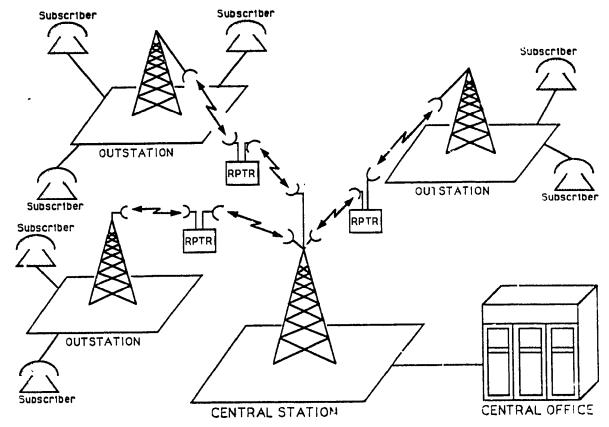

| 2. A typical Telephony network with echo6          |

| 3. Logical Structure of an Echo Suppressor8        |

| 4. Principle of Echo Cancellation9                 |

| 5. The Echo Canceller Model11                      |

| 6. Signal Processing Model of Echo Canceller18     |

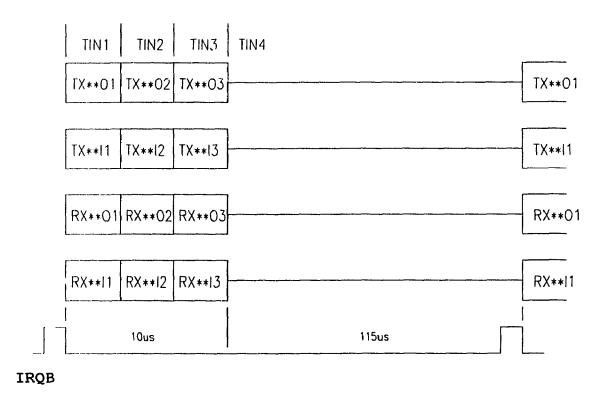

| 7. A Time Division Multiplex Structure35           |

| 8. A Simplified model to illustrate the location40 |

| of the MCDAEC in the Central station               |

| 9. A Model of The Echo Canceller Simulator62       |

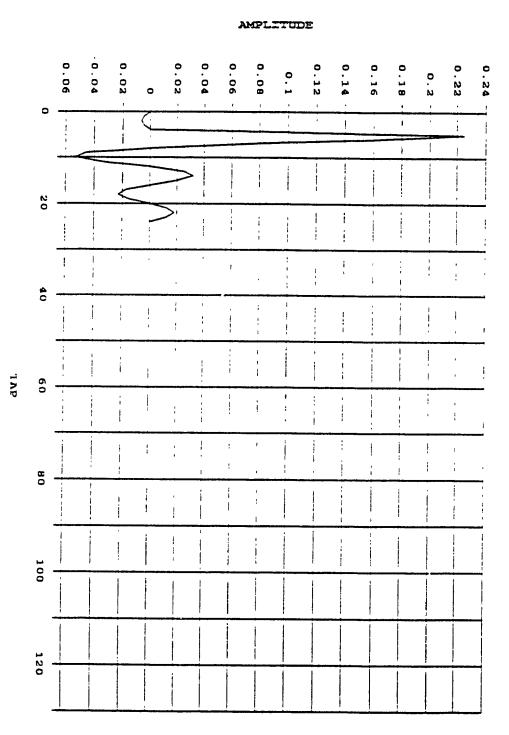

| 10. The Echo Path Impulse Response63               |

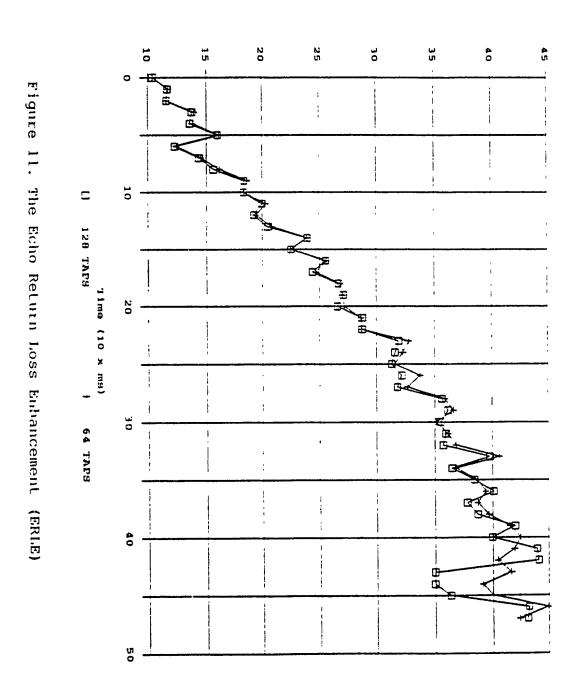

| 11. The Echo Return Loss Enhancement (ERLE)64      |

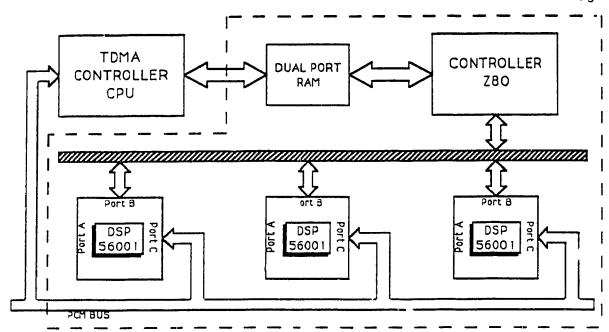

| 12.A simplified MCDAEC Block Diagram73             |

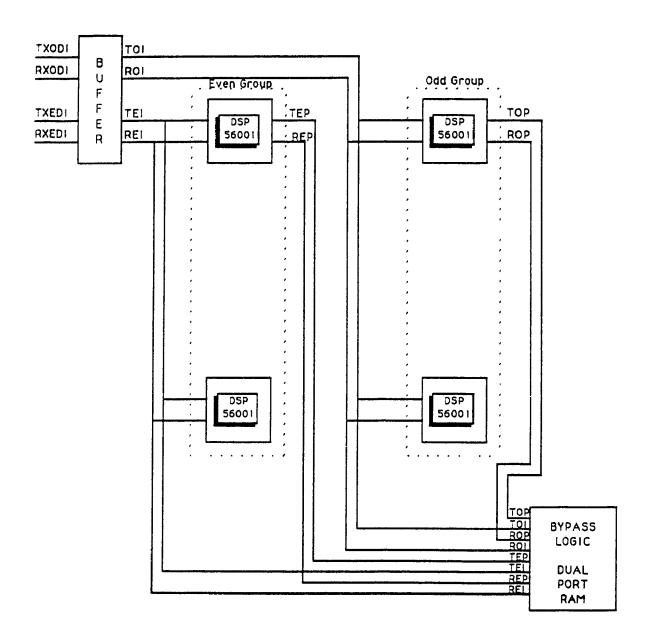

| 13.A Generalized Even/Odd PCM Structure77          |

| 14. Maintenance Functional Block Diagram           |

| 15.DSP56001 Functional Signal Group85              |

| 16.DSP56001 Architecture Block Diagram86           |

| 17. The MCDAEC Process90                           |

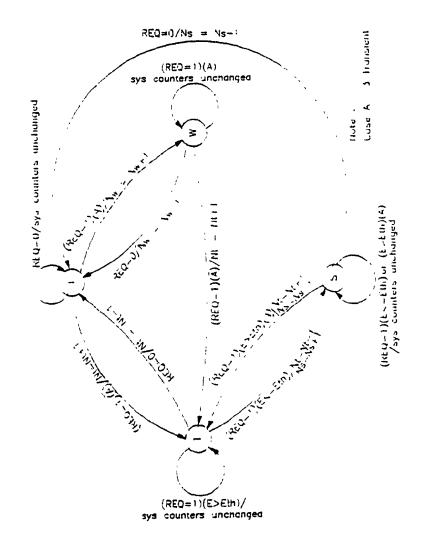

| 18. State Diagram for each channel91               |

| 19.Input/Output of the MCDAEC92                    |

| 20.A Test Set-Up100                                |

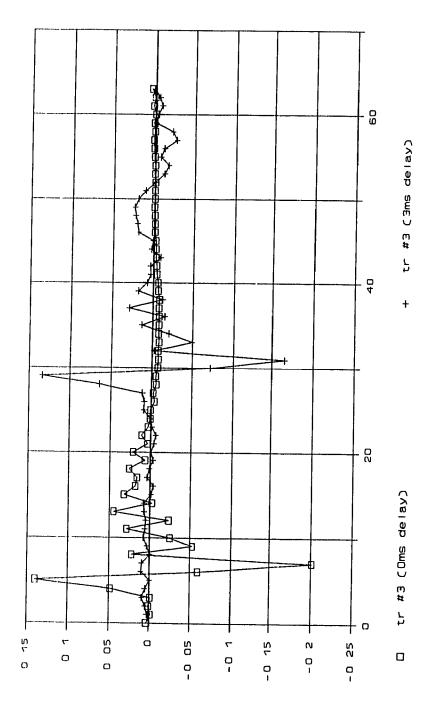

| 21. Adaptive Characteristic Test of the MCDAEC102  |

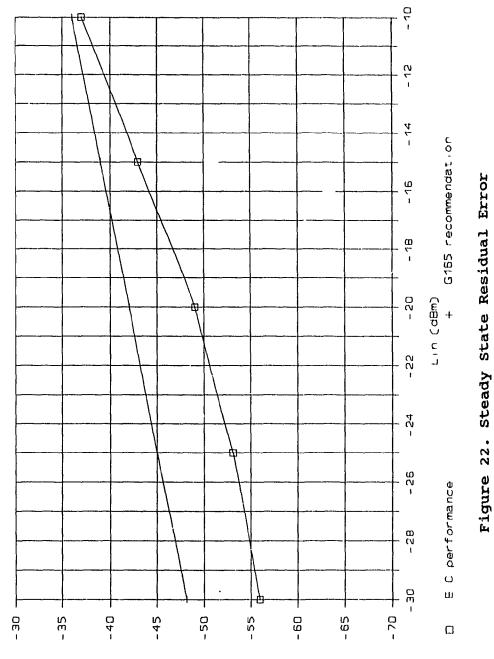

| 22. Steady State Residual Error103                 |

## LIST OF TABLES

| Table                                              | Page |

|----------------------------------------------------|------|

| 1. A Comparision of Echo Cancellation Algorithms . | 50   |

| 2. A Half-Duplex Echo Canceller Real-Time Analysis | 66   |

| 3. A System Real-Time Analysis                     | 71   |

| 4. Dual-port RAM Memory Map                        | 75   |

| 5. CPU Commands                                    | 75   |

| 6. Echo Canceller Status                           | 76   |

| 7. State transition                                | 94   |

#### CHAPTER 1

#### INTRODUCTION

Point-to-Multipoint (P-MP) Subscriber Radio systems have been widely used for services in rural, and suburban areas where conventional telephony applications may be costly, and inefficient in terms of maintenance. All P-MP systems share a common feature in having a Central station (C/S), and a number of Outstations (O/S).

Fig.1 shows a typical configuration of a P-MP subscriber radio system. An efficient Random-Request, Demand-Assignment, Time-Division Multiple-Access (RR-DA-TDMA) protocol [1] is used to provide services to M subscribers with N channels (or trunks) where M >> N on a demand basis. When a burst randomly requested by an O/S is received, the C/S will acknowledge the requesting station, and assign it an available traffic trunk. The traffic trunk can be data, PCM, or ADPCM. Due to the grouping voice samples in TDMA a nature of t.ne system. The transmission introduced in delay is transmission delay also increases with the number of inserted repeaters. This delay may increase the annoying effect of echo.

Echo is generated at any point where the speech signal encounters a mismatch in impedance. Essentially, all significant echoes are produced at the hybrid which acts as a two-wire to four-wire interface in a subscriber radio system.

The deleterious effects of such echoes depend upon their

Figure 1. A typical Point-to-Multipoint system loudness, signal distortion, and system delay. Generally speaking, the more echo is delayed, the more it is untolerable. The annoying effect of echo in the extreme case where the total round trip delay may exceed 30ms motivates a need for finding means to combat this problem.

Echo control devices are normally introduced at the subscriber interface points to reduce the echo path delay. This arrangement requires M pairs of echo control devices where M, the number of subscribers, is much larger than N, the number of available trunks in a DA, P-MP system. In a DA system, traffic trunks will be assigned upon receiving

requests by subscribers. Therefore, for economic reasons, it is more desirable to have a *Group Echo Control Device* operating on a trunk basis. This *Group Echo Control Device* is equivalent to a maximum of N pairs of trunk Echo Control devices. Also, due to the dynamic trunk allocation of DA schemes, echo control devices need to adapt to different connected subscribers. This is the motivation of the research on a *Statistical Multichannel*, *Demand-Assignment Echo Canceller* reported in this thesis.

The main objectives of this research are to study algorithms and structures of Statistical Multichannel, Demand-Assignment Echo Canceller suitable for P-MP systems. Pursuing these objectives, this research covers the following points:

- (i) Performance comparison of various Echo Cancellations in terms of complexity, convergence speed.

- (ii) Introduction of a statistical approach to design the Multichannel, Demand-Assignment Echo Canceller.

- (iii) Implementation and performance evaluation of the introduced Multichannel, Demand-Assignment Echo Canceller.

The thesis consists of five chapters. After this introduction, chapter 2 presents a review of Echo control methods and their performance. Via Net Loss (VNL), a technique which inserts loss in the transmission path, was first used to cancel the echo. The inefficiency of this method when applied in long-circuit network lead to the invention of echo

suppressor. Description of the echo suppressor will identify the lack of performance of this technique in double-talk situation. This leads to the concept of echo cancellation. Both the Least Mean-Squared (LMS), and Least Squares (LS) are discussed.

Chapter 3 describes the configuration of a P-MP subscriber radio system with an emphasis on the echo cancellation problem. Particular design parameters such as location of echo cancellers, echo path delay will be identified. The selection of suitable Echo Cancellation algorithms, and DSPs is discussed. Computer simulations based on deterministic approach are carried out to investigate the convergence speed of the selected echo cancellation algorithm. The statistical approach is proposed to increase the number of trunks per DSP. This approach is based on the statistical behavior of trunks that the probability of trunks activated at the same time is negligible.

Chapter 4 describes the implementation of the proposed Multichannel, Demand-Assignment Echo Canceller based on the statistical approach. Hardware and Software designs will be described along with test results.

Finally, chapter 5 presents the conclusion.

#### CHAPTER 2

## ECHO CONTROL TECHNIQUES & ALGORITHMS

Known echo control devices such as Via Net Loss, Echo Suppressor find their applications in many circuits. With the evolution of VLSI and DSP technologies echo canceller, the most recent echo control device, is widely used due to its high performance in echo cancellation, and double-talking situation. Following in this chapter we present a performance comparison of echo control devices, and also an analysis of echo cancellation algorithms.

#### 2.1 Echo Control Methods

With rare exceptions, all conversations take place in the presence of echo. Echo is a phenomenon in which one's speech reflected to him/her after some delay time due to impedance mismatch at the termination end. The effect of echo becomes more prorounced as the time delay between the speech and echo increases. Fig.2 shows a typical connection via a network where echoes are generated by the impedance mismatch, and imperfect isolation at the hybrids B, and A. To combat the effect of echo many approaches have been employed. In the following sub-sections we examine Echo Control methods such as Via Net Loss (VNL), Echo Suppressor, and Echo Cancellation.

#### 2.1.1 Via Net Loss (VNL):

Introduced in the early days of Echo Controlling, this technique inserts loss at both ends of the transmission paths to attenuate echo. The Vall has found its application in short circuit networks where delay is short, and the insertion loss is acceptable. In long circuit, however, the VNL degrades the system's performance because high insertion loss may block speech signals from one subscriber to another [2].

Figure 2. A typical Telephony network with echo

#### 2.1.2 Echo Suppressor:

The drawback of the VNL leads to the invention of Echo Suppressor. It was noted that most conversations consist of single talking, i.e one person speaks at a time. Under this

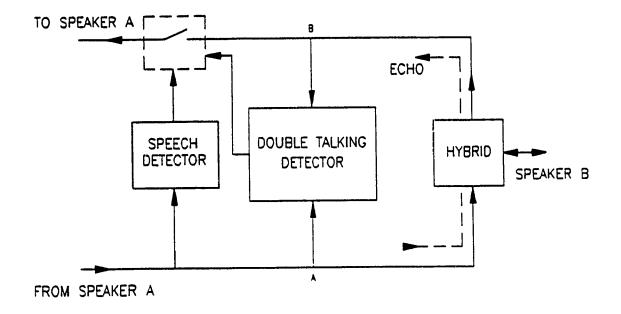

condition, echoes which return to the talker, are not mixed with desired signal, and therefore can be removed from the circuit by introducing a loss in the current transmission path. This echo control method is called Echo Suppressor. As shown in Fig. 3 the switch is activated upon detecting the A's signal. This switch will pass speaker A's signal, and blocks all returning signal from speaker B. Under this scheme it is apparent that Echo Suppressor may interfere with normal conversations when both subscribers speak at the same time, i.e double-talking. When the device is fully effective against echoes, it modifies the transmission system so that it is no longer a full-duplex link capable of carrying information in both directions simultaneously. Instead, it approaches a half-duplex system which can be used in either one direction or the other, but not in both at once. An operating Echo Suppressor must accomplish one major goal : removal of perceptible echo with minimum degradation of desired speech. An obvious problem with Echo Suppressor is that switch detection may not be fast enough when talking direction changes all the time. Modern Echo Suppressor is designed to improve this performance by introducing hang-over time. Such an Echo Suppressor is described by M.M. Sondhi and D.A. Berkley [2].

In a single-talk situation, signal at point A will cease following the transmission delay when speaker A stops talking. Because of the end delay, echo may be produced even after

speaker A stops talking. To prevent this, the switch as shown

Figure 3. Logical Structure of an Echo Suppressor

in Fig.3 will not be released until a certain time called hang-over time. This hang-over time must exceed the end delay. By introducing this hang-over time the switch detection can be relaxed. However, a hang-over time in excess of a few milliseconds may prevent transmission of B's speech if speaker B begins talking shortly after A is heard to stop. An Echo Suppressor is not satisfatory for the following reasons:

- It may clip, and chop speech or data signals.

- It does not provide good echo control during doubletalk.

- It requires switch control during signaling, and in tandem connection.

• It may effect touch-tone signaling when dial tone sent from the incoming switch system is being received.

### 2.1.3 Echo Cancellation :

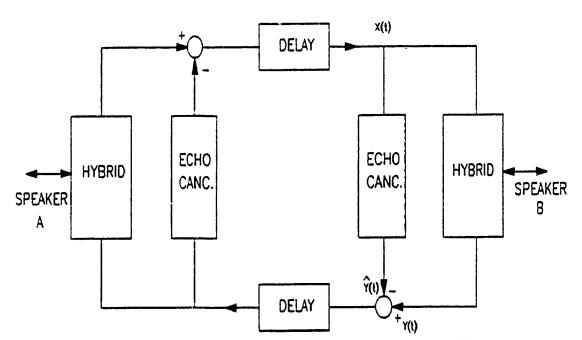

Emerged in the sixties, Echo Cancellation soon became recognized as the best technique of Echo control. As shown in Fig.4 it operates on the principle of adaptive modeling of the echo signal, and subsequently cancels the estimated echo in the received signal, thus leaving the speech paths unaffected.

Figure 4. Principle of Echo Cancellation

While the concept of Echo Cancellation may seem simple "To remove the echo, subtract it" it involves some difficulties as follows:

#### (i) Adaptive Modelling

Echo path is unknown, varied and must be identified and modelled. Using adaptive technique as shown in Fig.4 an estimated model of the impulse response of the actual echo path is generated. Normally, it is assumed that the echo path is linear, and time-invariant [3]. Under these assumptions, the return signal y(t) to the telephone A in Fig.4 can be expressed as:

$$y(t) = h(t) * x(t) + v(t)$$

(2.1)

where:

- x(t) is the far-end speech from telephone A.

- v(t) is the near-end speech from telephone B.

- h(t) is the impulse response of the echo path.

The function of the Echo Canceller box in Fig.4 is to estimate h(t) by  $\hat{h}(t)$ . The ideal case is when  $h(t) = \hat{h}(t)$ , i.e echo path response is perfectly estimated.

#### (ii) Double-talk detection

A major improvement compared with Echo Suppressor is the performance of Echo Canceller in presence of double-talk. Instead of blocking the far-end speech from returning to the talker, the Echo Canceller is transparent, i.e returning signal consists of both echo and near-end signals.

Different Echo Cancellation algorithms have been derived, and will be discussed in detail in section 2.3. We now examine the performance criteria of Echo Canceller.

## 2.2 Performance Criteria of an Echo Canceller:

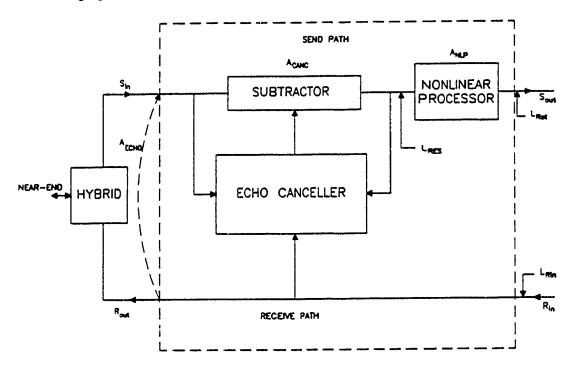

The CCITT G.165 Recommendation [4] specifies the required performance, and measured parameters of an Echo Canceller. Using the model of an Echo Canceller in Fig.5 we define the following parameters:

Figure 5. The Echo Canceller Model

# (a) Echo Loss (A echo ):

This is the attenuation of a signal from the receive-out port (Rout), to the send-in port (Sin) of an Echo Canceller, due to transmission and hybrid loss, i.e. the loss in the echo path.

# (b) Cancellation (A canc ):

This is the attenuation of the echo signal as it passes

through the send path of an Echo Canceller. This attenuation excludes the attenuation due to nonlinear processor.

# (c) Residual Echo Level (L Res ) :

This is the level of the echo signal at the send-out port of an operating Echo Canceller after cancellation of the circuit signal.

It is related to L by:

$$L_{Res} = L_{Rin} - A_{echo} - A_{canc}$$

(2.2)

Any nonlinear processor is not included.

### (d) Nonlinear processor (NLP) :

It is a device having a defined suppression threshold level and in which:

- signals with a detected level as being below the threshold are suppressed.

- signals with a detected level as being above the threshold are passed although the signal may be distorted.

# (e) Nonlinear processor loss (Anlp):

Additional attenuation of residual echo level by a nonlinear processor placed in the send path of an Echo Canceller.

# (f) Returned Echo level (L Ret ) :

The level of the signal at the send-out port of an operating Echo Canceller which will be returned to the

talker.

$$L_{Res}$$

is related to  $L_{Rin}$  by

$$L_{Ret} = L_{Rin} - (A_{echo} + A_{canc} + A_{nlp})$$

(2.3)

#### (q) Convergence time:

For a defined echo path, the interval between the instant a defined test signal is applied to the receive-in port of an Echo Canceller with the estimated echo path impulse response initially set to zero, and the instant the returned echo level at the send- out port reaches a defined level.

As explained in section 2.1.3, an Echo Canceller must be able to synthesize a replica of the echo path impulse response. This impulse response typically spans a time interval of the order of 2ms to 5ms. Following are the fundamental requirements of an Echo Canceller:

- (i) Rapid convergence: the echo paths change as the Echo Canceller is used in successive connections. Under these conditions the requirement is that the Echo Canceller should converge within 500ms.

- (ii) Subjective low returned echo level during single talk: residual echo level should be small regardless of the level of the receive speech, and the characteristics of the echo path. Typical Echo Canceller for voice cancellation has a residual echo level of -30dB (including the hybrid loss of 6dB).

- (iii) Low divergence during double-talk : when both

subscribers speak at the same time, the Echo Canceller may interpret the transmit signal \_\_ a new echo path, and try to adapt to it. It is desirable that very little divergence occurs while this is taking place.

#### 2.3 Echo Cancellation Algorithms :

As discussed earlier, the principle of Echo Cancellation is to generate a replica of echo, and to remove it from the received signal. To obtain this most algorithms employ what is called the adaptive estimation process. An initial guess of tap weights are made, and the residual error is calculated based on these values. In the next iteration, the tap weights are adjusted in such a way that as k (number of iterations) approaches infinity the residual error becomes negligible. At this stage, we say the algorithm converges. Two basic processes can be summarized in adaptive filter:

- The echo cancelling process which involves obtaining a replica of the desired response, and generating an estimation error by comparing the estimate with the actual value of the desired response.

- The coefficient updating process which involves the automatic adjustment of the filter coefficients in accordance with some algorithms. Algorithms for carrying out these two processes are: the Least Mean Squares (LMS), and the Least Squares (LS). The LMS minimizes mean-squared error, whereas

the LS approach is to minimize the sum of mean-squared errors.

Both approaches have different convergence characteristics.

Discussion of these algorithms focuses on the following points

- Derivation of the algorithm.

- Discussion of the convergence behavior.

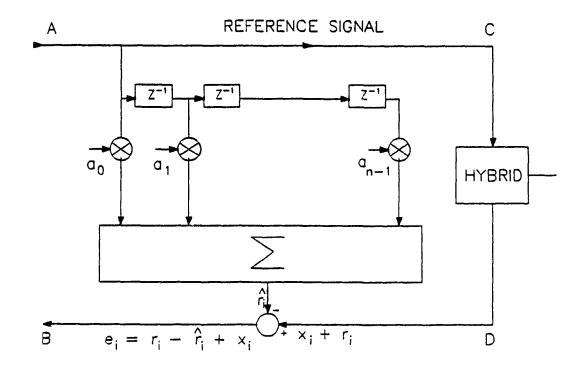

Signal processing model for both algorithms is shown in Fig.6. In this figure :

- a is the transversal filter coefficient vector.

- h is the echo path response coefficient vector.

- x is the far-end signal vector.

- y is the desired response vector.

- $\hat{\mathbf{v}}$  is the estimate of the desired response vector.

- e is the residual error vector.

- N is the length of the transversal vector.

Two assumptions are made in Echo Canceller:

- the echo path is linear.

- the echo path is time-invariant.

Because of these assumptions, the desired response can be expressed as a linear combination of filter coefficients and time delay. We begin the discussion with the LMS algorithm.

## 2.3.1 Least Mean Square (LMS) Algorithm

Based on the steepest descent method, the Least Mean Square (which is also called stochastic gradient) is derived

to minimize mean-squared error by updating weight vector in accordance with incoming data. Because it is simple (no matrix computation is required) it is implemented in most of the existing adaptive filters.

### 2.3.1.1 Derivation of the LMS algorithm

As shown in Fig.6:

$$e(k) = y(k) - \hat{y}(k)$$

(2.4)

where the estimated signal y(k) can be expressed as a convolution of input sequence x(k), and the transversal filter coefficients:

$$\begin{array}{l}

^{\circ} \quad N-1 \\

y(k) = \sum_{i=0}^{\infty} a(i) \ x(k-i) \\

i=0

\end{array}$$

(2.5)

Expressing as a vector inner product the above relation can be rewritten as:

$$\hat{\mathbf{y}}(\mathbf{k}) = \mathbf{a}^{\mathbf{T}}(\mathbf{k})\mathbf{x}(\mathbf{k}) \tag{2.6}$$

where :

$$\mathbf{a}^{\mathrm{T}}(\mathbf{k}) = (a_0(\mathbf{k}), a_1(\mathbf{k}), \dots, a_{N-1}(\mathbf{k}))$$

(2.7)

$$\mathbf{x}^{T}(k) = (x(k), x(k-1), \dots, x(k-N+1))$$

(2.8)

Substituting equation (2.6) in (2.4) yields:

$$e(k) = y(k) - a^{T}(k) x(k)$$

The squared err r is:

$$e^{2}(k) = (y(k) - \mathbf{a}^{T}(k) \mathbf{x}(k))^{2}$$

$$= y^{2}(k) + (\mathbf{a}^{T}(k)\mathbf{x}(k))^{2} - 2y(k)\mathbf{a}^{T}\mathbf{x}(k)$$

(2.9)

Assuming x(k) and y(k) are wide-sense stationary we can write

$$e^{2}(k) = y^{2}(k) + (a^{T}(k)x(k)x^{T}(k)a(k)) - 2 a^{T}(k)\phi_{XY}(k)$$

$$= y^{2}(k) + a^{T}(k) *_{XX}(k) a(k) - 2 a^{T}(k)\phi_{XY}(k) \qquad (2.10)$$

where:

$\Phi_{XX}(k) = (\mathbf{x}(k) \ \mathbf{x}^T(k))$  is the (N x N) autocorrelation matrix.  $\Phi_{XY}(k) = (\mathbf{x}(k) \ y(k))$  is the (N x 1) cross correlation matrix. The mean-squared error (MSE) is:

$$\epsilon(k) = E[e^2(k)]$$

=

$$E[y^2(k)] + a^T(k) = xx(k) a(k) - 2 a(k) \phi x(k)$$

(2.11)

The MSE function has a quadratic form in the estimated filter coefficients a, and the minimum can be obtained by setting the gradient  $\nabla$  to zero.

$$\nabla(\mathbf{k}) = \partial \epsilon(\mathbf{k}) / \partial \mathbf{a}(\mathbf{k}) = [\partial \epsilon / \partial \mathbf{a}_{0}(\mathbf{k}), \partial \epsilon / \partial \mathbf{a}_{1}(\mathbf{k}), \dots, \partial \epsilon / \partial \mathbf{a}_{N-1}(\mathbf{k})]$$

$$= 2 \sum_{\mathbf{x} \mathbf{x}} (\mathbf{k}) \mathbf{a}(\mathbf{k}) - 2 \phi_{\mathbf{x} \mathbf{y}}(\mathbf{k}) \qquad (2.12)$$

The optimum tap weight vector which minimizes the MSE is the solution to a set of N simultaneously linear equations called Wiener equation:

$$\mathbf{a}_{xx}(k) \mathbf{a}_{opt}(k) = \phi_{xy}(k) \tag{2.13}$$

Figure 6. Signal Processing Model of Echo Canceller

The Wiener equation (also called a normal equation) can be solved by "sing either Gaussian or Levinsion recursion where a fixed number of calculations is required [5]. As shown in equation (2.13) the computation of the optimum tap-weight vector  $\mathbf{a}_{\mathrm{opt}}(\mathbf{k})$  requires knowledge of two quantities:

- (i) The autocorrelation of the input signal.

- (ii) The cross correlation of the input signal, and the desired response.

Solution for obtaining the optimum tap-weight vector using this method is computationally difficult, especially when the number of taps is large. Adaptive technique based on steepest-descent method can also be employed to solve this equation. The steepest descent algorithm obtain the optimum tap-weight vector by using the following steps:

- (i) Make an initial guess of the tap-weight vector a(0).

- (ii) Compute the gradient vector  $\nabla$  as expressed in equation (2.12).

- (iii) Update the tap-weight vector by changing the present value of the tap-weight vector in negative direction of the gradient vector.

The steepest descent method is represented by :

$$a(k+1) = a(k) - \mu \nabla(k+1)$$

(2.14)

(iv) Go back to step (ii), and repeat the process.

The vector  $\mathbf{a}(k+1)$  and  $\nabla$  (k+1) represent the estimated coefficients of the optimum tap-weight vector, and the gradient at sample time k+1, respectively. The gradient  $\nabla(k)$  as represented in (2.12) can be expressed in different form as  $\nabla(k) = \delta \mathbf{E} \left[ (\mathbf{y}(k) - \mathbf{a}(k) \times (k))^2 \right] / \delta \mathbf{a}$

$$= \delta E [y(k)^{2} + \mathbf{a}^{T}(k) \mathbf{x}(k) \mathbf{x}^{T}(k) \mathbf{a}(k) - 2y(k)\mathbf{a}^{T}(k)\mathbf{x}(k)] / \delta \mathbf{a}$$

$$= -2E [\mathbf{x}(k) (y(k) - \mathbf{a}^{T}(k) \mathbf{x}(k))] \qquad (2.15)$$

The LMS recursive equations are :

$$e(k+1) = y(k+1) - a^{T}(k) x(k+1)$$

(2.16)

$$a(k+1) = a(k) + 2\mu x(k+1) e(k+1)$$

(2.17)

#### 2.3.1.2 Convergence

The LMS algorithm requires that the estimated impulse response a(k) reaches optimum a optafter a number of iterative processes.

Substituting

$$e(k+1) = y(k+1) - a^{T}(k) x(k+1)$$

into (2.17):

$a(k+1) = a(k) + 2\mu x(k+1) (y(k+1) - a^{T}(k) x(k+1))$  (2.18)

Taking expected values of both sides of (2.18) gives :

$$E[\mathbf{a}(k+1)] = E[\mathbf{a}(k) + 2\mu \mathbf{x}(k+1) \{y(k+1) - \mathbf{a}^{T}(k)\mathbf{x}(k+1)\}]$$

(2.19)

$$= E[\mathbf{a}(k) + 2\mu \mathbf{x}(k+1)y(k+1) - 2\mu \mathbf{x}(k+1) \mathbf{a}^{T}(k) \mathbf{x}(k+1)]$$

$$= E[\mathbf{a}(k)] [(\mathbf{I} - 2\mu\mathbf{x}(k+1)\mathbf{x}^{T}(k+1)] + 2\mu E[\mathbf{x}(k+1)y(k+1)]$$

$$= (\mathbf{I} - 2\mu \mathbf{x}(k)) E[\mathbf{a}(k)] + 2\mu \phi_{\mathbf{x}y}(k)$$

(2.20)

Assuming the input signal, and the desired response are uncorrelated:

$$\phi_{XY}(k) = 0$$

Equation (2.20) is simplified to :

$$E[a(k+1)] = E[a(k)] (I - 2 \mu \cdot \frac{1}{2}xx(k))$$

Defining the weight vector error at time k as :

$$\ddot{\mathbf{a}}(\mathbf{k}) = \mathbf{a}(\mathbf{k}) - \mathbf{a}_{\text{opt}} \tag{2.21}$$

where :

a(k) is the estimated tap-weight value at time k.

a opt is the optimum tap-weight value.

So :

$$E[\bar{a}(k+1)] = E[\bar{a}(k)] (I - 2 \mu \Phi_{xx}(k))$$

(2.22)

The autocorrelation can be rewritten as:

where:

Q is the unitary matrix which has a property that its transpose is equal to its inverse, and whose columns are eigenvectors of the autocorrelation  $\bullet$  (k).

$\Lambda$  is the diagonal matrix whose diagonal elements are eigenvalues of the autocorrelation  $\P$  (k). These eigenvalues are all positive, and real.

Substituting (2.23) in (2.22) :

$$E[\tilde{\mathbf{a}}(k+1)] = E[\tilde{\mathbf{a}}(k)](I - 2\mu Q \Lambda Q^{T}) \qquad (2.24)$$

To simplify the notation let ignore the expectation operator. Multiply both sides of (2.24) by Q:

$$Q^{T} \tilde{\mathbf{a}}(k+1) = Q^{T}(\mathbf{I} - 2\mu \ Q \ \Lambda \ Q^{T}) \tilde{\mathbf{a}}(k)$$

(2.25)

Using property of the unitary matrix :

$$\mathbf{Q}^{\mathrm{T}}\tilde{\mathbf{a}}(\mathbf{k}+1) = (\mathbf{I} - 2\mu \Lambda)\mathbf{Q}^{\mathrm{T}}\tilde{\mathbf{a}}(\mathbf{k})$$

(2.26)

Define :

$$v(k) = Q^{T}\tilde{a}(k)$$

Equation (2.26) can be rewritten as:

$$v(k+1) = (I - 2\mu \lambda_k) v(k)$$

(2.27)

By assuming an initial value of tap-weight vector as zero, and deducting (2.27) we obtain the general expression for  $\nu$  at time k is:

$$v_n(k+1) = (1 - 2\mu \lambda_n)^k v_n(k)$$

(2.28)

This has the form of a geometric series with a geometric ratio of  $(1-2\mu\lambda_n)$ .

For stability or convergence of the algorithm it is required that  $-1 < 1 - 2\mu\lambda_n$ ) < 1, or

$$0 < \mu < 1/\lambda_{max} \tag{2.29}$$

where  $\lambda_{\text{max}}$  is the largest eigenvalue of the autocorrelation  $\blacksquare$

## 2.3.2 Least Squares (LS) algorithm :

LS algorithm minimizes sum of squared errors. Both LS's derivation, and convergence behavior are given.

## 2.3.2.1 Derivation of LS algorithm :

In Fig.5 the residual error at sampling time k is expressed as

$$e(k) = y(k) - \sum_{i=0}^{N-1} a(i)x(k-i-1)$$

(2.30)

where a(i)'s are unknown parameters of the model, and y(k) is

the desired response. In a shorter form the above equation can be rewritten as :

$$e(k) = y(k) - \hat{y}(k)$$

(2.31)

with:

$$\hat{\mathbf{y}}(\mathbf{k}) = \sum_{i=0}^{N-1} \mathbf{a}(i) \mathbf{x}(\mathbf{k}-i-1)$$

The LS method minimizes sum of squared errors. In other words, we choose the tap weights a(k)'s such that the sum of squared errors is minimum.

$$\begin{array}{c|c}

i2 \\

\Sigma \\

i=i1

\end{array}$$

(2.32)

In equation (2.32) the i1, and i2 define the index limits at which the error minimization occurs. The values of i1 & i2 depend on the type of windowing methods. There exists four different methods of windowing [5].

(a) Covariance Method: which makes no assumption about the data outside the interval (i,M) with il = N, i2 = M, where N is the number of tap weights, and M is any arbitrary number such that  $M \ge N$ . The input data can be arranged in the matrix form as:

$$x(N-1)$$

$x(N)$  ....  $x(M)$

$$x(N-2)$$

$x(N-1)$  ....  $x(M-1)$

•• •• ••• ••

$$x(1)$$

$x(2)$  ....

$$x(0)$$

$x(1)$   $x(M-N+1)$

(b) Autocorrelation Method which makes the assumption that data prior to time i=1, and the data after i=M are zero. By using i1=1, and i2=M+N-1 the input data can be taken on the form :

$$x(1)$$

$x(2)$  ...  $x(N)$  ...  $x(M)$  ... 0 ... 0

$x(1)$  ...  $x(N-1)$  ...  $x(M-1)$  ...  $x(M)$  ... 0

... 0 ... ... 0

$x(1)$  ...  $x(M-1)$  ...  $x(M)$  ... 0

$x(1)$  ...  $x(M-1)$  ...  $x(M)$  ... 0

(c) Prewindowing Method which makes the assumption that the input data prior to i=1 are zero but makes no assumption about the data after i=M. The matrix of input data takes on the form :

$$x(1)$$

$x(2)$  .....  $x(N)$   $x(N+1)$  .....  $x(M)$

$0$   $x(1)$  .....  $x(N-1)$   $x(N)$  .....  $x(M-1)$

$0$   $0$  ..... .... ...

$0$   $0$  ..... .... ...

$0$   $0$   $x(1)$   $x(2)$   $x(M-N+1)$

(d) Postwindowing Method which makes no assumption about the data prior to time i=1, but assumes that the data after i=1 M are zero in the following form :

$$x(N)$$

$x(N+1)$  ....  $x(M)$  0 .... 0

$x(N-1)$   $x(N)$  ....  $x(M-1)$   $x(M)$  0

... ... 0

$x(1)$   $x(2)$   $x(M-N+1)$   $x(M-N)$  ...  $x(M)$

The derivation of the LS equation is carried out using the covariance windowing method. Other methods are given in [5]. As previously mentioned, the problem we have to solve is to determine a set of tap weights a(k)'s for which the sum of squared errors is minimum.

The residual error is:

$$e(k) = y(k) - a^{T}(k) x(k)$$

(2.33)

By expressing residual error e(k), and the desired response y(k) as elements of (M-N+1) by 1 vectors as follows:

$$\epsilon^{\mathrm{T}} = [e(N), e(N+1), \dots, e(M)]$$

, where  $M \ge N$  (2.34)

$$\mathbf{b}^{\mathrm{T}} = [y(N), y(N+1), \dots, y(M)]$$

(2.35)

then equation (2.33) can be rewritten as:

$$\epsilon^{\mathrm{T}} = \mathbf{b}^{\mathrm{T}} \cdot \mathbf{a}^{\mathrm{T}} \{ \mathbf{x}(\mathbf{N}), \mathbf{x}(\mathbf{N}+1), \dots, \mathbf{x}(\mathbf{M}) \}$$

$$\epsilon^{\mathrm{T}} = \mathbf{b}^{\mathrm{T}} - \mathbf{a}^{\mathrm{T}} \mathbf{A} \tag{2.36}$$

where:

$$\mathbf{A}^{\mathrm{T}} = [\mathbf{x}(\mathbf{N}), \mathbf{x}(\mathbf{N}+1), \dots, \mathbf{x}(\mathbf{M})]$$

Applying the Hermitian property of equation (2.36)

$$\epsilon = \mathbf{b} - \mathbf{a} \, \mathbf{A} \tag{2.37}$$

Expressing equation (2.32) in the other form using matrix representation of residual error e(k):

$$\sum_{i=N}^{M} |e(k)|^2 = \epsilon \epsilon \qquad (2.38)$$

Substituting equations (2.36), and (2.37) in (2.38) yields:

$$= \mathbf{b}^{\mathrm{T}}\mathbf{b} - \mathbf{b}^{\mathrm{T}}\mathbf{A} \mathbf{a} - \mathbf{a}^{\mathrm{T}}\mathbf{A}^{\mathrm{T}}\mathbf{b} + \mathbf{a}^{\mathrm{T}}\mathbf{A}^{\mathrm{T}}\mathbf{A} \mathbf{a}$$

Differentiating  $\Sigma |e(k)|^2$  with respect to a:

$$\delta \xi / \delta \mathbf{a} = -2\mathbf{A}^{\mathrm{T}} \mathbf{b} + 2\mathbf{A}^{\mathrm{T}} \mathbf{A} \mathbf{a}$$

$$= -2\mathbf{A}^{\mathrm{T}} \{ \mathbf{b} + \mathbf{A} \mathbf{a} \}$$

$$= -2\mathbf{A}^{\mathrm{T}} \epsilon$$

(2.40)

As before, denoting  $\mathbf{a}_{\text{opt}}$  as the optimum tap weight vector for which the sum of error squares is minimum, i.e  $\delta \xi/\delta \mathbf{a}=0$ . It follows:

$$\mathbf{A}^{\mathrm{T}}\mathbf{A} \ \mathbf{a}_{\mathrm{opt}} = \mathbf{A}^{\mathrm{T}} \ \mathbf{b} \tag{2.42}$$

Recall that A and b represent the inputs of the transversal filter, and the desired response, respectively. From the definitions of cross-correlation and autocorrelation equation (2.42) can be expressed in the following form:

Equation (2.43), which represents the LS estimate, is analogous to the Wiener equation as in the LMS algorithm. In many applications, we have to reconstruct (2.40), and to resolve it as new data becomes available. This approach is computionally expensive since matrix calculation is involved. For practical reasons, a Recursive Least Squares (RLS) algorithm is often used. In RLS the tap weight at sample time

k is recursively estimated based on previous tap value at time (k-1), and the new data x(k) and y(k).

A weighting factor is usually introduced into the sum of squared errors of equation (2.38). This factor is to fade out the past data, and one form of weighting used is the exponential function defined by:

$$w(k,i) = \lambda^{k-i}$$

,  $i = 1, 2, ..., k$

where  $0 < \lambda < 1$ .

Equation (2.38) is rewritten with the introduction of the weighting factor as:

$\Sigma w(k,i) | e(k)^2 |$

Correspondingly, we define :

$$\phi \quad (k) = \sum_{i=1}^{k} \lambda \quad \mathbf{x}(i) \quad y(i)$$

(2.45)

Taking the term i = k out of the summation, equation (2.44) can be rewritten as:

By definition in equation (2.46) the first term on the right side is equal to  $\Phi_{\chi\chi}(k-1)$ .

So:

$$\mathbf{E}_{\mathbf{X}\mathbf{X}}(\mathbf{k}) = \lambda \mathbf{E}_{\mathbf{X}\mathbf{X}}(\mathbf{k}-1) + \mathbf{x}(\mathbf{k})\mathbf{x}^{\mathbf{T}}(\mathbf{k})$$

(2.47)

Similarly:

$$\phi_{XY}(k) = \lambda \phi_{XY}(k-1) + \mathbf{x}(k)\mathbf{y}(k)$$

(2.48)

Using the LS estimate in equation (2.43) we can obtain a recursive formula for the tap-weight vector.

$$\mathbf{a}(\mathbf{k}) = \mathbf{\Phi}_{\mathbf{XX}}^{-1}(\mathbf{k}) \phi_{\mathbf{XY}}(\mathbf{k})$$

To compute the inverse of the autocorrelation we have to use the matrix inversion formula as defined by :

$$\mathbf{A} = \mathbf{B}^{-1} + \mathbf{C}\mathbf{D}^{-1}\mathbf{C}^{\mathrm{T}}$$

Relating A, B, C, D with th terms in equation (2.47)

$$\mathbf{A} = \mathbf{\Phi}_{\mathbf{Y}\mathbf{Y}}(\mathbf{k})$$

$$B^{-1} = \lambda \Phi_{XX}(k-1)$$

$$C = x(k) \qquad D = 1$$

By substituting the above relations in the matrix inversion lemma we obtain the inverse of the autocorrelation as:

$$\bar{\Phi}_{yy}^{-1}(k) = \lambda^{-1}\bar{\Phi}_{yy}^{-1}(k-1) - \lambda^{-1}\Gamma(k)x(k)\bar{\Phi}_{yy}^{-1}(k-1)$$

(2.49)

where:

$$\Gamma(k) = \{\lambda^{-1} \bar{*}^{-1}_{XX}(k-1) x(k)\} / \{1 + \lambda^{-1} x^{T}(k) \bar{*}^{-1}_{XX}(k-1) x(k)\}$$

(2.50)

Substituting (2.49) in the LS estimate, and using (2.48) we obtain:

$$a(k) = \frac{\sqrt{2} - 1}{XX} (k) \phi_{XY}(k)$$

$$= \lambda \frac{\sqrt{2} - 1}{XX} (k) \phi_{XY}(k-1) + \frac{\sqrt{2} - 1}{XX} (k) X(k) Y(k)$$

(2.51)

After manipulating by using the definition of  $\Gamma(k)$  as in equation (2.50) we can express the tap-weight updation in a similar form as the LMS algorithm:

$$\mathbf{a}(\mathbf{k}) = \mathbf{a}(\mathbf{k}-1) + \Gamma(\mathbf{k})\alpha(\mathbf{k}) \tag{2.52}$$

where :

$$\alpha(k) = y(k) - \mathbf{a}^{T}(k-1)\mathbf{x}(k)$$

(2.53)

Equations (2.50), (2.52), and (2.53) constitute the RLS algorithm.

## 2.3.2.3 Convergence

Three aspects of convergence have been extensively discussed in [5]:

- (a) Convergence of the estimate a(k) in the mean.

- (b) Convergence of the estimate a(k) in the mean square.

- (c) Convergence of the average mean-squared value of the "a priori estimation error".

In the following analysis we discuss the third aspect of convergence based on the RLS algorithm, and then make some comparision with that of the LMS algorithm (this aspect is selected for discussion because it is analogous to the LMS algorithm).

Two errors : the "a priori estimation error" and the "a posteriori estimation error" are defined as :

$$\alpha(k) = y(k) - a^{T}(k-1) x(k)$$

(2.54)

$$e(k) = y(k) - a^{T}(k) x(k)$$

(2.55)

Initial conditions of RLS require that :

$$\Gamma(0) = \zeta^{-1} \mathbf{I} \tag{2.56}$$

$$\mathbf{a}(0) = 0 \tag{2.57}$$

where \( \) is a small positive constant. For comparision between the convergence charateristics of the RLS and that of the LMS we discuss the "a priori estimation error" mean-squared value since its learning curve has the same shape as that of the LMS algorithm.

Substituting y(k) from equation (2.55) to equation (2.54):

$$\alpha(k) = e(k) + \mathbf{a}^{T}(k) \times (k) - \mathbf{a}^{T}(k-1) \times (k)$$

$$= e(k) - [\mathbf{a}^{T}(k) - \mathbf{a}^{T}(k-1)] \times (k)$$

$$= e(k) - \tilde{\mathbf{a}}^{T}(k) \times (k)$$

(2.58)

where  $\tilde{\mathbf{a}}(\mathbf{k}) = \mathbf{a}(\mathbf{k}) - \mathbf{a}(\mathbf{k}-1)$  is the weight error vector at time  $\mathbf{k}$ .

We are interested in obtaining the average of the mean-squared priori estimation error. Assuming that the measurement error e(k) has zero mean, and a variance of  $\sigma^2$  the following steps are taken:

# (i) Computing the priori estimation mean-squared error

$$E \mid \alpha^{2}(k) \mid = E[e^{2}(k)] - 2E[e(k) \bar{a}^{T}(k-1) x(k)] + \\ E[x^{T}(k)\bar{a}(k-1)\bar{a}^{T}(k-1)x(k)]$$

$$= E[e^{2}(k)] + E[\mathbf{x}^{T}(k) \ \tilde{\mathbf{a}}(k-1) \ \tilde{\mathbf{a}}^{T}(k-1) \ \mathbf{x}(k)]$$

$$= \sigma^{2} + \mathbf{x}^{T}(k) \ E[\tilde{\mathbf{a}}(k-1) \ \tilde{\mathbf{a}}^{T}(k-1)] \ \mathbf{x}(k)$$

(2.59)

#### (ii) Averaging the mean-squared error

Following steps shown in [5] the average mean-squared error produced by the RLS algorithm is:

$$E \left[ E \left| \alpha^{2} \left( k \right) \right| \right] \approx \sigma^{2} + N \sigma^{2} / n \qquad (2.60)$$

Some observations are made :

- (a) As shown in equation (2.60) the RLS algorithm is independent of the charateristics of the input signal. Convergence rate is therefore insensitive to the input signal. The LMS algorithm convergence behavior is dependent on the eigenvalues of the input signal.

- (b) The RLS algorithm convergence rate is of the order of 2N, where N is the number of the filter taps.

#### 2.3.3 Modified algorithms

In addition to the LMS and LS algorithms, there exists also some modified algorithms whi h are developed to reduce complexity of either the LMS or the LS algorithm. In the LMS category we have the Sign algorithm (SA), and the Block Least Mean Square (BLMS). Similarly, the Fast Recursive Least Square (FRLS), and the Fast Transversal Filters (FTF) belong to the

LS class [5].

#### 2.3.3.1 Sign Algorithm (SA)

A modified version of the LMS algorithm, the SA reduces number of computations by replacing the correlation e(k+1)x(k+1) of equation (2.14) by the sign of the error e(k)

$$\mathbf{a}(k+1) = \mathbf{a}(k) + 2\mu \operatorname{sign}(\mathbf{e}(k+1)) \mathbf{x}(k+1)$$

(2.61)

This replacement results in a degradation of speed, and high instability [5].

#### 2.3.3.2 Block Least Mean Square (BLMS)

Derived from the LMS algorithm, this BLMS approach updates a block of M coefficients per iteration. Equation (2.17) is modified as:

$$a(k+M) = a(k) + 2\mu \sum_{n=0}^{M-1} e(k-n)x(k-n-1)$$

(2.62)

When M=1 the BLMS becomes the LMS algorithm. The condition for convergence of the BLMS is the same as that of the LMS:

$$0 < \mu_{\rm B} < 1/\lambda_{\rm max}$$

# 2.3.3.3 Fast Recursive Least Square (FRLS) Algorithm

This modification of the RLS algorithm uses the shifting property of the  $\Gamma(k)$  of equation (2.52) to avoid computing this matrix. This is done without any storage of the M x M matrix as required by the conventional form of the RLS algorithm.

## 2.3.3.4 Fast Transversal Filters (FTF) Algorithm

Developed by Cioffi and Kailath in 1984 [5] this FTF algorithm employs four transversal filters:

- one filter defines the desired response of the adaptive filter.

- the other three filters perform convergence process.

The FTF algorithm uses simple equations of the LMS, and yet its speed is comparable with that of the RLS.

#### CHAPTER 3

#### ECHO CANCELLATION IN DA, P-MP SYSTEMS

This chapter first presents the concept of echo cancellation suitable to Point-to-Multipoint, Demand-Assignment Time Division Multiple Access (DA-TDMA) radio systems, and its characteristics. It then discusses the criteria and performance evaluation to select the echo cancellation algorithm, and appropriate DSP suitable to implementation of a Multichannel, Demand-Assignment Echo Canceller (MCDAEC). A statistical approach, which is based on the behavior of trunks, is introduced to increase the capacity of trunks per DSP.

#### 3.1 System Description

Previously we mentioned that all P-MP Subscriber Radio Systems share a common feature in having a Central Station (C/S), and a number of Outstations (O/S) communicated via microwave links. A typical P-MP subscriber radio system is shown in Fig.1. The Central station normally located in the Central office is equipped with an omnidirectional antenna. The Outstations (O/S's) may be placed in any location in the exchange serving area, and when a single hoop ranges are exceeded, repeaters are used. In this study we assume a typical system which can have up to 10 repeaters for a range

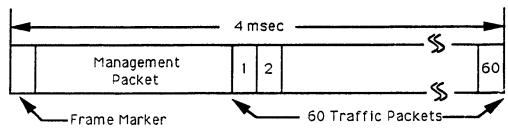

of 720 km. With N trunks, the system provides services to M subscribers on a Demand-Assignment basis, where M >> N. The transmission in the downward direction (from C/S to O/S) is in a Time Division Multiplexing mode with a 4ms frame. The transmission in the upward direction (from O/S to C/S) is a Time Division Multiple Access with a 8ms frame as shown in Fig.7.

#### Downward Frame Structure

#### Upward Frame Structure

Figure 7. A Time Division Multiplex Structure

Due to the nature of grouping samples in TDMA transmission delay is introduced in the system which may increase annoying effect of echo. Echo is present when there

is an impedance mismatch in O/S 2-wire loop cards (or C/S two wire line cards). There are two parameters which makes echo annoying:

- Level of echo due to mismatch at subscriber interface, and network terminal points.

- System round-trip delay.

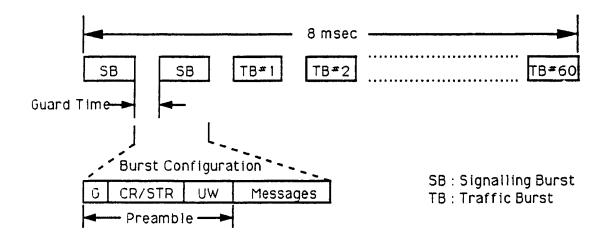

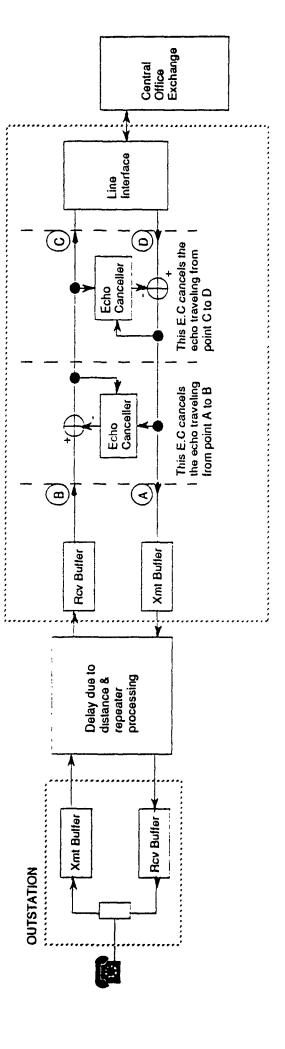

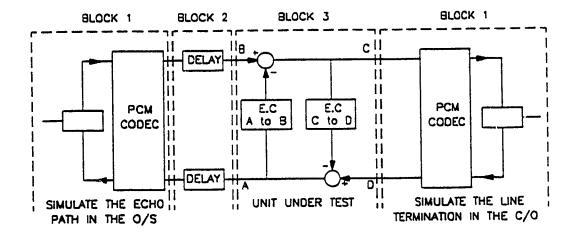

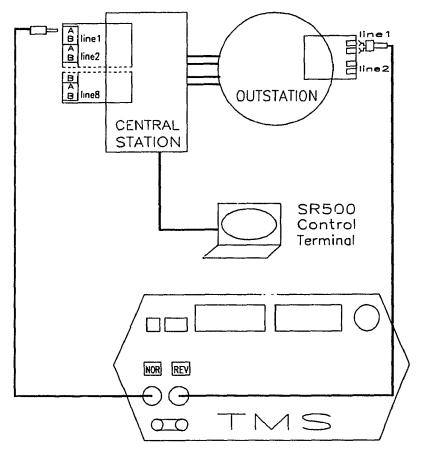

Echo Cancellers can be introduced to each subscriber interface loopcards in the Outstation. In this case, the number of echo canceller will be M, the number of the subscribers, much larger than N, the number of available trunks in the system. This unnecessarily increase the system cost. A more economical approach is to implement Echo Cancellers in the Central station. In this case the maximum required number of echo canceller pairs is N. Fig. 8 shows the model of a proposed Multichannel, Demand-Assignment Echo Canceller (MCDAEC).

When both Echo Cancellers are in the C/S, the echo paths include delay due to distance from echo canceller to the source of echo, propagation and frame delays. As shown in Fig.8, the echo path due to the mismatch impedance in the loopcard of the Outstation will be:

$$\tau_{EC} = \tau_{B} + \tau_{P} + \tau_{R} + \tau_{I}$$

where :

$\bullet$   $\tau_{\rm B}$  is the sum of the upward TDMA frame, and the downward TDM frame, e.g for a system with an upward TDMA frame of 8ms

and a downward TDM frame of 4ms, the  $\tau_{\rm B}$  is 12ms.

$\bullet$   $\tau_{\rm p}$  is round-trip propagation delay due to distance from the location of the Echo Cancellers to subscribers, e.g for a range of 720km :

$$\tau_{\rm p} = 2 \times (720/300)$$

- $\tau_{\rm R}$  is the total processing delay of the repeaters in tandem e.g for a link with 10 repeaters and individual repeater delay of 30  $\mu \rm s$ ,  $\tau_{\rm R}$  is 0.3ms.

- ${}^{\bullet}$   ${}^{\tau}$  is the impulse delay due to the spanning time of the echo. This delay is typically of the order of 2ms to 5ms. Measured result on a typical subscriber radio system shows a delay of about 2.9ms.

For values given in the above examples, the echo delay for this path is:

$$\tau_{EC} = (12ms) + (2 \times (720/300)) + (0.3ms) + (2.9ms)$$

$$= 20.0ms$$

This echo is handled by the Echo Canceller for direction from A to B.

• For echo due to mismatch impedance in Line Card at the Central station, its echo path delay is about 5ms. This echo is handled by the Echo Canceller for direction from C to D.

#### 3.2 Design Requirements

The calculations of echo paths from the model in Fig.8 lead to the design of two Echo Cancellers with different delays. Also, dynamic operation of a trunk (a trunk can be assigned to any subscriber) requires a dynamic structure of Echo Canceller. In this section we discuss the system requirements, performance specifications using the model in Fig.8.

#### 3.2.1 System Requirements

The design aim of the MCDAEC needs an Echo Cancellation algorithm which satisfies the following requirements:

- (a) Simple implementation: the P-MP system has N full-duplex trunks, hence needs N full-duplex Echo Cancellers required. It is economically desirable to multiplex all these N full-duplex E.C's in as few DSP's as possible. Common sense dictates that a simple algorithm is necessary.

- (b) Small number of operations (multiplications & additions): most consuming time operations in adaptive FIR filters are the multiplications and additions. To increase the real-time performance means number of multiplications and additions per iteration should be small.

- (c) Fast tracking speed: trunk status dynamically

changes from one subscriber to another, so it is necessary that the algorithm has the ability to track the changes rapidly.

(d) Small memory utilization: external memory access is more time expensive than internal memory access. We can multiplex more echo canceller pairs per DSP if small external memory is required, i.e a small memory utilization is desirable since most DSP's have small internal memory of the order of 512 words.

In previous chapter, we outlined various Echo Cancellation algorithms. The usefulness of these Echo Control techniques depends on each application. For application in Demand-Assignment, Point-to-Multipoint Radio System the areas of complexity in Echo Cancellation are:

- The speed of adaption, and the accuracy of the cancellation after adaption are two important measures of performance of an Echo Cancellation algorithm. A trade-off of the two measures are required: as the speed of adaption is increased (small number of taps used in FIR) the accuracy of the replica echo becomes poorer.

- The Demand-Assignment operation of the MCDAEC requires a "dynamic" structure of Echo Canceller. Since a trunk is not dedicated to any particular subscriber, the adaption must be dynamically changed on each new assignment, and possibly from one frame to another. The Echo Cancellation, therefore, has to be able to adapt to a new echo path with fast speed.

Figure 8. A Simplified model to illustrate the location

**CENTRAL STATION**

of the MCDAEC in the Central station

#### 3.2.2 Performance Requirements

The performance specifications for the design of the MCDAEC can be divided into two groups : the generic specifications, and the specific specifications.

- The generic specifications are based on the G.165 CCITT Recommendations [4]. These specifications are to provide the basic requirements for the design of an E.C with acceptable performance as follows:

- (a) Echo Return Loss Enhancement (ERLE): should be smaller than or equal to -24dB with reference to input signal.

- (b) Convergence Speed: the ERLE should be ≤ -24 dB

within 500ms with initial coefficients set to 0.

- (c) Real-time : PCM sampling time is 8 Khz, i.e the frame is 125  $\mu$ s.

- The specific specifications are the requirements for the design of the MCDAEC. These specifications are listed in the following:

- (d) Echo Path Delay: two Echo Cancellers are require for each full-duplex trunk. One has echo delay of 20ms, and the other has echo delay of 5ms. Details on the design will be described in section 3.3.1.

- (e) A small number of DSPs: as discussed earlier, a P-MP system with N trunks needs N pairs of echo cancellers. For cost- $\epsilon$  fective reason, a minimization of the number

of DSPs could be significant, especially when N is large. If the number of DSPs is Q, then Q should be as small as possible compared to N.

Both the generic and specific specifications represent a challenge in searching for an E.C algorithm, and a powerful DSP. The generic specifications suggest an E.C algorithm which should have fast convergence speed, and small ERLE. The least squares E.C algorithms are known for their fast convergence speed. Yet, these algorithms are expensive to implement because they require a large number of operations per iteration. These are the trade-off performance that have to be made in selecting an E.C algorithm. In the following section, we revisit both the Least Mean Squared (LMS) algorithm, and the Least Squares algorithm with focus on the following:

- Implementation complexity (number of operations per iteration).

- Tracking speed.

#### 3.3 Performance Evaluation of Echo Cancellation

The performance specifications for the design of the MCDAEC suggest for a selection criteria of echo cancellation algorithms. Echo cancellation algorithms should have fast convergence and tracking speeds. Since trunk is not dedicated to any particular subscriber, the adaption changes dynamically from on each new assignment. The echo canceller, therefore,

has to be able to adapt to new changes in the echo path with sufficiently fast speed. Furthermore, simple structure of echo cancellation algorithm is desirable due to the objective of minimizing the number of DSPs used in the MCDAEC. Simplicity means a small number of operations (multiplication & additions) per iteration, a small utilization of memory.

Echo cancellation algorithms are available in two basic categories: Least Mean Squared (LMS), and Least Squares (LS). In each category there also exists a number of modified algorithms such as Block Least Mean Square (BLMS) in the LMS category, or Recursive Least Square in the LS category.

#### 3.3.1 Least Mean Square (LMS) Algorithm:

#### 3.3.1.1 General Algorithm

The LMS is the most commonly implemented algorithm in many Echo Cancellers. The criterion function is taken to be the expected valued of the squared error, and the taps are adapted according to the stochastic steepest descent algorithm [6]. As previously discussed in chapter 2 the steepest-descent equations are

$$e(k) = y(k) - x(k) * h(k)$$

(3.1)

$$a (k+1) = a (k) + 2\mu \times e(k+1) \times x(k+1)$$

(3.2)

The LMS algorithm can be formulated in the following steps:

(i) Initializing: filter coefficients are set to zero,

and initial parameters are declared.

- (ii) Inputting: new samples are read.

- (iii) Echo Estimating: the echo replica is estimated, and residual error is computed using Eq. (2.16). The residual error is compared with optimum threshold value. If the optimum residual error has been achieved, go to step (v).

- (iv) Coefficient Updating: coefficients are updated using the current far-end sample and residual error as shown in equation (2.14).

- (v) Go to step (i).

- 3.3.1.2 Complexity: the steepest-descent equations require only O(2N) multiplications, and O(2N) additions per iteration for an N-tap filter, where O(J) stands for "on the order of J". In addition, a memory size of 2 x N words is required (N most recent far-end samples, and N tap coefficients). With the currently available DSPs having small memory size (on the order of 512 words) this LMS seems to suit just well. Furthermore, for some filters where a large memory is required the number of memory accesses per iteration should be small so that real-time execution performance is not deteriorated due to number of wait states being introduced.

- 3.3.1.3 Tracking Speed: the value of  $\mu$  in the above steepest-descent equations plays an important role in determining the convergence speed, stability, and residual

error after convergence. For a large value of  $\mu$ , the convergence becomes faster, but it results in a larger residual error and is more prone to instability. convergence speed of the LMS is considerably slow, and is dependent on the characteristics of the far-end signal [7]. To overcome this problem the loop gain  $\mu$  is allowed to vary inversely with signal power. As the power in the correlation k)x(k) is proportional to signal variance, the product choice of a loop gain  $\mu$  that is inversely proportional to the variance provides a performance which is invariant to far-end signal power. In the case of the MCDAEC the echo path is dynamically changed since a trunk is not dedicated to any particular subscriber. For a new echo path the Echo Canceller has to take some times to learn the characteristics of the new echo path, a slow tracking speed may cause an undesirable divergence.

#### 3.3.2 The Block Least Mean Square (BLMS) :

The BLMS is another class of Echo Cancellation in the LMS category. It involves the calculation of a block of finite set of outputs from a block of inputs values [8]. As before we are interested in the following characteristics:

3.3.2.1 Complexity: the BLMS algorithm is almost identical to the LMS one with respect to the implementation simplicity. The BLMS also requires 2N multiplications, and 2N

additions per iteration. Because of its structure (a block of coefficients are updated per iteration) the BLMS requires a larger memory storage by M words, where M is the block size of the BLMS. However, the memory access becomes less in the BLMS which does not need to update coefficients as often as in the case of the LMS. For the MCDAEC application this performance of the BLMS is equivalent to that of the LMS.

3.3.2.2 Tracking Speed: as shown by G.A.Clark, et al. [9] the speed of the BLMS is a function of block size M, and the loop gain  $\mu$ . Simulation results [10] also show that a BLMS using a block size of 16 and inversely proportional to far-end signal power loop gain performs better than the LMS algorithm under the same conditions.

## 3.3.3 The Sign Algorithm (SA)

This algorithm also belongs to the LMS category. The same principle as the previous two, but the correlation factor is avoided by using the signs of e(k), and x(k). Hence, the SA is simpler, and less expensive. Because of its unnormalized gain the SA convergence speed is slower. The following observations are obtained when we try to increase the convergence speed:

- If the gain is adjusted to give an acceptable residual error, the convergence speed is very slow.

- If the gain is increased for fast convergence, the residual error may not be acceptable [11].

# 3.3.4 Least Squares (LS) Algorithm

### 3.3.4.1 General Algorithm

Instead of minimizing the mean-squared-errors, this approach minimizes a weighted sum of squared errors. A more complete details have been discussed in chapter 2. Similar equations to the LMS have been obtained as follows:

$$e(k) = y(k) - \mathbf{a}^{T}(k)\mathbf{x}(k)$$

(3.3)

$$a_n(k+1) = a_n(k) + \sigma R^{-1}(k) \times (k) e(k)$$

(3.4)

$$R(k) = (1 - \sigma)R(k-1) + \sigma x(k) x^{T} (k)$$

(3.5)

The LS algorithm can be formulated as follows:

- (i) Initializing : filter coefficients are set to zero, and  $R^{-1}$  is initialized.

- (ii) Inputting: new samples are read.

- (iii) Echo Estimating: echo replica is generated, and residual error is computed, and compared with optimum threshold value. If an optimum residual error has been obtained, go to step (v).

- (iv) Coefficient Updating : two steps are involved :

- computing the matrix  $\Gamma(k)$ .

- updating the coefficients.

- (v) Go to step (i).

- 3.3.4.2 Complexity: the correlation term in the case involves matrix multiplications, and additions as compared to the LMS approach which is simpler because of scalar

correlation. The direct implementation of the above equations is very costly, as the computation of  $\Gamma(k) \times (k)$  requires more than N3/6 multiplications per iterations, where N is the size of the FIR.

3.3.4.3 Tracking Speed: the normalization with R<sup>-1</sup> (k) in the LS offers more than the simple power normalization (varying the loop gain inversely with signal power) in LMS: it essentially normalizes the adaption in each eigen vector direction by the signal power. Thus the convergence becomes independent of both signal type, and power.

This algorithm requires a large amount of computations. A number of modified algorithms have been devised to reduce the required number of multiplications and divisions per iteration to be proportional to N.

### 3.3.5 Fast Recursive Least Square (FRLS)

The FRLS Algorithm is governed by the equation :

$$a_n(k+1) = a_n(k) + K_n(k) e(k)$$

(3.6)

$$K_n(k) = R^{-1}(k) x(k)$$

(3.7)

3.3.5.1 Complexity: this algorithm exploits the shifting property to compute the vector  $K_n$  (k) recursively [12].

Therefore, it avoids the computation and storage of N by N matrix, i.e the vector x acts like a shift register such that x(k+1) is only a "push down" version of x(k) with a new sample

on top. The number of multiplications, and additions is then reduced to about O(10N).

3.3.4.2 Tracking Speed: as the LS approach this FRLS Algorithm offers a fast start-up convergence, independent of the characteristics of input signal.

Other improved algorithms have been introduced in [5]. Commonly, faster algorithms are obtained by reducing the number of multiplications, divisions, and additions per iteration. For instance, Memory-Tap Algorithm [13] uses table look-up method. The problem with this algorithm in the MCDAEC is that a very large memory is required. Several other authors [14] also attempted to improve real-time performance of E.C by using the fact that an impulse response consists of three parts: Flat delay, Active delay, and Tail delay. The Active part, if correctly detected, can help in using less number of taps in FIR, hence the computation is reduced.

As previously mentioned, the MCADEC requires a simple, but fast Echo Cancellation algorithm. The LS, Fast Recursive Least Square,... offers very fast start-up convergence, but their complexity is not attractive. On the other hand, LMS and BLMS is slow (but simulation results show their convergence speeds conform with the CCITT G.165 recommendation), and simple. The BLMS has an advantage in the reduction of the number of memory accesses per iteration.

Table 1. A Comparison of Echo Cancellation Algorithms

|                    |                                                | No. of oper.  |                     | MEMORY   |

|--------------------|------------------------------------------------|---------------|---------------------|----------|

| ALGORITHM          | BASIC THEORY                                   | per iteration | MEMORY STORAGE      | ACCESS   |

|                    |                                                |               | •Store N most       |          |

|                    |                                                |               | recent far-end      | Appr. 3N |

| Least Mean Squared | $e(k) = y(k) - \Sigma h(k)x(k-n)$              | 2N Mult       | samples.            | per      |

| LMS                | $a(k+1) = a(k) + 2\mu e(k) x(k-n)$             | 2N Add        | ·Store N updated    | iterat-  |

|                    |                                                |               | coefficients.       | ion      |

|                    |                                                |               | •Store M most       |          |

|                    |                                                |               | recent err. est.    | Appr.    |

|                    |                                                |               | ·Store N most       | 2N+N/M   |

| Block Mode Update  | $e(k) = y(k) - \Sigma h(k) x(k-n)$             | 2N Mult       | recent far-end      | per      |

|                    | $a(k+M) = a(k) + 2\mu L e(k-1) \times (k-n-1)$ | 2N Add        | samples.            | iterat-  |

| BLMS               |                                                |               | •Store N updated    | ion      |

|                    |                                                |               | coefficients.       |          |

| Recursive          | $e(k) = y(k) - \Sigma h(k)x(k-n)$              | 10N + 4 Mult  | •A total storage of | Appr.    |

| Least Square       | $a(k+1) = a(k) + \Gamma(k)x(k)$                | 12N + 5 Add   | 5N + 6 words.       | N8       |

|                    |                                                |               |                     |          |

### 3.4 Performance Evaluation of DSPs

One of the most time-consuming computation in E.C algorithm is the convolution, and correlation which involve multiplications and additions. Digital Signal Processors (DSPs) are specialized microcomputers suitable for these realtime digital signal processing applications. The most basic architecture is the integration of fast multiplier/accumulator hardware into the data path. Arithmetic operations are not done on a separate co-processor. They are integrated into basic instructions.

The selection of a powerful DSP is based on the specifications as discussed in section 3.2.2. The key performance of an DSP is its Multiply-Accumulate-Shift speed. Most of DSPs can perform these three operations in a single instruction cycle. The next performance criteria is DSP's internal memory capacity. This criteria is also important for the design of the MCDAEC which would multiplex echo canceller pairs per DSP. The real-time performance will be degraded if extensive external memory accesses are required (external memory access requires more real-time). In addition, the DSP multiprocessing configuration is also taken into consideration in designing the MCDAEC. These criteria of DSP selection are summarized below:

- (i) Multiply-Accumulate-Shift.

- (ii) Instruction Cycle.

- (iii) Memory.

- (iv) Multiprocessing configuration.

In addition to the above requirements, the following engineering aspects are also considered:

- (v) Cost (unit, development system).

- (vi) Engineering support.

The following discussion is based on the MCDAEC with specifications as :

- 64 x 64 taps for a full-duplex Echo Canceller.

- 160 far-end samples to be stored (representing 20ms).

In the remaining of this section, we will review the architectures of the MSM6992 (Oki Electric), the Nippon Electric µPD7729, µPD77230, the AT & T WEDSP16, WEDSP32, the Texas Instrument series TMS32020, TMS320C25, TMS320C30, and the Motorola DSP56000/01 with focus on each DSP's Multiply-Acumulate-Shift benchmark, Instruction Cycle, on chip memory, and the feasibility of supplementing this memory with external RAM, and DSP's peripheral using the Host architecture concept.

### 3.4.1 The Oki Electric Family

One member of this family, MSM6992, is described here. This DSP consists of four blocks: Arithmetic Block (AB), Data Memory Block (DMB), I/O Block (IOB), and the Control Block (CB). As a high speed floating point DSP the MSM6992

#### features :

- A ROM of 1024 words  $\times$  32 bits within the chip, and can be expanded to a maximum of 64K words  $\times$  32 bits by an external device.

- A data RAM of 256 words  $\times$  32 bits within the chip, and an external memory of a maximum of 64K words  $\times$  32 bits can be provided outside the chip.

- A fast instruction cycle of 100ns.

- A CMOS technology, 400mW.

- · Multiprocessor interface.

The Data Memory Block (DB) of the MSM6992 is partitioned into two parts: RAMX and RAMY, each has 128 words x 22 bits RAMX, RAMY can be used independently, or as a single page of memory. In the latter case it is called RAMXY. The Multiply-Accumulate is performed by a floating-point multiplier FMPY. With this arrangement of data it is very effective for Echo Canceller application where coefficients, and far-end signal can be stored in RAMX, and RAMY, and the convolution can be carried using a single instruction. The MCDAEC utilizes a large memory since a number of trunks shares the same DSP. External memory can be used at the expense of increasing the processing time. This DSP employs an effective Host design concept. The following modes are provided as the interface modes:

(i) Slave mode: in this mode the Host processor accesses the I/O register of the DSP.

- (ii) Master mode: in this mode the DSP itself, when instructed, accesses the external data memory, and I/O port.

- (iii) DMA mode: this mode performs the interface with the external 8-bit or 16-bit DMA controller [16].

The Slave mode would be very useful in the design of MCDAEC where of number of DSP's can be controlled by one Host processor which communicates with the main CPU of the TDMA controller of the Central station. Although the I/O interface mode of the MSM6992 is suitable in the design of the MCDAEC, its limited on-chip memory, and little engineering support make it unattractive.

### 3.4.2 The Nippon Electric Family

As a second generation DSP the NEC  $\mu$ PD7720 introduced in 1980 has a microcode-like instruction set and a parallel architecture which enable a single instruction to load the two multiplier inputs, accumulate the multiplied product, modify both RAM/ROM pointers, and execute a return from subroutine. The NEC  $\mu$ PD7720 has on chip:

- a 512 x 23-bit program ROM.

- a 510 x 13-bit data coefficient ROM.

- a 128 x 16-bit data RAM.

- a 250 nsec 16 x 16-bit parallel multiplier which gives a 32-bit result.

Although the NEC µPD7720 has several characteristics in common with the MSM6992, its low speed is a major problem in MCDAEC application where the real-time requirement is crucial. NEC µPD77230, a third generation, offers a high speed (150ns) and a larger memory storage: 1K x 32-bit RAM which is organized as two separately addressable 512 x 32-bit blocks. The Multiply- Accumulate operation can be accomplished by arranging coefficients and far-end samples in two blocks. However, a significant amount of overhead is required in manipulating pointers when performing the FIR computation [17].

### 3.4.3 The AT & T Family

The WEDSP16, a member of the AT&T DSP, is a general purpose, programmable, 16-bit fixed point DSP. It features:

- a 2K  $\times$  16-bit ROM, which can be expanded off-chip to 64K  $\times$  16 bits with no loss of speed.

- a 512 x 16-bit on-chip RAM.

- a 15 x 16-bit on-chip Cache which can be repeated up to 127 times. The advantage of the Cache is that it allows low programming overhead for looping (1 cycle of overhead for up to 127 repeats).

- a Serial I/O port, and a Parallel I/O port.

The Multiply-Accumulate instruction has three stages in the pipeline: data fetch, multiply, and accumulate. A typical

example to illustrate this instruction as follows [18]:

- Inst (1) y = \*r1++ x = \*pt++

- Inst (2) p = x\*y

- Instr (3) a0 = a0+p

In instruction 1, the data in the RAM location indexed by register r1 is moved to the y register, and r1 is incremented by one. Similarly, the data in the ROM location pointed by register pt is moved to x register, and pt is then incremented by one memory location. The product of contents of x and y registers is stored in p, and added to accumulator a0. The DSP16 instruction syntax follows the C programming language. Its 55ns per instruction, and a structured architecture provides users with an efficient design. However, as will be discussed later, the WEDSP16 is not well-supported and cost-effective compared to TI TMS320C25, and Motorola DSP56000/01.

#### 3.4.4 The Texas Instrument TMS320 Family

The TMS320 Family of processors includes the first generation such as TMS32010, TMS320C15, TMS320C17; second generation TMS32020, TMS320C25, and third generation TMS320C30 which is a floating-point DSP, and has the highest speed (33 MIPS) in the family. We will discuss some distinct architectures of the DSP related to the MCDAEC implementation.

As noted in [19], the high performance of the TMS320

series is accomplished using the following concepts:

- · Hardward architecture.

- Extensive pipelining.

- · Dedicated Hardware multiplier.

- Special DSP instruction such as MACD which performs multiply-accumulate-data shifting in the same instruction.

- · Fast instruction cycle.

The first generation of TMS320 Family is considerably slow for MCDAEC application, so the discussion is omitted here. The second generation includes TMS32020 which features

- 200ns instruction cycle.

- 544 words of on-chip RAM which is partitioned into blocks B0, B1, B2.

- Double-buffered serial port.

- NMOS technology.