Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa: Ontario K1A 0N4 Bibliotheque nationale du Canada

Direction des acquisitions et des services bibliographiques

395 rue Wellingter Ottawa (Ontare) K1A 0N 1

## NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

## **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

## A Unified Model for Protocol Test Suite Design

Priyadarshi Tripathy

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirement

for the Degree of Doctor of Philosophy at

Concordia University

Montreal, Quebec, Canada

November, 1992

© Priyadarshi Tripathy, 1992

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395 rue Wellington Ottawa (Ontano) KTA 0N4

Assistant Contract

A Commence

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque du Canada nationale reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette la thèse à disposition personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-84672-0

#### ABSTRACT

## A Unified Model for Protocol Test Suite Design

Priyadarshi Tripathy Ph. D.,

Concordia University, 1992.

This thesis is concerned with developing new algorithms for solving some basic problems of conformance testing. In particular, the following problems of conformance testing are considered: i) generation of test cases from Language Of Temporal Ordering Specification (LOTOS) and Specification and Description Language (SDL), ii) selection of test cases which meet certain data flow coverage criteria, and iii) representation of test cases for Local Single-layer (LS) and Remote Single-layer (RS) architectures. The algorithms presented in this thesis can be used to solve in an efficient manner these fundamental problems of conformance testing. These algorithms rely heavily on two concepts: the Extended Finite State Machine (EFSM) chart and the Input/Output (I/O) diagram. In this thesis, we introduce a unified model (using the EFSM chart and the I/O diagram) for existing protocol specification languages. Based on the new unified model, a conceptually simple, easy to implement and computationally efficient methodology is proposed in this thesis for studying conformance testing.

In this thesis, the protocol specification is mapped into an EFSM chart. The structure of input/output data is modeled by hierarchical diagrams called I/O diagrams. Test cases are generated from the EFSM chart. Furthermore, a data flow graph is constructed from the chart, and used to identify the protocol functions for testing the data flow aspects of an Implementation Under Test (IUT). The zero-one integer programming technique is used to select test cases to meet the data flow coverage requirement. The selected test cases are modeled as a dependency graph and then evaluated by taking predicate slices from the test case dependency graph. Predicate slices are used to identify infeasible test cases that must be eliminated. Redundant assignments and predicates in all the feasible test cases are removed by reducing the test cases. Reduction is achieved by using the test case dependency graph as well as the data flow graph. The reduced test case dependency

graph is adapted for LS and RS architectures. The tester's behaviour in each test case is obtained by a series of transformations called representation and selection. Test case representation refers to the steps of inverting the direction of events and the generation of base and dynamic constraints on the events. These constraints are generated in the form of an I/O diagram. Test case selection refers to the steps of assigning a test purpose according to the hierarchy of test cases in a test suite and then completing the tester's behaviour by assigning verdict and parameter value information.

# TO MY PARENTS PROFESSOR KUNJABEHARI AND SUREKHA

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to Professor B. Sarikaya, for his continued guidance, suggestions, encouragement and his careful reading of the manuscript and providing criticism on writing. Without his supervision, this work would not have been possible. I owe my knowledge of protocol testing to him.

I would like to thank Professor G.v.Bochmann of University of Montreal for financial assistance. I would also like to thank Professor J. W. Atwood for going through the thesis and improving the technical quality of the manuscript.

It is with great pleasure that I acknowledge the support and motivation provided by all my colleagues of Room No. H847, and in particular Sagar, Raghu, Costas, Aparna and Hamid. I also wish to acknowledge Ashima for her careful reading and improving the English of this thesis.

Last but not the least, it is with pride that I acknowledge the support and inspiration of my parents Professor Kunjabehari and Surekha, my brothers Bipeen and Banabehari, my sisters Kannan, Nalini, Gitanjali, Krishna and Yasodhara and my brothers-in-law Benoy, Pratap, Debendra, Rajendra and Biju —back home.

## TABLE OF CONTENTS

| LIST OF ABBREVIATIONS                             | x    |

|---------------------------------------------------|------|

| LIST OF FIGURES AND TABLES                        | XII  |

| CHAPTER I: INTRODUCTION                           | 1    |

| 1.1 Formal Specification                          | 4    |

| 1.2 Conformance Testing                           | 6    |

| 1.2.1 Test Method Overview                        | 6    |

| 1.2.2 Types of Testing                            | 8    |

| 1.2.3 Test Suite Structure                        | 8    |

| 1.3 Test Suite Design                             | 9    |

| 1.3.1 FSM Based Test Design                       | 9    |

| 1.3.2 Estelle Based Test Design                   | 11   |

| 1.3.3 LOTOS Based Test Design                     | 12   |

| 1.3.4 SDL Based Test Design                       | 13   |

| 1.4 Objective and Motivation                      | 13   |

| 1.5 Original Contributions                        | 14   |

| 1.6 Outline of the Thesis                         | 14   |

| CHAPTER II: UNIFIED MODEL                         | . 17 |

| 2.1 Abstract Syntax Notation 1                    | 17   |

| 2.2 SDL Specification Language                    | 19   |

| 2.3 LOTOS Specification Language                  | . 21 |

| 2.4 I/O Diagram                                   | 23   |

| 2.4.1 I/O Diagram for ASN.1                       | 24   |

| 2.4.2 I/O Diagram for ADT                         | 28   |

| 2.4.3 ASP/PDU Hierarchy from Specification        | 30   |

| 2.5 Transition System and EFSM Chart              | 32   |

| CHAPTER III: EFSM CHART OF SPECIFICATIONS         | . 35 |

| 3.1 From LOTOS to EFSM Chart                      | . 35 |

| 3.1.1 Transformation of a LOTOS Specification     | . 35 |

| 3.1.2 The Chart Construction Algorithm            | . 38 |

| 3.2 From SDL to EFSM Chart                        | . 50 |

| 3.2.1 Transformation of SDL Specification         | . 50 |

| 3.2.2 The Chart Construction Algorithm            | . 58 |

| 3.3 Size of the EFSM Chart                        |      |

| CHAPTER IV: GENERATION AND ANALYSIS OF TEST CASES |      |

| 4.1 Test Case Generation Algorithm                | 64   |

| 4.2 Data Flow Graph                               |      |

| 4.2.1 Decomposition of Data Flow Graph                     | 72         |

|------------------------------------------------------------|------------|

| 4.3 Test Selection from Protocol Function                  | 73         |

| 4.4 Test Case Dependency Graph                             | . 77       |

| 4.4.1 Predicate Slices                                     | 80         |

| 4.4.2 Infeasible Paths in Test Cases                       | 83         |

| 4.5 Reduction of Test Cases                                | 84         |

| 4.5.1 Reduction of Test Cases Using TCDG                   | 84         |

| 4.5.2 Reduction of Test Cases Using DFG                    |            |

| CHAPTER V: TEST SUITE SELECTION AND REPRESENTATION         | 89         |

| 5.1 Constraint Representation                              | 90         |

| 5.1.1 Instantiated I/O Diagram                             | <b>9</b> 0 |

| 5.1.2 Base Constraints                                     | 90         |

| 5.1.3 Dynamic Constraints                                  | 98         |

| 5.2 Control Flow Behaviour Representation                  | 102        |

| 5.3 Test Case Hierarchy                                    | 103        |

| 5.4 Test Purposes                                          | 104        |

| 5.5 Valid Behaviour Test Selection                         | 104        |

| 5.5.1 Behaviour Enhancement and Verdicts Assignment        | 104        |

| 5.5,2 Test Purpose and Parameter Values                    |            |

| 5.6 Adaptation of Generated Test Cases for RS Architecture | 107        |

| 5.7 Comparison Between Test Selection Strategies           | 110        |

| CHAPTER VI: APPLICATIONS                                   |            |

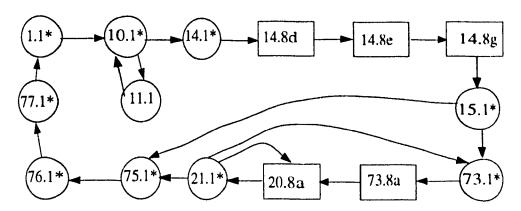

| 6.1 ACSE Specification in LOTOS                            | 111        |

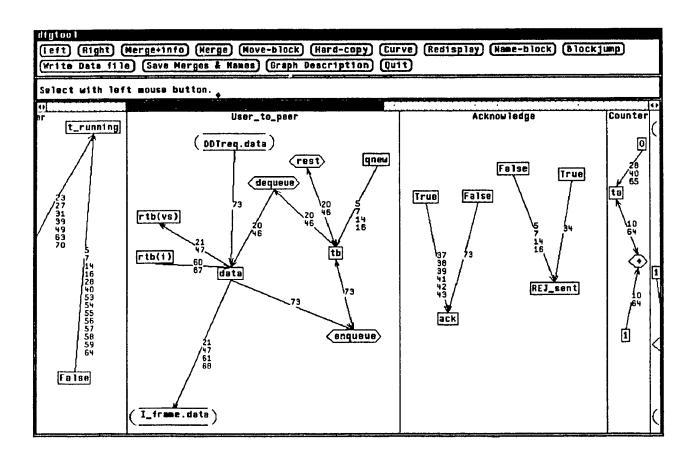

| 6.2 The LOTEST System                                      |            |

| 6.2.1 Compiler                                             |            |

| 6.2.2 Chart Generator                                      | 114        |

| 6.2.3 Interactive Tools                                    | 115        |

| 6.3 Test Suite Design From ACSE Protocol                   |            |

| 6.3.1 Generation and Selection of Test Cases               |            |

| 6.3.2 Analysis and Reduction of Generated Test Cases       | 119        |

| 6.3.3 Dynamic Constraint Representation                    |            |

| 6.3.4 Test Case Selection and Representation               |            |

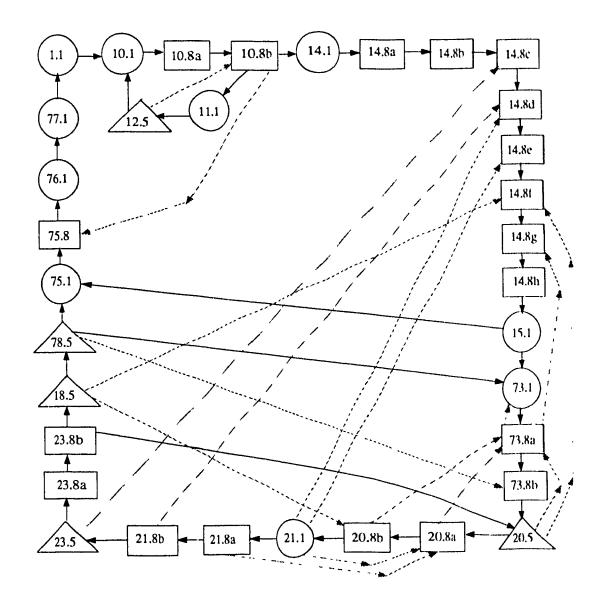

| 6.4 Test Suite Design for LAPB Protocol                    |            |

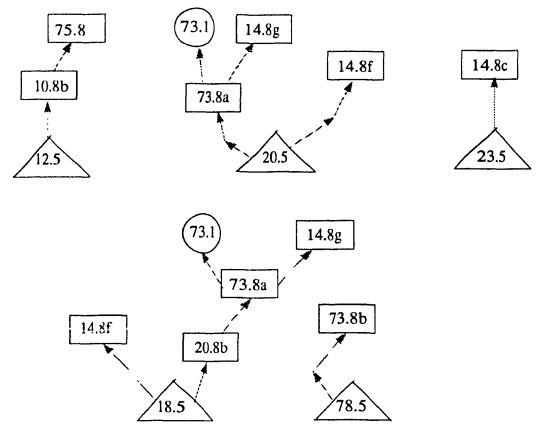

| 6.4.1 Analysis and reduction of Generated Test Cases       |            |

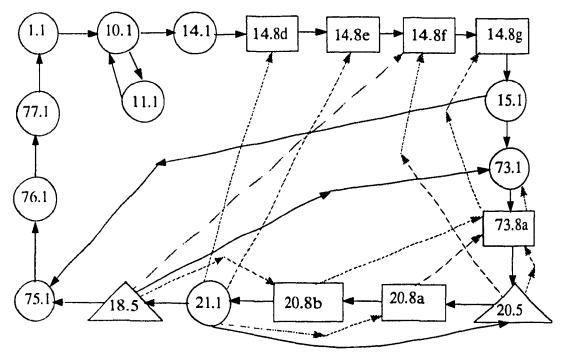

| 6.4.2 Test Case Selection and Representation               |            |

| CHAPTER VII: CONCLUSION AND FUTURE WORK                    |            |

| 7.1 Conclusion                                             |            |

| 7.2 Future Work                                            |            |

| DEFEDENCES                                                 | 138        |

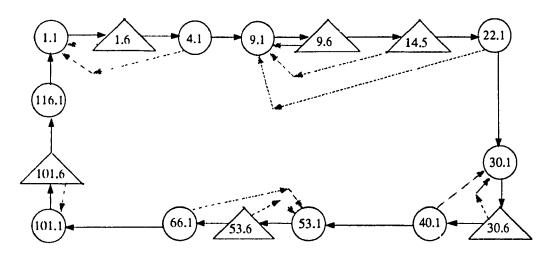

| APPENDIX A: EFSM CHART OF ASCE PROTOCOL                             | 144 |

|---------------------------------------------------------------------|-----|

| APPENDIX B: TEST GENERATED FROM ACSE PROTOCOL                       | 168 |

| APPENDIX C: EFSM CHART OF HDLC PROTOCOL                             | 170 |

| APPENDIX D: CONSTRAINTS GENERATED FOR THE TEST CASE T <sub>29</sub> | 186 |

| APPENDIX E: CONSTRAINTS GENERATED FOR THE TEST CASE T <sub>17</sub> | 191 |

## LIST OF ABBREVIATIONS

ACSE Association Control Service Elements

ACT Asynchronous Communication Tree

ADT Abstract Data Type

ASN.1 Abstract Syntax Notation One

ASP Abstract Service Primitive

CCITT International Consultative Committee for Telephones and Telegraphs

CCS Calculus of Communicating Systems

CFBR Control Flow Behaviour Representation

CS Coordinated Single-layer

CSE Coordinated Single-layer Embedded

CM Coordinated Multi-layer

DFG Data Flow Graph

DS Distributed Single-layer

DM Distributed Multi-layer

EFSM Extended Finite State Machine

FDT Formal Description Technique

FSM Finite State Machine

HDLC High-level Data Link Control

I/O Input/Output

ISO International Organization for Standardization

IUT Implementation Under Test

LAPB Link Access Procedure

LM Local Multi-layer

LOTOS Language Of Temporal Ordering Specification

LS Local Single-layer

LSE Local Single-layer Embedded

PCO Point of Control and Observation

PDU Protocol Data Unit

PIXIT Protocol Implementation eXtra Information for Testing

REBC Receive Event Base Constraint

RM Remote Multi-layer

RS Remote Single-layer

RSE Remote Single-layer Embedded

RTCDG Reduced Test Case Dependency Graph

SAP Service Access Point

SDL Specification and Description Language

SEBC Send Event Base Constraint

TMP Test Management Protocol

TN Transition Number

TTCN Tree Table Combined Notation

# LIST OF FIGURES AND TABLES

| Figure 1.1 | Protocol layers                                               |

|------------|---------------------------------------------------------------|

| Figure 1.2 | Abstraction of an entity in a multi-entity model 2            |

| Figure 1.3 | Domain of protocol engineering                                |

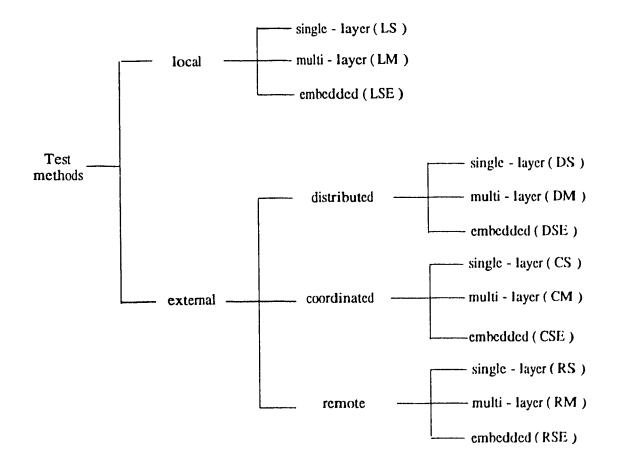

| Figure 1.4 | Abstract test methods 7                                       |

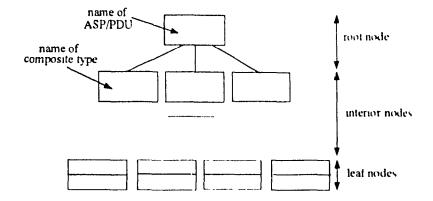

| Figure 2.1 | The components of an I/O diagram 25                           |

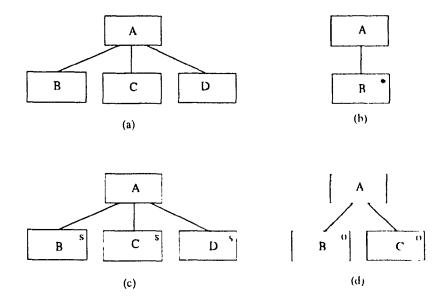

| Figure 2.2 | (a) Sequence. A consists of B, followed by C,                 |

|            | followed by D                                                 |

|            | (b) Iteration: A consists of zero or more repetitions of B 25 |

|            | (c) Unordered sequence: A consists of B, C, and D             |

|            | any order 25                                                  |

|            | (d) Alternation: A consists of B or C not both                |

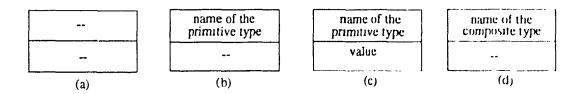

| Figure 2.3 | (a) Optional_leaf_node 25                                     |

|            | (b) Nonoptional_leaf_node 25                                  |

|            | (c) Default_leaf_node 25                                      |

|            | (a) Extension_leaf_node 25                                    |

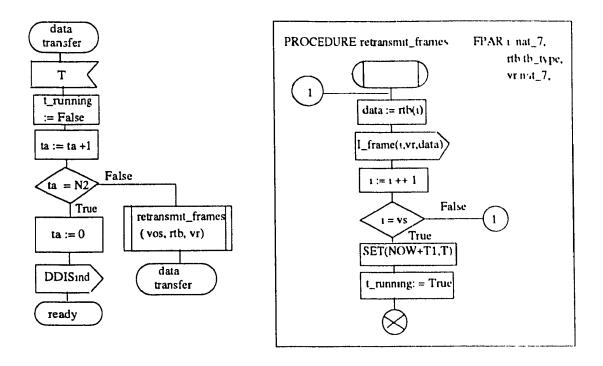

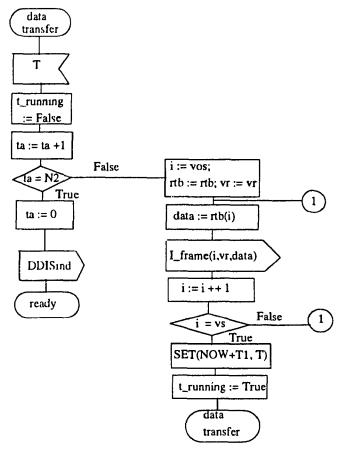

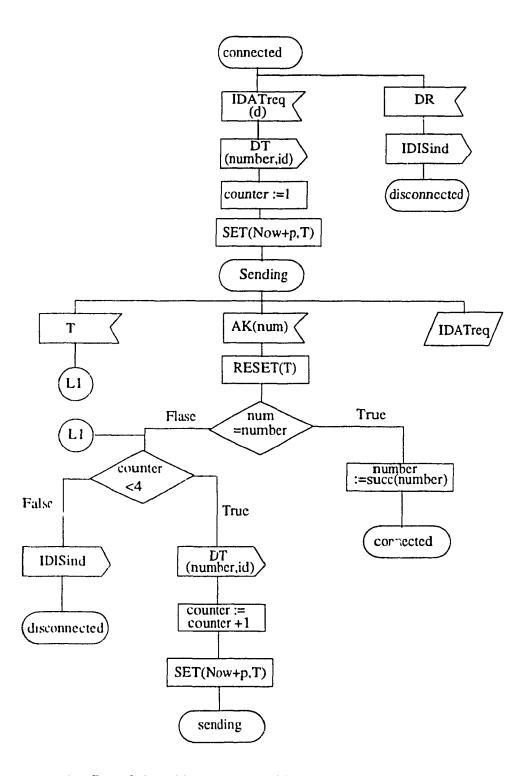

| Figure 3.1 | Data transfer process HDLC and the procedure                  |

|            | retransmit-frames 51                                          |

| Figure 3.2 | After elimination of procedure call                           |

|            | retransmit-frames 52                                          |

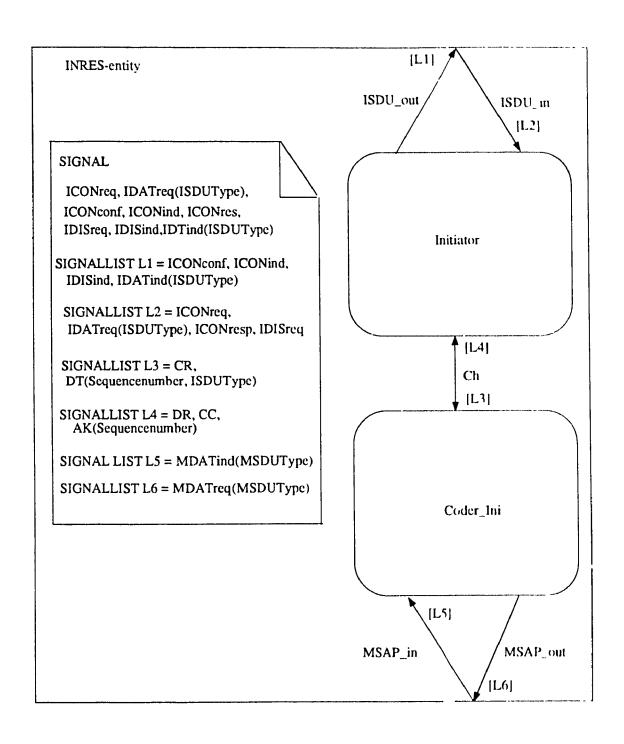

| Figure 3.3 | Definition of INRES_entity                                    |

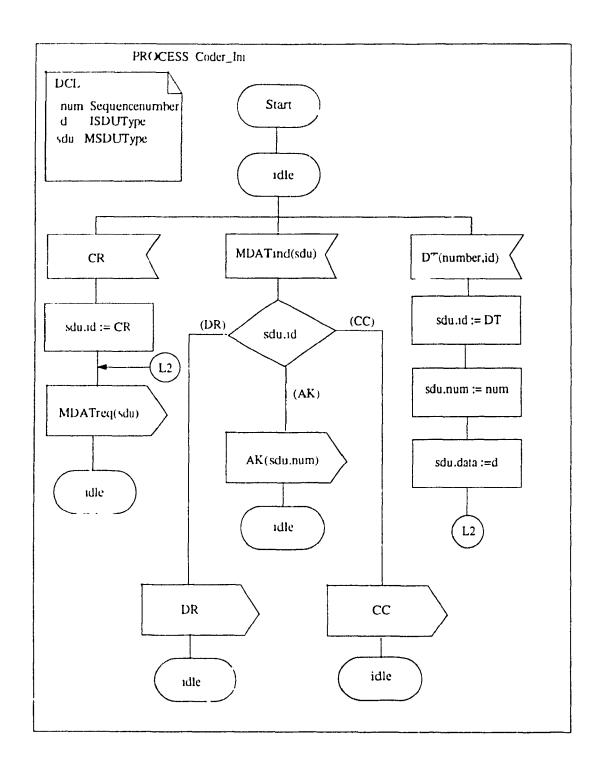

| Figure 3.4 | Coder_Ini process 53                                          |

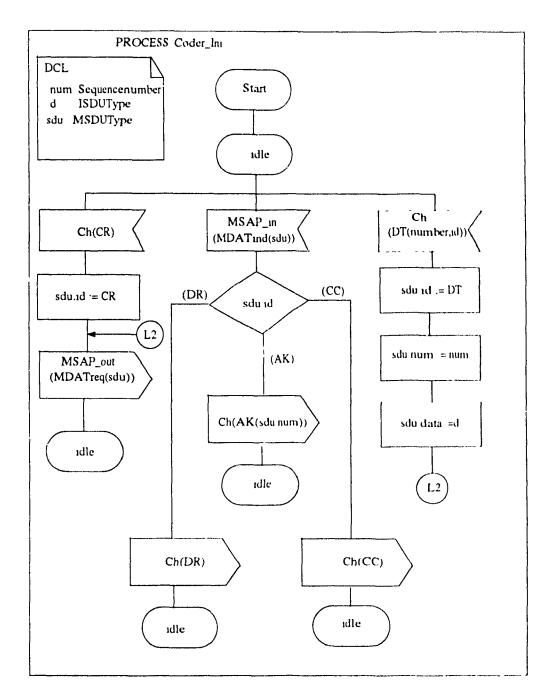

| Figure 3.5 | Modified Coder_Ini process 55                                 |

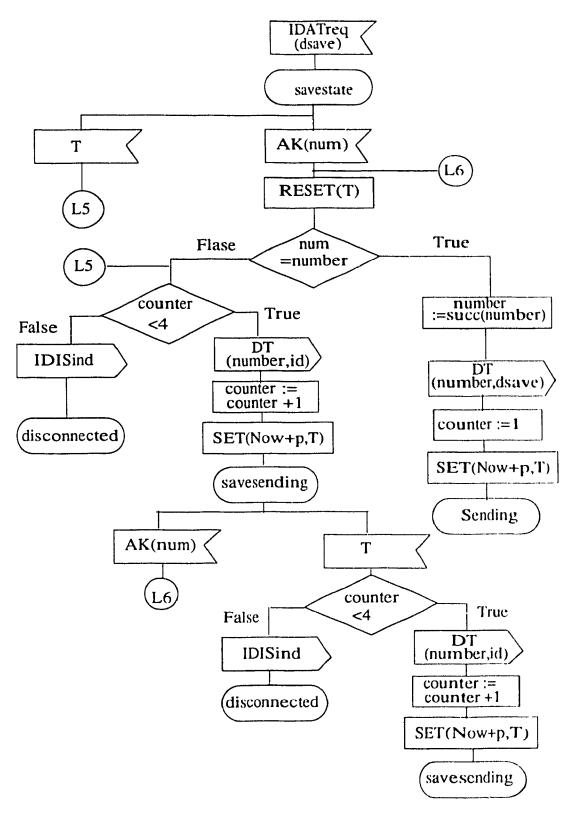

| Figure 3.6 | Part of the Initiator process of Inres protocol               |

|            | with Save construct                                           |

| Figure 3.7 | Behaviour that may be replaced for Save                       |

|            | construct IDATreq 57                                          |

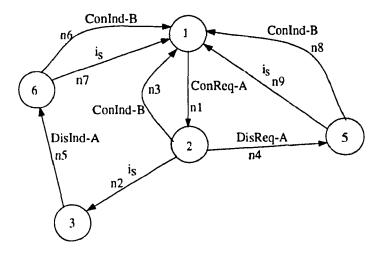

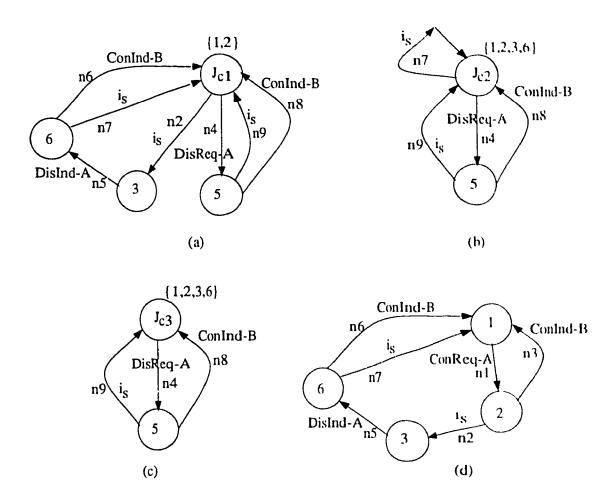

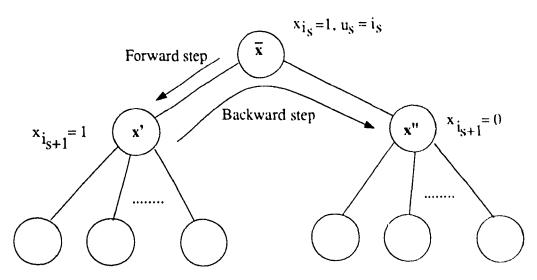

| Figure 4.1 | Transport service specification chart                         |

| Figure 4.2  | (a) $m_{c1}$ , condensed chart $m@R_s$                                |

|-------------|-----------------------------------------------------------------------|

|             | (b) m <sub>c2</sub> , condensed chart m <sub>c1</sub> @C <sub>1</sub> |

|             | (c) $m_{c3}$ , condensed chart $m_{c2}@n7$                            |

|             | (d) A test case of transport service specification 67                 |

| Figure 4.3  | Search tree                                                           |

| Figure 4.4  | test case dependency graph of the test case t <sub>1</sub>            |

| Figure 4.5  | Predicate slices of the test case dependency graph t <sub>1</sub>     |

| Figure 4.6  | Reduced test case dependency graph of the test case t <sub>1</sub>    |

| Figure 5.1  | The LS test architecture                                              |

| Figure 5.2  | Suitable structure for a single-layer test suite 105                  |

| Figure 5.3  | The RS test architecture                                              |

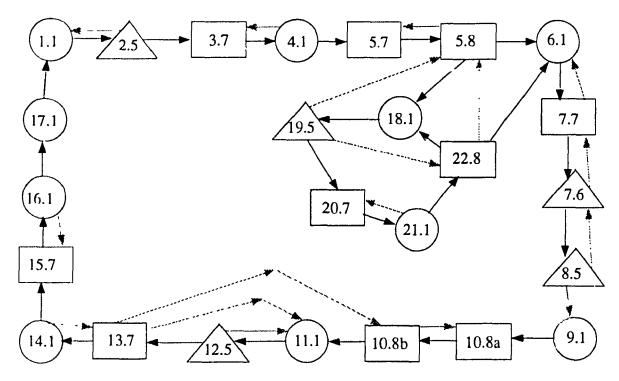

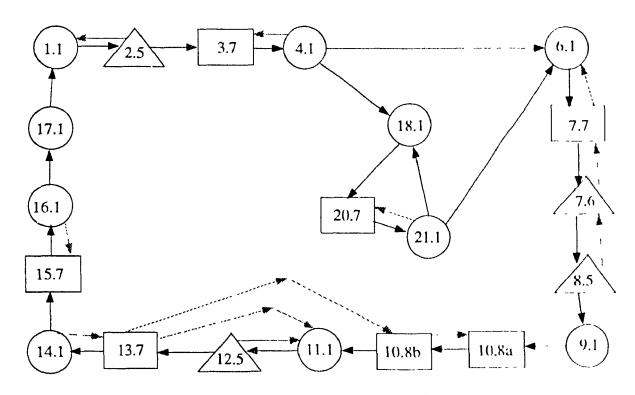

| Figure 6.1  | Global structure of LOTEST 114                                        |

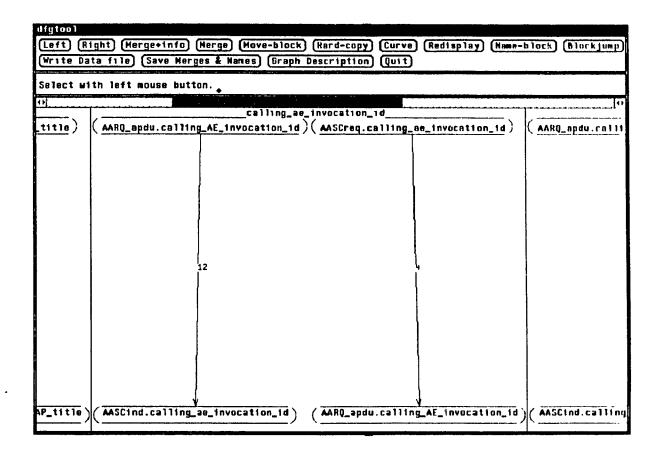

| Figure 6.2  | A part of the ACSE data flow graph displayed                          |

|             | by LOTEST 118                                                         |

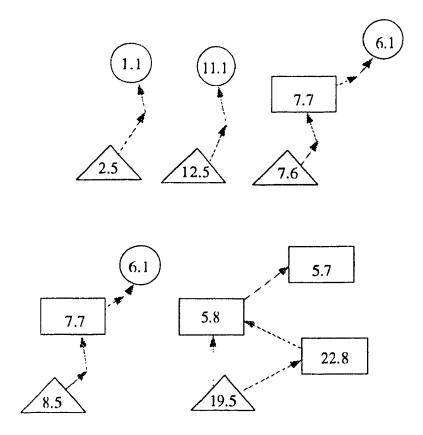

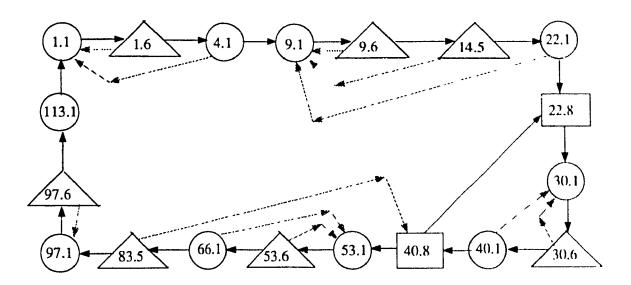

| Figure 6.3  | Test case dependency graph for t <sub>27</sub>                        |

| Figure 6.4  | Predicate slices of the dependency graph t <sub>27</sub> 120          |

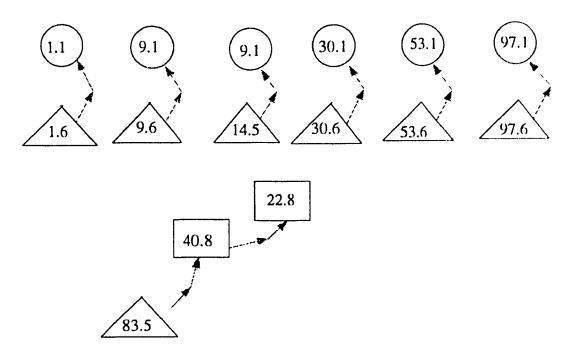

| Figure 6.5  | Reduced test case dependency graph of test case t <sub>29</sub>       |

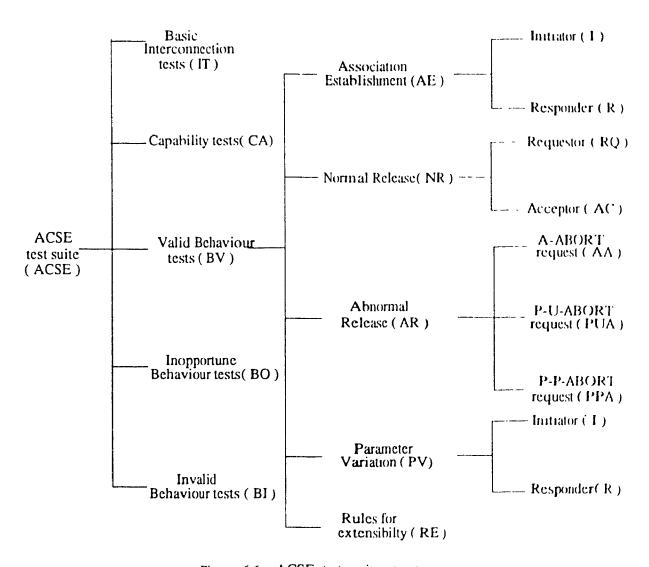

| Figure 6.6  | ACSE test suite structure                                             |

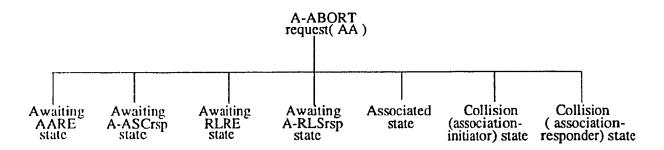

| Figure 6.7  | Test purpose of the test subgroup A-ABORT request 125                 |

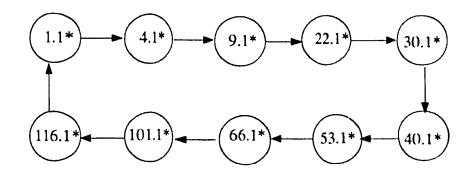

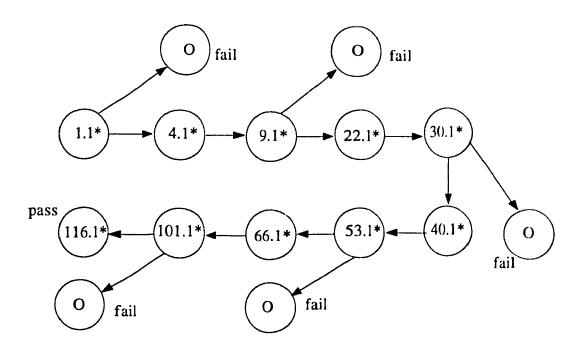

| Figure 6.8  | Control flow behaviour representation of the RTCDG                    |

|             | of t <sub>29</sub>                                                    |

| Figure 6.9  | Enhanced CFBR of the selected test case t <sub>29</sub>               |

| Figure 6.10 | A part of the HDLC data flow graph 129                                |

| Figure 6.11 | Test case dependency graph for t <sub>17</sub>                        |

| Figure 6.12 | Predicate slices of the dependency graph t <sub>17</sub>              |

| Figure 6.13 | Reduced test case dependency graph of test case t <sub>17</sub>       |

| Figure 6.14 | Control flow behaviour representation of the RTCDG                    |

|             | of t <sub>17</sub>                                                    |

| Figure 6.15 | Enhanced CFBR of the selected test case t <sub>17</sub> | 133 |

|-------------|---------------------------------------------------------|-----|

| Table 2.1   | The ASN.1 primitive types                               | 18  |

| Table 2.2   | The principal ASN.1 constructors                        | 18  |

#### CHAPTER I

#### INTRODUCTION

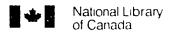

A computer communication protocol, or simply protocol, is a set of rules that govern the communication and interaction between various components in a distributed system. In order to organize the complexity of these rules, they are usually partitioned into a hierarchical structure of protocol layer entities (Figure 1.1), each built upon its predecessor layer.

Figure 1.1 Protocol layers.

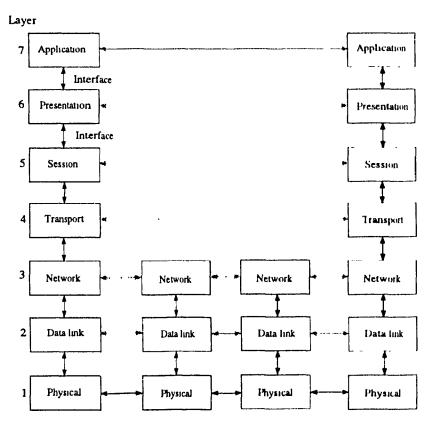

Although the number of layers may differ from network to net work, the purpose of an entity at layer N is to provide certain services, called (N)-services, to its upper layer entity using the services provided by the (N-1) layer while isolating the implementation details of the lower entities from the upper layers. Peer (N)-entities communicate with

each other through the (N-1)-service provider by using the (N)-protocol (Figure 1.2). An (N)-protocol defines the rules and conventions for the communication between two (N)-entities.

Figure 1.2 Abstraction of an entity in a multi-entity model.

Protocol design is not a new problem. The informal techniques traditionally used for designing and implementing many practical protocols have been largely successful, but also yield a disturbing number of errors or unexpected and undesirable behaviours in most protocols. The protocols being developed today are larger and more complicated than even before, and the automation of the whole design process is highly desirable. The fundamental and challenging problem that a protocol designer now faces is how to design a large set of communication and interaction rules for information exchange in such a way that the rules are minimum, logically consistent, complete and efficiently implemented.

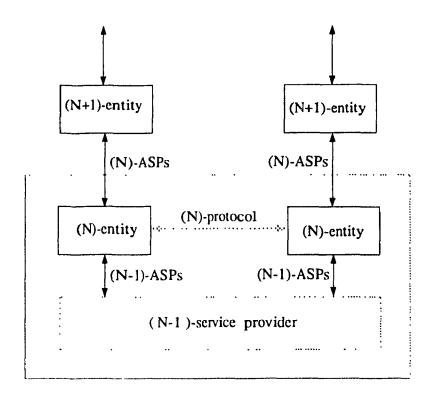

Recently, formal methods and software engineering methodologies have been extensively applied to protocol design. As a result, a new field called protocol engineering [39]

has emerged. The domain of protocol engineering includes protocol and service specification, protocol validation and verification, protocol synthesis, protocol conversion, performance analysis, automatic implementation and conformance testing (see Figure 1.3). Protocol specification plays a key role in all these activities, and the use of formal specification allows the partial automation of some of these activities.

Figure 1.3 Domain of protocol engineering.

#### 1.1 FORMAL SPECIFICATION

Many different formal specification languages have been developed for various purposes, and many of them have been applied to the description of distributed systems and communication protocols. The most important approaches are finite state machines (FSM), formal grammars, Petri nets, algebraic calculi, abstract data types, programming languages, logic programming and temporal logic. Various extensions of the above approaches have been defined by combining them with programming language or abstract data type approaches for the description of parameter values. In addition to the above formal methods, CCITT and ISO have developed so-called Formal Description Techniques (FDTs) for the description of protocol and services, namely Estelle [7], LOTOS [4] [26], and SDL [2], [9].

In Estelle, the specification module is modeled by an extended finite state machine. The interaction parameters and state variables are covered by type definitions, expressions and statements of the Pascal programming language. In addition, certain Estelle statements cover aspects related to the creation of the overall system structure consisting, in general, of a hierarchy of module instances. Communication between modules takes place through the interaction points of the module, which have been interconnected by the parent module. Communication is asynchronous, that is, an output message is stored in an input queue of the receiving module before it is processed.

LOTOS, a process algebraic language, is a combination of the Calculus of Communicating Systems (CCS) [41] formalism for behaviour description and Abstract Data Types (ADTs) called ACT ONE [13] for data description. A set of *composition rules* are used to derive larger specifications from the primitive notions of *event* and *processes*. A set of processes communicate among themselves through synchronization. Rather than simple value passing as in Estelle, LOTOS processes can agree on a common value when rendezvous is achieved.

SDL has the longest history. A subset of the present language was already recommended by CCITT in 1980. It is based on an EFSM model. For interaction parameters

and state variables, it uses the concepts of abstract data types with the addition of a notation of program variables and data structures, similar to what is included in Estelle. The communication is asynchronous and the destination process of an output message can be identified by various means, including process identifier or channel names. In contrast to other FDTs, SDL was developed, right from the beginning, with an orientation towards a graphical representation. The language includes graphical elements for the FSM aspects of a process and the overall structure of a specification.

In addition to FDTs described above, CCITT and ISO developed semiformal techniques Abstract Syntax Notation 1 (ASN.1) [28] for interaction parameters and Tree Tabular Combined Notation (TTCN) [30-31] for specifying test suites.

The Abstract Syntax Notation One was originally developed in conjunction with CCITT recommendations of 1984 on message handling systems. It is a notation for describing data structures, similar to data type definitions available in programming language such as Pascal or ADA. It is applied to the description of OSI application layer protocols, where it is used for the definition of the protocol data units (PDUs). Protocol data units are messages exchanged between different protocol entities. The same notation can also be used to define service primitives and PDUs of other layers. The notation includes a number of predefined data types, such as integers, reals, booleans, bit strings, octet strings and various kinds of character strings. It also allows the definition of composed data types, such as a group of elements (called SEQUENCE, corresponding to "record" in Pascal), a list of identical types (called SEQUENCE OF), a type of alternatives (called CHOICE, corresponding to Pascal's variant records), a tag defining a code to distinguish between different alternatives, and others.

The TTCN is relatively recent, and has been developed for the description of test cases for ISO conformance test suites [55]. The language includes several different notations. The overall organization of the language is in terms of a collection of tables defining different aspects of a test case, such as service primitives, PDUs and their parameters, order of interactions and constraints on parameter values. The interaction ordering is

defined in terms of a conceptual tree, where each branch represents a possible execution order. In addition to the tabular notation, a linear form of TTCN is being developed for the exchange of test cases in machine-readable form. The ASN.1 notation can also be used for certain aspects of test descriptions.

#### 1.2 CONFORMANCE TESTING

OSI protocols are presently being implemented by a large number of computer manufacturers and communication companies. In order to achieve global interworking among heterogeneous systems, the most practical means is testing. There exist three types of testing: performance, interoperability and conformance testing. The aim of conformance testing is to check the conformance of the implementations to the protocol standard. Protocol implementations can be tested by considering a single-layer, multi-layer, or embedded entity as a whole and stimulating the entity from the layers above and below and observing the reactions of the Implementation Under Test (IUT). Stimulation/observation is done by sending/receiving (N)-service primitives, also called (N)-Abstract Service Primitives (ASPs) and (N-1)-ASPs (the latter including (N)-PDUs) by an entity called the tester. Service Access Points (SAP) used by the tester for this purpose are called Points of Control and Observation (PCO).

## 1.2.1 Test Method Overview

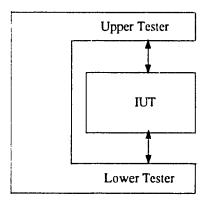

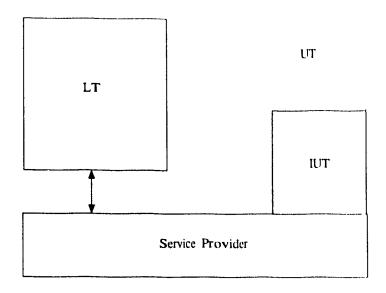

Various abstract methods [46] (Figure 1.4) are defined by ISO and CCITT based on the control and observation (i.e., availability of the ASPs) in an Implementation Under Test (IUT). The two main classes of test methods are *local* and *external*. In *local* test methods points of control and observation are defined at the lower and upper entities of the IUT. In other words, (N)-PDUs, (N)- and (N-1)-ASPs are assumed to be available such that upper and lower testers can control and observe them. External test methods, on the other hand, are characterized by the observation and control of PDUs taking place, on the other side of the underlying service provider from the IUT.

There are three types of external test methods: distributed, coordinated, and remote. Each comes in three variant forms: single-layer, multi-layer, and embedded. Single-layer methods are designed for testing a single-layer without reference to the layer above it. Multi-layer methods are designed for testing a multi-layer IUT as a whole. Embedded methods are designed for testing a single-layer within a multi-layer IUT, using knowledge of what protocols are implemented in the layers above the layer being tested. The external test methods vary according to their ability to define a test management protocol (TMP) to carry out the test coordination procedures or to express the test coordination procedures only in terms of requirements.

Figure 1.4 Abstract test methods.

## 1.2.2 Types of Testing

The objective of the conformance testing is to establish whether the implementation being tested conforms to the specifications in the relevant standard. Practical limitations make it impossible to be exhaustive, and economic consideration may further restrict testing. Therefore, four types of conformance testing are recommended by ISO, according to the extent to which they provide an indication of conformance.

- i) Basic Interconnection Test: This provides a limited testing to check that the IUT can establish a basic interconnection before thorough testing is performed.

- ii) Capability Tests: This is used to check that the IUT can provide the observable capabilities based on the static conformance requirements, which are the requirements describing the options, ranges of values for parameters and timers, etc.

- iii) Behaviour Tests: They test the dynamic conformance requirements of an IUT which are the requirements (and options) defining the observable behaviour of a protocol. A large part of behaviour tests, which constitute the major portion of conformance tests, can be generated from the formal specification.

- iv) Conformance Resolution Tests: These tests are used to provide definite diagnostic answers to specific requirements, such as previously identified situations that may cause incorrect behaviour of an IUT. For example, they provide a yes/no type of answer for whether a particular feature, such as reset, is implemented in an IUT.

In addition to conformance testing, the following types can be performed on an IUT depending on the application: *interoperability tests*, to check whether two or more implementations that pass the conformance tests can operate together, *performance tests*, to measure the maximum throughput that can be obtained, and *robustness tests* to determine how well an IUT recovers from various error conditions.

#### 1.2.3 Test Suite Structure

The test events, atomic interactions between the IUT and the upper or lower tester used in conformance testing, are described in an abstract conformance test suite. The

tests are represented in a hierarchical structure. The key level is called the *test case* which has a narrowly defined purpose. Test groups consist of several test cases according to a logical ordering of execution. A test case is divided into test steps each of which consists of several test events. Once the test cases are designed, they can be written in a test notation such as TTCN.

#### 1.3 TEST SUITE DESIGN

Designing test cases (suites) can be considered to be the most active research area of protocol testing. Research in this area is inspired from the rich results obtained previously in hardware/software testing. Nevertheless, it is evolving towards its own set of techniques, tools and disciplines, possibly due to the distinct characteristics of protocols and their architectures. We will discuss the existing protocol test case design based on FSM, Estelle, LOTOS and SDL.

## 1.3.1 FSM Based Test Design

Protocols are typically modeled as an extended finite-state machine [3] where the control portion is the finite state machine and the data portion consists of the program segment. The control portion of a protocol (henceforth referred to as the protocol for simplicity) can be specified as a deterministic finite state machine (FSM) [35]. The state of a protocol is defined as a stable condition in which the protocol rests until a stimulus, called an input is applied. The protocol generates a response to the stimulus, called output, (which may be null) when an input is applied, and moves into a new state (which may be the same as the previous state) where it stays until the next input. This exercise is complicated by the limitations on the controllability and the observability of the protocol implementation. In most cases, because of the limited controllability, the implementation cannot be directly put into a desired state, usually requiring several additional state transitions. Unless efficient solutions are found, this limitation may result in test sequences with infeasibly large numbers of state transitions. Limited

observability prevent the external tester from directly observing the state of the protocol implementation, which is critical for a test to detect errors.

Typically, the formal conformance testing techniques generate a set of input sequences that will force the FSM implementation to undergo all specified transitions. These techniques can be classified [11] as the transition tour method [44], [51], [63], the distinguishing sequence method [43], [17–18], [21], [35], the characterizing sequence method [18], [21], [10], [35], and the unique input/output sequence method [48–49], [1]. All of these techniques assume the so-called black box approach where only the outputs generated by the implementation (upon receipt of inputs) are observable to the external tester.

The transition tour method generates a state tour that exercises every state transition of the implementation [44], [51] and does not address the observability problem described above. For certain protocols, which have a special message to determine the state of the protocol (i.e., the observability problem is solved by the specification), the length of the tour can be minimized by the technique given in [63], which is based on a graph theoretic concept called the *Chinese Postman Problem* [36].

The remaining three methods emphasize the observability problem. In the distinguishing sequence method, an input sequence is found for a protocol such that the outputs generated by the implementation will identify its state. The requirement for this method is a fully specified protocol, which may be too strong for most actual protocols. The characterizing method defines a set of input sequences for a subset of states such that the resulting set of output sequences ultimately distinguishes each state from the others. In both of these methods, the current state of the implementation is assumed to be unknown and the sequences generated by them are powerful enough to find the current state. In other words, both the distinguishing and characterizing sequences answer the question of "what is the current state of the implementation?". However, in the unique input/output sequence method, this question is relaxed to "is the implementation currently in state x?", which results in much shorter sequences than the other two methods. A minimization

of the resulting sequences generated by the unique input/output method is given in [1], which is based on a more general form of the Chinese Postman problem called the Rural Chinese Postman problem. Experience with this method indicates that the test sequences generated are about one-third the size of those generated by ad hoc methods [1].

All of the above methods are based on the deterministic finite state machine. Systematic test design methods from the nondeterministic finite state machine are not yet well developed. This topic will be discussed in chapter V of the thesis.

## 1.3.2 Estelle Based Test Design

Since deterministic FSMs model only the control component of the protocol/services, there is a need to extend the FSM-based techniques to cover the data component, i.e., interaction primitive processing and data transfer mechanisms. Recently, two methods have been proposed to design test cases for testing the data flow aspects of an IUT. Both methods assume that protocol specifications are given in Estelle as a single module specification called a normal form specification. The first method [61-62] is based on data flow analysis techniques [45] and focuses on tracing the flow of data through the associations between assignments of values to variables and references of these variables in either assigning values to other variables or determining the outcome of conditional branching. The second method [52], [15], applies the principles of functional testing [25]. In the functional testing method two different graphs are obtained from the normalized specification: a control graph for major state changes and a data flow graph to show the flow of data from input service primitive/protocol data unit parameters to the context variables and from the context variables to output service primitive/protocol data unit parameters.

The Control graph is an FSM, thus the techniques described in section 1.3.1 are applicable. The data flow graph shows global flow of data over context variables. The data flow graph is partitioned into blocks, where each block corresponds to functions of the protocol. Test suite design with this methodology is based on obtaining the control

sequence for a test case and enumerating the parameters of the interaction primitives. Each block is tested with one or more test cases until all the arcs in the partitioned data flow graphs are covered. The resulting tests are used as behaviour tests for establishing the dynamic conformance of IUTs.

The above method is used in designing test suites from a more general : todel called an EFSM chart in this thesis. We use the zero-one integer programming technique for selecting the test cases, which will adequately exercise the protocol functions identified from the data flow graph. The zero-one integer programming technique is used in the path selection problem in software testing [65].

## 1.3.3 LOTOS Based Test Design

There has been much research on test suite generation from LOTOS specifications. The first related work can be found in [6] and [66], where the derivation of conformance testers T(S) for any specification S has been investigated. In [6] a failure model is used to identify processes that are testing equivalent, whereas in [66], a syntactical approach is explored, based on the work reported in [56]. The method is named the CO-OP method after its main components, the sets named COmpulsory and OPtional behaviours. At present the CO-OP method can produce canonical testers for basic LOTOS behaviour expressions that do not contain process abstraction. A conformance tester is not intended for practical testing, because of data, which is a significant aspect of protocol testing, not considered in the derivation of T(S) from the specification S, although some efforts to extend the approach have been reported [59].

In another related work [19], where manually an FSM model is derived by using LOTOS interpreter [40], classical methods are then applied to generate test cases. The authors have not yet considered the data flow aspect with the interpretation approach. Recently, a group of researchers at Neher laboratories [8] proposed an interactive methodology to generate test cases from a LOTOS specification. A symbolic evaluation

is used to derive test cases in the form of TTCN. However, the methodology is not algorithmic in nature. It is similar to the method proposed in [19].

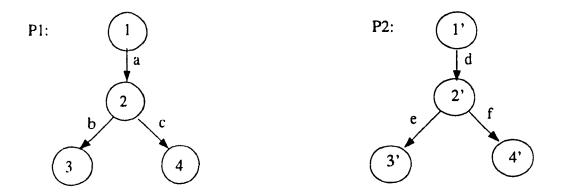

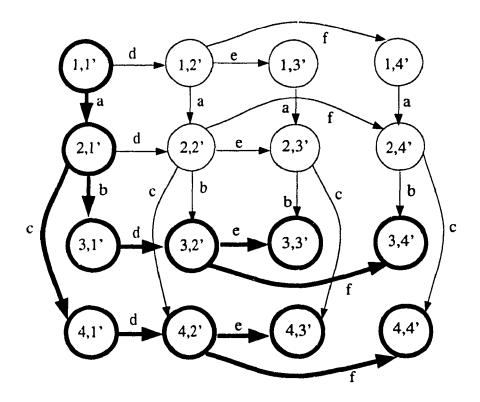

## 1.3.4 SDL Based Test Design

Generation of test suite from SDL has been studied by Hogrefe[23]. In this model SDL processes are transformed into an intermediate form called the asynchronous communication tree (ACT). The ACT is a tree, where the root is the initial system state, the nodes are all other system states and the arcs represent the valid transitions. The tree is constructed by considering in turn every possible distinct event that may occur at each node. The arc is labeled with the event and the node is identified by the resulting process states and queue contents. The depth of the tree is restricted by comparing the current state with the states generated previously; if an identical state is found, that branch is terminated. Finally, this ACT is traversed to generate test cases. Nondeterminism has not been taken into consideration in the generation of test cases. The test generation algorithm proposed in this thesis, which deals with nondeterminism, can be used to generate a test suite from an ACT.

## 1.4 OBJECTIVE AND MOTIVATION

Among the problems of protocol engineering, conformance testing is the most important one. An efficient solution of this problem will demonstrate networks in which components made by different manufacturers can interwork properly and effectively, which in turn is necessary to fulfill the requirements of the OSI standard. Therefore, the main objective of this thesis is the development of algorithms for frequently encountered problems in test suite design.

In the last decade, a large number of algorithms have been proposed to design test suites from formal specifications. The emphasis in most of these algorithms is placed on fault detection capability and optimization of the generated test suites. However, the test architectures have not been taken into consideration in the design of test suites. Moreover,

the test generation procedure is restricted to the deterministic model. In this thesis, the emphasis is placed on the development of new algorithms, which are general in nature, through a more efficient formulation of the formal model. Thus, our intention is to give a unified formal model for generation and representation of test cases. The methodology has to be conceptually simple, easy to implement, computationally efficient, and general in nature.

#### 1.5 ORIGINAL CONTRIBUTIONS

In the following, we outline a set of individual contributions which, when combined together, give rise to a test suite design methodology.

We introduce the unified model using the EFSM chart and the I/O diagram. The EFSM chart model is used to describe the behaviour of the protocol, and the I/O diagram model is used to describe the structure of ASPs/PDUs. Algorithms are presented to translate protocols specified in LOTOS or SDL into EFSM charts.

We present a new test generation algorithm, which takes nondeterminism into consideration. Furthermore, we propose an algorithm for the construction of the data flow graph that is used to identify the protocol functions.

We model a test case by a dependency graph and evaluate it by taking predicate slices. We propose two new algorithms to eliminate redundant assignments and predicates from the test case. The first one is based on the test case dependency graph and the second one is based on the data flow graph.

We propose algorithms to generate base and dynamic constraints. We obtain control flow behaviour algorithmically by inverting the direction of the actions and eliminating all the predicates from the test case dependency graph. Finally, we design test suites for RS and LS architectures.

We develop LOTEST, a computer aided software tool that partially implements our test suite design methodology for a LOTOS specification.

### 1.6 OUTLINE OF THE THESIS

This thesis presents a new methodology for the analysis and formulation of new algorithms for solving basic problems of conformance testing. The layout of the thesis is as follows. In Chapter II, the concepts of the EFSM chart and the I/O diagram are introduced. Chapter III is concerned with chart construction algorithms. New algorithms for generation and evaluation of test cases are proposed in chapter IV, while chapter V deals with test case representation. In particular, the main contents of each chapter are as follows:

## Chapter II: Unified Model.

This chapter introduces ASN.1, SDL, LOTOS, the Extended Finite State Machine(EFSM) chart and the Input/Output diagram to be used throughout the thesis. The structure of ASPs/PDUs is briefly discussed. Also this chapter presents the relationship between I/O diagrams and abstract data types.

## Chapter III: EFSM Chart of Specifications.

Algorithms to translate protocol specifications into Extended Finite State Machine Chart are developed in this chapter. The algorithm proposed by Karjoth [34] to translate a subset of LOTOS into EFSM chart is extended to full LOTOS and to SDL.

## Chapter IV: Generation and Analysis of Test Cases.

Based on the EFSM chart, a new test suite generation algorithm is proposed, which takes nondeterminism into consideration. Furthermore, a new algorithm for the construction of data flow graph from the chart is developed, which is used to identify the protocol functions for testing the data flow aspect of an IUT. The zero-one integer programming technique is used to select test cases that are optimal in nature to meet certain test coverage requirements or to exercise certain protocol functions adequately. The generated test cases are modeled as a test case dependency graph and then evaluated by taking predicate slices from it. After a brief review of program slicing [64], we introduce the concept of predicate slices that are used to identify infeasible test cases that must be eliminated. Redundant

assignments and predicates in all the feasible test cases are removed by using the test case dependency graph as well as using the data flow graph.

Chapter V: Test Suite Selection and Representation.

Test cases generated from specifications define the behaviour of an IUT. The behaviour of LT and UT considered together comprise the tester's behaviour. The tester's behaviour is the dual of IUT's behaviour. Therefore the tester's behaviour can be obtained by behaviour inversion. Behaviour inversion is based on viewing each test case as an extended finite-state machine. Complete behaviour generation of the test case EFSMs is a complex process consisting of several steps. In the previous chapters we discussed the steps of specification transformation, test case generation and test case reduction. In this chapter we discuss how the control flow representation can be obtained followed by input/output data flow representation. The control flow representation refers to the steps of inverting the interaction whereas input/output data flow representation refers to the generation of base and dynamic constraints on the events, which are in the form of an I/O diagram. New algorithms are developed to generate base and dynamic constraints for receive and send events. Specification of tester's behaviour in a test case is completed by test selection. Assuming a test case hierarchy with test purposes as leaf nodes, the selection process associates a purpose to each test case and using this information, a verdict is associated with some of the events. Finally the test cases are adapted for the RS architecture.

## Chapter VI: Applications.

We applied the test design methodology to two protocols: Association Control Service Element(ACSE) protocol written in LOTOS specification language and LAPB protocol written in SDL specification language.

## Chapter VII: Conclusions and Future Work.

Basic contributions of the research described in this thesis are summarized. Also, possible extensions of the results to specific, or perhaps, new problems are discussed.

#### CHAPTER II

#### UNIFIED MODEL

In this chapter we give an overview of ASN.1, SDL, LOTOS and some other concepts. We provide an abstract syntax of algebraic data types in order to describe the data world on which the unified EFSM chart model is defined. Furthermore, we propose a unified model to describe the structure of ASP/PDUs: Input/Output(I/O) diagram, a graphical notation based on Jackson Structured Programming [33]. Representation of ASN.1 in terms of I/O diagrams is discussed first. The signature part of the abstract data type definition of ASP/PDUs can also be represented in the form of I/O diagram, which is discussed next. The I/O diagram will be used in test case representation.

### 2.1 ABSTRACT SYNTAX NOTATION 1

The key to the whole problem of representing, encoding, transmitting and decoding data structures is to have a way of describing the data structures that is flexible enough to be useful in a wide variety of applications, yet standard enough that everyone can agree on what it means. As part of the OSI development work, ISO has devised just such a notation. It is called abstract syntax notation 1 or ASN.1 for short.

The ASN.1 primitive types are listed in Table 2.1. These types are built into the language and form the building blocks for more complex types. The names of these types are reserved words, and, like all ASN.1 reserved words, are always written in upper case letters.

| Primitive type    | Meaning                       |

|-------------------|-------------------------------|

| INTEGER           | Arbitrary length integer      |

| BOOLEAN           | TRUE or FALSE                 |

| BIT STRING        | List of 0 or more bits        |

| OCTET STRING      | List of 0 or more bits        |

| ANY               | Union of all types            |

| NULL              | No type at all                |

| OBJECT IDENTIFIER | Object name (e.g., a library) |

Table 2.1 The ASN.1 primitive types.

The primitive types can be combined to build more complex types. Table 2.2 shows the five principal constructors used in ASN.1 for this purpose.

| Constructor | Meaning                                      |

|-------------|----------------------------------------------|

| SEQUENCE    | Ordered list of various types                |

| SEQUENCE OF | Ordered list of a single type, like an array |

| SET         | Unordered collection of various types        |

| SET OF      | Unordered collection of a single type        |

| CHOICE      | Any one type taken from a given list         |

Table 2.2 The principal ASN.1 constructors.

In addition to the primitive types and the constructed types, the ASN 1 standard also discusses some predefined types that are useful in many applications. Eight different string types are defined. Each one is a different subset of OCTET STRING. The NumericString only includes the ten digits 0 through 9 and the space. The PrintableString includes the

upper and lower case letters, the ten digits, space, and the 11 characters in quotes: "()' + -., /:=?". Other string types are provided for the teletex character set, the videotex character set, various international version of ASCII, and some graphics character sets.

Another useful type is *GeneralizedTime*. Using this format avoids endless discussion about whether 5/12 is the 5th of December or the 12th of May. An example value of *GeneralizedTime* is 19910704210538.3, which represents 5 minutes, 38.3 seconds after 9 P.M. on the Fourth of July, 1991.

In practice, it is common to define complex data types many of whose fields are optional. For example, CONNECT REQUEST PDUs frequently have a large number of optional parameters. If these parameters are not used for a particular connection establishment, they need not be transmitted. To handle this situation, ASN.1 allows fields to be declared OPTIONAL. Alternatively, they can be declared DEFAULT, followed by the value to be used by the receiver if the field is not transmitted. The existence of OPTIONAL and DEFAULT types potentially causes problems with identifying the data when they are received. Suppose that a SEQUENCE has ten fields, all of them are of type INTEGER and all OPTIONAL. Now suppose that only three of them are transmitted. How does the receiver know which three they are?

This problem is solved by the concept of tagging. Four types of tags are allowed: UNIVERSAL, APPLICATION, PRIVATE, and CONTEXT SPECIFIC. Each tag consists of an integer, preceded by one of the reserved words UNIVERSAL, APPLICATION, PRIVATE, or no reserved words, in which the tag is CONTEXT SPECIFIC. Tags are written in square brackets.

#### 2.2 SDL SPECIFICATION LANGUAGE

SDL, the specification and description language adopted by CCITT, is a standard for specifications of telecommunication systems. The language is built around the following concepts:

- i. structure, which is described hierarchally by elements called systems, blocks, channels, processes, signal-routes and signals;

- ii. behaviour, which is described using an extension of the finite state machine concept;

- iii. data, which is defined as abstract data types with the type algebra ACT ONE [13];

- iv. communication, which is asynchronous via channels and infinite queues.

A SDL specification (a system) consists of a number of blocks interconnected via channels. The channels are the media through which blocks communicate with each other or with the environment. A channel can be unidirectional or bidirectional. A bidirectional channel can be considered as two independent unidirectional channels. The channels are typed, i.e., they can only contain messages of certain types. In SDL the messages are called signals.

A block can contain either a substructure of blocks, or one or several processes interconnected by *signal-routes*. The signal-routes are the media through which processes can communicate with each other inside a block, and with the environment (i.e., everything outside the block). Signal-routes are, like the channels, typed unbounded FIFO queues.

In SDL, behaviour is defined by a set of processes that execute in parallel. To each process is associated exactly one input queue, into which all input signals from different input signal-routes are merged. A SDL process is described by an extended finite state machine, which consists of states and transitions. For each state there is a set of input symbols, each with an associated transition, and a set of save symbols. Signals can only be received from the input queue when the process is in a state, and the reception of a signal is the only event that can cause a transition to a new state to occur. The signals to be received are specified in the input symbols. To each input symbol, an enabling condition can be associated. The signal specified in the input symbol can only be received if the enabling condition evaluates to true. There is also a possibility to specify that some input signals should be bypassed when in a specific state. Such signals are specified in save symbols and are saved in the input queue as explained below.

All signals sent to an SDL process are buffered in the input queue in the order of

arrival, until the process is in a state in which it can accept input. Then there are four possibilities:

- i. The signal at the front of the queue is specified as the beginning of a transition, in which case the signal is consumed by the process; it is removed from the queue and the process executes the associated transition.

- ii. The signal at the front of the queue is specified in a save construct, in which case that signal remains in the queue and the signal behind the saved signal is examined.

- iii. The signal at the front of the queue is neither specified as an input nor as a save, in which case the signal is removed from the queue and the next signal in the input queue is examined.

- iv. The input queue is empty, in which case the process is suspended until a signal arrives to the input queue.

A transition performs a sequence of actions when the process changes state. The actions can be *outputs*, *tasks* and *decisions*. An output transmits a signal to another process. A task is a manipulation of internal data. A decision is a generalized case statement.

#### 2.3 LOTOS SPECIFICATION LANGUAGE

LOTOS is a general-purpose language for specifying sequential, concurrent, or distributed systems based on CCS and ACT ONE concerning the concurrency and data type parts respectively.

LOTOS specifies a process by a behaviour expression that defines an ordering of events. LOTOS provides a set of temporal ordering operators that allow combining and structuring behaviour expression in different ways and so can be used to express important architectural concepts, such as orthogonality, sequential relationship, or non-deterministic operation. The operators inaction, choice, action-prefix, parallel composition, hiding and guarding act as a behaviour data type where the semantics of the corresponding LOTOS

behaviour expressions is given in term of action. Here, we explain briefly the process constructs. The formal definition can be found in [26].

internal action(i;B): A behaviour can nondeterministically choose to be an unobservable internal action, denoted by i. It is called unobservable because it is not an interaction, yet it can cause a change in other behaviour.

action prefix(gd<sub>1</sub> .. d<sub>n</sub>[c], where d<sub>i</sub> = !  $t_i$  or ?  $v_i$  :  $s_i$ ): The components of an action are either ! $t_i$ , denoting the offering of a certain value, or ? $v_i$  :  $s_i$ , offering the range of all values belonging to type  $s_i$ . The selected predicate c restricts the set of event values to those satisfying the predicate.

successful termination ( $exit(t_1, ..., t_n)$ ): The exit construct denotes successful termination of a behaviour. The values contained in it are passed on to the subsequent process. The value can also be any s. Exiting event is composed of an internal action followed by inaction stop.

inaction(stop): The process stop can not perform any action, and therefore does not have a successor behaviour. It is impossible to derive any transition from it.

**local definition**( let  $v_1$ :  $s_1 = t_1$ , ...,  $v_n$ :  $s_n = t_n$  in B): An identifier can be given the value of an expression.

summation (choice  $v_1$ :  $s_1$ , ...,  $v_1$ :  $s_1$  [] B ): This construct denotes the, possibly infinite, choice composition of copies of the behaviour B, where the variable v receives every possible value of the type s.

sequential composition (B1 >> accept  $v_1$ :  $s_1$ , ...,  $v_1$ :  $s_1$  in B2): In this construct the right hand behaviour is enabled by the successful termination of the left hand behaviour. Besides this, the resulting values of the left hand behaviour are assigned to the identifiers  $v_1$ , ...,  $v_n$ .

disabling (B1 [> B2 ): B1 [> B2 behaves like B1, until an event of B2 is performed, after which only events of B2 can occur. Once B1 has terminated successfully, events in B2 are no longer possible.

parallel composition (B1|[  $g_1$  , ...,  $g_n$ ]|B2 ): The expression B1|[  $g_1$  , ...,  $g_n$ ]|B2 allows

both behaviours to proceed independently, except for events on any of the gates  $g_1$ , ...,  $g_n$ . On those gates both processes must synchronize on the same event, which is then one of the events offered by the construct.

choice (B1 [] B2 ): A choice of behaviours offers all the events that any of the behaviour offer. In synchronization with the environment a choice is made, after which the corresponding behaviour results.

**guarding**([t]  $\rightarrow$  B): A behaviour prefixed by a guard is only possible if the guard evaluates to true, and is equivalent to *stop* otherwise.

**hiding**(hide  $g_1$ , ...,  $g_n$  in B): Parallel composition is the mechanism to add processes to a synchronization on an event. Hiding is the mechanism that converts those events into internal events, so that other processes can no longer influence the events.

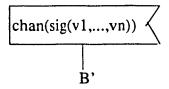

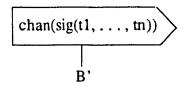

**process instantiation**( $p[g_1, ..., g_n]$  ( $t_1, ..., t_n$ )): The behaviour of a process instantiation is the behaviour of its corresponding definition with the value expression substituted for the value parameter, and the formal gates replaced by actual gates.

The use of abstract data types (ADTs) complements the process part of LOTOS in achieving implementation independence. It is based on the equational specification of ADTs with an initial algebra semantics. An ADT definition identifies a mathematical object, namely an algebra, formed by sets of data values, called data carriers, and a set of associated operators. The name of data carriers are referred to as sorts. The declaration of every operation includes its domain, which consists of a list of zero or more sorts and range, which consists of exactly one sort. The sorts and operations of a data type are referred to as the signature of that data type. The most basic form of data type specification in LOTOS consists of a signature and possibly a list of equations.

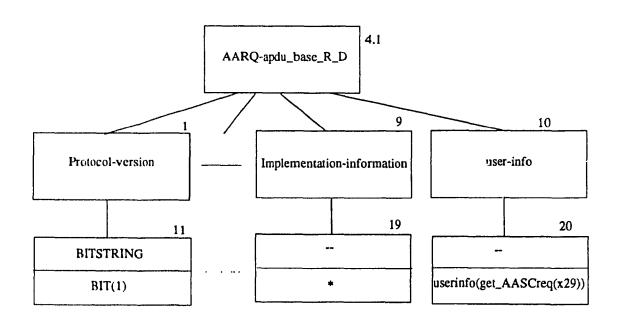

#### 2.4 I/O DIAGRAM

According to the OSI Reference Model, input/output messages of protocol entities are called Abstract Service Primitives (ASPs). Some of the ASPs contain as substructures the Protocol Data Units (PDUs) that are exchanged between two communicating peer

entities. ASPs and PDUs are in general complex data structures containing several substructures. This is specifically true for layer 7, i.e., the application layer. Having recognized this fact, standardization organizations have defined a data definition language called Abstract Syntax Notation One (ASN.1) to precisely specify PDUs [29]. On the other hand specification languages use different techniques to define data, e.g., abstract data types for LOTOS and SDL and Pascal types for Estelle.

The most widely used technique for specifying the important properties of data is the Jackson design method [33]. The Jackson technique is useful to model two fundamental relationships between the elements of data: composition and alternation. Composition occurs when the data in one class is formed by composing data items from a number of different less abstract classes of data items. Alternation occurs when the data in one class consists of data from a number of possible other classes that contain less abstract data entities. In this section, we extend this idea to model ASP/PDU structure, which we call I/O diagram.

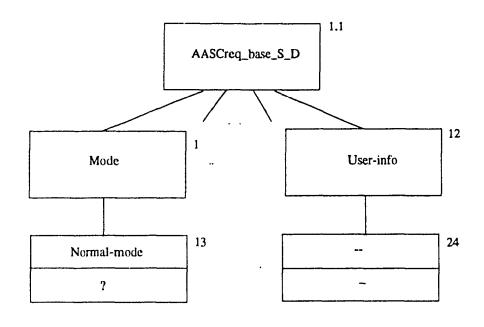

## 2.4.1 I/O Diagram for ASN.1

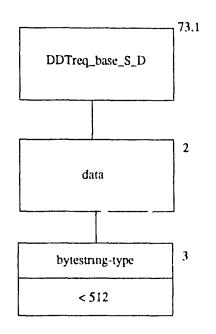

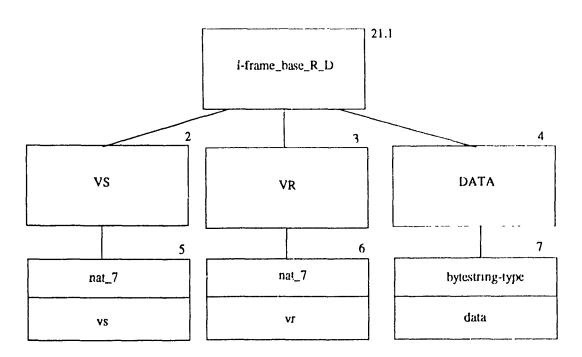

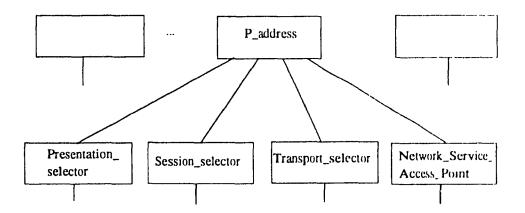

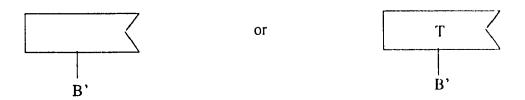

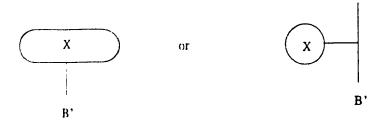

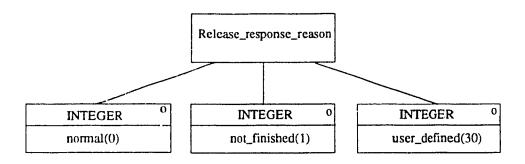

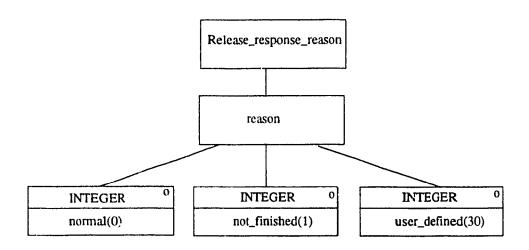

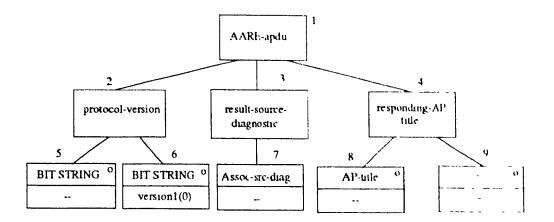

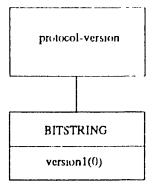

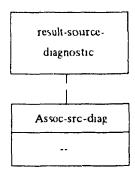

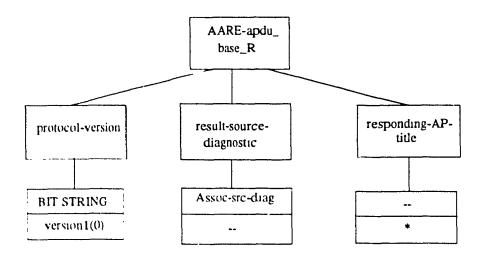

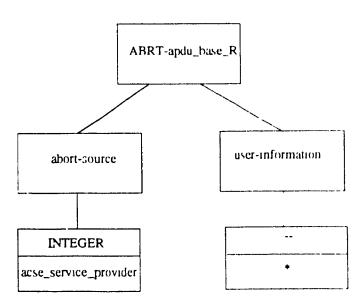

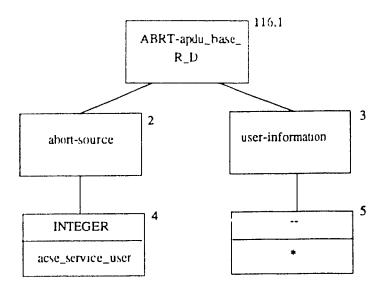

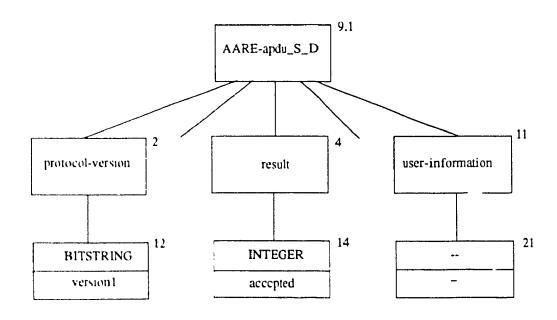

An I/O diagram is a tree as shown in Figure 2.1, whose root node is labeled with the name of the ASP/PDU and whose interior nodes are labeled with the name of composite types. The successors of a node are defined in terms of sequence, unordered sequence, alternation and iteration primitives as shown in Figure 2.2.

Two types of leaf nodes are defined, primitive type and nonprimitive type. We distinguish three kinds of primitive type leaf nodes: optional\_leaf\_node, nonoptional\_leaf\_node and default\_leaf\_node. A primitive type may have a value/range, which appears below the bar dividing the node. There is only one type of nonprimitive type leaf node: extension\_leaf\_node. The first field of the extension\_leaf\_node is labeled with a component type name and the second field is empty. Different kinds of leaf nodes are shown in Figure 2.3. Next, we describe representation of each composite type of ASN.1 using I/O diagram.

Figure 2.1 The components of an I/O diagram.

Figure 2.2 (a) Sequence: A consists of B, followed by C, followed by D. (b) Iteration: A consists of zero or more repetitions of B. (c) Unordered sequence: A consists of B, C and D in any order. (d) Alternation: A consists of B or C not both.

Figure 2.3 (a) Optional\_leaf\_node. (b) Nonoptional\_leaf\_node. (c) Default\_leaf\_node. (d) Extension\_leaf\_node.

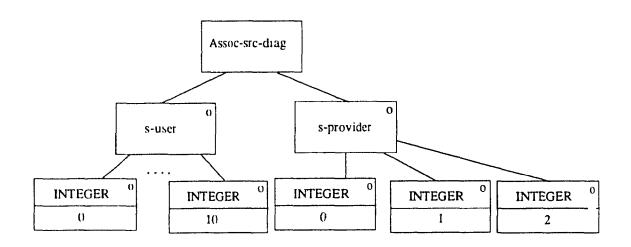

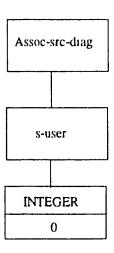

CHOICE: A CHOICE is represented using the alternation primitive. For example, the ASN.1 definition

```

Assoc-src-diag ::= CHOICE

{ s-user INTEGER { null (0), ..., called-AE-invalid-not-recognized(10) },

s-provider INTEGER { null (0), no-reason-given (1), no-common-acse-

version (2)}

is represented as

```

SEQUENCE/OPTIONAL/DEFAULT: An ordered SEQUENCE is represented using the sequence primitive. Optional fields are incorporated by the addition of a null leaf node. Default values are represented by an additional optional leaf node carrying the default value.

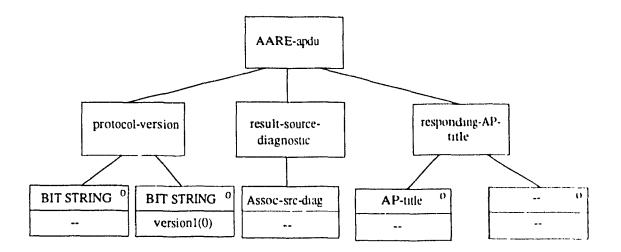

As an example, let us consider the following ASN.1 definition

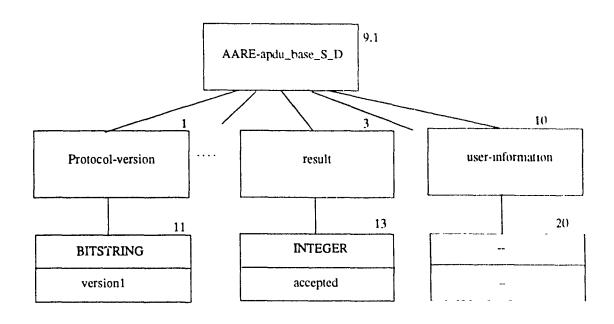

The I/O diagram of "AARE-apdu" is:

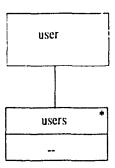

**SEQUENCE OF:** This ASN.1 construct is directly represented in terms of the iterative primitive. For example, the ASN.1 definition

user ::= SEQUENCE OF users

is represented as:

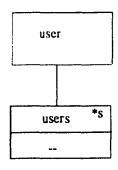

**SET OF:** This ASN.1 construct is represented by a combination of the unordered sequence and iteration primitives. For example, the ASN.1 definition

user ::= SET OF users

is represented as:

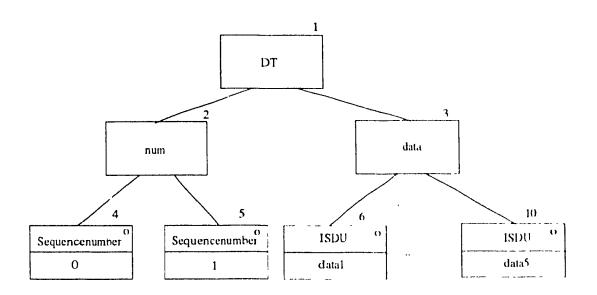

## 2.4.2 I/O Diagram for ADT

The I/O diagram describes the syntax of the ADT definition. Thus we need to be concerned with the operations part. We assume that in the operations there is an operation, that constructs the data type from its substructures. This operation is used to construct the I/O diagram. I/O diagrams for substructures are similarly constructed from the type definitions defining the substructures. Any constant values defined are mapped to primitive leaf nodes with values assigned. All the fields are assumed compulsory. For optional fields it is assumed that EFSM-chart contains send events in which omitted fields are assigned to Not\_present(field).

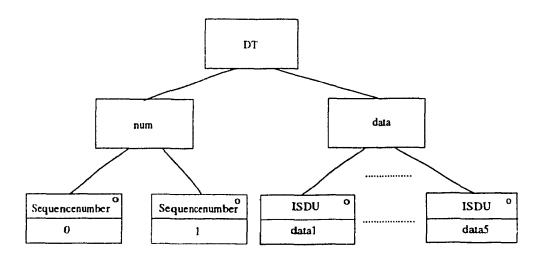

To illustrate the correspondence between an I/O diagram and the structure of an ADT, we consider the following ADT definition

```

type IPDUType is ISDUType, Sequencenumber sorts IPDU opns

```

$DT : Sequence number, ISDU \rightarrow IPDU$

AK : Sequencenumber → IPDU

data :  $IPDU \rightarrow ISDU$

$num: IPDU \rightarrow Sequence number$

eqn

for all f: Sequencenumber, d: ISDU, ipdu: IPDU

ofsort ISDU

```

data(DT(f,d)) = d;

ofsort Sequencenumber

num(DT(f,d)) = f;

num(AK(f)) = f

endtype

type Sequencenumber is Boolean

sorts Sequencenumber

opns

0: \rightarrow Sequencenumber

1: → Sequencenumber

succ : Sequencenumber → Sequencenumber

eqns

ofsort Sequencenumber

succ(0) = 1;

succ(1) = 0

endtype

type ISDUType is

sorts ISDU

opns

data1, data2, data3, data4, data5: → ISDU

endtype

```

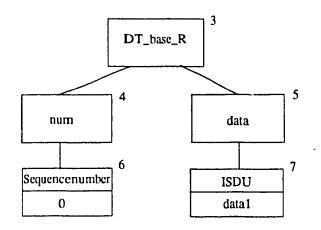

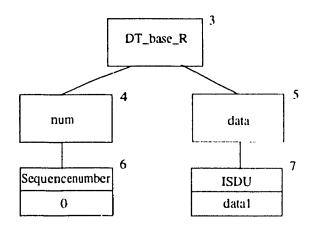

The I/O diagram corresponding to the above abstract data type of DT pdu is shown below:

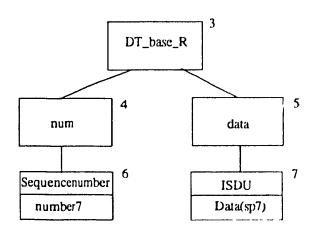

Similarly, the I/O diagram for the AK pdu is as follows:

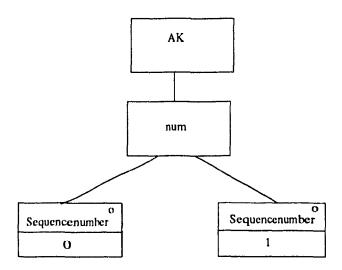

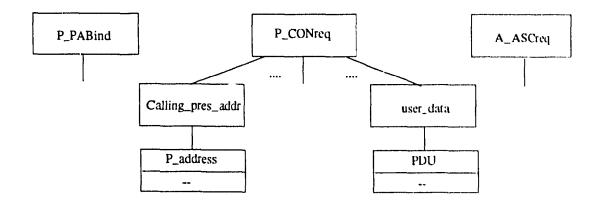

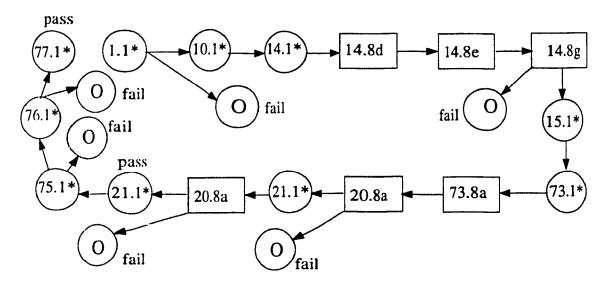

# 2.4.3 ASP/PDU Hierarchy from Specification

All the ASPs and PDUs defined in a specification can be mapped to I/O diagram hierarchies. There are three sets of I/O diagrams: one for ASPs, one for PDUs and another for all the substructures that ASPs/PDUs need.

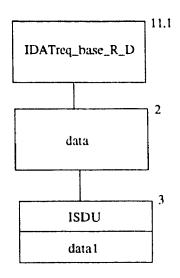

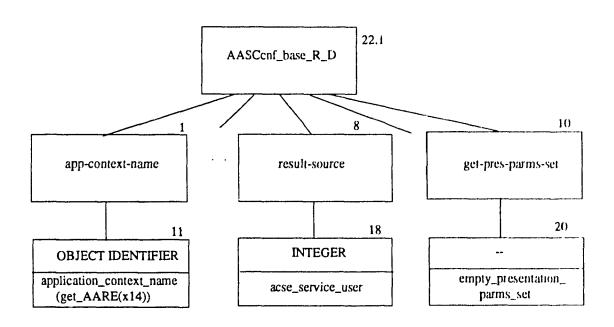

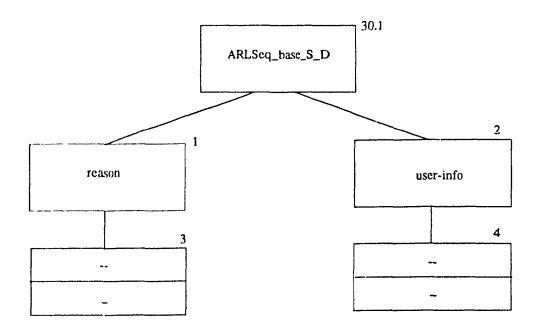

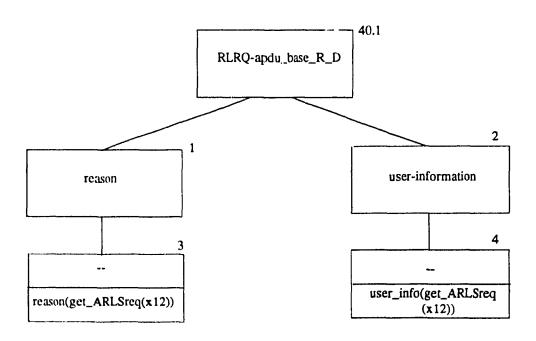

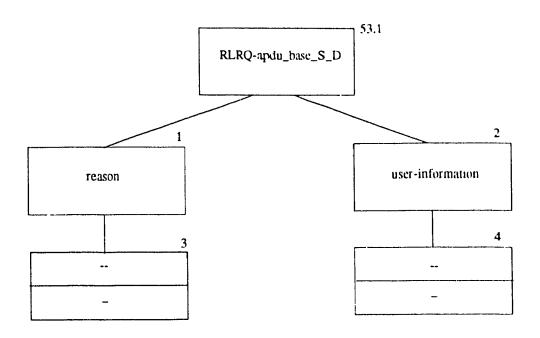

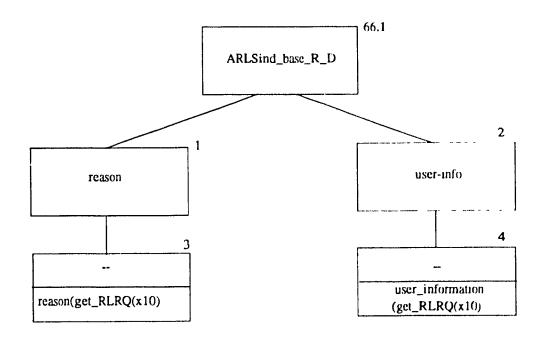

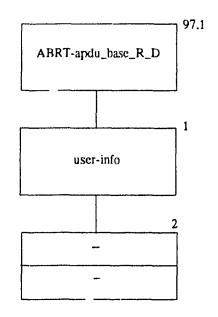

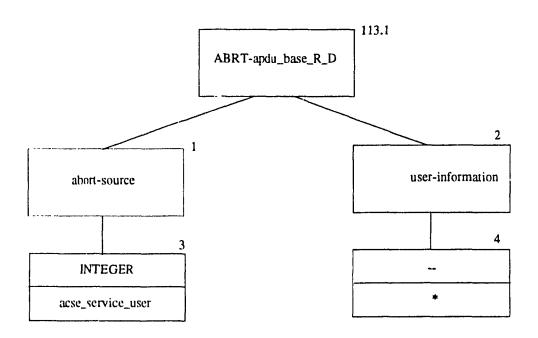

For example the set of ASP diagram:

## a set of PDU diagram:

and finally another set for all the substructures:

### 2.5 TRANSITION SYSTEM AND EFSM CHART

Our starting point is a well-accepted formal notion known as transition system to represent operational semantics of concurrent systems.

Definition 2.1 A transition system is a quadruple  $T = \langle Q, \Xi, \rightarrow, init \rangle$ , where

- Q is a set, the states of T,

- $\Xi$  is a set, the events of T,

- $\rightarrow \subseteq Q \times \Xi \times Q$  is a relation, the transitions of T,

- $init \in Q$  is the initial state of T.

The chart introduced in [42] is a particular kind of transition system. In a chart, a state is labeled by zero or more identifiers; an identifier indicates states at which the behaviour of a transition system may be extended by substitution of another transition system for that identifier. Before giving the formal definition of the chart, we provide an abstract syntax of algebraic data types in order to describe the data part on which the chart system is to be defined.

Definition 2.2 Let S be a set whose elements we call sorts which are names for various data domains. A signature over S is an  $S^* \times S$ -indexed family of sets  $\Omega = \langle \Omega_{w,s} \rangle_{w \in S^*, s \in S}$ ; the elements of a set  $\Omega_{w,s}$  in the family  $\Omega$  are called operators. A family of variables over S is an S-indexed family of sets  $V = \langle V_s \rangle_{s \in S}$ ; the elements of a set  $V_s$ , in the family V are called variables.

Given a signature  $\Omega$  over a set of sort S and a family of variables V over S, term over  $\Omega$  and V are constructed in the usual way and they also form an S-index family of sets  $T_{\Omega}(V)$ ;  $T_{\Omega}$  denote the subfamily of constant terms - i.e., terms not containing variables within  $T_{\Omega}(V)$ ; Let  $t_1, t_2, \ldots, t_n$  be metavariables over terms; the expression  $E\{t_1, t_2, \ldots, t_n \mid v_1, v_2, \ldots, v_n\}$  denote the result of a substitution, where each variable  $v_i$  of the expression E is replaced by the term  $t_i$ . The variable  $v_i \in V$  is free in E, and the sort of the term is the same as the sort of the substituted variable. Let  $D = D_{v_1} \times D_{v_2} \times \ldots \times D_{v_n}$  be the joint domain of the variables, with  $D_{v_i} \subseteq T_{\Omega}$  for each i.

Let G be the set of gates and channels; elements of G are denoted by g; let  $G_{sig}$  be the set of signals. S is a list of gate names. The distinguished symbols i,  $i_s$ ,  $i_r$  shall not be member of G. The set of actions is the set

$$A = \{i, i_s, i_r, gd_1..d_n | g \in G, d_i = !t_i \text{ or } !sig \text{ or } ?sig \text{ or } ?v_i : s_i,$$

$$t_i \in T_{\Omega}(V)$$

,  $sig \in \mathbf{G}_{sig}, v_i \in V, s_i \in S$

For each action a the function name(a) is defined as follows:

$$name(a) = \begin{cases} g & \text{if } a = gd_1..d_n \\ i_s & \text{if } a = i_s \\ i_r & \text{if } a = i_r \\ i & \text{otherwise} \end{cases}$$

The direction of data flow associated with an action is defined by

$$offer_{i}(a) = \begin{cases} ! & if d_{i} = !t_{i} \text{ or } !Sig \\ ? & if d_{i} = ?v_{i} : s_{i} \text{ or } ?Sig \end{cases}$$

undefined otherwise

Let I be the set of process identifiers. Each process identifier  $X \in I$  has a fixed arity  $n(X), n(X) \geq 0$ , the number of its arguments. The total function  $f_p: I \to V^*$  yields for each identifier X its formal parameter list. Fixed point operator  $\mu$  is used for the process declaration  $\mu X(v_1,...,v_n).B(t_1,...,t_n)$  as an alternative notation for process declaration used in LOTOS. This allows us to deal with a specification as being one expression. We are now in a position to define the EFSM chart formally.

**Definition 2.3** An EFSM chart is a 8-tuple  $m = \langle J, N, E, V, R, j_o, Z, h_o \rangle$ , where

- J is a finite set, the control states of m;

- N is a finite set, the transitions of m;

- $E \subseteq J \times I$  is a finite set, the extension of m;

- V is a finite set, the variables over S of m;

- R is a finite set, the rules of m (see below);

- $j_o \in J$  is the initial control state of m;

- $Z \subseteq J$  is a finite set, the terminal control states of m;

- $h_o \in \{v \leftarrow t | t \in T_{\Omega_D}\}$  is the initial assignment to the variables of m.

The possible transitions of a chart are defined by a set of rules whereby each rule defines a class of transitions.

**Definition 2.4** A rule of a chart is a 8-tuple  $r = \langle a, j, j', n, p, c, f, h \rangle$ , where

- $a \in A$  is an action, the when clause of r;

- $j \in J$  is a control state, the from clause of r;

- $j' \in J$  is a control state, the to clause of r;

- $n \in N$  is a transition number, the transition clause of r;

- $p \in T_{\Omega_{Bool}}(V)$  is a predicate, the guard clause of r,

- $c \in T_{\Omega_{Bool}}(V)$  is a predicate, the condition clause of r;

- $f \in \{v \leftarrow t | t \in T_{\Omega_D}(V)\}$  is a function, the action clause of r,

- $h \in \{v \leftarrow t | t \in T_{\Omega_D}(V)\}$  is a function, the assignment clause of r.

The transition n occurs, when the chart is in control state j and the predicate p is true for the current assignment of the variables, then it may participate in an event that matches the when clause a, if the condition c is satisfied. This leads to the new control state j'.

We shall frequently write

$$R(j) = \{ \langle a, j', n, p, c, f, h | \langle a, j, j', n, p, c, f, h \rangle \in R \}$$

the rules of j

$$E(j) = \{ x | \langle j, x \rangle \in E \}$$

the extension of j

We shall use subscripts to identify rules, so that when, refers to the when clause of rule r.

#### CHAPTER III

#### EFSM CHART OF SPECIFICATIONS

In this chapter, we develop algorithms to transform a protocol specification into an Extended Finite State Machine (EFSM) chart. An algorithm is proposed in [34] to translate a subset of LOTOS into an EFSM chart. We extend the algorithm to full LOTOS and SDL for our requirements. In section 3.1 we present the LOTOS to chart generation algorithm. In section 3.2, we present the SDL to chart generation algorithm. Finally, the size of the generated chart with respect to states and rules is discussed.

## 3.1 FROM LOTOS TO EFSM CHART

LOTOS specifications can be transformed into EFSM charts in two phases. In the first phase the specification is transformed into a semantically equivalent form. In the second phase it is converted into an EFSM chart by bottom-up synthesis. The translation algorithm is confined to the dynamic behaviour of the LOTOS specification, because no adequate theory exists for the automatic translation of algebraically specified abstract data types into statements of an imperative language.

## 3.1.1 Transformation of a LOTOS Specification

In order to facilitate the chart construction algorithm, it is convenient first to apply some transformations to the LOTOS specification. The transformation rules are explained below:

• Transformation of full synchronize composition to general composition

A full synchronize operator between  $B_1$  and  $B_2$  ( $B_1 || B_2$ ) can be transformed to a generalized parallel operator by inserting all synchronized gates inside the parallel operator at which  $B_1$  and  $B_2$  synchronize ( $B_1$  |[synchronized gates]| $B_2$ ). This transformation will reduce the number of rules in the chart construction algorithm.

Transformation of sequential composition to general composition

In LOTOS internal actions occur in execution sequences either explicitly (an *i* in the specification) or because they result from the dynamic behaviour of the system (an enable operator in the specification). Here, we deal with internal events, those due to an enable operator.

Let us first explain how nondeterminism appears, due to the enable operator [20]. For instance, consider the following process:

This behaviour is equivalent to

Unfortunately, this transformation does not work if there is value passing in the enabling. For example

endproc

This type of situation can be handled by first introducing an internal action just before the exit construct of the enabling process, then transforming the sequential composition to parallel composition by introducing an auxiliary gate at which the enabling process synchronizes its last action with an action implicitly prefixed to the enabled process.

Also, we should regard this synchronization as private to the enabling and the enabled process. As an example the process P[a,b] above can be transformed to:

```

process P[a,b]:=

hide \delta_1 in

( i ; \delta_1 ; stop ;

[] a ; i ;\delta_1 ; stop ;)

|[\delta_1]|

\delta_1 ; b ; stop

```

## endproc

endproc

Sequential composition with value passing can be similarly replaced by parallel composition. To achieve this, we have to do two things. First, replace the list of sorts of value offered at successful termination of the enabling process by value declarations attributed with the auxiliary gate. Second, replace the *accept* construct of the enabled process by variable declaration attributed with the auxiliary gate. For example, consider the previously defined process Q[a,b,c] which can be transformed to:

```

process Q[a,b,c]:=

hide \delta_1 in

(i; \delta_1! true; stop;

[] a; i; \delta_1! false; stop;)

[[\delta_1]!

\delta_1? ok: bool;

[ok] \rightarrow b; stop

[] [not(ok)] \rightarrow c; stop

```

In those cases where the enabling process itself is a composition of parallel processes, the last action of these processes synchronizes within themselves at the auxiliary gate, which in turn synchronizes with the first action of the enabled process. If the parallel composition is a pure interleaving, then it has to be transformed to generalized parallel

composition with the auxiliary gate as a synchronization gate.

## Conversion of generalized choice to choice expression

The structure of the generalized choice is: choice g in  $[a_1, a_2, \ldots, a_n]$  [X[g]], where gate identifiers are used for indexing. It can be mapped into the construct  $X[a_1]$   $[x_1]$ , ...,  $[x_n]$ . In this case, choice of x instances of x is created; for each one of them a formal gate x is actualized with a different element of the gatelist x, x, x, x.

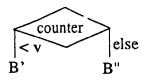

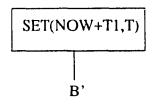

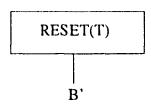

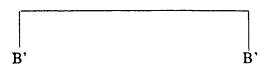

#### Process instantiation