National Library of Canada

Cataloguing Branch

Canadian Theses Division

Ottawa, Canada K1A 0N4

NOTICE

•

Bibliothèque nationale du Canada

Division des thèses canadiennes

Direction du catalogage

The quality of this microfiche is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us a poor photocopy.

Previously copyrighted materials (journal articles, published tests, etc.) are not filmed.

Reproduction in full or in part of this film is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30. Please read the authorization forms which accompany this thesis.

THIS DISSERTATION

HAS BEEN MICROFILMED

EXACTLY AS RECEIVED

La qualité de cette microfiche dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de mauvaise qualité.

Les documents qui font déjà l'objet d'un droit d'auteur (articles de revue, examens publiés, etc.) ne sont pas microfilmés.

La reproduction, même partielle, de ce microfilm est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30. Veuillez prendre connaissance des formules d'autorisation qui accompagnent cette thèse.

> LA THÈSE A ÉTÉ MICROFILMÉE TELLE QUE NOUS L'AVONS REÇUE

### ALGORITHMIC HARDWARE DESIGN LANGUAGE ( AHDL )

Allan Kang Ying Wong

A Thesis

in

The Faculty

of

Engineering

Presented in Partial Fulfillment of the Requirements for the degree of Master of Computer Science

Department of Computer Science

Concordia University

Montreal, Quebec, Canada

September 1978

(C) Allan Kang Ying Wong, 1978

ALGORITHMIC HARDWARE DESIGN LANGUAGE ( AHDL )

### Allan Kang Ying Wong

textual consensus multi-level language, intended specifically for the description, simulation, and design of computing hardware systems, is presented in this thesis. The language is AHDL ( Algorithmic Hardware Design Language ). Its structure contains a fluid hierarchy of three levels : behavioral level, functional level, and structural level. levels can be either applied individually for their designated purposes, or interacted in accordance with the rules described the text. The language AHDL is capable of expressing concurrent and parallel operations, which are the fundamental properties of, hardware systems. Ιt accommodates the also application of standard logic design techniques and available IC technologies.

The language AHDL is described on a theoretical level. This research was concentrated mainly on the validity of the language design. The implementation of AHDL was outside the scope of the work concerned. The structure of AHDL was, however, thoroughly tested on many different examples. Some of these examples are provided in the appendix, while others are presented in appropriate places throughout the body of this thesis.

The establishment of a "universal "language applicable to the simulation, description, and design of computing hardware systems, has recently been the subject of different researches. Such a language would require a consensus multi-level modular structure. It would support the formulation of algorithms at any desired level of detail. The aim of this project is to design a textual linguistic structure, which fulfills the requirements of the language concept stated above.

Hardware design and description languages, principally Register Transfer (RT) languages, were first designed early in the sixties. Since that time, they have been refined, and new ones have been developed, in attempts to keep pace with the evolution of IC technology. The RT languages presently in existence together cover the continuum of digital applications. Each RT language, however, has certain limitations on its application because of the framework of its structure. In general, a RT language is applicable only to a particular level of detail.

AHDL (Algorithmic Hardware Design Language) developed in this research is a textual consensus multi-level modular language. It is unique in that it potentially covers the complete range of contemporary digital design. It was derived by the technique of language tuning, which has been responsible for the emergence of most of the existing textual RT languages.

This thesis work was undertaken as a result of the ideas provided by Dr. Terill Fancott.

I wish to express my full gratitude to Dr. T. Fancott for his supervision and guidance during the research and development of the language AHDL.

PREFACE

| PREFA  | CE ,                                                  | · ·            | •                                     | III  |

|--------|-------------------------------------------------------|----------------|---------------------------------------|------|

|        | <b>n</b>                                              |                |                                       |      |

| CHAPTI | ER ONE : GENERAL INTRODUCTLO                          | ON ·           |                                       |      |

| •      |                                                       |                | ,                                     |      |

| ,      |                                                       |                | . •                                   | 1    |

|        | Rationale of Digital Hardwa                           | re Systems     |                                       | 1    |

|        | The Philosophy of Digital-S<br>Design and Description | ystem          |                                       | 3 .  |

|        | Digital System Design Objec<br>and Techniques         | tive           |                                       | 4    |

|        | Motivation for a High-level Universal Language        |                | · · · · · · · · · · · · · · · · · · · | 5.   |

|        | Requirements of a High-leve<br>Universal Language     | 1              |                                       | 7    |

|        | Is There Any Textual High-language?                   | evel Universal | •                                     | 8    |

|        | A Textual High-level University Design Automation     | sal Language   |                                       | 9    |

| •      | Survey on Textual HDLs in the                         | he Field       |                                       | 1 1  |

| ,      | This Thesis                                           | •              | • '                                   | 16.  |

| -      | Relationship to Other Work                            |                |                                       | 17   |

|        | Introduction to AHDL .                                |                |                                       | - 19 |

## CHAPTER TWO : BEHAVIORAL LEVEL OF AHDL

|    | Introduction -                              | 24               |

|----|---------------------------------------------|------------------|

| ٠. | Basic Language Elements and Some            |                  |

|    | Important Linguistic Structures             | 31               |

|    | Declarator                                  | · · 36           |

|    | Register                                    | 37               |

|    | Variable                                    | 40               |

|    | Operator                                    | 41               |

|    | Blocking Mechanism                          | 48               |

|    | Renaming Mechanism                          | 49               |

|    | Procedure Call                              | 50               |

|    | Control Structure                           | 52               |

|    | Expression and Statement                    | 5 <sup>-</sup> 3 |

|    | Active-Transition Indicator                 | 55               |

|    | Synchronous and Asynchronous Data Transfers | 58               |

|    | Subscript                                   | 58               |

|    | Summary and Comments                        | <b>è</b> 0       |

|    | Example                                     | 60               |

# CHAPTER THREE: FUNCTIONAL LEVEL OF AHDL

| ,     | Introduction                                                                                                                                                                                                                                                | 64  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|       | Terminal                                                                                                                                                                                                                                                    | 66  |

| •     | Rippling and Parallel Operations                                                                                                                                                                                                                            | 67  |

| -     | State                                                                                                                                                                                                                                                       | 71  |

|       | Representation of Synchronous and<br>Asynchronous Operations                                                                                                                                                                                                | 73  |

| •     | Coupling                                                                                                                                                                                                                                                    | 77  |

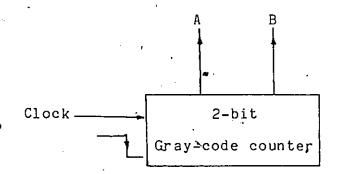

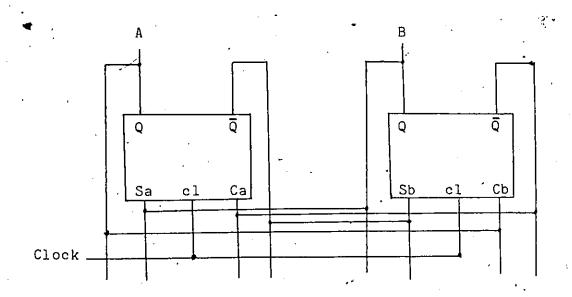

|       | Generic Definition of Counters                                                                                                                                                                                                                              | 79  |

| ,     | Terminal Rippling and Parallel Operations  State Representation of Synchronous and Asynchronous Operations  Coupling Generic Definition of Counters  Procedure Call Interaction Between Behavioral and Functional Levels  Summary and Comments  Example     | 8 1 |

|       | Terminal  Rippling and Parallel Operations  State  Representation of Synchronous and Asynchronous Operations  Coupling  Generic Definition of Counters  Procedure Call  Interaction Between Behavioral and Functional Levels  Summary and Comments  Example | 82  |

| -     | Summary and Comments                                                                                                                                                                                                                                        | 84  |

|       | Example                                                                                                                                                                                                                                                     | 86  |

|       |                                                                                                                                                                                                                                                             | •   |

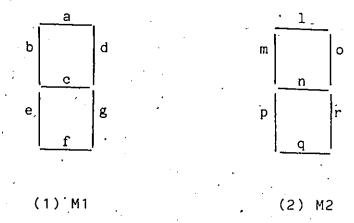

| CHAPT | ER FOUR : STRUCTURAL LEVEL OF AHDL                                                                                                                                                                                                                          |     |

|       |                                                                                                                                                                                                                                                             |     |

| Introduction            |    | 1 |   | , |   | 7  |

|-------------------------|----|---|---|---|---|----|

| Limk                    | •. | , | • |   | • | 9! |

| Modular Interconnection |    |   |   |   |   | 96 |

| State Assignment              |                                              | 97    |

|-------------------------------|----------------------------------------------|-------|

| Input Equations to Flip-      | -flops                                       | 100   |

| Design at the Structural      | Level                                        | 102   |

| Operator and Declarator       |                                              | 106   |

| Summary and Comments          |                                              | 10,7  |

| Example                       |                                              | 107   |

| CHAPTER FIVE : CLOSING REMARK |                                              | _     |

| The Language AHDL             |                                              | 115   |

| Comparison with Existing      | RT Languages                                 | 116   |

| The Development of AHDL       |                                              | 117   |

| Evaluation of AHDL            |                                              | .118  |

| The Potential of AHDL         |                                              | · 119 |

| APPENDIX                      | , <b>, , ,</b> , , , , , , , , , , , , , , , | 120   |

| BIBLIOGRAPHY                  |                                              | 134   |

#### CHAPTER ONE

### GENERAL INTRODUCTION

#### RATIONALE OF DIGITAL HARDWARE SYSTEMS

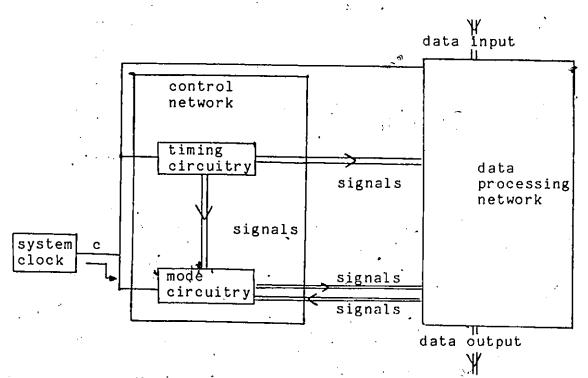

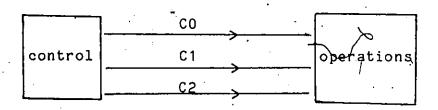

As pointed out by Dietmeyer ( Dietmeyer-01 ) and Peatman ( Peatman-02 ), the hardware organisation of any digital system. be simply represented in the model illustrated by Figure 1-1. The actual implementation of any digital system, however, take a variety of forms because of the two criteria: cost-effectiveness, and designated application (Fairchild-03). In Figure 1-1, the rational hardware organisation for any digital system would include two major networks interacting together. These two major networks are the control network the data processing network. The / data processing network transforms system inputs to meaningful outputs. All operations in the data processing network are sequenced by the control network. The control network itself may be subdivided into the timing circuitry and the mode circuitry. Operations which are functions of time only are sequenced bу the circuitry, and operations which are functions of both time and data are sequenced by the mode circuitry. The mode circuitry a decision-making structure, and the decisions made are the functions of timing issues from the timing circultry and data from the data processing network. Generally, the control network activates only the appropriate portion of the data processing network, for the specific data transformation.

The constituents of any digital system are discrete hardware components collectively known as structural primitives (Gardner-04). These basic building blocks may bear different levels of meaning and complexity. The lowest level has been generally accepted as gates and flip-flops at the SSI level. The higher levels may involve MSI and LSI.

Concurrency and parallelism are the fundamental properties of hardware systems. The harmonious co-operation of the structural primitives within a digital system must be ensured by synchronizing mechanisms. Hardware synchronization is achieved through enabling and disabling electrical signals. These binary signals are usually generated according to algorithms.

Figure 1-1 A rational hardware configuration for any digital system.

### THE PHILOSOPHY OF DIGITAL-SYSTEM DESIGN AND DESCRIPTION

Digital system design is usually a top-down multi-level process of algorithmic formulations and the assembly of appropriate structural primitives for the execution of the algorithms formulated. Each level in a design process represents a stage in the design cycle to provide rational feedback to the designer. Similiar to the philosophy of a design process, description of a digital system may also be a multi-level process. The purpose of any descriptive process is to express the pdesired level of detail of a system, ranging from simple behavioral information to subtle physical details.

Multi-level description is a method of making a digital system understandable by documenting information on an appropriate set of levels. It allows the different people, who take part in the different areas of a system, to communicate among themselves. The tool for communication, however, is a language, powerful and universal enough, for expressing different levels of ideas, but using a common syntax.

A top-down multi-level design methodology is a basic engineering principle. If there is a language, which can accommodate the different stages within a top-down design cycle and support the expressions of various design techniques, available in a design process, the ease of the design will be greatly enhanced.

DIGITAL SYSTEM DESIGN OBJECTIVE AND TECHNIQUES

" The ultimate objective of any digital system design is to achieve a given performance for the lowest total system cost. " Fairchild-03 ). In the past decade , system design, component selection and logic design were to a large degree independent of one another. Logic designers were concerned with designing with minimum number of gates and flip-flops by using conventional techniques such as Boolean algebra or Karnaugh The evolution of IC technologies has brought abundant choices of more cost-effective MSI and LSI logic components. The impact of these sophisticated logic components has changed radically the techniques of designing digital systems by making system design, logic design, and component selection heavily interdependant. To-day, designing by minimizing the number of gates and flip-flops is no longer sufficient. Modularization ( Ellis-05, Franklin-06, Clark-07 ), which is the partition of a system into subsystems or even sub-subsystems called modules, is far more important. Each module, which is a bounded system itself and is functionally complete, then lends itself to design increasingly sophisticated and cost-effective ICs. In some cases, a module is just a single IC logic component. A module is a bounded system because it cannot be affected by other systems except through the input interconnections. It is functionally complete because it has been isolated for designated performance to the specifications of a designer.

In order to cope with the rapid evolution of IC

technologies, a new design methodology for digital systems is required to include system design, logic design, and component selection as an integral part in any design process. In particular, such a design methodology must be hierarchical in order to do the following:

- 1. To formulate the algorithms for a system architecture at the schematic level.

- 2. To partition a system into modules so that each module can be individually and completely developed; then the control structure to make the modules interact harmoniously can be designed.

- 3. To provide a framework which can accommodate different IC technologies.

- 4. To accommodate conventional logic design techniques whenever needed.

Before a design technique can be applied at will to do the four things stated, it must contain enough basic elements which can be selectively assembled for any particular application during a design process.

MOTIVATION FOR A HIGH-LEVEL UNIVERSAL LANGUAGE

The motivation for a high-level universal language is to provide a versatile notation which can be used equally well as a descriptive, simulating and design tool, applicable to any wanted level of detail. The notation required is a formal mechanism to generate and transmit the right amount of

information needed. It must maintain proper and unambiguous communication among differents phases and areas of system development.

The first criterion of a high-level universal language is to establish an orderly framework capable of accommodating the development of numerous and yet distinctive dialects for communications as pointed by Iverson and Chu:

Iverson (1-Iverson-08):

"..., in the design of a data processing

system, it is imperative to maintain close

communication between the programmers/

(i.e. the ultimate users), the software

designers, and the hardware designers.."

Chu ( 1-Chu-10):

"Software designers, practically system programmers, need to know how the hardware system works without knowing electronics. In fact those who are in selling, servcing, operating, teaching, fabricating,

installing, and testing computers all need to know how a modern stored-program computer works rather than how the hardware is interconnected."

The second criterion of a high-level universal language is to provide a design tool that keeps up with technology evolution, but not the specific application of any technology as stated by Barbacci and Siewiorek (Siewiorek-12):

" Because of the rapid technology evolution, there is

a great need to attain independence from any specific technology in the design process. "

### REQUIREMENTS OF A HIGH-LEVEL UNIVERSAL LANGUAGE

A high-level universal language must fulfill three basic requirements. First, it must be based on а multi-level hierarchical modular philosophy in order to be compatible with the hierarchical nature of digital systems. The hierarchical nature of digital systems was clearly explained by Barbacci Barbacci-13 ), and the essence of a multi-level hierarchical modular philosophy was presented by Su (Su-15). Second, it must be consensus. As pointed out by Lipovski (Lipovski-18), a consensus hardware descriptive and design language contains a common set of linguistic elements applicable to any level of a digital design or descriptive process. These linguistic elements can then be assembled according to needs into the corresponding and appropriate constructs. Third, to permit a rapid top-down approach for any designated application, it must have a high degree of extensibility incorporated into its structure. The meaning and the advantages of extensibility in the structure of a language were well-explained by Schuman ( Schuman-19 ) .

### PROMISES OF A TEXTUAL LINGUISTIC STRUCTURE

A textual linguistic structure is more advantageous for a high-level universal language for four reasons. First, the descriptive power of conventional programming languages to

express 'algorithms in terms of language statements has implied that textual languages can better express subtleties variations than can graphical languages through shapes and sizes figures. Second, the control structures in the conventional programming languages have already benefitted from extensive work \_over the past two decades. The merits of these control structures can be extracted and incorporated into a universal language. Third. extensibility can be easily incorporated into textual language statements, and extensibility is the basic requirement for the generation of hierarchical language structure. Fourth, the. existing compilation techniques for compiling conventional programming languages are potentially applicable for a high-level textual universal language.

#### IS THERE ANY TEXTUAL HIGH-LEVEL UNIVERSAL LANGUAGE ?

description languages in the field. He pointed out that these languages, intended for the design and description of digital systems, were developed on the basis of a hierarchical top-down methodology. Therefore the developments of these languages were basically directed towards the concept of a textual high-level universal language. These languages are RT (Register Transfer) languages because they are operating at the register level. They have covered all the needs in both the design and descriptive processes for digital systems. However, each RT language is applicable to only a particular level of practice because its

applicability is limited by the language structure.

Up to the present, there is no textual HDL (Hardware Description Language) that can fulfill all the requirements of a textual high-level universal language, undoubtedly because there are always reasonable limitations for the application of any existing textual HDL. These limitations were explored by Lipovski (Lipovski-18) and Jordan (Jordan-20). Similar information can also be found in Barbacci-14.

A TEXTUAL HIGH-LEVEL UNIVERSAL LANGUAGE TO DESIGN AUTOMATION

Design automation using computers as design aids is a new and important subject in digital design methodology. The context of design automation is to provide a computerized hierarchical top-down design process from simulation to synthesis for any proposed digital design. It aims at a rapid top-down iterative design scheme by allowing efficient optimization of the many possible design tradeoffs which are part of the process of system or logic design. The book by Breuer (1-Breuer-21) gives a clear concept of design automation, mentioning different fundamentals and requirements.

1972, design automation had already received a great deal of attention as illustrated by Breuer in his survey (2-Breuer-22). Since then, the number of active researchers in this area has been ever increasing, as clearly indicated by the proceedings presented at the 1975 International Symposium on

C.H.D.L. and Applications (Proceedings-23). Design automation systems of variable degree of success were reported, and the better known projects providing an overview of the subject are presented in Siewiorek-12, and Stewart-26. All these researchers adopted somewhat different techniques and approaches for the developments of their design automation systems, but the quality and the feasibility of the languages used were always their primary considerations. It was not unusual that existing textual, RT languages were tuned to their, needs through appropriate modifications. This underlines the fact that a more universal textual high-level language would be desirable in the industry of design automation.

In order to derive a comprehensive automated design, the quality and the feasibility of the language adopted is very because of three reasons. First. top-down hierarchical nature of any automated design needs a compatible. hierarchical design language. Second, the language needed to convey accurately the design problem to the computer and vice versa. Third, the language used is required to support any design, stage in the cycle of an automated design by accommodating the pertinent and necessary design techniques. Therefore, a textual high-level universal language based multi-level hierarchical modular philosophy is potentially applicable to design automation. Its textuality allows a clear communication between the computer and the designér automated design process. The issue is however, how much latitude the language has in its structure to accommodate the

necessary information and the variety of design techniques possibly engaged.

SURVEY ON TEXTUAL HDLs IN THE FIELD

Hardware description and design languages developed so RT languages ( Jordan-20 ) because they always operate at the register level. However, no RT language can completely assume the service of a textual high-level universal language because any RT language is good for only a particular level of application. Since these RT languages have covered a wide range of applications, several of them appropriate to different levels of applications may be occasionally combined to fulfill the task of a textual high-level universal language. Somehow, application of different RT languages to the different levels of particular commitment may be hindered by the problem of ambiguity. This ambiguity is due to the use of a set of common symbols express different concepts in the different. languages.

Operations at the register level are fully reflected in the assignment statements generalised in the syntax:

condition ---- carrier --- data operation expression

The second part of the assignment statement carrier data operation expression

represents the source and destination of a data transfer. It can

be broken up to have the following meanings:

- 1. The left arrow ( ) is the transmit or assign operator which transmits or assigns what is on the right side to the destination on the left side.

- 2. The "data operation expression "represents any data transformation, whereas only the result will be transmitted or assigned. In special cases, it represents only a value to be transmitted or assigned but no data transformation at all.

- 3. The "carrier " is a memory entity acting as a destination for the corresponding data transfer.

As pointed by Barbacci (Barbacci-14), carriers can be registers, or terminals of a transient natures. The latter represents wires coming out of combinational networks.

The first part of the assignment statement : condition

represents the control which invokes the corresponding data transfer. The right arrow (-) is the operator which transfers control at a particular time interval from what is on the left to what is on the right. The "condition "abstracts the control signal generated by a "test network "or a "monitor ". The existence of the condition implies that dynamic data transfer is a rule rather than an exception. A more detailed description of the characterization of the RT level based on different RT languages was made by Barbacci (Barbacci-14).

As a conclusion drawn from the survey on different RT languages: ISP (Bell-27), DDL (Dietmeyer-01), CDL (2-Chu-11), APL (2-Iverson-09) and the language by Vogel (Vogel-28); and from the suggestions by Barbacci (Barbacci-14) and Jordan (Jordan-20); any RT language is, or can be completely defined by five basic abstract data types: register, terminal, variable, declarator, and operator. They are listed and explained in Table 1-1. They are called abstract data types because they abstract either the structures or the behaviors of the physical building blocks, as suggested by Flon (Flon-29-7).

The power and scope of the different RT languages range from stating a problem at the schematic level to representing structural details of physical objects. For example, ISP is good for any schematic-level application, DDL is good for descriptions of larger modular transfer, and CDL is good for the gate and flip-flop level. Though there are indeed overlapped capabilities among the different RT languages, one language may not be as suitable as another for a particular level of application.

In fact, the applicability-of a RT language is determined by the available abstract data types it contains, the transformations which can be applied to these abstract data types, and the characteristics of the language structure. In ISP, the absence of the "terminal "abstract data type makes explicit terminal wiring description impossible. The control labels in CDL specify timing to an accuracy of one clock pulse

making CDL applicable for description at the structural level.

The explicit dynamic multiplexed terminal assignment statements in DDL with the syntax:

<ST> condition : terminal identifier = expression

make the language more suitable for modular descriptions.

The procedural RT languages usually impose more rigid their applications because the execution of statements is based on their sequential ordering. The execution of a statement is basically conditioned by the completion of the preceding one. In addition, the consideration of timing in procedural RT languages is generally crude. Therefore the structures and the timing considerations in the procedural RT languages can rarely cope with the subtleties and the precision needed respectively in the gate and flip-flop level. non-procedural RT languages impose less rigidity in formatting because lexigraphical ordering of statements has no meaning. The execution of statements is based on a scheme of "dynamic selection " for a statement to be executed, and consideration is highly refined or even in terms of single descrete clock pulses. Therefore the non-procedural RT languages are more suitable for the level of gates and flip-flops. Barbacci ( Barbacci-14 ) and Jordan ( Jordan -20 )-compared the structures of different RT languages. They concluded that the limitations of these RT language were due to their particular linguistic structures.

Recently, moderate effort has been put into different research work, driving towards the development of a textual high-level universal language. Well-known researchers in terms of their efforts and ideas are Lipovski (Lipovski-18 ) and Su -(Su-16). Lipovski is now working on the development of a framework which can accommodate the different powerful RT languages in a consensus way. Thus, when several RT languages of different levels of applications are combined together, they can fulfill all the requirements of a textual high-level universal language. Su developed LALSD which has been claimed to be a language for automated logic and system design. LALSD has a hierarchical structure multi-level and reasonable MACRO facilities, and it is potentially capable of describing, documenting, simulating, and synthesizing digital systems. The applicability of the language LALSD is, however, still at the experimental stage.

Table 1-1 Abstract data types of RT languages

abstract data type : declarator structure : names or labels made up of natural language elements functión : identify the existence of different structures or declare the properties of different structures extension: declarators are generally freely choosable but rules may exist to determine the ways to choose. special remark : a system of nomenclature abstract data type : register structure: one-dimensional array of binary nature function : store information over a period of time extension: forming two dimensional arrays ( memory ) or other structures by means of indexing special remark: registers are identified by

declarations and they are candidates for

the destinations of data transferv

abstract data type : variable

structure : identifiers made up of a single character

or several characters

function : variables have no inherent meaning, but they

can take up either Boolean values or

numérical values . '

extension: subscripted or non-subscripted

special remark : basic units of control formulations

or computations; operated on by the appropriate operators; no physical

correspondence

abstract data type : terminal

structure : identifiers made up of a single character

or several characters

function : each terminal represents the output of a

"circuit node " by taking on the current

logical value of the node over a period of

time or in a transient manner

extension: terminals can be dimensioned

special remark: terminals are identified by declarations

abstract data type : operator

structure : symbols

function : data transformations, and control formulations

extension: forming expressions for data transformations

and control structures

special remark : choice based on convention

THIS THESIS

This thesis proposes a linguistic structure which theoretically encompasses all the essential features of a textual high-level universal language. The language which has been developed is called AHDL (Algorithmic Hardware Design Language). It is based on a consensus multi-level modular philosophy. The objective of the research work was concentrated mainly on the validity of the language proposal. Implementation of AHDL was not within the scope of the research.

The technique used for the development of AHDL is "language tuning" which is the technique responsible for the emergence of most of the existing RT languages. The basic principle of language tuning was implicitly justified by Barbacci (Barbacci-13):

"In fact, conventional programming languages have been used.

The issue is, however, how much they must be changed to reflect parallelism, timing and the structure of the bject being represented."

The power of language tuning was explicitly justified by Lipovski (Lipovski-18) saying:

"Specifically, what is more commonly referred to as hardware description language is a variation of a programming language tuned to the overall needs of describing hardware."

Overall, the tuning process derives the syntax and semantics of a RT language from the merits of conventional programming languages with the additional inclusion of linguistic elements able to express parallelism and concurrency. The rule for establishing these elements for AHDL is abstractive power and familiarity.

#### RELATIONSHIP TO OTHER WORK

Conventional procedure-oriented programming languages developed for serial computations are powerful and well

developed, but they all have serious limitations/for solving problems involving parallelism, Opler (Opler-65). There is, however, a'high degree of correspondence between software programming techniques and hardware operations. It is clearly indicated by the philosophy and techniques of micro-programming (2-Chu-11). In fact, some conventional programming languages have tuned by different researchers to describe hardware which has the inherent property of parallel and concurrent operations. The tuning process has produced different powerful hardware descriptive and design RT languages like CDL, ISP and many others. It follows that language tuning, as learned from the past experience, is an efficient technique for the work of this project.

The intended applications and structures of textual RT languages have been continually evolving. Informal work on textual RT languages was started early in the sixties by Bartee (Bartee-31), and Schorr (Schorr-32). Then came the more formal and powerful textual RT languages like CDL, ISP, DDL, among others. Since the backgrounds and the approaches for the development of the different textual RT languages in the field were different, the applicability of these RT languages vary. They cover a cintinuum of levels of description and design of digital systems.

Nowadays, the complexity of digital systems, the rapid evolution of IC technologies, and the trend of design automation necessitate a textual high-level universal language to

communicate with, to simulate with, to design with, and to drive comprehensive automated designs. However, no existing textual RT language can individually and sufficiently support the goals stated. As a result, different researchers are looking for a language which possesses a linguistic structure functionally compatible to the "genuineness" of a textual high-level universal language. This is also the main objective of the research for the development of AHDL.

### INTRODUCTION TO AHDL

AHDL, introduced by this thesis, is a consensus multi-level modular hardware design and descriptive language. It is capable of accommodating the three levels of detail of any digital system: the top or the behavioral level, the middle or the functional level, and the bottom or the structural level. The levels reflected in the structure of AHDL can be interacted, i.e. in a construct written in any given level, the features of the other two levels are available according to a set of rules described in the body of this thesis. A high degree of extensibility was incorporated into AHDL to ensure the smooth extension from the behavioral level through the functional level to the structural level.

The behavioral level, which concerns algorithmic formulation at the schematic level, is characterised by the register transfers, the procedural structures, and the basic set of operators. The structure of the behavioral level is basically

defined by "time blocks ". The generalised representation of a time block is

The structure of the behavioral level is procedurally similar to conventional programming languages, except for the possible inclusion of concurrent single actions in the block of single actions of the time blocks. Any single action may represent a basic unit of data operation, or a time block. The "condition "represents an active flow of control at a particular time interval.

The functional level represents the principles of the mechanisms contributing to the system dynamics. It is characterised structurally by Boolean equations and terminal variables. This level stresses the use of control variables as terminal functions. Modularization at the functional level becomes explicit. Modules may be specifically designed on this level in terms of input-output relationships.

The structural level considers timing in terms of single clock pulses. It is basically a level of logic design in terms of gates and flip-flops. This level is characterised by discrete modular descriptions and the interconnection of modules through input and output terminals.

The extensibility of AHDL partially comes from the

hierarchical nature of the set of operators it possesses. The operators situated at a higher level can always be defined by operators at the lower level so as to provide more detailed information.

Since the procedural structure of the behavioral level can not accommodate all the detailed information at the structural level, a non-procedural structure, which imposes less restrictions on the expression of digital functions, was adopted for this level. However, the time block characteristic prevails in the structures of the three levels, except that any time block in the structural level contains solely concurrent single actions in its block of single actions. Generally speaking, the procedural structure at the behavioral level fades into the non-procedural structure at the structural level through the compatibility of the time block construct to both structures.

The definition of a time block and a single action in its block of single actions can be recursive, because such a single action may be another time block itself. The procedural structure of the behavioral level and the non-procedural structure of the structural level defined in terms of time blocks are presented in the following:

1. The procedural structure outlined in BNF (Backus Naur Form) for the behavioral level is

<single action> ::= <simple action > | < time block>

<time block> ::= < condition> <execution>

<condition> ::= ⟨state of control⟩ ⟨→⟩

- ", denotes concurrent behavior "

- "; denotes sequential behavior "

The most important feature of the procedural structure is the <execution> . It signifies that sequential ordering of single actions carrys a significant meaning, because the execution of a single action may be conditioned by the completion of the preceding one.

The non-procedural structure outlined in BNF for the structural level is

<single action> ::= < simple action > ! < time block>

<time block> ::= <condition> <execution>

<condition> ::= <state of control> < >

In order to make the characteristics and the applicability of each level in AHDL more understandable, each level is compared in Table 1-2 with a well-known RT language which has the compatible level of behaviors and application.

Table 1-2 Comparison of each level of AHDL with a consistent RT language

| •        |                            | •                                                   |                                                                       |                                                                                                                                                  |

|----------|----------------------------|-----------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| LN:      | CĎ                         | )L                                                  | DDL                                                                   | ISP                                                                                                                                              |

| RE :     | 2-Chu-                     | 1.1                                                 | Dietmeyer-01                                                          | Bel1-27                                                                                                                                          |

| ST:      | non-pr                     | ocedural                                            | non-procedural                                                        | procedural                                                                                                                                       |

| AP:      | gate a<br>level<br>applic  |                                                     | transfer of data between automata or large modules                    | schematic-level<br>formulating tool                                                                                                              |

| CT :     | in ter<br>single<br>pulses | e clock                                             | state of contr<br>memory medium                                       | ·                                                                                                                                                |

| TB :     | contai<br>only o           | oncurrent                                           | containing on concurrent activities                                   | ly containing both sequential and concurrent activities                                                                                          |

| <br>CM : |                            | cural level                                         | functional le<br>but biased to<br>the structure<br>level              | of application                                                                                                                                   |

| Remark   | : 1.                       | with the r<br>the above<br>to make th<br>more under | espective leve<br>comparisons, s<br>e structure and<br>standable. The | different RT languages ls in AHDL, as shown in erves only as a guide-lin d applicability of AHDL actual differences betwe ages are not conveyed. |

|          | <b>2.</b><br>/ .           | The symbol in the fol                               |                                                                       | table are explained as                                                                                                                           |

| •        |                            | . LN = 1                                            | anguage                                                               | •                                                                                                                                                |

RE

ST

ΑP

CT

TВ

F - F =

=

resource

structure

flip-flop

= ·control

application .

time block

comparison with AHDL

#### CHAPTER TWO

### BEHAVIORAL LEVEL OF AHDL

### INTRODUCTION

The behavioral level of AHDL is designed to support the algorithmic formulations for digital-systems at the schematic level. It can represent the pertinent sequential and parallel operations clearly. Specifically, this level is applicable to describing and simulating the behavior of systems, without going into the details of construction.

All objects in the behavioral level are defined by the set of "basic language elements": separator, letter, digit, logical value, and abstract data types.

The separators are symbols chosen to do the following :

- 1. Represent ordinary punctuation marks to enhance the readability of any construct at the behavioral level.

- Indicate timing by marking sequential and concurrent relationship among the linguistic structures.

- Indicate the functional relationship among the different linguistic entities.

Letters and digits respectively do not have any inherent meaning. They serve to form the other linguistic structures.

Logical values are "true" and "false" as usually encountered.

There are four abstract data types in the behavioral level of AHDL, namely: register, variable, declarator, and operator.

They are the chief building blocks for the formation of any construct in the behavioral level.

The five basic language elements are combined together according to rules to form single actions and declarations. The declarations form a system to do the following:

- 1. They declare the existence of linguistic structures. In this case the declarators are simply " labels " without any intrinsic meaning.

- 2. They declare the properties of different objects. In this case the declarators are " reserved " words rather than freely choosable labels as in the previous case.

The single actions are the basic units of algorithmic formulation for the solution of design and descriptive problems. They are expressed by the three types of statements available in the behavioral level, namely : assignment statement, designational statement, and conditional statement. A statement is considered as an operational event occurring in a particular period of time.

Single actions which are acting as basic units of computations are expressed in assignment statements. Assignment

statements which characterise the RT level of operations are data transfer statements with the generalised syntax:

carrier ---- data operation expression

The operator (+-) transfers the computed result by the data operation expression to the designated " carrier ". Any carrier which is assumed to have the ability to hold data information is either a register or a variable. The data operation expression represents either a rule to compute a value or a rule to present a value before a transfer. Any computation, which is always a " simple data transformation ", is based on either arithmetic composition or Boolean algebraic operation. It is always a simple data transformation because its formation involves only either just a single unary operator on a single operand or a single binary operator on two operands. operands are themselves variables. The operators are symbols selected to abstraet the designated data transforming mechanisms. In certain " simple data transfer ", the data operation expression contains no operator at all, but just a single variable representing the value for the transfer.

The single actions, which constitute the basic structural units of control sequencing, are designational and conditional statements.

A designational statement creates a control path between itself and a particular part in a construct. Control will then be transferred to that part for its execution. When execution is

completed, control will be returned to either the designational itself, or the single action right after the designational statement. There are, therefore, two types of designational statements : sequential designational statement, and dynamic multiplexed designational statement . Sequential designational statements are represented by procedure calls . When a procedure call is executed; a branch to the corresponding procedure for the subsequent execution will be performed. If the execution of the procedure is completed, control will be returned back the single action right after the ·to procedural-call statement. Associated with any multiplexed designational statement, the presence of a decoding process is always assumed. This decoding process decodes a particular condition encoded as one of the states in a register. The switching operator in the dynamic multiplexed designational statement, then, transfers control to the corresponding part of the construct for execution. When execution of that part is complete, control is returned back to the dynamic multiplexed designational statement itself.

Conditional statements are built up from assignment statements, designational statements, and even conditional statements themselves. The characteristics of conditional statements are summarised in the following:

1. The basic structure of any conditional statement is generalised in the syntax:

condition → ACTION

It says that the ACTION part wi $^{\prime}$ 11 be executed only when the.

" condition " of Boolean nature is " true ".

- explicitly by the Boolean value of a Boolean expression or that of a relational expression. The Boolean value of a Boolean expression, which is of ordinary Boolean algebraic composition, is the function of the Boolean expression. The Boolean value of a relational expression, which represents a "test network" to compare the magnitudes of two variables, is the result of the corresponding comparison.

- 3. The condition of any conditional statement implies, a particular time interval during which the ACTION is completely executed.

- 4. The ACTION part may contain a single "unconditional statement "which is either an assignment statement or a designational statement.

- 5. The ACTION part may contain a " block " of several unconditional statements.

- 6. The ACTION part may contain a "block " of unconditional statements and conditional statements intermingled together, i.e. conditional statements can be nested.

- 7. The execution of the statements within a block can be sequentially dependent, concurrently independent, or sequentially and concurrently intermingled. This timing relationship among the statements is marked by appropriate separators.

The control structure of the behavioral level of AHDL .is

based on the concept of a time block. This is a condition and execution relationship working on the principle of a conditional statement, i.e. a time block is defined by the syntax:

condition - a single action or a block of single actions

A conditional statement, however, is only one of the ways to represent a time block. The condition of a time block can be represented in three possible ways. First, it may be represented explicitly as the condition of a conditional statement. Second, it may be encoded as one of the states in a register. In this case, the recognition of the condition is performed by decoding. Third, its existence may not be explicitly defined by any structure. Instead, it may be assumed by default at the "entry point "where execution begins. For example, in a construct containing several statements in sequential ordering, the execution of a statement is conditioned by the completion of the preceding one.

The inclusion of concurrent single actions in the block of single actions of a time block is a rule rather than an exception. Furthermore, any single action in a block of single actions may represent another time block. Therefore the definition of a time block and a single action can be recursive.

Single actions can always be grouped together to be identified by unique labels. These groups are named blocks. The representational effect of a block is the same as a single action. The way of partitioning a block of single actions into

uniquely named subblocks, or sub-subblocks is referred to as the blocking mechanism ".

The basic principle of control transfer is summarised in two steps. The first step is the interpretation of the condition of a time block. The second step is the activation and execution of the corresponding single actions. There are three modes of control transfer as described in the following:

- 1. When a condition is encoded as one of the states in a register, the control transfer is a dynamic and selective process. It involves decoding the condition and then interpreting the result for a particular path of control transfer. Special operators are incorporated for this mode of control transfers.

- 2. If a condition is represented by either a Boolean expression or a relational expression, the interpretation of the condition is directly assumed. Then control transfer to the corresponding block of single actions or the corresponding single action starts only when the condition is true.

- 3. In any construct which contains single actions or blocks of single actions in sequential ordering, control will pass down from a single action or a block to another sequentially and respectively. In other words, the execution of a single action or a block is conditioned by the completion of the preceding one. If a time-slot of concurrent single actions or blocks does exist between two sequential entities, the whole time-slot will receive the same control transfer as if it were a single éntity. This sequential mode of control

transfer in any case can only be violated by procedure calls which imply "jumps " to skip a certain number of single actions or blocks for the execution of the corresponding procedures.

The structure of the behavioral level is " procedural " because sequential ordering of statements has a significant meaning. It implies the consideration of consecutive timing issues. This level is for formulating the framework or architecture of any digital system. Formulations in the behavioral level do not consider the intrinsic properties of the basic building blocks. For example, a register is declared as a storage element irrespective to its ultimate principle of operation. However, " synchronous " and " asynchronous " operations can be reflected by the indicator " " which will be described later in this chapter.

BASIC LANGUAGE ELEMENTS AND SOME IMPORTANT LINGUISTIC STRUCTURES

Letters do not have individual meanings, but they are used to form "identifiers "and "information strings ". The letter set can be extended arbitrarily with any distinctive characters. The basic set provided is

<letter> ::=

راسا راسار الر

A | B | C | D | E | E | G | H | I | J | K | L | M | N | O | P | Q | R | S | T |

U|V|W|X|Y|Z|a|b|c|d|e|f|g|h|i|j|k|l|m|n| o|p|q|r|s|t|u|v|w|x|y|z

TO LE LE

Identifiers must start with a letter, but individually they do not have any inherent meaning. They serve to identify the existence of different entities in a construct. Within a construct, the identifiers must be "unique". The syntax of the identifiers is

The information strings are used for different purposes, but their principal purpose is to represent " number systems " in terms of bits, in the behavioral level. The syntax of information strings is

<information string> ::= nXr

- " n denotes numerical representation

- " X denotes number-system designator

- " r denotes bit-length of n "

The symbols n, X and r are left to the choice of the users for convenience. Any information string is binary in nature because it is defined by bits. In the above syntax, X specifies the number system, r specifies explicitly the bit length of the string in terms of a "decimal number ", and n is the value

represented particular to the number system. For example, if B designates "binary ", O designates "octal ", and D designates "decimal ", then the value of "nine "may have the representation of "001001B6 ", "1106 ", or "9D6 "respectively.

Digits are used to form identifiers, information strings, and " numbers ". The basic digit set provided is

<digit> ::= 0|1|2|3|4|5|6|7|8|9

Numbers have conventional structures and meanings. Real numbers are expressed in the form of

A"B

The symbol " separates the places of decimals specified by  $\dot{B}$  from A, and the example is the real number : 15"824 .

Logical variables may assume one of the two binary values : true or false. They are represented by appropriate identifiers.

The standard functions and properties of the separators, in the basic set at the behavioral level, are listed in Table 2-1.

Table 2-1 Standard functions and properties of the separators in the basic set.

Separator

Explanation

indicates concurrent activities

indicates sequential activities separates the places of decimals in real numbers separates declarator on the left and the structure on the right in any declaration : = separates the switching operator from the list of labels in any dynamic selective designational statement separates the upper limit from the lower limit by having the meaning of " from---to " denotes the beginning of a comment separates and defines the equivalence of two different representations containing the same number of entities; for example see Remark 3 at the end of this table 11/ separates and associates two parallel entities on both sides respectively; for example see Remark 2 at the end of this table begin end brackets to delimit the definition of an algorithm ( ) brackets to contain the parameter list of any procedure gall, and to be used freely to enhance readability brackets to contain label list for sequencing control brackets to contain subscripts for one-dimensional arrays [ ] brackets to contain the subscripts for the " rows " of the two-dimensional arrays brackets to be used freely to enhance readability Remark:

" Indexing " in the brackets of "  $\langle \rangle$  " , " [ ] ", " \* \*

always follows the convention of " from left to right ". When the separator "; " is used in the brackets of " < > " and " [ ] ", it acts like the separator " ~ ".

2. The two parallel entities separated and associated by the separator "//" are subject to the convention of indexing. The matching of "entity1 // entity2 " to the corresponding counterparts must be one to one correspondence. The principle of the matching is generalised as : entity1 // entity2 " matching mechanism "part1 //part2. Therefore entity1 is matched to part1, and so is entity2 to part2. If entity1 contains two subentities as "x,y", and part1 contains two subentities as "y,q", then the simultaneous matching is "x to p" and "y to q", i.e. corresponding to the position indexed. The matching mechanism is generally an appropriate operator. In the example of

(Addition//Subtraction//Division) --- (A//S//D)

the results of the parallel operations Addition, Subtraction, and Division are transferred to the registers A, S, and D respectively and parallelly. The symbol " " is the transfer operator.

3. Indexing is also applied to the both sides of the separator " / ". For example, in the construct of

A,B,C,D / a,b,c,d

A and a define each other, and so do B and b, C and c, and D and d.

The abstract data types: declarator, register, variable, and operator are the principal building blocks for any construct in the behavioral level. They are explained in detail in the next four sections.

DECLARATOR

U^

IÎ

110

E-

~

Declarators are the basic entities in the system nomenclature (which will be discussed in more detail in one of the latter sections ). They serve to define the properties of identifiers and declare the existence of different co-existing individual linguistic structures within a construct. In the behavioral level, some declarators are tuned to have inherent meanings. They are called the " reserved declarators ". The basic set of reserved declarators contains " Register ", "Subregister ", " Memory ", " Operator ", " Integer ", "Real", "Boolean ", " Operation ", " Sequence ", " Bus ", and " Procedure ". This set can be extended аt will b y "predefinition " to compensate for any deficiency that may arise. The purpose of the reserved declarators is to define properties of different identifiers. The existence of different individual linguistic structures, which may be identified for of clarity when structuring a behavioral-level construct, can be declared by non-reserved and unique labels. The syntax of any declaration is

declarator : structure

For example, the declaration of Register: A

means that the identifier A possesses the property of a register, and the declaration of

` L : A ← Y

means the corresponding assignment statement to be declared by the label L.

REGISTER

Registers are identifiers declared as data carriers. They may appear in the form of "simple identifiers "without any subscript, for example:

Register : A

Sometimes, registers represented by unsubscripted identifiers do not provide the necessary information, because they do not show the binary nature and the word-length of them. The provision of subscripts makes registers into one-dimensional arrays. The brackets " < > " are particular to the one-dimensional subscript specifications. The incorporation of indexing in these brackets makes the binary nature of a register clearer. In the first example:

Register: A <0;4>

the subscripts of 0 and 4 are respectively the lower and upper limits for the word-length of the register A. In the second example:

Register : A <0,1,2,3,4>

each bit is clearly indicated positionally from left to right.

Registers can be decomposed into subregisters by the appropriate "subregister declarations" of the syntax:

Subregister: identifiers of subregisters

The decomposition process is typified by the two examples presented in the following:

1. Example of decomposing a register into subregister :

Register : A<0;4>

Subregister : A <0;2>

A <3:4>

- \$ The register A  $\langle 0;4\rangle$  has been decomposed into subregister A  $\langle 0;2\rangle$  and subregister A  $\langle 3;4\rangle$ .

- 2. Example of decomposing a register into bits:

Register : A<0;4>

Subregister : A<0>

A<1>

A<2>

A<3>

A<4>

\$ The register A<0;4> has been decomposed into bits which have been declared as subregisters.

The concatenation operator " @ " allows the formation of a compound register by cascading several different registers positionally together, i.e. the opposite process to the decomposition a register. The compound register thus formed will

assume all the characteristics of the component registers which each individually, positionally, and uniquely contributes to the overall register specification. The compound register is represented by a new identifier. (Assignment of an identifier to a newly formed compound register is part of the "renaming mechanism" which will be discussed in more detail in one of the latter sections.) The formation of a compound register is illustrated in the following example:

Register : B<0;3>

**E** ~

Ĭ~

I~

C<0;3>

BC<0;7> # B<0;3> @ C<0;3>

\$ The compound register formed by cascading

the registers B and C has been renamed by the

operator " # " to be BC

Obviously from the above example, the operator "@" must override the operator "#" in the precedence of operations.

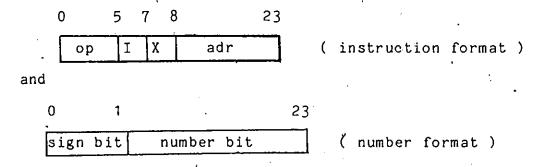

In fact, the decomposition of a register into subregisters or even into bits can also take place within the subscript by the aid of the concatenation operator. The subscript is then decomposed into different portions to be identified by unique identifiers. These identifiers are subsequently dimensioned by the brackets " < > " with the subscripts indexed corresponding to the original position in the " source register ". For example, if E<0;10> is the register to be decomposed deliberately into E<0p & adr>, then op and adr can be

dimensioned and indexed to have the designated format of E<op<0;4> @ adr<5;10>>. Therefore the two potential subregisters can be isolated as E<op> and E<adr>, or as op<0;4> and adr<5;10>, to be renamed and declared. The stacking of registers of the same word-length together forms a memory which is a two-dimensional array. The dimension of the stacking is contained in the brackets "[]". The syntax of a memory is

MR c;d]<a;b>

MR is the identifier of the memory to be declared. c and d tells how many registers are there, and a and b denote the word-length of each register. The decomposing and renaming mechanisms, which produce distinctive subregisters or bits, can also be applied to decompose a memory into memory blocks or single memory cells (individual registers). Such mechanisms, however, will be applied to the content contained in the brackets " ( ) " instead of that in the brackets " < > ".

## VARIABLE

A variable is an identifier to which either a Boolean value, a real value, or an integer value is assigned. It can be used as an operand in any "computation "or "control formulation". Any computation is defined by the data operation expression of an assignment statement, and any control formulation is regarded as the process of defining the condition for an execution. In the behavioral level, variables can be identified in three possible ways. First, identifiers can be

explicitly declared as either Boolean, integer, or real variables. Once a variable has been declared, it possesses the property as declared permanently, and it must be operated on by the same type (Boolean, arithmetic ) of operators. Second, declared data carriers like registers, subregisters, and identified bits can be taken as variables, but the properties of these variables are determined by the nature of the operators acting on them. Third, variables can be freely defined as "catalytic identifiers" to represent the required intermediate stages. Then, their nature depends on the nature of the corresponding assignment statements. The example of a catalytic identifier will be given in the section of CONTROL STRUCTURE later..

OPERATOR

The operators in the behavioral level serve three purposes: computation, control formulation, and the formation of syntactic structures. Operators for computations are referred to as " computational operators ", operators for control formulations are called " control operators ", and operators for the formations of syntactic structures are called " syntactic operators". Any operator is classified as computational operator if its operation has to be defined by an " data operation expression ". Some of the operators primarily designated for control formulations operate as if they are computational operators. Therefore they are included in the class of computational operators. Since some of the Boolean operators may

be used for computations as well as control formulations, they are included in both the classes of computational operators and Table 2-2 shows the complete set of control operators. computational operators subdivided into different functions. Table 2-3 illustrates the unary operations of the computational operators on the register A. Table 2-4 illustrates the binary operations of the computational operators on the registers A and B , and the constant C ( i.e. integer variable ). Table 2-5 shows the complete set of control into different groups according to operators subdivided functions. Table 2-6 illustrates the unary and binary operations of the control operators on the Boolean variables D and E, and the integer variable K. Table 2-7 shows the complete set of syntactic operators. It should be noted that the classification the basic set of operators into the three different types of operators is made only to provide a clearer concept.

Although the basic set of operators is sufficient to meet most of the general requirements, occasions may arise, where special operators are needed to be defined to describe either non-standard, or higher-level functions. The fact that an operator actually abstracts a modular logic network implies that a process to define a special operator corresponds to the definition of a particular module. The definition of any special operator can be worked out by either one of the two ways: simple declaration, and procedure call.

The simple declarations are having the syntax:

Operator: OPERATOR IDENTIFIER begin ALGORITHM end

For example, the operator which represents the operation of a A-to-D converter is declared:

Operator : convert

D

TI LI

افغ رو

begin

Integer: A \$ A represents an analog signal changing respective to time

Register : D

$(A>D) \longrightarrow D \longleftarrow count-up D$

$(A < D) \longrightarrow D \longrightarrow count-down D$

end

\$ The capability of the operator " convert "

\$ is assumed by the declaration. Then; it can

\$ be used like other standard operators

\$ available in the behavioral level of AHDL.

\$ What is delimited in the brackets " begin,

\$ end " serves to depict the basic property

\$ of this special operator, and it has the

\$ same meaning as the assignment statement

\$ of : D — convert A .

"convert " is the operator with the working algorithm defined within the separators (actually brackets) "begin "and "end". In this case the operator "convert "serves more for documentary purpose. It specifies the fact that an analog value represented by the integer variable A is converted into a binary value to be stored in the register D. The actual conversion-mechanism is not specified here, but its existence is implied.

The detailed working algorithm of any special operator can be theoretically described in an appropriate procedure. The application of the special operator then becomes a procedure call. The procedural algorithm may provide the framework for actual implementation. Therefore procedures to represent special operators are not only for documentary purposes, but they may represent the simple and ultimate drafts in the early phase of a design process. Procedures will be discussed in more details in one of the latter sections.

Table 2-2 The complete set of computational operators

| Operator Gro                            | úp Symbol  | Explanation                                          |

|-----------------------------------------|------------|------------------------------------------------------|

| arithmetic                              | +          | conventional addition                                |

|                                         | <i>-</i>   | conventional subtraction .                           |

|                                         | <b>x</b>   | conventional multiplication                          |

|                                         |            | conventional division .                              |

| logical                                 |            | logical NOT                                          |

| • · · · · · · · · · · · · · · · · · · · | ٧.`        | logical OR                                           |

|                                         | ^          | logical AND                                          |

|                                         | •          | logical EXCLUSIVE-OR                                 |

| vectoral                                | shift,     | conventional right shift                             |

| •                                       | rotate     | circular left shift                                  |

|                                         | exchange   | swap the contents of two registers                   |

| special                                 | count-up   | count up by one                                      |

|                                         | count-down | count down by one                                    |

|                                         | decode     | select one out of " 2 to the power n " possibilities |

transfer

transfer the computed result to the designated carrier

Table 2-3 Unary operations of the computational operators on register A.

| Expression of Unary<br>Data Operation | Explanation                                                                                                       | چەدىسەسى<br>ر |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------|

| v A                                   | logical OR all bits of A                                                                                          |               |

| _^A                                   | logical AND all bits of A                                                                                         |               |

| θA                                    | logical EXCLUSIVE OR all bits of                                                                                  | <b>,</b> A    |

| . A                                   | logical COMPLEMENT all bits of A                                                                                  | ,             |

| rotate A                              | shift A one bit to the left with the content of the leftmost bit inserted into the position of the right-most bit |               |

| shift A                               | shift A one bit to the right with the rightmost bit dropped off                                                   | . •           |

| count-up A                            | increase the content of A by one                                                                                  | •             |

| count-down A                          | decrease the content of A by one                                                                                  | <b>`</b>      |