Acquisitions and Bibliographic Services Branch

395 Weilington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file Notice references

Our frei Notic reference

## NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

**AVIS**

La qualité de cette microforme

If pages are missing, contact the university which granted the degree.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# The Design and Implementation of an Advanced Robot Controller

Jonathan Neil Brodkin

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at Concordia University Montréal, Québec, Canada

November 1990

© Jonathan Neil Brodkin, 1990

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your life. Votte référence

Our Ne Notre référence

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive Bibliothèque permettant à la nationale Canada du reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse disposition des à la personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-90942-0

# ABSTRACT

# The Design and Implementation of an Advanced Robot Controller

# Jonathan N. Brodkin

This thesis describes an architecture for implementing an Advanced Robot Controller (ARC). The ARC has been designed and built as a replacement for the controllers of conventional industrial robotic systems. The need for such a device arises because most industrial robots are constrained by tileir controllers' hardware and software to performing in a simple, pre-defined manner. The ARC hardware consists of a hierarchically-designed dual-processor operating in a master-slave configuration and communicating via dual-port RAM, a bank of quadrature decoders/counters, and a bank of digital to analog converters. A software library has been established consisting of various control and path planning algorithms. This library also contains a set of functions to facilitate algorithm coding and testing. The ARC was integrated with an IBM 7545 Manufacturing System and proved extremely successful in achieving tight control over the 7545's four joints.

# **ACKNOWLEDGEMENTS**

In submitting this thesis I must acknowledge Dr. R. V. Patel for the guidance and support that he provided to me throughout the course of my research and writing; but above all I must thank Dr. Patel for his unwavering trust in my abilities which contributed to my motivation and confidence in this endeavor.

There are several others whose assistance was most appreciated at particular junctures, including hardware suggestions, circuit construction, programming, debugging and text review: Guy Gosselin, Harvey Brodkin, Alan Robins, Claude-Marie Lafforgue, Henry Polley, Mike Stashin, Vladimir Zeman, Venkatram Pramod, and Claude Tessier.

Finally, I would like to thank my family and friends for their constant and enthusiastic support and encouragement.

# TABLE OF CONTENTS

| LIST       | OF TABLESvii                                                                                                                                                                                            | i           |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| LIST       | OF FIGURESi                                                                                                                                                                                             | x           |

|            | PTER 1 RODUCTION                                                                                                                                                                                        | 1           |

| 1.1        | Industrial Robotic Systems                                                                                                                                                                              | 1           |

| 1.2        | Summary of the Research Work                                                                                                                                                                            | 3           |

| 1.3        | Thesis Organization                                                                                                                                                                                     | 4           |

| CHA<br>THE | PTER 2 IBM 7545 MANUFACTURING SYSTEM                                                                                                                                                                    | 5           |

| 2.1        | Introduction                                                                                                                                                                                            | 5           |

| 2.2        | The IBM 7545 Manipulator                                                                                                                                                                                | 7           |

|            | 2.2.1       Motor Location and Transmission System       1         2.2.2       DC Servo Motors and Drivers       1         2.2.3       Incremental Encoders       1         2.2.4       Sensors       1 | 11<br>14    |

| 2.3        | Summary1                                                                                                                                                                                                | 17          |

|            | PTER 3 DWARE DESCRIPTION FOR THE ADVANCED ROBOT CONTROLLER1                                                                                                                                             | 18          |

| 3.1        | Introduction                                                                                                                                                                                            | 8           |

| 3.2        | Master Processor and Dual-Port RAM (DPR)                                                                                                                                                                | <b>X</b> O  |

| 3.3        | Slave Processor                                                                                                                                                                                         | 23          |

|            | 3.3.1 The EV80C196KA Interface                                                                                                                                                                          | 23          |

| 3.4        | Digital To Analog Conversion                                                                                                                                                                            | <b>X</b> 6  |

|            | 3.4.1 Digital Circuit Details                                                                                                                                                                           |             |

| 3.5        | Position Counters                                                                                                                                                                                       |             |

| 3.6        | Home Sensors, Encoder Index and Dual-Port RAM Connection                                                                                                                                                | <b>3</b> 3  |

| 3.7        | Hardware Implementation                                                                                                                                                                                 | <b>3</b> 6i |

| 3.8        | Summary and Future Work                                                                                                                                                                                 | 36          |

|            | TWARI                                                       | 4 E DESCRIPTION FOR THE ADVANCED ROBOT CONTROLLER                                                                                                                                                         | 37                                     |

|------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 4.1        | Introd                                                      | duction                                                                                                                                                                                                   | 37                                     |

| 4.2        | Dual-I                                                      | Port RAM Utilization                                                                                                                                                                                      | 38                                     |

|            | 4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7 | Sample_Period Register. Timing_A Register. Timing_B Register. Command Register. Error Register Actual_Position Registers Torque Registers                                                                 | 40<br>40<br>41<br>41                   |

| 4.3        | Slave                                                       | Processor Software                                                                                                                                                                                        |                                        |

|            | 4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                            | Main Program  Find-HOME Mode  Control Mode  Additional Procedures  4.3.4.1 Get_Joint_Positions  4.3.4.2 Delay  4.3.4.3 Zero_DACs  4.3.4.4 Joint_Overrun_Check  4.3.4.5 Check_Torques  4.3.4.6 Torques_Out | 44<br>46<br>50<br>51<br>52<br>53<br>54 |

| 4.4        | Maste                                                       | er Processor Software                                                                                                                                                                                     |                                        |

|            | 4.4.1<br>4.4.2<br>4.4.3<br>4.4.4                            | Master Sequence of Operation Servo Control Loop Robot Control Programs 4.4.3.1 PD Control 4.4.3.2 Decentralized Adaptive Control Path Planning Programs 4.4.4.1 The Cycloid Function 4.4.4.2 Cubic Spline | 60<br>61<br>62<br>63<br>63             |

| 4.5        | Summ                                                        | nary and Future Work                                                                                                                                                                                      | 65                                     |

| CHA<br>EXP | FTER S                                                      | 5<br>ENTAL RESULTS                                                                                                                                                                                        | 67                                     |

|            | PTER (                                                      | 6<br>IONS                                                                                                                                                                                                 | 102                                    |

| REF        | ERENC                                                       | CES                                                                                                                                                                                                       | 104                                    |

|            | ENDIX<br><b>754</b> 5                                       | A S WIRING DIAGRAMS                                                                                                                                                                                       | 106                                    |

|            | ENDIX                                                       | B<br>OTOR RATINGS AND SPECIFICATIONS                                                                                                                                                                      | 112                                    |

| APPENDIX C CALIBRATION                             | 114 |

|----------------------------------------------------|-----|

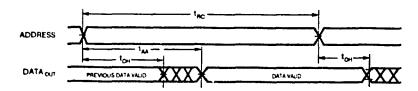

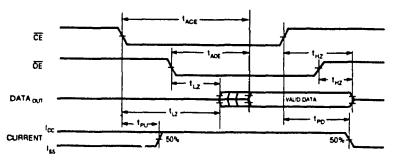

| APPENDIX D<br>PS/2 TIMING DIAGRAMS                 | 116 |

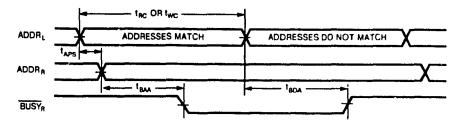

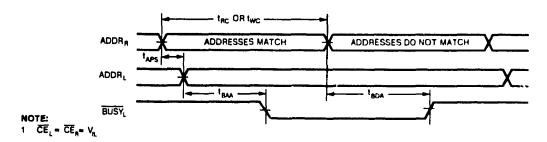

| APPENDIX E DUAL-PORT RAM TIMING WAVEFORMS          | 122 |

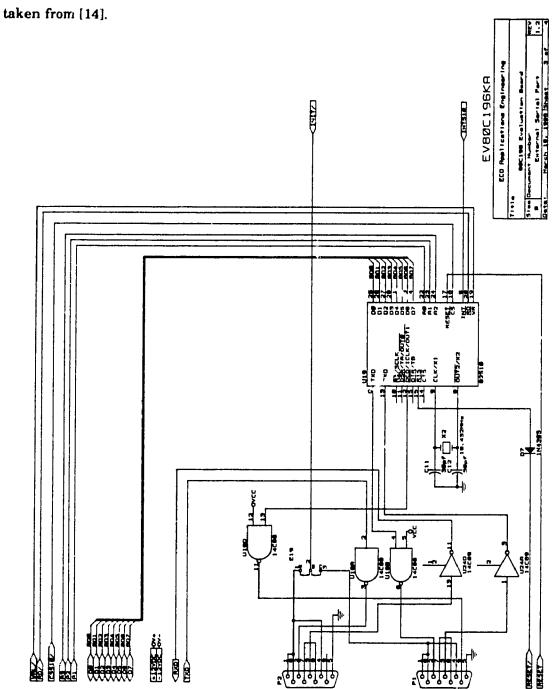

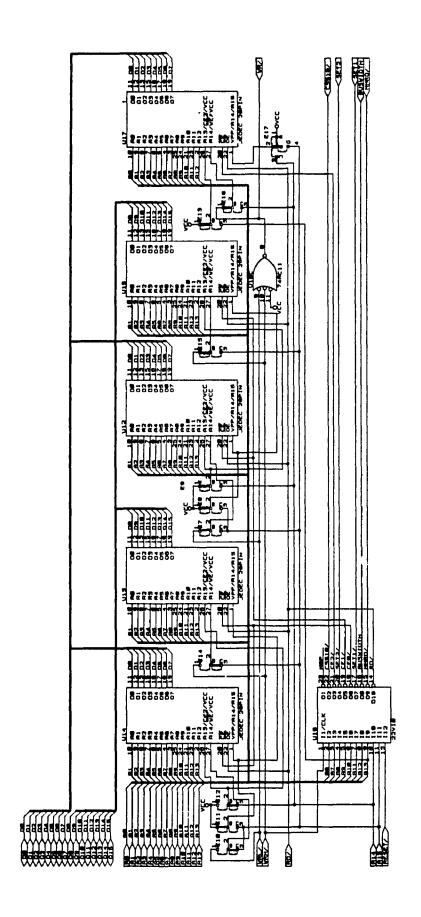

| APPENDIX F EV80C196KA SCHEMATIC DIAGRAM            | 126 |

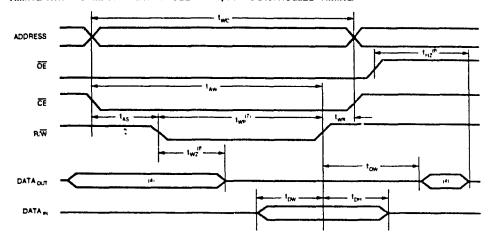

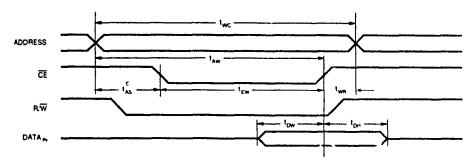

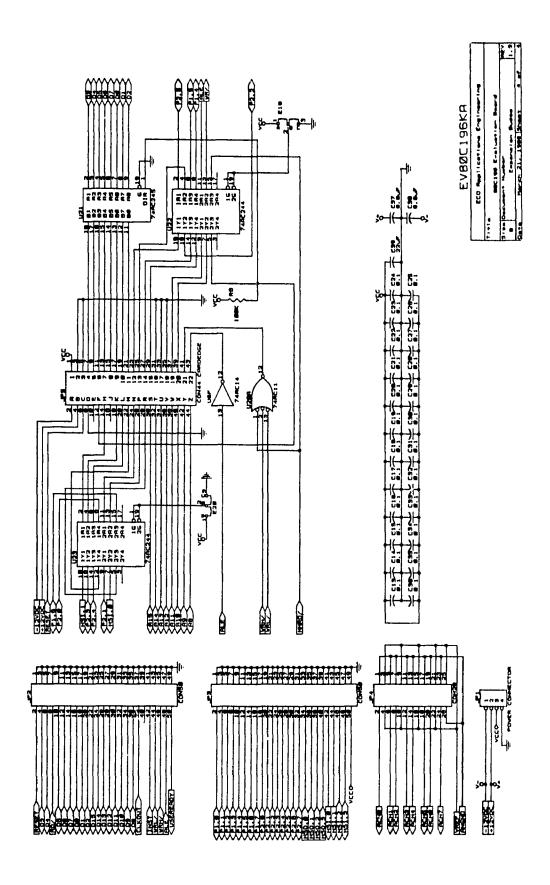

| APPENDIX G<br>80C196KA BUS TIMING                  | 130 |

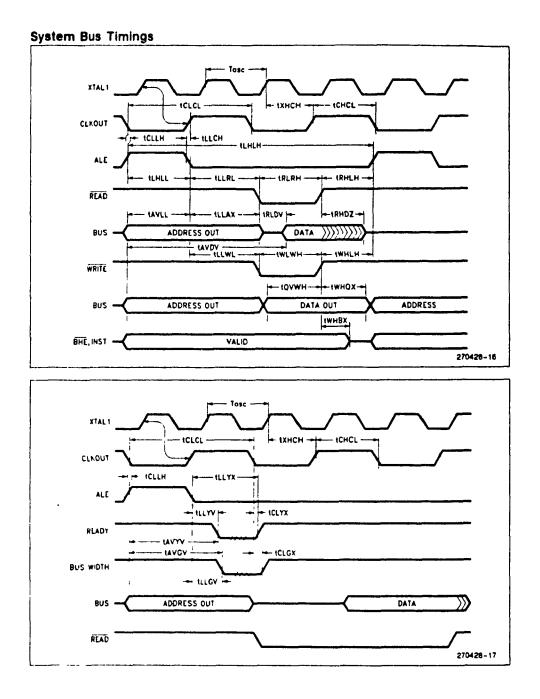

| APPENDIX H AD667 BLOCK DIAGRAM AND TIMING DIAGRAMS | 132 |

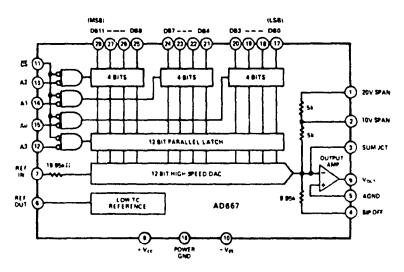

| APPENDIX I<br>HCTL-1000 BLOCK AND TIMING DIAGRAMS  | 133 |

| APPENDIX J<br>SLAVE SOURCE CODE                    | 136 |

| APPENDIX K MASTER SOURCE CODE                      | 143 |

# LIST OF TABLES

| 2.1 | 7545 Joint Position Resolutions        | 14 |

|-----|----------------------------------------|----|

| 3.1 | Digital to Analog Converter Addresses  | 2  |

| 3.2 | Memory Map for the HCTL-1000s          | 3  |

| 4.1 | Dual-Port RAM Register Reference Table | 3  |

# LIST OF FIGURES

| 2.1  | IBM 7545 Manufacturing System                           | . 6          |

|------|---------------------------------------------------------|--------------|

| 2.2  | Block Diagram of the IBM 7545 Manufacturing System      | . 6          |

| 2.3  | IBM 7545 Manipulator                                    | . 8          |

| 2.4  | IBM 7545 Manipulator Work Envelope                      | . 9          |

| 2.5  | Servopack Internal Block Diagram                        | 12           |

| 2.6  | Modified Servopack, Encoder and HOME Sensor Connections | 13           |

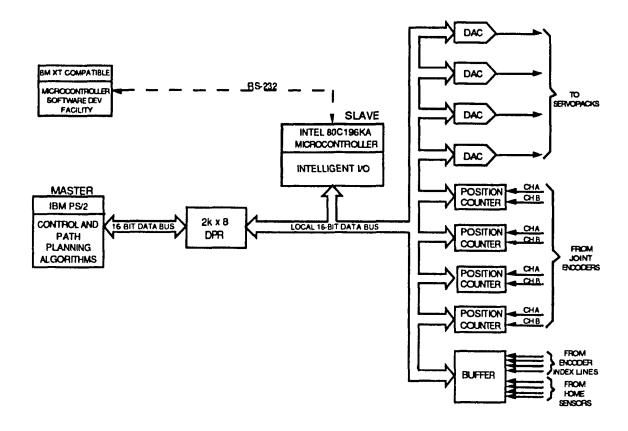

| 3.1  | Block Diagram of the ARC Hardware                       | 19           |

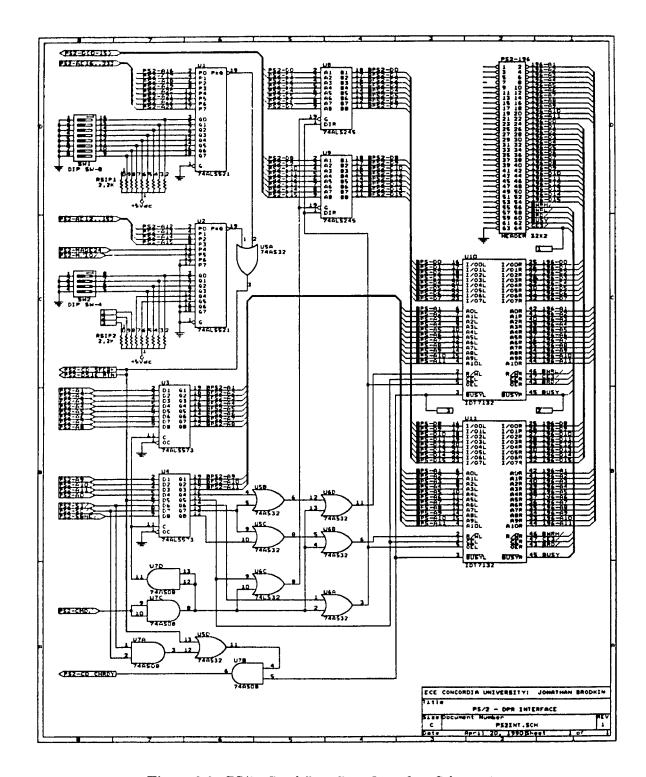

| 3.2  | PS/2 - Dual-Port Ram Interface Schematic                | 21           |

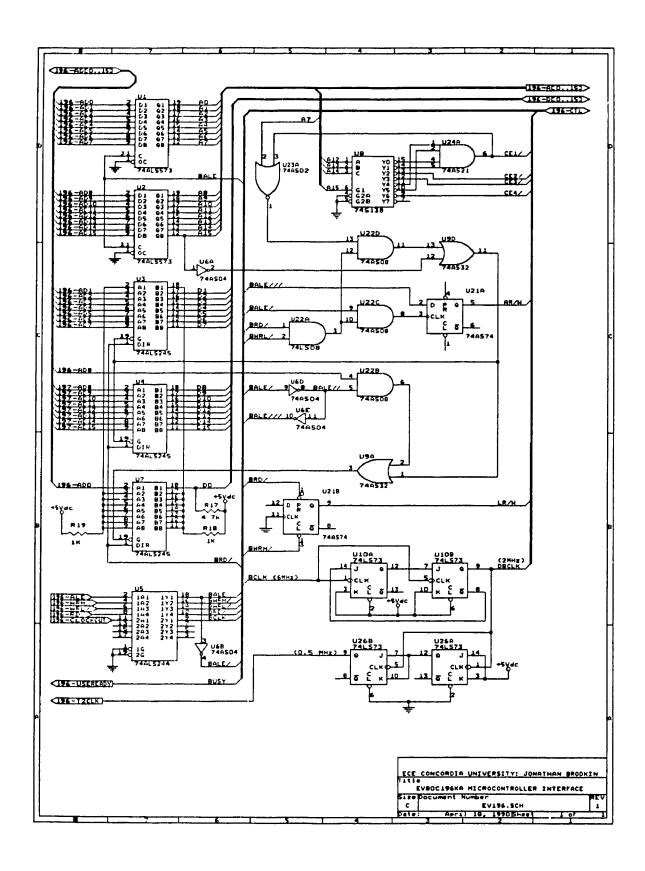

| 3.3  | 80C196KA Interface Schematic                            | 25           |

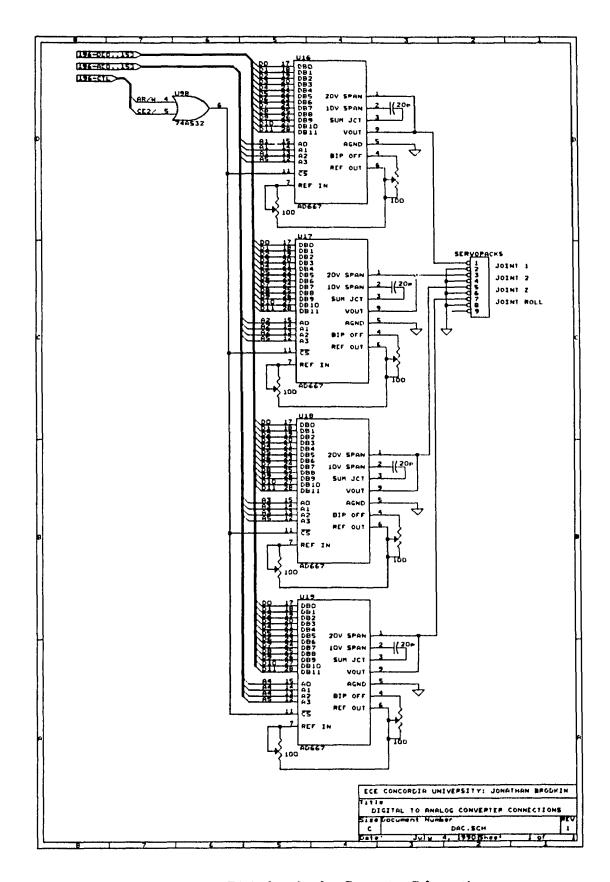

| 3.4  | Digital to Analog Converter Schematic                   | <b>2</b> 8   |

| 3.5  | HCTL-1000 Schematic                                     | 30           |

| 3.6  | Index and HOME Sensor Schematic                         | . 35         |

| 4.1  | Block Diagram of the ARC Software                       | . 33         |

| 4.2  | Flow Chart for the Slave's Main Program                 | . 43         |

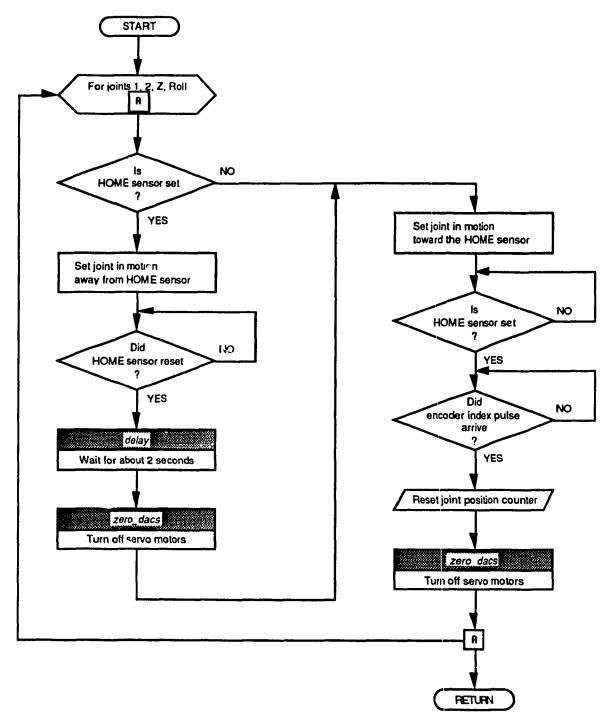

| 4.3  | Flow Chart for the Find-HOME Mode                       | . 45         |

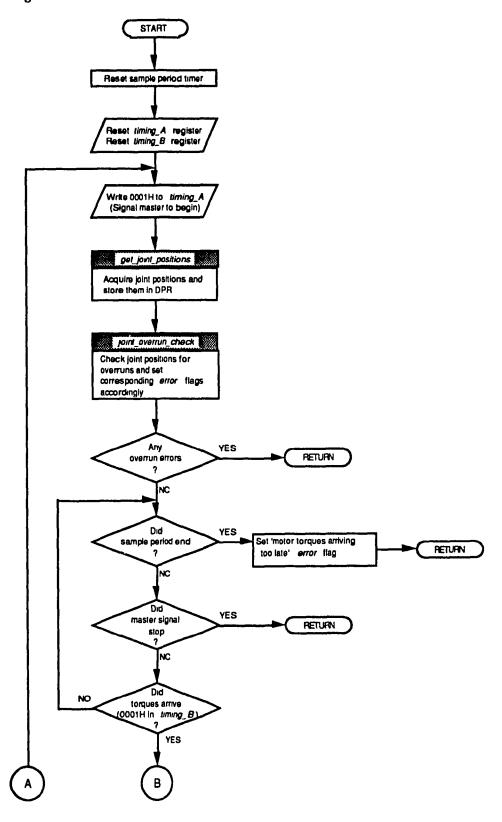

| 4.4  | Flow Chart for the Control Mode                         | . 48         |

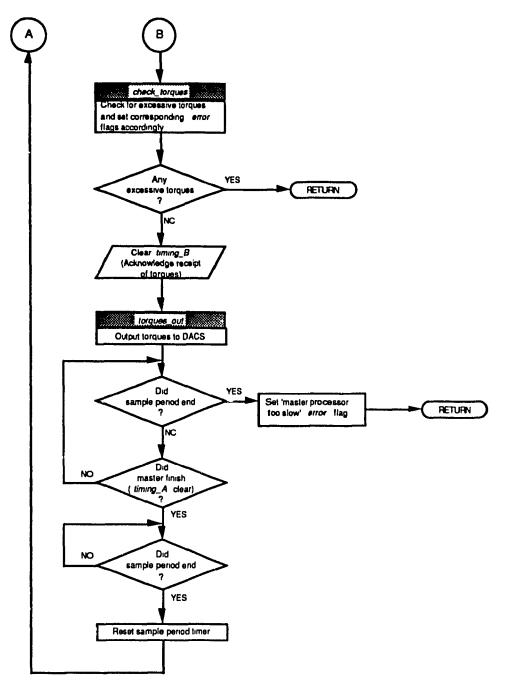

| 4.5  | Flow Chart for Delay Procedure                          | . 52         |

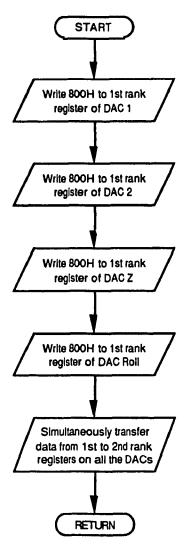

| 4.6  | Flow Chart for Zero_DACs Procedure                      | . 53         |

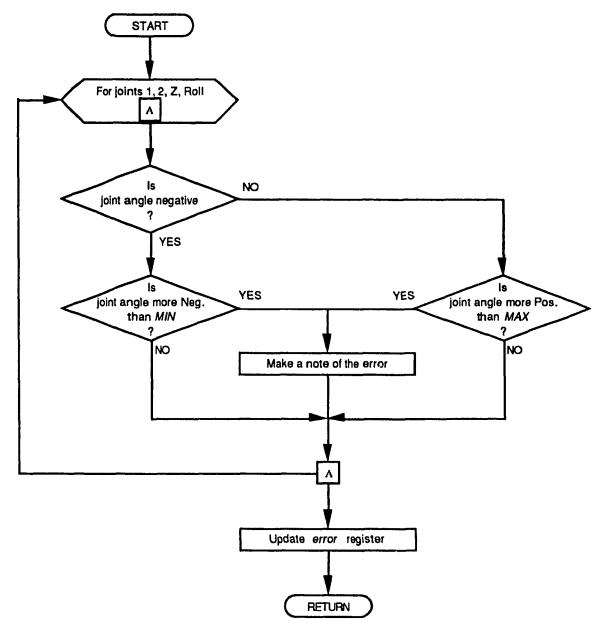

| 4.7  | Flow Chart for Joint_Overrun_Check Procedure            | . 54         |

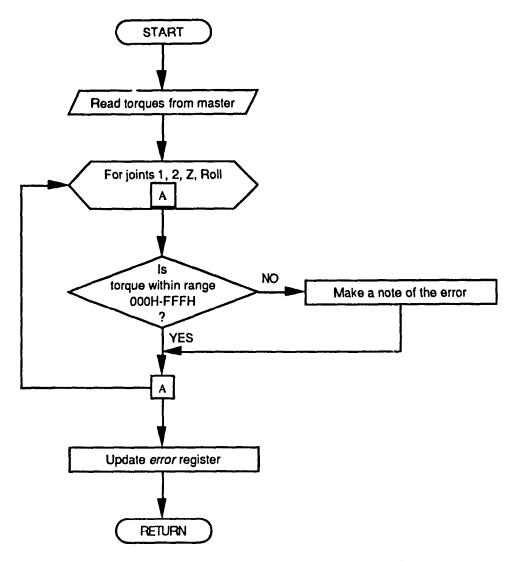

| 4.8  | Flow Chart for Check_Torques Procedure                  | . <b>5</b> 5 |

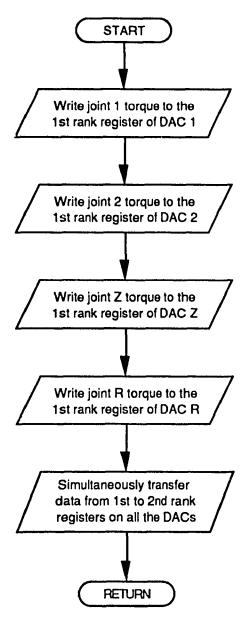

| 4.9  | Flow Chart for Torques_Out Procedure                    | . 56         |

| 4.10 | Sequence of Operation of the Master Software            | . 58         |

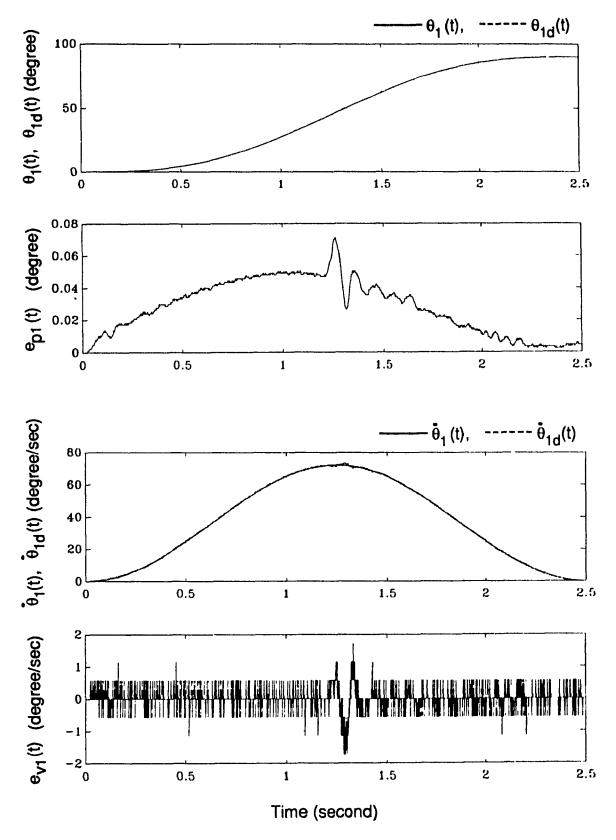

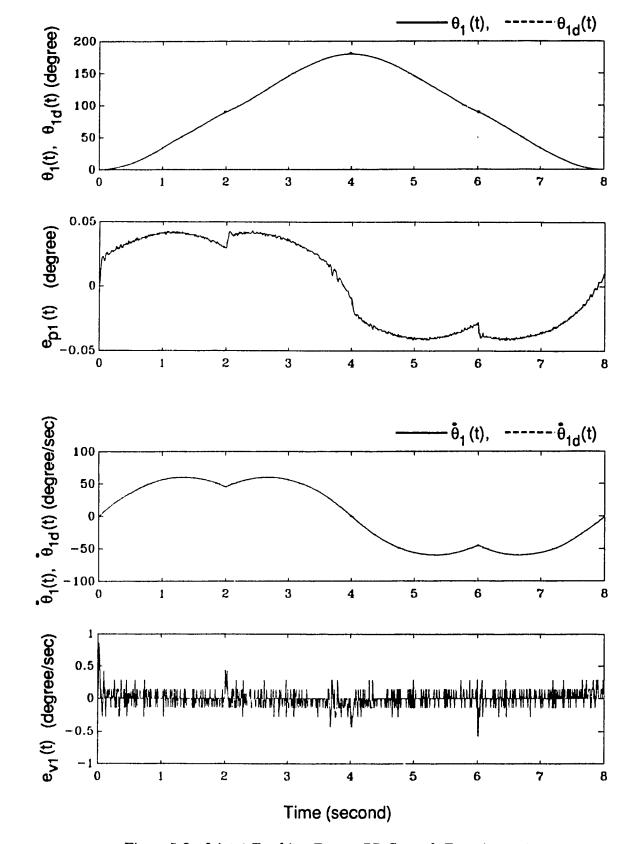

| 5.1  | Joint 1 Tracking Errors, PD Control, Experiment 1       | . 70         |

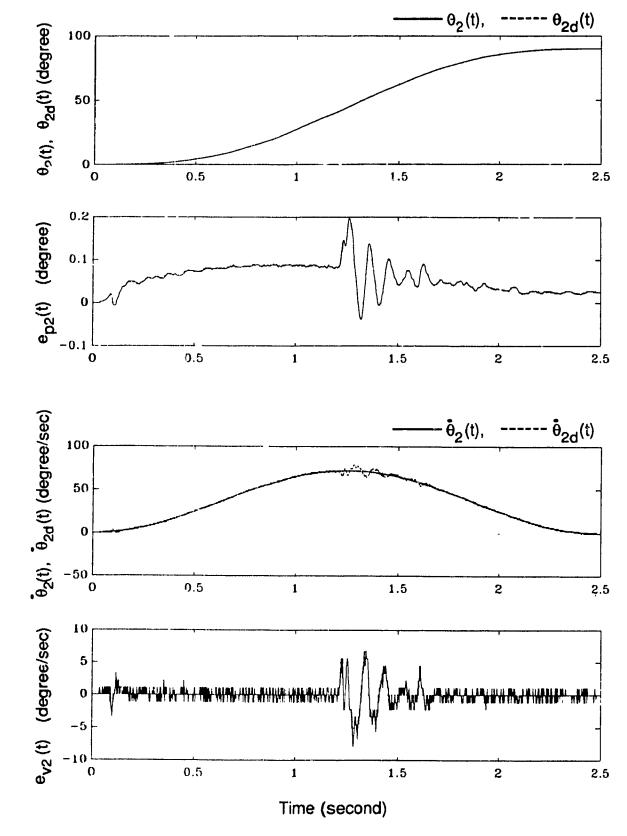

| 5.2  | Joint 2 Tracking Errors, PD Control, Experiment 1       | . 71         |

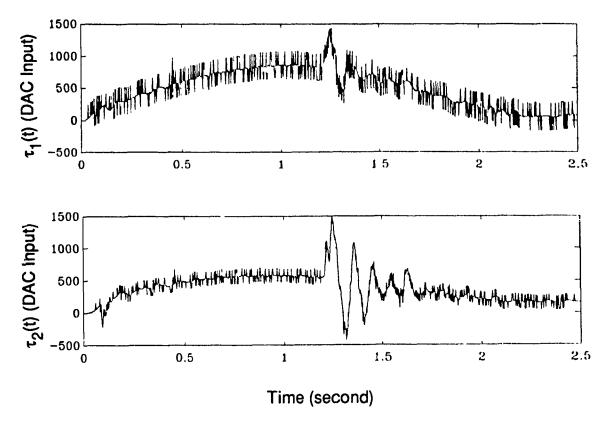

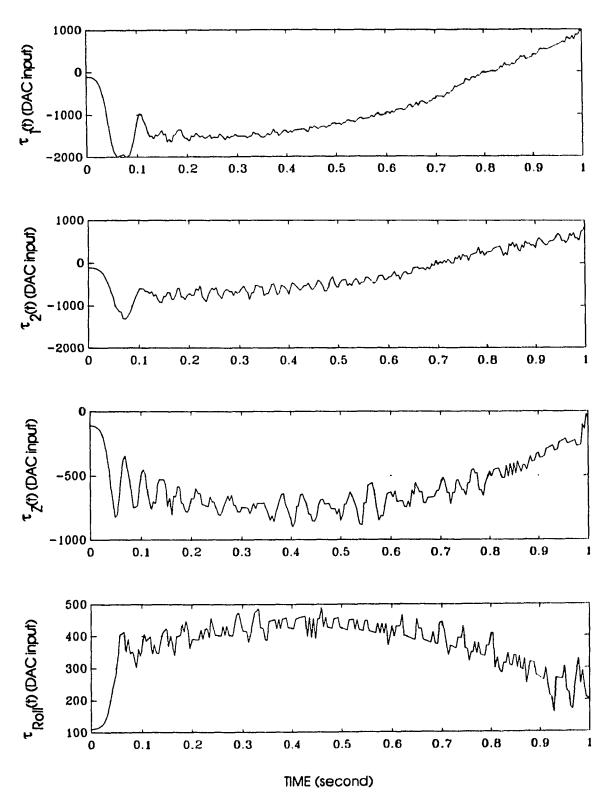

| 5.3  | Torques, PD Control, Experiment 1                                            | . <b>7</b> 2 |

|------|------------------------------------------------------------------------------|--------------|

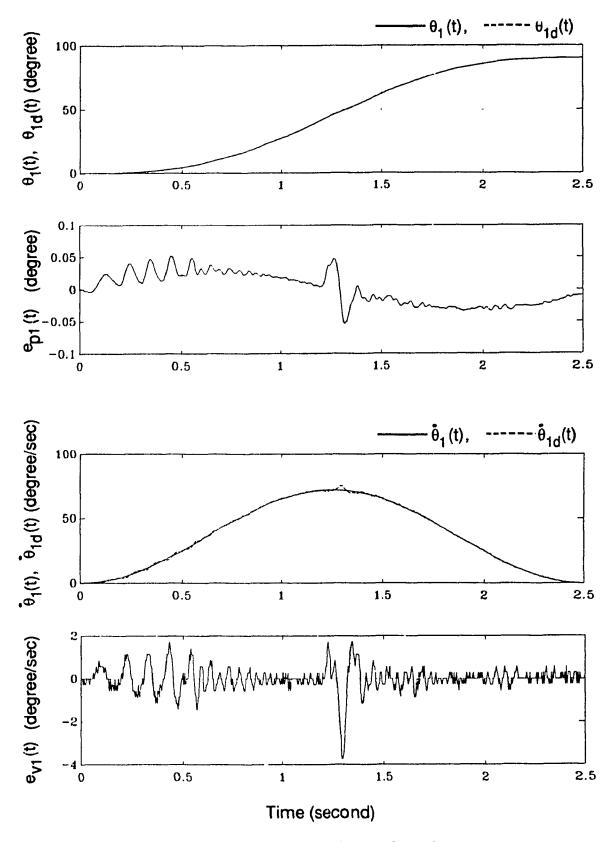

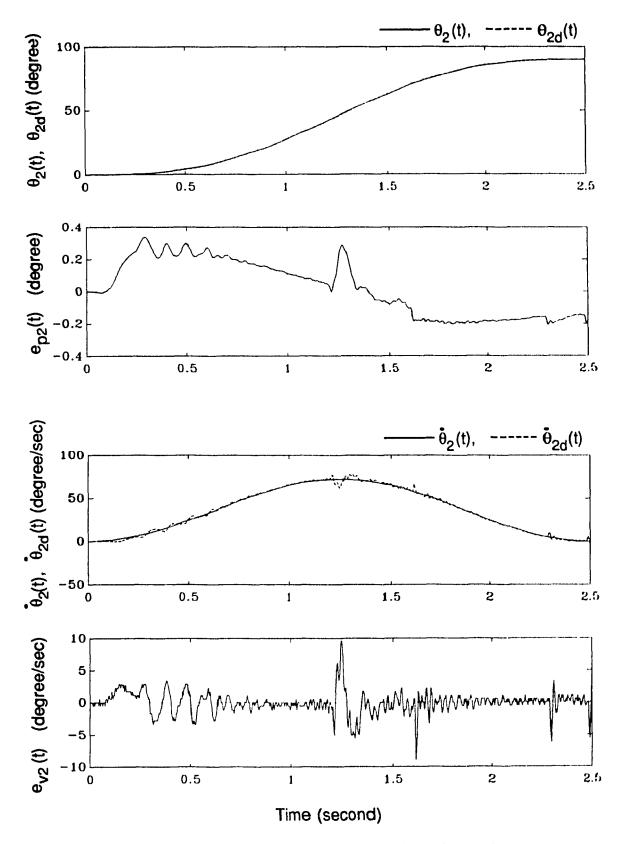

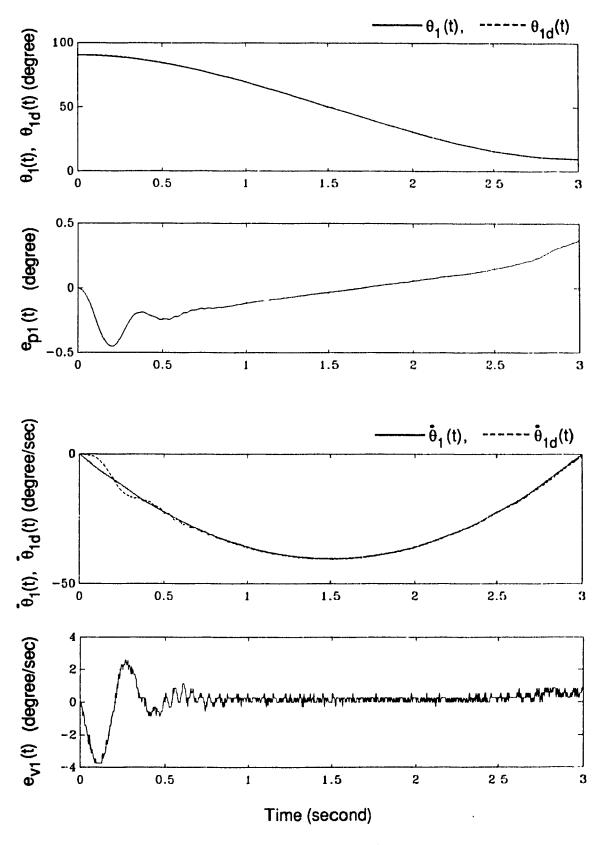

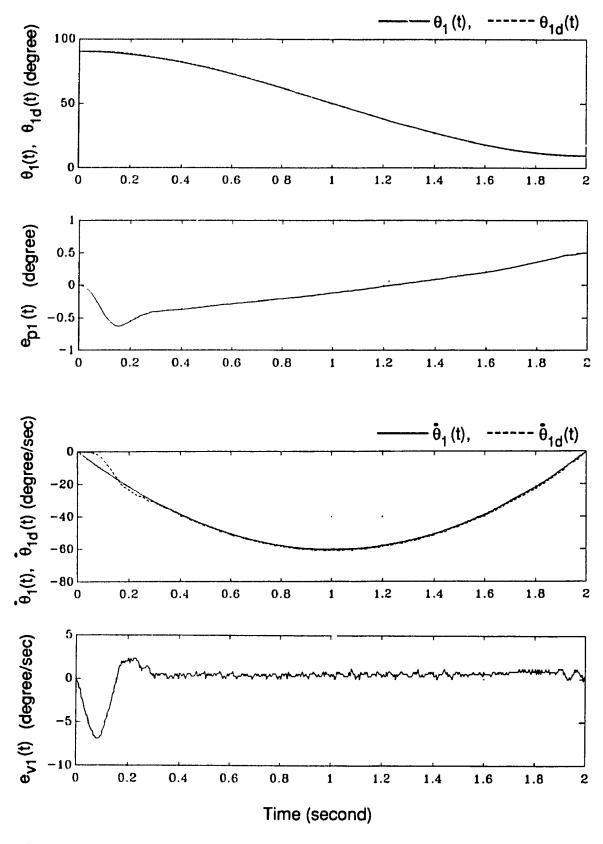

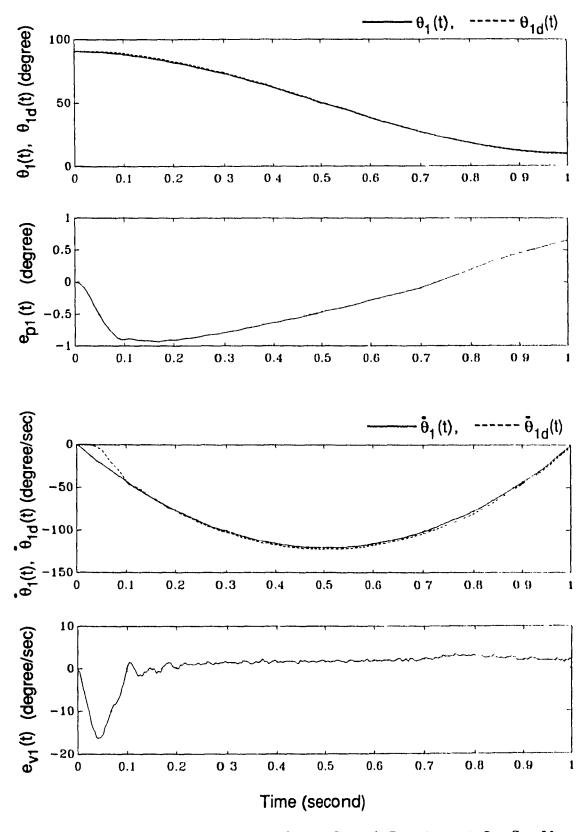

| 5.4  | Joint 1 Tracking Errors, Adaptive Control, Experiment 1                      | . <b>7</b> 3 |

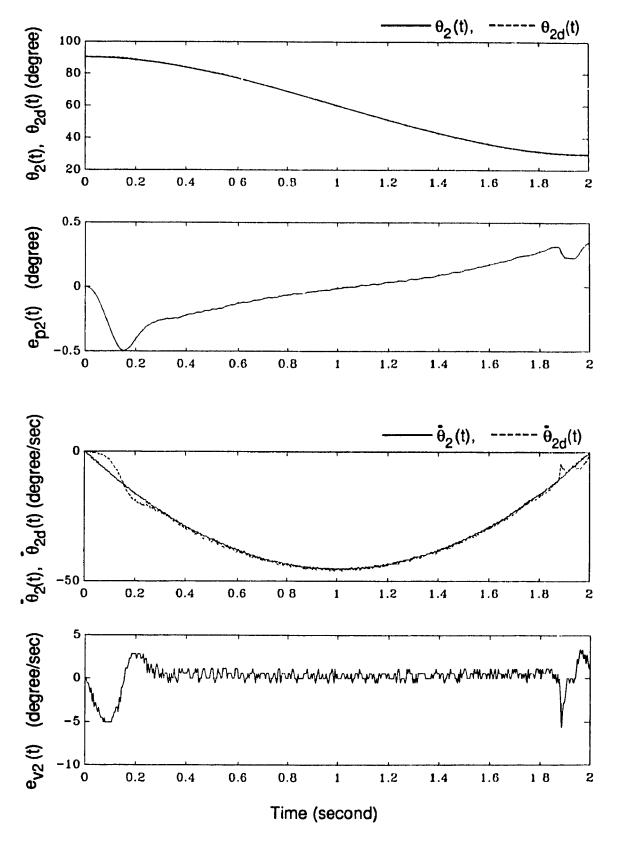

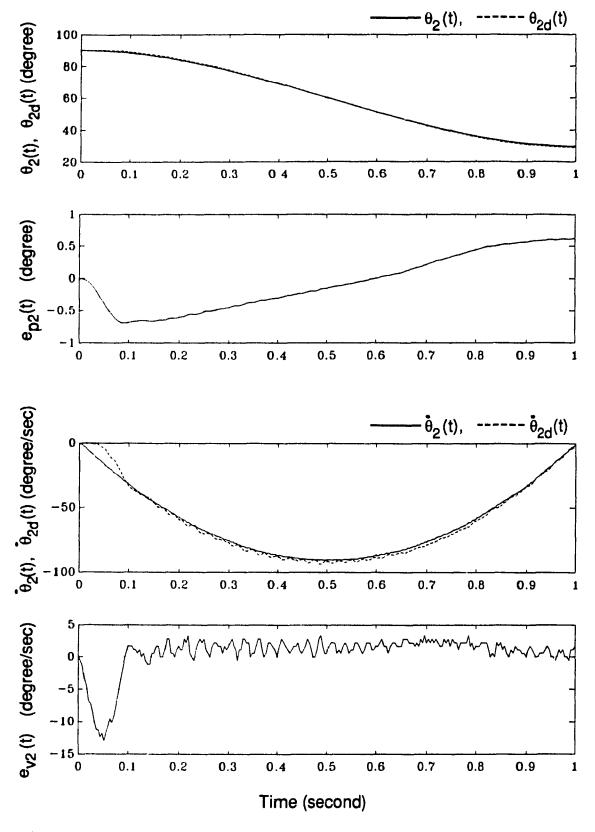

| 5.5  | Joint 2 Tracking Errors, Adaptive Control, Experiment 1                      | , 74         |

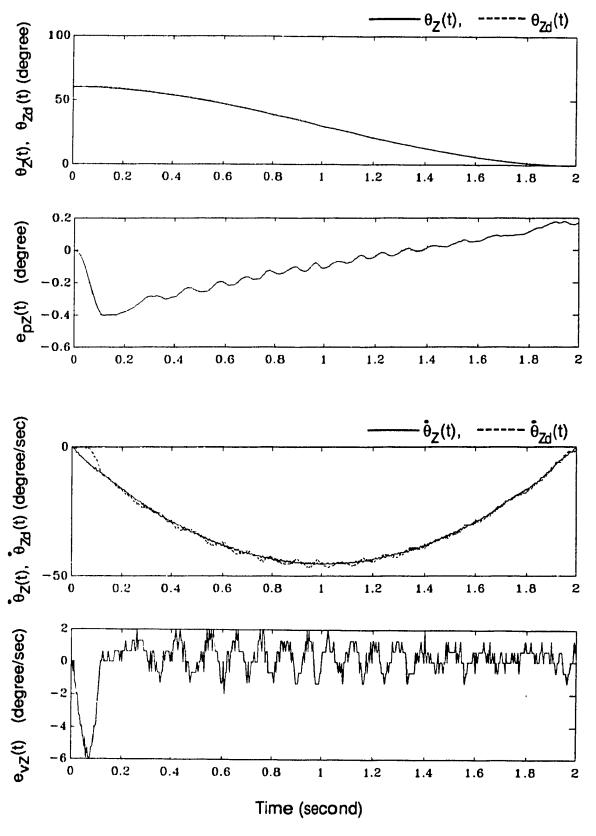

| 5.6  | Torques, Adaptive Control, Experiment 1                                      | . 75         |

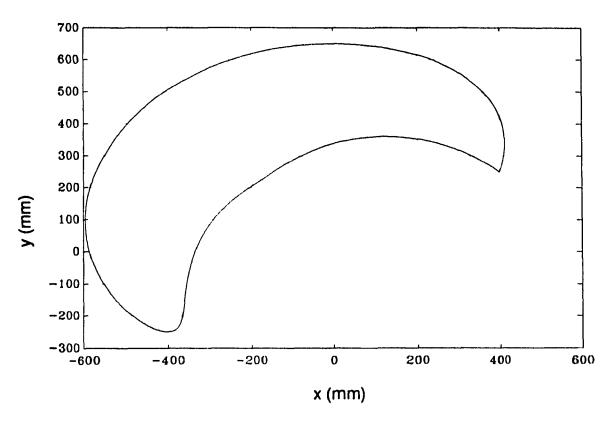

| 5.7  | Desired Path of Joints 1 and 2 for Experiment 2 Shown in Cartesian Space     | . 76         |

| 5.8  | Joint 1 Tracking Errors, PD Control, Experiment 2                            | . 77         |

| 5.9  | Joint 2 Tracking Errors, PD Control, Experiment 2                            | . 78         |

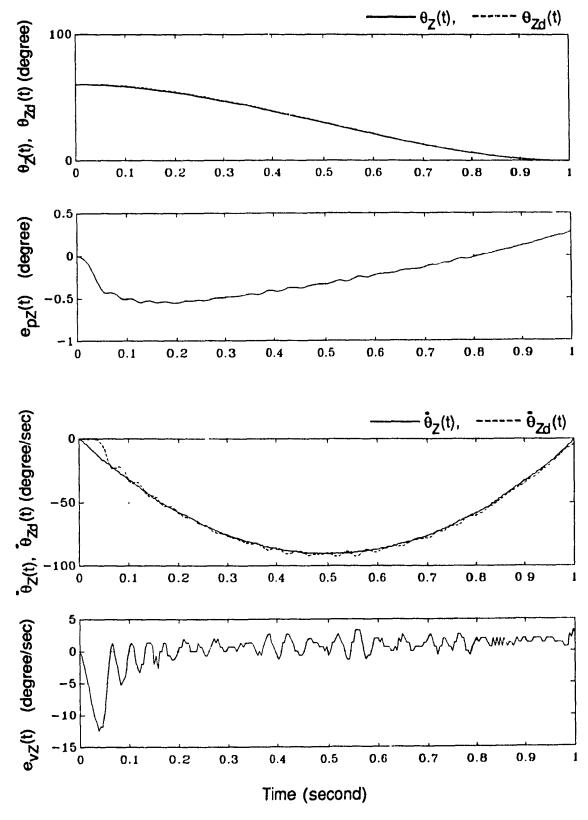

| 5.10 | Joint Z Tracking Errors, PD Control, Experiment 2                            | . <b>7</b> 9 |

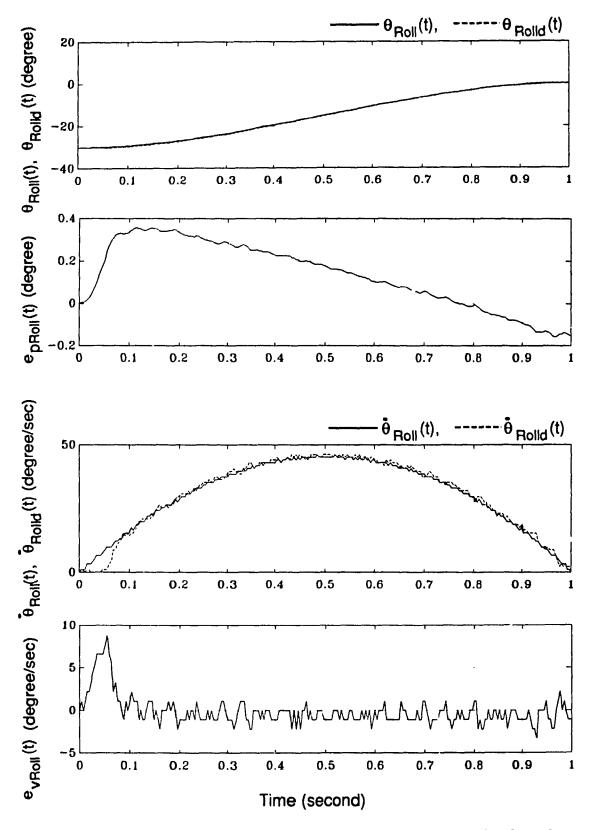

| 5.11 | Joint Roll Tracking Errors, PD Control, Experiment 2                         | . 80         |

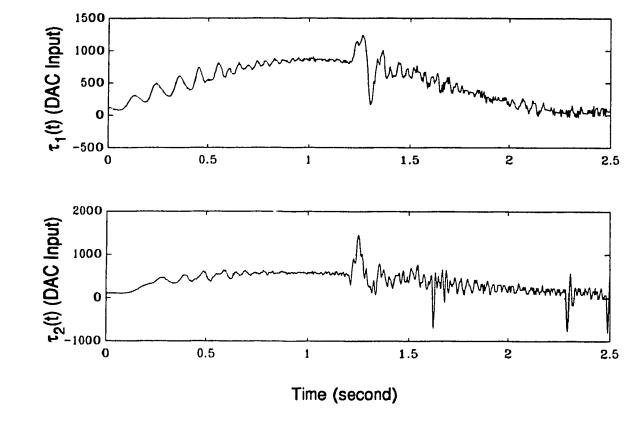

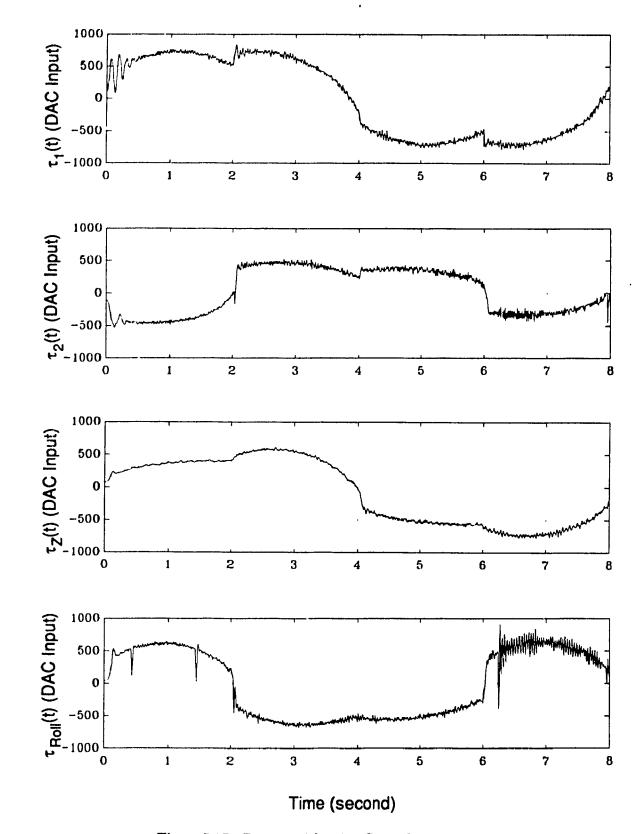

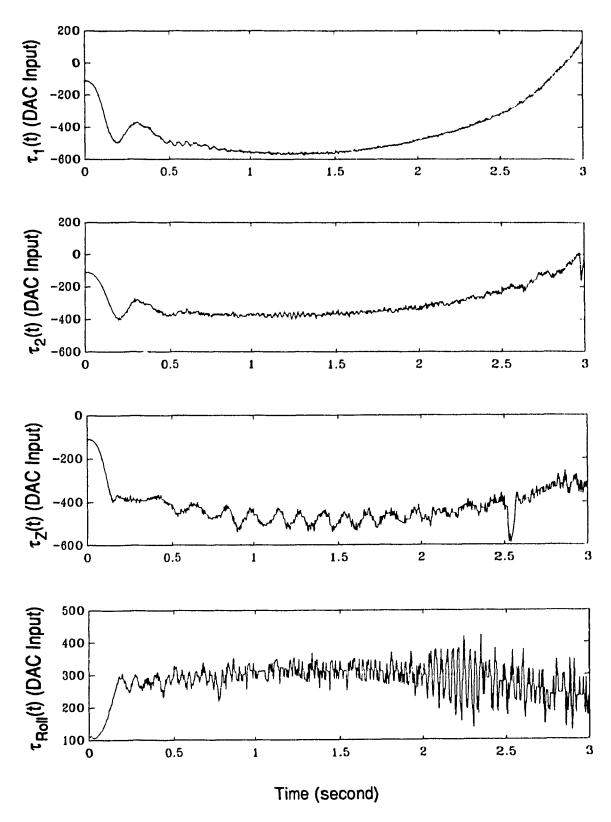

| 5.12 | Torques, PD Control, Experiment 2                                            | . 81         |

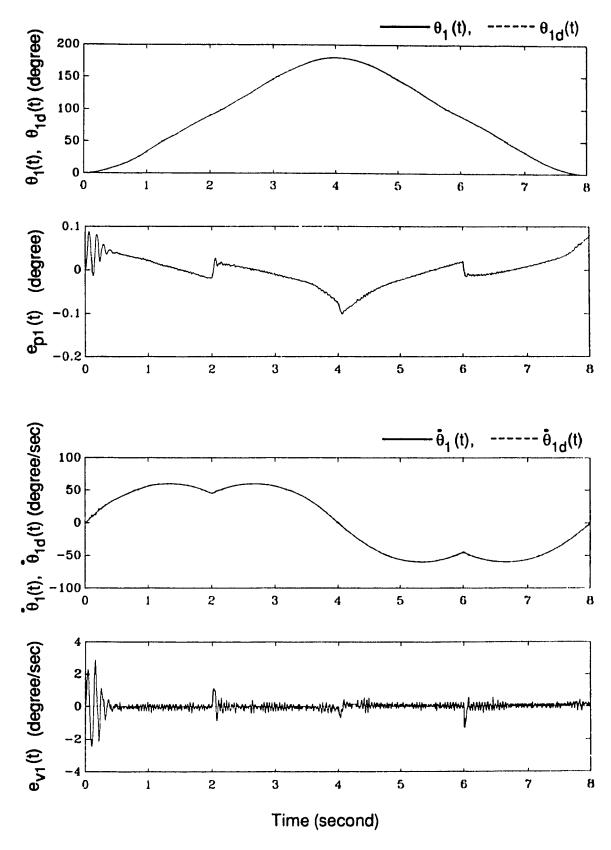

| 5.13 | Joint 1 Tracking Errors, Adaptive Control, Experiment 2                      | . 82         |

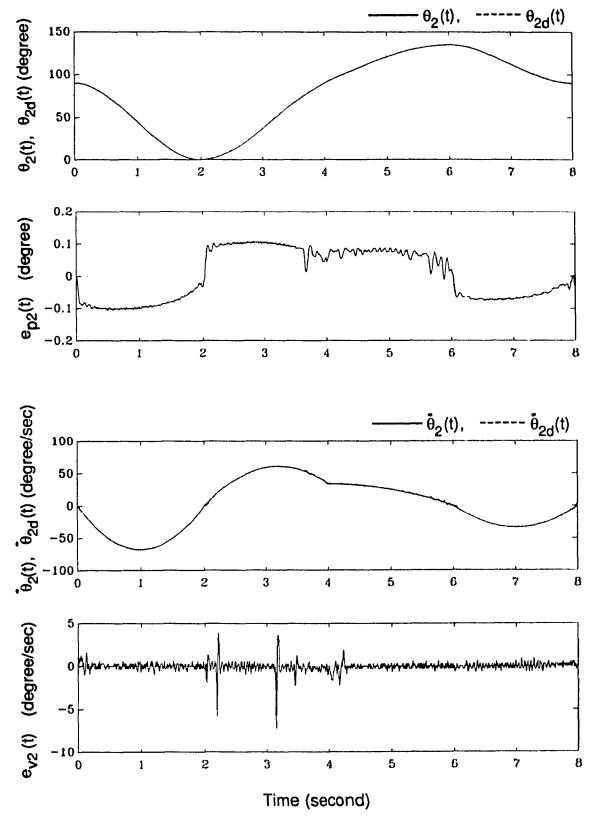

| 5.14 | Joint 2 Tracking Errors, Adaptive Control, Experiment 2                      | . 83         |

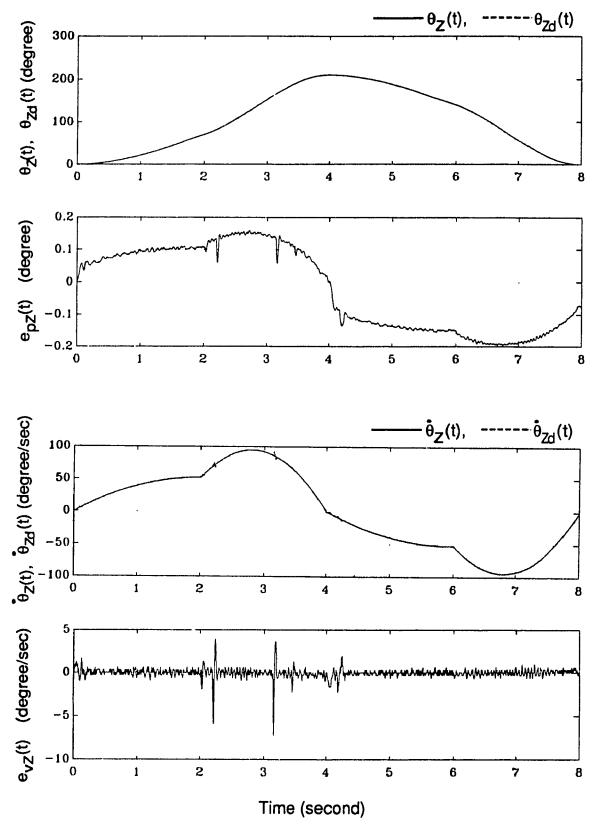

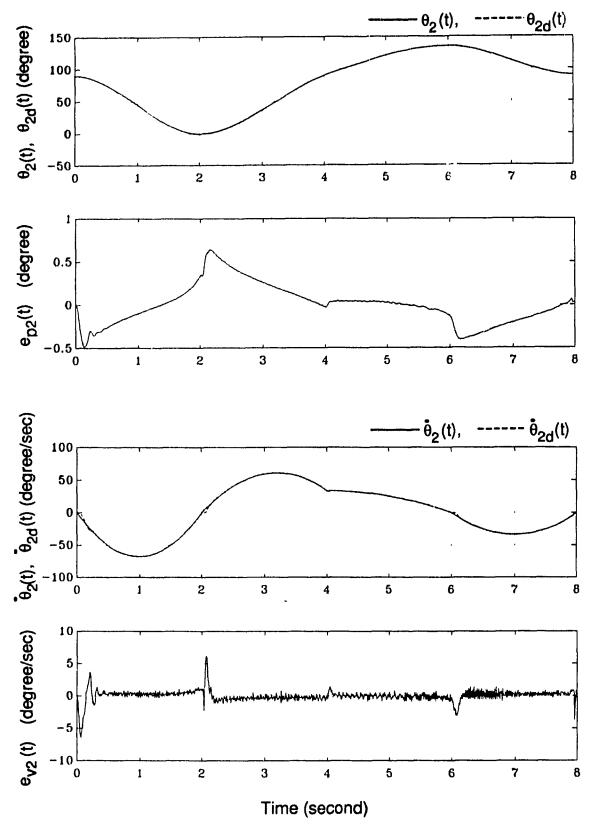

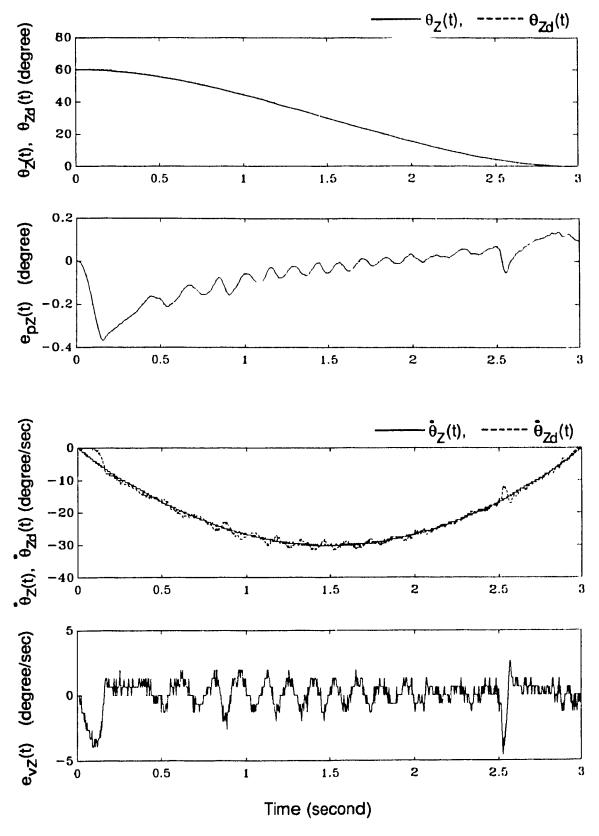

| 5.15 | Joint Z Tracking Errors, Adaptive Control, Experiment 2                      | . 84         |

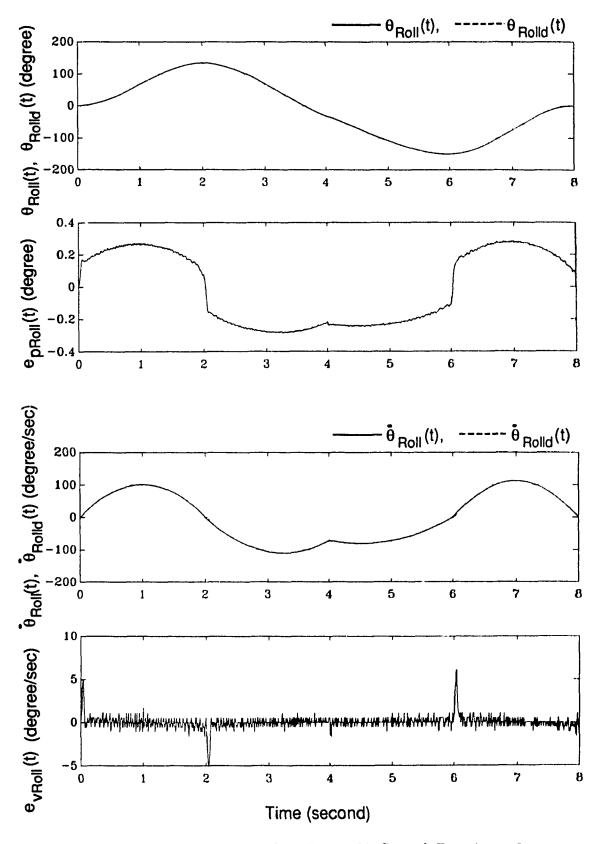

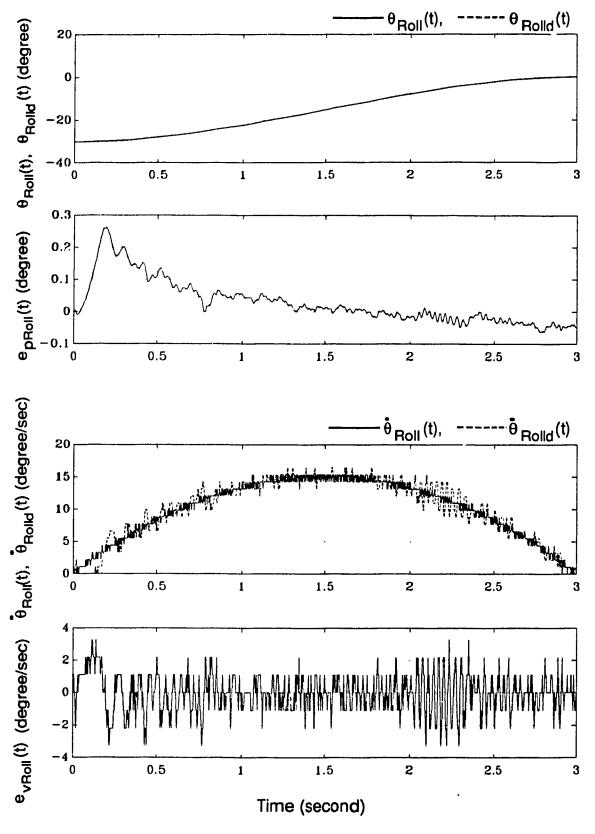

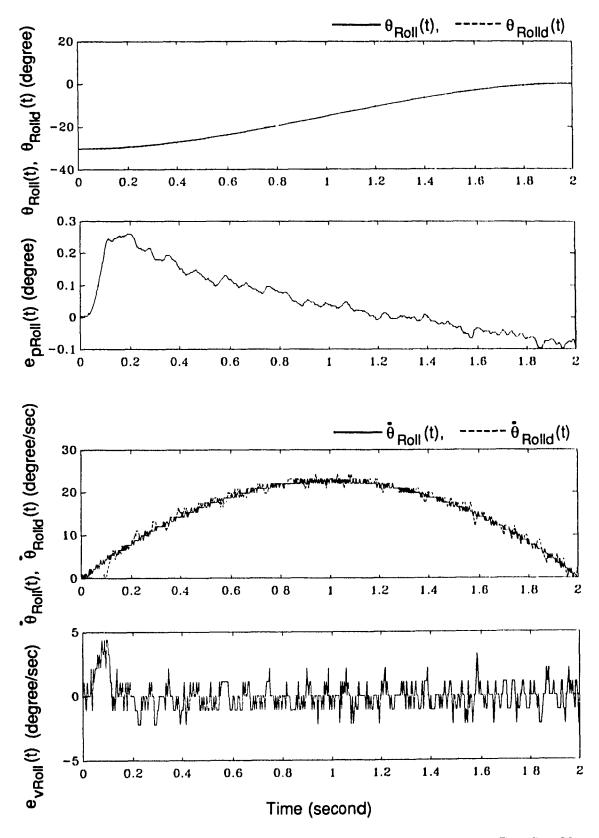

| 5.16 | Joint Roll Tracking Errors, Adaptive Control, Experiment 2                   | . 85         |

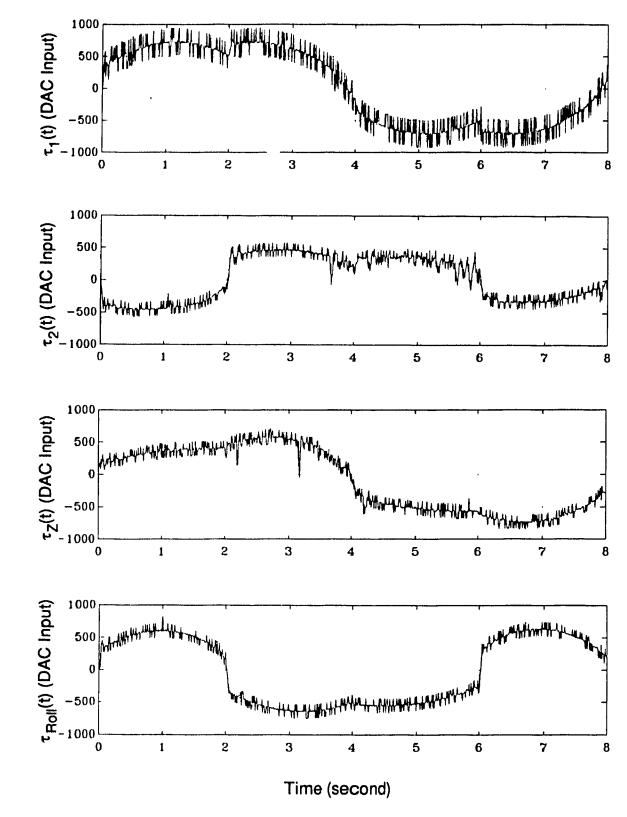

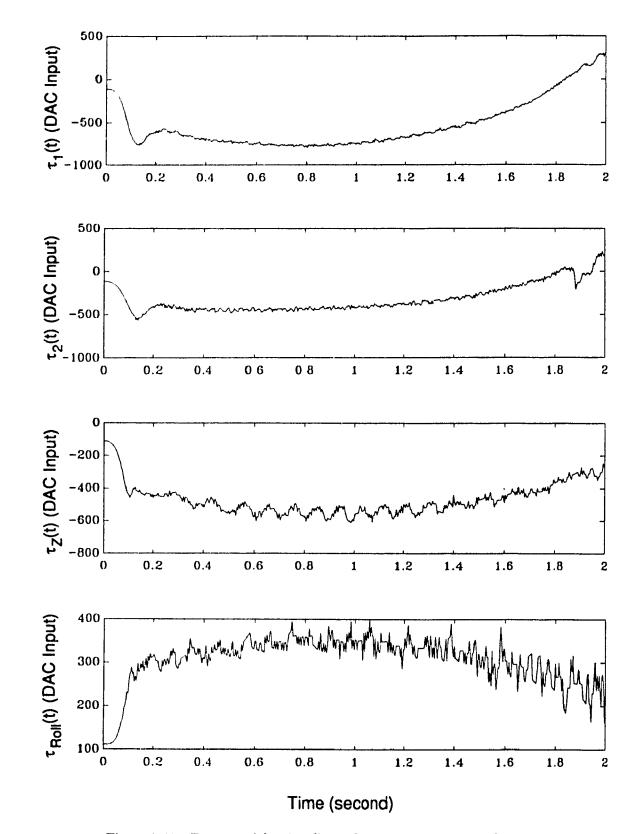

| 5.17 | Torques, Adaptive Control, Experiment 2                                      | . 86         |

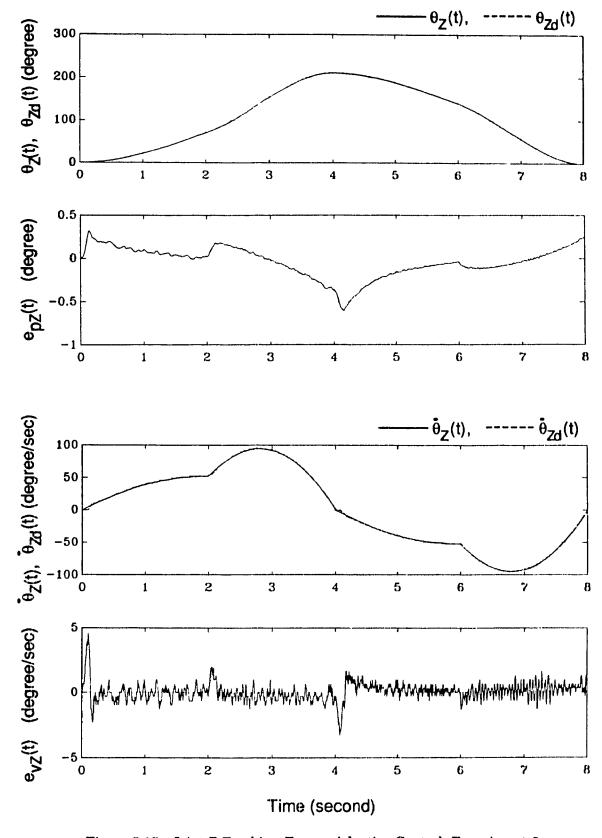

| 5.18 | Joint 1 Tracking Errors, Adaptive Control, Experiment 3, Three Sec.  Move    | . 87         |

| 5.19 | Joint 2 Tracking Errors, Adaptive Control, Experiment 3, Three Sec.  Move    | . <b>8</b> 8 |

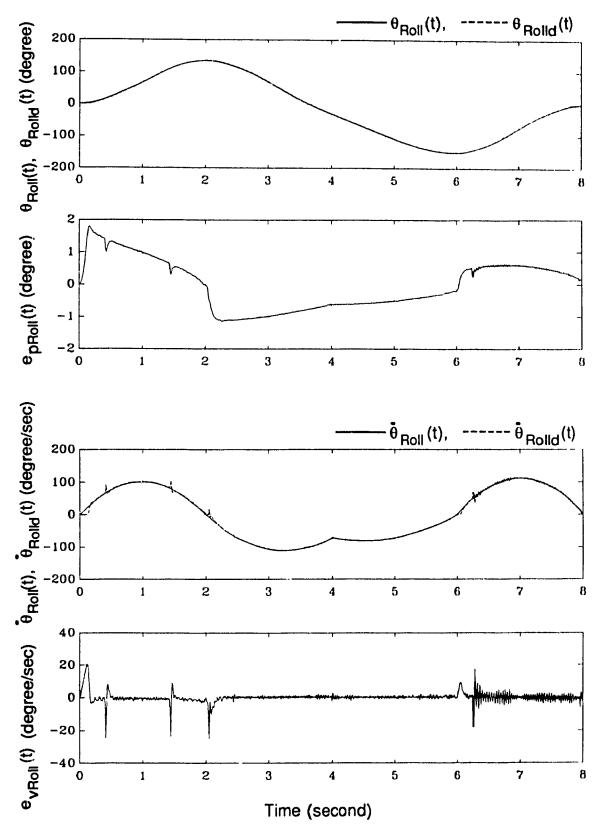

| 5.20 | Joint Z Tracking Errors, Adaptive Control, Experiment 3, Three Sec.  Move    | . 89         |

| 5.21 | Joint Roll Tracking Errors, Adaptive Control, Experiment 3, Three Sec.  Move | . 90         |

| 5.22 | Torques, Adaptive Control, Experiment 3, Three Sec. Move                     | 91           |

| 5.23 | Joint 1 Tracking Errors, Adaptive Control, Experiment 3, Two Sec.  Move      | . 92         |

| 5.24 | Joint 2 Tracking Errors, Adaptive Control, Experiment 3, Two Sec.  Move      | . 93         |

| 5.25 | Joint Z Tracking Errors, Adaptive Control, Experiment 3, Two Sec.  Move      | 94           |

| 5.26 | Joint Roll Tracking Errors, Adaptive Control, Experiment 3, Two Sec.  Move | 95  |

|------|----------------------------------------------------------------------------|-----|

| 5.27 | Torques, Adaptive Control, Experiment 3, Two Sec. Move                     | 96  |

| 5.28 | Joint 1 Tracking Errors, Adaptive Control, Experiment 3, One Sec.  Move    | 97  |

| 5.29 | Joint 2 Tracking Errors, Adaptive Control, Experiment 3, One Sec.  Move    | 98  |

| 5.30 | Joint Z Tracking Errors, Adaptive Control, Experiment 3, One Sec.  Move    | 99  |

| 5.31 | Joint Roll Tracking Errors, Adaptive Control, Experiment 3, One Sec.  Move | 100 |

| 5.32 | Torques, Adaptive Control, Experiment 3, One Sec. Move                     | 101 |

# **CHAPTER 1**

#### INTRODUCTION

#### 1.1 INDUSTRIAL ROBOTIC SYSTEMS

Since the early 1960s, robotic systems have steadily been replacing traditional automation techniques. Successful applications of robot manipulators have included manufacturing and assembly, materials handling and inspection in fixed automation environments. This type of automation involves the repetition of a specific sequence of operations for the continuous high-volume production of identical or nearly identical parts. Industrial robots intended for use in the fixed automation environment have been designed to perform relatively simple tasks in a preconceived manner. To perform these tasks, the robots require few if any sensors and practically no intelligent decision-making ability. Controllers for these systems, therefore, are based on weak processing hardware and unsophisticated control and trajectory generation software. These types of robots are generally referred to as "dumb" robots since they are inflexible to changes in their workspace and product design.

A characteristic of dumb robots is their high-level, application-oriented user-interface which enables the operator to specify a small variety of "move-type" commands. With this type of user-interface, the operator has little control over the desired trajectory and virtually no control over the servoing of the joint motors. In some cases, this limitation may adversely affect the robot's efficiency. For example, there exist dumb robotic systems whose application languages do not permit the specification of via points; to negotiate around an obstacle, the user must specify a piecewise path and the robot stops at the end of each segment.

Although there will always be applications for dumb robots, there is presently a growing demand for industrial robots which can operate in a flexible automation environment. This type of environment is dynamically complex, often containing moving obstacles and/or other manipulators sharing the same workspace. To perform in this environment, a robot must possess a significant level of intelligence as well as an assortment of advanced sensors. Although there will always be applications for which dumb robots are well suited, many may soon prove to be obsolete as the demand for more efficient and intelligent industrial robotic systems increases. This is unfortunate when one considers that relatively expensive robotic manipulators will go to waste simply because of the shortcomings of their controllers.

In addition to the industrial domain, robots are frequently found in research environments. Here, they are being used for testing modern advanced control strategies for the purpose of both basic research and prototype development. Once again, the limitations associated with the controllers of dumb robotic systems render them inadequate to serve in such a domain. The research presented in this thesis was conceived in order to overcome this problem.

The IBM 7545 Manufacturing System that was used in our research is representative of a large class of industrial robotic systems and can be classified as a dumb robot. Although the 7545 system is an older generation IBM system, its kirematic configuration is essentially identical to that of current IBM robotic systems; the difference being the intelligence of the controllers. Because the intelligence of the 7545 controller is markedly lower, it does not possess some of the features that have been incorporated into latest generation systems, e.g., the ability to specify desired trajectories. What these two generations of systems do share, however, is their inability to evolve as advanced requirements arise. This inability can be attributed to the design philosophy of the 7545

controller which like most robotic controllers makes it inherently difficult to modify the hardware and software.

### 1.2 SUMMARY OF THE RESEARCH WORK

One solution to overcoming the shortcomings mentioned above is to bypass the manufacturer-supplied controller with an alternate controller possessing sufficient processing power to execute various advanced robot control strategies and an architecture which would support future enhancement. This controller could then be programmed for use in an industrial or research environment. This was the solution adopted for the IBM 7545 Manufacturing System.

The Advanced Robot Controller (ARC) which has been designed and implemented incorporates a master/slave paradigm that assigns to the slave processor the tedious yet essential elements of implementing servo control (e.g., robot state acquisition and limit checking such as joint overruns and excessive torque demands). The slave takes over a significant percentage of the computations required for servo control and thus allows more computationally complex control strategies to be executed on the master. Although the results presented in this thesis reflect work undertaken on a particular commercial robotic system, the approach taken is easily applicable to virtually any robot. It is worth mentioning that an important constraint in the design and implementation of the ARC is that the resulting hardware/software is inexpensive (a small fraction of the cost of the robot) and relatively easy to develop and maintain.

Other researchers have recently reported developments of specialized robotic controllers for the same purpose [1-4]. The systems in [1] and [2] are based on simple single processor architectures. In [1] a robot controller based on an Intel 310 (6 MHz, 80286 processor) running XENIX and with its servo control algorithm linked to the Kernel was introduced. The controller was implemented and evaluated on a six degrees of freedom

PUMA 560 robot and was able to execute PD control for the PUMA's six joints at a servo rate of 100 Hz [5]. In [2] a specialized computer-robot interface was designed. The interface was used to link an IBM AT to a Mitsubishi RM-501 robot for the evaluation of simple and advanced control strategies. A 6.0 millisecond sampling period was achieved for PD control of the robot's first two joints [6]. The methodology and design philosophies which were adopted by us independently of [1] and [2] are in accordance with the suggestions found in the conclusions of these references. It should be noted that the cost of the ARC is of the same order as those for the architectures proposed in [1] and [2]. The systems described in [3] and [4] consist of host SUN workstations directing the efforts of multiple (3-5) VME-based 68000-series processors. These systems exhibit superior performance but at very significantly higher cost.

#### 1.3 THESIS ORGANIZATION

An introduction to the limitations associated with typical commercial industrial robot systems has been given in this chapter. Chapter 2 describes the IBM 7545 Manufacturing System which was used in this research. The required hardware modifications to the 7545 system are also described. Chapter 3 presents a complete ARC hardware description, justifying the ARC's adequacy for controlling the 7545 manipulator. The ARC software description is given in Chapter 4. This covers the high-level master software consisting of control and path planning algorithms as well as the low-level slave algorithms that were developed to increase the performance of the system. Suggestions for future extensions are included in both Chapters 3 and 4. Chapter 5 presents the results of experiments that were designed to show the ARC's effectiveness in executing various control strategies, including proportional-derivative and decentralized adaptive controllers and various path generation schemes. Concluding remarks are given in Chapter 6.

# **CHAPTER 2**

#### THE IBM 7545 MANUFACTURING SYSTEM

## 2.1 INTRODUCTION

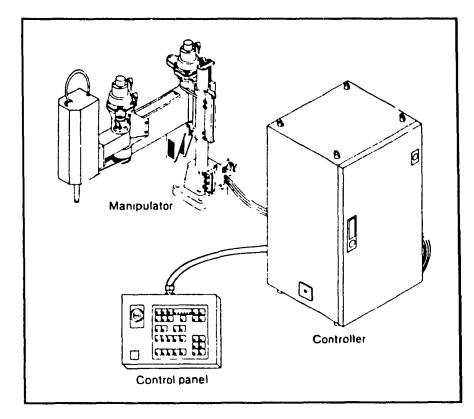

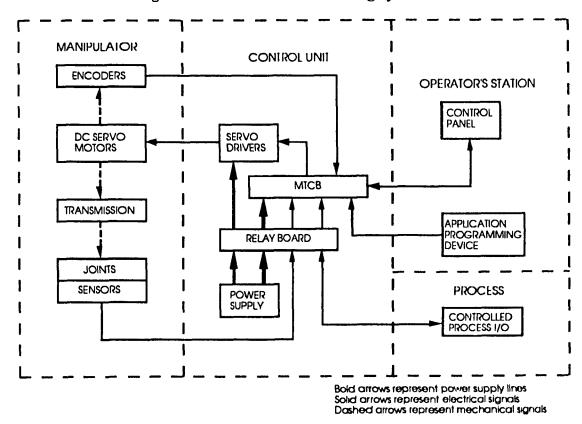

The IBM 7545 Manufacturing System (Figure 2.1) consists of a control unit, an operator control panel, a manipulator which consists of a four-joint, DC servo-actuated, Selective Compliance Assembly Robot Arm (SCARA) [7], and an application programming device (not shown). The contents of these components are shown in the block diagram in Figure 2.2.

The control unit houses a power supply, drivers for the servo motors, a motor control board (MTCB), and an interface and power distribution board (relay board). The MTCB contains a Z80 microprocessor, memory, communications interface circuits, and robot motion control circuits.

The 7545 system is pre-programmed by the user for a particular application using the AML/E (A Manufacturing Language/Editor) programming language which runs on the application programming device (e.g., IBM PC or compatible). The application program is compiled by AML/E and then downloaded to the MTCB and executed. AML/E supports simplistic high-level commands such as "move" and "grasp". All trajectory planning and joint motor control is performed by the MTCB in a predefined fashion. Inherent in the MTCB design are the shortcomings described in Chapter 1; consequently the MTCB is the sole 7545 component which needs to be bypassed. All other 7545 components can remain operationally intact.

Figure 2.1. IBM 7545 Manufacturing System [7].

Figure 2.2. Block Diagram of the IBM 7545 Manufacturing System [7].

This chapter provides the necessary information on the 7545 system to effectively bypass the MTCB with the ARC that has been designed. This includes the 7545 specifications as well as the required modifications to various 7545 system components.

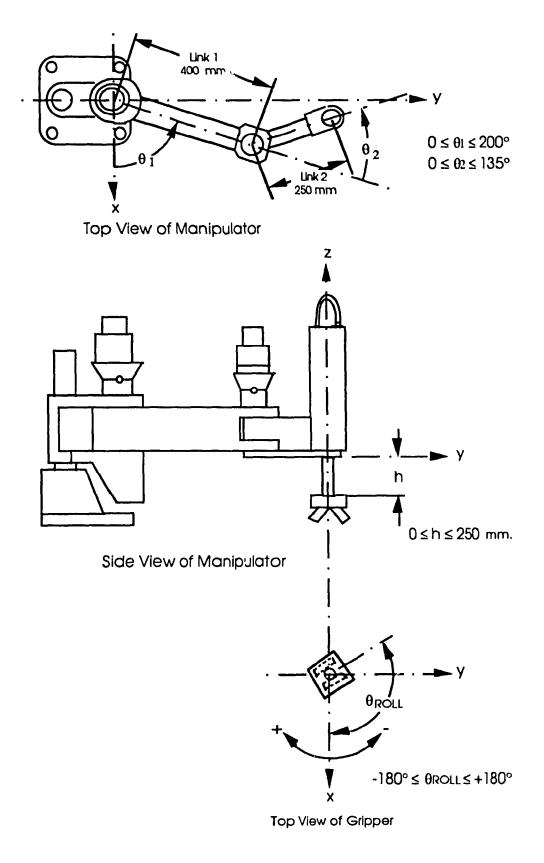

#### 2.2 THE IBM 7545 MANIPULATOR

The manipulator of the 7545 Manufacturing System (Figure 2.3) is a four-degrees-of-freedom mechanism with rigid links. The first two revolute joints of the arm, the shoulder  $(\theta_1)$  and the elbow  $(\theta_2)$ , give two degrees of freedom in the horizontal x-y plane.  $\theta_1$  is measured with respect to the x-axis (see Figure 2.3) and its range of motion is 0-200°.  $\theta_2$  is measured with respect to the radial axis of link 1 and has a range of motion of 0-135°.

Located at the end of the arm is a prismatic joint giving one degree of freedom along the vertical z-axis. Attached to the end of this z-axis shaft is a pneumatic gripper. In its uppermost position, the gripper lies in the x-y plane and the joint variable Z (uppercase denotes joint variable) is zero. The shaft can extend 250 mm in the negative z direction. This is the only joint motion affected by gravity.

The Roll joint consists of the revolution of the z-axis shaft (gripper) providing one degree of orientational freedom. The Roll angle,  $\theta_{roll}$ , is measured with respect to the x-axis and as will be shown in the following section, is independent of  $\theta_1$ ,  $\theta_2$ , and Z. The range of motion for this joint is from -180° to +180°.

The forward kinematic equations for the manipulator are:

$$\mathbf{x} = \mathbf{l}_2 \cos(\theta_1 + \theta_2) + \mathbf{l}_1 \cos \theta_1$$

$$\mathbf{y} = \mathbf{l}_2 \sin(\theta_1 + \theta_2) + \mathbf{l}_1 \sin \theta_1$$

$$\mathbf{z} = -\mathbf{h}$$

(2.1)

where  $l_1 = 400$  mm and  $l_2 = 250$  mm are the lengths of links 1 and 2, respectively.

Figure 2.3. IBM 7545 Manipulator [7].

The inverse kinematic equations are:

$$\theta_{1} = \operatorname{Atan2}(y, x) + \operatorname{Atan2}(\pm \sqrt{x^{2} \cdot y^{2} \cdot \omega^{2}}, \omega)$$

$$\theta_{2} = \operatorname{Atan2}(-x \sin \theta_{1} + y \cos \theta_{1}, x \cos \theta_{1} + y \sin \theta_{1} \cdot l_{1})$$

(2.2)

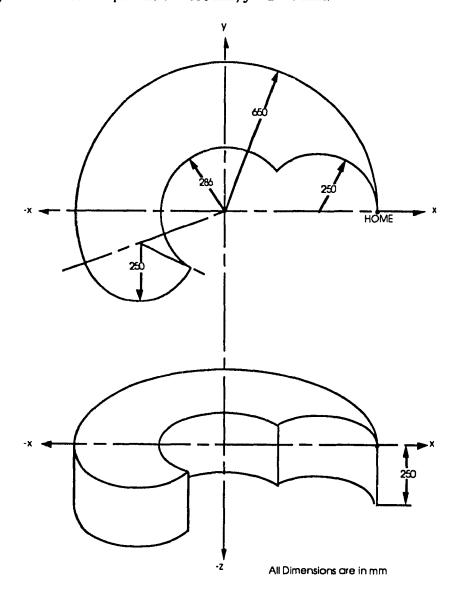

The dimensions of the manipulator's work envelope are shown in Figure 2.4. The manipulator's HOME (reference) position is located in joint space at  $\theta_1 = \theta_2 = \theta_{roll} = 0^\circ$ , Z = 0 mm, or in Cartesian space at x = 650 mm, y = z = 0 mm.

Figure 2.4. IBM 7545 Manipulator Work Envelope [7].

The manipulator has no positional redundancies, i.e., for any point in the work envelope, there exists a unique set of joint values to position the gripper at that point. Orientationally, there is redundancy in that the gripper can rotate a full 360 degrees, i.e.,  $\theta_{roll} = -180^{\circ}$  is equivalent to  $\theta_{roll} = +180^{\circ}$ .

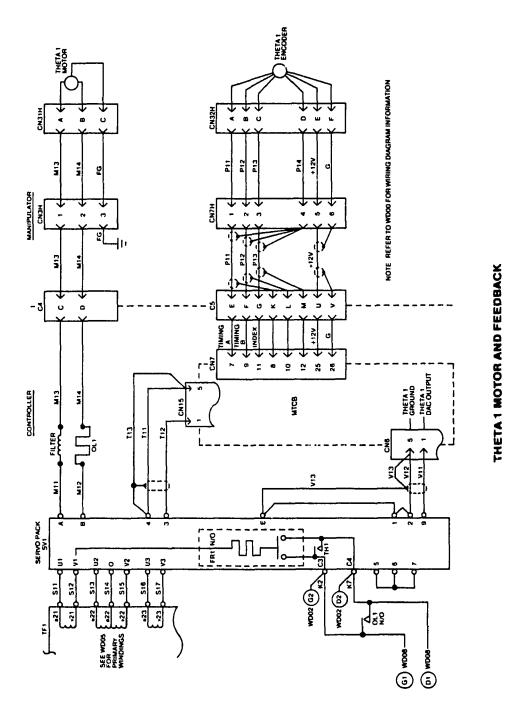

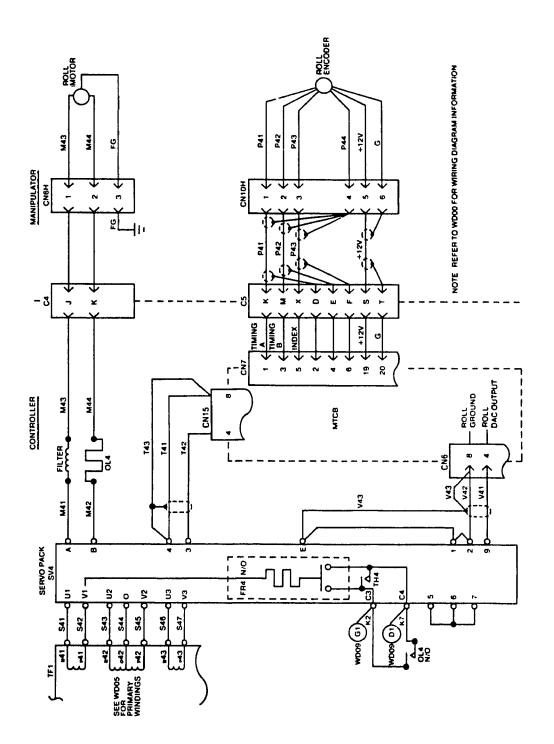

As indicated in the block diagram in Figure 2.2, each joint of the 7545 manipulator is equipped with a DC servo motor and driver (the latter located in the control unit), a transmission device, an incremental encoder, and various sensors. These components are described in the sections that follow. For reference, the wiring diagrams of the connections between these components and the MTCB are included in Appendix A.

## 2.2.1 Motor Location and Transmission System

Each link of the 7545 manipulator is driven indirectly by a DC servo motor. For joints 1 and 2, the motors are mounted on their respective joint axes. The transmissions for these joints are harmonic drive assemblies with gear ratios of 157:1 and 80:1, respectively.

The joint Z motor is mounted at the distal end of link 2 with its axis parallel to the z-axis. A belt and a ball-screw mechanism transform the rotational motion of the motor into translational motion along the Z-axis shaft. The transmission ratio is 0.2381 revolutions per mm.

The Roll motor and its associated harmonic drive transmission is located in the base of the manipulator. A drive belt transfers motion to the joint axis. Due to this configuration, the orientation of the gripper is independent of arm position, i.e., joint variable  $\theta_{roll}$  is independent of  $\theta_1$  and  $\theta_2$ . An interesting consequence of this configuration is that the drive belt dynamically couples the distal end of the arm to the base

of the manipulator. The harmonic drive together with the drive belt provide a reduction ratio of 51.2:1.

#### 2.2.2 DC Servo Motors and Drivers

The DC servo motors are permanent magnet type motors manufactured by Yaskawa Electric Mfg. Co., Ltd. The motors for joints 1 and 2 belong to the Print Motor series [8] while joint Z and Roll motors belong to the Minertia Motor series [9]. Their ratings and specifications are given in Appendix B.

Each motor is driven by a Yaskawa DC Servomotor Controller or Servopack [10]. Power for these units is obtained from the 7545 power supply via the relay board. Servopack power is controlled by the manipulator power key on the control panel which energizes a relay on the relay board. The Servopacks for the Print motors of joints 1 and 2 provide outputs of up to 200 W and for the Minertia motors of joints Z and Roll, up to 100 W.

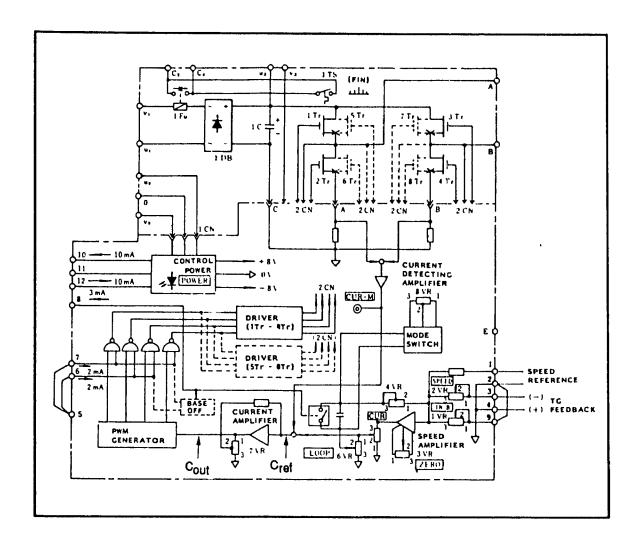

Figure 2.5 shows a Servopack's internal block diagram. The output (between terminals A and B) comes from a full bridge transistor switching circuit, the driver of which is controlled by the Pulse Width Modulation (PWM) generator. The PWM generator is fed by the output of the Current Amplifier. This amplifier constitutes an armature current controller. The armature current setpoint is located at the Cref testpoint and the control loop is closed by feedback from the Current Detecting Amplifier. Cref is set by the output of the Speed Amplifier which constitutes an armature speed controller. The setpoint of this amplifier is located at the speed reference input terminals of the Servopack and is driven by a digital to analog converter on the MTCB. The feedback for the speed controller is provided by the MTCB which performs a frequency to voltage conversion on the encoder signal. This feedback signal is fed to the TG (tachogenerator) Feedback input of the Servopack.

Figure 2.5. Servopack Internal Block Diagram [10].

The Servopack, in its manufacturer-supplied form, is incompatible with typical control strategies whose output driving signals are computed torque values. The Servopack does not support a torque input because of its speed control amplifier. The solution is to disable this speed controller. By doing this, the torque output signal from a robot controller such as the ARC would reach testpoint Cref undistorted. At Cref, the driving signal would be recognized as a desired armature current. (Note that armature current is directly proportional to motor torque.) The Speed Amplifier can be modified (by opening the speed control loop) to serve as an adjustable gain amplifier for calibration purposes. The following is a list of the required modifications.

- (a) Transform the Speed Amplifier into a simple inverting amplifier by shortingout its integrating capacitor (refer to Figure 2.5).

- (b) Short the TG feedback input.

- (c) Add an external potentiometer at the speed reference input for gain adjustment.

- (d) Connect a wire from the internal testpoint C<sub>ref</sub> to a point outside the Servopack for easy access during calibration. (The calibration procedure is listed in Appendix C.)

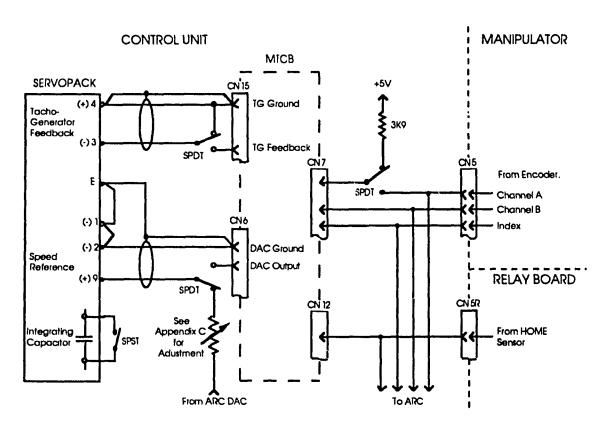

A wiring diagram of the modifications for one joint is shown in Figure 2.6. Note that the modifications are implemented using a SPST for (a) and SPDT selector switches for (b) and (c) so that the Servopack can be easily configured (by throwing the three switches) to serve either the MTCB or the ARC.

Figure 2.6. Modified Servopack, Encoder and HOME Sensor Connections.

#### 2.2.3 Incremental Encoders

An incremental optical shaft encoder is mounted on the motor shaft of each joint to provide relative joint position information. Channel A and B outputs are in quadrature (90° out of phase) and have resolutions of 500 pulses per revolution for joints 1 and 2 and 400 pulses per revolution for joints Z and Roll. Each encoder also has a one pulse per revolution index output.

The MTCB contains a counter for each encoder. On-board logic decodes the incoming pulse streams to determine the count direction. The counters increment for positive and decrement for negative joint motion. The counters are clocked only by a single transition on a single encoder channel (e.g., the rising edge of channel A).

The MTCB sets the counters to zero when the manipulator is initialized to the HOME position. The counters then give joint positions relative to the HOME position. Joint position resolutions in pulses per degree are calculated by multiplying the encoder resolution by  $\frac{1 \text{ rev.}}{360^{\circ}}$  (not necessary for joint Z since it is translational) and the transmission ratios given in section 2.2.1. Table 2.1 lists the joint position resolutions of the four joints of the 7545 manipulator.

Table 2.1. 7545 Joint Position Resolutions.

| Joint | Resolution |                  |

|-------|------------|------------------|

| 1     | 218.05     | pulses<br>degree |

| 2     | 111.1      | pulses<br>degree |

| Z     | 95.24      | pulses<br>m m    |

| Roll  | 56.8       | pulses<br>degree |

Because robot control strategies generally require joint position feedback, the ARC must have access to the outputs of the encoders when it is controlling the manipulator. A potential access point is at a test point on the MTCB (labelled CN16 in [7]) where the two channels and the index of each encoder are conveniently available. Unfortunately, it was discovered that this is not a feasible point for extraction of these signals for the following reason. When manipulator power is switched on, the MTCB's control scheme tries to maintain the manipulator in position. However, while the manipulator is under ARC control, the MTCB's control efforts are futile since its output signals have been prevented (by the SPDT switches mentioned in the previous section) from reaching the Servopacks. The problem arises when the ARC moves a joint to a point where the MTCB's computed tracking error becomes excessive. At this point, the MTCB shuts down manipulator power as a safety feature.

A solution to this problem is to extract the incoder signals before they reach the MTCB and to prevent them from entering the MTCB. Actually, preventing only one channel (channel A for joints 1, 2, and Roll and channel B for joint Z) from entering the MTCB and pulling the MTCB input for that channel to +5 V is sufficient to fool the MTCB into thinking that there is no motion.

To accomplish this, a small circuit board was built to extract the encoder signals at MTCB connector CN7 where the signal levels are TTL compatible. SPDT switches were used for selection of either MTCB or ARC mode. Figure 2.6 illustrates the circuit modification for one joint. (Note that for joint Z, channel B is the channel which is to be interrupted.)

An added benefit to the above approach is that the encoder outputs are available at the extraction point whether or not manipulator power is on while at MTCB testpoint CN7 the signals are provided only when manipulator power is on. The benefit is that the ARC can

continually monitor joint position and that reinitialization of position counters is not necessary if manipulator power is switched off and the manipulator is moved manually.

#### 2.2.4 Sensors

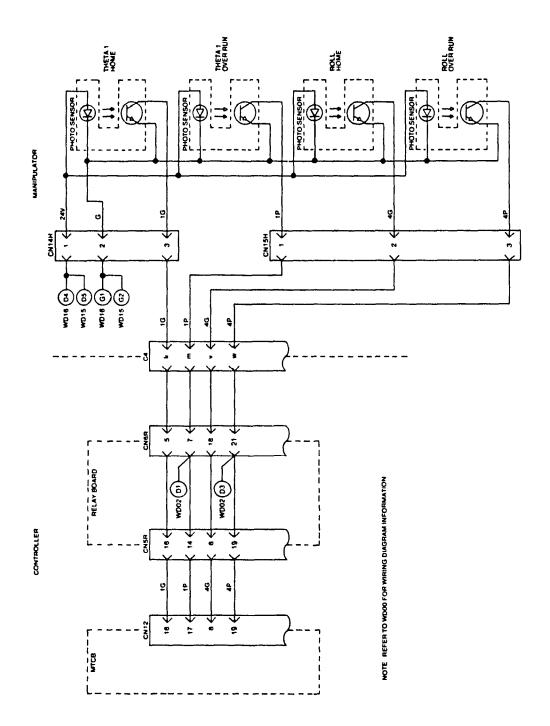

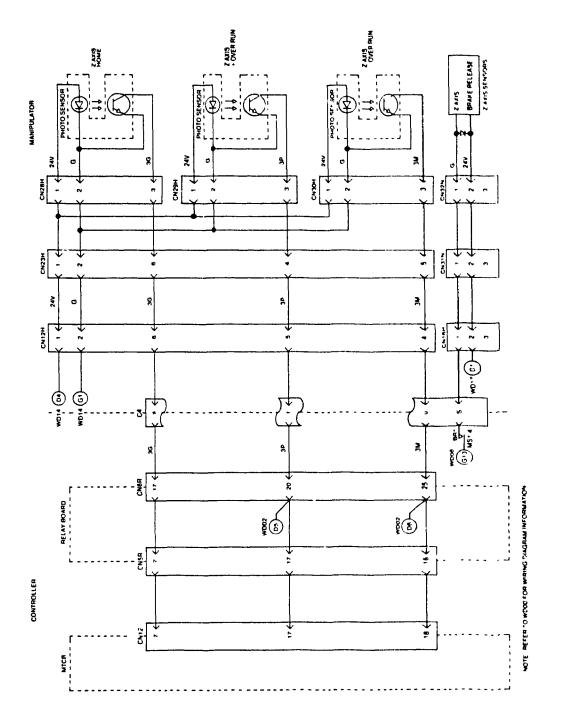

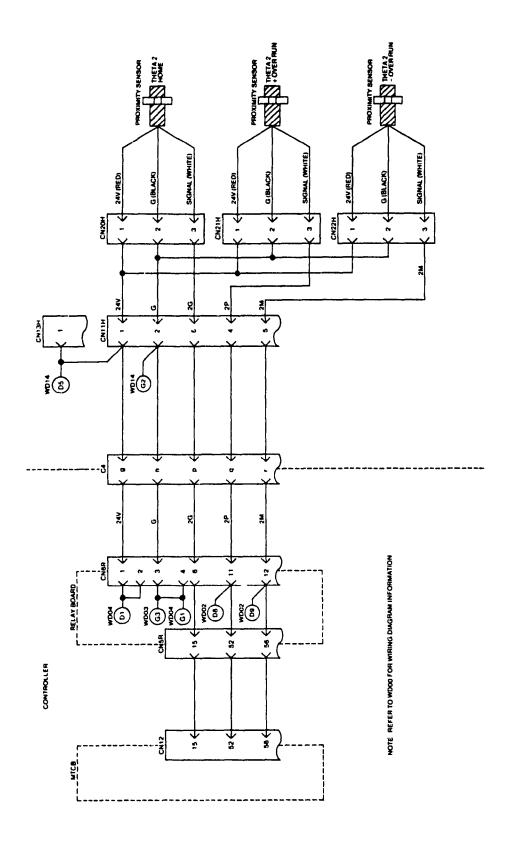

Each joint of the manipulator is equipped with overrun and HOME sensors (see Appendix A for wiring details).

The overrun sensors are limit switches that detect joint hyperextension. When an overrun sensor is tripped, manipulator power is turned off. This safety feature protects the links from hitting their mechanical limits and must remain intact. The ARC does not interfere with this safety feature.

The HOME sensors are proximity switches which are activated when a joint is in its HOME or reference position. Referring to Figure 2.3, the respective sensors indicate a HOME condition when link 1 becomes collinear with the x-axis, link 2 becomes collinear with the radial axis of link 1, the gripper point lies in the x-y plane, and the Roll angle is anywhere in its negative region. The HOME sensors are used in initialization of the joint position counters. The MTCB has a find-HOME routine that consists of moving a joint away from its HOME position if the sensor is already active and then moving it back towards the HOME sensor. When the HOME sensor becomes activated, the position counter for the joint is set to zero and the joint motion is discontinued.

The HOME sensor signals are extracted for use with the ARC from the ribbon cable connecting CN5R to CN12 as illustrated in Figure 2.6. HOME condition is indicated by 0V and not HOME condition by 22.5V.

# 2.3 SUMMARY

This chapter described the IBM 7545 Manufacturing System and identified the MTCB component as the source of some of its limitations. It was indicated that to overcome these limitations, the MTCB must be bypassed with a more powerful processing system such as the ARC which is presented in subsequent chapters. The chapter described important details of the 7545 system and outlined the modifications to be made to the system in order to bypass the MTCB.

# CHAPTER 3

#### HARDWARE DESCRIPTION

# FOR THE ADVANCED ROBOT CONTROLLER

#### 3.1 INTRODUCTION

This chapter discusses the design philosophy of the ARC and describes the hardware that was developed for its implementation.

The ARC was conceived primarily as a replacement for the MTCB in the IBM 7545 Manufacturing System for the purpose of converting the 7545 into a testbed for robotic research. For this purpose the following ARC design objectives were adopted:

- The ability to execute both simple and sophisticated robot control algorithms at respectable servo rates (baseline of 1000 Hz for PD control).

- Basic functions to facilitate the development and implementation of robot control strategies.

- An environment conducive to robotic research.

- The cost of the overall system a fraction of the cost of the 7545 system.

To achieve these objectives, a hierarchical dual-processor architecture was chosen (see Figure 3.1) whereby the master processor is used for developing and executing control strategies and the slave serves as an intelligent interface between the master and the robot. Good performance from this type of architecture is achieved since the slave relieves a significant portion of the computational and I/O burden from the master. The slave handles some of the tedious yet essential functions associated with servo control. For example, the slave can be programmed to keep track of joint positions by continuously reading the joint encoder signals emanating from the robot and test for overrun conditions. It can also verify that the output motor torques as computed by the master are

within the limitations of the robot. All the functions handled by the slave are invisible to the user and thus facilitate the development of the master software.

Figure 3.1. Block Diagram of the ARC Hardware.

The IBM Personal System /2 (PS/2) model 50 computer and the Intel 80C196KA microcontroller were chosen as the master and slave, respectively. The PS/2 model 50 is adequate for initial needs and can easily be substituted by the more powerful model 70 or model 80 for future needs. The Intel 80C196KA has many features which suit the ARC's needs. These will be discussed in Section 3.3.

The block diagram of Figure 3.1 also shows the remaining ARC hardware components: a dual-port RAM (DPR) for communication between the master and slave processors; four digital to analog converters (DACs) to drive the 7545's Servopacks; four

position counters to read the 7545's joint encoders; and an input buffer for reading the 7545's encoder index and HOME sensor lines.

The following sections of this chapter describe each of the components mentioned above and the manner in which they interconnect.

### 3.2 MASTER PROCESSOR AND DUAL-PORT RAM (DPR)

The master processor of the ARC is an 80286-based IBM Personal System /2 (PS/2) model 50 [11] which features the Micro Channel architecture and an 80287 math coprocessor. As indicated in Figure 3.1 the master communicates with the slave via a dual-port RAM (DPR).

The dual-port RAM, as its name implies, is RAM that can be accessed by two processors, one at each port. The DPR was chosen over other types of data communication methods (e.g., FIFO) as it can store control program variables required by both the master and the slave processors and it can hold predefined semaphores for timing purposes thus eliminating the need for hardware interrupts. Variable that are passed between the two processors via the RAM include the robot state from slave to master and computed torques from master to slave.

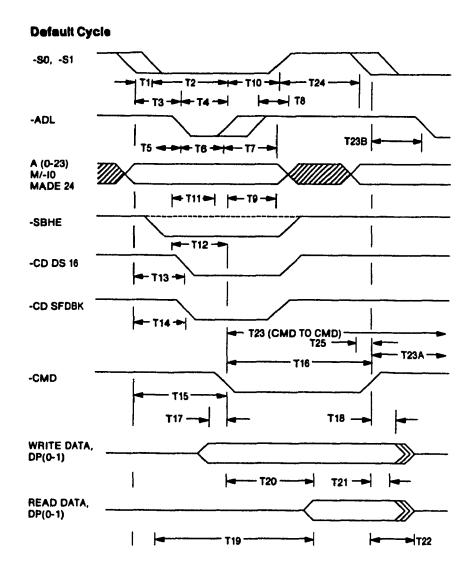

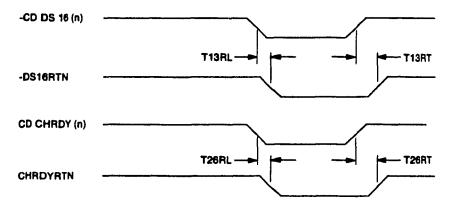

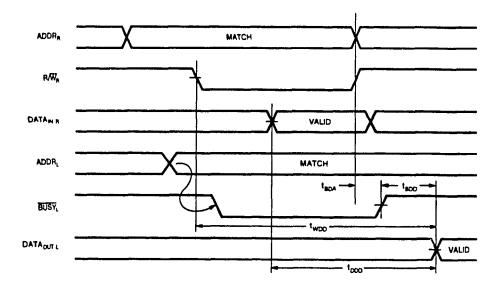

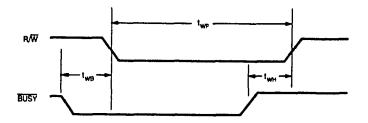

For implementation, an Integrated Device Technology's IDT7132/IDT7142, master/slave pair [12] was chosen. In parallel, these two 2k x 8 dual-port static RAMs form a 2k x 16 memory that interfaces directly to the 16-bit word width of the PS/2. The PS/2-DPR interface circuit that was designed is shown in Figure 3.2. This circuit was constructed on a Micro Channel prototype adapter card which can be inserted into an expansion slot inside the PS/2. The critical timing parameters of the Micro Channel's memory cycles are shown in Appendix D while the timing waveforms of the DPR are given in Appendix E. A short description of the circuit is given next.

Figure 3.2. PS/2 - Dual-Port Ram Interface Schematic.

Referring to Figure 3.2, the twelve DIP switches enable initialization of the starting address of the DPR. ICs U1 and U2 decode the upper 12 address lines A(12-23) along with the  $M/\overline{I/O}$  and MADE 24 signals to produce the unlatched address decode signal. This signal provides the required feedback to the master on lines  $\overline{CD}$  DS 16 and  $\overline{CD}$  SFDBK. The unlatched address decode signal, along with the lower 12 address lines A(0-11) and the control signals  $\overline{SO}$ ,  $\overline{S1}$ , and  $\overline{SBHE}$ , are latched by U3 and U4 on the leading edge of  $\overline{CMD}$ . The latched address decode signal then enables the left port of the dual-port RAM and, together with  $\overline{CMD}$ , enables the data bus buffers, U8 and U9.  $\overline{SO}$  and  $\overline{S1}$  are the write and  $\overline{CMD}$  read enable signals, respectively.

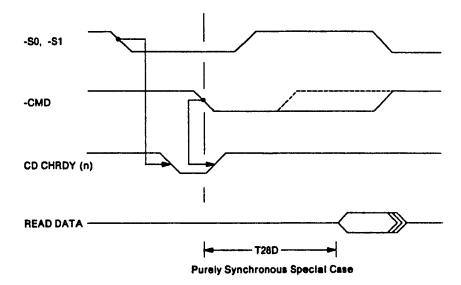

The IDT7132 has on-chip port arbitration logic to resolve the situation in which both ports simultaneously address the same memory location. When this situation occurs, the IDT7132 determines which processor has access and holds the operation of the other processor through the use of a BUSY flag. For example, the IDT7132 sets BUSYL to indicate right port priority. This signal is then used to delay the PS/2 by setting its CD CHRDY(n) (channel ready) line.

Unfortunately, implementation of the above is complicated by the fact that the propagation delays of the IDT7132 and the other interface circuit components cannot guarantee generation of the BUSYL within the time required by the PS/2. Referring to Figure 3.2, the solution is to automatically set the CD CHRDY(n) signal at the beginning of the memory cycle and reset it on the leading edge. CMD using gates U7A, U5D and U7B. This affords the circuit extra time to set the SYL signal. In this configuration, the hardware extends the Micro Channel's default cycle to the 300 nanosecond synchronous cycle given in Appendix D. It should be noted that the PS/2 model 50 automatically extends the default cycle to the 300 nanosecond synchronous extended cycle. It is performed by the interface hardware, however, to assist portability to other systems.

The starting address of the left port of the DPR is set by the DIP switches to 0C0000H.

An 18 inch twisted pair ribbon cable is connected to the header of the circuit board and links the right port of the DPR to the microcontroller which is described in the next section.

#### 3.3 SLAVE PROCESSOR

The slave processor chosen for the ARC system is the Intel 80C196KA Microcontroller [13]. To simplify the design of the slave system the Intel EV80C196KA Microcontroller Evaluation Board [14] was employed. This evaluation board consists of the 80C196KA 16-bit embedded microcontroller, 16k x 16 static RAM, 16k x 16 EPROM and a UART for communications with a host IBM or compatible. Edge connectors on the board provide easy access to the microcontroller's system (data, address, control) bus. For reference, the EV80C196KA schematic diagram is given in Appendix F.

The EV80C196KA also facilitates software development as it contains a system debug monitor (SDM) for loading, executing and debugging code. The SDM is actually composed of two separate programs. One resides in the EPROM on the evaluation board and executes on the EV80C196KA and the other runs on the host computer, in our case an IBM compatible. The two programs communicate via an RS-232 channel.

#### 3.3.1 The EV80C196KA Interface

As illustrated in the ARC block diagram of Figure 3.1, the microcontroller communicates with the DPR, the digital to analog converters, the position counters, and the robot overrun and HOME sensors. Each one of these components is viewed by the microcontroller as external memory residing somewhere in the upper half of the 80C196KA's 64k address space (8000H-FFFFH). Referring to Appendix F, the EV80C196KA's main interface is located at the JP2 memory expansion connector where the system bus is available. The timing diagram of the bus is given in Appendix G. The

schematic diagram of the first stage of the interface circuit which was designed to connect directly to JP2 is shown in Figure 3.3. A short explanation of the circuit follows.

U5 buffers all output control lines and is always enabled. U1 and U2 latch the 16-bit address from the multiplexed address/data bus (AD0-AD15) on the trailing edge of BALE. U3, U4 and U7 are bidirectional data bus buffers. Their direction is controlled by the BRD signal. D0 has its own buffer so that two position counters can be accessed simultaneously (this will be explained in more detail in the section 3.5). U8, a 3-8 decoder, generates the chip enable signals for the components of the ARC and is enabled for addresses in the range 8000H-FFFFH (A15 high). The outputs CE1, CE2, CE3, and CE4 enable the position counters, the digital to analog converters, the HOME and overrun sensors buffer, and the DPR, respectively. Since the chip enable signals are generated by a latched address decode, they are active for the entire memory cycle of the 80C196KA. In light of this, data transmission timing is controlled by the pulse width of the 80C196KA's read (RD) and write (WRH, WRL) lines. For ARC devices that require longer pulse widths than these lines provide, an antedated read/write signal AR/W is generated. The AR/W pulse begins earlier, on the trailing edge of ALE, and ends on the trailing edge of either RD or WRL.

U21B, the D flip-flop, is set and reset by  $\overline{RD}$  and  $\overline{WRH}$ , respectively. The output of the flip-flop, LR/W (latched read/write), drives the  $R/\overline{W}$  line of the position counters. This will be explained in greater detail in section 3.5. An additional requirement of the position counters is a 2 MHz clock. This clock is generated by dividing the 80C196KA's 6 MHz CLOCKOUT signal by three using the dual J-K flip-flops of U10. The clock signal, as shown in Figure 3.3, is termed DBCLK.

Figure 3.3. 80C196KA Interface Schematic.

TIMER2 is a 16-bit counter on the 80C196KA which is used by the ARC as a sample period timer. TIMER2 increments on any transition at the T2CLK terminal. The desired TIMER2 counting frequency is 1 MHz and the required 500 KHz clock for the T2CLK input is generated by dividing the 2 MHz clock by four using the dual J-K flip-flops of U26.

### 3.4 DIGITAL TO ANALOG CONVERSION

Digital to analog converters (DACs) are the means by which the computed motor torque values are converted into analog voltage signals to drive the Servopacks. In its present configuration, the ARC employs four Analog Devices AD667 12-bit double-buffered DACs [15], one for each joint of the 7545 manipulator. The double-buffered digital inputs enable all DACs to be simultaneously updated without the need for external latches and the 12-bits provides adequate resolution. The AD667's digital and analog circuits are discussed below.

# 3.4.1 Digital Circuit Details

The AD667 functional block diagram and write cycle timing diagrams are given in Appendix H. The AD667 bus interface logic consists of four independently addressable registers in two ranks. The first rank consists of three four-bit registers controlled by address inputs AO-A2. The second rank register holds all 12-bits and is controlled by address input A3.

The AD667-80C196KA interface is shown in Figure 3.4. The first rank register address lines (A0-A2) on each of the four DACs are tied together and connected to 80C196KA address lines A1-A4, respectively. The second rank register address line (A3) on all DACs are tied together and connected to 80C196KA address line A5. In this configuration, the first rank registers of each DAC can be loaded separately with their respective torque data as per Write Cycle #1. The transfer from first to second rank is then performed

simultaneously on all DACs as per Write Cycle #2. This double buffered organization eliminates spurious analog outputs originating from data bus activity while the DACs' chip select inputs (cs) are low.

The cs inputs are driven by CE2 whose base address is A000H. The CE2 signal is gated by the ARVW signal to provide the longer pulse width required by the DACs. The DAC addresses are listed in Table 3.1.

Table 3.1. Digital to Analog Converter Addresses.

| DAC # | RANK<br>REGISTER | 80C196KA<br>ADDRESS |

|-------|------------------|---------------------|

|       | 10001DIC         | 7,22,1255           |

| 1     | 1                | AFFCH               |

| 2     | 1                | AFFAH               |

| 3     | 1                | AFF6H               |

| 4     | 1                | AFEEH               |

| ALL   | 2                | AFDEH               |

Figure 3.4. Digital to Analog Converter Schematic.

# 3.4.2 Analog Circuit Details

The DAC's internal output amplifier supplies up to 40 mA of current to drive the 7545's Servopack. Each AD667 is configured to produce bipolar output voltage ranges of ±10V. Two 100Ω potentiometers are used in calibrating the outputs. The calibration process is described in Appendix C. A 20pF capacitor is connected across the feedback resistor to optimize dynamic performance.

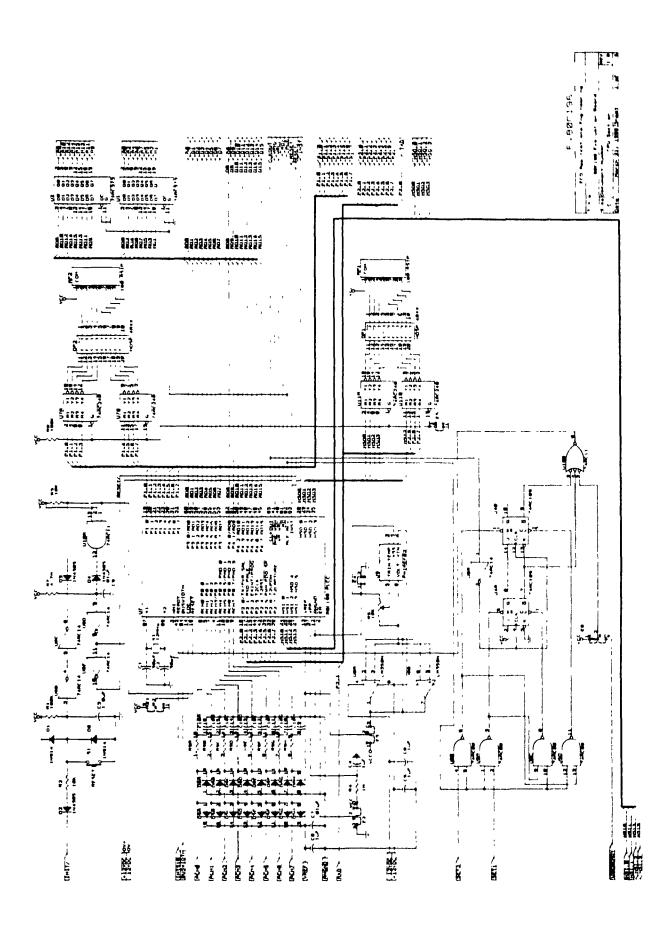

### 3.5 POSITION COUNTERS

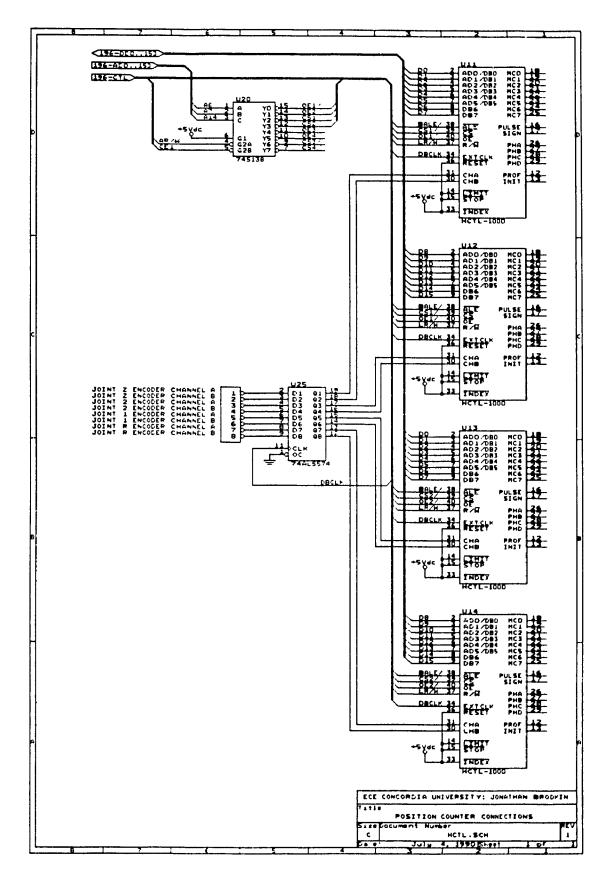

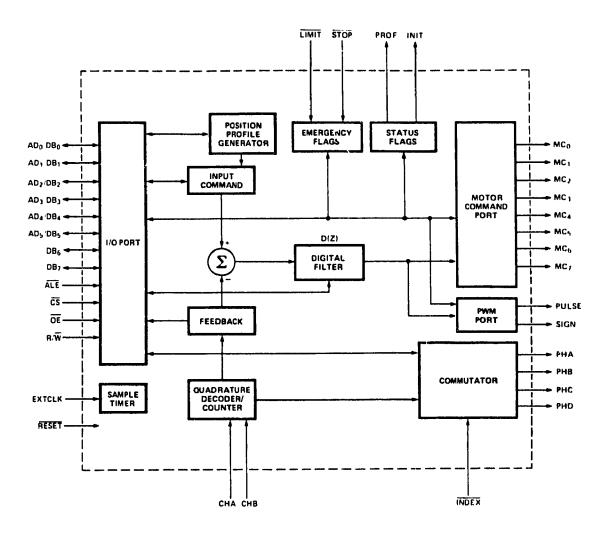

As mentioned in the first chapter, the joints of the 7545 manipulator are equipped with position feedback devices in the form of optical incremental encoders (see Section 2.2.3). To recover the encoded position information, the ARC employs four Hewlett Packard HCTL-1000 General Purpose Motion Control ICs [16]. These ICs were chosen as they contain quadrature decoders and 24-bit counters for reading the 7545's joint encoders as well as 3-bit state delay digital filters to remove noise spikes on the encoder lines. Each HCTL-1000 takes the place of a multitude of ICs used in [1] and [2] for the same purpose. Another feature of the HCTL-1000 is that a count is produced for both transitions (low→high and high→low) on Channel A and Channel B. Therefore, the 500-count encoders on the first two 7545 manipulator joints are decoded into 2000 quadrature counts per revolution. As a result, the HCTL-1000s give four times better resolution than the counters on the MTCB as well as the counter described in [1] and [2] which count on one transition of one encoder channel only. In addition, the 24-bit capacity of the HCTL-1000s is sufficient to hold the pulse counts corresponding to the maximum range of motion of the joints. Thus no special software is required to keep track of the total pulse count. The schematic diagram of the HCTL-1000 circuit is shown in Figure 3.5. A description of the circuit is given below.

Figure 3.5. HCTL-1000 Schematic.

The HCTL-1000s are clocked by the 2 MHz DBCLK line as are the D flip-flops in U25. The flip-flops ensure that all encoder pulse transitions occur at the HCTL-1000 encoder inputs coincident with the clock, thus preventing any possibility of erroneous encoder counts as explained in [16].

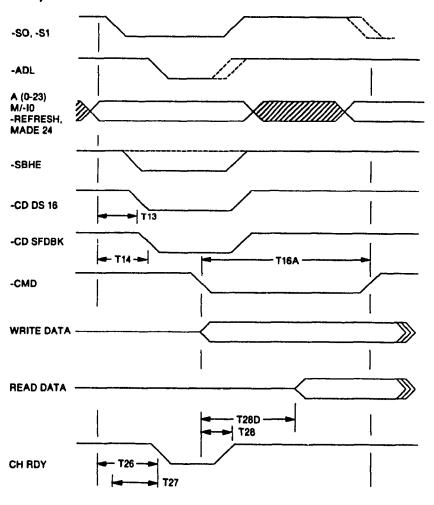

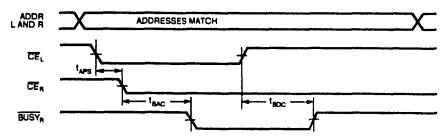

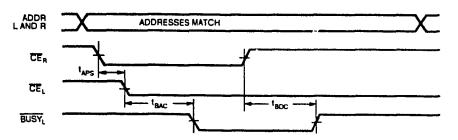

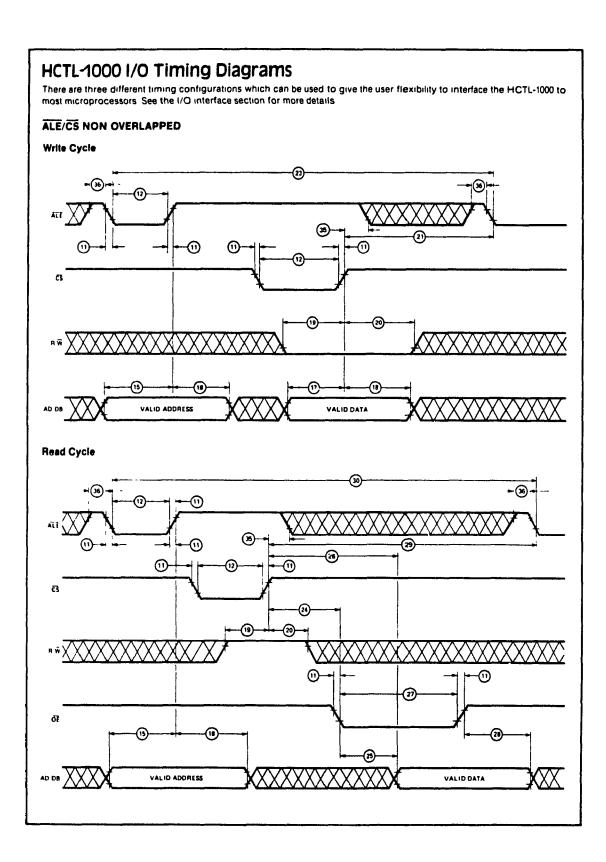

The 24-bit pulse count is located in three of the HCTL-1000s 64 8-bit internal registers. The registers are accessed over the HCTL-1000s multiplexed 6-bit address/8-bit data bus. The bus timing diagram for the HCTL-1000 is included in Appendix I and a description of the I/O operation follows.

On the leading edge of BALE the HCTL-1000 begins sampling the bus into an internal address latch. This bus information, which represents the 6-bit address of one of the HCTL-1000's 64 8-bit registers, gets latched on the trailing edge of BALE. Next, on the leading edge of  $\overline{CS}$ , the HCTL-1000 begins sampling the bus into an internal data latch. On the trailing edge of  $\overline{CS}$  the HCTL-1000 checks the LRW line and performs one of two operations. In the case of a write operation, the data in the data latch is written into the addressed location. In the case of a read operation, the data in the addressed location is sent to an internal output latch which can then be enabled onto the bus by setting  $\overline{OE}$ . Because the HCTL-1000 takes a relatively long time (minimum 1.8 microseconds) to transfer the data to the output latch, the read operation is performed by two microcontroller read instructions. The first read instruction sets the LRW line high, selects the desired register and begins the transfer process by asserting the appropriate  $\overline{CS}$  line. The second read instruction asserts the  $\overline{OE}$  line to enable the data onto the bus to be read by the microcontroller.

The  $\overline{\text{CS}}$  and  $\overline{\text{OE}}$  signals are generated by U20, a 3-8 decoder, which decodes address lines A6, A14, and A7. U20 is enabled by the  $\overline{\text{CE1}}$  and by the AR/W which provides the longer  $\overline{\text{CS}}$  and  $\overline{\text{OE}}$  pulse widths required by the HCTL-1000s.

To increase the ARC performance, the 8-bit HCTL-1000s are connected in pairs to the 16-bit bus of the EV80C196KA microcontroller. The upper and lower HCTL-1000s that make up a pair are connected to bus lines D8-D15 and D0-D7, respectively. The first pair is controlled by  $\overline{CE1}$  and  $\overline{OE1}$  and the second pair is controlled by  $\overline{CE2}$  and  $\overline{OE2}$ . Two other sets of control lines are generated by U20,  $\overline{CE3}$ ,  $\overline{OE3}$  and  $\overline{CE4}$   $\overline{OE4}$ , for future expansion. The memory map for these control signals is given in Table 3.2.

Table 3.2. Memory Map for the HCTL-1000s.

| CNTRL.     |     |     |     |     |     |     | A  | DDF | RESS | 3   |    |    |     |    |           |           |

|------------|-----|-----|-----|-----|-----|-----|----|-----|------|-----|----|----|-----|----|-----------|-----------|

| SIGNAL     | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8  | A7   | _A6 | A5 | A4 | A3_ | A2 | <u>A1</u> | <u>A0</u> |

| Œ1         | 1   | 0   | 0   | d   | d   | d   | đ  | d   | 0    | 0   | d  | d  | d   | d  | d         | 0         |

| OE2        | 1   | 0   | 0   | d   | d   | ď   | d  | d   | 0    | 1   | d  | d  | d   | d  | d         | 0         |

| CS1        | 1   | 0   | 0   | X   | X   | X   | X  | X   | 1    | 0   | ×  | X  | X   | X  | x         | 0         |

| CS2        | 1   | 0   | 0   | X   | X   | X   | X  | X   | 1    | 1   | X  | X  | X   | X  | x         | 0         |

| OE3        | 1   | 1   | 0   | d   | d   | d   | d  | d   | 0    | 0   | d  | đ  | d   | d  | d         | 0         |

|            | 1   | 1   | 0   | d   | d   | d   | ď  | d   | 0    | 1   | d  | d  | d   | d  | d         | 0         |

| OE4<br>CS3 | 1   | 1   | 0   | X   | X   | X   | X  | X   | 1    | 0   | X  | X  | X   | X  | X         | 0         |

| CS4        | 1   | 1   | 0   | X   | X   | X   | X  | ×   | 1    | 1   | X  | X  | x   | X  | ×         | 0         |

d-don't care

x-HCTL-1000 register address

Since address line A13 is always 0 only the first 32 registers on the HCTL-1000s can be accessed (i.e. registers R00H - R1FH). This does not pose a problem as the 24-bit actual position count is held in the three 8-bit registers R12H (MSB), R13H, and R14H (LSB) and the only other register of interest is R05H. Writing 01H to R05H commands the HCTL-1000 to enter the Initialization/Idle mode where it simply keeps track of joint position. Upon writing 00H to R05H, the position counter registers (R12H, R13H, R14H) are cleared and the Initialization/Idle mode is entered.

As seen in Table 3.2, address line A0 is always 0. This is due to the fact that the microcontroller requires an even operand in all instructions which refer to word (16-bit) memory locations. This would dictate that only even registers on the lower HCTL-1000 can be addressed. This limitation, however, is overcome by providing bus line D0 with its

own buffer (U7) as shown in the schematic diagram in Figure 3.3. When the buffer is enabled, D0 takes the level of AD0 and when the buffer is disabled, D0 is pulled high by the pull-up resistor R17. It is presumed that the microcontroller addresses the same location in both the upper and lower HCTL-1000s. Therefore, the D0 input of the lower HCTL-1000 should always be the same as D8 on the upper HCTL-1000 during addressing. Hence, during the addressing portion on the multiplexed bus (i.e., if AD8 is high during BALE the buffer will be disabled by U22B and D0 will be high even though AD0 is low. If AD8 is low, the buffer will be enabled and D0 will take on the value of AD0.

As was mentioned previously, the  $\overline{OE}$  line which enables the output of the HCTL-1000s onto the data bus begins with the antedated AR/W line on the rising edge of  $\overline{BALE}$ . Bus contention could occur at the beginning of this period when the microcontroller is asserting an address on AD[0..15]. The contention would last until the  $\overline{BRD}$  line goes low and the direction of the data buffers changes for a read instruction. The contention is avoided by means of U23A, U22D, U6A, U9A, and U9D, which act to disable the data buffers if the HCTL-1000s are being accessed ( $\overline{CE1}$  is low), if it is a read instruction (A7 and  $\overline{OE}$  are low), and if the  $\overline{BRD}$  line is high. This buffer disabling period begins on the address decode and ends with the start of the read pulse.

The final timing requirement of the HCTL-1000 is that its R/W input remain asserted for a short period after the CS pulse. This is accomplished by latching the BRD and BWRH lines in the D flip-flop, U21B. The output of the flip-flop, labelled LR/W (latched read/write), drives the R/W inputs of the HCTL-1000s.

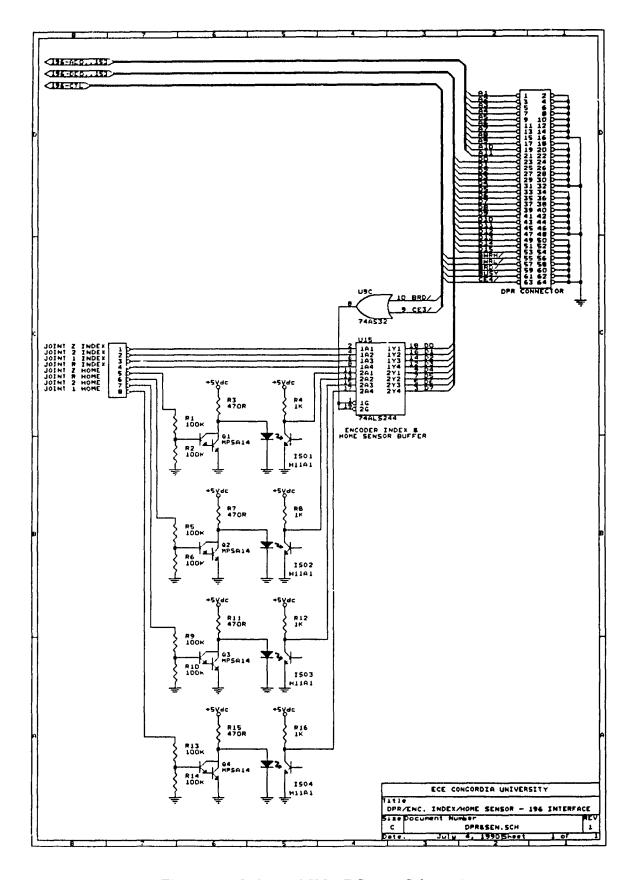

### 3.6 HOME SENSORS, ENCODER INDEX AND DUAL-PORT RAM CONNECTION

As described in section 2.2.4 the extracted HOME sensor signals have a voltage of approximately 22.5 V when the joint is not HOME and 0 V when the joint is HOME. These

voltages are converted to TTL levels by the circuit in Figure 3.6 which consists of a voltage divider, a Darlington transistor and pull-up resistor, and for buffering an opto-isolator. The HOME signals along with the index pulses generated by the optical encoders (TTL compatible) are made available to the microcontroller through buffer U15. The buffer is enabled by CE2 and BRD and its address is B000H.

Also included in Figure 3.6 is the edge connector for the dual-port RAM. Because the dual-port RAM has a very fast access time it can be connected directly to the basic interface circuit in Figure 3.3. The dual-port RAM is chip-enabled by  $\overline{CE4}$  and has a base address of E000H.

Figure 3.6. Index and HOME Sensor Schematic.

#### 3.7 HARDWARE IMPLEMENTATION

The circuits of sections 3.3 - 3.6 were wire-wrapped on a prototype board. The EV80C196KA microcontroller evaluation board was attached along side the prototype board and was electrically connected via a ribbon cable. The assembly was mounted on a Plexiglass base for attachment inside the 7545's control unit housing. As mentioned previously, connection to the dual-port RAM (residing in the PS/2) was via an 18 inch, 64 conductor, twisted-pair ribbon cable.

### 3.8 SUMMARY AND FUTURE WORK

This chapter described the hardware that was designed specifically for the ARC. The dual-processing nature of the ARC provides the processing power needed for advanced control strategies and also enables some of the basic functions executing on the slave to be invisible to the user. The system also serves as a basis for future hardware expansion. For example, supplemental hardware such as force sensor feedback circuits (required for impedance control) and circuitry for additional degrees of freedom can be easily interfaced to the slave system bus. As for the master processor, greater processing power can be easily achieved in two ways. The first is to replace the PS/2 model 50 by the model 70 or the model 80. The second is to add one or more transputer (processor) boards inside the PS/2.

# **CHAPTER 4**

# SOFTWARE DESCRIPTION

# FOR THE ADVANCED ROBOT CONTROLLER

### 4.1 INTRODUCTION

As mentioned in Chapter 1, the ARC was conceived to enhance the operation of the IBM 7545 Manufacturing System and, in the process, transform it into a testbed for robotic research. The previous chapter described the hardware that was designed to achieve this objective. This chapter presents the master and slave software that has been developed for the purpose of creating the research environment.

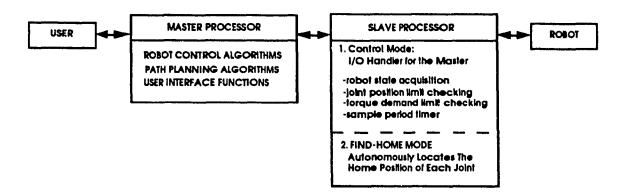

Figure 4.1 shows a block diagram illustrating the role of each processor in the overall system. Note that the user interfaces only with the master processor; the slave is completely invisible. The slave software performs the function of I/O handler for the master and some basic safety features such as limit checking of variables. The slave also contributes by maintaining the sample period timer. Perhaps the most valuable function of the slave, however, is the reading of the joint position counters (HCTL-1000s). This function, as detailed in Section 3.5, is both complicated and time consuming. The slave, therefore, performs some of the tedious yet essential tasks associated with robotic control and enables the master (and user) to concentrate on higher level issues. The slave software is described in Section 4.3.

Figure 4.1. Block Diagram of the ARC Software.

The master processor is used for developing, storing and executing path planning and robot control algorithms. So far, a library consisting of two path planning algorithms and two control algorithms has been coded in the C language. Each of the four functions in the library resides in its own separate file for developmental purposes. Once debugged, a function is linked to a main program for execution. The main program, also residing in a separate file, is composed of menu, display, and user-interaction functions. These functions help to create a user-friendly environment conducive to robotic research. Details of the master processor software are included in Section 4.4.

The following section describes how the dual-port RAM is set up to handle the flow of data between the master and slave processors.

#### 4.2 DUAL-PORT RAM UTILIZATION

The DPR of the ARC constitutes the ARC's shared memory system and is used for the passing parameters and variables between the master and slave processors. Each parameter and variable is assigned a specific location (register) in the DPR. The address and name of each register in the DPR is listed in Table 4.1.

Table 4.1. Dual-Port RAM Register Reference Table.

| ADDRESS |       | SIZE        | NAME                    | USER A | CCESS |

|---------|-------|-------------|-------------------------|--------|-------|

| Master  | Slave |             |                         | Master | Slave |

| С0000Н  | E000H | word        | sample_period           | w      | r     |

| C0002H  | E002H | word        | timing_A                | r/w    | r/w   |

| C0004H  | E004H | word        | timing_B                | r/w    | r/v/  |

| С0006Н  | E006H | word        | command                 | r/w    | r/w   |

| C0008H  | E008H | word        | error                   | r/w    | r/w   |

| C0010H  | E010H | double word | actual_position_joint_1 | r      | w     |

| C0014H  | E014H | double word | actual_position_joint_2 | r      | w     |

| C0018H  | E018H | double word | actual_position_joint_Z | r      | w     |

| C001CH  | E01CH | double word | actual_position_joint_R | r      | w     |

| C0020H  | E020H | word        | torque_joint_1          | w      | r     |

| C0022H  | E022H | word        | torque_joint_2          | w      | r     |

| C0024H  | E024H | word        | torque_joint_Z          | w      | r     |

| C0026H  | E026H | word        | torque_joint_R          | w      | r     |

The function of each of the registers listed in the table is described below.

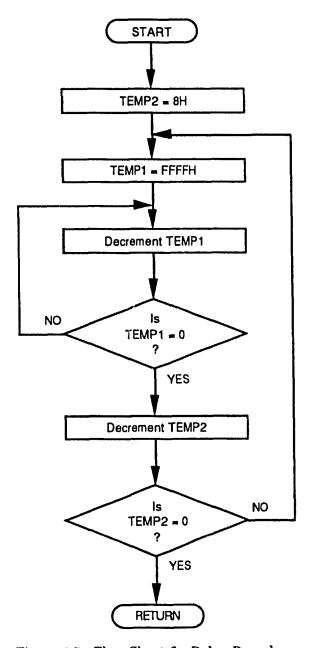

# 4.2.1 Sample\_Period Register

The sample\_period register is loaded by the master with a value corresponding to the controller sampling period. As mentioned in Section 3.3.1, sample period timing is handled by TIMER2 on the 80C196KA which counts up at a frequency of 1 MHz. Therefore, multiplying the value in the sample\_period register by 10-6 yields the actual sampling period in seconds. The slave maintains the sample period timer by resetting TIMER2 when it reaches or exceeds the value in the sample\_period register. The reset is accomplished by subtracting the value in the sample\_period register from TIMER2.

### 4.2.2 Timing\_A Register

The timing\_A register contains two semaphores which are set by the slave to initiate the master's sampling period and to indicate to the master that joint positions have been read and stored in the DPR. The semaphore indications are specified in the table below.

| Bit Number | Indication                |

|------------|---------------------------|

| 0          | Begin new servo loop      |

| 1          | Joint positions available |

The master resets both semaphores after completing the computations for the sampling period and then waits for bit 0 to become set indicating the start of the next period.

## 4.2.3 Timing\_B Register

The timing\_B register contains one semaphore (bit 0) which is set by the master to indicate to the slave that the joint motor torques have been computed and stored in the DPR. The slave resets the semaphore after reading the torques.

## 4.2.4 Command Register

As will become clear in Section 4.3, the slave processor can execute in one of two modes of operation: the find-HOME mode, and the control mode. The master indicates the desired mode by setting a semaphore in the command register. The slave reads the command register while in a waiting loop and performs one of the actions specified below.

| Bit Number Set | Indication               |

|----------------|--------------------------|

| 0              | Enter the Control Mode   |

| 7              | Enter the Find Home Mode |

| None           | Continue Waiting         |

# 4.2.5 Error Register

The slave processor informs the master of any error conditions that have been detected by setting flags in the error register. The flag indications are specified below. The errors will be described in their proper context in Section 4.3.

| Bit Number | Indication                      |  |

|------------|---------------------------------|--|

| 0          | Joint 1 in positive overrun     |  |

| 1          | Joint 1 in negative overrun     |  |

| 2          | Joint 2 in positive overrun     |  |

| 3          | Joint 2 in negative overrun     |  |

| 4          | Joint Z in positive overrun     |  |

| 5          | Joint Z in negative overrun     |  |

| 6          | Joint Roll in positive overrun  |  |

| 7          | Joint Roll in negative overrun  |  |

| 8          | Excessive torque for joint 1    |  |

| 9          | Excessive torque for joint 2    |  |

| 10         | Excessive torque for joint Z    |  |

| 11         | Excessive torque for joint Roll |  |

| 12         | Motor torques arriving too late |  |

| 13         | Master processor too slow       |  |

# 4.2.6 Actual\_Position Registers

The slave processor reads the HCTL-1000 position counters and stores the count values in the long integer or double word (32 bit) actual\_position registers.

# 4.2.7 Torque Registers

The master computes the joint motor torques and stores them in the torque registers.

## 4.3 SLAVE PROCESSOR SOFTWARE

The tasks of the slave are shown in Figure 4.1. These tasks are fundamental to virtually all robot control strategies and therefore do not require modification. By assigning these tasks to the slave, they in effect become invisible to the user. As shown in Figure 4.1, the slave software is designed to execute in one of two modes of operation: the find-HOME mode and the control mode. The first mode is used for locating the manipulator's HOME (reference) position, the second mode contains the tasks which assist the master's control program. An operating mode is selected while the processor is looping in a main program. The main program, the two operating modes and the common procedures are described in the following sections. Flow charts are included in the text and source code listings can be found in Appendix J. The slave processor software is written in 80C196KA assembly language and resides in a single module.

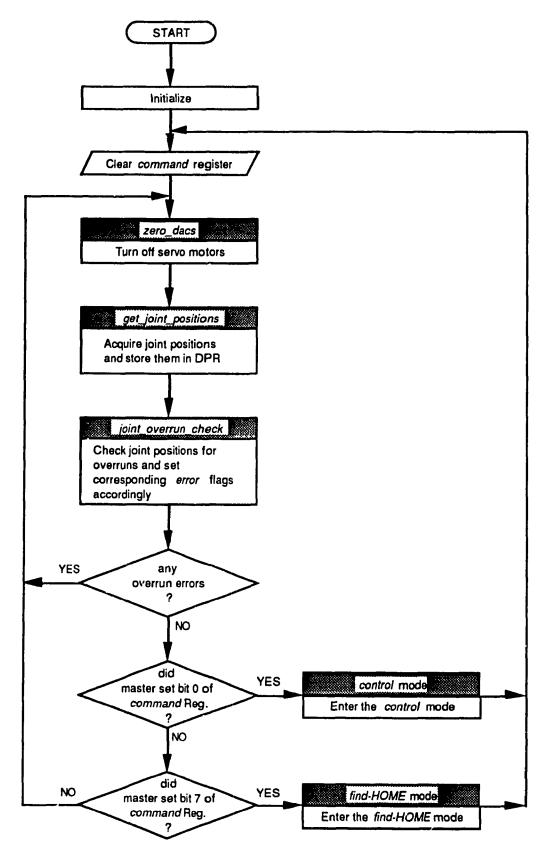

### 4.3.1 Main Program

The flow chart for the slave's main program is shown in Figure 4.2. The initialization sequence consists of program variable and pointer initialization, resetting of the HCTL-1000 position counters and putting the 80C196KA's TIMER2 into fast increment mode to enable it to count at the desired 1 MHz frequency. The slave then clears the command register in the DPR and enters the waiting loop.

Figure 4.2. Flow Chart for the Slave's Main Program.

While in the waiting loop, the slave calls procedures to zero the DACs so that no torques are fed to the Servopacks, to acquire the joint positions, and to check joint positions for overruns. If no joint overrun conditions exist, the command register is polled. Depending on the value in this register (see Section 4.2.4), the slave either enters the control mode, enters the find-HOME mode, or restarts the waiting loop. If, however, a joint overrun is detected, command is not polled and the waiting loop is restarted.

### 4.3.2 Find-HOME Mode