**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the

text directly from the original or copy submitted. Thus, some thesis and

dissertation copies are in typewriter face, while others may be from any type of

computer printer.

The quality of this reproduction is dependent upon the quality of the copy

submitted. Broken or indistinct print, colored or poor quality illustrations and

photographs, print bleedthrough, substandard margins, and improper alignment

can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and

there are missing pages, these will be noted. Also, if unauthorized copyright

material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning

the original, beginning at the upper left-hand corner and continuing from left to

right in equal sections with small overlaps. Each original is also photographed in

one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white photographic

prints are available for any photographs or illustrations appearing in this copy for

an additional charge. Contact UMI directly to order.

UMI<sup>®</sup>

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# BI-DIRECTIONAL DC-DC CONVERTER FOR LOW POWER APPLICATIONS

## Manu Jain

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Masters of Applied Science at Concordia University Montréal, Québec, Canada

February, 1998

© Manu Jain, 1998

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-39979-6

#### ABSTRACT

# BI -- DIRECTIONAL DC-DC CONVERTER FOR LOW POWER APPLICATIONS

#### Manu Jain

Applications that require exchange of power from the source to the load and viceversa have conventionally been implemented with two uni-directional converters; each processing the power in one direction. With growing emphasis on compact, smaller and efficient power systems there is increasing interest in the possibility of using bidirectional converters, especially in DC power based applications like space, telecommunication and computer systems. A bi-directional dc-dc converter, capable of bilateral power flow, provides the functionality of two uni-directional converters in a single converter unit. This thesis proposes a topology for a bi-directional dc-dc converter for use in low power applications. The implementation of this converter topology for a battery charger/discharger circuit, with applications in DC UPS systems, demonstrates its feasibility and advantages when compared to the conventionally used circuits. The topology is based on a half-bridge on the primary and a current fed push-pull on the secondary side of a high frequency isolation transformer. The small signal and steady state analyses of the proposed topology are presented. Characteristic curves generated from the analysis aid the design of a laboratory prototype as demonstrated by a detailed design example. Experimental results from the prototype, under different operating conditions, validate and evaluate the topology. Achieving bi-directional flow of power using the same power components provides a simple, efficient and galvanically isolated topology for a low power bi-directional dc-dc converter.

### **ACKNOWLEDGEMENTS**

I wish to express my gratitude to my supervisor Dr. Praveen Jain for his constant guidance, support and encouragement during the course of my graduate studies. I would also like to thank Dr. Geza Joos for providing me with technical literature and invaluable advice during the course of writing this thesis.

My most sincere thanks to my colleagues in the Power Electronics Laboratory Matteo Daniele, Humberto Pinheiro and Jose Espinoza who helped me immensely with various aspects of my research work. I am no less indebted to Ali Reza, Ali Hussein, Donato, Gerry, Haibo, Jian, Joe, Kevork, Mei, Neeraj, Randy, Simmi, and Xi for the help that they extended and all the good times we shared.

Financial support provided by the Natural Sciences and Engineering Research Council of Canada and the Ministry of Education (Quebec) through an FCAR grant is acknowledged.

| To my parents and family                          |

|---------------------------------------------------|

| who believed in me and encouraged me all the way. |

|                                                   |

|                                                   |

## TABLE OF CONTENTS

| List of Figuresxii                                                            |

|-------------------------------------------------------------------------------|

| LIST OF PRINCIPAL SYMBOLSXV                                                   |

| CHAPTER 1                                                                     |

| Introduction 1                                                                |

| 1.1 GENERAL INTRODUCTION1                                                     |

| 1.2 Literature Review                                                         |

| 1.2.1 High Power Bi-directional DC-DC Converters                              |

| 1.2.2 Medium and low power Bi-directional DC-DC converters                    |

| 1.3 SCOPE AND CONTRIBUTIONS OF THE THESIS                                     |

| 1.4 Thesis Outline6                                                           |

| CHAPTER 2                                                                     |

| DESCRIPTION OF THE BI-DIRECTIONAL CONVERTER 8                                 |

| 2.1 Introduction                                                              |

| 2.2 SELECTION OF THE APPROPRIATE POWER TOPOLOGY                               |

| 2.2.1 Half-Bridge topology for the buck-derived primary side converter 11     |

| 2.2.2 Flux balancing in the half-bridge topology                              |

| 2.2.3 Current-fed push-pull for the boost-derived secondary side converter 13 |

| 2.3 Basic Description of the Converter Components                             |

| 2.4 OPERATING MODES OF THE CONVERTER                                          |

| 2.4.1 Forward/ charging mode under ideal conditions                           |

| 2.4.2   | Forward mode operation with flux imbalance                              | 25 |

|---------|-------------------------------------------------------------------------|----|

| 2.4.3   | Backup/ Current Fed Mode                                                | 26 |

| 2.5 C   | ONTROL PRINCIPLE                                                        | 32 |

| 2.6 Co  | ONCLUSIONS                                                              | 33 |

| Снарт   | cp 2                                                                    |    |

|         |                                                                         |    |

| STEADY  | STATE ANALYSIS                                                          | 35 |

| 3.1 IN  | TRODUCTION                                                              | 35 |

| 3.2 Si  | MPLIFYING ASSUMPTIONS FOR STEADY STATE ANALYSIS                         | 36 |

| 3.3 DE  | FINING THE BASE QUANTITIES                                              | 37 |

| 3.4 ST  | EADY STATE ANALYSIS OF THE FORWARD/ CHARGING MODE                       | 38 |

| 3.4.1   | Duty ratio of switches $S_1$ and $S_2$                                  | 39 |

| 3.4.2   | Minimum value of output inductor L'                                     | 40 |

| 3.4.3   | Maximum voltage across switches $S_1$ and $S_2$                         | 42 |

| 3.4.4   | Maximum current through switches $S_1$ and $S_2$                        | 43 |

| 3.4.5   | Maximum voltage across the switches S' <sub>3</sub> and S' <sub>4</sub> | 44 |

| 3.4.6   | Maximum current through switches S' <sub>3</sub> and S' <sub>4</sub>    | 45 |

| 3.4.7   | Output capacitor C',                                                    | 46 |

| 3.4.8   | Input capacitors $C_1$ and $C_2$                                        | 47 |

| 3.4.9   | Balancing winding $N_{p_1}$ and catching diodes $D_1$ and $D_2$         | 48 |

| 3.5 STE | EADY STATE ANALYSIS FOR THE BACKUP/ CURRENT FED MODE                    | 48 |

| 3.5.1   | Duty ratio for the switches S' <sub>3</sub> and S' <sub>4</sub>         |    |

| 3.5.2   | Minimum value of Inductor L' <sub>o</sub>                               | 50 |

| 3.5.3   | Maximum voltage across switches S'2 and S'4                             |    |

| 3.5.4    | Current through switches $S'_3$ and $S'_4$                      |

|----------|-----------------------------------------------------------------|

| 3.5.5    | Maximum voltage across switches $S_1$ and $S_2$                 |

| 3.5.6    | Current through switches $S_1$ and $S_2$                        |

| 3.5.7    | Balancing winding $N_{p_1}$ and catching diodes $D_1$ and $D_2$ |

| 3.5.8    | Capacitors $C_1$ and $C_2$                                      |

| 3.6 Exp  | PERIMENTAL VERIFICATION OF THE STEADY STATE ANALYSIS            |

| 3.6.1    | Experimental waveforms for the forward mode                     |

| 3.6.2    | Experimental waveforms for the backup mode                      |

| 3.7 STE. | ADY STATE EFFICIENCY EVALUATION                                 |

| 3.8 Con  | iclusions                                                       |

| Снартен  | <b>8 4</b>                                                      |

| SMALL S  | IGNAL ANALYSIS65                                                |

| 4.1 INTR | RODUCTION                                                       |

| 4.2 STA  | TE-SPACE APPROACH66                                             |

| 4.3 SIME | PLIFYING ASSUMPTIONS                                            |

| 4.4 SMA  | LL-SIGNAL ANALYSIS OF THE FORWARD MODE                          |

| 4.4.1    | State-space equations for the circuit states                    |

| 4.4.2    | Linearized averaged state-space equation                        |

| 4.4.3    | Control constraint                                              |

| 4.4.4    | Control-to-output transfer function                             |

| 4.4.5    | Line-to-output transfer function                                |

| 4.5 SMA  | LL-SIGNAL ANALYSIS OF THE BACKUP MODE                           |

|          |                                                                 |

| 4.5.2    | Linearized averaged state-space equation                          | 78   |

|----------|-------------------------------------------------------------------|------|

| 4.5.3    | Control Constraint                                                | 79   |

| 4.5.4    | Control-to-output transfer function                               | 80   |

| 4.5.5    | Line-to-output transfer function                                  | 81   |

| 4.6 THI  | EORETICAL FREQUENCY RESPONSE FROM SMALL-SIGNAL ANALYSIS           | 81   |

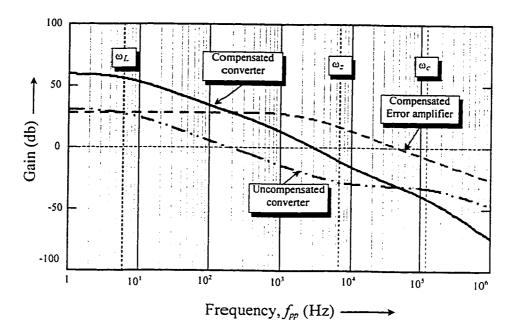

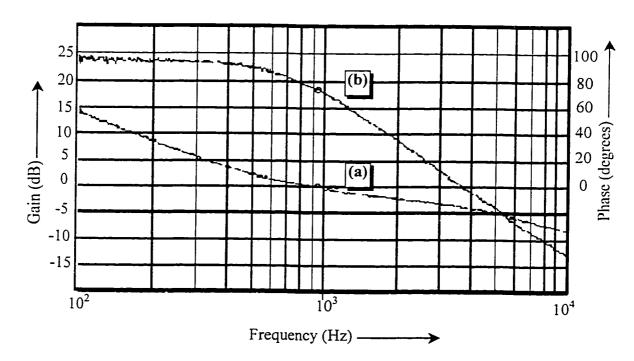

| 4.6.1    | Bode plots for the forward mode                                   | 82   |

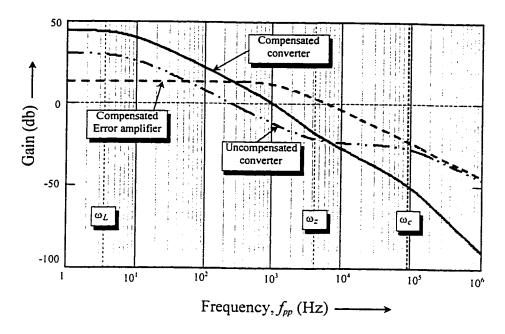

| 4.6.2    | Bode plots for the backup mode                                    | 83   |

| 4.7 Exp  | PERIMENTAL VERIFICATION OF SMALL-SIGNAL ANALYSIS                  | 85   |

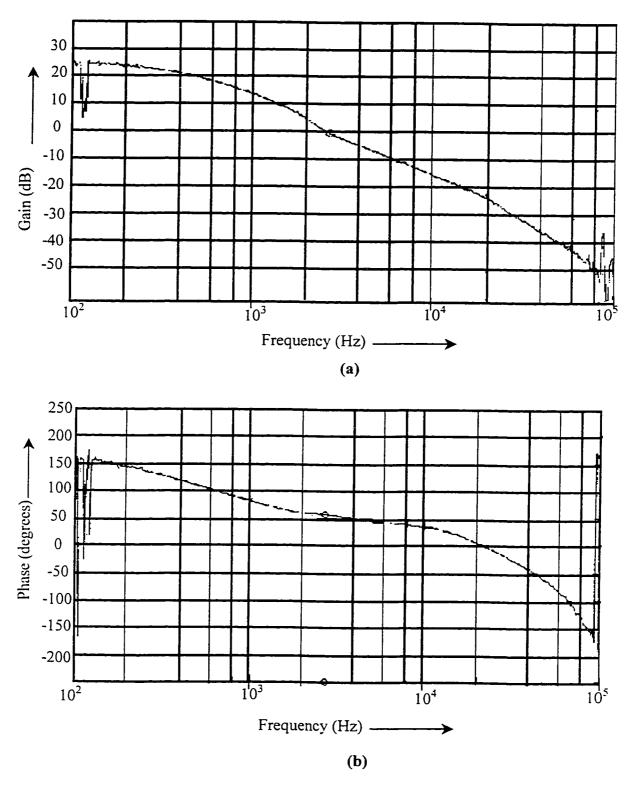

| 4.7.1    | Bode plot of the open loop frequency response in the forward mode | 86   |

| 4.7.2    | Bode plot of the open loop frequency response in the backup mode  | 88   |

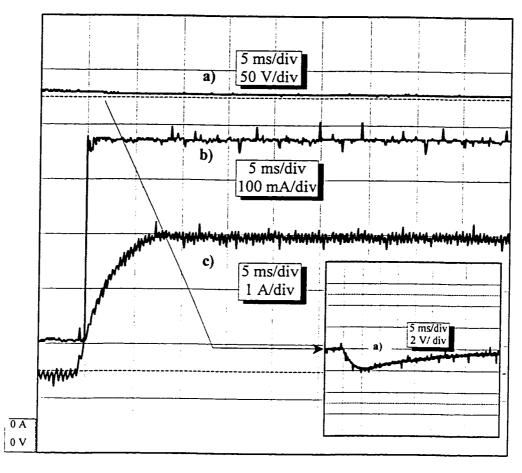

| 4.7.3    | Step change in load in the backup mode                            | 89   |

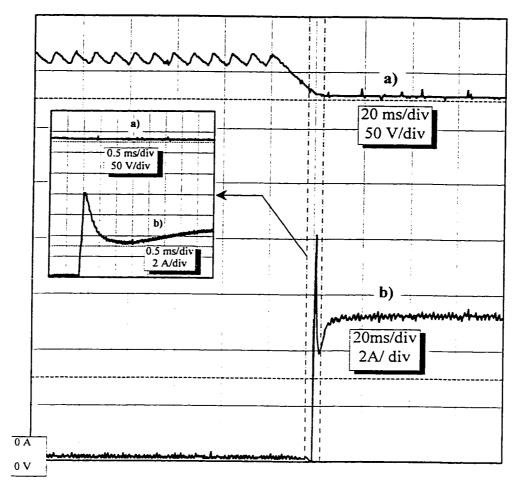

| 4.7.4    | Switchover from forward to backup mode when battery is charged    | 90   |

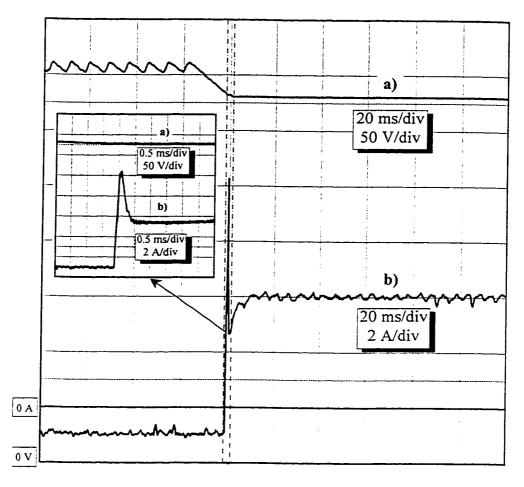

| 4.7.5    | Switchover from forward to backup mode when battery draws current | 92   |

| 4.8 Con  | CLUSIONS                                                          | 93   |

| Снартен  | 2.5                                                               |      |

|          |                                                                   |      |

| DESIGN I | EXAMPLE                                                           | .95  |

| 5.1 Inte | RODUCTION                                                         | 95   |

| 5.2 Des  | IGN SPECIFICATIONS                                                | 96   |

| 5.3 Seli | ECTION OF THE POWER COMPONENTS                                    | 97   |

| 5.3.1    | Backup battery voltage                                            | . 97 |

| 5.3.2    | Transformer turns ratio                                           | . 98 |

| 5.3.3    | Switch duty ratios                                                | . 99 |

| 5.3.4    | Inductor, $L_{\sigma}$                                            | . 99 |

| 5.3.5    | Switches, $S_1$ and $S_2$                                |

|----------|----------------------------------------------------------|

| 5.3.6    | Switches, $S_3$ and $S_4$                                |

| 5.3.7    | Output Filter capacitor, C <sub>o</sub>                  |

| 5.3.8    | Capacitors $C_1$ and $C_2$                               |

| 5.3.9    | Transformer primary winding, N <sub>p</sub>              |

| 5.3.10   | Transformer secondary winding, N,                        |

| 5.3.11   | Balancing winding, $N_{r_1}$                             |

| 5.3.12   | Catching diodes, $D_1$ and $D_2$                         |

| 5.4 Con  | IPONENT RATINGS AND VALUES USED IN EXPERIMENTAL SETUP105 |

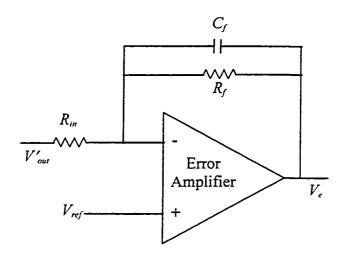

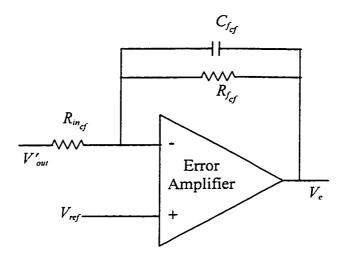

| 5.5 Com  | IPENSATED ERROR AMPLIFIER DESIGN                         |

| 5.5.1    | Compensated error amplifier for the forward mode         |

| 5.5.2    | Compensated error amplifier for the backup mode          |

| 5.6 Con  | CLUSIONS                                                 |

| Chapter  | . 6                                                      |

| SUMMARY  | Y AND CONCLUSIONS115                                     |

| 6.1 SUM  | MARY                                                     |

| 6.2 Cond | CLUSIONS                                                 |

| 6.3 Suga | GESTIONS FOR FUTURE WORK                                 |

| Referen  | CES118                                                   |

|          |                                                          |

| APPENDIX | (A123                                                    |

| A.1 SMAI | LL SIGNAL ANALYSIS FOR FORWARD MODE                      |

| A.1.1    | State variable description for the circuit states        |

| A.1.2  | Averaging the state variable equations over one time period 12     | :6 |

|--------|--------------------------------------------------------------------|----|

| A.1.3  | Linearized averaged state-space description of the forward mode 12 | :7 |

| A.1.4  | Control constraint                                                 | 8  |

| A.1.5  | Current programmed state equation                                  | 1  |

| A.1.6  | Control-to-output transfer function                                | 2  |

| A.1.7  | Line-to-output transfer function                                   | 3  |

| А.2 Sм | ALL SIGNAL ANALYSIS FOR THE BACKUP MODE                            | 4  |

| A.2.1  | State variable description for the circuit states                  | 6  |

| A.2.2  | Averaging the state variable equations over one time period        | 8  |

| A.2.3  | Linearized averaged state-space description of the backup mode     | 8  |

| A.2.4  | Control constraint                                                 | 0  |

| A.2.5  | Current programmed state equation                                  | 2  |

| A.2.6  | Control-to-output transfer function                                | 3  |

| A.2.7  | Line-to-output transfer function                                   | 5  |

## LIST OF FIGURES

| Fig. 2-1 Battery charger/discharger circuit.                                      |

|-----------------------------------------------------------------------------------|

| Fig. 2-2 Topology of the proposed bi-directional dc-dc converter                  |

| Fig. 2-3 Converter topology in the forward mode.                                  |

| Fig. 2-4 Converter topology in the backup mode.                                   |

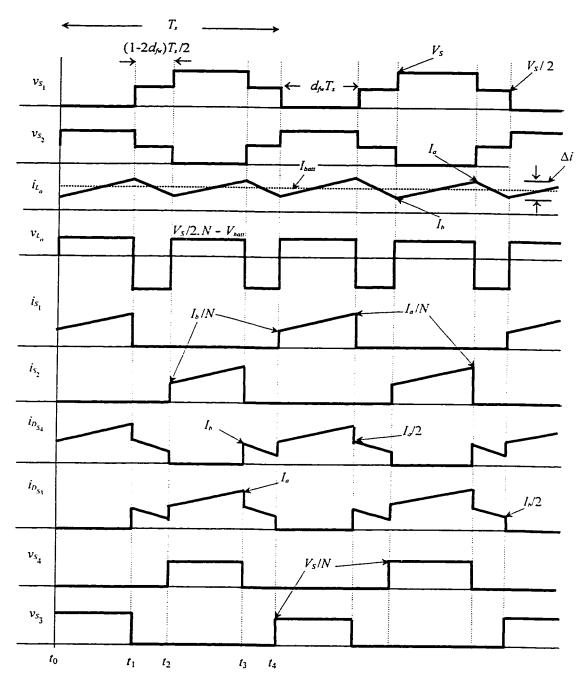

| Fig. 2-5 Idealized waveforms for the forward mode of operation                    |

| Fig. 2-6 Converter operation in the forward mode.                                 |

| Fig. 2-7 Converter operation in the forward mode.                                 |

| Fig. 2-8 Converter operation in the forward mode under flux imbalance conditions. |

| Fig. 2-10 Idealized waveforms for converter operation in the backup mode 27       |

| Fig. 2-12 Converter operation in the backup mode.                                 |

| Fig. 2-13 Converter operation in the backup mode.                                 |

| Fig. 2-14 Peak current-mode control.                                              |

| Fig. 3-1 Equivalent circuit for the forward mode.                                 |

| Fig. 3-2 Duty ratio for switches $S_1$ to $S_4$ .                                 |

| Fig. 3-3 Minimum value of inductance to maintain continuous inductor current. 41  |

| Fig. 3-4 Maximum voltage stress across switches $S_1$ and $S_2$ . 42              |

| Fig. 3-5 Rms current through the switches $S_1$ and $S_2$ . 43                    |

| Fig. 3-6 Maximum voltage stress across switches $S'_3$ and $S'_4$                 |

| Fig. 3-7 Average current through the switches $S'_3$ and $S'_4$                   |

| Fig. 3-8 Output capacitor, C'o                                                    |

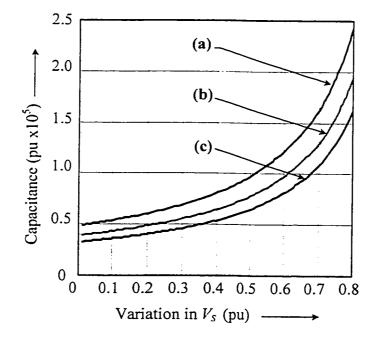

| Fig. 3-9 Input capacitor, plotted as a function of the DC bus variation           |

| Fig. 3-10 Equivalent circuit for the backup mode. 49                              |

| Fig. 3-11 Rms current through the switches $S'_3$ and $S'_4$                                                          |  |

|-----------------------------------------------------------------------------------------------------------------------|--|

| Fig. 3-12 Average current through the switches $S_1$ and $S_2$                                                        |  |

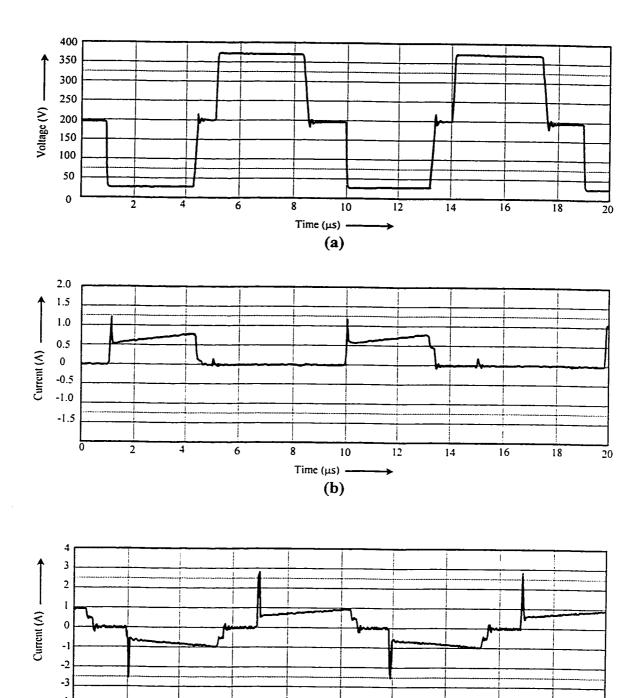

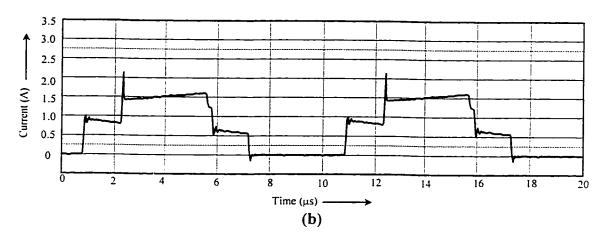

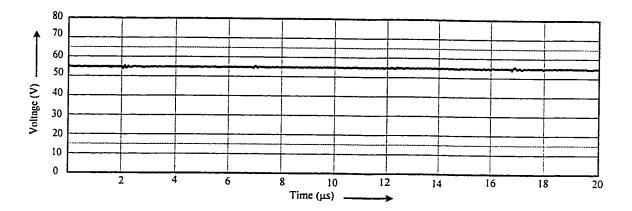

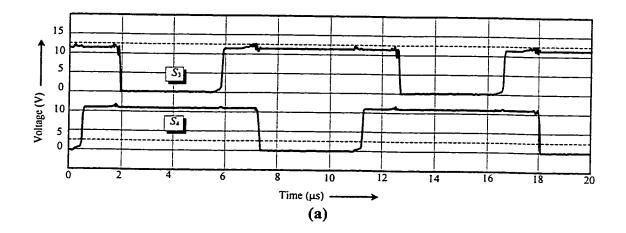

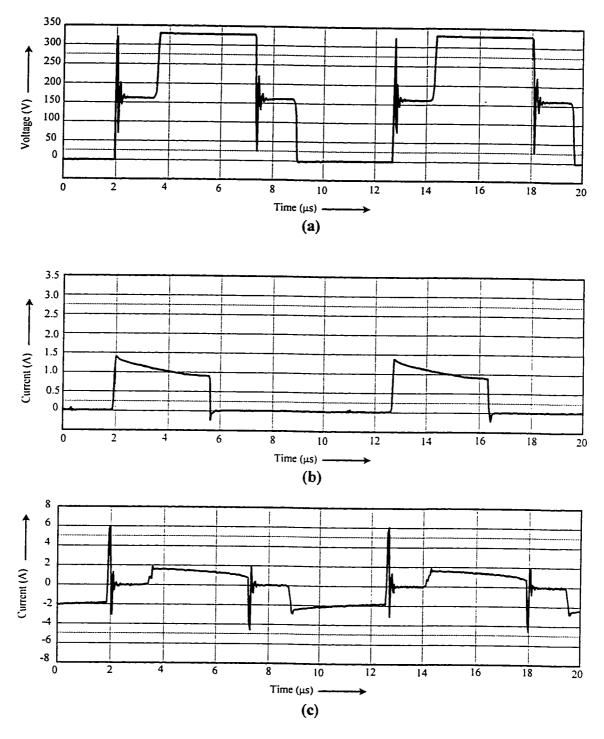

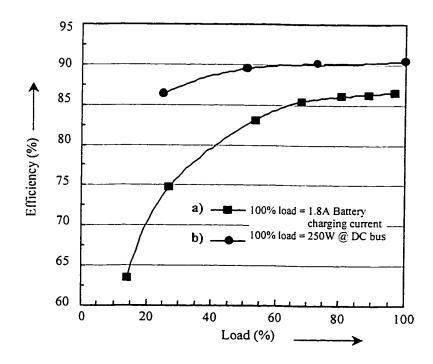

| Fig. 3-13 Experimental results for the forward mode in steady state 56                                                |  |

| Fig. 3-14 Experimental results for the forward mode in steady state 57                                                |  |

| Fig. 3-15 Experimental results for the forward mode in steady state                                                   |  |

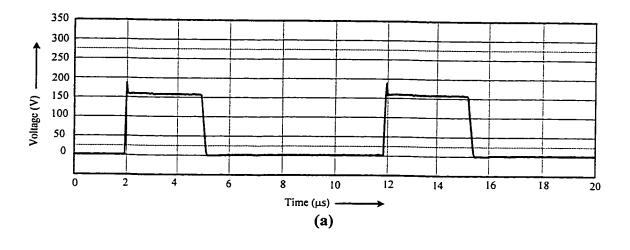

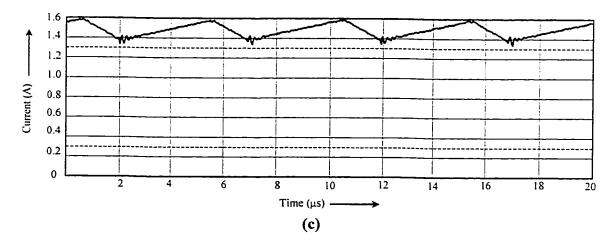

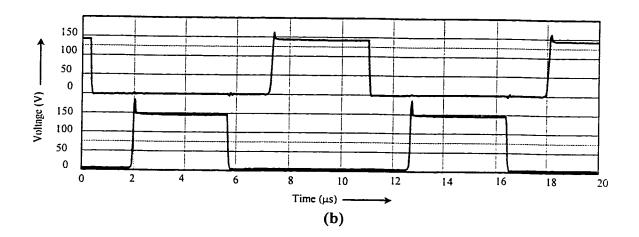

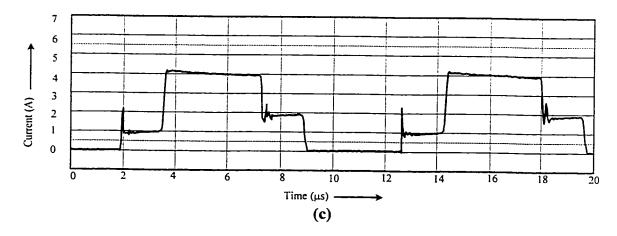

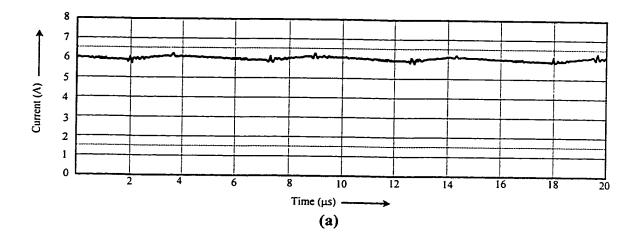

| Fig. 3-16 Experimental results for the backup mode in steady state                                                    |  |

| Fig. 3-17 Experimental results for the backup mode in steady state                                                    |  |

| Fig. 3-18 Experimental results for the backup mode in steady state                                                    |  |

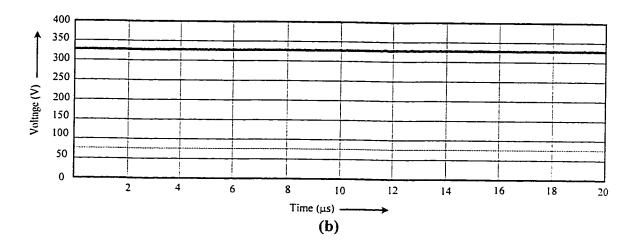

| Fig. 3-19 Converter efficiency in forward and backup modes                                                            |  |

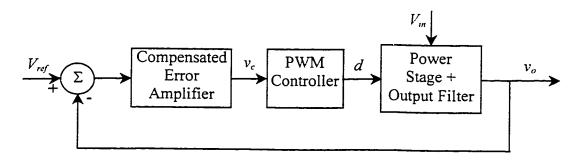

| Fig. 4-1 Block diagram representation of a converter with feedback control 65                                         |  |

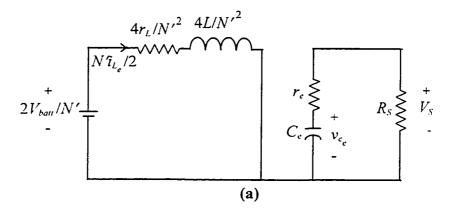

| Fig. 4-2 Equivalent circuit for the small-signal analysis of the forward mode 69                                      |  |

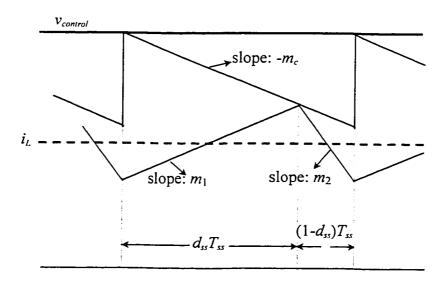

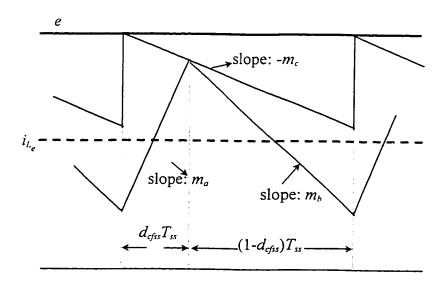

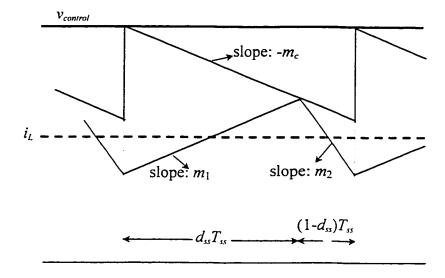

| Fig. 4-3 Waveforms showing relationship between programmed current and control signal in forward mode                 |  |

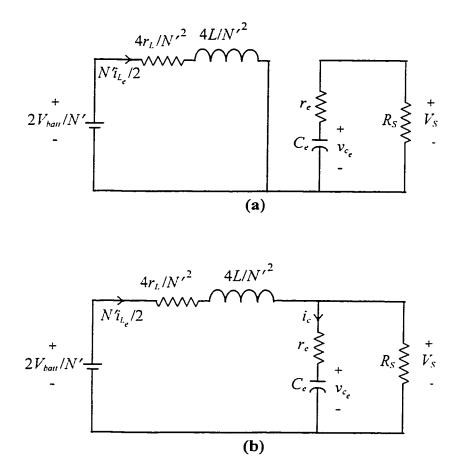

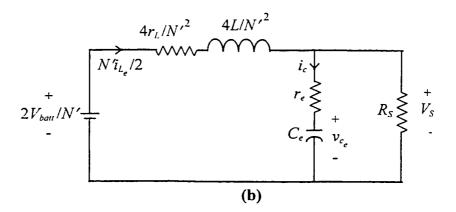

| Fig. 4-4 Equivalent circuit for the small-signal analysis of the backup mode 76                                       |  |

| Fig. 4-5 Waveforms showing relationship between programmed current and control signal in the backup mode              |  |

| Fig. 4-6 Theoretical Bode plot for the forward mode                                                                   |  |

| Fig. 4-7 Theoretical Bode plot for the backup mode                                                                    |  |

| Fig. 4-8 Experimentally obtained Bode plot for the forward mode                                                       |  |

| Fig. 4-9 Experimentally obtained Bode plot for the backup mode                                                        |  |

| Fig. 4-10 Step change in load (25% to 75%) in the backup mode                                                         |  |

| Fig. 4-11 Switchover from forward to backup mode with a charged battery and 75% load at the DC bus                    |  |

| Fig. 4-12 Switchover from forward to backup mode with the battery drawing charging current and 75% load at the DC bus |  |

| Fig. 5-1 Compensation circuit for the error amplifier in the forward mode 111                                         |  |

| Fig. 5-2 Compensation circuit for the error amplifier in the backup mode 113                                          |  |

| Fig. A- | 1 Equivalent circuit representation for the forward mode operation                  | 123 |

|---------|-------------------------------------------------------------------------------------|-----|

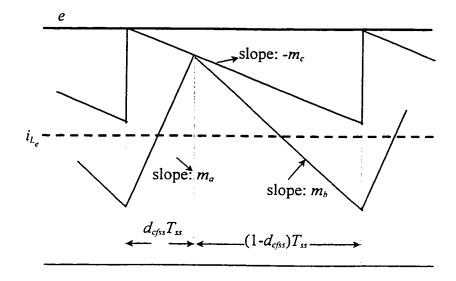

| Fig. A- | 2 Control constraint waveforms at the input of the comparator for the forward mode. | 129 |

| Fig. A- | 3 Equivalent circuit representation for the backup mode operation                   | 135 |

| Fig. A- | 4 Control constraint waveforms at the input of the comparator in the backup mode    | 141 |

### LIST OF PRINCIPAL SYMBOLS

$S_1$ : High side switch (MOSFET) of half-bridge topology.

$S_2$ : Low side switch (MOSFET) of half-bridge topology.

$S_3 \& S_4$ : Switches (MOSFETs) of current-fed push-pull topology.

$C_1 \& C_2$ : Input capacitors of the half-bridge.

$T_1$ : High frequency isolation transformer.

$N_p$ : Number of turns of transformer primary winding.

$N_s$ : Number of turns of transformer secondary winding.

N : Ratio of primary to secondary turns of transformer windings.

L<sub>o</sub> : Inductor on secondary side of isolation transformer; output filter

for half-bridge.

$C_o$ : Capacitor on secondary side of isolation transformer; output

filter for half-bridge.

$D_1 \& D_2$ : Catching diodes for flux balancing of half-bridge.

$N_{p_1}$ : Auxiliary winding flux balancing of half-bridge.

$V_s$ : Nominal DC bus voltage.

$V_{batt}$ : Nominal battery voltage.

$i_{bus}$ : Nominal DC bus (load) current.

*i*<sub>batt</sub>: Nominal battery charging current.

$i_{Lo}$ : Nominal inductor voltage.

$D_{S_1} - D_{S_2}$ : Body diodes of switches  $S_1 - S_4$ .

$T_s$ : Converter switching time period for both operating modes.

$d_{fir}$  : Duty ratio of  $S_1 \& S_2$  in forward mode.

Duty ratio of  $S_3 & S_4$  in backup mode.

$D_{ov}$ : Overlap duty ratio of  $S_1 & S_2$  in backup mode.

$\Delta i$ : Peak-to-peak ripple in inductor current.

$V_{base}$ : Base voltage.

$P_{base}$ : Base power.

$P_{bus}$ : Power at the DC bus.

$P_{batt}$ : Power at the battery end.

$f_{base}$ : Base frequency.

$I_{base}$ : Base current.

$L_{base}$ : Base inductance.

$C_{base}$ : Base capacitance.

$d_{fw_{max}} \& d_{fw_{min}}$ : Maximum and minimum duty ratio of  $S_1 \& S_2$  in forward

mode.

$V_{batt_{max}} \& V_{batt_{min}}$ : Maximum and minimum battery voltage.

$V_{S_{max}} \& V_{S_{min}}$ : Maximum and minimum DC bus voltage.

$L_{o_{min}}$ : Minimum value of inductor Lo.

$I_{batt_{min}} \& I_{batt_{max}}$ : Maximum and minimum value of battery charging current.

$V_{S_{1 max}} & V_{S_{2 max}}$ : Maximum voltage stress across  $S_1 & S_2$ .

$I_{S_{1rms}} \& I_{S_{2rms}}$ : Rms current through  $S_1 \& S_2$ .

$V'_{D_{S3\,max}} \& V'_{D_{S4\,max}}$ : Maximum voltage across  $S_3 \& S_4$ .

$I'_{D_{S3_{avg}}} \& I'_{D_{S4_{avg}}}$ : Average current through  $S_3 \& S_4$ .

$V_{\mathit{batt}_{\mathit{peak}}}$ : Peak allowable battery voltage.  $V_{ripple}$ Input voltage ripple for half-bridge converter. Deg & Ceg : Equivalent diode and capacitor for steady state analysis of backup mode operation.  $D_{min} & D_{max}$ : Minimum and maximum duty ratio of  $S_3 & S_4$  in the backup mode.  $D_L$ : Duty ratio for calculating the  $L_{o_{min}}$  in backup mode.  $d_{ss}$ : Duty ratio of switch in equivalent circuit for small-signal analysis of forward mode.  $T_{ss}$ : Switching time period of equivalent circuit for small-signal analysis of forward and backup modes. : Equivalent series resistance of inductor  $L_o$ .  $r_I$ C: Equivalent output capacitance for small-signal analysis of forward mode.  $r_c$ : Equivalent series resistance of capacitor  $C_a$ .  $v_c$ : Voltage across equivalent output capacitor C. R : Resistance representing load for small-signal analysis of

forward mode.

N': Ratio of secondary to primary turns of transformer windings.

$d_{cfsss}$ : Equivalent duty ratio of  $S_3$  and  $S_4$  for small-signal analysis of backup mode.

## CHAPTER 1

## INTRODUCTION

### 1.1 GENERAL INTRODUCTION

Power electronic circuits primarily process the energy supplied by a source to match the form required by the load, by means of using semiconductor devices to control the voltage and current. The energy is usually available from the utility grid or from a bank of batteries with the applications ranging from high-power conversion equipment processing megawatts to everyday low power equipment with requirements of a few milliwatts.

The majority of power converters are unidirectional with the power being supplied from the source to the load. But, a number of applications like motor drives [1-4], uninterruptible power supplies [5-10], alternate energy systems [11], battery charger-dischargers, telecommunication [12] and space systems [13-14], require the additional exchange of energy from the load to the source. These applications utilize power converters with bi-directional transfer properties.

Conventionally, two independent unidirectional converters were used to achieve bi-directional transfer of power. The escalating cost of energy in recent years has resulted

in growing emphasis on energy management due to the drain on natural resources and environmental pollution, and energy saving techniques are becoming more important. The demand for the development of sophisticated, compact and efficient power systems has prompted research in bi-directional converters providing the desired bilateral power flow and capable of replacing the two unidirectional converters.

Bi-directional power flow is an especially attractive proposition in DC power based systems such as spacecraft applications, telecommunication and computer systems, where the weight and physical size of the power processing modules are a critical aspect of design. Bi-directional dc-dc converters allow transfer of power between two dc sources, in either direction with the ability to reverse the direction of flow of current, and thereby power, while maintaining the voltage polarity at either end unchanged. Such converters are by nature more complex than unidirectional converters.

Although, extensive research has been conducted on unidirectional dc-dc converters, the focus on dc-dc converter topologies applicable for bi-directional power flow has been primarily on medium and high power applications [15-19] with few topologies presented for low power applications. This thesis presents a bi-directional dc-dc converter for low power applications.

## 1.2 LITERATURE REVIEW

In this section, previous work in the area of bi-directional dc-dc converters is reviewed with the objective of defining the current status of research in this area and evaluating topologies for their possible implementation in low power bi-directional dc-dc converters.

### 1.2.1 High Power Bi-directional DC-DC Converters

Various topological variations for DC-DC converters of high power applications with bi-directional power transfer properties have been proposed. The high power dc-dc converters use either resonant [20], soft switching achieved by controlled phase shift [17-19] or hard switched PWM. In general, despite their individual advantages, these topologies are unsuitable for low power applications due to one or all of the following reasons:

- Large number of switches.

- High component count.

- Many switches are active at any given instant of time and the gating pattern may be complicated.

- Limited range of satisfactory operation with high efficiency.

- Complex power and control circuitry.

Operation of the converters in resonant mode [20] uses SCR's, is seen to have high power densities and has the advantage of natural commutation and soft switching ability. However, they have penalties in terms of frequency sensitivity, higher voltage and current stresses in the devices and larger ripple currents in the input and output capacitive filters. Resonant converters also require careful matching of the operating frequency to the resonant tank circuit, and magnetic saturation or drift in the resonant frequency can result in failure.

The dual active bridge presented by Divan et. al. in [17] achieves lower switching losses by controlling the phase shift between the two inverting stages operating at high frequencies. It utilizes the leakage inductance of the transformer as the main energy

transfer element. At high powers and frequencies designing a transformer with controlled leakage is extremely complicated [22]. Also, this topology imposes limitations on the load range and the input voltage range to maintain soft switching for all devices.

The inverse-dual-converter [15-16] does not have the disadvantages of a limited range of operating conditions or complicated transformer design and has high power density at high efficiency. But, this topology is unsuitable for low power applications due to the higher number of switching devices and the sequential commutation technique for their gating.

# 1.2.2 Medium and low power Bi-directional DC-DC converters

As for the higher power applications, medium and low power bi-directional dc-dc converters are also based on either hard switching [6-9, 14, 23-29], soft switching or resonance [13, 30-31]. Most of these dc-dc converters are well suited for a particular application but have one or more of the following drawbacks:

- Lack of galvanic isolation between the battery and the load or source.

- High component stresses.

- Limited operating range when based on resonance or soft switching techniques.

- Large current ripple through the inductors.

- At high frequencies the converters designed to operate under resonance or soft switching may suffer from hard switching of the devices.

The converters operating in the resonant mode [13, 30-31] have a limited range of load and voltage conditions and also subject the devices to high stresses. The presence of

only one active switch in the circuit path during each direction of power flow, leads to higher ratings for the switch and the components as a whole and results in greater costs. In addition, conduction losses in the resonant converter maybe higher. The bi-directional converter topologies presented in [13, 26-31] do not provide galvanic isolation between the battery and the load or source, which is often required in battery operated dc-dc power systems.

Two significant applications of bi-directional dc-dc converters namely, DC UPS [26-28] and battery charger/discharger circuits [13, 14, 23, 29] are based on topologies that aim to achieve lower part count and therefore use components with higher ratings that are expensive and are not optimally selected.

### 1.3 SCOPE AND CONTRIBUTIONS OF THE THESIS

This thesis is concerned with a bi-directional dc-dc converter for low power applications. The purpose is to present a topology that attempts to overcome the drawbacks in the existing topologies. The unique combination of two well known power topologies to achieve the proposed topology of the bi-directional dc-dc converter is the principal contribution of this thesis. The main objectives of the thesis are:

- (i) To propose a bi-directional dc-dc converter topology that can be used for low power applications. The specific application of a battery charger/discharger is taken into account as a case study.

- (ii) To present the steady state and small-signal analysis of the proposed converter.

- (iii) To develop a design procedure for the converter that enables the selection and rating of components for its implementation.

(iv) To verify the feasibility of the proposed converter, the analysis and the design procedure with a design example and the experimental results obtained from the practical setup of the designed converter.

### 1.4 THESIS OUTLINE

The contents of each chapter of the thesis are organized as follows:

Chapter 2 presents the basic topology of the proposed bi-directional converter with application in a battery charger/discharger circuit. The selection of the proposed power topology as opposed to other possible topologies is discussed. The basic components of the converter are described. Operating principles of the bi-directional converter in both the charging and discharging modes are presented. The control of the converter is achieved by peak current mode control and its basic principles and advantages are discussed.

Chapter 3 presents the steady state analysis of the converter in both operating modes. This is used to generate characteristic curves, which provide an insight into the converter and can be used to rate and select the power components in an actual design. The experimental results from the steady state operation of a prototype are used to verify the analysis and the characteristic curves.

Chapter 4 presents the small-signal analysis of the converter while operating in the forward/charging mode and the backup/discharging mode. The key transfer functions for the converter and the error amplifier that aid in the compensated error amplifier design are presented. The theoretical frequency response is compared with the frequency response of the prototype to validate the small-signal analysis. Dynamic response of the

prototype, under switchover from one mode to another and load transients, is presented to demonstrate the closed loop response of the converter.

Chapter 5 presents the detailed design procedure for a laboratory prototype of the proposed converter. The procedure demonstrates the ease of selecting and rating power components when the characteristic curves provided by the steady state analysis are used. The compensated error amplifier in the control loop is designed with the information provided by the transfer functions resulting from the small-signal analysis.

Chapter 6 presents the contributions and conclusions of this thesis and suggestions for future work.

Appendix A shows the detailed mathematical procedure of the small-signal analysis and the derivation of key transfer functions for both operating modes.

# **CHAPTER 2**

# DESCRIPTION OF THE BI-DIRECTIONAL CONVERTER

### 2.1 Introduction

As discussed in the previous chapter, some applications require bi-directional transfer of power, which is now being achieved through a single bi-directional converter rather than the conventional approach of using two uni-directional converters. A bi-directional dc-dc converter topology for low power applications is proposed. A battery charger/discharger circuit is chosen as the application where such a converter can be implemented. The battery charger/discharger circuit can be used as part of a DC uninterruptible power supply (UPS).

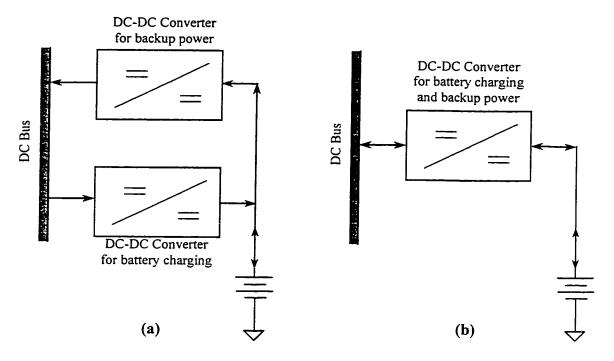

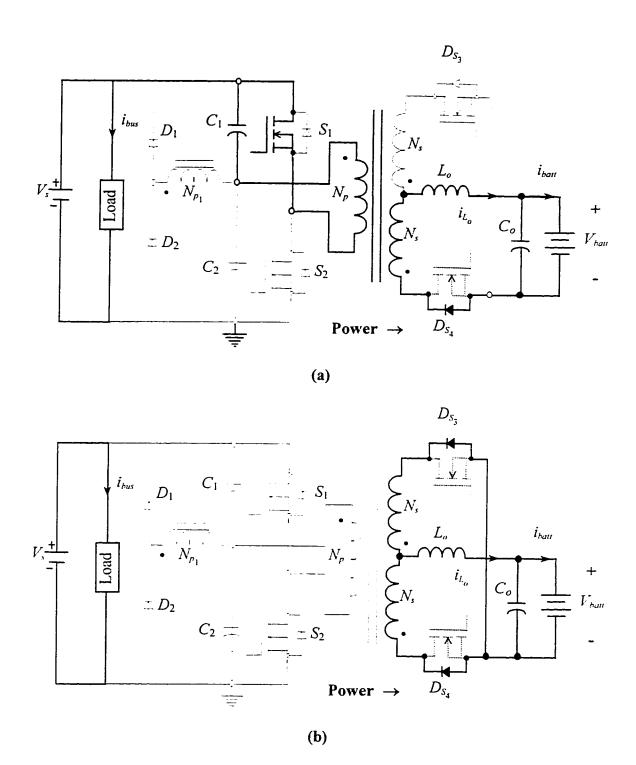

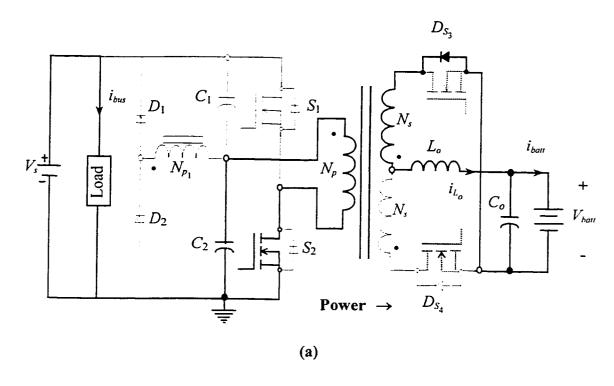

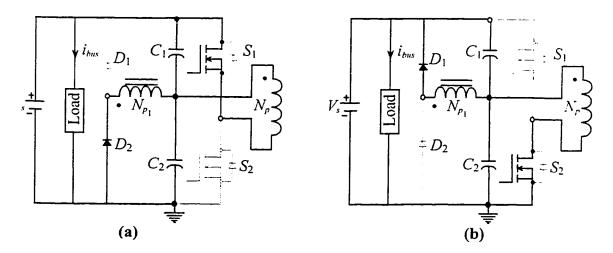

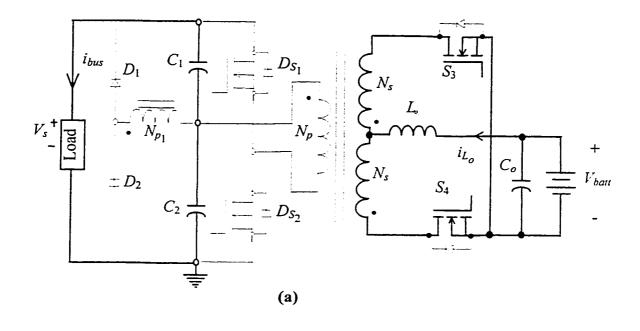

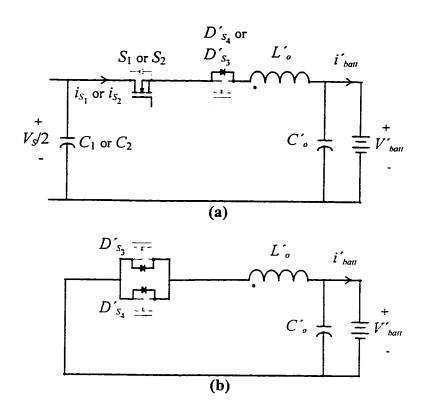

Conventional battery charger/discharger circuits, Fig. 2-1(a) comprise of two converters; one for the charging the battery from a DC bus and the other to provide power to the DC bus from the battery. The proposed bi-directional converter provides both functions of battery charging and discharging in a single conversion unit with its bi-directional power flow capability, Fig. 2-1(b).

Fig. 2-1 Battery charger/discharger circuit.

(a) Conventional circuit using two uni-directional converters. (b) Battery charger/discharger circuit using proposed bi-directional converter.

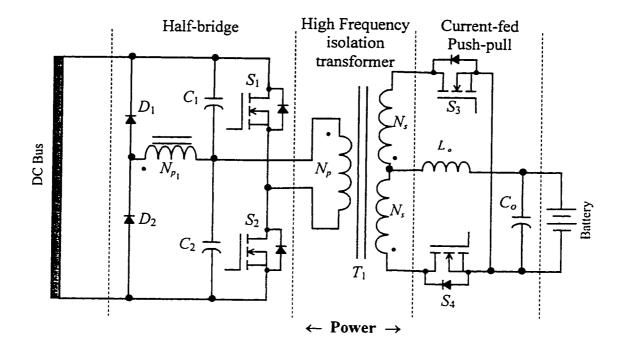

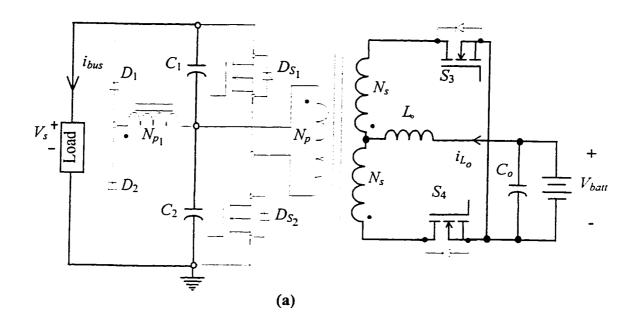

The basic power topology of the proposed bi-directional converter is shown in Fig. 2-2. The bi-directional converter is seen to consist of a half-bridge topology on the primary of a high frequency isolation transformer and a current-fed push-pull topology on the secondary of the transformer. The DC bus is connected to the half-bridge end and the battery is connected to the current-fed push-pull end of the converter. The converter operates in the forward/charging mode or the backup/discharging mode, depending on the status of the DC mains. All switches are bi-directional and are gated according to the operating mode of the converter.

The objective of this chapter is to describe in detail the topology, modes of operation and the control principle of the proposed bi-directional dc-dc converter for a battery charger/discharger application.

Fig. 2-2 Topology of the proposed bi-directional dc-dc converter.

## 2.2 SELECTION OF THE APPROPRIATE POWER TOPOLOGY

Various power topologies can be considered for implementation in bi-directional dc-dc converters. For the battery-charging/forward mode of converter operation, the low voltage battery is charged from the high voltage DC bus and a buck-derived converter must be used. In the backup mode, when the battery supplies the power to the DC bus, a boost-derived circuit is used to produce the higher voltage at the DC bus. Selecting the appropriate topologies is dependent on the application while taking into account their merits and demerits.

The proposed bi-directional dc-dc converter consists of a buck-derived half-bridge circuit on the primary (high voltage end) of the high frequency transformer and a boost-derived current-fed push-pull on the secondary (battery end). The use of these topologies is justified by comparing them to other possible converter topologies.

## 2.2.1 Half-Bridge topology for the buck-derived primary side converter

Bridge topologies are commonly used in converters being fed from a rectified AC line or a high voltage DC bus. Half- and full-bridge topologies subject their switches in the off state to a voltage stress equal to the DC input voltage and not to twice that as do the push-pull, single-ended and interleaved forward converter topologies. In addition, the drawback of voltage spikes on the primary of push-pull and the single-ended forward topologies due to leakage inductance in the transformer primary winding is absent in the bridge topologies. The primary leakage inductance spikes are clamped to the DC supply bus and any energy stored in the leakage inductance is returned to the bus instead of being dissipated in some resistive element. This allows the converters to be used from a high voltage DC bus with switches having lower voltage ratings that are inexpensive and easily available. The inherent problem of transformer saturation in the push-pull is easily overcome in bridge topologies. Bridge topologies also provide better utilization of the transformer windings and core than the conventional push-pull where only one half winding is used during each cycle.

Although the switches in full-bridge topology carry half the peak and rms currents compared to the half-bridge, for the same output power, the number of switches is twice that in the half-bridge. Thus, the full-bridge is usually used in higher power circuits.

The double-ended forward converter also subjects the off state switches to a voltage stress equal to the DC bus voltage like the half-bridge. But, the half-bridge secondary provides a full-wave output compared to a half wave in the forward converter. Thus the square-wave frequency in the half-bridge secondary is twice that in the forward converter, resulting in a smaller output LC inductor and capacitor. The number of

windings on the half-bridge primary is half that in the forward as it must sustain half the supply voltage as compared to the full voltage in the forward, resulting in reduce the winding cost and lower parasitic capacities. The half-bridge topology operates the transformer core in the bipolar flux mode of operation and utilizes the whole primary winding allowing full copper utilization of the transformer.

### 2.2.2 Flux balancing in the half-bridge topology

If the average volt-seconds applied to the primary winding for all positive going pulses is not exactly equal to that for all the negative going pulses, the transformer flux density will increase with each cycle and staircase into saturation. A volt-seconds inequality on alternate half cycles will cause the transformer core to be biased closer towards saturation and enter the curved part of the hysteresis loop. The magnetizing inductance, which is proportional to the slope of the hysteresis loop, decreases and the magnetizing current increases. Under such conditions, small temperature increases can bring about a runaway situation, which drives the core into saturation and destroys the power switches.

In half-bridge implementations using MOSFETs as switching devices, such a situation may arise due to unequal voltage drops across the MOSFETs when they are in the on state. Thus, the junction of  $C_1$  and  $C_2$  is not exactly at half of the supply voltage. Current-mode control when applied to the half-bridge will ensure that the peak current is identical for each half cycle. In order to correct any volt-second asymmetry a small differential offset in the pulse width will be created, but this results in unequal ampereseconds drawn through the primary switching devices. Use of a DC blocking capacitor in series with the transformer primary [32] has been suggested, but this will cause a voltage

to build up across it in a direction that reinforces the original volt-second asymmetry. The series capacitor will charge towards one of the supply voltages and alternate half cycles will have unequal voltage amplitudes.

A suitable method of avoiding the runaway saturation of the core is to use a separate balancing winding on the primary side of the transformer with two catching diodes  $D_1$  and  $D_2$  [33]. This will restore the centerpoint voltage on  $C_1$  and  $C_2$ , compensating for any unequal ampere-seconds in the switching devices by allowing restoration current to flow through them. The wire gauge and the diodes can be small, as they carry only small restoration currents. The number of turns on the balancing winding,  $N_{p_1}$ , should be the same as the primary turns,  $N_p$ .

## 2.2.3 Current-fed push-pull for the boost-derived secondary side converter

To provide bi-directional power transfer, the output rectifying stage for the half-bridge must be implemented with bi-directional switches. When the converter operates in the backup mode, the battery is the source of energy and provides power to the DC bus. The presence of the output filter inductor of the half-bridge topology in series with the source (battery) results in a current fed topology for the backup mode.

Current-fed converters present numerous inherent advantages, especially at high output voltages and higher output powers, which is the case when the battery is providing backup power to the DC bus. For high output voltages, the size and cost of an output inductor becomes prohibitive. Also, the current-fed converter inherently limits the current provided by the battery.

To allow bi-directional flow of power, the current-fed topology must be a boost-derived circuit. This is evident from the principle of duality for linear electrical networks.

as the half-bridge is a buck-derived circuit. Although switching power converters are nonlinear electrical systems by their very nature, linear duality analysis and principles can be applied to them. This can be demonstrated by the fact that linear small-signal models, using the state-space averaging methods can represent such converters.

A number of boost-derived current-fed topologies have been reported in literature and have been well received as they provide significant advantages over conventional circuits in many applications. Among them the current-fed push-pull operating with overlapping conduction intervals for the switches is probably the mostly widely used topology [34-36]. The disadvantages of other current-fed topologies include:

- poorly controlled inrush current at turn-on,

- use of multiple winding chokes and transformers,

- presence of a tapped input inductor, and

- use of two or more switches in series which reduce the conversion efficiency.

In the proposed converter, the rectifying stage of the half-bridge inverter naturally provides the current-fed push-pull topology. When used with overlapping switch conduction times, the above mentioned topology has the advantage of equal division of inductor current between the switching devices, thereby reducing their average and rms currents as well as the rms current magnitude in the transformer winding  $N_{\rm c}$ .

### 2.3 Basic Description of the Converter Components

The topology of the bi-directional converter is shown in Fig. 2-2. The basic elements of the converter, their functionality and advantages for both operating modes are described briefly in this section.

### (i) Capacitors, $C_1$ and $C_2$

The capacitors  $C_1$  and  $C_2$  provide the split voltage source at the primary winding of the transformer for the forward operating mode. With their large capacitance values, they are the input filters to the half-bridge converter and remove any ripple that may be present due to the rectified AC line. Also, a lengthy input, which adds series inductance and resistance between the source and the power supply, may not be able to deliver the high-frequency demands of the supply necessary for the fast voltage and current transitions within it. These capacitors will charge at a low frequency and source current over a much higher frequency range. In the backup mode, they form the output filter section for the loads at the DC bus. For the time intervals when the power is not transferred from the battery to the bus, the capacitors discharge to power the load at the DC bus. They are the holdup capacitors during the switchover from forward to backup mode.

### (ii) Switches $S_1$ and $S_2$

The power MOSFETs  $S_1$  and  $S_2$  are the primary switching devices of the halfbridge circuit while the converter is operating in the forward mode. They are gated at a constant frequency with variable on time to provide the necessary regulated output voltage at the battery end, from the DC bus. The intrinsic body diodes of these switches provide rectification at the DC bus end during backup mode operation.

### (iii) Transformer T<sub>1</sub>

The high frequency transformer  $T_1$  galvanically isolates the battery from the DC bus, thereby from the loads connected to it. It also performs a voltage step-up and/or step-

down function for the converter depending on the operating mode.  $N_p$  represents the transformer primary winding and each half of the center-tapped secondary is represented by  $N_s$ .

## (iv) Auxiliary winding, $N_{p_1}$ and diodes $D_1$ and $D_2$

The auxiliary winding  $N_{p_1}$  and the two catching diodes  $D_1$  and  $D_2$  restore the centerpoint of the capacitors  $C_1$  and  $C_2$  to half the input DC voltage and prevent staircase saturation of the transformer during operation as a half-bridge converter. In the backup mode, these elements enable equal and simultaneous charging of  $C_1$  and  $C_2$ , which are now the output filter capacitors.

### (v) Switches $S_3$ and $S_4$

The power MOSFET  $S_3$  and  $S_4$  are the main switching devices of the current-fed push-pull converter in the backup mode. They are switched at a constant frequency and their variable on time is controlled according to the load demand on the DC bus or the variation in the battery voltage. In the battery-charging mode, the body diodes of these switches are the rectifying elements for the half-bridge converter and carry the battery charging current,  $i_{ban}$ .

### (vi) Inductor L<sub>o</sub>

The inductor  $L_o$  is a part of the output filter for the half-bridge converter topology and reduces the ripple in the battery charging current. The energy stored in the inductance is used to charge the battery during the intervals when the switches  $S_1$  and  $S_2$  are not gated. In the backup mode,  $L_o$  is in series with the energy source (battery) resulting in a current-fed push-pull topology.

### (vii) Capacitor C.

The output filter for the half-bridge comprises of  $L_o$  and  $C_o$ . The voltage ripple at the battery side is determined by the capacitor  $C_o$ .  $C_o$  discharges to hold up the battery voltage when primary side switches are not conducting and its charge is replenished by the energy stored in the inductor  $L_o$ . This capacitance does not play any significant role in the battery discharging mode.

## 2.4 OPERATING MODES OF THE CONVERTER

The converter has two modes of operation. In the forward mode the battery is charged by energy from the DC bus and in the backup mode, in the absence of the DC mains the battery discharges to power the load at the bus.

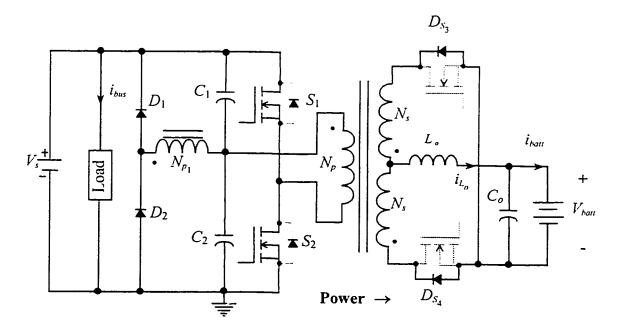

• Forward/ Charging Mode: In the forward/charging mode the converter operates as buck-derived topology. The energy from the DC mains charges the battery over the

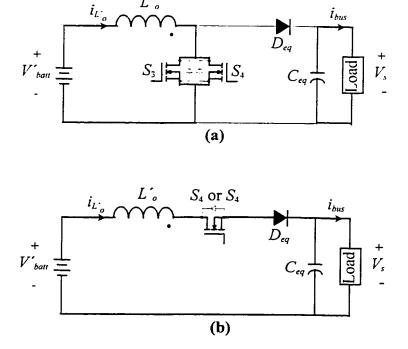

Fig. 2-3 Converter topology in the forward mode.

input voltage range of the bus, while also powering the down stream load converters. In this mode only the switches  $S_1$  and are  $S_2$  gated and the body diodes of the switches  $S_3$  and  $S_4$  provide battery side rectification. The converter topology for this mode of operation is shown in Fig. 2-3.

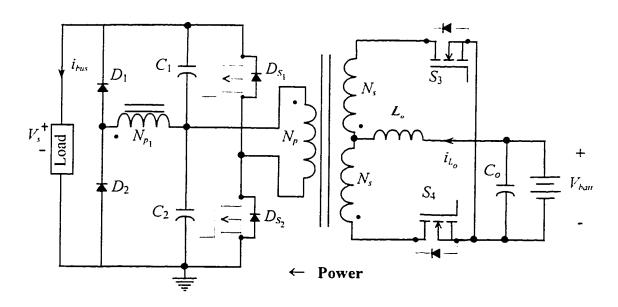

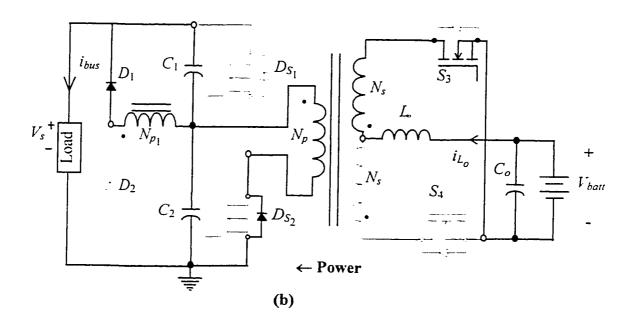

• Backup/ Current-fed Mode: On failure of the dc mains, reversal of power flow occurs resulting from a switchover to the battery. Now the converter operates in the boost-derived mode. The battery supplies the load power at the DC bus voltage. In this mode, the switches  $S_3$  and  $S_4$  are gated and the body diodes of the switches  $S_1$  and  $S_2$  provide rectification at the output DC bus side. This operating mode is shown in Fig. 2-4.

Fig. 2-4 Converter topology in the backup mode.

### 2.4.1 Forward/ charging mode under ideal conditions

Fig. 2-6 and Fig. 2-7 show the operation for this mode. The DC bus powers the down stream converters and charges the battery. The bus voltage,  $V_s$ , is bucked down by the half-bridge converter and charges the battery to the nominal voltage,  $V_{batt}$ , by supplying the battery charging current,  $i_{batt}$ . The switches  $S_1$  and  $S_2$  on the primary side are gated at duty ratios less than 0.5, while  $S_3$  and  $S_4$  are not switched at all.

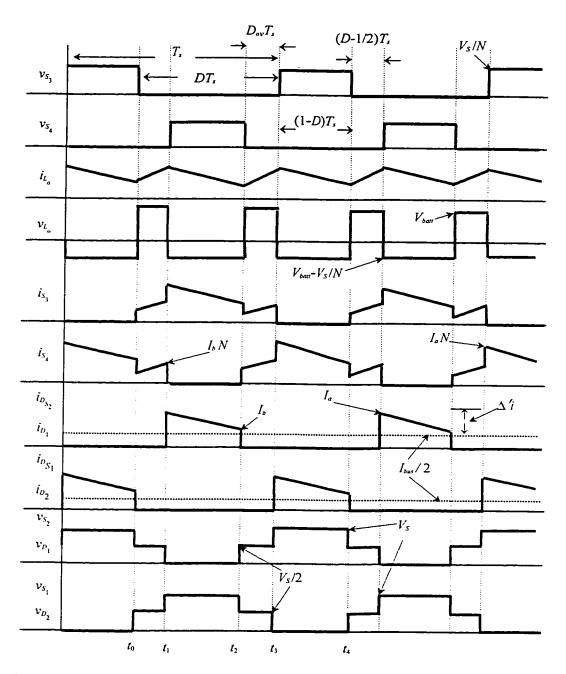

The converter operation is repetitive in the switching cycle,  $T_s$ . The various stages of operation during one switching time period are described by the time intervals between  $t_0$  to  $t_4$ , in the idealized waveforms of Fig. 2-5. Fig. 2-6 and Fig. 2-7 show the converter circuit for each time interval.

Fig. 2-5 Idealized waveforms for the forward mode of operation.

Waveforms for nominal input and battery voltages at full load at the battery end with switch duty ratio less than 0.5.

#### • Interval t<sub>0</sub>-t<sub>1</sub>:

Fig. 2-6(a) shows converter operation during this time interval. Both the switches  $S_1$  and  $S_2$  are in the OFF state before time  $t_0$ . Now, switch  $S_1$  is turned ON at  $t_0$  for a time interval of " $d_{fr}T_s$ ". The converter operates as a buck-derived half-bridge. A voltage  $V_s/2$  appears across the primary winding,  $N_p$ , and also the OFF switch,  $S_2$ . On the secondary side only the body diode of the switch  $S_4$ ,  $D_{S_4}$ , is forward biased and provides output rectification.  $D_{S_4}$  carries the total secondary current.  $D_{S_3}$  is subject to a reverse voltage stress equal to the voltage across the secondary winding of the transformer and does not carry any current during this interval. The output filter components,  $L_a$  and  $C_a$ , provide the necessary filtering action for the current and voltage at the battery end. The voltage across the inductor results in a linear increase in the inductor current, and therefore the primary switch current  $i_{S_1}$  for the ON period of primary switch.

#### • Interval t<sub>1</sub>-t<sub>2</sub>:

The converter operation during this time interval is shown in Fig. 2-6(b). Switch  $S_1$  is turned OFF at instant  $t_1$  while  $S_2$  continues to remain OFF. During this dead time interval there is zero voltage across the primary, and therefore secondary windings of transformer, and no power is transferred to the secondary side. The energy stored in  $L_o$  from the previous interval provides the battery power. Voltage across the inductor reverses and the inductor current  $i_{L_o}$  decreases linearly as it freewheels through the body diodes  $D_{S_3}$  and  $D_{S_4}$ , both of which are forward biased. The diodes share the current equally during this interval, thereby reducing the rms current through them. As none of the primary side switches,  $S_1$  or  $S_2$ , are conducting they are subject to a reverse voltage stress across them that is equal to half the supply voltage.

Fig. 2-6 Converter operation in the forward mode.

(a) Interval  $t_0 - t_1$ . (b) Interval  $t_1 - t_2$ .

#### • Interval t<sub>2</sub>-t<sub>3</sub>:

Fig. 2-7(a) describes the converter circuit during this interval. The switch  $S_2$  is turned ON at instant  $t_2$  while  $S_1$  continues to remain in the OFF state. The operation of the converter is similar to that during the interval  $t_0$ - $t_1$ , with  $S_2$  and  $S_3$  being analogous to  $S_1$  and  $S_4$  in the interval  $t_0$ - $t_1$ . Now  $S_2$  carries the primary side current and the body diode of switch  $S_3$ ,  $D_{S_3}$ , conducts and provides secondary side rectification. The voltage and current stresses for the switches in the OFF and ON states are identical to those in the interval  $t_0$ - $t_1$ .

#### • Interval t<sub>3</sub>-t<sub>4</sub>:

Converter operation during this interval is similar to that in the interval  $t_1 - t_2$ . None of the primary side switches is ON and the battery charging current, is provided by the energy stored in the inductor. The body diodes of both the switches on the secondary side,  $D_{S_3}$  and  $D_{S_4}$ , conduct simultaneously and share the inductor current equally. This interval is depicted in Fig. 2-7(b).

Fig. 2-7 Converter operation in the forward mode. (a) Interval  $t_2 - t_3$ . (b) Interval  $t_3 - t_4$ .

### 2.4.2 Forward mode operation with flux imbalance

The time intervals  $t_0 - t_4$  describe the half-bridge operation of the bi-directional converter in the forward/battery-charging mode under ideal conditions without any flux imbalance. As explained in section 2.2.2 of the text, if the voltage at the junction of the capacitors,  $C_1$  and  $C_2$  drifts away from the ideal condition of half the input DC supply voltage it may result in saturation of the transformer core and thereby damage the power switches irreversibly. Fig. 2-3 shows the balancing winding  $N_{p_1}$  and two catching diodes  $D_1$  and  $D_2$  that maintain the centerpoint voltage at the junction of  $C_1$  and  $C_2$ . The phasing of the balancing winding is in series with the primary winding  $N_p$ . By the nature of the two series windings of identical turns, the centerpoint of the high voltage capacitors is forced to one-half of the input DC voltage. Any drift in the midpoint voltage will cause a small amount of restoration current to flow through the balancing winding and the diodes. The primary circuit path in the event of a flux imbalance condition when either switch is shown in Fig. 2-8.

Fig. 2-8 Converter operation in the forward mode under flux imbalance conditions. (a) When switch  $S_1$  is ON. (b) When switch  $S_2$  is ON.

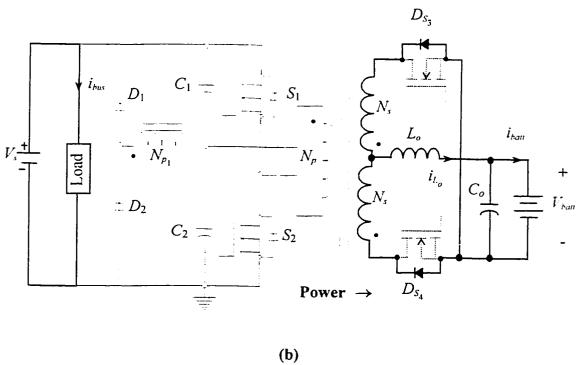

#### 2.4.3 Backup/ Current Fed Mode

The converter operates in this mode, Fig. 2-4, on failure of the DC mains. The backup mode is the boost-derived mode of operation. In the absence of the DC bus, the battery discharges to supply power to the down stream converters connected to the DC bus. The switches  $S_3$  and  $S_4$  of the current fed push-pull topology are gated at duty ratios greater than 0.5. Rectification at the output is provided by the body diodes of the switches  $S_1$  and  $S_2$ . The backup mode is described with reference to the waveforms presented in Fig. 2-9. As in the charging mode, inductor current is assumed to be continuous. The time intervals between  $t_0$  to  $t_4$  describe the converter operation, which is repetitive over a switching cycle,  $T_s$ . Each time interval is also represented by the converter circuits in Fig. 2-10 and Fig. 2-11.

Fig. 2-9 Idealized waveforms for converter operation in the backup mode. Waveforms for nominal DC bus and battery voltages at full load at the DC bus end with switch duty ratio greater than 0.5.

#### • Interval t<sub>0</sub>-t<sub>1</sub>:

Switch  $S_4$  is assumed to be in the ON state before the time instant  $t_0$  and  $S_3$  is turned ON at  $t_0$  with an ON time equal to  $DT_s$ . The converter topology during this time interval is shown in Fig. 2-10(a). The transformer secondary windings,  $N_s$ , are subject to an effective short circuit, which causes the inductor,  $L_o$ , to store energy as the total battery voltage appears across it. The inductor current,  $i_{L_0}$ , ramps up linearly and is shared equally by both  $S_3$  and  $S_4$ . During this interval, energy stored in the output bulk capacitors,  $C_1$  and  $C_2$ , provides the load power at the DC bus. There is no transfer of energy from the battery end to the DC bus end. None of the body diodes of the primary side switches is conducting and they are subject to a reverse voltage stress equal to half the output voltage at the DC bus.

#### • Interval t<sub>1</sub>-t<sub>2</sub>:

$S_4$  is turned OFF at instant  $t_1$  while  $S_3$  continues to remain ON during this interval, described by Fig. 2-10(b). The energy stored in  $L_o$  during the previous interval replenishes the charge in the output bulk capacitors and provides load power at the bus. through the body diode  $D_{S_2}$  and the diode  $D_1$ . Consequently, the inductor current ramps down and will reach the value equal to that at instant  $t_0$  if the operation is in steady state. Voltages across the auxiliary winding  $N_{p_1}$  and the primary winding  $N_p$  are identical due to their series phasing and equal number of turns. Thus, equal currents flow through  $D_1$  and  $D_{S_2}$  allowing simultaneous and equal charging of both  $C_1$  and  $C_2$ , respectively.

Fig. 2-10 Converter operation in the backup mode.

(a) Interval  $t_0 - t_1$ . (b) Interval  $t_1 - t_2$ .

#### • Interval t<sub>2</sub>-t<sub>3</sub>:

This interval, Fig. 2-11(a), is similar to interval  $t_0$ - $t_1$ . Switch  $S_3$  remains ON and  $S_4$  is switched ON at time  $t_2$ . The duty ratio for  $S_3$  is therefore greater than 0.5. With both  $S_3$  and  $S_4$  turned ON, the transformer secondary is effectively shorted and the inductor core stores energy, resulting in a linear rise in inductor current,  $i_{L_0}$ . Voltage across both  $N_p$  and  $N_{p_1}$  is zero, so load power is supplied by the discharge of the bulk capacitors. Current and voltage stresses for the switches on the battery side and the load side are identical to those across them in the interval  $t_0 - t_1$ .

#### • Interval t<sub>3</sub>-t<sub>4</sub>:

Converter operation during this interval, Fig. 2-11(b), resembles that during the interval  $t_1$ - $t_2$ .  $S_4$  remains ON and  $S_3$  is switched OFF at instant  $t_3$ . The stored energy in  $L_o$  is transferred to the primary side of the converter through the switch conducting on the secondary side,  $S_4$ , and the primary diodes  $D_{S_1}$  and  $D_2$ . The conduction of  $D_{S_1}$  and  $D_2$  results in equal charging of  $C_1$  and  $C_2$ , respectively.

Fig. 2-11 Converter operation in the backup mode.

(a) Interval  $t_2 - t_3$ .(b) Interval  $t_3 - t_4$ .

# 2.5 CONTROL PRINCIPLE

The average dc output in DC-DC converters must be regulated within a specified tolerance band around its nominal value in response to changes in the output load and the input voltage variations. Keeping the switching frequency constant, the output voltage of the converter is maintained at the desired level by varying the on time of the switch(es). Voltage or current mode control techniques are used for the regulating the voltage at the output of a converter.

Current mode control, with an additional inner control loop directly controls the inductor current with the error signal rather than controlling the duty ratio of the pulse width modulator. Current mode control presents many advantages, such as:

- improved transient response due to the faster inner current loop,

- automatic symmetry correction which eliminates the problem of transformer core saturation in most topologies,

- simpler loop compensation as it removes one pole from the control-to-output transfer function, especially in the presence of the right-half-plane zero,

- inherent feed-forward of the input voltage,

- capability for modular design of power supplies whereby several power supplies

can be operated in parallel and provide equal currents, and

- inherent pulse by pulse limiting of the switch current by measuring it directly or indirectly somewhere in the circuit.

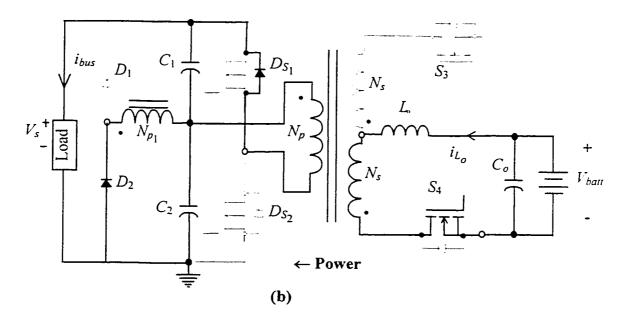

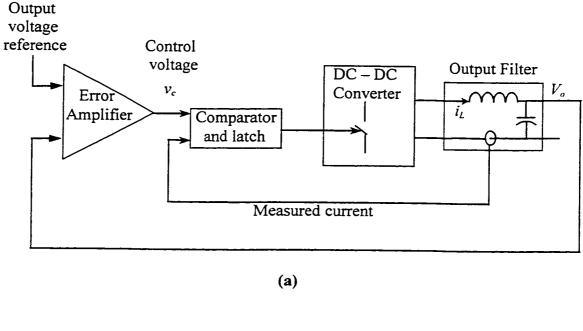

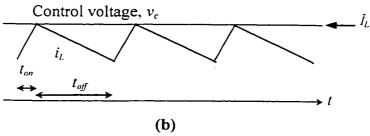

In the proposed converter, both the forward and backup modes use peak current-mode control, Fig. 2-12, to regulate the output voltage. The necessary control action on

Fig. 2-12 Peak current-mode control.

(a) Basic logic circuit. (b) Relevant waveforms.

the switch duty ratio is achieved by limiting the peak value of the sensed current against an error signal generated by the comparison of the output voltage with its reference value.

### 2.6 CONCLUSIONS

The bi-directional dc-dc converter is based two converter topologies, namely the half-bridge and the current-fed push-pull. The reasons justifying the choice of these topologies over possible other implementations are presented in this chapter. Bi-

directional converter operation in the forward mode as a buck-derived half-bridge converter and in the backup mode as a boost-derived current-fed push-pull converter is described over one steady state switching period. The advantages of using peak current-mode control for converter regulation are also mentioned.

# CHAPTER 3

# STEADY STATE ANALYSIS

### 3.1 Introduction

The previous chapter presented the details on the topology, operating modes and the basic elements of the proposed bi-directional dc-dc converter. In order to design a converter it is necessary to quantify circuit characteristics, such as the currents flowing through its elements, the voltages across these elements etc. Thus, the selection of components for the bi-directional converter is influenced by various circuit parameters and operating conditions. The design oriented steady state analysis of the converter in both operating modes provides design equations from which numerical values for steady state converter performance and component stresses are computed and used in the component selection process.

The design oriented steady state analysis is based on the pertinent idealized waveforms shown in Fig. 2-5 and Fig. 2-9. The key concept in the ensuing analysis is the fact that the converter must be boost-derived under all conditions in the backup mode and buck derived under all conditions in the forward mode. Thus the output voltage in the backup mode should always be greater than or at least equal to the lower limit of the DC bus voltage range; an operating condition that is specified before the converter design

commences. This condition must be satisfied under the worst case when the secondary switches are operating at minimum duty ratio with maximum battery voltage. This constraint determines the nominal battery voltage for a given turns ratio of the transformer which consequently effects all other circuit parameters.

The circuit parameters are normalized in this worst case analysis to ensure validity of the results and suitable converter operation over a wide range of operating conditions. Using the steady state design expressions, characteristic curves are generated for the circuit parameters to aid the component selection process. These curves are plotted as a function of the variation in the input DC bus. Other relevant qualitative considerations that must be accounted for while selecting the components in an experimental setup are also presented.

Finally, one must also bear in mind the dual set of constraints arising from the use of the same power circuit for both the operating modes and therefore choose the components accordingly.

# 3.2 SIMPLIFYING ASSUMPTIONS FOR STEADY STATE ANALYSIS

The following simplifying assumptions are made for the steady state analysis of both operating modes. Despite the limitations imposed by these assumptions, the expressions derived in the following sections are accurate enough for practical design purposes.

1. The circuit is operating under steady state, implying that all voltages and currents are periodic.

- 2. The switches are ideal. Therefore in the conducting state the voltage drops across them are zero and they have infinite resistance in the blocking state.

- 3. The transformer is ideal with unity turns ratio.

- 4. The output capacitor is very large and the output voltage is held constant.

- All circuit parameters are normalized over their base quantities and referred to the primary of the isolation transformer. Secondary side variables reflected to the primary are denoted by a prime ".".

- 6. The output power of the converter in the forward/battery-charging mode is between one-half and one-third the output power delivered in the backup mode.

- 7. The maximum theoretical duty ratio of the switching devices in the forward mode is 0.5 and the minimum theoretical duty ratio for the switching devices in the backup mode is 0.5.

- 8. The range in the input DC bus is specified which therefore determines the nominal battery voltage.

### 3.3 DEFINING THE BASE QUANTITIES

To normalize the circuit parameters for the analysis base quantities for voltage, power and frequency are defined and those for impedance and current are derived from the basic defined base quantities.

The output DC bus voltage in the backup mode,  $V_s$ , is chosen as the base voltage.

1 pu voltage,  $V_{base} = V_S$  volts.

The output power at the DC bus in the backup mode is defined as the base power.

1 pu power,  $P_{base} = P_{bus}$  watts.

The converter switching frequency in the backup mode is chosen as the base value for frequency.

1 pu frequency,  $f_{base} = f_s$  hertz.

Using these defined base quantities the derived base quantities for impedance and current are expressed as,

1 pu current,  $I_{base} = P_{bus} / V_S$  amps (base value for current),

1 pu inductance,  $L_{base} = P_{bus} / 2\pi f_s$  henries (base value for inductance), and

1 pu capacitance,  $C_{base} = 1 / 2\pi f_s P_{bus}$  farads (base value for capacitance).

# 3.4 STEADY STATE ANALYSIS OF THE FORWARD/ CHARGING MODE

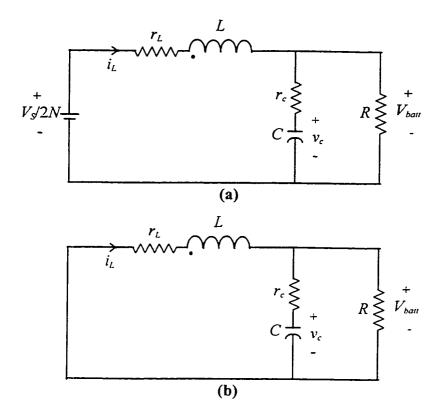

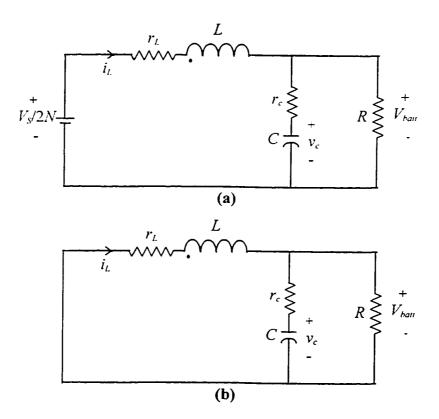

The half-bridge operation of the converter in the forward mode is analyzed for continuous inductor current at a fixed switching frequency. The equivalent circuits of Fig. 3-1 represent the two different states of forward mode operation with all parameters reflected to the primary of the isolation transformer.

Fig. 3-1(a) is the equivalent circuit representation of converter when either one of the primary side switches  $S_1$  or  $S_2$  is in the ON state, for a time interval of  $d_{fi}$   $T_s$ .

Fig. 3-1(b) is the equivalent circuit representation of the forward mode for the interval  $(1-d_{fw})T_s$  when none of the primary side switches is being gated. The output power is delivered by the energy stored in the inductor. Both the body diodes conduct simultaneously and share the battery charging current equally.

Fig. 3-1 Equivalent circuit for the forward mode. (a) Either  $S_1$  or  $S_2$  is ON. (b)  $S_1$  and  $S_2$  are both OFF.

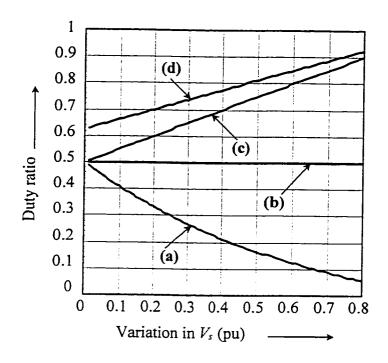

# 3.4.1 Duty ratio of switches S<sub>1</sub> and S<sub>2</sub>

The maximum theoretical ON time for the primary side switches,  $d_{fir}T_s$ , is 50% of the switching time period  $T_s$ . The maximum and minimum duty ratios of  $S_1$  and  $S_2$ ,  $d_{fir}$  and  $d_{fir}$  are given by the following expressions:

$$d_{fw_{max}} = \frac{V'_{batt_{max}}}{V_{S_{min}}}$$

(3.1)

$$d_{fw_{min}} = \frac{V'_{balt_{max}}}{V_{S_{max}}}$$

(3.2)

where  $V_{batt_{max}}$  is the normalized value of the maximum battery voltage and  $V_{S_{max}}$  and

Fig. 3-2 Duty ratio for switches  $S_1$  to  $S_4$ .

(a) Minimum duty ratio of  $S_1$  and  $S_2$ . (b) Maximum duty ratio of  $S_1$  and  $S_2$ . (c) Minimum duty ratio of  $S_3$  and  $S_4$ . (d) Maximum duty ratio of  $S_3$  and  $S_4$ .

$V_{S_{min}}$  are the maximum and minimum voltages at the DC bus in the forward mode. The theoretical values of the duty ratios for a specified variation in the DC bus voltage from its nominal value are shown in Fig. 3-2.

In a practical setup a dead time is provided between the turn OFF instant of one switch and the turn ON of the other to ensure that they do not overlap and thereby present a short circuit at the transformer primary.

# 3.4.2 Minimum value of output inductor L'

The current through  $L'_o$  is assumed to be continuous over the entire operating range of the bi-directional converter in the forward mode. The minimum required value of the output inductor,  $L'_{o_{min}}$ , is calculated at the boundary of continuous and discontinuous conduction of the inductor under minimum load conditions (i.e. when the

battery draws minimum charging current) at the maximum input DC bus voltage. This lower limit for the inductance value is expressed as

$$L'_{o_{min}} = \frac{V'_{batt_{max}}}{4 \cdot f_s \cdot I'_{batt_{min}}} \cdot \left(1 - 2d_{fw_{min}}\right) \text{ pu}, \qquad (3.3)$$

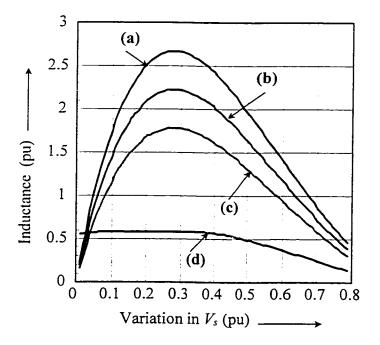

where  $I'_{batt_{min}}$  is the minimum pu battery charging current and  $V'_{batt_{max}}$  the normalized value of the maximum battery voltage. Fig. 3-3 shows  $L'_{o_{min}}$  as a function of the specified variation in the input DC bus voltage for typical values of the power at the battery end.

The actual value of the inductor in an experimental setup maybe larger than  $L'_{o_{min}}$  depending on the ripple current specifications for the battery charging current. A suitable tradeoff is be made between the output current ripple,  $\Delta'i$ , and the size of the inductor.

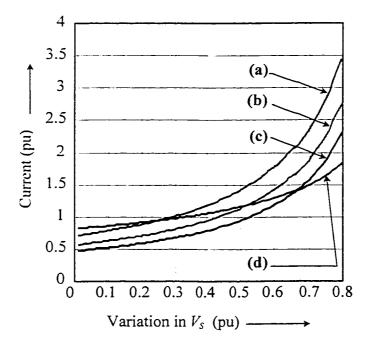

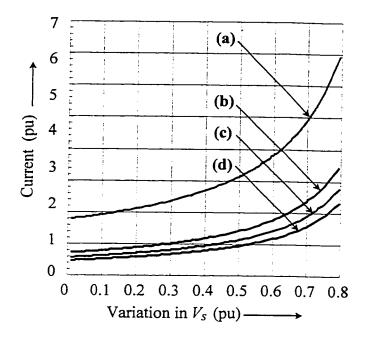

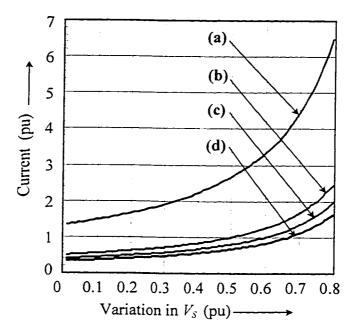

Fig. 3-3 Minimum value of inductance to maintain continuous inductor current. (a) Forward mode,  $P_{ball} = 0.33$  pu. (b) Forward mode,  $P_{ball} = 0.4$  pu. (c) Forward mode,  $P_{ball} = 0.5$  pu. (d) Backup mode,  $P_{bus} = 1.0$  pu.

### 3.4.3 Maximum voltage across switches $S_1$ and $S_2$

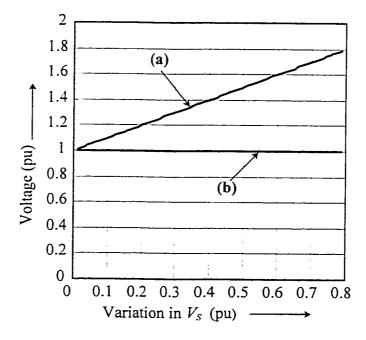

Power switches are generally the least reliable components within a power supply and must be selected carefully. The selection of the appropriate switch depends primarily on the voltage stresses across it and the rms current through it. The switch must be rated to withstand the maximum reverse voltage across it.

The maximum reverse voltage across the primary side switches,  $S_1$  and  $S_2$ , is equal to the maximum input voltage at the DC bus which is given by the expression,

$$V_{S_{1max}} = V_{S_{2max}} = V_{S_{max}}$$

pu (3.4)

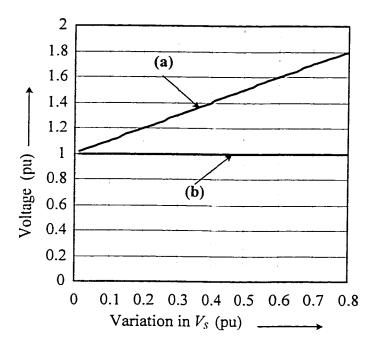

where,  $V_{s_{max}}$  is the maximum input DC bus voltage. The maximum voltage stress across  $S_1$  and  $S_2$  are shown in Fig. 3-4.

Fig. 3-4 Maximum voltage stress across switches  $S_1$  and  $S_2$ .

(a) Forward mode. (b) Backup mode.

#### 3.4.4 Maximum current through switches $S_1$ and $S_2$

Once the voltage rating for the switches is determined (3.4), the required current handling capability of the switch must also be calculated. The maximum rms current through the primary side switches,  $I_{S_{1mis}}$  and  $I_{S_{2mis}}$ , is defined under the worst case of minimum input voltage and maximum battery charging current,  $I'_{batt_{max}}$ .

The maximum rms current through the switch is given by,

$$I_{S_{1rms}} = I_{S_{2rms}} = \frac{1}{2\sqrt{3}} \sqrt{(12I'_{ball_{max}}^2 + \Delta i'^2) \cdot d_{fir_{max}}}$$

pu (3.5)

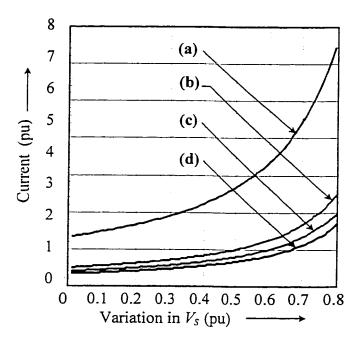

where  $\Delta i'$  is the normalized value of the ripple in the inductor current. Fig. 3-5 shows the design curves for the maximum rms current through  $S_1$  and  $S_2$  for the typical battery charging power levels.

Fig. 3-5 Rms current through the switches  $S_1$  and  $S_2$ .

(a) Forward mode,  $P_{batt} = 0.5$  pu. (b) Forward mode,  $P_{batt} = 0.4$  pu. (c) Forward mode,  $P_{batt} = 0.33$  pu. (d) Backup mode,  $P_{bus} = 1.0$  pu.

### 3.4.5 Maximum voltage across the switches S'3 and S'4

The body diodes of the switches  $S'_3$  and  $S'_4$  provide rectification at the secondary side of the high frequency transformer. Thus,  $D'_{S_3}$  and  $D'_{S_4}$ , are subject to maximum reverse voltages when they are reverse biased. The maximum voltage is determined from when only one diode is in the circuit path. The voltage stress across the body diode and therefore the switch itself, is given by,

$$V'_{D_{S3\,max}} = V'_{D_{S4\,max}} = V_{S_{max}}$$

pu (3.6)

Fig. 3-6 shows the voltage across the secondary side switches reflected to the primary.

Fig. 3-6 Maximum voltage stress across switches S'<sub>3</sub> and S'<sub>4</sub>.

(a) Forward mode. (b) Backup mode.

### 3.4.6 Maximum current through switches S'3 and S'4

The body diodes,  $D's_3$  and  $D's_4$ , carry the battery charging current. The average current through these diodes is therefore calculated to select the switches  $S'_3$  and  $S'_4$  with appropriate current ratings. The average current through the diodes over one switching time period computed for the worst case condition of minimum input voltage and maximum load conditions is shown in Fig. 3-7 and is given by the expression:

$$I'_{D_{S3_{avg}}} = I'_{D_{S4_{avg}}} = \frac{I'_{batt_{max}}}{2} \text{ pu}$$

(3.7)

Fig. 3-7 Average current through the switches  $S'_3$  and  $S'_4$ .

(a) Backup mode,  $P_{bus} = 1.0$  pu. (b) Forward mode,  $P_{batt} = 0.5$  pu. (c) Forward mode.  $P_{batt} = 0.4$  pu. (d) Forward mode,  $P_{batt} = 0.33$  pu.

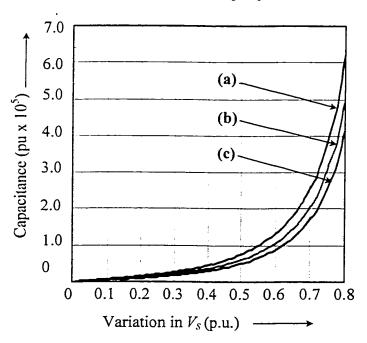

### 3.4.7 Output capacitor C'o

While operating in the forward mode, if the battery is suddenly removed, the energy stored in the inductor  $L'_o$  must be discharged into the output filter capacitor  $C'_o$ . This constraint and the maximum allowable value of output voltage ripple on  $V'_{batt}$ , based on the parasitic equivalent series resistance (esr) of the capacitor, define the choice of the filter capacitor  $C'_o$ . The first, and the dominant, constraint gives the minimum possible value of capacitor that can be used as,

$$C'_{o} = \frac{L'_{o} \cdot I'_{batt_{max}}^{2}}{V'_{batt_{peak}}^{2} - V'_{batt}^{2}}$$

pu (3.8)

where,  $V'_{batt_{peak}}$  is the peak allowable battery voltage when the load is removed. Fig. 3-8 shows the capacitor value for different values of output power in the forward mode.

Fig. 3-8 Output capacitor, C'o.

(a) Forward mode,  $P_{batt} = 0.5$  pu. (b) Forward mode,  $P_{batt} = 0.4$  pu. (c) Forward mode.  $P_{batt} = 0.33$  pu.

### 3.4.8 Input capacitors $C_1$ and $C_2$

The input bulk capacitors,  $C_1$  and  $C_2$ , Fig. 3-1(a), provide a split voltage source for switches  $S_1$  and  $S_2$  and are equal in value. These bulk capacitors must provide adequate filtering action for the input voltage ripple,  $V_{ripple}$ . They must also be large enough to provide sufficient hold up time at the DC bus voltage under dc mains failure, before the converter begins operation in the backup mode. The value of the capacitors is calculated from the expression given below and is shown as a function on the DC bus variation in Fig. 3-9.