Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file. Vot e reference

Our file Notre référence

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# Verification of Test Cases for Protocol Conformance Testing

#### Kshirasagar Naik

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirement

for the Degree of Doctor of Philosophy at

Concordia University

Montreal, Quebec, Canada

May, 1992

© Kshirasagar Naik, 1992

Acquisitions and

Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file. Votre référence

Our file Notice référence

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-81014-9

#### **ABSTRACT**

#### Verification of Test Cases for Protocol Conformance Testing

Kshirasagar Naik, Ph. D.,

Concordia University

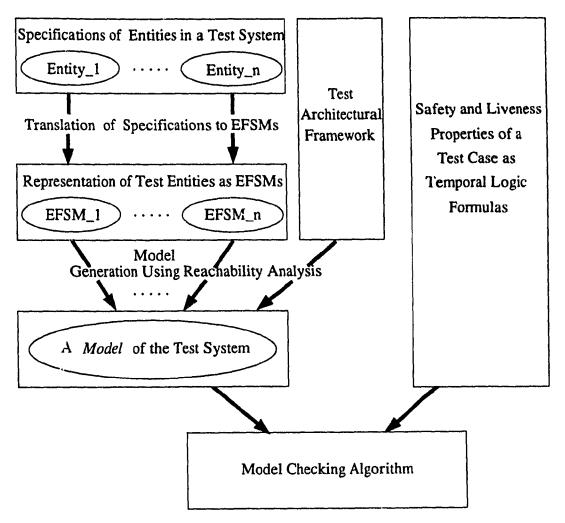

This thesis is concerned with verifying the correctness of human designed test cases for determining the conformance of a protocol implementation with its formal specification. Correctness of a test case, like any other software systems, is established by verifying the safety and liveness properties of the test case against the model of a test verification system.

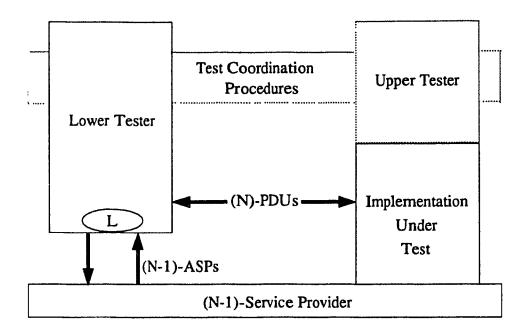

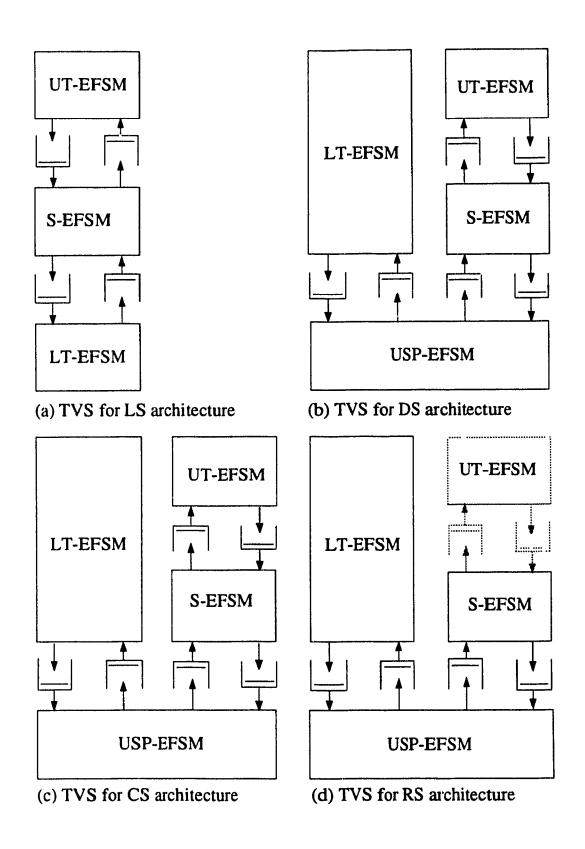

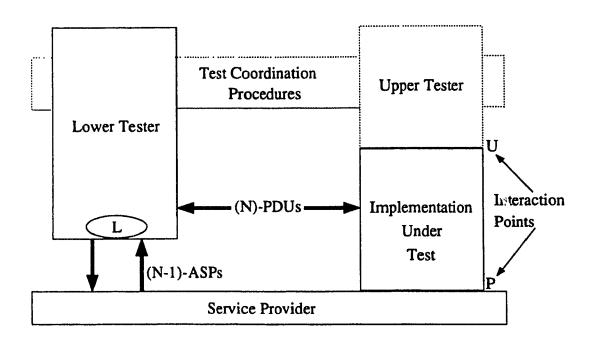

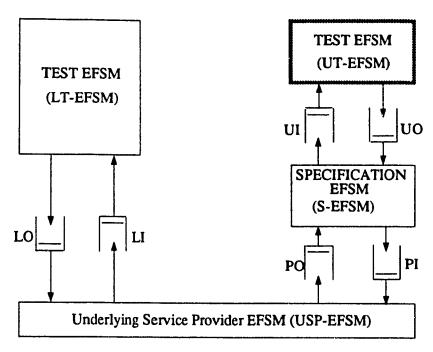

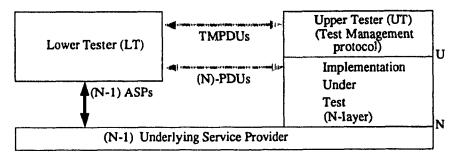

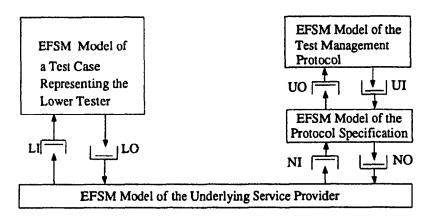

A test verification system is derived from the architectural basis of the test case by representing the Lower Tester as an extended finite state machine (EFSM), substituting the implementation under test by the EFSM model of the corresponding protocol specification, representing the Upper Tester as an EFSM model derived either from the test case or from the test management protocol depending on the test architecture, modeling the input/output service specification of the underlying service provider as an EFSM, and representing each interaction point between two EFSMs in the test architecture by two FIFO channels. Algorithms are presented to derive EFSMs from the Estelle specifications of protocols and Tree and Tabular Combined Notation (TTCN) descriptions of test cases.

The model of a test verification system represents the global state space of the verification system with a set of atomic predicates associated with each global state, such that a global state's atomic predicates evaluate to true in that state. An algorithm, based on the well known reachability analysis technique, is presented to derive the global state space of a test verification system.

Four types of test case safety properties are defined: transmission safety, reception safety, synchronization safety, and verdict safety. The first two types of safety properties are common to all communication systems and the latter two are specific

to protocol test systems. The liveness property of a test case is based on the idea that the test case behavior leading to a *Pass* test verdict fulfills the test *purpose*. We have proposed a set of notations to represent the safety and liveness properties as formulas in branching time temporal logic.

Test case properties are verified on the model of a test verification system by using a model checking algorithm. A methodology is also discussed to verify multiplexing test cases used in a multi-party test environment.

The verification methodology is applied to three test cases: one Remote Single-layer (RS) architecture based test case for an Association Control Service Element (ACSE) protocol, one Coordinated Single-layer (CS) architecture based single connection test case for a Class 2 transport protocol, and a CS architecture based multiplexing test case for the same Class 2 transport protocol.

#### **ACKNOWLEDGEMENTS**

I take this opportunity to thank many people and organizations for their direct and indirect technical, financial, logistic, and moral supports.

First of all, I express my deepest gratitude to my thesis supervisor Dr. Bencet Sarikaya for his valuable guidance, widespread encouragement, and instant willingness to spend time on my research work. Dr. Sarikaya's highly enthusiastic and thought provoking technical suggestions were a prominent factor in bringing this research to its present shape in a quite reasonable amount of time.

I am thankful to Prof. Phoivos Ziogas, the late Chairman of our Department, for his moral and logistic supports at some of the critical moments in the course of my work.

My most sincere thanks are due to the Canadian Commonwealth Fellowship Agency for providing me all kinds of financial supports for five years. I also gratefully acknowledge a partial financial support from the Natural Sciences and Engineering Research Council of Canada.

I sincerely thank Anindya, Basudeb, Deb, Gurinder, Kostas, Piyu, Rajveer, Ramesh Ahooja, Shesh, and many others for their innumerable supports.

I specially thank Sylvie for inspiring and helping me in many ways, in addition to taking the pain of thoroughly reading a part of this thesis.

Last but not the least, I express my whole hearted indebtedness to my mother, elder brother and sister, and my late father whose constant inspirations during my childhood guided me towards being educated.

#### TABLE OF CONTENTS

| LIST OF ABBREVIATIONS                                    | X   |

|----------------------------------------------------------|-----|

| LIST OF FIGURES                                          | xii |

| CHAPTER 1: INTRODUCTION                                  | 1   |

| 1.1 Protocol Engineering Life-cycle                      | 1   |

| 1.2 Conformance Testing and Test Case Verification       | 4   |

| 1.2.1 Conformance Testing                                | 4   |

| 1.2.2 Test Case Verification                             | 5   |

| 1.3 Previous Work on Test Case Verification              | 6   |

| 1.4 Model Checking                                       | 7   |

| 1.5 Original Contributions of this Thesis                | 9   |

| 1.6 Organization of the Thesis                           | 10  |

| CHAPTER 2: EXTENDED FINITE STATE MACHINE MODELS          | 14  |

| 2.1 Extended Finite State Machine                        | 15  |

| 2.2 EFSM Model of an Estelle Specification               | 16  |

| 2.2.1 Estelle Specification                              | 16  |

| 2.2.2 Translation of an Estelle Specification to an EFSM | 27  |

| 2.3 EFSM Model of a TTCN Test Case                       | 41  |

| 2.3.1 TTCN Specification                                 | 41  |

| <b>2.3.1.1</b> Overview                                  | 41  |

| 2.3.1.2 Declarations                                     | 42  |

| 2.3.1.3 Constraints                                      | 42  |

| 2.3.1.4 Dynamic Behavior                                 | 56  |

| 2.3.2 Translation of a TTCN Test Case to an EFSM         | 61  |

| 2.4 Input/Output Diagrams                                | 67  |

| 2.4.1 I/O Diagram Representation of Events in ASN.1      | 69  |

| 2.4.2 I/O Diagram Representation of Events in Estelle    | 71  |

| 2.4.3 I/O Diagram Representation of Events in TTCN       | 72  |

| 2.5 Complexity Analysis                              | 74  |

|------------------------------------------------------|-----|

| 2.5.1 Complexity for a TI'CN Test Case               | 74  |

| 2.5.2 Complexity for an Estelle Specification        | 74  |

| CHAPTER 3: TEST VERIFICATION SYSTEMS (TVS)           | 77  |

| 3.1 Test Architectures                               | 78  |

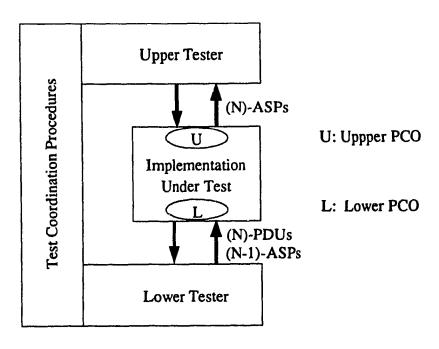

| 3.1.1 Local Single-layer Test Architecture           | 79  |

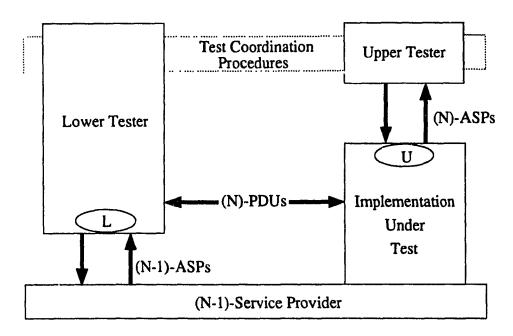

| 3.1.2 Distributed Single-layer Test Architecture     | 80  |

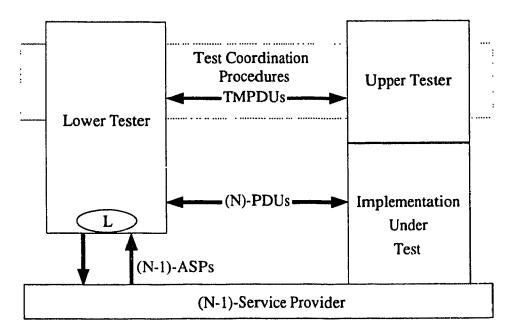

| 3.1.3 Coordinated Single-layer Test Architecture     | 81  |

| 3.1.4 Remote Single-layer Test Architecture          | 82  |

| 3.1.5 Comparison of LS, DS, CS, and RS architectures | 83  |

| 3.2 Test Verification System                         | 84  |

| 3.3 Model Generation                                 | 88  |

| 3.3.1 Reachability Analysis Algorithm                | 88  |

| 3.3.1.1 Predicate Evaluation                         | 91  |

| 3.3.1.2 Perturbation                                 | 92  |

| 3.3.2 Model Generation Algorithm                     | 96  |

| 3.4 Complexity Analysis                              | 99  |

| CHAPTER 4: MODEL CHECKING FOR TVS                    | 101 |

| 4.1 Temporal Logic                                   | 101 |

| 4.2 Safety Properties                                | 104 |

| 4.3 Liveness Property                                | 106 |

| 4.4 Verification of Test Case Properties             | 109 |

| 4.4.1 Evaluation of Until Operator                   |     |

| 4.4.2 Evaluation of → Operator                       |     |

| 4.4.3 Evaluation of SEQ Operator                     |     |

| 4.4.4 Model Checking Algorithm                       |     |

| 4.4.5 Complexity Analysis                            |     |

| CHAPTED & DC TEST CASE VEDICATION                    | 117 |

|                                            | 5.1 ACSE Specification                                    | 118 |

|--------------------------------------------|-----------------------------------------------------------|-----|

|                                            | 5.2 Test Case                                             | 126 |

|                                            | 5.3 Service Provider                                      | 129 |

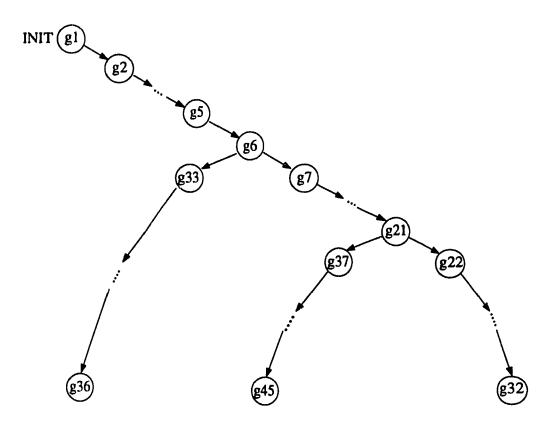

|                                            | 5.4 Global State Space                                    | 129 |

|                                            | 5.5 Verification of Test Case Properties                  | 132 |

|                                            | 5.5.1 Safety Properties of the Test Case                  | 132 |

|                                            | 5.5.2 Liveness Property of the Test Case                  | 133 |

|                                            | 5.6 Generation of an Upper Tester                         | 133 |

| CH.                                        | APTER 6: CS TEST CASE VERIFICATION                        | 135 |

|                                            | 6.1 Transport Protocol, TMP, and Service Provider         | 136 |

|                                            | 6.1.1 Class 2 Transport Protocol Specification            | 136 |

|                                            | 6.1.2 Service Provider                                    | 139 |

|                                            | 6.1.3 Test Management Protocol                            | 140 |

|                                            | 6.2 Single Connection Test Case                           | 144 |

|                                            | 6.2.1 EFSM Model of the Test Case                         | 144 |

|                                            | 6.2.2 Model Generation                                    | 148 |

|                                            | 6.2.3 Verification of Safety and Liveness Properties      | 150 |

| CH.                                        | APTER 7: VERIFICATION OF PARALLEL TEST CASES              | 154 |

|                                            | 7.1 Parallel Test Architecture                            | 154 |

|                                            | 7.2 Parallel Test Case Verification                       | 156 |

|                                            | 7.3 Example of Verifying a Parallel Test Case             | 159 |

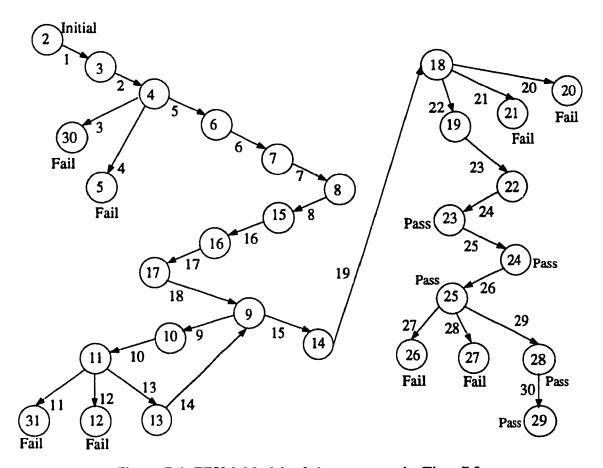

|                                            | 7.3.1 EFSM Model of the Test Case                         | 160 |

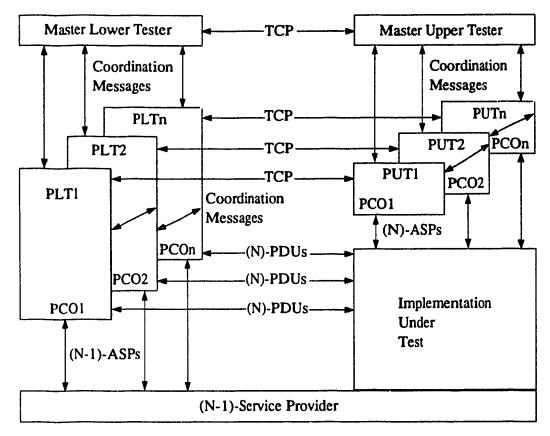

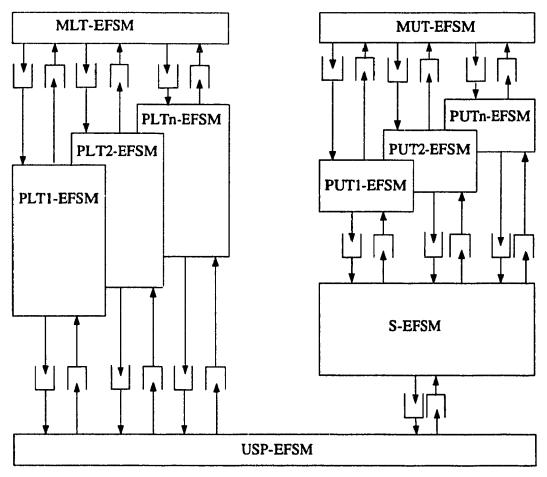

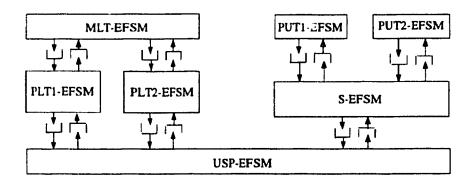

|                                            | 7.3.2 Test Verification System for the Parallel Test Case | 165 |

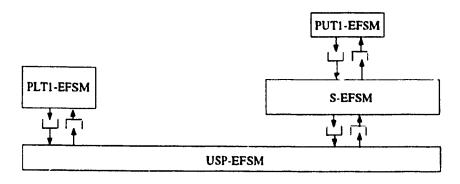

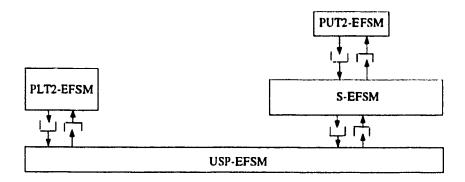

|                                            | 7.3.3 Model Generation                                    | 166 |

|                                            | 7.3.4 Verification of Safety and Liveness Properties      | 167 |

| CHAPTER 8: CONCLUSIONS AND FUTURE RESEARCH |                                                           |     |

|                                            | 8.1 Conclusions                                           | 173 |

|                                            | 8.7 Future Decearch                                       | 170 |

| 8.2.1 Implementation of the Verification System     | 179 |

|-----------------------------------------------------|-----|

| 8.2.2 Verifying Invalid Behavior Test Cases         | 180 |

| 8.2.3 Piecewise Test Verification                   | 181 |

| 8.2.4 Test Generation Using Model Checking Approach | 182 |

| REFERENCES                                          | 183 |

| APPENDIX 1                                          | 189 |

| APPENDIX 2                                          | 192 |

| APPENDIX 3                                          | 214 |

| APPENDIX 4                                          | 226 |

#### LIST OF ABBREVIATIONS

ACSE Association Control Service Element

ADT Abstract Data Type

AK Acknowledgement ASE Application Service Element ASN.1 Abstract Syntax Notation 1 ASP Abstract Service Primitive ATS Abstract Test Suite BNF Backus-Naur Form BTL Branching Time Logic CASE Common Application Service Element CC Connect Confirm CCITT International Consultative Committee for Telephone and Telegraph CCS Calculus of Communicating Systems CM Coordination Messages **CP** Coordination Point CR Connection Request CS Coordinated Single-layer DC Disconnect Confirm DR Disconnect Request DS Distributed Single-layer DT Data TPDU EFSM Extended Finite State Machine FDT Formal Description Technique FIFO First In First Out FTAM File Transfer and Access Management IOD Input/Output Diagram

ISO International Organization for Standardization

**IUT** Implementation Under Test

#### LOTOS LOTOS

LS Local Single-layer

LT Lower Tester

MHS Message Handling System

MTC Main Test Component

OSI Open Systems Interconnection

**OTH OTHERWISE**

PLT Parallel Lower Tester

PUT Parallel Upper Tester

PCO Point of Control and Observation

PDU Protocol Data Unit

PICS Protocol Implementation Conformance Statement

PIXIT Protocol Implementation eXtra Information for Testing

PTC Parallel Test Compoment

RS Remote Single-layer

S-EFSM Specification EFSM

SDL System Description Language

T-EFSM Test EFSM

TMP Test Management Protocol

TMPDU Test Management Protocol Data Unit

TPDU Transport Protocol Data Unit

TTCN Tree and Tabular Combined Notation

TVS Test Verification System

UT Upper Tester

relop relational operator

# List of Figures

| <b>Figure</b> |                                                            | Page |

|---------------|------------------------------------------------------------|------|

| Figure 1.     | An Outline of Test Case Verification by Model Checking     | 11   |

| Figure 2.     | A modular specification                                    | 17   |

| Figure 2.     | 2 A hierarchical task structure                            | 18   |

| Figure 2.     | A hierarchy of tasks created after an initialize statement | 22   |

| Figure 2.     | Task structure before the initialize statements            | 40   |

| Figure 2.     | Task structure after the attach statements                 | 40   |

| Figure 2.     | (a) Declaration of PDU_A                                   | 44   |

|               | (b) declaration of constraint C0                           | 45   |

| Figure 2.     | Declaration of constraint C1                               | 45   |

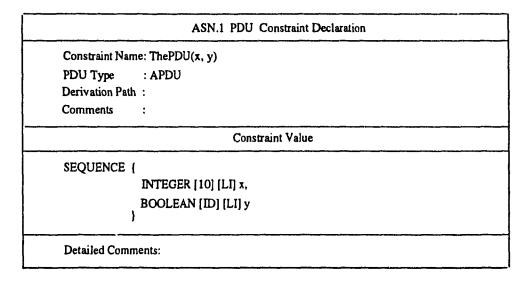

| Figure 2.     | An example of a parameterized constraint                   | 46   |

| Figur > 2.9   | An instantiation of the constraint in Fig. 2.8             | 46   |

| Figure 2      | 0 An example of static constraint chaining                 | 47   |

| Figure 2.     | 1 An example of dynamic constraint chaining                | 49   |

| Figure 2.     | 2 An example of an ASN.1 constraint                        | 53   |

| Figure 2.1    | 3 Test case dynamic behavior table                         | 57   |

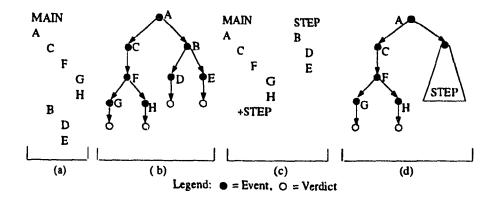

| Figure 2.1    | 4 (a) A test case                                          | 61   |

|               | (b) a test case in tree notation                           | 61   |

|               | (c) a structured test case containing a test step          | 61   |

|               | (d) a structured test case in tree notation                | 61   |

| Figure 2.1    | 5 (a) Structure of an internal node                        | 69   |

|               | (b) structure of a leaf node                               | 69   |

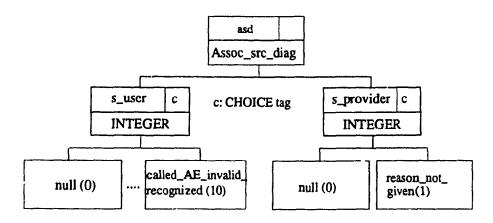

| Figure 2.1    | 6 An example of representing a CHOICE construct            |      |

|               | as an I/O diagram                                          | 70   |

| Figure      |                                                                 | Page |

|-------------|-----------------------------------------------------------------|------|

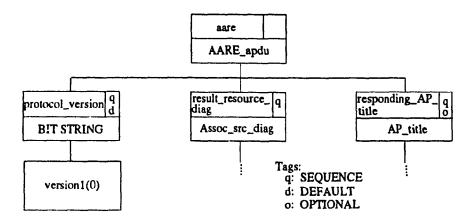

| Figure 2.17 | An example of representing a SEQUENCE construct                 |      |

|             | as an I/O diagram                                               | 70   |

| Figure 2.18 | An Estelle ConnectReq as an I/O Diagram                         | 72   |

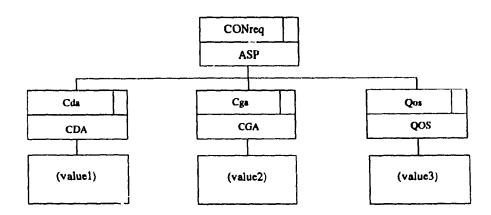

| Figure 2.19 | A CONreq ASP declaration in tabular notation                    | 73   |

| Figure 2.20 | I/O Diagram representation of the CONreq ASP in Fig. 2.19       | 73   |

| Figure 3.1  | The Local Single-layer Test Architecture                        | 79   |

| Figure 3.2  | The Distributed Single-layer Test Architecture                  | 80   |

| Figure 3.3  | The Coordinated Single-layer Test Architecture                  | 82   |

| Figure 3.4  | The Remote Single-layer Test Architecture                       | 83   |

| Figure 3.5  | Test Verification Systems corresponding to LS, DS, CS,          |      |

|             | and RS architectures                                            | 87   |

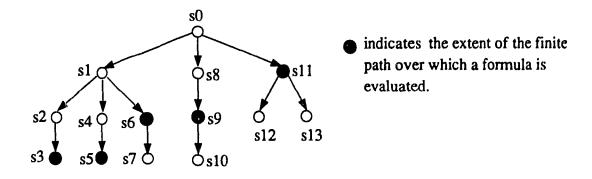

| Figure 4.1  | An example to compute last(f)                                   | 108  |

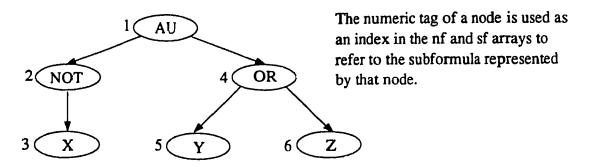

| Figure 4.2  | Tree representation of a formula $f = (AU(NOT X)(OR YZ)) \dots$ | 115  |

| Figure 5.1  | RS Test Architecture                                            | 117  |

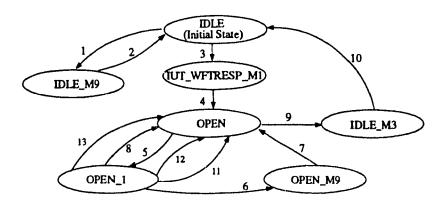

| Figure 5.2  | Test Verification System for the RS Architecture                | 118  |

| Figure 5.3  | A test case dynamic behavior                                    | 127  |

| Figure 5.4  | USP-EFSM, a simple model of the Presentation                    |      |

|             | Service used by an ACSE protocol                                | 129  |

| Figure 5.5  | The correct version of the test case in Fig. 5.3                | 130  |

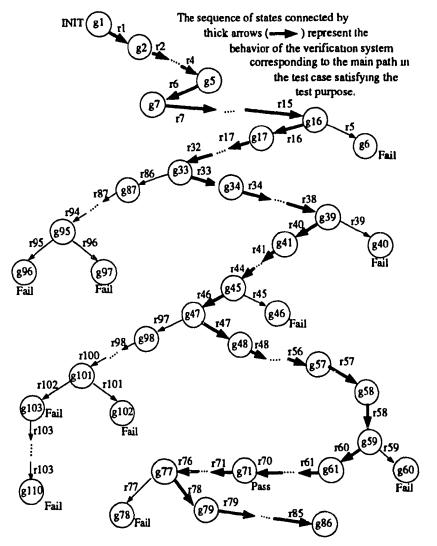

| Figure 5.6  | Structure of the global state space of the TVS in Fig. 5.2      | 131  |

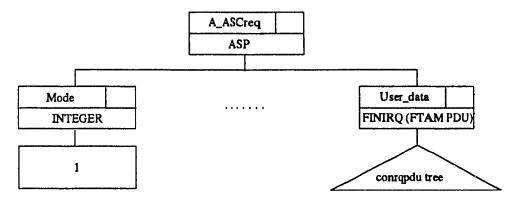

| Figure 5.7  | IOD representation of A_ASCreq message                          | 132  |

| Figure 5.8  | Dynamic generation of UT behavior                               | 134  |

| Figure     |                                                            | Page |

|------------|------------------------------------------------------------|------|

| Figure 6.1 | Coordinated Single-layer (CS) test architecture            | 135  |

| Figure 6.2 | The Test Verification System for the CS architecture       | 135  |

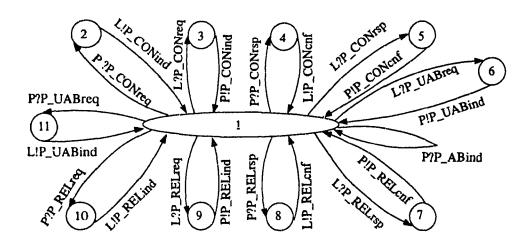

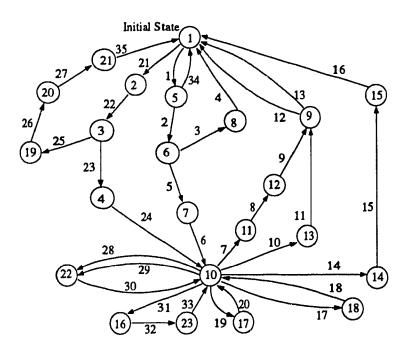

| Figure 6.3 | Class 2 Transport Protocol Specification                   | 137  |

| Figure 6.4 | Underlying Service Provider of the Transport Protocol      | 138  |

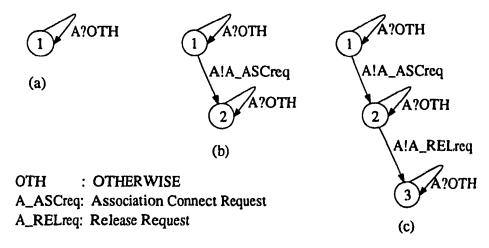

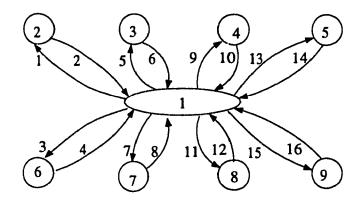

| Figure 6.5 | A part of the Test Management Protocol                     | 142  |

| Figure 6.6 | A CS architecture based single connection test case        | 145  |

| Figure 6.7 | EFSM representation of the test case in Fig. 6.6           | 146  |

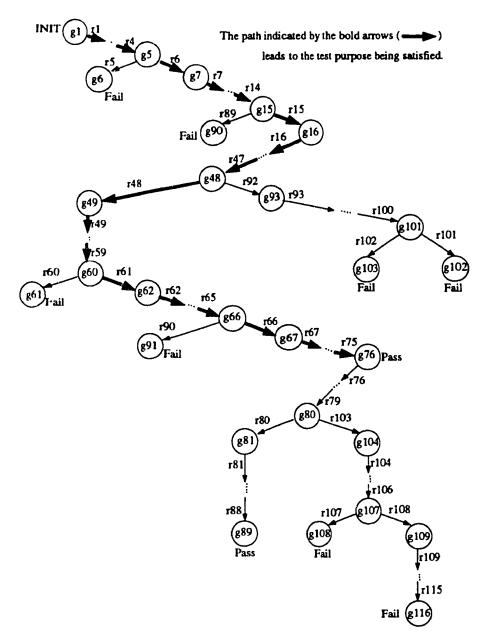

| Figure 6.8 | Structure of the global state space                        | 148  |

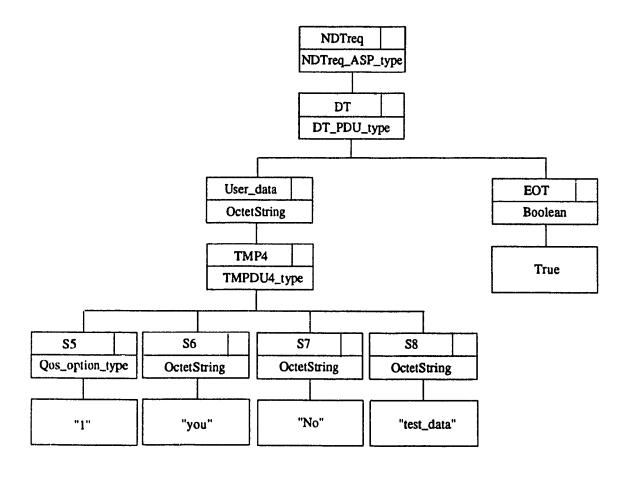

| Figure 6.9 | Representation of an event in a queue as an I/O diagram    | 149  |

| Figure 7.1 | A Multi-party Test Architecture                            | 155  |

| Figure 7.2 | A Test Verification System for parallel test architectures | 157  |

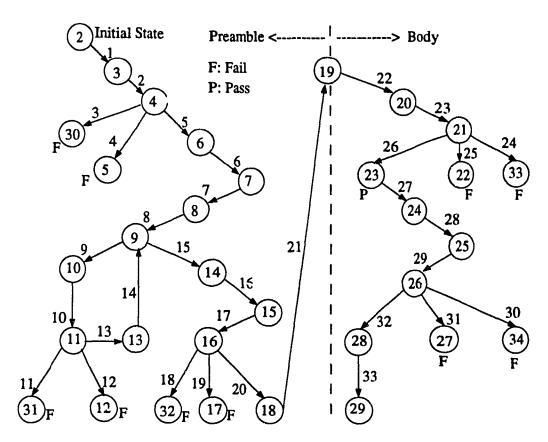

| Figure 7.3 | A CS architecture based multiple connection test case      | 162  |

| Figure 7.4 | EFSM Model of the test case in Fig. 7.3                    | 163  |

| Figure 7.5 | A TVS for the test case in Fig. 7.3                        | 165  |

| Figure 7.6 | A TVS for first connection in Fig. 7.3                     | 166  |

| Figure 7.7 | A TVS for second connection in Fig. 7.3                    | 166  |

| Figure 7.8 | Structure of the global state space                        | 167  |

## **CHAPTER 1**

## INTRODUCTION

The role of computer networks in interconnecting a set of geographically distributed computer systems for collecting, processing, and exchanging information has been vital to the technological and administrative developments in the present day society. Communication protocols are key to the operation of a network of computer systems. Therefore, there is significant ongoing research and development in methodologies for specification, verification, and conformance testing of data communication protocols.

The International Organization for Standardization (ISO) and the International Consultative Committee for Telephones and Telegraph (CCITT) are the two world bodies working towards the standardization of protocol specifications, data type definitions for information exchange, and test case specifications using Formal Description Techniques (FDT). Examples of standardized formal description techniques are LOTOS [IS8807], Estelle [IS9074], and SDL [Z100] for specifying protocols, Abstract Syntax Notation One (ASN.1) [IS8824] for specifying the format of data exchanged between two computing entities, and the Tree and Tabular Combined Notation (TTCN) [ISO 9646] for test case specifications.

## 1.1 Protocol Engineering Life-cycle

The four steps in the protocol development process, called the *Protocol Engineering Life-cycle*, are design of a protocol specification, validation and verification of the specification, generation of an implementation from the specification, and conformance testing of the implementation [NASA 92a].

Producing a formal specification of a protocol is a human design process and it largely involves intuition. Since a human design process is error-prone, the

resulting protocol specification needs to be validated and verified. On one hand, protocol validation refers to the detection of some well known types of errors in the specification, such as unspecified reception errors, blocking receptions errors, deadlock errors, livelock errors, and synchronization errors [ZAFI 80]. On the other hand, protocol verification refers to whether the protocol specification meets the required service specifications [SAB 88].

The first automated protocol validation technique is duologue-matrix analysis [ZAFI 78, WEZA 78]. A duologue matrix is a notation to represent interaction sequences between two interacting graphs. This technique addresses the validation of a protocol between a pair of asynchronous processes by defining a number of fundamental rules of protocol behavior, which are incorporated in a validation function that can be applied to an interaction sequence to determine whether the sequence contains errors. By applying the validation function to all possible interaction sequences defined by a protocol, design errors in the protocol can be detected. The limitations of the duologue-matrix analysis technique are that the interacting processes must return together to their initial states after a finite number of interaction steps and that the theory only addresses two-process protocols.

The most widely studied protocol validation technique is reachability analysis [WEST 78], which consists of two steps. In the first step, a global state space is generated from the multiprocess finite state description of a protocol using a state perturbation technique. In the second step, the global state space is analyzed to detect the presence of some well-defined errors such as reception errors, deadlock errors, livelock errors, and channel overflow errors. Some other state space exploration methods controlling the size of the global state space can be found in [GOYU 84, VUHU 87, GOHA 85, LU 86, HOLZ 87, WEST 87, ZHBO 87]. A state space exploration technique for protocol validation is particularly attractive because it very easily lends itself to complete automation requiring only a formal definition of a

protocol in state diagram notation.

Over the last decade, a number of protocol verification techniques have been reported in the literature. For protocols specified in programming languages, program verification techniques are used. One can check that a protocol provides a desired service specified using first-order logic or a first-order version of temporal logic. However, program verification usually requires some insightful proofs that are hard to automate [HAOW 83]. Protocol verification using symbolic execution [BRJO 78] is a technique combining program verification and reachability analysis. It has the advantage that a protocol is interpreted by the verifier in essentially the same way as in reality. Therefore, it is possible to verify protocol behavior affected by the actual contents of messages rather than merely by its arrival.

In [SAB 88] an algorithmic procedure has been presented to verify whether a protocol provides a desired service. In this methodology, a protocol is described as a collection of synchronously interacting processes similar to the Communicating Sequential Processes (CSP) language [HOAR 78]. The safety behavior of a protocol is described using Finite State Machines (FSM), whereas the liveness behavior is described using propositional temporal logic. For checking the safety part of the specification, the FSM descriptions of all the processes are composed using a reachability procedure [ZAFI 83] and for the liveness property, the verification methodology checks whether the protocol gets into a set of states in which it will not provide the intended service.

A model checking approach based on branching time temporal logic is another technique used in protocol verification [FRV 86, CES 86]. In a later part of this chapter, we present an outline of the model checking approach.

For any practical use of a protocol specification, an executable implementation must be generated from the specification. Like the production of a protocol specification, generation of an implementation from a specification is also a human design

process and is error-prone. A practical way of determining whether an implementation behaves as stated in its specification in representative instances of communications, that is, whether the implementation conforms with its specification, is to test the implementation with a set of test cases. The process of testing an implementation to determine its conformance with the specification is known as *conformance testing* [ISO 9646]. From a software engineering view point, conformance testing generates confidence in the implementation.

#### 1.2 Conformance Testing and Test Case Verification

#### 1.2.1 Conformance Testing

The process of conformance testing starts with the test design phase in which an abstract test suite is developed. A test suite is a collection of test cases, such that each test case is used to test one protocol feature. There are two main approaches to developing a test suite:

- human design of test suites,

- semi-automatic design of test suites based on formal protocol specifications.

Conventionally, a test suite is designed by a test designer or a team of designers having expertise in the protocol standard as well as in the conformance testing framework and methodology [ISO 9646]. Such a design is a complicated and an error-prone process. Since software testing is a practical way of building confidence in software systems, a lot of research is being carried out on automatic test generation techniques. However, software testing in general and protocol testing in particular have not yet reached a state where a readily usable test suite can be automatically generated from a specification. Presently, therefore, test suites are manually designed [NCC 88, PTT 90] and many techniques on automatic test generation are being explored [UYDA 86, SILE 89, DSU 90].

The behavior of a protocol providing a set of communication functions is marked by sequences of events appearing at its service access points and composed of input events to the protocol and the responses of the protocol in the form of output events. From the conformance point of view, the purpose of a test case is to check whether the implementation satisfies the specification requirements with respect to a protocol function. A test case does this checking by applying sequences of input events, allowed by the specification, to the implementation and comparing the responses from the implementation with the expected events stated in the protocol specification. At the end of the testing process, a test case assigns a test verdict indicating whether the implementation passes or fails the test, or behaves in an inconclusive manner. If the observed behavior of the implementation is allowed by the protocol specification and the test purpose is satisfied, then the test case assigns a Pass verdict to the implementation. If the behavior of the implementation is not allowed by the protocol specification, then the test case assigns a Fail verdict. However, if the behavior of the implementation is allowed by the specification, but the purpose of testing is not satisfied, then the test case assigns an Inconclusive verdict.

#### 1.2.2 Test Case Verification

Large size, nondeterministic events, combination of a large number of parameters, and communications among the modules of a protocol specification make the behavior of a communication protocol very complex and difficult to comprehend. Thus, manually designing a set of test cases to test an implementation of the specification becomes a nontrivial task. Those human designed test cases may contain several design errors. If erroneous test cases are used to test an implementation, the result of the testing process cannot be relied upon to decide the conformance of an implementation with its specification. Thus, it is essential to have a methodology to verify the correctness of test cases against the corresponding protocol specification.

The following are the issues contributing to the difficulties in verifying test cases: First, in general, test cases and protocols are specified in different formal description techniques, which use different notations to define data types and different behavioral semantics of their operations. For example, according to ISO's standardization framework, test cases are specified in TTCN, whereas a protocol can be specified in LOTOS, Estelle, or SDL.

Second, there are architectural differences between a protocol specification and the test cases. For example, because of the layered nature of OSI protocols, a protocol specification is written in such a way that it interacts with its user and service provider through two well-defined service access points, whereas depending on the test architecture [ISO 9646], a test case can interact with an implementation using only one service access point or two service access points one of which may be away from the implementation.

Third, the correctness of a Pass test verdict is directly coupled with the test purpose being satisfied.

Fourth, the correctness of a test behavior depends not only on the protocol specification, but also on the Test Management Protocol in some test architectures and on the service provider used as a communication medium between a test entity and the implementation under test.

Fifth, testing the multiple connection capability of an implementation involves parallelism in a test case, which adds an extra dimension to the test case verification problem.

Therefore, verifying a test case by comparing the behavior of the test case with that of a protocol specification is not a straightforward task.

#### 1.3 Previous Work on Test Case Verification

The idea of test case verification is relatively new and there is very little published

work on this topic. In the following, we summarize some early approaches to test case verification.

In the first approach [NASA 90b], first both the LOTOS specification of a protocol and the TTCN specification of a test case are translated into a common semantic model, an Extended Finite State Machine (EFSM), with first-in first-out (FIFO) queues modeling the communication mechanism between the test case and the protocol specification. Next, an interleaved symbolic execution mechanism is used to compare the behavior of the test case EFSM with the protocol specification EFSM. A limitation of this approach is that only some static aspects of a test case can be compared with the behavior of a protocol specification and dynamic aspects due to timeouts cannot be verified.

In the second approach [DUBO 90], the verification process consists of two steps. First, a TTCN test case is translated into a LOTOS specification to eliminate the language differences. Second, a Test and Trace Analysis (TETRA) tool, based on a LOTOS interpreter [LOGR 88], takes the LOTOS specification of the test case and that of the protocol specification as inputs and computes their parallel composition by tracing the executable paths in the two specifications. The concerns expressed about the tool are its large space and long verification time requirements. Moreover, this technique does not address the architectural difference between a test case and a protocol specification.

## 1.4 Model Checking

In the traditional approach to verification of concurrent systems, the proof that a concurrent system meets its specification is constructed by hand using various axioms and inference rules in a deductive system [HAIL 82, OWLA 82]. Theorem provers are not of much help in verifying concurrent systems, because the task of proof construction is in general quite tedious.

It is argued that proof construction is unnecessary in the case of finite state concurrent systems [CES 86], and can be replaced by a *model checking* approach which mechanically determines if a system satisfies a property expressed in branching time temporal logic. Therefore, from an automation point of view, the model checking approach to system verification has gained diverse interests in the last decade [FRV 86, CES 86].

The basic approach to verifying whether a concurrent system satisfies a property by using the model checking concept contains the following three steps.

- The concurrent system is expressed as a finite state machine and a set of

propositions evaluating to true is attached to each state. Such a finite state

machine with a set of propositions attached to each state is called a model of

the concurrent system.

- The properties to be verified on the concurrent system are expressed as formulas in branching time temporal logic.

- An algorithm, called a *model checker*, is used to verify whether the model satisfies the properties expressed as temporal formulas.

There are two kinds of properties one usually wants a concurrent system to satisfy:

- Safety properties, which state that something bad never happens—that is, the system never enters an unacceptable state.

- Liveness properties, which state that something good eventually does happen—that is, the system eventually enters a desirable state.

Some well known examples of safety properties of concurrent systems are partial correctness, absence of deadlock, and mutual exclusion. A liveness property that has received a lot of formal treatment is program termination. However, program termination is not a good thing to happen to every computing system. For example, an operating system should never terminate (crash). For such systems, other kinds of liveness properties are important, for example:

- Each request for service will eventually be answered.

- A message will eventually reach its destination.

- A process will eventually enter its critical section.

The nature of safety and liveness properties of a system depends on the nature of the computing system. Therefore, to verify the correctness of test cases one must define safety and liveness properties applicable to test systems.

## 1.5 Original Contributions of this Thesis

The contribution of this thesis is to develop a methodology to verify human designed test cases used to check the conformance of a protocol implementation with its formal specification. In the following, we outline a set of individual contributions which, when combined together, give rise to a test verification methodology.

In order to be able to compare the behavior of a test case with that of a protocol specification, the first barrier is due to the use of different languages in specifying protocols and test cases. Therefore, to eliminate their syntactic and semantic differences, a common representation notation, called an Extended Finite State Machine (EFSM), is defined and algorithms are presented to translate protocols specified in Estelle and test cases specified in TTCN into EFSMs.

The notion of control and observation is crucial to black-box testing. Since every test case is based on some test architecture, which defines the control and observation capability of a test case, it is important to take the architectural basis of a test case into account while verifying the test case. Therefore, we define the notion of a Test Verification System to account for the interconnection structure among the entities of a test architecture through service provider, points of control and observations, and other interaction points.

For a test verification system, we define a verification *model* representing the global behavior of the verification system and present an algorithm, based on reachability analysis, to generate a global state space from a test verification system.

To form a basis for verifying the correctness of a test case, we identify four classes of test case safety properties and one liveness property, and express them as formulas in branching time temporal logic. The four classes of safety properties are transmission safety, reception safety, synchronization safety, and verdict safety. The safety properties are designed to reflect some general characteristics of event-based communications and some particular characteristics of protocol testing.

The liveness property is designed to establish a relation between the test purpose and the Pass verdict. Presently, a test purpose is expressed in a natural language, which makes it difficult to verify whether the test case satisfies the test purpose. Therefore, we propose a notation in temporal logic to express what we call basic test purposes, which can be combined to construct larger test purposes. The liveness property is designed to verify that a test case behavior satisfying the test purpose ends in a Pass verdict.

We present a model checking algorithm to verify the test case properties on the model derived from the test verification system.

Our test verification methodology is applicable to all the ISO/CCITT test case and protocol specification languages such as TTCN, LOTOS, Estelle, and SDL and to all test architectures.

## 1.6 Organization of the Thesis

A pictorial description of the model checking methodology used to verify test cases is shown in Fig. 1.1. The thesis is organized according to the modular structure of the verification methodology.

Figure 1.1 An Outline of Test Case Verification by Model Checking.

Chapter 2 contains four sections. In the first part, we define an Extended Finite State Machine (EFSM), which serves as a common representation notation for all the operational entities, such as the test case entities, the protocol specification, the Test Management Protocol, and the service provider, in a test verification system. In the second part, the syntax and semantics of Estelle constructs and an algorithm to translate an Estelle specification to an EFSM are presented. In the third part, we present a detailed description of the TTCN test specification language and an algorithm to translate a TTCN test case to an EFSM. In the fourth part, a notation called Input-Output Diagram (IOD) is defined to represent the Abstract Service Primitives (ASP)

and Protocol Data Units (PDU) exchanged among the EFSMs in a test verification system. The IOD representations of ASPs and PDUs are used to refer to the values of the fields contained in them while evaluating a boolean condition involving those fields.

Chapter 3 contains three sections. In the first part, we discuss various test architectures used in conformance testing. In the second part, we define the notion of a test verification system and derive a test verification system from each of the test architectures. In the third part, we present an algorithm to generate a state space representing the global behavior of a test verification system and present a methodology to attach a set of propositions with each global state.

Chapter 4 is devoted to model checking and consists of four parts. In the first part, we present the branching time temporal logic formalism. In the second part, the safety and liveness properties of a test case are expressed as branching time temporal logic formulas. In the third part, we model basic test purposes as temporal formulas and present a rule to compose basic test purposes into larger test purposes and express the liveness property as a temporal formula. A model checking algorithm, to verify test case properties on the model generated from a test verification system, is presented in the fourth part of Chapter 4.

In Chapter 5, we illustrate the verification of a test case based on the Remote Single-layer test architecture. The first three sections describe an Association Control Service Element (ACSE) protocol, a test case, and a service provider. A global state space is generated in the fourth section. Properties of the test case are verified in the fifth section. Generation of an Upper Tester is discussed in the last section.

Chapter 6 contains three sections. In the first part, a Class 2 Transport Protocol, a service provider of a transport protocol entity, and a Test Management Protocol used in testing a Class 2 Transport Protocol implementation are presented. In the second part, an example of verifying a test case, designed to test a Class 2 Transport Protocol

implementation in the Coordinated Single-layer test architecture, is presented.

In Chapter 7, a methodology to verify multiple connection test cases is outlined. This chapter contains three parts. In the first part, a parallel test architecture is discussed. In the second part, verification of a multiple connection test case is formalized using the verification technique for a single connection test case. An example of the verification of a multiple connection test case is presented in the third part.

In Chapter 8, contributions of the research described in this thesis are summarized.

In addition, possible extensions of the verification methodology are discussed.

## **CHAPTER 2**

# **EXTENDED FINITE STATE MACHINE MODELS**

The use of Formal Description Techniques (FDTs) in the specification of communication protocols has received much attention, since such techniques allow a more systematic approach for protocol verification, validation, implementation, and testing compared to the traditional use of natural languages in protocol specifications. The three FDTs presently considered in this area are Estelle [IS9074], LOTOS [IS8807], and SDL [Z100]. The Tree and Tabular Combined Notation (TTCN) [ISO 9646] is the ISO's language for specifying a test suite for testing an implementation's conformance with its specification.

Estelle is based on a finite state machine model, which is extended by Pascal data types, expressions, and statements. The Estelle specification of a protocol may consist of a large nur. ber of interconnected finite state machine modules, which communicate among themselves through FIFO channels.

LOTOS, a process algebraic specification language, is a combination of Milner's Calculus of Communicating Systems (CCS) [MILN 80] formalism for behavior description and Abstract Data Types (ADTs) [EHMA 85] for data description. A set of composition rules is used to derive larger specifications from the primitive notions of events and processes.

SDL, like Estelle, is also based on an extended finite state machine model. It is largely oriented towards a graphical representation. Abstract data types are used to define data in an SDL specification.

In the TTCN test specification language, constrained events and subtrees constitute the building blocks in the design of the behavior part of a test case. Data in a test case are described using both a tabular notation and the Abstract Syntax Notation 1 (ASN.1) [IS882-4].

For verifying a TTCN test case against a protocol specified in one of the FDTs, it is essential to remove the syntactic and semantic barriers between the test case and the protocol specification. Therefore, in this chapter we define an Extended Finite State Machine (EFSM), a common notation for representing test cases and protocol specifications and present systematic procedures to translate them to the common notation. In this thesis, the scope of test case verification is limited to the Estelle specification language. In Section 2.1, we define an EFSM. A brief overview of Estelle features and rules to translate an Estelle specification to an EFSM are presented in Section 2.2. In Section 2.3, we discuss the TTCN specification language and present an algorithm to translate a TTCN test case to an EFSM. In Section 2.4, we define 1/O diagrams, which provide a notation for information exchange among the EFSMs.

#### 2.1 Extended Finite State Machine (EFSM)

We define a communicating EFSM to be a 9-tuple,

$$\mathsf{F} = \langle S, S_t, V, R, s_{init}, Z, h_0, C_I, C_O \rangle,$$

where S is a finite set of states,  $S_t = \{(s, x) | s \in S \text{ and } x \text{ is a tag value} \}$  is a tagged set of states,  $V = \{v1, v2, ..., vn\}$  is a finite set of data variables of types  $\{t1, t2, ..., tn\}$ , respectively, R is a finite set of transitions to be defined in the following,  $s_{init} \in S$  is the initial state,  $Z \subseteq S$  is a set of final states,  $h_0$  is a set of assignment functions initializing some variables in V,  $C_I$  is a set of input FIFO channels, and  $C_O$  is a set of output FIFO channels.

The set V is expressed as  $V_1 \cup V_2$ , where  $V_1$  contains the variables locally used in the EFSM and  $V_2$  contains the variables used for communication with other EFSMs. The variables in  $V_1$  are of the conventional types such as integer, boolean, octetstring, etc., whereas the variables in  $V_2$  are of types  $\{IOD_1, IOD_2, ..., IOD_m\}$ , where each Input/Output Diagram (IOD) type is defined to hold a structured value to be sent to or received from another EFSM. The IOD types are defined in detail in Section 2.4.

A transition in an EFSM is a 6-tuple,  $r = \langle s, s', a, e, h, n \rangle$ , where s is the from state and s' is the to state of the transition, a is the action or event clause causing the transition to fire, e is the enabling predicate that must evaluate to true for the transition to fire, h is a set of value assignments to a subset of V, and n is the priority number of the transition in a set of choice transitions with the same from state.

An event in a transition can be one from the set {input, output, internal}, where the input and output events are known as external events and occur at some well defined interaction points through which two EFSMs communicate. An external event is characterized by three parameters: interaction point, direction ("?" denotes an input and "!" denotes an output), and the value (message) passed in the event. No channel or direction is associated with an internal event. For example, the event L!msg means a message msg is output to an interaction point L.

## 2.2 EFSM Model of an Estelle Specification

This section contains two parts. In the first part, we introduce the Estelle specification language and in the second part, we give rules to translate an Estelle specification to an EFSM.

## 2.2.1 Estelle Specification

Estelle [BUDE 87] is based on a finite state machine extended with Pascal data types and statements to describe actions. A number of notions generally applicable to distributed systems such as module, task, process, synchronous/asynchronous communication, interaction point, channel, nondeterminism, parallelism, etc. are found in Estelle. In the following, we explain each of them.

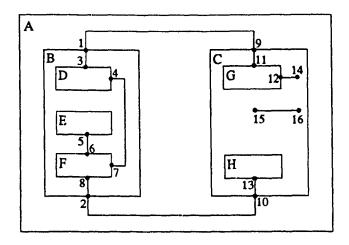

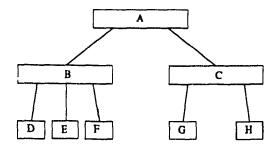

(A) Tasks: A distributed system specified in Estelle is viewed as a collection of communicating components called *module instances* or *tasks*. Each task has a number of input/output access points called *interaction points*, which are classified into two kinds: *external* and *internal*. For example, referring to Fig. 2.1, the distributed

system A consists of two concurrent tasks B and C. Task B is further refined into three concurrent tasks {D, E, F} and task C is refined into tasks {G, H}. The interaction points {1, 2,..., 13} are external, while points {14, 15, 16} are internal.

Figure 2.1 A modular specification in Estelle.

The behavior of a task is described in terms of a nondeterministic communicating extended finite state transition system. A task is active if its specification includes at least one transition; otherwise it is inactive. A task may have one of the following class attributes: systemprocess, systemactivity, process and activity. The tasks with systemprocess or systemactivity attributes are called system tasks. The class attributes of a collection of tasks represented in a structured manner in a specification determine the nature of parallelism in the specification as will be explained in the following.

(B) Structuring of Tasks: In a multitasking Estelle specification of a distributed system, two kinds of structuring principles are used: hierarchical structure and communication structure. The specification refinement principle in software engineering gives rise to a hierarchical structure of tasks as illustrated in Fig. 2.2, where the parent/child relationship is represented by edges and the root of the tree is the main task representing the specified system.

Figure 2.2 A hierarchical task structure.

Five attributing principles are observed within a hierarchy of tasks. (i) Every active task must be attributed. (ii) System tasks cannot be nested within an attributed task. (iii) Tasks with process or activity attributes must be nested within a system task. (iv) Tasks with process or systemprocess attributes may be substructured only into tasks attributed either process or activity. (v) Tasks with activity or systemactivity may be substructured only into tasks attributed activity.

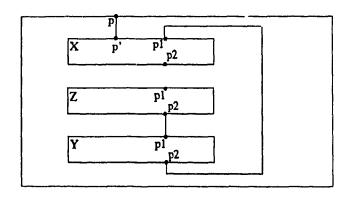

The interconnection of interaction points for communication among the tasks in a specification gives rise to a communication structure within a specification. The elements of this structure are represented graphically, as shown in Fig. 2.1, by line segments binding the tasks' interaction points. There are two kinds of bindings of interaction points: attached and connected. When an external interaction point of a task is bound to an external interaction point of its parent task, these two interaction points are said to be attached. Two bound interaction points are said to be connected if both are external interaction points of two sibling tasks, or one is an internal interaction point of a task and the other is an external interaction point of one of its children tasks, or both are internal interaction points of the same task. Three rules are observed while establishing a communication link between two tasks. (i) An interaction point may be connected to at most one interaction point and it cannot be connected to itself. (ii) An external interaction point of a task may be attached to at most one external interaction point of its children tasks. (iii) An external interaction point of a task

attached to an external interaction point of its parent task cannot be simultaneously connected.

- (C) Communication: In Estelle, there are two kinds of intertask communication mechanisms: (i) message exchange and (ii) restricted sharing of variables. Tasks may exchange messages, called *interactions*. A task can send an interaction to another task through a previously established communication link between two interaction points of the tasks. An interaction received by a task at its interaction point is appended to an unbounded FIFO queue associated with this interaction point. The FIFO queue may either exclusively belong to this single interaction point or be shared with other interaction points of a task. A FIFO queue is called an *individual queue* if it exclusively belongs to a single interaction point and is called a *common queue* if it is shared with other interaction points of a task. Certain variables, declared as *exported* by the children tasks, can be shared between a task and its parent task. The simultaneous access to those variables by both a parent and a child is excluded because the execution of the parent's actions always has priority.

- (D) Parallelism: Two kinds of parallelism between tasks can be expressed in Estelle: (i) asynchronous parallelism and (ii) synchronous parallelism. Parallelism and nondeterminism in Estelle are described using the nation of computation steps. A computation step begins by a selection of a set of transitions among those ready-to-fire by the subsystem's tasks with at most one transition per task. Then, the selected transitions are executed in parallel and, when all of them have completed, the next computation step begins. In that sense, the relative speed of tasks within a subsystem can be synchronized and the resulting parallelism is synchronous. If the selected set consists of exactly one transition for every computation step, then we have purely deterministic behavior within a subsystem. However, the selection of a set of transitions for synchronous or nondeterministic execution within one computation step of a subsystem depends on the parent/children priority principle and on the

way the subsystem's tasks are attributed. If a systemprocess is substructured into only processes, then all ready-to-fire transitions, with at most one transition per task, that are not in the ancestor/dependent conflict are selected, whereas in a task with systemactivity attribute, only one of them is selected. The intermediate selections, between the above two extremes are possible due to the fact that a systemprocess task may be substructured in both processes and activities.

(E) Channels and Interaction Points: In an Estelle specification, channels are abstract objects whose definitions specify sets of interactions. A particular interaction point has a precisely defined set of interactions that can be respectively sent and received through this point. For example, the following is a channel definition: channel CHANNEL\_ID (ROLE1, ROLE2);

by ROLE1:

ml; ...; mN;

by ROLE2:

n1; ...; nK

where m1, ..., mN, n1, ..., nK are interaction declarations. Each interaction declaration consists of a name and possibly some typed parameters such as "RE-QUEST(x: integer; y: boolean)". Now, an interaction point p1 may be declared as "p1: CHANNEL\_ID(ROLE1)" and another interaction point p2 as "p2: CHANNEL\_ID(ROLE2)." Two interaction points both referring to the same channel and different role identifiers play opposite roles, whereas if they refer to the same channel and the same role identifier, then they are said to play the same roles. Two interaction points that are connected must play opposite roles since the exchange of interactions takes place between them. Two interaction points that are attached must play the same role since the aim of attaching them is to replace one of them by the other. Finally, to specify whether the interaction point p1 does or does not share its queue with other interaction points, Estelle allows to specify "p1: CHANNEL ID(ROLE1)

common queue" or "p1: CHANNEL\_ID(ROLE1) individual queue."

(F) Modules: A module is specified by a pair of header and body definitions as shown below. A is the name of the header with systemprocess attribute and n is a formal parameter. It may be noted that a common queue is shared by the interaction points p1 and p2.

module A systemprocess (n: integer);

ip p: T(S) individual queue;

ip p1: U(S) common queue;

ip p2: W(K) common queue;

export X, Y: integer; Z: boolean

end

At least one module body definition is declared for each module header definition. For example, in the following body definition, B is associated with header A.

body B for A; "body definition" end

A body definition is composed of three parts: declaration, initialization, and transition.

- (i) Declaration Part: The declaration part of a body definition contains the usual Pascal declarations and declaration of objects specific to Estelle such as channels, modules, module variables, states and state-sets, and internal interaction points. A body definition may contain declarations of other modules giving rise to a tree structure. The definition "modvar X, Y, Z: A1" means that X, Y, and Z are variables of the module type specified by the module header A1. The internal behavior of each module is defined in terms of a state automaton whose control states are defined by enumeration of their names such as "state: IDLE, WAIT, OPEN, CLOSED." The state variable may assume only the values enumerated by the definition of the above form.

- (ii) Initialization Part: The initialization part of a module body, indicated by the keyword initialize, specifies the values of some variables of the module with which

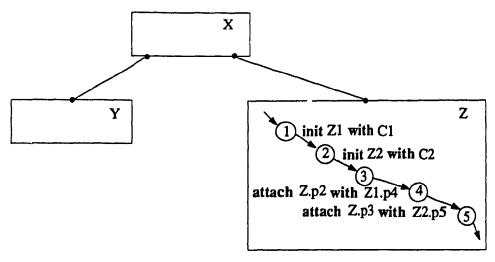

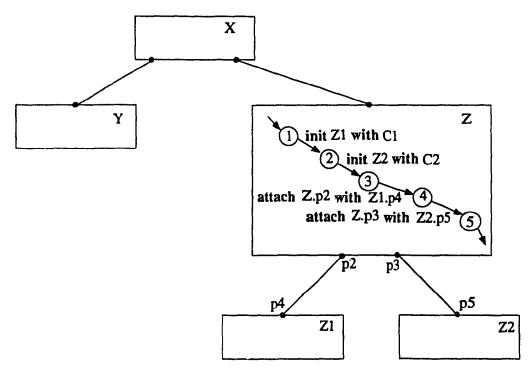

every newly created instance of this module begins its execution. Local variables and the control variable state may have their values assigned. Also, some module variables may be initialized which means that the module's children tasks can be created. To initialize Pascal variables, Pascal statements are used and to initialize the state variable to a control state, for example IDLE, "state to IDLE" is used. The following initialization part of a module (A, B) creates three module instances referenced by the module variables X, Y, and Z, respectively.

#### initialize

```

begin

init X with B1;

init Y with B2;

init Z with B1;

connect X.p1 to Y.p2;

connect Y.p1 to Z.p2;

attach p to X.p';

end

```

The concrete hierarchy of tasks of Fig. 2.3 corresponds to the hierarchical structure of the above module definitions. The initialization also establishes links between appropriate interaction points of the three newly created tasks.

Figure 2.3 A hierarchy of tasks created after an initialize statement.

- (iii) Transition Part: The transition part of a module describes its behavior. Each transition begins with the keyword trans. A simple transition is characterized by the fact that there is exactly one begin ... end block associated with each keyword trans. A nested transition is a shorthand notation for a collection of simple transitions. Each simple transition declaration is composed of two parts: transition condition and transition action. The transition condition is composed of one or more clauses of the following kinds:

- i. from-clause (from A1,...,An, where Ai is a control state or state-set identifier);

- ii. when-clause (when p.m, where p is an interaction point and m is an interaction);

- iii. provided-clause (provided B, where B is a boolean expression);

- iv. priority-clause (priority n, where n is a non-negative constant);

- v. delay-clause (delay(E1, E2), where E1 and E2 are non-negative integer expressions representing the lower and upper limits of the delay, respectively).

The when-clause and the delay-clause are mutually exclusive in a transition definition. Transitions with a when-clause in their conditions are called *input* transitions and those without a when-clause are called *spontaneous* transitions. A transition is said to be *enabled* in a task state if the "from", "when", and "provided" clauses, if present in the transition condition, are satisfied in the state. A transition is said to be firable/executable if:

- i. it is enabled in the state, and if it is a delay transition, with delay clause "delay(E1,

E2)", then it must have remained enabled for at least E1 time units, and

- ii. it has the highest priority among transitions satisfying the previous requirement, where higher priority corresponds to smaller non-negative integer.

The transition action is composed of (i) a to-clause (to A, where A is a control state identifier) and (ii) a begin ... end block containing a sequence of extended Pascal statements. The to-clause specifies the next control state, which will be attained by

a task once the transition is fired. If the to-clause is omitted, then the next state is the same as the current state.

The Pascal extensions consist of additional statements that make it possible to create and destroy module instances, to create and destroy bindings between interaction points, and to send interactions. The create statements include init, connect, and detach. These have already been explained. The statements for the destroy operations are (i) release X, (ii) disconnect p, (iii) disconnect X, and (iv) detach p. The "release X" statement destroys the task referenced by the module variable X and all its descendant tasks, the "disconnect p" statement disconnects the interaction point p from the interaction point to which it was connected, the "disconnect X" disconnects all the interaction points of the children task referenced by X, and the "detach p" statement detaches the interaction point p from the interaction point it was attached to. The ability of a task to execute these statements within a transition gives the possibility to dynamically change the hierarchical tree structure of tasks as well as the communication links between them.

There is also a special statement *output*, which allows a task to send an interaction via a specified interaction point. For example, the statement "output p1.m" sends the interaction m via the interaction point p1. If p1 and p2 are the two end-points of a communication link, then the "output p1.m" statement leads to appending interaction m in the queue associated with the interaction point p2.

Any-clause: A transition in which an any-clause occurs is a shorthand for a set of transitions without any-clauses. The syntax of an any-clause is shown below: any-clause := any domain-list do, where

domain-list:= ID-LIST: ORDINAL-TYPE,.., ID-LIST: ORDINAL-TYPE.

Each of these transition declarations contains an expanded transition resulting from the original expanded transition by replacing each applied occurrence of each ID in the ID-LIST of the any-clause. There shall be one simple, expanded transition for each vector of values of ORDINAL-TYPE(s) contained in the any-clause. The length of each of these vectors is given by the number of identifiers in the ID-LIST of the domain-list of the any-clause.

(G) Specification Module: All modules in an Estelle specification are embodied in a unique module called *specification* which is defined as follows:

```

specification SPEC-NAME [system-class]

[default-option]

[time-option]

"body-definition"

end.

```

where the parts in square brackets are optional. The system-class attribute is either systemprocess or systemactivity, and the default-option is either individual queue or common queue. The time-option defines the unit of time, millisecond, second, etc. to be used in a delay-clause.

- (H) Global Situations: The sementics of Estelle is operational, that is, a next-state relation is defined over the set of the system global states which are called global situations. The next-state relation, also called the next-situation relation, specifies all possible situations that may be directly derived from a given situation. The overall behavior of an Estelle specification is characterized by the set of all sequences of global situations which can be generated from an initial situation of the specification. Each global situation of an Estelle transition system is composed of current information on:

- i. the hierarchical structure of tasks within the specified system SP, the communication structure of tasks denoted by the bindings established between their interaction points, and the local state of each task. All this information is included in a global instantaneous description of SP denoted by gid(SP).

- ii. the transitions that are in parallel execution within each subsystem; the set of

these transitions for *i*th subsystem is denoted by Ai (i = 1,..., n, where n is the number of subsystems).

Each global situation is denoted by: sit = (gid(SP); A1,..., Ai,..., An). The global situation is said to be *initial* if the gid(SP) is initial and all sets Ai are empty. The gid(SP) is initial if it results from the initialization part of a specification SP. The next-situation relation defines the successive situations of an arbitrary current situation: (gid(SP); A1,..., Ai,..., An). It is defined in the following manner. For every i = 1, 2,..., n,

- i. if, in the current situation, Ai is empty, then (gid(SP); A1,..., AS(gid(SP)/i),..., An) is a next situation, where AS(gid(SP)/i) is the set of transitions selected for execution by the ith subsystem.

- ii. if, in the current situation, Ai is nonempty, then for each transition t of Ai,  $(t(gid(SP)); A1,..., Ai \{t\},..., An)$  is a next situation, that is, the new gid(SP) results from execution of t and t is removed from the set Ai.

The above two steps applied to the initial global situation define all possible sequences of global situations in the specification. The execution of a transition t of a task may cause a change in the task's local state. In particular, it may create a new child task and/or a new communication link. The transition may also output, that is, it may send an interaction which is put into the FIFO queue of another task. All these changes are expressed by t(gid(SP)). The selection of transitions to be executed within one computation step, by an ith subsystem, that is, the choice of the set AS(gid(SP)/i) is guided by the following: (i) the principle of parent/children priority, and (ii) the tasks' attributes. The rule applied to a task within a subsystem can be formulated as follows:

- if the task has a ready-to-fire transition, then this one will be selected,

- otherwise, depending on whether the task is attributed process (systemprocess) or activity (systemactivity), respectively, all or one chosen nondeterministically of these ready-to-fire transitions offered by its children tasks will be selected.

# 2.2.2 Translation of an Estelle Specification to an EFSM

In the EFSM construction process, the notation  $var(set\ of\ expressions)$  means the set of variables used in the "set of expressions", and the function Final(r,s) returns a transition r' which is identical to r except that the "to" state of r' is set to s.

Algorithm 2.1: The EFSM construction algorithm is divided into two phases.

- (A) First Phase: In the first phase, we derive an EFSM from the begin...end block in an Estelle transition using the following three steps.

- a. Process the functions.

- b. Derive an EFSM for each procedure, function, and the main "begin ... end" block in the transition.

- c. Resolve the procedure/function call references in the EFSMs derived in step b to obtain an EFSM for an Estelle transition.

- (B) Second Phase: The second phase of the algorithm consists of the following three steps:

- a. Update the EFSM obtained from the begin...end block of a transition to incorporate the Estelle transition-specific information such as from, to, when, and provided. We call such an updated EFSM a transition-EFSM, because it represents the EFSM for a complete Estelle transition. The collection of all the transition-EFSMs corresponding to the transitions in a module is called a module-EFSM.

- b. Create a substructure by processing an init statement.

- c. Combine the module-EFSMs for all the sub-modules in an Estelle specification to obtain an EFSM for the entire specification.

In the following, we explain each of the above steps in detail.

### (A) First Phase:

### a. Function Processing

In an Estelle specification, a function can be used in two ways:

- i. as an expression on the righthand side of a simple assignment statement, such as y = F-name(Plist), where F-name is a function name and Plist is a list of parameters that does not contain another function.

- ii. as a parameter in a procedure/function call, like *P-name(F-name(Plist1), Plist2)*, where *P-name* is a procedure name.

Processing a function means transforming a function reference of the second type to the first type by introducing a new variable. For example, the statement *P-name(F-name(Plist1), Plist2)* is rewritten as a sequence of two statements, where *new1* is a new variable:

new1 = F-name(Plist1);

P-name(new1, Plist2).

# b. Deriving an EFSM from a transition

The following algorithmic steps are used to systematically derive an EFSM from a function, a procedure, and the main **begin** ... **end** block in an Estelle transition. Each step of the algorithm is based on an Estelle construct that can be identified in the syntax analysis phase of an Estelle compiler.

# 1. compound-statement = "begin" statement-sequence "end"

The EFSM for this compound statement is the EFSM obtained from the "statement-sequence."

### 2. statement-sequence = statement1; statement-sequence2

Let

$$F_1 = \langle S_1, S_{t1}, V_1, R_1, s_1, Z_1, h_1, C_{I1}, C_{O1} \rangle$$

and

$F_2 = \langle S_2, S_{12}, V_2, R_2, s_2, Z_2, h_2, C_{12}, C_{02} \rangle$  be the EFSMs for statement1 and statement-sequence2, respectively. Then choose

$$F = \langle S, S_t, V, R, s, Z, h, C_I, C_O \rangle$$

, where  $S = (S_1 \cup S_2) - Z_1$ ,  $S_t = S_{t1} \cup S_{t2}, \ V = V_1 \cup V_2$ ,  $R = ((R_1 \cup R_2) - \{r_{1f}\}) \cup \{r_{2f}\}$ , such that  $(r_{1f} \in R_1) \wedge (To(r_{1f}) \in Z_1) \wedge (r_{2f} = Final(r_{1f}, s_2))$ ,  $s = s_1, \ Z = Z_2, \ h = h_1 oh_2$ .

### 3. Assignment statement

## (a) label: $X = Expression \{ no function call \}$

Choose  $F = \langle S, S_t, V, R, s, Z, h, C_I, C_O \rangle$  such that

$S = \{s_1, s_2\}$ , where  $s_1$  and  $s_2$  are two new states,

$S_t = \{ \langle s_1, L : label \rangle \}, V = var(Expression),$

$R = \{\langle s_1, s_2, i, [T], [X = Expression], 1 \rangle\}$ , where T stands for "true" and i denotes an internal event,

$$s = s_1, Z = \{s_2\}, h = \epsilon.$$

# (b) label: X = Fname(Plist) { function call }

Choose  $F = \langle S, S_t, V, R, s, Z, h, C_I, C_O \rangle$  such that

$$S = \{s_1, s_2\},$$

$S_t = \{\langle s_1, F : Fname(Plist) : label \rangle\}, V = var(Plist),$

$R = \{\langle s_1, s_2, +F, [T], [], 1 \rangle\}$ , where the +F event denotes that the transition is to be replaced by an EFSM corresponding to the declaration of the function *Fname* found as a tag of the *from* state of the transition,

$$s = s_1, Z = \{s_2\}, h = \epsilon.$$

### 4. Procedure call

# label: Pname(Plist) { procedure call }

Choose  $F = \langle S, S_t, V, R, s, Z, h, C_I, C_O \rangle$  such that

$S = \{s_1, s_2\}$ , where  $s_1$  and  $s_2$  are two new states,

$S_t = \{ \langle s_1, P : Pname(Plist) : label \rangle \}, V = var(Plist),$

$R = \{ \langle s_1, s_2, +P, [T], [], 1 \rangle \}$ , where +P denotes that the transition is to be replaced by an EFSM corresponding to the declaration of the procedure *Pname* found as a tag of the *from* state of the transition,

$$s = s_1, Z = \{s_2\}, h = \epsilon.$$

## 5. while-statement = "while" boolexpression "do" statement

Let

$F_1 = \langle S_1, S_{t1}, V_1, R_1, s_1, Z_1, h_1, C_{I1}, C_{O1} \rangle$  be the EFSM for the statement part. Choose

$F = \langle S, S_t, V, R, s, Z, h, C_I, C_O \rangle$  as the new EFSM, where

$S = S_1 \cup \{s, s_2\}$ , where s and  $s_2$  are two new states,

$$S_t = S_{t1}$$

$V = V_1 \cup var(boolexpression),$

$$R = R_1 \cup R_f \cup \{r_1, r_2\},\,$$

$$R_f = \{ \langle s_f, s, i, T, [], 1 \rangle | s_f \in Z_1 \},$$

$r_1 = \langle s, s_1, i, [boolexpression], [], 1 \rangle,$

$r_2 = \langle s, s_2, i, [not(boolexpression)], [], 1 \rangle,$

$$Z = \{s_2\}, h = h_1.$$

## 6. repeat-statement = "repeat" statement-sequence "until" boolexpression

Let

$F_1 = \langle S_1, S_{t1}, V_1, R_1, S_1, Z_1, h_1, C_{I1}, C_{O1} \rangle$  be the EFSM for the statement-sequence part. Choose

$F = \langle S, S_t, V, R, s, Z, h, C_I, C_O \rangle$  as the new EFSM, where

$S = S_1 \cup \{s_2\}$ , where  $s_2$  is a new state,

$S = S_{t1}$

$V = V_1 \cup var(boolexpression),$

$R = R_1 \cup R_f \cup R_b$

$R_f = \{ \langle s_f, s_2, i, [boolexpression], [], 1 > | s_f \in Z_1 \},$

$R_b = \{ \langle s_f, s_1, i, [not(boolexpression)], [], 1 \rangle | s_f \in Z_1 \},$

$s = s_1$

$Z = \{s_2\}, h = h_1.$

# 7. if-statement = "if" boolexpression "then" statemen1 "else" statement2

Let  $F_1 = \langle S_1, S_{t1}, V_1, R_1, s_1, Z_1, h_1, C_{I1}, C_{O1} \rangle$  and

$F_2 = \langle S_2, S_{t2}, V_2, R_2, S_2, Z_2, h_2, C_{I2}, C_{O2} \rangle$  be the EFSMs for statement1 and statement2, respectively. Choose

$F = \langle S, S_t, V, R, s, Z, h, C_I, C_O \rangle$  as the new EFSM, where

$S = S_1 \cup S_2 \cup \{s\}$ , where s is a new state,

$S_t = S_{t1} \cup S_{t2},$

$V = V_1 \cup V_2 \cup var(boolexpression),$

$R = R_1 \cup R_2 \cup \{r_1, r_2\},\$

$r_1 = \langle s, s_1, i, [boolexpression], [], 1 \rangle,$

$r_2 = \langle s, s_2, i, [not(boolexpression)], [], 1 \rangle,$

$Z = Z_1 \cup Z_2, h = h_1 \cup h_2.$

8. for-statement = "for" controlvar ":=" initval ("to"|"downto") finalval "do" statement

Let  $F_1 = \langle S_1, S_{t1}, V_1, R_1, s_1, Z_1, h_1, C_{I1}, C_{O1} \rangle$  be the EFSM for the statement part. Choose  $F = \langle S, S_t, V, R, s, Z, h, C_I, C_O \rangle$  as the new EFSM, where

$S = S_1 \cup \{s_1, s_2\}$ , where  $s_1$  and  $s_2$  are two new states,

$$S_t = S_{t1}$$

$V = V_1 \cup \{controlvar\} \cup var(initval) \cup var(finalval),$

$$R = R_1 \cup \{r_1\} \cup R_f \cup R_b,$$

$r_1 = \langle s, s_1, i, T, [controlvar = initval], 1 \rangle,$

$R_f = \{ \langle s_f, s_2, i, [not(controlvar \leq finalval)], [], 1 \rangle | s_f \in Z_1 \},$

$R_b = \{ \langle s_f, s_1, i, [controlvar \leq finalval], [], 1 \rangle | s_f \in Z_1 \},$

$$Z = \{s_2\}, h = h_1.$$

9. case-statement =

"case" caseindex "of"

case constantlist1: statement-1

•

case constantlistn: statement-n

"end"

Let