Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file Votre référence

Our file Notice inference

## NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

## **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# VOLTAGE CONTROLLED PULSE WIDTH MODULATION PATTERN GENERATORS FOR STATIC POWER CONVERTERS

### Manish Pande

A Thesis

in

The Department

of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at Concordia University

Montreal, Quebec, Canada.

December 1993 © Manish Pande, 1993

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file Votre référence

Our file Notre référence

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à disposition des personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-90807-6

#### **ABSTRACT**

# VOLTAGE CONTROLLED PULSE WIDTH MODULATION PATTERN GENERATORS FOR STATIC POWER CONVERTERS

#### Manish Pande

Many static power converter systems use uncontrolled diode rectifier bridges at the front end. Due to rectification, the resulting dc link voltage contains characteristic as well as uncharacteristic harmonics. In addition switching devices in a converter system have conduction voltage drops and finite turn-on and turn-off delays. These factors are found to degrade the overall performance of the converter system.

The objective of this research is to investigate the principle of converter output voltage integral duty cycle control. Two schemes, Reset Integral Control (RIC) and Modulated Integral Control (MIC) are derived and used in on-line PWM pattern generators for dc-dc and dc-ac converters. The switching pattern generated is a function of the non-ideal conditions. Thus a better performance with almost the same complexity as the conventional pattern generators is achieved. Performance features are illustrated through computer simulation case studies. Experimental results on a laboratory prototype confirm the feasibility of the proposed pattern generators.

# ACKNOWLEDGEMENTS

I wish to express my gratitude to Dr. H. Jin and Dr. G. Joos for their valuable advice and support during the course of this research work.

I would like to thank all my research colleagues in Power Electronics Lab for their encouragement and help.

# TABLE OF CONTENTS

| r                                                                | age  |

|------------------------------------------------------------------|------|

| List of Figures                                                  | x    |

| List of Tables                                                   | ХX   |

| List of Acronyms                                                 | жі   |

| List of Principal Symbols                                        | xxii |

| CHAPTER 1. INTRODUCTION                                          |      |

| 1.1. Introduction                                                | 1    |

| 1.2. Problem definition                                          | 2    |

| 1.2.1 Ripple in dc link voltage                                  | 3    |

| 1.2.1.1. Cause of ripple                                         | 3    |

| 1.2.1.2. Impact of low frequency ripple on converter performance | 5    |

| 1.2.2. Non-ideal power semiconductor devices                     | 7    |

| 1.2.2.1. Effect of switching delay in DC/DC PWM converters       | 9    |

| 1.2.2.2. Effect of dead times on output voltage in PWM inverters | 9    |

| 1.3. Review of previous research                                 | 12   |

| 1.3.1. Feedforward techniques                                    | 12   |

| 1.3.2. Advanced PWM techniques using microprocessors             | 16   |

| 1.3.3. Dead time compensation                                    | 17   |

| 1.4. Scope and contribution of this thesis.                      | 18   |

| 1.5. Outline of the thesis                                       | 18   |

| CHAPTER 2. PRINCIPLES OF OUTPUT VOLTAGE INTEGRA                                                                                                                                                                                                                                     | L DUTY         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| CYCLE CONTROL                                                                                                                                                                                                                                                                       |                |

| 2.1. Introduction.                                                                                                                                                                                                                                                                  | 20             |

| 2.2. Output Voltage Integral (OVI) Duty Cycle Control                                                                                                                                                                                                                               | 21             |

| 2.3. Reset Integral Control Technique                                                                                                                                                                                                                                               | 22             |

| 2.3.1. Principles of operation                                                                                                                                                                                                                                                      | 22             |

| 2.3.2. Waveforms                                                                                                                                                                                                                                                                    | 24             |

| 2.4. Modulated Integral Control Technique                                                                                                                                                                                                                                           | 26             |

| 2.4.1. Principles of operation                                                                                                                                                                                                                                                      | 27             |

| 2.4.2. Waveforms                                                                                                                                                                                                                                                                    | 27             |

| 2.5. Conclusions                                                                                                                                                                                                                                                                    | 29             |

| CHAPTER 3. PERFORMANCE ANALYSIS OF DC-DC CONV                                                                                                                                                                                                                                       | ERTERS         |

| CHAPTER 3. PERFORMANCE ANALYSIS OF DC-DC CONV<br>USING VOLTAGE INTEGRAL DUTY CYCLE CONTROL                                                                                                                                                                                          | ERTERS         |

|                                                                                                                                                                                                                                                                                     |                |

| USING VOLTAGE INTEGRAL DUTY CYCLE CONTROL  3.1. Introduction                                                                                                                                                                                                                        | 30             |

| USING VOLTAGE INTEGRAL DUTY CYCLE CONTROL                                                                                                                                                                                                                                           | 30             |

| USING VOLTAGE INTEGRAL DUTY CYCLE CONTROL  3.1. Introduction                                                                                                                                                                                                                        | 30<br>30       |

| USING VOLTAGE INTEGRAL DUTY CYCLE CONTROL  3.1. Introduction  3.2. Implementation aspects  3.3. Reset Integral Control                                                                                                                                                              | 30<br>30<br>32 |

| USING VOLTAGE INTEGRAL DUTY CYCLE CONTROL  3.1. Introduction                                                                                                                                                                                                                        | 30<br>32<br>33 |

| USING VOLTAGE INTEGRAL DUTY CYCLE CONTROL  3.1. Introduction  3.2. Implementation aspects  3.3. Reset Integral Control  3.3.1. Principles of operation  3.3.2. Selection of integrator time constant (τ)                                                                            | 30323335       |

| USING VOLTAGE INTEGRAL DUTY CYCLE CONTROL  3.1. Introduction  3.2. Implementation aspects  3.3. Reset Integral Control  3.3.1. Principles of operation  3.3.2. Selection of integrator time constant (τ)  3.3.2.1 Ideal dc bus                                                      | 3032333535     |

| USING VOLTAGE INTEGRAL DUTY CYCLE CONTROL  3.1. Introduction                                                                                                                                                                                                                        | 303233353537   |

| USING VOLTAGE INTEGRAL DUTY CYCLE CONTROL  3.1. Introduction  3.2. Implementation aspects  3.3. Reset Integral Control  3.3.1. Principles of operation  3.3.2. Selection of integrator time constant (τ)  3.3.2.1 Ideal dc bus  3.3.2.2. Non-ideal dc bus  3.3.2.3. Design example: | 30323335353738 |

| 3.3.4. Dynamic response                                                                                                                                                                                                                                                                                     | 45             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 3.3.5. Experimental results                                                                                                                                                                                                                                                                                 | 47             |

| 3.4. Modulated Integral Control                                                                                                                                                                                                                                                                             | 52             |

| 3.4.1. Principles of operation                                                                                                                                                                                                                                                                              | 53             |

| 3.4.2. Selection of the integrator time constant(τ)                                                                                                                                                                                                                                                         | 54             |

| 3.4.2.1. Ideal dc bus                                                                                                                                                                                                                                                                                       | 54             |

| 3.4.2.2. Non-ideal dc bus                                                                                                                                                                                                                                                                                   | 55             |

| 3.4.3. Steady state results                                                                                                                                                                                                                                                                                 | 55             |

| 3.4.3.1. Ideal dc bus                                                                                                                                                                                                                                                                                       | 56             |

| 3.4.3.2. Compensation of switching delays                                                                                                                                                                                                                                                                   | 56             |

| 3.4.3.3. Non ideal dc bus                                                                                                                                                                                                                                                                                   | 59             |

| 3.4.4. Experimental Results                                                                                                                                                                                                                                                                                 | 61             |

| 3.5. Conclusions                                                                                                                                                                                                                                                                                            | 63             |

|                                                                                                                                                                                                                                                                                                             |                |

| CHAPTER 4. PWM PATTERN GENERATORS FOR THREE P VOLTAGE SOURCE INVERTERS                                                                                                                                                                                                                                      | PHASE          |

|                                                                                                                                                                                                                                                                                                             |                |

| VOLTAGE SOURCE INVERTERS                                                                                                                                                                                                                                                                                    | 64             |

| VOLTAGE SOURCE INVERTERS 4.1. Introduction                                                                                                                                                                                                                                                                  | 64             |

| VOLTAGE SOURCE INVERTERS  4.1. Introduction                                                                                                                                                                                                                                                                 | 64<br>65       |

| VOLTAGE SOURCE INVERTERS  4.1. Introduction                                                                                                                                                                                                                                                                 | 64<br>65<br>65 |

| VOLTAGE SOURCE INVERTERS  4.1. Introduction                                                                                                                                                                                                                                                                 |                |

| VOLTAGE SOURCE INVERTERS  4.1. Introduction  4.2 Implementation aspects  4.2.1. Location of voltage sensor  4.2.2. Choice of reference control voltage  4.3.1. Reset Integral controller  4.3.1. Structure of the proposed pattern generator  4.3.1.1. Half bridge inverter  4.3.1.2. Three phase operation |                |

| 4.3.3.2. Design Example                                     | 72         |

|-------------------------------------------------------------|------------|

| 4.3.4. Performance analysis                                 | 73         |

| 4.3.4.1. Steady State                                       | 73         |

| 4.3.4.1.1. Quality of output voltage under ideal dc bus     | 74         |

| 4.3.4.1.2. Quality of output voltage under non-ideal dc bus | 75         |

| 4.3.4.1.3. Output voltage gain under ideal dc bus           | 83         |

| 4.3.4.1.4. Reduction in gain with non-ideal dc bus          | 84         |

| 4.3.4.2. Transient conditions                               | <b>8</b> 6 |

| 4.3.4.2.1. Change in the input dc bus                       | <b>8</b> 6 |

| 4.3.4.2.2. Change in the reference                          | <b>8</b> 6 |

| 4.3.5. Experimental results                                 | <b>8</b> 9 |

| 4.4. Modulated Integral Control (MIC)                       | 94         |

| 4.4.1. Structure of the proposed controller                 | 94         |

| 4.4.1.1. Half bridge inverter                               | 94         |

| 4.4.1.2. Principles of operation                            | 94         |

| 4.4.1.3. Three phase inverter                               | 97         |

| 4.4.2. Principles of compensation                           | 99         |

| 4.4.3. Design guidelines                                    | 100        |

| 4.4.3.1. Ideal DC Bus                                       | 100        |

| 4.4.3.2. Non-Ideal DC Bus                                   | 102        |

| 4.4.3.3. Design example                                     | 103        |

| 4.4.4. Performance analysis                                 | 104        |

| 4.4.4.1. Ideal DC Bus                                       | 104        |

| 4.4.4.2. Dead time compensation.                            | 106        |

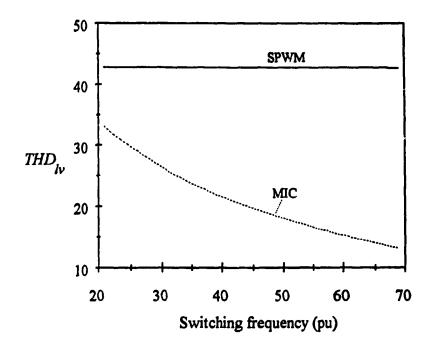

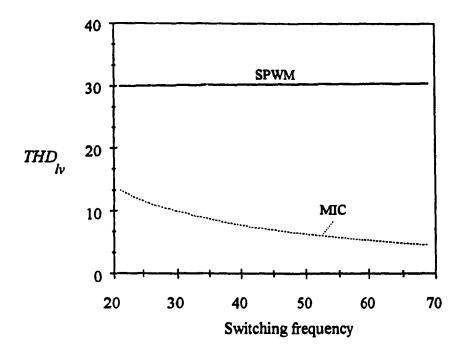

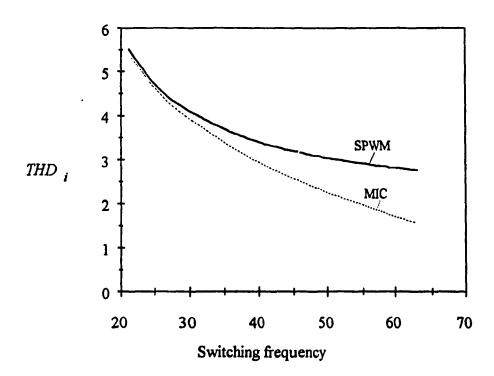

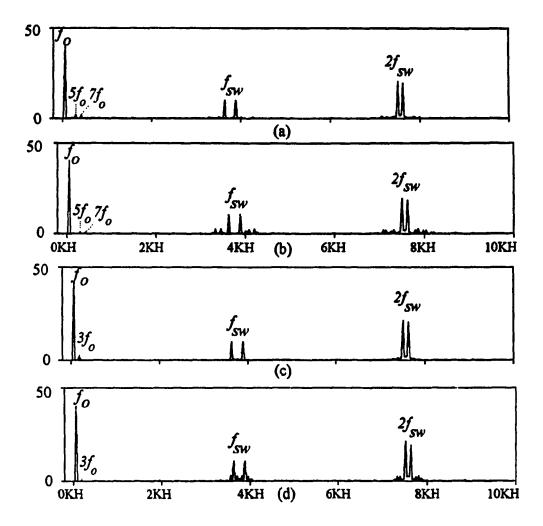

| 4.4.4.3. Non-ideal DC Bus                                   | 111        |

| 4.4.5. Experimental results                                 | 114        |

| 4.5 Conclusions                                             | 118        |

# **CHAPTER 5. CONCLUSIONS**

| 5.1. Conclusions                          | 119 |

|-------------------------------------------|-----|

| 5.2. Suggestions for future research work | 120 |

| REFERENCES                                | 121 |

| APPENDIX                                  | 125 |

# LIST OF FIGURES

| Fig. 1.1. A typical dc-dc or dc-ac power electronic converter system 2        |

|-------------------------------------------------------------------------------|

| Fig. 1.2. A PWM converter (dc/dc or dc/ac) with a front-end diode rectifier 3 |

| Fig. 1.3. DC bus spectrum. (without an input filter) (a) Balanced input       |

| supply. (b) Unbalanced input supply (fo: ac supply frequency)                 |

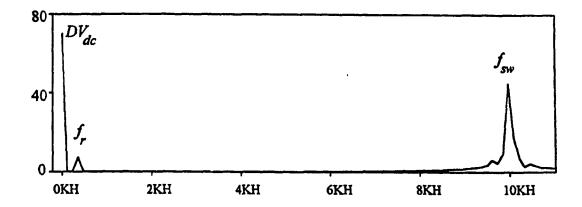

| Fig. 1.4. Output voltage spectrum of a dc-dc converter working under non-     |

| ideal dc bus. $(f_{sw}=10 \text{ kHz}, D=0.7, f_r=360 \text{ Hz})$ 6          |

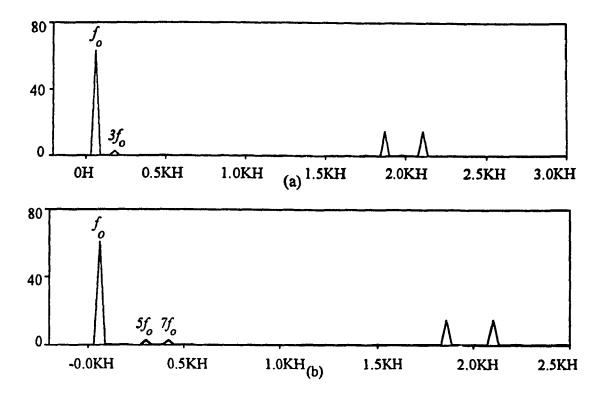

| Fig. 1.5. Output voltage spectra of a dc-ac converter working under non-      |

| ideal dc bus (a) $f_r$ =120 Hz (b) $f_r$ =360 Hz7                             |

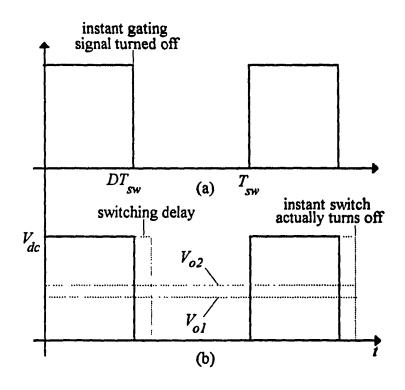

| Fig. 1.6. Effect of switching delay in dc-dc converters. (a) Ideal gating     |

| signal for the power switch. (b) Output voltage with and without switching    |

| delay9                                                                        |

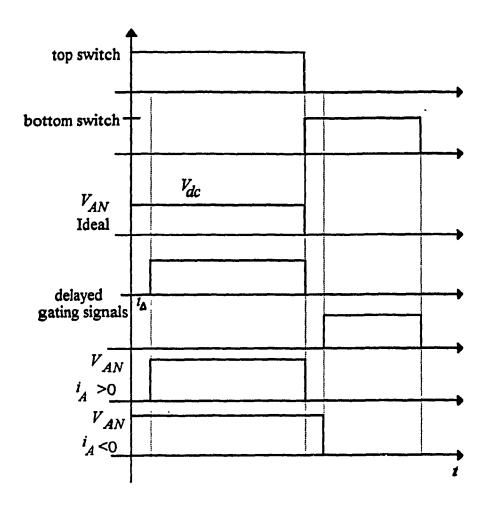

| Fig. 1.7. Dead time effects in a half bridge inverter                         |

| Fig. 1.8. Ideal PWM switching, no dead time. (a) Output voltage. (b)          |

| Harmonic Spectra                                                              |

| Fig. 1.9. Dead time of 10 µsec in gating signals. (a) Load Current and        |

| equivalent dead time voltage. (b) Output voltage (excluding the switching     |

| harmonics). (c) Harmonic spectrum of the output voltage                       |

| Fig. 1.10. A feedforward dc-dc buck converter                                 |

| Fig. 1. 11. Effect of a feedforward loop on ramp carrier and switch control   |

| signal 14                                                                     |

| Fig. 1.12. Block diagram implementation of the scheme proposed in [30] 15     |

| Fig. 1.13. Determination of switching function for technique proposed in      |

| [33][34]                                                                      |

| Fig. 1.14. Dead time compensation in [23][24]                                 |

| Fig. 2.1. Effect of varying input on duty cycle. (a) Input voltage to the                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| converter( $V_d$ ). (b) Open loop control. (c) Output voltage integral duty                                                                                                                                                     |

| cycle control21                                                                                                                                                                                                                 |

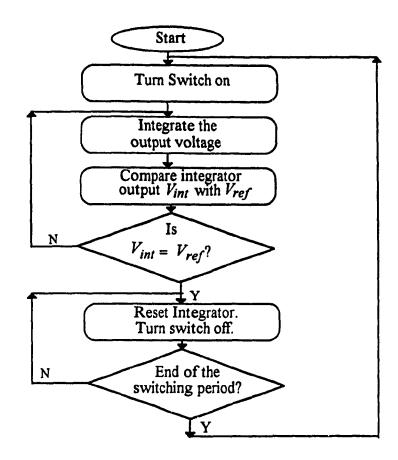

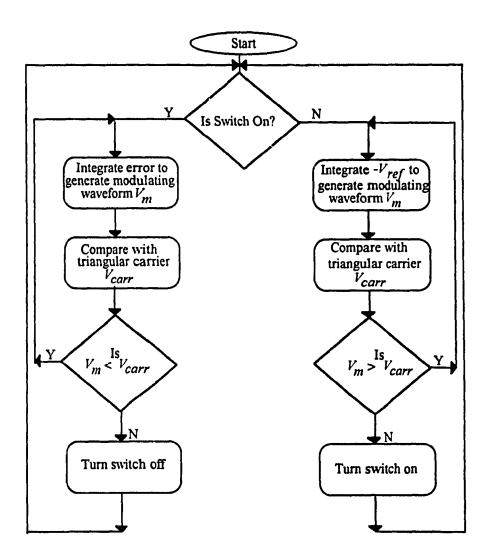

| Fig. 2.2. Flowchart for Reset integral control technique                                                                                                                                                                        |

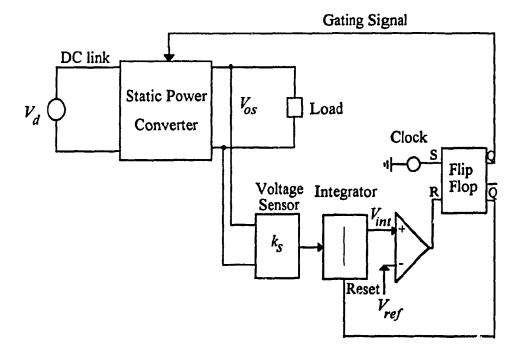

| Fig. 2.3. Reset Integral Control Technique for a general converter system 23                                                                                                                                                    |

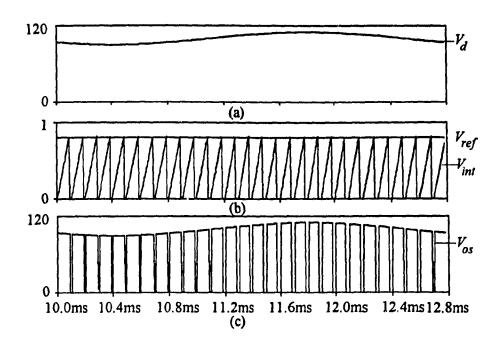

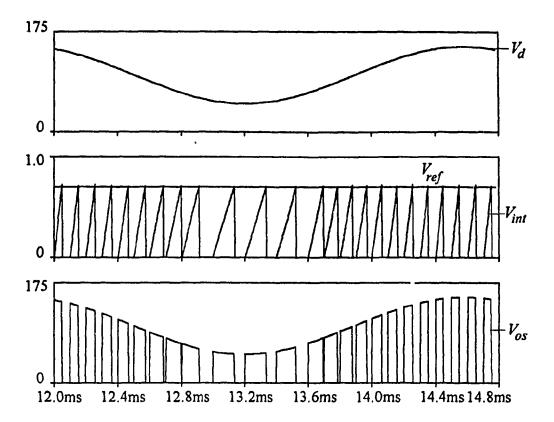

| Fig. 2.4. Waveforms under Reset integral control technique with a dc                                                                                                                                                            |

| reference (a) Input voltage $(V_d)$ . (b) Integrator output $(V_{int})$ and control                                                                                                                                             |

| reference $(V_{ref})$ . (c) Output voltage of the converter $(V_{os})$ 25                                                                                                                                                       |

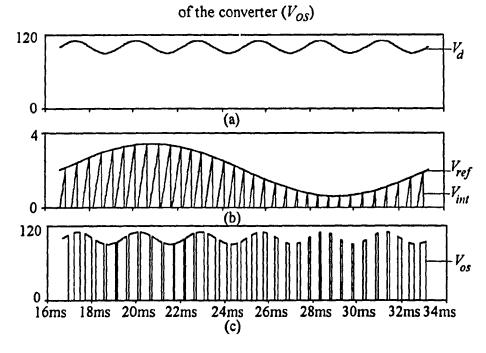

| Fig. 2.5. Waveforms under Reset integral control technique with a                                                                                                                                                               |

| sinusoidal reference. (a) Input voltage (Vd). (b) Integrator output (Vint)                                                                                                                                                      |

| and control reference ( $Vref$ ). (c) Output voltage of the converter ( $V_{os}$ )                                                                                                                                              |

| Fig. 2.6. Flowchart for Modulated integral control technique                                                                                                                                                                    |

| Fig. 2.7. Modulated Integral Control Technique for a general converter                                                                                                                                                          |

| system                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                 |

| Fig. 2.8. Waveforms under modulated integral control technique with a dc                                                                                                                                                        |

|                                                                                                                                                                                                                                 |

| Fig. 2.8. Waveforms under modulated integral control technique with a dc                                                                                                                                                        |

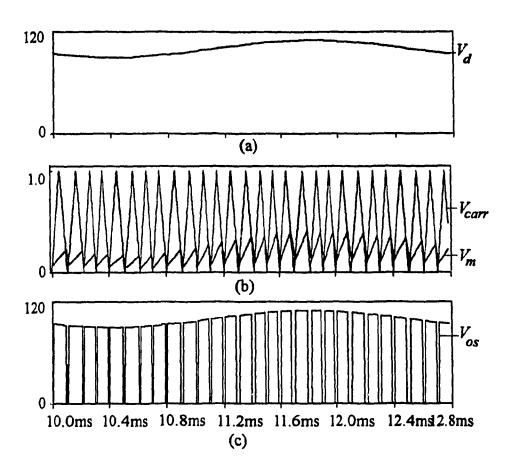

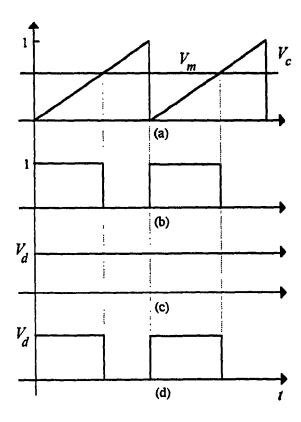

| Fig. 2.8. Waveforms under modulated integral control technique with a dc reference (a) Input voltage $(V_d)$ . (b) Integrator output $(V_m)$ and carrier                                                                        |

| Fig. 2.8. Waveforms under modulated integral control technique with a dc reference (a) Input voltage $(V_d)$ . (b) Integrator output $(V_m)$ and carrier waveform $(V_{carr})$ . (c) Output voltage of the converter $(V_{os})$ |

| Fig. 2.8. Waveforms under modulated integral control technique with a dc reference (a) Input voltage $(V_d)$ . (b) Integrator output $(V_m)$ and carrier waveform $(V_{carr})$ . (c) Output voltage of the converter $(V_{os})$ |

| Fig. 2.8. Waveforms under modulated integral control technique with a dc reference (a) Input voltage $(V_d)$ . (b) Integrator output $(V_m)$ and carrier waveform $(V_{carr})$ . (c) Output voltage of the converter $(V_{os})$ |

| Fig. 2.8. Waveforms under modulated integral control technique with a dc reference (a) Input voltage $(V_d)$ . (b) Integrator output $(V_m)$ and carrier waveform $(V_{carr})$ . (c) Output voltage of the converter $(V_{os})$ |

| Fig. 2.8. Waveforms under modulated integral control technique with a dc reference (a) Input voltage $(V_d)$ . (b) Integrator output $(V_m)$ and carrier waveform $(V_{carr})$ . (c) Output voltage of the converter $(V_{os})$ |

| Fig. 2.8. Waveforms under modulated integral control technique with a dc reference (a) Input voltage $(V_d)$ . (b) Integrator output $(V_m)$ and carrier waveform $(V_{carr})$ . (c) Output voltage of the converter $(V_{os})$ |

| Fig. 2.8. Waveforms under modulated integral control technique with a dc reference (a) Input voltage $(V_d)$ . (b) Integrator output $(V_m)$ and carrier waveform $(V_{carr})$ . (c) Output voltage of the converter $(V_{os})$ |

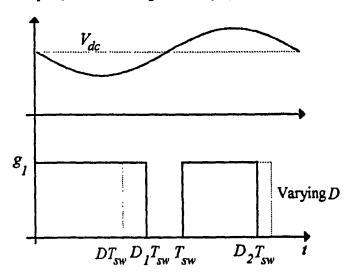

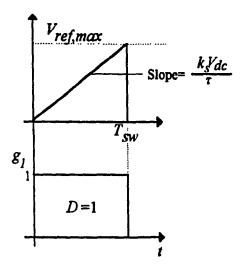

| Fig. 3.4. Effect of varying input on the duty cycle of the converter working           |

|----------------------------------------------------------------------------------------|

| under reset integral control. (a) Input voltage $(V_d)$ . (b) Gating signal $(g_1)$ 35 |

| Fig. 3.5. Design of integrator time constant (1)                                       |

| Fig. 3.6. Effect of non-ideal dc bus on design of integrator time constant.            |

| (a) Input voltage $(V_d)$ . (b) Control waveforms. (c) Output voltage $(V_{os})$       |

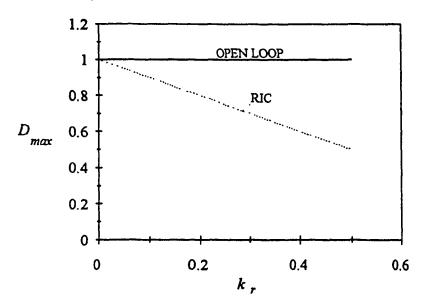

| Fig. 3.7. Maximum duty cycle $(D_{max})$ as a function of ripple factor $(k_r)$        |

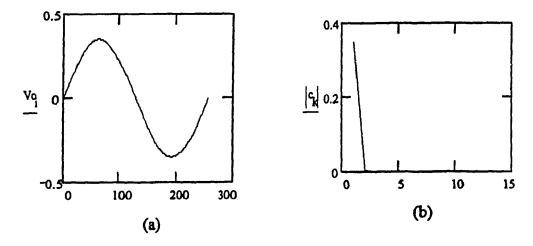

| Fig. 3.8. Buck converter under open loop control. (a). Inductor current.               |

| (b) Output voltage. (c) Control waveforms                                              |

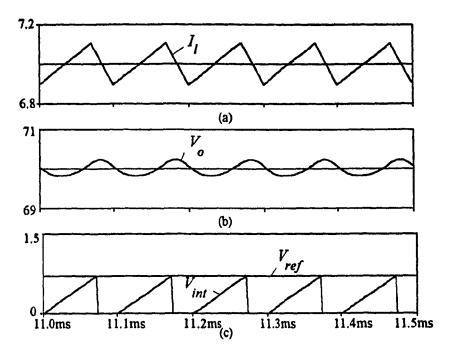

| Fig. 3.9. Buck converter under reset-integral control. (a). Inductor                   |

| current. (b) Output voltage. (c) Control waveforms41                                   |

| Fig. 3.10. Steady state results for a dc-dc converter operating under a non-           |

| ideal dc bus (a) Control waveiorms. (b) Output voltage (detailed view) 42              |

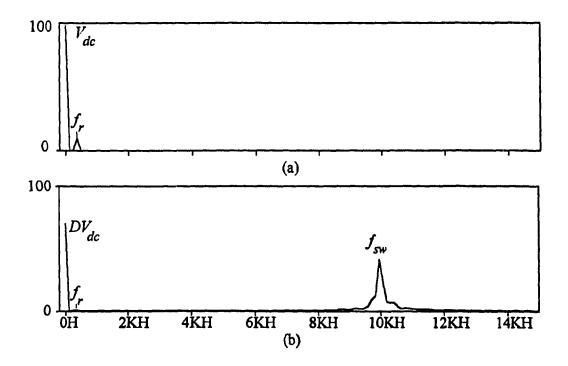

| Fig. 3.11. Operation of dc-dc converter with a non-ideal dc bus. (a) Input             |

| voltage spectrum. (b) Output voltage spectrum ( $f_{SW}$ =10 kHz, $D$ =0.7)42          |

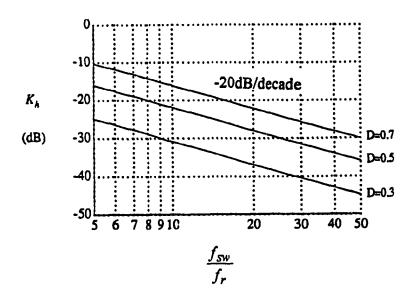

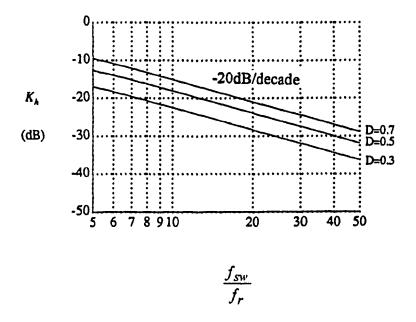

| Fig. 3.12. Harmonic attenuation of reset integral control                              |

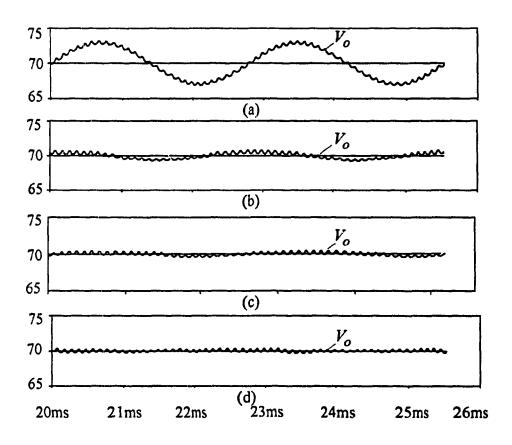

| Fig. 3.13. Output voltage (detailed view) with 10% input source harmonic.              |

| (a) Open loop (b) Conventional feedback (c) Reset integral control (d)                 |

| Reset integral control with feedback ( $k_r=0.1, f_r=360 \text{ Hz}$ )                 |

| Fig. 3.14. Response of dc-dc converter for a 20% change in input                       |

| voltage.(a) Input voltage. (b) Control waveforms. (c) Detailed view of                 |

| output voltage $(V_{os})$ and load voltage $(V_o)$ . (d) Output voltage $(V_{os})$ and |

| load voltage( $V_o$ )45                                                                |

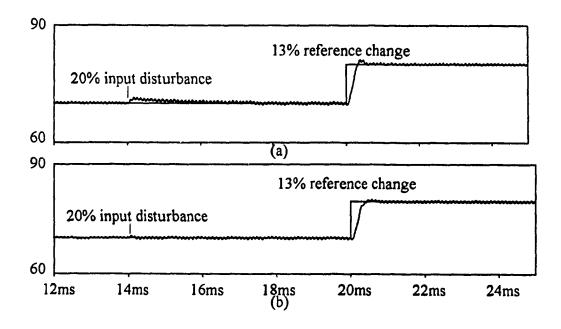

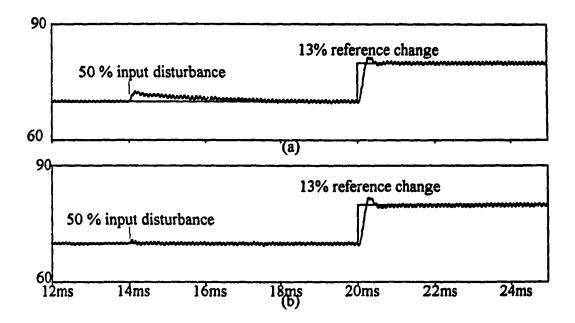

| Fig. 3.15. Converter output voltage for a 20% change in input voltage                  |

| and 13% change in reference. (a) Conventional feedback. (b) RIC with                   |

| feedback loop                                                                          |

| Fig. 3.16. Converter output voltage for a 50% change in input voltage and         |

|-----------------------------------------------------------------------------------|

| 13% change in reference. (a) Conventional feedback. (b) RIC with                  |

| feedback loop47                                                                   |

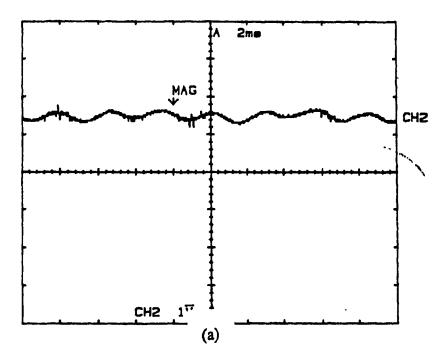

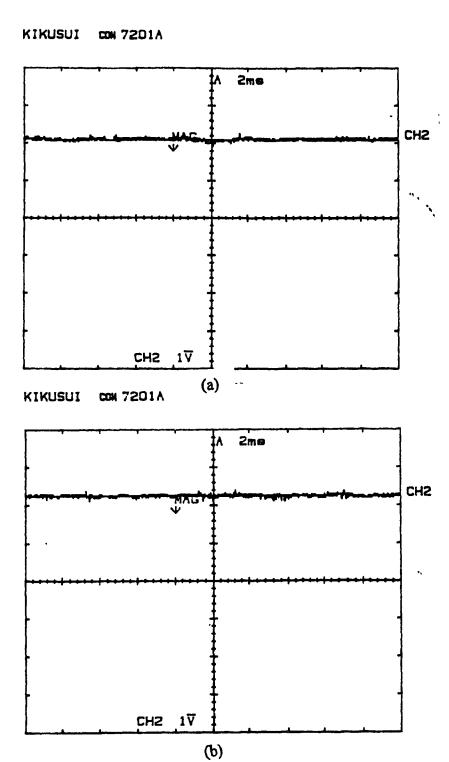

| Fig. 3.17. DC output voltage (a) Open loop. (b) Feedback loop                     |

| Fig. 3.18. AC component of dc output voltage. (a) Open loop. (b)                  |

| Feedback loop                                                                     |

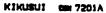

| Fig. 3.19. Reset integral control. (a) Control waveforms. (b) AC                  |

| component of the load voltage without feedback. (c) AC component of               |

| load voltage with feedback                                                        |

| Fig. 3.20. Output voltage under reset integral control. (a) Without               |

| feedback. (b) With feedback                                                       |

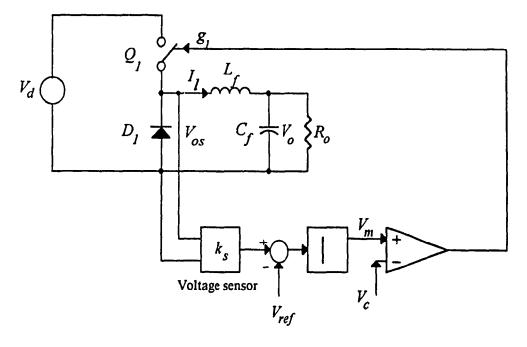

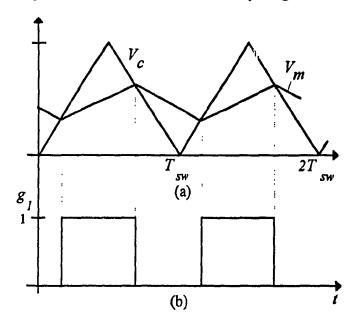

| Fig. 3.21. Modulated integral control technique for a buck converter 52           |

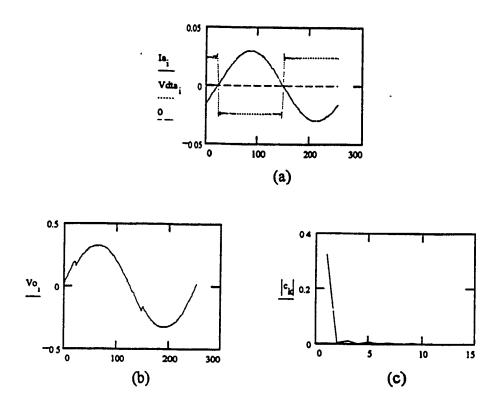

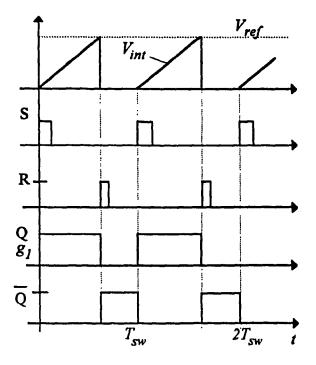

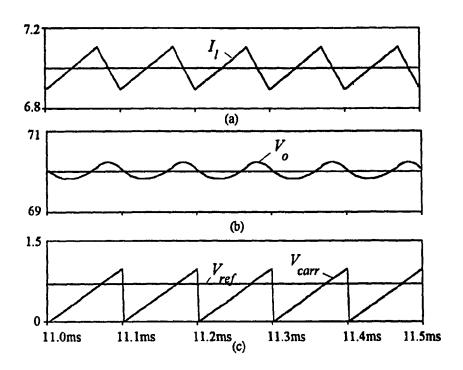

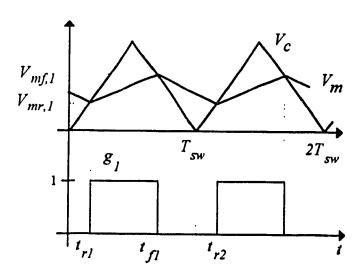

| Fig. 3.22. Control waveforms for modulated integral control technique 53          |

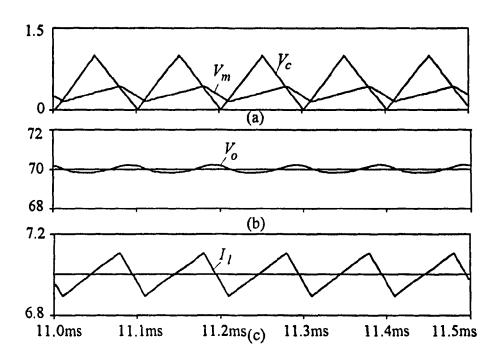

| Fig. 3.23. Modulated integral control. (a) Control waveforms. (b) Load            |

| voltage. (c). Inductor current. (D=0.7)                                           |

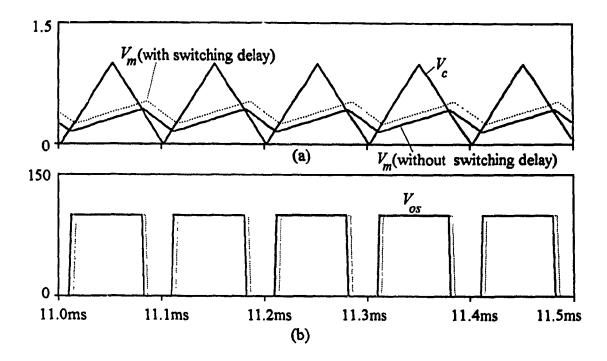

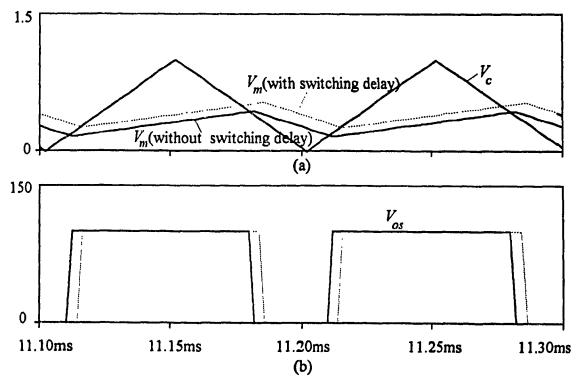

| Fig. 3.24. Output voltage with switching delay in open loop buck converter 57     |

| Fig. 3.25. Switching delay compensation using modulated integral control          |

| (a) Control waveforms (with and without delays).(b) Output voltage( $V_{os}$ ) 58 |

| Fig. 3.26. Switching delay compensation using modulated integral control          |

| (detailed view) (a) Control waveforms (with and without delays).(b)               |

| Output voltage( $V_{os}$ )58                                                      |

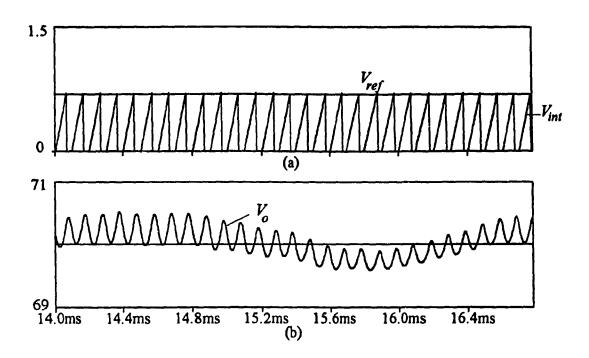

| Fig. 3.27. Steady state results for a dc-dc converter operating under a non-      |

| ideal dc bus (a) Control waveforms. (b) Output voltage (detailed view) 59         |

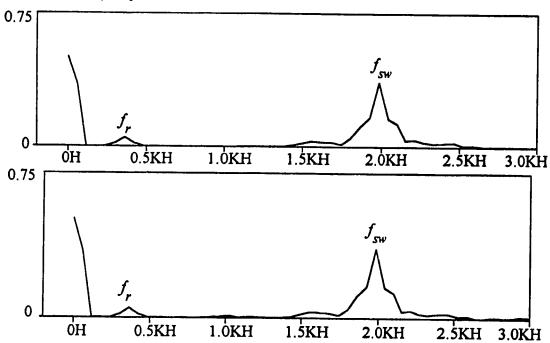

| Fig. 3.28. Operation of dc-dc converter with a non-ideal dc bus. (a) Input        |

| voltage spectrum. (b) Output voltage spectrum ( $f_r$ =360 Hz, $f_{sw}$ =10 kHz,  |

| <i>D</i> =0.7)                                                                    |

| Fig. 3.29. Harmonic attenuation of modulated integral control                     |

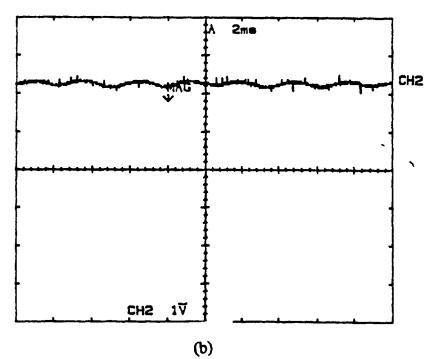

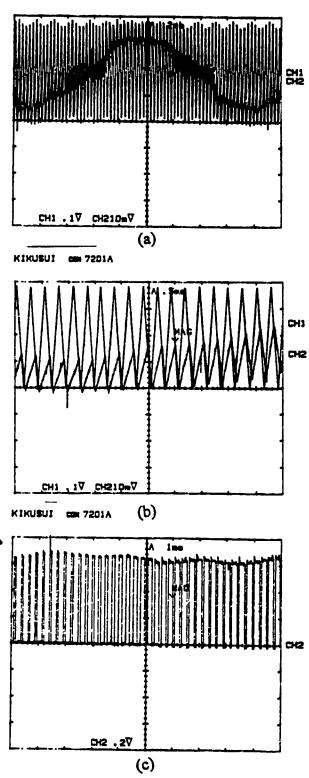

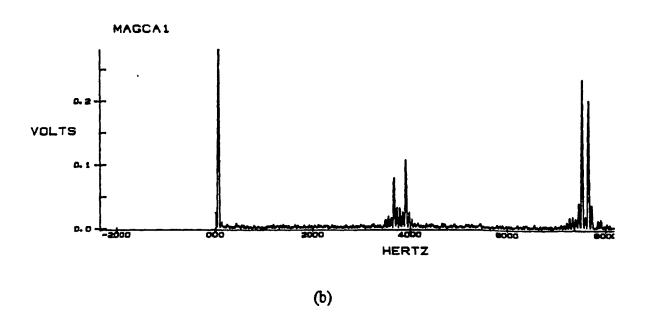

| Fig. 3.30. Modulated integral control. (a) Control waveforms. (b) AC                    |

|-----------------------------------------------------------------------------------------|

| component of the load voltage without feedback. (c) AC component of                     |

| load voltage with feedback                                                              |

| Fig. 3.31. Output voltage under modulated integral control with feedback 63             |

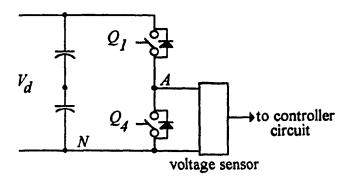

| Fig. 4.1. Location of voltage sensor in dc/ac converters                                |

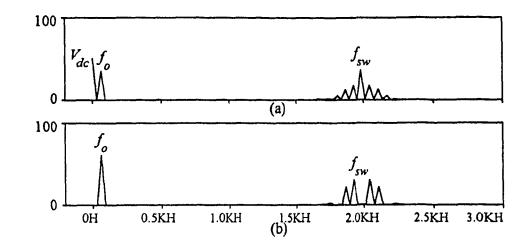

| Fig. 4.2. Voltage harmonic spectra. (a) Voltage across bottom switch (b)                |

| Line voltage( $f_{sw}$ =33pu $M$ =0.7)                                                  |

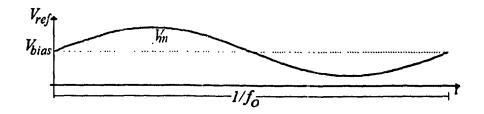

| Fig. 4.3. Reference voltage for a dc/ac converter                                       |

| Fig. 4.4. Proposed pattern generator for half bridge configuration                      |

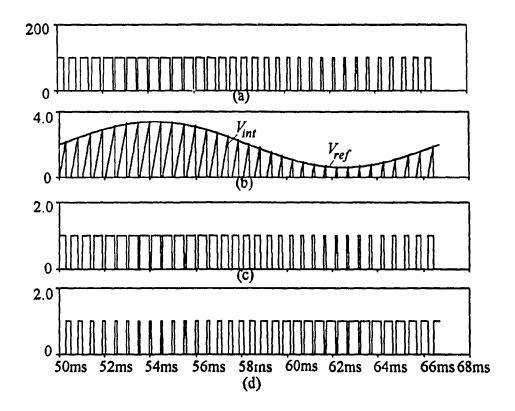

| Fig. 4.5. Waveforms for a half bridge inverter. (a) Voltage across the                  |

| bottom switch $(V_{Q4})$ . (b) Integrator output $(V_{int})$ and control reference      |

| $(V_{ref})$ . (c) Gating signal for the top switch $(g_1)$ (d) Gating signal for the    |

| bottom switch $(g_4)$                                                                   |

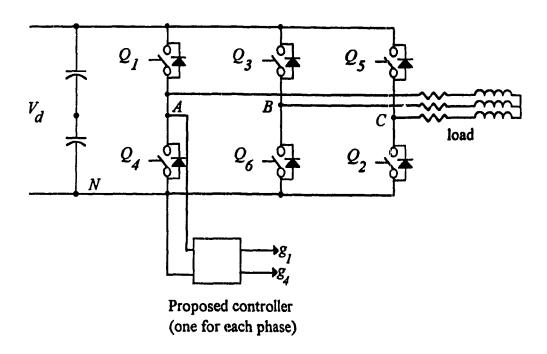

| Fig. 4.6. Proposed pattern generator for a three-phase inverter                         |

| Fig. 4.7. Waveforms for three phase inverter. (a) Control waveforms for                 |

| phase A. (b) Gating signal for switch $Q_I$ . (c) Control waveforms for phase           |

| B. (d) Gating signal for switch $Q_3$ . (e) Line voltage. (f) Line current              |

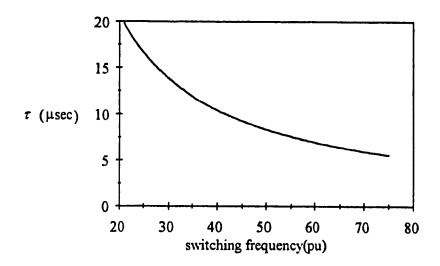

| Fig. 4.8. Design curve. Integrator time constant (7) versus switching                   |

| frequency $(f_{SW})$                                                                    |

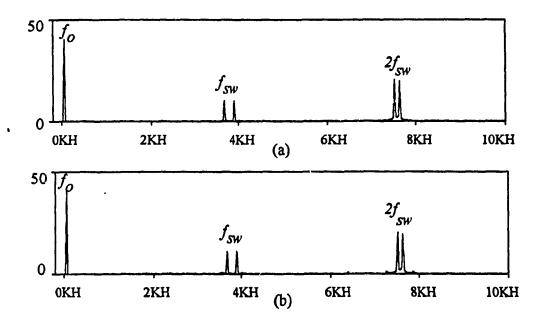

| Fig. 4. 9. Output line voltage harmonic spectra under steady state with an              |

| ideal dc bus under (a) SPWM. (b) Integral control. ( $M=0.7 f_{sw}=33$ pu)              |

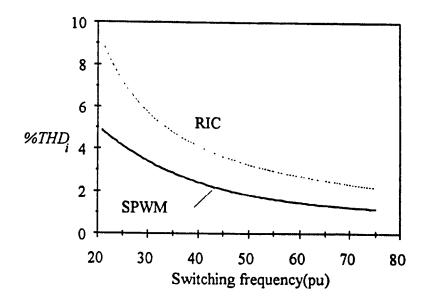

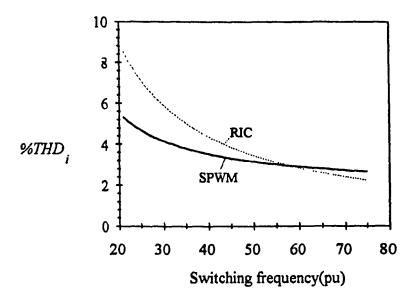

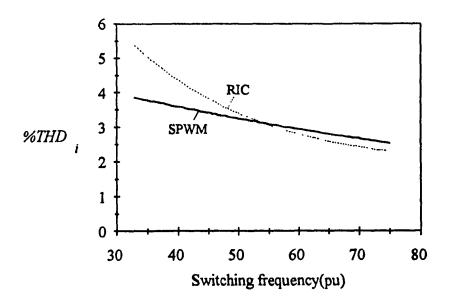

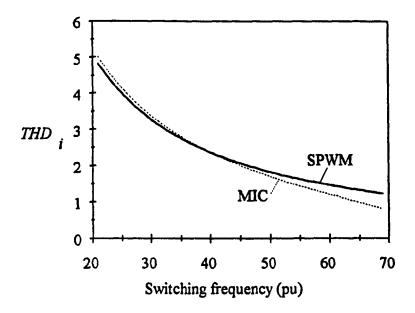

| Fig. 4.10. $THD_i$ with a typical inductive load ( $R_i$ =10 $\Omega$ , $L_i$ =16mH) as |

| function of switching frequency with an ideal dc bus ( $M=0.7$ )                        |

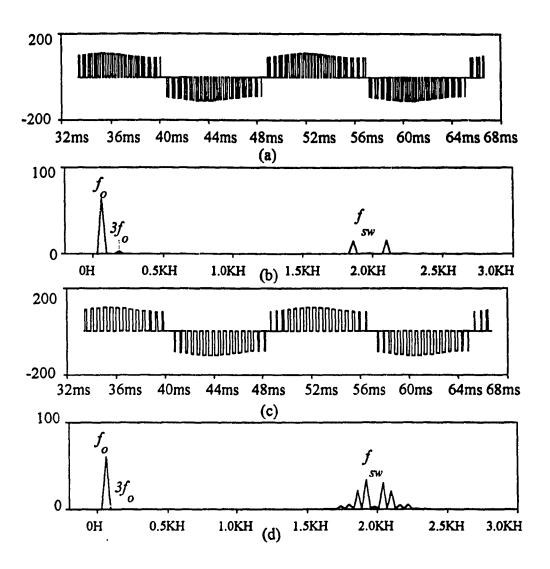

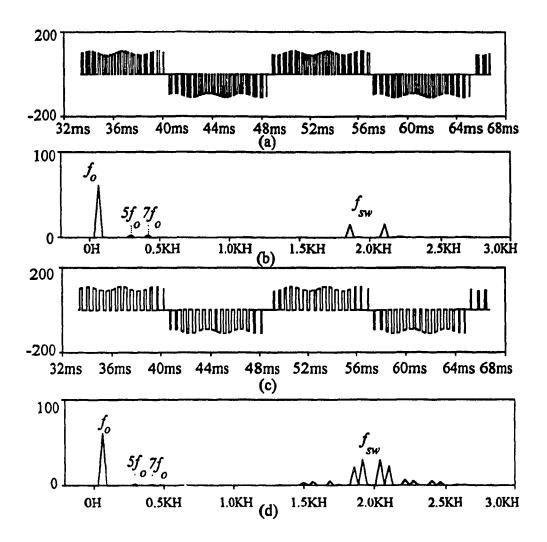

| Fig. 4.11. Steady state operation of a three phase inverter with ripple in the          |

| dc bus $(f_r=2pu)$ . (a) Output voltage under SPWM. (b) Harmonic spectrum               |

| . (c) Output voltage under RIC. (b) Harmonic spectrum. (M=0.7,                          |

| $f_{\text{cu}}=33\text{pu}$ )                                                           |

| rig. 4.12. Steady state operation of a three phase inverter with hppie in the      |

|------------------------------------------------------------------------------------|

| dc bus $(f_r=2pu)$ . (a) Output current under SPWM. (b) Harmonic spectrum.         |

| (c) Output current under RIC. (b) Harmonic spectrum. ( $M=0.7, f_{sw}=33$ pu) 78   |

| Fig. 4.13. Total current harmonic distortion (THD <sub>1</sub> ) versus switching  |

| frequency with 10% ripple ( $f_r$ =2pu). (a) Sine PWM. (b) Integral voltage        |

| control. (M=0.7)                                                                   |

| Fig. 4.14. Steady state operation of a three phase inverter with ripple in         |

| the dc bus $(f_r=6 \text{ pu})$ . (a) Output voltage under SPWM. (b) Harmonic      |

| spectrum. (c) Output voltage under RIC. (b) Harmonic spectrum. (M=0.7,             |

| <i>f<sub>sw</sub></i> =33pu)80                                                     |

| Fig. 4.15. Steady state operation of a three phase inverter with ripple in the     |

| dc bus $(f_r=6 \text{ pu})$ . (a) Output current under SPWM. (b) Harmonic spectrum |

| . (c) Output current under RIC. (b) Harmonic spectrum. (M=0.7,                     |

| <i>f<sub>sw</sub></i> =33pu)                                                       |

| Fig. 4.16. Total low-order harmonic distortion versus switching frequency          |

| for (a) SPWM. (b) Integral voltage control. (M=0.2 and 0.7)                        |

| Fig. 4.17. Total current harmonic distortion (%THD <sub>i</sub> ) versus switching |

| frequency with 10% 360 Hz ripple. (a) Sine PWM. (b) Integral voltage               |

| control. (M=0.7)                                                                   |

| Fig. 4.18. Harmonic reduction with RIC as a function of switching                  |

| frequency (a) $fr$ =6pu, $fsw$ =33pu (b) $f_r$ =6pu, $f_{sw}$ =63pu (c)            |

| $f_r$ =2pu $f_{sw}$ =33pu (d) $f_r$ =2pu $f_{sw}$ =63pu ( $k_r$ =0.1, $M$ =0.7)83  |

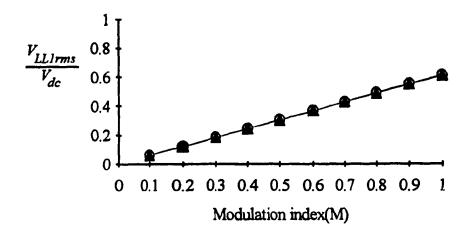

| Fig. 4.19. Transfer characteristics for the proposed pattern generator and         |

| SPWM                                                                               |

| Fig. 4.20. Intgrator output in a switching period with ripple in dc bus            |

| Fig. 4.21. Maximum modulation index $(M_{max})$ versus dc bus ripple factor 85     |

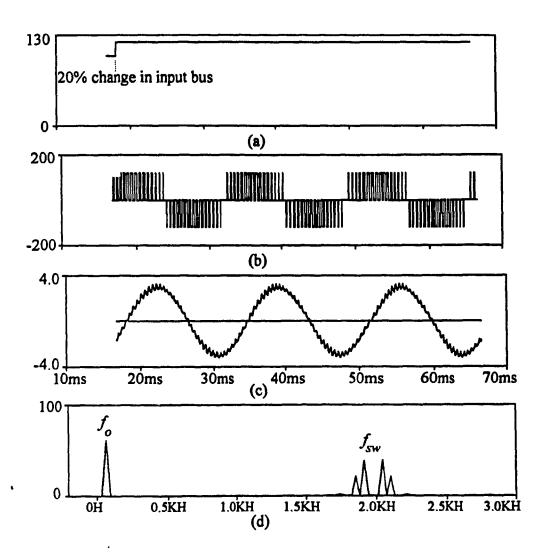

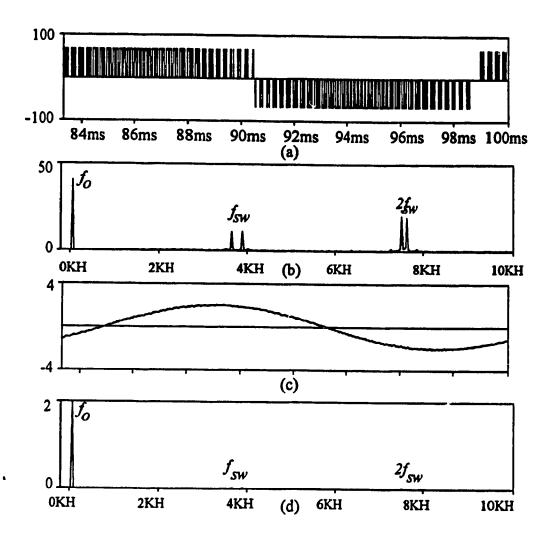

| Fig. 4.22. Response of the converter to a change in the input dc bus. (a)                |

|------------------------------------------------------------------------------------------|

| Input dc bus. (b) Line voltage. (c) Line current. (d) Harmonic spectra of                |

| the line voltage ( $M=0.7, f_{sw}=33$ pu)                                                |

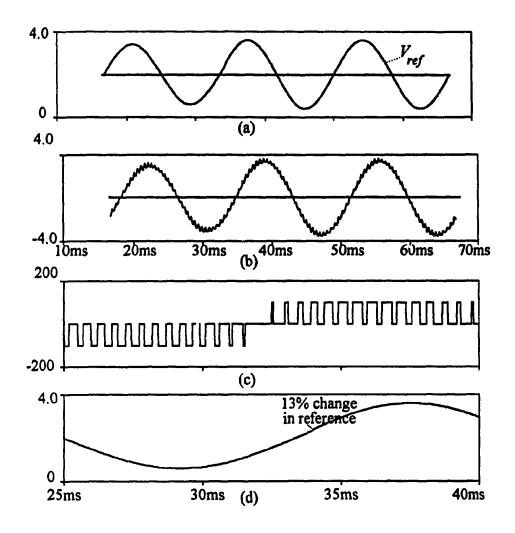

| Fig. 4.23. Response of voltage source inverter to a change in control                    |

| reference. (a) Control reference(Vref). (b) Line current. (c). Detailed view             |

| of line voltage. (d). Detailed view of control reference (13% change at                  |

| 34ms)                                                                                    |

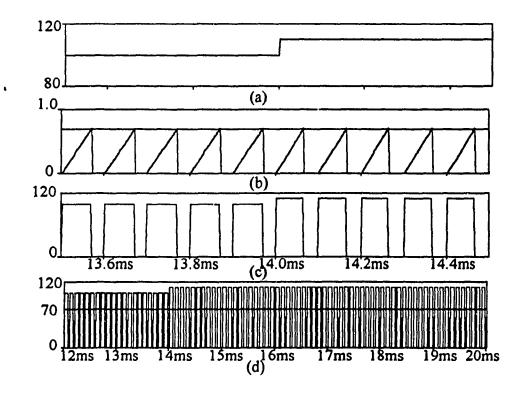

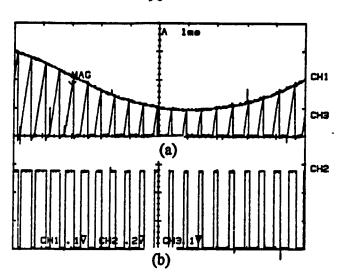

| Fig. 4.24. Control waveforms (a) Integrator output and control reference.                |

| (b) Gating signal for switch 1. ( $M=0.7, f_{sw}=33$ pu)                                 |

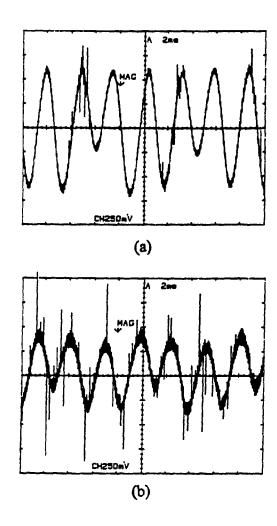

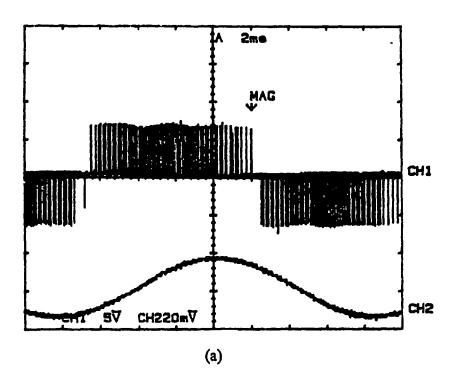

| Fig.4.25. (a) Experimental DC link voltage. (b) Inverter output line-line                |

| voltage. (c) Line current (f <sub>sw</sub> =33pu M=0.7)90                                |

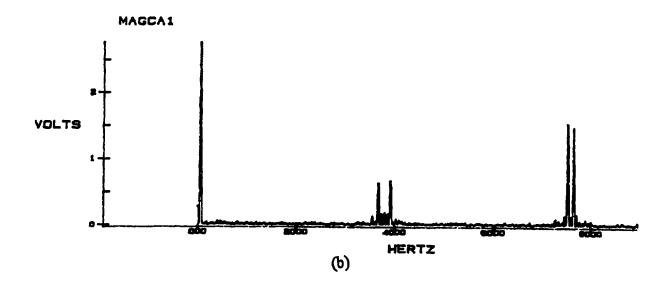

| Fig. 4.26. Experimental frequency spectra. (a) DC link voltage. (b)                      |

| Inverter output line-line voltage. (c) Line current. ( $f_{sw}$ =33pu $M$ =0.7)          |

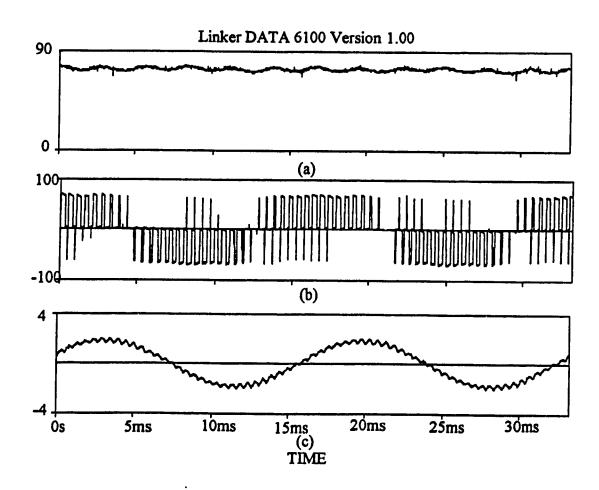

| Fig. 4.27. (a) Experimental DC link voltage with unbalance in the input.                 |

| (b) Inverter output line-line voltage. (c) Line current $(f_{sw}=33 \text{pu } M=0.7)92$ |

| Fig. 4.28. Experimental frequency spectra. (a) DC link voltage. (b)                      |

| Inverter output line-line voltage. (c) Line current. (f. =33pu M=0.7)                    |

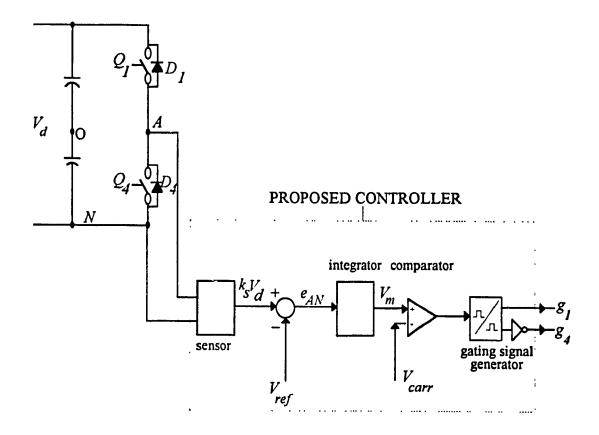

| Fig. 4.29. The proposed controller for a half bridge voltage source                      |

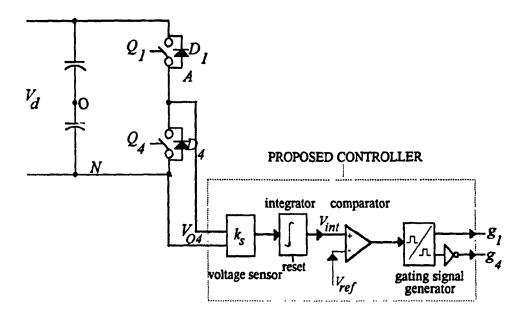

| inverter95                                                                               |

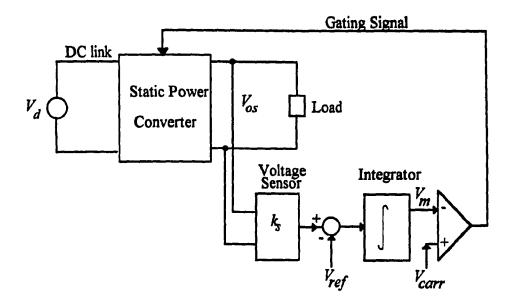

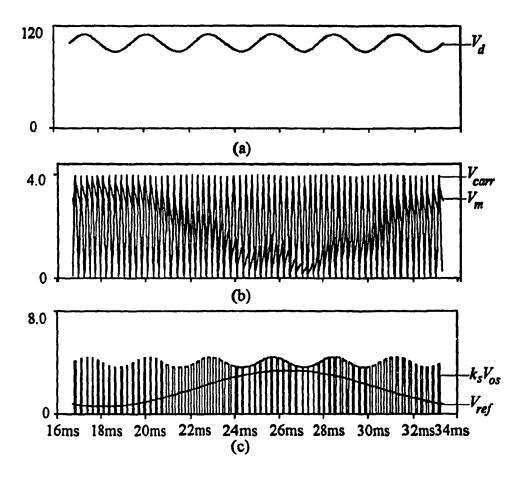

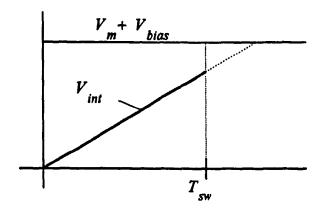

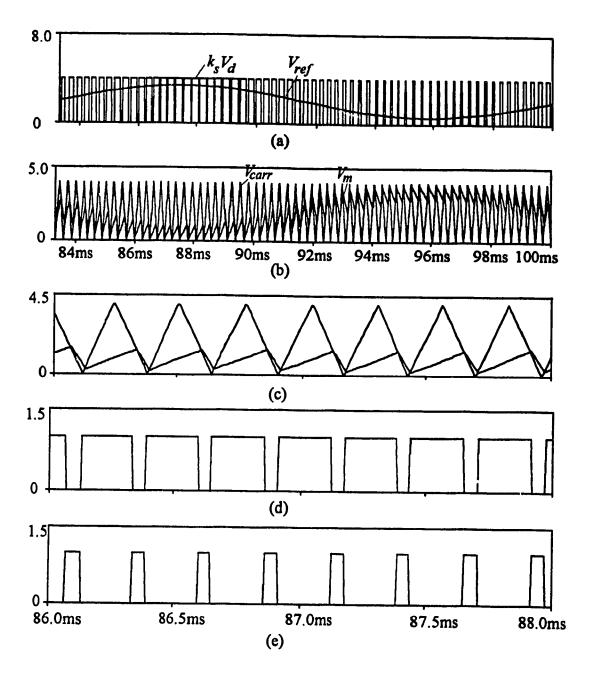

| Fig 4.30. Waveforms of a half bridge inverter. (a) Controller input $(k_s V_d)$          |

| and reference voltage $V_{ref}$ . (b) Modulation $(V_m)$ and carrier $(V_{carr})$        |

| waveforms. (c) Detailed view of the modulation and carrier waveform. (d)                 |

| Gating signal for the top switch.                                                        |

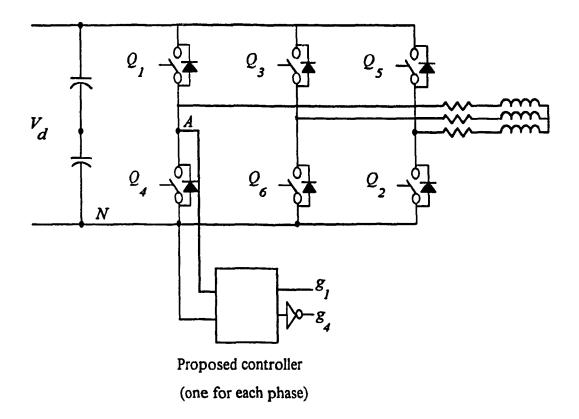

| Fig. 4.31. Proposed pattern generator for a three-phase inverter                         |

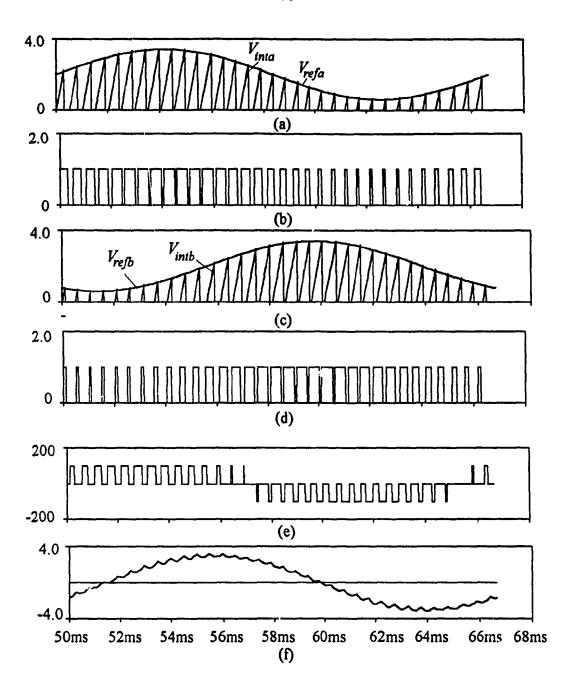

| Fig. 4.32 Control waveforms. (a) Modulation and carrier waveform phase                   |

| A. (b) Gating signal for switch $Q_{I}$ . (c) Modulation and carrier waveform            |

| phase B. (d) Gating signal for switch O <sub>2</sub>                                     |

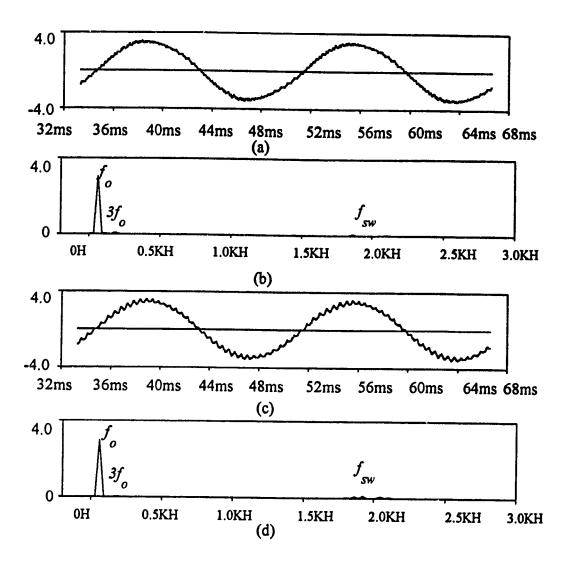

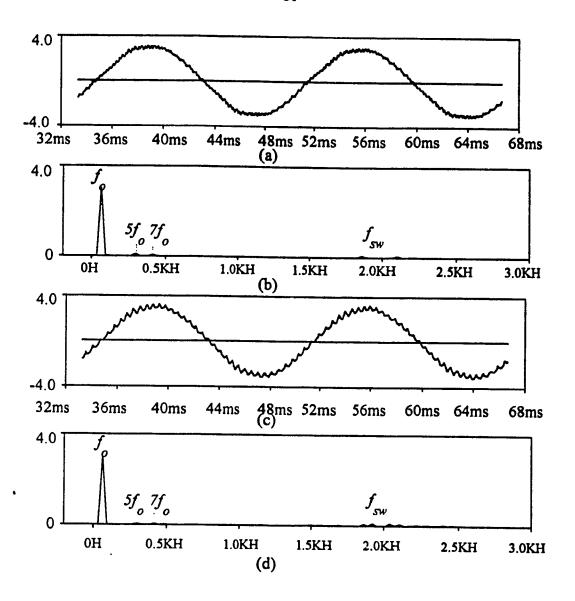

| Fig. 4.33. Waveforms for the three phase pattern generator. (a) Line                    |              |

|-----------------------------------------------------------------------------------------|--------------|

| voltage (b) Spectrum of line voltage (c) Line current (d). Spectrum of line             |              |

| current. (M=0.7 $f_{SW}$ = 3780Hz)                                                      | . <b>9</b> 9 |

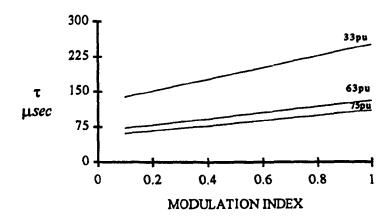

| Fig. 4.34. Integrator time constant versus modulation index                             | 102          |

| Fig. 4.35. Minimum recommended integrator time constant (for an ideal dc                |              |

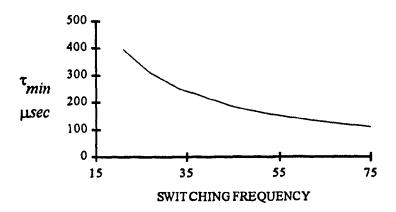

| bus) versus switching frequency.                                                        | 102          |

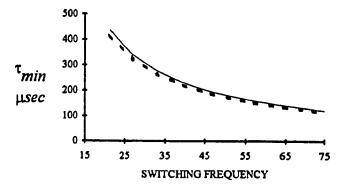

| Fig. 4.36. Minimum recommended integrator time constant (for an non-                    |              |

| ideal dc bus) versus switching frequency.                                               | 103          |

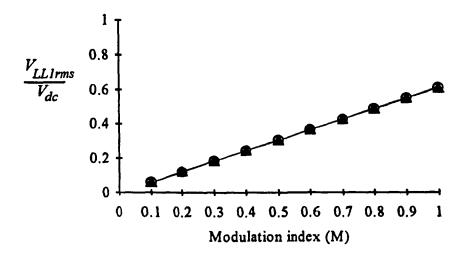

| Fig. 4.37. Transfer characteristics for the proposed pattern generator and              |              |

| SPWM                                                                                    | 105          |

| Fig. 4.38. Output line voltage harmonic spectra with an ideal dc bus under              |              |

| (a) SPWM. (b) Modulated Integral control. ( $f_{sw}$ =63pu $M$ =0.7)                    | . 105        |

| Fig. 4.39. % $THD_i$ with a typical inductive load $(R_i=10\Omega, L_i=16\text{mH})$ as |              |

| function of switching frequency with an ideal dc bus $(M=0.7)$                          | 106          |

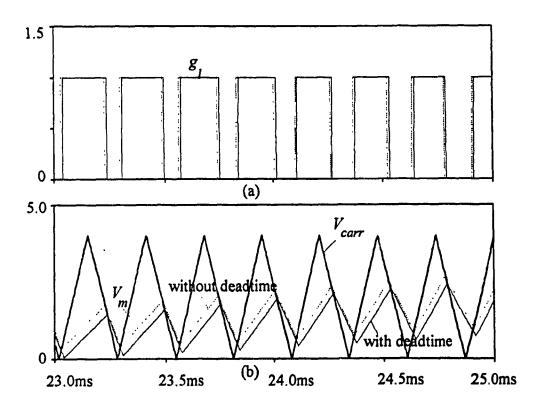

| Fig. 4.40. Dead time effect for negative direction of load current. (a)                 |              |

| Gating signal for top switch (with and without deadtimes). (b) Modulation               |              |

| $(V_m)$ and carrier $(V_{carr})$ waveforms.                                             | 107          |

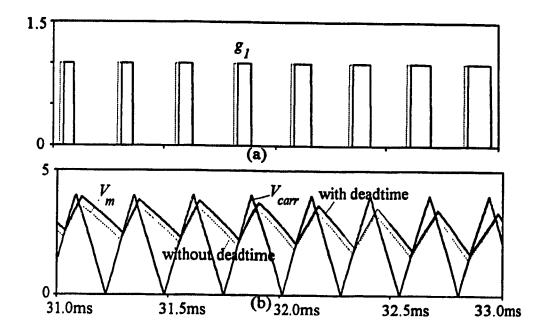

| Fig. 4.41 .Dead time effect for positive direction of load current. (a) Gating          |              |

| signal for top switch (with and without deadtimes). (b) Modulation $(V_m)$              |              |

| and carrier ( $V_{carr}$ ) waveforms.                                                   | 108          |

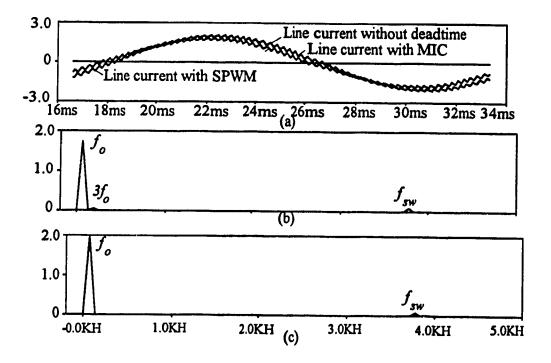

| Fig. 4.42. Deadtime effect in line current of a half bridge inverter. (a) Line          |              |

| current (b) Harmonic spectrum of line current with SPWM. (b) Harmonic                   |              |

| spectrum of line current under Modulated integral control (M=0.5,                       |              |

| <i>f<sub>sw</sub></i> =63pu)                                                            | . 108        |

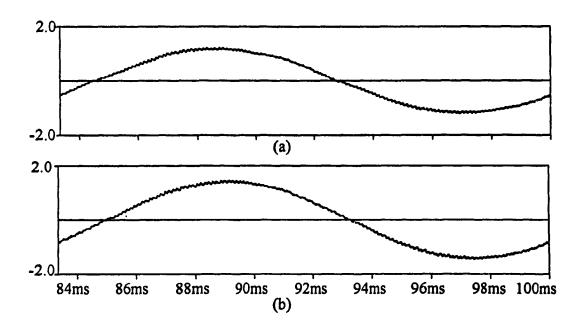

| Fig. 4.43. Line current in three phase inverter with deadtime effects. (a)              |              |

| SPWM (b)Mod. Int. Control. ( $M=0.5$ , $f_{m}=63$ nu. deadtime =10usec)                 | 100          |

| Fig. 4.44. Line voltage with deadtime effects. (a) SPWM (b) Mod. Int.              |

|------------------------------------------------------------------------------------|

| Control. ( $M$ =0.5, $f_{SW}$ = 63pu, deadtime =10 $\mu$ sec)                      |

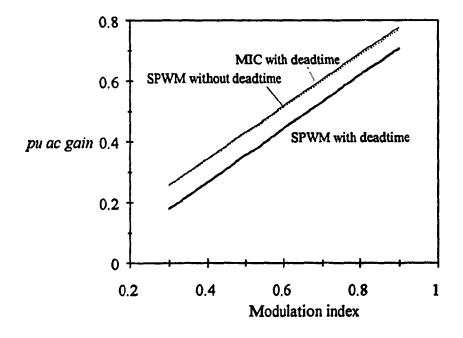

| Fig. 4.45. pu ac gain versus modulation index (with and without dead               |

| time)                                                                              |

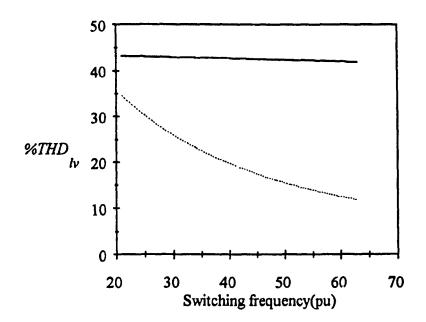

| Fig. 4.46. Total low-order harmonic distortion (% $THD_{lv}$ ) versus              |

| switching frequency. ( $M=0.7, f_r=6$ pu, $k_r=0.1$ )                              |

| Fig. 4.47. Total low-order harmonic distortion (%THD <sub>lv</sub> ) versus        |

| switching frequency. ( $M=0.7, f_r=6$ pu, $k_r=0.1$ )                              |

| Fig. 4.48. Total current harmonic distortion (%THD <sub>i</sub> ) versus switching |

| frequency with 10% 360 Hz ripple (M=0.7)                                           |

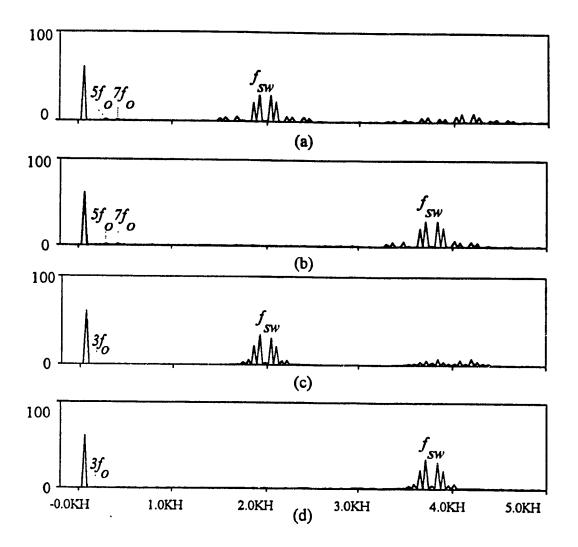

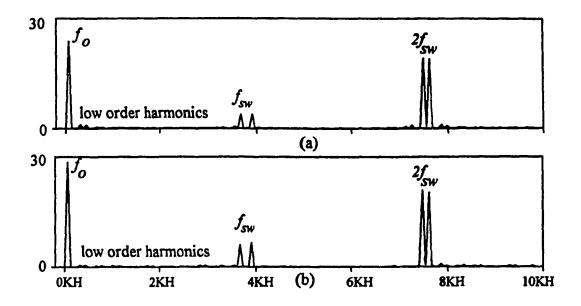

| Fig. 4.49. Line voltage spectra under (a) Mod. Int. Control ( $f_r$ = 6pu) (b)     |

| SPWM ( $f_r$ =6pu). (c) Mod. Int. Control ( $f_r$ =2pu) (d) SPWM (fr=2pu)          |

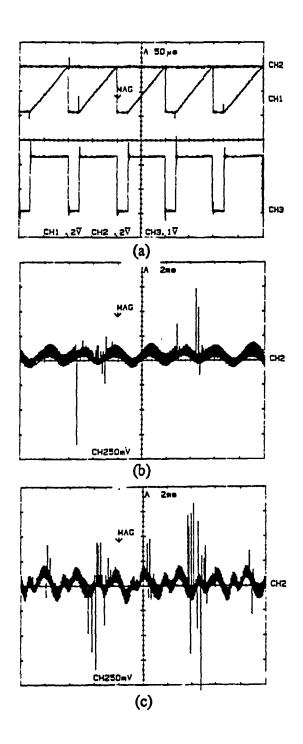

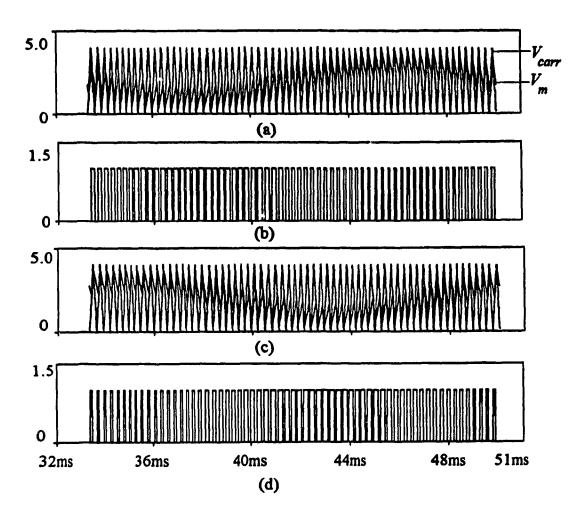

| Fig. 4.50. Control waveforms for modulated integral control. (a) Triangular        |

| carrier and modulating waveform. (b) Detailed view of control waveforms.           |

| (c) Voltage across the bottom switch $(M=0.6, f_{SW}=3780 \text{ Hz})$             |

| Fig. 4.51. Inverter waveforms for balanced operating conditions. (a) Line          |

| voltage and line current. (b). Harmonic spectrum of the line voltage 116           |

| Fig. 4.52. Inverter waveforms for unbalanced operating conditions. (a)             |

| Line voltage and line current. (b). Harmonic spectrum of the line voltage 117      |

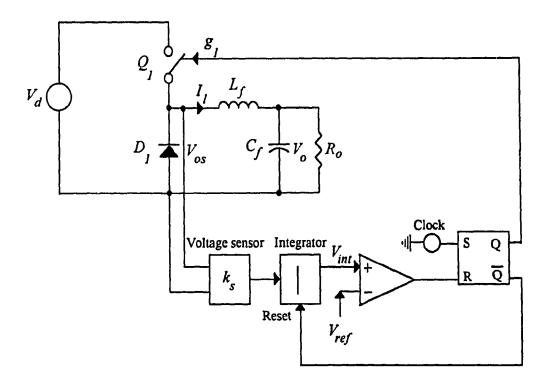

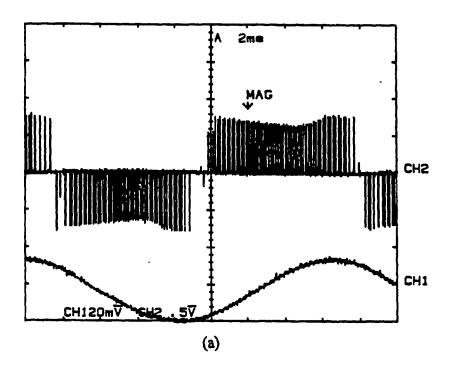

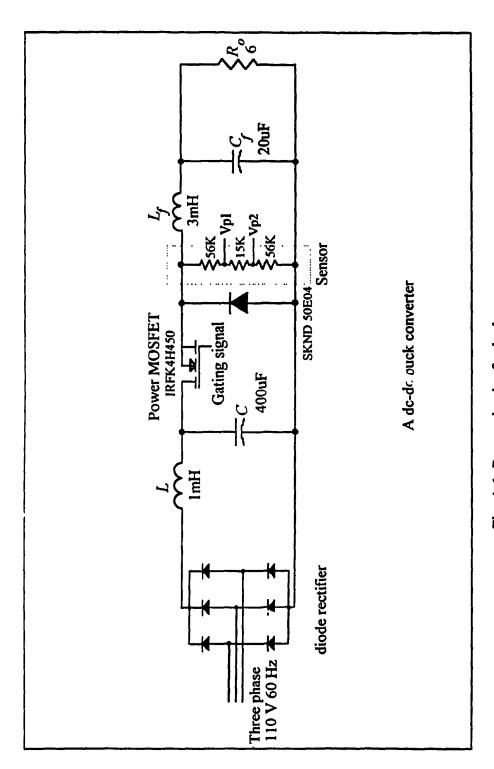

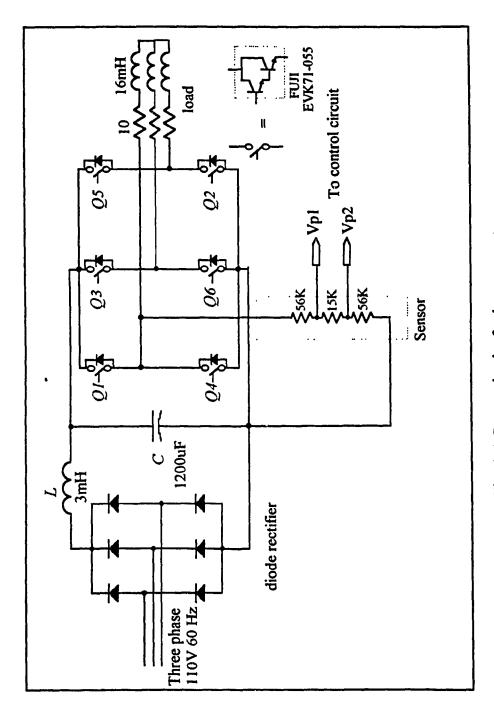

| Fig. A.1. Power circuit of a dc-dc converter                                       |

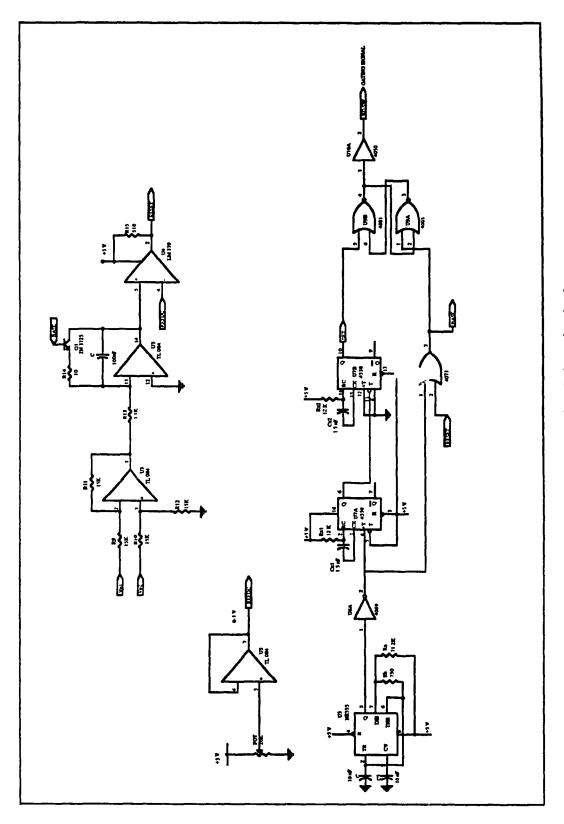

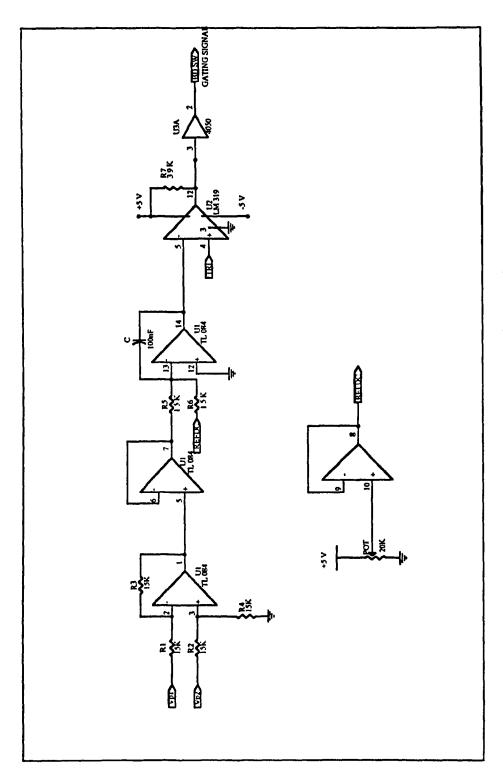

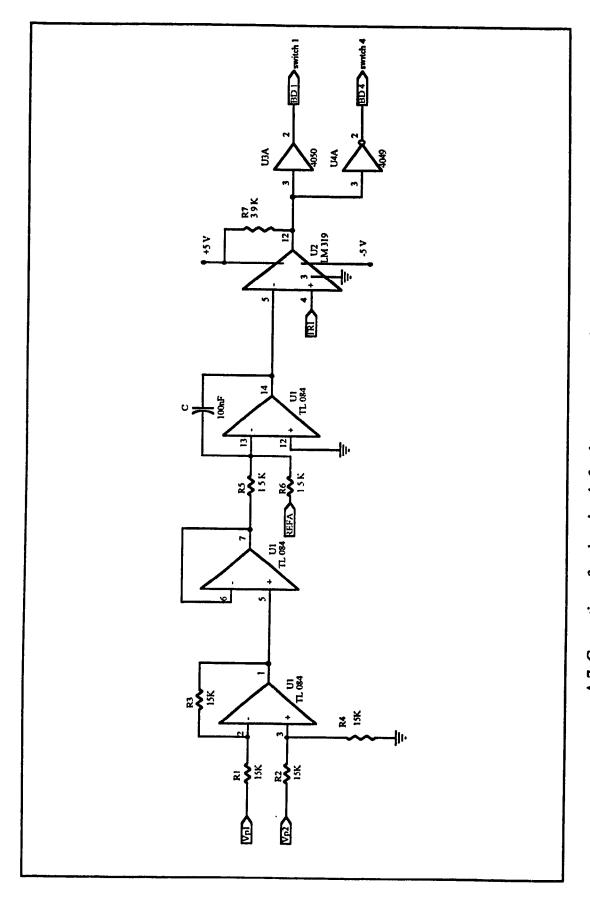

| Fig. A.2. Reset integral control technique for dc-dc converter 127                 |

| Fig. A.3. Modulated integral control technique for dc-dc converter 128             |

| Fig. A.4. Power circuit of a dc-ac converter                                       |

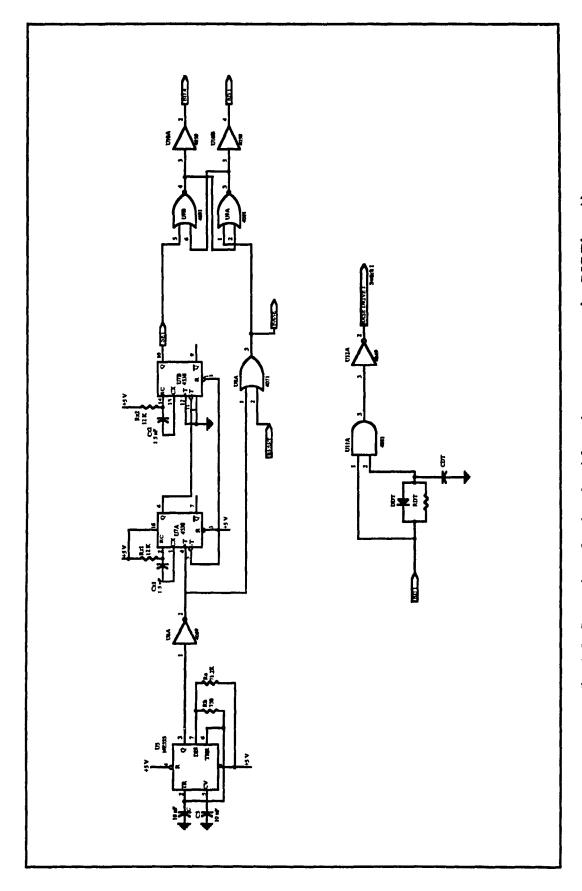

| Fig. A.5. Generation of gating signal for dc-ac converter using RIC-Phase A 130    |

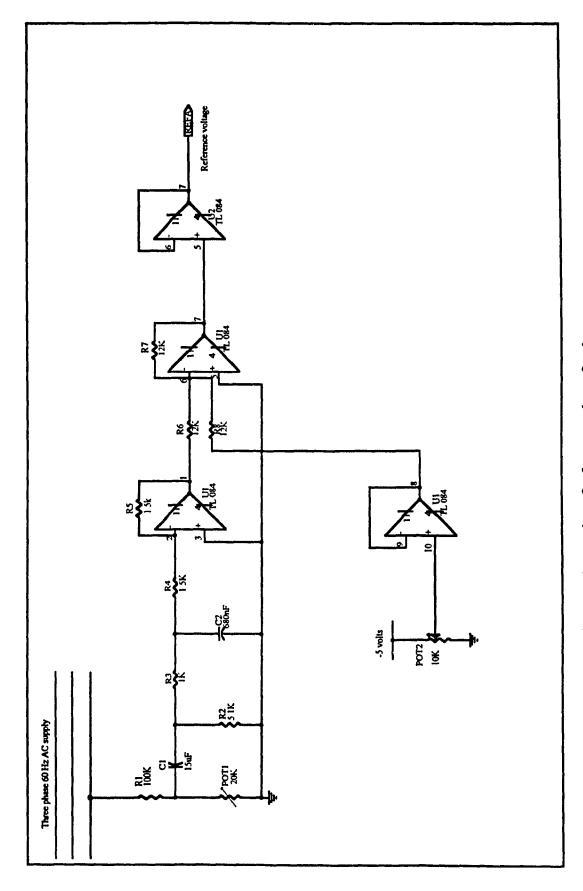

| Fig. A.6. Generation of reference voltage for dc-ac converter                      |

| Fig. A.7. Generation of gating signal for dc-ac converter using MIC-Phase A 132    |

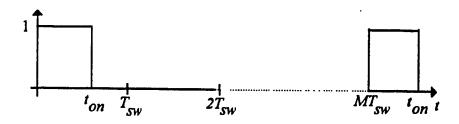

| Fig. A.8. First pulse with periodicity of $MT_{\text{sw}}$                         |

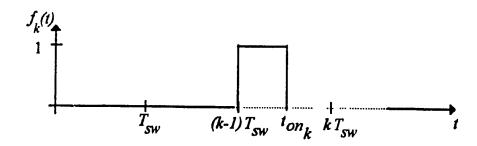

| Fig. A.9. Pulse in the general kth interval                                  | 133 |

|------------------------------------------------------------------------------|-----|

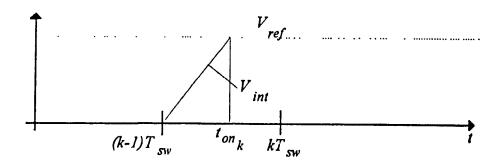

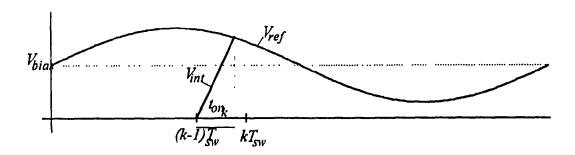

| Fig. A.10. Output of integrator in any $k^{th}$ interval to determine the on |     |

| time(t <sub>onk</sub> )                                                      | 134 |

| Fig. A.11. Computation of switching function for modulated integral          |     |

| control                                                                      | 135 |

| Fig. A.12. Determination of on time for a general pulse in the kth interval  | 138 |

| Fig. A.13. Switching function for phase A, $f_a(t)$ . (a) Mathematically     |     |

| computed. (b) Computer simulation ( $f_{SW}$ =33pu, $M$ =0.7)                | 140 |

# LIST OF TABLES

| TABLE I. | EFFECT OF DC  | BUS RIPPLE ON INVERTER | OUTPUT | 6 |

|----------|---------------|------------------------|--------|---|

| TABLE I  | I. PROPERTIES | OF SWITCHING DEVICES   |        | 8 |

## LIST OF ACRONYMS

OVI output voltage integral

RIC reset integral control

MIC modulated integral control

EPROM erasable programmable read only memory

PWM pulse width modulation

SPWM sine pulse width modulation

VSI voltage source inverter

A/D analog to digital

D/A digital to analog

GTO gate turn off thyristor

BJT bipolar junction transistor

MOSFET metal oxide field effect transistor

IGBT insulated gate bipolar transistor

CC compensation circuit

PG pattern generator

PECAN power electronic analyis program

kW unit of real power

kVA unit of apparent power

# LIST OF PRINCIPAL SYMBOLS

| C              | dc link filter capacitor                                   |

|----------------|------------------------------------------------------------|

| L              | dc link filter inductor                                    |

| $C_f$          | output filter capacitor in dc-dc converter                 |

| $L_f$          | output filter inductor in dc-dc converter                  |

| $R_o$          | load resistance in dc-dc converter                         |

| $R_l$          | load resistance in dc-ac converter                         |

| $L_l$          | load inductance in dc-ac converter                         |

| $f_{sw}$       | switching frequency                                        |

| $T_{sw}$       | switching period                                           |

| $f_i$          | input ac line frequency                                    |

| $f_o$          | inverter fundamental frequency                             |

| D              | duty cycle of a dc-dc converter                            |

| $D_{max}$      | maximum duty cycle                                         |

| $V_d$          | dc link voltage                                            |

| $V_{dc}$       | mean dc link voltage                                       |

| $f_r$          | dominant ripple frequency                                  |

| $k_r$          | dc bus ripple factor                                       |

| $V_{ol}$       | output voltage of dc-dc converter without switching delay  |

| $V_{o2}$       | output voltage of dc-dc converter with switching delay     |

| $\Delta V$     | equivalent dead time voltage                               |

| $M_n$          | number of switchings per cycle                             |

| t <sub>d</sub> | dead time interval                                         |

| $V_{AN}$       | voltage across the bottom switch in a half bridge inverter |

| $i_A$          | phase current in a half bridge inverter                    |

|                |                                                            |

# xxiii

| $V_c$         | carrier waveform                         |

|---------------|------------------------------------------|

| $V_m$         | modulating waveform                      |

| $SW_{II}$     | line switching function                  |

| $\Delta t$    | sampling interval                        |

| t             | time                                     |

| ton           | on time of the switch                    |

| toff          | off time of the switch                   |

| $S_I$         | area under the reference voltage         |

| $S_2$         | area under output voltage pulse          |

| $V_{int}$     | integrator output                        |

| $V_{ref}$     | reference voltage                        |

| $V_{os}$      | output voltage of a dc-dc converter      |

| $V_o$         | load voltage of a dc-dc converter        |

| $I_l$         | inductor current                         |

| $k_s$         | sensor gain                              |

| $V_{carr}$    | triangular carrier                       |

| τ             | integrator time constant                 |

| $	au_{min}$   | minimum integrator time constant         |

| $V_{ref,max}$ | maximum reference voltage                |

| $P_o$         | output power                             |

| $R_i$         | % maximum current ripple                 |

| $R_{\nu}$     | % maximum voltage ripple                 |

| f(t)          | switching function                       |

| $K_h$         | harmonic attenuation factor              |

| $m_r$         | rising slope of the modulating waveform  |

| $m_f$         | falling slope of the modulation waveform |

|               |                                          |

slope of the carrier waveform

$m_c$

### xxiv

| $V_{con,Q1}$ | conduction drop of switch Q1 |

|--------------|------------------------------|

|--------------|------------------------------|

$V_{bias}$  dc bias voltage

$V_{refa}$  reference voltage for Phase A.

$V_{refb}$  reference voltage for Phase B.

$V_{refc}$  reference voltage for Phase C.

M modulation index

M<sub>max</sub> maximum modulation index

THD<sub>i</sub> Total harmonic distortion in the line current

THD<sub>lv</sub> Low order harmonic distortion in the line voltage

V<sub>LL1(rms)</sub> fundamental line rms voltage

kac voltage gain

$k_{ac,ideal}$  voltage gain at unity modulation index

$e_{AN}$  error voltage

$f_k(t)$  switching function of the  $k^{th}$  pulse

C(n,k) Fourier coefficient

$\theta_{on,k}$  pulse width in the  $k^{th}$  interval in radians

$f_a$  switching function for phase A

$f_b$  switching function for phase B

$f_{ab}$  line switching function

#### CHAPTER 1

#### INTRODUCTION

#### 1.1. Introduction

Power Electronics[1][2][3] is associated with conversion and control of electrical power at high efficiencies and has found widespread use in industrial, commercial, residential, military and aerospace applications. A modern power electronic equipment, referred to as a Static Power Converter (because it contains no moving parts), comprises of power semiconductor devices that handle the electrical power under the guidance of control signals obtained from electronic chips.

In many application a dc input voltage is required for a converter. Static power converters of this type can be classified in two categories:

- dc to dc converter (chopper). It converts unregulated dc voltage to regulated dc voltage at different levels[4]. PWM dc-dc converters are being widely used in switch mode dc power supplies[5] and in motor drive applications[6].

- dc to ac converter (inverter). It can be either voltage fed or current fed and generates a variable magnitude, variable frequency ac output. PWM inverters provide linear control of output fundamental voltage and frequency and are being widely used in ac motor drive control[7][8], UPS systems and induction heating.

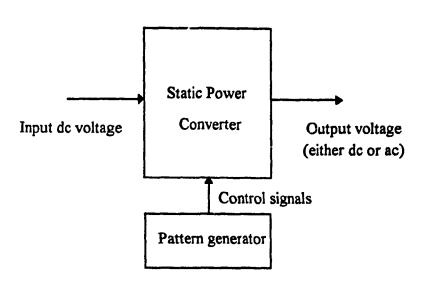

This thesis focuses on improving the performance of dc to dc and dc to ac converters by proposing voltage controlled PWM pattern generators. A generalized converter system is shown in Fig. 1.1.

Fig. 1.1. A typical dc-dc or dc-ac power electronic converter system

#### 1.2. Problem definition

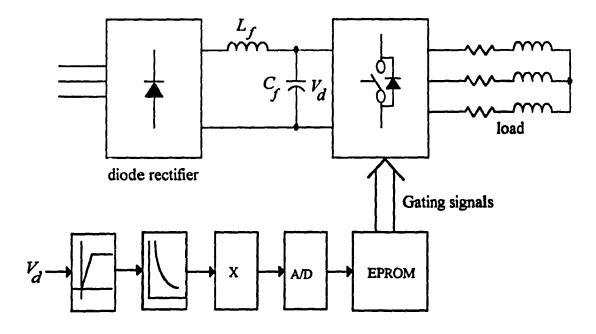

The dc input to most PWM converters is obtained by rectifying three phase ac line voltage with the help of a three phase diode bridge and is shown in Fig 1.2. A front end diode rectifier is preferred because it is rugged in nature, requires no external control and thereby reduces the cost in low and medium power applications and wherever regeneration capability is not desired.

A second order dc link filter comprising of passive elements like inductors and capacitors is used to attenuate the harmonics inherent in rectification. It is assumed that a well designed filter can establish a fixed, ripple free dc link voltage. This is the input to the power converter which is transformed into the required form.

It is also assumed that the semiconductor devices in the power converter configuration are ideal, i.e., they switch on or off at the precise instants the control signal dictates them to.

In a practical system these conditions are not always satisfied. Conventional PWM pattern generators in [9][10][11][12][13][14] overlook this fact while analyzing power

Fig. 1.2. A PWM converter (dc/dc or dc/ac) with a front-end diode rectifier

converters. Thus the performance of such converters is degraded and the quality of the output voltage is not as high as that predicted in [15][16][17][18].

Subsequent sections point as to why these assumptions are not valid and should not be ignored in analysis. A prior knowledge can result in a better and reliable design.

## 1.2.1 Ripple in dc link voltage

In a practical converter system, dc link voltage cannot be assumed to be ripple free. This section discusses the cause of the ripple and its impact on the performance of PWM converters.

# 1.2.1.1. Cause of ripple

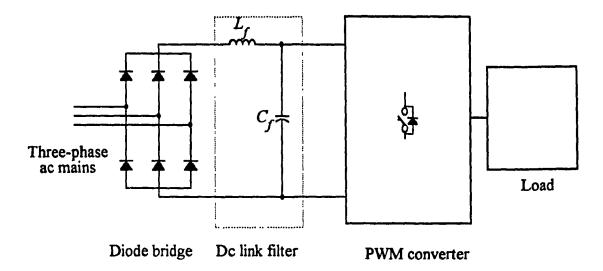

The notion of a ripple free dc link voltage is based on the filtering capability of a dc link filter. For a good performance the break frequency of the filter is chosen to be almost a decade below the expected lowest dominant harmonic inherent in rectification. As has been discussed in [19], the dc link voltage created with an uncontrolled front end diode bridge has characteristic harmonics of the order of  $6nf_i$ ,  $f_i$  being the input line frequency.

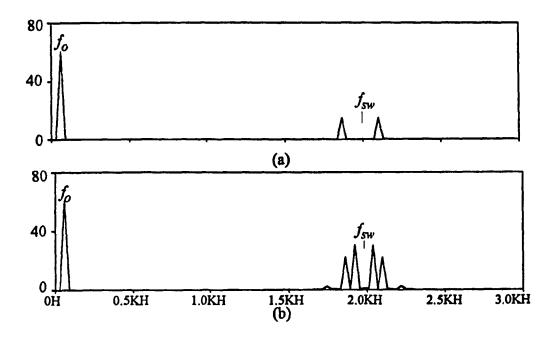

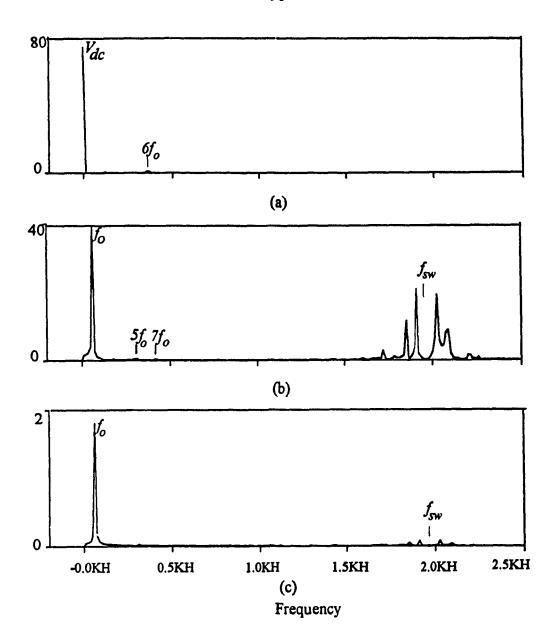

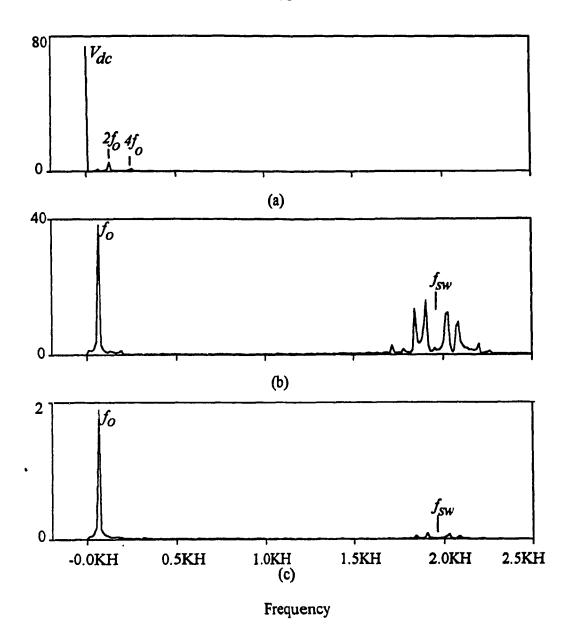

Fig. 1.3. DC bus spectrum. (without an input filter) (a) Balanced input supply. (b)

Unbalanced input supply  $(f_i)$ : ac supply frequency)

Furthermore an unbalance in ac input supply results in additional harmonics of the order of  $2nf_i$ . This is illustrated in the DC bus harmonic spectra of Fig. 1.3. For an ac line frequency of 60 Hz (1 pu), the dominant characteristic harmonics are the 120 Hz (2 pu) and 360 Hz (6 pu). Also unbalanced and non-linear loads result in waveforms distortions, leading to pollution of dc link with uncharacteristic harmonics.

Thus to obtain a ripple free dc link voltage, a filter with a break frequency that can reduce the low frequency harmonics will result in large values of L and C. This leads to a bulky dc link filter which increases the size of converter, slows the response of the system and reduces the overall efficiency. This is illustrated by designing the break frequency of the filter to be at 12 Hz. Choose  $C=10000\mu\text{F}$ . The value of L calculated, is 211 mH, which is very large and impractical. Thus a compromise has to be reached between the size of the filter components and the overall effectiveness of the filter.

It is therefore very difficult to design an input filter which could provide adequate filtering to harmonics present in the dc link voltage and yet have a reasonable size. Thus in a converter system, dc link voltage ripple cannot be ignored in the analysis.

## 1.2.1.2. Impact of low frequency ripple on converter performance

As discussed in the previous section, there is a substantial low-frequency voltage ripple on the dc link and cannot be neglected in the harmonic analysis of PWM converters. A qualitative analysis can be provided by assuming the ripple to be of a single dominant frequency,  $f_r$ .

The ripple in the dc link is the main cause of appearance of harmonics in the converter output not present in the PWM switching function. This increases the harmonic distortion in the output voltage and is hence undesirable.

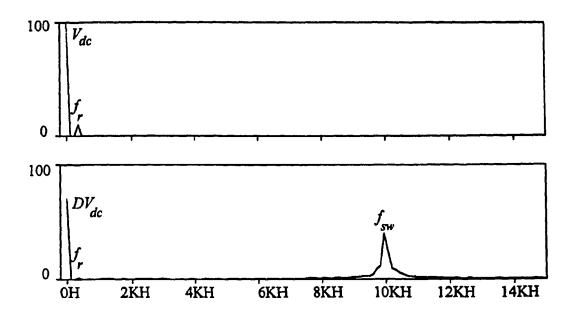

In PWM dc-dc converters, the output filter is designed to attenuate switching harmonics and for a good performance the cut-off frequency is chosen to be a decade below the operating frequency  $(f_{Sir})$ . Since the dc-dc converters are usually operated in the range of 10 kHz and greater, the cut off frequency is much greater than the ripple frequency. Therefore there is virtually no attenuation to the ripple frequency which appears in the output dc voltage deteriorating the quality of the output voltage. This is illustrated in the harmonic spectrum of the output voltage of a dc-dc converter working with a non-ideal dc bus (Fig. 1.4). The ripple frequency which is 360 Hz, appears in the output and increases the distortion in the output voltage.

Fig. 1.4. Output voltage spectrum of a dc-dc converter working under non-ideal dc bus.

$$(f_{SW}=10 \text{ kHz}, D=0.7, f_r=360 \text{ Hz})$$

In PWM dc-ac converters, operating at a fundamental frequency of  $f_0$ , ripple in the dc bus causes low order harmonics at  $(f_r \pm f_0)$  to appear in the inverter output. These harmonics are difficult to filter and increase the harmonic distortion. These can become an issue in motor drive applications in which the inverter frequency is varied over a range and the subharmonics in inverter output can degrade the performance of the drive system. The effect of a typical inverter operating frequency (60Hz) on the harmonic content of the output voltage has been summarized in Table I.

TABLE I

| EFFECT OF DC BUS RIPPLE ON INVERTER OUTPUT |                             |                                               |             |  |

|--------------------------------------------|-----------------------------|-----------------------------------------------|-------------|--|

| Inverter output<br>frequency(Hz)           | DC bus ripple frequency(Hz) | Low order harmonics<br>in inverter output(Hz) |             |  |

| f <sub>o</sub>                             | $f_r$                       | S <sub>r</sub> S <sub>0</sub>                 | $f_r + f_o$ |  |

| 60                                         | 120                         | 60                                            | 180         |  |

| 60                                         | 360                         | 300                                           | 420         |  |

Fig. 1.5. Output voltage spectra of a dc-ac converter working under non-ideal dc bus. (a)  $f_r$ =120 Hz (b)  $f_r$ =360 Hz.

For a inverter operating at a fundamental frequency of 60 Hz (1 pu) and subject to  $f_r=2$  pu, the low order harmonic is 3 pu (Fig. 1.5(a)). With dominant ripple frequency  $f_r=6$  pu, the low order harmonics in the line voltage are 5 pu and 7 pu (Fig. 1.5(b)).

## 1.2.2. Non-ideal power semiconductor devices

A power semiconductor device is assumed to provide processing of electrical power under ideal switching action i.e. with zero switching delays and conduction drops. However, a practical switching device takes a finite amount of time to turn-on and turn off, resulting in switching delays. Also any power device while conducting has a finite on-state resistance resulting in switch conduction drops.

An excellent review of the state-of-the-art devices and their characteristics in [20][21][22], reveals the non-ideal nature of semiconductor devices. Table II summarizes

a few important characteristics often neglected in conventional pattern generators and addressed in this thesis. The values specified are at rated current and voltage levels for typical commercially available devices.

TABLE II [20][21][22]

PROPERTIES OF SWITCHING DEVICES

| Characteristics                     | Thyristor | Triac | GTO | Darlington<br>BJT | MOSFET | IGBT |

|-------------------------------------|-----------|-------|-----|-------------------|--------|------|

| Conduction drop(V) at rated current | 1.9       | 1.4   | 4   | 1.9               | 3.2    | 3.2  |

| Turn on time<br>(μs)                | 1.1       | 1.7   | 4   | 1.7               | 0.09   | 0.9  |

| Tum off time<br>(μs)                | 220       | 200   | 10  | 5                 | 0.14   | 1.4  |

It can be inferred from Table II that a practical power conductor device has finite turn-on and turn-off times and conduction losses. Thus at high power, the output voltage (dc voltage in dc/dc converters and fundamental ac voltage in dc/ac converters) shows a considerable deviation from the desired value. Also in single/three phase voltage source inverters, finite turn-off times may cause a short circuit of the dc link at the instant of switch over. Thus dead times [23][24], have to be introduced in the gating signal to avoid shorting of dc link. Introducing dead times is detrimental to the performance of the voltage source inverters. These aspects are discussed in following sections.

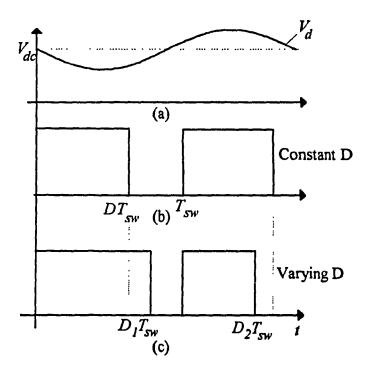

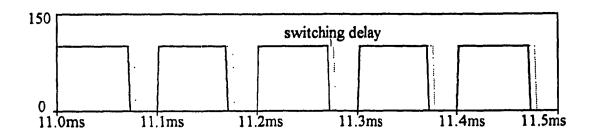

## 1.2.2.1. Effect of switching delay in DC/DC PWM converters

The effect of finite switching delays on the performance of dc-dc converters can be analyzed with respect to Fig. 1.6. As seen the switch turns-off after a certain time delay from the instant it was commanded by the desired gating signal. This results in extra volt seconds at the output of the converter which increases the mean dc voltage( $V_{o2}$ ) when the desired output is  $V_{o1}$ . This performance is undesirable and can be of significant concern when the device has a greater turn-off time.

Fig. 1.6. Effect of switching delay in dc-dc converters. (a) Ideal gating signal for the power switch. (b) Output voltage with and without switching delay.

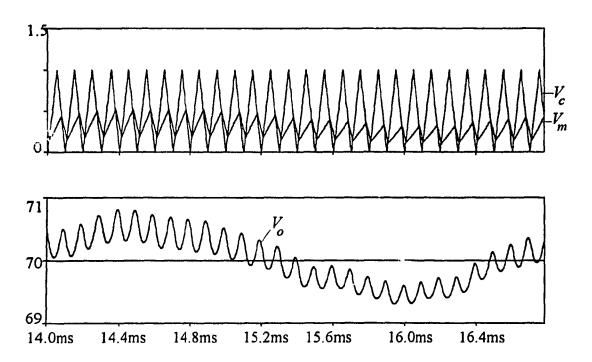

## 1.2.2.2. Effect of dead times on output voltage in PWM inverters

As discussed in section 1.2.2, because of the finite turn-off and turn-on times associated with a switching device, dead times have to be introduced in the gating signals of a voltage source inverter to prevent short circuit of the dc link. Introducing time delays

guarantees safe operation of the converter. A switch is turned off at the predefined switching instant. However the turn-on of the switch in the same inverter leg is delayed by dead time  $t_{\Delta}$ , which is typically 10-20 µsec.

Although the dead times are very short, they adversely affect the performance of the inverter. It results in a momentary loss of control causing deviations from precisely designed PWM signal. Since this is repeated over the switching period, the accumulated error may become significant in inverters operating at very high frequency.

A half bridge inverter is used to analyze the effect. The output voltage  $(V_{AN})$  for ideal and delayed base drive signals with positive and negative current directions are shown in Fig. 1.7.

As seen from the Fig. 1.7, each pulse of the output voltage is either shortened or lengthened by an amount according to whether the direction of the phase current is positive or negative respectively.

The average deviation over a half cycle from [23] is given by

$$\Delta V = \frac{M_n \ t_{\Delta} V_{dc}}{T_{sw}} \tag{1.1}$$

where  $M_n$  is the number of switching per cycle,  $V_{dc}$  is the dc link voltage  $T_{sw}$  is the switching period,  $t_{\Delta}$  is the dead time interval

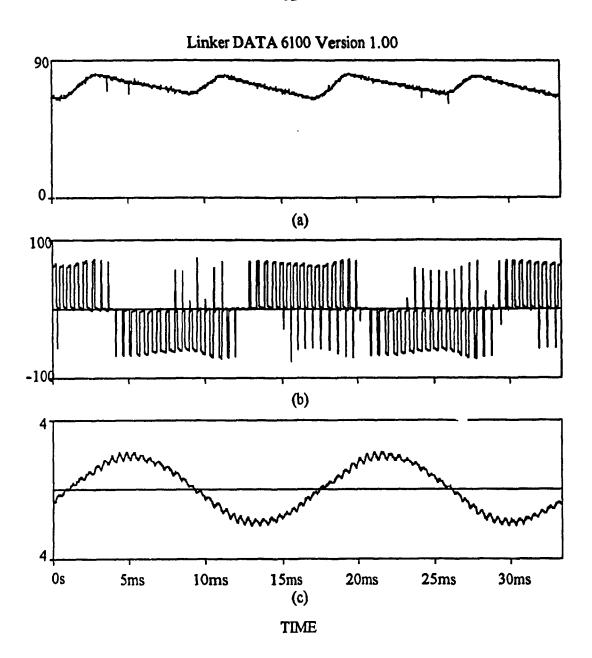

Thus the overall effect of the dead time can be studied by considering it as an addition of a square wave of magnitude  $\Delta V$  and  $180^{\circ}$  out of phase with the load current to the fundamental output voltage. A sample program was run in MCAD[43] and the results for a case without dead times is shown in Fig. 1.8. With a 10 $\mu$ sec dead time introduced in the analysis the results obtained from MCAD are shown in Fig. 1.9. There is appearance of low order harmonics of the order  $4m\pm l$  (m=1,2,3...). Also the fundamental voltage gain is lowered by 7.2%.

Fig. 1.7. Dead time effects in a half bridge inverter

Fig. 1.8. Ideal PWM switching, no dead time. (a) Output voltage. (b) Harmonic Spectra

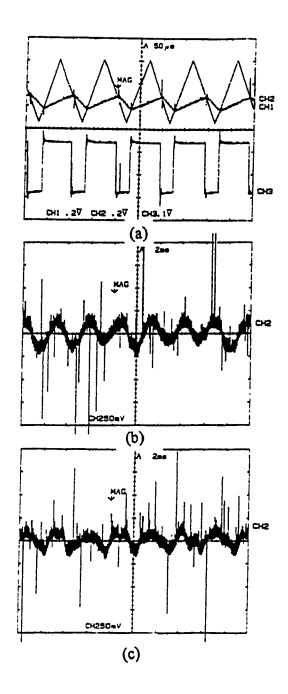

Fig. 1.9. Dead time of 10µsec in gating signals. (a) Load Current and equivalent dead time voltage. (b) Output voltage (excluding the switching harmonics). (c) Harmonic spectrum of the output voltage.

# 1.3. Review of previous research

In this section, a review of literature addressing the problems of non-ideal dc bus and switching delays in power converters is presented.

# 1.3.1. Feedforward techniques

It is important to realize that input source harmonics and disturbances are generated prior to the switching converter. Voltage feedforward techniques[25], make use of this feature and try to provide corrective action in the gating signals even before they propagate to the output voltage. This can provide better input harmonic/disturbance rejection.

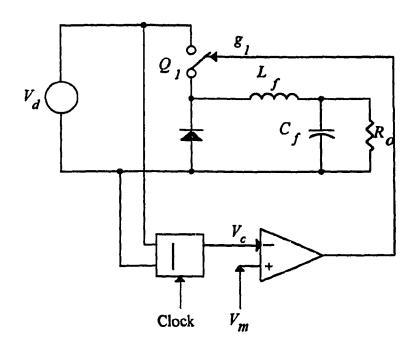

Fig. 1.10. A feedforward dc-dc buck converter

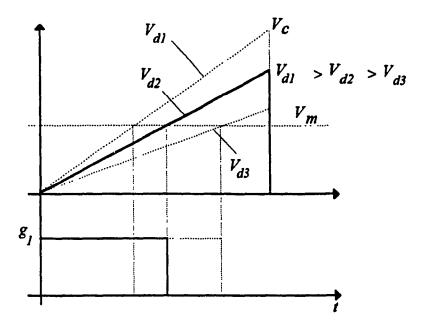

A typical feedforward loop in a dc-dc converter is shown in Fig. 1.10. The input voltage is directly sensed and passed through a integrator to generate the sawtooth ramp. It functions exactly like a direct-duty cycle control with one main exception: the sawtooth ramp is not constant in magnitude and is a function of the instantaneous input voltage. If the input is higher, the slope is higher and vice-versa. If control voltage is fixed, the duty cycle varies inversely with the input voltage resulting in a constant volt-second product. This is illustrated in Fig. 1. 11 which shows the ramp waveform for different input conditions  $(V_d)$ .

Fig. 1. 11. Effect of a feedforward loop on ramp carrier and switch control signal

Feedforward techniques have been documented in literature. An optimal feedforward compensation [26] was applied to dc-dc converters to reduce dc audio susceptibility. In [27], feedforward control was used to eliminate the input filter interaction with the feedback loop. However none of the above references quantify the harmonic rejection ability of the feedforward loop. Also conventional feedforward schemes based on input voltage sensing cannot compensate for non-ideal switches.

A feedforward technique that determines the exact switching function to eliminate harmonics is the objective of [28]. It is based on input voltage sensing and then determining the gating pulses for the converter switch. The technique however fails to correct for non-ideal conditions present in the switching environment.

In [29], a novel approach (One-cycle control) in controlling switching converters is proposed. In this technique the gating pattern is generated by sensing the voltage across the free-wheeling diode. Potential applications of the technique are identified but not quantified. Design guidelines are not specific. Based on this technique, a modified

feedforward loop is presented in this thesis for a dc-dc converter which can provide better performance than conventional feedforward scheme.

A feedforward technique (Fig. 1.12), involving sensing of the dc voltage is proposed in [30] to eliminate the effect of input dc bus ripple in dc-ac converters. The input dc bus voltage is expressed as:

$$V_d = V_{dc} + k_r V_{dc} \sin(2\pi f_r t)$$

(1.2)

where  $f_r$  is the dominant ripple frequency present in the dc bus.

This technique generates a new switching function  $(\overline{SW_{lln}})$  and is obtained by:

$$\overline{SW_{lln}} = \frac{1}{1 + k_r \sin(\omega_r t)} \overline{SW_{ll}}$$

(1.3)

where  $\overline{SW_{II}}$  is the line switching function[31].

The new switching function can thus eliminate the effect of the input dc bus ripple voltage. This switching function is applied to an off-line optimized PWM pattern stored in an EPROM. The technique however requires (a) dc bus voltage sensing (b) additional control circuitry to derive the new switching function and access the optimized pattern.

Fig. 1.12. Block diagram implementation of the scheme proposed in [30]

## 1.3.2. Advanced PWM techniques using microprocessors

To eliminate the effect of the input ripple, a selective harmonic reduction technique is presented in [32]. A sinusoidal reference is replaced by a quasi-sinewave whose magnitude varies inversely with the input voltage. The technique however requires real time calculations and in particular needs a large number of A/D and D/A conversions per cycle. Also the tradeoff involved are not analyzed. This is suitable only for microprocessor based control of PWM converters.

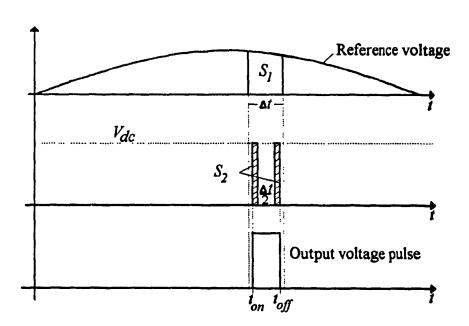

A digital control strategy for a three phase inverter is proposed in [33][34]. The pulse width is computed by sampling ( $\Delta t$ ) the input voltage and ensuring the crea under the voltage pulse is equal to the area under the reference voltage which in this case is chosen to be a sinusoidal voltage. Thus by ensuring the output voltage pulse follows a sinusoidal reference, a good harmonic rejection is reported. This is shown in Fig. 1.13, in which the area  $S_1$  is made equal to area  $S_2$ . The method to obtain the switching points( $t_{on}$  and  $t_{off}$ ) is detailed in the reference. The technique requires intensive mathematical computations and hence is suitable only for microprocessor implementation.

Fig. 1.13. Determination of switching function for technique proposed in [33][34]

A technique somewhat similar in concept, but much easier to implement using analog/digital circuits is introduced in this thesis.

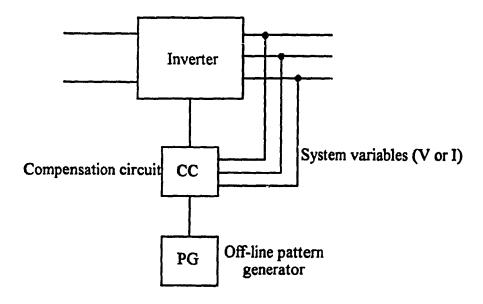

# 1.3.3. Dead time compensation

To reduce the effect of the dead-times in voltage source inverters, novel control schemes have been proposed in [23][24]. They essentially modify the control signals obtained from an off-line SPWM or memory based techniques in a way to minimize the effect of dead times on the output voltage. The principle of compensation is to detect any deviations in voltage and cancel it in the next switching instant. In [23] correction is based on sensing the line currents. On the other hand in [24], the correction circuit needs sensing of phase voltages for applying correction. Thus immunity to dead times is achieved at the expense of additional control circuitry (Fig. 1.14)

Fig. 1.14. Dead time compensation in [23][24].

## 1.4. Scope and contribution of this thesis.

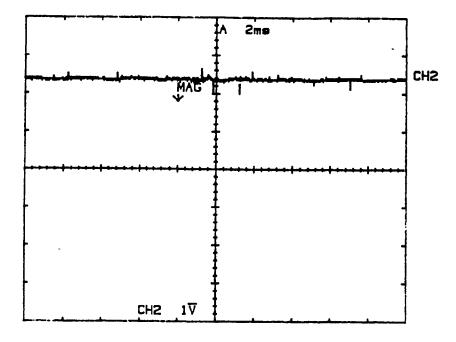

This thesis provides solutions to problems associated with a non-ideal dc bus and semiconductor devices in a power converter system. These solutions exploit the concept of converter output voltage integral control to improve the performance of PWM converters. Two control schemes, Reset Integral Control (RIC) and Modulated Integral Control (MIC) are identified based on this concept and applied to dc-dc [35] and three phase dc-ac voltage source inverters [36][37]. The purpose of these schemes is to produce an output voltage that minimize dc bus and inverter generated distortion. They can be used as pre-regulators for further control schemes. Theoretical analysis and computer programs written in FORTRAN[38] are used to compute the respective switching functions. The feasibility is exhibited and quantified through computer simulation on PECAN[39][40][41] software package. Experimental results are obtained on laboratory prototypes comprising of BJT based three phase voltage source inverter and MOSFET based dc-dc buck converter topology. The control circuit is designed using state-of-the-art analog and digital devices.

#### 1.5. Outline of the thesis

The contents of the thesis have been organized as follows: