National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

## NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

## **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous à fait parvenir une photocopie de qualité inférieure

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents

# ZERO VOLTAGE SWITCHING PULSE WIDTH MODULATED INVERTER TOPOLOGIES

## VASSILIOS G. AGELIDIS

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements

for the Degree of Master of Applied Science at

Concordia University

Montréal, Québec, Canada

December 1991

© VASSILIOS G. AGELIDIS, 1991

National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada KIA ON4

> The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

> The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-73683-6

#### **ABSTRACT**

## ZERO VOLTAGE SWITCHING PULSE WIDTH MODULATED INVERTER TOPOLOGIES

#### **VASSILIOS G. AGELIDIS**

Among the significant issues in static power converters are high switching frequency and high efficiency. However, switching losses usually limit switching frequencies. Historically, the size and the performance of the static power converters have been closely related to the performance of the semiconductor devices. Furthermore, in the past, any increase in converter switching frequency has almost always been obtained by advances in power semiconductor technology. More recently further improvements have been achieved through the use of appropriate dissipative snubber networks. However, this solution only partially solved the problems of switching losses.

Recent advances, in what are referred to as soft switching converter topologies, promise improved semiconductor utilization and substantially higher switching frequencies. The new developments in this area are extensively addressed in this thesis. Moreover, novel soft switching techniques, namely zero voltage switching (ZVS) converter topologies for single-phase and three-phase pulse width modulated (PWM) converters are proposed. The most important advantage of these topologies is that they combine features of resonant mode and standard PWM converter. The principles of operation of these topologies are discussed. A detailed design oriented analysis is provided. Simulated results are presented and verified experimentally on laboratory prototypes to establish the feasibility and effectiveness of the proposed converter topologies.

#### **ACKNOWLEDGEMENTS**

The author wishes to express his gratitude to his research advisors Dr. Phoivos D. Ziogas and Dr. Geza Joos for their friendship, guidance, support and encouragement during all the stages of this study.

The author wishes to acknowledge the financial support provided through the grants of the National Science and Engineering Council of Canada (NSERC) and the Government of Quebec through the FCAR grants.

Quebec Government's fee-remission through Concordia University is also acknowledged.

The author wishes to acknowledge the permission to use the on-line PC-based converter PWM modulator designed by Mr. D. Vincenti.

Comments on the thesis material and laboratory assistance from Mr. Ceasar Braz is greatly appreciated.

Thanks are due to Mr. J. Woods for laboratory assistance any time I asked for.

Thanks are also due to my friends and research colleagues, Alex Campos, Lautaro Salazar, D. Vincenti, J. P. Vandelac, and Navid Zargari, in the Power Electronics laboratory for the interesting discussions we shared.

## LIST OF CONTENTS

|                                                       | Page |

|-------------------------------------------------------|------|

| CHAPTER 1                                             |      |

| INTRODUCTION                                          |      |

| 1.1 Introduction.                                     | 1    |

| 1.2 Power semiconductor devices.                      | 2    |

| 1.3 Losses in power semiconductor devices.            | 3    |

| 1.4 Significant issues in power converter technology. | 4    |

| 1.5 Literature review.                                | 5    |

| 1.5.1 Converter snubber networks.                     | 5    |

| 1.5.2 Improved snubber networks.                      | 10   |

| 1.5.3 Soft switching converters.                      | 13   |

| 1.6 Scope and contributions.                          | 15   |

| 1.7 Summary of the thesis.                            | 15   |

| CHAPTER 2                                             |      |

| DC-DC & DC-AC CONVERTER TOPOLOGIES                    |      |

| 2.1 Introduction.                                     | 17   |

| 2.2 Hard switching PWM dc-dc converter topologies.    | 18   |

| 2.2.1 Advantages of PWM converters.                   | 21   |

| 2.2.2 Drawbacks of PWM converters.                    | 21   |

| 2.3 Soft switching dc-dc converters.                  | 23   |

| 2.3.1 Resonant dc-dc converters.                      | 23   |

| 2.3.1.a Advantages of resonant de-de converters.      | 25   |

|     |            | 2.3.1.b Drawbacks of resonant dc-dc converters.      | 25 |

|-----|------------|------------------------------------------------------|----|

|     |            | 2.3.1.c Comparison between ZCS and ZVS.              | 26 |

|     | 2.3.2      | Quasi-resonant dc-dc converters.                     | 27 |

|     | 2.3.3      | Multi-resonant dc-dc converters.                     | 28 |

|     | 2.3.4      | Other soft switching dc-dc converters.               | 28 |

|     | 2.3.5      | Soft switching single-phase full-bridge PWM dc-dc    |    |

|     |            | converter topology.                                  | 29 |

|     |            | 2.3.5.a Phase-shifted PWM technique for single-phase |    |

|     |            | full-bridge converter.                               | 29 |

|     |            | 2.3.5.b Phase-shifted PWM technique and zero voltage |    |

|     |            | switching (ZVS).                                     | 32 |

|     |            | 2.3.5.c Advantages of the single-phase full-bridge   |    |

|     |            | phase-shifted PWM soft switching topology.           | 32 |

|     |            | 2.3.5.d Drawbacks of the single-phase full-bridge    |    |

|     |            | phase-shifted PWM soft switching topology.           | Ĵŝ |

|     |            | 2.3.5.e Improved single-phase full-bridge PWM soft   |    |

|     |            | switching topologies.                                | 34 |

| 2.4 | Hard swi   | tching dc-ac inverters.                              | 35 |

| 2.5 | Soft swite | ching dc-ac inverters.                               | 37 |

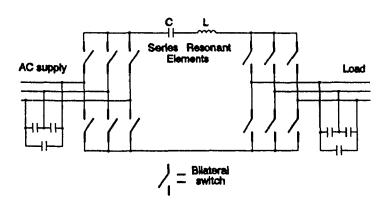

|     | 2.5.1      | Resonant ac link inverters.                          | 37 |

|     | 2.5.2      | Resonant de link inverters.                          | 38 |

|     | 2.5.3      | De-side commutated inverters.                        | 42 |

| 2.6 | Conclusi   | ons.                                                 | 43 |

|     |            |                                                      |    |

## CHAPTER 3

# AN IMPROVED LOW-FREQUENCY HIGH-POWER SINGLE-PHASE FULL-BRIDGE PWM CONVERTER TOPOLOGY

| 3.1 | Introduc  | tion.                                             | 44 |

|-----|-----------|---------------------------------------------------|----|

| 3.2 | Converte  | er power circuit description.                     | 44 |

| 3.3 | Advanta   | ges of the proposed PWM converter topology.       | 45 |

| 3.4 | Principle | es of operation.                                  | 47 |

|     | 3.4.1     | PWM converter employing low loss snubber network. | 47 |

|     | 3.4.2     | PWM converter employing lossless snubber network. | 48 |

| 3.5 | Modes o   | of operation - Steady state analysis.             | 48 |

|     | 3.5.1     | Single-phase full-bridge PWM converter            |    |

|     |           | topology with low loss snubber network.           | 49 |

|     | 3.5.2     | Single-phase full-bridge PWM converter            |    |

|     |           | topology with lossless snubber network.           | 59 |

| 3.6 | Discussi  | on - Design guidelines.                           | 61 |

|     | 3.6.1     | Design procedure for the single-phase full-bridge |    |

|     |           | PWM converter with low loss snubber network.      | 62 |

|     | 3.6.2     | Design procedure for the single-phase full-bridge |    |

|     |           | PWM converter with lossless snubber network.      | 63 |

| 3.7 | Design 6  | example                                           | 65 |

|     | 3.7.1     | PWM converter topology with the low loss          |    |

|     |           | snubber network.                                  | 65 |

|     | 3.7.2     | PWM converter topology with the lossless          |    |

|     |           | snubber network.                                  | 66 |

| 3.8 Compone    | ent ratings                                           | 67  |

|----------------|-------------------------------------------------------|-----|

| 3.8.1          | Component ratings of the single-phase full-bridge     |     |

|                | PWM converter topology with low loss snubber network. | 67  |

| 3.8.2          | Component ratings of the single-phase full-bridge     |     |

|                | PWM converter topology with lossless snubber network. | 68  |

| 3.9 Simulated  | d results.                                            | 70  |

| 3.10 Experim   | nental results.                                       | 76  |

| 3.11 Conclus   | ions.                                                 | 77  |

| CHAPTER 4      | 4                                                     |     |

| A ZERO VO      | OLTAGE SWITCHING MEDIUM-POWER HIGH-FREQUEN            | 1CY |

| SINGLE-PHA     | ASE FULL-BRIDGE PWM CONVERTER TOPOLOGY                |     |

| 4.1 Introduct  | ion.                                                  | 81  |

| 4.2 A novel 2  | ZVS PWM converter topology.                           | 81  |

| 4.3 Principles | s of operation.                                       | 82  |

| 4.4 Modes of   | operation - Steady-state analysis.                    | 83  |

| 4.5 Discussio  | n - Design quidelines.                                | 94  |

| 4.6 Design ex  | sample.                                               | 96  |

| 4.7 Compone    | ent ratings.                                          | 97  |

| 4.8 Simulatio  | n results.                                            | 98  |

| 4.9 Experime   | ntal results.                                         | 102 |

| 4.10 Conclusi  | ions.                                                 | 105 |

| CHAPTER 5      |                                                       |     |

| A NOVEL T      | HREE-PHASE SOFT SWITCHING PWM VSI TOPOLOG             | Y   |

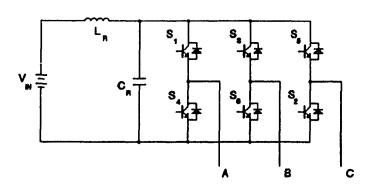

| 5.1 Introducti | ion.                                                  | 106 |

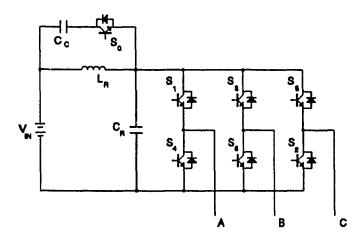

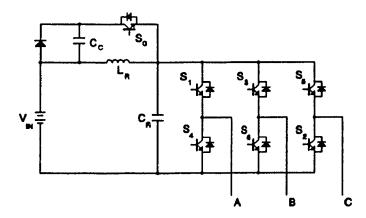

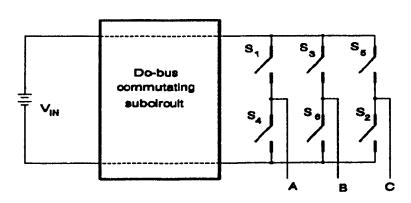

| 5.2 Inverter power circuit description.           | 106 |

|---------------------------------------------------|-----|

| 5.3 Principles of operation.                      | 107 |

| 5.4 Modulation strategy.                          | 109 |

| 5.4.1 The third harmonic injection PWM technique. | 112 |

| 5.4.2 The refined PWM technique.                  | 113 |

| 5.5 Steady-state analysis - Modes of operations.  | 120 |

| 5.6 Discussion - Design guidelines.               | 127 |

| 5.7 Design example.                               | 128 |

| 5.8 Simulated results.                            | 129 |

| 5.9 Experimental results.                         | 130 |

| 5.10 Conclusions.                                 | 136 |

| CHAPTER 6                                         |     |

| SUMMARY AND CONCLUSIONS                           |     |

| 6.1 Summary of the thesis.                        | 137 |

| 6.2 Conclusions.                                  | 138 |

| 6.3 Suggestions for future work.                  | 140 |

|                                                   |     |

| REFERENCES                                        | 141 |

## LIST OF FIGURES

|              |                                                          | Page |

|--------------|----------------------------------------------------------|------|

| Figure 1-1:  | Conventional dissipative snuber subcircuits.             | 7    |

| Figure 1-2:  | Soft switching elements.                                 | 14   |

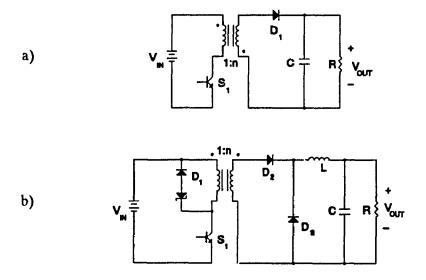

| Figure 2-1:  | Single quadrant topologies.                              | 19   |

| Figure 2-2:  | Isolated low power converter topologies.                 | 19   |

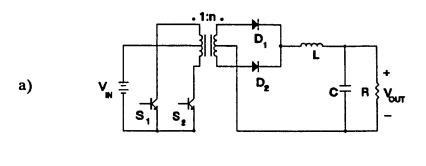

| Figure 2-3:  | Isolated medium power converter topologies.              | 20   |

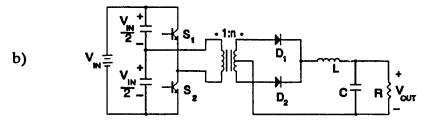

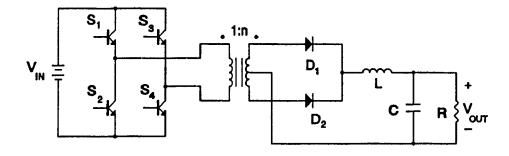

| Figure 2-4:  | Full-bridge switching converter.                         | 20   |

| Figure 2-5:  | Resonant dc-dc converter topologies.                     | 24   |

| Figure 2-6:  | The ZCS-quasi resonant converter.                        | 27   |

| Figure 2-7:  | Three phase dual bridge soft switching converter.        | 28   |

| Figure 2-8:  | Zero voltage switching converter topology with a passive |      |

|              | clamping circuit across the secondary side employing     |      |

|              | phase-shifted PWM technique.                             | 30   |

| Figure 2-9:  | Conventional PWM technique for single-phase              |      |

|              | full-bridge converter.                                   | 31   |

| Figure 2-10: | Phase-shifted PWM technique for single-phase             |      |

|              | full-bridge converter.                                   | 31   |

| Figure 2-11: | Hard switching six-switch voltage source inverter.       | 36   |

| Figure 2-12: | Series resonant ac link inverter topology.               | 38   |

| Figure 2-13: | The six-switch resonant dc link inverter topology.       | 39   |

| Figure 2-14: | Actively clamped resonant dc link inverter topology.     | 40   |

| Figure 2-15: | Synchronized resonant dc link inverter topology.         | 41   |

| Figure 2-16: | Three-phase bridge inverter with dc-side commutation.        | 43 |

|--------------|--------------------------------------------------------------|----|

| Figure 3-1:  | The single-phase full-bridge PWM dc-dc converter             |    |

|              | topology with the low loss snubber network.                  | 46 |

| Figure 3-2:  | The single-phase full-bridge PWM dc-dc converter             |    |

|              | topology with the lossless snubber network.                  | 46 |

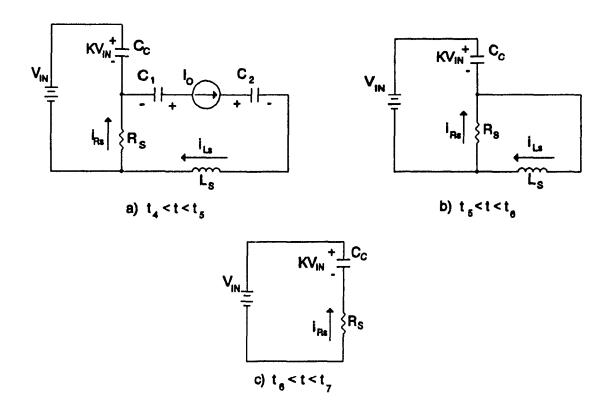

| Figure 3-3:  | Converter topological modes (TM's) during switching          |    |

|              | cycle turn-on. Low loss snubber network.                     | 51 |

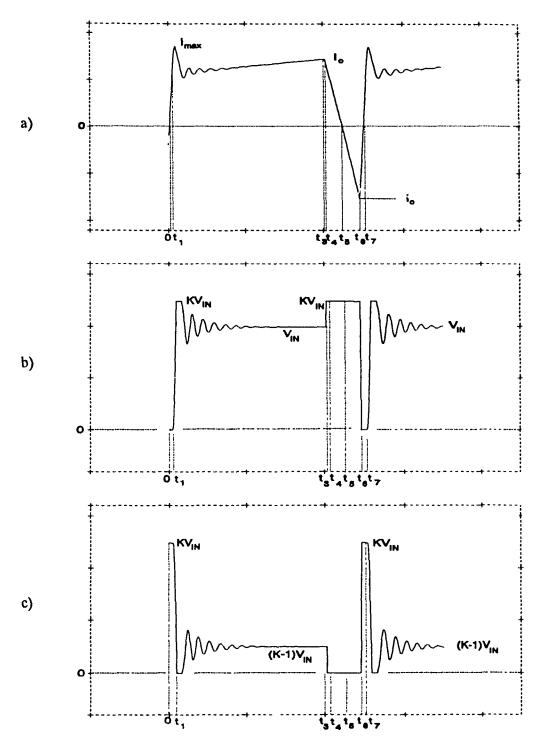

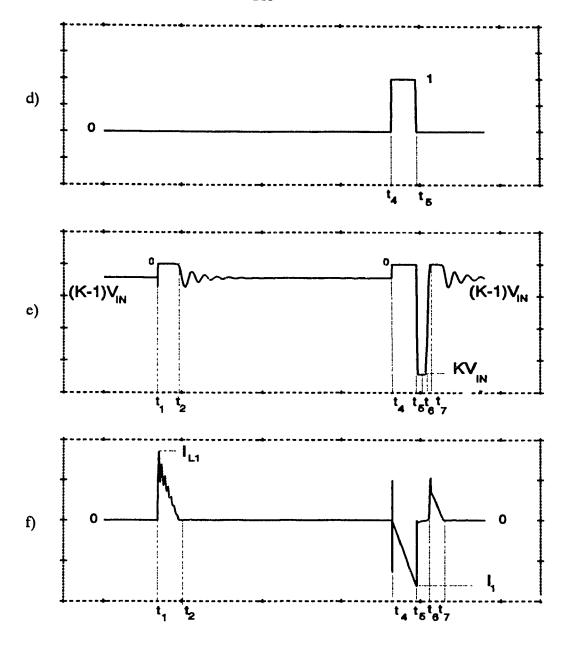

| Figure 3-4:  | Converter waveforms at turn-on of $S_1$ , $S_4$ .            | 54 |

|              | Low loss snubber network.                                    |    |

| Figure 3-5:  | Converter topological modes (TM's) during switching          |    |

|              | cycle turn-off. Low loss snubber network.                    | 57 |

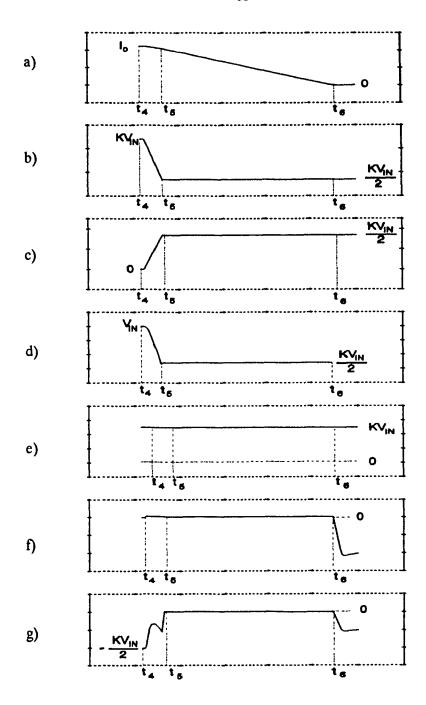

| Figure 3-6:  | Converter waveforms at turn-off of $S_1$ , $S_4$ .           | 60 |

|              | Low loss snubber network.                                    |    |

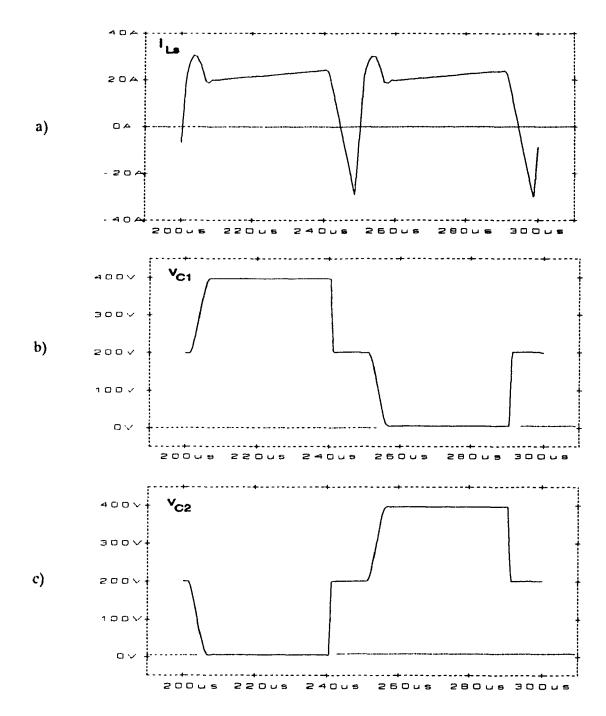

| Figure 3-7:  | Converter steady-state waveforms - Low loss snubber network. | 71 |

| Figure 3-8:  | Converter steady-state waveforms - Lossless snubber network. | 73 |

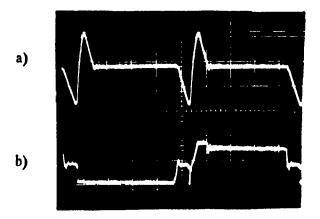

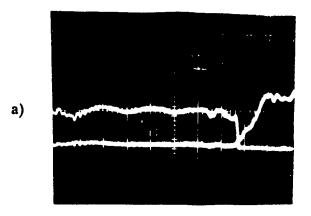

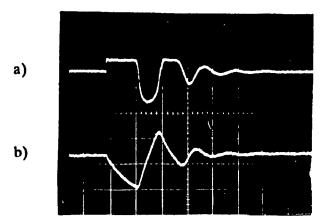

| Figure 3-9:  | Experimental converter waveforms - Low loss snubber network. | 78 |

| Figure 3-10: | Switch voltage and current during switching interval.        | 78 |

|              | Low loss snubber network.                                    |    |

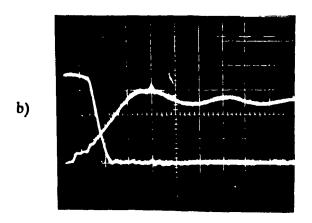

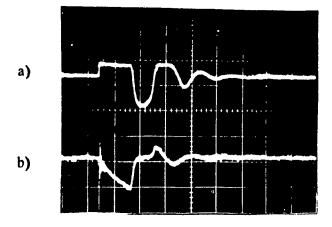

| Figure 3-11: | Experimental converter waveforms - Lossless snubber network. | 79 |

| Figure 3-12: | Switch voltage and current during switching interval.        | 80 |

|              | Lossless snubber network.                                    |    |

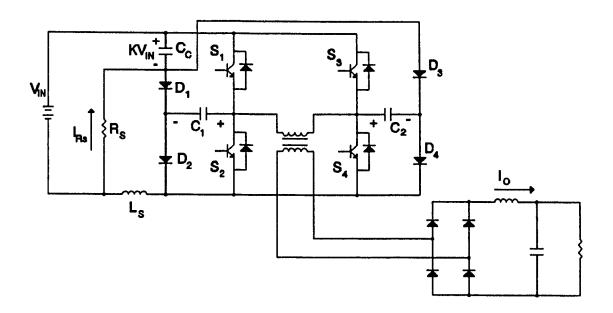

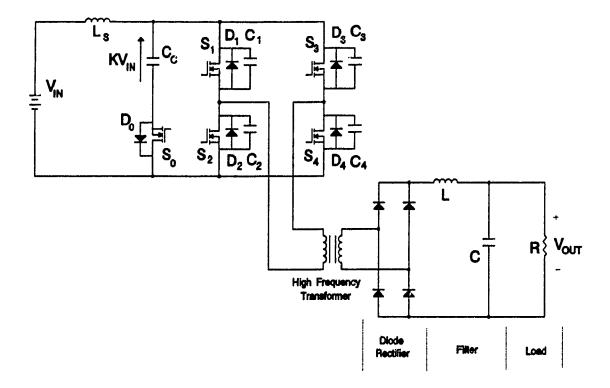

| Figure 4-1:  | The proposed single-phase full-bridge medium-power high      |    |

|              | frequency zero voltage switching PWM converter topology.     | 82 |

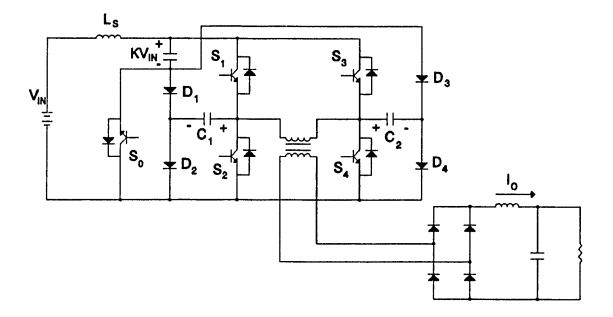

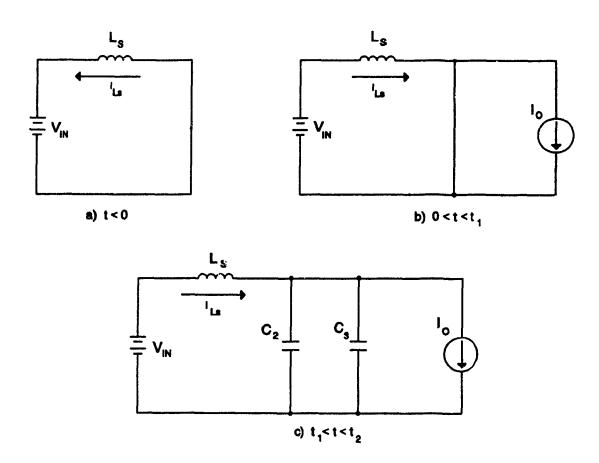

| Figure 4-2:  | Converter topological modes (TM's) during                    |    |

|              | switching cycle turn-on.                                        | 86  |

|--------------|-----------------------------------------------------------------|-----|

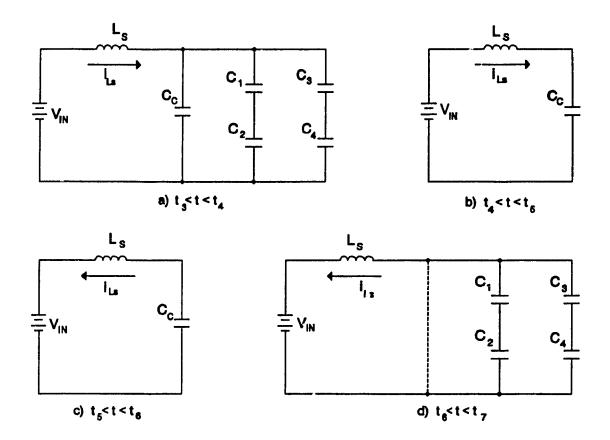

| Figure 4-3:  | Converter topological modes (TM's) during                       |     |

|              | switching cycle turn-off.                                       | 90  |

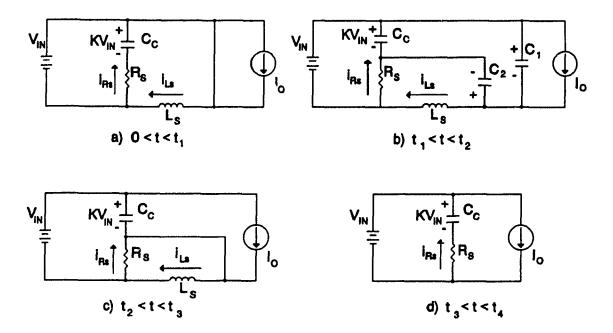

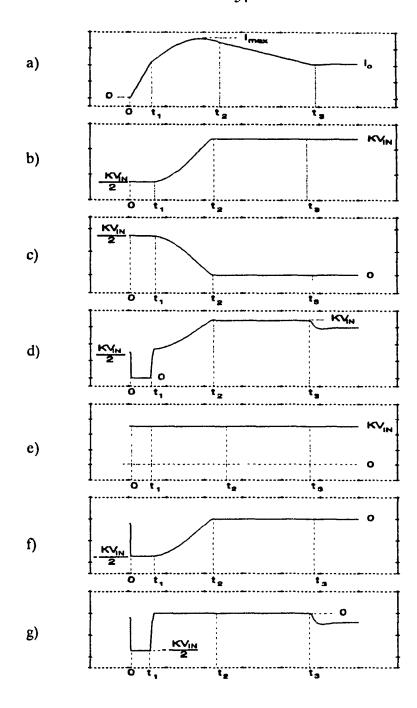

| Figure 4-4:  | Steady-state voltage and current waveforms.                     | 93  |

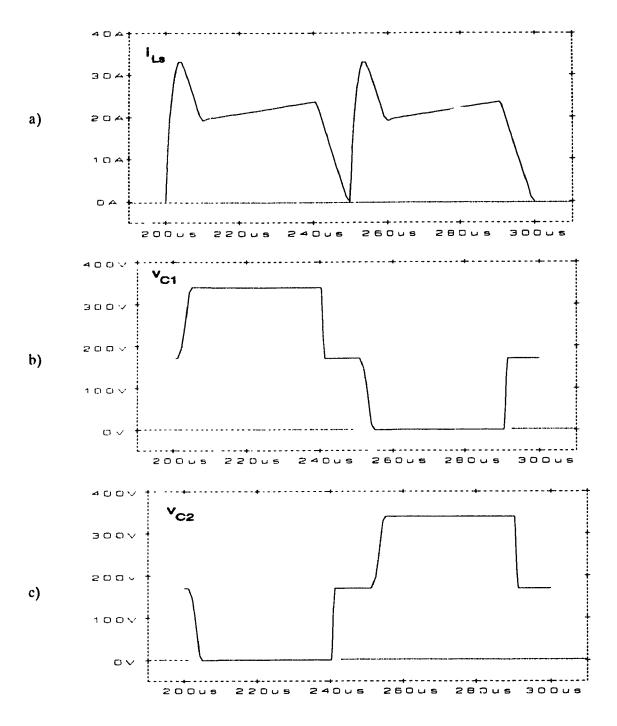

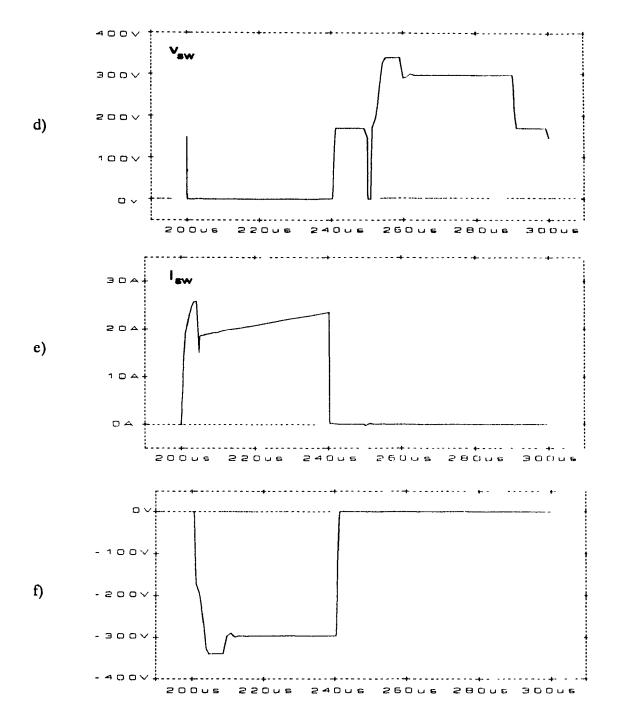

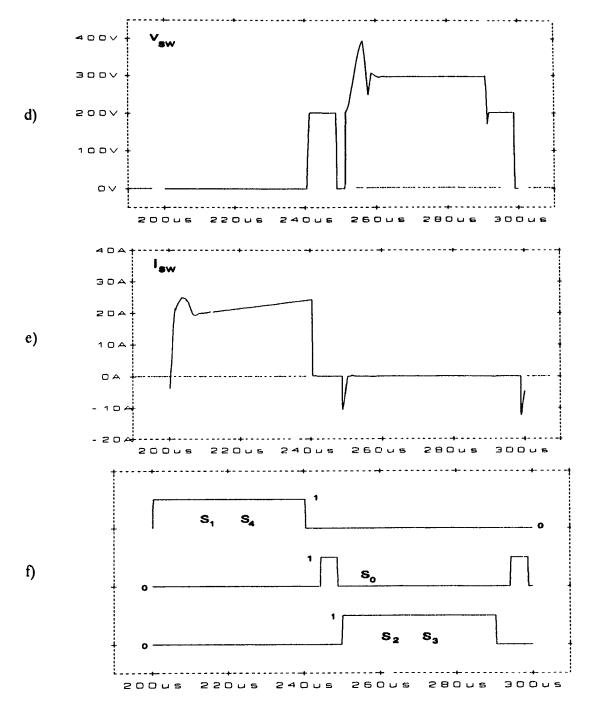

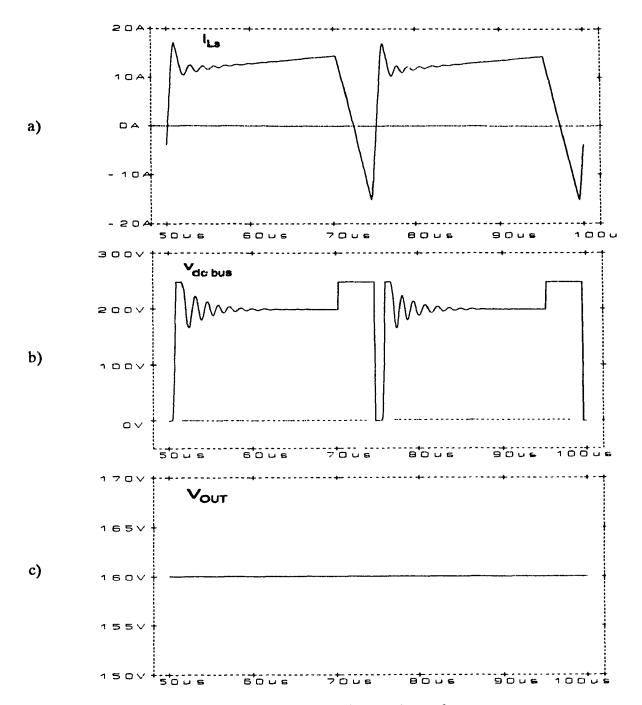

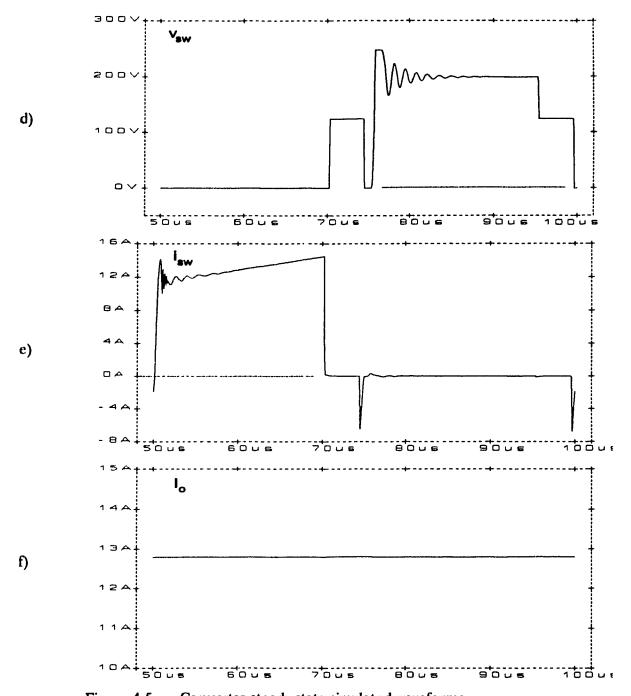

| Figure 4-5:  | Converter steady-state simulated waveforms.                     | 99  |

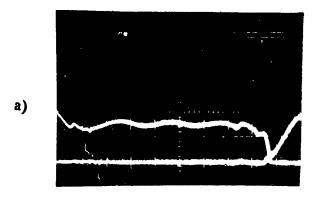

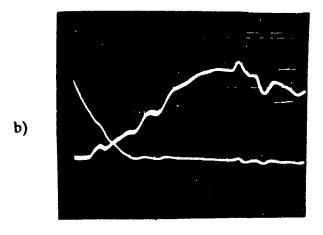

| Figure 4-6:  | Experimental converter waveforms.                               | 103 |

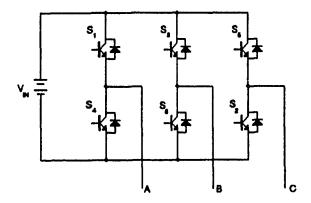

| Figure 5-1:  | The novel notch commutated 3-phase PWM ZVS VSI topology.        | 107 |

| Figure 5-2:  | A microscopic view of the dc bus commutating subcircuit         |     |

|              | operation.                                                      | 110 |

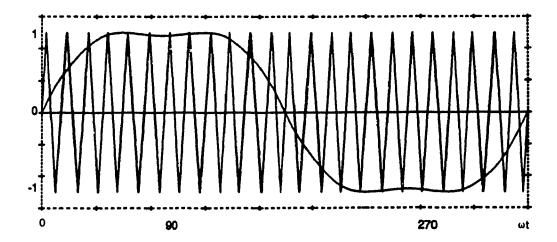

| Figure 5-3:  | HIPWM (1st - 3rd) - Description and modulation                  |     |

|              | index control.                                                  | 114 |

| Figure 5-4:  | Refined PWM technique - Description and modulation              |     |

|              | index control.                                                  | 114 |

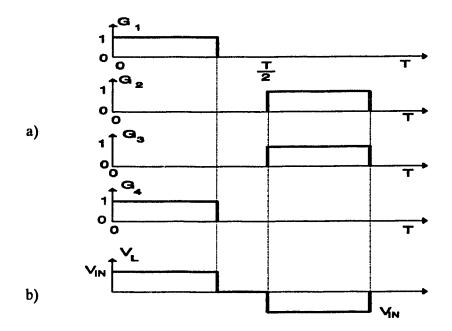

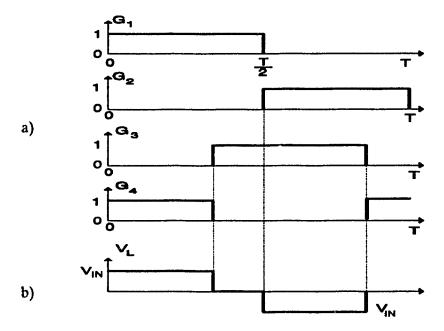

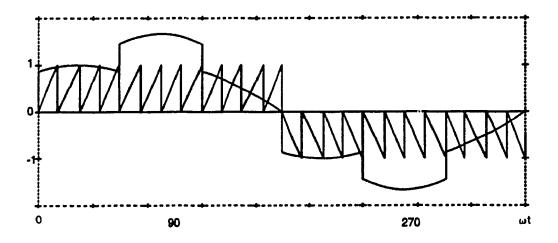

| Figure 5-5:  | a) Inverter switching states.                                   | 116 |

|              | b) Associated inverter output voltage vectors.                  |     |

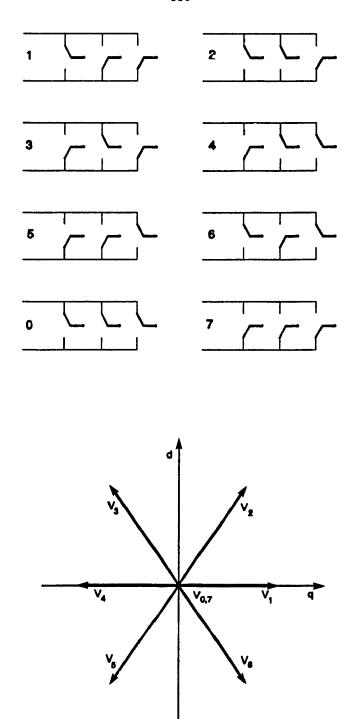

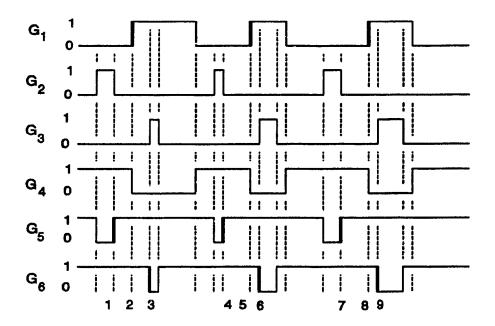

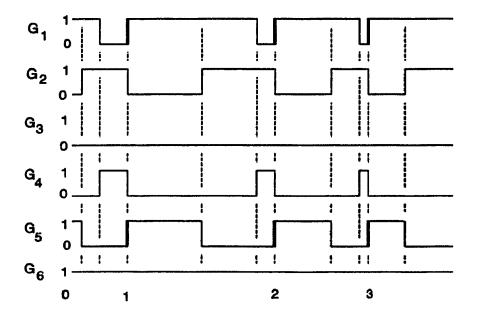

| Figure 5-6:  | An expanded 45° segment of gating signals generated with        |     |

|              | the HIPWM (1st -3rd) technique.                                 | 118 |

| Figure 5-7:  | An expanded 45° segment of gating signals generated with        |     |

|              | the refined PWM technique.                                      | 118 |

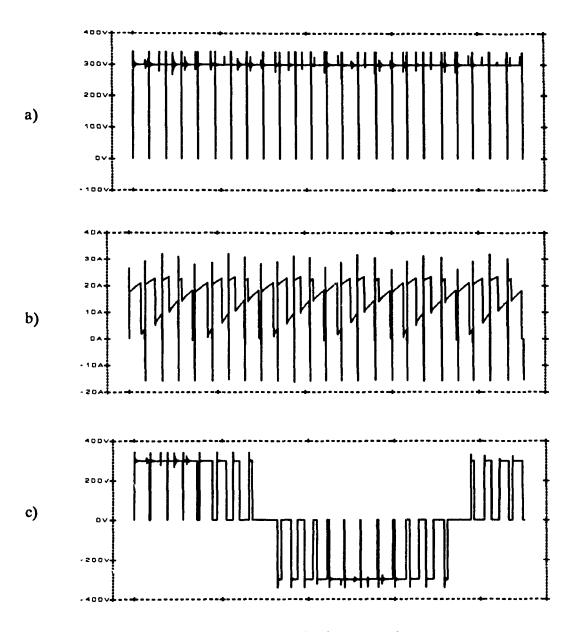

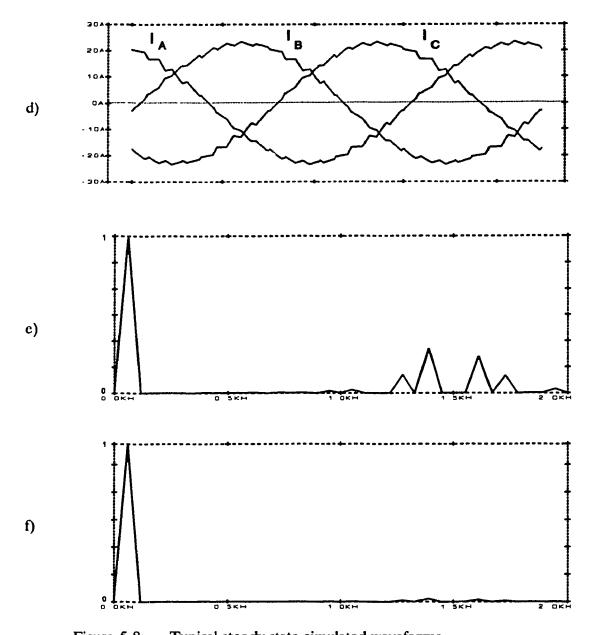

| Figure 5-8:  | Typical steady-state simulated waveforms.                       | 131 |

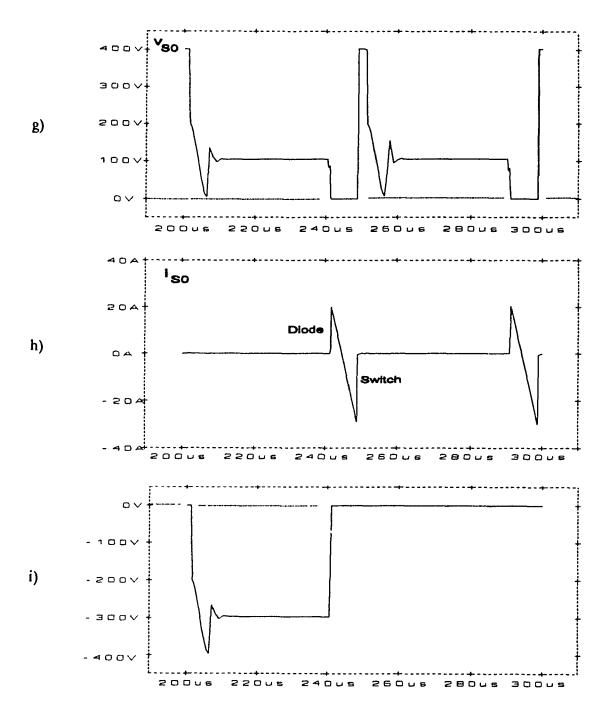

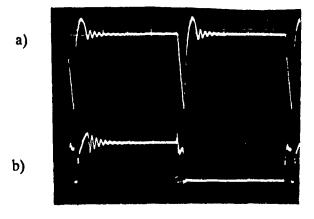

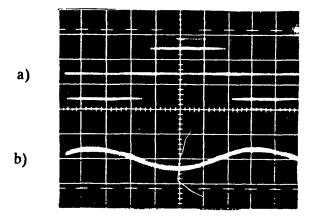

| Figure 5-9:  | Experimental results - Dc bus commutating subcircuit operation. | 134 |

| Figure 5-10: | Experimental results - Dc bus commutating subcircuit operation. | 134 |

| Figure 5-11: | Experimental results - Inverter waveforms.                      | 135 |

| Figure 5-12: | Experimental results - Inverter waveforms.                      | 135 |

## LIST OF TABLES

| Table 5-1: | Switching states of the three-phase inverter and |     |

|------------|--------------------------------------------------|-----|

|            | normalized output voltages.                      | 115 |

#### LIST OF ACRONYMS

AC Alternating Current

ACRLI Actively Clamped Resonant dc Link Inverter

BJT Bipolar Junction Transistor

CMSRC Clamped-Mode Series Resonant Converter

DC Direct Current

DWM Discrete Width Modulation

DPM Discrete Pulse Modulation

EMI Electromagnetic Interference

ESR Equivalent Series Resistance

ESL Equivalent Series Inductance

GTO Gate Turn-Off Thyristor

HIPWM Harmonic Injection Pulse Width Modulation

IGBT Insulated Gate Bipolar Transistor

JFET Junction Field Effect Transistor

kW kilo Watt

MI Modulation Index

MCT MOS Controlled Thyristor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

ms mili seconds

mH mili Henry

PWM Pulse Width Modulation

PORC Parallel Output Series Resonant Converter

RDCLI Resonant DC Link Inverter

RFI Radio Frequency Interference

RMS Root Mean Square

SRC Series Resonant Converter

Si-Thy Static Induction Thyristor

SOAR Safe Operating Area

SMR Switch Mode Rectifier

SCR Silicon Controlled Rectifier

SRDCLI Synchronized resonant DC Link Inverter

SMPS Switch Mode Power Supply

TM Topological Modes

UPS Unninterruptible Power Supply

VVI Variable Voltage Inverter

VSI Voltage Source Inverter

VA Volt-Ampere

ZCS-QRC Zero Current Switching Quasi Resonant Converter

ZVS Zero Voltage Switching

ZCS Zcro Current Switching

μP microProcesssor

μH micro Henry

μF micro Farad

μs micro seconds

ΣΔM Sigma Delta Modulator

## LIST OF PRINCIPAL SYMBOLS

| <i>C</i> ,                  | snubber capacitor                              |

|-----------------------------|------------------------------------------------|

| $C_s$                       | value of the snubber capacitor                 |

| d                           | converter duty cycle                           |

| $d_{MIN}$                   | minimum duty cycle                             |

| $f_o$                       | inverter fundamental output frequency          |

| $f_{sw}$                    | converter switching frequency                  |

| G,                          | switch $S_j$ gating signal                     |

| $G_{AC}$                    | AC gain of the PWM technique                   |

| $i_{L_s}$                   | instantaneous current through $L_s$            |

| $I_o$                       | load current                                   |

| $I_{max}$                   | maximum value of current through $L_s$         |

| $I_{ow}$                    | worst value of $i_{Ls}$                        |

| $I_{Ls,RMS}$                | RMS current through $L_s$                      |

| $I_{CC,MAX}$                | maximum current through $C_c$                  |

| $I_{AUX,RMS}$               | RMS current through auxiliary switch           |

| $I_{AUX,AVG}$               | average current through auxiliary switch       |

| $I_{AUX,MAX}$               | maximum current through auxiliary switch       |

| $I_{sw;RMS}$                | RMS current through converter main switch      |

| $I_{sw_{\mathcal{A}^{VG}}}$ | average current through converter main switch  |

| $I_{PRI,RMS}$               | RMS current of transformer primary winding     |

| $I_{PR;,MAX}$               | maximum current of transformer primary winding |

RMS current through a rectifier diode  $I_{D.RMS}$ average current through a rectifier diode  $I_{DAVG}$  $I_{D,MAX}$ maximum current through a rectifier diode  $I_{A}$ line current in the three-phase inverter line current in the three-phase inverter  $I_{R}$ line current in the three-phase inverter  $I_{c}$ current through  $L_s$  $I_{LI}$ current through  $L_s$  $I_{L2}$ RMS inverter line current  $I_{L,RMS}$ current through  $R_s$  $I_{Rs}$ K overvoltage factor snubber inductor  $L_{\rm s}$ converter rated output power  $P_{our}$ power dissipation in the snubber resistor  $R_s$  $P_{R_s}$ snubber resistor  $R_{s}$  $S_{I}$ inverter main switch So auxiliary switch dead time of the converter (free-wheeling mode) t<sub>dead</sub> time instant  $t_1$ on-time of the auxiliary switch  $t_{ON,So}$  $V_{IN}$ dc input power supply  $V_{INMAX}$ maximum dc input power supply  $V_{INMIN}$ minimum dc input power supply

voltage of storage-clamp capacitor  $C_c$

$V_{cc}$

| $I_{D,RMS}$        | RMS current through a rectifier diode           |

|--------------------|-------------------------------------------------|

| $I_{D,AVG}$        | average current through a rectifier diode       |

| $I_{D,MAX}$        | maximum current through a rectifier diode       |

| I <sub>A</sub>     | line current in the three-phase inverter        |

| $I_B$              | line current in the three-phase inverter        |

| $I_C$              | line current in the three-phase inverter        |

| $I_{LI}$           | current through $L_s$                           |

| $I_{L2}$           | current through $L_s$                           |

| I <sub>L,RMS</sub> | RMS inverter line current                       |

| $I_{Rs}$           | current through $R_s$                           |

| K                  | overvoltage factor                              |

| $L_s$              | snubber inductor                                |

| $P_{our}$          | converter rated output power                    |

| $P_{Rs}$           | power dissipation in the snubber resistor $R_s$ |

| $R_s$              | snubber resistor                                |

| $S_{I}$            | inverter main switch                            |

| $S_o$              | auxiliary switch                                |

| l <sub>dead</sub>  | dead time of the converter (free-wheeling mode) |

| $t_{I}$            | time instant                                    |

| l <sub>ON,So</sub> | on-time of the auxiliary switch                 |

| $V_{IN}$           | de input power supply                           |

| V <sub>INMAX</sub> | maximum de input power supply                   |

| $V_{INMIN}$        | minimum dc iput power supply                    |

| $V_{cc}$           | voltage of storage-clamp capacitor $C_c$        |

$V_{CI}$  voltage across snubber capacitor  $C_{I}$

$V_{OUT}$  converter output voltage

$V_{LsMax}$  maximum voltage across  $L_s$

$V_{CC,MAX}$  maximum voltage across  $C_C$

V<sub>AUX,MAX</sub> maximum voltage across auxiliary switch

$V_{SW,MAX}$  maximum voltage across converter main switch

$V_{PRLRMS}$  RMS voltage of transformer primary winding

$V_{PRLMAX}$  maximum voltage of transformer primary winding

$V_{DMAX}$  maximum reverse voltage across a rectifier diode

V<sub>AB</sub> normalized inverter line-to-line voltage

$V_{RC}$  normalized inverter line-to-line voltage

V<sub>C</sub> normalized inverter line-to-line voltage

$V_{LL}$  fundamental component of the line-to-line output inverter voltage

$V_{L-LRMS}$  RMS value of the inverter line-to-line voltage

y analytical expression for the reference waveform of the HIPWM

technique

$W_{CI}$  capacitor energy

$W_{IN}$  energy that enters  $C_C$

$W_{OUT}$  energy that leaves  $C_C$

$\Delta V_{CC}$  difference in voltage across  $C_C$

$\eta$  efficiency

$\omega_r$  resonant frequency

#### CHAPTER 1

#### **INTRODUCTION**

#### 1.1 Introduction

In power electronic technology, static converters can be viewed as power conditioners which employ semiconductor devices to convert or control energy. Specifically, they enable the energy flow between different systems to be controlled.

When ac and dc systems are coupled, the basic functions that can be realized are as follows:

- rectification, the conversion of ac into ac (i.e. diode or controlled rectifiers, etc.);

- inversion, the conversion of dc to ac (i.e. ac variable speed drives, unninteruptible power supply (UPS) systems, etc.);

- dc conversion, the conversion of dc of a given voltage and polarity into that of another voltage and where applicable, reversed polarity (i.e. dc power supplies, dc variable speed drives, etc.);

- ac conversion, the conversion of ac of a given voltage, frequency, and number of phases into that of another voltage, frequency, and where applicable number of phases (i.e. cycloconverters, ac power controllers, etc.).

Power semiconductor devices are employed to realize the numerous static power converters which perform the previously mentioned functions. A brief discussion of the various semiconductor devices and their essential characteristics is provided in the following section.

#### 1.2 Power semiconductor devices

Power semiconductor devices perform the on-off action which is the basic operation in static power converters. The beginning of the power electronics technology is usually associated with the development of the thyristor (Silicon Controlled Rectifier - SCR) in the laborateries of the General Electric Company in 1957 [1],[2],[3],[4]. Since then, the thyristor has undergone much development. It has not only been improved to become the high-speed thyristor but has also been diversified into various kinds, such as Triac, Gate Turn-Off thyristor (GTO), etc. The high-voltage/high-current capability and the high short-time current-carrying capability ensure that the thyristor is an indispensable part of power electronic converters, especially at high power levels. The GTO, with capability of switching at higher voltages and currents, deserves a special mention since high power converters employing self-commutated devices can be realized. GTO's, as compared with thyristors, reduce the size of static power converters, since all the necessary and complicated networks for the commutation of the thyristors are eliminated.

One important achievement has also been the development and continuing improvement of the Bipolar Junction Transistor's (BJT's) power ratings during the 1980's. The Metal Oxide Semiconductor Field Effect Transistor (MOSFET) has been also developed which provides higher speeds and larger safe operating area (SOAR) than the BJT's. Other advances have been the reduction of the on-resistance of the power MOSFET's and increase in their power ratings during the last decade.

Hybrid devices comprised of bipolar and MOS devices such as the Insulated Gate Bipolar Transistor (IGBT), have also been fabricated which are suitable for higher voltages and currents than MOSFET's and are also capable of switching at higher frequencies than BJT's. Additionally, MOS controlled thyristors (MCT), comprised of a MOSFET and a

thyristor, have been developed. These devices are also expected to have high voltage and current capability.

One of the most important problems in static power converters is addressed in the following section.

## 1.3 Losses in power semiconductor devices

The ever increasing development of self-commutated switching devices has led to increased use of transistors (BJT's, JFET's, MOSFET's, IGBT's, etc.) in many industrial applications related to power electronic technology. However, proper use of these devices requires determination of semiconductor losses since adequate cooling means have to be provided to keep the device temperature within rated values.

Generally, the semiconductor losses are grouped into three categories [5]:

- i) conduction losses

- on-state losses

- dynamic saturation losses

- ii) switching losses

- turn-on losses

- turn-off losses

- iii) off-state losses.

The relative magnitudes of the conduction and switching losses are greatly dependent on the type of the converter (i.e. resonant, quasi-resonant, PWM, etc.), the operating frequency, the type of the load (linear or nonlinear, resistive or inductive), and certain characteristics of the switch itself (i.e. turn-on time, turn-off time, etc.). Off-state losses are generally a very small portion of the total losses and are considered negligible.

The most vital issues in power electronics technology are addressed in the following section.

## 1.4 Significant issues in power converter technology

In all areas of power electronics, the most significant issues and research interests concerning the static power converters are as follows:

- the improvement of efficiency,

- the reduction of size, weight, and cost,

- fast transient response,

- better input/output spectral characteristics,

- minimization or elimination of acoustic noise and electromagnetic interference (EMI), and

- wide range control of output voltage, current or frequency.

Higher switching frequencies are an essential requirement for achieving all the previously mentioned performance improvements. However, switching losses limit the switching frequencies.

Historically, the size and the performance of the static power converters have been closely related to the performance of the semiconductor devices [2]. In the past, any increase in converter switching frequency has almost always been obtained by advances in power semiconductor technology [4]. Further improvements have been achieved by the use of appropriate lossy snubber networks [6]. However, employing snubber networks only partially solved the problems associated with switching losses. Therefore, development of topologies which employ low loss snubber subcircuits is an important goal, since these converters can operate at higher frequencies without introducing the problems associated

with the switching losses.

Over the last decades, the different approaches dealing with switching losses are critically discussed in the following sections.

#### 1.5 Literature review

Depending upon the application, there are several ways of dealing with switching losses in static power converters. In this section, previous research work, related to various approaches towards alleviating semiconductor devices from switching losses, is reviewed.

#### 1.5.1 Converter snubber networks

Snubber networks are a primitive way to minimize switching losses in pulse width modulated (PWM) converters. In general, snubber networks are converter subcircuits used for the reduction of switching losses of power semiconductor devices [6]. The turn-on and turn-off networks are placed in series/parallel to power switching devices, respectively. For instance, one major purpose of using such networks, especially for power BJT's and GTO's, is to keep the power device within its safe operating area (SOAR).

Two different types of snubber subcircuits can be defined:

- dissipative

- nondissipative (low loss snubbers)

The basic difference between the dissipative and the nondissipative snubber subcircuits is as follows:

- in dissipative snubber networks, the energy stored in the reactive elements (limiting di/dt inductor and limiting dv/dt capacitor) is dissipated in resistors and converted into heat [7]. This type is certainly not the best choice to achieve high switching

frequencies and/or high power levels.

- in nondissipative (low loss) snubber networks, there are no fundamental losses.

In this case, losses are only caused by nonideal device properties, such as conduction and transient switching losses of the switching devices contained in the snubber networks.

It is certainly possible and sometimes advantageous, depending upon the application, to combine dissipative turn-on networks with nondissipative turn-off networks and vice versa [6]. The specific topologies of the snubber subcircuits can vary considerably depending upon the switching characteristics of the components being protected. For instance, the turn-off snubber for a thyristor is primarily intended to control and limit the rate of rise of voltage across the semiconductor device during turn-off. The need to limit that rate (dv/dt) is based on the thyristor's ability to commutate the current in a certain time interval which is usually given in the manufacture's data sheets. The design and the operation of the snubber networks for converters employing thyristors are well documented in the technical literature and they are not the object of this thesis [8],[9].

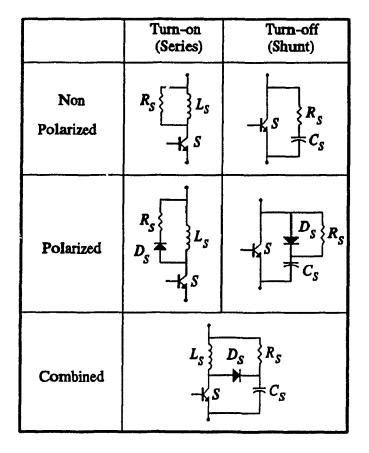

For the modern semiconductor devices such as power BJT's, JFET's, MOSFET's, IGBT's, and GTO's, snubber subcircuits are also employed in PWM converters. Fig. 1-1 shows the conventional dissipative snubber networks. Specifically, the turn-on snubber  $(R_S - L_S)$  to control the rise rate of the switch current during turn-on and the turn-off snubber  $(R_S - C_S)$  to control the rise rate of the switch voltage during turn-off are shown. The polarized snubber networks (turn-on/turn-off) are included. The combined polarized complete turn-on/turn-off snubber network is also depicted. The transistor S in each case is the respective semiconductor device that is being protected by the passive snubber components  $R_S$ ,  $L_S$ ,  $C_S$  and  $D_S$ .

Figure 1-1: Conventional dissipative snubber subcircuits.

With the use of a combined snubber subcircuit (Fig. 1-1), the interaction between the semiconductor device and the snubber subcircuit is as follows:

- During turn-on the voltage fall is a linear time function completely dictated by the switch characteristics, while the current rise is dictated by the series snubber inductor  $L_s$ .

- During turn-off, the current fall is a linear time function completely determined by the switch characteristics, while the voltage rise is determined by the shunt snubber capacitor  $C_s$ .

The operation of the combined snubber network (Fig. 1-1) is described as follows: After switch turn-on, the snubber capacitor  $C_s$  discharges via the semiconductor device through the  $C_s$  -  $R_s$  -  $L_s$  loop. The discharge current is superimposed on the load current. The snubber capacitor  $C_s$  voltage reaches zero afterwards, at which moment the snubber polarizing diode  $D_s$  begins to conduct and the remaining overcurrent in the inductor  $L_s$  decays exponentially through the  $L_s$  -  $R_s$  loop. Respectively, after switch turn-off, the series snubber inductor  $L_s$  begins to discharge and the snubber diode  $D_s$  conducts thus connecting  $C_s$  in parallel with the semiconductor device. The discharge voltage of the inductor is superimposed over the input voltage already present across the switch. The discharge network consists of the parallel branch  $L_s$  -  $C_s$  -  $R_s$ . The inductor current reaches zero afterwards at which moment the snubber polarizing diode  $D_s$  blocks and the remaining overvoltage decays exponentially through the  $C_s$  -  $R_s$  loop.

The advantages of the conventional dissipative snubber networks can be summarized as follows:

- transfer of the switching losses from the semiconductor device to an external resistor;

- suppression of high voltage transients;

- control of the rise rate of the current during turn-on and the rise rate of the voltage during turn-off;

- reduction of the generated noise and the electromagnetic interference (EMI);

- avoidance of the secondary breakdown in transistor (BJT) converters.

On the other hand, the following disadvantages associated with these snubber networks can be identified:

- the energy stored in the reactive elements is dissipated in external resistors, thus

decreasing converter efficiency as the switching frequency increases;

- overvoltages can still occur as a result of resonances between snubber or stray inductors and snubber or parasitic capacitors;

- extra components are required, thus increasing power circuit complexity;

- the power losses also complicate the thermal layout and the heat sink design thus leading to an increase in cost.

The operation of the conventional dissipative snubbers at high frequencies and high power levels becomes extremely critical since the dissipated energy increases as a function of the switching frequency.

A thorough analysis by W. McMurray provides an optimization technique that can be employed to design a conventional dissipative R-L-C network for a specific application [10]. The results presented show that certain values of snubber capacitor and inductor will minimize the total switching losses, including losses in the device and the eventual dissipation of energy stored in the snubber elements. However, as stated earlier, these passive snubber subcircuits only partially solved the problems associated with the switching losses. Diverting the losses from an active switching device to an external resistor is a primitive solution resulting in a low converter efficiency. Moreover, adequate cooling means have to be provided for the dissipating resistors, increasing converter size, weight and cost.

At higher power levels and switching frequencies, it is more desirable to rather use nondissipative (low loss) snubber networks. An analysis and optimization technique for nondissipative snubber networks has been done by Charl G. Steyn [11]. The paper only treats the single storage element for turn-on (inductor) and turn-off (capacitor) separately and independently of each other. It provides only mathematical information for designing an optimum snubber since no specific subcircuit for energy recovery is addressed.

### 1.5.2 Improved snubber networks

The snubber subcircuits previously presented (Fig. 1-1) can be used for each switching device separately. However, it is more efficient to combine components and to use for instance one reactive element (inductor/capacitor) for both switches of a PWM converter leg. There are various snubber subcircuits that improve the overall component count by reducing the number of snubber elements.

A snubber subcircuit suitable for BJT-inverter topology using a minimum number of components is proposed in [12]. The snubber components are designed in such a way that maximum ratings associated with semiconductor devices are not exceeded. Modifications have been discussed in cases that power MOSFET's are used as switching devices. However, all the energy associated with the snubber subcircuits is dissipated in passive components which makes this solution unattractive for high frequency high power converters.

Some snubber networks for PWM bridge converters with BJT's or GTO's have been proposed and analyzed by T. M. Undeland [13]. They are simple and give less extra stresses than the conventional configurations (Fig. 1-1). Most of the turn-on and turn-off losses in the semiconductor devices are removed and dissipated in a single snubber resistor, therefore loss recovery can be easily done if desired. A common inductor is used to protect all converter diodes and switches during switching turn-on. Similarly, only one snubber capacitor is used for each pair of switches of a converter phase-leg. However, this paper does not include any way of recovering the losses associated with snubber elements.

An improved snubber configuration for both BJT's and GTO's PWM inverters has been also analyzed by T. M. Undeland [14]. It is a complete turn-on/turn-off snubber network that has the advantages of conventional snubbers, and in addition:

- it has fewer components;

- it introduces lower additional stresses;

- the snubber diodes do not cause any difficulties associated with reverse recovery;

- all the losses are dissipated in one resistor, therefore loss recovery can be easily done, if desired.

As stated earlier, the snubber is suitable for both GTO's and BJT's, but the size of the snubber components may differ for different applications. A three-phase inverter with the same snubber has been also discussed in this paper. However, this paper does not propose any solution to recover the losses associated with the snubber components.

Another snubber configuration based on that proposed in [14] has been further investigated in [15] for PWM-VSI with IGBT's. However, in this paper the inductors as well as the dissipating resistors are split to reduce EMI but loss recovery is not considered at all. Some proposed arrangements include an increased number of components making the power circuit layout more complex.

Based on the snubber configuration proposed in [14], an improved snubber with energy recovery by simple passive network is proposed by J. Matthias [16]. This configuration is suitable for high power and low switching frequency applications using GTO's. In this case, a substantial part of the snubber energy can be recovered by a secondary winding on the turn-on snubber inductor, reducing the total snubber losses to less than one third compared with a conventional snubber. However, the energy recovery subcircuit is complicated making the solution unattractive.

A snubber network suitable for a phase-leg of a voltage source GTO or BJT inverter is proposed and analyzed by W. McMurray [17]. This arrangement reduces the size of the reactive components as well as their number. It also provides efficient means of recovering

a substantial part of the energy trapped in the snubber elements, since the discharge resistor may be replaced by a transformer which conserves trapped energy in both the series (inductor) and shunt (capacitor) reactive components. However, the proposed solution to recover the snubber energy is complicated.

Another snubber circuit for high power GTO inverter which is composed of only passive elements is proposed in [18]. Ideally, no losses occur due to snubber components since the configuration completely recovers the trapped energy of the turn-on and turn-off snubber elements. The overall converter efficiency is increased, which is especially preferred for high power applications. However, the proposed power circuit layout is cumbersome.

A snubber configuration using active switching devices for energy recovery is proposed for PWM transistor inverters [19]. The requirement of being basically a lossless network is fulfilled. However, the complexity of the circuit is high and it can be added that the snubber network itself becomes another power converter topology.

Active way of protecting power transistors and eliminating the necessary snubber subcircuits is also proposed in [20]. Feedback methods are studied to achieve a faster, lighter and integrable solution. The detection of an overvoltage when the device turns-off activates a negative feedback path and drives the device back into conduction in such a way that the overvoltage originated by the inductor current discontinuity is kept constant at a predefined level. With this approach, the current carried by the transistor is decreased in a controlled way, during turn-off, and the voltage does not exceed a certain limit. Similar active drive techniques for power transistor are also discussed in [21]. However, this method deals with protecting the semiconductor device from overvoltages only. Moreover, all the energy associated with switching turn-off is dissipated inside the transistor, since the device is driven back to conduction till the overvoltage is not detected, therefore increasing

semiconductor losses.

## 1.5.3 Soft switching converters

The switch stresses, as discussed in previous sections, can be reduced by connecting simple dissipative snubber subcircuits in series and parallel with the switches in the switch mode converters (Fig. 1-1). However, these dissipative snubbers shift the switching power losses from the active device to the snubber elements, and therefore do not provide a significant reduction in the overall switching power losses.

In contrast to dissipative snubbers in switch-mode converters, the combination of proper converter topologies and switching strategies can overcome the problems of switching stresses, switching power losses, and the EMI by turning on and turning off each of the converter switches when either the switch voltage or the switch current is zero. Ideally, both the switch voltage and current should be zero when the switching transition occurs.

The converter topologies that can provide an automatic and lossless resetting of the snubber components through inherent converter operation are referred to as soft switching converters. Such topologies are very attractive at high-power levels when high-frequency operation is to be achieved concurrently, since they allow an oversizing of the snubber subcircuit without introducing the normal penalty of the trapped energy which needs to be dissipated.

Generally, soft switching topologies are divided into the following two types:

- zero current switching (ZCS) which refers to device turn-on and turn-off occurring with nearly no current in the switch.

- zero voltage switching (ZVS) which refers to device turn-on and turn-off occurring with almost no voltage across the device.

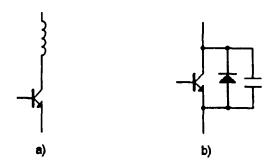

Figure 1-2: Soft switching elements.

- a) Zero current switching during turn-on only.

- b) Zero voltage switching during turn-off only.

Fig. 1-2 shows the two types of devices that experience zero current switching during turn-on only and zero voltage switching during turn-off only respectively. The snubber subcircuits associated with zero current switching are purely inductive. The snubber subcircuits associated with zero voltage switching are purely capacitive and the device turn-on must occur with the antiparallel diode conducting.

The main advantages gained by using soft switching elements are as follows:

- very low switching losses and stresses;

- improved converter reliability;

- recirculation of the energy associated with snubber elements, therefore improved overall system efficiency;

- reduced need for cooling means;

- achievement of higher switching frequencies.

Some of these converter topologies which experience zero-voltage and/or zerocurrent switching, are presented in Chapter 2.

## 1.6 Scope and contributions

The scope and objective of this thesis is to present, analyze and verify experimentally soft switching, namely zero voltage switching pulse width modulated inverter topologies. In particular, the principal contributions of this thesis are as follows:

- The analysis, design and experimental verification of a single-phase full-bridge high-power low-frequency PWM converter topology employing a low loss snubber network (Chapter 3).

- A simple energy recovery subcircuit to improve the efficiency of the same topology is investigated (Chapter 3).

- The analysis, design and experimental validation of a zero voltage switching PWM converter topology using a lossless dc bus commutating subcircuit (Chapter 4).

- A three-phase zero voltage switching pulse width modulated voltage source inverter topology is presented (Chapter 5).

## 1.7 Summary of the thesis

The contents of the thesis have been organized as follows:

Chapter 2 presents the most widely used converter topologies for dc-dc and dc-ac energy conversion. The hard switching topologies (mainly PWM converters) and the soft switching ones (i.e. resonant, quasi-resonant, etc.) are presented. The advantages and the drawbacks of these converters are critically discussed.

In Chapter 3, a low loss snubber network for high-power low-frequency single-phase full-bridge PWM converter first is considered. A modified lossless snubber network for the same type of converter is proposed. The main advantage of the converter under consideration is that, at least, theoretically, no energy associated with the snubber reactive

elements is lost. Detailed analysis and design procedures for both power converter topologies are included. Experimental results are presented to verify the principles of operation of the proposed topology.

In Chapter 4, a zero voltage switching (ZVS) high-frequency medium-power single-phase full-bridge PWM converter topology is proposed. The inverter purely capacitive snubber provides nearly zero switching losses during turn-off. The active dc bus subcircuit provides almost zero switching losses during turn-on, by forcing the respective switch antiparallel diodes to conduct prior to main switch turn-on. Converter analysis and design procedure are included. Experimental results are presented to verify the feasibility of the proposed converter topology.

In Chapter 5, a three-phase ZVS PWM VSI topology is studied. The main advantage of the proposed scheme is that the dc bus commutating circuit is synchronized with an appropriate PWM technique. Both the power inverter topology and the modulation technique minimize switching losses thus improving the overall system performance. Detailed description of the modulation strategy and the principles of operation of the inverter are presented. It is also shown that the modulation strategy is optimum for the proposed inverter topology.

Finally, Chapter 6 contains a summary and conclusions of the thesis as well as suggestions for future work.

#### CHAPTER 2

# DC-DC & DC-AC CONVERTER TOPOLOGIES

#### 2.1 Introduction

The three major application areas of power converter technology using selfcommutated devices are as follows:

- dc-dc converters.

- dc-ac inverters, and

- ac-dc converters such as pulse width modulated rectifiers.

There exist numerous converter topologies, depending upon the power level, to accomplish the desired conversion functions.

In this chapter, first the conventional PWM dc-dc topologies are presented [22],[23],[24]. Thereafter, converter topologies referred to as soft switching topologies such as resonant, quasi-resonant, multi-resonant, and other soft switching topologies are also considered. The six-switch three-phase PWM converter, which is widely used for dc-ac energy conversion, is then discussed. Since 1986, significant new developments have been made in the area of power electronic inverter topologies, especially for high power applications. For these new converter topologies attempt has been made to substantially eliminate the semiconductor switching losses. Converters with these properties allow the semiconductor devices to be operated at increased switching frequencies which are then only limited by the device intrinsic delay times rather than its thermal characteristics. Consequently, power electronic converters can be designed which attain higher efficiencies

and bandwidth and which achieve higher power densities. The various soft switching threephase inverter topologies are critically presented in the following sections.

### 2.2 Hard switching PWM dc-dc converter topologies

Most dc-dc applications require single quadrant operation, unipolar voltage and current and unidirectional power flow. The most widely used converter topologies may be classified as hard switching pulse width modulated converters. These topologies are referred to as hard switching topologies because the switching trajectory of the semiconductor devices results in device stresses. Specifically, with hard switching, the power device experiences simultaneously high voltages and currents during turn-on and turn-off leading to high switching losses. The reverse recovery of the free-wheeling diode in a converter phase leg may cause current spikes and EMI. A simple and rugged way of improving semiconductor switching trajectory is by employing snubber networks. These snubber networks have been discussed briefly in Chapter 1.

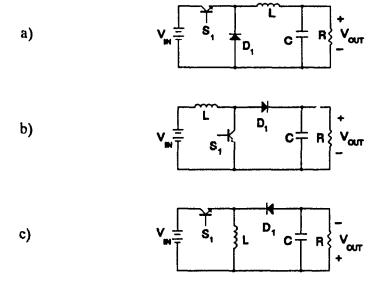

Most dc-dc converters are derived from the three single quadrant topologies, namely, the buck, the boost and the buck-boost converters [23]. These basic converter topologies are shown in Fig. 2-1. For dc-dc power applications such as the off-line switch mode power supplies (SMPS), there exist a need for high frequency isolation using a transformer. Such static power converters requiring galvanic isolation, include the flyback and forward converters for low power applications (Fig. 2-2), the dual forward and half bridge converters for moderate power applications (Fig. 2-3) and lastly the full bridge converter for high power applications (Fig. 2-4). The advantages and the problems of the hard switching PWM dc-dc converters are discussed in the following sections.

Figure 2-1: a) Buck switching converter.

- b) Boost switching converter.

- c) Buck-Boost switching converter.

Figure 2-2: a) Flyback switching converter.

b) Forward switching converter.

Figure 2-3: Isolated medium power converter topologies

- a) Dual forward switching converter.

- b) Half-bridge switching converter.

Figure 2-4: Full-bridge switching converter.

#### 2.2.1 Advantages of PWM converters

PWM converters still represent the dominant technology in use by industry today.

The reason being that they offer a great deal of advantages which can be summarized as follows:

- simple and rugged power circuit;

- voltage/current control techniques are simple as well;

- low cost;

- minimum VA ratings of semiconductor devices.

Although PWM converters provide a simple solution, they have a numbe. of undesired features. The next section addresses the most serious drawbacks of the PWM converters.

#### 2.2.2 Drawbacks of PWM converters

Most PWM converters operate at low and medium frequency. The reason being that PWM converters need to switch rapidly to minimize switching losses. However, the fast rising edges in the switching waveforms generate a lot of EMI. Both switching losses and EMI tend to increase according to switching frequency. Any attempt to improve converter efficiency by switching faster also increases the level of generated EMI.

The above mentioned problems can be overcome to a certain extend by selecting converter components very carefully. Nevertheless, energy stored in the parasitic inductances is still a significant issue. Therefore, effective snubber networks such as the conventional ones presented in Chapter 1 are required.

Additional problems of the PWM converters at low and medium power levels operating at high switching frequencies are as follows:

- more drive power is required, especially for MOSFET's, which are used to realize high frequency energy conversion;

- equivalent series resistance of capacitors and parasitic effects of magnetic components become significant limiting factors;

- the layout of the power circuit becomes particularly critical to the performance of the converter.

Parasitic elements also create problems. Some of the most important parasitics are the stored charge in the diodes and other semiconductor devices such as MOSFET's, the stray inductance of even short wire connections and the stray capacitance associated with circuit elements.

Generally, limitations in any power converter topology are introduced by the following parameters:

- peak semiconductor voltage and current;

- peak capacitor voltage;

- RMS current in all components;

- size, weight and cost of passive filter components;

- overall circuit efficiency;

- controllability;

- fault tolerance;

- electromagnetic interference.

During the last two decades, a lot of research work has been done towards achieving higher switching frequencies. This work has produced topologies known as *soft switching* topologies and some of them are presented in the following sections.

#### 2.3 Soft switching de-de converters

Although the area of soft switching converters is new, it is very broad. An attempt has been made in the following sections to present only the basic topologies of such dc-dc converter topologies.

#### 2.3.1 Resonant dc-dc converters

Historically, prior to the availability of self-commutated switches with appreciable voltage- and current-handling capability, the switch-mode converters consisted of thyristors (currently thyristors are employed only at very high power levels). Each thyristor in such a converter required a current-commutation subcircuit, which consisted of an *L-C* resonant circuit plus other auxiliary thyristors and diodes, which turned the main thyristor off by forcing the current through it to go to zero.

A need to increase switching frequencies resulted in replacing the thyristors with self-commutated switches and a simple L-C resonant circuit was used to shape the switch voltage and current in order to yield zero-voltage and/or zero-current switching.

The series resonant converter is one of the earlier resonant dc-dc converters, proposed in the technical literature, that provides zero current switching [25]. The circuit proposed in this paper is mainly suitable for high power applications employing thyristors as switching devices. Switch mode power supplies (SMPS) employing series or parallel resonant tank have been also proposed in the literature. Although the series resonant topology is more suitable for high power applications, the parallel output series resonant converter (POSR) provides better characteristics for SMPS systems [26]. The respective converter topologies are shown in Fig. 2-5. If the circuit operates below the  $L_R$  -  $C_R$  tank resonant frequency, it allows natural commutation of these devices, providing zero current

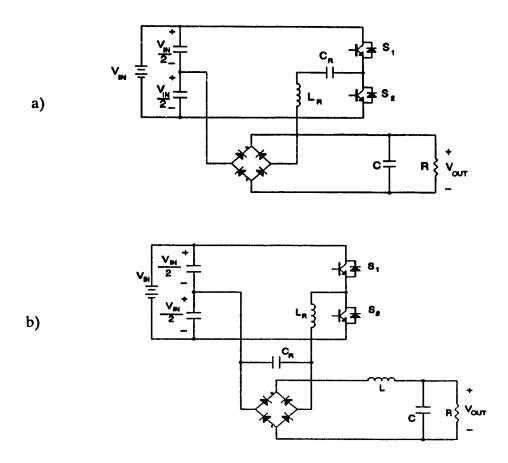

Figure 2-5: Resonant dc-dc converter topologies.

- a) Half-bridge series resonant converter.

- b) Half-bridge parallel output series resonant converter.

switching in all power devices. It is further shown in [26] that if the switching devices are force-commutated elements such as MOSFET's or BJT's switches, operation of the circuit above the resonant frequency of the  $L_R$  -  $C_R$  tank can be obtained. Moreover, zero voltage switching for all devices is achieved. Another zero voltage switching resonant mode dc-dc converter is also proposed in [27].

# 2.3.1.a Advantages of resonant dc-dc converters

The primary objective in selecting resonant mode operation is the reduction of device switching losses. Both ZCS and ZVS topologies attempt to minimize switching losses through the use of low loss snubbers.

The advantages of the resonant dc-dc topologies can be summarized as follows:

- low di/dt stress on components due to the non-rectangular waveforms;

- low level of generated EMI;

- improved efficiency since they provide nearly zero switching losses (switching is done either at zero current or zero voltage);

- parasitic elements can be utilized as part of the power processing circuit;

- fast transient response due to higher switching frequencies attained.

#### 2.3.1.b Drawbacks of resonant dc-dc converters

The most serious problems that can be identified for the various resonant converter topologies are as follows:

- generally, both kind of topologies, namely, ZCS and ZVS require a wide range of frequency control, thus making the optimization of the filter components and design of output transformer and EMI filters difficult;

- high RMS currents which result in high conduction losses;

- the use of a resonant mechanism to transfer power from the source to the load implies the use of an underdamped L-C circuit with substantial circulating energy trapped in these elements;

- significantly higher VA ratings, compared with the output power, for the devices and other circuit components are required, resulting in inefficient utilization of

device capabilities;

- high control circuit complexity since the switching of the semiconductor devices must be done either at zero current or zero voltage.

The above mentioned problems make these topologies unattractive for medium and high-power high-frequency industrial applications.

#### 2.3.1.c Comparison between ZCS and ZVS

In ZCS converters, the current produced by L-C resonance flows through the switch, thus causing it to turn-on and off at zero current. In ZVS converters, the resonant capacitor produces a zero voltage across the switch at which instant the switch can be turned on or off. Both of these techniques require a variable frequency control to regulate the output voltage.

The ZCS topologies are limited in frequencies achievable by the reverse recovery phenomena associated with the antiparallel diode of the main switching device. Moreover, high peak currents during reverse recovery process of the antiparallel diodes contribute high switching losses and high voltage spikes.

On the other hand, ZVS topologies require that the antiparallel diode is conducting prior to the main switch turn-on. By synchronizing the turn-on instant with antiparallel diode conduction, also eliminates the snubber dump phenomenon which normally occurs during main device turn-on and thus allowing the use of purely capacitive snubber elements.

It has been shown that zero voltage switching as opposed to zero current switching is more appropriate control strategy for high-frequency resonant mode converters [27],[28]. This has to do with the internal capacitors of the switch. Specifically, with the turn-on at zero current but at a finite voltage, the charge on the internal capacitors is dissipated in the

switch. This loss becomes significant at very high switching frequencies. However, no such loss occurs if the switch turns on at a zero voltage. In the ZCS, the switch is required to conduct a peak current that is higher than the load current. In the ZVS the switch is required to withstand a forward voltage that is higher than the input supply voltage. This results in a very large rating of the switch for both type of converters.

#### 2.3.2 Quasi-resonant dc-dc converters

To overcome the problems associated with the resonant topologies, quasi-resonant converters such as the zero-current-switching quasi-resonant converter (ZCS-QRC) have been developed [28]. The respective circuit is shown in Fig. 2-6. Different quasi-resonant converters that experience ZVS or ZCS are also discussed in the technical literature [29].

Although these circuits provide improved characteristics compared with the resonant converters, various problems can be also identified. Peak voltage stress associated especially with the ZVS topologies is the most serious problem of the "family" of the quasi-resonant converters. Reverse diode recovery causes voltage spikes and finally the need to limit the voltage stresses restrict the operating range of the quasi-resonant converters.

Figure 2-6: The ZCS-quasi resonant converter.

#### 2.3.3 Multi-resonant dc-dc converters

Another promising development has been the recently proposed multi-resonant converter [30]. The ZVS quasi-resonant topology is extended to incorporate the additional parasitic elements associated with the free-wheeling diode. The frequency range is reduced therefore the optimization of the filter components becomes easier. However, the high component stresses make it impractical at high-power or high-voltage applications.

#### 2.3.4 Other soft switching dc-dc converters

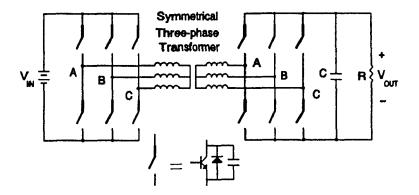

For high-power multi-quadrant applications, dual bridge topologies such as the circuit shown in Fig. 2-7 can be used [31]. These topologies feature minimal device ratings for a given output power and have almost no switching losses. They fall into the category of soft switching converters that employ resonant transitions, but are very similar to hard switching topologies.

Figure 2-7: Three-phase dual bridge soft switching converter.

# 2.3.5 Soft switching single-phase full-bridge PWM dc-dc converter topology

In this section a soft switching single-phase full-bridge PWM dc-dc converter topology that experiences zero voltage switching is considered in detail. A phase-shifted PWM technique is presented. The problems associated with this topology are identified. The various topologies proposed in this research area are discussed.

# 2.3.5.a Phase-shifted PWM technique for single-phase full-bridge converter

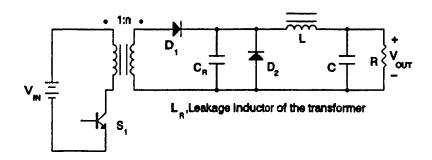

When the conventional PWM technique is employed with the single-phase full-bridge topology shown in Fig. 2-8, the diagonal switches are turned on simultaneously  $(S_1 - S_4)$ , or  $S_2 - S_3$  to apply the input voltage  $V_{IN}$  across the primary circuit of the high frequency transformer. Fig. 2-9 shows the switch gating signals as well as the respective voltage waveform  $V_L$  across the transformer primary winding. To achieve a freewheeling mode, all the switches are turned off forcing the primary current to decrease towards zero. The load current freewheels through the rectifier diodes and the transformer magnetizing current circulates through the secondary winding and the rectifier diodes as well.

In the phase-shifted PWM technique, the gating signals are such that, instead of turning on the diagonally opposite switches in the bridge simultaneously, like in the conventional PWM technique, a phase-shift is introduced between the gating signals of the switches in the left leg and those in the right one. This phase-shift determines the duty cycle of the converter. The switch gating signals and the respective voltage  $V_L$  across the primary circuit are shown in Fig. 2-10. Specifically, with this method, top and bottom switches of the same bridge leg are alternately gated for the fixed interval of nearly half a period (delays to avoid short-circuit path are necessary). Output power control or voltage regulation is obtained by phase shifting the fixed duty cycle gating signals of the two bridge

Figure 2-8: Zero voltage switching converter topology with a passive clamping circuit across the secondary side employing phase-shifted PWM technique.

legs with respect to each other. Consequently, when the two pairs of gating signals are in phase, the output voltage is zero and when they are completely out-of-phase, the output voltage is maximum. During the freewheeling mode, either the top two  $(S_1, S_3)$  or the bottom two  $(S_2, S_4)$  switches are on (Fig. 2-10). The load and the magnetizing currents reflected to the primary can therefore continue to flow in the primary winding, through one switch and one antiparallel diode, thus providing a zero volts interval across the primary circuit. The secondary also freewheels using the energy stored in the output filter inductor.

Figure 2-9: Conventional PWM technique for single-phase full-bridge converter.

- a) Switch gating signals.

- b) Voltage waveform across the primary circuit.

Figure 2-10: Phase-shifted PWM technique for single-phase full-bridge converter.

- a) Switch gating signals.

- b) Voltage waveform across the primary circuit.

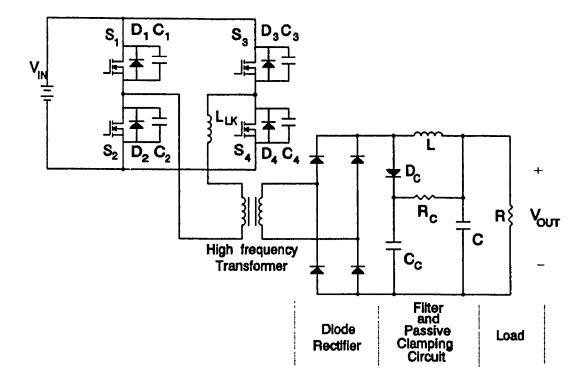

#### 2.3.5.b Phase-shifted PWM technique and zero voltage switching (ZVS)

Employing the phase-shifted PWM technique, and utilizing circuit parasitic elements  $(L_{LK} \text{ and } C_1, C_2, C_3, C_4, \text{ Fig. 2-8})$ , zero voltage switching conditions for all the devices  $(S_1 - S_4)$  can be obtained as follows [32],[33],[34]:

The zero-voltage turn-on is achieved by using the energy stored in the leakage inductor  $L_{LK}$  (Fig. 2-8) of the transformer to discharge the switch capacitors ( $C_1 - C_4$ ) before turning the transistors on. Specifically,  $S_4$  and  $S_1$  are conducting and switch  $S_4$  is turned off. The current through the primary of the transformer charges first the respective capacitor  $C_4$  and discharges the capacitor  $C_2$ , turning on the antiparallel diode  $D_2$ . After diode  $D_2$  conduction,  $S_2$  can be turned on with zero voltage across the switch. However, in order to achieve zero-voltage turn-on, the energy stored in the leakage inductor  $L_{LK}$  needs to be larger than the energy trapped in the switch capacitor. For the other leg, the ZVS is obtained as follows. Switch  $S_1$  is turned off and the current through the primary discharges the capacitor  $C_3$ . Consequently, diode  $D_3$  is turned on. After  $D_3$  starts conducting,  $S_3$  can be turned on under zero voltage conditions. In this case, when  $S_1$  is turned off, the current through the primary of the transformer is the output current reflected to the primary. Furthermore, ZVS for switches  $S_1$ ,  $S_3$  is achieved easily since the energy of the large filter inductor in the secondary side is used to obtain ZVS.

# 2.3.5.c Advantages of the single-phase full-bridge phase-shifted soft switching PWM topology

The advantages of the single-phase full-bridge converter (Fig. 2-8) operating with the phase-shifted PWM technique (Fig. 2-10) can be summarized as follows:

- zero-voltage-switching (ZVS) which enables high frequency operation due to

reduced switching losses;

- simplicity of the control circuit due to the PWM technique compared with the resonant converter control circuit which is very complicated;

- snubberless topology since parasitic elements are utilized to achieve soft switching conditions;

- easy optimization of the magnetics and filter designs due to the constant frequency operation;

- the Miller effect for MOSFET devices is minimized due to the ZVS resulting in reduced EMI;

- lower RMS currents than the resonant converter;

# 2.3.5.d Drawbacks of the single-phase full-bridge phase-shifted soft switching PWM topology

On the other hand, for the topology under consideration, the following disadvantages can be identified:

- zero voltage switching conditions are difficult to obtain at very low load (typically lower than 50%);

- the topology is not symmetrical; that is the ZVS conditions for one leg are obtained easier than the other one;

- increased conduction losses due to the higher circulating primary currents;

- the delay time between turn-off of one switch and turn-on of the other in the same leg is not precisely controllable due to the inherent delays associated with the drive circuits;

- higher RMS currents than the conventional hard switching PWM topology;

- energy loss during switching turn-off of the rectifier diodes since they are switched at finite but not zero voltage;

In order to overcome the aforementioned drawbacks, improved single-phase full-bridge topologies employing phase-shifted PWM technique have been recently proposed.

A brief presentation of these topologies is provided in the following section.

# 2.3.5.e Improved single-phase full-bridge PWM soft switching topologies

The topology discussed above (Fig. 2-8) however, does not provide any means of absorbing the parasitic capacitors of the rectifier diodes [32],[33]. The interaction of the diode rectifier parasitic capacitors with the leakage inductor of the high frequency transformer causes severe voltage overshoot and ringing across the diodes. This problem cannot be solved easily since the leakage inductor of the power transformer is necessary for the operation of the circuit (ZVS).

A passive snubber R-C network that clamps the maximum peak voltage of the ringing and returns part of the energy to the output load is proposed in [34]. This arrangement has been shown in Fig. 2-8. The same network is employed in [35] but it is also shown in this paper that this solution can be impractical for high-frequency high-voltage applications. Moreover, this circuit clamps the peak voltage in the secondary circuit, but does nothing to damp or prevent the ringing. The excessive ringing causes EMI and control problems.

More recently, an alternative topology with an active clamping circuit across the secondary winding and the rectifier diodes is investigated [38]. In this case, when the secondary voltage is high, the active clamp circuit, consisting of a clamp capacitor, a snubber diode and an auxiliary switch, connects a large capacitor (voltage source) in parallel with

the diode rectifiers. Therefore, there is no voltage overshoot in the secondary circuit. In steady-state, the average power flow through the clamping capacitor is zero. Energy from the leakage inductor of the transformer is transferred to the clamp capacitor through the snubber diode. The extra energy is discharged to the load through the snubber auxiliary switch. However, the main drawback of this topology is that the duty cycle is restricted to close to unity values. The reason being that under lower values of duty cycle, the overvoltage across the clamping capacitor is increased drastically, therefore the stresses across the semiconductor devices are also increased.

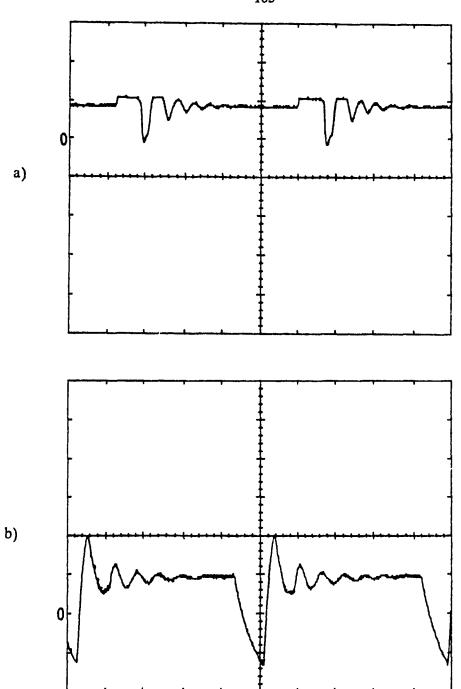

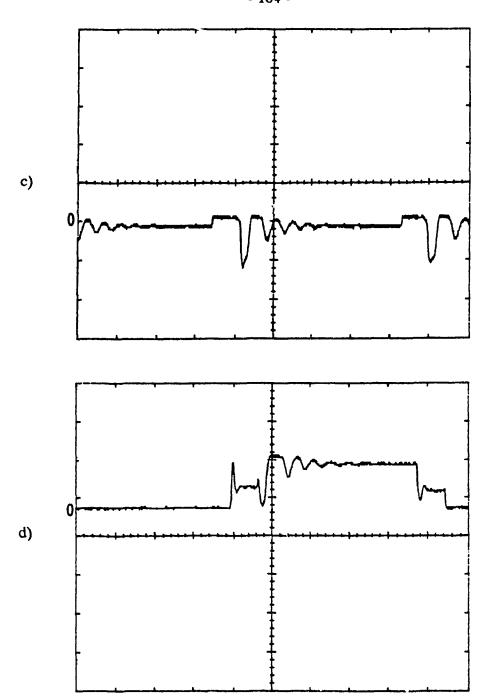

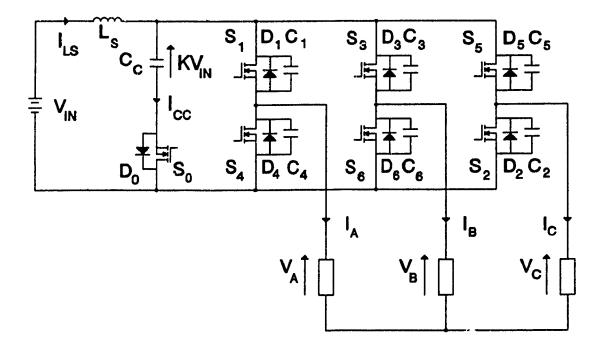

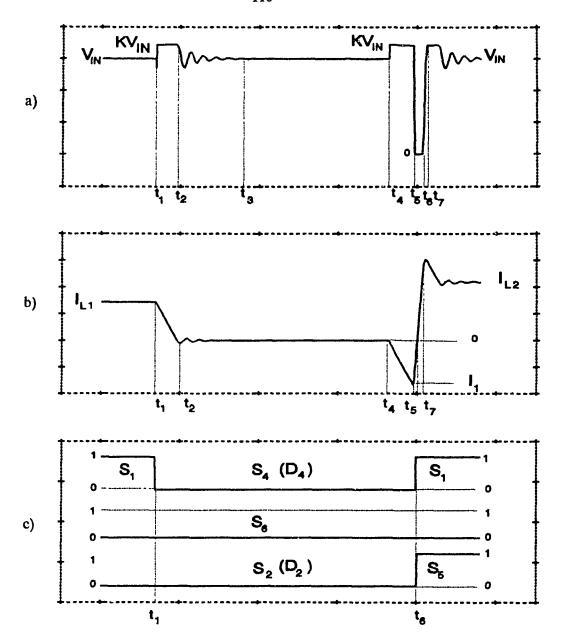

An improved single-phase full-bridge soft switching topology, using phase-shifted PWM technique and being able to achieve ZVS under lower load conditions, has been recently proposed [37]. An external commutating inductor and two clamp diodes, added to the phase-shifted single-phase full-bridge PWM converter, substantially reduce the switching losses of the semiconductor devices and the rectifier diodes under lower load conditions as well. However, this topology requires the use of a low leakage power transformer. The design process is complicated and ZVS conditions cannot be obtained under wide range of load.