A VIRTUAL MACHINE FOR CONCURRENT PASCAL

ON THE TI 980B

Tri Manh Pham

A Thesis in the .

Department of Computer\_Science

Presented in Partial Fulfillment of the Requirements

for the Degree of Master of Computer Science at

Concordia University

Montreal, Quebec, Canada

June, 1981

(c) Tri Manh Pham 1981

#### **ABSTRACT**

## A VIRTUAL MACHINE FOR CONCURRENT PASCAL

ON THE TI 980B

## Tri Manh Pham

Concurrent Pascal is a programming language designed for the writing of portable operating systems, originally implemented on a DEC PDP-11/45. This thesis describes the transportation of Concurrent Pascal from the PDP-11/45 to the TI 980B. Some comments are made about the portability of this language.

## ACKNOWLEDGEMENTS

It is my pleasure to gratefully acknowledge the advice and support of Professor J. W. Atwood during the preparation of this thesis.

I wish' to thank Mr. Pierre Desjardins, Université de Montreal, for his availability and assistance in explaining the SOLO operating system.

I wish to thank Professor D. Thalmann of the Department of Computer Science, Université de Montréal, with whom I had fruitful discussions on virtual machines as tools for software portability.

I wish to thank Professor V. Wallentine and Mr. David Neal of the Department of Computer Science, Kansas State University, for having kindly sent me the invaluable technical reports on Concurrent Pascal.

I wish to thank Dr. I. Greenshields for his availability and precious advice in debugging concurrent programs.

I wish to thank all my friends who have helped me one way or another to get this work done.

This work was supported by a research assistantship from the Natural Sciences and Engineering Reasearch Council of Canada, through Dr. Atwood.

# TABLE OF CONTENTS

| 1       | Introduction                                    |             | 1  |

|---------|-------------------------------------------------|-------------|----|

| 1.1     | Systems implementation languages                | •           | 1  |

| 1,1.1   | Assembly languages                              | · p         | 1  |

| 1.1.2   | Machine-oriented high-level languages           |             | 2. |

| 1.1.2.1 | BLISS                                           | ·           | 3  |

| 1.1.2.2 | PL360                                           | ۰ نسر       | 3, |

| 1.1.2.3 | BCPL                                            | f" <b>b</b> | 4  |

| 1.1.3   | Machine-independent high-level languages        | •           | 4  |

| 1.1.3.1 | Concurrent Pascal                               |             | 4  |

| 1.1.3.2 | Modula                                          |             | 5  |

| 1.2     | Software portability and abstract machines      |             | 5  |

| 1.2.1   | Virtual machines                                | ,           | 6  |

| 1.2.1.1 | The UNCOL machine                               | •           | 7  |

| 1.2.1.2 | The JANUS machine                               |             | 8  |

| 1/2.1.3 | The OCODE and INTCODE machine                   | ٠.          | 8  |

| 1.2.1+4 | The PICA-B machine -                            |             | 9  |

| 1.2.1.5 | The MUSS machine                                |             | 10 |

| 1.2.1.6 | The LAMDA machine                               |             | 10 |

| 1.2.1.7 | The Concurrent Pascal machine                   |             | 11 |

| 1.3     | Thesis structure .                              |             | 12 |

|         |                                                 |             |    |

|         |                                                 |             |    |

| 2 ;     | Concurrent Pascal as an implementation language | • '         | 13 |

| 2.1     | Abstract data types                             |             | 13 |

| e de la companya de la companya |                                             | against de referencement on the sufficient of the suffine sufficient of the sufficient of the sufficient of the sufficie |

|---------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •                               |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| •                               |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                 |                                             | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.1.1                           | Processes                                   | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.1.2                           | Monitors                                    | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| a 2.1.3                         | Classes                                     | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.2                             | Conclusion                                  | 20.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| į                               |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.                              | The Concurrent Pascal virtual machine       | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.0                             | The Structure of Concurrent Pascal programs | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| (3.1.                           | The Architecture of the virtual machine     | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| /3 <b>.2</b>                    | The PDP-11/45 architecture                  | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.2.1                           | The CPU                                     | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.2.2                           | The registers,                              | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.2.3                           | The memory organization                     | 27 .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.2.4                           | The memory management                       | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| *<br>3.2.5                      | The I/O architecture                        | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.3                             | Concurrent Pascal and the PDP-11/45         | 30 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.3.1                           | Use of the CPU                              | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| / 3.3.2                         | * Use of memory management unit             | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.3.3                           | The interpreter on the PDP-11/45            | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.3.3.1                         | The jump table                              | 34*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.3.3.2                         | The Process Head                            | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <b>4</b> 3.3.3.3                | The interpreter routines                    | ·35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.3.3.4                         | Threaded-code implementation                | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.3.3.5                         | Interpreter tracing                         | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.3.4                           | , The kernel on the PDP 11/45               | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.3.4.1                         | Processor multiplexing                      | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.3.4.2                         | Monitor implementation                      | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.3.4.3                         | Peripheral activation                       | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                 |                                             | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                 | - V -                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.4     | Execution of a Sequential Pascal program     | 44   |

|---------|----------------------------------------------|------|

| 3.5     | Initiating the system                        | 47   |

| •       |                                              |      |

| 4.      | The Concurrent Pascal machine on the TI 980B | 49   |

| 4.0     | The transportation process                   | 49   |

| 4.1     | The TI 980B architecture                     | 5 σ  |

| 4.1.1   | . The CPU                                    | 50   |

| 4.1.2   | The registers                                | 50   |

| 4.1.3   | Memory organization                          | 51   |

| 4.1.4   | Memory management                            | 52   |

| 4.1.5   | I/O architecture                             | , 52 |

| 4.2     | Concurrent Pascal and the TI 980B            | 53   |

| 4.2.1   | Use of the CPU                               | 53   |

| 4,2.2   | Use of memory with LLR                       | 54   |

| 4.2.3   | Simulating the PDP-11/45 virtual memory      | , 54 |

| 4.2.3.1 | Address translation                          | 54   |

| 4.2.3.2 | Memory allocation                            | . 57 |

| 4.2.4   | The Interpreter on the TI 980B               | 57   |

| 4.2.4.1 | Register allocation                          | 58   |

| 4.2.4.2 | Simulating the bit/byte numbering system .   | 59   |

| 4.2.4.3 | Threaded-code implementation                 | 59   |

| 4.2.4.4 | Stack addressing                             | 6,0  |

| 4.2.5   | The Kernel on the TI 980B                    | 61   |

| 4.2.5.1 | Processor multiplexing                       | 61   |

| 4.2.5.2 | Simulating PDP-11/45 real arithmetic         | 62   |

| 4.2.5.3 | Peripheral activation                        | 62   |

| 4.3     | Initiating the system                        | 62   |

| 4.4    | Validating the system              |    | . 64         |

|--------|------------------------------------|----|--------------|

| 4.5    | Portability of Concurrent Pascal   |    | 6            |

| 4.6    | Conclusion                         |    | 61           |

| 5.     | Conclusion                         |    | 69           |

| •      |                                    |    | • •          |

|        |                                    | 13 | i            |

| Refere | ences ,                            | ٧. | <b>,</b> 7   |

| Append | lîx 1: PREFACE user manual         | ,  | 7            |

| Append | dix 2: Interpreter operations      |    | 7            |

| Append | dix 3: Abstract data type examples | 2  | . <b>8</b> 1 |

# LIST OF FIGURES

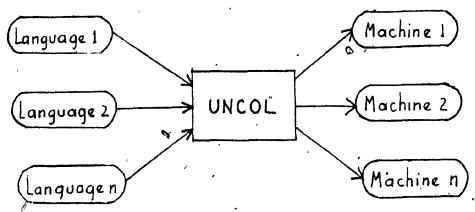

| Figure 1.1 The UNCOL approach to portability          | 7    |

|-------------------------------------------------------|------|

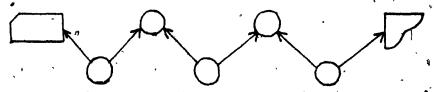

| Figure 2.1 A pipeline system                          | 16   |

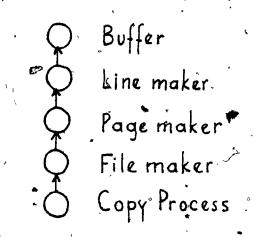

| Figure 2.2 Decomposition of the copy process          | . 17 |

| Figure 3.1 Skeleton of a Concurrent Pascal program    | 22   |

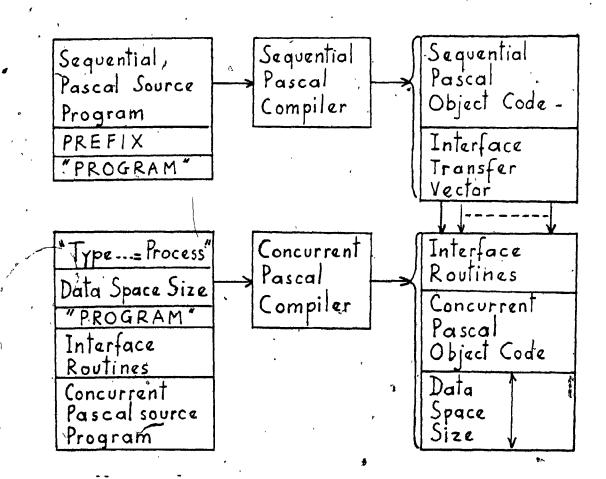

| Figure 3.2 Concurrent and Sequential Pascal interface | 24   |

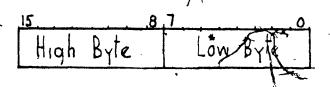

| Figure 3.3 A PDP-11 memory word                       | . 27 |

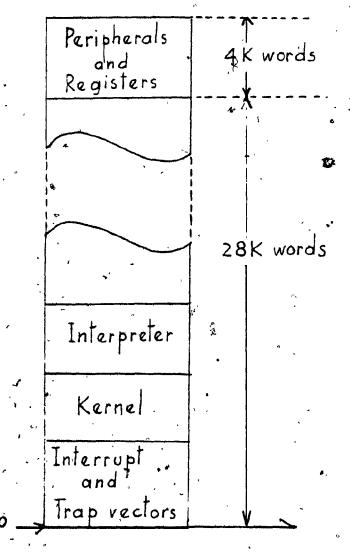

| Figure 3.4 Virtual address space in kernel mode       | 31   |

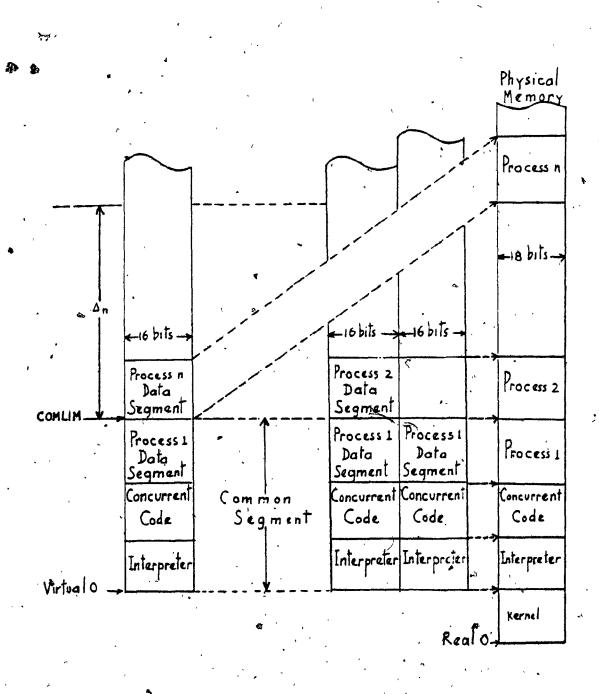

| Figure 3.5 Virtual address space for process n        | 33   |

| Figure 3.6 A simple job process skeleton              | . 46 |

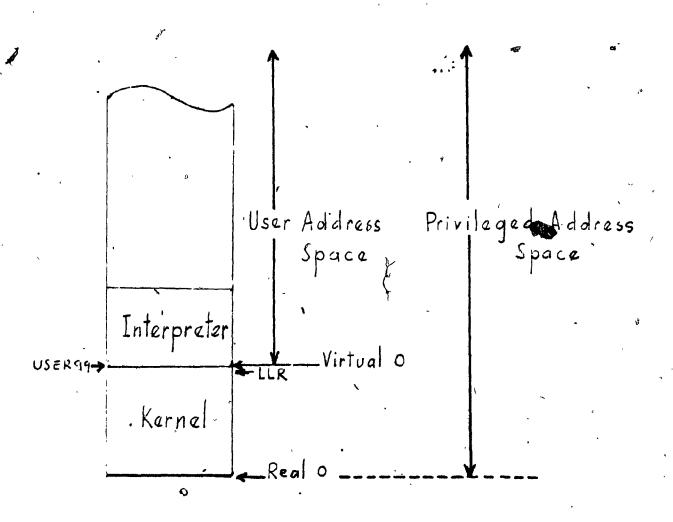

| Figure 4.1 The two address spaces on the TI 980B      | 55   |

#### INTRODUCTION

1.1 Systems implementation languages

Concurrent programming is intellectually intriguing and is essential in the design of operating systems. Operating systems have been written in three types of languages:

- 1- assembly languages

- 2- machine-oriented high level languages

- 3- high level languages

## 1.1.1 Assembly languages

Assembly languages allow maximum exploitation of hardware and therefore are advocated for their run-time and, memory efficiency. On the other 'hand, 'assembly languages unsafe because their complete of accessibility to sensitive areas of the hardware. operating systems in assembly code is very fastidious work. Bit-picking cleverness and machine-instruction intricacies <sup>a</sup>tend to camouflage program logic and underlying algorithms. Operating systems written in assembly code are rarely well documented; modifications are hard to implement and often turn out as a source of errors. Improvements may therefore in actual degradation. Furthermore, systems are not portable from one machine to another.

## 141.2 Machine-oriented high-level languages

"While the need for space and time efficiency is a relevant criterion for operating systems, other criteria have increased in importance, largely because of the increasing cost of software development and maintenance:

- High programmer productivity

- Clarity of system structure

- Readability

- Control over programming style

- Ease of testing and debugging

- Portability