# Table of Contents

| Lis       | t  | 0     | f   | τ.       | <u>.</u> + | . 1      |    | _   |            |            |   |            |          |          |   |        |            |            |         |    |   |     | •          |   |    |   |   |     |   |   | ,   | r   |     |   |    |     |   |   | • |   |     |             |     |   | P       | a g | ) e  |

|-----------|----|-------|-----|----------|------------|----------|----|-----|------------|------------|---|------------|----------|----------|---|--------|------------|------------|---------|----|---|-----|------------|---|----|---|---|-----|---|---|-----|-----|-----|---|----|-----|---|---|---|---|-----|-------------|-----|---|---------|-----|------|

|           |    |       |     |          |            |          |    |     |            |            |   |            |          |          |   |        |            |            |         |    |   |     |            |   |    |   |   |     |   |   |     |     |     |   |    |     |   |   |   |   |     |             |     | • |         | ,   |      |

| Lis       |    |       |     |          |            |          |    |     |            |            |   |            |          |          |   |        |            |            |         |    |   |     |            |   |    |   |   |     |   |   | - 7 |     |     |   |    |     |   |   |   |   |     | •           |     |   |         | i i | 1    |

| lnt       | rc | dı    |     | t ·      | ic         | 'n       | ٠, |     |            | •          | • | •          | •        |          | • |        |            |            |         | •  | • |     |            |   | •  | • | • |     | • |   | •   |     |     |   |    | •   |   | • |   | • | •   |             | •   |   |         |     | 1    |

| · , , , , |    | •     | Th  | ε        | (          | ŀn<br>\r | i  | b ( | u s<br>t r | ٠,         | t |            | •<br>ດ ເ |          |   | •      | • ·        | •`4<br>t i | · ·     | 'n | • | •   | • •        | • | •  | • |   | • • | • | - | •   | ٠,  | ٠.  |   |    |     |   |   | • | • |     | •           |     |   |         |     | 2    |

|           |    |       | P   |          | 0          | ) a      | t  | ٤   | t          | r          | ó | n          | S        | fe       | r | •      | S (        | 2 (        | t       | j  | 0 | n   | • •        |   |    |   |   |     |   |   |     | •   |     |   | •  | • • |   |   | • | • | • • |             |     |   | *       |     | 7 62 |

| ΙI        | •  |       |     | €        |            |          |    |     |            |            |   |            |          |          |   |        |            |            |         |    |   |     |            |   |    |   |   |     |   |   |     |     |     |   |    |     |   |   |   |   |     |             |     |   |         | 1   | 7    |

| 111       | •  |       | ۲ħ  | ε        | F          | ≀K       | 1  | 1   | С          | 0          | n | t          | r        | οĹ       | l | Ē      | r,         |            | •       | •  | • | •   |            | • | •  | • | • | •   |   | • | •   |     |     |   | ٠, |     |   | • |   |   |     |             |     |   | ,       | 1   | 3    |

| 1 V       | •  |       |     |          | ı          | r        | 0  | u l | i i        | n          | e | <b>5</b> € | ا<br>د 1 | r e      | i | d<br>Y | t é        | e c<br>S t | ;<br>:r | t  | 0 | ti  | I /        | 0 | •  |   | • | • • | • |   | •   | • • | • • | • |    | • • |   | • | • | • |     | ,           |     |   | •       | 2   | 2    |

|           |    |       |     |          | F          | 1        | Ĺ  | 6   | I          | ้า         | P | u          | t,       | 0        | u | ŧ.     | pı         | υţ         |         |    |   |     |            |   | •  |   |   |     |   | • |     |     |     |   |    |     |   |   |   |   |     | ·<br>·<br>· |     |   | •       | -   | 7    |

| V         |    |       | O t | h e      |            |          |    |     |            |            |   |            |          |          |   |        |            |            |         |    |   |     |            |   |    |   |   |     |   |   |     |     |     |   |    |     |   |   |   |   |     | ·           |     |   |         | -   | . 4  |

|           | -  |       |     |          | F          | ŀ        | ę  | s s | s e        | <b>.</b> y | , | P          | M·       | - 0      | C | 1      | 1          | 14         | + 0     | ١. |   |     | . 's       |   |    |   |   |     |   |   |     |     |     |   |    |     |   | • |   |   |     |             |     |   | •       | 4   | 4    |

|           |    |       |     |          | C          | o        | m  | рá  | a r        | ij         | S | 0          | n        | F        | Y | -      | D          | C 1        | 1       | 1  | 4 | O   | t          | 0 |    | Ř | Ρ | 1 1 |   | • | •   | • • | • . | • |    | •   |   | • | • |   | • • | ,           |     | , |         |     | 0    |

| Dıs       |    |       |     |          |            |          |    |     |            |            |   |            |          |          |   |        |            |            |         |    |   |     |            |   |    |   |   |     |   |   |     |     |     |   |    |     |   |   | • |   | ٠.  | •           |     |   |         | 5   | 1    |

| Con       |    |       |     |          |            |          |    |     |            |            |   |            |          |          |   |        |            |            |         |    |   |     |            |   |    |   |   |     |   |   |     |     |     |   |    |     |   |   | • | • |     | ,           |     |   | •       | 5   | 2    |

| Bib       | lί | i o g | gr  | a p      | o h        | У        | •  | •   |            | · . •      | • | •          | •        |          | • | ۲.     |            |            |         | •  |   | •   |            | • | ٩. | • |   | , . |   | • |     | • • |     | • | •  |     |   | • | • | • |     | ,           |     |   | į       | , 5 | 4    |

|           |    |       |     |          | ,          |          | _  |     |            |            |   | _          |          | ٠ _      | ن | ^      | _          | į          |         |    |   |     |            |   |    |   |   | ,   |   |   |     |     | ,   |   |    |     |   | ٠ |   | • | ļ   | ,<br>dq     | e r |   |         |     |      |

|           |    |       |     | ۱<br>۱۰  |            |          |    |     |            |            |   |            |          |          |   |        |            |            |         |    |   |     |            |   |    |   |   |     |   |   |     |     |     |   |    |     |   | • |   |   |     |             |     |   | ٨.      |     |      |

|           | *  |       | - ' | . ,<br>I | אן כ       | -        | D  | c   | 1 1        | /          | 4 | 0          | , (      | rr<br>re | g | į      | o )<br>S 1 | t          | r       |    | 1 | a : | <b>,</b> c | u | ŧ  | s | • |     | • |   | •   | • • | •   | • | •  |     | • |   | • | • | • • | 1           | ,   |   | .В<br>С |     |      |

# List of Tables

|                      |          | · ·                | •            |            | *;                           | * , -  | Page |

|----------------------|----------|--------------------|--------------|------------|------------------------------|--------|------|

| 1.1 List<br>1.2 List | of<br>of | signals<br>signals | used<br>used | for<br>for | arbitration.<br>data transmi | ission | 3    |

# List of Illustrations

|   | *       |     |     |            |          |     |     |     |      |            |     |    |     |                |   | ٠  |    |   |    | ,      |   |   |     |           | ,            |     |           |     |    |    |   |    |    |   |     |     |     |     |    |    |   |   |    |    |    |   |    |   |   |   |   |   |     |   |   |   |   |   | 1 | Pΰ | g | e  |

|---|---------|-----|-----|------------|----------|-----|-----|-----|------|------------|-----|----|-----|----------------|---|----|----|---|----|--------|---|---|-----|-----------|--------------|-----|-----------|-----|----|----|---|----|----|---|-----|-----|-----|-----|----|----|---|---|----|----|----|---|----|---|---|---|---|---|-----|---|---|---|---|---|---|----|---|----|

| 1 | . 1     | i   | 3   | u          | S        |     | C ( | 1.0 | ገ '  | f          | í   | g  | U   | Γ              | î | t  | 'n | 0 | n  |        |   |   |     |           | •            | -   | •         |     |    | •  | • | •  |    |   |     | ٠,  |     | •   |    |    |   |   |    |    |    |   |    |   |   |   |   |   |     |   |   |   |   |   |   |    |   |    |

| 1 | . 2     | 1   | £,  | r          | b        | i   | t I | r;  | 3 1  | t          | 7   | 0  | n   |                | S | Ç  | q  | u | €  | n      | c | e |     |           |              | -   | -         |     |    |    |   |    | •  |   |     |     | •   |     | •  | ,  |   |   |    | -  |    |   |    | Ť |   |   | - |   | ٠.  |   |   |   |   |   |   |    |   | 7  |

| 1 | ::      |     | I   | η          | t        | e   | r   | rı  | J,   | ו נ        | t   |    | t   | 1              | m | 7  | n  | g |    | d      | i | O | g   | r         | ر ا          | 71  |           |     |    | ,  |   |    |    |   |     |     |     |     |    |    |   |   | ,  |    |    |   |    |   |   |   |   |   |     |   |   |   |   |   |   | ,  | 1 | C  |

| 1 | . 4     | -   | D   | A,         | Ţ        | Ţ   | 1   | ŀ'  | ir   | n.         | i   | n  | g   |                | d | i  | ä  | g | r  | t.     | m | ٠ |     |           |              | . ' |           |     |    |    |   |    |    |   |     |     |     |     |    |    |   | ٠ |    |    |    |   |    |   |   |   |   | _ |     |   |   |   |   |   |   |    | 1 | 1  |

| 1 | . 5     | 1   | D   | Λ          | T        | G   | 1   | t · | ir   | n          | i   | n  | g   |                | đ | 7  | ć  | g | r  | ć,     | m |   |     |           |              |     |           |     | ٠, | à• |   |    |    |   |     |     |     | •   |    |    |   | : |    |    |    |   |    |   |   |   | • | - |     |   |   |   |   |   |   |    | 1 | 2  |

|   |         |     |     | ŧ          |          |     |     |     |      |            |     |    |     |                |   | ٠  |    | , |    |        |   |   |     |           |              |     |           |     |    | •  |   |    |    |   |     |     |     |     | ,  |    |   |   |    |    |    |   |    |   |   |   |   |   |     | , |   |   |   |   |   |    |   |    |

| 2 | . 1     | 1   | ?   | K          | () (     | 5   | •   | fι  | ۲    | 1          | ָ   | t. | i   | Œ              | n | u  | Į  |   | þ  | ι      | o | Ç | ļ   | (         | a ·          | i,  | ī.        | g   | r  | ċ  | M |    |    |   |     |     |     |     |    |    |   |   |    |    |    |   |    |   |   |   |   |   |     |   |   |   |   |   |   |    | 1 | ť, |

| 2 | . 2     | 1   | ?   | K          | ì        | 1   | 1   | 0   | ) †  | 1          | t : | r  | Q   | Į              | l | €  | r  | 1 | R  | K      | O | 5 |     | Ú         | r            | i · | v         | Č   |    | i  | n | ŧ  | ŧ  | r | ٠ 1 | fa  | . ( | . ( | ļ. |    |   |   |    |    |    |   |    |   |   |   |   |   |     |   |   |   |   |   |   |    | 1 | 7  |

|   |         |     | •   |            |          |     |     |     |      |            |     |    |     |                |   |    |    |   |    |        |   |   |     |           |              |     |           |     |    |    |   |    |    |   |     |     |     |     |    |    |   |   |    |    |    |   |    | _ |   |   |   |   |     |   |   | • | • |   |   |    |   | ٠  |

| Ĵ | 1<br>[c | . : | 9   |            |          | t   | 0 1 | _   | 1    | f          | 2   | ٦  | M . | i.             | t |    |    |   |    |        |   |   | ٠,  | \         |              |     | -         |     |    |    |   |    |    |   |     |     |     |     |    |    |   |   |    |    |    |   |    |   |   |   |   |   | ٠   |   |   |   | J |   |   |    | 1 | ۶  |

| _ | مإد     | 1   | ₹   | K          | 1        | 1   | 1   | ) ( | : 1  | : 2        |     |    | P   | ( <sub>U</sub> | t | h  | 5  |   |    |        |   |   |     | •         | •            |     |           |     |    | •  |   |    |    |   |     |     | ,   |     |    |    |   |   |    |    |    |   |    |   |   |   |   |   |     |   |   |   |   |   |   |    | 5 | 1  |

|   |         |     |     |            |          |     |     |     | ٠.   |            |     |    |     |                |   |    |    |   | ,  |        |   |   |     |           |              |     |           |     |    |    |   |    |    |   |     | `   |     |     |    |    | ١ |   |    |    |    |   |    |   |   |   |   |   | c   |   |   |   |   |   |   |    |   |    |

| 4 | . 1     | ŧ   | ₹   | K          | 1        | 1   | Ì   | ١,  | . 1  | 1          | ב   | t. | e   | r              |   | f  | ţ  | 0 | ١, |        | d | i | a j | 9         | r            | 3   | n         |     |    |    |   |    |    |   |     | ٠,٠ |     |     |    |    |   |   | ·  |    |    |   | .' |   |   |   |   |   |     | • | , |   |   |   |   |    | 5 | 5  |

| 4 | ءَ .    |     | ŝ   | C.         | : 1      | 1   | į   | 1 6 | : ۱  | <i>i</i>   | i   | C  | E   |                | d | i  | r  | ŧ | C  | t      | 0 | r | y   |           | ٠            |     |           |     |    |    |   | *  |    |   |     |     |     |     |    |    |   |   |    |    |    |   |    |   |   |   |   |   |     |   |   |   |   |   |   |    | 2 | S  |

| 4 |         | 5   | •   | Ċ:         | SI       | N   | 1   | ٠.  | : !: | ) (        | lι  | С  |     | e              | Ĺ | ć  | m  | ٥ | n  | t      |   |   |     |           |              | ٠,  |           |     |    |    |   |    |    |   |     |     |     | . , |    |    |   |   |    |    | •( |   |    |   |   |   |   |   | _   |   |   |   |   |   |   | _  | 2 | 9  |

| 4 | . 4     | , [ | Ξ Ι | ٧.         | T        | E I | R   | 1   | ft   | . (        | וכ  | W  | ,   | ď              | 1 | C, | q  | r | ï, | m      |   |   | Ρ.  | ا ت       | r 1          | t   |           | 1   |    |    |   |    | ·_ |   |     |     |     | ١.  |    |    |   | _ |    |    | 1  | _ |    |   |   |   | _ | _ | _   | Ī |   | 1 |   |   |   |    | 7 | -  |

|   |         | ч   | į   | ij.        | T I      | ΕI  | R   | 1   | fl   | . (        | וכ  | W  | ,   | d              | í | Э  | g  | r | ć  | m      |   |   | P   | 3         | ri           | t   | _         | 2   |    |    | • |    |    |   |     |     |     |     |    |    |   |   |    |    |    |   |    |   |   |   |   | - | •   |   | • |   |   |   |   |    | 3 |    |

| 4 | . 5     | •   | = : | Χ.         | T        | Ė   | N   | )   | 1    | 1          | Lα  | 0  | W   |                | d | ì  | a  | q | r  | ا ،    | m | ر |     |           |              |     |           | ٠.  |    |    |   |    |    | _ |     |     |     |     |    | _  | _ | _ |    | ٠. | _  | _ | _  | • |   | _ | _ | _ | _ ` |   |   |   |   |   |   |    | 5 |    |

| 4 | . ሪ     | ١   | _ ( | 0 (        | از       | K١  | Uf  | )   | 1    | 1          | Ĺ   | 0  | W   |                | d | 7  | â  | q | r  | ے      | m |   | •   |           |              |     | _         |     |    |    |   |    |    | _ |     |     |     |     | _  |    | _ | - | -  | -  | -  | - | •  | • |   |   | - | • | •   | • |   |   |   |   |   |    | 7 |    |

| 4 | . 7     | -   | ۲ ا | E i        | ٨        | D   | 1   | f   |      | ) <b>L</b> | ń   |    | یک  | i              | ئ | q  | r  | a | m  |        |   |   |     |           |              |     |           |     |    |    |   |    |    | _ |     |     |     |     |    | 7  | • |   |    | •  | -  | - | •  | • |   |   | - | • | •   | • |   |   |   |   |   |    | 3 | ç  |

| 4 | . Ն     | ١   | d l | R :        | 1 .      | TI  | E   | 1   | fl   | . (        | וכ  | w  | ,   | đ              | 1 | ä  | ٥  | r | é  | m      | _ | _ | _   | _         |              | _   | _         | _   | _  | (  |   | _  | _  | _ |     | 4   |     |     |    | ٠, | Ĩ |   | ٠, | •  |    | • | •  | • |   | • |   | • | •   | • |   |   | ø |   |   |    | 4 |    |

| 4 | . ý     | (   | 3 1 | П          | -<br>E 1 | L I | E   | ١   | 1/   | 1          | V.  | A  | G   | E              | R |    | f  | Ł | 0  | ,<br>Ш | • | ď | i   | a,<br>a ( |              | r;  | -<br>-: 1 | m   | Ī  | •  | P | 7  | r  | + | •   | . 1 |     |     | •  | 7  | • | • | •  | •  | •  | • | •  | • | • | • | • | • | •   | • |   |   |   |   |   |    | 4 |    |

| • | •       | 4   | וב  | ייי<br>ענו | Εį       | U   | E   | ı   | 1    | Ü          | v.  | A  | Ğ:  | E              | R |    | f  | i | o  | w      |   | ď | i   | a         | ייני<br>פוני | r   | ä.        | m   |    | •  | P | ٠. | ŗ  | t | •   |     |     | ,   |    | •  | • | • | •  | •  | •  | • | •  | • | • | • | • | 7 | •   | • |   |   |   |   |   |    | 4 |    |

|   |         |     |     | - '        | _        | - ' | _   | •   |      | Ī          |     |    | _   | _              |   |    | ,  | • | -  | • '    |   | _ | ·   | - :       | ₹ '          |     | _         | ••• |    |    | • | _  | •  | Ī | •   |     | -   | ,   | •  |    | • |   | •- | •  | -  | • | •  | • | • | • | • | • | *   | • |   |   |   | • |   |    | 7 | _  |

| 5 | .1      | F   | > [ | v.         | - (      | 0 : | s ' | 1 1 | 1    | 1          | 4 ( | Ü  |     | s.             | e | C  | t  | o | F  |        | f | 0 | r   | 7         | <u> </u>     | t   | _         |     |    |    |   |    |    |   | ٠.  |     |     |     |    |    |   |   |    |    | í  |   | ٠  |   |   |   |   |   |     |   |   |   |   |   |   |    | 4 | 7  |

### Introdu**≱**tion

This report examines the interface (both hardware and sefaceare), under RT-11, between the PDP-11 processor and the RKC5 disk drive. A This link is Looked at with the objective of connecting drives, from other manufacturers to the processor.

The processor is linked to other devices by a set of signal lines called the Unibus. The disk drive does not contain the hardware to communicate violthe Unibus, this circuitry is placed in the disk controller. The advantage of this configuration is that one controller can handle communications for more than one drive, decreasing the cost of expanding storage, capacity.

Input/Output (I/O) transfers in RT-11 are handled by the monitor through routines known as device handlers. A handler is used to transfer data between physical devices and memory, each device type having its own handler.

#### Chapter I

The Unibus is a set of signal lines that connects the processor, memory and peripheral devices. The Unibus has one single protocol which defines the procedures used for communication between any two devices connected on the bus. Data is transmitted on the bus either as 16 bit words or 3 bit bytes. Data is exchanged between a master and a slave. Only one master and one slave can exist at any one time.

A device may request use of the bus when it is ready for a data transfer. Several requests may be outstanding at a time. The arbitrator implements a scheme to determine which device will obtain use of the data section of the bus, when it becomes free. This device will become next bus master. The master then determines which device will become slave by placing the address of the slave device on the bus. The bus master releases comtrol of the bus at the end of the data transfer and another master may take control.

A device that is capable of being bus master requests use of the Unibus in order to:

1) do I/O directly with memory or another device i.e. disk to display terminal

2) interrupt the processor and force it to execute code at a specified, address where an interrupt service routine resides.

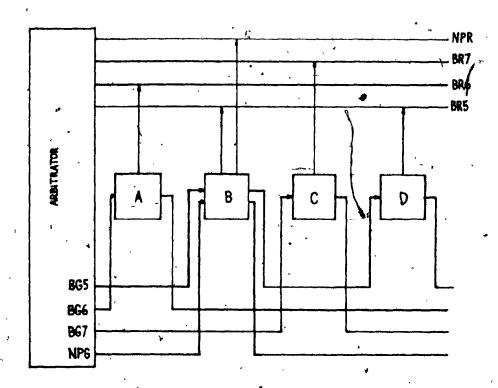

Figure 3.1 Bus configuration

- 1) Device priorities are determined by which signal line they are tied to.

- 2) Device will receive grant at same level as request was made i.e. BG5 for a BR5

- 3) Device B and device D are at the same priority. If they both have an outstanding nequest, device B will receive grant first.

- 4) A device may be connected to more than one signal line. A disk controller would be such a device. Data transfers occur with an NPR request, interrupts with the BRn request.

To use the Unibus a device must first obtain permission from the arbitrator and then carry out the required transfer. While one master is using the bus,

arbitration for next bus master may occur simultaneously on a different set of lines. Therefore, the Unibus can be broken down into two secrions; the arbitration section and the data transfer section.

Arbitration Section:

The bus arbitrator is a lugic circuit that compares priorities from devices requesting the use of the data section of the bus, in order to determine which device is to be granted control next. A Unibus must have only one arbitrator. The arbitrator monitors the priority level of the interrupt fielding processor and five hordware priprity levels to which other devices are connected. A signal line is dedicated to each of these levels and each signal line is driven by all devices assigned to the priority. Invel. The arbitrator issues a grant to the highest priority request active.

The case quest lines are labeled EF4,8R5,8R6,8R7,NPR from lowest to highest priority. The CPU priority (PRI) can vary from 0 to 7. The arbitrator algorithm is then:

- 1. Grant an NPG whenever an NPR is received.

- 2. if PRI < 7 and BR7 then assert EG7.

- if PRI < 6 and BR6 then assert BG6

- if PRI < 5 and ER5 then assert BG5

- 1 ₱ PRI < 4 and ER4 them assert BG4

Grant lines are transmission lines in which only the device electrically closest to the signal receive's the signal. This device either transmits or does not transmit the signal to the next device on the same line. The device will retransmit the signal only if it does not have an active request. In the case of two devices at the same priority level, both asserting a request, the one

electorically closer to the arbitrator will receive the grant first, and therefore is considered to have higher priority.

In table 1.1 is a list of signals used by arbitration sequences. A timing diagram for an arbitration transaction is shown in figure 1.2.

| Label                                    | lo of<br>lines | Name ,                             | Function                                                                                                                                          |

|------------------------------------------|----------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| RPR<br>NPG<br>BRN<br>BGN<br>SACK<br>BBSY | 1 4<br>4<br>4  | Non processor grant<br>Bus request | Request bus for data transfer Grant bus for data transfer Request bus (interrupt) Grant bus (interrupt) Acknowledge grant Bus data section in use |

Table 1.1

REQUEST **GRANT** SACK NEGATED ASSERTED

Figure 1.2 Ambitration sequence

- 1. Device asserts a request line (BRn or NPR)

2. Device receives grant from arbitrator.

3. In response to event 2, device asserts SACK.

4. In response to event 2, device negates request.

- 5. Arbitrator negate's grant in response to event 3.

- 6. Device becomes bus måster.

- 7. Device negates SACK. This can occur anytime between events 6 and 8. Arbitration for next master begins at this point.

- 8. Device releases the bus.

Data Transfér Section

A data transfer begins when a device asserts BBSY, signalling to all other devices that it is mester. The master then puts the address of the slave, the control bits, and the data when applicable, on their respective Unibus lines. The control bits indicate the direction of the transfer. This direction is always defined in relation to the master for the transaction, i.e. DATI (data in) means the master is requesting data from the slave. The master then asserts its syncronization line.

The slave decodes the address and control lines and accepts or places duta on the data lines. The slave then asserts its "syncronization line. The master would now accept the data if applicable, and negate ats syncronization line. The transaction is now complete. If the master has more than one transfer to execute, it would wait for the slave to negate its syncronization line and start its next transfer by placing a new address on the Unibus. When the master is finished it negates DBSY.

The master must always negate its syncronization signal prior to removing the address and control signals. This is done to assure that a spurious selection is not made while the address lines are changing.

In the case of an interrupt transaction, the master places the interrupt vector on the D lines and then asserts

INTR. The processor strobes the D lines and asserts its syncronization signal. The master responds by negating INTR, followed by negation of BBSY.

The master must assert INTR prior to negating SACK to ensure that the arbitrator does not become active during this interrupt transaction. The arbitrator should not accept furthur interrupts until the processor has established its new priority level.

A description of the signals in this section is provided in table 1.2. The figure's 1.5 to 1.5 show timing diagrams for an interrupt transaction, DATI and DATO respectively.

| Label                   | no of<br>lines |                                                  | Function                                                                    |

|-------------------------|----------------|--------------------------------------------------|-----------------------------------------------------------------------------|

| MSYN<br>SSYN            | 1 1            | Master syncronization Slave syncronization       | Master timing Slave timing Interrupt request                                |

| INTR<br>D<br>A<br>CO.C1 | 16 18          | Interrupt Data lines Address lines Control lines | Interrupt request Information transfer Select slave device Type of transfer |

Tab/1e 1.2

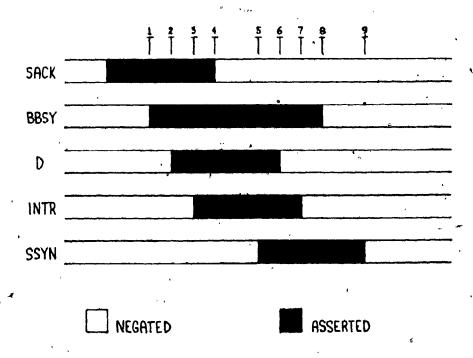

Figure 1.3 Interrupt timing diagram

- 1. Device becomes bus master.

- 2. Interrupt vector is placed on D lines.

- L. Master asserts INTR.

- 4. Master negates SACK.

- 5. Processor strobes D lines and asserts SSYN.

- Master removes interrupt vector.

Master negates INTR.

Master negates BBSY.

- Y. Processor negates SSYN.

| <b>、</b> ノ | }.' | †      | <b>2</b> | 3 | 5 |          | ! |

|------------|-----|--------|----------|---|---|----------|---|

| BBSY .     |     |        |          |   |   |          |   |

| A,C        |     |        |          |   |   |          |   |

| MSYN       | ' / | Ļ      |          |   |   |          |   |

| SSYN       |     |        | ,        |   |   |          |   |

| D.         | 1   |        |          |   |   |          |   |

|            |     | NEGATI |          | • |   | ASSERTED |   |

- 1. Master loads A and C lines.

- 2. Master asserts MSYN.

3. Stave places data on D lines.

4. Slave asserts SSYN.

- 5. On receipt of SSYN master negates MSYN.

- 6. Master removes A and C. Lines.

- 7. Master negates BBSY.

- E. Slave removes data from Ditines.

- 9. Slave negates SSYN:

| , ~    | ₹,  | †                                      | Ť.       | 3 | • 5<br> | † †      |  |

|--------|-----|----------------------------------------|----------|---|---------|----------|--|

| BBSY   | · . |                                        |          |   |         |          |  |

| A,C    |     |                                        |          | • |         |          |  |

| 0      |     |                                        |          |   |         |          |  |

| MSYN _ |     |                                        |          |   |         |          |  |

| SSYN   |     | ······································ |          | * |         |          |  |

| ,      |     | NEGA                                   | D<br>TED |   |         | ASSERTED |  |

Figure 1.5 DATO timing diagram

- 1. Master toads A, C and D lines.

2. Master asserts MSYN.

3. Stave after strobing data lines asserts SSYN.

4. Master removes data lines and negates MSYN.

5. Stave negates SSYN.

6. Master removes A and C lines.

7. Master releases the bus.

## Chapter II

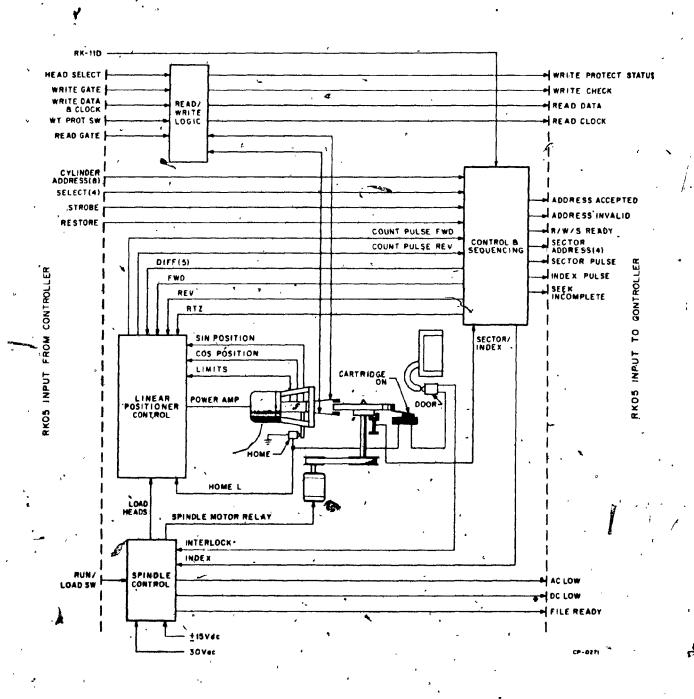

The RKU5 disk drive provides a safe operating environment to the disk and interfaces to the controller. A functional block diagram is provided in figure 2.1.

To start the drive, the disk contridge must be entered, the uoor closed and the RUN switch depressed. The drive will ensure that the cantridge is properly seated and the door is locked before activating the spindle. With the disk notating at proper speed, the heads are loaded. The speed of rotation is important to ensure that the heads will fly at the proper distance from the disk surface.

The drive contains logic to prevent addressing of cylinders beyond cylinder 202(10). This is done to prevent damage that could be caused when exceeding the limits of the linear positioner, the device which controls head motion.

Five signal lines are for drive addressing (figure 2.2). RK11D-L determines the addressing mode. A logical "O" on this line means that SEL DR 0-3 lines are to be decoded as a linear set (4-drive max). A logical "1" means decode as a binary set (8 drive max). The controller places

the cylinder address on lines BUS CYL ADD 6-7 and then places a logical "1" on the STROPE line to gate the discontinuite decoder circuit. With the correct sector under the read/write heads, the controller enables a read or write function by selectively enabling HEAD SELECT, WT GATE, RD GATE or WT DATA + CLK. The WT PROT line has the same effect as the WT PROT switch on the drive. The RESTORE line is activated by the controller when it is executing a Drive Reset function. The drive does an internal reset and the read/write heads are positioned above cylinder C.

FILE READY is set tomological "1" whenever the crive is in a ready state i.e. no error conditions and the spindle is at the correct speed. PUS R/W/S RDY indicates that FILE READY exists and the read/write heads are stationary. ADDRESS ACCEPTED / ADDRESS INVALID inform the controller the drive has accepted the address from lines BUS ADD O-? or has rejected the operation due to an involid address. If the drive does not complete a seek within 280 ns the drive asserts SEEK INCOMPLETE. WT PROT STATUS set indicates to the controller that the drive is write protected. WRITE CHK indicates an error condition and the drive FAULT indicator is lit.

During a read operation, the selected read/write head detects flux reversals from a recorded data track on the disk surface. The read waveform is amplified, filtered to remove high frequency noise components, and applied to wave

shaping circuits. The resulting waveform is passed through and ata separator circuit which produces RD DATA and RD CLK.

The line's SEC CNTR C-3, contain the address of the current sector under the read/write heads. The dirve also asserts two lines, SEC PES and INDX PLS, indicating a change of sector and next sector is sector 0, respectively. The drive derives these pulses from the sector transaucer, an optical device which detects slots in the disk hub.

Figure 2.1 RK05 functional block diagram

|                           | ¬                       | <del></del> |

|---------------------------|-------------------------|-------------|

|                           | BUS RKIID-L             | A- 07 U1    |

| }                         | BUS SEL DR Ø/A/E L      | A 07 J2     |

|                           | BUS SEL DR 1/B/F, L     | A 07 K2     |

|                           | BUS SEL DR 2/C/H L      | A 07 L2     |

|                           | BUS SEL OR 3/D/J L      | A 07 M2     |

| E                         | BUS CYL ADD Ø L         | A 07 KI     |

| 7                         | BUS CYL ADD 1 L         | - A 07 DI   |

| CONTROLLER                | BUS CYL ADD 2 L         | A 07 L1     |

| , 8                       | BUS CYL ADD 3 L         | A 07 C1     |

| r Prow                    | BUS CYL ADD 4 L         | A 07 F1     |

| · . . . . .               | BUS CYL ADD 5 L         | A 07 JT     |

| 5                         | BUS CYL ADD 6 L         | A 07 E1     |

| RKOS INPUT                | BUS CYL ADD 7 L         | 'A 07 H4    |

| 8                         | BUS STROBE L .          | B 07 H1     |

| ž                         | BUS HEAD SELECT L       | 8 07 M2     |

| 1 1                       | BUS WT PROTECT L        | 8 07 R2     |

| ,                         | BUS WT DATA & CLK L     | A 07 F2     |

|                           | BUS WT GATE L           | B 07 L2     |

|                           | BUS RESTORE L           | A 07 M1     |

|                           | BUS RD GATE L           | - B O7 R1   |

| CONTROLLER                | BUS FILE READY L        | B 08 N1     |

| . [                       | BUS R/W/S ROY L         | A .08 H2    |

|                           | BUS ADDRESS ACCEPTED L  | A 08 HZ     |

| 34                        | BUS ADDRESS INVALID L   | A 09 T2     |

| `                         | BUS SEEK INCOMPLETE L   | A 08 52     |

| 9                         | BUS WT PROT STATUS L    | 8 06 PI     |

| <u>8</u>                  | BUS WT CHK L            | 9 08 Kf     |

| 8                         | BUS RD DATA L           | 8 08 52     |

| Ö                         | BUS RD CLK L            | 8 O6 S1     |

| [ [                       | BUS SEC CNTR & L        | 8 08 L1     |

| RECS OUTPUT TO CONTROLLER | BUS SEC CHTR 1 L        | A 08 P2     |

| 5                         | BUS GEC CNTR 2 L        | 8 08 KZ     |

| 98                        | BUS SEC CNTR 3 L        | B 08 J1     |

| ž                         | BUS SEC PLS L           | B 08 N2     |

|                           | BUS INDX PLS L          | B 08 M1     |

|                           | BUS AC LO L             | 8 08 F1     |

|                           | BUS DC LO L             | 8 08 F2     |

| ľ                         | BUS RKOS/HIGH DENSITY L | B 08 P2     |

|                           |                         |             |

|                           | = ,                     |             |

CP - 0641

RKOS DISK DRIVE

Figure 2.2 RK11 controller/RKO5 drive interface

#### Chapter III

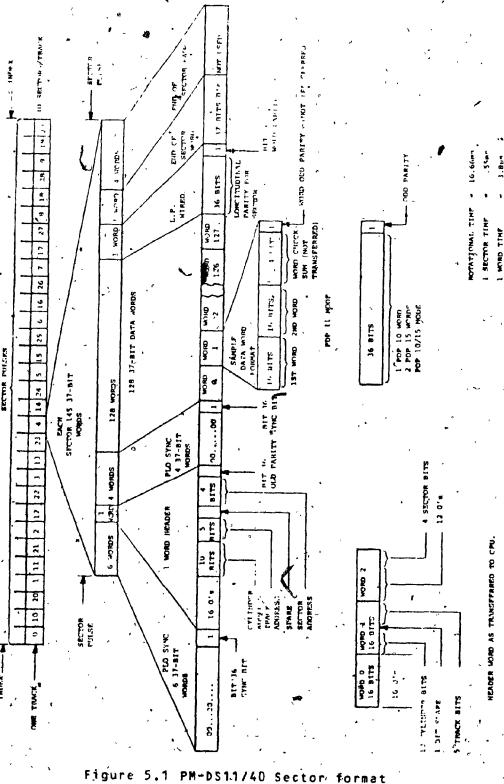

The RK11 disk controller is the interface between the RK65 disk drive and the rest of the computer. The RK11 contains seven 16 bit programmable registers, addressable from the Unibus. It is capable of 8 functions. The sector format output by the RK11 is shown in figure 3.1.

| PREAMBLE                           | HEADER                          | DATA                                                              | CHECKSUM                       | POSTAMBLE               |

|------------------------------------|---------------------------------|-------------------------------------------------------------------|--------------------------------|-------------------------|

| 15 <sub>8</sub> Words<br>of Zeroes | Cylinder<br>Address<br>(1 Word) | 256 <sub>10</sub> (400 <sub>8</sub> ) Words<br>(16-Bit or 18-Bit) | Sector<br>Checksum<br>(1 Word) | · 1 Word<br>· of Zeroes |

Figure 5.1 Sector format

The RK11 functions are :

CONTROL RESET

Resets all RK11 registers (internal and programmable).

SEEK

The RK11 directs the drive to move its head mechanism to a specified cylinder.

DRIVE RESET

The controller octivates the RESTORE line on the DR bus, causing the drive to reset.

WRITE LOCK

The RK11 asserts the WT PROTECT line on the DR bus. The drive will assert WT PROT STATUS from then on. This can be switched off by operating the WT PROT switch on the drive.

The next four functions all begin with the following: ~

a) a seek to the cylinder address

prontained in the RKDA register.

b) reading a header word to verify that;

the proper cylinder has been reached.

**LRITE**

Using the Judgess in the RKBA register the RK11 obtains data from memory by NPR transfers. The controller writes a full sector i.e. preamble thru postamble.

READ

Data is read from the disk and transferred to memory by NPR transfers. The chacksum is verified,

WRITE CHECK

The controller compares data from the drive with data obtained from memory by. NPR's. The checksum is verified...

READ CHECK

The checksum is calculated and compared with the checksum read from the disk, drive. No NPR transfers occur.

Diagrams of the RK11 registers are provided in the appendix.

Under normal read/write operations, a header word will be verified to determine that the correct cylinder has been reached. When the format bit (RKCS 16) is set, the header word check is inhibited. A program could set the format bit, write eros to every sector, and thus format the disk. It is feasible to format only one sector, but the data on that sector is lost.

The maximum seek time for the RKO5 is 80ms. A description of the seek function follows. The cylinder address is set in the controller RKDA register and passed on to the disk drive. The controller waits for either ADDRESS ACCEPTED or ADDRESS INVALID from the disk drive and interrupts the processor. The RK11 sets an internal

flip-flop (1 flip-flop per drive) to indicate that a seek was initiated on this drive. The drive is now still moving the read/write heads. The controller is now free to do another function. A seek to another drive could now be initiated. This feature is known as overlapped seek. Using overlapped seek is very advantageous, as seek time is a large percentage of total disk access time.

While the controller is idle it does's poll to see if any drive has completed a seek. If it finds one, it sets the SCP bid (RKCS 15) and initiates another interrupt to the processor. This second interrupt is only generated for a Seek or Drive Reset function, not for the implied' seek in the other functions.

Read and write operations begin with an automatic scek. If the beads are already above the proper cylinder, the R/W/S'RDY line on the DR but is immediately asserted by the drive. The controller continues executing the rest of the function.

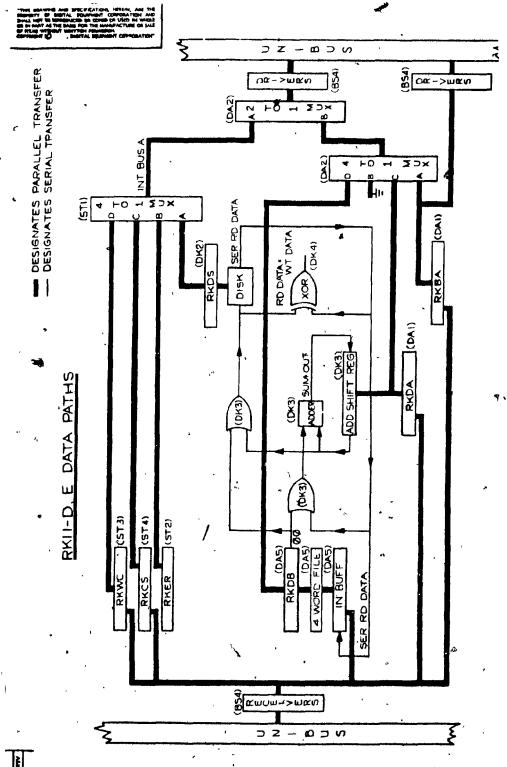

Figure 3.2 shows the data paths from the Unibus, through the RK11 controller to the disk drive. The data to be transferred to/from the drive passes through, a buffer called the 4 Word File. The buffering allows other devices to use the Unibus during a controller function. Otherwise the controller would hold the Unibus for a full 2.8 ms, the time to read or write a sector of data.

Figure 3.2 RK11 Data Paths

## Chapter IV

When using RT11, there is a routine which handles, loading the controller registers to initiate I/O, and contains code the processor executes when the RK11 issues an interrupt. This routine is called the RK11 disk handler.

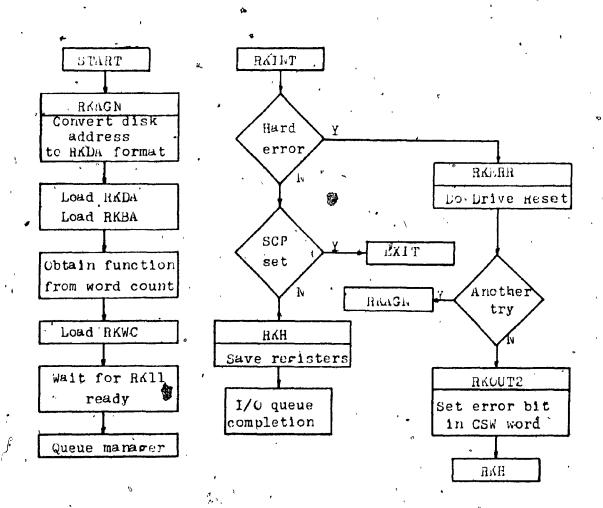

A flow diagram of the handler is provided in figure 4.1. Listings are available in the appendix.

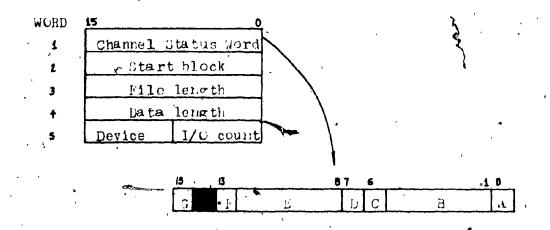

The I/O parameters are passed to the handler in the form of a table called an I/O queue element. The contents of this queue element are:

| Word | Contents                                                                                              |

|------|-------------------------------------------------------------------------------------------------------|

| 1 ,  | Pointer to next queue element.                                                                        |

| 2    | Pointer to CSW area.                                                                                  |

| Š    | Physical device address. (sector number)                                                              |

| 4    | Unit number of device to be used.                                                                     |

| 5 .  | Memory address to start transfer.                                                                     |

| 6    | Word count. A value $>0$ indicates a read, a value $=0$ 0 is a seek, and a value $\neq 0$ is a write. |

7

Completion function.

U = Wait for I/C transfer to complete.

1 = Return after quoting request. No action on completion.

N = Return after quoting request. On completion, transfer to completion routine, at address N.

All I/O requests are translated by RT11 into a queue element and an entry into the appropriate handler.

Taking data from this queue element, the handler loads the controller registers. Looking at the flow diagram, the first procedure converts the disk address to the format of the RKDA. The fact that there are only 12(10) sectors per track necessitates this conversion. By the sign of the word count value, the handler determines whether the operation is a read, seek, or write. When the ready bit (RKCS 7) is set, the handler initiates the new function. The handler then exits back to the queue manager.

After an interrupt from the RK11, the processor will begin executing code at label RKINT (figure 4.1). If no errors occured, the handler saves some registers and returns control to the I/O queue completion routine. If errors have occured, the handler issues a drive reset to the controller. After a number of retries, the handler sets the error bit in the CSW word and exits at to the I/O queue completion routine.

To set up the queue element for the handler a number of RT11 routines are involved. To better understand how this is done, an overview of RT11 will now be presented.

To do \$\( \) to a file on disk, the user must first associate the file with a channel number. This operation is known as a file "open". The user then sees the file as a collection of blocks, each block being one physical vector of data. Plock no. 1 is the first sector of the file. The user does input and output by specifying the block number to transfer on a specific channel. When the user is finished with the file, he must "close" it. This dissociates the channel from the file and causes RT11 to do some disk directory updating (when applicable). To describe the RT11 internals, we will start with the directory structure.

Figure 4.1 RK11 handler flow diagram

RT11 directory structure

RT11 looks for the start of the directory on any disk at sector no. 6. The complete directory can be made up of from 1 to 31 segments, each 512 words (2 sectors) long. Each directory segment contains 5 header words, the remaining 567 are for file entries. Each file entry is 7 words long; containing the filename, file length, and the date of file creation. The user may add some "extra words" to each file entry for additional information.

File entries are added to a segment until it is full. When adding the next file entry, half the entries are left in this segment and half are entered into the next segment. Thus, the maximum number of files that can be stored in an N segment directory are N\*507 / (2\*(7+n)) or 36 files per segment if there are no extra words (n=0).

The header words in a directory segment are as follows:

| Word<br>1 | Content Total number of segments in the directory.   |

|-----------|------------------------------------------------------|

| 2         | Pointer to next logical directory segment.           |

| • ·       | Highest segment currently in use (1st segment only). |

| 4         | Number of extra words per file entry.                |

| 5         | Block number where files in this segment begin.      |

The format of a file entry is:

| Word 1 Even | Content  Used for tentative files only. Pointer to the \$CSW element associated with this file.  Type of file i.c. tentative, empty permanent or end of segment marker. |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-4 🕏 -     | Filename in RAD5C.                                                                                                                                                      |

| 5           | File length.                                                                                                                                                            |

| 6           | Not currently used.                                                                                                                                                     |

| 7           | Date of creation.                                                                                                                                                       |

All files are contiguous, so the starting sector, and length of the file are sufficient to locate any block in the file. When a file is deleted an empty file entry is made to the directory.

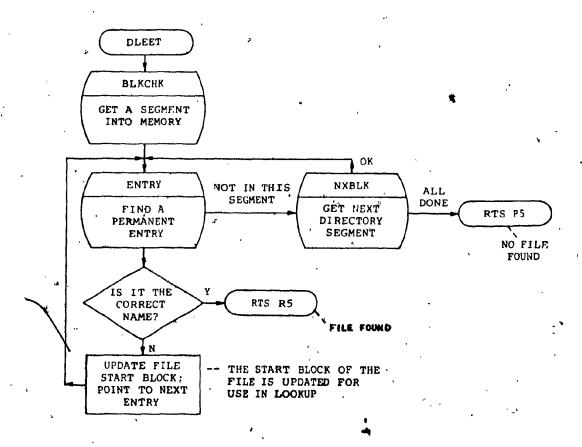

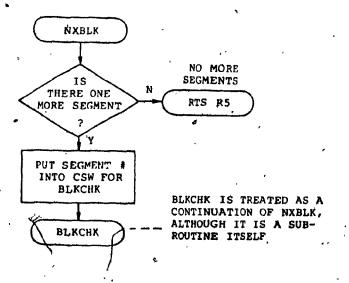

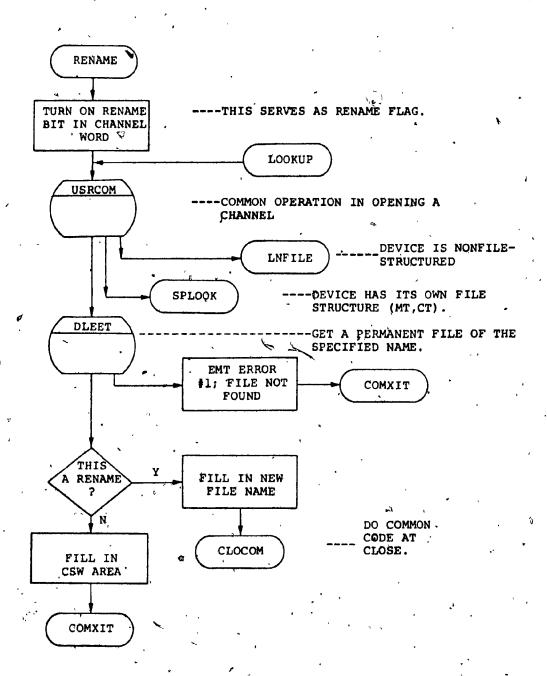

Figure 4.2 shows the RT11 routines involved in finding a filename in a directory. Start at label DLEET. The routine BLKCHK checks which directory segment is in memory, if not the first one, it will call SEGRW to read in the first segment. ENTRY, scans the file entries in the segment in memory one by one. If the filename entry is, found, a FILE FOUND exit is taken. If no match is found, an exit is made to routine NXBLK. NXBLK checks the next segment pointer, and if it is not, 0 (end of directory), it calls SEGRW to read in the next segment. If the end of directory is reached, a NO FILE FOUND exit is taken.

NXBLK - Gets the next in the series of directory segments, if one exists.

Figure 4.2 Scan device directory

### File-Channel Assignment

The objective of a file open is to update the SCSW (channel status word) table with pointers to the file.

Having the file location in memory will speed further I/O to the file. The format, of a table elemente is provided in figure 4.3. One, such entry is made for every channel opened by the user.

Figure 4.3 \$CSW table element

- A Hard error bit

- B Index to physical device table

- C When set, a Rename is in progress

- D When set, a Close requires a directory rewrite

- E Segment no. in which file entry was found

- F When set, an EOF was found on this channel

- G When set, a file is open on this channel

The user opens a file by means of a "programmed request". A programmed request is an assembler macro call

which is interpreted by the monitor during program execution. The are two programmed requests to open a 'file, one to create a new file (.EMTER) and one to access an existing file (.LGOKUP).

The format of the .ENTER request is :

.ENTER area, chan, dblk, length

is a pointer to work space required for the macro expansion.

chan is the channel number.

ablk is a pointer to the filename in RADSC.

length is a file size specification.

-1 means take the largest space available.

O moons take the larger of 1/2 the largesta space or the second largest

~ N means open a file of size M blocks.

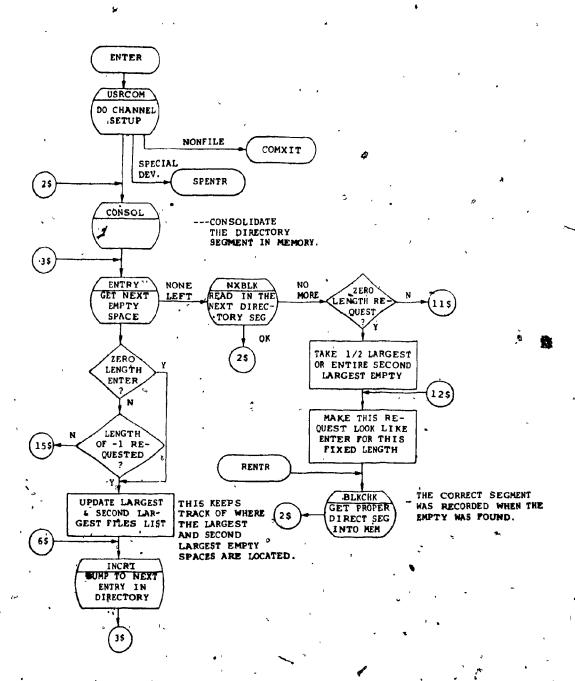

Figure 4.4 contains a flow diagram of the .ENTER programmed request. The first routine, USRCOM, assumes that the specified channel is not already in use and does validation on the device name. For a directory structured device, it calls routine BLKCHK to read the first segment into memory and exits to CONSOL. This routine consolidates consecutive empty entries into one larger empty entry (an empty entry is a file entry indicating the presences of unused blocks). ENTRY then scans this segment and examines each empty entry.

If a 0 or -1 file length specification was given, the whole directory is examined and a table with the two largest

empty entries is maintained. A tentative file entry is then made in the appropriate segment with a length as described above (.ENTER request format).

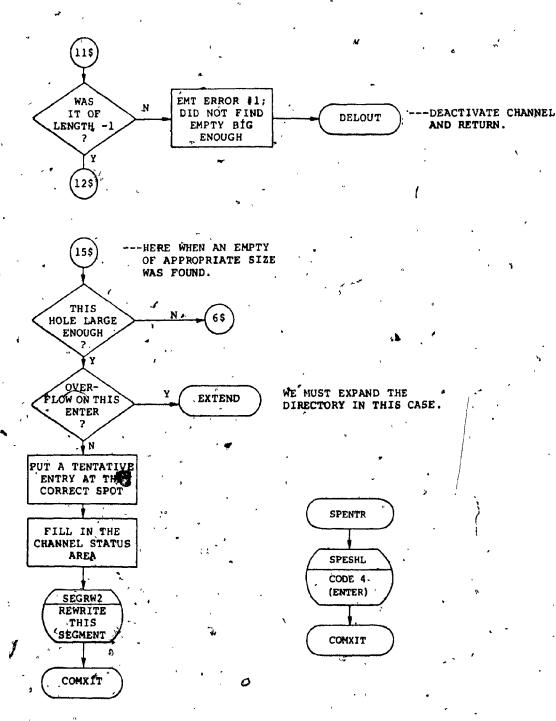

In the case of a fixed length ENTER, each tempty entry is checked-till one large enough to accommodate the file is found (label 15% in figure 4.4 part 2). Adding the tentative entry may cause a segment overflow. Figure 4.5 shows how the new segment is linked to the directory.

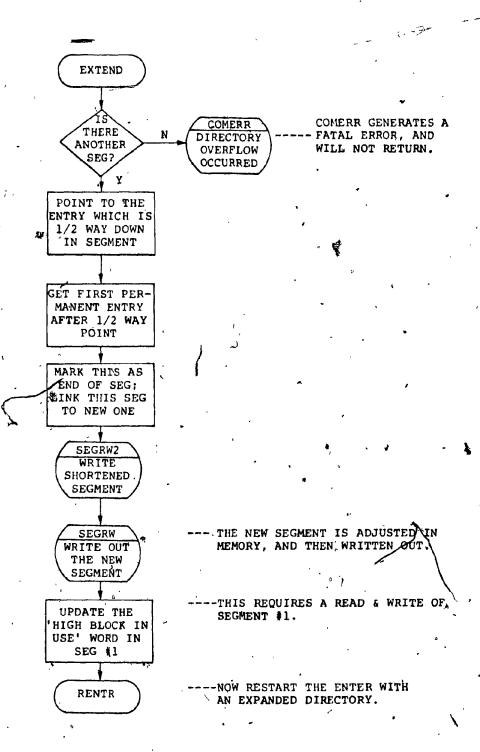

The format of the LOOKUP request is:

LOOKUP area, chan, dblk

arca · is a pointer to

required in the programmed request

expansion for argument passing.

chan is the channel number

dblk is a pointer to the filename in RAD50

request. Start at the label LOOKUP. The routine USRCCM checks that the channel specified is not already open and that the device in the filename specification is a valid device. USRCOM then updates the CSW word with the index to the physical device table and the channel active bit. The next routine executed is DLEET, the directory scan routine already described. If the FILE FOUND exit is taken, the CSW word is updated with the directory segment number the filename was found in. In addition the \$CSW element is updated with the starting block of the file, the file length

- 32 -

and the device unit number.

Figure 4.4 ENTER flow diagram P.1

Figure 4.4 ENTER flow diagram P.2

Figure 4.5 EXTEND flow diagram

Figure 4.6 LCOKUP flow diagram

File Input/Output

The programmed request format for input and output are:

READW area, chan, buff, wont, blkWRITW area, chan, buff, wont, blk

area is a pointer to a work area for macro rexpansion

chan is the channel number

buff is the starting address in memory from/to which data will be transfered

wont , is number of words to be transferred

blk is the block no. in the file at which the transfer will begin

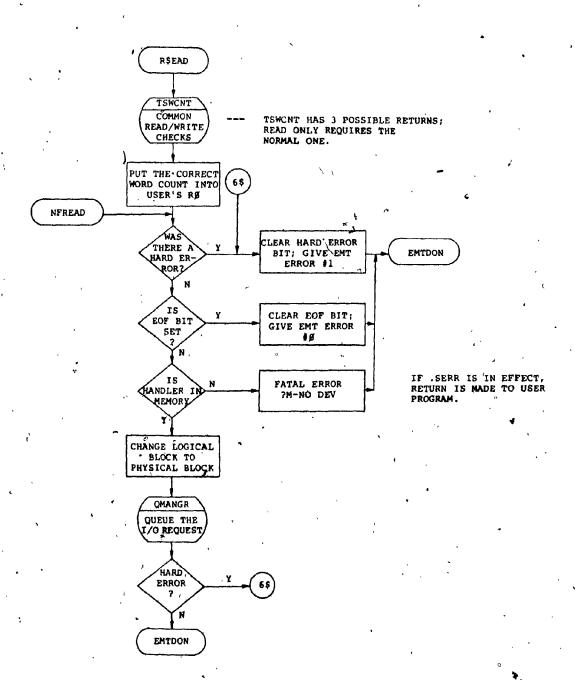

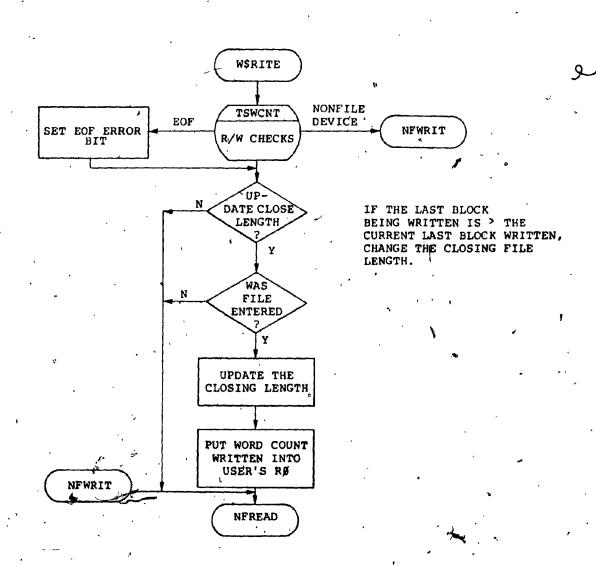

Flow diagrams of read and write requests are provided in figures 4.7 and 4.8. For both requests, the first routine entered is TSWCNT. This routine checks that the memory locations involved in the transfer are in the user's job space and if the data transfer will exceed the file's length. For the write request, if the file was opened by an ENTER request and the current write is to a higher block than any previous write, the data length word in the \$CSW element is updated. The rest of the code, from NFRPAD on, is common to both requests.

NFREAD does some error checking and verifies the handler is in memory. The user is responsible for loading the handler into memory unless the device being accessed is of the same type as the system device (the system device

`- 38 -L

handler is always in core). The fite's block number is then converted to a physical sector number.

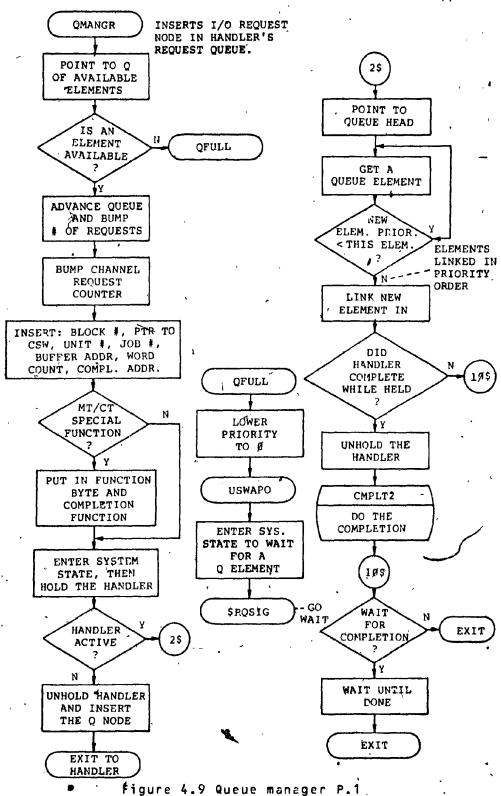

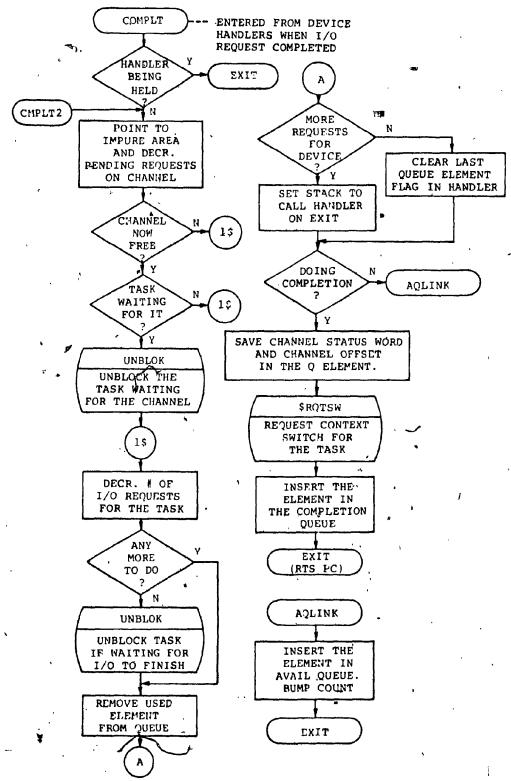

QNANGR' picks up the parameters of the transfer and builds a queue element. If the handler is available, it passes the queue element directly to the handler. Otherwise, its queue element is linked into the list of outstanding elements for this device. In any case, the handler eventually is given the queue element and initiates the transfer. When the transfer is finished the RK11 produces an interrupt, the handler stores some register values and exits to the I/O queue completion routine (label COMPLT in figure 4.9 part 2). This routine then removes the queue element for the completed transfer and returns control to the user program.

· Figure 4.7 READ flow diagram

figure 4.8 WRITE flow diagram

J

THE TANK THE

Figure 4.9 Queue manager P.2

Close Channel

The .CLOSE request terminates activity on a specified channel. For a file opened by a LOOKUP request, the \$CSW element is cleared; no further processing is required as a permanent entry already exists for this file on the disk.

Each filename in a directory must be unique. Before closing the channel for a tentative entry, the entire directory must be scanned for a permanent entry by the same name. If one is found, the permanent entry is replaced by an empty entry. The tentative entry is then replaced by a permanent entry with a length equal to the highest block written to the file (comtained in the \$CSW element data\* length value).

### -Chapter V

Plessey PM-DS11/40

Plessey produces the PM-DS11/40, a high capacity (31.2Mbyte) storage device for the PDP computers. This includes a PM-DC11/40 controller and a PM-DD11/40 drive. The specifications of the controller to drive interface are not available.

The packs used in this drive have six oxide recording surfaces (3 platters). Five are used for data, the sixth contains permanently recorded positioning information (set by the manufacturer). One track contains 30(10) sectors. The sectors are not numbered consecutively i.e. there is an interleave to provide time for buffering on, a multiple sector access. There is very little wasted space on a track, the inter sector gap is only 4 - 37 bit words long. This passes beneath the heads in .015ms, hence the need for interleave.

The controller writes data to the disk as 37 bit words. This format is adopted in order to be compatible with other PDP series computers, namely the PDP-10 and PDP-15. The controller packs two PDP-11 words together and

adds a 4 bit checksum and a parity bit.

The header word of a sector contains the full disk address i.e. cylinder, track and sector. In format mode, with RKCS 11 and RKCS 12 set, the header word is sent to memory as three words (illustrated at the bottom of figure 5.1).

The appendix contains a detailed description of the controller registers. The PM-DC11/40 does not contain a data buffer register. Such a register is not required, as the user would never want to do a read or a write to the disk, word by word, under program control. The controller contains a 256(10) 16 bit word silo. During a write operation the silo must be filled before the data is transcribed to the disk. During a read, the silo must either be empty before the next sector is read, or the controller will begin emptying the silo at the maximum silo transfer rate while the next sector is being read.

There are two disk address registers, one for the cylinder address (10 bits) and one for the track (5 bits) and sector (4 bits) information. Since the disk is organized with 412(10) cylinders, 5 tracks/cylinder and 30(10) sectors/track, a hardware address conversion must be done.

. Plessey has another drive (PM-DS11/80) with 62.4Mbyte capacity. This is achrieved by halving the track width and

doubling the cylinder density. The same controller can be used.

Digital Equipment - RP11

The RP11 is a controller for an PPC2 disk drive with 20Mbyte capacity. Again, the controller to drive interface specification is not available.

The RPQ2 drive accepts packs with 20 data surfaces. Where the sector and index pulses are generated is not described. A 777 bit dask word format is used, the last bit being a parity bit.

The RP11 contains a 64(10) word silo of 16 bit words. During a write operation, data is shifted through the silo to a buffer register and written to the disk. For a read operation, the data enters the silo from the buffer register. When a new data word "bubbles" to the output, a Unibus NPR transfer is initiated. A data buffer register is provided in this controller, for maintenance purposes only.

This controller contains two disk address, registers.

The RPCA contains 9 bits of cylinder address, the RPDA has 5 bits of track address and 4 bits of sector address. The disk structure is: 200 cylinders, 20 tracks/cylinder and 10 sectors/track.

The RP1(1 also contains three maintenance registers RPM1-RPM3. These provide information, on the state of the disk drive and the controller to drive interface, in a special maintenance mode.

Digital Equipment Corporation also produces a dual density drive, the RPO3, which operates on this controller. (40 Mbyte capacity).

comparison of PM-DC11/40 to RP11

Plessey designed their controller to work on the Unibus and to have the same register layout as the RP11 controller. All the controller commands have the same codes and the error status bits are in the same locations. Therefore, the RP11 handler will work with a PM-DC11/40. Plessey provides patches to the handler, but these probably just change the register assignments (the register addresses are different).

The RP11 is a supported device under RT11 version 3 (it was not under version 2). Throughout RT11 a single 16 bit ord is alloted for the starting sector of a file, thereby limiting this value to 65,536. This is sufficient to handle the low density versions of both the RP11 and the PM-DC11 which contain 40,600 and 61,800 sectors respectively. A way to expand this value would be to take a bit from somewhere else. In the \$C\$W element a bit from the unit number word could be used. In the I/O queue clement likewise. The disk directory however would also have to be modified. The RT11 version 3 manuals do not describe how this is done.

## Discussion

To summarize the procedure for doing I/O under RT11: the user opens a file and is assigned a buffer for this channel. The user manipulates data in this buffer and gives commands to read/write into the buffer. RT11 translates the request into an I/O queue element and the queue manager transfers the element to the disk handler. The handler contains all the device specific code, i.e. knows the location and format of all the disk controller registers, and executes the data transfer.

To interface any drive to the machine the software requirement is to have a handler that the interface to RT11 and the disk controller. The hardware requirement is that the disk controller be compatible with Unibus protocol.

### Conclusion

Manufacturers seem to produce a controller for drives with different capacities, usually one drive geing double the capacity of the other. The controller can be identical, as everything about these drives is identical except the density of the tracks. As long as the controller has a spare bit in the cylinder address field, no problem arises. More sophisticated handlers even allow a contoller to handle a mixed population of these drives.

As the velocity of the drive increases and the density on the disk surface increases, the buffering demands increase. This can be seen with the RK05 (1500rpm/2000bpi) having a 4 word buffer; RP03 (2400rpm/2200bpi) having 64 word buffer and the PM-11DS/40 (3600rpm/6000bpi) with a 256 word buffer. The clock frequency is proportional to disk velocity and density. The frequency ratio for RK11, RP11, PM-11DS/40 is 1:1.6:7.

The RP11 is not supported (Digital Equipment does not supply a handler) by RT11-V2 which is described in this paper. This is understandable, as rthe \$CSW element and the 1/0 queue element as described allow only one 16bit word

(64K sectors) for a device block address. The RP03 contains 80,000(10) sectors. RT11-V3 does support the RP11 and hence changes to these tables have been made, perhaps just placing additional address bits in the unit number word of the \$CSW element and the unit number byte of the I/O queue element.

## Bibliography

- 1. PDP11 Bus handbook 1979.

- 2. PDP11 Peripherals handbook 1975.

- 3. RKO5 Disk drive manual

- 4. RT11 Software support manuals

DEC-11-ORPGA-A-D

DEC-11-ORPGA-B-D

- 5. RK11-D and RK11-E moving head disk drive controller manual DEC-11-HRKDA-B-D .

- 6. RT11 System reference manual DEC-11-ORUGA-C-D

- 7. Eckhouse, R.H.Jr. and Morris L.R.

Minicomputer Systems

Prentice-Hall 1979

```

RT-11 MACRO VM81-61

.TITLE RKO'S VUI-RI

JRT-11 DISK (HK11) HANDLEH

· JUEC-11-OHTKA-A-LA

JED FRIERMAN

JMAY, 1973

JCOPYHIGHT 1973 "

IDIGITAL EQUIPMENT CORPURATION

IMAYNARO, MASSACHUSETTS #1754

IUEC ASSUMES NO RESPONSIBILITY FOR THE

TUSE OR RELIABILITY OF ITS SOFTWARF ON

JEQUIPMENT WHICH IS NOT SUPPLIED BY OLC.

IMEGISTER DEFINITIONS

20

999999

#0 = 1 A

040001

P2= $2

53

906905

R3=13

000903

25

409006

PARXA

000005

K5= %5

56

27

000006

3F= 16

28

000001

PL#X7

99

30

IGLOBAL DEFINITIONS

31

GLOBL SYSTATISYSIZE, SHLUCK

35

.GLOHL

SY, SYINT, SYINPP

GLOBL RKSYS, DTSYS

33

34

35

MODRUD DISYS.

ITHES IS AK HANDLER

IRKUS STATUS WORD

100000 SYSTAT = 100000

36

37

811595 SHFOCK. 11595

ISIZE IN BLUCKS

JAK CONTROL DEFINITIONS:

38

177400 ---

117400

39

FKD5=

177492

40

RKENA

117402

177464

KKC5=

177484

177406

177486

FKKC .

177410

FKBA#

177416

177412

FEDAR

177412

45

00001P RKCNT=10

I# EPHON RETRYS

47

THE THAP ADURESS

. *OHD

48 WAGAG BAGZEG STAHT:

550

STOFFSET FROM INTERRUPT ADDRESS SINTERRUPTS SERVICE AT LEVEL &

88885 B88136

WORD

RKINT ..

. WORD

54 40004 40000

51 66666

RKSYSI

52 88686

3 Y 1

ILAST G ENTRY AUDHESS

ICURRENT W ENTRY ADURESS

. MORO

53 UAGUS BAUAUA RKLUE!

54 UBBIR HRORER RECUE!

. NORD

MOV

55 40912 012727

#HKCNT, (PC)+

ISET ENNOW HETRIFS

B100NB

MBW16 MOMBMO PKTHYI

```

### RK85 V41-81 RT-11 MACRO VH81+41 23-001-73 PAGE 1+

| 57       | 98950 | 016701 R           | KAGNI     | MOV           | RKCUE, R1         | IGET O PARAMETEN POINTEN            |

|----------|-------|--------------------|-----------|---------------|-------------------|-------------------------------------|

| 58       | 00024 | 012702             |           | MOV'          | #14,R2            | IDE MEDEN TO ME DISK ADDRESS        |

|          | -     | 612103             |           | MOV           | (H1)+,R3          | JRAN BLOCK NUMBER                   |

| -        |       | 000402<br>062702 1 |           | AR<br>AÙD     | *58'45<br>57      | · ·                                 |

| ~<br>• 2 | 00040 | 162793 2           | <b>51</b> | SUB           | #14,83            | •                                   |

| 63       | 00044 | 100373             |           | BPL           | 1 \$              | ·                                   |

|          |       | 015105 -           |           | ADG<br>Mov    | R2,H3<br>(H1)+,R2 | JH3 MAS DISK ADDRESS<br>JGET UNIT # |

| 66       | 49452 | 23588A             |           | SWAB          | R2                | JRK HAS IT IN MITS 15-13            |

| 66       |       | VVV V V V          |           | HOR           | Rea               | •                                   |

| 69<br>78 | 86064 | 858583             |           | , ENDR<br>815 | R2, H3            | SPUT IN UNIT #                      |

```

2 848866 012742

MOV

#KKD1, R2

INON LOAD OSK

177412

MOV

3 000472 414312

RS, (R2)

IDISK AUD, AND UNIT SELECT

INUFFER ADDRESS

4 480074 012142

MOV

(H1)+,- (R2)

5 848476 412743

MOV

#183,H3

IFUNCTION, GUESS AT BEING A WHIT

20103

6 666105 011145

MOV

· (H1), *(H2)

INORD COUNT

7 800 104 001412

BEG

IN WORDS IS A SEEK

4 5

IMH

8 808 186 1864 483

33

9 000110 005412

(H2)

SHEAD. MAKE WURD COUNT NEG.

NEG

ADD

FALTER PUNCTION

TH MB112 062703

#2,H3

200000

STEST ALCERS HEADY

11 40116 032737 351

BIT

#188,F#RKDS

0001 UP

177460

12 00124 001774

ALG

<sup>2</sup>3 &

13 00126 010342

MOV

(SH)-, LA

ISTAPT TRANSFER

KTS

PC

14 88139 888287

15 40132 962743 431

ADD

#6,H3

IMAKE IT A SEEK

99389A

BR

16 400136 896767

33

17

SYINT:

18 00140

000240 SYINPHOCAU

#120000. P#RKCS

STEST FOR FRE AND SEEK LMPLT

20 00140 032737 RKINT: BIT

120000

177464

RKEHR

BMI

FERROR

21 00146 100013

ISFER, COMPLETE, IGNORE INTERRUPT

22 00150 '001035

23 00152 005837 HKH:

BNE

PKOUT

BULL NOW

CLR

177776

24 40156 444317

J5₽

R3, (PL)

INS ON STACK AND GET CURRENT PC

JOURNENT O TO RE

25 44164 462743

ADD

# MKCOL-. , #3

177650

MOV

ISAVE RU

RU, - (5P)

26 40164 416946

MOV

INON GO INTO MESTUENT A CUMPLETE

27 00166 U1370P

4848341

OFF SET=270

INORD IS 256 BYTES PAST RHMUN

994570

85

FINTO PESIDENT.

29 40172 416047

MOV

OF FSET(HØ),PC

888278

FSAVE R1

R1,=(SP)

31 80176 810146 RKEHRE

MOV

#15, PARKCS

JUD DRIVE RESET

FUV

32 JA200.012737

000015

17/464

33 00206 105737 111

TSTE

PPRKCS

177404

BPL

SWAIT FOR PEADY

34 00212 100375

13

35 40214 495037

CLR

177776

JUONF THYING?

HKTHY .

36 40220 005367

DEC

17757-2 .

37 48224 19419

BMI

" RKOUTZ

IND. SAVE REGISTERS AND GO AGAIN

MOV

F2, -(SP)

38 40226 010246

MOV

H5,+(SP)

39 49234 914346

JSH

7 , RKAGN

AJ W#232 084767

```

RT-11 MACRO VMB1-U1 177562 41 80530 015603 HOV (SP).+, H5 (SP)+, H2 42 00240 012602 HOV 18921N 28248 CB HUV STÚCNA SUBBNO BEZOB BE RTI VON PETUDAN INTOIN SPENU CP 177536 46 84252 452751 818 #1,#=(Ri) ITUHN ON HARD ERRUR 100000 47 80256 812681 MUV (SP)+,R1 BH RKH ISTART NEXT TRANSFER 49 WHUZEZ SYSIZE = . - STANT 54 WBW991" , END

RKP5 V01-01 RT-11 MACHO VM81-81 23-001-73 PAGE 2+ SYMBOL TABLE 01545 - 800080 G OFFSET= AUALTE P C BARRAVAT RKAGN RUSUSUR MKMA = 177410 HECNT . BUPULO FKCS RKCUE 900010A . 177484 PKDA = 117412 RKO'S . 177466 RKEH # 177492 RKEHP 444176R RKH RKINT 989152R BUBLOUR HALLE PURMPER RKOUT 848244R PROUTE BUBZAGR RKSYS DROUBHOND HKHC = 177476 Hø RKTHY 808016R \* zauayay Ri # X N U O U O 1 B 2 \* 1 0 0 0 0 0 0 C #3 LUNGHURS R4 \*\*\*\*\*\*\*\*\*\*\* P5 \*\*\*\*\*\*\*\* SHLUCK# M11262 6 30 = 14000000 START RUBUBUB BUPERBRE 3 Y SYINPR . ...... SYINT PUR146P6 SYSIZE ANASES 6 , SYSTAT = 100000 G KAUS. 400084 600 MANSOS 601 EHRORS DETECTEDE & FREE CORE: 6941. MONDS

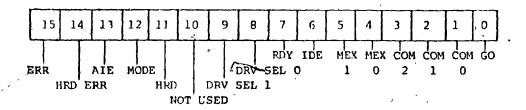

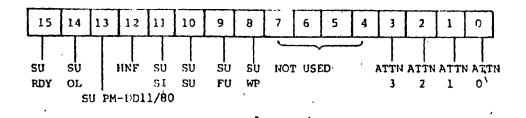

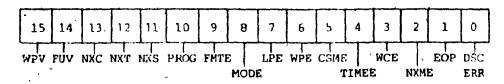

### DRIVE STATUS REGISTER (RKDS) Address = 777400

NOTE

This register is a read-only register, and contains the selected drive status and current sector address.

| DRIVE IDENT | DPL | RK05 | DRU | SIN | SOK | DRY | R/W/S<br>RDY | i 1 |   |   |   | , | UNTER |   |

|-------------|-----|------|-----|-----|-----|-----|--------------|-----|---|---|---|---|-------|---|

| .15 14 13   | ,12 | 11   | 10  | , 9 | 8   | 7   | 6            | 5   | 4 | 3 | 2 | 1 | 4 O · | • |

| Bit   | Designation                                    | Description and Operation                                                                                                                                         |

|-------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00⊶03 | Sector Counter (SC)                            | These 4 bits are the current sector address of the selected drive. Sector address 00 is defined as the sector following the sector that contains the index pulse. |

| 04    | Sector Counter Equals Sector Address (SC = &A) | Indicates that the disk heads are positioned over the disk address currently held in the sector address.                                                          |

| 05    | Write Protect Status (WPS)                     | Sets when the selected disk is in the write protected mode.                                                                                                       |

| 06    | Read/Write/Seek , Ready (R/W/S RDY) | Indicates that the selected drive head mechanism is not in motion, and that the drive is ready to accept a new function.                                                                                                                                                                                                                                                      |

|-------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07    | Drive Ready (DRY)*                  | Indicates that the selected disk drive complies with the following conditions:                                                                                                                                                                                                                                                                                                |

| à     |                                     | a. The drive is properly supplied with power.                                                                                                                                                                                                                                                                                                                                 |

|       |                                     | b. The drive is loaded with a disk cartridge.                                                                                                                                                                                                                                                                                                                                 |

| , ,   | , ,                                 | c. The disk drive door is closed.                                                                                                                                                                                                                                                                                                                                             |

|       |                                     | d. The LOAD/RUN switch is set to RUN.                                                                                                                                                                                                                                                                                                                                         |

|       | ₹.                                  | e. The disk is rotating at a proper speed.                                                                                                                                                                                                                                                                                                                                    |

| •     |                                     | f. The heads are properly loaded.                                                                                                                                                                                                                                                                                                                                             |

| •     |                                     | g. The disk is not in a DRU (bit 10 of RKDS) condition.                                                                                                                                                                                                                                                                                                                       |

| 08    | Sector Counter OK<br>(SOK)          | Indicates that the Sector Counter operating on the selected drive is not in the process of changing, and is ready for examination. If this bit is not set, the Sector Counter is not ready for examination, and a second attempt should be made.                                                                                                                              |

| 09    | Seek Incomplete<br>(SIN)            | Indicates that due to some unusual condition a Seek function cannot be completed. Can be accompanied by RKER 15 (Drive Ersor). Cleared by a Drive Reset function.                                                                                                                                                                                                             |

| 10    | Drive Unsafe<br>(DRU)               | Indicates that an unusual condition has occurred in the disk drive, and it is unable to properly perform any operations. Reset by setting the RUN/LOAD switch to LOAD. If, when the switch is returned to RUN, the condition recurs, an inoperative drive can be assumed, and corrective maintenance procedures should be begun. Can be accompanied by RKER 15 (Drive Error). |

| į1    | RK05 Disk on Line<br>(RK05)         | Always set, to identify the selected disk drive as RK05.                                                                                                                                                                                                                                                                                                                      |

| 12    | Drive Power Low<br>(DPL)            | Sets when an attempt is made to initiate a new function, or if a function is actively in process when the control senses a loss of power to one of the disk drives. Can be accompanied by RKER 15 (Drive Error). Reset by a BUS INIT or a Control Reset function,                                                                                                             |

| 13-15 | Identification of Drive (ID)        | If an interrupt occurs, these bits will contain the binary representation of the logical drive number that caused the interrupt.                                                                                                                                                                                                                                              |

\ Description and Operation

ERROR REGISTER (RKER) Address = 777402

Bit

Designation

## NOTE -This is a read-only register.

|   |     |     |     |     |       |      | <b></b> |    |     |     |     |   |      |      |     |     |   |

|---|-----|-----|-----|-----|-------|------|---------|----|-----|-----|-----|---|------|------|-----|-----|---|

| , | DRE | OVR | WLO | SKE | PGE 1 | W.M  | DLT     | TE | NXD | NXC | NXS | υ | NUSI | ED . | CSĘ | WCE | ľ |

|   |     |     |     |     |       | 10 . |         |    |     |     |     | 4 | 3    | 2    | 1   | 0   | , |

**Description and Operation**

| , n         | Write Check Error (WCE)     | Indicates that an error was encountered during a Write Check function as a result of a faulty bit comparison between disk data                                                                                                                 |

|-------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ٠ .         |                             | and memory data. Clears upon the initiation of a new function.  This is a soft error condition.                                                                                                                                                |

| 01.         | Checksum Error<br>(CSE)     | Sets while performing a Read Check of a Read function as a result of a faulty recalculation of the checksum. Cleared upon the initiation of any new function. This is a soft error condition.                                                  |

| 02-04       | Unused.                     |                                                                                                                                                                                                                                                |

| The rema    |                             | are all hard errors, and are cleared only by a BUS INIT or a Control                                                                                                                                                                           |

| 05          | Nonexistent<br>Sector (NXS) | Indicates that an attempt was made to initiate a transfer to a sector larger than 138.                                                                                                                                                         |

| <b>.</b> 06 | Nonexistent Cylinder (NXC)  | Indicates that an attempt was made to initiate a transfer to a cylinder larger than 312s.                                                                                                                                                      |

| 07          | Nonexistent Disk (NXD)      | Indicates that an attempt was made to initiate a function on a nonexistent drive.                                                                                                                                                              |

| . 08        | Timing Error<br>(TE)        | Indicates that a loss of timing pulses for at least 5 $\mu$ s has been detected.                                                                                                                                                               |