**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the

text directly from the original or copy submitted. Thus, some thesis and

dissertation copies are in typewriter face, while others may be from any type of

computer printer.

The quality of this reproduction is dependent upon the quality of the copy

submitted. Broken or indistinct print, colored or poor quality illustrations and

photographs, print bleedthrough, substandard margins, and improper alignment

can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and

there are missing pages, these will be noted. Also, if unauthorized copyright

material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning

the original, beginning at the upper left-hand corner and continuing from left to

right in equal sections with small overlaps. Each original is also photographed in

one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white photographic

prints are available for any photographs or illustrations appearing in this copy for

an additional charge. Contact UMI directly to order.

UMľ

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# A HIGHLY EFFICIENT LOW OUTPUT VOLTAGE DC TO DC CONVERTER

### Edoardo O. L. Gotti

A Thesis

in

The Department

of

Electrical And Computer Engineering

Presented in Partial Fulfillment of the Requirements

for the degree of Master of Applied Science at

Concordia University

Montreal, Quebec, Canada

February, 1998

© Edoardo Gotti, 1998

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-39475-1

Canadä

### **ABSTRACT**

### A Highly Efficient Low Output Voltage DC to DC Converter

### Edoardo O. L. Gotti

The purpose of this work is to develop a 100 V to 3.3 V, 50 W DC to DC converter which achieves the best compromise between low mass and high efficiency. A particular emphasis is put on using components qualified for the aerospace environment. The work was carried out through the following steps:

- Explore all possible topologies which lend themselves to efficiently convert a raw 100 V input bus to a tightly regulated 3.3 V output, galvanically isolated from the input.

- 2. Among all these topologies, select the one which leads to the highest efficiency and the lowest mass.

- 3. Optimize the chosen topology.

- 4. Develop a small signal moded of the selected topology.

In order to validate the calculations and the mathematical models developed, a prototype of a 100 V to 3.3 V, 50 W converter was built with Space qualified components and tested. With this prototype, conversion efficiencies in excess of 87 % (including control circuit consumption) were measured.

### **Acknowledgements**

The author would like to express his gratitude to his thesis supervisor, Professor Geza Joós, for his advice and support, especially in obtaining the National Science and Research Council (NSERC) scholarship.

The author is also very thankful to Ms. Patricia Verret, Graduate Awards Coordinator at Concordia University who helped him through the various steps involved in obtaining the NSERC scholarship.

The author is very much grateful towards his family whose constant, sometimes humorous support made it possible to carry out this project to the end.

The work performed in this thesis was jointly funded by NSERC and SPAR Aerospace Ltd, and this financial support is gratefully acknowledged. In particular, the author would like to thank Mr. Peter Shield, Director of Marketing, and Mr. Harold Knowles, Manager, Power, Digital and Software Department for granting their support in funding this project.

The experimental part of this thesis was carried out in the Power Laboratory of SPAR Aerospace Ltd., Ste-Anne-de-Bellevue, Québec. The author wishes to thank SPAR Aerospace and in particular Mr. Harold Knowles for making available laboratory facilities, test equipment, components, Printed Circuit Board layout facilities and the support of a technologist, all of which greatly contributed to the realization of this work.

The author is also thankful to his colleagues at SPAR, Daniel Vallée and Ian Edward for their advices and constructive criticism throughout this work.

Finally, last but not least, the author wishes to express his deepest gratitude to Mr. Peter Drago, Senior Technologist, SPAR Aerospace Ltd., who built the prototype and whose great skill, experience and educated suggestions were instrumental in the success of this project.

## **Table of Contents**

| ABS  | TRACT                                                  | III      |

|------|--------------------------------------------------------|----------|

| ACK  | KNOWLEDGEMENTS                                         | ıv       |

| TAB  | BLE OF CONTENTS                                        | vı       |

| LIST | T OF TABLES                                            | viii     |

| LIST | r of figures                                           | IX       |

| LIST | T OF SYMBOLS AND ABBREVIATIONS                         | xı       |

| LIST | T OF APPENDICES                                        | xıv      |

| СНА  | APTER 1 INTRODUCTION                                   | 1        |

| 1.1  | GENERAL INTRODUCTION                                   |          |

| 1.2  | PROBLEM STATEMENT                                      |          |

| 1.3  | LITERATURE REVIEW                                      |          |

| 1.4  | SCOPE AND CONTRIBUTIONS OF THIS THESIS                 | 6        |

| 1.5  | THESIS OUTLINE                                         |          |

| СНА  | APTER 2 A COMPARATIVE STUDY OF SEVERAL TOPOLOGIES      | 9        |

| 2.1  | INTRODUCTION                                           | 9        |

| 2.2  | CHOICE OF A TOPOLOGY                                   | 10       |

| 2.3  | COMPARISON CRITERIA                                    | 19       |

| 2.4  | THE ACTIVE CLAMP SINGLE ENDED FORWARD CONVERTER        | 21       |

| 2.5  | THE COMPLEMENTARY HALF BRIDGE CONVERTER                |          |

| 2.6  | THE ZVT FLYBACK CONVERTER                              |          |

| 2.7  | COMPARISON SUMMARY                                     | 71       |

| СНА  | APTER 3 DESIGN OF A ZVT COMPLEMENTARY HALF BRIDGE CONV | ERTER.73 |

| 3.1  | INTRODUCTION                                           |          |

| 3.2  | POWER CIRCUIT DESCRIPTION                              |          |

| 3.3  | OUTPUT FILTER DESIGN                                   |          |

| 3.4  | TRANSFORMER DESIGN                                     |          |

| 3.3   | GATE DRIVE CIRCUIT                        | ······································ |

|-------|-------------------------------------------|----------------------------------------|

| 3.6   | CONVERTER TEST RESULTS AND WAVEFORMS      | 92                                     |

| 3.7   | CONVERTER EFFICIENCY                      | 96                                     |

| 3.8   | CONVERTER SIZE OPTIMIZATION               | 104                                    |

| 3.9   | CONCLUSIONS                               | 107                                    |

| CHA   | PTER 4 CHBC DYNAMIC MODELLING             | 108                                    |

| 4.1   | INTRODUCTION                              | 108                                    |

| 4.2   | THE BASIC AVERAGED DYNAMIC MODEL          | 109                                    |

| 4.3   | THE SMALL SIGNAL MODEL                    |                                        |

| 4.4   | DERIVATION OF THE MAIN TRANSFER FUNCTIONS | 120                                    |

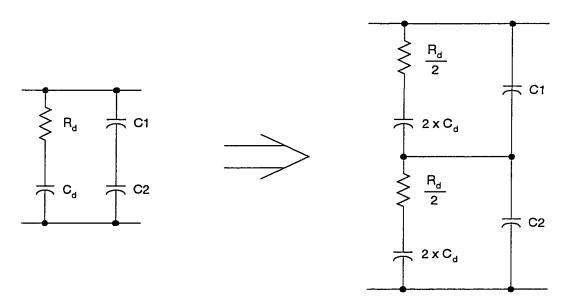

| 4.4.1 | INPUT FILTER DESIGN                       | 121                                    |

| 4.4.2 | MAIN TRANSFER FUNCTIONS                   | 127                                    |

| 4.5   | COMPENSATION LOOP DESIGN                  | 131                                    |

| 4.6   | CONCLUSIONS                               | 147                                    |

| CHA   | PTER 5 SUMMARY AND CONCLUSIONS            | 149                                    |

| 5.1   | SUMMARY                                   | 149                                    |

| 5.2   | CONCLUSIONS                               | 151                                    |

| 5.3   | SUGGESTIONS FOR FUTURE WORK               | 153                                    |

| REFI  | ERENCES                                   | 156                                    |

| APPE  | ENDIX A                                   | A-1                                    |

| APPE  | ENDIX B                                   | В-1                                    |

| APPE  | ENDIX C                                   | C-1                                    |

| APPE  | ENDIX D                                   | D-1                                    |

## **List of Tables**

| Table 2.1 | LOW OUTPUT VOLTAGE CONVERTER SPECIFICATIONS | 10 |

|-----------|---------------------------------------------|----|

| TABLE 2.2 | EFFICIENCY COMPARISON OF THREE TOPOLOGIES   | 71 |

## **List of Figures**

| FIGURE 2.1  | DUAL ACTIVE BRIDGE CONVERTER                                                                     | . 18 |

|-------------|--------------------------------------------------------------------------------------------------|------|

| FIGURE 2.2  | FORWARD CONVERTER WITH ACTIVE CLAMP AND SELF DRIVEN SYNCHRONOUS RECTIFIER                        | . 23 |

| FIGURE 2.3  | FORWARD CONVERTER SECONDARY RECTIFIER STAGE SHOWING EFFECT OF LEAKAGE INDUCTANCE                 | . 25 |

| FIGURE 2.4  | FORWARD CONVERTER EQUIVALENT CIRCUIT DURING PHASE I                                              | . 28 |

| FIGURE 2.5  | FORWARD CONVERTER EQUIVALENT CIRCUIT DURING PHASE II                                             | . 29 |

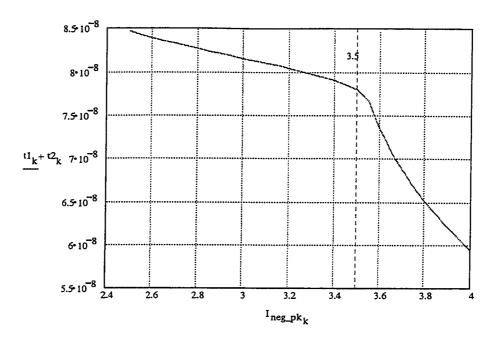

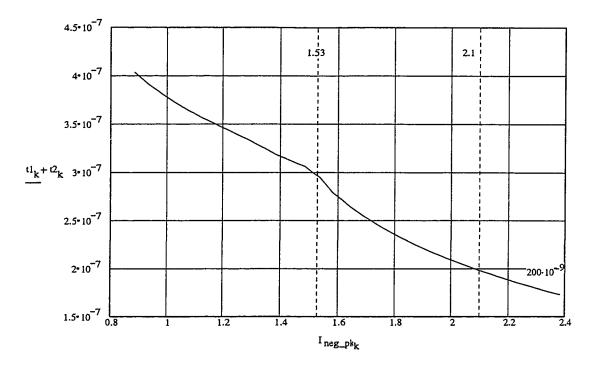

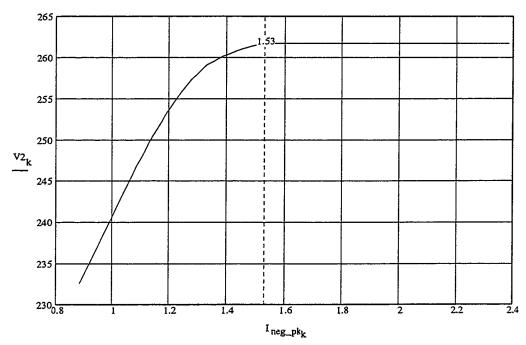

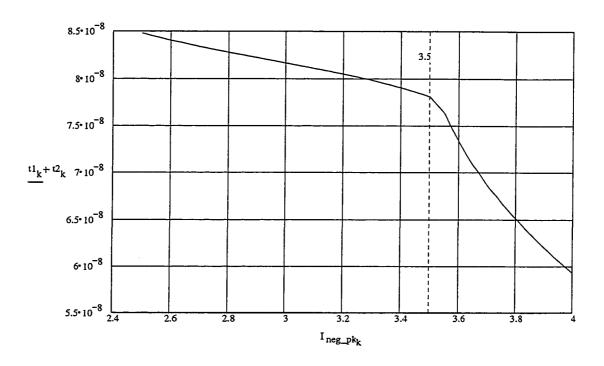

| FIGURE 2.6  | TOTAL TRANSITION TIME AS A FUNCTION OF $I_{NEG\_PK}$                                             | .40  |

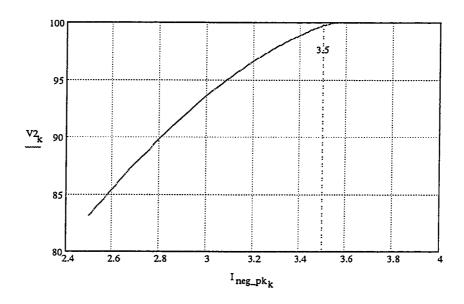

| FIGURE 2.7  | PRIMARY VOLTAGE EXCURSION AS A FUNCTION OF INEG. PK                                              | .40  |

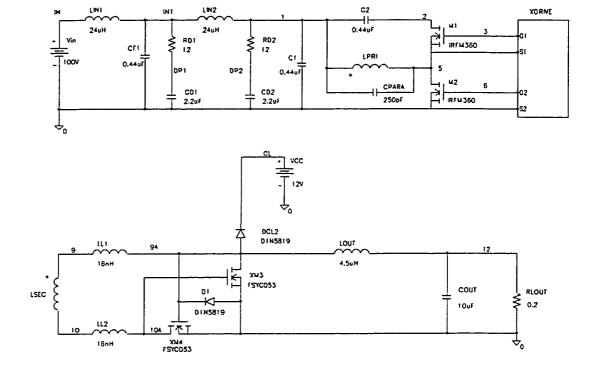

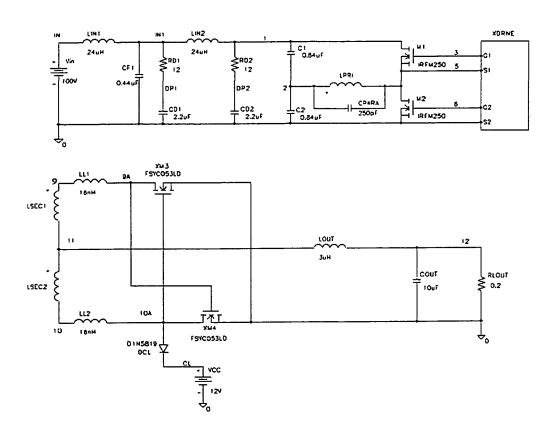

| FIGURE 2.8  | PSPICE MODEL OF FORWARD CONVERTER WITH ZERO VOLTAGE SWITCHING                                    | . 42 |

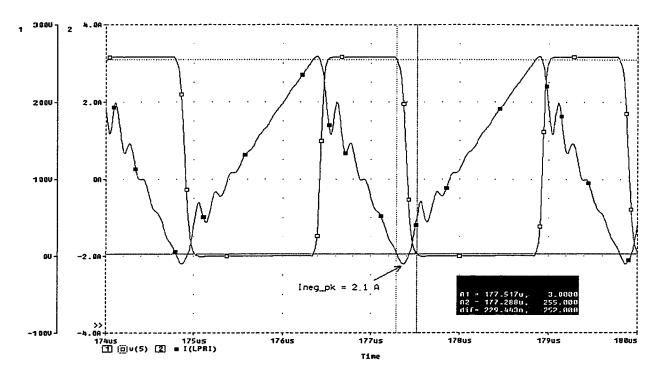

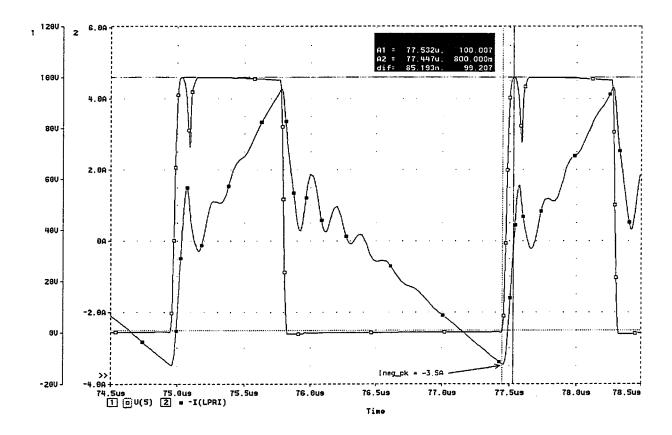

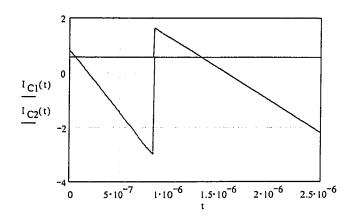

| FIGURE 2.9  | SIMULATION RESULTS OF FORWARD CONVERTER WITH ZERO VOLTAGE TRANSITION                             | . 43 |

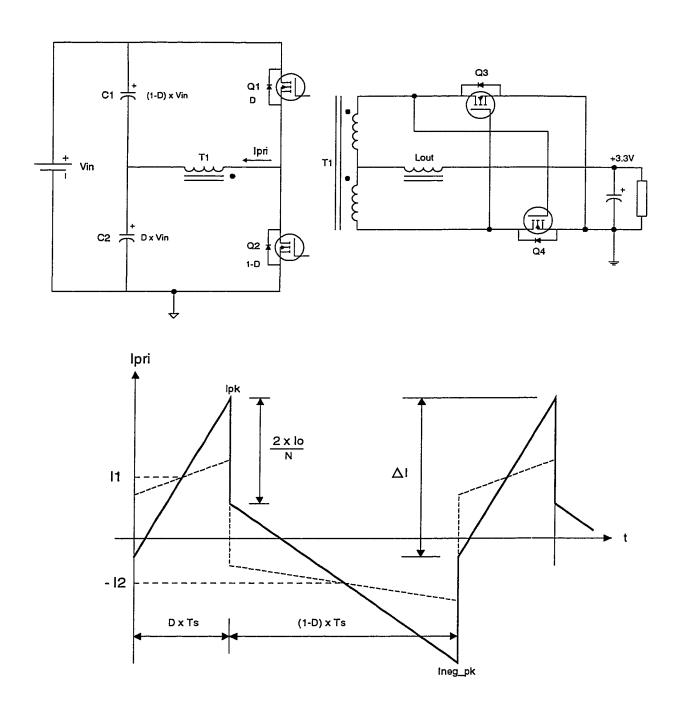

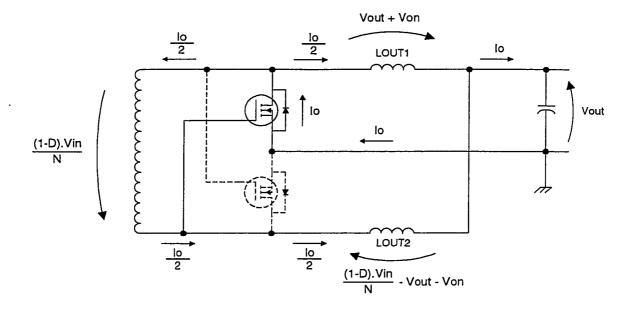

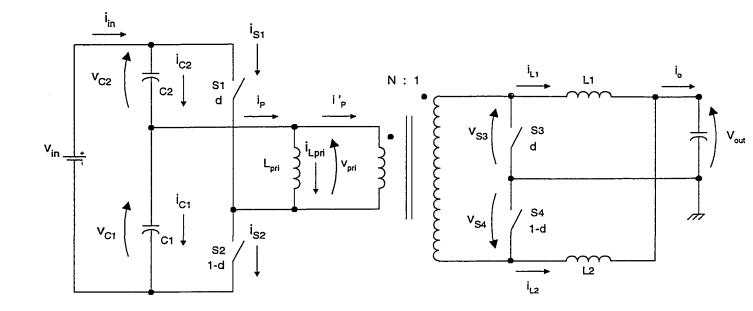

| FIGURE 2.10 | COMPLEMENTARY HALF BRIDGE WITH SELF DRIVEN SYNCHRONOUS RECTIFIERS                                | 45   |

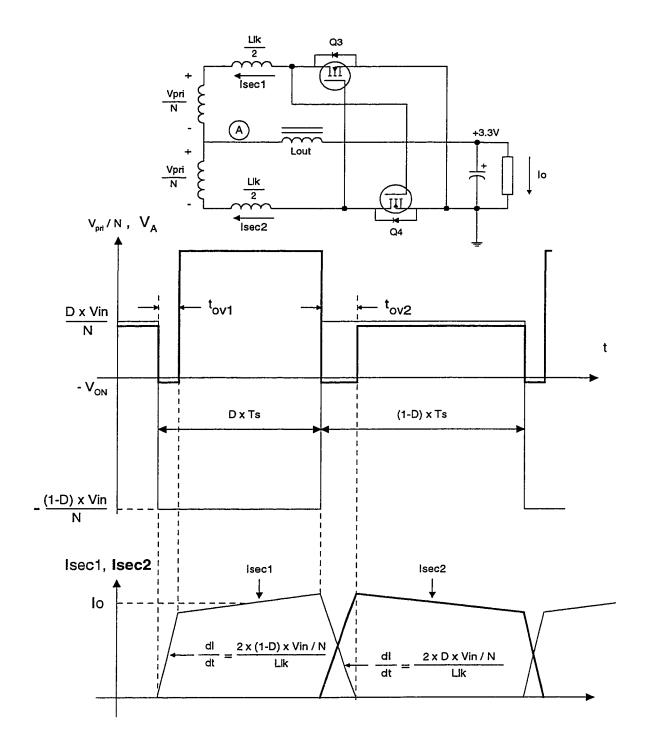

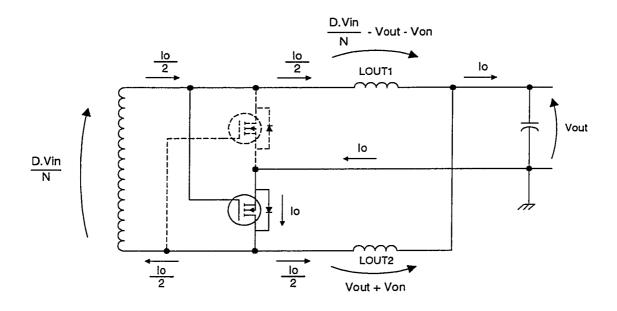

| FIGURE 2.11 | COMPLEMENTARY HALF BRIDGE CONVERTER SECONDARY STAGE                                              | .47  |

| FIGURE 2.12 | COMPLEMENTARY HALF BRIDGE CONVERTER EQUIVALENT CIRCUIT DURING PHASE I                            | 50   |

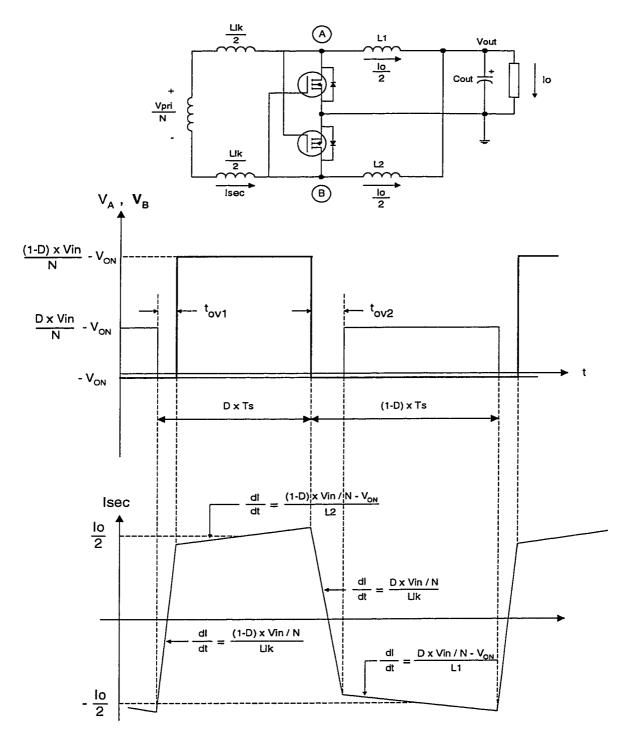

| FIGURE 2.13 | COMPLEMENTARY HALF BRIDGE CONVERTER EQUIVALENT CIRCUIT DURING PHASE II                           | 50   |

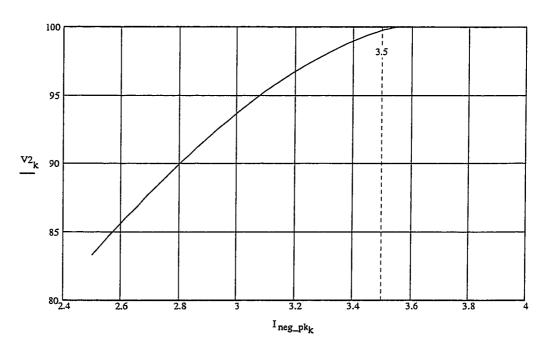

| FIGURE 2.14 | TOTAL TRANSITION TIME AS A FUNCTION OF INEG_PK                                                   | . 52 |

| FIGURE 2.15 | PRIMARY VOLTAGE EXCURSION AS A FUNCTION OF INEG_PK                                               | 52   |

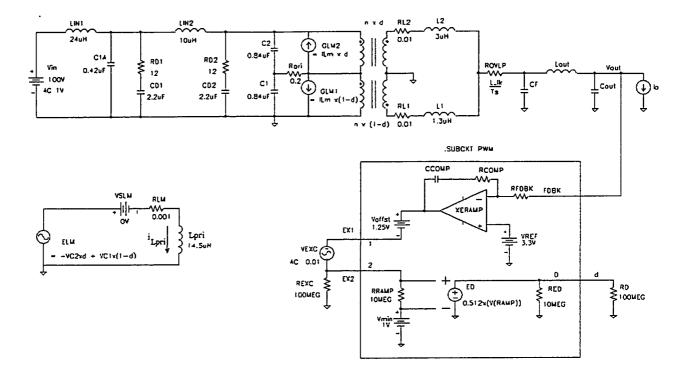

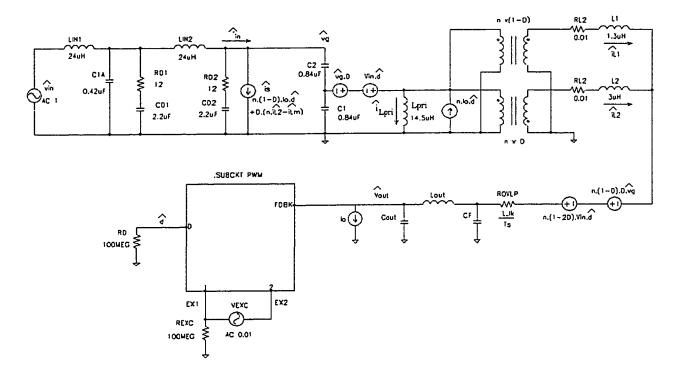

| FIGURE 2.16 | PSPICE MODEL OF THE COMPLEMENTARY HALF BRIDGE CONVERTER                                          | . 55 |

| FIGURE 2.17 | SIMULATION RESULTS OF COMPLEMENTARY HB CONVERTER WITH ZVT                                        | 56   |

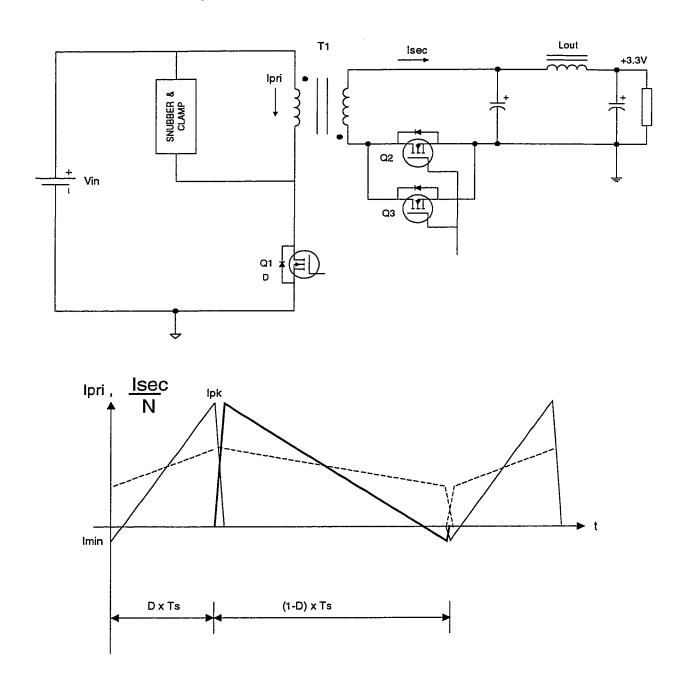

| FIGURE 2.18 | FLYBACK CONVERTER WITH ZVT FOR BOTH PRIMARY SIDE AND SECONDARY SIDE TRANSISTORS                  | 58   |

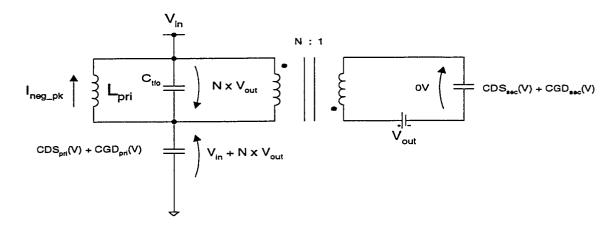

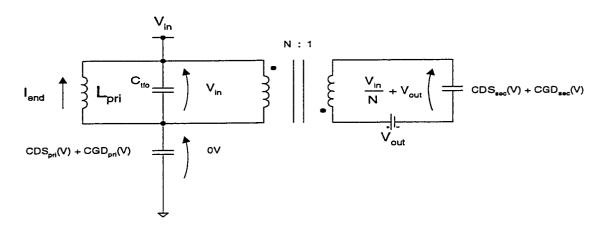

| FIGURE 2.19 | ZVT FLYBACK EQUIVALENT SCHEMATIC DURING THE SOFT TRANSITION                                      | 62   |

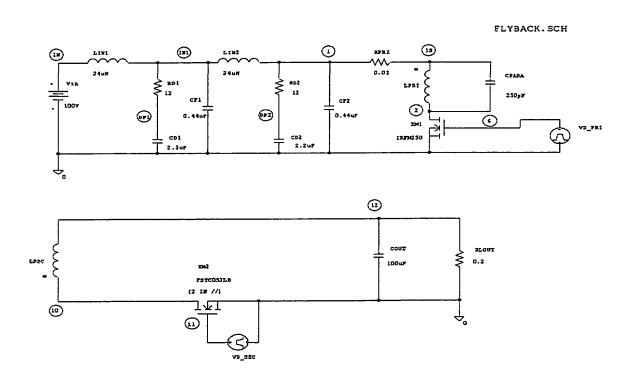

| FIGURE 2.20 | PSPICE MODEL OF ZVT FLYBACK CONVERTER                                                            | 69   |

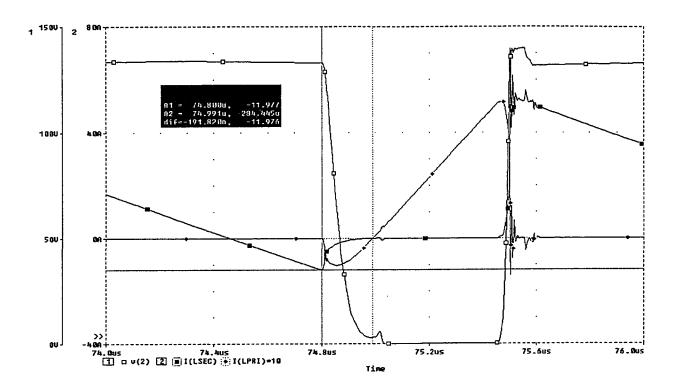

| FIGURE 2.21 | SIMULATION RESULTS FOR THE ZVT FLYBACK CONVERTER                                                 | 70   |

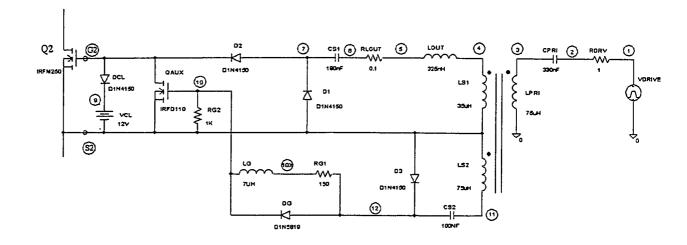

| FIGURE 3.1  | ZVT CHB SCHEMATIC (POWER SECTION)                                                                | 75   |

| FIGURE 3.2  | ZVT CHB SECONDARY STAGE DURING $D \times Ts$ and During $(1-D) \times Ts$                        | 76   |

| FIGURE 3.3  | ZVT CHB SECONDARY STAGE: IDEALIZED WAVEFORMS                                                     | 77   |

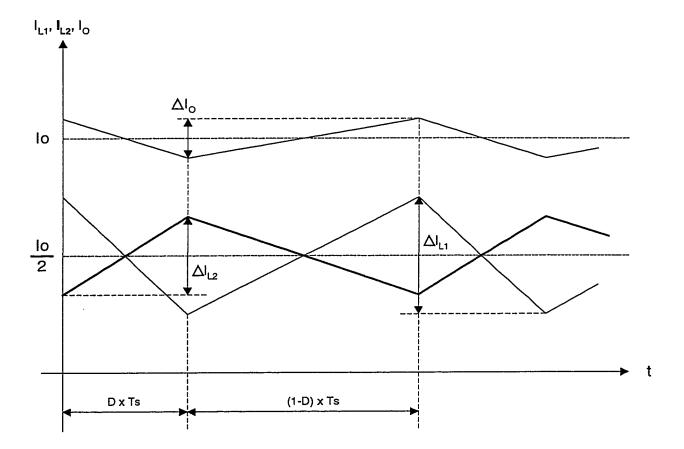

| FIGURE 3.4  | IDEALIZED CURRENT WAVEFORMS IN ZVT CHB OUTPUT INDUCTORS                                          | 80   |

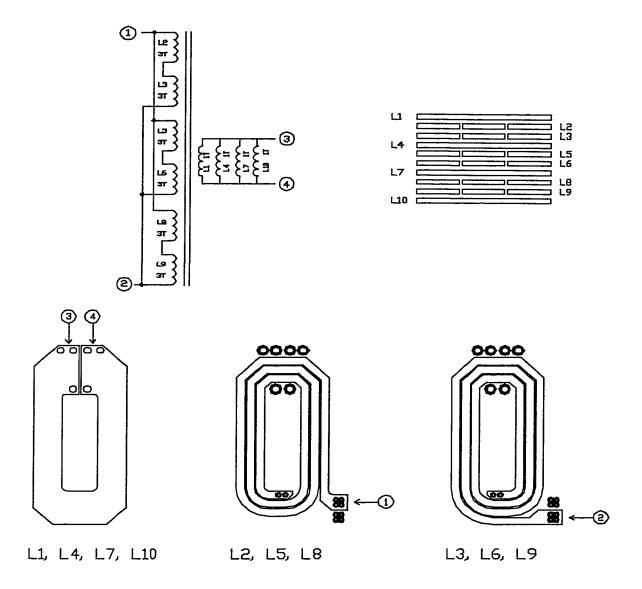

| FIGURE 3.5  | MAIN POWER TRANSFORMER DESIGN                                                                    | 84   |

| FIGURE 3.6  | GATE DRIVE SIGNAL GENERATION FOR Q1 AND Q2                                                       | 89   |

| FIGURE 3.7  | PRIMARY MOSFET GATE DRIVE CIRCUIT                                                                | 91   |

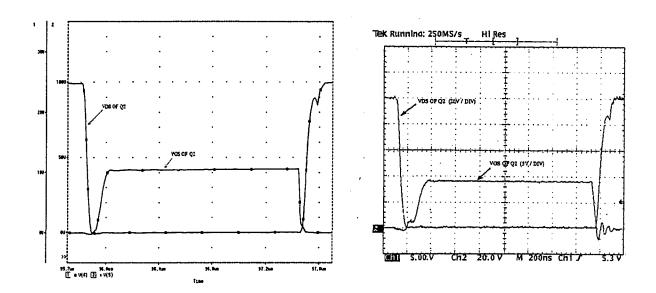

| FIGURE 3.8  | Simulated $V_{\text{GS}}$ and $V_{\text{DS}}$ of $Q2$                                            | . 94 |

| FIGURE 3.9  | MEASURED V <sub>GS</sub> AND V <sub>DS</sub> OF Q2                                               | 94   |

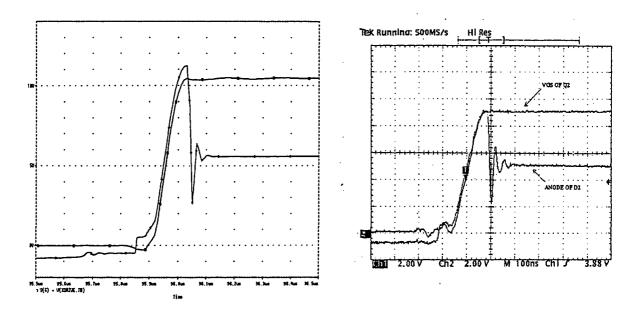

| FIGURE 3.10 | SIMULATED Q2 V <sub>GS</sub> AND V AT ANODE OF D2                                                | 95   |

| FIGURE 3.11 | MEASURED Q2 V <sub>GS</sub> AND V AT ANODE OF D2                                                 | 95   |

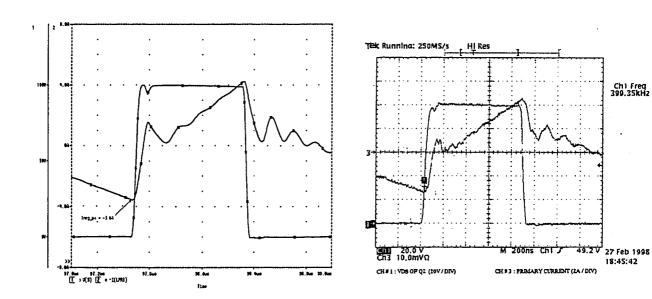

| FIGURE 3.12 | SIMULATED Q2 VDS AND PRIMARY CURRENT                                                             | 95   |

| FIGURE 3.13 |                                                                                                  | 95   |

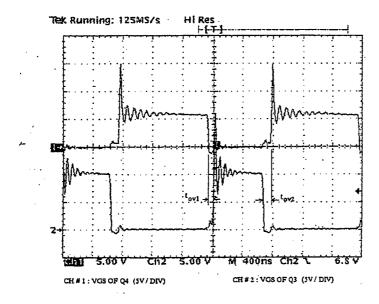

| FIGURE 3.14 | Measured V <sub>gs</sub> of Q3 and Q4                                                            | . 96 |

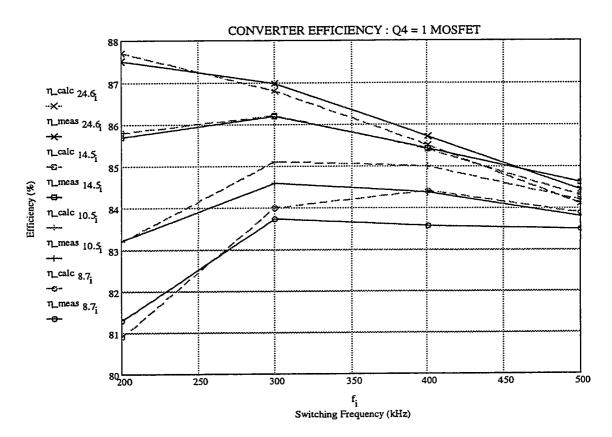

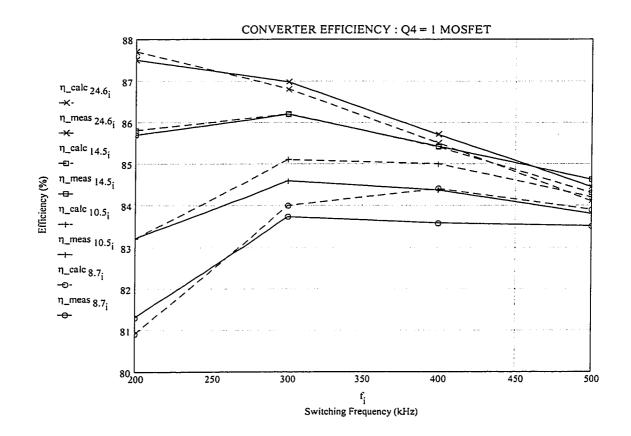

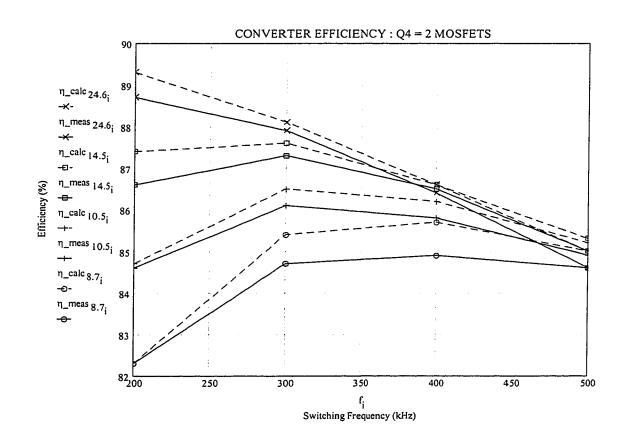

| FIGURE 3.15 | 3.3 V CONVERTER CALCULATED VERSUS MEASURED EFFICIENCIES WHEN Q4 CONSISTS OF ONLY ONE MOSFET      | 101  |

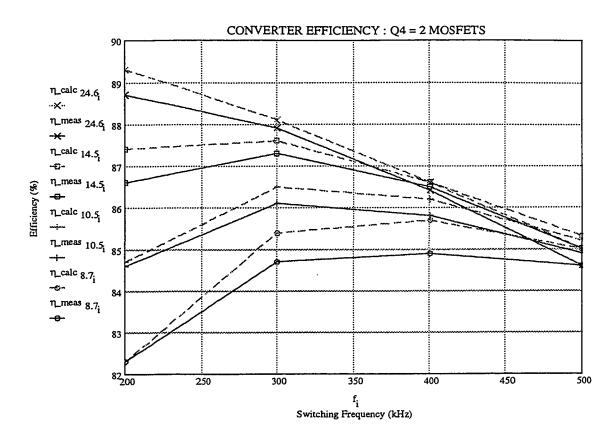

| FIGURE 3.16 | 3.3 V CONVERTER CALCULATED VS MEASURED EFFICIENCIES WHEN Q4 CONSISTS OF TWO MOSFETS IN PARALLEL. | 102  |

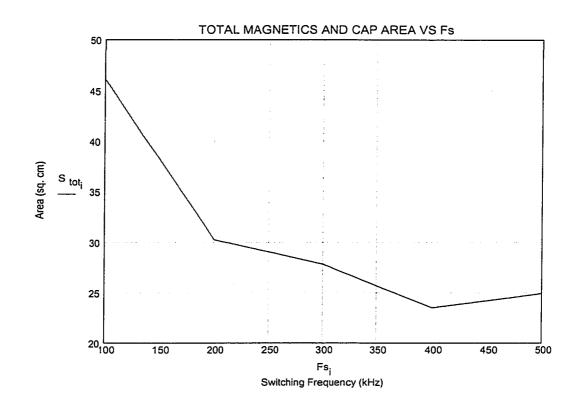

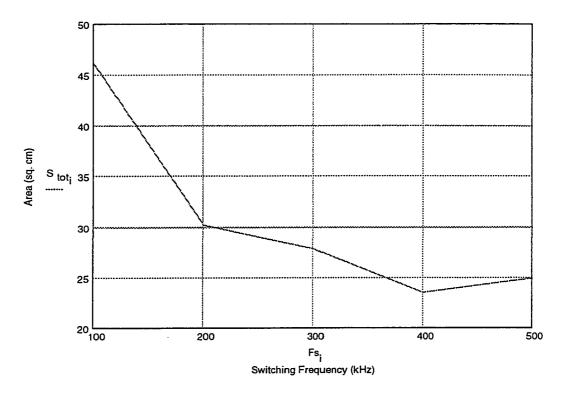

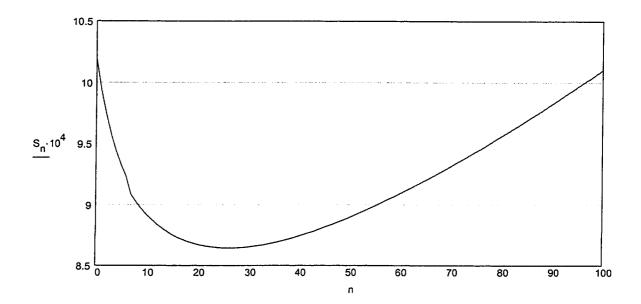

| FIGURE 3.17 | TOTAL AREA OF MAGNETICS AND CAPACITORS VERSUS SWITCHING FREQUENCY                                | 106  |

| FIGURE 4.1  | SIMPLIFIED SCHEMATIC OF CHBC                              | [ ] ] |

|-------------|-----------------------------------------------------------|-------|

|             | CHBC BASIC AVERAGED MODEL                                 |       |

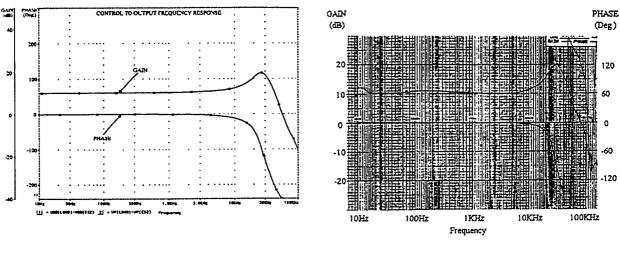

|             | SIMULATED CONTROL TO OUTPUT FREQUENCY RESPONSE            |       |

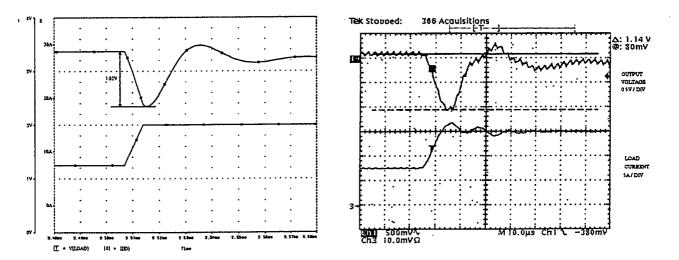

| FIGURE 4.4  | MEASURED CONTROL TO OUTPUT FREQUENCY RESPONSE             | 116   |

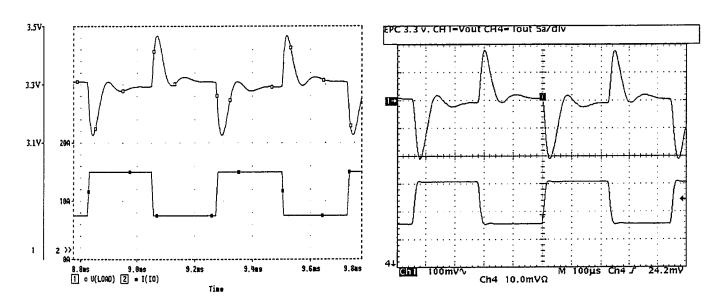

|             | SIMULATED RESPONSE TO A STEP LOAD CHANGE FROM 7.5A TO 15A |       |

| FIGURE 4.6  | MEASURED RESPONSE TO A STEP LOAD CHANGE FROM 7.5A TO 15A  | 116   |

| FIGURE 4.7  | SMALL SIGNAL MODEL OF THE CHBC                            | 119   |

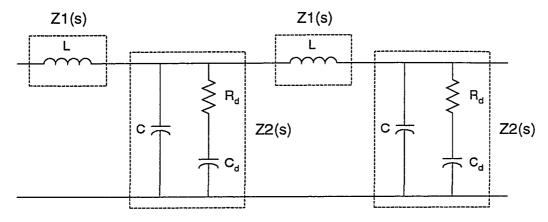

|             | CHBC DOUBLE STAGE INPUT FILTER                            |       |

| FIGURE 4.9  | INPUT FILTER FREQUENCY RESPONSE                           | 126   |

| FIGURE 4.10 | INPUT FILTER OUTPUT IMPEDANCE                             | 126   |

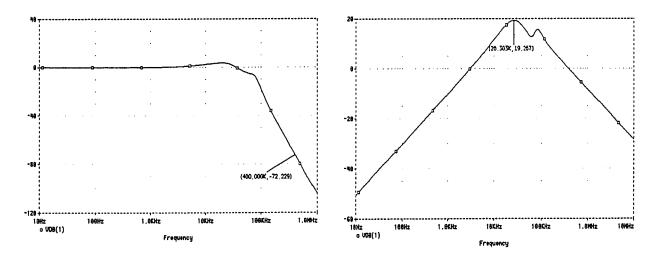

| FIGURE 4.11 | MODIFIED SECOND STAGE INPUT FILTER                        | 136   |

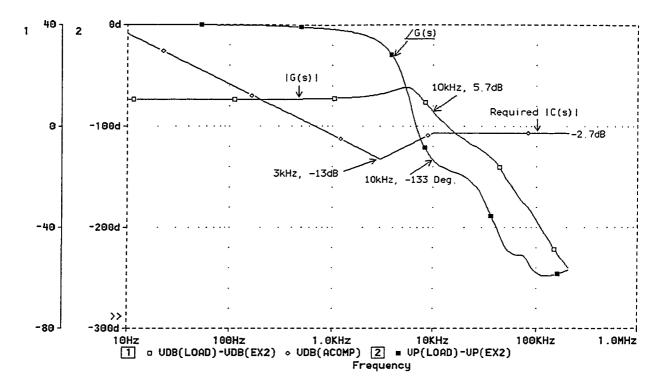

| FIGURE 4.12 | CONTROL TO OUTPUT RESPONSE WITH REQUIRED COMPENSATION     | 139   |

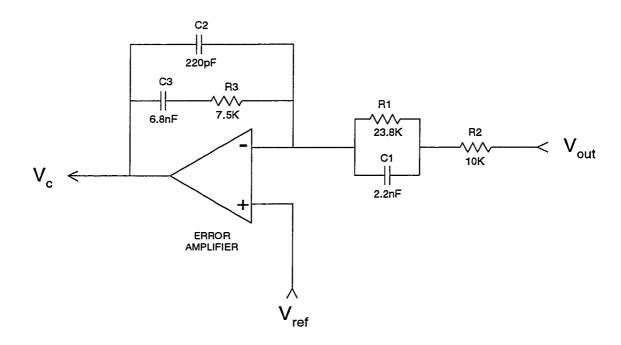

|             | COMPENSATION SCHEMATIC                                    |       |

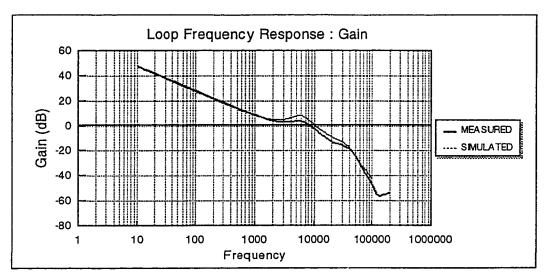

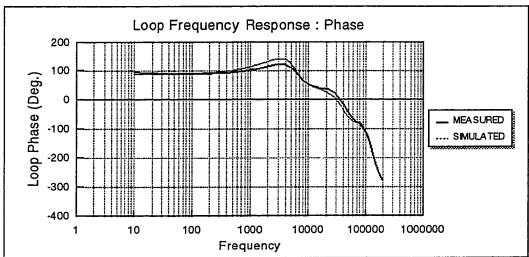

| FIGURE 4.14 | SIMULATED AND MEASURED LOOP FREQUENCY RESPONSE            | 142   |

| FIGURE 4.15 | SIMULATED STEP LOAD CHANGE TRANSIENT                      | 143   |

| FIGURE 4.16 | MEASURED STEP LOAD CHANGE TRANSIENT.                      | 143   |

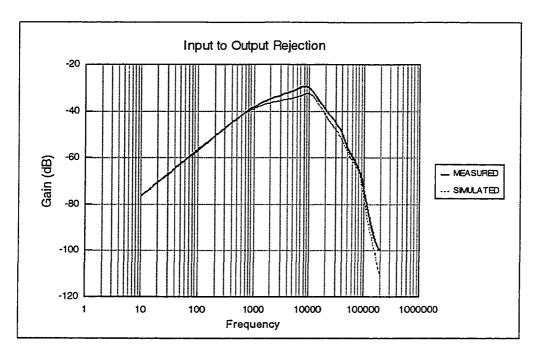

| FIGURE 4.17 | SIMULATED AND MEASURED INPUT TO OUTPUT REJECTION          | 145   |

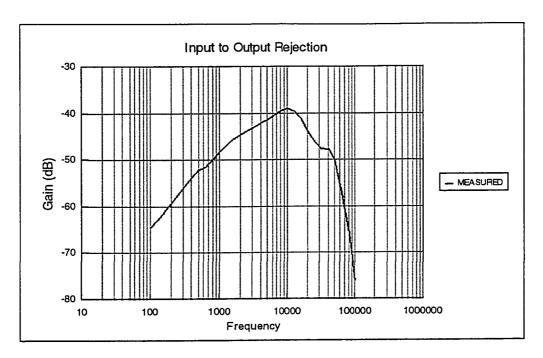

| FIGURE 4.18 | MEASURED INPUT TO OUTPUT REJECTION WITH FEEDFORWARD       | 147   |

## **List of Symbols and Abbreviations**

| $C_o$         | Output Capacitor                                                                                           |

|---------------|------------------------------------------------------------------------------------------------------------|

| C1, C2        | Complementary Half Bridge Converter input capacitors                                                       |

| Coss(V)       | Parasitic output capacitance of a MOSFET as a function of the voltage $V$ applied across it.               |

| $C_{GS}$      | Parasitic Gate to Source capacitance of a MOSFET                                                           |

| $C_{GD}(V)$   | Parasitic Gate to Drain capacitance of a MOSFET as a function of the voltage V applied across it.          |

| $C_{DS}(V)$   | Parasitic Drain to Source capacitance of a MOSFET as a function of the voltage V applied across it.        |

| $C_{tfo}$     | Main Power Transformer Primary to Secondary parasitic capacitance                                          |

| $C_{pri}$     | Overall parasitic capacitance connected to the primary side of the main power transformer $\ensuremath{T}$ |

| $C_{sec}$     | Overall parasitic capacitance connected to the secondary side of the main power transformer                |

| Cossoff       | Parasitic output capacitance of a MOSFET in its non-conducting state                                       |

| Cisson        | Parasitic input capacitance of a MOSFET in its conducting state                                            |

| CHBC          | Complementary Half Bridge Converter                                                                        |

| C(s)          | Small signal control loop compensation transfer function                                                   |

| D             | Power Converter Duty Cycle                                                                                 |

| $E_{Coss}(V)$ | Energy stored in a MOSFET output parasitic capacitance as a function of the voltage V applied across it.   |

| $E_{Vin}$     | Energy supplied by voltage source $V_{in}$ during a soft transition                                        |

| $E_{Vc}$      | Energy supplied by voltage source $V_c$ during a soft transition                                           |

| EI            | Energy stored in the reactive elements at the end of soft transition Phase I                               |

| E2              | Energy stored in the reactive elements at the end of soft transition Phase II                                                       |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| Fs              | Switching Frequency                                                                                                                 |  |

| F(s)            | Small signal open loop input voltage to output voltage transfer function                                                            |  |

| $F_{cl}(s)$     | Small signal closed loop input voltage to output voltage transfer function                                                          |  |

| G(s)            | Small signal duty cycle to output voltage transfer function                                                                         |  |

| $I_{pk}$        | Current through the main transformer primary winding at the beginning of the first soft transition (end of Q1's conduction period)  |  |

| $I_{neg\_pk}$   | Current through the main transformer primary winding at the beginning of the second soft transition (end of Q2's conduction period) |  |

| $I_{Lpri}$      | Main power transformer primary magnetizing current                                                                                  |  |

| II              | Current through main power transformer leakage inductance at the end of soft transition Phase I.                                    |  |

| <i>I</i> 2      | Current through main power transformer leakage inductance at the end of soft transition Phase II.                                   |  |

| $I_o$           | Output current                                                                                                                      |  |

| $\Delta I_o$    | Peak to peak variation of output current                                                                                            |  |

| ΔΙ              | Peak to peak variation of main power transformer primary magnetizing current                                                        |  |

| $\Delta I_{LI}$ | Peak to peak ripple current in CHBC output inductor L1                                                                              |  |

| $\Delta I_{L2}$ | Peak to peak ripple current in CHBC output inductor L2                                                                              |  |

| $L_{pri}$       | Main power transformer primary magnetizing inductance                                                                               |  |

| $L_{sec}$       | Main power transformer secondary magnetizing inductance                                                                             |  |

| $L_{lk}$        | Main power transformer leakage inductance including secondary side stray inductance.                                                |  |

| $L_{out}$       | Output filter inductor                                                                                                              |  |

| L1, L2          | Complementary pair of output inductors in CHBC current doubler configuration                                                        |  |

| $L_{\it eff}$   | CHBC effective output inductance                                                                                                    |  |

| N               | Main power transformer primary to secondary turns ratio                                                                             |  |

| n               | Main power transformer secondary to primary turns ratio ( = $1/N$ )                                                                 |  |

| Q1, Q2          | Primary MOSFETs                                                                                                                     |  |

| Q3, Q4          | Secondary synchronous rectifier MOSFETs                                                                                             |  |

| Ts              | Switching period                                                                                                                    |  |

| T(s)            | CHBC small signal loop transfer function                                                                                            |  |

|                 |                                                                                                                                     |  |

Duration of soft transition Phase I tΙ t2 Duration of soft transition Phase II Duration of secondary synchronous rectifiers first overlap period  $t_{ov1}$ Duration of secondary synchronous rectifiers second overlap period  $t_{ov2}$ Total overlap duration ( =  $t_{ov1} + t_{ov2}$ )  $t_{ov}$  $V_{in}$ Input voltage Output voltage  $V_{out}$ Voltage across clamping capacitor in ZVT Forward Converter  $V_c$  $V_{GS}$ Gate to Source voltage of a power MOSFET Drain to Gate voltage of a power MOSFET  $V_{DG}$ Drain to Source voltage of a power MOSFET  $V_{DS}$ VIVoltage variation across the main transformer primary winding during the soft transition Phase I. Voltage variation across the main transformer primary winding during the soft V2transition Phase II.  $V_{on}$ Voltage drop across one secondary synchronous rectifier in its conducting state  $V_{CI}$ Voltage across CHBC primary capacitive divider top capacitor Voltage across CHBC primary capacitive divider bottom capacitor  $V_{C2}$ CHBC small signal open loop output impedance Zo(s)CHBC small signal closed loop output impedance  $Zo_{cl}(s)$ ZVS Zero Voltage Switching ZVT Zero Voltage Transition

## **List of Appendices**

| APPENDIX A | A COMPARATIVE STUDY OF THREE TOPOLOGIES IN TERM OF CONDUCTION LOSSES    | .A-1 |

|------------|-------------------------------------------------------------------------|------|

|            | A MATHEMATICAL MODEL OF THE GATE TO DRAIN CAPACITANCE FOR POWER MOSFETS |      |

|            | EFFICIENCY CALCULATION OF 3.3 V COMPLEMENTARY HALF BRIDGE CONVERTER     |      |

| APPENDIX D | SIZE OPTIMIZATION OF 3.3 V COMPLEMENTARY HALF BRIDGE CONVERTER          | .D-1 |

## Chapter 1 Introduction

### 1.1 General Introduction

The last decade has seen significant advances in the area of digital microcircuits; our quest for more speed, more performance with even less electrical power consumption has prompted the development of digital microcircuits working off supply voltages as low as 1.5 V. This downwards trend of supply voltages has posed numerous interesting challenges to the power supply designers as they must now cope with new difficulties which are described below.

- 1. At a given output power, the output current is inversely proportional to the output voltage; this means that currents delivered by low voltage converters are high; as an example, the nominal output current of a 3.3 V, 50 W converter is equal to 15 A. These high output currents, in turn, create substantial voltage drops in their output rectifier and filter stage which are a significant fraction of the (low) output voltage and therefore cause a significant efficiency degradation.

- 2. The high output currents combined with the low output voltages have a negative impact on the size of the output filters: assuming that the maximum allowed output voltage ripple is a fixed percentage of the output voltage, the allowed output voltage ripple is much lower in a low voltage converter than in a voltage converter of same output

power supplying a higher output voltage. This means that the filter corner frequency must decrease, and therefore the capacitance and/or inductance values of the filter must increase. If we choose not to increase the filter inductance, we must increase the filter capacitance (and therefore its size) in order to comply with the lower output voltage ripple. However, the size of the inductor will increase too, even though its inductance value remained unchanged, because it must now handle a higher DC current.

3. One of the most important advances achieved in the area of digital microcircuits is certainly the high degree of miniaturization; as a result, complex digital functions can now be implemented on a single printed circuit board, which can now operate independently from the neighbouring printed circuit boards. This has created the possibility of building modular digital systems where each module corresponds to a printed circuit board. For high reliability systems such as those found in Aerospace applications, a certain degree of redundancy can be implemented in the system by simply adding more modules to those strictly required by the application; those additional modules remain in a standby mode until failure of one of the working modules forces one of the spare modules to take over operation from the failed module. Such a system can be quite large (30 modules) and its consumption can easily exceed 1.5 kW (50W per module x 30 modules = 1.5kW). For a 3.3 V power converter, an output power of 1.5 kW would correspond to an output current of 450 A. Not only is it quite difficult to design a converter having such a high output current, but also this high current level will create significant distribution losses as the 3.3 V power is conveyed from the converter output to the many modules which compose the whole system. A viable alternative to this situation is to design several lower power converters, each of which would be providing power to a subset of the system modules, in a decentralized manner; the question is to define how many modules each converter should be providing power to. It was pointed out above that in order for the whole system to have a certain degree of redundancy, each module should operate in an independent fashion; therefore a logical

choice is to provide each module with its own dedicated power supply; since a module corresponds to a printed circuit board, the power converter must be located on the board itself or in its immediate neighbourhood. An additional advantage of having the converter residing on the functional board and therefore co-located with its load is that the dynamic voltage drops due to the load current variations are minimized.

### 1.2 Problem Statement

The requirement of making the converter on-board resident raises the need to miniaturize the converter since only a given percentage (usually small) of the board area is allocated to it. Unfortunately, as is widely known in the power engineering community, the miniaturization requirement is in conflict both with the high efficiency requirement and also with the low output ripple requirement as explained the previous paragraph.

In many cases, the response of the power supply designers to this need of having a on-board resident converter has been to design a simple non isolated buck converter which steps down the +5 V rail to the required lower voltage rail. This approach is justified by the coexistence, on the same PC board, of circuits requiring +5 V and circuits requiring +3.3 V or lower supply voltages. Although simple, this approach is ineffective for the following reasons:

1. If the +5 V rail is supplied by a centralized converter, then the failure of this converter causes the loss of the whole system, which defeats the redundancy requirement. Moreover, a centralized converter supplying the +5 V rail to the whole system leaves the systems engineer faced with the high distribution losses as explained in (3) above. If the +5 V rail is supplied by a localized converter, then the overall size of this converter and the low voltage converter will be significantly higher than the size of a single low voltage converter operating from the input line.

2. Although a non isolated buck converter which takes its input from the +5 V can be designed with efficiencies in the order of 95 %, the overall efficiency of providing the low voltage rail (+3.3 V or lower) is equal to the product of the +5 V converter efficiency and the buck converter efficiency, which makes the double stage conversion inefficient.

From the above discussion, the only viable alternative lies in a single stage converter which turns the input voltage directly into +3.3 V and provides galvanic insulation between input and output.

### 1.3 Literature Review

Several topologies have been proposed to convert a medium to high input voltage source into a low output voltage; a common viewpoint expressed in most of the literature reviewed is the need for secondary synchronous rectifiers, as opposed to Schottky diodes; in addition, these synchronous rectifiers should be self driven, i.e. their driving signals should be derived from the waveforms appearing on the power transformer secondary winding in order to avoid the added complexity of dedicated gate drive circuitry. Therefore, the problem is to apply a suitable waveform to the gates of the synchronous rectifiers, such that those will remain in full conduction during their conduction interval; this waveform is shown to be very much dependent on the topology. Comparative studies carried out in [7], [8] and [9] conclude that high frequency resonant topologies are inadequate because the waveforms applied to the gates of the synchronous rectifiers are sinusoidal and hence, they fail to maintain the MOSFETs in full conduction throughout the conduction period. For the same reason, classical Pulse Width Modulation symmetrical topologies are unanimously rejected because inherent to their operation is a dead time during which zero volt is applied to the gates of the secondary synchronous rectifiers; this results in the conduction of the associated antiparallel diode of the MOSFET rather than of the MOSFET itself; as these

diodes typically have a forward voltage drop much higher than that of the MOSFET, this has a negative impact on efficiency.

As a result, most of the recent research on low output voltage converters focuses on asymmetrical topologies where typically two switching MOSFETs operate in a complementary fashion [1-9], [13-16]; this results in no dead time and consequently no zero voltage gap on the gates of the synchronous rectifiers; in turn, this maximizes their utilization and hence, improves overall efficiency. Furthermore, the complementary operation is taken one step further by introducing a small delay between the turn-off of one of the complementary MOSFETs and the turn-on of the other. It is shown that if sufficient magnetizing energy is stored in the power transformer at the moment the first MOSFETs is turned off, then a natural or "soft" commutation takes places which eventually results in the second MOSFET being turned on under zero voltage. This has the effect of dramatically reducing the switching losses and therefore, paves the way for higher switching frequencies at little penalty in terms of efficiency.

The proposed topologies which take advantage of the complementary operation as well as the Zero Voltage Transition (ZVT) phenomenon are basically derived from classical topologies. The ZVT Forward Converter is described in [1-3], [7] and [8]. The ZVT Complementary Half Bridge Converter is described in [4-6] and [9]. In [13-16], a variant of the above topologies is proposed which utilizes the concept of output current doubling, based on earlier work described in [11] and [12]. In [17] and [19], a modification of conventional Forward and Flyback topologies is described whereby an auxiliary circuit is employed to achieve the desired Zero Voltage Switching. Finally, the phase shift modulated Dual Active Bridge is described in [10].

The choice of one topology versus another is complex and depends on parameters such as input voltage, output power, variations of input voltage and output current, total number of semiconductors and hence cost. One contribution of this thesis is an attempt to

develop objective criteria which lead to the choice of one topology given a set of operating conditions.

### 1.4 Scope and Contributions of this Thesis

The purpose of this thesis is two-fold:

- Explore different topologies which make use of the soft commutation phenomenon and

determine which topology will lead to the highest conversion efficiency under a given

set of operating conditions. In order for this comparative study to be successful, it is

necessary to analyze in detail the mechanisms which govern the phenomenon of Zero

Voltage Transition (ZVT).

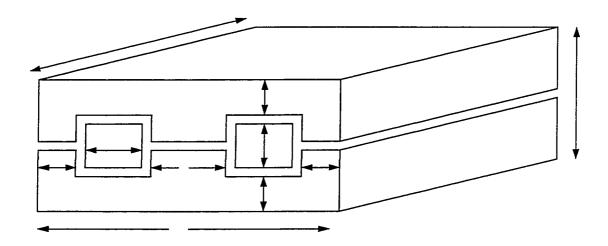

- 2. Build a prototype based on the selected topology. The small size requirement for this type of on-board resident converter can only be satisfied if the converter is miniaturized by such techniques as "Chip on Board"; this miniaturization effort is beyond the scope of this work; therefore, only a prototype with conventional, packaged components will be developed; however, as a step towards miniaturization, low profile transformers where the windings lie on a printed circuit board will be experimented.

The main contributions of this thesis are the following:

1. The development of a mathematical model which, for a given topology precisely calculates the amount of reactive energy which must be stored in the transformer magnetizing inductance in order to achieve a full ZVT. This mathematical model takes into account the non-linear nature of the switching MOSFET parasitic capacitances. Once the magnetizing current required for a full ZVT has been determined, the RMS values of the currents through the transformer windings and through the primary and secondary MOSFETs can be calculated which in turn enables a precise calculation of the conduction losses. These conduction losses are then compared to those incurred in

other topologies; the topology retained is the one which exhibits the lowest conduction losses.

- 2. Based on the results of the above model, a more general mathematical model is developed which, for a given topology and a given switching frequency precisely calculates the size of the converter power stage and the converter overall efficiency. The results obtained from this model allow a quick determination of the optimum switching frequency.

- 3. The development of dynamic large signal and small signal models for the selected topology in an output current doubler configuration.

### 1.5 Thesis Outline

The contents of this thesis are organized as follows:

In Chapter 2, a comparative study is carried out between three topologies using the concept of ZVT, in terms of their conduction losses. This comparative study is based on a mathematical model which, for a given topology, precisely calculates the amount of primary magnetizing inductance required for ZVT to occur. For each topology, a PSPICE model of the converter which includes the MOSFET non-linear capacitances is developed in order to validate the results obtained from the mathematical model. The topology selected is the one exhibiting the lowest conduction losses.

Chapter 3 is devoted to the design and construction of a prototype based on the selected topology. The waveforms measured on the prototype are compared to those predicted by the PSPICE model corresponding to the selected topology. A more general mathematical model is developed which, for any switching frequency precisely calculates the overall efficiency. The efficiencies obtained from this mathematical model are then compared to those measured on the prototype operating under the same conditions. The same mathematical model also calculates the size of the converter power stage for a given

set of constraints and operating conditions, and for different switching frequencies. This in turn allows a quick determination of the optimum switching frequency, i.e. the frequency corresponding to the minimum size.

Chapter 4 is devoted to the large signal and small signal modelling of the converter. Analytical expressions and PSPICE models are developed to predict the main transfer functions as well as the transient responses of the converter. The predicted frequency and transient responses obtained from the models are then compared to those measured on the real prototype.

Chapter 5 summarizes the work carried out in this project, the results obtained, the conclusions and the areas requiring future research and development.

# **Chapter 2 A Comparative Study of Several Topologies**

#### 2.1 Introduction

The purpose of the low voltage DC to DC converter we are to develop is to provide power to many identical digital boards located side by side. In such configurations, system redundancy requirements dictate that each individual board be powered by its own dedicated converter. This results in a large number of identical converters each of which typically resides on the functional board it is providing power to or in the immediate neighborhood of it (for example on a backplane to which the functional board is connected).

This situation results on one hand in a tight volume constraint because each local converter occupies a portion of the functional board where it resides and on the other hand, it imposes a severe efficiency requirement; the high efficiency demand which is put on the converter is the direct result of the high power typically consumed by modern digital On Board processing systems.

It will be shown in this chapter that the two conflicting requirements of low volume and high efficiency can only be met with a class of topologies which allow a high frequency of operation while avoiding the high switching losses normally associated with a high switching frequency. These topologies make use of soft commutations and complementary operation between the different power switches.

### 2.2 Choice of a Topology

The choice of a topology is dictated by several factors which are:

- Input voltage and its variations

- Input to output isolation requirement

- Total output power

- Voltage and current ratings of the power semiconductors

- Number of output rails

- Input current ripple requirement

- Output voltage ripple requirement

- Volume constraints

- Efficiency requirement

The requirements of the converter we are to develop are summarized in Table 2.1 below.

Table 2.1 Low Output Voltage Converter Specifications

| Input voltage            | 90 V DC to 110 V DC                         |

|--------------------------|---------------------------------------------|

| Output voltage           | 3.3 V, electrically isolated from the input |

| Output voltage ripple    | 10 mV peak to peak                          |

| Load and Line regulation | ±1%                                         |

| Output power             | 30 W to 60 W                                |

| Efficiency               | 87 % at an output power of 50 W             |

| Size                     | 2.5" × 4" × 0.75"                           |

| Frequency of operation   | 350 kHz to 500 kHz                          |

The output power of 50 W corresponds to the maximum predicted consumption of a digital printed circuit board.

The input voltage of 100 V corresponds to one of the three bus voltages which are becoming standard in the Aerospace world, the other two being the 70 V bus and the 50V bus. The 100 V bus was deliberately chosen for this work since it corresponds to the worst case in terms of efficiency.

The small envelope specified in Table 2.1 imposes a high switching frequency in order to reduce the size of the switching transformer and filtering magnetics. Early estimates suggest that the optimum frequency of operation may lie between 200 kHz and 500 kHz.

It should be noted that the frequency of operation is determined by the minimum efficiency and maximum volume goals.

The low output voltage, in conjunction with the high efficiency goal dictates the use of synchronous rectifiers at the output in order to reduce the conduction losses. Unfortunately, synchronous rectifiers may increase the switching losses if proper caution is not exercised in the timing of their gate drive signals.

The conflicting requirements of high switching frequency and high efficiency (which means low conduction and switching losses) can only be met with a topology which meets the following conditions:

- 1. Complementary operation among the following pairs of switches:

- a) Primary switch No. 1 vs. Primary switch No. 2

- b) Sync. Rectifier No. 1 vs. Sync. Rectifier No. 2

- 2. Primary Switch vs. Sync. Rectifier for topologies like the Flyback which only have one switch on the primary and one switch on the secondary.

- 3. Zero voltage turn-on (ZVT) for all the semiconductor switches, be they located on the primary or on the secondary side.

Complementary operation between two transistors Q1 and Q2 means that Q1 conducts during one portion of the switching period, and that Q2 conducts during the remainder of the period. Q1's conduction time is usually called  $D \times Ts$ , where D designates the duty cycle and Ts the switching period. Then, Q2's conduction time equals  $(1-D) \times Ts$ .

Ideally, the complementary operation should be a true one, i.e. there should be no conduction overlap and no dead time.

This complementary operation is desirable for the following reasons:

- 1. Any conduction overlap means that Q1 and Q2 are simultaneously conducting; this situation, if not well controlled, leads to momentary current spikes which in turn cause an increase of conduction and switching losses.

- 2. Any significant dead time between the conduction of Q1 and Q2 always results in no synchronous rectifier being ON, whether Q1 and Q2 represent the sync. rectifiers themselves or the primary transistors. This means that during this dead time, the output current is being carried by the internal antiparallel diodes inherent to the sync. rectifiers MOSFETs; since these diodes have a forward drop significantly higher than the MOSFET, conduction of these diodes causes a significant increase of conduction losses.

- 3. Complementary conduction is the only mode of operation which allows zero voltage turn-on of the transistors.

Zero voltage turn-on for a MOSFET (also called "soft" transition) means that when a voltage is applied between its Gate and Source terminals to turn it ON, the voltage between its Drain and Source terminals must already be zero. In practice, this means that the internal Body-Drain diode is already conducting reverse current when the ON command is applied to the gate of the MOSFET. This mode of operation is desirable because it avoids the dissipation in the MOSFET of the energy stored in its parasitic capacitance, which normally occurs during a "hard" turn-on. At high switching frequencies, this dissipated energy represents a significant amount of power, which is calculated as follows:

It is shown in Appendix B that the output capacitance of a MOSFET can be expressed as

$$Coss(V) := \frac{Cdso}{\sqrt{1 + \frac{V}{0.8}}} + \frac{Cgdo}{(A+V)^{\gamma}}$$

(2.2.1)

The first term of (2.2.1) represents the drain to source capacitance, whereas the second term represents the drain to gate capacitance. The coefficients of (2.2.1) have been calculated in Appendix B for several MOSFETs. In order to calculate the energy wasted during a hard turn-on, we must consider that the MOSFET which is being turned on must not only discharge its own output parasitic capacitance, but it must also charge the parasitic capacitance of the MOSFET connected in series with it (see Figure 2.10); in addition, it must also charge the transformer parasitic capacitance. With reference to Figure 2.10, (which represents the best case in terms of turn-on losses), we shall assume that the voltage at the connection point of the two MOSFETs equals  $0.5 \times V_{in}$  or 50 V at the moment the lower transistor Q1 is being turned on; we also assume that the transformer parasitic capacitance equals 250 pF (measured on a real PCB transformer); the elemental energy being dissipated when the capacitances are being discharged from V to V - dV is equal to

$$dE = V \cdot dQ = V \cdot C_{eq}(V) \cdot dV = \left(Coss(V) + Coss(V_{in} - V) + C_{tfo}\right) \cdot V \cdot dV$$

(2.2.2)

In the above expression, Coss(V) represents the output capacitance of MOSFET Q1 which is being turned on and whose drain to source voltage equals V. On the other hand,  $Coss(V_{in}-V)$  represents the output capacitance of the upper transistor Q2 whose drain to source voltage equals  $V_{in}-V$ . The equivalent capacitance  $C_{eq}$  must be discharged from 50 V to zero; we choose the MOSFETs as IRFM250 (whose capacitance coefficients are calculated in Appendix B) and we take a switching frequency of 300 kHz. Therefore, the turn-on losses are equal to

$$P_{ON} := \left[ \int_{0}^{V_{in}} \frac{1}{2} \left( Coss(V) + Coss(V_{in} - V) + C_{tfo} \right) \cdot V \, dV \right] \cdot 2 \cdot Fs$$

$$P_{ON} = 1.105 \text{ W}$$

$$(2.2.3)$$

In the above equation, the coefficient 2 accounts for two hard turn-ons per period. As can be seen, the power dissipated due to hard turn-on equals 1.1 W at 300 kHz and will increase proportionally to the switching frequency. This dissipation of 1.1 W represents an efficiency loss of 2 % at an output power of 50 W and is considered unacceptably high. Again, it must be stressed that the above calculation corresponds to the best case. Therefore, if we are to operate at frequencies equal to or higher than 300 kHz, the only viable alternative is Zero Voltage turn-on.

Zero voltage turn-on is achieved in the following way. If Q1 and Q2 represent two primary MOSFETs connected such as in Figure 2.2 below, turning off Q1 causes the magnetic energy stored in the transformer during the conduction time of Q1 (either in the leakage inductance or in the magnetizing inductance) to charge Q1's parasitic capacitance and to discharge Q2's parasitic capacitance.

If the magnetic energy is high enough, then the two parasitic capacitances are fully discharged and Q2 starts conducting reverse current through its antiparallel diode.

If an ON command is then applied to the gate of Q2, the latter is being turned on under zero Drain-Source voltage. Subsequently, circuit operation causes the current through Q2 to become positive and the same phenomenon occurs when Q2 is turned off.

It should be noted however that the soft transition just described is only possible in topologies where Q1 and Q2 are driven in a complementary fashion.

If a significant dead time existed between Q1 and Q2 conduction, not only would Q1 and Q2 experience a "hard" turn-on but also all the magnetic energy which could have otherwise been utilized to turn on the complementary transistor under zero voltage is now totally wasted, which creates additional losses.

Four topologies so far have been found to meet the above requirements:

- 1. The dual active bridge converter (Figure 2.1).

- 2. The active clamp single ended forward converter with high magnetizing primary current (Figure 2.2).

- 3. The complementary half bridge converter (Figure 2.10).

- 4. The continuous mode flyback converter (Figure 2.18).

It should be noted that all classical Pulse Width Modulation topologies were rejected because inherent to them is a dead time in the conduction of the primary transitors which leads to the undesirable effects described above.

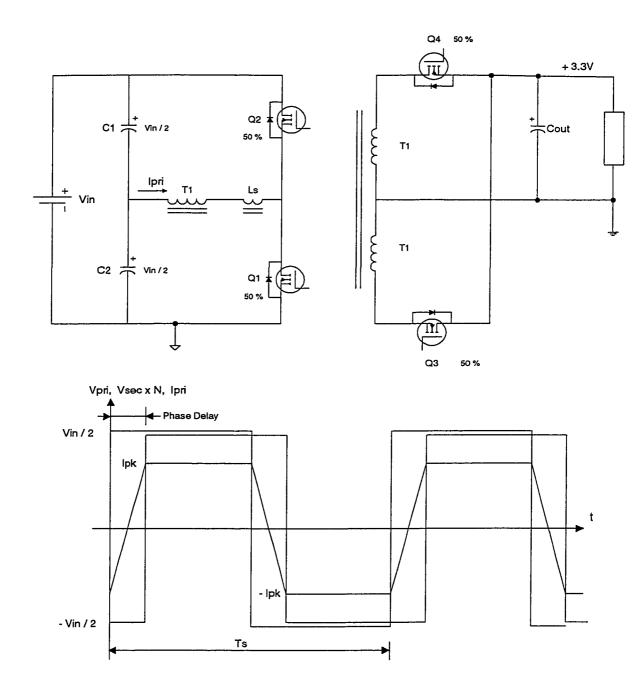

The first three topologies are derived from classical PWM topologies. The dual active bridge is a topology where the primary and secondary switches are externally driven and where the power throughput is a function of the phase shift between the primary and secondary bridges.

As mentioned above, the two conditions which must be met in order to achieve ZVT are:

- 1. Complementary operation.

- Enough magnetic energy must be stored in the transformer on the primary side in order to fully charge/discharge the MOSFET parasitic capacitances.

The maximum output power of the +3.3 V EPC is equal to 50 W. At that power level, it was found that insufficient energy was being stored in the leakage inductance of the transformer in order to guarantee ZVT; therefore, these topologies were modified in order to increase the magnetizing current of the transformer so as to increase the energy stored in the magnetizing inductance.

Referring to the diagrams at the bottom of Figure 2.2, Figure 2.10 and Figure 2.18, the solid line waveform represents the primary current of the modified circuit whereas the dotted line represents the primary current of the original circuit.

As can be seen from the diagrams, the solid lines have a much steeper slope than the corresponding dotted lines, which causes the minimum current  $I_{min}$  to be negative. This negative value of  $I_{min}$  guarantees ZVT of Q1 because it represents the current going initially through its antiparallel diode. It should be noted that ZVT operation of the Flyback converter (Figure 2.18) is impossible without this modification.

The modification of the primary current cannot be implemented on the dual active bridge (Figure 2.1) because in this topology the transformer is being actively driven from both the primary and the secondary sides [10]. Therefore, the voltage across the transformer does not change when Q1 is turned off since it is determined by the conduction status of Q3 and Q4. Therefore, only the leakage inductance (or external series inductance Ls) is available to charge and discharge the MOSFET parasitic capacitances. As a consequence, this converter does not lend itself to handle an output power in the order of 50 W and hence will not be studied any further. The interested reader may refer to [10] for a detailed description of this circuit.

The modification of the primary current described above carries a penalty which is an increase of the RMS value of the primary current, which in turn causes an increase of conduction losses. The impact of these additional conduction losses on the overall EPC efficiency depends on the topology. In the next paragraph, we will calculate for each of the

three topologies under consideration the amount of magnetizing current which must be added to the primary current in order to guarantee ZVT operation.

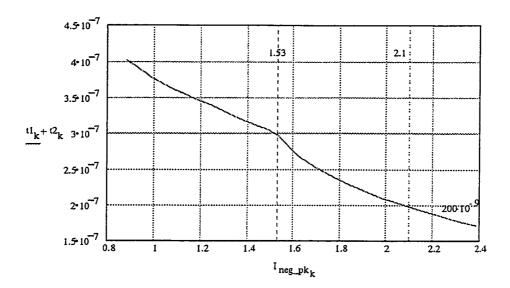

In addition to achieving ZVT, an important parameter to consider is the time it takes to do so, that is the amount of time it takes the combined primary load current and magnetizing current to completely discharge the MOSFET parasitic capacitances. This time interval represents a dead time, i.e. a time during which insufficient or no voltage is applied to the gate of the secondary synchronous rectifier MOSFETs. It is therefore mandatory to minimize this transition time and this can only be done by increasing the primary magnetizing current beyond the value strictly needed to perform ZVT. As explained further in the next paragraph, one of the constraints we will be imposing on the three competing topologies is to perform ZVT in less than 200 ns.

Figure 2.1 Dual active bridge converter

### 2.3 Comparison Criteria

For the three topologies being studied, if we increase the primary magnetizing current in order to guarantee ZVT in each of them, then the turn-on losses become negligible.

It will be shown in Chapter 3 that by properly designing the gate drive circuit, the turn-off losses can be made negligible too. Therefore, the final choice of the topology can only be made after a comparison of conduction losses for topologies No. 1, No. 2 and No. 3 is carried out.

This comparison of conduction losses for all three topologies will be made based on the following operating conditions and constraints:

Input voltage : 100 V

Output power: 50 W

For all three topologies, the secondary winding of the transformer is assumed to have the same resistance per section, in order to provide a fair basis of comparison. The resistance of the primary winding was taken as the secondary winding resistance multiplied by the square of the turns ratio.

All three topologies use two secondary synchronous rectifiers. (In the Flyback converter, they are connected in parallel). For the active clamp single ended forward converter and for the complementary half bridge converter, the secondary synchronous rectifiers are self driven, i.e. their gate to source voltage is derived from the power transformer secondary winding voltage waveform. For the Flyback converter, the secondary synchronous rectifiers are externally driven. For all three topologies, the synchronous rectifiers used are Logic Level MOSFETs FSYC053LD made by HARRIS which are presently under development. The Logic Level MOSFET was chosen because in a self-driven scheme, and due to the low value of the output voltage, insufficient voltage is

developed across the transformer secondary winding to drive a conventional MOSFET. The HARRIS MOSFET was chosen because it is radiation hardened, which is a requirement in most aerospace applications.

The primary MOSFETs used depend on the topology. In the Complementary Half Bridge, the maximum Drain to Source voltage of the primary switches never exceeds the input voltage; since the input voltage does not exceed 110 V, 200 V MOSFETs are used. In the ZVT Flyback converter, it will be shown that the Drain to Source voltage of the primary MOSFETs will not exceed 145 V; therefore, 200 V MOSFETs can also be used. In the active clamp forward converter, the Drain to Source voltage of the primary MOSFETs will be significantly higher than the input voltage; therefore, 400 V MOSFETs are used for this topology.

Although  $V_{in}$  equals 100 V, The power stages of all three topologies were designed to handle input voltage variations ranging from 90 V to 110 V.

For all three topologies, the combined primary load current and magnetizing current must have a value such as to guarantee a ZVT in less than 200 ns.

Having defined all the constraints and criteria, it is now necessary that we undertake a more detailed study of each topology in order to accurately calculate the amount of primary current needed to perform ZVT in less than 200 ns.

## 2.4 The active clamp single ended forward converter

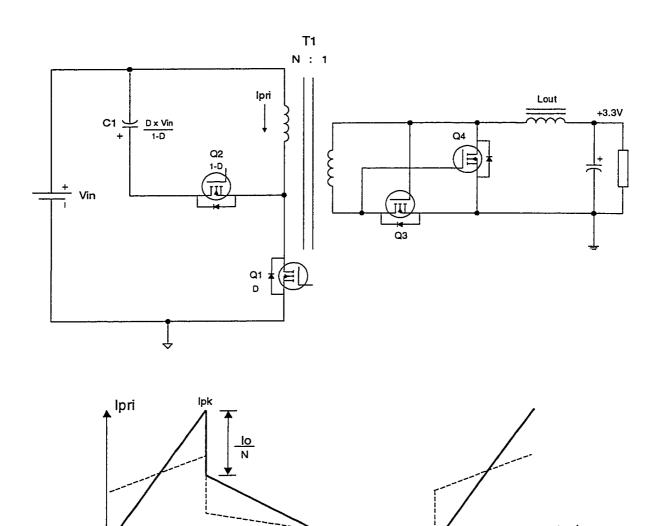

The simplified schematic and the primary current waveform of the active clamp single ended forward converter are shown on Figure 2.2 below. The theory of operation is identical to that of a conventional PWM single ended forward converter with the following modifications, which are covered in detail in [1], [2], [14], [15] and [16]:

When Q1 turns off, the energy stored in the transformer magnetizing and leakage inductances charges the parasitic capacitances of Q1 and discharges the parasitic capacitance of Q2 until the Drain to Source voltage of Q1 is clamped by capacitor C1 through Q2's antiparallel diode. At this time, Q2 is turned ON for the remainder of the switching period whose duration is given by  $(1-D) \times Ts$ . Since the lower end of the transformer primary is now held at a voltage higher than the input voltage, the magnetizing current through the transformer decreases and eventually changes sign.

At the beginning of the next switching period, Q2 is turned OFF. Since the magnetizing current of the transformer is now negative, it starts charging Q2's parasitic capacitance and discharging Q1's parasitic capacitance until Q1's antiparallel diode conducts. At this time, Q1 is turned ON. It should be noted that under those conditions, both Q1 and Q2 experience a Zero Voltage turn-on; for this to occur however, the magnetizing inductance of the transformer must be lower than the one of a conventional forward converter in order to allow the transformer to store energy during the conduction periods of Q1 and Q2; as explained above, this is why the solid line of the current waveform in Figure 2.2 has a steeper slope than the dotted line which corresponds to the current waveform of a conventional converter.

Since the voltage across the switching transformer is either positive or negative but never zero (no dead time), both secondary synchronous rectifiers are always being driven on their gates in a complementary fashion, with the exception of the transition periods where Q1 and Q2's parasitic capacitances are charged and discharged. Moreover, since the gate to source voltage of the synchronous rectifiers is synchronized with their drain to source voltage (the gate to source signal is derived from the transformer secondary winding), the synchronous rectifiers also turn on under zero voltage on their drain.

Before we attempt to calculate the minimum amount of primary current needed to achieve ZVT, it is necessary to perform a rough design of the converter in order to extract the important parameters such as the transformer turns ratio, nominal and worst case duty cycle.

The detailed calculations are performed in Appendix A; the complete characterization of the primary and secondary power MOSFETs used is performed in Appendix B; therefore, only the important steps will be outlined in this chapter.

The voltage across the clamping capacitor C1 is easily calculated by noting that the transformer is always being driven in one direction or the other and must therefore satisfy the volts - microseconds balance.

Therefore,

$$V_{CI} = \frac{D \cdot V_{in}}{1 - D}$$

Figure 2.2 Forward converter with active clamp and self driven synchronous rectifier

(1-D) x Ts

The Drain to Source voltage of Q1 and Q2 is equal to

lmin

D x Ts

$$V_{DS} = V_{in} + V_{CI} = \frac{V_{in}}{I - D}$$

(2.4.1)

lneg\_pk

We pose the constraint that the maximum  $V_{DS}$  across the primary switches never exceeds 300 V (consistent with the use of 400 V devices); let's find the condition where  $V_{DS}$  reaches its maximum value; from the above expression of  $V_{DS}$  given in (2.4.1), we have

$$V_{DS} = \frac{V_{in}}{I - D} = \frac{N \cdot V_{out}}{D \cdot (I - D)}$$

where N is the power transformer turns ratio.

The above expression only depends on the duty cycle (the numerator is constant); from the denominator expression, it can be seen that  $V_{DS}$  reaches a minimum when D=0.5 and increases for values of D higher than 0.5. On the other hand, it is desirable to run the converter at duty cycles higher than 0.5 in order to reduce the output inductor ripple current and hence the output voltage ripple; if the converter always operates above 50 % cycle, then the above expression of  $V_{DS}$  reaches its maximum when D is maximum; this corresponds to  $V_{in}$  being minimum; we know that  $Vin_{min} = 90 \text{ V}$ ; therefore, we readily calculate the maximum duty cycle:

$$D_{max} := I - \frac{Vin_{min}}{300}$$

$$D_{max} = 0.7$$

Let us now calculate the transformer turns ratio N.

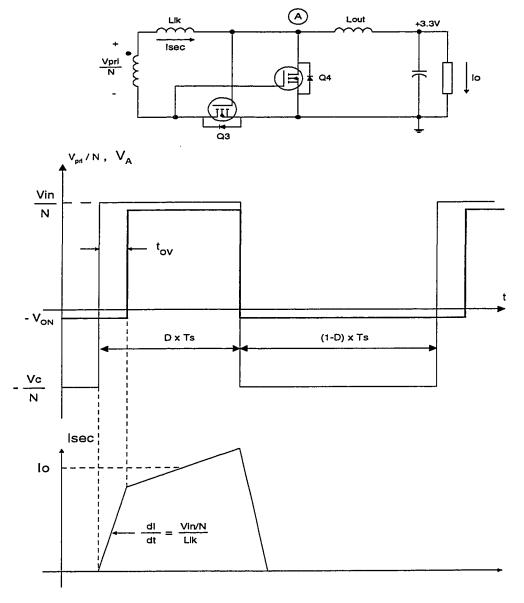

Figure 2.3 below shows the Forward Converter secondary rectifier stage along with the waveforms of the voltage across the transformer secondary, the voltage at point A on the schematic and the secondary current.

Figure 2.3 Forward Converter Secondary Rectifier Stage Showing Effect of Leakage Inductance

As can be seen from Figure 2.3, when the secondary voltage becomes positive, the voltage at point A stays at zero for a period of time  $t_{ov}$  during which the output current is gradually transferred from Q4 to Q3; during this time, both Q3 and Q4 conduct through their antiparallel diodes because  $V_{cs}$  of both Q3 and Q4 are equal to zero. Neglecting the

ripple current through the output inductor and assuming the reverse recovery current of Q4's body-drain diode is negligible, the overlap time is given by

$$t_{OV} = \frac{L_{lk} \cdot I_{O}}{\left(\frac{V_{in}}{N}\right)}$$

(2.4.2)

where  $L_{lk}$  is the leakage inductance value as seen from the secondary.

On the other hand, the time overlap diminishes the converter effective duty cycle; if we call  $V_{on}$  the voltage drop across Q3 or Q4 when they conduct, the expression of the output voltage is given by

$$V_{out} = \frac{V_{in}}{N} \cdot \frac{D \cdot Ts - t_{ov}}{Ts} - V_{on}$$

(2.4.3)

where Ts is the switching period.

It should be noted that if  $t_{ov}$  is made equal to zero, the above expression reduces to the classical input to output relationship for a forward converter.

Introducing the expression of  $t_{ov}$  given by (2.4.2) in (2.4.3) yields:

$$V_{out} = \frac{V_{in}}{N} \cdot D - L_{lk} \cdot I_o \cdot Fs - V_{on}$$

(2.4.4)

where  $Fs := \frac{1}{Ts}$  is the switching frequency.

From (2.4.4), it can be seen that the leakage inductance introduces an extra term proportional to the switching frequency and to the output current; this effect has been described in detail in [3].

Based on the above considerations, we can now calculate the minimum turns ratio needed to achieve output regulation at minimum input voltage and maximum load  $(I_o = 15 \text{ A})$ :

Assuming that  $L_{lk}$  is equal to 33 nH (measured on a real breadboard with a low profile transformer), and with the value of  $V_{on}$  calculated in Appendix A, we obtain

$$N := \frac{D_{max} \cdot Vin_{min}}{V_{out} + V_{on} + L_{lk} \cdot I_{o} \cdot Fs}$$

$$N = 17.331$$

We choose N = 17.

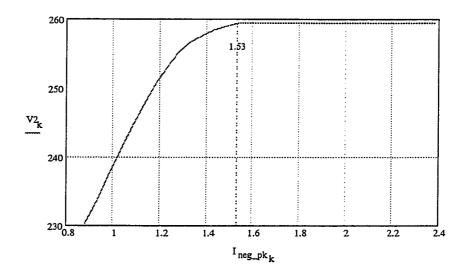

With the above value of N, the maximum and nominal values of  $V_{DS}$  on the primary MOSFETs corresponding respectively to  $V_{in} = Vin_{min} = 90 \text{ V}$  and  $V_{in} = Vin_{nom} = 100 \text{ V}$  are calculated in Appendix A:

$$Vds_{max} = 283.8$$

$$Vds_{nom} = 259.4$$

We must now calculate the maximum magnetizing inductance of the transformer which will guarantee ZVT in less than 200 ns. Referring to the current waveforms shown on Figure 2.2, it should be noted that the current value Ipk (at the end of Q1's conduction period) is higher than the current value Ineg\_pk (at the end of Q2's conduction period); thus, the latter represents the worst case because less energy is stored in the transformer magnetizing inductance to achieve ZVT. Therefore, if we can guarantee that ZVT takes place in less than 200 ns when Q2 is being turned off, then automatically the condition will be met when Q1 is turned off. Therefore, we shall study ZVT on the converter at the turn-off of Q2 only.

In order to do so, it is important to recognize that the parasitic MOSFET capacitances which play an important role in the phenomenon are not constant but rather

are functions of the applied voltage, as explained in paragraph 2.2 above. As a result, the energy exchange phenomena which we will be analyzing are non linear in nature. As explained in [5], the voltage transition takes place in two phases:

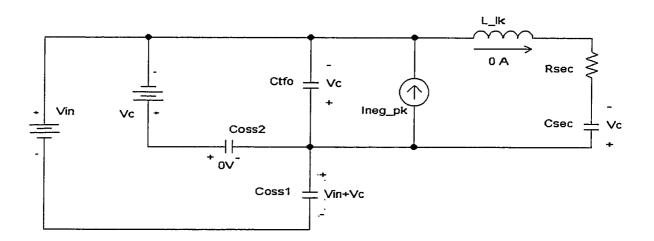

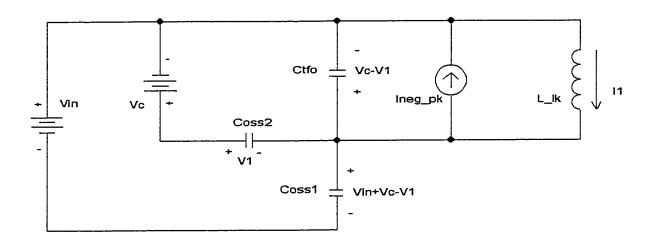

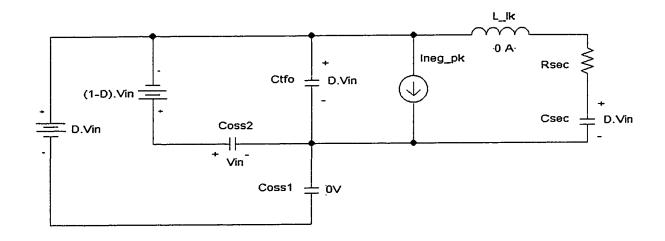

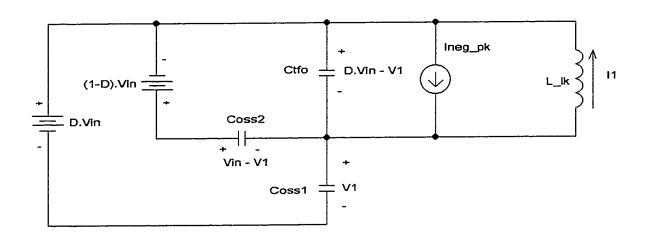

Phase I: A resonant transition takes place between the equivalent primary capacitance, the transformer leakage inductance and the equivalent secondary capacitance. The equivalent primary capacitance is the sum of the primary MOSFETs parasitic capacitances and the transformer capacitance; the equivalent secondary capacitance is the sum of the secondary MOSFETs parasitic capacitances. This phase ends when the voltage across the secondary capacitance reaches zero. At this moment, MOSFET Q3 (see Figure 2.2) starts to conduct through its anti-parallel diode and the secondary current is being gradually transferred from Q4 to Q3. Figure 2.4 below is the equivalent schematic of the forward converter during Phase I. Also represented on Figure 2.4 are the voltages across the capacitances and the current through the leakage inductance at the beginning of the phase.

Figure 2.4 Forward Converter Equivalent Circuit During Phase I

**Phase II**: During this phase, the voltage across the equivalent secondary capacitance is clamped to zero because both secondary synchronous rectifiers are ON and the output

current is being transferred from one synchronous rectifier to the other; this phase consists in a resonance between the equivalent primary capacitance and the transformer leakage inductance. This phase ends when the current through the synchronous rectifier which is being turned off has reduced to zero; in practice however some negative current will flow through the synchronous rectifier being turned off due to the reverse recovery of its antiparallel diode; this means that the overall current excursion is higher than the output current. Figure 2.5 below is the equivalent schematic of the forward converter during Phase II, which also shows the voltages across the capacitances and the current through the leakage inductance at the beginning of the phase.

Figure 2.5 Forward Converter Equivalent Circuit During Phase II

Referring to Figure 2.4, voltage source  $V_c$  represents the clamping capacitor C1 of Figure 1.2. Since the transition will last less than 200 ns (this is one of the conditions we must meet), we can safely neglect the voltage variation across this capacitor during the transition, and therefore the clamping capacitor can be represented by voltage source  $V_c$ . Current source  $I_{neg\_pk}$  represents the primary current at the end of Q2's conduction period: it is the sum of the load current and the magnetizing current stored in the transformer primary magnetizing inductance. Again, we make the assumption that this current remains constant

during the whole transition. Coss2 represents the output capacitance of primary MOSFET Q2 and is completely discharged at the beginning of Phase I, which corresponds to the instant Q2 is being turned off; Coss1 represents the output capacitance of Q1 and is charged at  $V_{in} + V_c$  at the beginning of Phase I;  $C_{tfo}$  represents the transformer parasitic capacitance and is charged to  $V_c$ .  $C_{sec}$  is the overall capacitance of the secondary MOSFETs, reflected to the primary side of the transformer; at the beginning of Phase I, it is also charged to  $V_c$ . Rsec represents the gate resistance of the secondary MOSFETs, reflected to the primary side.

Although the MOSFET parasitic capacitances are non linear and can only be represented by an equation such as (2.2.1), the resonant transition of Phase I involves too many elements and its description by non linear capacitances would make the calculations too complex. Rather, a good approximation is obtained by averaging expression (2.2.1) over the voltage range covered by each of the identified capacitances during Phase I.

Referring to Figure 2.2, when Q2 is turned off, Q3 is OFF and Q4 is ON. Therefore, the secondary capacitance consists of Q4's input capacitance (constant), in parallel with Q3's output capacitance, whose value is averaged from zero to  $V_c / N$ . Referring to Appendix A, the averaged value of Q3's output capacitance is given by

$$Coss_{OFF} = \frac{1}{\left(\frac{V_c}{N}\right)} \cdot \int_{0}^{\frac{V_c}{N}} Coss_{sec}(V) dV$$

(A.4)

The overall secondary capacitance as seen from the primary of the transformer is given by

$$C_{sec} = \frac{Ciss_{ON} + Coss_{OFF}}{N^2}$$

(A.5)

where Cisson represents Q4's input capacitance, Cossoff represents the average value of Q3's output capacitance and N is the transformer turns ratio.

From Figure 2.2 again, the primary capacitance consists of the parallel combination of Q1's output capacitance, Q2's output capacitance and the transformer's capacitance; while the latter is constant, Q1 and Q2's output capacitances must be averaged over their respective voltage ranges. The overall primary capacitance is given by

$$C_{pri} = \frac{1}{V_{c} \cdot M_{ov}} \cdot \left| \int_{0}^{V_{c} \cdot M_{ov}} Coss(V) dV + \int_{V_{in} + V_{c} - V_{c} \cdot M_{ov}}^{V_{in} + V_{c}} Coss(V) dV \right| + C_{tfo}$$

(A.6)

where  $M_{ov}$  is a correction factor which accounts for the fact that the primary voltage actually extends beyond  $V_c$  during Phase I.

The analytical expressions of the current through the leakage inductance, the voltage across the secondary capacitance and the voltage across the primary capacitance (the latter being defined as the voltage across  $C_{tfo}$  as shown on Figure 2.4) have been calculated in Appendix A and are given by

$$I_{L,lk}(I_{neg\_pk},t) = \frac{I_{neg\_pk} \cdot C_{sec}}{C_{pri} + C_{sec}} \cdot \left[ 1 - exp\left(-\frac{R_{sec}}{2 \cdot L_{lk}} \cdot t\right) \cdot \left(\frac{sin(\omega_I \cdot t)}{\sqrt{4 \cdot Q^2 - 1}} + cos(\omega_I \cdot t)\right) \right]$$

(A.8)

$$V_{Csec}(I_{neg\_pk},t) = -V_{C} - \frac{I_{neg\_pk} \cdot C_{pri} \cdot C_{sec}}{\left(C_{pri} + C_{sec}\right)^{2}} \cdot R_{sec} + \frac{I_{neg\_pk}}{C_{pri} + C_{sec}} \cdot t \dots + exp\left(-\frac{R_{sec}}{2 \cdot L_{lk}} \cdot t\right) \cdot \left[\frac{sin(\omega_{I} \cdot t)}{\sqrt{4 \cdot Q^{2} - 1}} \cdot \frac{I}{\omega_{o}} \cdot \left(\frac{I}{Q} - 2 \cdot Q\right) + \frac{cos(\omega_{I} \cdot t)}{\omega_{o} \cdot Q}\right] \cdot \frac{I_{neg\_pk}}{C_{pri} + C_{sec}}$$

(A.9)

$$V_{Cpri}(I_{neg\_pk},t) = -V_{C} + \frac{I_{neg\_pk}}{C_{pri} + C_{sec}} \cdot t \dots + I_{neg\_pk} \left( \frac{C_{sec}}{C_{sec} + C_{pri}} \right)^{2} \cdot R_{sec} \cdot \left( I - exp \left( \frac{R_{sec}}{2 \cdot L_{lk}} \right) \cdot cos(\omega_{I} \cdot t) + \frac{2 \cdot Q^{2} - 1}{\sqrt{4 \cdot Q^{2} - 1}} \cdot exp \left( \frac{R_{sec}}{2 \cdot L_{lk}} \right) \cdot sin(\omega_{I} \cdot t) \right)$$

$$(A.10)$$

where  $\omega_o$ ,  $\omega_l$  and Q are defined in Appendix A.  $R_{sec}$  is the secondary MOSFET gate resistance reflected to the primary side and is also calculated in Appendix A. As can be seen from the above expressions,  $I_{Llk}$ ,  $V_{Csec}$  and  $V_{Cpri}$  are functions of time and of  $I_{neg\_pk}$ , the latter being the primary current at the moment Q2 is being turned off, as shown in Figure 2.4 and in Figure 2.5. As explained above, Phase I ends when the secondary capacitance is completely discharged, and from there on, the secondary voltage is clamped to zero because both Q3 and Q4 are conducting through their anti-parallel diodes.

Therefore, the time tI which corresponds to the end of Phase I is obtained by making Equation (A.9) above equal to zero:

$$V_{Csec}(I_{neg\_pk}, t) = 0$$

Solving the above equation for t yields the time tl we are looking for. We are now in a position to calculate the current through the leakage inductance and the voltage across the primary capacitance at the end of Phase I by making t = tl in (A.8) and (A.10) above, we obtain:

$$V_{Cpri}$$

at end of Phase I =  $V_{Cpri}(I_{neg\_pk}, tI)$

$I_{L.lk}$  at end of Phase I =  $I_{L.lk}(I_{neg\_pk}, tI)$  (Called II on Figure 2.5)

The above values are the initial conditions for Phase II. To simplify the subsequent analysis, it is convenient to define VI as the voltage variation across the primary capacitance during Phase I. From Figure 2.4, the initial value of  $V_{Cpri}$  (across  $C_{tfo}$ ) equals  $-V_c$ . From

Figure 2.5, the final value of  $V_{Cpri}$  (at the end of Phase I) equals  $-V_c + VI$ . Since the final value of  $V_{Cpri}$  was calculated above, we have

$$VI - V_c = V_{Cpri}(I_{neg\_pk}, tI)$$

or  $VI = V_{Cpri}(I_{neg\_pk}, tI) + V_c$

As can be seen from Figure 2.5, VI also represents the voltage variation across Coss1 and Coss2 during Phase I.

Having calculated all the initial conditions, we are now ready to study Phase II.

Referring to Figure 2.5, Phase II ends when one of the two following conditions occurs:

- 1. The voltage across *Coss*1 reduces to zero in which case the Zero Voltage Transition is over.

- 2. The current through the leakage inductance  $L_{lk}$  reaches  $I_{neg\_pk}$ ; in this case, the net current flowing from the primary capacitance reduces to zero, which means that the primary capacitance cannot be discharged any further; this occurs when the value of  $I_{neg\_pk}$  is insufficient to ensure a complete ZVT.

For the subsequent analysis, it is convenient to call V2 the total voltage variation (Phase I + Phase II) across the primary capacitance. Having called VI the voltage variation across the primary capacitance during Phase I, the voltage variation during Phase II simply equals V2 - VI.

At the end of Phase II, the voltages across the different components of the primary capacitance are the following:

Across Coss1  $V_{in} + V_c - V2$

Across Coss2 V2

Across  $C_{tfo}$   $V2 - V_c$ .

Since our goal is to achieve ZVT, we look for a complete discharge of Coss1, hence,

$$V_{in} + V_c - V2 = 0$$

We called tI the duration of Phase I. Likewise, let's call t2 the duration of Phase II. One additional constraint we have imposed on the transition is that: tI + t2 < 200 ns.

Since we deal with the discharge of non-linear capacitors, the best way to analyze Phase II is by writing the energy balance at the beginning and at the end of Phase II.

Let's define the following variables:

EI = total energy stored in the reactive elements at the end of Phase I (At t = tI)

E2 = total energy stored in the reactive elements at the end of Phase II (At t = tl + t2)

II =current through  $L_{lk}$  at the end of Phase I.

$I2 = \text{current through } L_{lk} \text{ at the end of Phase II.}$

$$\Delta I = I2 - I1$$

$I_{Lpri} = I_{neg\_pk}$  - II: this is the net current available at the beginning of Phase II to discharge the primary capacitance.

$E_{Coss}(V)$  = energy stored in a MOSFET output capacitance when the voltage across this output capacitance is equal to V.

From inspection of Figure 2.5, we have

$$EI = E_{Coss}(VI) + E_{Coss}(V_{in} + V_c - VI) + \frac{1}{2} \cdot C_{tfo} \cdot (VI - V_c)^2 + \frac{1}{2} \cdot L_{lk} \cdot II^2$$

(2.4.5)

$$E2 = E_{Coss}(V2) + E_{Coss}(V_{in} + V_{c} - V2) + \frac{1}{2} \cdot C_{tfo} \cdot (V2 - V_{c})^{2} + \frac{1}{2} \cdot L_{lk} \cdot I2^{2}$$

(2.4.6)

Subtracting (2.4.5) from (2.4.6), we obtain

$$E2 - EI = E_{Coss}(V2) - E_{Coss}(VI) + E_{Coss}(V_{in} + V_{c} - V2) - E_{Coss}(V_{in} + V_{c} - VI) ... + \frac{1}{2} \cdot C_{tfo} \cdot \left[ (V2 - V_{c})^{2} - (VI - V_{c})^{2} \right] + \frac{1}{2} \cdot L_{lk} \cdot (I2^{2} - II^{2})$$

$$(2.4.7)$$

Applying the same principle as the one which lead to equations (2.2.2) and (2.2.3), we obtain

$$E_{Coss}(V2) - E_{Coss}(VI) = \int_{VI}^{V2} Coss(V) \cdot V \, dV$$

Therefore, (2.4.7) can be rewritten as