INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the

text directly from the original or copy submitted. Thus, some thesis and

dissertation copies are in typewriter face, while others may be from any type of

computer printer.

The quality of this reproduction is dependent upon the quality of the copy

submitted. Broken or indistinct print, colored or poor quality illustrations and

photographs, print bleedthrough, substandard margins, and improper alignment

can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and

there are missing pages, these will be noted. Also, if unauthorized copyright

material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning

the original, beginning at the upper left-hand corner and continuing from left to

right in equal sections with small overlaps. Each original is also photographed in

one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white photographic

prints are available for any photographs or illustrations appearing in this copy for

an additional charge. Contact UMI directly to order.

UMI<sup>®</sup>

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# ARCHITECTURAL SUPPORT FOR MASSIVELY-CONCURRENT PARALLEL COMPUTING

JAYA NARAIN

A THESIS

IN

THE DEPARTMENT

OF

COMPUTER SCIENCE

PRESENTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF MASTER OF COMPUTER SCIENCE

CONCORDIA UNIVERSITY

MONTRÉAL, QUÉBEC, CANADA

June 1998 © Jaya Narain, 1998

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-39489-1

## Abstract

## Architectural Support for Massively-Concurrent Parallel Computing

### Jaya Narain

Parallel computing is an intricate mix of marketplace requirements, architectural understanding, technology issues, and issues concerning costs. One controlling myth is that high-volume commodity processors must, by the nature of things, be the common building blocks for both desktop clients and room-size servers. This myth—and the supporting myth of architectural convergence of clients and servers—should be subject to dispassionate analysis.

With only one program counter per processor, conventional processors are becoming increasingly unresponsive in spite of faster clock rates. We will show that reliance on Instruction-Level Parallelism (ILP) for performance drives processor state upwards. When this massive state is not distributed across multiple program counters, processors choke on their own expensive context switches, here reconceptualized to show their true cost.

Within the framework of Little's law from queueing theory, we analyze conventional RISC superscalar processors as a case study of the inadequacy of the class of "ILP" processors. We contrast this to multithreaded processors that exploit both ILP and Thread-Level Parallelism (TLP).

As a contribution to parallel programming, we show how data caches in multithreaded architectures can be used to manage speculative state, and perform atomic updates involving multiple variables.

There is no "convergence architecture"; there are only divergence architectures.

## Acknowledgments

Thank you Dr. David Probst for being my friend and guru! Without your excellent supervision, intellectual drive, continuous motivation, patience and financial support, this work would not have been realised so effectively in just 12 months.

I am grateful to the other members of the thesis committee, Drs. R. Jayakumar, H.F Li and Peter Grogono, for their valuable suggestions and reading my thesis in limited time. Dr. Li was, throughout, a virtual sounding board on architectural issues, and a feedback control on excessive religious zeal! I owe a particular debt of gratitude to Dr. Li and Dr. Probst for their generosity in extending financial support to me when I really needed it. My thanks to the Department of Computer Science for awarding me Teaching Fellowships and to the School of Graduate Awards for a partial tuition waiver.

My thanks to all faculty members, the System Analysts Pool and the secretaries for providing an environment congenial to academic research with fewer frustrations. Many thanks to Guy Dumais for answering all my *LATEX* questions, to Rachit, Manolo, Bhaskar, Sriram, Venkat, Jennifer, Manu, Rajat, Shilpee, Vinu and Manish who have provided priceless friendships and made my life in Montreal fun and exciting. I am particularly grateful to Krishna for his magnanimity. I cannot thank enough Ganesh (often my greatest critic!) for being an unfailing friend and standing by me, no matter what.

I am eternally indebted to my parents, my family and my relatives for their love and intellectual motivation. I adore my father for his countless sacrifices and constant struggle to provide me with the best education. I thank my little nephews, the desire to see whom has hastened the completion of this thesis.

# Contents

| Lis | t of | Figur   | es                                                     | vii  |

|-----|------|---------|--------------------------------------------------------|------|

| Lis | t of | Table   | s ·                                                    | viii |

| 1   | Intr | oducti  | ion                                                    | 1    |

|     | 1.1  | Motiv   | ation: The crisis in high-end computing                | 1    |

|     |      | 1.1.1   | Why the crisis is real                                 | 5    |

|     | 1.2  | Little' | s law                                                  | 7    |

|     |      | 1.2.1   | Two ways to go                                         | 7    |

|     | 1.3  | Contri  | ibutions of this thesis                                | 8    |

| 2   | Sup  | erscal  | ar Architectures                                       | 11   |

|     | 2.1  | Cache   | s                                                      | 12   |

|     | 2.2  | Supers  | scalar techniques to implement and exploit concurrency | 15   |

|     |      | 2.2.1   | Historical perspective                                 | 15   |

|     |      | 2.2.2   | Model of a superscalar processor                       | 16   |

|     |      | 2.2.3   | Instruction fetching and branch prediction             | 19   |

|     |      | 2.2.4   | Instruction decoding, renaming, and dispatch           | 21   |

|     |      | 2.2.5   | Instruction issuing and parallel execution             | 24   |

|     |      | 2.2.6   | Handling memory operations                             | 25   |

|     |      | 2.2.7   | Committing or retiring instructions                    | 26   |

|     | 2.3  | Out-o   | f-order issue/execution of instructions                | 26   |

|     | 2.4  | Specul  | lative Execution                                       | 28   |

|     | 25   | Summ    | eary of the disadvantages of superscalar machines      | 30   |

| 3 | Mu  | ltithre                                                    | ading                                                                                                                             | 31                               |

|---|-----|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|   | 3.1 | Early                                                      | multithreading                                                                                                                    | 36                               |

|   |     | 3.1.1                                                      | Coarse-grained or blocked multithreading                                                                                          | 37                               |

|   |     | 3.1.2                                                      | Fine-grained or switch-on-every-cycle multithreading                                                                              | 39                               |

|   |     |                                                            | 3.1.2.1 Fine-grained multithreading with full single-thread sup-                                                                  |                                  |

|   |     |                                                            | port and caching                                                                                                                  | 39                               |

|   |     |                                                            | 3.1.2.2 Fine-grained multithreading without caches                                                                                | 41                               |

|   | 3.2 | Simul                                                      | taneous multithreading                                                                                                            | 42                               |

|   |     | 3.2.1                                                      | Simultaneous multithreading with heavyweight threads (SMT1)                                                                       | 43                               |

|   |     | 3.2.2                                                      | Simultaneous multithreading with lightweight threads (SMT2)                                                                       | 46                               |

|   |     |                                                            | 3.2.2.1 Architectural overview of SMT2                                                                                            | 46                               |

|   |     | 3.2.3                                                      | Qualitative and Quantitative Comparisons between SMT1 and                                                                         |                                  |

|   |     |                                                            | SMT2                                                                                                                              | 49                               |

| 4 | Sha | red Re                                                     | esponsibility for Parallellism                                                                                                    | 53                               |

|   | 4.1 | 1.                                                         | to December 11 December 14 and                                                                                                    | 55                               |

|   |     | Explic                                                     | cit Programmer Control Decomposition                                                                                              | 99                               |

|   |     | 4.1.1                                                      | The CC++ Programming Model (Explicit Control Constructs)                                                                          | 55                               |

|   |     | -                                                          | •                                                                                                                                 |                                  |

|   |     | 4.1.1                                                      | The CC++ Programming Model (Explicit Control Constructs)                                                                          |                                  |

|   |     | 4.1.1                                                      | The CC++ Programming Model (Explicit Control Constructs) The OpenMP Programming Model (Control Constructs as Com-                 | 55                               |

|   | 4.2 | 4.1.1<br>4.1.2<br>4.1.3                                    | The CC++ Programming Model (Explicit Control Constructs) The OpenMP Programming Model (Control Constructs as Compiler Directives) | 55<br>60                         |

|   | 4.2 | 4.1.1<br>4.1.2<br>4.1.3                                    | The CC++ Programming Model (Explicit Control Constructs) The OpenMP Programming Model (Control Constructs as Compiler Directives) | 55<br>60<br>65                   |

|   | 4.2 | 4.1.1<br>4.1.2<br>4.1.3<br>Exam                            | The CC++ Programming Model (Explicit Control Constructs) The OpenMP Programming Model (Control Constructs as Compiler Directives) | 55<br>60<br>65<br>68             |

|   | 4.2 | 4.1.1<br>4.1.2<br>4.1.3<br>Exam<br>4.2.1<br>4.2.2          | The CC++ Programming Model (Explicit Control Constructs) The OpenMP Programming Model (Control Constructs as Compiler Directives) | 55<br>60<br>65<br>68<br>69<br>75 |

| 5 | 4.3 | 4.1.1<br>4.1.2<br>4.1.3<br>Exam<br>4.2.1<br>4.2.2<br>Wait- | The CC++ Programming Model (Explicit Control Constructs) The OpenMP Programming Model (Control Constructs as Compiler Directives) | 55<br>60<br>65<br>68             |

# List of Figures

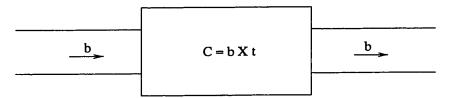

| 1.1 | Little's law says: concurrency equals bandwidth times latency            | 7         |

|-----|--------------------------------------------------------------------------|-----------|

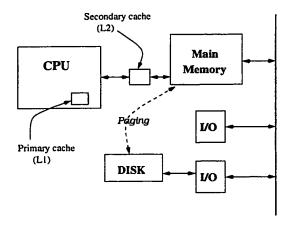

| 2.1 | Memory hierarchy with primary $(L_1)$ and secondary $(L_2)$ caches       | 13        |

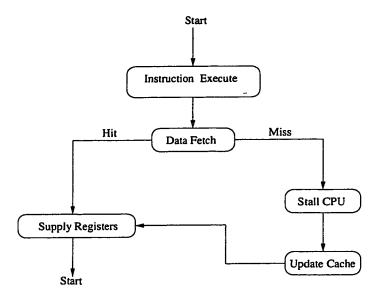

| 2.2 | Flow Diagram of Lockup or Blocking Cache                                 | 13        |

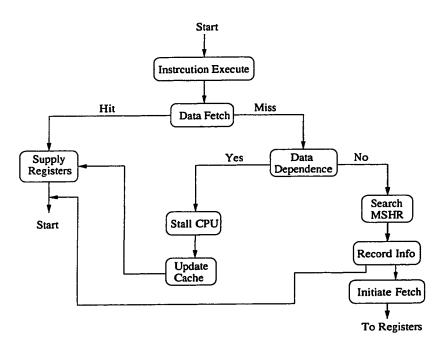

| 2.3 | Flow Diagram of a Lockup-free or Nonblocking Cache                       | 14        |

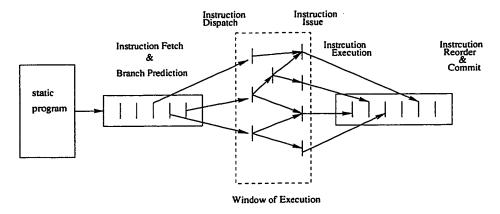

| 2.4 | Stages of parallel processing in a superscalar execution                 | 17        |

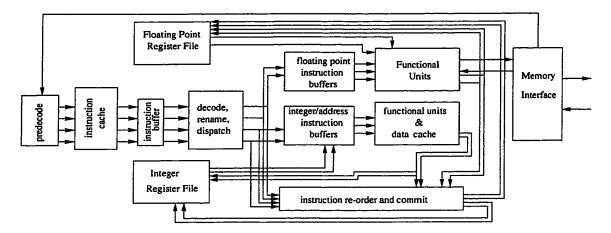

| 2.5 | Organization of a Superscalar Processor                                  | 18        |

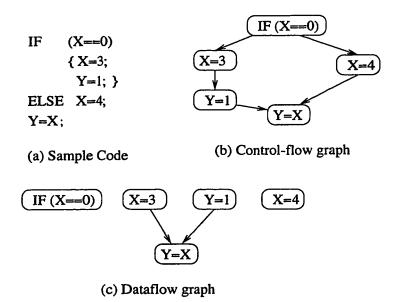

| 2.6 | A Sample Program with corresponding Control-flow and Dataflow Graphs     | . 23      |

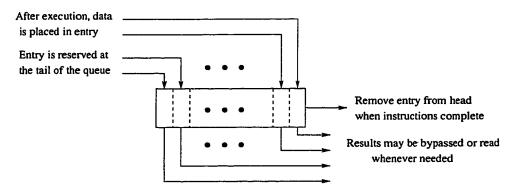

| 2.7 | A reorder buffer                                                         | 28        |

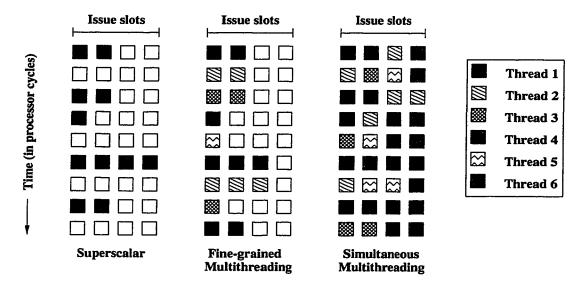

| 3.1 | Comparison of issue slot partitioning in various architectures           | 44        |

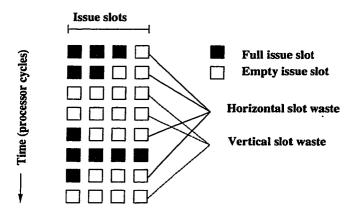

| 3.2 | Empty issue slots as vertical or horizontal wastes                       | <b>45</b> |

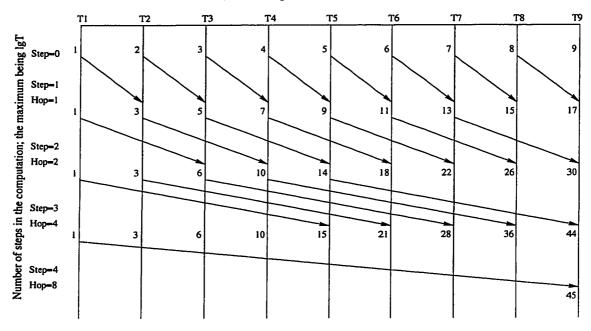

| 4.1 | An example of cyclic reduction using 9 threads to compute the sum of     |           |

|     | the first 9 array elements starting from 1. The maximum number of        |           |

|     | steps is $\lceil log_2 9 \rceil$                                         | 74        |

| 4.2 | Thread 1's transaction on variables a and b                              | 80        |

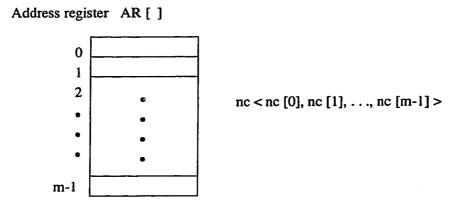

| 4.3 | Thread 2's transaction on variables $b$ and $c$                          | 81        |

| 4.4 | The simple address register $AR[\ ]$ required to increment the multiword |           |

|     | sync variable $nc$                                                       | 82        |

# List of Tables

# Chapter 1

## Introduction

"There is nothing more difficult to take in hand, more perilous to conduct, or more uncertain in its success, than to take the lead in the introduction of a new order of things."

- Niccolo Machiavelli, The Prince (1532)

Today, high-end computing is at a crossroads. We offer a possible scenario as to how we arrived at this crisis. The thesis itself provides increased architectural understanding of a proposed solution to this crisis in the time frame of the next five years. In a word, we explain why multiple program counters matter: they are the prequisites for the massive concurrency required to run a new class of large-scale irregular problems.

## 1.1 Motivation: The crisis in high-end computing

The traditional design space of parallel computers is fairly well agreed on. In grouping processors together, one chooses weak or powerful processors, and one chooses few or thousands of processors. Few, powerful processors is the world of conventional mainframes and supercomputers. Thousands of weak processors is the world of the traditional massively parallel processors. The former are costly, with limited scalability, while the latter are often special-purpose machines. Designers have looked for

a "sweet spot" in this design space by designing parallel computers with hundreds (rather than thousands) of rather more powerful uniprocessors, or tightly-coupled SMP clusters as the basic repeatable computer engine. While we cannot address all the issues in this design space, we can refer to some trends that will help situate the problem of this thesis, and its proposed solution.

Five years ago, there was little talk of the "end of architecture", and little sense of a crisis in high-end computing. Some users had migrated to symmetric multiprocessors (SMPs) because they had modest performance needs. They benefited from the standard programming model (i.e., performance model). The performance of an application on a true SMP is independent of data layout. And this has enormous benefits for programming, for the availability of independent software vendor (ISV) applications software, etc. The problem with SMPs is that the computer industry has no way to scale them to higher and higher number of processors without losing memory uniformity, and hence the desirable programming model.

If SMPs are not enough, then—always in the view of the computer industry—we are left with two¹ alternative architectures that might possibly permit high-end computation. The first architecture is that of parallel vector processors like the Cray T90 and the NEC SX-4. A significant portion of the technical community has grown dependent on vector processors, and is loath to give them up. There are problems, however. First, for economic reasons, vector vendors cannot afford—aside from the Japanese manufacturers of course—to invest the R&D money necessary to design follow-on generations. Hence, users are either deserting vector processors for mid-range machines with better price/performance, or are very, very unhappy at the unavailability of new generations of vector machines. They may certainly buy Japanese machines, however, when this is permitted by law.

Why is it difficult for vector users to switch? Simply because legacy vector codes do not port to other parallel architectures without profound reprogramming, which is often prohibitively expensive. Also, vector processors have trouble attracting new user communities because many of the new application programs—coming from commercial users or sophisticated technical users with modern simulation and visualization codes—do not match well with vector strengths. These applications have short vector

<sup>&</sup>lt;sup>1</sup>We could also mention message-passing multicomputers, which forsake shared memory altogether, but multicomputers are outside the scope of this thesis. Although much work has been done on them, they are not the royal road to general-purpose parallel computing.

or even scalar arithmetic, frequent conditional branches, etc., which do not perform well on vector machines.

The crisis in high-end computing started with the realization that SMP multiprocessors and vector machines were together inadequate to meet the needs of several important user communities. The most prominent of these are: weather-prediction agencies, automobile and aircraft manufacturers, the Pentagon, the DoD's High-Performance Computing and Modernization Office (HPCMO), and the intelligence community (e.g., the standard three-letter agencies).

Vector processors and SMPs provide complementary approaches to supporting parallelism. Vector processors exploit parallelism in inner loops, and use a very fast, very expensive, memory system. Ironically, parallel vector processors do not scale because of memory contention at memory banks. Commodity processors exploit parallelism by aggressive attempts to expose instruction-level parallelism (ILP), and avoid latency by heavy reliance on data caches—so as to require less parallelism. As clock rates scale, vector lengths must become longer, and caches must become larger and hierarchical. The result is that such machines support an increasingly smaller fraction of application programs. Cray Research could not scale the Triton: as processors beyond 32 were added, it became impossible to sustain flat memory. Essentially, Cray did not spend enough money on its interconnection network. The inadequate bandwidth impeded scalability because of memory contention. Both vector processors and SMPs are predicated on flat memories, and cannot reconcile high processor count and flatness. Because there appeared to be no alternative, computer vendors turned to the idea of grouping together large numbers of "commodity" processors into parallel computers.

The second basic architectural alternative for high-end computing in 1998 might as well be called massively parallel processing (MPP). The idea is to take large numbers of scalar processors that are produced in great volumes by Intel, MIPS Co., Sun Microsystems Inc., etc., and to group them together into larger and larger multiprocessors—conceivably with as many as 10,000 or 20,000 CPUs. The computer industry of the MPP flavor is reconciled to nonuniform shared memory, which abandons the SMP programming model, but tries to find a middle ground by building reasonably large SMP clusters, and then going out to a more loosely-coupled interconnect as the computation outgrows its SMP node. Hence, the trend now is to back off from uniform shared memory, and to pay for scalability with nonuniform shared

memory as a programming/performance model. These attempts are called scalable parallel systems (e.g., the IBM SP), massively parallel systems (e.g., ASCI Red), or cluster computers (e.g., the SGI/Cray Origin2000). Nonuniform shared memory results in reprogramming, and extensive retuning to minimize communication cost and enhance cache effectiveness.

With the exception of Intel processors, most commodity processors are conventional Reduced Instruction Set Computing (RISC) superscalar designs. These designs share the design decision that there should be one program counter per processor. The problem is that the limited ILP budget must be spent on both high superscalar issue rate and sustained feeding of multiple function units. The solution as understood was in finding many parallel operations by developing sophisticated approaches to mining individual threads for ILP. Also, aggressive branch prediction was a standard technique to increase ILP by creating larger and larger basic blocks.

Nonetheless, the RISC processors in MPPs suffered from latency disease except for easy cases such as applications where either working sets could be held in the cache, or data-access patterns were regular and predictable. Increasing memory nonuniformity in cache-coherent non-uniform memory architecture (CC-NUMA) machines produced an unfortunate coupling between control and data decomposition. One important question is, is it possible to retain the basic design decisions of conventional RISC superscalar processors and extract enough parallelism to overcome latency disease? We think the answer is no. We believe that there are fundamental limits to ILP. ILP needs to be supplemented by other forms of parallelism. We have spent considerable time in this thesis, analysing the consequences of single-program-counter design. We show that as one attempts to extract more ILP, threads become heavyweight, making it impossible to benefit from thread-level parallalism (TLP). Since ILP is limited, so is sustained performance of multiprocessors whose only source of processor concurrency is ILP.

Our abstract goal is to increase the degree of processor-operation concurrency. Cache-based systems rely on massive data locality. RISC superscalar designs and Merced rely on out-of-order execution permitted by ILP. The problem is that ILP is limited. Vector processors rely on long vectors and massive vectorization. Only multithreading allows us to find concurrency in both ILP and TLP. Although we do not discuss Merced, which uses an alternative to speculative branch prediction to get more ILP, and which moves out-of-order control from the hardware to the compiler,

there are reasons to believe that, because it depends on ILP alone for parallelism, it too has no fundamental solution to providing massive concurrency of processor operations. We leave to future work the demonstration that Merced is intrinsically unable to profit from TLP, albeit for very different reasons than the ones that make RISC processors unscalable and unable to tolerate latency. Another problem for future work would be to point out that parallel computers built from Merced suffer the low processor utilization of their RISC based cousins.

## 1.1.1 Why the crisis is real

The crisis in high-end computing is real because major (e.g., mission-critical) software applications (e.g., structural-analysis simulations) do not scale on existing parallel computers. Urgent large problems exist that do not run well on any existing parallel machine. Many experts believe that large applications with irregular, dynamically changing grids or poor data locality due to algorithmic constraints will not scale on any of today's highly parallel systems.

The difficult larger applications that require the reinvention of computer architecture can be characterized as follows:

- 1. They require large amounts of time and memory, and produce large amounts of output.

- 2. Data is organized using irregular meshes rather than simple arrays or grids.

- 3. Memory accesses exhibit very little spatial and temporal locality.

- 4. The shape of the problem changes as the computation proceeds.

Thus, while there are many applications that do run well on existing parallel computers, there is a growing class of large problems with novel computational attributes that cannot be solved efficiently unless we succeed in implementing programmable, scalable, general-purpose parallel computers. In this thesis, we explore how massive concurrency is the key to successful implementation of such computers.

Until net-centric computing takes over completely—and perhaps even after then—there are powerful, significant user communities who desperately need massive computing engines. Some customers can, of course, design or buy special-purpose parallel

computers. But, if the parallel computing industry is to survive, then market share must grow, and this means that someone has to design, implement, and sell

- easily programmable,

- general-purpose parallel computers (which we may call, servers),

- with multiteraflops (or whatever) performance.

This is our problem domain. The solutions are often guided by some myths that are widely shared:

- Myth 1: There is no way to build a parallel computer unless you use high-volume commodity processors. Competing approaches are doomed to failure for reasons of economies of scale. Clients and servers should use the same processors.

- Myth 2: Nowadays, there are no significant architectural differences between one multiprocessor and another. SMPs and CC-NUMA DSM machines have identical cache-coherence protocols. Shared-memory machines are moving to a universal "convergence architecture." If you really need message passing, we'll add it for you! Etc.

These myths are a recipe for stagnation. But, reality is sinking in slowly. In general, the hardware prerequisites for scalable, parallel servers are:

- scalable bisection bandwidth (which is an interconnection problem),

- scalable latency tolerance (which is a processor problem),

- fine-grained synchronization facilities (which is a processor/memory problem).

Roughly, processors must request and receive data constantly in order to compute. High bisection bandwidth in a multiprocessor allows all processors to do this. Scalable latency tolerance is essential to keep processor utilization high. And, finally, fine-grained synchronization is required to support fine-grained parallelism. All this is intimately related to architectural support for massive concurrency. We do agree though, that not all machines must have these properties; some machines must have these properties. Customers will, for example, buy low- or high-bandwidth machines depending on their needs.

## 1.2 Little's law

Elementary queueing theory places easily understood limits on any architecture that supports massive concurrency. Little's law says that,

$$C = b \times t$$

where C is concurrency, b is the bandwidth (desired machine performance) and t is the latency of processor operations, where we have taken averages everywhere. This means, for example, that if a processor accepts b operands and delivers b floating-point results per cycle, and if the average flop latency is t cycles, then the number of concurrent flops in progress during each cycle must be at least  $C = b \times t$ .

Figure 1.1: Little's law says: concurrency equals bandwidth times latency

Suppose, for example, that we have a processor that is required to sustain  $10^{15}$  operations per second. Suppose also, that the average processor-operation is  $10^{-9}$  second. An inevitable consequence is that the processor must have  $10^6$  operations in progress at all times to sustain this bandwidth (that is performance) in the face of this latency. Concurrency hence implies and becomes a shorthand for "has large number of operations in progress at all times." We also see that to achieve a petaflops ( $10^{15}$ ) per second performance we will require memory-reference concurrency of up to a billion outstanding memory references, and up to ten million concurrently executing threads assuming 100 outstanding operations per thread per cycle. We believe that it is possible that superscalar processors are incapable in principle of supporting the large number of real or virtual threads that are required for massively-concurrent parallel computing. The question is how do we generate this massive concurrency?

## 1.2.1 Two ways to go

There are essentially two alternatives that hope to provide massive concurrency:

- having a single program counter per processor or,

- having multiple (100) program counters per processor.

Our study and analysis in Chapters 2 and 3, proposes that the use of multiple program counters per processor provides support for massive concurrency by sharing the enormous processor state among those multiple program counters (see Section-3.2.3).

## 1.3 Contributions of this thesis

The major contribution is analytical: we explain why certain architectural distinctions matter, and why. Although we do make some architectural proposals, our real work has been to compose in a *new way* two well-known architectural families: RISC processors and multithreaded processors. Specifically,

- 1. we explain why conventional RISC superscalar processors do not provide architectural support for massive concurrency (see Chapter 2).

- 2. we explain why multithreaded architectures do support fine-grained parallelism and fine-grained synchronization by providing architectural support for massive concurrency (see Chapter 3).

- 3. we propose a division of labor between the programmer and the compiler in extracting and exploiting parallelism that places a reasonable burden on the complexity-management skills of programmers (see Chapter 4).

- 4. we make a contribution to parallel programming methodology by extending the full/empty bit structure of memory words in the Tera MTA architecture [Tera, SC97] to implement a Multiword Compare-and-Swap operation. In particular, we shift the problem of the atomicity of a set of transactional variables to the problem of the atomicity of a single multiword synchronization variable which has been partitioned into counters, thus providing a practical and efficient implementation (see Chapter 4).

In Chapter 2, we explain simply and clearly, with novel analysis, why conventional RISC superscalar processors do not provide architectural support for massive concurrency. Our fundamental conclusion is that, because concurrency is sought exclusively from instruction-level parallelism (ILP), and because data locality is fundamental in determining performance, threads depend on the state built up in both their data cache and the caches that are used for branch prediction. When context switching occurs, this state must be laboriously rebuilt, leading to a long interval during which threads that resume, regain their former performance levels. We quantify all this by including the time to rebuild this nonarchitectural state as part of the "effective context-switch time". When this is large, it is the same thing as heavyweight threads, and also means absence of support for fine-grained parallelism—the biggest downside of conventional RISC superscalar processors. This is the fundamental reason that grouping larger and larger number of such processors is unlikely to lead to multi teraflops performance.

In Chapter 3, working as analysts rather than as designers, we explain why multithreaded architectures can support fine-grained parallelism and fine-grained synchronization, and relate the costs of context-switching on a multithreaded machine (which only sometimes involves movement of execution contexts in or out of processors) to the corresponding effective context-switch time of RISC superscalar processors.

Finally, we propose a division of labor in extracting and exploiting parallelism that reconciles the need for truly massive concurrency with the limitations of the human mind in managing complexity. Reasonably, we leave most of the burden to the compiler. The compiler needs some help, however, so we advocate both explicit parallelism (within reason) and compiler directives which lead to more effective language translation.

We also make a contribution to parallel programming methodology by extending the full/empty bit structure of memory words in the Tera MTA architecture to design a Multiword Compare-and-Swap operation. The primary value of this is to allow database-like programming where agreed-upon lock orderings are hard to come by, when we do not wish to be bothered by the danger of deadlocks.

Other authors [Herlihy, Moss 91] [Herlihy, Moss 93] have suggested implementing Compare-and-Swap-Two using the conventional hardware-managed cache-coherence protocol. We do not use such protocols in multithreaded machines, and find an efficient dynamic (i.e., addresses of shared transaction variables are known only at

runtime) implementation that allows us to do transactional programming in the spirit of optimistic concurrency control. Apart from the sector data-cache, the only new hardware instructions we require are a few multiword synchronization variables and the ability to increment indexed fields in these shared variables. The fully dynamic solutions do require some address registers so that shared variables whose addresses are disambiguated at runtime can be associated with counters in the multiword synchronization variable.

## Chapter 2

# Superscalar Architectures

"He is one of those people who would be enormously improved by death."

- H. H. Munro

Since the beginning of this decade, seeking microprocessors with higher and higher performance has led to many advanced microarchitectural designs. There is a heavy emphasis at present on superscalar microprocessors [Smith, Sohi]. These are multiple-issue machines which contain a number of micro-architectural features specifically designed to achieve concurrency by exploiting the parallelism contained in a program at the instruction level called instruction-level parallelism (ILP) [Jouppi, Wall]. ILP is the parallelism within single threads. A general outline of superscalar machines is given in Section 2.2.

The major drawback of the ILP processors is that they create heavyweight hard-ware threads leading to slow context-switching and poor fine-grained synchronization which often results in the disciplined avoidance of both features. The amount of parallelism that can be exploited depends on the controlflow and also on the dataflow inherent in the code. There are problems not only with context switching but also with frequent branches. Frequent branching, for example, limits the performance of a superscalar processor due to the maintenance of a large number of registers and cache footprints. We discuss this issue in detail in Section 2.4. Another major design issue is out-of-order execution in a superscalar machine which we discuss in Section 2.3.

As systems scale up, the data-locality requirements grow larger and so does the need to avoid and tolerate large-scale latency. Object-oriented or multithreaded applications strain cache capacity, adding to the bandwidth and I/O burden. Caches are essential to parallel superscalar processors and we discuss them briefly in Section 2.1.

## 2.1 Caches

One of the major obstacles limiting application performance of superscalar machines is long latency of remote memory operations. Wide-issue multiprocessors issue multiple instructions per clock cycle. Instruction pipelines must be well fed in order both to avoid bubbles in the pipelines and to maximize performance. As the gap between processor and memory speeds continues to grow, there is need to develop and exploit techniques to avoid or tolerate such memory latencies, thereby improving processor performance.

Caching of data has been the most popular way to avoid memory latency. A cache is a small, higher speed memory system which stores the most recently used instructions or data from a larger but slower main memory system. The larger the cache, the more instructions and data it can store, and higher is the probability of finding the data or instruction in the cache. When a memory request does not find an address in the cache—a cache miss is incurred; whereas, if the search is successful a cache hit is supposed to have occurred. An  $n^{th}$  level cache is n-1 levels away from the CPU. The first level (L1) or primary cache is the fastest in the memory hierarchy. It resides on the processor chip itself and runs extremely fast. Each time the processor requests information from memory, the cache controller on the chip uses special circuitry to first check if the memory data is already in the cache. If it is, then the system is saved from accessing the slow main memory. Most computers also use a secondary or second level (L2) cache, to catch some of the recently used data that does not fit in the smaller primary cache. The L2 cache is much larger but also much slower than the primary cache. Most modern processors, for example Pentium II processors actually have both L1 and L2 caches built into the processor chip. The rest of the n-2 higher level caches reside outside the processor chip. Caches each level away from the processor are typically larger and slower than the levels closer to the CPU.

Figure 2.1: Memory hierarchy with primary  $(L_1)$  and secondary  $(L_2)$  caches

The first level cache is relatively small and has split instruction and data caches. It is usually direct-mapped or, has low associativity. L2 is much larger, is shared by both instructions and data, and usually has high associativity. L1 and L2 caches are located on-chip for fast access times. In case of a cache miss, the processor stalls until such time as the memory address is found in one of the cache levels. Figure 2.2 shows a flow diagram of a blocking cache, which stalls the CPU in case of a cache miss.

Figure 2.2: Flow Diagram of Lockup or Blocking Cache

As remedies *lockup-free* or *non-blocking* caches [Kroft] (see Figure 2.3) were designed to enable processing cache-accesses inspite of cache misses. Special registers

Figure 2.3: Flow Diagram of a Lockup-free or Nonblocking Cache

called miss status holding registers (MSHR's) along with the necessary control logic, contain adequate information to enable the processor to overlap processing of a cache miss with processing of subsequent instructions in the instruction cache. Nevertheless, with rise in the number of MSHR's, complexity and cost associated with non-blocking schemes rose quite rapidly.

In case of a cache miss there are overheads incurred in searching for the memory address in the cache. A single cache miss taking place is pipelined to higher and higher levels of caches until there is a cache hit—the processor remaining stalled until such a time. Thus, if the hit rate is too low, the overhead incurred as a result is very high and the processor stalls frequently.

Recently, integration of the two cache levels L1 and L2 into a single cache has been successful. Nevertheless, this has a major disadvantage in that the size of the cache footprint grows massively, which in turn causes context-switching to become increasingly more expensive.

The faster the processor, the more acute is the need to keep them fed with newer instructions and data. More and more instructions and data require more and more levels of cache in order to avoid *misses*. In events of higher context-switchings there

are overwhelmingly large cache-footprints making context-switching sluggish. Moreover, the problem of available memory bandwidth becomes all the more acute when systems scale up, given the memory overhead associated with building large cache-coherent systems. Caches are useful only to the extent that cache-lines are small and are managed by users and compilers rather than automatic cache-coherence protocols.

Thus, the state penalty of context-switching makes caches a bad implementation technique in avoiding latency tolerance.

# 2.2 Superscalar techniques to implement and exploit concurrency

Superscalar processing is the technique used to fetch, decode and execute multiple instructions in parallel (out of order execution) from an instruction stream executing on a single processor. Typically, the state of the instruction stream is stored in register files, various buffers and a single program counter. Indeed, we will use the term instruction-level parallelism (ILP) in the restricted sense of extracting and exploiting the parallelism in an instruction stream using a single program counter as architectural support. Though viewed by many as an extension of the Reduced Instruction Set Computer (RISC) [MIPS RISC] movement of the 1980's, superscalar implementations have forever been heading toward increasing complexity. These superscalar methods have been applied to a wide spectrum of instruction sets, ranging from the DEC Alpha [DEC Alpha], to the latest RISC instruction set, to non-RISC Intel x86 instruction set.

## 2.2.1 Historical perspective

Pipelining of instructions in order to exploit instruction-level parallelism has been in use for many decades. A pipeline acts like an assembly line with instructions being processed in phases, as they pass down the pipeline. With simple pipelining, only one instruction at a time is initiated into the pipeline, though multiple instructions may be in some phase of execution, concurrently. The CDC 6600 used some degree

of pipelining and achieved most of its instruction-level parallelism through parallel functional units. The 360/91 was heavily pipelined, and although it provided a dynamic instruction-issuing mechanism known as *Tomasulo's algorithm*, could sustain only a single instruction per cycle and was not a superscalar processor. The pipeline initiation rate of one instruction per cycle was perceived to be a serious practical bottleneck. There exist several implementation techniques for exploiting instruction-level parallelism, such as vector processing, multiprocessing and others. Superscalar processors succeeded in eliminating the *single-instruction-per-cycle* bottleneck by initiating more than one instruction per cycle. Ever since their invention in mid 1980s, superscalars became the standard method for implementing high-performance microprocessors.

## 2.2.2 Model of a superscalar processor

In the sequential execution model, a program counter is used to fetch a single instruction from memory. The instruction is then executed and the program counter incremented to fetch the next consecutive instruction from memory or a nonconsecutive instruction in case of a branch or jump instruction.

A superscalar machine eliminates much of the non-essential sequentiality (out-of-order execution) to turn the program into a parallel, high-performance version, yet retaining the outward appearance of sequential execution. Often, instructions are written in sequence in a program because of the language syntax with no implication that they need be executed in that order. The sequential program text, in effect masks the intended program order. A number of techniques including dependence analysis, attempt to recover the intended (essential for correctness) program order from the sequentially-written program order. Although this is certainly not an algorithm for uncovering it, formally we may say that the essential partial order among instructions (say, within a basic block) is conserved.

Parallel processing of instructions involves the following stages:

#### 1. Instruction fetch

Simultaneously fetching multiple instructions (which are partially predecoded) for later decode, using aggressive branch prediction (state explosion), and out-of-order issue (hardware complexity) and an instruction cache (conservative and

Figure 2.4: Stages of parallel processing in a superscalar execution.

well accepted).

#### 2. Instruction decode

Breaking apart instructions for determining true dependencies and other types of dependencies.

### 3. Dispatch and schedule

Initiating or issuing multiple instructions in parallel.

#### 4. Execute

Contains the functional units (FUs).

#### 5. State update

Handling (precise) interrupts and instruction reordering.

Maintaining the process state in a coherent sequential order and implementing precise interrupts in the presence of out-of-order execution and superscalar execution.

Figure 2.5 illustrates the microarchitecture, or hardware organization of a typical superscalar processor. A static program in essence describes a set of executions, each corresponding to a particular set of data that is given to the program. Implicit in the static program is the sequencing model, i.e., the order in which the instructions are to be executed.

As a static program executes with a specific set of input data, the sequence of executed instructions forms a dynamic instruction stream. As long as instructions

Figure 2.5: Organization of a Superscalar Processor.

to be executed are consecutive, static instructions can be entered into the dynamic sequence simply by incrementing the program counter, which points to the next instruction to be executed. When there is a conditional branch or jump instruction the program counter is updated to a non-consecutive address. An instruction is control dependent on its preceeding instruction(s) if the flow of program control must pass through the preceeding instructions first.

The most vital step in increasing instruction-level parallelism is to overcome control dependencies incurred due to incrementing or updating program counters. A static program can be taken as a collection of basic blocks—a contiguous block of instructions with a single entry point and a single exit point. Once a basic block has been entered by the instruction fetcher, all instructions in the basic block are executed eventually, i.e., any sequence of instructions in the basic block can be initiated into a conceptual window of execution, and they are free to execute in parallel subject merely to data dependence constraints.

Control dependencies due to updates of a program counter, especially due to conditional branches, must be overcome to get more parallelism. One way to do this is to predict the outcome of a conditional branch and speculatively fetch and execute instructions from the predicted path. Instructions from the predicted path are moved into the window of execution. If the prediction is later found to be correct, then the speculative status of the instructions is removed, and their effect on the state is the same as any other instruction. If the predicted path is later found to be incorrect, the speculative execution was wrong, and recovery actions must be initiated so that

process-state is not corrupted; all effects of the wrong speculative execution (misspeculation) are nullified.

Instructions in the window of execution begin execution subject to data dependence constraints. The precedence requirements in executing some instructions is that operations can not be issued before their operands are available. Data dependencies occur among instructions due to the possibilities (hazards) of these instructions accessing the same storage location. Ideally, instructions can be executed subject only to true dependence constraints. These true dependencies appear as read-afterwrite(RAW) hazards, so that the consuming instruction can only read the value after the producing instruction has written it.

There is also a possibility of having artificial dependencies which have to be overcome during the execution of the program to increase the available level of parallelism. These artificial dependencies result from write-after-read(WAR), and write-after-write(WAW) hazards.

After resolving these kinds of dependencies, instructions are issued and begin execution in parallel. In essence, the hardware forms a *parallel execution schedule* which takes into account necessary constraints, such as true dependencies and hardware resource constraints of the functional units and data paths.

A parallel execution schedule often implies that instructions complete in an order diffrent from that indicated by the sequential execution model. Thus, architectural storage cannot be updated immediately when instructions complete execution. Rather, the results of an instruction must be held in a temporary status until the architectural state can be updated. Eventually, when it is determined that the parallel model conformed to the sequential execution model, the temporary results are made permanent by updating the architectural state. This process is called *committing or retiring* the instruction.

## 2.2.3 Instruction fetching and branch prediction

The multiple instructions fetched in the instruction fetching phase feed the rest of the pipeline in a superscalar. A small memory called an *instruction cache* (different from data cache) containing the most-recently used instructions, reduces latency and increases bandwidth of the instruction fetching process. The instruction cache is organized into blocks or lines containing several consecutive instructions. The program counter is used to search the cache contents associatively to determine if the instruction being fetched is present in one of the cache blocks; if present there is a cache hit, if not a cache miss and the instruction is fetched from the main memory.

The number of instructions thus fetched per cycle should be equal to at least the peak instruction decode and execution rate. The extra margin of instruction fetch bandwidth allows for instruction cache misses and for situations where fewer than the maximum number of instructions can be fetched. There is often an *instruction buffer* designed to hold multiple fetched instructions in order to feed the processor pipeline during periods of instruction fetch restriction or processor stall.

The default mechanism of fetching, involves incrementing the program counter by the number of instructions fetched and fetching the next block of instructions [Lee, Smith]. In case of branch instructions which alter the flow of control, the fetch mechanism must be redirected to get instructions from the branch target buffer (BTB).

Processing and handling of branch instructions can be broken down into the following parts:

#### • Recognizing a conditional branch

Special instruction decode information is contained in some extra bits in the instruction cache, which assists in speeding up the process of identification of all instruction types not just branches. These extra bits allow very simple logic to identify the basic instruction types. For example, the *pre-decode logic* generates pre-decoded bits and stores them alongside the instructions as they are placed in the instruction cache.

### • Determining the branch outcome (taken or not-taken)

In case of data dependence between a fetched branch instruction and a preceding uncompleted instruction, the outcome of a conditional branch can be predicted using one of the several types of branch prediction techniques. rather than waiting for the uncompleted instructions to terminate. There are broadly, two types of conventional branch prediction techniques, namely—

- Static branch prediction using information from the binary which is put there by the compiler. Often the profiling information, or the program execution statistics collected during previous runs of the program are used by the compiler as an aid for static branch prediction.

- Dynamic branch prediction where, as program executes more information becomes available, which is used for further prediction. A branch history table or branch prediction table contains information regarding the past history of the branch outcomes. These tables are typically organized in a cache-like manner and accessed with the address of the branch instruction to be predicted.

#### • Computing the branch target

Branch targets are computed relative to a program counter and using an offset value held in the instruction, in order to eliminate the need for read-registers. This requires a program counter and a number of register counters which slow down the process. A branch target buffer (BTB) that holds the target address that was used the last time a particular branch was executed, can be used to assist in finding the target address.

• Transferring control by redirecting fetch (taken branch)

There can be bubbles in the instruction pipeline if there is a delay in recognizing the "taken branch," modifying the program counter, and fetching instructions from the target buffer. Usually, instruction buffers are used to minimize such delays and hence avoid bubbles in the pipeline.

## 2.2.4 Instruction decoding, renaming, and dispatch

In this phase of execution, instructions are removed from the instruction fetch buffers and examined. Control and data dependence linkages are then set up for the remaining pipeline phases. True data dependencies (RAW hazards) and resolution of other register hazards (WAW, WAR) are detected.

Instructions that have been placed in the window of execution may begin execution, subject to data-dependence constraints. Data dependencies occur among instructions because the instructions may access (read or write) the same storage (a register or memory) location. When instructions reference the same storage location, a hazard is said to exist— i.e., there is the possibility of incorrect operation unless

some steps are taken to make sure the storage location is accessed in the correct order. Ideally, instructions should only be ordered according to true dependence constraints. These true dependencies appear as read-after-write (RAW) hazards, because the consuming instruction can only read the value after the producing instruction has written it.

Artificial dependencies result from write-after-read (WAR) and write-after-write (WAW) hazards. A WAR hazard occurs when an instruction needs to write a new value into a storage location, but must wait until all preceding instructions needing to read the old value have done so. A WAW hazard occurs when multiple instructions update the same storage location; it must appear that these updates occur in proper sequence. Artificial dependencies can be caused in a number of ways, for example, by unoptimized code, by limited register storage, by the desire to economize on mainmemory storage, and by loops where an instruction can cause a hazard with itself. For example, here is some dummy machine code:

The move instruction produces a value in r3 that is used by both the load and add instructions. A dynamic execution must ensure that accesses to r3 made by instructions that occur after the add, access the value bound to r3 by the add instruction. Moreover, it must ensure that the value of r3 used in the load instruction is the value created by the move instruction.

Thus, there are mainly two types of instruction dependencies, namely, control-flow and dataflow dependencies. A possible change in control flow causes a control-flow dependency. For instance, a branch instruction that does not always go in the same direction causes a control-flow dependency on instructions that follow it, because the execution of the branch instruction determines whether these instructions execute. Control-flow and dataflow dependencies can be explained as shown in Figure 2.6.

The directed graph has nodes representing instructions and edges that connect instructions that may follow one another. In Figure 2.6 the statements X=3 and X=4 are both control dependent on the statement IF(X=0). However, note that Y=X is not control dependent on any of the other instructions because it executes

Figure 2.6: A Sample Program with corresponding Control-flow and Dataflow Graphs.

regardless of the path taken from the IF statement.

In the example, the statement Y=X has a data dependency with both statements X=3 and X=4. True dependencies are typically viewed in a data flow or data dependency graph. Each node represents an instruction and each edge represents a true data dependency in Figure 2.6. In the example, the statement X=3 causes an antidependency with the statement IF(X==0). The result of the second update should be seen by all instructions following the second instruction. In the example, the statement Y=1 has an output dependency with the statement Y=X.

A parallel-execution schedule often means that instructions complete execution in an order different from that dictated by the sequential-execution model. Consequently, the architectural storage (the storage that is outwardly visible) can not be updated immediately after instructions complete execution. Rather, the results of an instruction must be held in a temporary status until the architectural state can be updated. Meanwhile, to maintain high performance, these results must be used by dependent instructions. Eventually, when it is determined that the sequential model would have executed an instruction, its temporary results are made permanent by updating the architectural state. This process is typically called *committing or retiring* the instruction. This instructions are dispatched into the window of execution, issued from the window of execution as allowed by dependences, complete, and are

finally reordered at the time they commit.

The decode phase sets up one or more tuples for each instruction. Each tuple consists of information like what operands to execute, the location where the operands can be found and where to store the results. These locations are generally memory locations or logical registers.

The register renaming methods are used to replace the logical register name in the instruction's execution tuple with the real name of the physical storage location. A method of register renaming uses a physical file of the same size as the logical register file and a one-to-one relationship is maintained. In addition, there is a buffer called the reorder buffer with one entry per active instruction (an instruction that has been dispatched but has not yet been committed). The reorder-buffer stores instructions that have been dispatched but have not yet been committed, is used to maintain proper instruction ordering for precise interrupts. As the number of instructions become large, the size of the reorder-buffer becomes increasingly large leading to larger state. Reorder-buffers are discussed in detail later in Section 2.3.

## 2.2.5 Instruction issuing and parallel execution

An execution tuple consisting of opcode plus physical register storage locations is formed in the decode/rename/dispatch phase. Once these tuples have been created and buffered, they are examined to decide upon which ones to be issued for execution. Instruction issue is defined as runtime checking for the availability of data (operands) and resources such as execution units, interconnect, and register file (reorder buffer) ports. This is an area of the processing pipeline which contains the "window of execution" and is at the heart of many Superscalar implementations.

Instruction issue buffers can be organized in a number of ways in order of increasing complexity, namely—

- Single, Shared Queue: There is a single queue with no out-of-order issue and no register renaming. A register is reserved for any instruction that modifies the register after being issued. This register is cleared when such an instruction completes. Instructions may be issued as soon as operands are available.

- Multiple Queue Method (Out-of-order execution): Multiple queues (one per

instruction type) may issue out-of-order with respect to one another, though instructions from each queue are issued in order. The individual queues are organized according to their instruction type, for example, floating point instruction queue or integer instruction queue or a load/store instruction queue.

— Multiple Reservation Stations one per Instruction Type: The idea of reservation stations was first proposed in Tomasulo's algorithm wherein, instructions were supposed to be issued out-of-order, i.e., there was no strict FIFO ordering. Thus, all reservation stations simultaneously monitor their source operands for data availability. Reservation stations hold the operands or pointers to the register file where the operands may be found. When all operands for an instruction are ready in the reservation station then the instruction may be issued.

## 2.2.6 Handling memory operations

To reduce memory latencies, memory hierarchies are used so that most data requests will be serviced by data cache memories (Section 2.1) residing at the lower levels of the hierarchy. It is not possible to identify the memory locations that will be accessed by load/store instructions until after the issuing phase. Address calculation and address translation are required to generate the physical address of a memory location. A translation lookaside buffer(TLB) which is a cache of translation descriptors of recently accessed pages is used to speed up the address translation process. Once a valid memory address has been obtained, the load or store operation can be submitted to the memory.

In most fast Superscalars, the idea has been to overlap the address translation and memory access. The initial cache access is done in parallel with address translation and the translated address is then used to compare with the cache tags to determine if it was a cache hit. The key issue then is to allow memory operations to be overlapped, or to proceed out-of-order to ensure that hazards are properly resolved and that sequential execution semantics are preserved. Store address buffers, or store buffers are used to make sure that operations submitted to the memory hierarchy do not violate hazard conditions. The store buffers contain addresses of all pending store operations. Prior to issuing an instruction to memory, the store buffer is examined to see if there is a pending store to the same location.

## 2.2.7 Committing or retiring instructions

This is the final phase of the lifetime of an instruction where the effects of the instruction are allowed to modify the logical process state. This phase implements the appearance of a sequential execution model even though the actual execution is non-sequential due to out-of-order execution and speculative execution. The actions necessary in this phase depend on the techniques used to recover a precise state, discussed in detail in Section 2.4.

The state of the machine is saved or *checkpointed* in history buffers. Instructions update the state of the machine as they execute and when a precise state is needed, it is recovered from the history buffer. Finally, in this phase the history buffer is discarded because it is no longer needed.

The state of the machine is separated into two parts, namely, the implemented physical state which is updated immediately as the operations complete, and a logical state which is updated in the sequential order as the speculative status of operations is cleared. The speculative state is maintained in the reorder buffer from where it is moved into the architectural register file or memory, and space is freed up for the reorder buffer.

In most superscalar implementations the reorder buffer is used as a method of register renaming, though it also holds useful control information used to move physical registers to the free list. In case of interrupts, the control information is used to adjust the logical-to-physical mapping table so that the mapping reflects the correct precise state.

## 2.3 Out-of-order issue/execution of instructions

The in-order-issue of instructions implies that instructions be issued sequentially in order as they appear in the program code. The problem with in-order-issue is that the processor stops decoding instructions whenever there is a dependency or the functional units are busy. Such wastage of CPU time can be avoided by just keeping decoding instructions and issuing them when dependencies have been resolved and busy functional units are clear. This is accomplished by simply adding an instruction window or buffer between the decode and execution stages. Instructions are issued

from the window whenever all dependencies are clear and a functional unit is available, regardless of instruction order as specified in the code.

The technique however introduces the problem of antidependencies or WAR hazards which happens when one instruction requires a register value for input, but a later instruction writes to this register. If the execution of these instructions are reversed then the first instruction reads a wrong value from its source register.

The key issue in allowing memory operations to be overlapped, or to proceed outof-order is to ensure that hazards are properly resolved and that sequential execution

semantics are preserved. Register renaming can be used to overcome both output and

antidependencies. If register R4 is assigned a value, another register R4' is allocated

and all reads of register R4 in the future are directed to R4'. When a new assignment

to register R4 is made another register R4'' is allocated and this process continues.

Out-of-order execution implies the extensive use of reorder buffers to maintain proper instruction ordering for precise interrupts. Should the execution of the program need to be interrupted and restarted later in case of external or internal interrupts, the state of the machine needs to be captured. The sequential execution model has led to the idea of precise state.

In case of an interrupt, the pipelined instruction may modify the process state in an order different from the sequential order. The state of the interrupted process is saved by the hardware or software or a combintion of both. The process states consists of a program counter, registers and memory. If the saved process state is consistent with the sequential architectural model than the interrupt is said to be a precise interrupt.

There can be two kinds of interrupts, the first one being called program-interrupts or traps which result from exception conditions detected during fetching/execution of the program. These are caused by an illegal opcode, overflow of arithmetic data or page faults. The other kind called external interrupts are caused by sources outside the executing process, for example, I/O or timer interrupts. At the time of an interrupt, a precise state of the machine is the state that would be present if the sequential execution model was strictly followed and processing was stopped precisely at the interrupted instruction. Restart can then be made by simply executing that interrupted instruction.

The reorder buffer can be imagined as a FIFO queue implemented in hardware

Figure 2.7: A reorder buffer.

as a circular buffer with head and tail pointers, and gets entries as instructions are dispatched according to sequential program order. As instructions complete execution, the results are inserted into their previously assigned entry, wherever it may happen to be in the reorder buffer. At the time an instruction reaches the head of the reorder buffer, if it has completed execution, its entry is removed from the buffer and its result value is placed in the register file. An incomplete instruction blocks at the head of the reoder buffer until its value arrives.

The disadvantage of using reorder buffers is that as more and more instructions are pumped into the instruction pipeline, the size of the reorder buffer grows substantially. The buffer must be able to store the results of all outstanding operations. Vendors regularly increase the size of their reorder buffers with successive processor generations. Think of the total register size as proportional to the amount of ILP being used.

## 2.4 Speculative Execution

When a branch is encountered in the instruction stream, it can cause a change in control flow. This change in control flow can cause branch penalties that can sigficantly degrade the performance of superscalar pipelined processors. To overcome these penalties, these processors typically provide some form of control-flow prediction. Speculative execution means the execution of code at one or more destinations of a branch before the branch outcome is known [Calder et al.]. The basic purpose

of speculative execution is to speed up program execution by running some code segments before it is known whether or not they are actually taken. This technique is primarily used in trying to prevent branches from disrupting long execution pipelines. Speculative execution is an integral part of modern ILP processors, be they statically-or dynamically-scheduled designs. Speculation may take two forms, namely, control speculation and data speculation. Control speculation implies the execution of an instruction before the execution of a preceding instruction on which its control is dependent. Data speculation implies the execution of an instruction before the execution of a preceding instruction on which it may be or is data dependent.

Control flow speculation uses several branch prediction mechanisms to enhance performance of the superscalar machines. Opportunities for parallelism can be increased by performing control-dependent analysis, in which a program trace is analyzed to decide on exactly which branch each block is dependent. Speculative execution implies executing the code at one or more destinations of a branch before the branch outcome is known. The following steps are involved:

- Adding branch prediction to processor core.

- When branch is predicted, begin executing instructions until outcome is known.

- Mark these speculative instructions in the reorder buffer.

- If the branch is predicted Taken(NotTaken) and it is actually NotTaken(Taken), then:

- Flush all instructions from branch to end of reorder buffer.

- Resume execution at correct path of branch.

When there is a taken (or predicted taken) branch there is often at least a clock cycle delay in recognizing the branch, modifying the program counter, and fetching instructions from the target address. This delay results in pipeline bubbles unless remedied steps are taken. The most common solution is to have an "instruction buffer" with an abundance of instructions to mask the delay. Still complex buffers contain instructions from both the taken and not-taken paths of the branch.

In case of mispredictions the penalty is very high. All instructions along the wrong path and the modifications in the state made by them have to be squashed leading to a wastage in processor cycles. The size of the Branch Translation Buffer (BTB) grows exponentially with the number of branch predictions made due to the combinatorial explosion of nested branches.

To expose parallelism that is hindered by ambiguous dependences, data dependence speculation may be used. In data dependence speculation the load is allowed to execute before a store on which it is ambiguously dependent. If no true dependence is violated in the resulting execution, the speculation is successful. If, however a true dependence is violated, the speculation is erroneous (i.e, mis-speculation). In the latter case the effects of the speculation must be undone. Consequently some means required for detecting erroneous speculation and for ensuring correct behaviour. As window sizes grow larger, the mis-speculation becomes more frequent, and the cost of mis-speculations becomes very high.

# 2.5 Summary of the disadvantages of superscalar machines

Superscalar processors because of their ambitious attempts to exploit ILP have steadily raised the heaviness of threads to the point where context switching is now a high-cost operation. The process or thread state has grown incrementally with new superscalar techniques. At the bottom, large state is simply large number of registers and large cache-footprints. As other techniques, such as speculative execution are added, state includes new things like branch-target buffer foot-prints. The state mostly affects context switching, but superscalar features also have large negative impact on programs with frequent conditional branching. The result is that we may be shy about programming with either frequent context switching (i.e., fine-grained parallelism with fine-grained synchronization) or fine-grained conditional branching.

# Chapter 3

# Multithreading

"Everything comes to him who hustles while he waits."

- Thomas Edison

The problem that multithreading comes to solve is latency tolerance at all levels of granularity. Both SRAM and DRAM speeds are increasing much slowly than the processor speeds—in fact the gap between processor and memory speeds is growing exponentially. Small operations and large operations alike incur some non-zero latency. For example, memory references have to wait a finite amount of time before loads or stores complete. The longest latencies come from synchronization operations that do not succeed. Small but important latencies come from (for example) floating-point operations. We will discuss caches as a latency-avoiding technique below, as this is a long story. The waiting time for (remote) memory accessing is called memory latency and can be long enough to pose a major threat to the performance of any computer system. Approximately, every third instruction in a modern parallel program is a memory reference. The latency of memory operations is determined by the access time, which is growing exponentially larger than the processor clock cycle time. The numbers are dramatic when memory latency is expressed in clock cycles.

As is well known, when a user program blocks for disk I/O in a multiprogramming environment, the operating system blocks that program and merely switches to some other user program in the ready queue. This overlapping of disk latency with useful

work done by some other program is appropriate for the granularity of the context switching, which is a function of burst size and quantum size. Typically, many machine instructions are required to switch from one process to another. Although the execution time of the blocked process is not reduced in any way, the throughput of the system improves drastically.

Hardware-supported multithreading is the hardware analogue of multiprogramming (which tolerates disk latency). Ideally, in multithreading, independent parallel activities (threads) not only context-switch freely, but also frequently synchronize and communicate with each other. In a multithreaded processor, the essence of multiprogramming is implemented at a much smaller granularity of switching, with a much smaller switching cost, and cheaper and better inter-thread communication. In this way, the focus shifts from switching between jobs to switching between threads, which may well, belong to a single program. Moreover, memory latencies and latencies of functional units in a multithreaded processor are much smaller than disk latencies in multiprogramming; and are usually not visible to the operating system. As result, such latencies can not be dealt with by the operating system, where the cost of context switching that saves and restores processor-state is very high.