INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the

text directly from the original or copy submitted. Thus, some thesis and

dissertation copies are in typewriter face, while others may be from any type of

computer printer.

The quality of this reproduction is dependent upon the quality of the copy

submitted. Broken or indistinct print, colored or poor quality illustrations and

photographs, print bleedthrough, substandard margins, and improper alignment

can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and

there are missing pages, these will be noted. Also, if unauthorized copyright

material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning

the original, beginning at the upper left-hand comer and continuing from left to

right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white photographic

prints are available for any photographs or illustrations appearing in this copy for

an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA

U\_800-521-0600

# **EMTP Simulation Of An Active Filter**

# **Operating With Weak AC Distribution System**

## **Rachit Arora**

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements

for the Degree of Master of Applied Science at

Concordia University

Montreal, Canada

January 1999

© Rachit Arora, 1999

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre reférence

Our file Notre reférence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-43547-4

### **Abstract**

## **EMTP Simulation Of An Active Filter**

## **Operating With A Weak AC Distribution System**

### Rachit Arora

An AC distribution system has a myriad of loads connected at the system bus. Many of the DC based loads cause disturbance on the ac bus due to high harmonic load currents. Traditionally passive filters are used for filtering these load harmonics. Recent technological advances have enabled the use of high frequency switching devices in the development of active filtering techniques.

In this thesis, an active filter topology was selected for the system, and a test system was modeled using EMTP. The objective of active filtering is to meet the harmonic and reactive load locally, and thus removing the harmonic content of source currents. The AF controller based on the on-line power computation scheme was modeled. Tracking control was demonstrated using two control methodologies - hysteresis band control and sliding mode control.

A performance comparison was made between the two control schemes, and the impact of various circuit and control parameters on the filtering performance was studied. To assess the transient performance achieved with the control schemes presented, results from EMTP based studies for this distribution system under various AC-DC fault conditions are analyzed.

# Acknowledgment

I would like to thank my supervisor, Dr. V. K. Sood for his financial support during my Masters research work, and appreciate his valuable advice and patience with which he guided me during my deliberations.

The other aspect of my stay here has been made possible in the company of many friends who have been a constant support with their love, affection and presence.

Thanks Meghana, Cthru, Mahesh, Subha, V. Pisini, Tanu & Vijay, Miki, Uju, Daksha, Jaya, Jasjit and Sraddha for everything. I also thank all my colleagues at GM 905, for making the office a habitable place to stay late hours.

The assistance of Department secretaries and Computing Services is appreciated. I also owe my gratitude to Dr. B. N. Singh and Dr. A. Chandra of the ETS for assisting me in technical clarifications.

My parents and my sister, *Ruchi* were always a source of encouragement and moral support. I dedicate this work to them.

Dedicated to my parents and my sister Ruchi

# **CONTENTS**

|            |                                                              | Page |

|------------|--------------------------------------------------------------|------|

| List of Fi | gures                                                        | viii |

| List of Ta | bles                                                         | x    |

|            |                                                              |      |

| Chapter    | : Introduction                                               | I    |

| 1.1        | Effect of Harmonics                                          | 2    |

| 1.2        | Passive AC Filters                                           | 2    |

| 1.3        | Problem Definition                                           | 4    |

| 1.4        | Literature Survey                                            | 4    |

| 1.5        | Proposed Approach                                            | 11   |

| 1.6        | Thesis Outline                                               | 11   |

|            |                                                              |      |

| Chapter 2  | : System Configuration                                       | 12   |

| 2.1        | Introduction                                                 | 12   |

| 2.2        | Active Filters                                               | 12   |

| 2.3        | Active Filter Topology Selection                             | 16   |

| 2.4        | System Model                                                 | 17   |

| 2.5        | Summary                                                      | 23   |

|            |                                                              |      |

| Chapter 3  | : Control Circuits                                           | 24   |

| 3.1        | Introduction                                                 | 24   |

| 3.2        | Rectifier Control Unit                                       | 24   |

| 3.3        | AF Control Unit                                              | 25   |

|            | 3.3.1 On-line Power Computation Scheme (Feedforward Control) | 27   |

|            | 3.3.2 Tracking Control (Feedback Control)                    | 35   |

|            | 3.3.2.1 Hysteresis Control                                   | 35   |

|            | 3 3 2 2 Sliding-Mode Control                                 | 49   |

| 3.4 Summary                                                                                  | 61  |

|----------------------------------------------------------------------------------------------|-----|

| Chapter 4: Transient Behavior of the Active Filter Model                                     | 62  |

| 4.1 Introduction                                                                             | 62  |

| 4.2 System Tests                                                                             | 62  |

| 4.3 Initialization Tests                                                                     | 63  |

| 4.3 Initialization of Rectifier Control Unit                                                 | 63  |

|                                                                                              |     |

| 4.3.2 Initialization of AF Control Unit                                                      | 65  |

| 4.3.3 Comparison of Hysteresis and Sliding-Mode Control                                      | 70  |

| 4.3.4 Harmonic Analysis                                                                      | 70  |

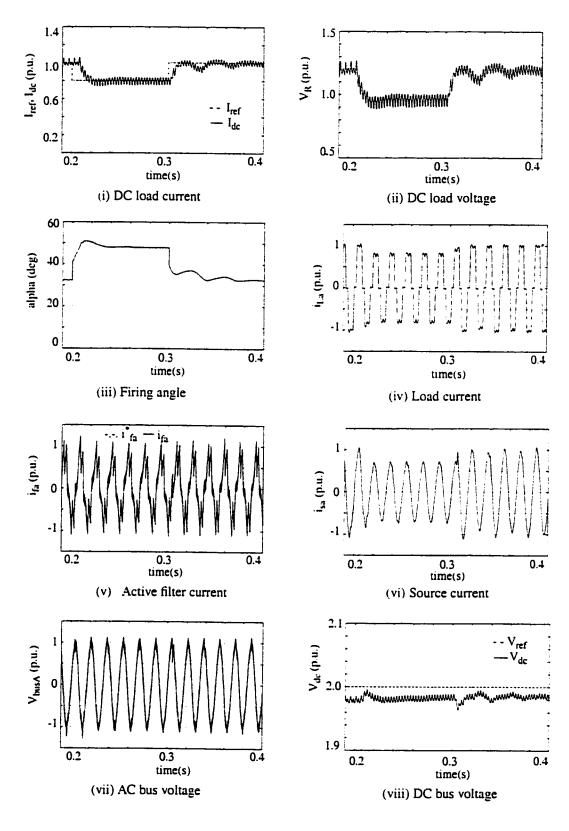

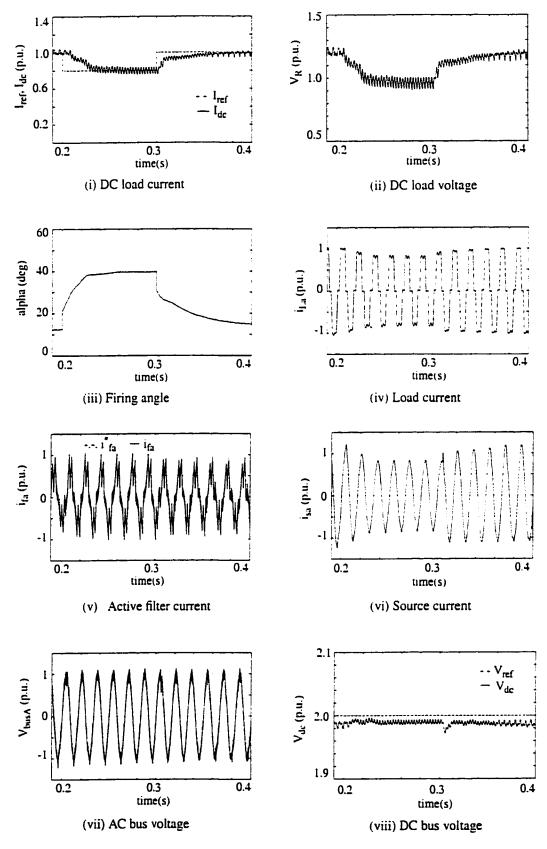

| 4.4 Dynamics Tests                                                                           | 72  |

| 4.4.1 Step change of 20% in DC current reference, I <sub>ref</sub>                           | 71  |

| 4.4.2 Fault Tests                                                                            | 76  |

| 4.4.2.1 Single Phase Solid Line to Ground 3-cycle Fault at AC Bus (Commutation Failure Test) | 75  |

| 4.4.2.2 Single Phase Line to Ground 3-cycle Fault at AC bus (with fault impedance)           | 77  |

| 4.4.2.3 Line to Line 3-cycle Fault at AC bus (phases A,B)                                    | 82  |

| 4.4.2.4 Three Phase Solid Line to Ground Fault at AC bus (Phases A,B,C)                      | 82  |

| 4.4.2.5 DC 6-cycle Fault at Rectifier load end                                               | 83  |

| 4.5 Summary                                                                                  | 91  |

| Chapter 5: Conclusions                                                                       | 92  |

| References                                                                                   | 96  |

| Appendix A                                                                                   | 101 |

| Appendix B                                                                                   | 103 |

| Annendix C                                                                                   | 110 |

# **List of Figures**

|      |                                                 | Page  |

|------|-------------------------------------------------|-------|

| 1.1  | Harmonic Elimination by magnetic compensation   | 5     |

| 2.1  | Active Filter Topologies                        | 14    |

| 2.2  | System Model                                    | 18    |

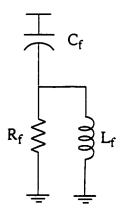

| 2.3  | High Pass Filter                                | 19    |

| 2.4  | Converter Unit                                  | 20    |

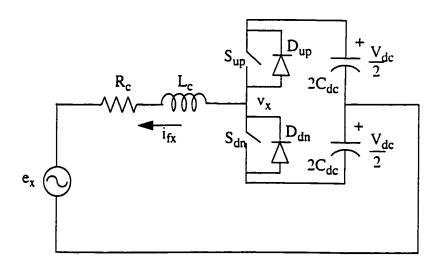

| 2.5  | Voltage Source Inverter Unit                    | 21    |

| 3.1  | Rectifier Control Unit                          | 25    |

| 3.2  | System Model                                    | 26    |

| 3.3  | AF Control Unit                                 | 27    |

| 3.4  | AF Control Unit Schematic                       | 28    |

| 3.5  | Simulation of On-line Power Computation Scheme  | 33-34 |

| 3.6  | Hysteresis Controller implementation            | 36    |

| 3.7  | Simulation of Hysteresis Controller             | 37    |

| 3.8  | Variation of Hysteresis Bandwidth               | 39    |

| 3.9  | Effect of variation of Hysteresis Bandwidth, hb | 40    |

| 3.10 | Variation of L <sub>c</sub>                     | 42    |

| 3.11 | Effect of variation of L <sub>c</sub>           | 43-44 |

| 3.12 | Variation of V <sub>dc</sub>                    | 46    |

| 3.13 | Effect of variation of V <sub>dc</sub>          | 47-48 |

| 3.14 | Sliding-Mode Controller implementation          | 50    |

| 3.15 | Simulation of Sliding-Mode controller           | 51    |

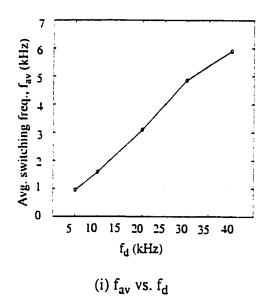

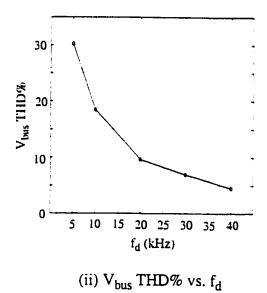

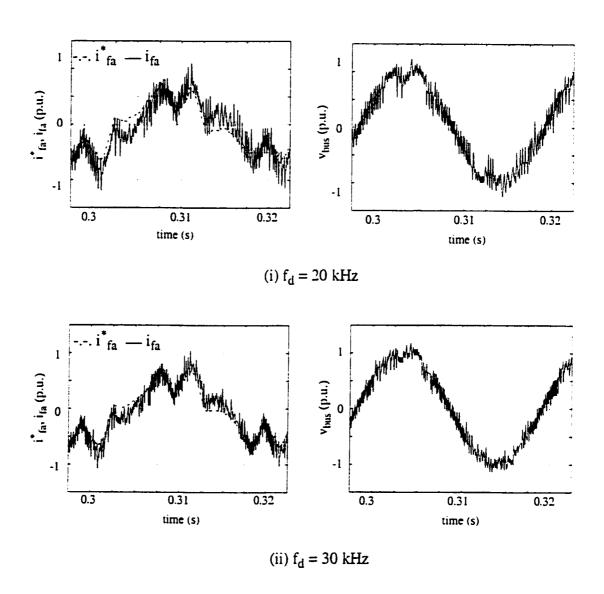

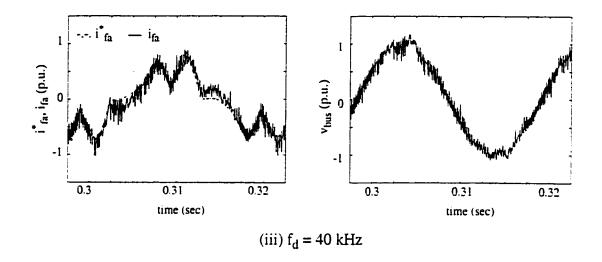

| 3.16 | Variation of decision frequency                 | 53    |

| 3.17 | Effect of variation of decision frequency       | 54-55 |

| 3.18 | Variation with L <sub>c</sub>                   | 56    |

| 3.19 | Effect of variation of L <sub>c</sub>           | 57    |

| 3.20 | Variation of V <sub>dc</sub>                    | 59    |

| 3.21 | Effect of V <sub>dc</sub> variation                           | 59-60 |

|------|---------------------------------------------------------------|-------|

| 4.1  | Initialization of Rectifier Unit                              | 64    |

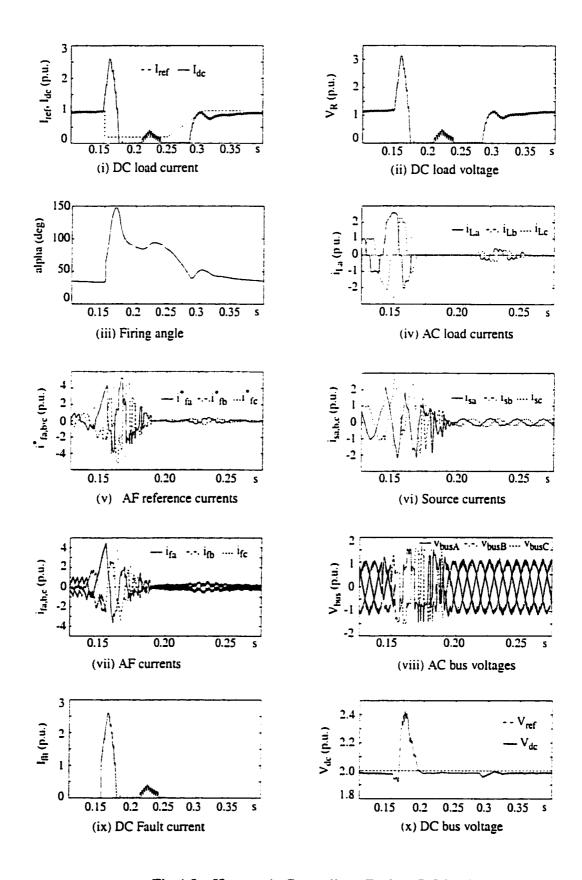

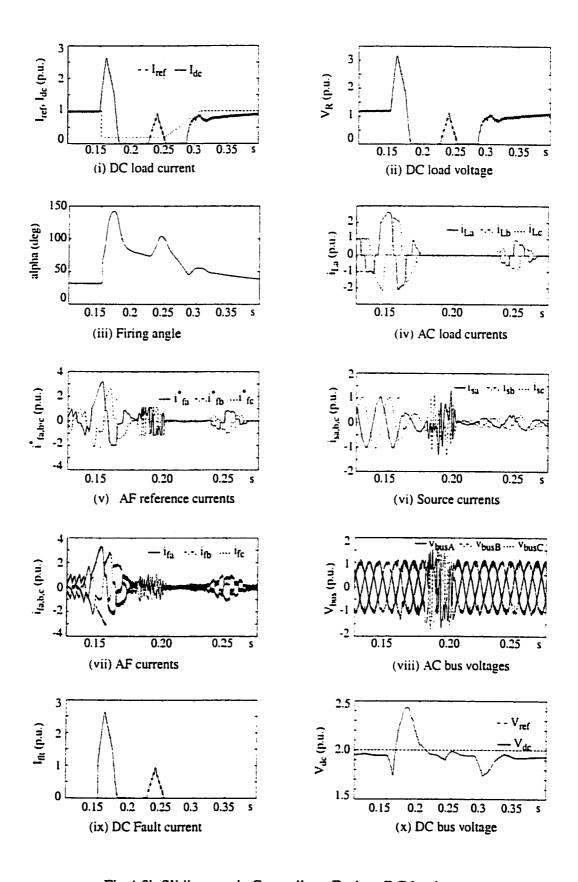

| 4.2a | Active Filter Initialization - Hysteresis control             | 66-67 |

| 4.2b | Active Filter Initialization - Sliding-Mode Control           | 68-69 |

| 4.3a | Hysteresis Controller - transient response                    | 74    |

| 4.3b | Sliding-Mode Controller - transient response                  | 75    |

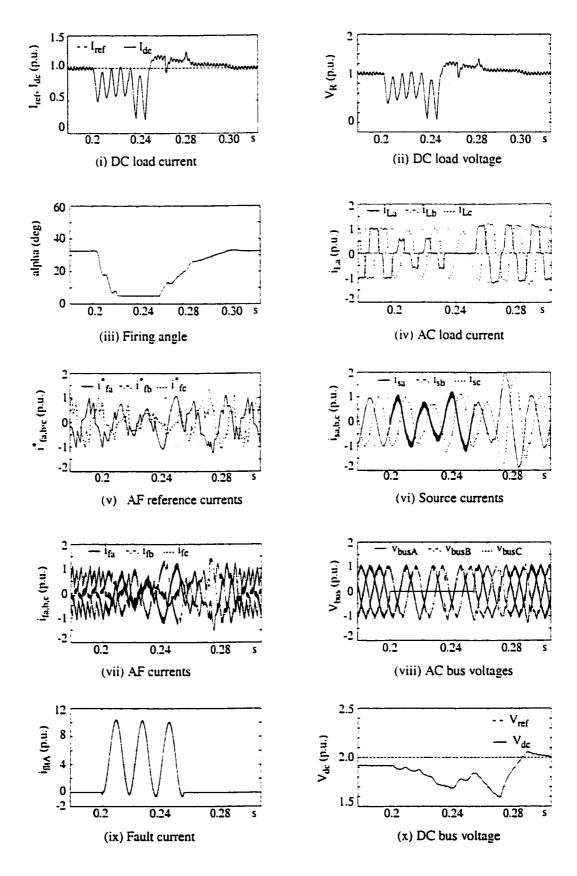

| 4.4a | Hysteresis Controller - Single phase fault at AC bus          | 78    |

| 4.4b | Sliding-Mode Controller - Single phase fault at AC bus        | 79    |

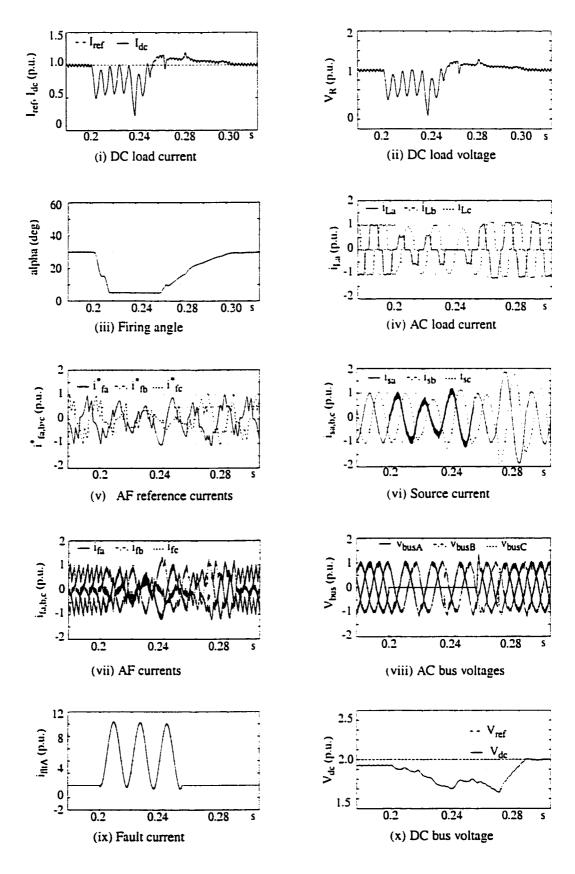

| 4.5a | Hysteresis Controller - Single phase fault (50%) at AC bus    | 80    |

| 4.5b | Sliding-Mode Controller - Single phase fault (50%) at AC bus  | 81    |

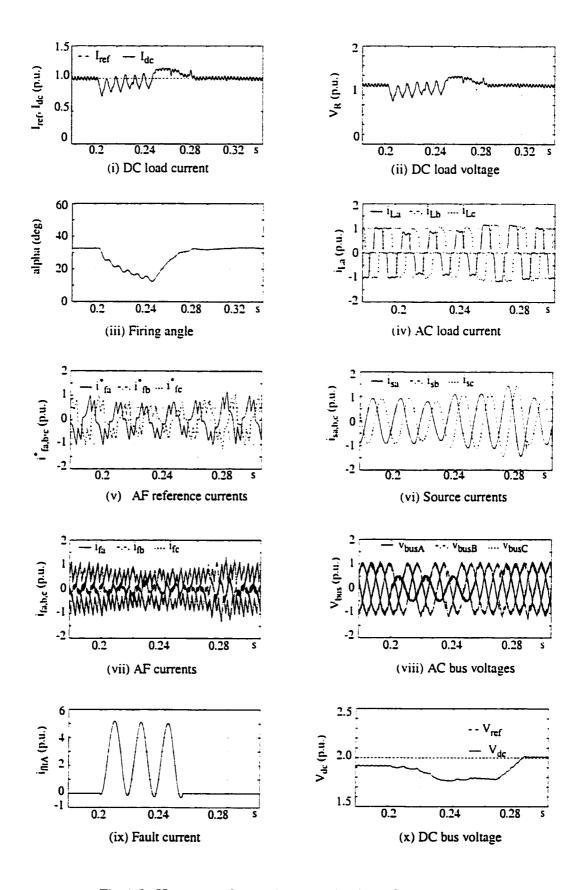

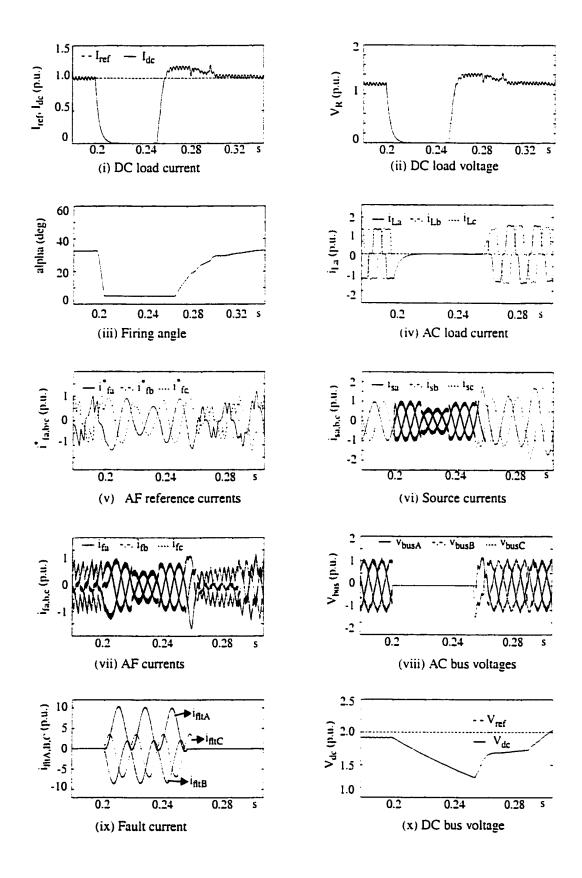

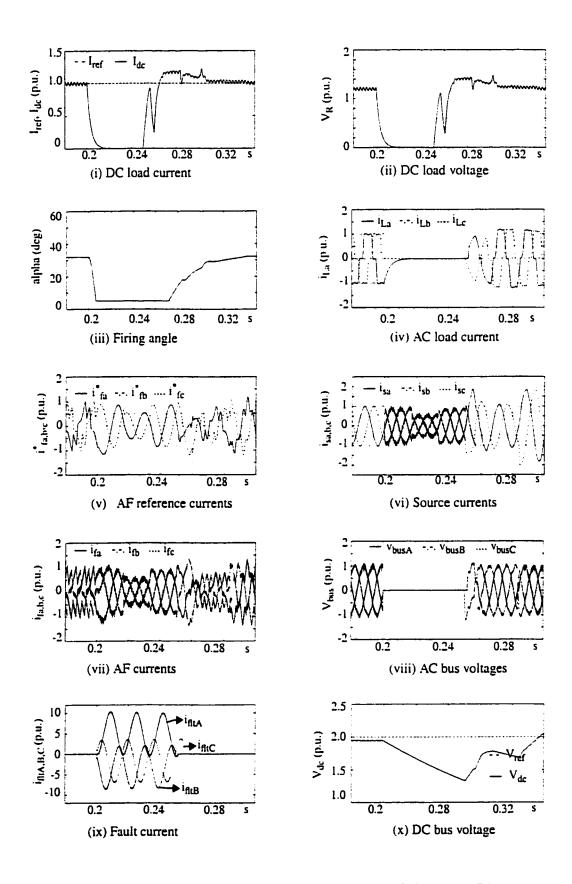

| 4.6a | Hysteresis Controller - Line-Line fault at AC bus (ph. A-B)   | 85    |

| 4.6b | Sliding-Mode Controller - Line-Line fault at AC bus (ph. A-B) | 86    |

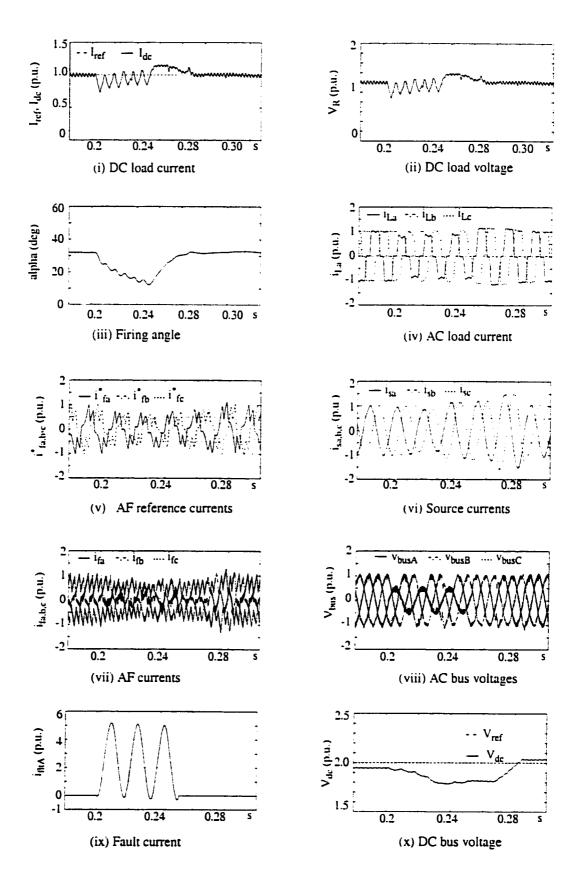

| 4.7a | Hysteresis Controller - 3 phase L-G fault at AC bus           | 87    |

| 4.7b | Sliding-Mode Controller - 3 phase L-G fault at AC bus         | 88    |

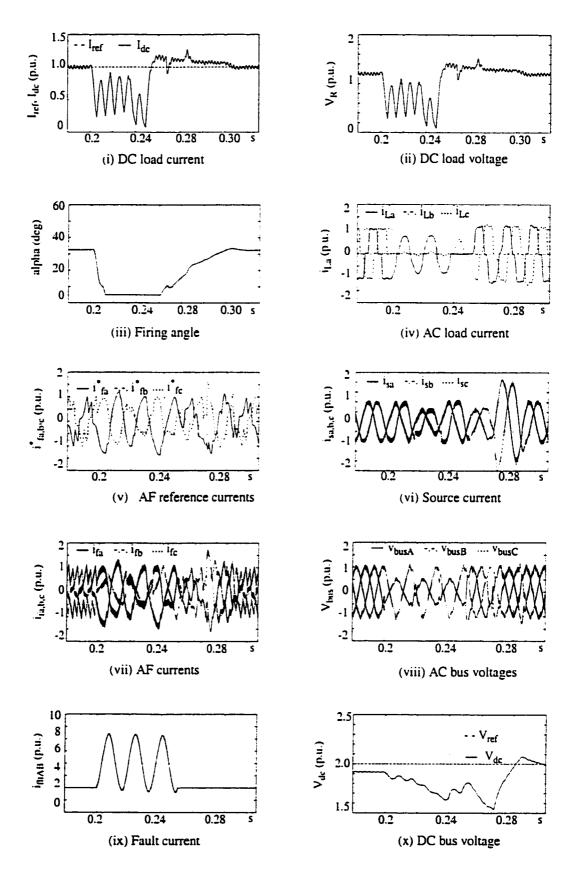

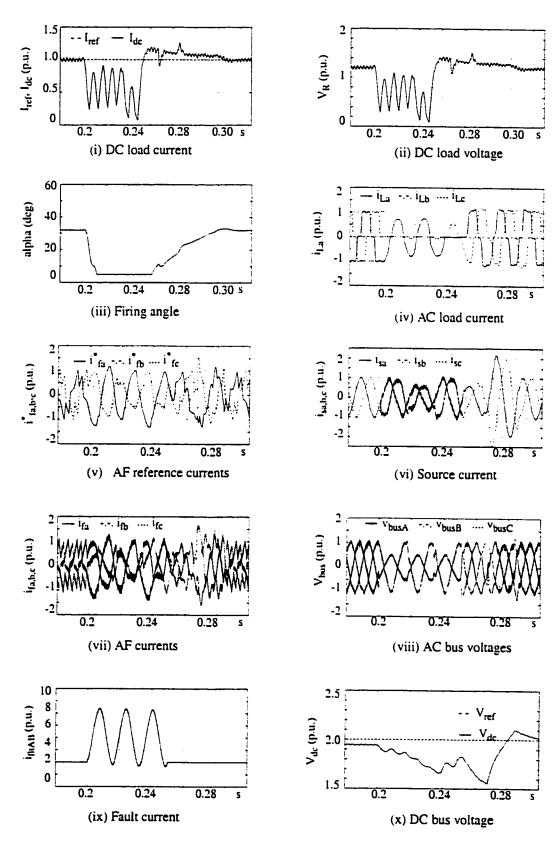

| 4.8a | Hysteresis Controller - Fault at DC load                      | 89    |

| 4.8b | Sliding-Mode Controller - Fault at DC load                    | 90    |

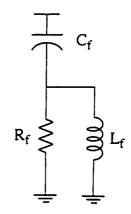

| A.1  | 2 <sup>nd</sup> order high pass filter                        | 101   |

| B.1  | Single phase equivalent circuit                               | 103   |

| B.2  | Wave-shaping of if in hysteresis band                         | 104   |

# **List of Tables**

|     |                                                    | Page  |

|-----|----------------------------------------------------|-------|

| 3.1 | Variation of hysteresis bandwidth, hb              | 39    |

| 3.2 | Variation of Connection inductance, L <sub>c</sub> | 41-42 |

| 3.3 | Variation of DC bus voltage, V <sub>dc</sub>       | 45    |

| 3.4 | Variation of decision frequency, f <sub>d</sub>    | 53    |

| 3.5 | Variation of Connection inductance, L <sub>c</sub> | 55-56 |

| 3.6 | Variation of DC bus voltage, V <sub>de</sub>       | 58    |

| 4.1 | Harmonic Analyses (without AF compensation)        | 71    |

| 4.2 | Harmonic Analyses (with AF compensation)           | 72    |

## Chapter 1

### Introduction

Power Electronics technology has been increasingly used in many fields in recent years. The proliferation of non-linear loads on distribution systems has resulted in the deterioration of power quality in a substantial way. In a utility system, it is desirable to prevent harmonic current which result in EMI and resonance problems, and limit reactive power flow so as to reduce the losses in transmission and/or distribution lines. Further more a stable and harmonic-free bus voltage is required at the user end.

Traditionally, shunt passive filters comprised of tuned LC elements and capacitor banks were used to filter the harmonics and to compensate for reactive current due to non-linear loads. However, in practical applications these methods have many disadvantages.

In the last two decades, considerable progress has been made in the field of Active Filters (AFs). AFs are inverter circuits, comprising of active devices i.e. semiconductor switches that can be controlled so as to act as harmonic current or voltage generators. Different topologies and control techniques have been proposed for their implementation. AFs are superior to passive filters in terms of filtering characteristics and improve the system stability by removing resonance related problems.

This thesis deals primarily with an EMTP (Electro-magnetics Transient Program) based digital simulation of a shunt active filter compensating for harmonic and reactive power drawn by a three phase controlled rectifier. The system AC bus is fed from a weak AC source, hence the effect of source impedance on system behavior is studied here. The performance of the AF system is presented for steady state and transient analyses.

#### 1.1 Effect of Harmonics

Harmonic terminal voltages may be produced partly by the power generator itself (source harmonics) and partly by non-sinusoidal load currents flowing through the internal impedance of the generator (load harmonics).

Harmonic voltages at the terminal end cause harmonic currents in the connected load. This leads to extra losses and heating in the load. Capacitors attached at the terminal end for power factor correction also suffer extra heating losses.

Overvoltages may arise due to resonance conditions between a shunt capacitor bank and the rest of the system at a harmonic frequency. Due to the distortion of the terminal bus voltage, unstable or inappropriate converter operation may result. Ripple control systems using the power distribution network for transmission of control signals may suffer interference problems. Harmonics also produce noise and interference in telephone circuits running adjacent to power networks.

Such problems lead to reduced system stability and safety margins, and may require derating of distribution equipment.

#### 1.2 Passive AC Filters

Passive filters in power systems are usually used as shunt filters, the accepted practice being to connect a number of separate shunt branches across the terminals of the AC bus to reduce the harmonic distortion in the AC system. Each of these branches is tuned to one of the predominant harmonics, with a high pass branch added that exhibits low impedance for the remaining higher order harmonics.

Passive filters serve two purposes: (1) to reduce the harmonic voltages and currents in the AC power network to acceptable levels and (2) to provide all or part of the reactive power consumed by the converter, the remainder being supplied by shunt capacitor banks, by synchronous condensers, or by the AC power system.

The design of passive filters for a system is complicated by several factors:

- The source impedance, which is not accurately known and varies with the system configuration, strongly influences filtering characteristics of the shunt filter. The impedance of the tuned branches must be low with respect to the source impedance at the harmonic frequencies to provide the filtering required. If the source impedance is low, and the desired degree of attenuation is high, the size and cost of passive filters can become prohibitive.

- The shunt passive filter acts as a current sink to the harmonic voltages present in the AC source voltage. In the worst case, the shunt passive filter may come to series resonance with the source impedance. Even small ripple voltages at resonant frequencies present in the source voltage may produce excessive harmonic currents in the filter.

- At a specific frequency ( $f_0 = 1/\{2*pi*sqrt([L_{source} + L_{filter}]C_{filter})\}$ ), an anti-resonance or parallel resonance condition occurs between the source impedance and the shunt passive filter, which leads to harmonic amplification in the source and filter.

- The tuned branches are designed for a range of frequency variation allowed for by the AC source. The larger the variation of the supply frequency, larger would be the variation of predicted harmonic frequencies and more impractical the sizes of components used in each branch.

- The passive filter also does not handle uncharacteristic lower order harmonics (such as 2nd, 4th, etc.) which may be present in the load current due to unbalanced loads, faulty equipment etc.

With remarkable progress in the speed and capacity of semiconductor switching devices like GTO thyristors and IGBTs, active filters composed of voltage or current source inverters are being put to practical use, because they have the ability to overcome the above mentioned disadvantages inherent in passive filters. Moreover, active filters act as "harmonic eliminators" rather than "harmonic attenuators", thus improving filtering characteristics.

#### 1.3 **Problem Definition**

A test system needs to be defined for distribution system studies. It consists of a DC load connected to a rectifier, that presents a non-linear load and an active filter (AF) that compensates for harmonics and reactive power drawn by the load. The AF should exhibit fast dynamic response and good efficiency. The AF control scheme should function irrespective of the source impedance, and be simple to implement. After compensation the non-linear load should present a fundamental frequency, unity power factor load to the AC source.

The AF should also be able to maintain the Total Harmonic Distortion (THD) of source current within 5%. The simulation model assumes ideal switches, but the switching frequency limit imposed by real switches is taken into consideration during the model design.

The strength of an AC system is measured in terms of Short Circuit Ratio (SCR) which is defined as

$$SCR = \frac{Short Circuit Level at AC bus}{Rated Power}$$

If SCR is less than 3, the AC system is considered weak.

Most of the published works consider a strong AC system feeding non-linear loads, thus not considering the distortion introduced in the terminal voltage. This escapes the practical situations faced by distribution systems, and hence does not give a realistic model. The model developed here would take a weak AC system into consideration and also give detailed analysis of the model under various AC-DC fault conditions.

#### 1.4 Literature Survey

Harmonic levels in distribution systems have been well investigated by utility companies [1,2,3]. In [1], results of a research project involving the investigation of power system harmonic levels on selected distribution circuits on the American Electric Power

System (AEP) were presented. Field measurements were done to record harmonic levels in three classes of distribution circuits - residential, commercial and industrial. Analysis of data collected provided an insight into harmonic distortion in a real distribution system.

In [3], the authors emphasized a probabilistic approach for data collection and the importance of statistical distributions of harmonics in terms of maximum, mean and minimum levels.

The problems faced by passive filter systems influenced the development of active filters. Active filters have been studied, since their basic compensation principles were proposed in the 1970's, to compensate for reactive power, negative-sequence currents and harmonics in industrial power systems.

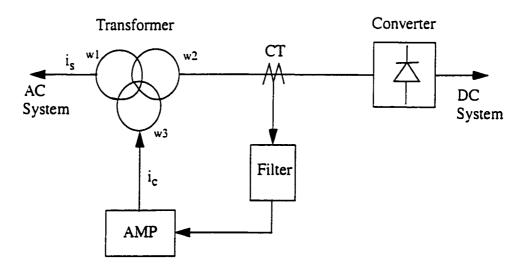

Fig 1.1 Harmonic elimination by magnetic compensation

The basic principle of a shunt active filter was originally presented by H. Sasaki and T. Machida in 1971 [4]. As shown in Fig 1.1, a shunt active filter is controlled in such a way so as to actively shape the source current, i<sub>s</sub>, into a sinusoid by injecting the compensating current i<sub>c</sub>. The authors proposed a new method of eliminating AC harmonic current based on the principle of magnetic flux compensation in a transformer core. A signal

detection circuit extracted the fundamental current component of the non-linear load current flowing in the secondary transformer winding and generated the harmonic current, which after appropriate turns-ratio amplification, is injected in the transformer tertiary winding. This produced harmonic flux cancellation in the transformer core, and resulted in only fundamental frequency current in the primary winding. This technique is considered as the archetype of shunt active filters. Since a linear amplifier was used to generate the compensating current, its realization is unreasonable due to low efficiency.

In 1976, L. Gyugyi and E. C. Strycula [5], presented a family of shunt and series active filters, and established the concept of active filters consisting of PWM inverters using power transistors. However, they could not be realized in real power systems because high-power high-speed switching devices were unavailable in the 1970's.

The work is considered a pioneering effort, as it laid fundamental principles in the theory of active filters. Later research evolves around the same fundamental concepts, but advancing towards newer control techniques for switching signals generation. With the remarkable development and advances in switching speed and capacity of power semiconductor devices in the 1980's, active filters consisting of PWM inverters have been put to practical applications in real power systems.

Earlier work on active filters discussed compensation characteristics only for steady state conditions. The calculation circuit for the compensating current references was simple, and only ideal compensation characteristics could be attained. However, in transient states such as those caused by fluctuating loads, the design of compensating current calculation circuit becomes difficult.

In 1984, H. Akagi et al. [6] introduced a new concept of instantaneous reactive power. It dealt with arbitrary 3 phase voltages and currents considering their distortion content. The instantaneous voltages and currents were represented as instantaneous space vectors on the a-b-c coordinate system, with the a,b,c vectors fixed on the same plane, apart from each other by 2 pi/3. These space vectors were then transformed along the

alpha-beta orthogonal coordinate system. The instantaneous real and reactive power defined along the alpha-beta coordinates have a DC and AC component. The AC component pertains to the reactive and harmonic current of the load. The instantaneous active and reactive power were computed on-line and the AC component was extracted with a suitable filter. The design of the extraction filter has a significant effect on the compensation characteristics of the active filter. With the choice of cut-off frequency, the AF can be made to compensate for only the harmonic current or the reactive current or both. However the theory was conceptually limited to three phase systems without zero-sequence currents.

A generalized instantaneous reactive power theory which is valid for sinusoidal or non-sinusoidal, balanced or unbalanced three phase power systems with or without zero-sequence currents was later proposed by F. Z. Peng and J. S. Lai [7]. Active filters controlled on the basis of instantaneous reactive power theory provided good compensation characteristics in steady state as well as transient states.

At the same time, the following problems of active filters were pointed out:

- It was difficult to realize high power PWM inverters with rapid current response and low loss for use as a main circuit of active filters.

- The initial cost was high as compared with that of passive filters, and active filters were inferior in efficiency to passive filters.

- Injected currents by shunt active filters may flow into shunt passive filters and capacitors connected to the power system.

Therefore attention was paid to combined or hybrid systems of active filters and shunt passive filters.

In [8], the authors presented a novel compensation scheme using a shunt active filter along with a conventional shunt passive filter. By sharing their roles so that the active filter absorbs lower order harmonic currents and the passive filter absorbs higher order ones, the active filter can fulfil its function with relatively small capacity, which brings an economical system. A lead function was introduced in its controller which brought about an interesting characteristic that the active filter can act as a damping device in a parallel resonance circuit formed by the passive filter and the power supply system. This made it possible to realize an ideal harmonic filter with no amplification due to the parallel resonance over a whole range of harmonic orders. Experimentally the technique was verified on a cycloconverter load (2 sets of 2800 kW), being compensated with a 900 kVA active filter and a 6600 kVA passive filter.

In [11], the authors proposed a combined system of a shunt passive filter and a small rated series active filter. The combined system gave better filtering characteristics and lower initial and running costs. The technique was verified on a 20 kVA 3-ph, thyristor load, compensated by a shunt passive filter of 10 kVA and a series active filter of 0.45 kVA. The function of the series active filter is not to directly compensate for the harmonics of the rectifier, but to improve the filtering characteristics of the shunt passive filter and to solve the resonance related problems of a passive filter used alone.

It was shown that the series AF acts as a "damping resistance" which could eliminate the parallel resonance between the shunt passive filter and the source impedance, and also acts as a "blocking resistance" which could prevent the harmonic current produced by the source harmonic voltage from flowing into the shunt passive filter.

A novel hybrid filter topology was presented by M. Rastogi, N. Mohan and A. E. Edris in [12]. A passive filter in series with an inverter operating in current controller mode was connected in shunt at the system bus. It was shown that the proposed filter has a rating of only 9% as compared to the converter in an active filter acting alone and approximately half of that of a series hybrid filter.

In [13], P. T. Cheng, Subhashish Bhattacharya and D. M. Divan presented a hybrid parallel active filter (HPAF). The AF implements square-wave inverters in series with

tuned passive L-C filters, to provide supply-load harmonic isolation at dominant harmonic frequencies (5<sup>th</sup> & 7<sup>th</sup>) and meets IEEE 519 harmonic standards for high power application. It was shown that small rated AFs (1%-2%) of the load rating, provide a practically viable and cost effective solution for high power non-linear loads upto 100 MW.

In [14], P. G. Barbosa, J. A. Santisteban and E. H. Watanabe proposed a shunt series active power filter. The AF consisted of a shunt AF connected to the AC side and a series AF connected to the DC side of a rectifier unit. The shunt AF was controlled to eliminate current harmonics in ac line currents and the series AF was controlled to cancel the output voltage ripple of the rectifier.

For moderate power ratings, active filters function well independently with small power rated filters connected to eliminate switching voltages and currents. Different control techniques like PWM carrier based error sawtooth control [8,11,19,20,23], hysteresis based dead band control [6,10,16,21], magnetic flux compensation have been proposed and experimentally verified.

In [15], an AF for a 3-phase controlled rectifier system was presented. The active filter comprised of a 3-phase voltage source inverter (VSI) with a DC bus capacitor source, connected in shunt to the AC source. The converter used 2 control loops. The outer control loop regulated the voltage across the DC bus capacitor, and generated reference phase AF currents. The inner control loop used sliding mode control to shape the AF currents in accordance with the reference currents.

In this work, the following assumptions were made:

- An infinite (strong) AC system was assumed. Since source impedance was not considered, the problem of voltage distortion at the terminal end does not occur.

- The line currents supplied by the source are in phase with the source voltages.

- An isolation transformer served as the connection impedance between the AF and the AC system.

The sliding mode control principle was used to check the state of the system at a constant decision frequency, and to generate appropriate gating signals for the AF switches.

The sliding mode control principle used is easy to implement, and sets an upper limit to the switching frequency. The authors gave a good analysis of the effect of decision frequency, DC bus voltage, and variation of load on the THD of source current, power factor and efficiency of the system. The AF was able to supply load harmonics and limit the source current THD to 12-13% at full load.

In [16], a different control scheme was used to estimate the reactive and harmonic content of the non-linear load. The system here too, comprised of a shunt connected 3-phase voltage source active filter.

But here also, the effect of source impedance was not considered. The non-linear load considered was a diode-rectifier feeding a capacitive load. The control scheme measured the active power requirements of the load on-line, and generated reference currents for the AF switches. The switching signals for the AF switches were generated by a hysteresis based controller. The scheme provided excellent performance in terms of limiting the THD of source current to less than 5% at full load, along with a good efficiency.

Although hysteresis controllers provide excellent current tracking, they inherently rely on having a variable switching frequency. However, a proper choice of the hysteresis band and the connection impedances limits the average switching frequency to within the switching constraints. The work also highlighted the fast response of the active filter to transient and load variations.

An interesting application of an active filter as a "load balancer" has been shown by V. B. Bhavaraju and P. N. Enjeti in [17]. An active filter based on a PWM-controlled static ac to dc converter topology with inductive load is designed to act as a continuous load balancer. The negative sequence component of load current is continuously measured

and an equal but opposite of this quantity is injected by the AF at the point of installation, thereby achieving the objective of continuous load balancing of unbalanced load.

#### 1.5 Proposed Approach

The objective of this thesis is to develop test models and control schemes for an active filter system. Practical difficulties in distribution system studies are realized by considering a weak AC system. A line impedance (20% base impedance) connects the AC source to the system AC bus. An active filter along with a small high pass AC filter is connected at the AC bus to filter current harmonics generated by nonlinear loads connected at the bus. Hysteresis based current control and sliding-mode control techniques are applied to the active filter and the performance of the system is compared under different test conditions.

#### 1.6 Thesis Outline

In Chapter 2, the concept of AFs is explained. The shunt active filter topology is selected, and its working principle is described. The distribution system test model considered is described. Each building block and its circuit configuration is discussed.

In Chapter 3, the control schemes implemented for active filter control are presented. The impact of circuit parameters, and controller elements on the AF performance is discussed.

In Chapter 4, simulation results for the system under steady and transient state are presented. The system model is tested under various AC-DC fault conditions, and its performance analyzed.

Finally, in Chapter 5, conclusions from this study, and recommendations for further work are provided.

## Chapter 2

## **System Configuration**

#### 2.1 Introduction

This chapter introduces the concept of active filters. The basic active filtering methodologies are explained. The system model considered to verify this technique is described. The various sub-units of the model and their circuit configurations are explained. The selection of an active filtering technique, for a weak AC distribution system is discussed.

#### 2.2 Active Filters [5]

Active filters are the modern approach to harmonics filtering. They act as ideal current or voltage sources connected in shunt or series with the AC supply to cancel harmonic terminal voltages or to supply harmonic currents produced by both the internal harmonic voltages of the supply and the nonlinear load.

The realization of these generators is accomplished by appropriately modulated switching circuits which operate in a self-sufficient manner from passive reactive storage elements (inductors, capacitors) without the need of a DC source. A number of control schemes like PWM, hysteresis-control, sliding-mode control etc. are used to generate switching signals for the controllable switching devices. The switching rate in these circuits is high enough to achieve good filtering characteristics in the low harmonic range, with distortion components shifted to higher frequencies where they may easily be

removed by passive filtering.

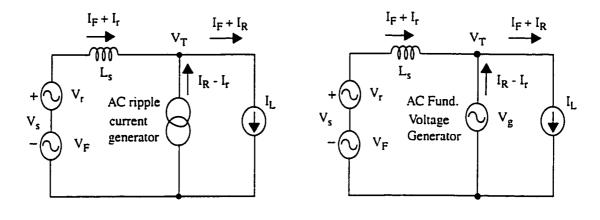

There are two basic filtering techniques - shunt and series filters [2]. The different topologies are shown in Fig. 2.1.

The system consists of a non-sinusoidal voltage source with a reactive internal impedance,  $(X_s = w.L_s)$ , supplying a nonlinear load. The AC source  $V_s$  with fundamental component  $V_F$  and internally generated ripple component  $V_p$  supplies a nonlinear load current  $I_L$ , with fundamental component  $I_F$  and harmonic component  $I_R$ .

$$V_s = V_F + V_r$$

$$I_{I} = I_{F} + I_{R}$$

In this general case, the distortion of the terminal voltage  $V_T$  is caused by both the internally generated source harmonics  $V_{\rm P}$  and the harmonic load current  $I_{\rm R}$  flowing through the source's internal impedance. An ideal filter should remove all the harmonics from the terminal voltage without affecting the flow of the fundamental load current  $I_{\rm F}$  from the AC source.

#### (i) Shunt ripple current generator

The shunt filters work on the concept of harmonic compensation. An ideal ripple current generator is connected in shunt at the terminal bus, as shown in Fig. 2.1(i). It supplies all the load harmonics ( $I_R$ ) and absorbs all the source harmonic current ( $I_r$ ). This ensures that no load harmonics flow through the source impedance and that no source harmonic current flows into the load. It therefore acts as a short circuit at all harmonic frequencies. Consequently, the terminal voltage  $V_T = V_F - I_F Z_s$ , is a pure sinusoidal voltage of fundamental frequency.

(i) Shunt ripple current generator

(ii) Shunt fundamental voltage generator

Fig. 2.1 Active Filter Topologies

#### (ii) Shunt fundamental voltage generator

An equivalent filtering technique is realized by an ideal voltage generator connected in shunt at the terminal bus (Fig. 2.1(ii)). It produces a voltage,  $V_g$  equal to the fundamental of the terminal bus voltage,  $V_T = V_F - I_F Z_S$ . As a result the load harmonics ( $I_R$ )

are restricted to flow through the shunt filter, and the ripple voltage  $(V_r)$  drops across the source impedance. The shunt filter thus absorbs the source harmonics  $(I_r)$  and supplies the load harmonics  $(I_R)$ , thereby maintaining a sinusoidal voltage at the terminal bus.

#### (iii) Series ripple voltage generator

This technique uses the concept of voltage cancellation. As shown in Fig.2.1(iii), a ripple voltage generator is connected in series with the source impedance. The terminal voltage  $V_T$  is the sum of the fundamental voltage,  $V_F$ , the internal source ripple voltage,  $V_T$  and the load ripple voltage,  $V_{XR}$  produced by the load current harmonics flowing through the source impedance  $X_s$ , i.e.  $V_T = V_F + V_r + V_{XR}$  (the voltage drop of  $I_F$  is not considered as it doesn't contribute to the filtering problem). The terminal ripple voltage can be cancelled by connecting a perfect ripple voltage generator,  $V_g = -(V_r + V_{XR})$  between the source and the load, producing a sinusoidal voltage at the terminal bus.

#### (iv) Series ripple current generator with series impedance

An equivalent technique is realized by using an AC ripple current generator as shown in Fig. 2.1(iv). Here the ripple voltage required is produced across the impedance  $Z_R$ , inserted between the AC source and the load, by an appropriate current generator having a ripple current component  $I_r$  such that  $I_r Z_R = -(V_r + V_{XR})$ . The current generator has another component,  $I_R$ , to ensure that the load ripple current bypasses the impedance  $Z_R$ .  $Z_R$  must exhibit negligible impedance for the fundamental load current  $I_F$  in order not to cause an appreciable fundamental voltage drop. Since the ripple voltage is cancelled, the terminal voltage,  $V_T$  becomes a fundamental harmonic voltage ( $V_T = V_F - I_F Z_s$ ).

#### 2.3 Active Filter Topology Selection

Theoretically perfect active filters can be realized by ideal current and voltage generators, connected in shunt or series configuration. In the practical realization of such generators, inverter circuits comprising of controllable switches are used. A DC current source in the form of a charged capacitor or inductor powers the inverter circuit. Appropriate modulation schemes are used to generate switching signals for the active filter to modulate required harmonic currents. The filtering characteristic can be improved indefinitely by increasing the switching frequency, but owing to switching rate limitation of semiconductor devices, a proper selection of AF parameters is essential. The switching inverters introduce high frequency distortion components, but these can be removed by passive filters.

Both the series and shunt topologies produce sinusoidal voltages at the terminal end by voltage cancellation or harmonic compensation, but it can be seen from Fig. 2.1 (iii&iv) that in series compensation the AC source carries the load harmonics,  $I_R$ , whereas in shunt compensation, Fig 2.1 (i&ii), the load harmonics are filtered locally at the terminal bus, leading to a source current consisting of only the fundamental load current,  $I_F$  and a small amount of source ripple current,  $I_r$  (if source voltage harmonics are considered).

For a distribution system model, the shunt filter topology is better suited as the load harmonics are not carried by the transmission lines connecting the AC source to the terminal bus, but are compensated locally by an active filter connected at the terminal bus.

Therefore, the shunt active filter topology has been selected in this work.

The shunt ripple current generator topology, as shown in Fig 2.1(i) was preferred over the shunt ripple voltage generator topology (Fig 2.1 (ii)), as an accurate value of source impedance ( $L_s$ ) is required for the second case in the evaluation of terminal voltage  $V_T$  ( $V_T = V_F - I_F Z_s$ ), and it would be of interest to have a control scheme that provides

compensation irrespective of source or line impedance.

The ripple current generator can be realized by a voltage source inverter (VSI) or a current source inverter (CSI). The voltage source inverter powered by a DC bus capacitor is preferred to an inductor powered current source inverter, because a VSI is higher in efficiency and lower in cost than a CSI.

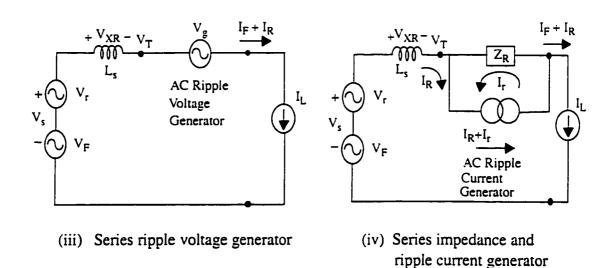

#### 2.4 System Model

The system model considered here to verify the active filter control technique is shown in Fig. 2.2. The system considered is 3 phase and a one-line diagram is shown in the figure. The base quantities for the system taken are:

1 p.u. voltage = 100 Volts

1 p.u. current = 1 Amp

The system has been modeled for 60 Hz line frequency.

It can be divided into the following sub-units:

- 1. AC side of the system

- 2. DC side of the system

- 3. Active Filter

- 4. Control Circuits

#### 1) AC side of the system

The AC side of the system consists of the distribution system and an AC filter connected to the system terminal AC bus. The system bus is separated from the DC side of the system by an isolation transformer.

i) Distribution System: The distribution system is represented by its simplified Thevenin equivalent circuit. The AC source phase voltage taken is 1 p.u.. A weak AC system is assu-

Fig. 2.2 System Model

med with a typical source impedance of 20% base impedance. The impedance is primarily inductive, and a small value of resistance is assumed using a typical quality factor of 50.

ii) AC filter: A high pass AC filter is connected at the system bus to filter out high switching frequency currents introduced by the active filter. The AC filter is of high pass type, and is tuned to the 12<sup>th</sup> harmonic. The filter components calculation are shown in Appendix A. Fig 2.3 shows the filter circuit configuration.

Fig. 2.3 High Pass Filter

iii) Isolation: The AC side of the system is isolated from the DC side by a 3 phase starstar isolation transformer. The transformer line impedance is taken as 20% of base impedance and is divided equally on the primary and secondary side. The impedance is taken as being primarily inductive, and a small value of resistance is assumed.

#### 2) DC side of the system

The DC side of the system comprises of a converter unit and an inductive load.

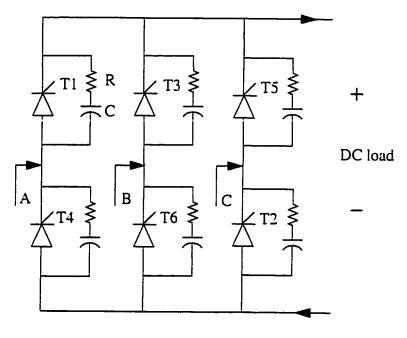

i) Converter unit: This unit comprises of a 3 phase current controlled rectifier (Fig. 2.4). The rectifier performs conversion of AC bus voltage to DC voltage, which feeds an inductive load. A current controller maintains the output DC current close to its reference value.

The DC controller generates appropriate firing signals for each of the thyristors. The thyristor switches are protected from over-voltages by connecting R-C snubbers across them.

Fig. 2.4 Converter unit

ii) DC load: The DC load of the system comprises of a resistor load  $R_{dc}$ =120 ohms and a smoothing reactor  $L_{dc}$ =300 mH in series. The high inductance value smooths the ripple in the DC current and prevents it from becoming discontinuous at light loads.

#### 3) Active Filter

The active filter unit comprises of an inverter and connection impedances. The active filter supplies the harmonics and reactive power, thus enabling the AC source to supply only the active power component of the nonlinear load.

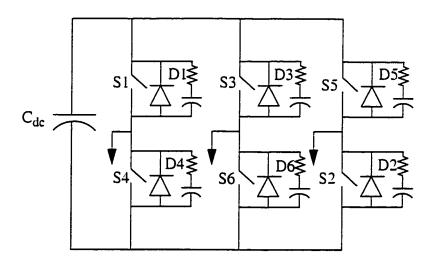

i) Inverter unit: The AF consists of a 3 phase voltage source inverter (Fig. 2.5). The inverter switches are made bidirectional by connecting anti-parallel diodes across the

switches. Snubbers are connected across the switch-diode pair to protect the devices from dv/dt and di/dt stresses. The inverter is sourced by a DC bus capacitor,  $C_{dc}$ , the voltage of which is maintained at a fixed level to overcome the switching and conduction losses incurred by the AF providing harmonic compensation. The AC source replenishes the energy lost by the AF during compensation period.

Fig. 2.5 Voltage Source Inverter unit

The choice of switching devices for the inverter depend on the power level of compensation provided by the AF. For medium power application, IGBTs, and for high power application GTOs are suitable. The choice of switching device sets an upper limit to the frequency of operation for the inverter circuit. A GTO inverter can operate to a limit of around 5 kHz, whereas an IGBT inverter may operate upto 80 kHz.

- ii) Connection impedances: The active filter is connected to the system bus through series R-L impedances. The connection impedances serve 2 purposes:

- 1. They separate the high frequency switching AF end terminals from the system bus by

taking the switching voltage harmonics drop across them.

2. They serve an important role in wave shaping the AF line currents about their reference currents.

The component values for the connection impedances are decided upon by the switching frequency constraint imposed by the inverter switching devices. The design of connection impedances is discussed in Chapter 3.

#### 4) Control Circuits

The system comprises of 2 control units.

#### i) Rectifier Control Unit

The Rectifier Control unit consists of a PI current controller that maintains the DC output current close to its reference value by generating appropriate triggering pulses for the rectifier thyristors.

#### ii) AF Control Unit

The AF controller consists of an on-line power controller and a tracking controller. The on-line power controller computes the reference currents for the active filter to generate so as to supply the reactive and harmonic current of the nonlinear load. The tracking controller compares the actual AF line currents with the reference currents and generates switching signals for the inverter switches to modulate the reference currents. Different tracking control techniques are available to do so. Hysteresis-band control and sliding-mode control were implemented in this work. The control philosophy for both the schemes is discussed in Chapter 3 and performance of the controllers under different test conditions is demonstrated in Chapter 4.

### 2.5 Summary

This chapter introduced the concept of active filters. The different techniques of active filtering were stated and the shunt ripple-current generator AF topology was selected for a weak AC distribution system. The test system considered to model a weak AC distribution system was described. Also the various sub-units of the test system and their configurations were elaborated.

## Chapter 3

### **Control Circuits**

#### 3.1 Introduction

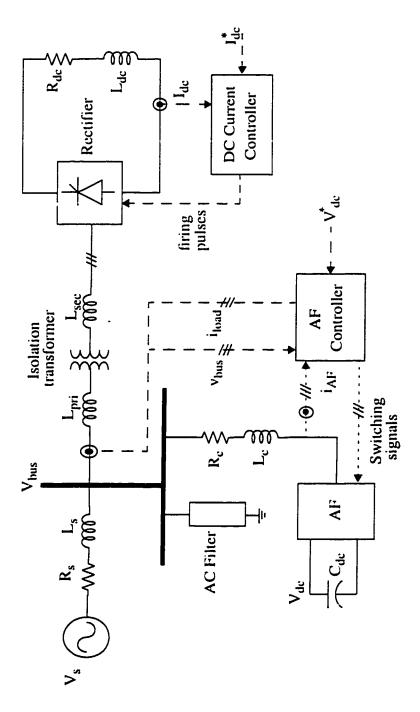

In this chapter, control circuits of a distribution system operating with a weak AC source are presented. The control circuit consists of a rectifier control unit and an AF control unit.

The rectifier control unit controls the output DC current by generating an appropriate firing angle. A gate firing unit generates firing pulses for each of the rectifier thyristors.

The AF control unit comprises of two controllers. The feed-forward controller implements the on-line power computation scheme to compute the active power drawn by the load. It calculates the reference currents for the AF to supply the reactive and harmonic current required by the nonlinear load.

The feedback controller tracks the AF currents close to the reference currents. Tracking control is demonstrated by two methodologies - hysteresis control and sliding-mode control. The controller design and parameter selection is discussed.

#### 3.2 Rectifier Control Unit

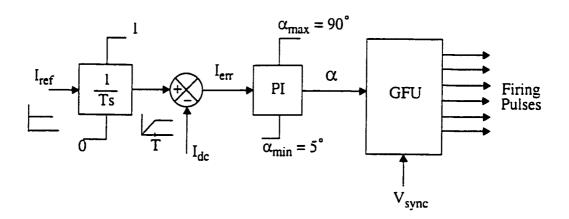

The rectifier control unit maintains the output DC current close to the current order  $I_{ref}$ . It consists of a PI controller that generates an alpha order or firing angle shift, appropriate to load requirements. The alpha order is fed to a Gate Firing Unit that generates firing pulses for each of the rectifier thyristors. The block diagram of the rectifier control unit is

shown in Fig. 3.1.

The current order  $I_{ref}$  is a step function. It is fed to an integrator-limiter to get a ramp-step signal. This prevents the DC current to shoot up at start, and provides a smooth initialization for the rectifier system. It is then compared with the measured output current  $I_{dc}$  to give an error signal  $I_{err}$ . The error signal is fed to a PI block that generates the firing angle order,  $\alpha$  (alpha). The Gate Firing Unit (GFU) block takes the alpha order and synchronous bus voltages to generate firing pulses for the rectifier thyristors. Phase locked loop (PLL) filters were used to extract synchronous sinusoidal voltage signal  $V_{sync}$ , from the system AC bus voltage which suffers from high harmonic distortion, inherent in weak AC systems.

Fig. 3.1 Rectifier Control Unit

### 3.3 AF Control Unit

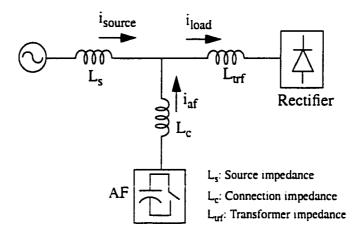

The system model including the active compensator is shown in Fig. 3.2.

The AF control unit controls the operation of the shunt active filter. It ensures that the AF, in steady state, provides all the harmonics and reactive current demand of the rec-

tifier load.

Fig 3.2 System model

The rectifier load current iload can be expressed in fourier series as

$$i_{load} = \Sigma 4 \frac{I_{dc}}{n\Pi} \sin\left(\frac{n\Pi}{2}\right) \sin\left(\frac{n\Pi}{3}\right) \sin(nw_0 t)$$

$$n = 1.5.7...$$

where I<sub>dc</sub> is the output DC current.

The fundamental harmonic of load current consists of an active and a reactive component. In steady state the AC source should supply only the active component of the load fundamental harmonic, and the reactive component and higher harmonics be supplied by the AF.

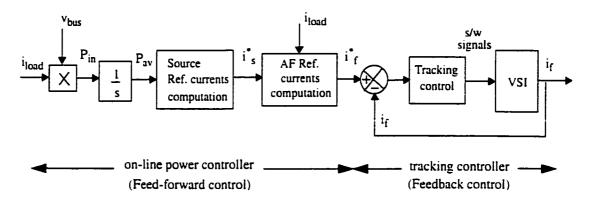

The AF control unit consists of a feed-forward and a feedback controller. The feed-forward controller implements the on-line power computation scheme. It measures AC bus voltages and line currents on-line and computes AF reference currents ( $i_f^*$ ), which are fed to the feedback controller. The feedback controller (tracking control) ensures tracking of AF currents ( $i_f$ ) about their reference values. The feedback loop is a faster control loop

and implements either hysteresis-based control or sliding-mode control. The block diagram of the AF control unit is shown in Fig. 3.3.

Fig. 3.3 AF control unit

## 3.3.1 On-line power computation scheme (Feed-forward Control)

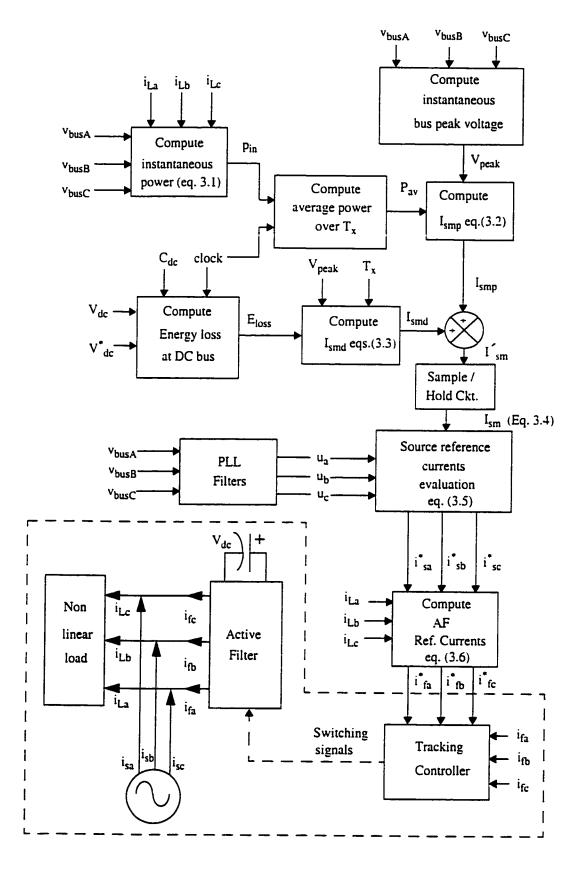

The on-line power computation scheme is a feed-forward control that computes reference currents for the feedback controller by measuring AC line currents and bus voltages on-line. Fig 3.4 shows the schematic of the AF Control Unit: on-line power controller and tracking controller (segmented block).

The scheme computes on-line, the average power consumed by the load. The measured instantaneous bus phase voltages  $v_{busA}$ ,  $v_{busB}$ ,  $v_{busC}$  and line currents  $i_{La}$ ,  $i_{Lb}$ ,  $i_{Lc}$  are fed to a block that computes the instantaneous power  $p_{in}$  given by

$$p_{in} = v_{busA} * i_{La} + v_{busB} * i_{Lb} + v_{busC} * i_{Lc}$$

(3.1)

Since it is a 3 phase, 6 pulse rectifier system, the instantaneous power is periodic at 6 times the line frequency. A clock cycle of 6 times the line frequency is taken to provide

Fig 3.4 AF Control Unit Schematic

computational instants and timing reference for the scheme.

The instantaneous power is averaged over 1 clock period  $T_x$ . This average power  $P_{av}$  should be supplied by the AC source as a fundamental frequency current  $i_{smp}$  at unity power factor. Therefore the average power supplied can also be expressed as

$$P_{av} = 3/2 * V_{peak} * I_{smp}$$

(3.2)

where  $V_{peak}$  is the bus peak voltage and  $I_{smp}$  is the peak value of  $i_{smp}$ . The system measures the bus peak voltage,  $V_{peak}$ , at all instants as the bus voltage may fluctuate with load variations. Since the  $P_{av}$  has been computed over 1 clock cycle and the  $V_{peak}$  is measured on-line, the  $I_{smp}$  value can be calculated from eq. (3.2).

The AC source should also supply the losses occurring in the AF due to switching and conduction. A reference voltage  $V_{ref}$  is set for the DC bus, high enough to pump harmonics into the system bus (Appendix B1.3). The energy lost due to switching and conduction can be estimated by the voltage dropped across the DC bus capacitor,  $V_{dc}$ . The energy loss during one clock cycle is given by

$$E_{loss} = 1/2 * C_{dc} * (V_{ref}^2 - V_{dc}^2)$$

(3.3a)

This energy lost is replenished by the AC source which supplies an additional fundamental harmonic current  $i_{smd}$  at unity power factor to meet the AF losses.  $E_{loss}$  can also be expressed as

$$E_{loss} = 3/2 * V_{peak} * I_{smd} * T_x$$

(3.3b)

where I<sub>smd</sub> is the peak value of i<sub>smd</sub>.

Eqs. 3.3 a,b can be equated to yield  $I_{smd}$ .

The  $I_{smp}$ ,  $I_{smd}$  values are sampled signals computed at each clock cycle.

The sampled peak value,  $I'_{sm}$  of total current supplied by the AC source is given by

$$I'_{sm} = I_{smp} + I_{smd}$$

(3.4)

The sampled peak value signal  $I'_{sm}$  is fed to a Sample/Hold circuit to generate a continuous peak value signal  $I_{sm}$ .

To generate sinusoidal waveforms for each of the source reference currents, unit amplitude sinusoidal template waveforms are required. It is further required that the source current should be at unity power factor, i.e. the nonlinear load should present a unity power factor sinusoidal load to the AC source. Phase locked loop (PLL) filters extract the fundamental harmonic component from the bus phase voltages to generate synchronous voltages (without any phase shift), which are further scaled to generate unit amplitude template waveforms  $u_a$ ,  $u_b$ ,  $u_c$ . The source reference currents  $i^*_{sa}$ ,  $i^*_{sb}$ ,  $i^*_{sc}$  are obtained by multiplying the template signals with the continuous peak source current  $I_{sm}$ .

$$i_{sa}^* = I_{sm}^* u_a$$

$$i_{sb}^* = I_{sm}^* u_b$$

$$i_{sc}^* = I_{sm}^* u_c$$

(3.5)

The AF reference currents  $i_{fa}^*$ ,  $i_{fb}^*$ ,  $i_{fc}^*$  are generated by subtracting the source reference currents from the load line currents. (Note: The AF is considered as a harmonic source here).

$$i_{fa}^* = i_{La} - i_{sa}^*$$

$$i_{fb}^* = i_{Lb} - i_{sb}^*$$

$$i_{fc}^* = i_{Lc} - i_{sc}^*$$

(3.6)

As shown in the segmented block in Fig 3.4, the tracking controller compares the reference currents with the actual AF currents, and appropriate switching signals are generated for the inverter circuit to achieve close tracking of the reference values.

## Validation of On-line Power Computation Scheme

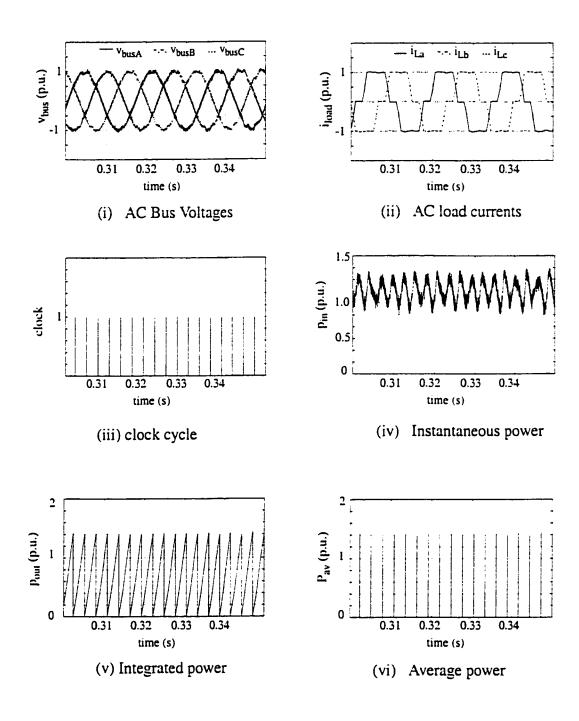

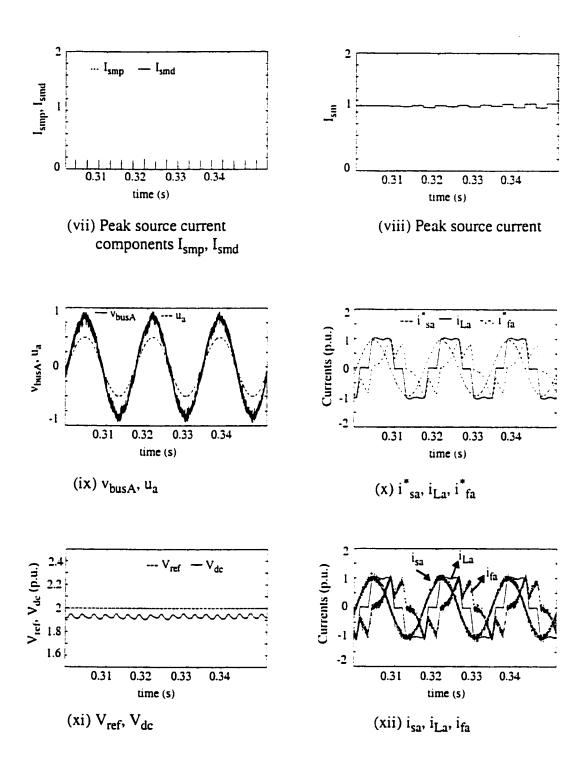

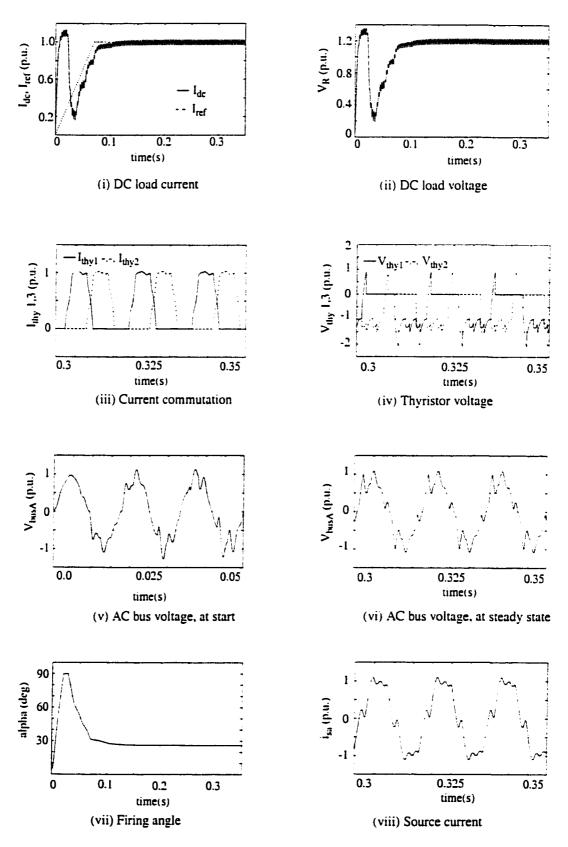

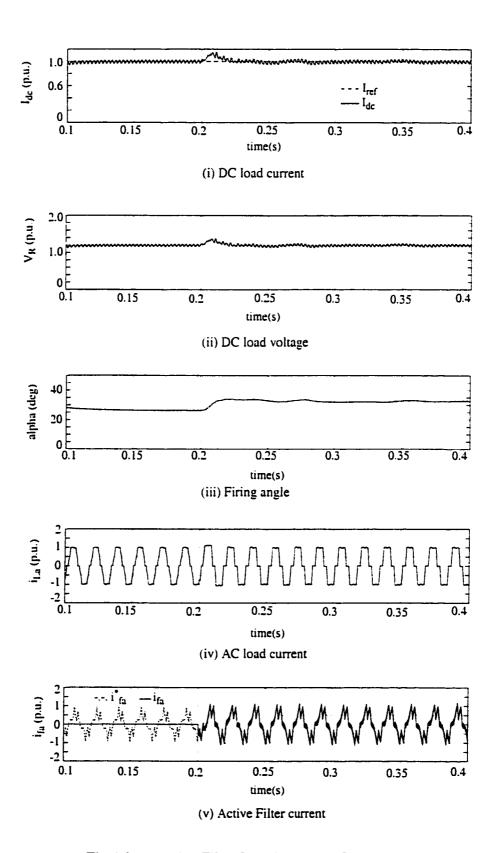

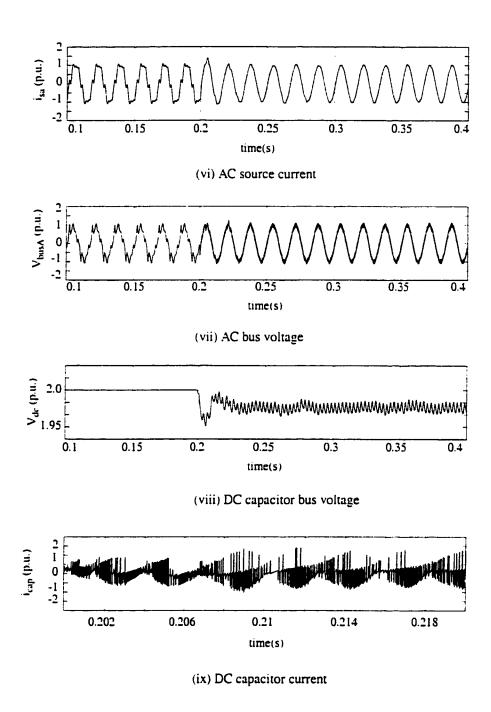

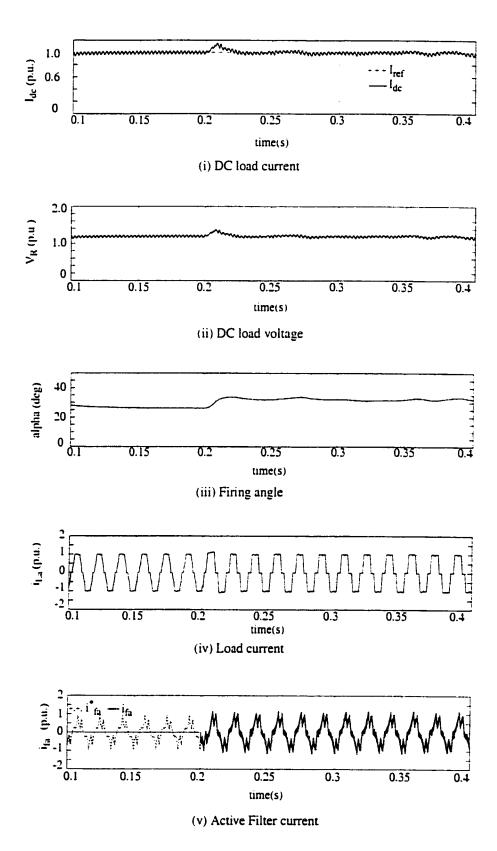

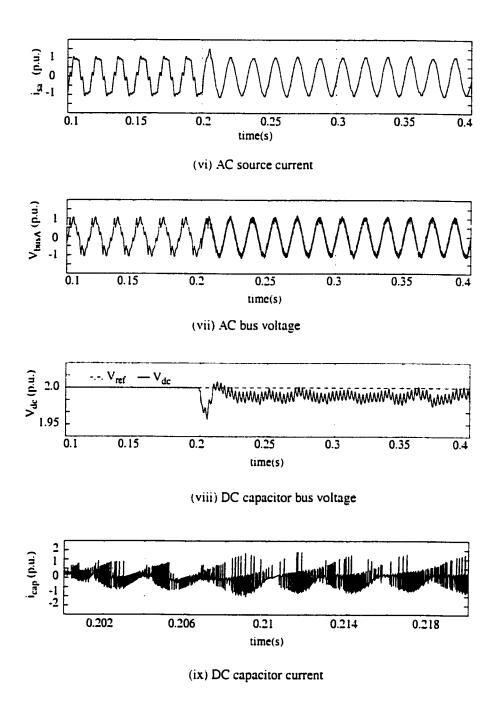

Fig. 3.5 shows the simulation of the on-line power computation scheme. Plots (i)&(ii) show the three phase bus voltages and the AC load currents. A clock signal of 6 times the line frequency is chosen. Computation is performed at each clock pulse. The instantaneous power  $p_{in}$  oscillates at 6 times the line frequency. A high frequency ripple is observed along with characteristic  $6^{th}$  harmonic of 6-pulse three-phase systems. This is due to distortion in the system bus voltage caused by high frequency switching currents injected by the active filter. The instantaneous power  $p_{in}$  is fed to a reset integrator that integrates it over one clock period to generate  $p_{out}$  and resets at the next clock pulse. The average power  $P_{av}$  is obtained by sampling the  $p_{out}$  signal at clock frequency. The peak source current components  $I_{smp}$  and  $I_{smd}$  are computed at the clock instants. The sampled peak source current ( $I_{smp}+I_{smd}$ ) is fed to a sample-hold circuit to generate a continuous peak value,  $I_{sm}$ .

Synchronized voltage signals are obtained from the bus voltages by PLL filters and are further scaled to produce unit amplitude template voltages  $u_a$ ,  $u_b$ ,  $u_c$ . In the plot (ix), the signals  $u_a$ ,  $u_b$ ,  $u_c$  have been scaled by 50% to show that they lie in phase with the bus voltages and are free from distortion.

The unit template voltages are multiplied with the continuous peak source current  $I_{sm}$ , to generate sinusoidal source reference currents  $i^*_{sa}$ ,  $i^*_{sb}$ ,  $i^*_{sc}$  at unity power factor. The difference of source reference currents from load currents gives the active filter reference currents  $i^*_{fa}$ ,  $i^*_{fb}$ ,  $i^*_{fc}$ . It can be observed from plot (xii) that the active filter currents  $i_{fa}$ ,  $i_{fb}$ ,  $i_{fc}$  track the reference currents very closely.

The source current, isa is sinusoidal at unity power factor with a high frequency

ripple superimposed due to switching errors. The high frequency ripple current is filtered by the AC high pass filter attached at the AC bus, and a harmonic free sinusoidal current flows in the source phase.

At steady state the DC bus voltage maintains itself at a constant level, consistent with the voltage difference necessary to replenish the losses incurred by the DC capacitor during switching and conduction. During transient conditions the DC bus voltage may exceed or go below the reference voltage, as per the energy transaction between the active filter and the load.

Fig 3.5 Simulation of On-line Power Computation Scheme

Fig 3.5 contd. Simulation of On-line Power Computation Scheme

### 3.3.2 Tracking Control (Feedback control)

The tracking control is a feedback control that compares the actual AF currents with the reference currents and generates switching signals for the AF to regulate them. The switching signal generation depends on the control law implemented. Two control laws have been tested.

- (a) Hysteresis control

- (b) Sliding-mode control

### 3.3.2.1 Hysteresis control

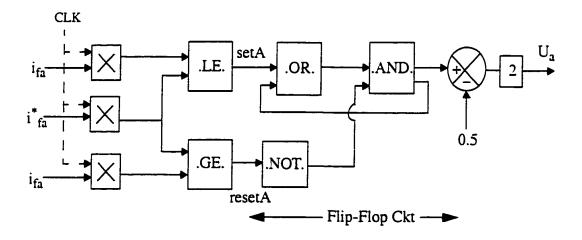

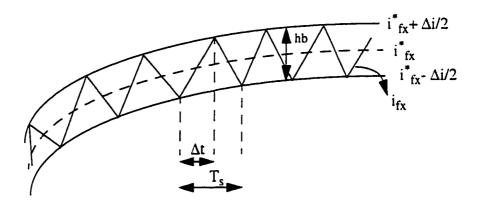

In this control technique, a tolerance or hysteresis band is drawn about the reference current, and the AF current is restricted within the band. The hysteresis bandwidth, hb, chosen corresponds to the ripple allowed in the AF current. Switching functions  $U_a$ ,  $U_b$ ,  $U_c$  are generated for each of the phases independently.

The switching function is a bipolar function (1 or -1) and changes state as the AF current reaches the upper or lower hysteresis band limits.

The switching logic for phase a is as follows:

(i)

$$i_{fa} < (i_{fa}^* - hb/2)$$

(U<sub>a</sub> = +1) (3.7a)

i.e. when the AF current reaches the lower band limit, the inverter supplies less current than required. The upper s/w goes ON and lower switch goes OFF, connecting the DC bus capacitor to the AC bus. The DC bus maintained at higher voltage is able to boost the phase current, thus causing it to rise. The switching function becomes unity  $(U_a = +1)$ .

(ii)

$$i_{fa} > (i_{fa}^* + hb/2)$$

(U<sub>a</sub> = -1) (3.7b)

i.e. when the AF current exceeds the upper band limit, the inverter supplies more current than required. The upper s/w goes OFF and lower s/w goes ON, removing the DC bus capacitor from the phase circuit. The switching function reverses sign ( $U_a = -1$ ). As the DC source is removed from the phase, the current begins to fall.

Thus, the hysteresis controller is able to regulate the rise and fall of AF currents within tolerance limits about the reference currents, by appropriately switching the inverter legs.

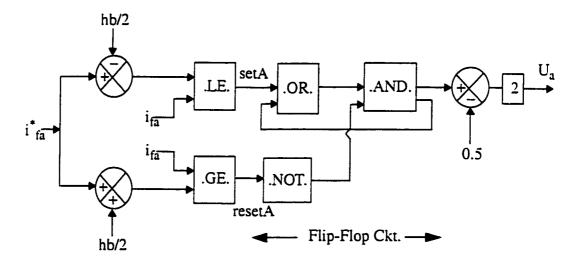

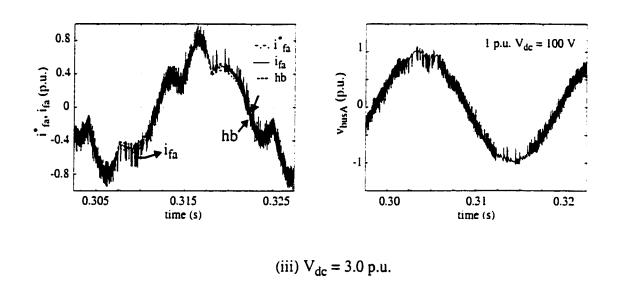

The implementation of hysteresis control is shown as a block diagram in Fig. 3.6. A hysteresis band of width hb is drawn about the reference current  $i^*_{fa}$ . A detection circuit checks when the AF current exceeds band-limits. The setA signal goes high when the AF current becomes equal to or less than the lower band limit ( $i^*_{fa}$ - hb/2). The resetA signal goes high when the AF current exceeds the upper band limit ( $i^*_{fa}$ + hb/2). The setA and resetA signals are fed to a flip-flop circuit, that gives out the switching function  $U_a$ .

Fig 3.6 Hysteresis controller implementation

The switching functions  $U_b$  and  $U_c$  for phases b and c are determined similarly, using the corresponding reference and measured currents and the hysteresis band hb.

Fig. 3.7 shows the hysteresis control tracking of reference current  $i_{fa}^*$  within the hysteresis band.

Fig 3.7 Simulation of Hysteresis Controller

The inverter switching frequency depends on the frequency at which the AF current hits the hysteresis band limits. This frequency is variable in nature as the variation of current within the hysteresis band is dependent on circuit parameters. The waveshaping of current within the band limits depends upon the hysteresis band width, the connection inductance and the DC bus voltage of the AF inverter. The circuit and control parameters have to be chosen such that the switching frequency doesn't exceed the limit imposed by semiconductor switches, but is high enough to provide good modulation of reference cur-

rents.

The maximum switching frequency attained by the inverter can be estimated by the relationship (Appendix B1.5):

$$f_{\text{max}} = \frac{V_{\text{dc}}}{(2L_c \cdot \text{hb})}$$

(3.8)

This relationship is derived for the maximum switching frequency, but since for the hysteresis control technique the switching frequency is variable, the above expression can be approximated for the average switching frequency. From the above relationship, it may be observed that the average switching frequency  $f_{av}$  depends on the following factors:

### (i) Hysteresis bandwidth, hb

The hysteresis bandwidth corresponds to the ripple allowed in the AF current. Keeping other factors constant, an increase in the bandwidth causes the AF current to hit the tolerance limits less frequently, thus reducing the switching frequency. Whereas a decrease in the bandwidth causes the AF current to hit the tolerance limits more often thus increasing the inverter switching frequency. In terms of performance, a smaller hysteresis bandwidth causes the AF current to track the reference current more closely. The magnitude of switching error currents introduced at the system bus reduces, the switching frequency shifts to higher ranges thus improving the THD of system bus voltage.

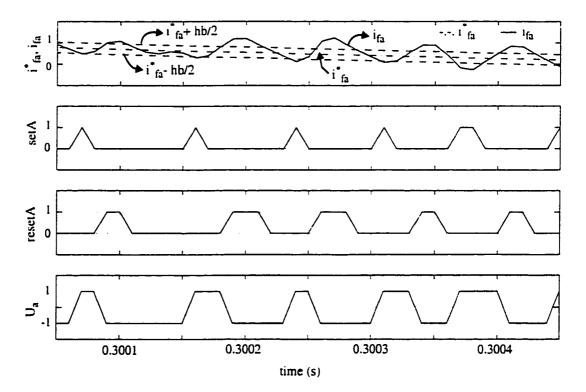

Table 3.1 and Fig. 3.8 show the effect of variation of hysteresis bandwidth on the inverter switching frequency and the THD of bus voltage.

It can be observed that the average switching frequency decreases and the  $V_{bus}$  THD deteriorates with increasing bandwidth. Fig 3.9 shows simulation results for different values of hysteresis bandwidths chosen.

Table 3.1: Variation of Hysteresis Bandwidth, hb

| Hysteresis<br>Bandwidth<br>hb (% I <sub>base</sub> ) | Avg. Switching<br>Frequency<br>(kHz) | V <sub>bus</sub><br>THD% |

|------------------------------------------------------|--------------------------------------|--------------------------|

| 1%                                                   | 15.75                                | 2.36                     |

| 2%                                                   | 14.65                                | 3.09                     |

| 5%                                                   | 10.25                                | 3.46                     |

| 10%                                                  | 8.25                                 | 3.85                     |

| 20%                                                  | 4.95                                 | 5.65                     |

Average switching freq. (kHz) V<sub>bus</sub> THD% Hysteresis Bandwidth (%Ibase) Hysteresis Bandwidth ( $\%I_{base}$ ) (i)  $f_{av}$  vs. hb (ii)  $v_{bus}$  THD% vs. hb

Fig. 3.8 Variation of Hysteresis Bandwidth

It is noted that the AF performance and switching frequency is very sensitive to the hysteresis bandwidth.

Fig 3.9 Effect of variation of Hysteresis bandwidth, hb

## (ii) Connection impedance inductance, L<sub>c</sub>

The connection impedance plays an important role in shaping the AF current within the hysteresis band. A large value of inductance, decreases the rate of change of current within the tolerance band, thus reducing the switching frequency. Whereas a smaller value of  $L_c$  would allow more frequent changes in the AF current, thus increasing the switching frequency.

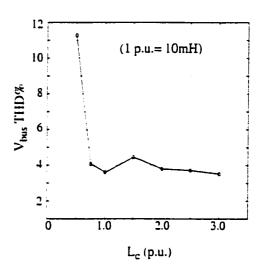

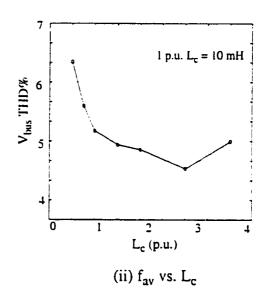

Table 3.2 and Fig 3.10 show the effect of variation of connection inductance on the switching frequency and the THD of bus voltage. It may be observed from Fig. 3.10 (i) that the switching frequency decreases with an increase in  $L_c$ . This can be naturally expected, since an increase in  $L_c$  reduces the rate of change of AF current within the hysteresis band.

An increase in the inverter switching frequency does not necessarily indicate better performance in terms of THD. At a high switching frequency of 10.25 kHz, the THD is unexpectedly high. This is so because the  $L_c$  value is very low, and the low impedance is unable to contain the AF current within the hysteresis band, inspite of corrective action taken by the tracking controller. As a result the switching error currents, although shifted to high frequencies, have greater magnitude and produce larger distortion at the system bus.

Table 3.2: Variation of Connection inductance,  $L_c$

| Connection Inductance L <sub>c</sub> (1p.u=10mH) | Avg.<br>Switching<br>Freq.(kHz) | V <sub>bus</sub><br>THD% |

|--------------------------------------------------|---------------------------------|--------------------------|

| 0.5                                              | 10.25                           | 10.28                    |

| 0.75                                             | 8.55                            | 3.07                     |

| 1.0                                              | 7.65                            | 2.6                      |

| 1.5                                              | 5.80                            | 3.45                     |

| 2.0                                              | 4.95                            | 2.79                     |

Table 3.2: Variation of Connection inductance, L<sub>c</sub>

| Connection Inductance L <sub>c</sub> (1p.u=10mH) | Avg.<br>Switching<br>Freq.(kHz) | V <sub>bus</sub><br>THD% |

|--------------------------------------------------|---------------------------------|--------------------------|

| 2.5                                              | 3.85                            | 2.71                     |

| 3.0                                              | 3.30                            | 2.52                     |

(i) L<sub>c</sub> vs. switching freq. f<sub>av</sub>

(ii) L<sub>c</sub> vs. V<sub>bus</sub> THD%

Fig. 3.10 Variation of L<sub>c</sub>

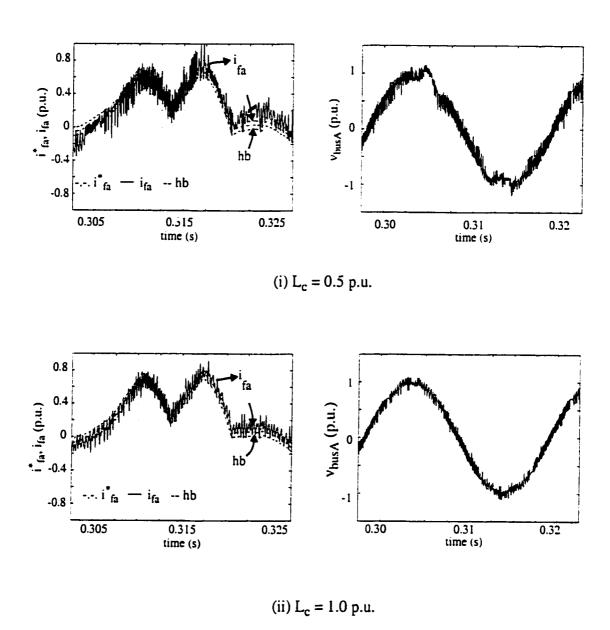

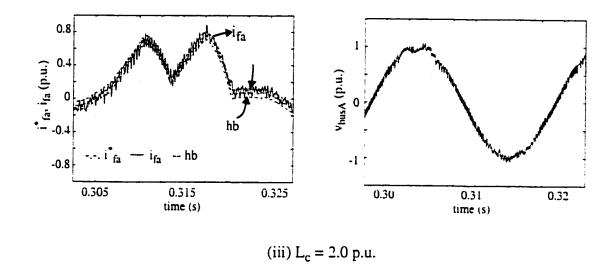

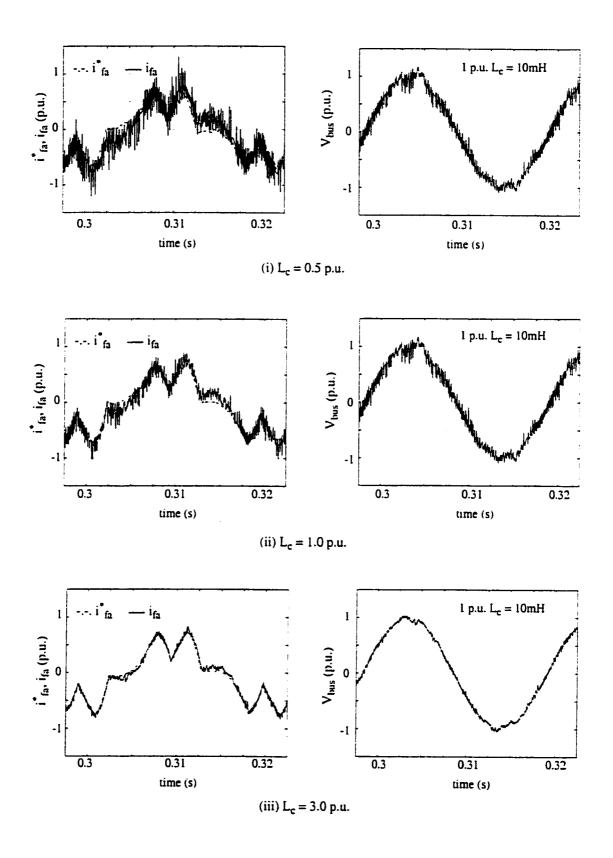

Fig 3.11 shows the modulation of AF current within hysteresis band for different values of  $L_{\rm c}$ .

Ideally it may be expected that a higher switching frequency would shift the switching error components to higher frequencies improving the THD. But simulation results show that THD remains more or less constant. At a low value of  $L_c$ , the switching frequency is high, but the magnitude of switching error currents is higher. Therefore the THD in this case is contributed by higher frequency switching error currents of larger magnitude. At a higher value of  $L_c$ , the switching frequency is low. The THD is contrib-

uted by lower order switching error currents with smaller magnitude, keeping it almost constant for  $L_{\rm c}$  values greater than 0.75 p.u.

Fig 3.11 Effect of variation of  $L_c$

Fig 3.11 contd. Effect of variation of L<sub>c</sub>

# (iii) DC bus capacitor voltage V<sub>dc</sub>

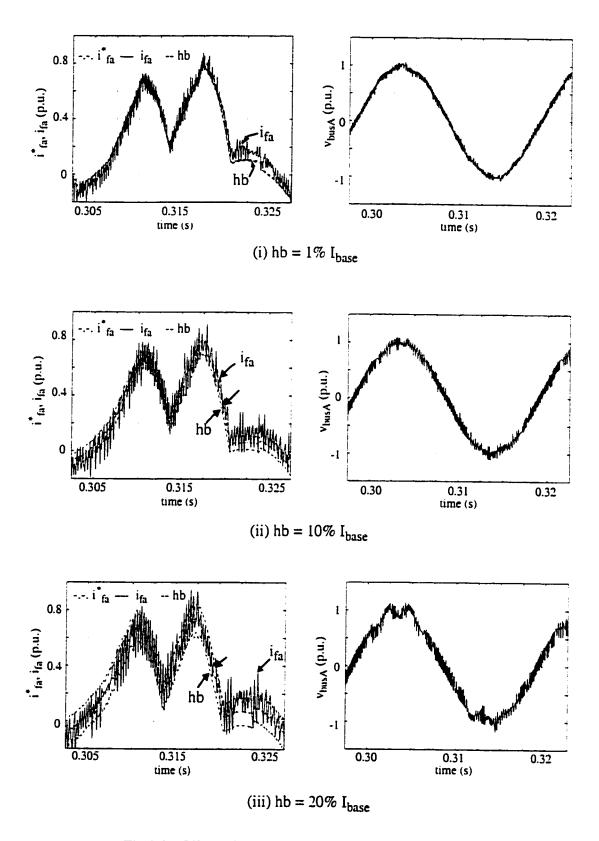

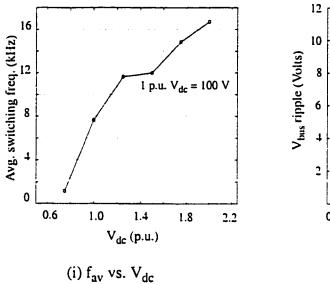

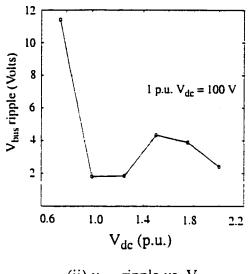

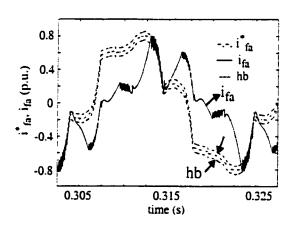

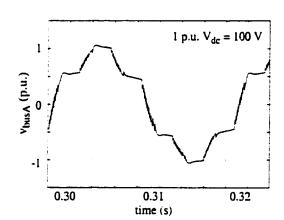

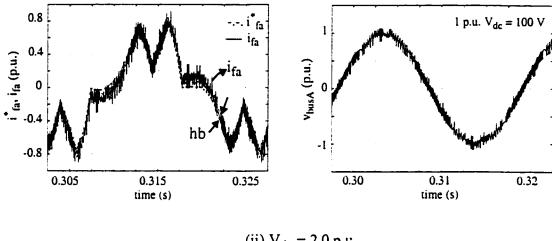

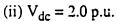

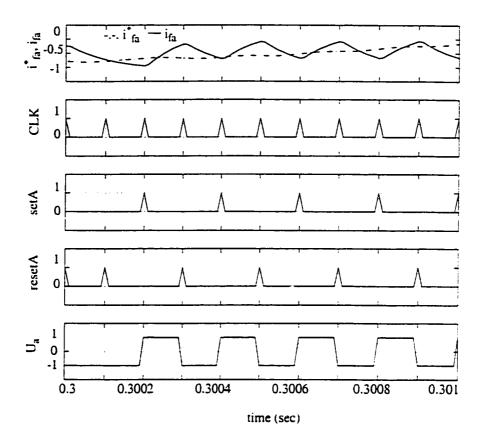

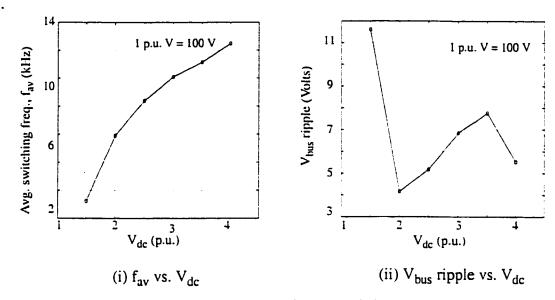

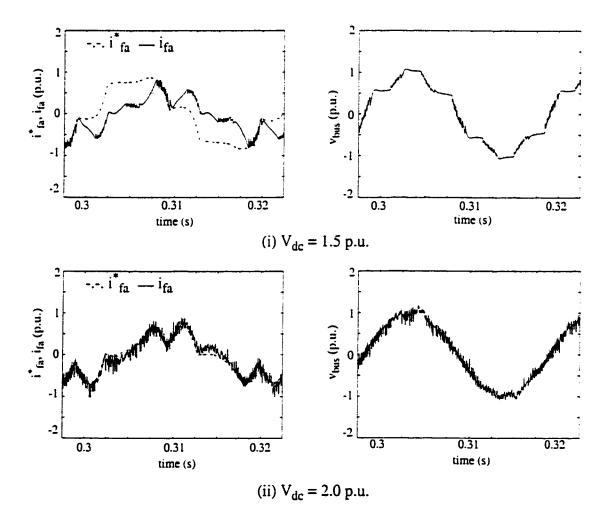

The DC bus voltage  $V_{dc}$ , must be maintained at a minimum level, so as to have sufficient power to modulate AF currents about their reference values. For independent phase control, the DC bus voltage must be minimum 2 times the system AC bus peak voltage (Appendix B1.3). A voltage level higher than the minimum level gives the DC capacitor higher energy to modulate the AF current, thus increasing the switching frequency. Table 3.3 and Fig 3.12 show the effect of variation of  $V_{dc}$  on the average switching frequency and the  $V_{bus}$  ripple voltage.

An increase in the DC bus voltage increases the rate of change of current, thus increasing the switching frequency (Fig. 3.12 i). The  $V_{bus}$  THD is not a correct measure for performance in this case. This is so because an increase in  $V_{dc}$  leads to an increase of  $I_{smd}$  component (Eqns. 3.3 a,b) of source current and a greater voltage drop across source

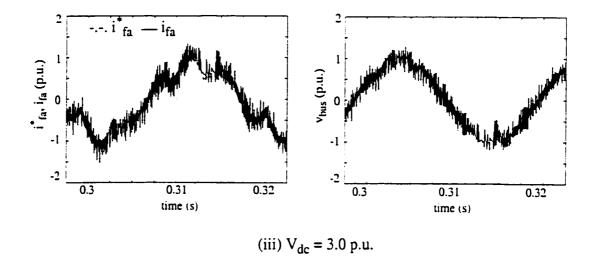

impedance. The bus fundamental voltage component gets reduced and although the ripple voltage reduces with the increase in  $V_{dc}$ , the THD shows an increase. The bus ripple voltage reflects the AF performance in this case. Fig 3.13 shows the modulation of AF current for different  $V_{dc}$  values.

It may be observed (Fig 3.13 1) that at a voltage level of 1.5 p.u. (lower than the minimum level of 2.0 p.u.), the AF reference current departs from its usual waveform, as the distortion at AC bus is high. The AF modulates its currents about their reference values only when the DC bus voltage exceeds the AC bus voltage. At other instants it falls out of tracking, leading to higher switching error currents and higher THD at system bus voltage.

The  $V_{bus}$  ripple voltage shows a general decline with an increase in  $V_{dc}$ , but for higher values of  $V_{dc}$  (beyond 1.4 p.u.), the DC bus has higher energy to modulate the AF current, and the high rate of di/dt causes the AF currents to exceed the hysteresis bandlimits. This leads to greater switching error currents and higher ripple in  $V_{bus}$ .

Table 3.3: Variation of DC bus voltage, V<sub>dc</sub>

| V <sub>dc</sub> (p.u.)<br>(1 p.u.=100 V) | Avg.<br>Switching<br>Freq. (kHz) | V <sub>bus</sub><br>THD% | RMS V <sub>bus</sub><br>ripple<br>(Volts) | RMS V <sub>bus</sub><br>fundamental<br>(Volts) |

|------------------------------------------|----------------------------------|--------------------------|-------------------------------------------|------------------------------------------------|

| 1.5                                      | 1.15                             | 16.6                     | 11.41                                     | 68.74                                          |

| 2.0                                      | 7.65                             | 2.61                     | 1.81                                      | 69.82                                          |

| 2.5                                      | 11.65                            | 2.67                     | 1.85                                      | 69.02                                          |

| 3.0                                      | 12.0                             | 6.40                     | 4.34                                      | 67.85                                          |

| 3.5                                      | 14.85                            | 5.91                     | 3.89                                      | 65.88                                          |

| 4.0                                      | 16.7                             | 3.83                     | 2.41                                      | 62.86                                          |

(ii)  $v_{bus}$  ripple vs.  $V_{dc}$

Fig 3.12 Variation of V<sub>dc</sub>

(i)  $V_{dc} = 1.5 \text{ p.u.}$

Fig 3.13 Effect of variation of  $V_{dc}$

Fig 3.13 contd. Effect of variation of V<sub>dc</sub>

## AF Design (Calculations in Appendix):

Keeping with the restriction imposed by the semiconductor switches on inverter switching frequency, a judicious selection of parameters has to be made so as to limit the

switching frequency below the maximum limit and to have good performance in terms of low THD at the system bus voltage.

The active filter provides compensation for a 1 p.u. output DC current load. For this load requirement, IGBT switches would be adequate. The simulation model assumes an ideal switch, but considers the switching frequency restraint imposed by a real switch. For high power application, GTO switches would be chosen, and the AF design would be according to their switching frequency constraints.

- (i) Hysteresis bandwidth, hb: To have a good replication of reference currents, the hysteresis bandwidth was chosen at 10% of  $I_{base}$  i.e. 0.1A. From simulation studies (Fig. 3.9 i&ii), a hysteresis bandwidth of 10%  $I_{base}$ , kept the switching frequency below 10 kHz, and the THD less than 4%.

- (ii) DC bus capacitor voltage,  $V_{dc}$ : Since the system AC bus voltage is 100V(peak), the DC bus voltage was taken at 200V. A higher voltage value would further increase the switching frequency, and also increase switching losses. Thus the DC bus voltage reference was set at the minimum value.

- (iii) Connection inductance,  $L_c$ : Substituting the  $V_{dc}$  and hb values in eq.(3.7) and taking the maximum switching frequency for the inverter at 80 kHz, the value of  $L_c$  obtained is 12.5 mH. As shown in Fig.3.10 (ii), the THD remains practically constant for a range of  $L_c$ , unless it is a very low value. Simulations for the circuit show that the  $L_c$  value at 10 mH provided good modulation conforming with the switching frequency restraint, and acceptable THD.

- (iv) DC bus capacitor,  $C_{dc}$ : The DC bus capacitor should be large enough to store enough energy to supply the total power required by the load, for short duration failures at the system AC bus. The capacitor was selected at 200uF, so as to meet load requirements, during 1 cycle faults at AC bus. A higher value of  $C_{dc}$ , improves the DC bus voltage ripple, but

adds to the cost.

## 3.3.2.2 Sliding-Mode Control

This control technique is based on the concept of Variable Structure Systems (VSS) [7,15]. Variable structure systems consist of a set of continuous subsystems with proper switching logic. The control actions are discontinuous functions of system state and reference inputs. The switching inverter used as an active filter is a natural variable structure system because its topology changes from one continuous state to another with the switching action.

For a given circuit, a state vector, usually a set of voltages or currents to be controlled, is defined. The objective of the technique is to derive a control law for the switching function to maintain the system state on a desired trajectory or sliding surface.

A switched circuit topology imposes natural restraint on the switching function. For the inverter circuit, the switches may be in open or closed state. The switching function is thus bipolar and is expressed as

$U_x = +1$  (Upper switch of leg x closed, lower switch open)

$U_x = -1$  (Lower switch of leg x closed, upper switch open)

The continuous control concept is used to derive the equivalent switching function  $U_{eq}$  (Appendix B2).

The equivalent switching function for phase x is given by

$$U_{eqx} = \left(i_{cx} + \frac{e_{xn}}{L_c}\right) \times \frac{2L_c}{V_{dc}}$$

(3.9)