## Integrating SAT with MDG for Efficient Invariant Checking

Khaza Anuarul Hoque

A Thesis in The Department of Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science (Electrical & Computer Engineering)

$\operatorname{at}$

Concordia University Montréal, Québec, Canada

November 2010

© Khaza Anuarul Hoque, 2010

#### CONCORDIA UNIVERSITY SCHOOL OF GRADUATE STUDIES

This is to certify that the thesis prepared

By: Khaza Anuarul Hoque

Entitled: "Integrating SAT with MDG for Efficient Invariant Checking"

and submitted in partial fulfillment of the requirements for the degree of

### **Master of Applied Science**

Complies with the regulations of this University and meets the accepted standards with respect to originality and quality.

Signed by the final examining committee:

|                        | Chair                                |

|------------------------|--------------------------------------|

| Dr. D. Qiu             |                                      |

| Dr. J. Bentahar, CIISE | Examiner, External<br>To the Program |

| Dr. S. Hashtrudi Zad   | Examiner                             |

| Dr. M. Boukadoum       | Examiner                             |

| Dr. O. Ait Mohamed     | Supervisor                           |

Approved by: \_

Dr. W. E. Lynch, Chair Department of Electrical and Computer Engineering

\_\_\_\_20\_

Dr. Robin A. L. Drew Dean, Faculty of Engineering and Computer Science

### ABSTRACT

#### Integrating SAT with MDG for Efficient Invariant Checking

#### Khaza Anuarul Hoque

Multiway Decision Graph (MDG) is a canonical representation of a subset of many-sorted first-order logic. It generalizes the logic of equality with abstract types and uninterpreted function symbols. The area of Satisfiability (SAT) has been the subject of intensive research in recent years, with significant theoretical and practical contributions. From a practical perspective, a large number of very effective SAT solvers have recently been proposed, most of which based on improvements made to the original Davis-Putnam algorithm. Local search algorithms have allowed solving extremely large satisfiable instances of SAT. The combination between various verification methodologies will enhance the capabilities of each and overcome their limitations. In this thesis, we introduce a methodology and propose a new design verification tool integrating MDG and SAT, to check the safety of a design by invariant checking. Using MDG to encode the set of states provide powerful mean of abstraction. We use SAT solver searching for paths of reachable states violating the property under certain encoding constraints. In addition, we also introduce an automated conversion-verification methodology to convert a Directed Formula (DF) into Conjunctive Normal Form (CNF) formula that can be fed to a SAT solver. The formal verification of this conversion is conducted within the HOL theorem prover. Finally, we implement and conduct experiment on some examples along with a case study to show the correctness and the efficiency of our approach.

To My Family

#### ACKNOWLEDGEMENTS

At first, I would like to thank almighty Allah for his blessing to finish this research and for giving me opportunity for my higher studies.

It is a great pleasure for me to thank all those who have helped me in my research work. I would like to sincerely thank and express my gratitude to my supervisor, Dr. Otmane Ait Mohamed. This thesis would not have been possible without his guidance, his expert advice, his support and encouragements. Also, I sincerely thank Dr. Mounir Boukadoum, for co-supervising my research work. To all my fellow researchers and colleagues in Hardware Verification Group (HVG) at Concordia University, I thank you for your friendship, your thoughtful discussions and productive feedbacks. Most importantly, I thank the two most helpful people, Naeem Abbasi and Dr. Fariborz Fereydouni-Forouzandeh. They have always encouraged and motivated me whenever I was frustrated with the research progress. Also thanks to Dr.Sa'ed Abed for giving his valuable comments on my thesis. Without their encouragements and support, I would not have been able to continue my research work.

Last but not least, I thank my family for their constant moral support and their prayers. They are the people who are closest to me and suffered most for my higher study in abroad. Their support was invaluable in completing this thesis.

## TABLE OF CONTENTS

| LI       | ST O           | F TAB                               | LES                         | iii |  |  |  |

|----------|----------------|-------------------------------------|-----------------------------|-----|--|--|--|

| LI       | ST O           | F FIGU                              | URES                        | ix  |  |  |  |

| LI       | ST O           | F ACR                               | ONYMS                       | х   |  |  |  |

| 1        | Intr           | ntroduction                         |                             |     |  |  |  |

|          | 1.1            | Motiv                               | ation                       | 1   |  |  |  |

|          | 1.2            | Forma                               | d Verification Techniques   | 4   |  |  |  |

|          |                | 1.2.1                               | Theorem Proving             | 5   |  |  |  |

|          |                | 1.2.2                               | Equivalence Checking        | 6   |  |  |  |

|          |                | 1.2.3                               | Model Checking              | 6   |  |  |  |

|          | 1.3            | Thesis                              | S Contribution              | 9   |  |  |  |

|          | 1.4            | Thesis                              | s Outline                   | 10  |  |  |  |

| <b>2</b> | $\mathbf{Rel}$ | elated Work 1                       |                             |     |  |  |  |

|          | 2.1            | EUF I                               | Elimination                 | 12  |  |  |  |

|          | 2.2            | CNF (                               | Conversion                  | 13  |  |  |  |

|          | 2.3            | SAT a                               | and BDD Based Verification  | 14  |  |  |  |

| 3        | Bac            | Background                          |                             |     |  |  |  |

|          | 3.1            | .1 Temporal Logic and Specification |                             | 17  |  |  |  |

|          |                | 3.1.1                               | Linear Time Logic           | 18  |  |  |  |

|          |                | 3.1.2                               | Computation Tree Logic      | 20  |  |  |  |

|          |                | 3.1.3                               | Full Branching-time Logic   | 21  |  |  |  |

|          |                | 3.1.4                               | Categories of Specification | 22  |  |  |  |

|          | 3.2            | Multiv                              | way Decision Graph          | 22  |  |  |  |

|          |                | 3.2.1                               | Abstract State Machine      | 22  |  |  |  |

|          |                | 3.2.2                               | Structure                   | 23  |  |  |  |

|          | 3.3    | The MDG-Tool                                      |                                                               |    |

|----------|--------|---------------------------------------------------|---------------------------------------------------------------|----|

|          |        | 3.3.1                                             | MDGs Model Checking                                           | 28 |

|          |        | 3.3.2                                             | Invariant Specification in MDG                                | 29 |

|          | 3.4    | Boole                                             | an Satisfiability                                             | 30 |

|          | 3.5    | The H                                             | IOL Theorem Prover                                            | 32 |

|          | 3.6    | Norma                                             | al Forms                                                      | 34 |

| 4        | Inte   | egratin                                           | g SAT with MDG                                                | 36 |

|          | 4.1    | Forma                                             | alization of the Problem                                      | 36 |

|          | 4.2    | Propo                                             | sed Methodology                                               | 37 |

|          |        | 4.2.1                                             | Using MDG for Reachibility Analysis                           | 39 |

|          |        | 4.2.2                                             | Preprocessing to Impose Boolean Encoding                      | 41 |

|          |        | 4.2.3                                             | CNF Conversion of Directed Formula                            | 45 |

|          |        | 4.2.4                                             | Verification of the Conversion                                | 47 |

|          |        | 4.2.5                                             | Specification of Invariant Property and Correctness Formula . | 50 |

|          |        | 4.2.6                                             | Using SAT as a Verification Engine                            | 51 |

| <b>5</b> | Imp    | plementation and Case Study 5                     |                                                               |    |

|          | 5.1    | Conve                                             | ersion-Verification of Directed Formula                       | 53 |

|          |        | 5.1.1                                             | Experiment Description                                        | 53 |

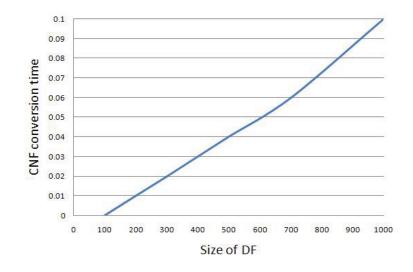

|          |        | 5.1.2                                             | Experimental Results                                          | 54 |

|          | 5.2    | 2 Integrating SAT with MDG for Invariant Checking |                                                               |    |

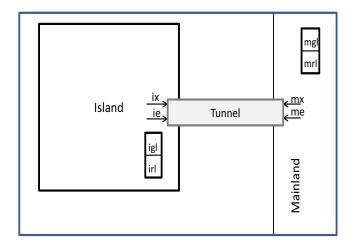

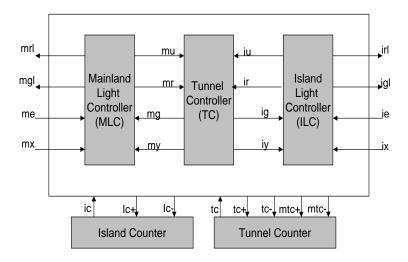

|          |        | 5.2.1                                             | Case Study: Island Tunnel Controller (ITC)                    | 58 |

|          |        | 5.2.2                                             | Implementation Description                                    | 60 |

|          |        | 5.2.3                                             | Experiment Results                                            | 62 |

| 6        | Cor    | nclusio                                           | n and Future work                                             | 64 |

| Bi       | ibliog | graphy                                            |                                                               | 66 |

## LIST OF TABLES

| 1.1 | Deductive theorem proving vs. state exploration method $\ldots \ldots \ldots$ | 2  |

|-----|-------------------------------------------------------------------------------|----|

| 1.2 | Raising the abstraction level                                                 | 9  |

| 5.1 | CNF conversion time                                                           | 54 |

| 5.2 | Invariant Checking Results with MDG tool and MDG-SAT approach                 | 58 |

| 5.3 | Total time for SAT-MDG approach                                               | 62 |

| 5.4 | Invariant checking time: SAT-MDG and MDG tool                                 | 63 |

## LIST OF FIGURES

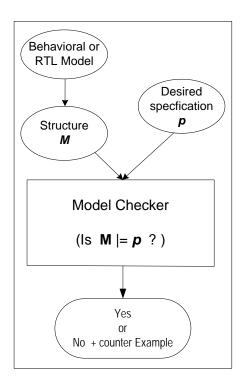

| 1.1 | Model-checking method                                                 | 7  |

|-----|-----------------------------------------------------------------------|----|

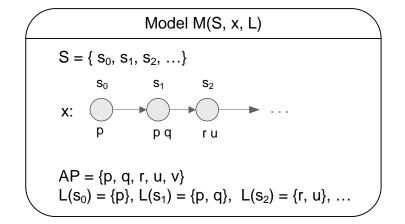

| 3.1 | Model Structure                                                       | 18 |

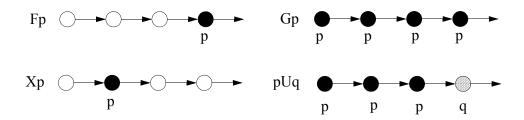

| 3.2 | LTL formulae and time.                                                | 19 |

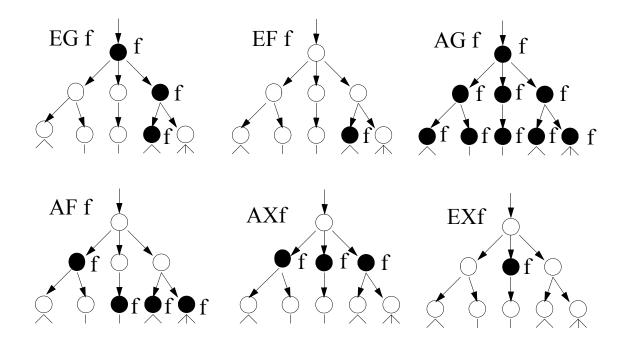

| 3.3 | CTL formulae and time.                                                | 21 |

| 3.4 | BDDs to MDGs.                                                         | 24 |

| 3.5 | MDG of an ALU                                                         | 26 |

| 3.6 | The Structure of the MDGs-tool                                        | 27 |

| 3.7 | Invariant specification in MDG tool                                   | 30 |

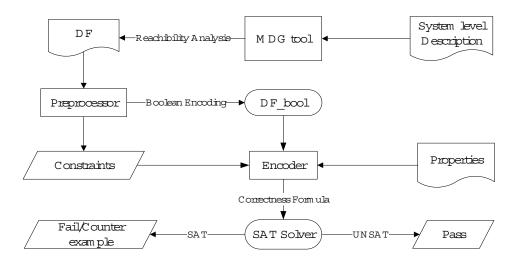

| 4.1 | Verification Methodology using MDG tool and SAT solver                | 38 |

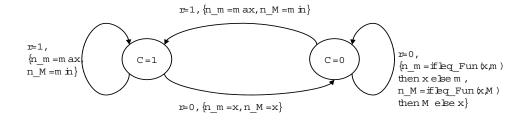

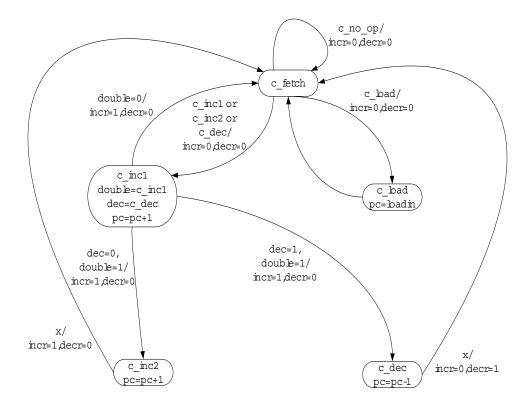

| 4.2 | MIN-MAX State Machine                                                 | 43 |

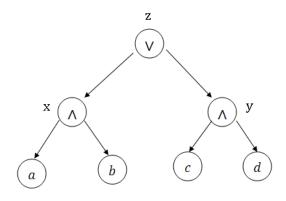

| 4.3 | Tesitin encoding to convert a propositional formula to CNF linearly . | 47 |

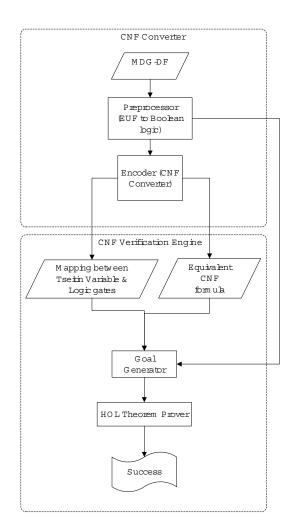

| 4.4 | Overview of the DF to CNF conversion-verification methodology         | 48 |

| 5.1 | DF size vs. CNF conversion time                                       | 55 |

| 5.2 | An abstract counter                                                   | 56 |

| 5.3 | The Island Controller                                                 | 59 |

| 5.4 | The Island Controller                                                 | 59 |

## LIST OF ACRONYMS

| ASM  | Abstract State Machine        |

|------|-------------------------------|

| BDD  | Binary Decision Diagram       |

| CNF  | Conjunctive Normal Form       |

| SAT  | Satisfiability Checking       |

| HDL  | Hardware Description Language |

| DNF  | Disjunctive Normal Form       |

| BMC  | Bounded Model Checking        |

| HOL  | Higher Order Logic            |

| CTL  | Computation Tree Logic        |

| DAG  | Directed Acyclic Graph        |

| DF   | Directed Formula              |

| FSM  | Finite State Machine          |

| LTL  | Linear Temporal Logic         |

| MDG  | Multiway Decision Graph       |

| RTL  | Register Transfer Level       |

| ITC  | Island Tunnel Controller      |

| RelP | Relational Product            |

| PbyS | Pruning by Subsumption        |

|      |                               |

# Chapter 1

## Introduction

## 1.1 Motivation

Faulty systems (bugs in digital systems) can be very dangerous and very expensive; especially for those which have safety-critical applications such as Magnetic Resonance Imaging (MRI) machines, space shuttles, microprocessors and so on. For example, bugs in Therac-25 machine caused 3 deaths and 3 serious injuries in 1985. In 1994, FDIV bug in Intel pentium processor caused them about \$500 million USD followed by Mars polar lander loss in 1996 which cost NASA \$165 million USD. There is a great advantage in being able to verify the correctness of such systems, whether they are hardware, software, or a combination. In the case of safety-critical systems, this is most obvious, but also applies to those that are commercially-critical, such as mass-produced chips. Formal verification methods have quite recently become usable by industry and there is a growing demand for professionals able to apply them [58]. Detection of bugs in design involves extra effort, time and cost. The overhead is even worse if the bug is detected late in the design process increasing the overall cost of the chip as well. The traditional debugging technique is simulation. However, due to the increasing size and complexity of VLSI circuits, it is impossible to simulate large designs properly. To overcome these limitations, formal verification comes into play as a complement to simulation to detect errors in the design as early as possible.

Formal verification techniques have origins in the field of applied mathematics and have been successfully used in the past to prove that the implementation of a design meets its specification. These techniques can be categorized into two main groups: (1) state exploration based techniques [51], namely model checking and equivalence checking, and (2) deductive reasoning based techniques, namely theorem proving. Both of these techniques have their own strengths and weaknesses. Equivalence and model checkers are automatic tools and can be used by an engineer with no special knowledge about formal methods. These techniques, however, suffer from the state space explosion problem [36]. On the other hand, verification using theorem proving with higher-order-logics is not an automatic technique but can be applied to larger sized problems. Strengths and weakness of both, state exploration method and deductive theorem proving are summarized in Table 1.1 [11].

| Method   |      | State exploration method | Deductive method |

|----------|------|--------------------------|------------------|

| Automat  | ion  | completely automatic     | interactive      |

| Domain   | size | finite system            | infinite system  |

|          |      | (large)                  | (complex)        |

| Debuggii | ng   | generates                | expert based     |

|          |      | counter-example          |                  |

Table 1.1: Deductive theorem proving vs. state exploration method

Multiway Decision Graphs (MDGs) [25], are a special kind of decision diagrams that subsumes Binary Decision Diagrams (BDDs) and extends them by canonically and compactly representing a subset of first-order functions. The MDG system is a decision diagram-based verification tool, primarily designed for hardware verification. MDG tool supports both equivalence checking and model checking. With MDGs, a data value is represented by a single variable of an abstract type and operations on data are represented in terms of an uninterpreted functions. MDGs consist of a set of algorithms. The specification and the implementation of the design are described using Hardware Description Languages (HDL) and then translated into the decision diagrams via intermediate languages. The algorithms in the system are used to efficiently and automatically deal with the decision diagrams so as to obtain a correct result.

Satisfiability Checking (SAT)-based tools to perform various forms of model checking has achieved a lot of attention these days [29, 9], as they are less sensitive to the problem sizes and the state explosion problem of classical Binary Decision Diagram (BDD)-based [21] model checkers. Expressing transition relation using Conjunctive Normal Form (CNF) along with SAT is an alternative to decision graphs and BDD-based approach. Such an approach, performance wise, is less sensitive to the problem size. As a result, many researchers have developed methods for performing Bounded Model Checking (BMC) [40, 71] using SAT. The common theme in these works is to convert the problem of interest into a SAT problem, by figuring out an appropriate propositional Boolean formula, and to utilize other non-canonical representations of state sets. These methods exploit the ability of SAT solvers to find a single satisfying solution, when it exists. In the recent years the SAT solver technology has improved significantly and a number of sophisticated packages are now available. Some of the well known state-of-the-art SAT solvers include CHAFF [62], GRASP [59] and SATO [80]. Most of the model checking techniques, in their implementation, involve state set manipulations. The state set manipulation problem can be transformed into a SAT problem. SAT solvers, thus, have the potential of enormously boosting the speed and applicability of model checking techniques.

In [9], an overview of a very interesting methodology integrating SAT and MDG model checker tool, was presented by the authors with preliminary experimental results. They used a rewriting based SAT solver to prune the transition relation of the circuits to produce a smaller one that is fed to the MDG model checker. The basic idea was to use the SAT solver as a reduction engine within the MDG model checker tool [25]. In our work, we propose a new methodology to build a verification tool for invariant checking. An *invariant* is a liner time property that is given by a condition  $\phi$  for the states and requires that  $\phi$  holds for all the states. For our proposed methodology we use SAT [33] as a verification engine for MDG models. MDG as data structure, for representing transition systems or set of states, provide a powerful means for abstraction in order to suit large models intended for model checking. As an alternative of using MDG as a stand alone tool for invariant checking, we explore the benefits of combining SAT and MDG in our proposed methodology- for a new verification tool.

## **1.2** Formal Verification Techniques

Formal verification is a technique to prove mathematically that an implementation satisfies a given set of specification. The implementation(description of the design) to be verified can be described at different level of abstraction which leads in to different verification methods. The class of the implementation system or circuit to be verified is another issue. For example different verification approaches may be required for combinational/sequential, synchronous/asynchronous, pipelined or non-pipelined circuits. The correctness of the system is determined with respect to properties derived from specification. In practice, implementation and specification both are needed to be modeled in the tool. Then formal verification algorithm of that tool is applied to check the correctness of the system. A counter example is generated to trace error/errors, if the verification fails.

Although formal verification techniques use mathematical reasoning to establish that an implementation meets the specification, such correctness proof cannot guarantee that a real device will never malfunction. An actual device may still show unintended behavior, even if the hardware design is proved correct using formal verification tool. Wrong specification can play a major role in this or defects in physical fabrication can cause this problem too. In formal verification, a model of the design is verified rather than a real physical implementation. As a result, a fault in the modeling process can result in false negatives (design errors that do not exist). Formal verification techniques can be divided into 3 categories, namely:

- Theorem proving

- Equivalence checking

- Model checking

### 1.2.1 Theorem Proving

In theorem proving, both the implementation and specification is described in formal The correctness is obtained by mathematically proving their relationship logic. formed as a theorem [48]. The logic is characterized by a proof system which refers to a set of axioms and a set of inference rules. Inference rules are applied until the desired theorem is proven. HOL(Higher Order Logic), ISABELLE, PVS (Prototype Verification System) and ACL2 [57, 64, 68, 50] are some of the high performance theorem provers. Unfortunately, using theorem prover requires expertise. Using theorem prover for verification is a white box approach, which means user is expected to know the whole design. It is not fully automated and requires a large amount of time on the part of the user in developing specifications of each component and in guiding the theorem prover through a large set of lemmas. A theorem prover may sometimes provide an insight into the reasons why a proof failed but is unable to provide counter-example in case the proof fails. The higher-order logics used in theorem proving are expressive. As a result, they allow modeling and verification of very complex systems and circuits very easily. Because they require a considerable interactive effort, theorem provers have less practice in industry and are mainly used for safety critical applications.

#### **1.2.2** Equivalence Checking

Equivalence checking is a method to prove that two designs, represented at two different levels of abstraction of the same system are functionally equivalent [48]. A possible common scenario of equivalence checking can be comparing a circuit's gatenetlist description with its RTL description. Equivalence checking is usually divided into two classes: *Combinational* equivalence checking and *Sequential* equivalence checking. In combinational equivalence checking, the circuits to be compared are converted into canonical representation of Boolean functions, usually BDDs [21] which are then structurally compared. MDG [38] in academia, Synopsys Formality and Cadence Conformal [6] in the industry are two examples of tools that offer combination equivalence checking. On the other hand, in sequential equivalence checking, the given two designs are represented using state-encoding and later on the equivalence is then established by building the product finite state machine followed by checking whether the output is invariant for any initial states of the product machine. Sequential equivalence checking can verify between RTL and behavioral models because it only considers the behaviors of the models while ignoring details of the implementation. However, state space explosion problem restricts it from checking large designs. MDG and VIS [7] are examples of tools which can perform sequential equivalence checking.

#### 1.2.3 Model Checking

Model checking as a verification technique was developed independently by Clarke and Emerson [36] and by Quielle and Sifakis [66] in the early 1980s. In model checking, a system is modeled as a set of states together with a set of transitions between states that represents how the system behavior evolves from one state to another over time, in response to internal and external stimulus. Model checking tools allow automatic verification of properties expressed in some temporal logic. In case the verification fails, a counter example is generated that helps in tracing bugs in the design.

Figure 1.1: Model-checking method

Just like other verification techniques, model checking also has its own advantages and disadvantages. Model checker has two important advantages. First, model checking is fully automatic. Once the correct design of the system and the required properties has been fed in, it requires no further information or interaction from the user. Second, if the property fail to hold, the verification process is able to produce a counter-example (i.e. an instance of the behavior of the system that violates the property) which is extremely useful in helping the human designers pinpoint and fix the flaw. On the other hand, model checkers are unable to handle very large designs due to the state space explosion problem [36]. Another drawback is the problematic description of specifications as properties, this description sometimes may not give full system coverage. SPIN [5], SMV [4], NuSMV [2], and MDG tool [77] are some of the commonly used model checking tools. They take as input, design description in a structural form along with system specifications or properties described in an appropriate temporal logic, and automatically check to see whether the system satisfies the property.

Since the model is usually a finite-state transition system, the problem of model checking is considered to be decidable. The design or model is formalized in terms of a state machine (Transition System), or a Kripke [49] structure:

$$M = (P, S, I, R, L)$$

where M is a state machine (model) with transitions to describe the circuit behavior, P is a set of atomic propositions, S is a finite set of states,  $I \subseteq S$  is a set of initial states,  $R \subseteq S \times S$  is a transition relation that must be total (i.e. for every  $s \in S$ there exists  $s' \in S$  such that  $(s, s' \in R)$ ), and  $L : S \to 2^P$  maps each state to the set of atomic propositions true in that state.

The property  $\phi$  is formalized as a logical formula that the machine should satisfy. The verification problem is stated as checking the formula  $\phi$  in the model M:

$$M \vDash \phi$$

If the model M is represented as a transition relation, then the size of the model is limited to the number of states that can be stored in the computer memory. This is about a few million states with the current state-of-the-art technology. Recently, the use of efficient state representations and manipulations using BDDs and/or SAT solving techniques has increased the size of problems that can be handled with model checking techniques by an order of magnitude.

An alternate approach based on a new class of decision graphs known as the Multiway Decision Graph (MDG) was proposed by Cerny et al. in 1997 [30]. This approach is capable of dealing with the state-space explosion problem very effectively. In MDG based model checking, data signals are denoted by abstract variables, and data operators are represented by uninterpreted function symbols. As a result, a verification based on abstract-implicit-state-enumeration can be carried out independently of data path width. This results in a substantial reduction of the state space size. Table 1.2 shows [11] the abstraction level of MDG corresponding to traditional methods. A model-checking methodology typically consists of three major parts: a specification language, a system modeling language and a set of algorithms to perform model-checking. In existing MDG methodology, these are  $L_{MDG}$ [77], MDG-HDL [79] and MDG-tool [77, 78] respectively.

| Conventional method             | Multiway Decision Graph                    |

|---------------------------------|--------------------------------------------|

| ROBDD [21]                      | MDG                                        |

| Finite State Machine            | Abstract State Machine                     |

| Implicit state enumeration [26] | Abstract state implicit enumeration of ASM |

| CTL based model-checking        | Subset of first-order abstract CTL         |

Table 1.2: Raising the abstraction level

### **1.3** Thesis Contribution

A desirable approach is to develop synergies between various verification methodologies, and between design and verification, in order to overcome the limitations and to enhance the capabilities of each and our work is motivated by this goal. Traditional invariant checking using MDG tool is the direct use of MDG reachability analysis algorithm [79]. We propose a new invariant checking methodology integrating SAT with MDG. SAT has already been integrated with MDG tool as a *reduction engine* [9]. In our work, we integrate SAT as a *verification engine*, to enhance the performance of invariant checking. Our study and implementation of the methodology suggest a new verification tool combining the strengths of both: MDG and SAT. In terms of reviews of related work, proposed methodology and discussions, we believe our contribution can be specified as:

- We proposed a SAT based invariant checking methodology. For the completeness of the methodology:

- We implemented a Preprocessor, an automated uninterpreted function removal method to impose Boolean encoding on Directed Formula (DF) with adequate encoding constraints.

- 2. An *Encoder* is also implemented to apply a linear CNF conversion algorithm on a Boolean Directed Formula. The *Encoder* also generates a *correctness formula* to be fed to a SAT solver.

- We proposed a technique to formally verify the correctness of CNF conversion *Directed Formula* and also implemented a *goal generator* that takes the input from the *Preprocessor* and generates a goal. Later on, an automated call to the HOL [57] theorem prover is placed to check the goal.

## 1.4 Thesis Outline

The rest of the thesis is organized as bellow:

- In Chapter 2, we present some of the related work in the area of *Equality with Uninterpreted function* removal, different CNF conversion algorithms and also some SAT based Verification approaches.

- In Chapter 3, we review the basics of temporal logic and specification, the structure of Multiway Decision Graph (MDG), MDG-tool followed by MDG model checking approach. Some basic review on Boolean SAT solvers, HOL theorem prover and normal forms concludes the chapter.

- In Chapter 4, we propose our methodology to integrate SAT with MDG and provide step by step description of the methodology. Also we present the methodology to formally verify the correctness of the CNF conversion algorithm.

- In Chapter 5, we present some experimental results showing the correctness of our conversion-verification approach. Also we present the case study, to show the efficiency of our proposed SAT-MDG invariant checking methodology.

- We conclude the thesis in Chapter 6 and provide some future research directions.

# Chapter 2

# **Related Work**

In this Chapter, we present some related research work in the area of SAT based verification. We divide the related works in three different categories. The first category focuses on different techniques to translate the formulas in Equality with Uninterpreted Functions(EUF) to propositional logic. The second category describes several algorithms for the conversion of propositional formula to CNF. In last and final category we discuss some related SAT based verification techniques.

## 2.1 EUF Elimination

Their exist two possible ways to eliminate EUFs [69], while enforcing their property of functional consistency, Ackermann constraints [12] and nested If-Then-Else operators (ITE) [67, 74]. In Ackermann's approach, the UF was replaced with a new term variable and the next application of UF with respect to the previous one was enforced by extending the resulting formula with constraints. Such constraints added for each pair of applications of that UF. Bryant and Velev presented an approach to eliminate the applications of UF with nested ITEs in [67]. In nested ITE scheme, the first application of the UF is still replaced by a new term variable. However the subsequent applications are eliminated by introducing nested ITEs with new term variables while preserving functional consistency. We prefer nested ITE scheme which directly captures the functional consistency and readily exploit the maximal diversity property while Ackermann's can not [67]. For our methodology, we use the nested-ITE approach. However we add few small modifications to match the MDG directed formula syntax.

## 2.2 CNF Conversion

Lack of fast and efficient CNF generation algorithm has always been a bottle neck for CNF based SAT solvers. Hence researchers paid much attention to this point. Until recently [20], most of the CNF generation algorithms used in practice were minor variations of Tseitin linear time algorithm [73]. Another CNF conversion algorithm came from Velve [75] showing an efficient CNF generation technique with identifying gates with fan-out count of 1 and merging them with their fan-out gate to generate single set of equivalent CNF clauses. Nested ITE chains where each ITE is used only as else argument of the next ITE are similarly merged and represented with a single set of clauses without introducing intermediate variables. Such approach is good for pipelined machine verification problems, identifying certain patterns arising in formulas. Another approach for CNF generation is based on technological mapping [32] and its implemented in ABC [72]. This algorithm computes the mapping sequence, partial functions from And-Inverter-Graph (AIG)[16] nodes in order to cut of the graph for minimization of the heuristics cost function. CNF is then generated for the cuts of the nodes with respect to the final mapping by using their sum of products representation. Very recently an algorithm was presented [23] for converting Negation, ITE, Conjunction and Equivalence (NICE dags) to CNF. A new data structure called NICE dag subsume AIGs.

All the approaches described above use an intermediate representation or data structure for the boolean formula (either RBC, AIGER or NICE dag). The MDG DF is itself a DAG, so intermediate DAG representation is not required to facilitate the conversion. The most interesting thing we observed is in most of the papers a "paper and pencil" sketch was given for the proof of their conversion approach. This motivated us to build an automated tool for the verification of conversion as well.

## 2.3 SAT and BDD Based Verification

Most of the efforts today are spent on developing Satisfiability Checking (SAT) based tools to perform several forms of model checking as they are less sensitive to the problem size and the state explosion problem of classical Binary Decision Diagram (BDD) based model checkers. As a result, many researchers have developed routines for performing Bounded Model Checking (BMC) [40][71] using SAT.

BDD and SAT based verification have been a major field of interest for researchers for a long time. Given that both techniques perform an implicit search in the underlaying Boolean space, it is no surprise that different approaches have been explored recently to combine both of them for target applications. Their benefits have been combined in many applications such as BMC[41, 8] and model checking [46]. In [47], the authors used BDDs to represent state sets, and a CNF formula to represent the transition relation. All valid next state combinations are enumerated using a backtracking search algorithm for SAT that exhaustively visits the entire space of primary input, present state and next state variables. However, rather than using SAT to enumerate each solution all the way down to a leaf, they invoked BDDbased image computation at intermediate points within the SAT decision procedure, which effectively obtains all solutions below that point in the search tree. In a sense, their approach can be regarded as SAT providing a disjunctive decomposition of the image computation into many subproblems, each of which is handled in the standard way using BDDs. Model checking techniques for security protocol analysis based on reduction to Boolean logic has been explained in [15]. The main idea was, given a protocol description in multi-set formalism and an integer k, to build propositional formulas whose models correspond to attacks on the protocol. Propositional formulas are checked for satisfiability to indicate an attack on the protocol. For checking invariant properties of the form  $AG_p$  (p is globally true along all paths) of transition systems using Induction [29], Deharbe and Moreira modified a standard model checking algorithm. Set of states and image computation are expressed using BDD. Velev presented an indirect method to automatically prove the safety and liveness of a pipelined microprocessor. The term-level simulator TLSim [76], used for the symbolic simulation of the implementation and specification and a EUFM correctness formula is produced. The decision procedure EVC [76] exploits the positive equality, performs some other optimizations and converts the EUFM formula to an equivalent. An efficient SAT solver proves the formula to be a tautology in order for the implementation to be correct. In [70], A safety property checking technique of finite state machines using SAT solver was presented. Their approach demonstrates the practicality of combining a SAT-solver based safety property checking of in a real design flow using induction. All the works described above relies on BDD based state encoding, which suffers from state explosion for larger designs. In our case, We use MDG to encode the set of sates to get rid of the state explosion problem.

SAT and MDG integration was proposed in [9], while using SAT solver as a **reduction engine**. On the other hand, our proposed SAT based invariant checking methodology for MDG model, uses a SAT solver as a **verification engine**. Moreover, we implemented SAT encoding technique (CNF conversion) for MDG Direct formula (DF) and proposed another automated methodology to formally verify the correctness of the conversion. For the conversion part, we use Tseitin [73] approach while introducing "fresh variables" only for AND gates and for the verification part we use the HOL [57] theorem prover. Implementation of SAT for model checking with Multiway Decision Graph (MDG) distinguishes our approach from others. In this Chapter, we presented some of the works related to uninterpreted function removal, different techniques of CNF conversion followed by some works related to SAT based verification. Also, we also mentioned how our work differs from those. In next Chapter, we present some preliminaries required to understand our contribution better.

## Chapter 3

# Background

In this chapter, we give a brief introduction to the Temporal Logic, Multiway Decision Graphs (MDGs) with MDG tool, followed by some basics of Boolean SAT solvers, the HOL theorem prover and normal forms. The intent is to familiarize the reader with the main concepts and notations that are used in the rest of the thesis. Section 3.1 presents temporal logic and how they are specified with LTL, CTL and  $CTL^*$ . Section 3.2 describes the underlying formal logic of MDGs, the Abstract State Machine (ASM) and the MDGs structure. Introduction to MDG tool, MDG model checker and invariant specification in MDG tool is described in Section 3.3. A brief introduction to SAT solver and SAT solving algorithm is described in Section 3.4. Section 3.5 starts by a basic description of higher-order logic concepts as well as the proof methods supported by the HOL theorem prover. We conclude the chapter in Section 3.6 describing the basic format of Conjunctive Normal Form(CNF) and Disjunctive Normal Form(DNF).

## **3.1** Temporal Logic and Specification

Desired specifications in model checking methods, are usually written in propositional temporal logic formulae [65]. This allows the user to write propositions with respect to time. The model of time is represented either in linear time (LTL) [55, 48] or branching time (CTL) [24]. A logic that combines the expressive power of LTL and CTL is known as CTL\* which is also known as full branching-time logic.

### 3.1.1 Linear Time Logic

The structure of time in linear time logic, is a totally ordered set (S, <), isomorphic to the set of natural numbers (N, <) [31]:

If AP is a set of atomic propositions, a linear time structure is defined as M(S, x, L), where:

- S is a set of states;

- $x: N \to S$  is an infinite sequences of states;

- $L: S \to 2^{AP}$  is a labeling of each state with the set of atomic propositions in AP at the state.

Following is an example (Fig. 3.1):

Figure 3.1: Model Structure

In propositional linear temporal logic (PLTL), one can use propositional logic as building block and apply temporal operators to specify properties. The PLTL syntax is defined as a least set of formulae generated by the following rules [31]:

- 1. Each atomic proposition is a formula;

- 2. If p and q are formulae then  $\neg p$  and  $p \land q$  are formulae;

- 3. If p and q are formulae then pUq and Xp are formulae.

The semantics of a formula p of PLTL with respect to a linear-time structure M(S, x, L) is defined below. Here, we write  $M, x \models p$  iff  $p \in L(s_0)$  for atomic proposition p to mean that in structure M formula p is true on timeline x;  $x^i$  denotes the suffix path  $s_i, s_{i+1}, s_{i+2}$ , and so forth.

- 1.  $M, x \models p \text{ iff } p \in L(s_0).$

- 2.  $M, x \models \neg p \text{ iff } not \ M, x \models p.$

- 3.  $M, x \models \{p \land q\}$  iff  $M, x \models p$  and  $M, x \models q$ .

- 4.  $M, x \models Xp$  iff  $M, x^1 \models p$ .

- 5.  $M, x \models p \cup q \text{ iff } \forall j(M, x^i \models q, \text{ and } \forall_{0 < i < j}(M, x^k \models p)).$

- 6.  $M, x \models Fp \text{ iff } \exists j(M, x^j \models p).$

- 7.  $M, x \models \mathbf{G}p \text{ iff } \forall j(M, x^j \models p).$

A PLTL formula p is satisfiable iff there exists a linear-time structure M = (S, x, L) such that  $M, x \models p$ , and any such structure defines a model of p. Examples are as following (Fig. 3.2):

Figure 3.2: LTL formulae and time.

#### 3.1.2 Computation Tree Logic

Computation tree logic (CTL) is based on branching time temporal logic (BTTL). It was first proposed by Clarke and Emerson [35]. In CTL, the time is modeled as a branching tree-like structure where each moment may have many different successor moments. Along each path, the timeline is isomorphic to the natural number. To specify a property in CTL, we simply apply the path operators along with temporal operators to the propositional building blocks. There are two strict restrictions in CTL:

- 1. Only single linear time operator F, G, X or U can follow a path quantifier;

- 2. Time operators cannot be combined directly with the propositional connectives.

The syntax of CTL is governed by the following rules:

- 1. Every proposition is a CTL formula;

- 2. If p and q are CTL formula, then so are p,  $(p \land q)$ , AXp, EXp, A(pUq), E(pUq).

The remaining operators can be derived from the above rules. The truth of a formula is determined on a given state and not on a branch of the time structure. The structure resembles an infinite computation tree. A temporal formula p is satisfied by a model M with transitions T, if it is true for all the initial states  $s_0$  of the model. The semantics of CTL formula is given below:

- 1.  $M, s_0 \models p$  iff  $p \in L(s_0)$ .

- 2.  $M, s_0 \models \neg p$  iff not  $M, s_0 \models p$ .

- 3.  $M, s_0 \models \{p \land q\}$  iff  $M, s_0 \models p$  and  $M, s_0 \models q$ .

- 4.  $M, s_0 \models AXp$  iff for all states  $s'_0$  with  $(s_0, s'_0) \in T, M, s'_0 \models p$ .

- 5.  $M, s_0 \models \text{EX}p$  iff for some state  $s_0^{'}$  with  $(s_0, s_0^{'}) \in T, M, s_0^{'} \models p$ .

- 6.  $M, s_0 \models A(pUq)$  iff for all paths  $(s_0, s_1, ...)$ , there exists a j > 0 with  $M, s_j \models q$ , and  $M, s_i \models p$  holds  $\forall 0 \le i < j$ .

- 7.  $M, s_0 \models E(pUq)$  iff for some path  $(s_0, s_1, ...)$ , there exists a j > 0 with  $M, s^j \models q$ , and  $M, s^i \models p$  holds  $\forall 0 \le i < j$ .

Figure 3.3 shows intuitive meanings of some CTL formulae.

Figure 3.3: CTL formulae and time.

### 3.1.3 Full Branching-time Logic

Full branching-time logic is the class of logic formulas that combines the branchingtime and linear-time operators. In CTL<sup>\*</sup>, a path quantifier can be a prefix to an assertion composed of arbitrary combination of the temporal operators: F, G, X and U. Like CTL, the tree is formed by designating an initial state  $s_0$  in model M, and then unwinding the structure into an infinite tree with  $s_0$  as the root. The semantics of the path quantifiers and temporal operators remain the same.

### 3.1.4 Categories of Specification

The specifications are written as properties of the system. They are categorized as follows:

- Safety property ensures that nothing 'bad' will ever happen. A temporal logic formula is a safety property if it can be written as AG<sub>φ</sub>(in CTL or CTL\*) or G<sub>φ</sub>(in PLTL), where φ is a propositional fromula.

- 2. Liveness property ensures that something 'good' will eventually happen. Depicted as  $\models Fp$  or  $\models AFp$ , where p will eventually be true at some point in the future.

- 3. Precedence property ensures precedence order of events. Depicted as  $\models pUq$ , where q is true in present time or p is true until q becomes true.

Among the three, safety property is the most used when writing specifications of a design under verification.

## 3.2 Multiway Decision Graph

### 3.2.1 Abstract State Machine

In MDG, a state machine is described using finite sets of input, state and output variables, which are pair-wise disjoint. The behavior of a state machine is defined by its transition/output relations including a set of reset states. An abstract description of the state machine, called Abstract State Machine (ASM) [37], is obtained by letting some data input, state or output variables be of an abstract sort, and the datapath operations be uninterpreted function symbols. As ROBDDs are used to represent sets of states and transition/output relations for finite state machines (FSM), MDGs are used to compactly encode sets of (abstract) states and transition/output relations for ASMs. This technique replaces the *implicit enumeration technique*[27] with the *implicit abstract enumeration* [25].

#### 3.2.2 Structure

MDGs are graph representation of a class of quantifier-free and negation-free firstorder many sorted formulae. It subsumes the class of Bryant's (ROBDDs) [19] while accommodating abstract data and Uninterpreted Function symbols. MDG can be seen as a Directed Acyclic Graph (DAG) with one root, whose leaves are labeled by formulae of the logic True (T) [25], such that:

- Every leaf node is labeled by the formula T, except if the graph G has a single node, which may be labeled Tor F.

- 2. The internal nodes are labeled by terms, and the edges issuing from an internal node v are labeled by terms of the same sort as the label of v.

Following is an example: Let graph G represent Boolean formula  $(\neg x \wedge F_0) \lor (x \wedge F_1)$ , Where,  $F_0$  and  $F_1$  are the Boolean formulas represented by the sub-graphs  $G_0$  and  $G_1$  respectively. In many sorted first-order logic the graph G can be viewed as representing a formula:  $((x = 0) \land F_0) \lor (x = 1) \land F_1)$ .

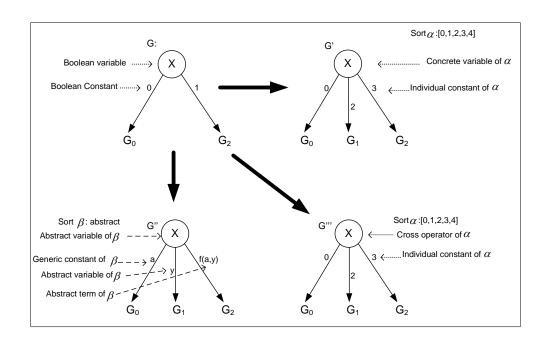

Three possible generalizations of G and the corresponding formulas are shown in (Fig. 3.4.  $F_0$ ,  $F_1$  and  $F_2$  are first-order formulas represented by the sub-graphs  $G_0$ ,  $G_1$  and  $G_2$  respectively:

1. From G to G':  $x \in \{0,1\} \to x \in \{0,2,3\}$ , and Graph G' represents the formula

$$((x = 0) \land F_0) \lor ((x = 2) \land F_1) \lor ((x = 3) \land F_2).$$

2. From G to G'':  $x \in \{0,1\} \to x \in \{a, y, f(a, y)\}$ , and Graph G'' represents the formula

$$((x = a) \land F_0) \lor ((x = y) \land F_1) \lor ((x = f(a, y)) \land F_2).$$

3. From G to G''':  $x \in \{0,1\} \to g(x) \in \{0,2,3\}$ , and Graph G''' represents the formula

$$((g(x) = 0) \land F_0) \lor ((g(x) = 2) \land F_1) \lor ((g(x) = 3) \land F_2)$$

Figure 3.4: BDDs to MDGs.

The above generalized decision graph G', G'' and G''' are examples of Multiway Decision Graphs (MDGs).

As in ordinary many-sorted First Order Logic (FOL), terms are made out of sorts, constants, variables, and function symbols. Two kinds of sorts are distinguished: concrete and abstract. Concrete sort is equipped with finite enumerations, lists of individual constants. Concrete sorts are used to represent control signals. Abstract sort has no enumeration available and represents a data signal. MDGs represent and manipulate a certain subset of first order formulae, which we call *Directed Formulae (DFs)*.

| Sort $S$                          | ::= | $S \mid \underline{S}$                                                          |

|-----------------------------------|-----|---------------------------------------------------------------------------------|

| Abstract Sort $S$                 | ::= | $lpha \mid eta \mid \gamma \mid \cdot \cdot \cdot$                              |

| Concrete Sort $\underline{S}$     | ::= | $\underline{\alpha} \mid \underline{\beta} \mid \underline{\gamma} \mid \cdots$ |

| Generic Constant ${\cal C}$       | ::= | $a \mid b \mid c \mid \cdots$                                                   |

| Concrete Constant $\underline{C}$ | ::= | $\underline{a} \mid \underline{b} \mid \underline{c} \mid \cdots$               |

| Variable $\mathcal{X}$            | ::= | $V \mid \underline{V}$                                                          |

| Abstract Variable ${\cal V}$      | ::= | $x \mid y \mid z \mid \cdots$                                                   |

| Concrete Variable $\underline{V}$ | ::= | $\underline{x} \mid \underline{y} \mid \underline{z} \mid \cdots$               |

| Directed Formulae $DF$            | ::= | $Disj \mid \top \mid \bot$                                                      |

| Disj                              | ::= | $Conj \lor Disj \mid Conj$                                                      |

| Conj                              | ::= | $Eq \wedge Conj \mid Eq$                                                        |

| Eq                                | ::= | $\underline{A} = \underline{C}(A \in \mathcal{T}(\mathcal{F}, V))$              |

|                                   |     | $ \underline{V} = \underline{C}$                                                |

|                                   |     | $ V = A(A \in \mathcal{T}(\mathcal{F}, \mathcal{X}))$                           |

|                                   |     |                                                                                 |

Let  $\mathcal{F}$  be a set of function symbols and  $\mathcal{V}$  a set of variables. We denote the set of terms freely generated from  $\mathcal{F}$  and  $\mathcal{V}$  by  $\mathcal{T}(\mathcal{F}, \mathcal{V})$ . The syntax of a Directed Formula is given by the grammar given above. [13]. The underline is used to differentiate between the concrete and abstract variables.

The vocabulary consists of generic constants, concrete constants (individuals), abstract variables, concrete variables and function symbols. DFs are always disjunctions of conjunctions of equations or  $\top$  (true) or  $\perp$  (false). The conjunction *Conj* is defined to be an equation only (*Eq*) or a conjunction of at least two equations. Atomic formulae are the equations, generated by the clause *Eq*. An equation can be an equality of concrete terms and an individual constant, equality of a concrete variable and an individual constant, or equality of an abstract variable and an abstract term.

A directed formula DF of type  $U \to V$  is a formula in Disjunctive Normal Form (DNF) plus  $\top$  (truth) and  $\perp$  (false), where U and V are two disjoint sets of variables. Just as ROBDD must be *reduced* and *ordered*, MDGs must obey a set of well-formedness conditions given in [25]. DFs are used for two purposes: to represent sets (viz. sets of states as well as sets of input vectors and output vectors) and to represent relations (viz. the transition and output relations) as well as the set of possible initial states and the sets of states that arise during reachability analysis.

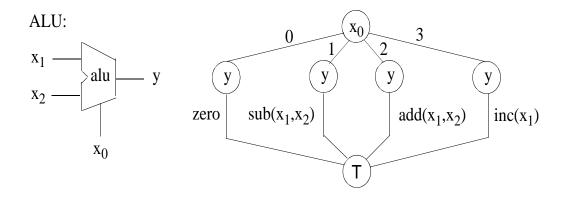

Figure 3.5: MDG of an ALU

Figure 3.5 shows MDG reforestation of a simple Arithmetic Logic Unit (ALU). Depending on the value of selection signal  $x_0$  the output value is chosen between the addition or the subtraction of  $x_1$  and  $x_2$ , increment of  $x_1$  or the output value can be zero as well. The Directed Formula(DF) representation of the MDG is as following:  $[(x_0 = 0) \land y = zero] \lor$  $[(x_0 = 1) \land y = sub(x_1, x_2)] \lor$  $[(x_0 = 2) \land y = add(x_1, x_2)] \lor$  $[(x_0 = 3) \land y = inc(x_1)] \lor$

## 3.3 The MDG-Tool

The MDG-tool [79] is a well known academic tool. It supports invariant checking, sequential equivalence checking, and model checking. The MDGs tool uses a Prolog-style hardware description language called the MDG-HDL(MDG-HDL) [25]. MDG-HDL supports structural, behavioral and mixed styles of coding. A structural specification is usually a netlist of components connected by signals. A behavioral description consists of a tabular representation of the transition and output relations in the form of a truth table.

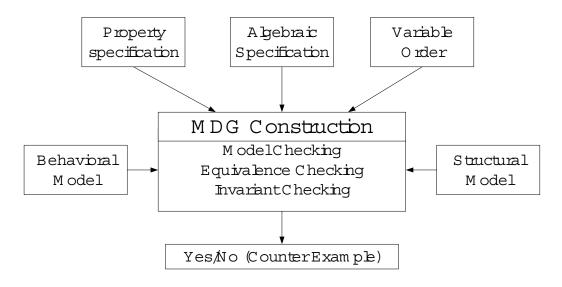

Figure 3.6: The Structure of the MDGs-tool

The first step in the verification is to describe the design specifications and implementations using MDG-HDL, as shown in Figure 3.6. An MDG-HDL algebraic specification consists of sorts, function types, and generic constants. Rewrite rules needed for interpreting function symbols are also provided. Symbol ordering (like for ROBDD) can either be specified by the user, or can be dynamically generated by the MGD tool. Symbol ordering can critically affect the size of the generated MDGs and the performance of the verification.

## 3.3.1 MDGs Model Checking

The MDGs model checking is based on an abstract implicit state enumeration. The circuit under verification is expressed as an Abstract State Machine (ASM) and the properties to be verified are expressed as formulae in  $\mathcal{L}_{MDG}$  [77, 11]. The ASM description of the digital systems is at a higher level of abstraction.  $\mathcal{L}_{MDG}$  atomic formulae are Boolean constants (True and False), or equations of the form  $(t_1 = t_2)$ , where  $t_1$  is an ASM variable (input, output or state variable) and  $t_2$  is either an ASM system variable, an individual constant, an ordinary variable or a function of ordinary variables. Ordinary variables are defined to memorize the values of the system variables in the current state. The basic Next\_let\_formulas contain temporal operator **X** (next time) is defined follows [13]:

- Each atomic formula is a *Next\_let\_formula*;

- If p, q are Next\_let\_formulas, then so are: !p (not p), p&q (p and q), p|q (p or q), p → q (p implies q), Xp (next-time p) and LET (v=t) IN p, where t is a system variable and v an ordinary variable.

Using the temporal operators AG (always), AF (eventually) and AU (until), the supported  $\mathcal{L}_{MDG}$  properties are defined in the following BNF grammar:

Model checking in MDGs is carried out by automatically building additional circuits that represent the Next let formulas appearing in the property to be verified, composing it with the original circuit, and then checking a simpler property on the composite machine [77].

## 3.3.2 Invariant Specification in MDG

An invariant file specifies the invariant condition to be checked during reachability analysis[79]. An invariant condition can be specified by a combinational circuit whose output signals are named by the variables that occur in the condition. By convention, an assignment of values to those variables satisfies the condition iff the outputs of the combinational circuit take those values for some assignment of values to the inputs. An MDG representing the invariant is obtained from the MDG representing the functionality of the combinational circuit by existentially quantifying the concrete inputs. The variables representing abstract inputs are left in the graph as implicitly quantified secondary variables [82].

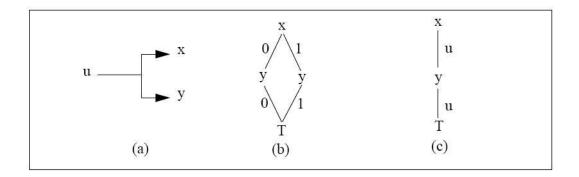

For example, for the equivalence checking of two ASMs, we need to specify the equality of two corresponding signals as the invariant. This is expressed by the simple fork as shown in Figure 3.7 (a). The fork may yield different MDGs depending on the sort of the signals. If u, x and y are of the Boolean sort, then u is existentially quantified and we get the MDG as shown in Figure 3.7 (b) which simply represents x = y. If x and y are of an abstract sort, then we get an MDG as shown in Figure 3.7 (c) which represents the formula  $(x = u) \land (y = u)$ . Taking the secondary variable u to be existentially quantified, the invariant is  $\exists u((x = u) \land (y = u))$ , which is logically equivalent to x = y.

This combinational circuit is described completely in this invariant specification file, including the following predicates: *signal*/2, *component*/2, *outputs*/1 and *order\_cond*/1 which gives the node order for the variables and the cross-function symbols appeared in the circuit.

Figure 3.7: Invariant specification in MDG tool

## **3.4** Boolean Satisfiability

The Boolean Satisfiability (SAT) problem is a well-known constraint satisfaction problem. It has many applications in the field of computer aided design such as test generation, logic verification and timing analysis. Given a Boolean formula, the objective is to either find a boolean assignment to the variables so that the formula evaluates to true, or establish that such an assignment does not exist. The Boolean formula is typically expressed in Conjunctive Normal Form (CNF), also called product-of-sums form. Each sum term (clause) in the CNF is a sum of single literals, where a literal is a variable or its negation.

Most state-of-the-art SAT solvers are based on the Davis-Putnam algorithm [28]. The basic algorithm begins from an empty assignment, and proceeds by assigning a 0 or 1 value to a free variable at a time. After each assignment, the algorithm determines the direct and transitive implications of that assignment on other variables. This process is sometimes also called the Boolean Constraint Propagation (BCP). If no contradiction is detected during the implication procedure, the algorithm picks the next free variable, and this process is repeated. Otherwise, the algorithm attempts a new partial assignment by complementing the most recently assigned variable for which only one value has been tried so far. This step is called backtracking. The algorithm terminates either when all clauses have been satisfied and a solution has been found, or when all possible assignments have been exhausted. The algorithm is complete in that it will find a solution if it exists.

| Algorithm 1 Davis_Putn | am() |

|------------------------|------|

|------------------------|------|

|     | -                                                  |  |  |  |

|-----|----------------------------------------------------|--|--|--|

| 1:  | 1: while true do                                   |  |  |  |

| 2:  | if $DecideNextBranch() == false then$              |  |  |  |

| 3:  | return(SATISFIABLE);                               |  |  |  |

| 4:  | end if                                             |  |  |  |

| 5:  | while $Deduce() = = CONFLICT do$                   |  |  |  |

| 6:  | if $\text{ResolveConflict}() == \text{false then}$ |  |  |  |

| 7:  | RETURN(UNSATISFIABLE);                             |  |  |  |

| 8:  | end if                                             |  |  |  |

| 9:  | end while                                          |  |  |  |

| 10: | end while                                          |  |  |  |

| -   |                                                    |  |  |  |

Algorithm 1 shows the Pseudo code adapted from the basic Davis-Putnam search procedure. The function DecideNextBranch() selects a variable that is not currently assigned, and gives it a value. This variable assignment is referred to as a decision. The Deduce() function carries out Boolean Constraint Propagation (BCP). It propagates variable assignments based on the current decision. Basically, if a clause consists of only literals with value 0 and one unassigned literal, then that unassigned literal must take on a value of 1. Clauses in this state are said to be unit, and this rule is referred to as the unit clause rule. In the pseudo-code, Deduce() carries out BCP transitively until either there are no more implications (in which case it returns SATISFIABLE) or a conflict is produced (in which case it returns UNSATISFIABLE). A conflict occurs when implications for setting the same variable to both 1 and 0 are produced.

#### Algorithm 2 ResolveConflict()

d = most recent decision not tried both ways;

if d == NULL then

return(false);

end if

flip the value of d;

mark d as tried both ways;

undo any invalidated implications;

return(true);

In order to deal with a conflict, we can flip the value of the decision assignment, undo all the implications by the decision, and allow BCP to then proceed as normal. If both values have already been tried for this decision, then we backtrack through the decision stack until we encounter a decision that has not been tried both ways, and proceed from there in the manner described in Algorithm 2.

## 3.5 The HOL Theorem Prover

The HOL system is an LCF [45, 11] (Logic of Computable Functions) style proof system. It was originally intended for hardware verification, but because of its ability to handle a variety of applications, it is now considered a general purpose proof system. Some of these applications include security systems, verification of faulttolerant computers, compiler verification, program refinement calculus, software and algorithms verification, modeling, and automation theory. HOL provides a wide range of proof commands, rewriting tools and decision procedures. The system is user-programmable and proof tools can be developed for specific applications without compromising reliability [44].

The set of types, type operators, constants, and axioms available in HOL are organized in the form of theories. The theories are arranged in a hierarchy. These theories include various formalized mathematical concepts such as lists, products, sums, numbers, primitive recursion, and arithmetic etc. On top of these, users are allowed to introduce application-dependent theories by adding relevant types, constants, axioms, and definitions.

The HOL system supports higher order logic with three main expressions:

- Variables can range over functions and predicates.

- The logic is typed.

- There is no separate syntactic category of formulae.

The basic interface to the system is a Standard Meta Language (SML) interpreter. SML [54] is both the implementation language of the system and the Meta Language in which proofs are written. The HOL system supports both forward and backward proof methods common in a natural-deduction style calculus. In the forward proof method, the steps of a proof are implemented by applying inference rules chosen by the user, and HOL checks that the steps are safe. All derived inference rules are built on top of a small number of primitive inference rules. This approach has some limitations since it is hard to know where to state the proof and, for large proofs, to determine which sequence of rules to apply. The results are strong and the user can have great confidence since the most primitive rules are used to prove a theorem. In the backward proof method, the user sets the desired theorem as a goal. Small programs written in SML called tactics and tacticals are applied to break the goal into a list of subgoals. Tactics and tacticals are repeatedly applied to the subgoals until they can be resolved. In practice, forward proof is often used within backward proof to convert each goals assumptions into a suitable form.

Theorems in the HOL system are represented by values of the ML abstract type thm. There is no way to construct a theorem except by carrying out a proof based on the primitive inference rules and axioms. HOL system has many built-in inference rules and ultimately all theorems are proved in terms of these axioms and basic inferences of the calculus. By applying a set of primitive inference rules, a theorem can be created. Once a theorem is proved, it can be used in further proofs without recomputation of its own proof. In this way, the ML type system protects the HOL logic from arbitrary construction of a theorem, so that every computed value of the type-representing theorem is a theorem. The user can have a great deal of confidence in the results of the system.

The HOL system has been used in hardware verification, reasoning about security, verification of fault-tolerant computers, and reasoning about real-time systems. It has also found application in compiler verification, program refinement calculus, software and algorithms verification, modeling, and automation theory. HOL also has a rudimentary library facility which enable theories to be shared. This provides a file structure and documentation format for self contained HOL developments. Many basic reasoners are given as libraries such as **mesonLib**, **bossLib**, and **simpLib**. These libraries integrate rewriting, conversion and decision procedures and free the user from performing low-level proof.

## 3.6 Normal Forms

**Definition 1.** A formula is in Disjunctive Normal Form (DNF) if it is a disjunction of minterms (conjunctions of literals). In other words, a DNF formula is a sum of products and looks like:

$$(x_{11} \land x_{12} \land \dots \land x_{1n_1}) \lor (x_{21} \land \dots \land x_{2n_2}) \lor \dots \lor (x_{m1} \land \dots \land x_{mn_m})$$

where each  $x_{ij}$  is a literal. Literal is a variable or it's negation. In short:

$$\bigvee_i \bigwedge_j x_{ij}$$

**Definition 2.** A *literal* L is either an atom p or the negation of an atom  $\neg p$ . A formula C is in *Conjunctive Normal* Form(CNF) if it is a conjunction of clauses, where each clause D is a disjunction of literals:

$$L ::= p |\neg p$$

$$D ::= L | L \lor D$$

$$C ::= D | D \land C$$

**Definition 3.** Given a formula  $\phi$  in propositional logic, we say that  $\phi$  is *satisfiable* if it has a valuation in which it evaluates to T. For example, the formula  $p \lor q \to p$  is *satisfiable* since it computes T if we assign T to p. Clearly,  $p \lor q \to p$  is not valid. Thus, satisfiability is a weaker concept since every valid formula is by definition also satisfiable but not vice versa. However, these two notions are just mirror images of

each other, the mirror being negation.

**Proposition 4.** Let  $\phi$  be a formula of propositional logic. Then  $\phi$  is satisfiable iff  $\neg \phi$  is not valid.

Proof: First, assume that  $\phi$  is satisfiable. By definition, there exists a valuation of  $\phi$  in which  $\phi$  evaluates to T; but that means that  $\neg \phi$  evaluates to F for that same valuation. Thus,  $\neg \phi$  cannot be valid.

Second, assume that  $\neg \phi$  is not valid. Then there must be a valuation of  $\neg \phi$  in which  $\neg \phi$  evaluates to F. Thus,  $\phi$  evaluates to T and is therefore satisfiable. (Note that the valuations of are exactly the valuations of  $\neg \phi$ ).

This result is extremely useful since it essentially says that we need to provide a decision procedure for only one of these concepts. For example, lets say that we have a procedure P for deciding whether any  $\neg \phi$  is valid. We obtain a decision procedure for satisfiability simply by asking P whether  $\neg \phi$  is valid. If it is,  $\phi$  is not *satisfiable*; otherwise  $\phi$  is *satisfiable*. Similarly, we may transform any decision procedure for satisfiability into one for validity.

In this Chapter, we presented some of the basics required for better understanding the rest of chapters of this book. We provided the basics of temporal logics, Multiway Decision Graph, MDG tool, boolean SAT solvers as well as HOL theorem prover. In the next chapter, we describe our proposed methodology in detail.

## Chapter 4

# Integrating SAT with MDG

In this chapter, we present the proposed methodology for SAT based invariant checking. SAT has already been integrated with MDG tool as a *reduction engine* in [9]. This chapter provides a step by step description of the complete methodology using SAT as *verification engine* with MDG.

## 4.1 Formalization of the Problem

Given a state machine M with initial states I and transition relation Tr, we would like to check whether a property P holds for all the reachable states. The reachable states are those which can be reached by Tr transitions starting from an initial state. Let S denote the entire set of states. A system is a *safe system*, where all the reachable states satisfy P.

Introduction of various type of paths through the graph of a transition relation is required to formalize the problem more precisely. We write Tr(x, y) to indicate that x is related to y by a transition relation Tr. We define the sequence of states to be a path through Tr.

$$path(s_{[0...n]}) \triangleq \bigwedge_{0 \le i < n} Tr(s_i, s_{i+1})$$

Here " $\triangleq$ " sign means "is defined to be" and  $s_{[0...n]}$  denotes a sequence of states (set of state) e.g.  $s_0, s_1, s_2, ..., s_n$ . A path can have a length n, if it makes n transitions. For us, we are interested to show that, starting from the initial state and repeated application of transition relation always leads to a state that satisfies P. We want to show that,

$$\forall i.\forall s_0....si.(I(s_0) \land path(s_{[0...i]}) \to P(s_i))$$

where,  $i \ge 0$  and  $s_i \in S$ . Similarly, proving backward from bad states involves showing that, starting from a state that violates P and going backwards through Tr always leads to a non-initial state, which is

$$\forall i.\forall s_0....si. \neg (I(s_0) \leftarrow path(s_{[0...i]}) \land \neg P(s_i))$$

To get a more symmetric view at the problem, we say there are no paths that start in an initial state and end in a non-P-state, that is,

$$\forall i.\forall s_0....s_i.\neg(I(s_0) \land path(s_{[0...i]}) \land \neg P(s_i))$$

## 4.2 Proposed Methodology

We propose a methodology (Figure 4.1) to formulate and verify a formula (we call this formula *Correctness formula*), to check the safety of a system or design. In our methodology, we are interested to check if the formula,

$$\forall i.\forall s_0....si.\neg(I(s_0) \land path(s_{[0...i]}) \land \neg P(s_i))$$

holds for i = 0, i = 1, i = 2 and so on. It is similar to check  $I(s_0) \wedge path(s_{[0...i]}) \wedge \neg P(s_i)$  is a contradiction for each *i*, for  $s_0$  to  $s_i$ ; i.e.  $\neg(I(s_0) \wedge path(s_{[0...i]}) \wedge \neg P(s_i))$  is a tautology. If the property *P* is violated in a reachable state, then,  $\exists i.I(s_0) \wedge path(s_{[0...i]}) \wedge \neg P(s_i)$  is satisfiable. A SAT solution refers that there exists a path

Figure 4.1: Verification Methodology using MDG tool and SAT solver

of length i starting from initial states that violates P and it can be used for tracing errors.

Automation of this approach with MDG involves four main tasks:

- Compute the reachable states, starting from the initial state. It will give us the path by which each possible reachable state can be reached, by each transition, until all the reachable states have been visited.

- The reachable states are computed in *Directed Formula* format. Removal of *Uninterpreted functions* and introduction of boolean encoding is required to convert the formula suitable for boolean SAT solvers.

- Perform the *CNF* conversion of the boolean formula using a linear algorithm to avoid exponential blow up (direct conversion from *DNF* to *CNF* has exponential blow up).

- Fed the formula to a SAT solver to check the satisfiability.

Using SAT solver with MDG tool is a new and efficient approach for invariant checking. The steps in the methodology are as following:

- We use MDG tool to compute the sets of reachable states for the given MDG model (behavioral/RTL) written in MDG-HDL language. Any other implementation of MDG reachability analysis algorithm can be used instead of MDG tool. We conjunct all the sets of states which gives us the a set S<sub>reachable</sub> consisting of all the reachable states for the system in DF format.

- 2. Boolean Encoding is imposed by the preprocessor to reduce the DF in propositional logic. After removal of *uninterpreted functions* the encoder generates a pure boolean formula  $DF_{bool}$  with certain encoding constraints.

- 3. We get formula  $B_{DF}$  after conjunction of  $DF_{bool}$  with Encoding constraints and *negated* invariant property.

- 4. The  $B_{DF}$  is converted into CNF using Tseitin algorithm. The output is SAT encoded CNF formula in DIMACS [3] format. At this stage we call this formula *Correctness Formula*.

- 5. The SAT encoded correctness formula is fed to a SAT solver to prove  $\neg(S_{reachable} \land \neg P \land constraints)$  a tautology or  $(S_{reachable} \land \neg P \land constraints)$  is a contradiction.

Detail description of these steps is explained in the following subsections.

#### 4.2.1 Using MDG for Reachibility Analysis

The presence of uninterpreted symbols in the logic means that we must distinguish between a state machine M and its abstract description D in the logic. This is called Abstract State Machine, a state machine given an abstract description in terms of DFs, or equivalently MDGs, as defined in [25, 11].

Definition 1. An Abstract Description of a State Machine (ASM) M is a tuple D = (X, Y, Z, Y', IS, Tr, Or), where:

• X : finite set of input variables,

- Y : finite set of state variables,

- Z : finite set of output variables,

- IS : MDG of type U<sub>0</sub> → Y , where U<sub>0</sub> is a set of disjoint abstract variables, IS is the abstract description of the set of initial states,

- Tr : MDG of type  $X \cup Y \to Y'$ . Tr is the abstract description of the transition relation,

- Or : MDG of type  $X \cup Y \to Z$ . Or is the abstract description of the output relation.

Algorithm 3 shows how the analysis of the reachable states of M is performed based on the abstract description D.

Algorithm 3 MDG Reachibility Analysis

| 1: $R := IS;$                                                     |

|-------------------------------------------------------------------|

| 2: Q := IS;                                                       |

| 3: i := 0;                                                        |

| 4: while $Q \neq F$ do                                            |

| 5:  i:=i+1;                                                       |

| $6: IN := new\_inputs(i); - \texttt{Produce new inputs}$          |

| 7: $NS := next\_states(IN, Q, Tr);$ - Compute next state          |

| 8: $Q := frontier(NS, R);$ - Set difference                       |

| 9: $R := union(R,Q);$ Merge with set of states reached previously |

| 10: end while                                                     |