#### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, Mi 48106-1346 USA

# HIGH PERFORMANCE VIRTUAL ARCHITECTURE PARALLEL LIBRARIES WITH DATA REDISTRIBUTION FOR MULTICOMPUTERS

HASSAN HOSSEINI

A THESIS

THE DEPARTMENT

OF

COMPUTER SCIENCE

PRESENTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

CONCORDIA UNIVERSITY

MONTRÉAL, QUÉBEC, CANADA

January 1998 © Hassan Hosseini, 1998

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-40310-6

#### Abstract

High Performance Virtual Architecture Parallel Libraries With Data Redistribution For Multicomputers

Hassan Hosseini, Ph.D. Concordia University, 1998

Sequential programs which use library calls to perform their intensive numerical computations may not deliver satisfactory performance for large problem instances in uniprocessor systems. Replacing the library system with one that performs the computations on a multicomputer can provide significant improvement in the execution time of these programs. These parallel libraries also encourage programmers who have no knowledge of multicomputer programming to use multicomputers to run their newly developed compute-intensive applications.

Multicomputer programs perform computations on distributed data. Transfer of data between processors is carried out using communication operations which are normally costly. Introduction of parallel library systems gives rise to four important issues. The first one is the design of the library routine without knowing the problem instance size and the physical system size, as this is the case with many partitionable and reconfigurable systems. Performance of the library routine which is sensitive to the granularity of the computation and the mapping of the computation onto the physical system is the second issue. Maintaining a call interface which resembles those of sequential libraries is the third one. Finally, once ported to a new platform, parallel system speedup becomes a major concern.

Data distribution at each parallel library call is performed sequentially which, consequently, degrades the performance of the library routine. Since distributed data used or produced by one library call is often used in the subsequent calls to the same routine or other library routines, it is beneficial to redistribute the data from the former library call to prepare for the latter. The redistribution operation is a parallel operation and reduces the overall execution time of a parallel library call.

This thesis presents the design of a parallel library system which possesses several unique properties. The design supports dynamic grain adjustment and delayed mapping of the virtual to physical processors in order to reduce the communication overhead of the library calls. It also supports transparent distributed data management that results in a call interface similar to those of sequential libraries. Furthermore, the design supports transparent data redistribution across parallel library calls. Once ported to a new system, the library can be easily adjusted with the target system parameters to deliver the best performance based on the new parameters.

Feasibility, performance, and overhead of our design have been experimented using a source to source transformer, a compiler, library design of several virtual architecture parallel algorithms, a mapping module, a virtual communication library, a redistribution library, and a multicomputer simulator. The implementation of the library system on an actual multicomputer has been thoroughly discussed in the thesis.

## Acknowledgments

Parents and teachers play a big role in shaping a person's life, but hardly ever appreciated enough. This is an opportunity to express my gratitude towards my supervisor, Dr. Lixin Tao, in assisting me in getting this work to this stage. I would also like to dedicate this work to the memories of my father and to my mother.

My family will certainly remember these years in the future. My wife, Parvaneh, gave me the support and encouragement I needed to pursue this work. My children Behnam, and Behnaz, the highlights of my life, have made this a much more challenging endeavor.

Thanks to the members of our research team, Dr. Lixin Tao, Hoang Uyen Trang Nguyen, and Thien Bui who each contributed to the implementation of our programming environment. Dr. Lixin Tao led the team, Trang developed the Wormhole routing simulator, and Trang and Thien contributed to the code execution module.

My good friends and partners are difficult not to mention. Trang and Thien were always there for advice and assistance on technical and non-technical issues. I am thankful to Ken Hahn, George Felfli, and Osama Abu-Shihab for giving me encouragement and, in some cases, technical advice. My relatives and friends who were concerned and, therefore, will be remembered were: My brother-in-law Hassan, Ben, Helen, Jahan, and Firoozeh.

Many thanks to the UNIX system administrators at Concordia who have provided superior system support and services. I would especially like to thank Stan for his technical support. A token of appreciation also goes to the secretarial staff at Concordia, especially Halina Monkiewicz, who were always friendly and prompt in providing assistance.

## Contents

| Li             | st of | Figures                                                          | vii       |  |  |  |  |  |  |  |  |  |

|----------------|-------|------------------------------------------------------------------|-----------|--|--|--|--|--|--|--|--|--|

| List of Tables |       |                                                                  |           |  |  |  |  |  |  |  |  |  |

| 1              | Inti  | roduction                                                        | 1         |  |  |  |  |  |  |  |  |  |

|                | 1.1   | Parallel Library Issues                                          | 2         |  |  |  |  |  |  |  |  |  |

|                | 1.2   | Current Status                                                   | 6         |  |  |  |  |  |  |  |  |  |

|                | 1.3   | Our Approach                                                     | 7         |  |  |  |  |  |  |  |  |  |

| 2              | Bac   | kground and Related Work                                         | 10        |  |  |  |  |  |  |  |  |  |

|                | 2.1   | Parallel Libraries                                               | 11        |  |  |  |  |  |  |  |  |  |

|                |       | 2.1.1 ScaLAPACK and CMSSL Parallel Libraries                     | 11        |  |  |  |  |  |  |  |  |  |

|                |       | 2.1.2 Performance Metrics                                        | 12        |  |  |  |  |  |  |  |  |  |

|                |       | 2.1.3 Conformance Model                                          | 18        |  |  |  |  |  |  |  |  |  |

|                |       | 2.1.4 Delayed Granularity Adjustment and Delayed Mapping         | 20        |  |  |  |  |  |  |  |  |  |

|                |       | 2.1.5 Data Distribution                                          | 21        |  |  |  |  |  |  |  |  |  |

|                | 2.2   | Application Domain                                               | 25        |  |  |  |  |  |  |  |  |  |

|                | 2.3   | Programming Paradigms                                            | 26        |  |  |  |  |  |  |  |  |  |

|                | 2.4   | Communication Model                                              | 29        |  |  |  |  |  |  |  |  |  |

|                | 2.5   | Automatic Data Redistribution                                    | 30        |  |  |  |  |  |  |  |  |  |

|                | 2.6   | Examples of Library Systems                                      | 33        |  |  |  |  |  |  |  |  |  |

| 3              | Par   | allel Library Design                                             | 39        |  |  |  |  |  |  |  |  |  |

|                | 3.1   | Integrated Components of the Library                             | 45        |  |  |  |  |  |  |  |  |  |

|                |       | 3.1.1 Virtual Processor Implementation                           | 49        |  |  |  |  |  |  |  |  |  |

|                |       | 3.1.2 Virtual Communication Library                              | <b>52</b> |  |  |  |  |  |  |  |  |  |

|                |       | 3.1.3 Library Routine Handle: A Dynamic Entity                   | 58        |  |  |  |  |  |  |  |  |  |

|                |       | 3.1.4 Representation of Data and Processor Mapping               | 62        |  |  |  |  |  |  |  |  |  |

|                |       | 3.1.5 Handle Allocation and Initialization Modules               | 67        |  |  |  |  |  |  |  |  |  |

|                |       | 3.1.6 Virtual Architecture Initialization and Contraction Module | 68        |  |  |  |  |  |  |  |  |  |

|                |       | 3.1.7 Mapping Module                                             | 68        |  |  |  |  |  |  |  |  |  |

|                |       | 3.1.8 Data Distribution Module                                   | 70        |  |  |  |  |  |  |  |  |  |

|    |            | 3.1.9 Data Accumulation Module                                      | 71  |

|----|------------|---------------------------------------------------------------------|-----|

|    | 3.2        | Conversion of the User Program to Single Program Multiple Data Form | 71  |

|    | 3.3        | Performance Analysis                                                | 79  |

|    | 3.4        | Experimental Results and Performance Evaluation                     | 89  |

|    | 3.5        | Impacts on the Library User, Designer, and the Compiler             | 100 |

| 4  | Aut        | omatic Data Redistribution                                          | 104 |

|    | 4.1        | Data Redistribution Design                                          | 107 |

|    | 4.2        | Data Redistribution and the Source to Source Transformation         | 117 |

|    | 4.3        | Performance Analysis                                                | 120 |

|    | 4.4        | Performance Results                                                 | 121 |

| 5  | An         | Integrated Parallel Library Programming Environment                 | 123 |

|    | 5.1        | Source to Source Transformation and the Compiler                    | 123 |

|    | <b>5.2</b> | The Multicomputer Simulator                                         | 129 |

|    |            | 5.2.1 Scheduling and Communication Cost Model                       | 131 |

|    |            | 5.2.2 Communication Library                                         | 133 |

| 6  | Соп        | clusion                                                             | 135 |

| A  | A P        | rogramming Example: Matrix Multiplication                           | 137 |

| В  | Maj        | oping Library                                                       | 153 |

| C  | Vir        | tual Communication Library                                          | 156 |

| D  | Red        | istribution Library                                                 | 162 |

| E  | Exa        | mple User Program and Compilation                                   | 177 |

| Bi | blios      | raphy                                                               | 184 |

## List of Figures

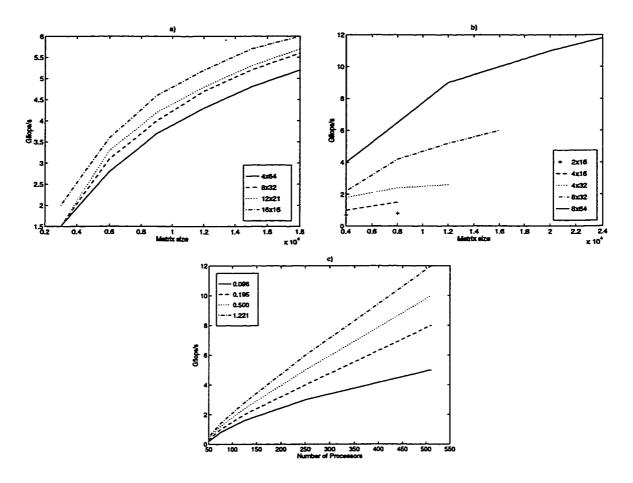

| 1  | Performance metrics of ScaLAPACK LU decomposition library routine. a) Perfor-         |    |

|----|---------------------------------------------------------------------------------------|----|

|    | mance for different processor templates. b) Performance for different number of pro-  |    |

|    | cessors. c) Isogranularity curves where labels are reduced by a factor of a million   | 19 |

| 2  | Block and cyclic decomposition example for 8 elements over 3 processors               | 22 |

| 3  | Block cyclic decomposition example for 23 elements over 3 processors for a block      |    |

|    | size of 2 (top) and the corresponding inverse mapping from the triplets to the global |    |

|    | indices (bottom)                                                                      | 23 |

| 4  | A matrix object in ScaLAPACK                                                          | 24 |

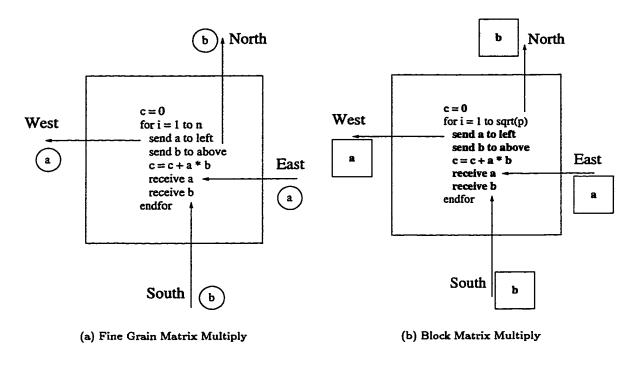

| 5  | Fine grain and block matrix multiply                                                  | 26 |

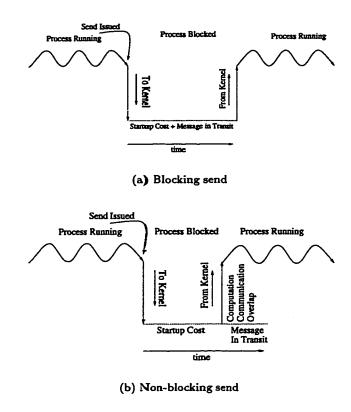

| 6  | Blocking and non-blocking send                                                        | 30 |

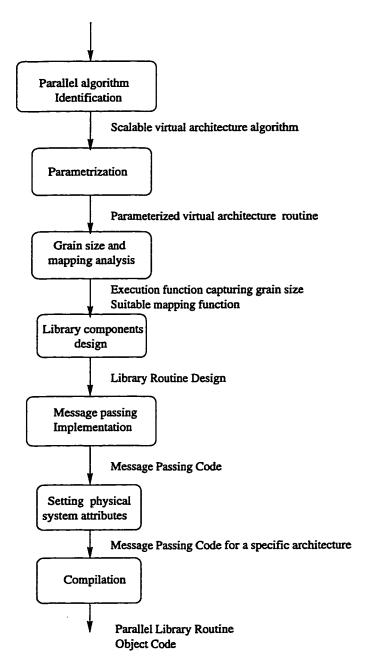

| 7  | Steps of library routine creation                                                     | 43 |

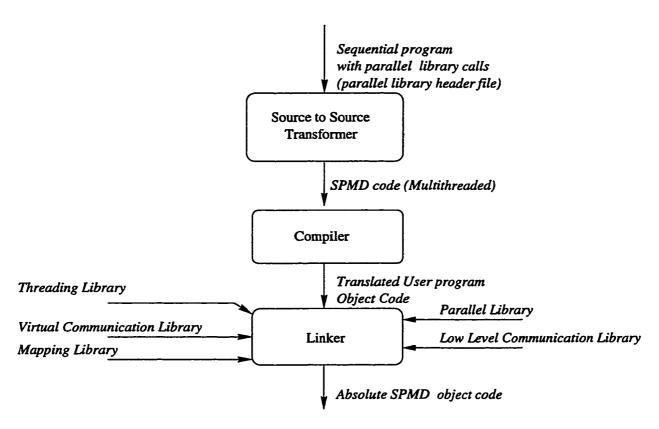

| 8  | Compilation process of a sequential program with library calls                        | 44 |

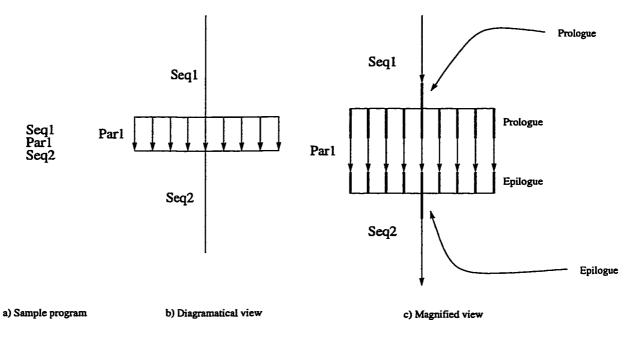

| 9  | Prologue and epilogue in a parallel call                                              | 45 |

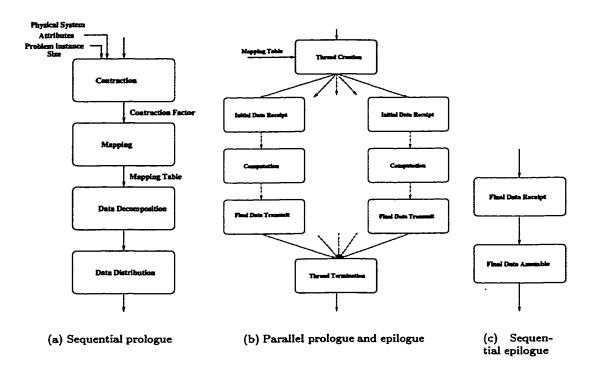

| 10 | The components of a parallel library call                                             | 47 |

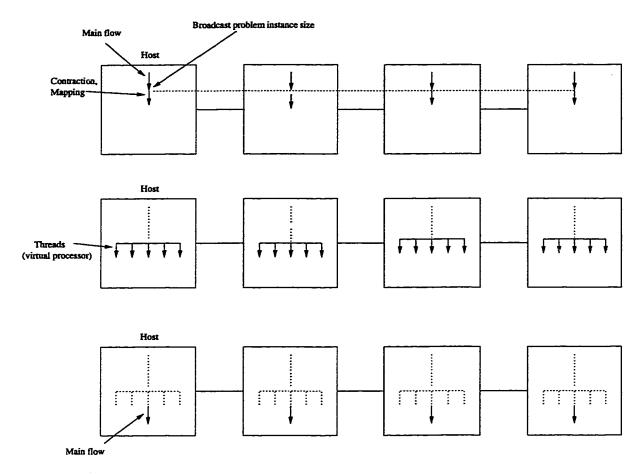

| 11 | Flow of control in a parallel library call                                            | 48 |

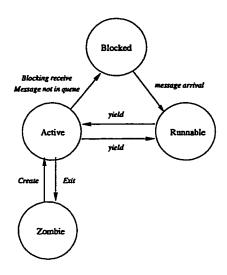

| 12 | Thread state transition diagram                                                       | 50 |

| 13 | Thread library calls                                                                  | 51 |

| 14 | Communication library calls                                                           | 53 |

| 15 | Virtual who and the virtual point-to-point communication prototypes                   | 55 |

| 16 | Virtual collective communication library prototypes                                   | 57 |

| 17 | Virtual broadcast communication operation                                             | 58 |

| 18 | Definition of a library routine handle                                                | 59 |

| 19 | Pictorial view of a library handle                                                    | 60 |

| 20 | Structure for virtual architecture declaration                                        | 61 |

| 21 | Structure for data mapping                                                            | 61 |

| 22 | Structure for processor mapping                                                       | 61 |

| 23 | Structure for distributed data                                                        | 61 |

| 24 | Structure describing data contraction                                                 | 62 |

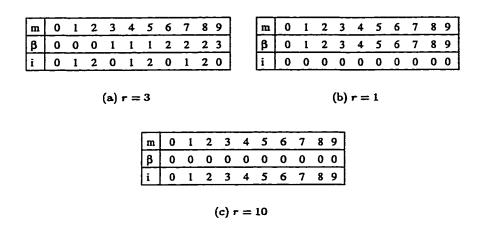

| 25 | Examples of block(r) data mapping for $M = 10 \dots \dots \dots$                      | 63 |

| 26 | Examples of block $(r, s)$ mapping for $m = 6$ and $n = 4$                            | 64 |

| 97 | Representation of block(3.3) mapping for $m=6$ and $n=4$                              | 65 |

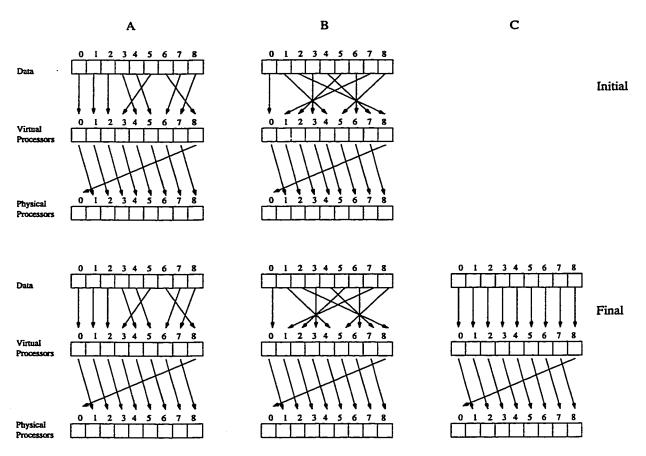

| 28        | Initial and final data distribution for matrix multiply - $3 \times 3$ blocks of data onto a |     |

|-----------|----------------------------------------------------------------------------------------------|-----|

|           | $3 \times 3$ mesh of processors                                                              | 66  |

| 29        | Change of storage to accommodate block matrix algorithms (Single element row major           |     |

|           | storage to row major storage with block size of $2 \times 2$ )                               | 72  |

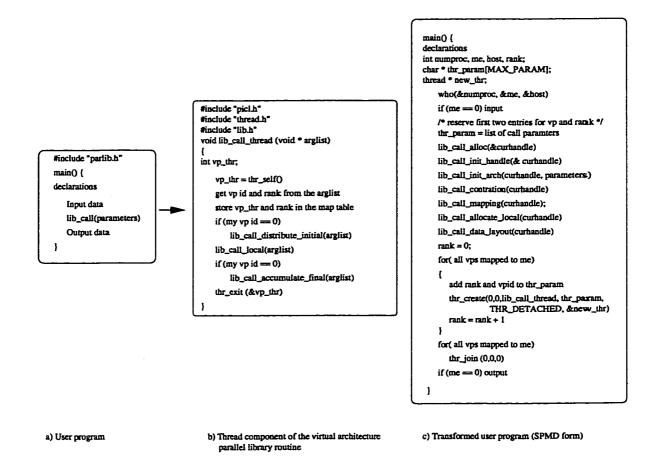

| 30        | An example of source to source transformation                                                | 77  |

| 31        | An example of translation of a write to a poly variable                                      | 78  |

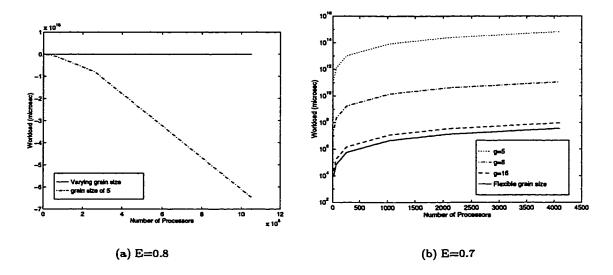

| 32        | Comparison of the isoefficiency functions for $g = 5, 8, 16$ and $g = \frac{n}{\sqrt{p}}$    | 83  |

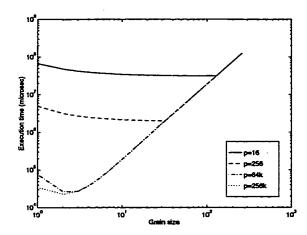

| 33        | Optimal grain size selection                                                                 | 84  |

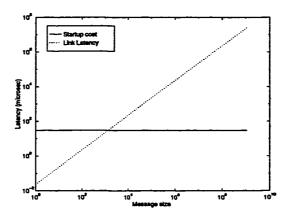

| 34        | Link latency as a function of the message size                                               | 86  |

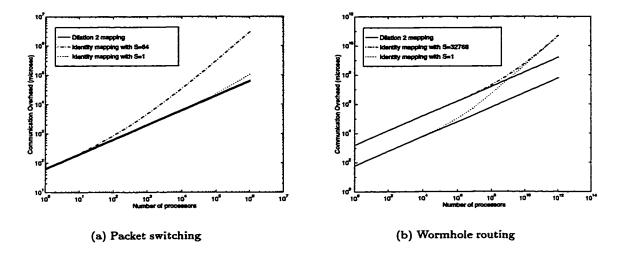

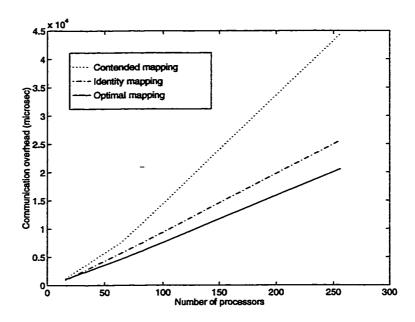

| 35        | Comparison of the cumulative overhead between two different mapping functions for            |     |

|           | n=1024                                                                                       | 89  |

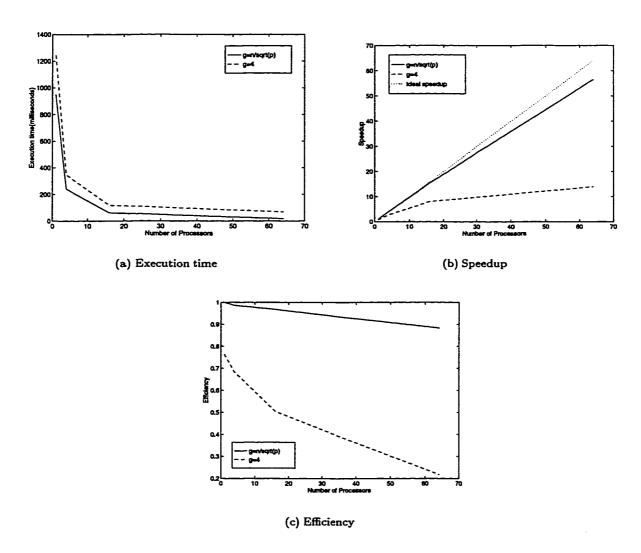

| 36        | Comparison of $g=4$ and $g=\frac{n}{\sqrt{p}}$ . a) Execution time b) Speedup c) Efficiency  | 91  |

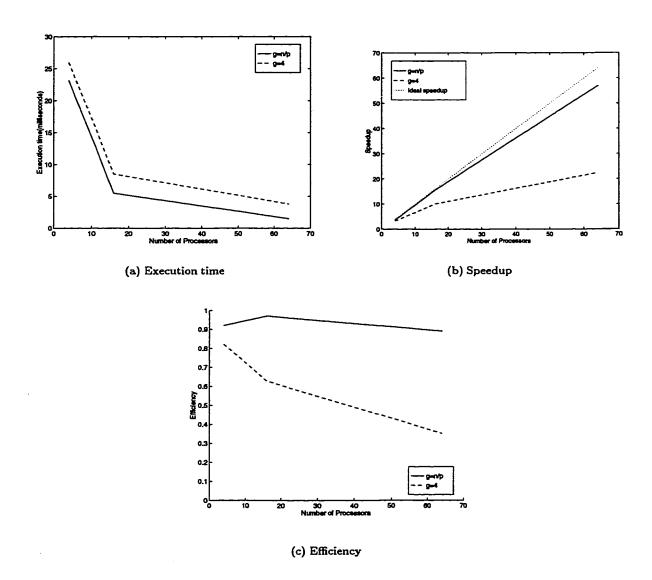

| 37        | Comparison of the FFT algorithm for $g=4$ and $g=\frac{n}{p}$ . a) Execution time b) Speedup |     |

|           | c) Efficiency                                                                                | 93  |

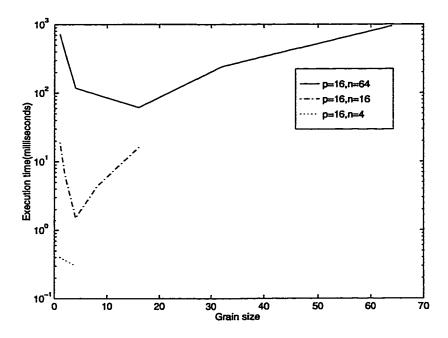

| 38        | Runtime Granularity Adjustment                                                               | 94  |

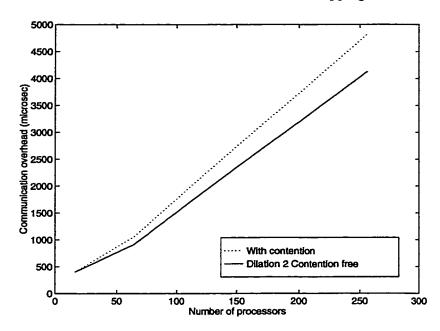

| 39        | Effects of contention in packet switching                                                    | 97  |

| 40        | Effects of contention in wormhole routing                                                    | 98  |

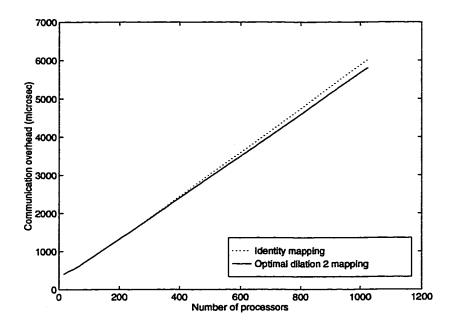

| 41        | Effects of communication bottleneck in wormhole routing                                      | 99  |

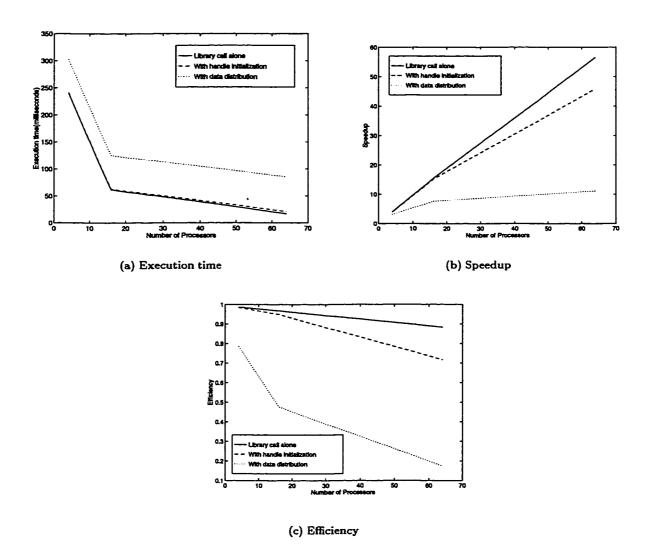

| 42        | Comparison of the execution time, speedup, and performance of matrix multiplica-             |     |

|           | tion library routine alone, with handle initialization overhead, and with initial data       |     |

|           | distribution overhead                                                                        | 101 |

| 43        | Example of distribution versus redistribution time                                           | 105 |

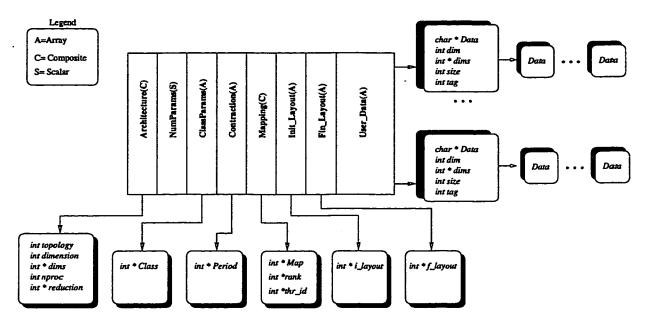

| 44        | Enhanced user structure for data redistribution                                              | 109 |

| 45        | Enhanced Structure of a Library Handle                                                       | 110 |

| 46        | Three cases of redistribution                                                                | 111 |

| 47        | Computation of the source (left) and the destination (right) sets for the case $g' = kg$     | 113 |

| 48        | Computation of the source (left) and the destination (right) sets for the case $g = kg'$     | 114 |

| 49        | Computation of the source (left) and the destination (right) sets for the case with no       |     |

|           | multiplicative relationship between $g$ and $g'$                                             | 116 |

| 50        | Source to source transformation with support of redistribution                               | 118 |

| 51        | An example invalidation of distributed data                                                  | 119 |

| <b>52</b> | Source to source transformation and compilation process                                      | 124 |

| 53        | Example of a source to source transformation (Redistribution ON)                             | 125 |

| 54        | An example generation of guards (Redistribution OFF)                                         | 126 |

| 55        | Example mapping of a mesh to a line                                                          | 129 |

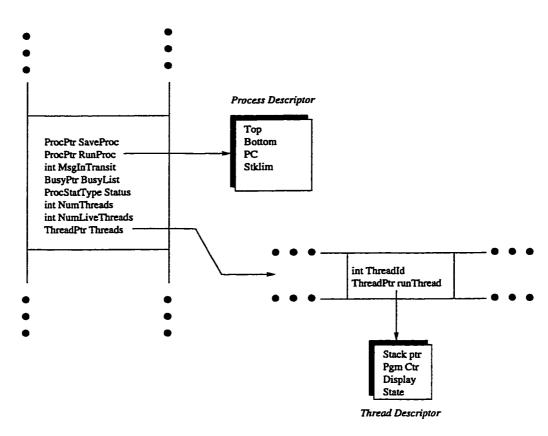

| 56        | Physical processor and thread table                                                          | 130 |

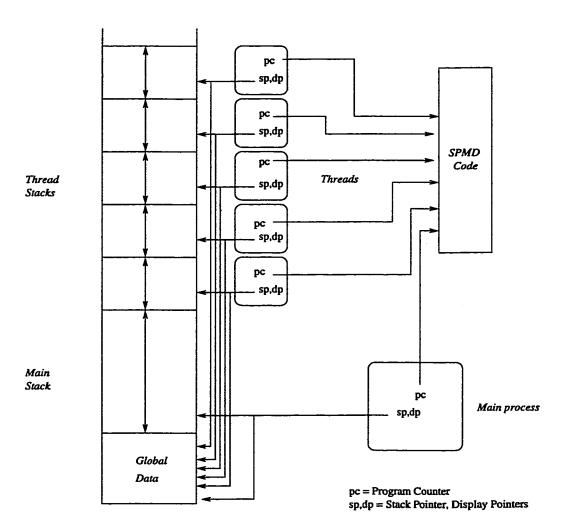

| 57        | Physical processor and threads stack utilization                                             | 132 |

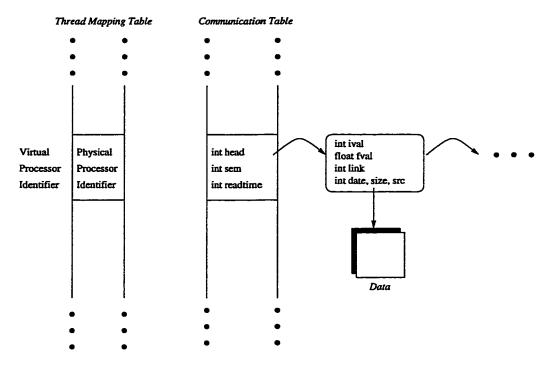

| 58        | Physical communication structures                                                            |     |

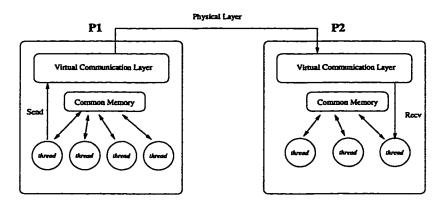

| 59        | Intraprocessor vs. interprocessor communication                                              |     |

## List of Tables

| 1  | Local and global performance per node for some library routines in CMSSL              | 17  |

|----|---------------------------------------------------------------------------------------|-----|

| 2  | Space of the call models                                                              | 20  |

| 3  | Characteristics of the most commonly known parallel systems                           | 31  |

| 4  | Initial and final distribution of data in the torus based matrix multiply             | 65  |

| 5  | Simulation data: Execution, speedup, and efficiency for different problem and system  |     |

|    | sizes for torus based matrix multiplication                                           | 90  |

| 6  | Simulation data: Execution, speedup, and efficiency for different problem and system  |     |

|    | sizes for Cooley-Tukey algorithm                                                      | 92  |

| 7  | Simulation data: Execution time as function of grain size                             | 92  |

| 8  | Simulation data: Contention free vs. contended mapping in packet switching            | 97  |

| 9  | Simulation data: Contention free vs. contended mapping in wormhole routing            | 98  |

| 10 | Simulation data: Effects of communication bottleneck in wormhole routing              | 99  |

| 11 | Simulation data: Execution time of the library routine alone, with handle initializa- |     |

|    | tion, and with initial data distribution for torus based matrix multiplication        | 100 |

| 12 | Simulation data: Performance gain in data redistribution.                             | 122 |

## Chapter 1

## Introduction

Reusability, modularity, and portability are aspects of software engineering that allow fast development of reliable, easily maintainable, and portable programs [63]. Libraries are a mechanism to support these aspects. Moreover, ease of use, efficiency, and correctness of a library system encourage the programmers to take advantage of the existing routines as opposed to developing new ones from scratch. There are many existing sequential programs that rely on numerical library routines, such as LINPACK [21], to perform their intensive numerical computations such as matrix and vector operations, Gaussian elimination, Fast Fourier Transform, and so on. These libraries have been designed to facilitate programming and provide good performance. Some hardware characteristics such as the hierarchy of memory, the number of registers and the memory latency have been considered in the design of these libraries to improve the performance. However, when large problem instance sizes need to be solved using these library routines, regardless of the various optimizations, the performance may still be unsatisfactory due to the sequential nature of the library routines. Even if the libraries are based on the multitasking or multithreading technique, the performance will be limited by the speed of the uniprocessor system.

With the advent of parallel computing, programmers have considered running their existing or newly developed programs on distributed-memory systems to reduce the execution time of their programs beyond the limits of the uniprocessor systems. Since, for large problem instance sizes, the majority of the execution time of the program is spent in the sequential library routines, these library routines have been the first target for improving the overall performance of the programs. Programming on multicomputers is in general difficult because many fine details must be managed by the programmer. Performance gain is also challenging on these systems since communication operations are expensive. The execution time is usually sensitive to the granularity of the computation and the mapping of the computation to the physical processors. Partitionable and reconfigurable systems make programming on these systems even more difficult because the programmer is not aware of the system size and topology at programming time. Parallel libraries can greatly reduce the programmer's task in using multicomputers. A desirable parallel library design preserves the sequential call interface, offers good performance, and can be easily ported. Parallel libraries which

possess these characteristics allow the existing sequential programs with library calls to be easily assimilated into a multicomputer environment. The library system can provide the programmer with the tool to convert the sequential program, that interfaces with the parallel library, to an SPMD<sup>1</sup> form. The library system can then provide the necessary components to be linked with the SPMD form to obtain an executable image for the specific multicomputer. These components are either the library routine and its constituents or other runtime libraries used in the parallel library routine implementation, such as a threading library, mapping library, communication library, or redistribution library provided by a one-time compilation using the resident compiler of the target system. In any case, no parallel programming knowledge will be required from the programmer. Knowledge of how to load and run an executable image on the target system can be easily encapsulated. Portability can be easily accommodated in such design by using standard calls, such as calls to standard communication and threading libraries. This will require absolutely no changes to the user program to run on the new system. However, a scheme is required to ensure the best speedup on the target system after porting. With advances in the hardware technology, the latency and the startup cost of communication will be reduced in the future systems. Even in the currently existing multicomputers, the communication latency varies noticeably between different multicomputers. Consequently, library routines must adjust the degree of concurrency and the granularity based on the physical system attributes, such as the communication latency and the processor speed.

Once a design with the above characteristics is implemented, the best algorithms for the scientific and numerical applications can be selected and placed in a parallel library to be used by the programmers. These library routines can also be tuned for better performance prior to compilation. Providing such a system for the programmer requires a rather elaborate design of the library system. There are several design issues which affect either the performance, the user interface, or the portability.

In the following sections, we unravel the problems in the design of parallel libraries, provide a critical view of the current approaches to solve some of these problems, and present a comparative view of the current approaches with the ones proposed in this thesis.

#### 1.1 Parallel Library Issues

The difficulty of parallel library design stems from the lack of a clear model similar to the sequential stack model. In sequential library calls, input and its size are passed as parameters on the stack to the library routine. The library routine also returns the results to the caller through the parameters on the stack. This provides a natural and easy interface for the callers. The performance of the library routine, for a given problem instance, is then solely determined by the underlying algorithm and the optimizations performed by the compiler. Sequential library routines are easy to write and optimize. The associated cost of calling these routines is also well defined. These libraries are also easy to port bearing in mind the interoperability issues. In a parallel library routine, on the other hand, the library writer must deal with the distributed data and its impact on the user interface,

<sup>&</sup>lt;sup>1</sup> Single Program Multiple Data model is referred to the programming model where computation is described by the same code operating on different data items.

the communication overhead of the library routine, and the complexity in the design of the library routine itself. Unknown physical system size, topology, and physical system characteristics at the library routine design time make this problem even harder to deal with. Mapping of processes to the processors, grain size of computation and communication, and scalability of the parallel algorithm have serious impact on the communication overhead of the program. In addition, the communication overhead of the library routine upon invocation, due to data distribution, may be avoided by data redistribution. Here we elaborate on the factors which concern the design of parallel libraries and their impact on the library writer, the user of the library, and the compiler.

Performance - Degree of parallelism and the granularity of the computation used by a library routine must be selected to minimize the execution time of the routine. Different systems require different values for the degree of parallelism and the granularity to deliver their best performance. A parallel library must harness the underlying system based on its hardware characteristics such as the communication latency and the processor speed. When the library is ported to another system, a centralized modification to the library may be used to ensure that the library routine selects the granularity and the mapping based on the characteristics of the new system. An example would be to relay to the library system the startup cost of communication and the link bandwidth.

Problem instance size - The problem instance size is usually input at runtime. The parallel library routine based on the logical architecture must be described without this knowledge. This also delays the grain adjustment and mapping of the library routine to runtime when the problem instance size is known.

System size and topology - We use the term partitionable for systems which are based on a fixed topology from which a partition is granted to the user upon request. Size of this partition depends on the system availability at the time of the request. The term reconfigurable is used for systems in which the topology may also change statically or dynamically. In these systems a user's request for a partition is submitted after an executable image of the parallel program is built. The granted partition may differ between different runs of the same program depending on the requested size, system load, the maximum system size, and the scheduling policy. Partitionable and reconfigurable systems give rise to unknown attributes at the time of library routine design. The library routine writer is unaware of the physical system size at implementation time. Hence, the library routine must minimize the execution time of the library routine given the size and topology of the granted processors.

Mapping - Communication among the processors is much more expensive than an instruction execution. Assignment of the logical processors to the physical processors impacts the communication requirements of the parallel program which, in turn, affects the execution time of the program. Since the physical system size and topology are not known until runtime in both partitionable and reconfigurable systems, mapping of the computation to the physical processors must be delayed to runtime. The design of the library system for partitionable systems is simpler since only a limited number of mappings from the logical processors to the physical

processors needs to be considered. The mapping library can be simplified on these systems since the target topology is known. For reconfigurable systems, the physical topology may also change, so the library designer must consider all possible physical topologies. The mapping library must be extended to accommodate any target topology. These systems, however, may provide better performance as there is a higher possibility of matching the logical topology with the physical one. Mismatch between the logical topology and the physical topology may introduce additional communication overhead. Since the topology of a logical architecture algorithm is generally representative of the communication pattern of that algorithm, it is desirable to map the neighboring nodes of the logical topology as close as possible in the target architecture. Mapping functions that minimize this distance tend to reduce the communication overhead through avoidance of hot spots in the network and reduction of the communication latency between the nodes. If the communication pattern of the parallel algorithm is based on a unique pattern or topology not supported by the mapping library, or it requires a mapping function not commonly used or supported, the mapping function can be built into the library routine. The most commonly used mapping functions can, however, be placed in a common library to be used by all the library routines.

If the size of the logical architecture and the physical system are the same, one-to-one mapping can be used to execute the parallel library routine. Even with the flexibility of dynamic grain adjustment the logical architecture size may not be reducible to the physical system size. In such case, many-to-one mapping will be required to execute the parallel library routine. In other words, more than one logical processor will be emulated at least by one physical processor. Logical processors must be emulated using a model that allows execution of multiple logical processors in a physical processor without intolerable overhead. In addition, communication between logical processors will require resolution of message destination at each physical processor.

Call parameters and Distributed data - Prior to calling a parallel library routine, the actual parameters must be decomposed and distributed among the logical processors. A library writer must determine the level of the caller intervention on the initial data distribution, the final data accumulation, and the corresponding impact on the user interface to the library routines. Each parallel algorithm requires its data in a specific distribution upon starting the parallel computation and leaves the distributed data in a specific distribution in the memory of the physical processors. Although the data distribution can be hard-coded in the library routine, the information can be used for data redistribution in the later phases.

Granularity - The amount of computation by a process between two communication phases is known as the *Granularity*. The granularity of a library routine must not be fixed at library routine implementation time since, depending on the problem instance size and the physical system size, the fixed grain size may have adverse effect on the performance of the program. Therefore, the granularity must also be determined by the library routine once the problem instance size and the physical system size are known. Runtime grain size adjustment has been

shown to provide larger range of scalability for many algorithms. Higher scalability is desirable for parallel libraries since the routines are more likely to deliver desirable performance when the problem instance size and system size are determined at runtime. The majority of parallel algorithms behave poorly for small problem instance sizes. It is, therefore, necessary for the parallel library routine to identify such cases and possibly execute these using fewer processors or even sequentially. Considering the cost of communication, this seems to be a reasonable solution for small problem instance sizes. Our interest is in extending the range of scalability on large problem instance sizes.

Data redistribution - In a program with two or more parallel library calls, it is beneficial to keep the distributed data of one phase in the processors' local memories to be reshuffled for a subsequent phase. Data redistribution across the parallel phases of a program may enhance the performance of the program by avoiding unnecessary accumulation and distribution of data. Each library routine considered in isolation must distribute the initial data and accumulate the final results. With data redistribution in mind, the library routine implementor must set up such distribution and accumulation routines as part of the library routine. The distribution and accumulation routines are inserted by the compiler based on the requirement of the caller program. If the runtime system recognizes potential redistribution, it executes necessary code to perform reshuffling of the data between two parallel library calls. The library routine writer must design the routines bearing in mind the potential redistribution between parallel phases.

Portability - Effortless porting of the parallel library and the user programs from one system to another is a desirable property. If the library system relies on commonly used runtime libraries and storage schemes, this process is straightforward. However, using special programming constructs, runtime libraries, or communication libraries not commonly available will make the porting problematic.

Coherency - The parallel library calls may be nested within various programming constructs or may be called in other functions. The conditions and loop bounds of these programming constructs may not be known statically. Some of the values may be input by the user. The SPMD code images loaded onto the nodes of the physical system must stay coherent so that all the physical processors can potentially participate in every parallel library call even though some nodes may not be mapped any logical processors to emulate. Input and output statements must be executed by the processor which has I/O capability. Some of these values are required by the other nodes so that the nodes follow the same execution path as the host.

The design of parallel libraries becomes even more complex since the factors mentioned above are intertwined. These factors create several new dimensions which are not pertinent to the sequential libraries. Therefore, parallel libraries require a more elaborate design. Providing a level of encapsulation equivalent to the sequential libraries leaves many of the design issues to be considered by the library routine designer.

#### 1.2 Current Status

Two commonly known parallel libraries are ScaLAPACK [12] and CMSSL [42]. The routines in both these libraries have been designed to be called either from message passing programs or data parallel programs such as the ones written in HPF (High Performance Fortran) [27]. Existing compilers for HPF convert the user's HPF program to the message passing form [6]. In this section we will highlight the distinct features of these libraries. We consider these libraries in their handling of the parallel library design issues discussed in the previous section. Since the aforementioned parallel libraries rely on the user's HPF program to specify the logical system size and the data distribution prior to the call, we evaluate these libraries in the context of HPF.

Performance is largely determined by the granularity of the computation, the mapping of the data to the logical processors, and the mapping of the computation onto the physical processors. ScaLAPACK and CMSSL libraries perform the parallel computation using the granularity and the data mapping specified by the user's HPF program. Data distribution is explicit in the program and obtaining good performance would require several trial and error runs which vary the granularity and the mapping of the data onto the logical processors.

The mapping of the logical processors to the physical processors is considered a compiler dependent issue in HPF and the current parallel libraries. The programmer does not have the freedom to specify a mapping which suits the parallel program. The HPF language does not support directives which relay the communication pattern of the program to the compiler so that proper mapping of the computation to the physical processors can be performed. User defined mapping of the computation to the physical processors is recommended as an extension in the HPF language specification. Current implementations of the HPF language such as [2] do not support this feature.

Unknown problem size, physical system size, and physical system topology have high impacts on the programmer in HPF. The programmer must declare a logical mesh that matches the physical system in size. If an algorithm is based on a logical architecture that is not a mesh, the programmer's task in describing the algorithm in HPF is very difficult. Although the programmer is not aware of the physical system size and topology at programming time, the intrinsic functions can be used to describe the logical architecture size equal to the physical architecture size. Using this feature of HPF and the data distribution directives, the grain size of the computation can be set so that the ScaLAPACK or CMSSL routines use only part of the physical system for the computation. There are two shortcomings in this scheme. The first shortcoming is that determining what fraction of the granted system delivers the best performance is not a trivial task for the programmer. To only use a fraction of the physical system, the granularity of the computation must be statically defined in the specification part of the program. As it was previously described, when the grain size is selected statically, the program may not deliver its best performance when ported to a different platform. The second shortcoming has to do with dynamically allocated data used in the distribution directives. In such case, the actual distribution does not take place until the data is allocated. However, the user is required to specify its distribution and granularity at programming time. If the problem size is not known statically, the programmer has no way of deciding on a suitable granularity and distribution at programming time. Even when the problem instance size is known, partitionable and

reconfigurable systems pose a similar problem since the best grain size of the computation depends on the size of the system at load time.

Although ScaLAPACK and CMSSL have interfaces that resemble the sequential library routines, the user's HPF program must manage the distributed data. Therefore, the sequential call interface with transparent data distribution is not supported in ScaLAPACK and CMSSL. The HPF compiler translates the distribution directives into message passing code that sets up and maintains the information about the distributed data in designated structures. Internally, ScaLAPACK and CMSSL are designed to accept these structures as parameters. Obviously, ScaLAPACK and CMSSL routines cannot be called from sequential programs.

Redistribution of data is supported in HPF. The redistribution is completely transparent to ScaLAPACK and CMSSL routines. The programmer specifies the redistribution of data across the logical architectures using compiler directives. The fact that the HPF compiler must allow any logical architecture declaration that matches in size with the physical architecture, limits the redistribution support in HPF. HPF requires the two parallel phases to have equal virtual architecture sizes. This greatly simplifies the redistribution task. In extended compilers that allow the two phases to have different size logical architectures, the redistribution becomes more complex.

The issue of coherency in implementations of HPF and parallel libraries is handled using proper translation of data-parallel global name space programs to message passing programs. Access to the distributed data is translated into communication operations. If conditional and iterative programming constructs use the distributed data for decision making, the compiler must produce appropriate code so that all logical processors use the most current value of the variable. The owner-compute rule, used in HPF, causes the owner of an element to perform the write to that element of the distributed data. A read operation of the distributed data must be broadcast, by the owner of the data, to all the logical or physical processors (Note that these are the same size in an HPF program).

In the current implementations of the HPF compiler, portability is not a major concern. The compiler translates the data parallel programs to message passing programs based on well known communication libraries. User programs compile and run successfully on different platforms. However, the delivered performance may not be the best on the target system. This is because HPF, and obviously Scalapack and CMSSL, do not perform any adjustment of granularity and mapping across different systems to account for the hardware characteristics of the target system.

#### 1.3 Our Approach

We have based our library routines on the virtual architecture programming model [53, 69, 38, 78]. In this model the program is described on a virtual architecture of desired size and topology, to which is then associated an SPMD code. We have based our parallel libraries on virtual architecture algorithms the following reasons. 1) The virtual topology of these algorithms is generally representative of the communication pattern of these algorithms. This information can assist the compiler or the run time system to perform mapping of the computations to the physical processors. Suitable mapping of the regular communication can reduce the communication overhead of the program.

2) Virtual architecture parallel algorithms are easy to implement since the programmer can describe the algorithms on the virtual architecture matching that of the algorithm and let the compile time or the runtime system perform the necessary translation to account for the mapping of the computation and handle the communication among the virtual processors. 3) The size of the virtual topology of an algorithm is related to the problem instance size. This property can be used to deduce the size of the virtual architecture at run time once the problem instance size is known. 4) These algorithms can be easily described in block form by reducing the size of the virtual architecture and recoding the computation performed by each virtual processor. This property can be used to implement the algorithms in coarse grains and reduce the communication overhead.

We have extended our application domain by several design decisions. A large number of virtual topologies have been accounted for in our library design, and extensions to handle new topologies can be added with very minimal effort through changes in the mapping library. The communication library provides collective communication operations. Consideration of both partitionable and reconfigurable systems in our design has further extended our application domain.

Like other programming models, there are compile time and runtime concerns to deal with in the virtual architecture programming model. The mismatch between the virtual architecture size and the physical system size (which is usually not known at compile time) dictates the use of delayed many-to-one mapping. The quality of the mapping, on the other hand, affects the communication cost of the program. A collection of rich mapping functions [58, 57, 5] across regular topologies ensures that the communicating nodes are placed as close as possible in the physical system. This strategic mapping reduces communication cost of the program in many currently used packet switching systems [79, 15, 16, 26, 50] by reducing the distance between the communicating nodes, hence lower latency and link contention. On other systems that use wormhole routing, poor mapping degrades the performance due to contention [71, 17, 59, 18, 3, 76, 61].

Following the design and the implementation of the virtual architecture programming paradigm, we decided to implement these parallel routines in a precompiled form, parameterized by the virtual architecture size. Although this task may not seem difficult at first, assuring efficiency of these routines and low overhead are rather challenging problems. A large problem instance size described at fine grain may run poorly on a small physical system due to the abundance of small messages. This granularity problem is then overcome by our contraction technique which ensures efficient execution of these routines by runtime granularity adjustment.

Our goal in this research is to offer a new design of precompiled virtual architecture routines and parallel libraries of scientific numerical applications for multicomputers. The novel features of this design are performance improvement through dynamic grain adjustment and delayed mapping of the virtual processors, automatic data distribution, and the initial and final data layout maintenance for redistribution. The representation of the parallel library routines, in this thesis, is appropriate for parallel numerical and scientific applications that can be described in block matrix form. Sequential programs may call these parallel library routines in different language constructs and benefit from efficient execution and automatic data redistribution between phases. Contrary to the currently used techniques, our parallel library routines, which are in parameterized contracted form, support

coarse grain communication as well as coarse grain data redistribution between two consecutive phases. The coarse grains reduce not only the initial data distribution communication cost but also the communication overhead of the parallel library routine in the course of its execution.

Our design meets the ease of use criteria by providing a sequential call interface to the virtual architecture parallel library routines. This is achieved by encapsulating the virtual architecture library components in the library and completely transparent to the caller. From the viewpoint of the library routine implementor, our library design offers a set of guidelines to follow in setting up a new virtual architecture parallel library routine. Virtual architecture parallel routines are independent of physical architecture and are easy to implement. Our centralized mapping library and our virtual communication library further facilitate implementation of these library routines in the message passing model. Our design meets the performance criteria through several design choices. The first one of these is the selection of virtual architecture parallel algorithms as the basis for these libraries. The communication pattern of these algorithms is often regular and matches their virtual topologies. This information can be used by the runtime system to perform systematic mapping of the computation to the physical processors. The centralized mapping library of optimal mapping functions is used to map the virtual processors to the physical processors. The mapping is delayed to runtime since the virtual architecture size and the topology of a parallel library routine are not known at library routine design time. Runtime grain adjustment is another scheme offered in our design which reduces the communication overhead of the library routines. Our design allows runtime grain adjustment based on the problem instance size, physical system size, and physical system attributes. This is suitable for partitionable and reconfigurable systems where the allocated partition is not known before hand. Once a partition is allocated, for each parallel library call, the objective is to minimize its execution time even by limiting parallelism and using only a subset of the physical processors. We have met the portability criteria in our design by not requiring any special language features. The user program and the SPMD form are both based on the conventional programming language constructs. Our library routines require the use of a threading library and a communication library. The implementation can be easily altered to use any threading or communication library. Our virtual collective communication library is based on our virtual point-to-point communication routines which, in turn, use a low level communication library such as PICL. Finally, our library design utilizes a physical system based on its physical characteristics. Once the library system is ported to a new architecture readjustment of the library parameters with those of the new system allows all routines in the library to perform grain adjustment based on the new system parameters.

Chapter 2 of this thesis gives a motivation of parallel libraries and a detailed presentation of the related work. Chapter 3 describes our parallel library routine design and representation. Chapter 4 discusses data redistribution in multiphase programs. In Chapter 5, we discuss our integrated programming environment implementation details. Finally, we conclude this research in Chapter 6.

### Chapter 2

## Background and Related Work

Matrix and vector algorithms form the core part of many numerical computations. Broad use of these algorithms motivated programmers to develop these routines in the form of precompiled routines or libraries. These library routines increased the programmers' efficiency as well as their confidence in the correctness of the programs. With the introduction of parallel systems and implementation of many programming languages on these systems, the need for new libraries recurred. These new libraries facilitate the programming of parallel systems by encapsulating many of the details in the library routines. Henceforth, numerous researchers have been studying the design of parallel libraries for multicomputers. These libraries have also been customized for integration into programming environments [6, 22] based on languages such as HPF [52, 67], Fortran 90 [1, 20, 68, 63, 81], Fortran D [38], and Vienna Fortran [8, 7].

ScaLAPACK [12, 23, 35, 13, 24, 12, 9, 32] is one of the most commonly known parallel libraries on multicomputers. This library is a distributed-memory version of the LAPACK [23] software for dense, banded, and sparse matrix computations. The design goals of ScaLAPACK are scalability, portability, flexibility, and ease-of-use. In sequential and shared memory versions of this library, performance is enhanced by efficient use of the hierarchical memory through data reuse by avoiding frequent cache reloads. This is achieved by describing the computations using block oriented matrix-matrix operations known as the Level 3 BLAS [11]. In the distributed-memory version of ScaLAPACK, block forms of the algorithms are used to reduce the frequency of communication.

Another distinguished parallel library is the CMSSL [40, 41, 44, 43, 42] of Thinking Machines Corporation. The design goals of CMSSL are performance, scalability, robustness, and portability. Routines to handle data distribution provide data distribution independent functionality in CMSSL. Careful scheduling, data motion, and automatic algorithm selection at runtime are the techniques employed to achieve performance. CMSSL routines can be invoked from languages that support array syntax.

In this chapter we unravel the parallel library specific design issues and the measures taken in the current systems to resolve them. Example programs and performance data are presented, where necessary, to form a basis for comparison with our design in this thesis. The examples are based on the integrated environment of HPF and Scalapack or CMSSL.

#### 2.1 Parallel Libraries

In design of parallel library routines, the transparency on the side of the programmer and a suitable call interface does not come for free. The library designer must encapsulate many details of the parallel computation to achieve this task. The interoperability of the compiled code and the library routine is a critical area in the design of the system. The analogy with sequential programming is the stack model used in the sequential library calls. The caller and the callee must abide by certain conventions to ensure a proper library call and return. In high level programming languages, the compiler must ensure the correct call sequence in the code generation phase.

Performance of a parallel library routine depends on factors such as the problem size, system size and characteristics, and mapping. In order for the library routine to maintain the desirable performance for larger problem sizes, its algorithm and the supporting design must be scalable.

The library routine must be easily *portable* across different platforms. Porting requires recompilation of the library routine using the native compiler and fine tuning certain parameters in the library routine to take advantage of the system characteristics of the target architecture.

#### 2.1.1 ScaLAPACK and CMSSL Parallel Libraries

ScaLAPACK and CMSSL are the most commonly known parallel libraries in the parallel computing community. In this section we will highlight the main features of these two libraries.

The performance goal has been achieved in ScaLAPACK through elimination of overhead due to load imbalance, data movement, and algorithm restructuring for Cholesky, LU, and QR factorization. The authors propose block matrix versions of these algorithms based on meshes of processors. In the analysis of their algorithms they assume a mesh of physical processors (matching that of the logical architecture) is available. The mapping of the logical processors to the physical processors is not addressed in ScaLAPACK and is considered a machine-dependent optimization issue.

The authors claim that range of use of a library package may be identified by how stable the algorithms are over a wide range of input problems and the range of data structures the library supports. For example, dense, packed, and banded matrices each require a different internal data structure. Ease of use is one of the goals of the ScaLAPACK parallel library. The authors state that ease of use is concerned with factors such as portability and the user interface to the library. In ScaLAPACK portability is claimed using the fact that the library is implemented using a standard language such as Fortran. It is assumed that the system to which the ScaLAPACK library is being ported to has the Level 3 BLAS and the BLACS library. The Level 3 BLAS is the sequential version of the matrix numerical routines and BLACS is the communication library. The BLACS library provides point-to-point communication routines as well as communication routines over rows and columns of the logical meshes. The authors further claim that the user interface of ScaLAPACK can be enhanced if many of the implementation details are hidden from the programmer. The interface to ScaLAPACK has been developed for HPF. When calling ScaLAPACK routines from HPF programs, the programmer must specify the data distribution and redistribution.

CMSSL is another parallel library which consists of a collection of numerical routines. The

objectives of CMSSL are scalability across systems and problem sizes, consistency with languages with an array syntax, high performance, robustness, and portability.

CMSSL supports global shared address space as well as node level programming. In the global mode, CMSSL accepts distributed data structures. Internally, the library consists of a set of routines executing on each node and a set of communication functions. CMSSL extracts the data distribution information, selects the best algorithm for both the global and the local computation, and carries out the computation using the local routines and the communication routines. The information about the shape of the arrays and their distribution is passed to the CMSSL routines in array descriptors. Similar to the Scalapack library routines, CMSSL routines perform the computation using the distribution and the granularity defined by the programmer. Mapping of the processes to the processors is not addressed in CMSSL.

Both ScaLAPACK and CMSSL support limited form of virtual architecture programming. These libraries assume the logical processors are arranged in form of meshes. They further assume that these meshes of logical processors are selected to match the physical system. HPF allows definition of logical meshes which match the physical system size using intrinsic functions. However, it does not allow definition of other topologies. The virtual architecture parallel library design allows description of parallel algorithms based on various virtual topologies. Gaining efficiency through granularity adjustment is the job of the programmer. Improving efficiency through mapping cannot be supported by libraries such as ScaLAPACK and CMSSL, since the communication pattern of the algorithm is not relayed to the compiler, where the authors claim mapping should be done.

Both ScaLAPACK and CMSSL are suitable for languages such as HPF where data distribution is defined by the programmer. Our libraries encapsulate data distribution in the library routine and require absolutely no intervention from the programmer. The programmer may use the sequential programming model with calls to parallel numerical library routines based on the design in this thesis.

As it will be described in the thesis, in many cases a parallel library call may deliver better performance if it is run on a part of the available partition. In these cases, the virtual architecture size is smaller than the physical system size. As the future technology reduces communication latency, these calls can take advantage of more physical processors to reduce the execution time of the library routine. Even if the logical architecture definition of HPF is extended to allow definition of any logical mesh of processors, it will still not provide the runtime grain adjustment. Providing such functionality requires the programmer's intervention and it is not a trivial task.

#### 2.1.2 Performance Metrics

In view of the fact that the main purpose in parallel computing is performance, an acceptable design of libraries must adhere to this criteria. Performance is usually measured using speedup.

The sequential execution time of a routine is the time elapsed between the beginning and the end of the execution of the routine on a single processor system. On the other hand, parallel execution time is the time elapsed from the start of the execution of the routine on a multiple processor system until the last processor is done. Speedup of a parallel algorithm is defined as the ratio of the parallel

execution time of a program to the execution time of the best existing sequential program. There may be several algorithms to solve the same problem sequentially. It is, however, reasonable to consider only the fastest sequential algorithm in the computation of speedup. Assuming  $T_{Seq}(n)$  is the runtime for the best existing sequential algorithm for a problem of size n, and  $T_{Par}(n,p)$  is the parallel execution time of the problem of size n on p processors, speedup, S, can be defined as:

$$S(n,p) = \frac{T_{Seq}(n)}{T_{Par}(n,p)}$$

Speedup S gives us an insight as to how well we have utilized the p processors in the computation. Theoretically, speedup greater than the number of processors is unattainable. Gaining such speedup is a contradiction, since it implies that one could emulate the parallel processors to obtain a better sequential execution than the one used for the computation of speedup. In practice, however, speedup greater than the number of processors is sometimes observed. This may occur due to the nature of the sequential algorithm or hardware characteristics. For example, searching a tree for an element may result in superlinear speedup depending on the location of the element in the tree, or the memory limitations of the program, such as the cache size, may significantly degrade the sequential execution time of the program. In the latter example, the parallel version may meet the memory requirements better since each processor holds a smaller data partition. In general, one desires linear speedup regardless of the number of processors used.

The ratio of speedup and the number of processors can be used to determine the fraction of time that the processors are effectively employed to solve the problem. This ratio is known as the efficiency, E. Therefore, efficiency is defined as:

$$E(n,p) = \frac{1}{p} \frac{T_{Seq}(n)}{T_{Par}(n,p)} \tag{1}$$

where n and p are as previously defined. The value of efficiency varies between 0 and 1. Speedup of p results in an efficiency of 1.

In scientific computations the sequential execution time is usually proportional to the floating point operation count. Therefore, the performance, G in operations per second, can be defined as:

$$G(n,p) = \frac{p}{t_{calc}} E(n,p) \tag{2}$$

where  $t_{calc}$  is the time for a floating point operation. Scalability is measured using the rate at which the problem size must grow in order to maintain a constant efficiency when the system size grows. An algorithm is highly scalable if the efficiency depends on the problem size and number of processors only through their ratio. In other words, in such algorithms if the problem size and the system size are increased at the same rate, efficiency remains constant. Other definitions of scalability will be shortly discussed.

Speedup and efficiency are two measures that give us an insight on how well we have utilized the parallel system. Based on this definition, on a single processor both speedup and efficiency are one, however as the number of processors increases, a diminishing return is observed. In other words, the speedup will be lower than the number of processors, and therefore the efficiency drops below one. To increase the speedup and efficiency, the problem size must be increased.

The term scalability has been widely used to express the system behavior when changes to the problem size or system size occur. Scalability has significant importance in parallel computing, because it provides information as to what algorithm is the most suitable for a specific architecture and allows one to predict the behavior of algorithms on specific machines when very large problems are used. This information is of high importance in design of parallel libraries where the problem instance size and the physical system size are only known at runtime. The information can be used by the library routine to make decisions on what algorithm would provide the fastest execution time<sup>1</sup>.

In [31] scalability is defined using isoefficiency metric. Using this metric, an algorithm is analyzed for the relationship between the system size and the problem size. Many algorithmic and architectural factors that affect the execution time of the algorithm can be captured in a single expression. As it was previously described, in most parallel programs, as the number of processors increases, efficiency drops and as the problem size is increased, efficiency increases. Using isoefficiency function, one can formulate the rate at which the problem size must increase with respect to the system size in order to maintain a constant efficiency. Algorithms that require the problem size to increase at the same rate as the system size to maintain constant efficiency, are said to be highly scalable. On the other hand, algorithms that require the problem size to grow at a faster rate than the system size are said to poorly scale. These algorithms will require memory beyond the capacity of the underlying architecture to deliver constant efficiency.

A parallel algorithm incurs overhead due to communication, blocking receives, link contention, and load balancing. The accumulation of these times in the execution of a parallel program is called the *overhead*. The overhead,  $T_{OH}$ , is a function of the problem size, system size and topology, given a specific mapping of the virtual processors to the physical processors. Considering the overhead, the speedup and efficiency can be restated as:

$$S(n,p) = \frac{T_{Seq}(n)}{\frac{T_{Seq}(n) + T_{OH}(n,p)}{p}}$$

$$E(n,p) = \frac{1}{1 + \frac{T_{OH}(n,p)}{T_{Co}(n)}}$$

(3)

Assuming the number of sequential operations and the time for a single operations are W(n) and  $t_{comp}$  respectively, equation 3 can be restated as:

$$W(n) = \frac{1}{t_{comp}} \left( \frac{E(n,p)}{1 - E(n,p)} \right) T_{OH}(n,p)$$

(4)

For a given algorithm and architecture, one can obtain  $T_{OH}(n, p)$  which, in turn, shows how W must grow with respect to p to maintain a constant efficiency. For scalable algorithms, the lower the rate of increase of W, the more scalable the algorithm is. The ideal case is when W must grow linearly with p. Let's consider the example of matrix multiplication on a torus. For simplicity, assume a physical torus of p processors is used to perform an  $n \times n$  matrix multiplication. The algorithm

<sup>&</sup>lt;sup>1</sup>Routines based on selection of algorithms are known as polyalgorithms.

<sup>&</sup>lt;sup>2</sup>problem size here refers to the number of operations in the sequential program. The author defines the problem size in this form to have a uniform meaning of problem size.

is described in chapter 3. The number of operations required by the best sequential algorithm <sup>3</sup> is  $n^3$ . In the parallel algorithm, during each iteration  $\left(\frac{n}{\sqrt{p}}\right)^3$  operations are performed by each processor to compute the new values for the resulting submatrix, followed by two communication operations to send the operand submatrices to the neighbors. Therefore, during each iteration, the total number of operations performed by all the p processors is  $\left(\left(\frac{n}{\sqrt{p}}\right)^3 + 2\right)p$ . Over  $\sqrt{p}$  iterations, a total of  $n^3 + 2p^{3/2}$  operations are performed, out of which  $n^3$  operations are useful work. The overhead is, therefore,  $\theta(p^{3/2})$ . The number of operations by the sequential algorithm can then be stated as  $W = 2Kp^{3/2}$ , where K is  $\frac{1}{t_{comp}} \left( \frac{E(n,p)}{1-E(n,p)} \right)$  in equation 4. If the number of processors is increased from p to p', where both  $\sqrt{p}$  and  $\sqrt{p'}$  divide n, then W must increase by a factor of  $(p'/p)^{3/2}$  to maintain the same efficiency. Another way to view this is that increasing the number of processors by a factor of p'/p requires the number of operations, W, to be increased by a factor of  $(p'/p)^{3/2}$  to increase the speedup by a factor of p'/p. An increase of  $(p'/p)^{3/2}$  in W implies an increase of  $(p'/p)^{1/2}$  in n. For instance, increasing the number of processors from 16 to 64 mandates doubling n to maintain a constant efficiency. This results in an increase of a factor of 8 in the number of operations, W. Algorithms that require an increase of W less than the rate of change in p to maintain a constant efficiency, will not sustain the efficiency as p increases beyond certain limits, because eventually the number of processors supersedes the number of operations. Therefore, some processors will be idle, and drop in efficiency is not escapable. Therefore,  $\theta(p)$  is the lower bound on the isoefficiency function. This lower bound is imposed by the degree of parallelism of the underlying algorithm. For example, in the matrix multiplication algorithm, the total amount of computation is  $O(n^3)$ , however, each iteration uses values from the previous iteration of the same processor. In other words, the n intermediate values of each processor have to be computed one after another. Thus, at most  $\theta(n^2)$  processors can be busy at a time. For this problem the degree of parallelism is  $\theta(W^{2/3})$ . So, given p processors, W must be at least  $\theta(p^{3/2})$  in order to use all the processors. This is the lower bound on the isoefficiency function. The optimal value for isoefficiency function due to degree of parallelism is  $\theta(p)$ , and it occurs when the algorithm's degree of parallelism is  $\theta(W)$ . If the algorithm's degree of parallelism is less than  $\theta(W)$ , then the isoefficiency function due to parallelism is greater than  $\theta(p)$ . In this case, the accumulative isoefficiency function will be the maximum of isoefficiency due to parallelism or communication. For our matrix multiplication example, the isoefficiency function due to degree of parallelism and communication is  $\theta(p^{3/2})$ . Algorithms that have an isoefficiency of  $\theta(p)$  are ideally scalable.

In [75] and [73], Sun and Rover propose the *isospeed* metric of scalability. Their scalability analysis has been applied to several problems, and further supported by experimental results on the nCube 2 and the MasPar MP-1. They claim that isospeed scalability metric provides a quantitative measure of performance that other metrics fail to provide. The authors further claim that the *fixed-size speedup*, *fixed-time speedup*, and *memory-bound speedup* [74] are all based on the conventional definition of speedup which is deficient. The isoefficiency metric [31] is more advanced than these models, however, it is still implicitly tied to speedup.

<sup>&</sup>lt;sup>3</sup> Although there are other algorithms for matrix multiplication with lower time complexities, these algorithms tend to have very large constants. Therefore, we use the conventional sequential matrix multiplication for the computation of speedup.

Sun and Rover address the issue of how the system size affects performance and what the costs are to maintain the performance. They believe that the metric should be quantitative and reflect the actual goals of parallel computing. Scalability must be a function of the algorithm and the machine. Both algorithm and the machine introduce parallel overhead. Fast execution time or speed is the major objective in parallel computing. Speed is defined as the amount of work divided by time. The work is usually quantified by the number of floating point operations. Average speed is the achieved speed of a system divided by the number of processors. Scalability is defined for an algorithm-machine combination as its ability to maintain a constant average speed when system size increases. The cost of maintaining this average speed is an increase in the problem size. This increase is a quantitative measure of scalability. If W is the amount of work for an algorithm when p processors are used, and W' is the amount of work for p' > p processors to maintain a constant average speed. The scalability from p to p' is defined as:

$$\psi(p,p') = \frac{p'W}{pW'} \tag{5}$$

In the ideal case,  $W' = \frac{p'W}{p}$ , when  $\psi(p, p') = 1$ . This occurs when the algorithm does not require any communication and the work is evenly divided among the processor. Generally,  $W' > \frac{p'W}{p}$  and  $\psi(p, p') < 1$ . In order to define a unique scalability for an algorithm and machine pair, the authors define the initial speed as the maximum speed reached by the single processor execution of the algorithm on the machine as the problem size increases toward infinity. The scalability is then defined as:

$$\psi(1, p') = \frac{T_1}{T_{p'}} = \frac{\text{Sequential execution time with problem size } W}{\text{Parallel execution time with problem size } W' \text{ and } p' \text{ processors}}$$

(6)

This formula is based on constant speed metric of scalability. The primary difference with the conventional scalability based on speedup is that this metric is not based on the fixed problem size model.

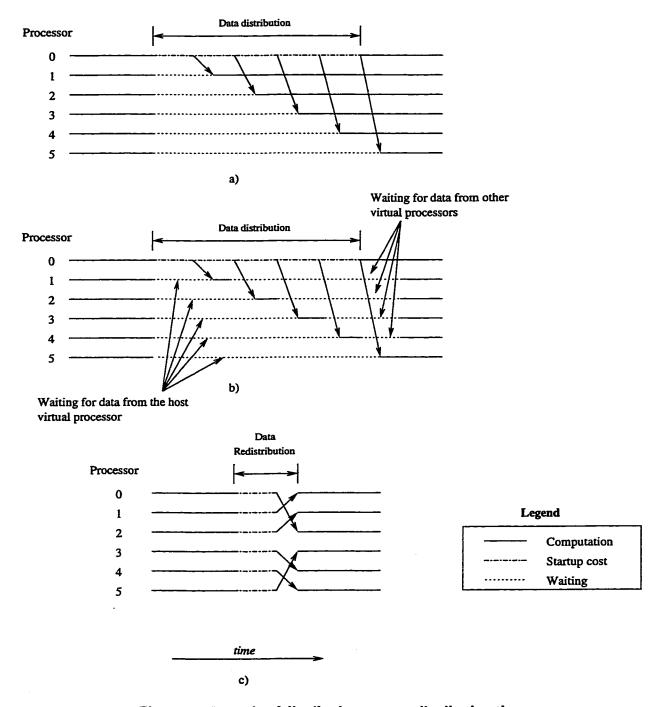

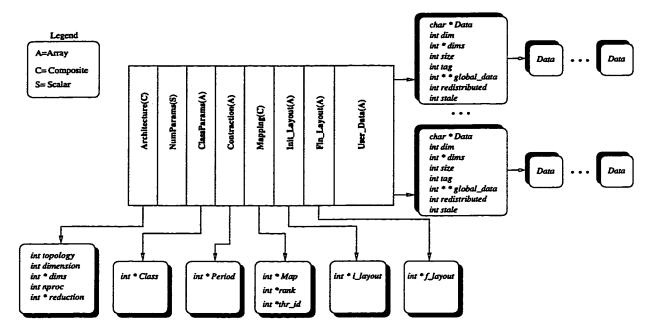

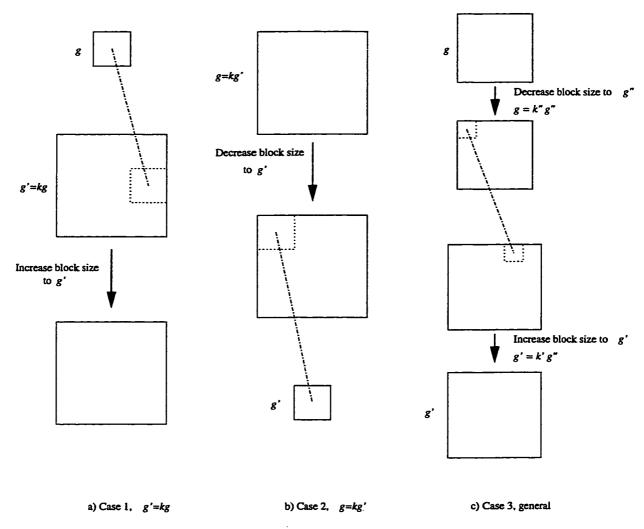

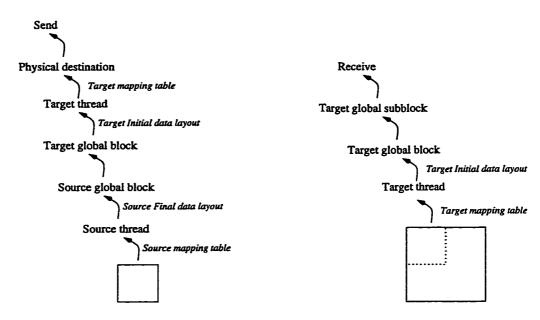

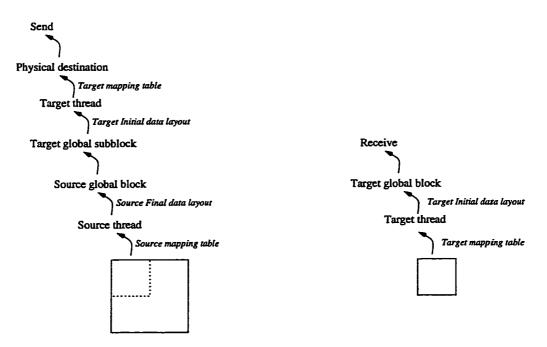

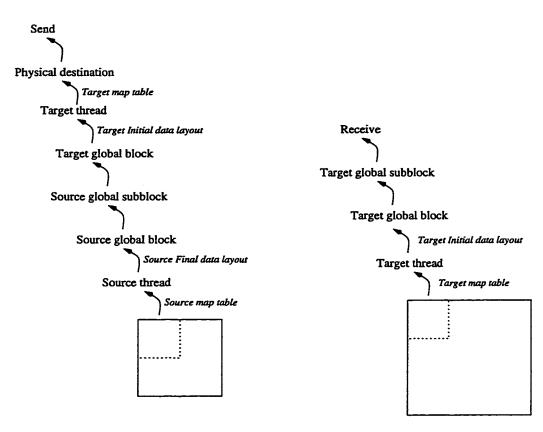

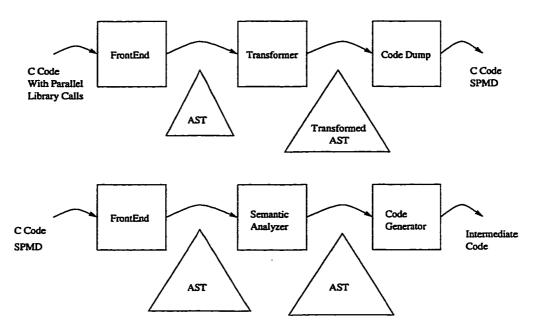

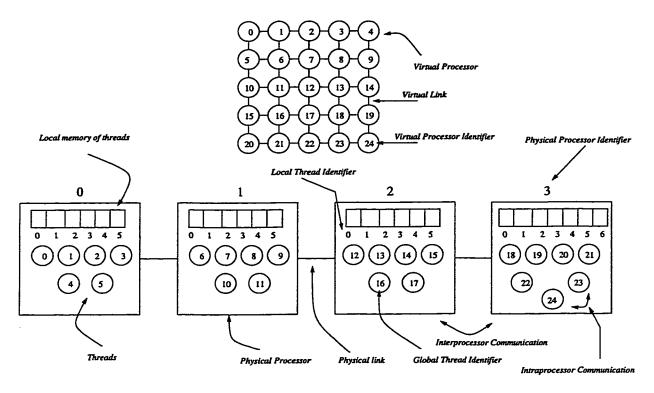

Based on the commonly known definition of scalability, an algorithm is considered highly scalable if it can maintain constant efficiency as the system size and problem size linearly increase. This definition of scalability, however, does not capture the execution time of the parallel algorithm. Based on this definition, if an algorithm maintains a low efficiency when the system size and the problem size vary as stated above, the algorithm is considered highly scalable. Obviously, such algorithms are not desirable for library implementation. If a single algorithm is to be used for library implementation, it is important that the algorithm maintains a constant high efficiency over a wide range of problem sizes. Once the algorithm is selected, the major objective in its design will be to minimize its parallel execution time even for range of problem sizes that do not deliver desirable efficiency. On the other hand, if multiple algorithms (also known as polyalgorithms) are to be used for a library routine implementation, range of scalability (at high efficiency) of the algorithms can be examined. Suitable algorithms can then be selected to cover a wider range of system and problem sizes. Our parallel library design provides support for the use of algorithms based on runtime grain adjustment. ScaLAPACK and CMSSL have shown that algorithms based on block partitioned matrices have a wider range of scalability and can maintain a higher efficiency than the ones based on fine grain.