# Architecture and Circuit Techniques for a 2 GHz Advanced High-Speed Bus SoC Interconnect Infrastructure

Alexandre Landry

A thesis

in

The Department

of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements for the degree of Master of Applied Science (Electrical Engineering) at Concordia University Montréal, Québec, Canada

April 2005

© Alexandre Landry, 2005

Library and Archives Canada

Branch

Published Heritage Dia

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-494-04379-2 Our file Notre référence ISBN: 0-494-04379-2

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

#### **ABSTRACT**

#### Architecture and Circuit Techniques for a 2 GHz

#### Advanced High-Speed Bus SoC Interconnect Infrastructure

By: Alexandre Landry

A key issue with high performance SoC platforms is how to interconnect their modules to effectively transfer large amounts of data in real-time. Today's most practical communication infrastructures are bus-based due to the small number of processing elements residing on a silicon die. Since the bandwidth of a shared bus goes down with the number of bus masters, hierarchical structures are used to parallelize transfers and to obtain a higher throughput. Hence, a novel shared memory SoC communication infrastructure based on the Advanced High-Speed Bus (AHB) is defined in this thesis.

The objective of this dissertation is to explore various avenues to design a bus operating with a clock in excess of 2 GHz when targeting a 0.18 µm CMOS process. As a first iteration, the fastest circuit techniques are reviewed so as to traverse the learning curve that a designer must experiment with very high-speed designs. To enhance the understanding of high-speed circuit styles, the main cores of an AHB are implemented from a novel, and aggressive, true-single-phase-clocking (TSPC) circuit style. The 2 GHz AHB arbiter has been laid out to prove the performance of the circuit techniques explored with the full-custom SoC infrastructure. In addition, an innovative 2 GHz pipelined memory has been created to respond to the hard IP requirements.

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to Professor Yvon Savaria for his excellent guidance during my graduate career. He is surely the giant upon whose shoulders I stand. In the same line of thought, I would like to acknowledge my sincere recognition to Professor Mohamed Nekili for his accurate supervision of this research and his precious help to overcome unusual difficulties. I would like to thank all the members of the Very Large Scale Integration (VLSI) group at Concordia University and give a special thanks to Tadeusz Obuchowicz who took care of difficult CAD tool issues. I gratefully acknowledge the support of the Microelectronics Research Group (GRM) from École Polytechnique of Montréal for their valuable collaboration, particularly Normand Bélanger who reviewed this thesis.

I also express my deepest gratitude to my beloved family and my only sister, Marie-Ève, who have always supported me in all decisions. Finally, I would like to thank my many friends for their understanding and endless support.

# TABLE OF CONTENT

| LIST OF FIGURES                                        | VIII |

|--------------------------------------------------------|------|

| LIST OF TABLES                                         | X    |

| LIST OF ACRONYMS                                       | XI   |

| 1 INTRODUCTION                                         | 1    |

| 1.1 BACKGROUND                                         | 1    |

| 1.2 OVERVIEW OF THESIS                                 | 2    |

| 1.3 SUMMARY OF THESIS                                  | 4    |

| 2 STATE-OF-THE-ART                                     | 5    |

| 2.1 DESIGN TOOLS LIST                                  | 6    |

| 2.1.1 AMS Environment                                  | 6    |

| 2.1.2 Affirma Analog Artist and SpectreSVerilog        |      |

| 2.1.3 VerilogXL                                        | 8    |

| 2.1.4 Virage memory compiler                           | 8    |

| 2.2 STANDARD ON-CHIP BUS OVERVIEW                      | 8    |

| 2.2.1 Advanced Microcontroller Bus Architecture (AMBA) | 9    |

| 2.2.2 CoreConnect                                      | 11   |

| 2.2.3 STBus                                            | 12   |

| 2.3 STANDARD INTERFACES OVERVIEW                       | 13   |

| 2.3.1 Advanced eXtensible Interface                    |      |

| 2.3.2 Open Core Protocol                               | 14   |

| 2.4 HIGH-SPEED CIRCUIT STYLES OVERVIEW                 | 15   |

|   | 2.4.1   | NORA Dynamic Logic Style                           | 16 |

|---|---------|----------------------------------------------------|----|

|   | 2.4.2   | True-Single-Phase-Clocking Style                   | 18 |

|   | 2.4.3   | MOS-Current-Mode-Logic                             | 20 |

|   | 2.5 Sui | MMARY                                              | 21 |

| 3 | FULL-   | CUSTOM CIRCUIT METHODOLOGY AND TECHNIQUES          | 22 |

|   | 3.1 Es  | TABLISHING A DESIGN METHODOLOGY                    | 23 |

|   | 3.1.1   | Architectural Planning                             | 24 |

|   | 3.1.2   | Protocol Design Phase                              | 25 |

|   | 3.1.3   | Logic Design                                       | 25 |

|   | 3.1.4   | Technology Mapping                                 | 26 |

|   | 3.1.5   | Physical design                                    | 26 |

|   | 3.2 SIM | ULATION PROCESS                                    | 27 |

|   | 3.3 CIR | CUIT TECHNIQUES                                    | 29 |

|   | 3.3.1   | Selecting a TSPC Style                             | 30 |

|   | 3.3.2   | TSPC Device Sizing                                 | 32 |

|   | 3.3.3   | Logic style and Design Rules                       | 34 |

|   | 3.4 SUN | /MARY                                              | 35 |

| 4 | AHB IN  | FRASTRUCTURE ARCHITECTURE                          | 36 |

|   | 4.1 AH  | B Interconnect Megacell Overview                   | 37 |

|   | 4.1.1   | Clock Domains                                      | 37 |

|   | 4.1.2   | Architectural Overview of the Communication Fabric | 39 |

|   | 4.1.3   | Specialized AHB signals                            | 42 |

|   | 4.2 INT | ERLEAVED MEMORY                                    | 43 |

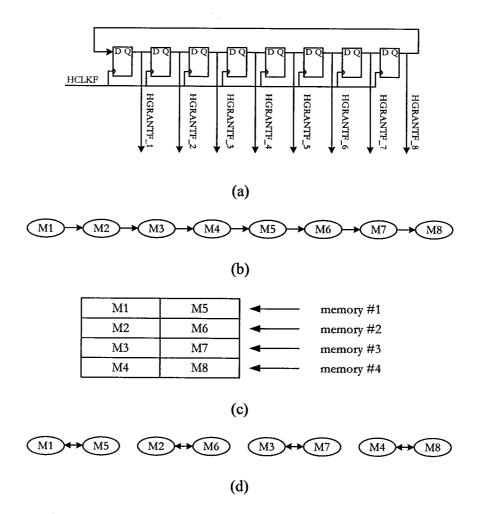

|   | 4.3 VE  | RY LONG INSTRUCTION WORD ARBITER                   | 49 |

|   | 4.3.1   | Traffic Analysis                                   | 53 |

|   | 4.3.2   | Timing Model                                       | 59 |

|   | 4.4 14. | STED RAIDCES                                       |    |

|   | <b>4</b> .4 | 4.1         | READ Bridge                          | 62  |

|---|-------------|-------------|--------------------------------------|-----|

|   | 4.4         | 4.2         | WRITE Bridge                         | 65  |

|   | 4.5         | SUM         | 1MARY                                | 67  |

| 5 | CIR         | RCU:        | ITS IMPLEMENTATION                   | 68  |

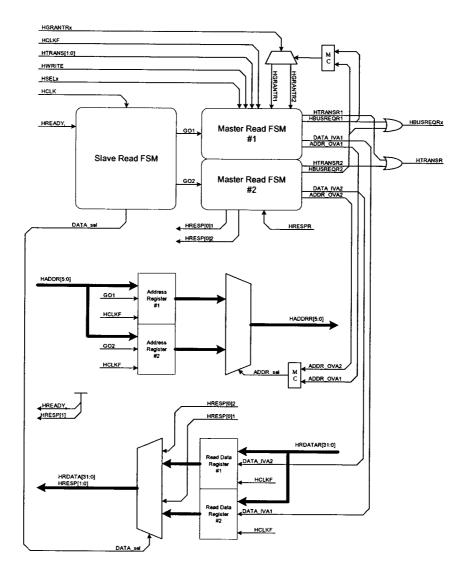

|   | 5.1         | SPE         | CIALIZED-TO-STANDARD AHB BRIDGE      | 69  |

|   | 5.1         | 1.1         | Master Finite State Machine          | 69  |

|   | 5.1         | 1.2         | Slave Finite State Machine           | 75  |

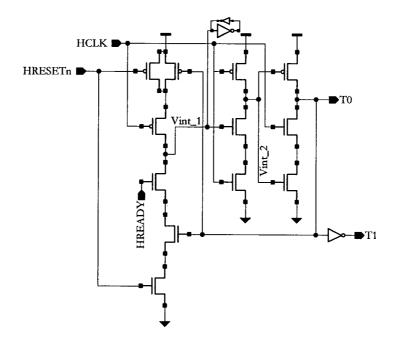

|   | 5.1         | 1.3         | Synchronizing Register               | 77  |

|   | 5.1         | 1.4         | High-Speed Resource Sharing Arbiters | 78  |

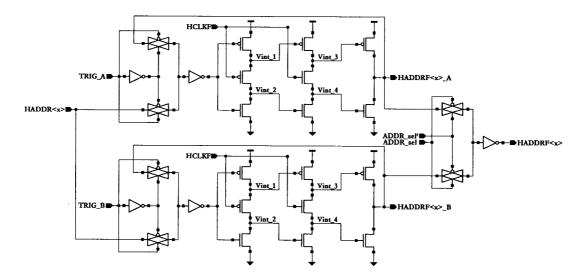

|   | 5.1         | 1.5         | Address and Data Datapath            | 81  |

|   | 5.1         | 1.6         | Implementation Results               | 82  |

|   | 5.2         | Ver         | Y-LONG-INSTRUCTION-WORD AHB ARBITER  | 85  |

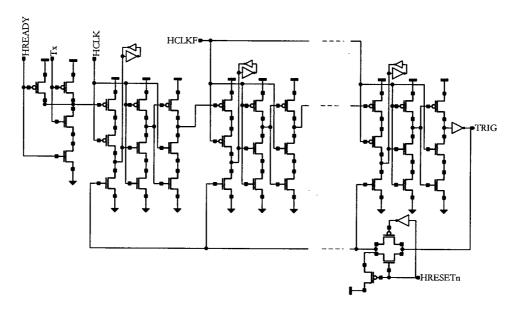

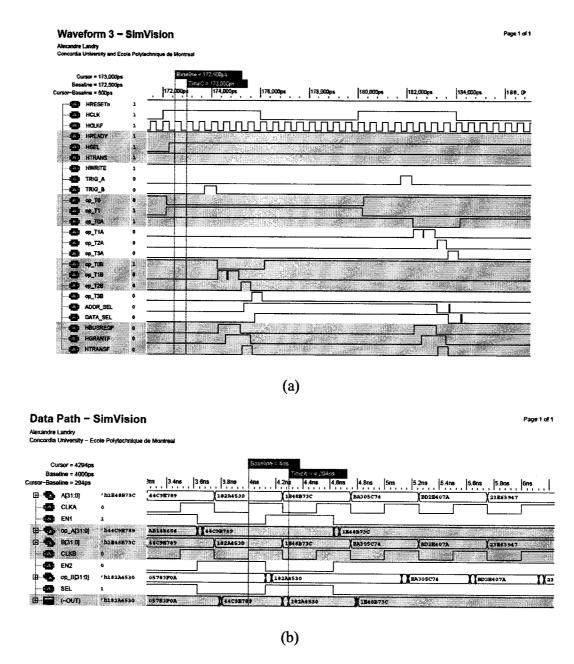

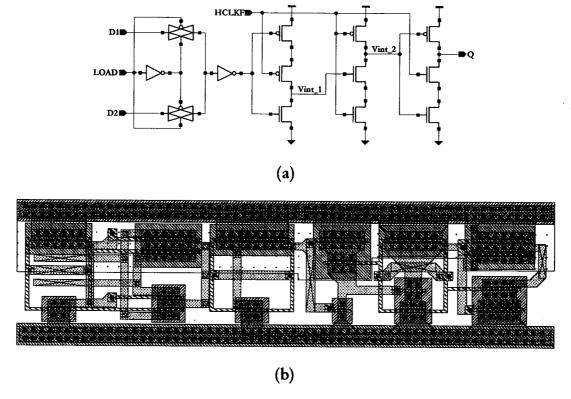

|   | 5.2         | 2.1         | Shift Register                       | 85  |

|   | 5.2         | 2.2         | Decoder                              | 86  |

|   |             |             | Layout and Implementation Results    |     |

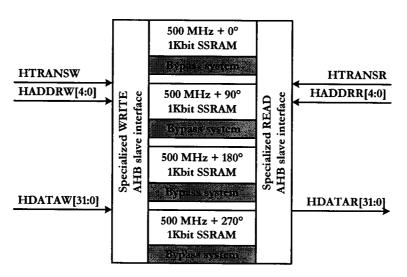

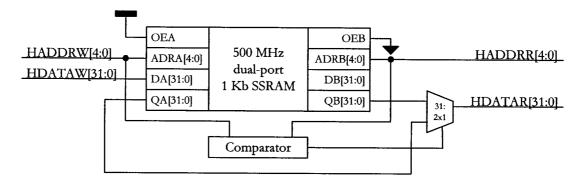

|   | 5.3         | HIG         | H-THROUGHPUT MEMORY AND ITS WRAPPERS | 90  |

|   | 5.3         | 3. <i>1</i> | Memory Wrappers                      | 92  |

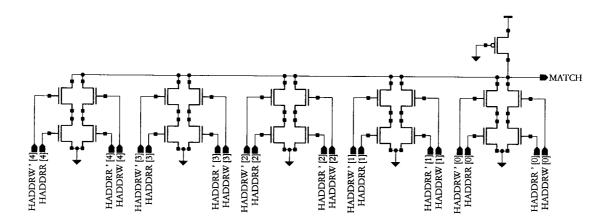

|   | 5.3         | 3.2         | Address Comparator                   | 93  |

|   | 5.4         | Sum         | IMARY                                | 94  |

| 6 | CO          | NCL         | USION AND FUTURE WORK                | 96  |

|   |             |             | URE WORK                             |     |

|   |             |             | CLUSION AND SUMMARY                  |     |

| 7 | I 1C'       | י חי        | F REFERENCES                         | 100 |

|   |             |             |                                      |     |

# **LIST OF FIGURES**

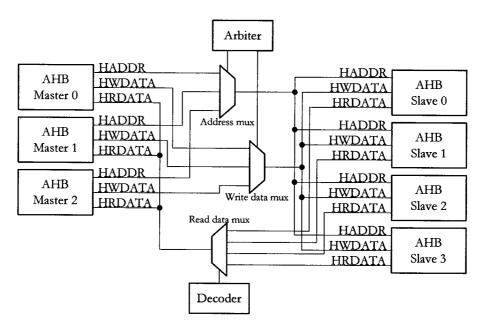

| Figure 2.1. | Multiplexed AMBA AHB interconnections [2].                              | . 10 |

|-------------|-------------------------------------------------------------------------|------|

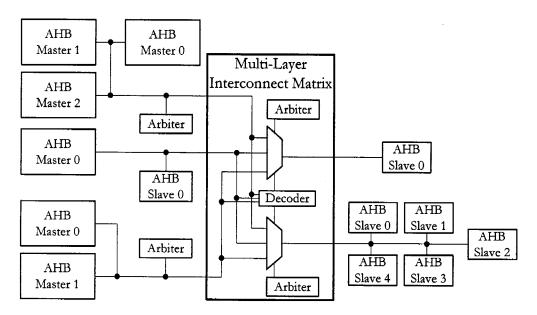

| Figure 2.2. | Complex Multi-layer AHB system example.                                 | . 11 |

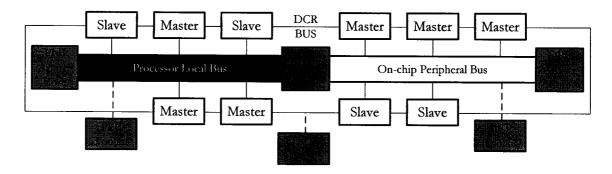

| Figure 2.3. | CoreConnect organizational diagram (reproduced from [19])               | . 12 |

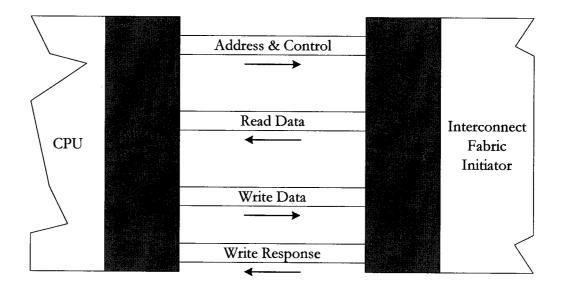

| Figure 2.4. | AXI channel configuration.                                              | . 14 |

| Figure 2.5. | System showing an NoC with OCP instances (reproduced from [26])         | . 15 |

| Figure 2.6. | C <sup>2</sup> MOS dynamic logic                                        | . 17 |

| Figure 2.7. | NORA dynamic logic.                                                     | . 17 |

| Figure 2.8. | True-single-phase-clock latches.                                        | . 19 |

| Figure 2.9. | MCML method.                                                            | . 20 |

| Figure 3.1. | Proposed design flow                                                    | . 24 |

| Figure 3.2. | Test fixture used for full-custom simulation.                           | . 28 |

| Figure 3.3. | Positive edge-triggered latch candidates for the 2 GHz AHB. (a) TSPC-2, | (b)  |

| Split-outpu | t, (c) C <sup>2</sup> MOS                                               | .31  |

| Figure 3.4. | Buffering TSPC stages.                                                  | . 33 |

| Figure 4.1. | Clock domains division.                                                 | .38  |

| Figure 4.2. | Overall structure of the proposed communication infrastructure          | 41   |

| Figure 4.3. | Block diagram of the high-throughput interleaved memory.                | 44   |

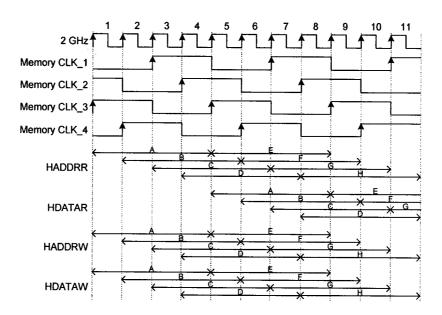

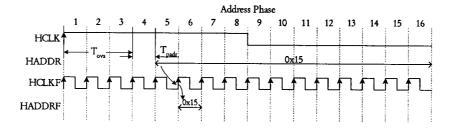

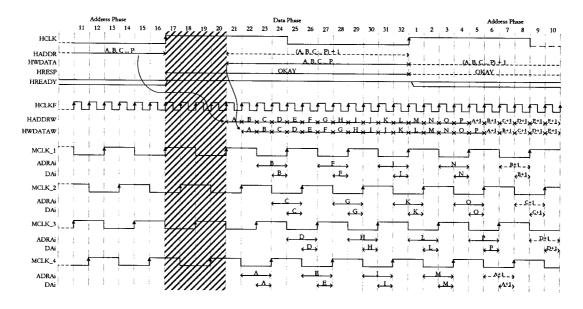

| Figure 4.4. | Interleaved memory timing diagram.                                      | 45   |

| Figure 4.5. | Block diagram of the bypass system.                                     | 48   |

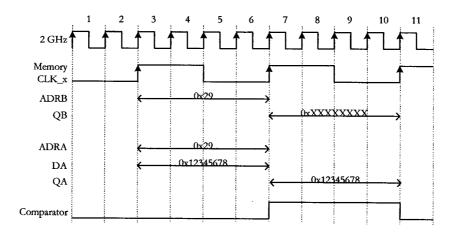

| Figure 4.6. | Timing diagram of a conflict resolution.                                | 49   |

| Figure 4.7. Arbitration with phases: problem definition. (a) Round-Robin arbiter,            | (b) |

|----------------------------------------------------------------------------------------------|-----|

| Target dataflow, (c) Memory map, and (d) Resulting dataflow                                  | 50  |

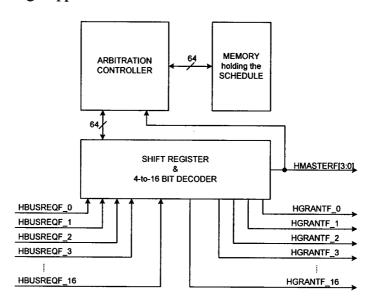

| Figure 4.8. Block diagram of the VLIW micro-programmed arbiter.                              | 53  |

| Figure 4.9. Exclusion zone to steal the address to a processing element                      | 55  |

| Figure 4.10. Exclusion zone to deliver READ data.                                            | 56  |

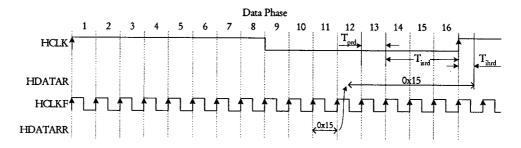

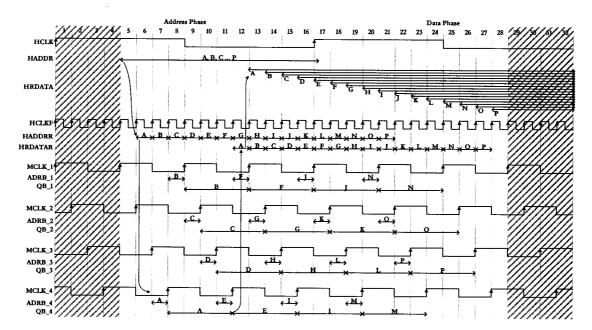

| Figure 4.11. Performing 16 READ cycles with no apparent latency.                             | 57  |

| Figure 4.12. Performing 16 WRITE cycles with no apparent latency.                            | 59  |

| Figure 4.13. Block diagram of the READ master bridge.                                        | 62  |

| Figure 4.14. Detailed READ Master Bridge block diagram.                                      | 64  |

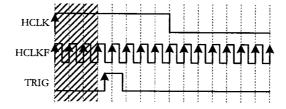

| Figure 4.15. Triggering pulse waveform.                                                      | 66  |

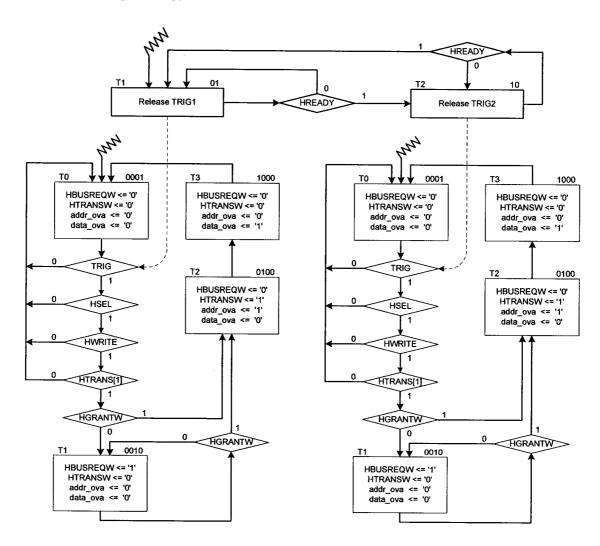

| Figure 5.1. Controller's state diagram.                                                      | 70  |

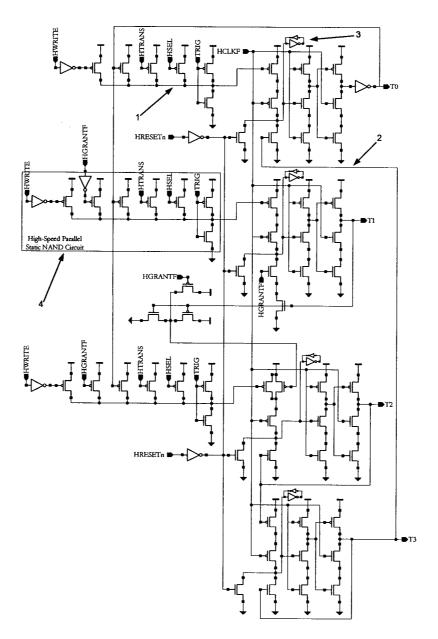

| Figure 5.2. Circuits of the Master Finite State Machine.                                     | 73  |

| Figure 5.3. Circuits of the Slave Finite State Machine.                                      | 77  |

| Figure 5.4. Circuits of the synchronizing register.                                          | 79  |

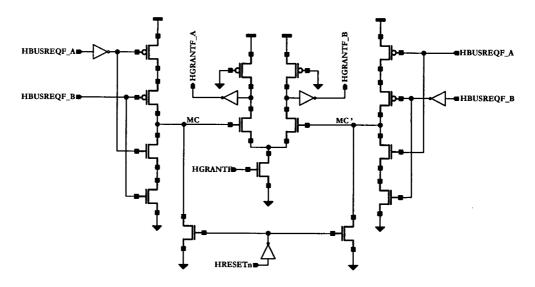

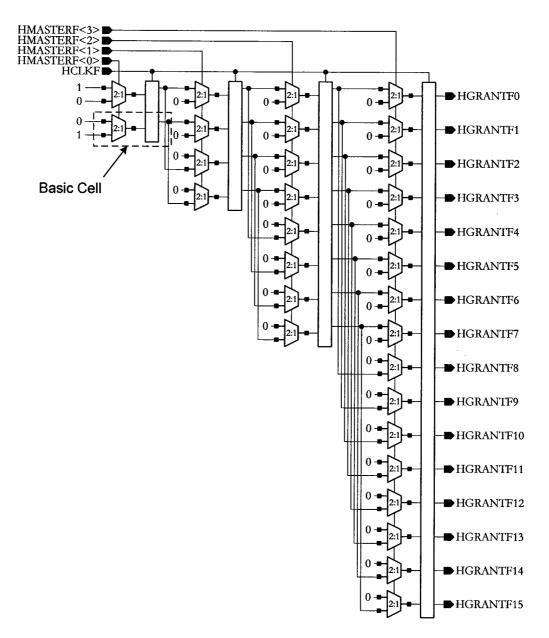

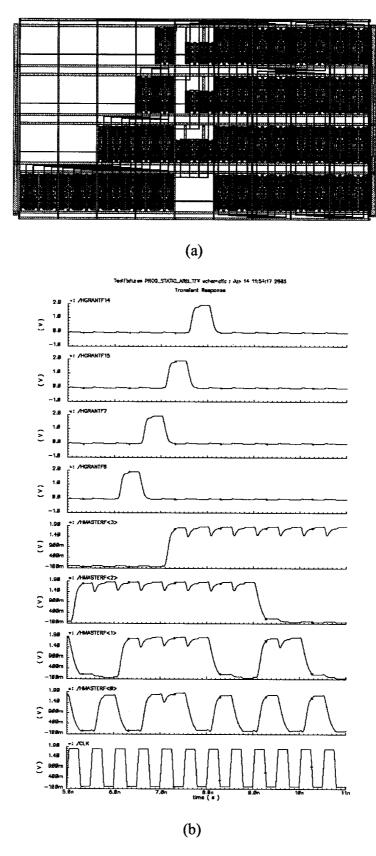

| Figure 5.5. Circuits of HGRANTF arbiter.                                                     | 81  |

| Figure 5.6. Circuit slice of the address datapath.                                           | 83  |

| Figure 5.7. StS WRITE Bridge (a) controller and (b) datapath output waveform                 | 84  |

| Figure 5.8. C <sup>2</sup> MOS latch with 2-to-1 multiplexer cell. (a) Schematic, (b) Layout | 86  |

| Figure 5.9. Structure of the 4-to-16 bit logarithmic decoder.                                | 88  |

| Figure 5.10. (a) Layout of the 4-to-16 bit decoder, (b) Simulation results                   | 91  |

| Figure 5.11. 5-bit XNOR comparator transistor organization.                                  | 94  |

# LIST OF TABLES

| Table 3.1. | Comparison parameters of three TSPC latches      | . 31 |

|------------|--------------------------------------------------|------|

| Table 4.1. | Specialized AMBA AHB signals                     | . 43 |

| Table 4.2. | Proper scheduling for a continuous dataflow      | . 51 |

| Table 4.3. | Timing parameters definition.                    | . 60 |

| Table 4.4. | Tracing the state of the standard AHB.           | . 63 |

| Table 4.5. | Specialized READ AHB pipeline structure.         | . 64 |

| Table 5.1. | State equations for the WRITE Master FSM.        | .71  |

| Table 5.2. | SFSM state relationship with the standard AHB.   | .76  |

| Table 5.3. | Truth table of HGRANTFx arbiter.                 | . 81 |

| Table 5.4. | StS WRITE Bridge Circuits and Simulation Summary | 84   |

#### LIST OF ACRONYMS

ADC:

Analog-to-digital converter.

AHB:

Advanced High-Speed Bus.

AMBA:

Advanced Microcontroller Bus Architecture.

AOI:

AND-OR-INVERTER standard gate.

APB:

Advanced Peripheral Bus.

ASB:

Advanced System Bus.

ASIC:

Application specific integrated circuit.

AXI:

Advanced eXtensible Interface.

C<sup>2</sup>MOS:

Complementary CMOS.

CAD:

Computer aided design.

CIW:

Command Interpreter Window.

CMC:

Canadian Microelectronics Corporation.

CMOS:

Complementary metal-oxide semiconductor.

CTMC:

Custom-Touch-Memory-Compiler.

DAC:

Digital-to-analog converter.

DCR:

Device Control Register.

DCVSL:

Differential cascade voltage switch logic.

DMA:

Direct memory access.

DSM:

Deep submicron.

DSP:

Digital signal processing.

DUT:

Device under test.

FIFO:

First-in-first-out register.

FSM:

Finite state machine.

GALS:

Globally-asynchronous-locally-synchronous.

GRM:

Microelectronics Research Group.

HDL:

Hardware description language.

HVL:

Hardware verification language.

IC:

Integrated circuit.

IP:

Intellectual property.

LHS:

Left-hand side.

MCML:

MOS-current-mode-logic.

MESI:

Modified-Exclusive-Shared-Invalid invalidate protocol.

MFSM:

Master finite state machine.

NMOS:

n-type MOS field-effect transistor.

NoC:

Network-on-a-chip.

NORA:

No-race.

OAI:

OR-AND-INVERTER standard gate.

OCP:

Open Core Protocol.

OPB:

On-chip Peripheral Bus.

PCB:

Printed circuit board.

PDN:

Pull-down network.

PE:

Processing element.

PLB:

Processor Local Bus.

PLL: Phase-lock-loop.

PMOS: p-type MOS filed-effect transistor.

PUN: Pull-up network.

QoS: Quality-of-service.

RC: Resistor-capacitor.

RHS: Right-hand side.

RT: Real-time.

RTL: Register transfer level.

SFSM: Slave finite state machine.

SoC: System-on-a-chip.

SSRAM: Synchronous static random access memory.

StS: Standard-to-Specialized.

tr: Rise time.

tf: Fall time.

TSPC: True-single-phase-clocking.

UDSM: Ultra deep submicron.

VHDL: Very high-speed integrated circuit hardware description language.

VIH: Input high voltage

VIL: Input low voltage.

VLIW: Very long instruction word.

VLSI: Very large scale integration.

VOH: Output high voltage.

VOL: Output low voltage.

#### 1 INTRODUCTION

#### 1.1 Background

Advances in deep submicron (DSM) technology allow integrating so many transistors on a single silicon die that complete systems can be merged into a single chip. Typically, systems-on-chip (SoC) are conceived from a mixture of custom circuits and preexisting intellectual property (IP) macrocells (sometimes called megacells). Intellectual property macrocells may be designed with two distinct approaches: (1) a soft IP follows a semi-custom flow in which hardware description files are synthesized to obtain the circuits, while (2) a full-custom flow is more appropriate to design a hard IP in which only the masks are available. However, for SoC integration, it is not critical whether we use hard or soft IP megacells. What is really important is to meet the system requirements and reduce time-to-market.

The momentum in the industry hints that SoCs are taking the path that printed circuit boards (PCB) systems took two decades ago. At first, microprocessors were implemented with discrete components over a PCB, and then VLSI improvements allowed packing enough transistors in a chip to merge complete microprocessors on a single chip substrate [1]. In a short time span, electronic systems grew more complex and interconnect standards became most needed to keep up with performance enhancements. Nowadays, PCB interconnect standards span over a large range of applications. SoCs do not escape this movement as their performance is partly set by the

efficiency of the on-chip communication infrastructure used to transfer large amounts of data. To this regard, interconnect standards, tuned for the SoC realm, help achieving high-throughput and reduce design efforts.

Key issues with SoC communication infrastructures are testability, flexibility, and their ability to exchange data at high rates on demand between system modules. For the time being, SoCs are characterized by a small number of processing elements, so a shared memory accessed from a shared bus is a practical SoC interconnect infrastructure to use. To this regard, the Microelectronics Research Group (GRM) of École Polytechnique of Montréal has performed significant work using AMBA standards [2] prior to this Hence, different bus standards have been studied in [3], and a novel research. architecture was invented in [4], [5]. All previous interconnect infrastructures at GRM were implemented with a semi-custom design flow (synthesis followed by placement and This abides by the AMBA specifications since this norm describes routing). synthesizable buses. Yet again, the performance obtained by this design flow is limited by the use of standard libraries, and sparse layouts created by automated placement and routing [6], [7], [8]. Hence, interconnecting high-performance cores with an AMBA bus is a problem that remains unsolved.

#### 1.2 Overview of Thesis

As presented earlier, the design of communication infrastructure's architecture is a critical issue with systems-on-chip. The complete shared memory interconnect fabric proposed in this thesis consists of a hierarchical AMBA Advanced High-Speed Bus (AHB), a group of processing elements and a shared memory acting as a communication buffer. Since the heart of this SoC communication infrastructure operates at a frequency

in excess of 2 GHz, it is imperative to implement the main system cores with full-custom circuits to optimize the speed of the AHB shaping the hard IP.

The purpose of this research is to undergo the learning curve involved with the design and the optimization of high-speed circuit, and the many twists involved with their layout. To enhance the understanding in high-frequency circuit design, a thorough study of dynamic logic is completed so as to isolate the fastest avenues. The work reported in this document spans a wide range of abstraction levels. An implementation as ambitious as the one presented in this dissertation requires a sequence of actions carefully planned to overcome the many obstacles to be encountered in the design process.

To accomplish this research goal, three tasks have been identified:

- 1. Architectural definition: A chain is never stronger than its weakest link. Defining a robust architecture forms the first link of the design chain. Though the architecture of an AHB is defined by its specifications, the AHB hierarchy, the pipeline structure, and the communication protocol of the entire high-speed hard IP must be described in a first step.

- 2. Circuit Decisions: Designing sequential circuits operating above the GHz mark is no easy task. Conventional circuit techniques may not be applicable since their structure limits the maximum frequency. A careful study of high-speed methodologies is required to select appropriate sequential logic style.

- 3. *Circuits Design*: Once a high-performance architecture is defined and a high-speed sequential logic style is selected, circuits design may start. Finite state machines (FSM), registers, combinational logic blocks, and datapaths need to be designed.

#### 1.3 Summary of Thesis

The design of a very high-performance SoC communication infrastructure is a thorough commitment that forces engineers to work over several levels of abstraction. Based on the tasks identified in this chapter, the complete hard IP is described in the next chapters. State-of-the-art computer aided design tools (CAD) utilized in this project, along with the well-established on-chip communication industry standards are presented in Chapter 2. In addition, Chapter 2 surveys circuit styles known to be the fastest with CMOS IC design. The design flow and circuit techniques used with the novel interconnect infrastructure are presented in Chapter 3. Chapter 4 presents the global architecture of the proposed communication fabric. An ambitious arbitration procedure and the high-level description of a pipelined high-throughput shared memory are described in the same chapter. Circuit implementations with their results are described in Chapter 5, and an AHB arbiter layout is presented to prove the accuracy of the investigated methodology. Finally, Chapter 6 concludes this document and presents the many avenues available for improvements as future work.

#### 2 STATE-OF-THE-ART

Systems-on-chip (SoC) design in the forthcoming ultra deep submicron (UDSM) technologies will be dominated by multi-core (multi-processor) platforms in a number of application areas [9]. A key issue to enable this type of platform is to develop a communication-centric interconnect infrastructure to effectively transfer large amounts of data within the SoC. Obviously, such communication-centric fabrics are characterized by a number of tradeoffs, e.g., with regards to latency, parallel programming capability, design effort and circuit complexity. The requirements of the target application set the boundaries for tradeoffs to be considered. For instance, the type and the structure of the communication fabric is a significant factor that directly influences the performance of a network-on-chip (NoC). Outstanding NoCs allow for record-breaking SoC platforms' performance, as far as the SoC cores can keep up. The computer-aided-design (CAD) tools at hand impact the design flow and the overall complexity envisioned for a design. Inadequate design tools often entail excessive time-to-market delays and possibly project failure.

This chapter lists the CAD tools used for the design of the high-performance communication infrastructure. The main tools and their capabilities are documented so as to shorten the learning curve that other designers could experiment when undertaking a project of similar target frequencies with significant design efforts. Then, various NoC standards are surveyed. Abiding to a standard facilitates design integration since they encourage uniform interfaces with specific protocols. Finally, high-performance circuit

styles are discussed since full-custom design requires selecting the best logic style manually.

#### 2.1 Design Tools List

The Canadian Microelectronics Corporation (CMC) distributes tool sets, for many IC design styles, to its member universities across Canada. Hence, all tools utilized in the design of the high-speed communication fabric were obtained from the CMC.

#### 2.1.1 AMS Environment

The AMS flow uses the AMS Environment<sup>tm</sup> and a set of tools tuned to facilitate the development of mixed-signal designs [10]. In essence, the AMS Environment is a feature within Cadence's toolbox that enables mixed-signal and mixed-language designs to be developed by analog and digital designers from the same environment. When large full-custom designs are developed using Cadence tools, means to create and tune transistor circuits are required, along with a solution to create a test fixture with functional testbenches to stimulate the digital "analog-like" circuit. A variety of Cadence tools are necessary within the AMS flow to achieve that:

- 1. Command Interpreter Window (CIW).

- 2. Cadence Hierarchy Editor [11].

- 3. AMS netlister [10].

- 4. AMS compiler [10]

- 5. AMS Design Prep [10]

- 6. AMS elaborator [10]

- 7. AMS simulator [10], using SimVision [12] as waveform viewer.

The AMS Environment presents a familiar interface to both digital designers and analog designers. For instance, analog designers typically work at the transistor level using a graphical editor. On the other hand, digital designers specify circuits using a text editor and they rely on digital synthesis to map the behavioral circuit description into physical circuits. AMS provides means to seamlessly integrate these two types of design entry tools together in the same design flow.

The CIW is the root of the Cadence environment. It is used to invoke different tools, set design options (such as AMS options), and monitor status, warning and error messages issued by Cadence tools. Virtuoso is used to build the target system. Its versatility allows specifying cells at different levels of abstraction: functional, spectre, hspice, schematic, layout, extracted, etc. The Hierarchy Editor is used to complement Virtuoso. It is this editor that recognizes mixed-signal designs within Cadence, and it provides accurate representations of analog/digital interface boundaries used by AMS to automatically insert interface elements. AMS works intimately with the Hierarchy Editor to generate, compile, and simulate Verilog-AMS metlists. Finally, the AMS Simulator is used to run the Verilog-AMS netlist and it displays mixed-signal circuit results using SimVision.

#### 2.1.2 Affirma Analog Artist and SpectreSVerilog

Affirma Analog Artist<sup>tm</sup> is the typical simulator used for analog design simulations within Cadence. It encapsulates a variety of simulators tuned to simulate different types of designs. For instance, Spectre<sup>tm</sup> [13] and Hspice<sup>tm</sup> [15] are both used to simulate flat analog designs. On the other hand, SpectreSVerilog<sup>tm</sup> [13] is a super-set of Spectre as it can simulate mixed-signal circuits. Unfortunately, the waveform viewer

used by Affirma only displays a small number of signals at a time, and it does not support buses. Hence, some workarounds are required to export the waveforms to other waveform viewers.

#### 2.1.3 VerilogXL

VerilogXL<sup>tm</sup> [15] is another tool distributed by Cadence. As its name suggests, it is used to compile, simulate, and synthesize Verilog [16] hardware description language files. Even though, it is tuned for digital designs, it turns out to be a handy tool to elaborate and verify Verilog testbenches to be included later in the AMS test fixtures. Here again, SimVision is used to display simulation results and process them.

#### 2.1.4 Virage memory compiler

Virage offers a specialized memory compiler optimized for various memory structures. Embed-It! Integrator<sup>tm</sup> and Custom-Touch-Memory-Compiler<sup>tm</sup> (CTMC) are used to rapidly create high-performance memories. Synopsys VCS does not recognize memory structures effectively and the results it offers are often disappointing. Unlike Synopsys, CTMC generates high-speed memories on much smaller footprints from a specialized standard cell library. With CTMC, it is possible to generate a memory with its description, and a RTL VHDL and/or Verilog files in less than five minutes.

## 2.2 Standard On-Chip Bus Overview

Since SoC platforms emerged as feasible VLSI circuits, a number of industrial norms appeared to standardize on-chip communication infrastructures. As of today, large SoCs asking for scalable NoCs are almost inexistent for a number of reasons [17]. It makes sense to use smaller types of interconnect fabrics to link cores on the same

substrate with modern SoCs. As the complexity of those systems will eventually scale up, it is expected that the set of available standards will grow so as to offer a variety of solutions tuned for different requirements, similarly to what happened with printed circuit boards (PCB). Hence, this section surveys the main bus standards in the industry.

#### 2.2.1 Advanced Microcontroller Bus Architecture (AMBA)

ARM<sup>Ltd</sup> owns one of the most accepted shared buses for SoCs in industry. The reason for it is simple: ARM owns a significant market share of embedded processors that are commonly sold with a built in AMBA interface. The AMBA Specification 2.0 [2] defines a set of three fully synchronous SoC buses: Advanced High-Speed Bus (AHB), Advanced System Bus (ASB), and Advanced Peripheral Bus (APB). Both AHB and ASB buses are used with systems requiring the highest performance. On the other hand, the APB bus is oversimplified. It makes no provisions for multiple bus masters and it is used with modules that are so simple, and yet so slow, that using an AHB or ASB bus would increase their complexity without any gain in return.

The AHB standard supersedes its ASB predecessor. ASB suffers from tri-stated bus signals known to be impossible to test with integrated circuits. It was issued rapidly after SoCs emerged, to fill in the gap between the available standards of that time. Unfortunately, it is inspired from standard PCB buses, which makes ASB maladapted to its environment. The AHB norm was introduced as a remedy to testability problems. In addition, it offers a new set of functions related to split transactions, a feature that is not supported by ASB. Therefore, ASB is not recommended for new designs.

The architecture of an AMBA AHB is illustrated in Figure 2.1. It is characterized by five different actors. Firstly, the bus master is an entity that initiates transfers on the

AHB, i.e., it issues addresses and READ data while it receives WRITE data. Note that the bus master has no authority over the AHB as it must wait for a bus grant issued by the bus arbiter. Secondly, the bus slave is the reciprocal of the bus master. It is the entity that answers the transfer request issued by a master. Hence, it receives addresses and READ data while it issues WRITE data. Thirdly, the bus arbiter rules over the AHB to grant the bus to only one bus master at a time. Many algorithms can be implemented by the arbiter and the specifications leave the arbitration policy open to be chosen by system architects. Fourthly, the AHB decoder interprets addresses to select the one slave corresponding to the target destination. Finally, multiplexed interconnections link all AHB entities together to form the communication infrastructure. Further details are available from the AMBA specification 2.0 [2].

Figure 2.1. Multiplexed AMBA AHB interconnections [2].

An advanced concept of AHB allows defining a hierarchy of buses to effectively augment the bandwidth of a NoC made of AHBs. To achieve that, an interconnect matrix

is used [18], as illustrated by Figure 2.2. The interconnect matrix is shaped as a specialized bridge that accepts multiple AHB "masters" as inputs, and then it multiplexes those AHBs with some arbitration policy toward a number of AHB "slaves". This advanced structure allows the creation of high-throughput communication fabrics where several Advanced High-Speed Buses may evolve in parallel, i.e., concurrently.

Figure 2.2. Complex Multi-layer AHB system example.

#### 2.2.2 CoreConnect

CoreConnect<sup>tm</sup> is another well accepted on-chip standard bus and it is owned by IBM [19]. It offers similar characteristics as the AMBA AHB standard, yet its typical structure is more complicated than AMBA, as shown in Figure 2.3. The Processor Local Bus (PLB) is similar to an AHB or ASB as it is used where the best performance is needed. The On-chip Peripheral Bus (OPB) is used with low performance cores. Interestingly, the OPB supports multiple bus masters, which is an added value over its equivalent APB. The traffic over the PLB is lightened by the use of a dedicated control bus called Device Control Register (DCR).

Figure 2.3. CoreConnect organizational diagram (reproduced from [19]).

CoreConnect supports advanced features such as split transactions, decoupled read and write buses to perform two transactions concurrently, address pipelining to reduce overall bus latency, and it is a fully synchronous bus. Even though the many advanced features supported by CoreConnect boost its performance to a higher level than AMBA, its increased complexity makes it less appropriate to implement with full-custom circuits. This is the main reason why CoreConnect was not considered for this research.

#### 2.2.3 STBus

In a multi-processor environment, the system bus is the main shared resource. To this regard, the STBus [20] is a true split-transaction bus. As a matter of fact, CoreConnect PLB and AMBA AHB support split-transaction transfers, but they should occur rarely since they tend to increase the latency. STBus is shaped as a split-transaction bus by definition [21]. The STBus address bus is completely decoupled from the READ data bus and the WRITE data bus, i.e. they are separately arbitrated. This bus is designed to minimize the average latency in a multi-processor system where several simultaneous requests are made for large amounts of data. In addition, the STBus supports shared memory multiprocessing with data coherence using a modified MESI write-invalidate snoopy coherence protocol [21], [22]. The STBus, as any other split-

transaction bus, is extremely complicated to design since each interface must be equipped to keep track of a number of transfers in order to assemble data with the corresponding address. This action is performed with the transaction tags and a tag index.

#### 2.3 Standard Interfaces Overview

An alternative to standard buses that gains acceptance with the SoC industry is to use standard interface protocols to design a custom NoC. Intuitively, standard interfaces define the protocol to exchange data from one instance to the next. Hence, the interconnect architecture is left free to system architects. With this approach, the cores are wrapped into a standard interface and they exchange data with the NoC via the specified unidirectional channel protocol. Simple bus-based NoC to complex interconnect infrastructures, such as butterflies, meshes, or trees [21] can be implemented with such standard interfaces.

#### 2.3.1 Advanced eXtensible Interface

The Advanced eXtensible Interface<sup>tm</sup> (AXI) [23] protocol is the newest AMBA SoC infrastructure offered by ARM. The AXI protocol is burst-based. Each transaction has the address and control information on the address channel that describes the nature of the data to be transferred. The data is transferred between a master and a slave using a write channel to the slave or a read channel to the master. In write transactions, in which data flows from the master to the slave, an additional write response channel is used to allow the slave to signal completion of the write transfer to the master. The AXI protocol permits address information to be issued ahead of the actual data and enables support for multiple outstanding transfers as well as out-of-order completion of transactions. An

identification tag is associated with every transactions issued between two interfaces. Hence, address and data association is seamlessly performed by the interface. Figure 2.4 shows the AXI channel configuration.

Figure 2.4. AXI channel configuration.

AXI is well suited for high-speed designs since its unidirectional channels allow for register slicing. This feature is used to pipeline interconnects that are known to become increasingly slow with respect to gate delays [24], [25] as the technology scales down. A possible drawback of AXI is that it does not offer dedicated signals to exchange system flags through its normalized interface. Then again, this drawback comes with the advantage of simplicity so as to reduce design efforts and time-to-market.

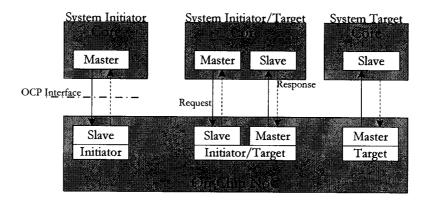

#### 2.3.2 Open Core Protocol

The Open Core Protocol (OCP) [26] is maintained by an international partnership composed of industrial and academic members. The idea behind OCP is similar to AXI. Here again, different interconnect architectures are possible with OCP as it simply

encapsulates an ASIC core into a standard interface to communicate with the interconnect infrastructure. Figure 2.5 illustrates the resulting system organization (also applicable to AXI). Each SoC core is wrapped into a slave and/or master interface to communicate with the interconnect fabric, which is itself wrapped into standard interfaces, via a unidirectional channel. Unlike AXI, OCP supports several options that are more or less required, depending of the system requirements, which may create diversity within a number of implementations.

Figure 2.5. System showing an NoC with OCP instances (reproduced from [26]).

### 2.4 High-Speed Circuit Styles Overview

Designing circuits that operate in the GHz range requires state-of-the-art circuit structures and innovative system architectures. Traditionally, high-speed CMOS logic is achieved with the use of dynamic logic [27]. The circuit style employed to design a circuit makes a significant difference when it comes to challenging the limits of a given technology. Though transistor sizing plays a vital role in circuit speed, the structure of the circuit ultimately sets an upper bound on the maximum achievable performance. Over the past decade, emitter coupled logic, which was widely used with high-performance circuit, has faded away because high-speed CMOS structures become more

and more competitive with more traditional methods (ECL) [27]. This section surveys three sequential logic styles that offer very high performance: no-race (NORA), true-single-phase-clocking (TSPC) dynamic logic, and MOS-current-mode-logic (MCML).

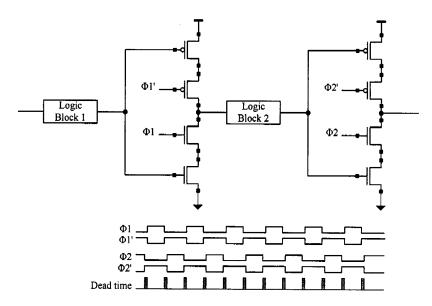

#### 2.4.1 NORA Dynamic Logic Style

In typical CMOS circuits, both static and dynamic CMOS logic are used. For the purpose of system timing, a synchronization strategy [24], [27] is always involved, except for self-timed systems [27]. One of the early popular clocking strategies is clocked CMOS logic (C<sup>2</sup>MOS) [27], which uses a non-overlapping pseudo-two-phase clock, as shown in Figure 2.6. Four clocks have to be distributed in such a system in a way that prevents overlaps between two clock pairs. Obviously, clock skew is a serious problem that threatens this requirement and it becomes more apparent with increasing circuit speed [24]. A dead time must be settled between two pairs of clocks to avoid races. Combining clock skew problems with race issues, the dead time must be large enough to provide sufficient stability guaranties. As a result, a significant time is lost with each clock phase to avoid failures and this tends to limit the maximum attainable clock frequency.

NORA stands for NO-RAce CMOS logic [27], [28], and targets the implementation of fast, pipelined datapaths using dynamic logic. NORA uses a true-two-phase clock signal ( $\Phi$  and  $\Phi$ '). Forcing some rules on circuit structures avoids races in NORA systems. Two types of stages are used within a NORA pipelined system,  $\Phi$ -C<sup>2</sup>MOS and  $\Phi$ '-C<sup>2</sup>MOS latches (see Figure 2.7). To avoid races, a designer must ensure that the number of inversions between two C<sup>2</sup>MOS latches is even. Furthermore, if dynamic nodes are present, the number of static inverters between a latch and the

dynamic node should be even. Finally, the number of static inversion between the last dynamic node and the C<sup>2</sup>MOS latch should be even as well. Adhering to the above rules is not always trivial and requires a careful analysis of the logic equations to be implemented. Nonetheless, the elimination of races in case of clock overlap allows speed optimization that qualifies NORA logic as a high-performance design styles.

Figure 2.6. C<sup>2</sup>MOS dynamic logic.

Figure 2.7. NORA dynamic logic.

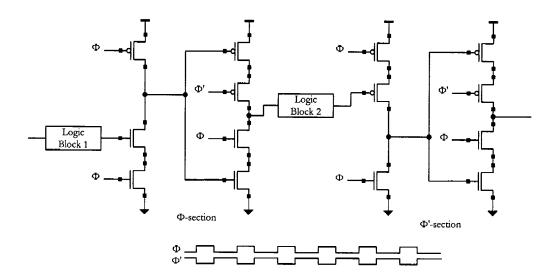

#### 2.4.2 True-Single-Phase-Clocking Style

NORA logic introduced a dynamic CMOS circuit style that avoids races. It turns out that a further development in clocking strategy is possible, so that a single clock is used to operate dynamic-sequential circuits. The never-ending quest for higher clock rates has led to the proposal of true-single-phase-clocking (TSPC) [27], [29], [30], a powerful design style. Its efficiency partly comes from its use of a single clock phase with no inversion. This leads TSPC to enhanced speed in comparison with NORA logic by eliminating intra-cell clock skew [29]. Yuan and Svensson were the instigators of TSPC logic style. They introduced four level-sensitive latches initially: double-C<sup>2</sup>MOS, split-output, TSPC-1, and TSPC-2 (see Figure 2.8). Construction of pipelined-sequential circuits is possible by alternating n-blocks with p-blocks, as with NORA.

Since then, a considerable amount of work has been invested in TSPC and more complex TSPC elements appeared. For instance, edge-triggered TSPC latches were invented so that positive, negative, and double-edge triggered TSPC latches are now commonly used with high-performance systems. For example, a positive-edge triggered TSPC latch may be constructed from the fusion of a p-block with an n-block. In addition, a new variety of TSPC latches makes them appropriate for an increasing number of applications. Non-differential semi-static TSPC flip-flops, dynamic ratio-insensitive differential TSPC latches, static ratio-insensitive differential TSPC latches, and single-transistor-clocked TSPC dynamic and static differential latches are only few examples of the diversity within this powerful design style [30]. Hence, the TSPC circuit technique is not only suitable for high-speed designs, but it also becomes attractive for low-power systems, static and dynamic random access memories for example.

In summary, true-single-phase-clocking has the advantages of simple and compact clock distribution, high-speed, and logic design flexibility. No intra-cell clock skew problem exits with this design style. At a larger scale, clock skew caused by clock delay between different logic blocks in a large system may be minimized with clock distribution networks, and reverse clock distribution [24]. TSPC has been used successfully for the implementation of a number of very high-speed CMOS circuits.

Figure 2.8. True-single-phase-clock latches.

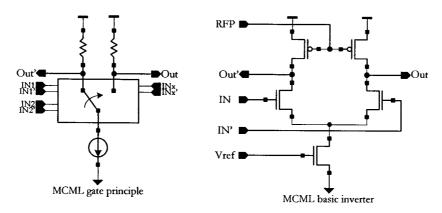

#### 2.4.3 MOS-Current-Mode-Logic

Traditionally, very high-performance digital circuits were implemented using bipolar current-mode-logic (CML) [27]. A MOS-Current-Mode-Logic (MCML) [31], [32] circuit consists of differentially operating MOSFET transistors and a constant current source. Its performance at low voltage is comparable with that of a CMOS circuit and bipolar current-mode-logic circuits. MCML circuits can be used to construct any logic circuits. High-speed compact circuits are feasible, because MCML circuits output complementary signals. An MCML has good characteristics and is widely applicable to logic circuits. It is a useful circuit method for producing GHz processors. It is important to note that the voltage swing is not rail-to-rail with MCML gates but in fact much less, in the order of hundreds of mV [32].

Figure 2.9 shows the theory of operation of an MCML gate with a basic inverter. An MCML gate consists of a differential NMOS pair used to perform logic equations, an NMOS constant-current source used to determine drive current, and two PMOS loads used to determine the voltage swing. Even though MCML is very appealing for high-speed circuits, its design is far more involved than CMOS logic since MCML circuits are much closer to analog design.

Figure 2.9. MCML method.

#### 2.5 Summary

The high-speed communication infrastructure is implemented using top notch computer aided design tools. Even though the design flow is particularly involved compared with conventional digital logic design methods, a full-custom design flow is used to implement an AMBA AHB SoC infrastructure. The circuits are built with TSPC logic to obtain GHz circuits. AMBA AHB is preferred over other standards for its simplicity and its past history within Microelectronics Research Group (GRM, École Polytechnique of Montréal). Finally, TSPC is selected for its speed, compactness, and ease of use over MCML. MCML can possibly offer better performance, but the complexity of the system to be developed over several levels of abstraction leaves no room to stress design efforts further.

# 3 FULL-CUSTOM CIRCUIT METHODOLOGY AND TECHNIQUES

As integrated circuits become less expensive and more compact, many new types of products are being introduced, based on digital systems. Consequently, digital logic design is being performed under different motivations. Since each case is different, different design problems are encountered. As a result, different design flows have been established to respond to different needs. For instance, semi-custom design (recently referred to as ASIC design) exists to speedup time-to-market and to reduce design efforts at the expense of reduced speed, higher power consumption, and increased area. On the other hand, deliberate design for high-performance is called full-custom design because each design is manually tuned to high-performance. Digital systems' speed can be significantly improved by deliberate logic design.

This chapter defines the full-custom design flow used to realize a novel 2 GHz AHB SoC infrastructure. The complete design methodology, acquired with experience, is detailed. In addition, a complicated simulation process has been researched in order to fill the gap created by an unusual design approach within Canadian universities. The complexity of the circuit and the relatively complicated set of inputs required for complete stimulus controllability and observability. For instance, a mixed-signal simulation approach has been employed to integrate HDL testbenches into the analog-like circuit simulation process.

Finally, circuit techniques are surveyed in this chapter to further detail the methodology used. Hence, the selection of a TSPC style is explained together with accurate logic design styles and rules enforced in this project.

#### 3.1 Establishing a Design Methodology

Designing a 2 GHz AMBA High-Speed Bus (AHB) [2] is not straightforward. The fastest reported implementation prior to this research adopted a semi-custom design flow. The AHB resulting from the logic synthesis could operate up to 510 MHz according to circuit simulations [33]. This bus is indeed fast considering the numerous bottlenecks raised by limitations of the synthesis process, standard cell libraries, and relatively sparse layouts created by automatic placement and routing [6], [7], [8]. To overcome those bottlenecks caused by the ASIC flow used, a full-custom flow is most appropriate [6], [7], [8]. This led to the implementation of a hard IP operating at 1.4 GHz [34] initially, and that was further improved to sustain a clock rate in excess of 2 GHz [35], the initial target. Nevertheless, achieving a digital VLSI circuit clocked in the GHz range requires careful planning since the best design cannot compensate for an underperforming circuit stage. Hence, this section describes the design methodology followed to develop the 2 GHz AHB fabric.

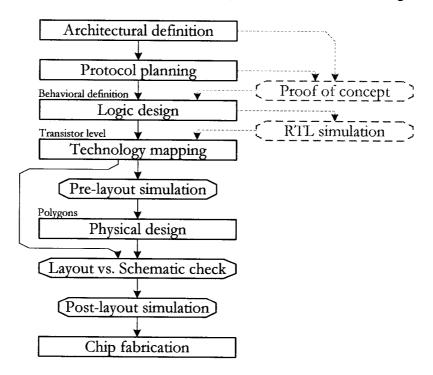

Even though digital systems' performance can be significantly improved with deliberate logic, every steps of the full-custom design flow is important to achieve performance requirements. Actually, the design of the 2 GHz AHB fabric spans multiple levels of abstraction and follows a long sequence of design stages, as illustrated by Figure 3.1.

## 3.1.1 Architectural Planning

Defining the bus architecture is the first of many design steps. The structure of a digital system is, without any doubt, a determining factor in obtaining the required performance. This is true regardless of the design flow that is used. Then again, the pressure goes up when a full-custom design is employed. As a matter of fact, the iterative process involved with full-custom design directly threatens time-to-market and profitability. For instance, a product being introduced on the market one year before the competition has a potential of more than twice the profit of the latecomers. The firm that introduces the product has free way to capture the majority of the market share at higher prices, whereas the latecomers can only gather leftovers of the market share at lower prices [8]. Actually, an architectural limitation discovered in a latter design phase may require redoing a significant portion of the design to set the architecture right.

Figure 3.1. Proposed design flow.

To be successful with the architectural design phase, an intimate understanding of the application under development is required. That implies being comfortable with the specifications and requirements of the system, thoughtful planning of modules' interactions, and foreseeing architectural implications on hardware and firmware.

## 3.1.2 Protocol Design Phase

The communication infrastructure being addressed by this research shapes a network-on-chip (NoC). For this reason, the communication protocol must be meticulously designed since the overall SoC performance depends on the NoC efficacy. Luckily, the AMBA AHB standard helps setting the communication protocol between different systems' actors. As a matter of fact, the AHB standard sets the bus architecture and it defines the signals' behavior. This allows interconnecting modules from different design teams with less effort since a standard interface is strictly compulsory. Nevertheless, the hard IP under development may require going beyond the standard to optimize the SoC infrastructure. In Chapter 4, the hard IP architecture is explained and some amendments to the standard are formulated. Amending the protocol set by the standard brings a risk that must be tackled appropriately. Obviously, a bug in the protocol would force time consuming iterations to fix it.

## 3.1.3 Logic Design

The logic design phase involves defining the behavioral model of the communication infrastructure. Logic networks with pipelining are described by this design phase. With careful partitioning, it is possible to establish behavioral equations manually. However, when the functions of a partition are too involved for human minds,

it is possible to describe the behavior of the component using a hardware description language to extract the logic functions [8]. The resulting equations will be given under an AOI (AND, OR, and INVERTER) or OAI shape in most cases. Then, it is possible to map those equations into transistor circuits. Yet again, the full-custom circuit resulting from that approach is similar to what CAD tools would create using standard libraries. Hence, the performance gain may be limited.

## 3.1.4 Technology Mapping

Technology mapping consists of translating logic networks into transistor circuits. Of course, it is possible to use a simple AOI/OAI design style (standard AND, OR, INVERTER / OR, AND, INVERTER gates) to perform this step, but deliberate logic design allows for more aggressive circuit structures. As a result, each equation is studied cautiously so as to research an optimized transistor structure minimizing fanin effects, logic depth, and intrinsic delays. Obviously, technology mapping is the first design phase where a significant speed improvement is achieved from meticulous circuit techniques. The freedom brought by full-custom design often results in unconventional transistor constructs outperforming any equivalent semi-custom designs.

## 3.1.5 Physical design

The physical design phase is the last phase capable of great speed improvements over automated designs. Performing layout for a full-custom design is a painstaking endeavor to most draftspersons. However, circuits laid out using handcrafted polygons are more compact than those obtained from CAD tools. Needless to say, physical design

is critical to high performance if meticulous done, yet a lousy layout can rapidly destroy all speed gains made previously.

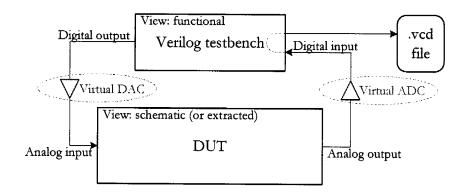

## 3.2 Simulation Process

Interestingly, the full-custom design flow utilized with the 2 GHz AHB fabric raised a serious problem regarding simulations. The digital design flow [36] maintained by the Canadian Microelectronics Corporation (CMC) is inadequate for full-custom design since it is meant for ASIC design. Intuitively, the 2 GHz AHB fabric resembles more to an analog design, since the work is performed at transistor level in an analog way. For this reason, the analog design flow [37] is more appropriate to the design style employed with the hard IP. However, digital circuits are often characterized by numerous digital signals where a specific bit organization is important. In order to stimulate the circuits with relevant test vectors, or simply to activate a specific state, controllability of the test vectors is required. Achieving this objective with the analog design flow at hand is not easily realized. Furthermore, a great number of signals are to be observed in order to attest the correctness of the design. WaveScan<sup>tm</sup> [38], the waveform viewer provided by Affirma Analog Artist<sup>tm</sup>, does not support the notion of bus. For this reason, WaveScan explodes groups of signals to display them, so groups are difficult to read and they consume precious space on the display to analyze the response of the modules. Here again, a solution had to be envisioned to observe the system response to test vectors. Therefore, an alternate simulation flow has been researched in order to apply test vectors from either a hardware description language (HDL) or a hardware verification language (HVL), and to observe them accurately.

The solution for the above stated problem resides in Cadence mixed-signal design tools and Verilog [16] as the hardware description languages used to specify test cases. It is possible to specify functional views into Cadence Virtuoso<sup>tm</sup>, so as to create test fixtures including the analog component with a Verilog file to control the stimulus applied to the device under test (DUT). The Hierarchy Editor inserts digital-to-analog (DAC) instance in between the digital stimulator and the DUT to effectively convert the digital signal into an analog signal. Options allow specifying V<sub>IH</sub>, V<sub>IL</sub>, t<sub>r</sub>, and t<sub>f</sub> to shape the signals according to the specifications of the DUT. Similarly, an analog-to-digital (ADC) instance is used to interpret the out coming analog signal by the testbench. Hence, V<sub>OL</sub>, V<sub>OH</sub>, and the maximum transition time can be specified for conversion. Figure 3.2 shows a typical test fixture used in the design of the 2 GHz AHB fabric.

Figure 3.2. Test fixture used for full-custom simulation.

SpectreSVerilog<sup>tm</sup> is a mixed-signal simulator that combines SpectreS<sup>tm</sup> capabilities with Verilog XL<sup>tm</sup> to effectively simulate analog and digital cell views cooperatively. Hence, Verilog XL feds the virtual DAC with test vectors that are applied to the analog cell view. On the other end, the response of the DUT is converted back to digital signals that are dumped in a .VCD file. The .VCD file saves all signals involved in the Verilog file. Hence, observability is possible from Verilog XL since the ADC

provides a mean to read back the DUT response. Afterward, it is possible to enter post-processing in Verilog XL<sup>tm</sup> and verify the correctness of the design with SimVision<sup>tm</sup>, the waveform viewer included with Verilog XL. The resulting waveform is similar to a typical RTL simulation. Any signals that remain in between V<sub>OH</sub> and V<sub>OL</sub> longer than the maximum transition time specified for the ADC interface are shown with a red rectangle, meaning undefined value. Hence, voltage level problems along with slow transitions are seamlessly traced with this simulation method.

# 3.3 Circuit Techniques

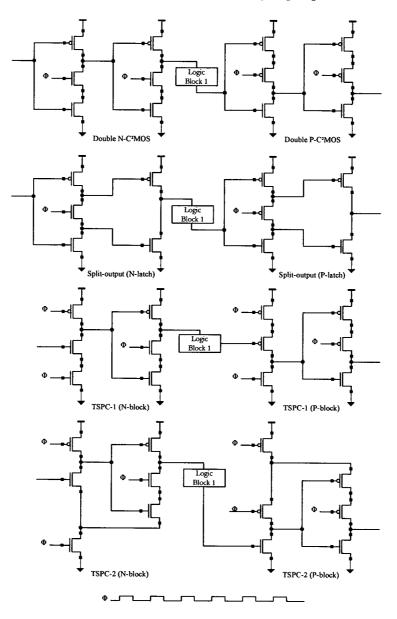

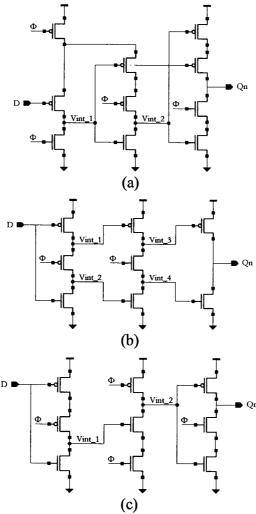

Designing digital circuits clocked in the GHz range is a thorough commitment that requires state-of-the-art circuit techniques combined with aggressive transistor sizing. The never-ending quest for higher clock rates led to the proposal of true-single-phase-clocking (TSPC) [27], [29], [30], a powerful design style. This dynamic circuit technique allows reaching high frequencies. Its efficiency partly comes from its use of a single clock phase with no inversion. This leads TSPC to improved speed in comparison with the no-race (NORA) [28] as it avoids intra-cell synchronization bottlenecks [29]. Yuan and Svensson [29], [30] proposed four high-speed TSPC latches: TSPC-1, TSPC-2, C<sup>2</sup>MOS, and split-output. Even though they claimed that TSPC-1 and TSPC-2 should perform faster, other researchers have shown that C<sup>2</sup>MOS and split-output outperforms the former latches [39]. However, beyond this debate, the question of which TSPC style is best suited for a design remains unanswered. This section attempts answering this question based on the experience gained through the design of a 2 GHz communication infrastructure targeting high-end SoCs.

In addition to the TSPC style employed, a discussion on transistor sizing is included in this section, along with the preferred logic styles, and the design rules enforced to improve the probability of success. The aim here is to transmit the knowledge on high-speed circuits, acquired through experience, to possibly shorten the learning curve that other designers targeting this kind of performance could experiment.

## 3.3.1 Selecting a TSPC Style

To implement 2 GHz AHB cores, three positive edge-triggered latches have been studied: TSPC-2, split-output, and C<sup>2</sup>MOS (see Figure 3.3). Even though all candidates meet the target speed, there are timing issues to account for in selecting an optimal style (speed wise). As a matter of fact, besides the transistor count, the optimal TSPC solution should maximize the slack time allotted to useful computation (t<sub>logic</sub>) and interconnect delays (t<sub>INT</sub>). Hence, the maximum allowable slack time (t<sub>SL</sub>) between two sequentially adjacent registers is given using equations (3.1) and (3.2) [24]:

$$t_{SL} \le t_{CP} - (t_{C-Q} + t_{SETUP})$$

(3.1)

where,

$$t_{SL} = t_{LOGIC} + t_{INT}$$

(3.2)

and  $t_{C-Q}$  is the time from rising clock edge to output valid,  $t_{CP}$  is the clock period, and  $t_{SETUP}$  is the setup time of a register.

Table 3.1 summarizes various parameters of the TSPC latches obtained by circuit simulations. Even though the hold time of TSPC-2 (Figure 3.3a) outperforms any other style, its high setup time severely hinders the slack time. This is further aggravated by a slower clock-to-output delay, which creates the worst slack time of all three styles. Hence, TSPC-2 is considered the least effective for the design of 2 GHz AHB cores.

(c)

Figure 3.3. Positive edge-triggered latch candidates for the 2 GHz AHB. (a) TSPC-2, (b) Split-output, (c) C<sup>2</sup>MOS.

TABLE 3.1. COMPARISON PARAMETERS OF THREE TSPC LATCHES.

|                             | TSPC-2 | Split-output | C <sup>2</sup> MOS |  |  |

|-----------------------------|--------|--------------|--------------------|--|--|

| <b>Transistor Count</b>     | 10     | 9            | 8                  |  |  |

| t <sub>SETUP</sub> (ps)     | 195    | 170          | 50                 |  |  |

| t <sub>HOLD</sub> (ps)      | 0      | 165          | 55                 |  |  |

| t <sub>C-O (MAX)</sub> (ps) | 125    | 105          | 81                 |  |  |

| t <sub>SL</sub> (ps)        | 180    | 249          | 345                |  |  |

The reduced clock fan-in of split-output latches (Figure 3.3b) is an advantage that cannot be overlooked, since the power consumption in clock distribution networks is a very significant factor in modern ICs [24]. The reduced transistor count of the split-

output TSPC latch has a tendency to speedup clock-to-output delay, but these latches require a long setup and hold (more than half the clock period). Another possible drawback of the split-output approach is that all internal nodes (Vint\_x) do not have a full voltage swing, as some single transistors are used to propagate high and low logic [29]. Therefore, accounting for all factors, split-output latches are used sparingly with the 2 GHz AMBA bus, where there is no logic involved in signals path, as in the case of the datapath. For instance, the datapath is mostly made of 2-to-1 multiplexers, used as an enabling mechanism, and latches. As the bus width and address space increases, the complexity of the datapath explodes. This damps the clock distribution network significantly. For this reason, a reduced clock fanin is appropriate to reduce the burden put forward to the clock drivers.

Finally, C<sup>2</sup>MOS (Figure 3.3c) offers the best trade off to obtain the fastest logic as its slack time appears to be the best of all three TSPC techniques. For this reason, it is largely used in the design of the high-speed bus, especially where complex decisions need to be computed between two sequentially adjacent registers. In addition, its internal nodes offer improved stability over split-output latches so that PMOS and NMOS are used more effectively. Also, it is easier to embed logic into C<sup>2</sup>MOS latches.

#### 3.3.2 TSPC Device Sizing

The design of a digital circuit operating in the GHz range requires aggressive transistor sizing. Each component must drive a sufficiently large current to overcome the parasitic capacitance and resistance, which are extracted from the process used for the physical design. Since gate delays decrease as the technology scales down, an ever increasing disparity between wire delays and gate delays is seen [24], [25], [40]. This

phenomenon is mainly due to parasitic RC components that, in a sense, create a low pass filter limiting the maximum frequency of a circuit. Hence, it is desirable to size the memory elements in a way that minimizes input load and maximizes output current.

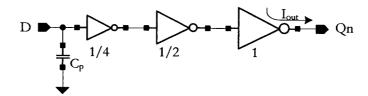

In essence, an edge-triggered TSPC latch is made of three inverting stages. This hints at using buffer theory to gradually boost the current capabilities of each succeeding stage [27]. Furthermore, each device is configured with the minimal gate length specified by the process used, whereas its gate width is optimized for speed. Proper transistor sizing significantly impacts a device performance, as discussed in [6], [8], [27], [29]. To perform TSPC device sizing, the output stage is sized in the first place to match the attributes of an inverter driving a large output load. From that point, the second stage is scaled down by a factor of two and the first stage by a factor of four, with respect to the output stage so as to maximize current driving capabilities within the latch. Figure 3.4 illustrates the buffering theory applied with TSPC stages. This approach generates a small latch input capacitance with respect to its output current capabilities. Hence, the third stage can muddle through with a large fanout, while the fanin of the latch is small to minimize RC delays experienced by the input logic, and to allow for longer interconnects.

Figure 3.4. Buffering TSPC stages.

## 3.3.3 Logic style and Design Rules

The maximum clock frequency in synchronous systems is constrained by logic coupled with interconnects delays, from one latching instant to the next [24]. One way to minimize this delay is to decompose the complexity of each logic block so as to create small and manageable sub-blocks that operate within one clock period. Even though this approach suffers from an initial delay, this is acceptable in pipelined structures, yet a practical limit to logic reduction sets the system efficiency [41]. To a certain extent, the logic style employed makes a difference.

The complementary CMOS circuit technique allows the creation of complex logic functions. Unfortunately, this design style is particularly sensitive to RC delays caused by connecting transistors in series. It is quite obvious that the number of transistors interconnected in series should be minimized to obtain high-speed logic.

As a result, a design rule was created to limit the number of transistors used in series. Simple decisions were implemented using pass logic [8], [27] while complex computations were designed with a parallel static-NAND (or a parallel static-NOR) structure close to pseudo-NMOS logic, as described in Chapter 5 and [35]. This is seamlessly implemented, since many logic networks can be reorganized in a parallel static NAND structure with simple algebraic manipulations. Note that with CMOS technology, inverter delays are still small so that extra inverters can be accepted in the blocks.

In addition, to guide logic design, a supplemental rule was enforced with the high-speed AHB circuits to obtain successful "at speed" simulations after layout extraction. With the 0.18 µm CMOS process in use, it was expected that the parasitic capacitances

would double from circuit level simulations to extracted layout simulations, due to the many added wires. This affects the slack time by a factor of two, as suggested by (3.3):

$$t_{SL} = R \cdot 2C_{p} \tag{3.3}$$

where  $C_p$  represents the total parasitic capacitive load attached to a device. Obviously, the capacitive load has a linear relationship with the slack time. Hence, logic blocks were not allowed to consume more than 50% of  $t_{\rm SL}$  during circuit level simulations so as to prevent exceeding the time budget after layout extraction.

Finally, keeping the transition times below 100 ps in circuit level simulations ensured further room for degradation. In addition,  $V_{OH}$  and  $V_{OL}$  were kept within VDD  $\pm$  10% to respect industrial practice to this regard.

## 3.4 Summary

The aim of this chapter is to describe various methodologies used to cope with the design of a novel 2 GHz communication infrastructure. The full-custom design flow employed is explained in details. In addition, a difficult simulation process has been researched and described in details in this chapter. This mixed-signal simulation method is most needed to apply well thought test vectors and to verify the correctness of the high-speed fabric.

Finally, a section is devoted to circuit techniques since deliberate logic has the potential of improving system performance significantly. In addition, designing for high-frequencies is poorly documented in the literature as most books only define the problematic. Hence, metrics for choosing a TSPC style over another are discussed, along with means for sizing the device for high-performance. Preferred logic styles with design rules are also enumerated.

# 4 AHB INFRASTRUCTURE ARCHITECTURE

The performance of high-end SoCs is characterized by their processors' ability to communicate effectively within the silicon die. Even though a number of communication standards exist to answer this concern, none were designed to interconnect high-speed modules in a simple fashion. As a result, the throughput offered is low, and complex parallel structures need to be constructed to achieve the data crunching rates required by modern applications. A new communication infrastructure, based on the AMBA AHB specification [2], is described in this chapter. Its architecture supports multiple-outstanding data streams through a pipelined shared-memory, specifically designed to meet the data rates required by the new communication fabric. The derived structure is simple, yet powerful, to interconnect a small number of bus masters. In addition, its components support clock rates outperforming every shared bus reported in the literature to our knowledge. The internal targeted frequency is 2 GHz.

This chapter explores the architecture and the operations of the major components of the new communication infrastructure. The master bridges required to link the platform's processor with the high-speed bus are explained. Finally, the structure of the pipelined shared memory is presented with its conflict resolution mechanism, and the arbitration method is detailed.

# 4.1 AHB Interconnect Megacell Overview

Modern SoCs are typically developed using a semi-custom design flow (commonly referred to as ASIC flow) [6], [7], [8]. This hints that new communication infrastructure interfaces mainly with soft intellectual property (IP) modules, and sporadically with hard IPs when enhanced performance is needed. As a result, the high-performance AHB requires a cautiously designed architecture that combines seamless integration of the modules to provide high-throughput. Obviously, the communication fabric's interfaces must be capable of accepting different clock rates, sometimes much lower than its 2 GHz frequency. This solicits multi-frequency bridges. In addition, several modifications are implemented with respect to the AHB standard so as to obtain the highest possible performance [34]. They range from protocol leveraging techniques to interconnect reconfiguration with an increased pipeline depth. This section introduces the many modules of the new SoC infrastructure together with initial assumptions made to reduce the complexity of this research project.

## 4.1.1 Clock Domains

As mentioned previously, the 2 GHz communication infrastructure is a hard IP intended to enhance the bandwidth offered by the most demanding SoCs. This suggests that the proposed megacell is surrounded by a number of processing elements that sometimes operate from a much lower clock frequency. This situation is the result of performance bottlenecks caused by the synthesis, placement, and routing processes [6], [7], [8]. Hence, a module developed using an ASIC flow and a 0.18 µm CMOS technology typically operates up to 200 to 300 MHz. This phenomenon must be taken into consideration when designing a high-performance communication infrastructure.

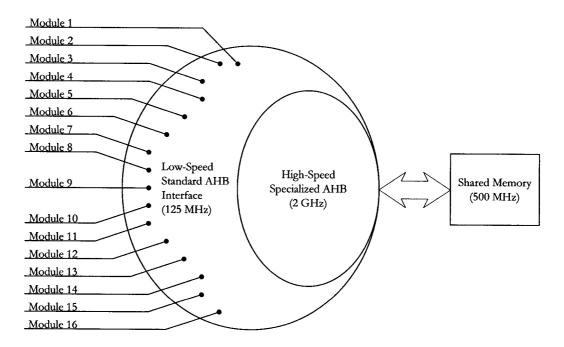

Three distinct clock domains have been considered in designing the 2 GHz AHB fabric. The first domain, referred to as the standard AHB domain, is formed by the processing elements and their local AHB. All standard AHBs share an equal fraction of one specialized AHB's bandwidth. Hence, the standard AHB domain works from a clock frequency of 125 MHz. The second clock domain encapsulates specialized READ and WRITE AHBs. Both specialized AHBs operate with a 2 GHz clock frequency. The third clock domain of interest is again encapsulated by the hard IP. It provides a 500 MHz clock frequency to synchronize the operation of the high-throughput shared-memory. Figure 4.1 illustrates the three clock domains and their components. It is important to mention that synchronization of the different domains is beyond the scope of this research. For the time being, it is assumed that the clocks are generated and synchronized by a phase-lock-loop (PLL) [42].

Figure 4.1. Clock domains division.

The new high-speed bus infrastructure does not include advanced synchronization mechanisms such as a globally-asynchronous-locally-synchronous (GALS) wrappers, asynchronous FIFOs, nor synchronizers to decouple the clock domains. For this reason, clock edge alignment is required from the PLL to avoid synchronization failures. This imposes a limitation on the clock rates that a designer may select. As a matter of fact, the clocks of the standard AHB and the clock of the memory must have a period that is a multiple of the period of the 2 GHz clock used by the specialized AHB. This safeguard is required to ensure that edges from interacting clocks coincide with each other on a regular and predictable basis.

Note that even though a unique clock frequency is assumed for the standard AHB domain, it may use multiple clock frequencies in practice, since typical SoCs are composed of several modules of different nature often provided by different vendors. Then again, to simplify the complexity of the first implementation of the high-speed AHB infrastructure, the standard AHB domain has been constrained to use only one clock frequency.

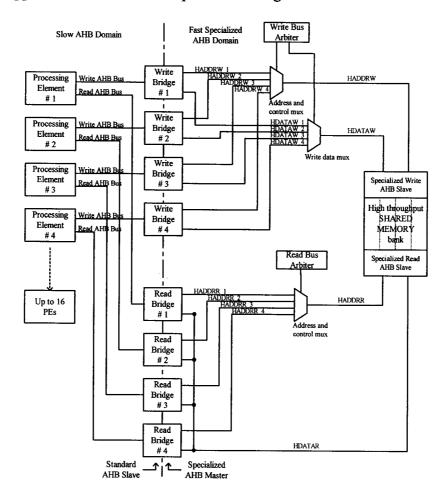

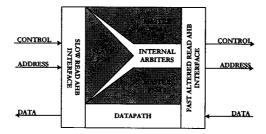

## 4.1.2 Architectural Overview of the Communication Fabric

The architecture of an Advanced High-Speed Bus is mostly determined by its specifications [2]. However, there exist some grey spots that give room for customization. The new hard IP makes effective use of those grey spots to elaborate an architecture slightly different from what has been specified to effectively provide an aggregate bandwidth that corresponds to a 4 GHz clock speed. Thus, the heart of the high-speed bus is derived from the AHB standard. Still, to obtain the fastest possible speed out of this interconnect infrastructure, READ and WRITE operations have been

separated on two physically independent AHB, referred to as specialized AHB. In addition, all superfluous signals to the shared memory were screened out from the implementation to simplify the circuits. Finally, the pipeline depth has been adjusted to optimize the throughput of the specialized READ and WRITE AHBs.

The specialization made to the high-speed AHB buses is not forbidden by the standard. In addition, it allows doubling the effective bandwidth since the READ and the WRITE buses operate concurrently. Furthermore, several processors offered by ARM (the owners of AMBA standards) are available with specialized AHBs, here also to increase the processors' bandwidth. As an example, the ARM1136J(F)-S processor [43] is offered with five concurrent AHB master interfaces: one interface is dedicated to instruction fetch, the second to data write, the third to data read, the fourth to peripheral access and the fifth handles direct memory access (DMA) only.

The proposed communication infrastructure guarantees high-performance access to all the modules it services. An AHB interface supporting the basic features of the standard is provided to facilitate modules integration with the high-performance communication infrastructure, as shown in Figure 4.2. Standard AHB interfaces are used by the processing elements as AHB slaves to access the high-performance communication fabric. Each specialized bus resembles strangely to what has been specified by the standard, except for the AHB decoder which is absent from this design. Banning the decoder is perfectly acceptable since the memory bank forms a single slave. The memories are accessed upon a specific clock phase and not upon the address criteria as in conventional shared-buses. Hence, it is the bus arbiter that determines which SSRAM from the memory bank is accessed at what time. This is not against the

specifications since the preferred arbitration method depends on the specifics of a particular application. It is thus left open to the designer.