#### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

|  |   | • |

|--|---|---|

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  | • |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

## On the Formal Verification of ATM Switches

### Jianping Lu

A Thesis

in

The Department

of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements

for the Degree of Master of Applied Sceience at

Concordia University

Montréal, Québec, Canada

1999

© Jianping Lu, 1999

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre reference

Our file Notre reférence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-43654-3

### **ABSTRACT**

#### On the Formal Verification of ATM Switches

#### Jianping Lu

Because of the difficulty of adequately simulating large digital designs, there has been a surge of interest in formal verification, in which a mathematical model of the design is proved to satisfy a precise specification. *Model Checking* and *Equivalence Checking*, which have the advantage of automatic verification, are two main formal verification techniques that people are working on. The main problem of model checking and sequential equivalence checking is the state space explosion. Another drawback of model checking is lack of methods on establishing an environment and expressing a property. In this thesis, we propose *Property Division* techniques which avoid the state space explosion problem by deducing a property from several sub-properties. A number of methods on establishing an environment and expressing a property are illustrated.

Although ATM hardware is hard to design due to its high speed and various features, the applications of model checking and equivalence checking on ATM hardware verification are few. In this thesis, Fairisle ATM switch fabric, Fairisle ATM null port controller, Input FIFO of RCMP-800 and Concentrator of Knockout ATM switch are developed. With the techniques we propose, all these ATM hardware designs are formally verified in the formal verification tools called Verification Interacting with Synthesis (VIS).

### **ACKOWLEDGEMENTS**

I have been very fortunate to have Dr. Tahar as my advisor through out my stay at Concordia University. Dr. Tahar devotes considerable time and energy to his students, and many of my idea about verification and about what constitutes interesting research arose from talks with him. His insistence on motivation, discussion, and examples has hopefully turned this thesis from a wasteland of formality into something readable. I was fortunate to be a student of Dr. Al-khalili when he was the instructor of the course "digital design system". His excellent teaching on digital designs helped me to build up the ATM models presented in the thesis. Special thanks are due to Dr. Mehmet-Ali and Dr. Bouguerba for their constructive criticism and comments through the course of this work.

I also wish to acknowledge all the teachers and individuals who have contributed to my knowledge during the period of my stay at Concordia.

Finally, my wife gave me her constant love and encouragement, I can never thank her enough.

## **TABLE OF CONTENTS**

| CHAPTER 1 INTRODUCTION                                      | 1          |

|-------------------------------------------------------------|------------|

| 1.1 THEOREM PROVING BASED METHODS                           | i          |

| 1.2 DECISION GRAPH BASED METHODS                            | 2          |

| 1.3 VERIFICATION INTERACTING WITH SYNTHESIS                 | 5          |

| 1.4 FORMAL VERIFICATION AND DESIGN FLOW                     | 8          |

| 1.5 SCOPE OF THE THESIS                                     | 10         |

| 1.6 RELATED WORK                                            |            |

| CHAPTER 2 MODEL CHECKING METHODOLOGY                        |            |

| 2.1 COMPOSITIONAL VERIFICATION                              | 16         |

| 2.1.1 CTL and ACTL                                          | 17         |

| 2.1.2 Compositional Reasoning                               | 18         |

| 2.2 ENVIRONMENT                                             | 20         |

| 2.3 PROPERTY DIVISION                                       | 20<br>27   |

| 2.3.1 Cascade Property Division                             |            |

| 2.3.2 Parallel Property Division                            | 20<br>20   |

| 2.4 PROPERTY EXPRESSION                                     | 32         |

| CHAPTER 3 VERIFICATION OF FAIRISLE ATM SWITCH               |            |

| 3.1 THE ATM SWITCH FABRIC                                   |            |

| 3.1.1 Switch Fabric Behavior                                | 37         |

| 3.1.2 Switch Fabric Implementation                          | 37         |

| 3.2 MODEL CHECKING                                          | 38         |

| 3.2.1 Environment for the switch fabric                     | 38         |

| 3.2.2 Property description                                  | 40         |

| 3 3 ABSTRACTED FABRIC                                       | 42         |

| 3.4 DISCUSSION ON ENHANCEMENT OF MODEL CHECKING             | 44         |

| 3.4.1 Cascade property division example                     | 44         |

| 3.4.2 Parallel property division                            | 45         |

| 3.4.3 Latches Reduction                                     | <b>4</b> 7 |

| 3.4.4 Concluding Results on Model Checking                  | 48         |

| 3.5 ERROR DETECTION IN MODEL CHECKING                       | 49         |

| 3.6 VERIFICATION OF THE ENTIRE FAIRISLE ATM SWITCH          | 49<br>57   |

| 3.6.1 ATM Switch Modeling                                   |            |

| 3.6.2 Property Description and Deduction                    | 58<br>58   |

|                                                             |            |

| CHAPTER 4 VERIFICATION OF ATM PORT CONTROLLER               |            |

| 4.1 BEHAVIOR OF THE NULL PORT CONTROLLER                    |            |

| 4.2 STRUCTURE OF THE NULL PORT CONTROLLER                   | 66         |

| 4.4 EXAMPLES ON PROPERTY DESCRIPTION IN CTL                 | 67         |

| 4.4.2 Internal Signal Usage                                 | 74         |

| 4.4.2 Internal Signal Usage                                 | 81         |

| 4.4.4 Experimental Results and Summary on the Three Methods | 82         |

| 4.5 EXPERIMENTAL RESULTS AND ERROR DETECTION:               | 83         |

| 4.6 SUMMARY                                                 | 84         |

| CHAPTER 5 MODEL CHECKING OF INPUT FIFO                      | 85         |

| 5.1 Introduction on RCMP-800                                | 85         |

| 5.1.1 Behavior of Input FIFO                            | 88              |

|---------------------------------------------------------|-----------------|

| 5.1.2 Functions of the input FIFO                       | 90              |

| 5.2 VERIFICATION OF THE INPUT FIFO                      | 90              |

| 5.2.1 The environment of the input FIFO                 | 91              |

| 5.2.2 Model Checking                                    | 92              |

| 5.2.3 Experimental Results and Error Detection          | 96              |

| 5.3 SUMMARY                                             | 97              |

| CHAPTER 6 EQUIVALENCE CHECKING                          | 98              |

| 6 1 FOUVALENCE CHECKING OF FAIRISLE ATM SWITCH FABRIC   | 100             |

| 6.1.1 The Timing module: An example                     | 101             |

| 6.1.2 Experimental Results on Equivalence Checking      | 103             |

| 6.1.3 Analysis on sequential equivalence checking       | 10 <del>4</del> |

| 6.1.1 From detection with equivalence checking          | 103             |

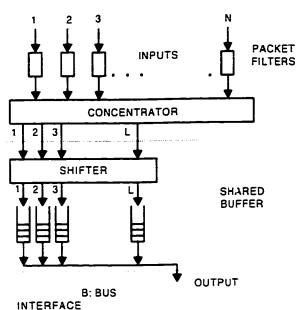

| 6.2 FOUVALENCE CHECKING OF KNOCKOUT SWITCH CONCENTRATOR | 105             |

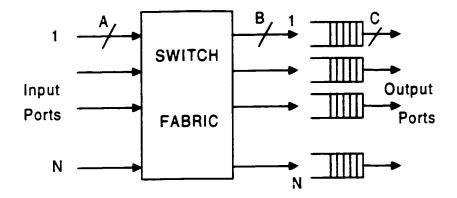

| 6.2.1 Architecture of Knockout ATM Switch               | 100             |

| 6.2.2 Equivalence Checking of the Concentrator          | 109             |

| 6.2.3 Experimental results and discussion               | 111             |

| 6.3 SUMMARY                                             | 112             |

| CHAPTER 7 CONCLUSIONS                                   | 113             |

| APPENDIX A                                              | 122             |

| A.1 TIME DIVISION SWITCHES                              | 122             |

| A.2 SPACE-DIVISION SWITCH                               | 125             |

| APPENDIX B                                              | 134             |

| B.1 COUNTER REDUCTION IN PROPERTY 3                     | 134             |

| B.2 MODEL CHECKING OF THE NULL PORT CONTROLLER          | 140             |

## **LIST OF FIGURES**

| Figure 1.1 Digital design flow using VIS                                                       | 10             |

|------------------------------------------------------------------------------------------------|----------------|

| Figure 2.1.A handshake circuit                                                                 | 21             |

| Figure 2.2 Environment of the circuit of Figure 2.1                                            | 21             |

| Figure 2.3 State transition diagram for the circuit of Figure 2.1                              | 22             |

| Figure 2.4 State transition diagram for the circuit of Figure 2.2                              | 22             |

| Figure 2.5 Composed circuit                                                                    | 23             |

| Figure 2.6. State transition diagram, representing the composite circuit                       | 24             |

| Figure 2.7 The maximal closing environment for the structure of Figure 2.3                     | 24             |

| Figure 2.8 The composition of the structure Figure 2.3 and its maximal closing environment     | 25             |

| Figure 3.1 The structure of the Fairisle ATM switch                                            | 30             |

| Figure 3.2 The routing tag of a Fairisle ATM cell                                              | 36             |

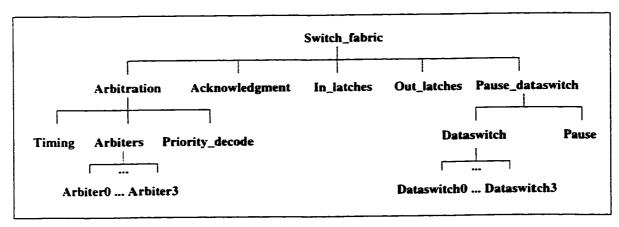

| Figure 3.3 Fairisle switch fabric implementation                                               | 38             |

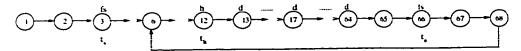

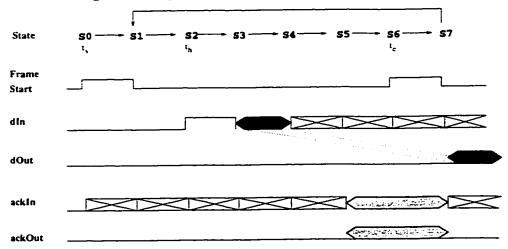

| Figure 3.1.68 state environment state machine                                                  | 39             |

| Figure 3.5 Abstracted environment state machine with related timing diagrams                   | 39             |

| Figure 3.6 The abstracted switch fabric                                                        | 43             |

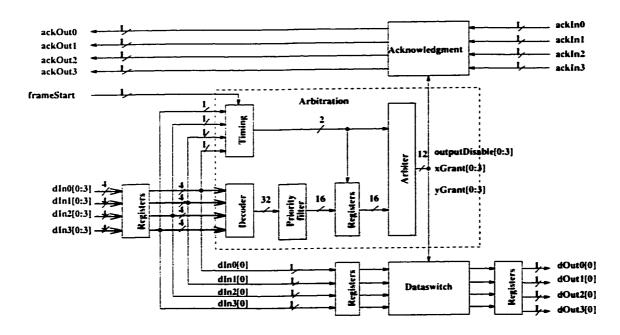

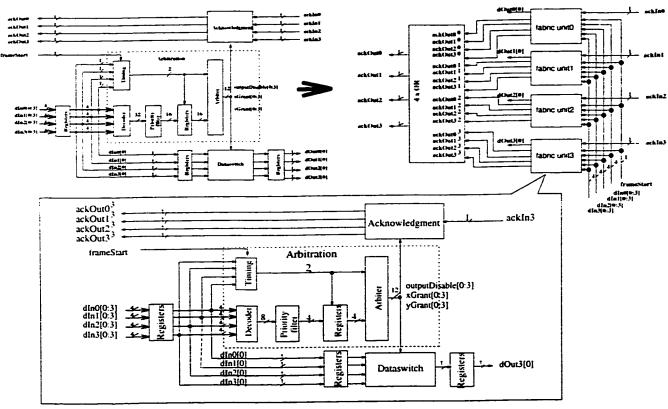

| Figure 3.7 The abstracted fabric units                                                         | 46             |

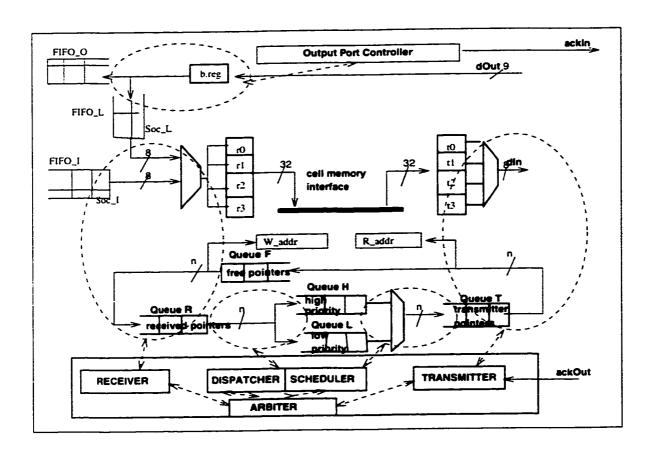

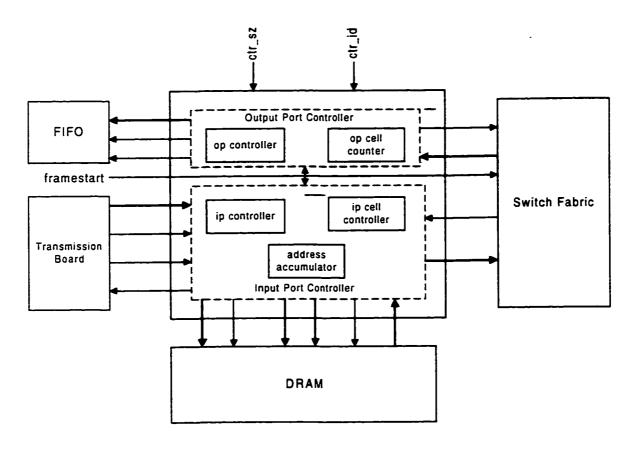

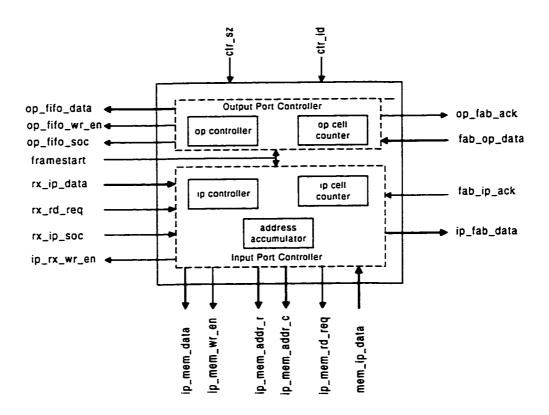

| Figure 3.8 Fairisle input and output port controller                                           | 51             |

| Figure 4.1 The structure of the null port controller                                           | 60             |

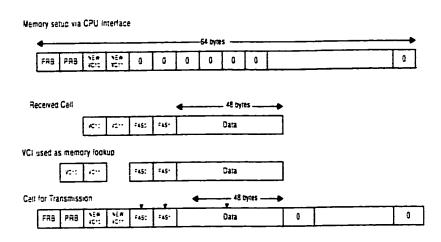

| Figure 4.2 The format of received cell and cell for transmission                               | 61             |

| Figure 4.3 The structure of the null port controller                                           |                |

| Figure 4.4 The state transition diagram in the environment of the null port controller         | 68             |

| Figure 4.5 Environment of the null port controller for Property 3 using EM                     | /U             |

| Figure 4.6 Environment of null port controller for the internal signals involved CTL           | / 3            |

| Figure 4.7 State diagram of the input port controller                                          | / /            |

| Figure 4.8 Environment of null port controller using counter reduction method                  | 0 L            |

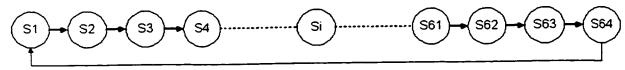

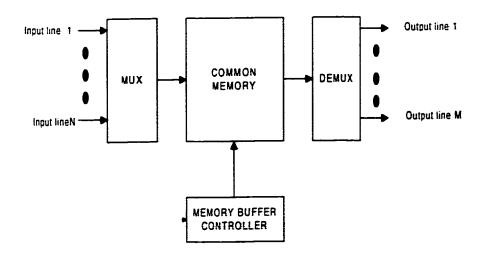

| Figure 5.1 Structure of RCMP-800.                                                              | 00             |

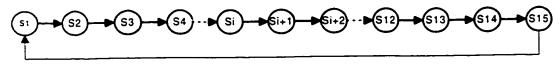

| Figure 5.2 Environment of the input FIFO                                                       | 91             |

| Figure 6.1 The modular structure of the switch fabric                                          | 100            |

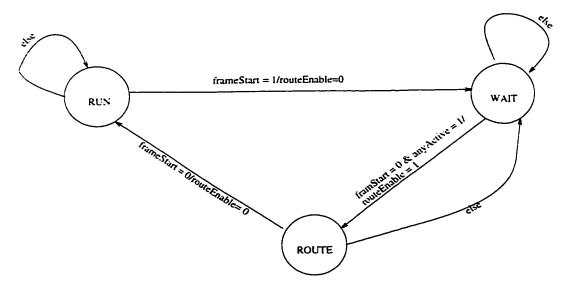

| Figure 6.2 State transitions of the timing module                                              | 101            |

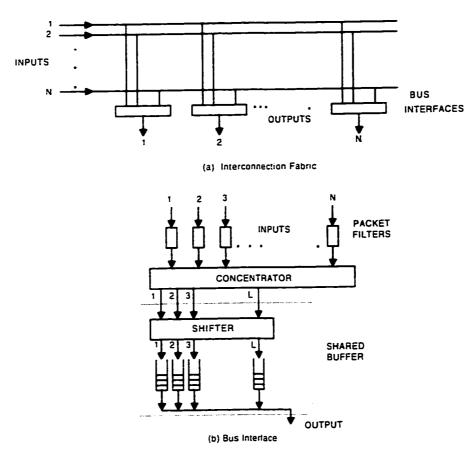

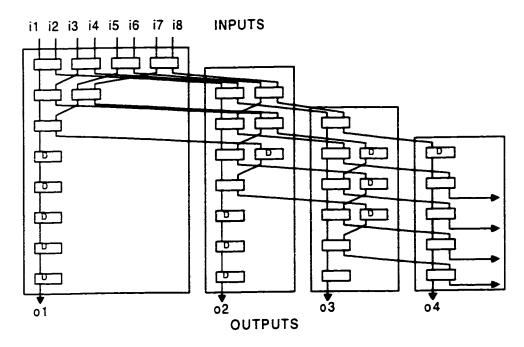

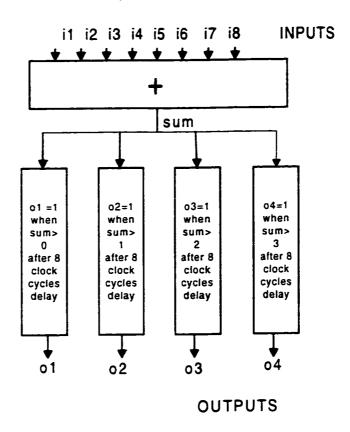

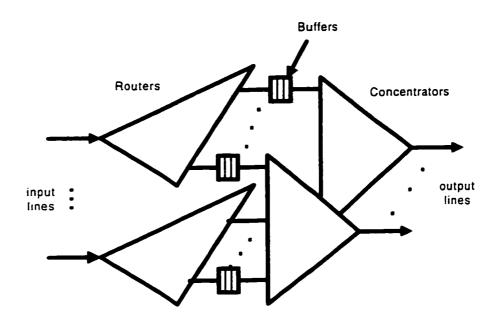

| Figure 6.3 Structure of Knockout ATM Switch                                                    | 107            |

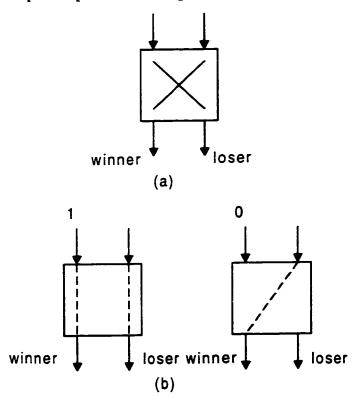

| Figure 6.4 (a) The 2 X 2 contention switch (b) State of a x 2 contention switch                | 100            |

| Figure 6.5 The 8-input / 4-output concentrator                                                 | 110            |

| Figure 6.6 The specification of the concentrator specification                                 | 110            |

|                                                                                                |                |

|                                                                                                | 122            |

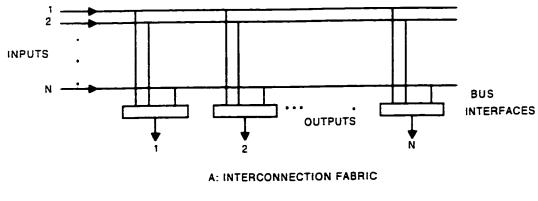

| Figure A.1 Structure of ATM Switch                                                             | 123            |

| Figure A.2 The structure of shared memory ATM switch                                           | 124            |

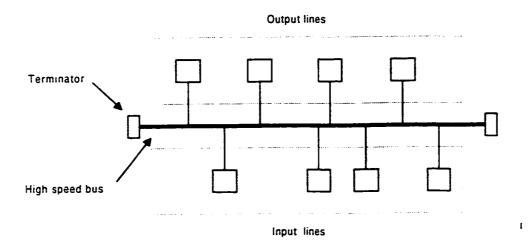

| Figure A.3 The structure of shared bus ATM switch                                              | 126            |

| Figure A.4 Common abstract ATM switch model                                                    | 120            |

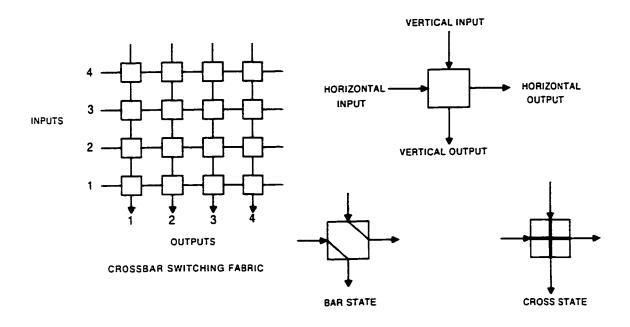

| Figure A.5 Structure of crossbar ATM switch                                                    | 120            |

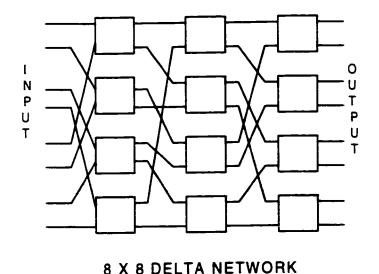

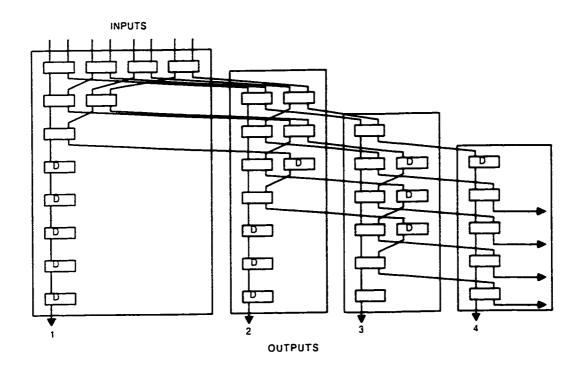

| Figure A.6 Structure of Banyan ATM switch                                                      | 133            |

| Figure A.7 Structure of knockout ATM switch                                                    | 122            |

| Figure A.8 Structure of Knockout concentrator                                                  | 125            |

| Figure B.9 Environment for property 3 using counter reduction and Environment Modification     | 130            |

| Figure B.10 Environment for Property 3 using Counter Reduction and Internal Signal Usage       | 133<br>ironmen |

| Figure B.11 Environment of null port controller for Property 4 using Counter Reduction and Env | 142            |

| [Vi( )                                                                                         | · <del>-</del> |

## **LIST OF TABLES**

| Table 3.1 Property checking on the abstracted fabric                           |            |

|--------------------------------------------------------------------------------|------------|

| Table 3.2 Dynamic ordering in property checking                                | <b>4</b> 4 |

| Table 3.3 Cascade property division in property checking                       | 45         |

| Table 3.4 Parallel property division in Property 4                             | 47         |

| Table 3.5 The number of latches among different models                         | 47         |

| Table 3.6 Latches reduction in model checking.                                 | 48         |

| Table 3.7 Summary of enhanced property checking of the fabric                  | 48         |

| Table 3.8 Error detection in property checking                                 | 49         |

| Table 4.1 VCI to memory location conversion                                    | 63         |

| Table 4.2 Experimental results and summary on the three methods                | 82         |

| Table 4.3 Experimental results on the model checking of null port controller   | 83         |

| Table 5.1 The format of an unassigned cell                                     | 94         |

| Table 5.2 The format of a physical cell                                        | 95         |

| Table 5.3 Experimental results of input FIFO model checking                    | 97         |

| Table 6.1 Equivalence checking of each submodule                               | 104        |

| Table 6.2 Equivalence checking among modules with different DMUX units         |            |

| Table 6.3 Error detection in equivalence checking of submodules                | 105        |

| Table 6.4 Experimental results of the equivalence checking on the concentrator | 11         |

# Chapter 1

## Introduction

With the increasing reliance of digital systems, design errors can cause serious failures, resulting in the loss of time, money, and long design cycle. Large amounts of effort are required to correct the error, especially when the error is discovered late in the design process. For these reasons, we need approaches that enable us to discover errors and validate designs as early as possible. Conventionally, simulation has been the main debugging technique. However, due to the increasing complexity of digital systems, it is becoming impossible to simulate large designs adequately. Therefore, there has been a recent surge of interest in formal verification. In formal verification, a mathematical model of the design is compared with a formal specification describing the correctness criteria for the design. The verification is exhaustive: all possible behaviors of the model are considered [2].

Most formal verification methods fall into one of two classes: theorem proving based methods and decision graph based methods.

### 1.1 Theorem proving based methods

In theorem proving based methods, the designer constructs a mathematics proof, perhaps with the aid of some automated support, to prove that the model meets its specification. Because the full power of mathematics is available, such techniques are very flexible and powerful. It is possible to model systems at almost any level of

detail, and to prove properties of entire classes of systems.

The theorem-proving methods have been around for over 35 years, and definitely have their staunch adherents. They have been extensively in government pilot projects, notably a popular theorem proving tool PVS [36] was used in NASA. HOL (Higher Order Logic) [19] which is another famous theorem proving tool was used in many research projects. Although there are many theorem proving tools in the world, they all prove the equivalence or implication between a specification and an implementation.

In spite of impressive demonstrations in the hardware domain and elsewhere, the theorem-proving methods have never achieved the broad level of acceptance for which their advocates had hoped. The reason undoubtedly lies in the need for expert users, and an application cycle which evolves generally slower than a normal product design cycle, so even just keeping up with the project development schedule is a problem.

### 1.2 Decision graph based methods

Decision graph based methods restrict the model to be finite-state and use state space search algorithms to automatically check if the specification is satisfied. Further, if the verification fails, then a counterexample trace can be produced to show the user why this is the case. The particular types of decision graph based methods that we will be considering are called *model checking* and *equivalence checking*.

### Model Checking

Model checking is an automatic technique for verifying finite-state reactive systems, such as sequential circuit designs and communication protocols. Specifications are expressed in a propositional temporal logic, and the reactive system is modeled as a state-transition graph. An efficient search procedure is used to determine automatically if the specifications are satisfied by the state-transition

graph. The technique was originally developed in 1981 by Clarke and Emerson [12]. Quielle and Sifakis [29] independently discovered a similar verification technique shortly after thereafter. An alternative approach based on showing inclusion between automata was later devised by Kurshan [20] at AT&T Bell Laboratory.

Model checking has several important advantages over mechanical theorem proving. The most important is that the procedure is highly automatic. Typically the user provides a high level representation of the model and the specification to be checked. The model checker will either terminate with the answer *true* indicating that the model satisfies the specification or give a counterexample execution that shows why the formula is not satisfied. The counterexamples are particularly important in finding subtle errors in complex reactive systems.

The first model checkers were able to find subtle errors in small circuits and protocols. However they were unable to handle very large examples due to the state explosion problem. The problem arises in systems composed of multiple state holding elements operating in parallel: the total number of states in the system generally grows exponentially with the number of state holding elements. Because of the limitation, many researchers in formal verification predicted that model checking would never be useful in practice.

The possibility of verifying systems with realistic complexity changed dramatically in the late 1980's with the discovery of how to represent transition relation using ordered binary decision diagram (OBDD) [6]. The original model checking algorithm, together with the new representation for transition relations, is called symbolic model checking [26]. By using the combination, it is possible to verify large reactive systems. In fact, some examples with more than 10 120 states have been verified [9]. This is possible because the number of nodes in the OBDDs that must be constructed no longer depends on the actual number of states or the size of the transition relation. Because of this breakthrough it is now possible to verify reactive systems with realistic complexity and a number of major companies including Intel, Motorola, Fujitsu, AT&T and Nortel have started using symbolic

model checkers to verify actual circuits and protocols. In several cases errors have been found that were missed by extensive simulation.

While symbolic representations have greatly increased the size of the system that can be verified, most realistic systems are still too large to be handled. Thus, it is important to find techniques that can be used in conjunction with the symbolic methods to extend the size of the systems that can be verified. Current well-known techniques are compositional reasoning and abstraction [23].

### Equivalence Checking

Equivalence checking is used to prove functional equivalence of two design representations modeled at different levels of abstraction [34]. Equivalence checking can be divided into two categories: one is combinational equivalence checking, and the other is sequential equivalence checking.

The main approaches to combinational equivalence checking are based on canonical representations of Boolean functions, typically binary decision diagram (BDDs) or their derivatives. The functions of the two circuits to be compared are converted into canonical forms [6] which are then structurally compared. The major advantage of BDDs is their efficiency for a wide variety of practically relevant combinational circuits. If the BDD size does not grow too large, this type of Boolean reasoning is fast and independent of the actual circuit structure. Moreover, if structural similarities of the two designs are exploited, BDDs can effectively find implications between nets even if they are farther away from the primary inputs.

Some commercial equivalence checking tools have been used in industries. For example, Chrysalis's equivalence checking tool Design Verifyer is being used in many IC design companies. Equivalence checking tools are often used to verify the equivalence between RTL and synthesized gate-level design. Also they are used to ensure the correctness of manual optimization during the fabrication process.

However, since current designs are mainly clock-driven synchronized, to perform the combinational equivalence checking between two different sequential

models, we have to divide a design into pieces, and map each register (or flip-flop) of one model into another, and compare their combinational circuits between every two consecutive registers. This will lead to a drawback: combinational equivalence checking cannot handle the equivalence checking between RTL and behavioral model because RTL model and behavioral model are developed separately and should have the same outputs at some certain clock cycles, but it is impossible to map each register in RTL model to that of behavioral one.

Sequential equivalence checking is to verify the equivalence between two sequential designs at each valid state. It is done by building the product finite state machine, and checking whether a state where the values of two corresponding outputs differ, can be reached from the set of initial states of the product machine. In other words, sequential equivalence checking only considers the behavior of two designs while ignoring their implementation detail such as latch mapping. Therefore, sequential equivalence is able to verify the equivalence between RTL and behavioral model. According to this, sequential equivalence checking is very useful in design verification, but its drawback is that it cannot handle a large design due to state space explosion problem.

## 1.3 Verification Interacting with Synthesis

Today, there are a lot of academic and commercial formal verification tools. One can purchase verification tools from Abstract Hardware Ltd. (CheckOff - core technology developed at Siemens), Chrysalis (Design Verifyer), Compass (Vformal-core technology developed at BULL), IBM (RuleBase-core technology developed at CMU), and Cadence (FormalCheck - core technology developed at Lecent). In addition to these, some universities develop their own academic verification tools. CMU has SMV [26], which is based on symbolic model checking. University of Montreal developed *Multiway Decision Graph* (MDG) [13], which supports property checking and equivalence checking. The most popular academic formal verification tool for both model checking and equivalence checking is Verification Interacting

with Synthesis (VIS) [5], which is developed by University of California, Berkeley.

VIS integrates the verification, simulation, and synthesis of finite-state hardware systems. It uses a Verilog front-end and supports model checking, combinational and sequential equivalence checking, cycle-based simulation, and hierarchical synthesis, etc. Because of these practical features, we choose VIS as the verification tool in this thesis. In the following, we give a brief description of VIS.

#### Verilog front-end

VIS operates on an intermediate format called BLIF-MV, which is an extension of BLIF, the intermediate format for logic synthesis accepted by SIS [33]. VIS includes a stand-alone compiler from Verilog to BLIF-MV, called VL2MV, which supports a synthesizable subset of Verilog. VL2MV extracts a set of interacting finite state machines that preserves the behavior of the source Verilog program defined in terms of simulated results. Two new features have been added to Verilog [35]:

- 1) Nondeterminism. A nondeterministic construct, \$ND, has been added to specify nondeterminism on wire variables; this is the only legal way to introduce nondeterminism in VIS.

- 2) Symbolic variables. Sometimes it is desirable to specify and examine the value of variables symbolically, rather than having to explicitly encode them. VL2MV extends Verilog to allow symbolic variables using an enumerated type mechanism similar to the one available in the C programming language.

### Hierarchy and initialization

When a BLIF-MV description is read into VIS, it is stored hierarchically as a tree of modules, which in turn consist of sub-modules. This hierarchy can be traversed in a manner similar to traversing directories in UNIX. Simulation and verification operations can be performed at any subtree of the hierarchy. It is possible to replace the subhierarchy rooted at the current node with a new hierarchy specified by a new BLIF-MV file, which might be a synthesized module or a manually

abstracted module. VIS can also output the hierarchy below the current node to a BLIF-MV file.

#### • Interaction with synthesis

VIS can interact with SIS to optimize the existing logic by reading and writing the BLIF format, which SIS recognizes. Synthesis can be performed on any node of the hierarchy.

#### • Symbolic model checking

VIS performs symbolic model checking under Büchi fairness constraints [4] which assumes that a system will fairly go to each possible transition state and cannot miss any possible states forever. VIS reports the failure with a counterexample, (i.e., behavior seen in the system that does not satisfy the property). This is called the "debug" trace. Debug traces list a set of states that are on a path to a fair cycle and fail the CTL formula.

#### Equivalence checking

VIS provides the capability to check the combinational equivalence of two designs. An important usage of combinational equivalence is to provide a sanity check when re-synthesizing portions of a network. VIS also provides the capability to test the sequential equivalence of two designs. Sequential verification is done by building the product finite state machine, and checking whether a state where the values of two corresponding outputs differ, can be reached from the set of initial states of the product machine. If this happens, a debug trace is provided. Both combinational and sequential equivalence verification are implemented using BDD-based routines.

#### Simulation

VIS also provides traditional design verification in the form of a cycle-based simulator that uses BDD techniques. Since VIS performs both formal verification and simulation using the same data structures, consistency between them is ensured. VIS can generate random input patterns or accept user-specified input patterns. Any

subtree of the specified hierarchy may be simulated.

#### Algorithms

The fundamental data structure for these algorithms is a multi-level network of latches and combinational gates that is created by flattening the hierarchy. It is assumed that there are no combinational cycles in the network.

The primary inputs and latch outputs are referred to as combinational inputs and the primary outputs and latch inputs are referred to as combinational outputs. The variables of a network are multi-valued, and logic functions over these variables are represented by multi-valued decision diagrams (MDDs) which are an extension of BDDs.

The combinational input variables and next state variables must be ordered before MDDs can be constructed. The combinational input variables are ordered by doing a depth-first traversal of the logic that generates the combinational outputs. The order in which the output logic cones are visited is determined using the algorithm of Aziz et al. [1]. This algorithm orders the latches to decrease a communication complexity bound (where backward edges are more expensive than forward edges) on the latch communication graph. The traversal of an output logic cone is done in such a way that the combinational inputs farthest from the outputs appear earlier in the ordering. Finally, each next state variable is inserted into the variable ordering immediately after the corresponding present state variable.

A good partial or total ordering on the variables can be read in to improve the performance. In addition, dynamic variable ordering is supported. Generally, a good initial ordering followed by one or two forced dynamic reorderings gives good results.

### 1.4 Formal Verification and Design Flow

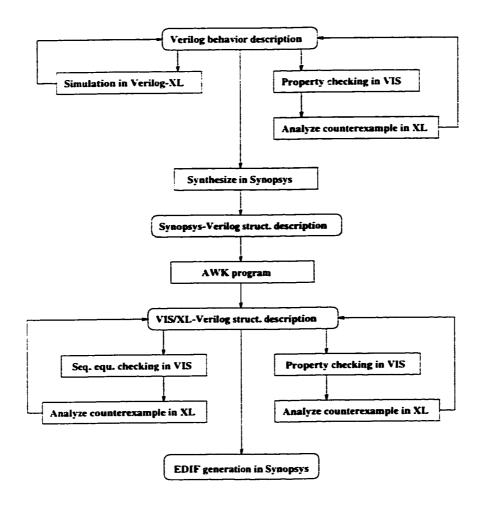

Formal verification can be automatically used in an top-down design phase. Figure 1.1 shows an example of employing formal verification in a digital design phase. In this example, an RTL design is first described in Verilog [35] hardware

design language, and then it is tested by a Verilog simulation tool (e.g. Cadence Verilog-XL). After that, model checking is further applied to verify the RTL design. Since model checking, which concentrates on logic relations, has a totally different mechanism from simulation, it could detect design errors which were not caught by simulation. The verified RTL design is synthesized into the gate-level netlist (referred to as Synopsys-Verilog in Figure 1.1) in Synopsys Design Compiler which is a synthesis tool. But the format of the structural description cannot be used directly in VIS or XL-simulator, and also the primitive modules of Synopsys are different from those of VIS and XL-simulator. A program in AWK [1] automatically translates the Synopsys-Verilog format to a Verilog format that is accepted by VIS and XLsimulator (referred to as VIS/XL-Verilog in Figure 1.1) and a file including the primitive modules of Synopsys is created so that VIS is interacted with Synopsys and XL simulator directly. In addition to simulation and model checking, equivalence checking between the RTL description and the synthesized netlist description of each submodule is employed. Equivalence checking ensures the correctness of synthesis with less human effort. An important advantage of formal verification using VIS is counterexample generation whenever equivalence or model checking fails. However, some counterexamples are difficult to analyze directly, but the counterexamples can be converted into Verilog-XL and analyzed graphically. There are some trivial differences between the syntaxes of VIS-Verilog and that of XL-simulator, but if a design is described by a subset of syntaxes which are accepted by both tools, the design description can be interacted by VIS and XL-simulator without any change.

Figure 1.1 Digital design flow using VIS

### 1.5 Scope of the Thesis

High-speed networks are being required for carrying all applications (voice, data, video and images) in an integrated fashion, and the most appropriate switching technique for such multimedia application is known as Asynchronous Transfer Model (ATM) [25]. Although ATM hardware is one of the most difficult designs, its formal verification examples are pitifully few. This thesis is concerned with methods for applying model checking and equivalence checking on the verification of ATM switches.

With the increasing intensive competition in ATM systems, time to market is becoming a more and more important issue in industries, so industries prefer to use decision graph based methods than theorem proving based methods. However, even if graph based formal verification tools are used, the overhead of using formal verification is still quite high. There are four major reasons to cause this problem.

- Many formal verification tools (especially academic formal verification tools) use some special hardware description languages instead of Verilog or VHDL [3] which are two hardware description language widely used in industry designs.

- 2. Due to the state space explosion problem, a design has to be abstracted in order to be verified.

- Graph based tools have the advantage of automatic proof, but most of them

must use propositional temporal logic to express properties. However, it is

very difficult to express a complicated property by propositional temporal

logic formulas directly.

- 4. Model checking can only be applied on a component without inputs. So if a component with inputs is under test, a closed environment [23], which defines the inputs, is mandatory. However, such environment is difficult to build due to the lack of rules and methods.

The thesis is aiming at the above four points. All the designs present in the thesis are described in Verilog. Using techniques introduced in the thesis, we were able to successfully verify them in VIS, and a number of design errors have been found during the verification process. Our experience proves that formal verification could be used in ATM switch designs with less overhead.

We discuss some general methods for the verification of ATM switches. Based on these methods, several different ATM switches are verified. The goal of these methods is to avoid the state explosion problem. As to model checking, we apply abstraction, reduction and compositional reasoning methods, and propose a method called *Property Division* in order to capture the property of a large system. In addition, we introduce our methods on establishing environments and describing properties in propositional temporal logic formulas. In terms of equivalence checking,

we adopt modular verification to verify the equivalence between a RTL design and a netlist design.

The principle contributions of this thesis are as follows:

- 1. A method for constructing environments of ATM switches using compositional reasoning, and modeling ATM switches by reduction and abstraction.

- 2. A method for capturing the properties of a large system and enhancing model checking.

- 3. Methods for describing properties using CTL[10].

- 4. Model checking of Fairisle ATM switch fabric, Fairisle ATM null port controller, and further verify the entire Fairisle ATM switch by property division; model checking of a commercial design block: Input FIFO of RCMP-800.

- 5. Equivalence checking of Fairisle ATM switch fabric and Knockout ATM switch concentrator.

#### 1.6 Related Work

During recent years, some ATM switches were verified by various formal methods, and those ATM switches were either from academic designs or abstracted from commercial designs. The following is ATM formal verification examples we found in the literature.

### • Verification of Fairisle ATM switch fabric in HOL

P. Curzon [14] formally verified Fairisle ATM switch fabric [14] using HOL [19]. HOL is an LCF style proof system based on higher-order logic. The verification was structured hierarchically following the implementation's module structure. The hierarchical, modular nature of the proof facilitated the management of its complexity. The structural and behavioral specifications of each module were given

as relations in higher-order logic [19]. The major advantages of the verification of the switch fabric in HOL are: the excellent expressivity of the specification language; the confidence afforded in its results and the potential for scalability. However, the verification in HOL required expertise and lots of efforts on circuit interpretation.

## Verification of Fairisle ATM switch fabric in MDG

Tahar et al. [37] [38] verified the Fairisle ATM switch fabric in an automatic fashion using the MDG (*Multiway Decision Graphs*) [13] by property checking and equivalence checking. MDG is used to represent sets of states as well as the transition and output relations. Based on a new technique called *abstract implicit enumeration* [13], the MDG tools are able to perform safety property checking, combinational and sequential equivalence checking. The verification in MDG has the advantage of using abstract data types and un-interpreted functions with a rewriting facility, hence allowing larger circuits to be verified. However, the current MDG tools are using a special hardware design language (MDG-HDL) which need interpretation if we verify an industry design.

## Verification of a Commercial ATM switch in SMV

Chen et al. [8] at Fujitsu Digital Technology Ltd, identified a design error in an ATM circuit using the tool SMV (Symbolic Model Verifier) [26] by verifying some properties expressed in CTL. Actually, the error was found during the chip testing process. Aiming at the specific test error, they established an ATM model by the abstraction and reduction of their original design. Using model checking in SMV, a design error was identified in the ATM model. However, the ATM model was reduced and abstracted a lot from the original design according to the specific error, and the same ATM model may not be used to verify other properties of the original design.

## High-Level Design and Validation of ATM Switch

Rajan et al. [30] used a combination of theorem proving [19], model checking and simulation to verify a high-level ATM model. They used model checking to verify some control components in the ATM model, and applied exhaustive simulation to verify some operational components. Then theorem proving was applied to verify the whole ATM switch model. They discovered bugs in the high-level ATM model which was presumed correct by simulation. Combination of various formal verification methods is a trend in the formal hardware verification, but such a high-level model ignored a lot of details of a real design. In addition, since theorem proving was involved in the verification, the expertise in theorem proving was required.

## Verification of Fairisle ATM Switching Fabric in MEPHISTO

Schneider et. al [33] formally verified Fairisle ATM switch fabric using the verification system MEPHISTO which is based on the HOL theorem prover. They described the structure of each of the modules used in the design hierarchically and provided their behavioral specification using hardware formulas. Although they automated the verification of lower-level hardware submodules, they have not accomplished the complete verification of the implementation against the intended overall behavior of the switch fabric.

## Verification of Fairisle ATM Switching Fabric using HSIS

Gracez [18] has also verified some properties on the implementation of fabric using the HSIS model checking tool. The author described the netlist implementation of the ATM switch fabric using a subset of Verilog, and checked properties on submodules of the fabric using model checking. No model checking on the whole switch fabric, nor a verification against a high-level specification was reported, however. Moreover, in some cases a slightly different implementation of a module

was described in order to ease the verification.

The above ATM formal verification examples demonstrate that some simple ATM switches can be verified by formal verification methods. However, these methods either use their own hardware design language or require a large changes from the original designs, so the overall overhead are pretty large. In this thesis, we will use Verilog hardware design language to describe the design. Using the methods introduced in the thesis, we are able to verify the ATM switches with relatively small modifications on the original designs.

# Chapter 2

# **Model Checking Methodology**

In this chapter, we consider the model checking methodology of ATM switches. We will exploit a number of verification methods into the model checking of ATM switches. These methods include compositional verification, property division, abstraction and reduction, and they are jointly applied in the verification of ATM switches. Compositional reasoning gives the theory fundamental for the establishment of environments. Property division methods, which are jointly adopted with compositional reasoning, facilitates capturing properties of a large design model. Reduction and abstraction dramatically decrease the complexity of an ATM switch model without changing the relations of target signals.

Using the above methods, we have to build up an environment and express a property in temporal logic formulas (i.e. CTL). So we also introduce our methods on establishing an environment and representing a property in CTL.

## 2.1 Compositional Verification

The idea behind compositional reasoning is to exploit the natural decomposition of a system into communicating parallel processes. We will try to verify properties of individual components, infer that these properties hold in the complete system, and use them to deduce additional properties. The second step, inferring that local

properties hold on the complete system, is the key requirement for compositional verification. Thus, we wish to examine the compositional model checking problem: how do we check that a specification is true of all systems that can be built using a given component? The theorems which support full CTL compositional model checking are very hard to develop [23]. But as for ACTL, a subset of CTL, the problem is efficiently decidable.

#### 2.1.1 CTL and ACTL

Temporal logic is a logic for expressing the relative ordering of events in time without mentioning time explicitly. CTL is a well-known temporal logic used in model checking. All temporal operators in CTL are interpreted relative to an implicit "current state", and each operator consists of two parts. The first is called a path quantifier and is either A or E. A denotes that something should be true of all "paths" starting at a current state. In contrast, E is used to specify the existence of a path with a certain property. The second part of a temporal operator is either X, U, or V. These are used to describe the ordering of events along the path or paths indicated by the A or E. The intuitive meanings of X, U and V are as follows:

- 1. Xp: X is read as "next time". Xp is true of a path if the formula p is true at the second state on the path. Thus, p is used to express properties about the immediate successors of the current state.

- 2. q U p: U is the "until" operator. The formula expresses that q is true until a point where p is true. Thus, A(true U p) indicates that p will be true in any paths in the future. A(true U p) also can be expressed as "AFp" where "F" means "future". Similarly, E(true U p) can be expressed as EFp.

- 3. q V p: The V operator is the dual of U and is read as "release". A path satisfies q V p if p is true at the current state, and p remains true up to and including the first point where q is true. There is no requirement that q ever becomes true, but when it does, it "releases" the requirement that p be true. A(false V)

p) means that p never releases in any path, so it has the same meaning as AGp where G is intended to express invariance. Similarly,  $E(\text{false }V\ p)$  has the same meaning as  $EG\ p$ .

Let us now consider some example CTL formulas and their intuitive meanings.

- 1.  $AG(req=1 \rightarrow AF \ ack=1)$ : This formula states that for all reachable state(AG), if the state satisfies req = I ("a request is made"), then at some later point (AF) we must encounter a state with ack=1 ("an acknowledgment is received"). Note that AF is interpreted relative to the state where req = I. The outer AG is interpreted starting with the initial states of the system.

- 2. AG AF enabled = 1: No matter what state we reach, at some later pointer we must encounter a state where enabled is 1, then we must reach yet another such state. In other words, enabled must be 1 infinitely often.

- 3. AG EF restart =1: For any reachable state, there must exist a path starting at that state that leads to a state satisfying restart=1. It must always be possible to "restart the system".

ACTL is a subset of CTL, which eliminates the ability to represent the existence of a path, i.e., the *E* path quantifier, and this subset is sufficiently expressive to cover almost all of the temporal formulas that are used as specification in practice. Intuitively, this is because we generally want to require that a system *must* behave correctly, rather than it *may* behave correctly.

### 2.1.2 Compositional Reasoning

In order to avoid state space explosion problem, compositional reasoning method [23] was proposed. It exploits the natural decomposition of a system. By using composition reasoning method, we verify components in the system with their environments, rather than a whole system. To show that the properties which are valid in individual components with the environment are still hold in the entire system, Long [23] has formally proved that "if the other components in the system

guarantee the behavior of the environment, then the verified properties are true of the entire system". This is the assume-guarantee style of verification [28].

The assume-guarantee style of verification was first advocated in the context of temporal logic by Pnueli [28]. In Pnueli's system, we work with triple of the form  $\langle g \rangle M \langle f \rangle$ . The most common reading of such a triple is "if the environment of M satisfies g, then M in this environment satisfies f". A typical chain of reasoning would be as follows:

$$\begin{array}{c}

\langle\rangle N \langle g\rangle \\

\langle g\rangle M \langle f\rangle

\end{array}$$

$$\begin{array}{c}

\langle\rangle M \parallel N \langle f\rangle

\end{array}$$

Equation 2.1 Assume-guarantee style of verification

Here, we are asserting that if:

- 1. N satisfies g: and

- 2. if the environment of M satisfies g, then M satisfies f

then the composition of M and N (i.e.  $M \parallel N$ ) will satisfy f. The advantage of doing the verification in this manner is that we never have to examine the composite state space of  $M \parallel N$ . Instead, we check g using just N, and then check f using only M and the assumption g which is an environment of M (i.e. N').

Based on the above compositional reasoning method, we establish an environment of M (i.e. N') which satisfies temporal formulas g, and check the property f on the module M with N'. If the property f is satisfied by  $M \parallel N'$ , we can conclude that  $M \parallel N$  satisfies f. Since N' is much smaller than N, the state space of  $M \parallel N'$  is much less than that of  $M \parallel N$ . By this method, model checking can handle much larger circuits. However, Long [23] has proved that such compositional reasoning method is only applicable in a ACTL.

Once the logic can only represent behavior over all paths, we will just need to consider a single "maximal" closing environment [23]. Although composing with any other closing environment will eliminate some paths, since our formulas only express behavior overall paths, such pruning will not change a formula from true to false.

Further, if the composition of the given component with its maximal closing environment satisfies the specified formula, then the formula obviously must be true of all closed systems containing the component. We will use an example to further illustrate this in Section 2.2.

#### 2.2 Environment

Using model checking, a verification target must be a structure which has no inputs [23]. So when we verify a design which has a number of inputs, we must build up an environment to define each input signal. Because there is no input in the environment, we call it closing environment. In [23], Long introduced maximum closing environment in model checking, however we do find some drawbacks on maximum closing environment. We will use an example to illustrate its drawbacks first, and then introduce an actual closing environment which is more closed to the real environment circuit than an maximum closing environment, and further explain how to implement an actual environment.

A real environment for a circuit M is components associated with M in the original system, denoted as N. The maximal closing environment for a circuit M, denoted E(N) is defined as follows:

- 1. S' = F, where F is the set of all labeling functions over  $A_i$ .

- 2.  $\Gamma = F$ .

- 3.  $A'_1 = \Phi$ .

- 4.  $A'_{0} = A_{I}$ .

- 5.  $R'(s_0', f', s_i')$  is identically true.

- 6. L'(f, a) = f(a)

S is set of states; I is a nonempty set of initial state.  $A_I$  is a set of input state components, and each element a of  $A_I$  has a correspondent domain  $D_a$  of possible values.  $A_O$  is a set of output state components, and each element a of  $A_O$  has a corresponding domain  $D_a$  of possible values. R is a transition relation relating a starting state in S, a labeling function over  $A_I$ , and a ending state in S. For every  $S_O \in S$  and labeling function S over S, there must exist some S is a set of input state of input state.

is a function that takes a state component a and return an element of  $D_a$ .

In the above definition, the symbols with "'" mean the symbols of E(N), and symbols without "'" means the symbols for M.

According to the above definition, the states of a maximum environment is the set of all labeling functions over  $A_I$  while the states of a real environment is the subset of all labeling functions over  $A_I$ . That means that if the composition of the circuit M and its maximum environment E(N) (denoted as  $M \parallel E(N)$ ) is satisfied by an ACTL property, and the property must be valid for the composition of the circuit M and its real environment N (denoted as  $M \parallel N$ ). We will use the following example to illustrate this, and the example was also used in [23].

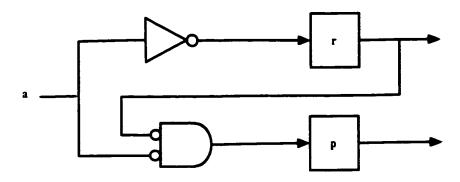

Figure 2.1 A handshake circuit

Figure 2.2 Environment of the circuit of Figure 2.1

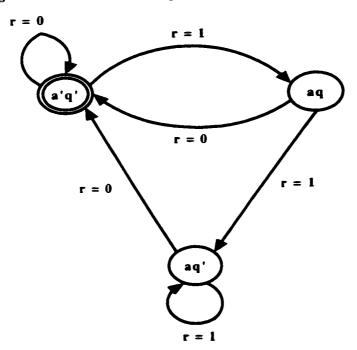

Figure 2.3 State transition diagram for the circuit of Figure 2.1

Figure 2.4 State transition diagram for the circuit of Figure 2.2

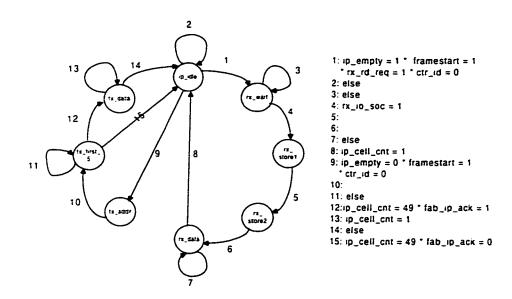

Consider a process that communicates with its environment via a 4-phase handshaking protocol. The process can make requests of the environment by setting one of its visible state component r to 1. The environment responds this request by setting the visible state component a to 1. When the process sees the

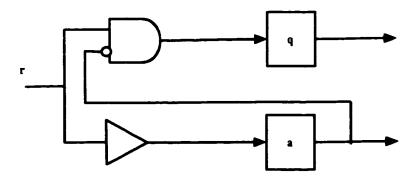

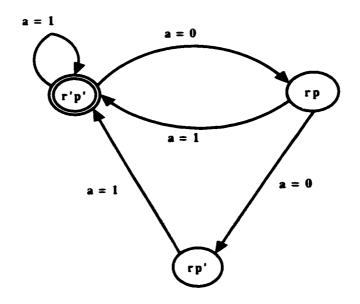

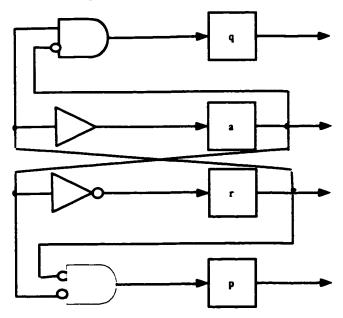

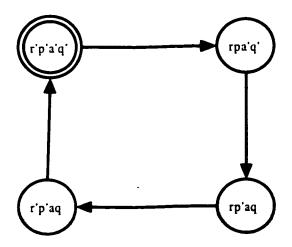

acknowledgment, it removes its request by setting r to 0. Then after the environment sets a back to 0, the cycle repeats. The process will also have a state component p that will set to 1 when it first makes request. The state transition diagram corresponding to this process is shown in Figure 2.3, and the actual circuit is Figure 2.1. In Figure 2.3 and other state transition diagrams in Chapter 2, the double circle indicates an initial state, conditions on arcs are used to give the input conditions under which the transition can be taken, and "," denotes logic "NOT". The circuit shown in Figure 2.2 is a possible environment for the circuit of Figure 2.1. It receives requests via the input r and gives acknowledgments using the output a. It also has an output a that becomes 1 when it first produces an acknowledgment. When we compose the two circuits, the output a of Figure 2.1 is tied to the input a of Figure 2.2. Similarly, the output a of Figure 2.2 drives the input a of Figure 2.1. The overall circuit is shown in Figure 2.5. Figure 2.4 and Figure 2.6 are the state transition diagrams for Figure 2.2 and Figure 2.5, respectively.

Figure 2.5 Composed circuit

Figure 2.6 State transition diagram representing the composite circuit

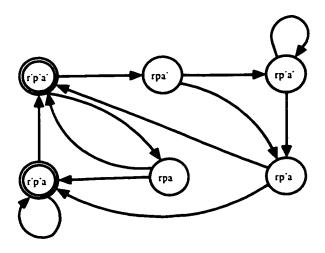

According to the above definition of a maximum environment, the maximal closing environment of Figure 2.3 can be expressed as Figure 2.7. (Here we use state transition diagram of Figure 2.1 (Figure 2.3) to represent the circuit of Figure 2.1 because they are functionally equivalent) In Figure 2.7, a is either "0" or "1", and it can be expressed as a nondeterministic variable in some formal verification tools. If we consider Figure 2.1 and Figure 2.7 as a circuit M and its maximum environment E(N),  $M \parallel E(N)$  can be obtained from Figure 2.3 by considering the states when a is '1' and '0'. Figure 2.8 is the state transition diagram of  $M \parallel E(N)$ . Figure 2.2 is a real closing environment of M (i.e. N), and Figure 2.5 can be expressed as  $M \parallel N$ . Comparing Figure 2.6 and Figure 2.8 for each state in  $M \parallel N$ , we can obtain a corresponding state in  $M \parallel E(N)$  by dropping the labeling for the state component q. As an example, the state  $r \cdot p \cdot a \cdot q \cdot q \cdot in M \parallel N \cdot in M \cdot$

Figure 2.7 The maximal closing environment for the structure of Figure 2.3

Figure 2.8 The composition of the structure Figure 2.3 and its maximal closing environment

In essence, the state transition of  $M \parallel N$  can be embedded in that of  $M \parallel E(N)$ . Now consider a formula of ACTL which describes properties of all paths from a state. If such a formula is false at some states in  $M \parallel N$ , then we can find a path demonstrating why it is false. This path is then mapped into a corresponding path in  $M \parallel E(N)$ , so we can prove that this path demonstrates that the corresponding state in  $M \parallel E(N)$  does not satisfy the property either. If we verify that a formula is true for  $M \parallel E(N)$ , then we know that the formula holds in all closed systems that contain M. Further, if the formula is false for  $M \parallel E(N)$ , then obviously we could find a closed system containing M for which the formula is false. Therefore, to prove a property is valid on  $M \parallel N$ , we can deduce it by proving the property is valid on  $M \parallel E(N)$ .

But, if a property is false for  $M \parallel E(N)$ , it may be true for  $M \parallel N$  because every state of N can be mapped in E(N) while each state of E(N) may not be mapped into N. To explain this, we still use the example of subsection 2.2.1. Figure 2.6 is the state transition diagram of the circuit Figure 2.5 which can be seen as the composition of Figure 2.1 and Figure 2.2. If the circuits Figure 2.1 and Figure 2.2 are considered to be M and N, respectively, Figure 2.5 can be expressed as  $M \parallel N$ . Figure 2.7 is an maximum environment of M (i.e. E(N)), and  $M \parallel E(N)$  is represented as Figure 2.8. In Figure 2.6 (i.e.  $M \parallel N$ ), it has the property that the next state of rpa'q' will always be rp'aq, but this property is no longer satisfied in  $(M \parallel E(N))$  because

the next state of rpa' can be rp'a' or rp'a (Figure 2.8). Therefore, a maximum closing environment is not the best environment in model checking.

In order to make the verification accurate, a environment which uses the same variables as the maximum environment and expresses its original model as much as possible is the best one. So we propose to use actual closing environment which defines some inputs as the original behaviors and some inputs as nondeterministic variables. In reality, some input signals behave in a simple manner, then we can specify its behavior in the environment. For instance, in some ATM switches, there is "framestart" signal which can synchronize the cell transmission, and it strobes cyclically in a certain period. So we can define this signal as its real behavior in the environment. However, some input signals have a complicated behavior, and expressing it as its original model will increase the state space dramatically. For this case, we can leave these signals as nondeterministic variables. And also, data path signals could be defined as non-deterministic variables. The following chapters include some actual environment implementations.

Since it is possible that a nondeterministic variable holds one value all the time, the behavior with other values will never come out. Therefore, we sometimes need to give fairness constraint [4] to prevent a nondeterministic variable sticking on a certain value.

## 2.3 Property Division

To capture the whole behavior of a system, we usually need to verify some global properties. However, the global properties are difficult to be verified due to state space explosion. Therefore, we propose property division techniques which subdivide a property to several sub-properties and check each sub-property in its correspondent submodule separately. According to the dependencies of subproperties, we classify property division into cascade property division and parallel property division.

## 2.3.1 Cascade Property Division

Cascade property division divides a property into several sequentially related sub-properties, and every consecutive sub-properties are related with each other.

To illustrate this, we use a simple example. Consider a target system S(M | I | N) which consist of submodule M and N. M and N are sequentially related. If we want to verify a property P of S, we can divide P into two subproperties PI and P2 which are expected to be valid in M and N, respectively. If submodule M and the environment of M (i.e. N) satisfies P1 and submodule N and the environment of N (i.e. M) satisfies P2, we can conclude that the target system S satisfies P. The proof strategy can also be expressed as an inference rule:

\langle true \rangle M || N' \langle P1 \rangle \rangle (P2) \\ \langle true \rangle P1 || P2 \langle P \rangle \rangle M || N = S \\

\tag{true} S < P >

Equation 2.2 The proof of cascade property division

The above formula is similar to that in Section 2.1. Actually, cascade property division is based on compositional reasoning. In Equation 2.2, the proof strategy for  $\langle true \rangle M \parallel N' \langle P1 \rangle$  and  $\langle true \rangle N \parallel M' \langle P2 \rangle$  are exactly the same as Equation 2.1. The proof of Equation 2.2 is straightforward. By compositional reasoning, if  $M \parallel N'$  satisfies P1, then  $M \parallel N$  satisfies P1. Similarly, if  $M' \parallel N$  satisfies P2, then  $M \parallel N$  satisfies P2. These two important assumption make the above proof valid.

Since cascade property division is based on compositional reasoning, it works only for ACTL property. The following lists a set of typical properties which can be used in cascade property division.

• Safety Property:

IF

$$\mathbf{AG}$$

(P ->  $\mathbf{AX}^{n}$  Q) and  $\mathbf{AG}$  (Q ->  $\mathbf{AX}^{m}$  R)

THEN  $\mathbf{AG}$ (P ->  $\mathbf{AX}^{m+n}$ R)

where  $\mathbf{AX}^{n}$  Q is an abbreviation for

#### AX AX AX ...AX AX AX Q

Liveness Property:

IF

$$AG (P \rightarrow AF Q)$$

and  $AG(Q \rightarrow AF (or AX^n)R)$

THEN  $AG(P \rightarrow AF R)$

IF

$$AG (P \rightarrow AF (or AX^n) Q)$$

and  $AG (Q \rightarrow AF R)$

THEN  $AG (P \rightarrow AF R)$

The proof of above equations is based on the following three theorems, and we do not give the detail proof here.

- 1. IF  $P \rightarrow Q$  and  $Q \rightarrow R$ , THEN  $P \rightarrow Q$

- 2.  $AX^n AX^m R = AX^{n+m} R$

- 3.  $(AX^n \text{ or } AF) AF R = AF R$

The cascade property division is quite useful in the verification of an ATM switches. In any ATM switches, ATM cells carry ATM headers through a switch, and a switch processes the headers and transmit ATM cells to their destined output ports. So if we track the ATM cells through an ATM switch, it is possible to get proper break points where the properties could be appropriately divided. However, using cascade property division, the target design cannot be seen as a black box. How to divide a property depends on the understanding of a design. Sections 3.6 and 3.4.1 will give real examples of cascade property division.

## 2.3.2 Parallel Property Division

While cascade property division divides a property into sequentially related sub-

properties. parallel property division divides a property into several independent subproperties, and checks every sub-property by every correspondent reduced submodule that is extracted from a design.

The idea behind parallel property division is to remove the redundant structure of a design and perform model checking only on the property-related circuits. By proper partition, a design may be divided into several design units while keeping the functional equivalence with the original design. Each design unit could have some inputs of the original design, but it cannot share outputs with the other one. Also design units ought not to have any interactive signals among them. If one global property can be separated to several independent sub-properties, each sub-property may be checked in a certain design unit. Since a design unit is much smaller than the whole design, state space is saved.

Here is a virtual example of parallel property division. Consider a closed system S: (1) S is functionally equivalent to the combination of n submodules ( $M_1$  ||  $M_2$  || ... ||  $M_n$ ). (2) The submodules have some or entire inputs of S, but they are independent. That means that they have different outputs and have no interactive signals with each other. We intend to check the property ( $I \rightarrow O_1$  and  $O_2$  and ... and  $O_n$ ) which might not be verified directly due to the large state space, then if we check each sub-property (step 1 to step 4 in Equation 2.3), we can conclude that step 5 is valid. In Equation 2.3, "I" represents inputs expression, and " $O_i$ " (i=1, 2, ..., n) denotes different outputs expression. " $I\rightarrow O_i$ " means the property which "I" implies " $O_i$ ".

- 1. IF  $M_l$  satisfies the property  $(l \rightarrow O_l)$ ; and

- 2. IF  $M_2$  satisfies the property  $(I -> O_2)$ ; and

- 3. ..., and

- 4. IF  $M_n$  satisfies the property  $(I -> O_n)$

- 5. THEN S satisfies Property  $(I \rightarrow O_1 \text{ and } O_2 \text{ and } ... \text{ and } O_n)$

Equation 2.3 A virtual example of parallel property division

The proof of Equation 2.3 is based on the following two theorems, and we do not give the detailed proof here.

- 1. If a property is satisfied by its related circuits of a system, the property will be also valid in the system.

- 2. If  $(I \rightarrow Q1)$  and  $(I \rightarrow Q2)$ , THEN  $I \rightarrow Q1$  and Q2

Since most of ATM switches are regular designs, we could divide an ATM switch into several parts, and check each sub-property in a certain design unit. In addition, as an ATM switch, any input ports can be routed to every output port, and every output ports are relatively independent, so an *n-output* ATM switch may be divided into *n* switch units. The actual example is shown in Section 3.4.2. Furthermore, the idea of parallel property division could also be used to "hide" property-unrelated circuits when verifying a property, and Chapter 5 uses the "hide" method to verify some properties of RCMP-800 Input FIFO.

## 2.4 Property Expression

As well known, higher level language has better expressivity. For instance, C language has better expressivity than assembly language. Among logic languages, such rule is still valid. Higher Order Logic [19] have much better representation ability than CTL which belong to temporal propositional logic. Although CTL model checking has an automatic fashion, its poor expressivity really restricts the application. To ease expressing a property in CTL, we summarize three methods: Environment Modification, Internal Signal Usage and Counter Reduction.

#### • Environment Modification

A property consists of two parts: assumptions and conclusions. However, if several assumptions do not happen at the same state, it is impossible to express them in a CTL formula. In this case, we could use the environment to express one or more assumptions. We call this method Environment Modification. Environment Modification is really able to express a lot of properties, but the overhead is that we

have to modify the environment for each property.

#### • Internal Signal Usage

A property is a logic relation between the inputs and outputs of a component. If the property is impossible to be represented by the inputs and outputs in CTL directly, we could use "Internal Signals" to express a number of sub-properties in CTL. After these sub-properties are verified, the property could be deduced from these sub-properties by property division. This method is called "Internal Signal Usage". Internal Signal Usage can be used to express any kind of properties, but the verifier must be very clear about the design to choose appropriate internal signals in CTL formulas.

#### • Counter Reduction

Counters are often used to synchronize various behaviors inside the system, and the scale of counters directly affect the possible states of the system. Needless to say, counter reduction will dramatically reduce the CPU time during model checking. In Environment Modification method, the number of CTL formulas for a property sometimes is a proportional to the scale of the counters. By using Counter Reduction and Environment Modification, we could write much less CTL formulas to represent a property. Also in Internal Signal Usage method, the scale of counters sometimes has an influence on the number of CTL formulas for a property which is related to the counter. So Internal Signal Usage method also can get benefits from Counter Reduction.

While Environment Modification and Internal Signal Usage are two methods on expressing a property in CTL, Counter Reduction reduces the number of CTL formulas for a property when it combines with either Environment Modification or Internal Signal Usage method. The practical examples on how to apply the three methods will be demonstrated in Chapter 4.

## 2.5 Reduction and Abstraction

An ATM switch consists of memory, control circuits and data-path circuits. In simulation, we usually build up a memory model and simulate the whole system. However, we could not use such memory model in either model checking or equivalence checking because the memory will introduce a lot of states. Instead, we often do reduction and abstraction on a system in order to perform model checking and equivalence checking on it.

Because the advantage of model checking is to verify a control circuit with a lot of interactive signals, we usually perform reduction and abstraction on the memory and datapath. In some cases, we need to reduce the scale of control circuit as well. For example, we often reduce the scale of a cell counter in an ATM switch control circuit.

Memory is a kind of state holding element. It is impossible to verify memories by model checking because the state space increases exponentially with the capacity of a memories. For example, for 1000 byte memories, there will be 2 8000 states while the largest example that model checking can handle is around 2<sup>120</sup> states. To verify a system with memory, we usually take memories away from the system and only verify the memory read / write address, the memory data bus and read / write enable signals. In Chapter 4, we use Fairisle ATM null port controller as an example to illustrate how to use the memory peripheral signals to verify the correct memory access. Likewise, when verifying the FIFO in Chapter 5, we only check the FIFO read and write in its control circuits. This reduction is reasonable because the target of function verification is logic circuits instead of memories which are usually regular and verified by other ways.

Another component which is often reduced or abstracted is datapath circuits. Datapath circuits usually have wide data buses and operational circuitry, these circuits are not very complicated but they did occupy a lot of state space in the verification. For this reason, we usually do reduction and abstraction on it. Reduction is often used in the data bus. For example, we could reduce the data bus from 8 bits to

I bit as we will show in Chapter 3. On the other hand, for the operational circuits, we often use abstraction. For example, we can use three registers (a, b, c) to replace an adder (a + b = c) [23]. When register a and b have a value, (a+b) value is updated in register c. Instead of verifying a system with the adder, we only verify the system with three registers, so the state space can be decreased.

Although reduction and abstraction are very powerful methods in model checking and equivalence checking, it is not a good solution for the practical verification because it needs to modify a design. Even if we have to use them, we must try to modify our design as little as possible. A good coding style will make some reduction and abstraction easier. For example, if we define the width of a data bus as a constant variable. We can only re-define the constant variable to change the data bus width.

In this following three chapters, we apply the above model checking techniques on ATM hardware verification. In Chapter 3, we will introduce our experience on the model checking of Fairisle ATM switch fabric, and we will also adopt property division to enhance model checking and verify the entire Fairisle ATM switch which consists Fairisle ATM switch fabric and Fairisle ATM port controller model. In Chapter 4, we will illustrate three CTL property expression methods by verifying Fairisle ATM switch null port controller. A commercial ATM design block will be verified in Chapter 5 by using "hide" method, and we demonstrate that it is practical to verify an ATM commercial block using model checking.

There are a lot of CTL formulas in this thesis. The numbering of CTL formulas follows this rule: the first digit denotes the chapter number, and second digit means property number, and the last digit indicates the number of CTL formulas for a certain property. For instance, (3.3.2) means the second CTL formula of Property 3 in Chapter 3. Beside the above numbering rules, we use a, b and c to indicate Environment Modification, Internal Signal Usage and Counter Reduction, respectively in Chapter 4. For example, (4.3.a.1) means the first CTL formula of

Property 3 using Environment Modification in Chapter 4. In addition, in all the CTL formulas of the thesis. "!". "->". "\*", "+" and "^"denote logical "not". "imply". "and". "or" and "xor", respectively.

# Chapter 3

## **Verification of Fairisle ATM Switch**

In this chapter, we present our results of formally verifying an ATM switch fabric using VIS. By this example, we show how to use model checking to verify a design. In addition, we introduce how to apply property division to enhance the model checking and further verify an entire ATM switch by property division.

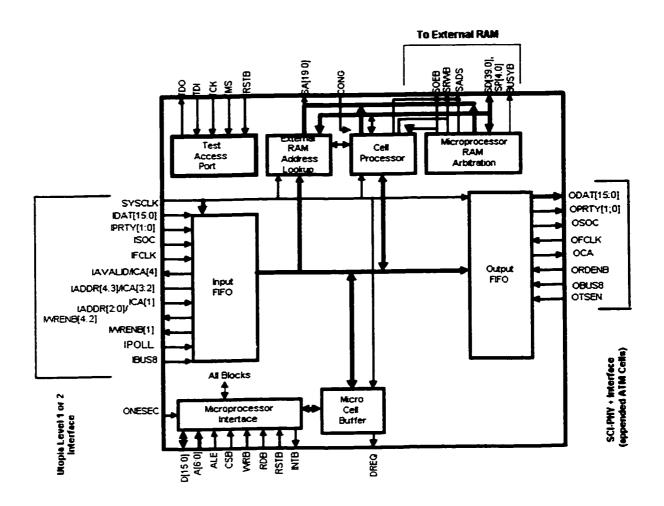

The device we investigated is a part of a network which carries real user data: the Fairisle ATM network, designed and in use at the Computer Laboratory of the University of Cambridge. The component we considered is the Fairisle 4 by 4 switch which consists of a Fairisle 4 by 4 switch fabric and four Fairisle ATM port controllers, performs the actual switching of data cells and forms the heart of the ATM Fairisle communication network.

## 3.1 The ATM Switch Fabric

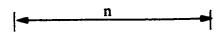

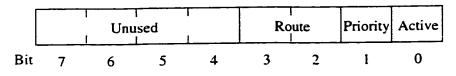

The Fairisle ATM switch consists of three types of components: input port controllers, output port controllers and a switch fabric (Figure 3.1).

Figure 3.1 The structure of the Fairisle ATM switch

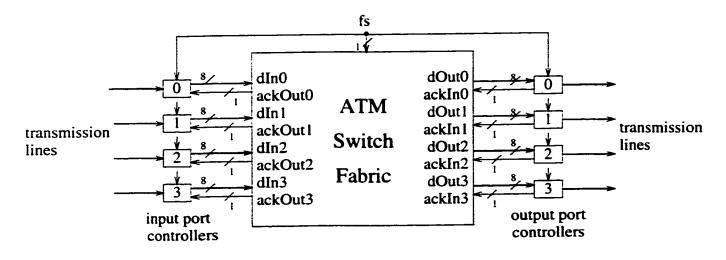

The null port controller synchronizes incoming and outgoing data cells, appending control information in the front of the cells in a routing tag (Figure 3.2).

Figure 3.2 The routing tag of a Fairisle ATM cell