#### A New High Performance LDPC Code for DVB-S2

Massoud Khajeh

A Thesis

In

The Department

of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science( Electrical Engineering) at Concordia University

Montreal, Quebec, Canada

April 2006

© Massoud Khajeh, 2006

Library and Archives Canada

chives Canada Archives Canada

Published Heritage Branch

Direction du Patrimoine de l'édition

395 Wellington Street Ottawa ON K1A 0N4 Canada 395, rue Wellington Ottawa ON K1A 0N4 Canada

Bibliothèque et

Your file Votre référence ISBN: 0-494-14264-2 Our file Notre référence ISBN: 0-494-14264-2

#### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

#### **ABSTRACT**

## A New High Performance LDPC Code

### for DVB-S2

#### Massoud Khajeh

In spite of their powerful error correcting capability, Low Density Parity Check codes (LDPC) have been ignored due to their high complexity. Around three decades after the invention of this code, researchers returned back their attention to it and tried to make some significant improvements in complexity. As the result, the LDPC codes were widely considered in the next generation error correcting codes in telecommunication systems. In 2005, the new standard for Digital Video Broadcasting (DVB-S2) used LDPC codes as its channel coding scheme. The features of the above mentioned code allow a transmission near the Shannon limit.

In this thesis, we first review the LDPC codes in general, and then we present the encoding and decoding scheme which is used in the DVB-S2 standard. We discuss regular and irregular LDPC codes and compare the advantages and disadvantages of these codes with each other.

In this thesis, we consider a higher block length for the LDPC code compared to DVB-S2 standard to improve the performance. We propose an efficient hybrid parity check matrix for this code. This parity check matrix has the same number of base addresses as the case for DVB-S2 which processes high block length with the same

complexity. At the end, simulation results are provided to show the improvement in the performance.

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere appreciation to my supervisor Dr. Y. R. Shayan for his guidance, patience and insightful comments throughout this project. Without Dr Shayan help and advice, I would not have completed my thesis.

I would also like to thank my friends in VLSI and Wireless Laboratories. They helped me and encouraged me to finish this thesis. With their help, I overcome some technical and software problems. I wish that our friendship will continue beyond our professional lives.

I would like to give special thanks to my family. They support me throughout all the time that I've been studying and did not forget me even though they are living thousands of miles from me.

I am grateful to the department of Electrical and Computer Engineering in Concordia University for providing facilities for all students in their research program.

It is the time to appreciate all of the efforts, done by all of my teachers in my life, from kind elementary school teachers, to knowledgeable university professors. I respect their skills and sincerely thank all of them.

# TABLE OF CONTENTS

| List of | Tables         |                                               | ix  |

|---------|----------------|-----------------------------------------------|-----|

| List of | Figures        |                                               | x   |

| List of | f Abbreviation | ons and Symbols                               | xii |

|         |                |                                               |     |

| 1       | Intr           | oduction                                      | 1   |

|         | 1.1            | Overview                                      | 1   |

|         | 1.2            | Digital Communication System                  | 2   |

|         | 1.3            | Error Correcting Codes                        | 3   |

|         | 1.4            | LDPC Codes                                    | 5   |

|         | 1.5            | DVB-S2                                        | 9   |

|         | 1.6            | Thesis Contributions                          | 9   |

|         | 1.7            | Organization of the Thesis                    | 10  |

|         |                |                                               |     |

| 2       | Bac            | kground                                       | 11  |

|         | 2.1            | DVB-S2                                        | 11  |

|         |                | 2.1.1 Transmission System Description         | 13  |

|         |                | 2.1.2 Mode and Stream Adaptation              | 14  |

|         |                | 2.1.3 Forward Error Correction (FEC) Encoding | 14  |

|         |                | 2.1.4 Mapping                                 | 15  |

|         |                | 2.1.5 Physical Layer Framing                  | 19  |

|   |      | 2.1.6 Base-band Filtering and Quadrature Modulation2 | 0: |

|---|------|------------------------------------------------------|----|

|   | 2.2  | Linear Block Codes                                   | 20 |

|   | 2.3  | Low Density Parity Check Codes                       | 24 |

|   |      | 2.3.1 Tanner Graph2                                  | 25 |

|   | 2.4  | Designing LDPC Code2                                 | :9 |

|   |      | 2.4.1 Designing the Parity Check Matrix              | 30 |

|   | 2.5  | LDPC Encoding                                        | 31 |

|   |      | 2.5.1 Gaussian Elimination                           | 33 |

|   |      | 2.5.2 Efficient Encoding Techniques                  | 33 |

|   |      | 2.5.3 Semi-random LDPC                               | 36 |

|   | 2.6  | LDPC Decoding.                                       | 37 |

|   |      | 2.6.1 Bit Flipping Algorithm3                        | 8  |

|   |      | 2.6.2 The Sum-Product Algorithm                      | 39 |

|   | 2.7  | Code Performance                                     | 10 |

| 3 | A ne | ew parity check matrix for LDPC                      |    |

|   | code | e Suitable for DVB-S2 4                              | 3  |

|   | 3.1  | Organization of the Parity Check Matrix4             | 13 |

|   | 3.2  | LDPC Codes: Analysis4                                | 9  |

|   | 3.3  | Density Evolution for LDPC Codes5                    | 3  |

|   | 3.4  | Analysis and Design of Irregular LDPC Codes5         | 5  |

|   |      |                                                      |    |

| 4 | Simu | alation results 61                |

|---|------|-----------------------------------|

|   | 4.1  | Simulation Procedure61            |

|   | 4.2  | Maximum A Posteriori Decoding63   |

|   | 4.3  | Variable Node Processing67        |

|   | 4.4  | Check Node Processing69           |

|   | 4.5  | Iterative Decoding70              |

|   |      |                                   |

| 5 | Conc | clusion 86                        |

|   | 5.1  | Summary of Contributions86        |

|   | 5.2  | Possible Future Work87            |

|   |      |                                   |

| 6 | App  | endix                             |

|   | A.1  | Base Addresses of Code Rate 1/392 |

|   | A.2  | Base Addresses of Code Rate 1/293 |

# LIST OF TABLES

| 1.1 | Application of error correcting code                                 |

|-----|----------------------------------------------------------------------|

| 1.2 | Performance comparison between different types of the channel codes6 |

| 1.3 | Complexity comparison                                                |

| 2.1 | Shannon limit of continuous output AWGN channel with BPSK signaling  |

|     | for various code rate                                                |

| 3.1 | Number of bit nodes of various degree in DVB-S249                    |

| 3.2 | Degree distribution in LDPC code in DVB-S259                         |

| 3.3 | Degree distribution in new LDPC code60                               |

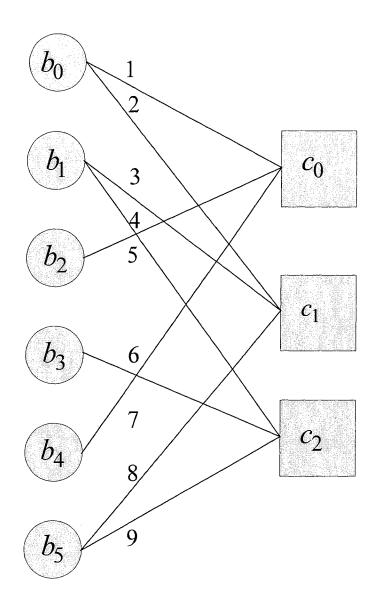

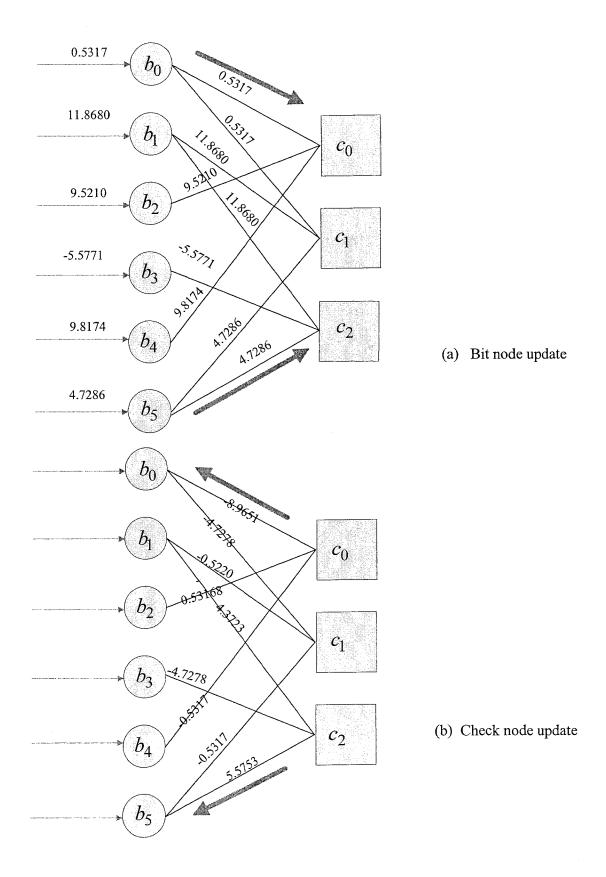

| 4.1 | Edge numbering from the bit node view                                |

| 4.2 | Exchange messages between bit and check nodes during first three     |

|     | iterations                                                           |

| 4.3 | Soft and hard decision outputs80                                     |

# LIST OF FIGURES

| 1.1  | Basic elements of a digital communication system                        | 2    |

|------|-------------------------------------------------------------------------|------|

| 2.1  | Functional block diagram of the DVB-S2 transmission system              | . 13 |

| 2.2  | Format of data before bit interleaving                                  | .15  |

| 2.3  | Bit mapping into QPSK constellation                                     | 17   |

| 2.4  | Bit mapping into 8PSK constellation                                     | 17   |

| 2.5  | 16 APSK signal constellation                                            | .18  |

| 2.6  | 32 APSK signal constellation.                                           | .19  |

| 2.7  | Systematic format of a codeword                                         | .21  |

| 2.8  | A graph with six vertices and 10 edge                                   | 26   |

| 2.9  | Tanner graph of the irregular LDPC code of matrix $H$                   | 28   |

| 2.10 | The parity check matrix in approximate lower triangular form            | .34  |

| 3.1  | Tanner graph for the DVB-S2 LDPC code                                   | 44   |

| 3.2  | Organization of the parity check matrix of the DVB-S2 with code rate R. | 45   |

| 3.3  | Internal organization of the bth sub-block matrix $H^{(u)}$             | 48   |

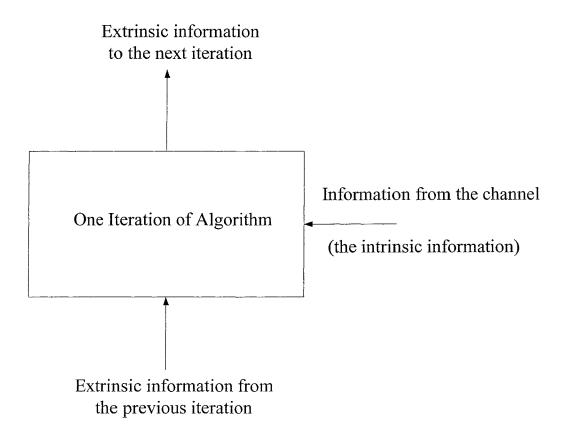

| 3.4  | The principle of iterative decoding.                                    | .50  |

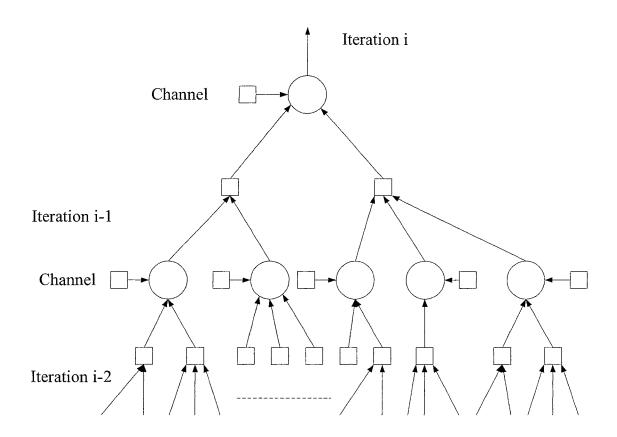

| 3.5  | The depth-one decoding tree                                             | 51   |

| 3.6  | A depth-two decoding tree for an irregular LDPC code                    | 52   |

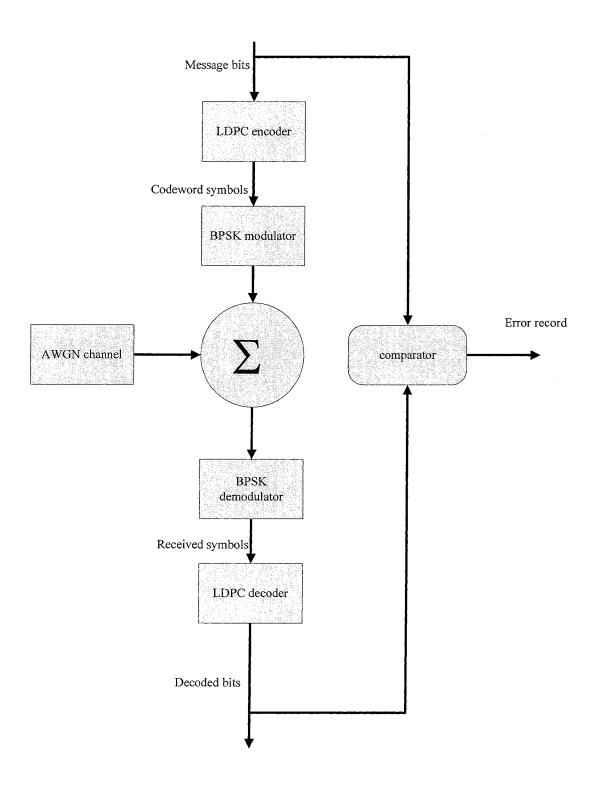

| 4.1  | Block diagram for simulating LDPC code                                  | .62  |

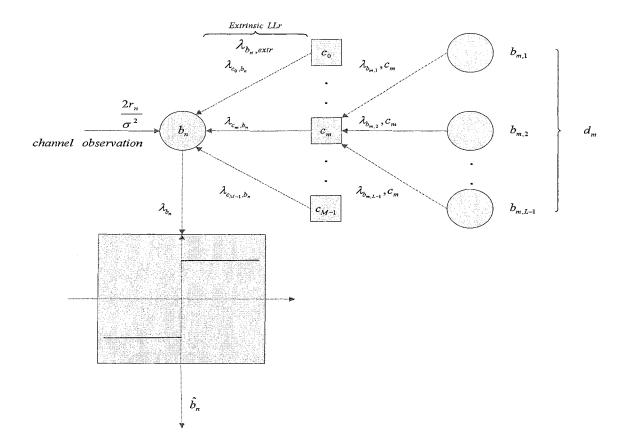

| 4.2  | Tanner graph of regular LDPC code for nth bit node                      | .67  |

| 4.3  | Message passing on the Tanner graph                                     | .71  |

| 1.4  | Edge numbering on the Tanner graph.                                     | .75  |

| 4.5 | Message passing at first iteration.         | .79 |

|-----|---------------------------------------------|-----|

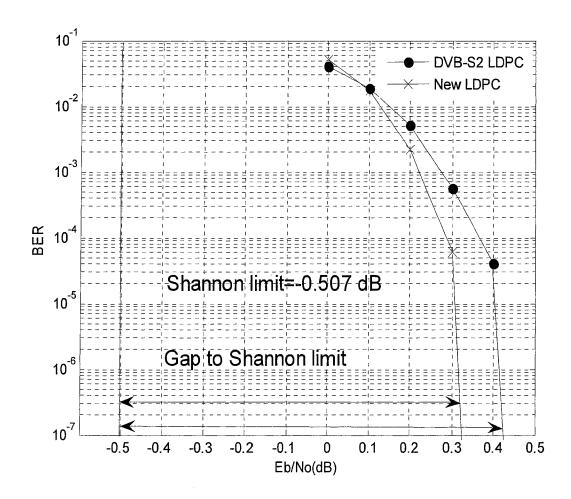

| 4.6 | Error performance of LDPC codes with R=1/3  | .82 |

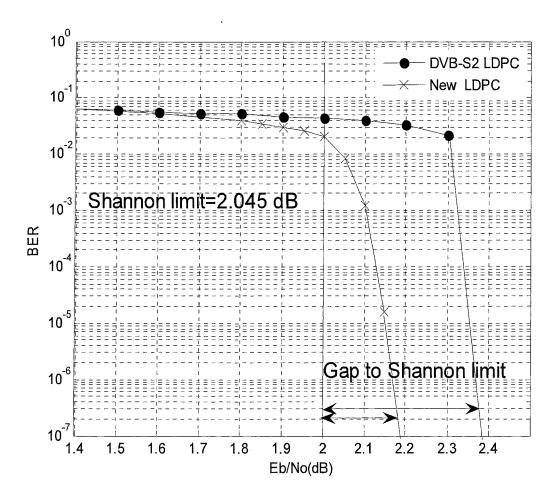

| 4.7 | Error performance of LDPC codes with R=4/5  | .83 |

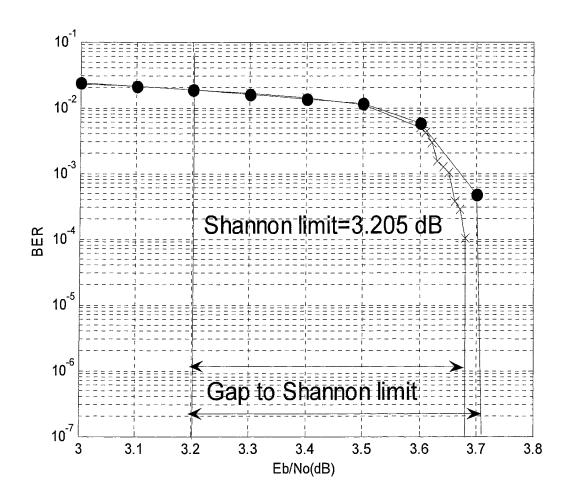

| 4.8 | Error performance of LDPC codes with R=9/10 | .84 |

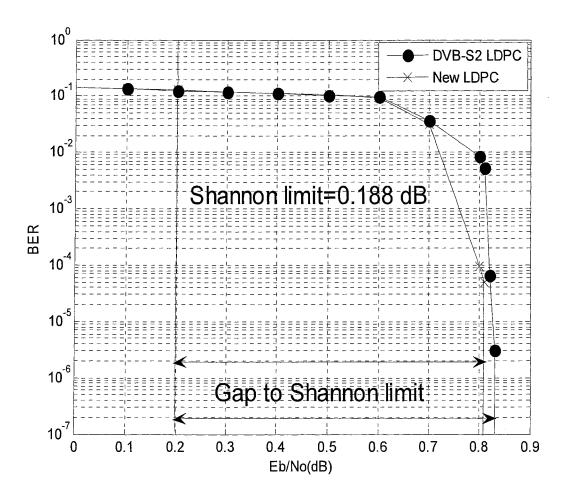

| 4.9 | Error performance of LDPC codes with R=1/2  | .85 |

### LIST OF ABBREVIATIONS AND SYMBOLS

ACM Adaptive Coded and Modulation

APP A Posteriori Probability

APSK Amplitude Phase Shift Keying

AWGN Additive White Gaussian Noise

B Number of Block

b Generic Word

L Block Length

BB Base-Band

BCH Bose, Chaudhuri, Hocquenghem Code

BER Bit Error Rate

BPSK Binary Phase Shift Keying

C Channel Capacity

C Codeword Matrix

CN Check Node

$D_b$  Bit Node Degree in Block B

DVB-S Digital Video Broadcasting Satellite

DVB-S2 Digital Video Broadcasting Satellite 2

d<sub>c</sub> Check Node Degree

d<sub>v</sub> Variable Node Degree

$E_b/N_o$  Bit Power over Noise Power

$E_s$  Average Symbol Energy

ECC Error Correcting Codes

ETSI European Telecommunication Standard Institute

$f_N$  Nyquist Frequency

$f_o$  Carrier Frequency

$f_{y|x}$  Conditional Probability Density Function

FDM Frequency Division Multiplexing

FEC Forward Error Correcting

G A Generator Matrix

H Parity Check Matrix

$H^{(u)}$  Systematic Part of H

$H^{(p)}$  Parity Part of H

$H^T$  Transpose of Parity Check Matrix

$I_k$  A  $k \times k$  Identity Matrix

IN Information Node

IRA Irregular Repeat Accumulate

k Message Bits

L Block Length

LDPC Low Density Parity Check

LLR Log Likelihood Ratio

m Message Vector

MAP Maximum A Posteriori

MLD Maximum Likelihood Decoding

$M_n$  Set of Check Nodes for Bit Node  $b_n$

MPEG Moving Picture Expert Group

n Coded Digit Length

n-k Redundancy Bits (parity bits)

$\frac{N_o}{2}$  Two Sided Noise Power Spectral Density

$N_m$  Set of Bit Nodes Which Check at Check Node

$n_n$  Normal Random Variable of Noise

Pdf Probability Density Function

PLframe Pilot Frame

$P_{(b)}$  Probability of Bit Error

pmf Probability Mass Function

PN Parity Node

Q Code Dependent Permanent

QPSK Quadrature Phase Shift Keying

R Channel Rate

R Code Rate

r Received Vector

RA Repeat Accumulate

$r_n$  nth Received Vector

RF Radio Frequency

SISO Soft Input Soft Output

SNR Signal to Noise Ratio

$t_{b,d}$  Base Addresses for Each Block

TDM Time Division Multiplexing

VCM Variable Coded Modulation

VN Variable Node

W Channel Bandwidth

$z_n$  nth Transmitted Symbol

8PSK 8 Phase Shift Keying

$\alpha$  Roll of Factor

$\phi$  Phase Vector

γ Column Degree

8PSK 8 Phase Shift Keying

$\eta$  Parallelism Factor

$\lambda_{b_n}$  A Posteriori Log Likelihood of  $b_n$

$\lambda_{b_n,c_m}$  Messages Leaving Bit Nodes to Check Nodes

$\lambda_{c_m,b_n}$  Messages Leaving Check Nodes to Bit Nodes

$\rho$  Row Degree

$\sigma^2$  Variance of the Channel Noise

# Chapter 1

# Introduction

#### 1.1 Overview

In order to have a reliable communication with low power consumption over noisy channels, error correcting code may be used. Error correcting codes insert redundancy into the transmitted data stream so that the receiver can detect and possibly correct errors that occur during transmission. Several types of codes exist. Each of which are suitable for some special applications.

Researchers are searching for the best codes suitable for Communication systems. There exists a large design space with trade-offs between the area of the chip, speed of the decoding, complexity, Gap to Shannon limit, and power consumption. In this thesis we discuss a particular type of error correcting codes, namely, Low Density Parity Check (LDPC) codes and its application in DVB-S2 (Digital Video Broadcasting Satellite Version 2). These codes have very good performance over noisy channels.

In this chapter, we will start with an overview of digital communication systems and coding schemes. Then, a general description of error control codes and their applications will be given. Subsequently, LDPC codes, their properties, and applications will be discussed. Finally, some of the related works regarding the architecture design for LDPC codes will be reviewed.

## 1.2 Digital Communication System

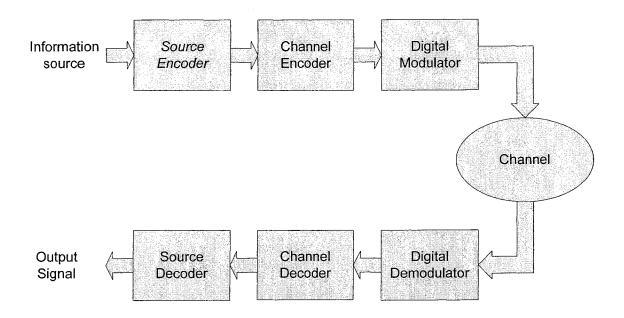

Figure 1.1: Basic elements of a digital communication system

Figure 1.1 shows a basic block diagram of a digital communication system [1]. The source input may be either an analog signal such as audio or video signal or a digital signal such as teletype machine. The messages produced by the source are converted into a sequence of binary digits. The purpose of the channel encoder is to introduce in a controlled manner, some redundancy in the binary information sequence that can be used to overcome the effects of noise and interference encountered in the transmission of the signal through the channel. Then, the binary sequence is passed to the digital modulator to map the information sequence into signal waveforms. The modulator acts as an interface between the digital signal and the channel.

The communication channel is the physical medium which is used to send the signal from the transmitter to the receiver which may be the atmosphere (for wireless

communications); wire line or optical fiber cable. The transmitted signal in all of these channels is corrupted in a random manner with additive thermal noise generated by electronic devices, manmade noise, atmosphere noise and etc.

At the receiving side the digital demodulator processes the channel-corrupted transmitted waveform and reduces the waveforms to a sequence of digital values that feed into the channel decoder. The decoder reconstructs the original information by the knowledge of the code used by the channel encoder and the redundancy contained in the received data. Then, the source decoder decompresses the data and retrieves the original information.

The basic decoding idea is based on the rules of channel encoding and the noise characteristics of the channel. The channel decoder makes an estimate of the transmitted message. There is a trade-off between the power of transmission, bandwidth, and the bit error rate. Researchers are trying to minimize the power consumption and bandwidth while maintaining a reliable communication. This increases a need for stronger codes with more error correction capabilities.

### 1.3 Error Correcting Codes

Error correcting coding (ECC) is the critical point of modern communication systems. In many applications a substantial portion of the baseband signal processing is dedicated to ECC. The wide range of ECC applications include, space and satellite communications, data transmission, data storage, and mobile communications.

In 1948, Claude Shannon founded the field of "Information Theory" which is the basis of modern ECC by discovering the noisy channel coding theorem [4]. In his work, he introduced a metric in which the information can be quantified. This theorem states that the capacity C (which is now known as the Shannon limit) of a band-limited Additive White Gaussian noise (AWGN) channel with bandwidth W, is given by:

$$C = W \log_2 \left( 1 + \frac{E_s}{N_0} \right)$$

Bits per second (bps) (1.1)

where  $E_s$  is the average signal energy in each signaling interval of duration T=1/W, and  $N_0/2$  is the two-sided noise power spectral density. The proof of this theorem demonstrates that for any transmission rate R less than or equal to the channel capacity C, there exists a coding scheme that achieves error-free transmission. Conversely if R is greater than C, no coding scheme can achieve reliable performance. Since this theorem was published, an entire field of study has grown out to design coding schemes that approach the Shannon limit of various channels.

In table 1.1, we mention some of the applications and required coding schemes. Satellite downlinks are generally characterized as power-limited channels. On board batteries and solar cells are heavy and thus contribute significantly to launch costs. Therefore, strong error control codes need to operate efficiently at extremely low signal to noise ratio. LDPC and Turbo codes are choices for these applications. Similar principles apply to the wireless communications for cell phones and laptops. In order to increase battery life we need to use powerful codes like LDPC, or Turbo codes.

Table 1.1: Application of error correcting codes

| Application                                | CODE                                   | COMMENT         |

|--------------------------------------------|----------------------------------------|-----------------|

| Wireless communications Satellite downlink | Convolution, Turbo,<br>LDPC            | Random<br>Noise |

| CD player<br>Tape storage                  | Reed – Solomon<br>+cross- interleaving | Bursty channel  |

| Computer memory                            | Hamming code                           |                 |

| Magnetic discs                             | Fire codes                             |                 |

| Computer networks                          | CRC                                    |                 |

Various applications exist for the error control codes in computer systems, such as memory (random access and read-only memory), disk storage, tape storage and interprocessor communication. Each of these has their unique characteristic that indicates the use of certain type of codes. Hamming codes are used for the computer memories, Fire codes for magnetic discs and Reed Solomon based system is used for the tape mass storage system. Computer networks and internet use Cyclic Redundancy Code (CRC) to detect packet errors [5].

### 1.4 LDPC Codes

In the past few years, LDPC codes have received much attention because of their excellent performance, and have been widely considered as the most promising ECC candidate for many applications in telecommunications and storage devices. LDPC codes were proposed by Gallager in 1962 [6]. He defined an  $(n, d_v, d_c)$  LDPC code as a code of block length n in which each column of the parity-check matrix contains  $d_v$  ones and

each row contains  $d_c$  ones. Due to the regular structure (uniform column and row weight) of Gallager's code, they are now called regular LDPC codes. Gallager provided simulation results for codes with blocks in the order of hundreds of bits. The results indicated that LDPC codes have very good potential for error correction. However, the high storage and computation requirements interrupted the research on LDPC codes. After discovering Turbo codes by Berrou [2], Mackay [7] [8] re-established the interest in LDPC codes during the mid to late 1990s.

LDPC codes can be used in any digital environment that high data rate and good error correction is important, such as optical fiber communications, satellite (digital Video and Audio broadcast), storage (magnetic, optical, holographic), wireless (mobile, fixed), and wired-line (cable modems, DSL). Table 1.2 shows a comparison between the best-known error correcting codes. Chung [9] showed that a rate 1/2 LDPC code with block length of 10<sup>7</sup> Additive White Gaussian Noise channel can achieve a threshold of 0.0045 dB away from Shannon limit. This table shows that for very large block lengths, LDPC is the best-known code in terms of performance.

Table 1.2: Performance comparison between different types of the channel codes

| Code Type             | Shannon | LDPC  | Turbo | Convolutional |

|-----------------------|---------|-------|-------|---------------|

|                       | Limit   |       |       | /Viterbi      |

| Performance(dB)       | 0.18    | 0.185 | 0.6   | 4.5           |

| $P_{error} = 10^{-6}$ |         |       |       |               |

While standards for Viterbi and turbo codes have been emerged in communication systems, the flexibility of designing LDPC codes allow for a larger family of codes and encoder /decoder structures. Some initial proposals for LDPC codes for DVB-S2 are emerging [10].

Another feature of LDPC codes is their simple graphical representation, which is based on Tanner's [11] representation of linear codes. This simple structure allows for accurate asymptotic analysis of LDPC codes as well as design of good irregular LDPC codes and optimization under specific constraints.

Irregular LDPC [12] codes can significantly outperform regular LDPC codes.

These codes have approached Shannon limit for different channel type.

One issue with irregular LDPC codes is their encoding complexity. People have considered different ways to add structure to LDPC codes to make the encoding process less complex. One of the best solutions is Repeat Accumulate (RA) codes, which have a slightly different structure than LDPC codes and suffer minor performance loss compared to LDPC codes. The encoding complexity of RA codes grows linearly with the block length.

Irregular Repeat-Accumulate (IRA) codes have a linear-time encoding complexity with a straight forward hardware realization. It outperforms the currently deployed Turbo-codes. Like irregular LDPC codes, IRA [13] codes can be represented by a Tanner graph with arbitrary connections between nodes. An IRA code is defined by the degree distribution of the nodes. Their complexity strongly depends on the randomness of

the Tanner graph. Regularity in the Tanner graph simplifies the implementation but degrades the communication performance.

Table 1.3 shows a comparison between the complexity of the encoders and the decoders for three different types of coding. In this table n is the code length, d is the constraint length, J is the maximum number of the decoding iterations,  $d_c$  is the row degree, and  $d_v$  is the column degree of the nodes in the parity check matrix of the LDPC decoder. Comparison shows that LDPC decoding is linear with the block length, whereas in turbo codes, it has exponential relation with the constraint length.

Table 1.3: Complexity comparison

| Encoder           | Decoder                       |

|-------------------|-------------------------------|

| O(nd)             | $O(n2^d)$                     |

| $O(n(d_1+1+d_2))$ | $O(Jn(1+2^{d_1}+2^{d_2}))$    |

| $O(nd_c^2)$       | $O(Jn(d_c + d_v))$            |

|                   | $O(nd)$ $O(n(d_1 + 1 + d_2))$ |

Complexity in iterative decoding has three parts. First, complexity of the computations at each node, second the complexity of the interconnection, and third the number of times that local computations need to be repeated, usually referred to as the number of iterations. All of these are manageable in practice. There is a trade-off between the performance of the decoder, complexity and speed of decoding.

#### 1.5 DVB-S2

The new DVB-S2 [14] standard features a powerful forward error correction (FEC) system that enables transmission close to the theoretical limit (Shannon limit). This is enabled by using Low Density Parity Check (LDPC) codes one of the most powerful codes known today which can even outperform Turbo codes. To provide flexibility, 11 different code rates ranging from (R=1/4 up 9/10) are specified with a codeword length up to 64800 bits. This huge codeword length is the reason for the outstanding communications performance (~ 0.7 db to Shannon limit) of this DVB-S2 LDPC code proposal. The LDPC codes as defined in the DVB-S2 standard are IRA codes, thus the encoder realization is straightforward. Furthermore, the DVB-S2 code shows regularities that can be exploited for an efficient hardware realization.

The DVB-S2 standard uses a serial concatenation of two binary linear codes: an outer BCH code and inner low density parity check (LDPC) code. Note that the outer BCH code used by DVB-S2 helps to clean up additional errors at the output of the LDPC decoder and will improve the overall performance.

#### 1.6 Thesis Contribution

In this thesis, we propose a hybrid parity check matrix with different block length which is used in DVB-S2 standard. LDPC codes that use this type of parity check matrix show performance improvements in communication systems. In this work, a parity check matrix is generated by using semi-random technique, consisting of two submatrices of  $H^{(u)}$  and  $H^{(p)}$ .  $H^{(u)}$  is defined as a randomly generated matrix, while  $H^{(p)}$  is a

deterministic one. Moreover,  $H^{(u)}$  is divided in small blocks, where each block has a special base address. Weight distribution of the random part has major effect in code performance. The method for replacing and expanding '1's in parity check matrix is done in both of regular and irregular techniques. In the irregular method, at first we find base addresses and then with the help of a simple rule, the other entries will be found. This hybrid parity check matrix can be considered as an efficient tool for practical hardware implementation of both decoder and encoder. As we will show in this thesis, the performance of the new code is better than the performance of the LDPC code which is used in DVB-S2. However, both codes have the same complexity.

## 1.7 Organization of the Thesis

In chapter 2 we provide the necessary background on DVB-S2 and LDPC codes.

Various types of LDPC encoding and decoding algorithms are discussed.

In chapter 3 we explain new parity check matrix which can be used in DVB-S2 standard and the conventional design method for analysis, designing and checking performance of irregular LDPC codes.

In chapter 4 we describe the simulation procedure, the class of decoding algorithm and analysis of the decoder. In this chapter we show some simulation results.

Finally a summary of contributions and some suggestions for future work are provided in chapter 5.

# Chapter 2

# Background

#### 2.1 DVB-S2

The European Telecommunications Standard Institute (ETSI) with the goal of standardizing digital television services founded the Digital video Broadcasting (DVB) project in 1993 [15]. Its initial standard for the satellite delivery of digital television, dubbed DVB-S, used a concatenation of an outer (204,188) shortened Reed Solomon code and an inner constraint length 7, variable rate (R ranging from 1/2 to 7/8) convolutional code.

The latest standard, called DVB-S2, replaces the concatenated Reed-Solomon /convolutional coding approach of DVB-S with a concatenation of outer BCH code and inner low-density parity check (LDPC) code. The result is a 30% increase in capacity over DVB-S.

The new DVB-S2 standard presents a powerful forward error correction (FEC) system, which enables transmission close to the theoretical limit (Shannon limit). This is possible using low density parity check (LDPC) codes which are one of the most powerful kinds, even outperforming Turbo codes. To provide flexibility, 11 different code rates ranging from (R=1/4 up to 9/10) are specified with a codeword length up to 64800 bits. This huge maximum codeword length is the reason for the outstanding communications performance (~0.7 dB to Shannon limit).

DVB-S2 is a single and flexible standard that covers a variety of applications by satellite, as described below. It is characterized by the following features:

- A flexible input stream adapter, suitable for operation with single and multiple input streams of various formats (packetized or continuous);

- A powerful FEC system based on LDPC (low density parity check) codes concatenated with BCH codes, allowing Quasi-Error-Free operation at about 0.7 dB to 1 dB from the Shannon limit, depending on the transmission mode;

- A wide range of code rates (from 1/4 to 9/10); 4 constellations, ranging in spectrum efficiency from 2 bits/s/HZ to 5 bits/s/HZ, optimized for operation over non-linear transponders;

- A set of three spectrum shapes with roll-off factors 0.35, 0.25 and 0.20;

- Adaptive coding and modulation (ACM) functionality, optimizing channel coding and modulation on a frame-by-frame basis.

DVB-S2 is suitable for use on different satellite transponder bandwidths and frequency bands. The symbol rate is matched to give transponder characteristics, and in the case of multiple carriers per transponder (FDM), it is possible to adopt bandwidth to the frequency plan. Digital transmissions via satellite are affected by power and bandwidth limitations. Therefore, DVB-S2 provides for many transmission modes (FEC coding and modulations) giving different trade-offs between power and spectrum efficiency.

DVB-S2 is compatible with Moving Picture Experts Group (MPEG-2 and MPEG-4) coded TV services with a transport stream packet multiplex. Multiplex flexibility allows the use of the transmission capacity for a variety of TV service configurations,

including sound and data services. All service components are Time Division Multiplexed (TDM) on a single digital carrier.

### 2.1.1 Transmission System Description

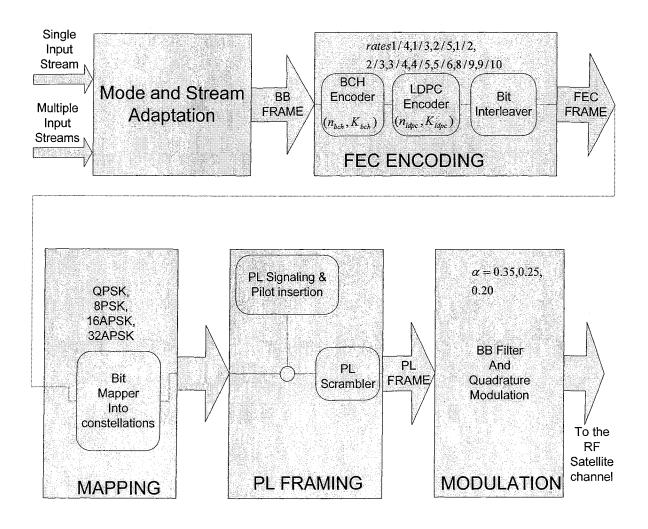

Figure 2.1 shows the functional block diagram of DVB-S2 [14] system.

Figure 2.1: Functional block diagram of the DVB-S2 transmission system

#### 2.1.2 Mode and Stream Adaptation

The mode and stream adaptation block provides input stream interfacing, input stream synchronization (optional), null packet deletion (for the ACM and Transport Stream input format only), CRC-8 coding for error detection at packet level in the receiver (for packetized input stream only), and slicing into Data Fields. This block also provides padding to complete the base-band frame and base-band scrambling.

#### 2.1.3 Forward Error Correction (FEC) Encoding

It will be carried out by the concatenation of BCH outer codes and LDPC inner codes (rates 1/4,1/3,2/5,1/2,3/5,2/3,3/4,4/5,5/6,8/9,9/10). Depending on the application area, the FEC coded block will have the length of 64800 or 16200 bits. When VCM and ACM are used, FEC and modulation mode may be changed in different frames but they remain constant within a frame. Bit interleaving will be applied to FEC coded bits for 8PSK, 16APSK, and 32APSK.

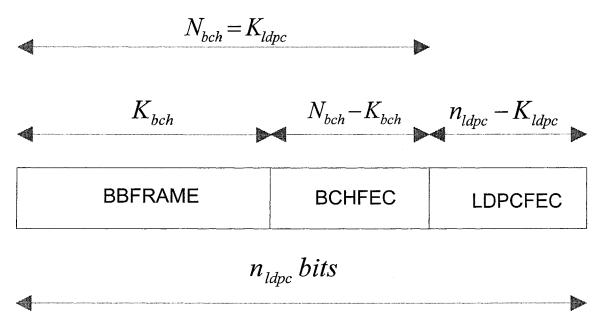

Each BBFRAME ( $K_{bch}$  bits) will be processed by the FEC coding subsystem to generate a FECFRAME ( $n_{ldpc}$  bits). The parity check bits (BCHFEC) of the systematic BCH outer code append after the BBFRAME and the parity check bits (LDPCFEC) of the inner LDPC encoder append after the BCHFEC field as shown in Figure 2.2.

For 8PSK, 16APSK, and 32APSK modulation formats, the output of the LDPC encoder will be interleaved using a block interleaver. Data are serially written into the interleaver column-wise and serially read out row-wise.

Unlike turbo codes, LDPC codes have an easily parallelizable decoding algorithm which consists of simple operations such as addition, comparison, and look-up table. Moreover, the degree of parallelism is adjustable, which makes it easy to trade-off throughput and complexity.

Figure 2.2: Format of data before bit interleaving

(  $n_{ldpc}$  =64800 bits for normal FECFRAME  $\,$  ,  $\,$   $n_{ldpc}$  =16200 bits for short FECFRAME)

### 2.1.4 Mapping

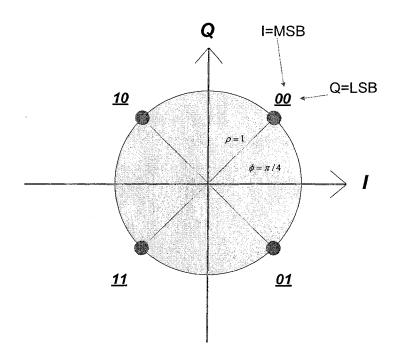

After bit interleaving, mapping QPSK, 8PSK, 16APSK, and 32APSK constellations will be applied depending on the application area. Gray mapping of constellations will be used for QPSK and 8PSK.

Each FECFRAME (which is a sequence of 64800 bits for normal FECFRAME, or 16200 bits for short FECFRAME) must be converted to parallel sequence (parallelism factor  $\eta_{\rm mod}$ =2 for QPSK, 3 for 8PSK, 4 for 16APSK, and 5 for 32 APSK). Each parallel sequence will be mapped into a constellation. This mapping generates a sequence of variable length (I, Q) depending on the selected modulation efficiency  $\eta_{\rm mod}$ .

The input sequence is FECFRAME and the output sequence is XFECFRAME. Complex XFECFRAME are composed of  $64800/\eta_{mod}$  or  $16200/\eta_{mod}$  modulation symbols. Each modulation symbol will be a complex vector in the format (I, Q) (I being the in-phase component and Q the quadrature component) or in the equivalent format  $\rho \exp(j\varphi)$  ( $\rho$  being the modulus of the vector and  $\varphi$  being its phase).

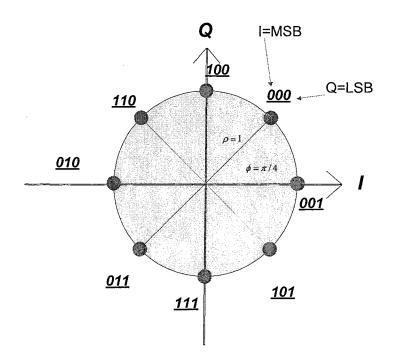

For QPSK and 8PSK, the system employs conventional Gray-coded modulation with absolute mapping (no differential coding). Bit mapping for QPSK and 8PSK are shown in Figure 2.3 and Figure 2.4 respectively. The normalized average energy per symbol is equal to  $\rho^2 = 1$ .

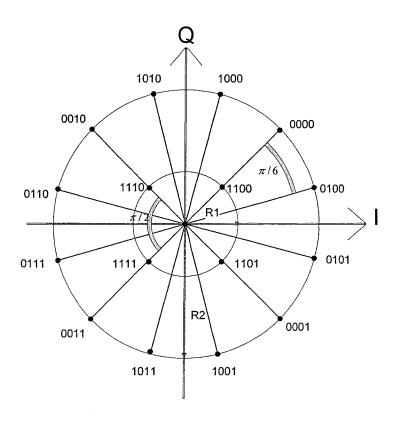

The 16APSK modulation constellation is composed of two centric rings of uniformly spaced 4 and 12 PSK points; the radius of inner ring is R1 and the outer ring is R2. If  $4[R1]^2 + 12[R2]^2 = 16$ , the average signal energy becomes 1.

Figure 2.3: Bit mapping into QPSK constellation

Figure 2.4: Bit mapping into 8PSK constellation

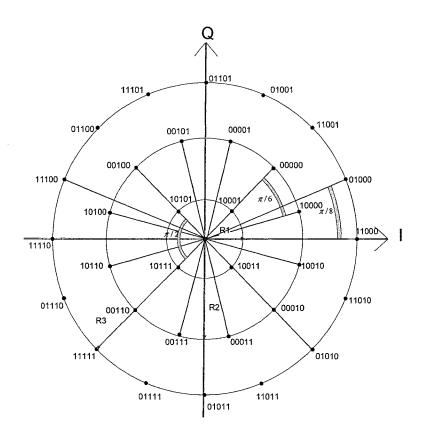

The 32APSK modulation is composed of three concentric rings of uniformly spaced 4, 12 and 16PSK points in the inner ring of radius R1, the intermediate ring of and radius R2 the outer ring of radius R3, respectively. If  $4[R1]^2 + 12[R2]^2 + 16[R3]^2 = 32$ , the average signal energy becomes equal to 1. Constellation labeling is shown in Figures 2.5 and 2.6. 16APSK and 32APSK (as opposed to 16QAM and 32QAM) are chosen due to their "non-linearity friendly" characteristics. Moreover, their performances on linear channels are almost as good as their QAM competitors.

Figure 2.5: 16 APSK signal constellation

Figure 2.6: 32 APSK signal constellation

## 2.1.5 Physical Layer Framing

This block is employed for synchronization with the FEC frames and provides dummy PLFRAME insertion, physical layer signaling, pilot symbols insertion (optional), and physical layer scrambling for energy dispersal. Dummy PLFRAMEs are transmitted when no useful data are ready to be sent on the channel. Carrier recovery in the receivers may be facilitated by the introduction of a regular raster of pilot symbols, while a pilot-less transmission mode is also available, offering an additional 2.4% useful capacity.

#### 2.1.6 Base-band Filtering and Quadrature Modulation

This block is employed for shaping the signal spectrum and for generating the RF signal. Its frequency characteristic is the square-root raised cosine with the roll-off factor of 0.35 or 0.25 or 0.20. The baseband square root raised cosine has an analytical function defined by the following expression:

$$H(f) = 1 for |f| \langle f_N(1-\alpha)$$

(2.1)

$$H(f) = \left\{ \frac{1}{2} + \frac{1}{2} \sin \frac{\pi}{2f_N} \left[ \frac{f_N - |f|}{\alpha} \right] \right\}^{\frac{1}{2}} for \qquad f_N(1 - \alpha) \langle |f| \langle f_N(1 + \alpha) \rangle$$

(2.2)

$$H(f) = 0$$

for  $|f|$   $\rangle$   $f_N(1+\alpha)$  (2.3)

where  $f_N = \frac{1}{2T_s} = \frac{R_s}{2}$  is the Nyquist frequency and  $\alpha$  is the roll-off factor.

Quadrature modulation will be performed by multiplying the in-phase and quadrature samples (after baseband filtering) by  $\sin(2\pi f_0 t)$  and  $\cos(2\pi f_0 t)$  respectively, where  $f_0$  is the carrier frequency. The two resulting signals will be added to obtain the modulator output signal.

#### 2.2 Linear Block Codes

The low-density parity check coding scheme is one of the hottest topics in coding theory. It was introduced by Gallager in his Ph.D thesis in early 1960. It is a special case of linear block codes and for this reason, an introduction to these classes of codes is necessary for a better understanding of LDPC codes.

Linear block codes are a class of parity check codes that can be characterized by (n,k) notation [16]. The encoder transforms a block of k message digits into a longer block of n codeword digits constructed from a given alphabet of elements. For linear codes, the mapping transformation is linear. Linear codes have the following interesting properties:

- The linear combination of any set of codeword is also a codeword. Therefore, linear codes always contain the all zero codeword.

- 2. The minimum distance of a linear code is equal to the weight of the lowest weight nonzero codeword.

- 3. The undetectable error patterns for a linear code are independent of the codeword transmitted and always consist of a set of all nonzero codewords.

A desirable property that a linear block code may posses is the systematic structure of the codeword. A systematic codeword is divided into two parts: the message part and the redundant checking part

| Redundant checking part | Message part |

|-------------------------|--------------|

| n-k digits              | k digits     |

Figure 2.7: Systematic format of a codeword

the message part consists of k unaltered information digits, and the redundant checking part consists of n-k parity check digits, which are linear sums of the information digits.

A linear systematic (n,k) code is completely specified by  $k \times n$  matrix G of the following form:

$$G = \begin{bmatrix} g_0 \\ g_1 \\ g_2 \\ \vdots \\ g_{k-1} \end{bmatrix} = \begin{bmatrix} p_{00} & p_{01} \cdots & p_{0,n-k-1} & \vdots & 1 & 0 & 0 & \dots & \dots & 0 \\ p_{10} & p_{11} \cdots & p_{1,n-k-1} & \vdots & 0 & 1 & 0 & \dots & \dots & 0 \\ p_{20} & p_{21} \cdots & p_{2,n-k-1} & \vdots & 0 & 0 & 1 & \dots & \dots & 0 \\ \vdots & \vdots \\ p_{k-1,0} & p_{k-1,1} \cdots & p_{k-1,n-k-1} & \vdots & 0 & 0 & 0 & \dots & \dots & 1 \end{bmatrix}$$

$$(2.4)$$

where  $p_{ij} = 0$  or 1 and  $I_k$  is  $k \times k$  identity matrix. Then,  $G = [P|I_k]$ .

The generation of the codeword U is written in matrix notation as the product of m (message vector) and G, and we write

$$U = mG (2.5)$$

Thus, the code vector corresponding to a message vector is a linear combination of the rows of G. Since the code is totally defined by G, the encoder needs only to store the k rows of G instead of the total vectors of the code.

There is another useful matrix associated with all linear block codes, called the parity check matrix that will enable us to decode the received vectors. For any  $k \times n$  matrix G with k linearly independent rows, there exists an  $(n-k) \times n$  matrix H with n-k linearly independent rows, such that any vector in the row space of G is orthogonal to the rows of H, and any vector that is orthogonal to the rows of H is in the row space of G. Hence,  $GH^T = 0$ , where  $H^T$  is the transpose of H and H is a H is a H in the row space of H.

matrix. To fulfill the orthogonality requirements for a systematic code, the components of the H matrix are written as:

$$H = \left| I_{n-k} \right| P^T$$

(2.6)

We can use the parity check matrix to test whether or not a received vector is a valid member of the codeword set. U is a codeword generated by matrix G if and only if:

$$U.H^T = 0. (2.7)$$

When a data block is encoded using a systematic generator matrix, the data block is embedded without modification in the last k coordinates of the resulting codeword.

$$c = mG$$

$$= [m_0 m_1 \cdots m_{k-1}] [P|I_k]$$

$$= [c_0 c_1 \cdots c_{n-k-1}] m_0 m_1 \cdots m_{k-1}]$$

After decoding, the last k symbols are removed from the selected codeword and passed along to the data sink. Given a systematic generator matrix, the corresponding parity check matrix can be obtained as shown below:

$$H = \begin{bmatrix} 1 & 0 & 0 & \cdots & 0 & \vdots & p_{00} & p_{10} & \cdots & p_{k-1,0} \\ 0 & 1 & 0 & \cdots & 0 & \vdots & p_{01} & p_{11} & \cdots & p_{k-1,1} \\ 0 & 0 & 1 & \cdots & 0 & \vdots & p_{02} & p_{12} & \cdots & p_{k-1,2} \\ & & & & & & & & \vdots \\ 0 & 0 & 0 & \cdots & 1 & \vdots & p_{0,n-k-1} & p_{1,n-k-1} & \cdots & p_{k-1,n-k-1} \end{bmatrix}$$

$$(2.8)$$

and we can obtain the generator matrix from the parity check matrix in systematic form by using Gaussian elimination. By these definitions and properties, we are ready to discuss LDPC code properties.

#### 2.3 Low Density Parity Check Codes

LDPC codes are systematic, block codes that can be represented in either of the two basic ways: analytical or graphical. The analytical way is a matrix representation, whereas the graphical approach is described with Tanner graphs (or bi-partite graphs). In matrix representation, LDPC codes can be described with a check constraints matrix H which is sparse. This means that the density of '1's in this matrix is very low.

The matrix H has n columns and n-k rows, n being the size of the codeword and k the size of the information block. n-k are also referred to as the number of constraints of the LDPC code.

$$H = \{h_{ij}\}_{n-k,n}$$

$i = 0, \dots, n-k-1$   $j = 0, \dots, n-1$

Elements  $h_{ij}$  are binary symbols drawn from the set  $\{0,1\}$  and the *jth* coded bit is checked at the *ith* constraint node if and only if  $h_{ij} = 1$ .

An LDPC code is defined as the null space of a parity check matrix H that has the following structural properties:

- each row consists of  $\rho$  1's;

- each column consists of  $\gamma$  1's;

- the number of '1's common between any two columns, denoted by z, is no greater than 1; that is, z=0 or 1;

- both  $\rho$  and  $\gamma$  are small compared to the length of the code and the number of rows in H.

This is the definition of regular LDPC codes but if degrees per row or column are not constant, then the code is irregular. Some of the irregular codes have shown better performance than regular ones. Code rate R is equal to  $\frac{k}{n}$  (k be information bit and n is code length) which means that (n-k) redundant bits have been added to the message so as to correct the errors.

### 2.3.1 Tanner Graph

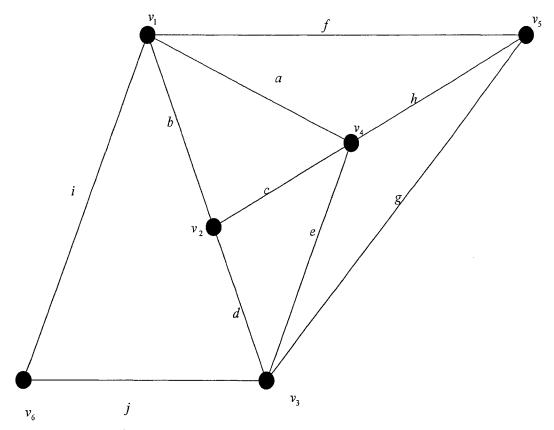

LDPC codes can be represented effectively by a bi-partite graph called a "Tanner" graph [11]. A graph is most commonly represented by a diagram in which the vertices are represented by points and each edge by a line joining its end vertices. Figure 2.8 shows a graph consisting of six vertices and 10 edges. The number of edges that are incident on a vertex  $v_i$  is called the degree, denoted by  $d(v_i)$  of vertex  $v_i$  as shown in Fig 2.8.

Figure 2.8: A graph with six vertices and 10 edges

In the Tanner graph, following characteristics hold:

- Two edges that are incident on common vertex are said to be adjacent or connected.

- Two vertices are said to be adjacent if they are connected by an edge.

- A graph with a finite number of vertices as well as a finite number of edges is called a finite graph.

- The number of edges on a path is called the length of the path.

- A cycle of length l in a graph is a path comprised of l edges which closes back on itself.

- The length of the shortest cycle in a graph is called the girth of the graph.

- A graph without cycles is said to be acyclic and is called a tree.

- An edge for which the initial and terminal vertices are the same forms a cycle of length 1 called a self loop.

A graph  $g = (v, \varepsilon)$  is called a bipartite graph if its vertex set v can be partitioned into two disjoint subsets  $v_1$  and  $v_2$  such that every edge in  $\varepsilon$  joins the vertex in  $v_1$  with a vertex in  $v_2$  and no two vertices in either  $v_1$  or  $v_2$  are connected. If a bipartite graph  $g = (v, \varepsilon)$  contains cycles, then all the cycles have even lengths and it is obvious that a bipartite graph has no self loop.

For LDPC codes with the length n, and the parity-check matrix H, a Tanner graph consists of two sets of vertices. The first set consists of n vertices that represent the n code bits of the code and is called the code-bit vertices (or variable nodes). The second set consists of (n-k) vertices that represent the (n-k) parity—check sums (or equations) that the code bit must satisfy. These vertices are called the check-sum vertices (or check nodes). No two code-bit vertices are connected, and no two check-sum vertices are connected.

The degree of a code-bit vertex is simply equal to the number of the parity sums that contain this code-bit, and the degree of the check-sum vertex is simply equal to the number of code bits that are checked by this check-sum vertex. For a regular LDPC code, the degrees of all the code-bit vertices in the tanner graph of the code are the same and equal to  $\gamma$  (the column weight of the parity-check matrix); and the degrees of all the check-sum vertices are the same and equal to  $\rho$  (the row weight of the parity-check matrix). For an irregular LDPC code, the degrees of code-bit vertices and check-sum vertices are different and depend on codes that have been used. From the definition of

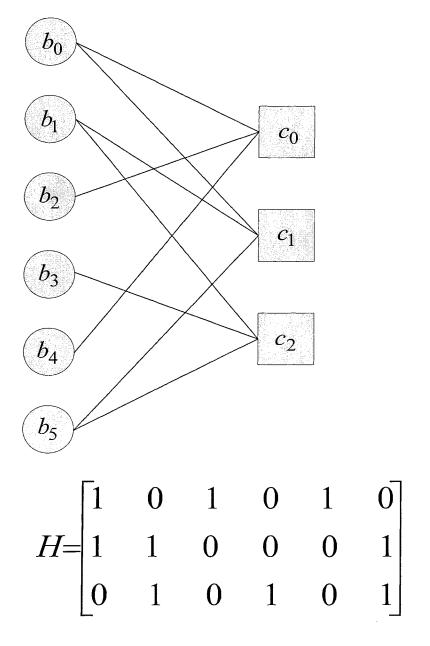

LDPC codes and for better performance in decoding, no two code bits of an LDPC code are checked by two different parity-check sums. Now let us introduce a simple example of an LDPC code. Consider parity check matrix H which describes an irregular LDPC code with rate  $R = \frac{1}{2}$ , information block size k = 3, and code length n = 6. Figure 2.9 shows the matrix and the related bipartite graph.

Figure 2.9: Tanner graph of the irregular LDPC code of matrix H

The shortest possible cycle in a bipartite graph is clearly length 4 which means four '1's that lie in the corners of a sub-matrix of H. We are interested in cycles, especially in short cycles, because they have a negative effect on the decoding algorithm for the LDPC codes.

## 2.4 Designing LDPC Code

The first step in designing an LDPC code is answering the following questions:

- What is the desired block length of the code? It is obvious that codes with large block lengths have very good performance, but the problem is that large block lengths have a high complexity and are unfeasible in practice.

- What is the type of code? Regular or irregular?

- What is the degree of each bit node or check node? In other words, how many ones are allowed in each row or column of the parity check matrix? For the regular codes, degrees of all bit nodes will be the same. For irregular codes, one should decide how many different degrees are allowed for the bit nodes and check nodes. High degrees mean that more computations should be done in each node to generate the outgoing message. Also, nodes with higher degrees have faster convergence to their correct value, and in decoding with a high degree, complexity will be increased.

- What is the rate of the code? The rate of the code show us how much redundancy we have in the code and how much bandwidth is allowed to increase, because if for better performance we increase the rate it means that we must increase our bandwidth at the end of communication systems.

• What is the maximum number of decoding iterations? It is possible that by increasing the maximum iteration number, code performance can improve but it increases decoding time which is important in some applications. After deciding the above parameters, we can design the parity check matrix.

#### 2.4.1 Designing the Parity Check Matrix

The parity check matrix plays a major role in the performance of the LDPC encoding/decoding. As mentioned by Gallager, this matrix should be very sparse. It also determines the complexity of the encoder/ decoder. Depending on the application, this matrix can be random or structured. Random matrices are suitable for decoders running on general purpose processors, but for special hardware like FPGAs or ASIC, it is better to have a structured matrix. The structure in the parity check matrix leads to a more efficient hardware representation. It also requires less memory to keep the matrix. Here, we will list ways to generate a sparse matrix H. Some of these ways are more complex than others, but they don't necessarily lead to a better code.

- Start from an all zero matrix of the size  $(n-k)\times n$  and randomly invert some elements in the matrix to reach the resulting degrees for different nodes.

- Generate H by randomly creating weight  $\gamma$  columns.

- Generate H with weight  $\gamma$  columns and uniform row weight  $\rho$ .

- Generate H with columns of weight  $\gamma$  and uniform rows of weight  $\rho$ ; with no two columns having an overlap of more than one. This condition removes all the length four cycles which results in better performance.

- Generating H and avoiding all short cycles (4, 6...).

- Generating the parity check matrix in a structured manner. For example, a structure that is used in hardware design is to generate this matrix using a combination of the shifted blocks of identity matrices.

- Generate the parity check matrix using a polynomial.

Each of the above ways has their advantages and disadvantages, and we can choose them based on the application. Now we are ready to discuss LDPC encoding.

#### 2.5 LDPC Encoding

The encoding problem consists of solving a set of linear equations or constraints. A generic word U with size n is a valid codeword if and only if the following condition is met:

$$H.U^T = 0 (2.9)$$

The dot product in (2.9) provides the parity of the codeword. In particular, even parity is adopted, and equation (2.9) states that the number of '1's in the codeword b must be even at any check constraint.

LDPC codes are systematic codes, thus the codeword b can be thought as:

$$U = (b, P)$$

where b is the systematic part (the information data) of b with size k, and P is the redundant part with size n-k:

$$\begin{cases}

b = (b_0 & b_1 \cdots & b_{k-1}) \\

P = (p_0 & p_1 \cdots & p_{n-k-1})

\end{cases}$$

(2.10)

The redundant part P represents the added value of the encoding process and allows for forward error correction at the receiver.

Having the parity check matrix of a set of LDPC codes, we can draw the corresponding Tanner graph. To give a general perspective about encoding of the LDPC codes first, we assign each of the information bits to bit nodes in the graph, and then the values of the remaining bit nodes are determined so that all the parity check constraints satisfy. In this way, encoding LDPC codes is selecting the nodes for assigning information bits and a strategy for calculating the values of the other bit nodes. This is the process of encoding in the matrix notation:

$$H = [P^{\mathsf{T}} : I] \Rightarrow G = [I : P] \Rightarrow C = mG$$

in which C is the n bit codeword and  $G_{k\times n}$  is the generator matrix of the code and m is the k-bit message.

At first glance, encoding might seem to be a computationally extensive task, since all the parity check equations should satisfy, which can be in quadratic relation with the code length. But in reality, encoding can be done very efficiently and the encoding complexity can be a fraction of the decoding complexity. Several low complexity algorithms exist for the encoding of the LDPC codes. Some techniques exploit the sparseness of the parity check matrix for efficient encoding. Another approach is to impose some structure to the Tanner graph so that the encoding is transparent and simple. Repeat –Accumulate codes are examples of structured graphs.

#### 2.5.1 Gaussian Elimination

Gaussian elimination represents the most straightforward way to encode a generic LDPC code [17]. With Gaussian elimination the check constraint matrix H can be put in the following form by permutation of its rows and columns:

$$H = \left(H^{(u)}, H^{(p)}\right)$$

(2.11)

$H^{(u)}$  is the  $(n-k)\times k$  systematic part and  $H^{(P)}$  the parity part of H. Matrix  $H^{(u)}$  is sparse, while  $H^{(P)}$  is a lower triangular matrix with size n-k:

$$H^{(P)} = \begin{pmatrix} 1 & 0 & 0 \\ x & 1 & 0 & 0 \\ x & x & 1 \cdots & 0 \\ \vdots & & & \\ x & x \cdots & 1 \end{pmatrix}$$

(2.12)

where  $x = \{1,0\}$ . This approach allows the encoder to determine the parity bits of the codeword by means of so called back substitution. With the same notation, it is easy to show that the encoding problem ends up in solving the following set of equations:

$$p_{i} = \sum_{i=0}^{k-1} H_{i,i}^{(u)} u_{i} + \sum_{i=0}^{l-1} H_{i,i}^{(p)} p_{i}$$

(2.13)

which are successively computed for  $l = 0,1,\dots,n-k-1$ . It can be proven that the complexity of the encoding process is proportional to the square of information bit size,  $O(n^2)$ .

#### 2.5.2 Efficient Encoding Techniques

Several techniques are currently used to reduce the encoding complexity such as the one proposed by Urbanke and Richardson [18]. They show that the encoding is accomplished in two steps, a preprocessing step, which is an offline calculation performed once only for the given code, and the actual encoding step which is the only data-dependent part.

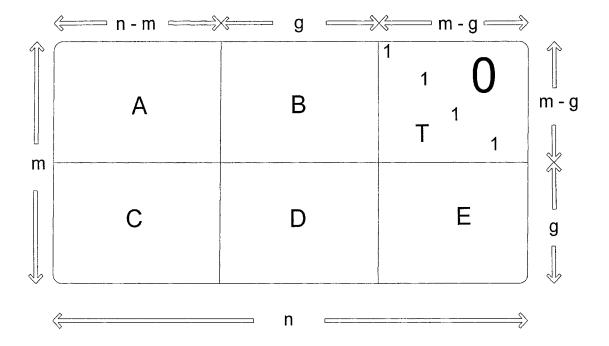

The efficiency of the encoder is proportional to the sparseness of the parity-check matrix H and the algorithm can be applied to any sparse H. If by performing row and column permutations we convert the parity-check matrix into the form indicated in Figure 2.10, we say that H is in the approximate lower triangular form.

Figure 2.10: The parity check matrix in approximate lower triangular form

The matrix in Figure 2.10 can be shown as,

$$H = \begin{pmatrix} A & B & T \\ C & D & E \end{pmatrix} \tag{2.14}$$

where A is  $(m-g) \times (n-m)$ , B is  $(m-g) \times g$ , T is  $(m-g) \times (m-g)$ , C is  $g \times (n-m)$ , D is  $g \times g$  and finally E is  $g \times (m-g)$ . Further, all of these matrices are sparse and T is lower triangular with ones along the diagonal. Multiplying this matrix from the left by

$$\begin{pmatrix} I & 0 \\ -ET^{-1} & I \end{pmatrix} \tag{2.15}$$

we obtain

$$\begin{pmatrix}

A & B & T \\

-ET^{1}A+C & -ET^{1}B+D & 0

\end{pmatrix}$$

(2.16)

If  $x = (s, p_1, p_2)$  where s denotes the systematic part,  $p_1$  and  $p_2$  combined denote the parity part,  $p_1$  has length g and  $p_2$  has length (m-g), then we can define the equation  $Hx^T = 0^T$  naturally into the two following equations:

$$As^{T} + Bp_{1}^{T} + Tp_{2}^{T} = 0 (2.17)$$

$$(-ET^{-1}A + C)S^{T} + (-ET^{-1}B + D)p_{1}^{T} = 0$$

(2.18)

By defining as  $\phi = -ET^{-1}B + D$  and assuming that  $\phi$  is non singular, then we conclude from (2.18) that

$$p_{1}^{T} = -\phi^{-1}(-ET^{-1}A + C)s^{T}$$

(2.19)

$$p_{2}^{T} = -T^{-1}(As^{T} + Bp_{1}^{T}) (2.20)$$

The proposed encoding procedure can be summarized in two steps: a preprocessing step and actual encoding step. In the preprocessing step, we first perform row and column permutations to bring the parity check matrix into approximate lower triangular form with small gap.

#### 2.5.3 Semi-random LDPC

In semi-random LDPC the parity check matrix features some regularity which is used to reduce the encoding complexity. There are two main examples of semi-random LDPC:

- $\pi$  rotation LDPC codes [19].

- Codes proposed by Hughes Network Systems [20] for the DVB-S2 standard [14].

As we show, matrix H splits into two parts which corresponds to the systematic and parity bits of the codeword. Matrix  $H^{(u)}$  is a random matrix, whilst  $H^{(p)}$  is bidiagonal.

$$H^{(p)} = \begin{pmatrix} 1 & 0 & & \cdots & 0 \\ 1 & 1 & 0 & & \cdots & 0 \\ 0 & 1 & 1 & 0 \cdots & 0 \\ 0 & 0 & 1 & 1 & 0 \cdots & 0 \\ \vdots & & & & & \\ 0 \cdots & & & 1 & 1 \end{pmatrix}$$

(2.21)

From equation (2.9) we can write:

$$H^{(u)} u^{T} + H^{(p)} p^{T} = 0 (2.22)$$

or equivalently:

$$H^{(u)}.u^T = H^{(p)}.p^T = z.$$

(2.23)

To encode one frame at first, we solve  $H^{(u)}.u^T=z$ , which in overall calls for  $k.(d_c-1)$  XOR's (assume regular LDPC code). Then, the redundant bit should be computed through back substitution:

$$\begin{cases}

p_0 = z_0 \\

p_i = z_i + p_{i-1}

\end{cases} \qquad l = 1, 2, \dots, n - k - 1$$

(2.24)

It should be noted that all the computations for the encoding are on binary values. So, instead of adders and multipliers, XORs and AND gates can be used which are cheaper. As back substitution only requires n - k - 1 XOR's, the overall computational complexity amounts to  $n(1-R)d_{\epsilon} - 1 \approx O(n)$ .

Matrix H must also be stored in a memory and from sparseness of this matrix it is efficient to store only the address of its non-zero elements, so the resulting memory requirement is:

$$(n-k).(d_c-2).q$$

(2.25)

where  $q = \log_2 n$  is the number of bits used to represent the addresses of the '1's within a row of H.

# 2.6 LDPC Decoding

Decoding of LDPC codes is an iterative message passing algorithm. The reason for their name is that at each round of the algorithm, messages are passed from message (bit) nodes to check nodes, and from check nodes back to message nodes [21]. The messages from message nodes to check nodes are computed based on the observed value of the message node and some of the messages passed from the neighboring check nodes to that message node. One important subclass of message passing algorithms is the belief propagation algorithm. The messages passed along the edges in this algorithm are probabilities or beliefs. More precisely, the message passed from a message node  $\nu$  to a check node  $\ell$  is the probability that  $\ell$  has a certain value given the observed value of that message node, and all the values communicated to  $\nu$  in the prior round from check

nodes incident to v other than c. On the other hand, the message passed from c to v is the probability that v has a certain value given all the messages passed to c in the previous round from message nodes other than v.

In order to describe the iterative decoding, we need to use a Tanner graph for LDPC coding. We have to, because the messages are passing along the edges of the Tanner graph. Local computations are done in each node of the graph. To facilitate the subsequent iterative processing, the graph must be designed as sparse as possible. Although that approach can be suboptimal, it is usually quite close to optimal and has an excellent complexity versus performance trade off.

# 2.6.1 Bit Flipping Algorithm

In this section we explain a simple hard decision decoding algorithm which is known as "bit flipping algorithm" [6]. It is interesting to use this algorithm in very high speed applications, such as optical networks. Despite its lower performance, bit flipping algorithm has lower complexity advantage over message passing. This algorithm works based on the hard decision of the received signal and the messages are considered to be single bits.

The idea behind this algorithm is to flip the least number of bits until all the check constraints are satisfied. Assume that each bit node starts with a value of either zero or one. In each iteration, the bit node decides to flip its value or to keep it unchanged. When large numbers of neighboring check equations are unsatisfied, the bit node decides to flip its value. The algorithm has been considered from the assumption that the bit node value in error has the most number of unsatisfied check equations. This process is repeated

until all the parity check constraints are satisfied, at this point the modified received sequence is a codeword. This decoding is an iterative decoding algorithm. For error patterns whose number of errors is less than or equal to the error-correcting capability of the code, the decoding will be completed in one or few iterations. Otherwise, more decoding iterations are needed. Therefore, the number of decoding iterations is a random variable and is a function of the channel SNR. A limit may be set on the number of iterations. When this limit is reached, the decoding process is terminated to avoid excessive computations. Owing to the nature of low-density parity checks, bit flipping decoding algorithm corrects many error patterns whose number of errors exceeds the error-correcting capability of the code. This process is easier when H is low density, when only a few bits are involved in each check equation and each bit is involved in only a few equations. A very simple BF decoding algorithm is given here:

- Compute the parity check sums (syndrome bits). If all the parity check sums are zero, stop the decoding.

- Find the number of failed parity check equations for each bit, denoted by  $f_i \ , i=0,1,\cdots,n-1 \, .$

- Identify the set s of bits for which  $f_i$  is the largest.

- Flip the bits in set s.

- Repeat steps 1 to 4 until all the parity check sums are zero or a preset maximum number of iterations is reached.

## 2.6.2 The Sum-Product Algorithm

The sum-product algorithm is an iterative decoding algorithm based on belief propagation that is extremely efficient for decoding LDPC codes. This algorithm is a

symbol-by-symbol soft-in, soft-out decoding algorithm. It processes the received symbols iteratively to improve the reliability of each decoded code symbol. With sparse parity-check matrix H of an LDPC code, parity-check sums are computed from the hard decisions of the received symbols in an iterative manner. The computed reliability measures of the code symbols at the end of the each decoding iteration are used as input for the next iteration. The decoding iteration process continues until a certain stopping condition (or criteria) is satisfied. Then, based on the computed reliability measures of code symbols, hard decisions are made.

To perform this decoding type, real number addition, subtraction, multiplication, division, exponential and logarithm operations are needed. The computational complexity and decoding delay (or decoding time) of the sum product algorithm increases when the number of iterations increases. Long decoding delays are not desirable in high speed communication and data storage systems.

With sum product algorithm, the error performance of an LDPC code depends on several important parameters:

- the girth of its Tanner graph;

- The minimum distance;

- the column and row weights of the parity-check matrix;

- the number of minimum weight codeword.

#### 2.7 Code Performance

The performance of a coded communication system is generally measured by probability of bit error (BER) rate. A coded communication system should be designed to

keep the bit error rate as low as possible under certain system, such as power, bandwidth and decoding complexity.

The other performance measure of a coded communication system is the coding gain. Coding gain is defined as the reduction in the  $E_b/N_o$  required to achieve a specific error probability (BER) for a coded communication system compared to an uncoded system. In low values of  $E_b/N_o$ , the coding gain becomes negative. There exists a specific value for SNR which is called coding threshold. Any SNR below this threshold degrades the performance of a coded system compared to uncoded one. It is important to keep this threshold low and to be sure that the code system operates at higher than this threshold.

Another method that measures the code power is gap to Shannon limit. Shannon limit is based on Shannon noisy coding theorem [4]. This theoretical limit says that for coded system with code rate R, error free communication is achievable only if the SNR exceeds this limit. As long as the SNR exceeds this limit, Shannon's coding theorem guarantees the existence of a coded system capable of achieving error free communication. For transmission over a binary input, continuous output AWGN channel with BPSK modulation, the Shannon limit (in terms of  $E_b/N_o$ ) as a function of code rate R does not have a closed form, however, it can be evaluated numerically. Table 2.1 shows the Shannon limit as a function of the code rate R for BPSK modulation on a continuous output AWGN channel [16]. Gap from Shannon limit can be reduced by using a longer and more powerful code, decoded with an efficient soft decision MLD or near MLD algorithm.

Table 2.1: Shannon limit of a continuous output AWGN channel with BPSK signaling for various code rates R

| R    | $E_b/N_o(dB)$ | R    | $E_b/N_o(dB)$ | R     | $E_b/N_o(dB)$ | R     | $E_b/N_o(dB)$ |

|------|---------------|------|---------------|-------|---------------|-------|---------------|

| 0.01 | -1.548        | 0.35 | -0.432        | 0.69  | 1.208         | 0.954 | 4.304         |

| 0.02 | -1.531        | 0.36 | -0.394        | 0.70  | 1.275         | 0.958 | 4.425         |

| 0.03 | -1.500        | 0.37 | -0.355        | 0.71  | 1.343         | 0.961 | 4.521         |

| 0.04 | -1.470        | 0.38 | -0.314        | 0.72  | 1.412         | 0.964 | 4.618         |

| 0.05 | -1.440        | 0.39 | -0.276        | 0.73  | 1.483         | 0.967 | 4.725         |

| 0.06 | -1.409        | 0.40 | -0.236        | 0.74  | 1.554         | 0.970 | 4.841         |

| 0.07 | -1.378        | 0.41 | -0.198        | 0.75  | 1.628         | 0.972 | 4.922         |

| 0.08 | -1.347        | 0.42 | -0.156        | 0.76  | 1.708         | 0.974 | 5.004         |

| 0.09 | -1.316        | 0.43 | -0.118        | 0.77  | 1.784         | 0.976 | 5.104         |

| 0.10 | -1.285        | 0.44 | -0.074        | 0.78  | 1.867         | 0.978 | 5.196         |

| 0.11 | -1.254        | 0.45 | -0.032        | 0.79  | 1.952         | 0.980 | 5.307         |

| 0.12 | -1.222        | 0.46 | 0.010         | 0.80  | 2.045         | 0.982 | 5.418         |

| 0.13 | -1.190        | 0.47 | 0.055         | 0.807 | 2.108         | 0.983 | 5.484         |

| 0.14 | -1.158        | 0.48 | 0.097         | 0.817 | 2.204         | 0.984 | 5.549         |

| 0.15 | -1.126        | 0.49 | 0.144         | 0.827 | 2.302         | 0.985 | 5.615         |

| 0.16 | -1.094        | 0.50 | 0.188         | 0.837 | 2.402         | 0.986 | 5.681         |

| 0.17 | -1.061        | 0.51 | 0.233         | 0.846 | 2.503         | 0.987 | 5.756         |

| 0.18 | -1.028        | 0.52 | 0.279         | 0.855 | 2.600         | 0.988 | 5.842         |

| 0.19 | -0.995        | 0.53 | 0.326         | 0.864 | 2.712         | 0.989 | 5.927         |

| 0.20 | -0.963        | 0.54 | 0.374         | 0.872 | 2.812         | 0.990 | 6.023         |

| 0.21 | -0.928        | 0.55 | 0.424         | 0.880 | 2.913         | 0.991 | 6.119         |

| 0.22 | -0.896        | 0.56 | 0.474         | 0.887 | 3.009         | 0.992 | 6.234         |

| 0.23 | -0.861        | 0.57 | 0.526         | 0.894 | 3.114         | 0.993 | 6.360         |

| 0.24 | -0.827        | 0.58 | 0.574         | 0.900 | 3.205         | 0.994 | 6.495         |

| 0.25 | -0.793        | 0.59 | 0.628         | 0.907 | 3.312         | 0.995 | 6.651         |

| 0.26 | -0.757        | 0.60 | 0.682         | 0.913 | 3.414         | 0.996 | 6.837         |

| 0.27 | -0.724        | 0.61 | 0.734         | 0.918 | 3.500         | 0.997 | 7.072         |

| 0.28 | -0.687        | 0.62 | 0.791         | 0.924 | 3.612         | 0.998 | 7.378         |

| 0.29 | -0.651        | 0.63 | 0.844         | 0.929 | 3.709         | 0.999 | 7.864         |

| 0.30 | -0.616        | 0.64 | 0.904         | 0.934 | 3.815         |       |               |

| 0.31 | -0.579        | 0.65 | 0.960         | 0.938 | 3.906         |       |               |

| 0.32 | -0.544        | 0.66 | 1.021         | 0.943 | 4.014         |       |               |

| 0.33 | -0.507        | 0.67 | 1.084         | 0.947 | 4.115         |       |               |

| 0.34 | -0.469        | 0.68 | 1.143         | 0.951 | 4.218         |       |               |

# Chapter 3

# A New Parity Check Matrix for LDPC

# Code Suitable for DVB-S2

# 3.1 Organization of the Parity Check Matrix

As mentioned before in chapter 2 LDPC codes have recently been selected as the forward error correcting scheme for the new generation satellite Digital Video Broadcasting (DVB-S2) [14].

LDPC codes for DVB-S2 are semi-random and has parity check matrix as in 2.11. A high degree of regularity in random part of the matrix  $H^{(u)}$  helps to implement highly parallelized decoder architectures.

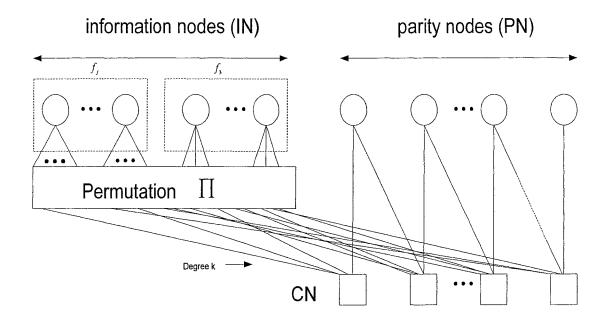

The LDPC codes as defined in the DVB-S2 standard are IRA codes, thus the encoder realization is straightforward. Furthermore, the DVB-S2 code shows regularities which can be exploited for an efficient hardware realization [22]. This type of LDPC codes can be represented by a bipartite graph. The Tanner graph for DVB-S2 is shown in Figure 3.1. For the DVB-S2 code, 64800 variable nodes (VN) and  $64800 \times (1-R)$  check nodes exist. LDPC codes can be specified through their parity check matrices. For LDPC code in DVB-S2 certain structure is imposed on parity check matrix H. The main criteria for parity check matrix structure is having low complex encoding and decoding algorithm.

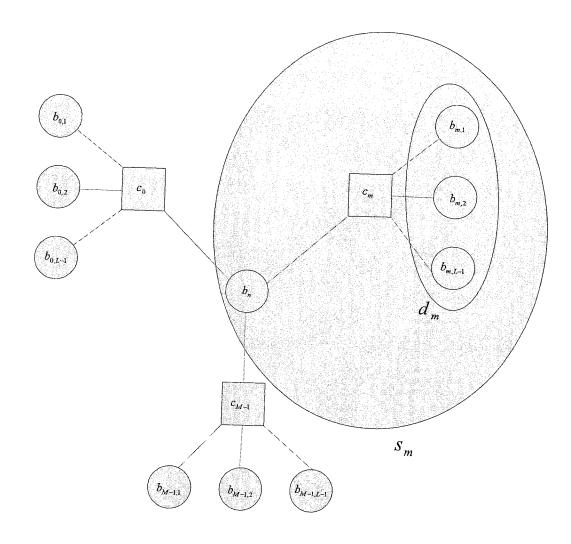

Figure 3.1: Tanner graph for the DVB-S2 LDPC code

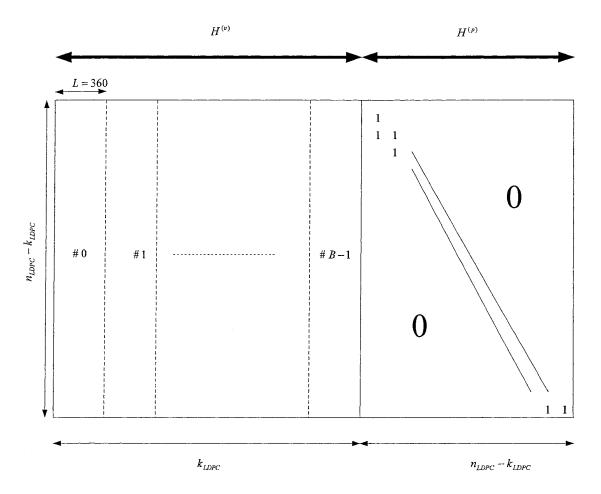

To understand the organization of the DVB-S2 parity check matrix; let us see Fig 3.2 that focuses on the code rate  $R = k_{LDPC} / n_{LDPC}$ . If we assume block length of  $n_{LDPC} = 64800$ , therefore the information word is  $k_{LDPC} = n_{LDPC} \times R$ . Placement of the '1's into the parity check matrix is performed by resorting to code specific table that assembles the base address of the parity check matrix. More precisely we just assign the placement of the '1's into a set of L = 360 consecutive columns of the parity check matrix  $H^{(u)}$ . As a consequence, the parity check matrix is split overall into  $B = k_{LDPC} / L$  blocks. This is graphically depicted in Figure 3.2.

Within a block, the '1's are placed according to the base addresses specified in the table. There is an address in the table for each sub-block of  $H^{(u)}$ . In particular, if we show the sub-blocks of  $H^{(u)}$  with  $b=0,1,\ldots,B-1$ , the '1's of the b th block are placed at the locations (i,j) where:

- $i \in [0, n_{LDPC} k_{LDPC} 1]$  is the row address determined from the table.

- $j = 0, \dots, L-1$  is the column address related to the current block.

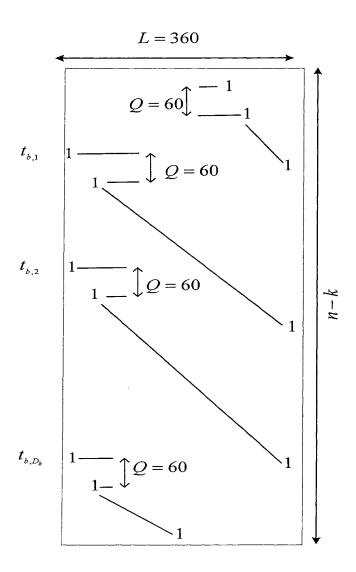

Figure 3.2: Organization of the parity check matrix of the DVB-S2 with code rate R

The DVB-S2 codes exhibit certain regularity that row addresses of the '1's are computed in a deterministic way from the table. If  $D_b$  is the bit node degree of the bit nodes in the b th block (degree  $D_b$  is common to any bit node within block b) and  $t_{b,d}$  is the address of '1's in the first column that exist in table and  $d=0,1,\ldots,D_b-1$ . In

each column of the block, the location of the non-zero elements is formed by the following algorithm:

$$i = \left| t_{b,d} + j.Q \right|_{(n_{LDPC} - k_{LDPC})} \tag{3.1}$$

In the above equation, i is in the range  $[0, n_{LDPC} - k_{LDPC} - 1]$ , j is the column index (relative to block b) and  $Q = \frac{n_{LDPC} - k_{LDPC}}{I_c}$  is a code-dependent parameter (for example for R = 2/3  $Q = \frac{64800 - 43200}{360} = 60$ ). Address table gives the address of the '1's of the first column of the current block then the remaining '1's are derived from these base addresses and the above algorithm. For better illustration, the generic structure of a subblock of H is plotted in Fig 3.3. As we know, address table does not specify the same bit node degree for any sub-block of the parity check matrix because of the DVB-S2 codes are irregular. For example for code rate R = 2/3 [14], the first twelfth sub-blocks has weight 13  $(D_b = 13, b = 0, 1, ..., 11)$  and the following B - 12 = 102 blocks has weight 3  $(D_b = 3, b = 12, 13, \dots, B-1)$ . This means that  $12 \times L = 4320$  bit nodes out of 64800 have degrees 13 and  $102 \times L = 36720$  have degree 3. The remaining bit nodes are only involved in the parity part  $H^{(p)}$  of H, therefore their degree is simply 2 (except the last bit node, whose degree is 1). The list of bit node degrees and the total number of nodes with those degrees are shown in table 3.1 for all code rates. For each code rate, a parity check matrix is specified by listing adjacent check nodes for the first bit node in a group of L = 360. For a group of L bit nodes, if the check nodes connected to the ith bit node

of degree, say  $D_b$  are numbered as  $c_1, c_2, c_3, \dots, c_{D_b}$  then the check nodes connected to the j th bit node  $(j \le L)$  are numbered as:

$$\{c_1 + jQ\} \operatorname{mod}(n_{LDPC} - k_{LDPC}), \dots, \{c_{D_b} + jQ\} \operatorname{mod}(n_{LDPC} - k_{LDPC})$$

(3.2) where  $n_{LDPC} - k_{LDPC} = \operatorname{total}$  number of check nodes [23].

For the following groups of L bit nodes, the check nodes connected to the first bit node of the group are in general randomly chosen so that the resulting LDPC code is cycle-4 free and occurrence of cycle-6 is minimized. Too many short cycles (such as cycle-4 and cycle-6) in bipartite graph decreases the code performance since they lead to non-extrinsic information being fed back after a small number of iterations.

From the above description, it is clear that the adjacent check nodes of only one bit node need to be specified in a group of L, simplifying the code description by a factor of L. In DVB-S2 standard, L is equal to 360.