# First Order Model Checking of $\omega$ -Automata using Multiway Decision Graphs

Fang Wang

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy at Concordia University Montréal, Québec, Canada

Apirl 2005

© Fang Wang, 2005

Library and Archives Canada

Branch

Published Heritage

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-494-05723-8 Our file Notre référence ISBN: 0-494-05723-8

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

#### Abstract

# First Order Model Checking of $\omega$ -Automata using Multiway Decision Graphs

Fang Wang, Ph.D.Concordia University, 2005

As the complexity of hardware digital systems increases, their correctness becomes a major concern. Traditional verification by simulation is infeasible to exhaustively test and guarantee correctness. More than a decade ago, however, formal verification has been introduced as complement technique to simulation. Formal methods establish that a design implementation satisfies its specification by mathematical reasoning. Among several techniques, model checking is one of the most successful technology, which is based on the exploration of the design state space. In this thesis, we propose a new model checking method based on the theory of  $\omega$ -automata and multiway decision graphs (MDGs). Unlike reduced ordered binary decision diagrams (ROBDDs), MDGs allow system models to be described using abstract state machines (ASMs) through abstract data sorts and uninterpreted function symbols, hence enabling the verification of larger designs independent of the datapath width.

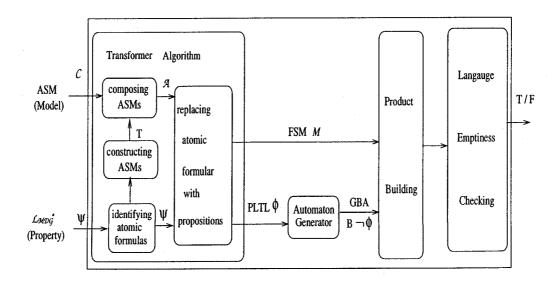

Given an ASM and a first-order linear time temporal logic property, the model checking problem proposed in this thesis is reduced to a language emptiness checking of an  $\omega$ -automaton that accepts all  $\omega$ -words produced by the system violating the property formula. The checking method comprises four steps: (1) transforming the first-order property into a propositional formula by constructing ASMs for the

atomic formulas of the property; (2) generating an  $\omega$ -automaton from the negation of the transformed propositional formula; (3) computing the product of the generated automaton, the system model ASM and the constructed ASMs; and (4) applying a language emptiness checking algorithm on the product automaton. Three different checking algorithms have been developed, implemented, and proved correct in this thesis.

To evaluate the performance of the proposed model checking method and implemented tool, we conducted several experimentations and case studies. We also compared the efficiency of our tool with an existing MDG regular model checking application, as well as with popular ROBDD-based automata model checking tools such as VIS. Our model checker was found to be outperforming the above tools.

# Acknowledgments

First and foremost, I would like to express my heartfelt thanks to my supervisor, Dr. Sofiène Tahar, for his extensive time, extreme patience, valuable suggestions and constant encouragement during my entire doctoral studies. It is he who looks after me as an international student, academically, financially and socially, always with great responsibility, which I appreciate so much and will always remain deeply in my memory.

I am especially grateful to thank Dr. Otmane Ait Mohamed for many discussions and helpful suggestions, which are invaluable to this thesis. I would like also to thank my PhD committee members: Dr. J. Chen, Dr. Xiaoyu Song, Dr. J. Paquet, Dr. V. Ramachandran, and Dr. O. Ait Mohamed for reviewing my thesis and giving me invaluable feedbacks.

Furthermore, I would like to thank my friends and fellow graduate students in the hardware verification group (HVG) for their help and discussions.

Last, but not least, I would like to thank all my family for their support and encouragement for my studies.

# Contents

| Li | st of | Figures                                        | ix |

|----|-------|------------------------------------------------|----|

| Li | st of | Tables                                         | xi |

| 1  | Intr  | roduction                                      | 1  |

|    | 1.1   | Background                                     | 2  |

|    | 1.2   | Related Work                                   | 4  |

|    | 1.3   | Scope of the Thesis                            | 7  |

|    | 1.4   | Outline of the Thesis                          | 8  |

| 2  | Mul   | ltiway Decision Graphs                         | 10 |

|    | 2.1   | Formal Logic                                   | 10 |

|    |       | 2.1.1 Syntax                                   | 10 |

|    |       | 2.1.2 Semantics                                | 12 |

|    | 2.2   | Directed Formulas                              | 13 |

|    | 2.3   | Multiway Decision Graphs                       | 14 |

|    |       | 2.3.1 Basic MDG Algorithms                     | 15 |

|    | 2.4   | Abstract State Machine (ASM)                   | 18 |

|    |       | 2.4.1 Representing Sets using MDGs             | 18 |

|    |       | 2.4.2 Describing ASM with MDGs                 | 18 |

|    |       | 2.4.3 State Exploration and Invariant Checking | 20 |

|    | 2.5   | MDG Verification Applications                  | 22 |

|    | 2.6   | Conclusion                                     | 25 |

| 3  | Mod   | del Checking and $\omega$ -Automata            | 26 |

|    | 3.1   | Kripke Structure                               | 26 |

|    |       | 3.1.1 ROBDD Representation                     | 27 |

|    |       | 3.1.2 Bisimulation Relation                    | 28 |

|    | 3.2   | $\omega$ -Automata Theory                      | 29 |

|    | 3.3   | Property Specification Language                | 31 |

|    |       | 3.3.1 Propositional Logic                      | 31 |

|    |       | 3.3.2 First Order Logic                        | 32 |

|   |     | 3.3.3 Temporal Logics                          |

|---|-----|------------------------------------------------|

|   |     | 3.3.4 Comparison of Logics                     |

|   | 3.4 | $\omega$ -Automata based Model Checking 4      |

|   |     | 3.4.1 Constructing Büchi Automaton from LTL 4  |

|   |     | 3.4.2 Product Operating of Büchi Automaton     |

|   |     | 3.4.3 Language Emptiness Checking Algorithms 4 |

|   | 3.5 | Conclusion                                     |

| 4 | ME  | G Language Emptiness Checking Approach 5       |

|   | 4.1 | The Structure of the MDG LEC                   |

|   | 4.2 | $\mathcal{L}_{MDG}^*$                          |

|   | 4.3 | Transformation Algorithm                       |

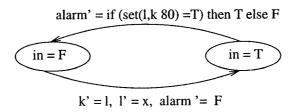

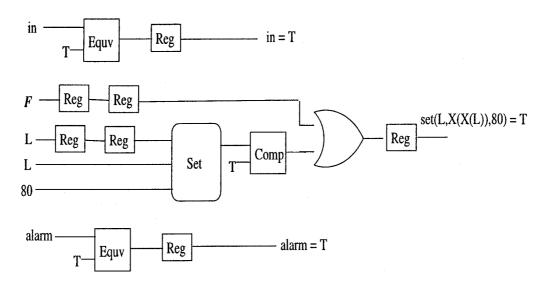

|   | 1.0 | 4.3.1 Example: An Alarm Setting Controller     |

|   |     | 4.3.2 Transformation Algorithm                 |

|   |     | <b>O</b>                                       |

|   | 4.4 | • • •                                          |

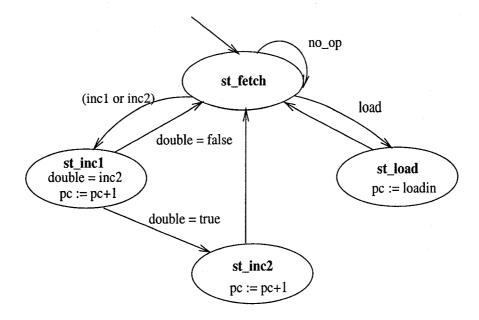

|   | 4.4 | An Example: Abstract Counter                   |

|   | 4.5 | Conclusion                                     |

| 5 |     | G LEC Algorithms 70                            |

|   | 5.1 | Preliminaries                                  |

|   |     | 5.1.1 Generalized Büchi Automaton and MDG      |

|   |     | 5.1.2 Graph and SCC                            |

|   | 5.2 | MDG EL/EL2 Algorithms                          |

|   |     | 5.2.1 Generic SCC Hull Algorithm               |

|   |     | 5.2.2 EL/EL2 Algorithms                        |

|   |     | 5.2.3 MDG EL/EL2 Algorithms                    |

|   | 5.3 | MDG Fair Cycle Detection Algorithm             |

|   | 0.0 | 5.3.1 FCD Algorithm                            |

|   |     | 5.3.2 MDG FCD Algorithm                        |

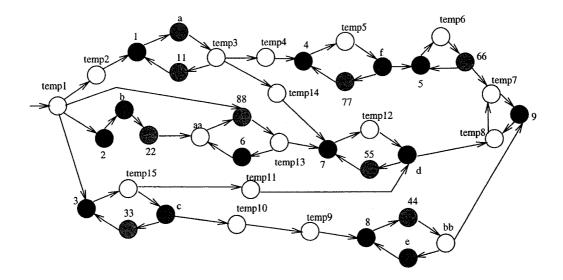

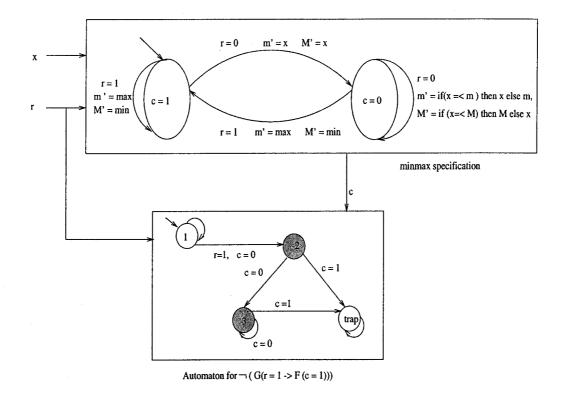

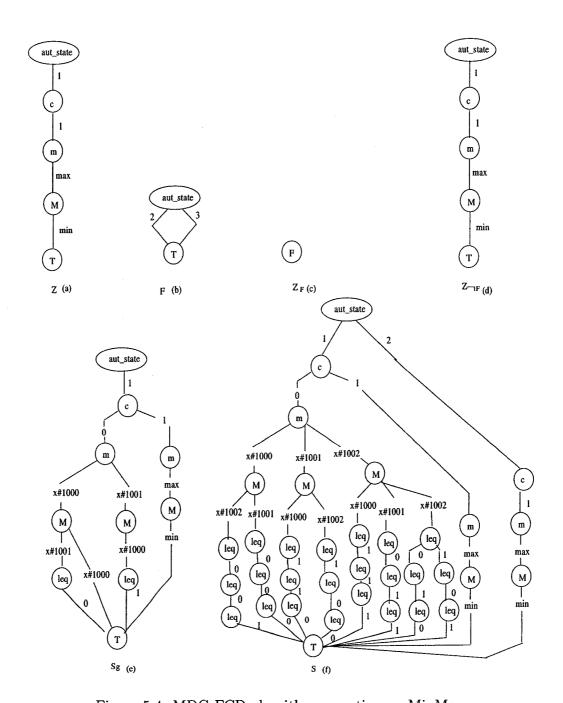

|   |     | 5.3.3 An Example: MinMax                       |

|   | 5.4 | Conclusion                                     |

|   |     |                                                |

| 6 |     | e Studies 9'                                   |

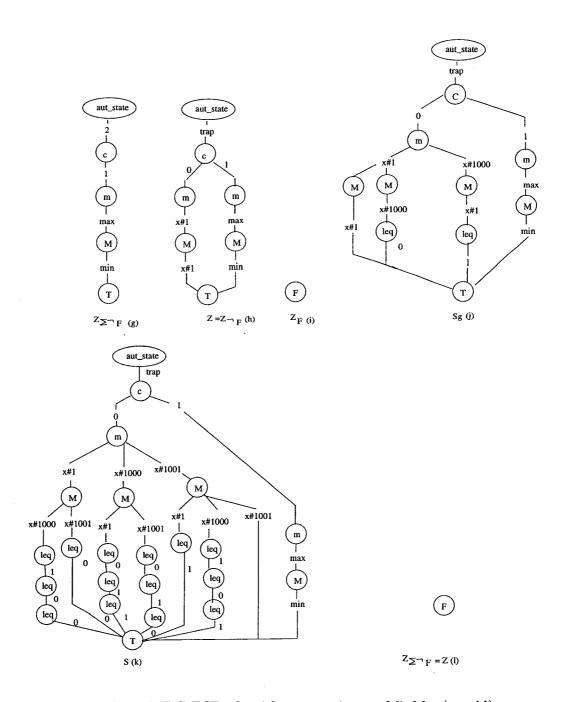

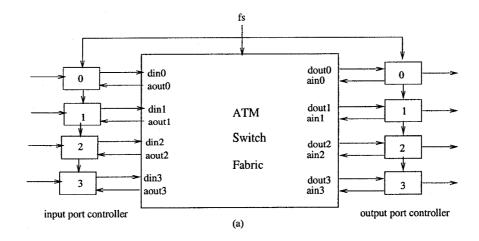

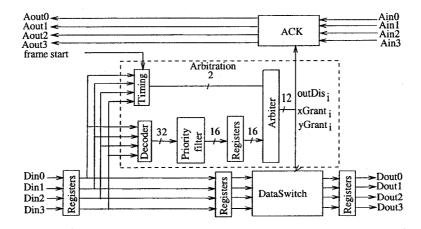

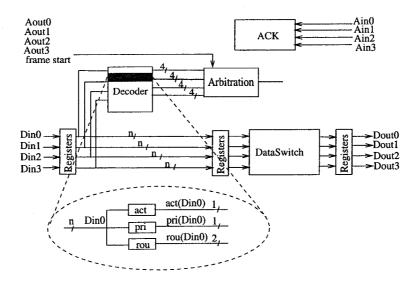

|   | 6.1 | ATM Switch Fabric                              |

|   |     | 6.1.1 System Description                       |

|   |     | 6.1.2 System Model                             |

|   |     | 6.1.3 Verification                             |

|   |     | 6.1.4 Discussion                               |

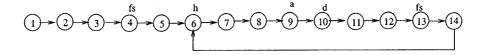

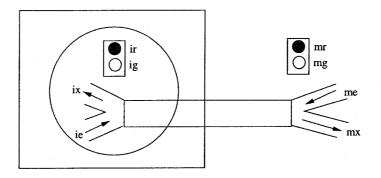

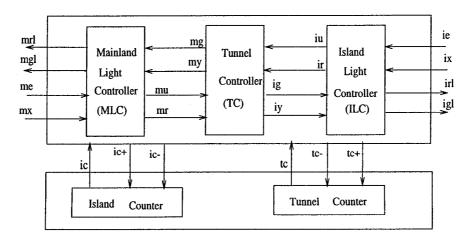

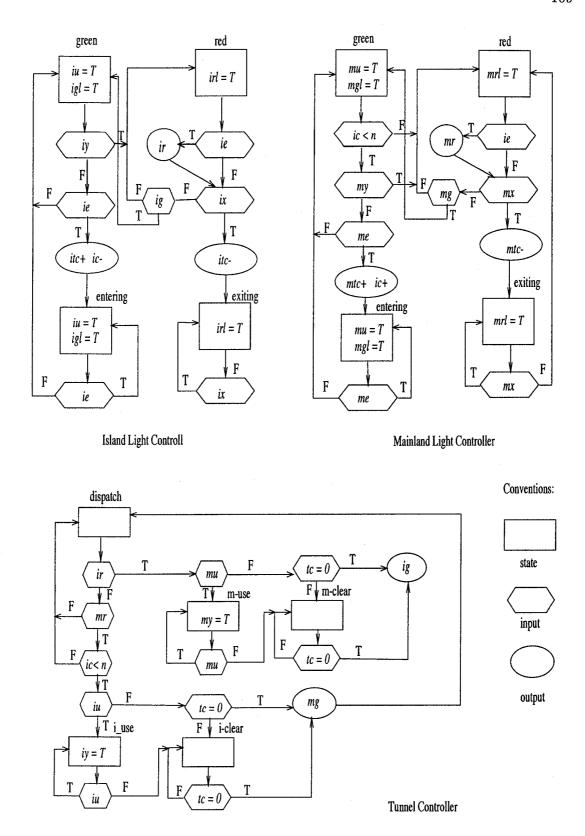

|   | 6.2 | Island Tunnel Controller                       |

|   |     | 6.2.1 System Description                       |

|   |     | 6.2.2 System Model                             |

|   |     | 6.2.3 Varification 100                         |

|              | 6.3 | 6.2.4 Discussion                |                |

|--------------|-----|---------------------------------|----------------|

| 7            |     | aclusions Summary of the Thesis | <b>110</b> 110 |

|              |     | Future Research Directions      |                |

| Bibliography |     |                                 |                |

# List of Figures

| 2.1<br>2.2<br>2.3                                                   | An MDG example                                  | 15<br>20<br>23                                     |

|---------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------|

| 3.1<br>3.2<br>3.3                                                   | An example of the bisimulation relation         | 28<br>29<br>45                                     |

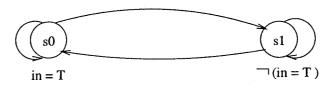

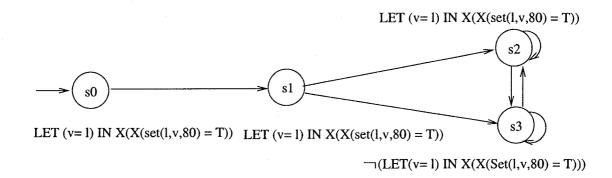

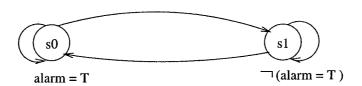

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10 | An alarm setting controller                     | 51<br>56<br>57<br>58<br>58<br>59<br>60<br>63<br>67 |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5                                     | An example of a GBA                             | 72<br>74<br>93<br>95<br>96                         |

| 6.1<br>6.2<br>6.3<br>6.4                                            | The header (routing tag) of a Fairisle ATM cell | 98<br>98<br>99<br>00                               |

| 6.5 | The ATM Switch Fabric environment                       | 101 |

|-----|---------------------------------------------------------|-----|

| 6.6 | The Island Tunnel Controller                            | 104 |

|     | The specification of the Island Tunnel Controller       |     |

| 6.8 | State transition graphs of the Island Tunnel Controller | 109 |

# List of Tables

| 6.1 | Experimental results with MDG LEC using EL and EL2 for ATM   | 102 |

|-----|--------------------------------------------------------------|-----|

| 6.2 | Experimental results with VIS using EL algorithm for ATM     | 103 |

| 6.3 | Experimental results with VIS using EL2 algorithm for ATM    | 103 |

| 6.4 | Experimental results with MDG FCD algorithm and MDG MC algo- |     |

|     | rithms for the ITC                                           | 107 |

# List of Acronyms

ASM Abstract State Machine

ATM Asynchronous Transfer Mode

BTTL Branching Time Temporal Logic

CTL Computation Tree Logic

DNF Disjunctive Normal Form

FCD Fair Cycle Detection

FO First Order

FOBTL First Order Branching time Temporal Logic

FOTL First Order Temporal Logic

FOLTL First Order Linear time Temporal Logic

FSM Finite State Machine GSH Generic SCC-Hull

GBA Generalized Büchi Automata

ITC Island Tunnel Controller LC Language Containment

LEC Language Emptiness Checking

LHS Left Hand Side

MC Model Checking

MDG Multiway Decision Graph

PLTL Propositional Linear time Temporal Logic

PTL Propositional Temporal Logic

ReAn Reachability Analysis

RHS Right Hand Side

ROBDD Reduced Ordered Binary Decision Diagrams

RTL Register Transfer Level

SCC Strongly Connected Component

TL Temporal Logic

# Chapter 1

## Introduction

During the last decades, technological advances in microelectronics have greatly increased the complexity of digital hardware designs. Their correctness thus becomes a major concern, especially in critical applications where failure is unacceptable. Traditionally, simulation is the only tool to validate a design. Using simulation, the designer needs to create a set of test vectors that represents the possible inputs to the system. The outputs for each of these test vectors are compared with the expected responses. This method is very costly and incomplete because of the large number of input sequences. In almost all practical situations it is infeasible to exhaustively simulate a design to guarantee its correctness.

As a complement to simulation, formal verification methods intend to establish an implementation satisfies a specification by mathematical reasoning [42]. The implementation refers to the hardware design to be verified and the specification refers to the property with respect to which correctness is to be determined. Formal verification conducts an exhaustive exploration of all the possible behaviors. Thus, when a design is pronounced correct by a formal verification method, it implies that all behaviors relative to the property have been explored [19].

Logic is a formalism to represent specification. The hierarchy of logics is arranged according to the generality of their data types and operators. In propositional logic, only propositional variables, Boolean operators and their derivations are allowed. First-order logic is much more general than propositional logic in that it allows vari-

ables over one or more other types. It also allows constant operators, functions and predicates over added types. Higher order logic is more general than first-order logic in that it allows variables and operators over functions and predicates. Therefore, functions and predicates can be defined and manipulated as objects by themselves.

Formal verification is a very broad and well studied research topic and numerous achievements have been contributed to the literature. This thesis focuses on the particular techniques of model checking based on the  $\omega$ -automata theory [79]. In this introduction, we first describe the background of this thesis. We then survey the literature and present related work. Finally, we summarize the scope of this thesis in Section 1.3 and give an outline of the thesis in Section 1.4.

## 1.1 Background

Formal verification methods can be classified in two main categories: interactive verification with a theorem prover and automated Finite State Machine (FSM) verification based on state enumeration [42].

Interactive verification with a theorem prover uses a powerful formalism such as higher order logic that allows the verification problem to be stated at many levels of abstraction. This approach has achieved significant successes in verifying microprocessor designs. However, interactive verification has the drawback that the user is responsible for coming up with the proof of correctness and feeding it to the theorem prover, which requires great expertise [37].

Automated FSM verification based on state enumeration techniques provides automation for behavior comparison and model checking. Model checking works on a finite-state model of the system to be verified and the logical specification of the desired behavior of the system model. It algorithmically checks if the finite state machine is a model of the specification formula. Since model checking can be completely automatic and has been used successfully to verify complex sequential circuit designs and communication protocols, it is emerging as an industrial standard tool for hardware design [58].

Model checking algorithms are based on exploring the reachable state space of

design models. The state space of a finite state model for a concurrent system, however, grows exponentially as the number of components of the system increases. This is known as the state explosion problem in automatic verification, which is the main challenge of model checking.

The most promising approach to tackle the state explosion problem has been the application of ROBDDs (Reduced Ordered Binary Decision Diagrams) to the representation of state graphs [10]. ROBDDs encode the set of states as well as transition and output relations and perform an implicit enumeration of the state space, making it possible to verify finite state machines with a larger number of states [5]. ROBDDs have been proved to be a powerful tool for automated hardware verification. However, because they require a Boolean representation of the circuit, ROBDD-based verification cannot be directly applied to circuits with complex and large datapath [20].

To overcome this limitation, Multiway Decision Graphs (MDGs) [12] have been proposed as a new class of decision graphs, of which ROBDDs are a special case. MDGs efficiently represent a class of well formed formulas of a many-sorted first-order logic with a distinction of abstract and concrete sorts [21]. In an MDG, a data signal is represented by a single variable of abstract sort rather than by a vector of Boolean variables, and a data operation is represented by an uninterpreted function symbol. Therefore, MDGs are much more compact than ROBDDs for circuits having complex and large datapaths.

Many ROBDD based (propositional) verification methods have been generalized into a first order level and developed using MDGs. The MDG based verification tools verify designs at the Register Transfer Level (RTL) using their models of ASM (Abstract State Machine), where MDGs encode the sets of (abstract) states and transition/output relations. The current MDG verification tools include an MDG package, a reachability analysis procedure, and applications for formal hardware verification. The MDG package implements manipulation algorithms of MDGs, the reachability algorithm checks that an invariant holds on the reachable states of an ASM using abstract implicit enumeration techniques. The existing MDG tool set provides the following verification applications: combinational verification, sequential equivalence

checking, invariant checking and a first-order model checking [1, 12, 21, 81].

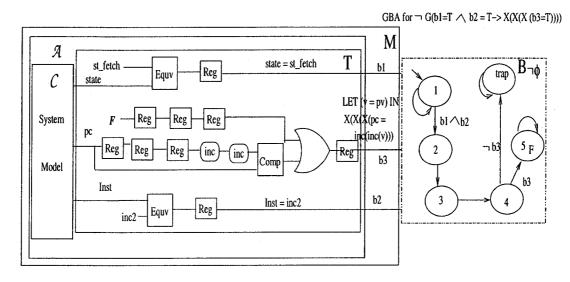

To complete the MDG tools, this thesis proposes to lift the  $\omega$ -automata based model checking method to a First-order Temporal Logic (FTL) model checking using MDGs.  $\omega$ -automata based model checking is a well studied and widely used model checking technique. Many research tools, such as VIS [9], SMV [62], SPIN [44] etc., have this application and the most successful commercial model checking tool FormalCheck [58] was built on this idea. Model checking of  $\omega$ -automata accepts a FSM modeling system design and a propositional formula as the property. Both of them are transformed into  $\omega$ -automata [57], and the model checking reduces to checking if the language (behaviors) of the system automaton  $\mathcal{L}(M)$  is contained in the language (behaviors) of the property automaton  $\mathcal{L}(\mathcal{B}_{\phi})$  [57]. By constructing an  $\omega$ -automaton  $\mathcal{B}_{\neg \phi}$  accepting all the language (behaviors) violating the specification, the model checking is converted into a Language Emptiness Checking (LEC) on the product automaton  $M \times \mathcal{B}_{\neg \phi}$ . If the language is not empty, this means there is a behavior produced by the design not accepted by the specification. In this case, the specification fails on the design. Otherwise, all the behaviors produced by the system are contained in the behaviors of the property, and the property is verified on the design [7, 57, 79].

In this thesis, we present a model checking based on the  $\omega$ -automata theory using MDGs. Our approach checks a first-order temporal logic specification on an abstract of the state machine model, where the data signal is described as a single variable of abstract type rather than by a vector of Boolean variables, and a data operation is represented by a function symbol rather than by vectors of Boolean variables.

#### 1.2 Related Work

The application of symbolic techniques to the model checking using  $\omega$ -automata theory has been a hot topic since 1980s, and thus numerous achievements have been reported in the literature. However, lifting this method to the first-order logic is a pretty new research direction. In this section we survey relevant first-order model checking techniques available in the literature.

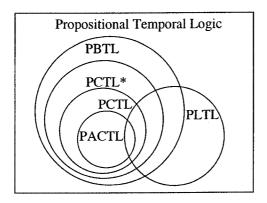

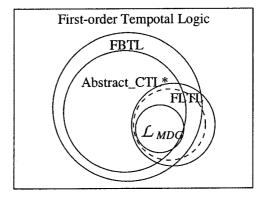

The most related work to our thesis is the MDG based regular model checking technique (MDG MC) developed by Xu et. al. [81]. They defined a first-order branching time temporal logical with accepting existential quantifications and abstract variables, called Abstract\_CTL\*. They then obtained a subset, called  $\mathcal{L}_{MDG}$  [82], by restricting  $Abstract\_CTL^*$  to the universal quantification that can only appear at the beginning of the formula, and using a limited nesting of temporal formulas. This limited nesting of  $\mathcal{L}_{MDG}$  is defined by the following templates: A(P), AG(P), AF(P), A(P)U(Q),  $AG(P \Rightarrow (F(Q))$ , and  $AG((P) \Rightarrow (Q)U(R))$ , where P, Q, and R are next-let-formulas. A next-let-formula is composed by well-typed equations, Boolean connectives and temporal operator X (nexttime). To check an  $\mathcal{L}_{MDG}$  formula  $\phi$  on an ASM M, for each next-let-formula p, MDG MC first constructs an abstract state machine. It then composes M and all the constructed ASMs to produce a composed machine P. It finally checks a simplified property on the composed machine. Both MDG MC and our proposed MDG LEC, which will be described in Chapter 4, model the system design using ASM and construct circuit descriptions for the formula to be verified; however, there are significant differences between them: First, the MDG LEC method is based on the theory of  $\omega$ -automata, and the approach uses an Language Containment (LC) checking algorithm to check the satisfaction of any property, while MDG MC uses a different checking algorithm for each property template. Second, MDG LEC uses a broader FTL, which we will call  $\mathcal{L}_{MDG}^*$ , to describe the property.  $\mathcal{L}_{MDG}^*$  breaks the template limitation of  $\mathcal{L}_{MDG}$  and allows arbitrary temporal nesting. For example, an  $\mathcal{L}_{MDG}^*$  formula  $G(a=1 \to F(b=1) \land F(c=1))$  is not allowed by  $\mathcal{L}_{MDG}$ .

Bohn et. al [6, 50] presented an algorithm for checking a First Order (FO) ACTL (a subset of computation tree logic restricted to universal quantification) specification on FO Kripke structures. The FO Kripke structure is an extension of the "ordinary" Kripke structures by transitions represented with conditional assignments. The FO ACTL algorithm models data values and operations by means of FO predicates. The algorithm separates the control parts of a system under verification from its data parts and refines the resulting model into an intermediate description that contains sufficient information about the property to be checked. The enrichment of the control

flow model introduces verification conditions, which can be generated automatically. If a property does not contain predicates on data, then ROBDD model checking is applicable. Otherwise, all FO predicates are substituted by true. If the model checking procedure reports a failure, this failure will be part of the control flow and occurs on the concrete model as well. If no failure can be found, correctness is not guaranteed in the original model since failure in the abstracted data cannot be detected. Therefore, the generated verification conditions have to be proven using a theorem prover [6, 50]. Compared to this work, our logic is less expressive since  $\mathcal{L}_{MDG}^*$  cannot accept existential quantification. However, in our approach the property is checked on the whole model automatically, while in [6, 50] a theorem prover is needed to validate the first-order verification conditions. Besides, our method can be applied to any finite state models, while their application was limited to designs with a clear separation between data and control part and terminating data loops, where the control parts only allow a bounded number of computation on data.

Namjoshi and Kurshan [66] presented an algorithm to verify an FO model by a syntactic abstraction. The FO model is defined on a set of variables, and each variable has an associated domain of values. The initial states and transition relation of the model are defined as quantifier free first-order predicates. The property is described as a formula composed of  $ACTL^*$  (a subset of the branching time temporal logic restricted to universal quantification) operator and first-order predicates. To verify the FO model, they first transform it into a finite Kripke structure by the syntactic abstraction, and then proceed the model checking with a propositional model checker. The syntactic abstraction starts with the set of predicates from the property formula, iteratively computes the predicates required for the abstraction relating to that property, and represents these predicates by Boolean variables in the finite model. Compared to this work, we model the system design as an ASM, where abstract variables and uninterpreted function symbols can be used. Although our property language cannot express quantifications, it is defined on atomic formulas within temporal operator X. Furthermore, our model checking implements an on-the-fly method, namely, abstraction and model checking are proceeded in parallel.

There exists other work on abstract model checking [46, 17] which combine ab-

straction interpretation and model checking to improve the automatic verification of infinite systems. Abstraction interpretation transforms the infinite system model M into an finite model  $M^+$ . Usually  $M^+$  is an over-approximation of the original model M, which means that given a state s of M and a trace t produced by M, it is possible to find a state  $s^+$  of  $M^+$  and a trace  $t^+$  produced by  $M^+$  representing s and t, respectively. However this transformation cannot preserve the negative correctness, that is, the failure of a property in the finite model does not imply that the property will fail in the original model. Two techniques have been successfully developed to construct  $M^+$ . The predicate abstraction [17] approach consists of substituting some selected model expressions with Boolean variables, which leads to important simplification. In contrast, the data abstraction [46] method reduces the type of certain data by transforming its original domain into an approximate and simpler domain [17]. Compared to these work, our method generates an approximation model which ensures both negative preservation and positive preservation. Moreover, most of these approaches are done manually, but ours is totally automatic.

## 1.3 Scope of the Thesis

This thesis explores a model checking based on  $\omega$ -automata using MDGs. While traditional ROBDD based method accepts Finite State Machine (FSM) as the system model, our method is based on Abstract State Machine (ASM), which uses abstract variables to model the data signals and function symbols to model the data operations. Due to the appearance of abstract variables and function symbols, we cannot directly implant ROBDD based methods into the MDG tool set.

To develop this new application, we define the syntax and semantics of the first-order specification language  $\mathcal{L}_{MDG}^*$ . We also propose an algorithm to transform a  $\mathcal{L}_{MDG}^*$  formula into a Propositional Linear time Temporal Logic (PLTL) formula by constructing the ASMs. The algorithm is implemented by building circuit descriptions in MDG-HDL for the constructed ASMs. The constructed ASMs are further composed with the system model ASM to produce a composed ASM. Finally, we check the satisfaction of the PLTL on the composed ASM with an existing automa-

ton constructing procedure and three new developed language emptiness checking algorithms.

The contributions of the thesis can be summarized as follows:

- The definition of a first-order specification language  $\mathcal{L}_{MDG}^*$ .

- The development of an algorithm to translate a  $\mathcal{L}_{MDG}^*$  formula into a PLTL formula by constructing ASMs and proof of the correctness.

- The definition of rules for building the circuit descriptions for ASMs.

- The development of three language emptiness checking algorithms using MDG operators.

- Implementation of the new MDG LEC application into the MDG tool set.

- Performing case studies and experimental work on a set of benchmarks such as an ATM (Asynchronous Transfer Mode) switch fabric and Island Tunnel Controller (ITC).

## 1.4 Outline of the Thesis

The rest of the thesis is organized as follows:

Chapter 2 introduces MDGs and the ASM system modeling technique. We also present the existing ASM-based model checking method.

Chapter 3 reviews model checking techniques including Kripke structure models,  $\omega$ -automata theory, property specification languages and  $\omega$ -automata model checking techniques.

Chapter 4 proposes the MDG LEC structure. We describe the first-order temporal specification language  $\mathcal{L}_{MDG}^*$ . We also present the transformation algorithm which constructs ASMs and builds the circuit descriptions in MDG-HDL language.

Chapter 5 presents three language emptiness checking algorithms and proves their soundness.

In Chapter 6, several case studies are presented and some experimental results are provided.

Finally, conclusions and future directions of research are stated in Chapter 7.

# Chapter 2

# Multiway Decision Graphs

Multiway Decision Graphs (MDGs) are a data structure introduced to symbolically encode Abstract State Machines (ASMs) to model hardware designs at the Register Transfer Level (RTL). MDG was first proposed by Corella, et. al [20, 21]. Using MDGs, a data value can be represented by a single variable of abstract type, rather than by a vector of Boolean variables, and a data operation is represented by an uninterpreted function symbol, rather than vectors of Boolean variables.

In this chapter, we review the basic concepts of MDGs and MDG-related verification techniques. Section 2.1 describes the underlying formal logic of MDG. Section 2.2 introduces the *directed formulas*. In Section 2.3, we reviews the MDG data structure and describes a set of logic operators on MDGs. Section 2.4 gives the definition of an ASM and its implicit state enumeration technique. This chapter is concluded with the presentation of the MDG tool set.

## 2.1 Formal Logic

## 2.1.1 Syntax

The formal logic underlying MDG is a many-sorted first-order logic, augmented with the distinction between abstract sorts and concrete sorts [20]. This distinction is motivated by the natural division of datapath and control circuitry in RTL designs.

Concrete sorts have enumerations that are finite sets of individual constants, while abstract sorts do not. Variables of concrete sorts are used for representing control signals, and variables of abstract sorts are used for representing datapath signals. Data operations are represented by uninterpreted function symbols. An n-ary function symbol has a type  $\alpha_1 \times \ldots \times \alpha_n \to \alpha_{n+1}, n \geq 1$ , where  $\alpha_1, \ldots, \alpha_{n+1}$  are sorts.

The distinction between abstract and concrete sorts leads to three kinds of function symbols. Let f denote a function symbol of type  $\alpha_1 \times \ldots \times \alpha_n \to \alpha_{n+1}$ . If  $\alpha_{n+1}$  is an abstract sort, then f is an abstract function symbol; If all the  $\alpha_1 \cdots \alpha_{n+1}$  are concrete, f is a concrete function symbol; If  $\alpha_{n+1}$  is a concrete sort, and at least one of the sorts  $\alpha_1, \ldots, \alpha_n$  is abstract, then we refer to f as a cross-operator. Abstract function symbols are used to denote data operations; cross-operators are useful for modeling feedback signals from the datapath to the control circuitry. Both abstract function symbols and cross-operators are uninterpreted, i.e., their intended interpretations are not specified.

The terms and their types (sorts) are inductively defined as follows: a constant or a variable of sort  $\alpha$  is a term of sort  $\alpha$ ; and if f is function symbol of type  $\alpha_1 \times \ldots \times \alpha_n \to \alpha_{n+1}, n \geq 1$  and  $A_1, \dots, A_n$  are terms of  $\alpha_1 \cdots \alpha_n$ , then  $f(A_1, \dots, A_n)$  is a term of type  $\alpha_{n+1}$ . A term consisting of a single occurrence of an individual constant has multiple sorts (the sorts of the constant), but every other term has a unique sort. The top symbol of a term is defined as follows: the top symbol of  $f(A_1, \dots, A_n)$  is f, and the top symbol of a term consisting of a single occurrence of a variable or a constant is that variable or constant.

We say that a term, variable or constant is concrete (resp. abstract) to indicate that it is of concrete (resp. abstract) sort. A term is concretely reduced iff it contains no concrete terms other than individual constants. Thus a concretely reduced term can contain abstract function symbols, abstract variables, abstract generic constants and individual constants, but it can contain no cross-operators, concrete function symbols, concrete generic constants, or concrete variables; and a concretely reduced term that is itself concrete must be an individual constant. A term of the form " $f(A_1, \dots, A_n)$ " where f is a cross-operator and  $A_1, \dots, A_n$  are concretely-reduced terms is called a cross-term. For example, if f is an abstract function symbol, c is

an individual constant, x is a variable of concrete sort, and y is a variable of abstract sort, then f(c, y) is a concretely-reduced term (assuming that it is well typed), while f(x, y) is not.

A well-typed equation is an expression  $A_1 = A_2$ , where the left-hand side (LHS)  $A_1$  and the right-hand side (RHS)  $A_2$  are terms of same type  $\alpha$ . The atomic formulas are the equations, plus T (truth) and F (falsity). The formulas are defined inductively as follows: an atomic formula is a formula; if P and Q are formulas, then  $\neg P$ ,  $P \land Q$  and  $P \lor Q$  are formulas; if P is a formula and x is a variable, then  $(\exists x)P$  is a formula (with x bound in P). We use the abbreviation  $P \Leftrightarrow Q$  for  $(P \Rightarrow Q) \land (Q \Rightarrow P)$ .

#### 2.1.2 Semantics

An interpretation is a mapping  $\psi$  that assigns a denotation to each sort, constant and function symbol such that [21]:

- 1. The denotation  $\psi(\alpha)$  of an abstract sort  $\alpha$  is a non-empty set.

- 2. If  $\alpha$  is a concrete sort with enumeration  $\{a_1, \dots, a_n\}$ , then  $\psi(\alpha) = \{\psi(a_1), \dots, \psi(a_n)\}$ , and  $\psi(a_i) \neq \psi(a_j)$  for  $1 \leq i \leq j \leq n$ .

- 3. If c is a generic constant of sort  $\alpha$ , then  $\psi(c) \in \psi(\alpha)$ .

- 4. If f is a function symbol of type  $\alpha_1 \times \cdots \times \alpha_n \to \alpha_{n+1}$ , then  $\psi(f)$  is a function mapping from  $\psi(\alpha_1) \times \cdots \times \psi(\alpha_n)$  into the set  $\psi(\alpha_{n+1})$ .

- 5. Let X be a set of variables, a variable assignment with a  $\psi$ -compatible interpretation is a function  $\phi$  that maps every variable  $x \in X$  of sort  $\alpha$  to an element of  $\phi(x)$  of  $\psi(\alpha)$ .

The truth of a formula P under an interpretation  $\psi$  and  $\psi$ -compatible variable assignment  $\phi$  whose domain contains the variables that occur free in P, written  $\psi, \phi \models P$  is defined by induction:

•  $\psi, \phi \models A_1 = A_2$  iff  $A_1$  and  $A_2$  have the same denotation

- $\psi, \phi \models \neg P$  iff it is not the case  $\psi, \phi \models P$

- $\psi, \phi \models P \land Q \text{ iff } \psi, \phi \models P \text{ and } \psi, \phi \models Q$

- $\psi, \phi \models P \lor Q \text{ iff } \psi, \phi \models P \text{ or } \psi, \phi \models Q$

- $\psi, \phi \models (\exists x)P$  iff  $\psi, \phi' \models P$  for some  $\phi'$  that assigns an arbitrary value to x and otherwise coincides x with  $\phi$ .

We write  $\Phi_X^{\psi}$  for the set of  $\psi$ -compatible assignments to the variables in X. Formula  $\psi \models P$  when  $\psi, \phi \models P$  for every  $\psi$ -compatible assignment  $\phi$  to the variables that occur freely in P, and  $\models P$  when  $\psi \models P$  for all  $\psi$ . Two formulas P and Q are logically equivalent iff  $\models P \Leftrightarrow Q$ . A formula P logically implies a formula Q iff  $\models P \Rightarrow Q$ .

#### 2.2 Directed Formulas

MDG provide efficient representation to a class of well-formed first-order formulas defined on well-typed equations. A well-typed equation is an expression  $A_1 = A_2$ , where  $A_1$  and  $A_2$  are terms of the same sort. Given two disjoint sets of variables U and V, a directed formula of type  $U \to V$  is a formula in Disjunctive Normal Form (DNF) such that:

- 1. Each disjunct is a conjunction of equations of the form

- A = a, where A is a term of concrete sort  $\alpha$  of the form  $f(B_1, \dots, B_n)$  (f is thus a cross-operator) that contains no variables other than elements of U, and a is an individual constant in the enumeration of  $\alpha$ , or

- w = a, where  $w \in (U \cup V)$  is a variable of concrete sort  $\alpha$ , and a is an individual constant in the enumeration of  $\alpha$ , or

- v = A, where  $v \in V$  is a variable of abstract sort  $\alpha$  and A is a term of type  $\alpha$  containing no variables other than elements of U.

- 2. In each disjunct, LHSs of the equations are pairwise distinct.

3. Every abstract variable  $v \in V$  appears as the LHS of an equation v = A in each of the disjuncts. Note that there need not be an equation v = a for every concrete variable  $v \in V$ .

Intuitively, in a directed formula of type  $U \to V$ , the U variables play the role of independent variables, the V variables play the role of dependent variables, and the disjuncts enumerate possible cases. In each disjunct, the equations of the form u=a and A=a specify a case in terms of the U variables while other equations specify the values of (some of the) V variables in that case. The cases need not be mutually exclusive, nor exhaustive.

A directed formula is said to be concretely reduced iff every A in an equation A=a is a cross-term, and every A in an equation v=A is a concretely reduced term. It is easy to see that every directed formula is logically equivalent to a concretely reduced direct formula, given complete specifications of the concrete function symbols and concrete generic constants; the reduction can be accomplished by case splitting.

## 2.3 Multiway Decision Graphs

An MDG is a graphical representation of a directed formula as defined above. Given a concretely reduced directed formula P of type  $U \to V$ , a standard term order, and a custom symbol order comprising all the variables in V and all the cross-operators in P, it is easy to construct an MDG representing a directed formula that coincides with P.

**Definition 2.3.1** A multiway decision graph is a finite directed acyclic graph G where the leaf nodes are labeled by formulas, the internal nodes are labeled by terms, and the edges issuing from an internal node N are labeled by terms of the same sort as the label of N. Such a graph represents a formula defined inductively as follows:

- if G consists of a single leaf node labeled by a formula P, then G represents P;

- if G has a root node labeled A with edges labeled  $B_1, \ldots, B_n$  leading to subgraphs  $G_1, \cdots, G_n$ , and if each  $G_i$  represents a formula  $P_i$ , then G represents

the formula

$$\bigvee_{1 \leq i \leq n} ((A = B_i) \wedge P_i)$$

.

To illustrate the above definitions, we give an example.

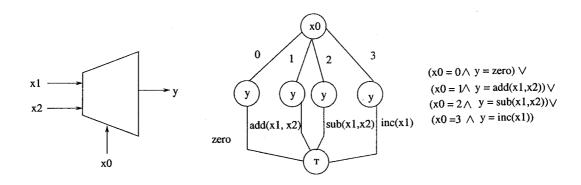

**Example 2.3.1** Figure 2.1 shows the ALU of a microprocessor. The variables  $x_1, x_2$  and y representing the data inputs and the output are of an abstract sort, while the variable  $x_0$  representing the control input is of concrete sort with the enumeration  $\{0,1,2,3\}$ . Depending on the value of  $x_0$ , the ALU can add, subtract, increment, or produce zero. The operations are represented by function symbols add, sub, inc. The symbol zero is a generic constant.

Figure 2.1: An MDG example

## 2.3.1 Basic MDG Algorithms

The following basic MDG algorithms were implemented in the MDG package [85]. To simplify the description of the algorithms we identify an MDG with the *directed* formula that it represents.

**Disjunction:** The disjunction algorithm is n-ary. It takes as inputs a set of directed formulas  $P_i$ ,  $1 \le i \le n$ , of type  $U_i \to V$ , and produces a directed formula  $R = \text{Disj}(\{P_i\}_{1 \le i \le n})$  of type  $(\bigcup_{1 \le i \le n} U_i) \to V$  such that

$$\models R \Leftrightarrow (\vee_{1 \leq i \leq n} P_i).$$

Note that this algorithm requires that all the  $P_i$ ,  $1 \leq i \leq n$ , have the same set of abstract primary variables. If two directed formulas  $P_1$  and  $P_2$  do not have the same set of abstract primary variables, then there is no directed formula R such that  $\models R \Leftrightarrow (P_1 \vee P_2)$ .

**Conjunction**: The conjunction algorithm takes as inputs a set of directed formulas  $P_i, 1 \leq i \leq n$ , of types  $U_i \rightarrow V_i$  and produces a directed formula  $R = \text{Conj}(\{P_i\}_{1 \leq i \leq n})$  of type

$$((\cup_{1 \leq i \leq n} U_i) \setminus (\cup_{1 \leq i \leq n} V_i)) \longrightarrow (\cup_{1 \leq i \leq n} V_i).$$

such that

$$\models R \Leftrightarrow (\wedge_{1 \leq i \leq n} P_i).$$

Note that for  $1 \leq i < j \leq n$ ,  $V_i$  and  $V_j$  need not have any abstract variables in common, otherwise the conjunction cannot be computed.

Relational product: This algorithm takes as inputs a set of directed formulas  $P_i, 1 \leq i \leq n$ , of types  $U_i \to V_i$ , a set of variables E to be existentially quantified, and a renaming substitution  $\eta$ , and produces a directed formula  $R = Relp(\{P_i\}_{1 \leq i \leq n}, E, \eta)$  such that

$$\models R \Leftrightarrow (((\exists E)(\land_{1 \leq i \leq n} P_i)) \cdot \eta).$$

The algorithm computes the conjunction of the  $P_i$ , existentially quantifies the variables in E, and applies the renaming substitution  $\eta$ . For  $1 \le i < j \le n$ ,  $V_i$  and  $V_j$  must not have any abstract variables in common. The result of only computing the conjunction is a directed formula of type

$$((\cup_{1\leq i\leq n}U_i)\setminus(\cup_{1\leq i\leq n}V_i))\to(\cup_{1\leq i\leq n}V_i).$$

The set E of variables to be existentially quantified must be a subset of  $(\bigcup_{1 \leq i \leq n} V_i)$ . The result of only computing conjunction and existential quantification would be a directed formula of type

$$((\cup_{1\leq i\leq n}U_i)\setminus(\cup_{1\leq i\leq n}V_i))\to((\cup_{1\leq i\leq n}V_i)\setminus E).$$

The domain  $\eta$  must be a subset of  $((\bigcup_{1 \leq i \leq n} V_i) \setminus E)$ . The type of the result R is then

$$(\cup_{1 \leq i \leq n} U_i) \setminus (\cup_{1 \leq i \leq n} V_i)) \to (((\cup_{1 \leq i \leq n} V_i) \setminus E) \cdot \eta).$$

**Pruning by subsumption**: This algorithm takes as inputs two directed formulas P and Q of types  $U \to V_1$  and  $U \to V_2$  respectively, and produces a directed formula R = PbyS(P,Q) of type  $U \to V_1$  derivable from P by pruning (i.e., by removing some of the disjuncts) such that

$$\models R \lor (\exists U)Q \Leftrightarrow P \lor (\exists U)Q. \tag{2.1}$$

**Remark 2.3.1** The name of the algorithm comes from the fact that the disjuncts that are removed from P are subsumed by Q.

Since R is derived from P by pruning, after the formulas represented by R and P have been converted to Disjunctive Normal Form (DNF), the disjuncts in the DNF of R are a subset of those in the DNF of P. Therefore, we obtain  $\models R \Leftrightarrow P$ . And from (2.1), it follows tautologically that

$$\models P \land \neg(\exists U)Q \Rightarrow R,\tag{2.2}$$

from which, we have

$$\models (P \land \neg(\exists U)Q \Rightarrow R) \land (R \Rightarrow P). \tag{2.3}$$

Hence, we can view R as an approximation to the logical difference of P and  $(\exists U)Q$ . In general, there is no directed formula logically equivalent to  $P \land \neg(\exists U)Q$ . If R is  $\mathsf{F}$ , then it follows tautologically from (2.1) that  $\models P \Rightarrow (\exists U)Q$ .

Those basic algorithms are the building blocks of the procedures for MDG-based verification. In MDG-based verification, abstract state machines (ASM) are used to model the systems. In the next section, we introduce abstract state machines and their related state exploration algorithm.

## 2.4 Abstract State Machine (ASM)

An ASM is a finite state machine given by an abstract description in terms of directed formula [20].

#### 2.4.1 Representing Sets using MDGs

Let P be an MDG of type  $U \to V$ . Then, for a given interpretation  $\psi$ , P can be used to represent the set of vectors  $Set_V^{\psi}(P) = \{\phi \in \Phi_V^{\psi} | \psi, \phi \models (\exists U)P\}$ . In the next section, directed formulas will thus be used in this fashion to represent sets of states and sets of output vectors. We shall also see how MDG can be used to represent relations.

#### 2.4.2 Describing ASM with MDGs

An abstract state machine is defined as a tuple  $D = (X, Y, Z, F_I, F_T, F_O)$ , where

1. X, Y and Z are pairwise disjoint sets of input symbols, state symbols and output symbols, respectively. Let  $\eta$  be a one-to-one function that maps each state variable y to a distinct variable  $\eta(y)$  obtained, for example, by adorning y with a prime. The variables in  $Y' = \eta(Y)$  are used to denote the next-state variables. X, Y and Z must be disjoint from Y'.

Given an interpretation  $\psi$ , an input vector of the state machine M represented by D is a  $\psi$ -compatible assignment to the set of input variables X; thus, the set of input vectors, or input alphabet, is  $\Phi_X^{\psi}$ . Similarly,  $\Phi_Z^{\psi}$  is the set of output vectors. A state is a  $\psi$ -compatible assignment to the set of state variables Y; hence, the state space is  $\Phi_Y^{\psi}$ . A state  $\phi$  can also be described by an assignment  $\phi' = \phi \circ \eta^{-1} \in \Phi_{Y'}^{\psi}$  to the next state variables.

A variable in  $X \cup Y \cup Z$  is called an  $ASM\_variable$  [82].

2.  $F_I$  is a directed formula representing the set of initial states, of type  $U \to Y$ , where U is a set of abstract variables disjoint from  $X \cup Y \cup Y' \cup Z$ . Typically,  $F_I$  is a one-disjunct directed formula representing the set of initial states.

Given an interpretation  $\psi$ , a state  $\phi \in \Phi_Y^{\psi}$  is an initial state iff  $\psi, \phi \models (\exists U)F_I$ . Thus, the set of initial states is

$$S_I = Set^{\psi}(F_I) = \{ \phi \in \Phi_Y^{\psi} \mid \psi, \phi \models (\exists U)F_I \}.$$

3.  $F_T$  is a directed formula of type  $(X \cup Y) \to Y'$ , representing the transition relation.

Given an interpretation  $\psi$ , an input vector  $\phi \in \Phi_X^{\psi}$  and a state  $\phi' \in \Phi_Y^{\psi}$ , a state  $\phi'' \in \Phi_Y^{\psi}$  is a possible next state iff  $\psi, \phi \cup \phi' \cup (\phi'' \circ \eta) \models F_T$ . Thus the transition relation of the state machine M represented by D is given by:

$$R_T = \{ (\phi, \phi', \phi'') \in \Phi_X^{\psi} \times \Phi_Y^{\psi} \mid \psi, \phi \cup \phi' \cup (\phi'' \circ \eta) \models F_T \}.$$

4.  $F_O$  is a directed formula of type  $(X \cup Y) \to Z$ , representing the output relation. Given an interpretation  $\psi$ , the output relation of the state machine M represented by D is

$$R_O = \{ (\phi, \phi', \phi'') \in \Phi_X^{\psi} \times \Phi_Y^{\psi} \times \Phi_Z^{\psi} \mid \psi, \phi \cup \phi' \cup \phi'' \models F_O \}.$$

To recapitulate, for every interpretation  $\psi$  of the sorts, constants and function symbols of the logic, the abstract description  $D = (X, Y, Z, F_I, F_T, F_O)$  represents the state machine  $M = (\Phi_X^{\psi}, \Phi_Y^{\psi}, \Phi_Z^{\psi}, S_I, R_T, R_O)$  with the set of the input vectors  $\Phi_X^{\psi}$ , the state space  $\Phi_Y^{\psi}$ , the set of output vectors  $\Phi_Z^{\psi}$ , the set of initial states  $S_I$ , the transition relation  $R_T$ , and the output relation  $R_O$ .

To illustrate the above definitions, we give an example.

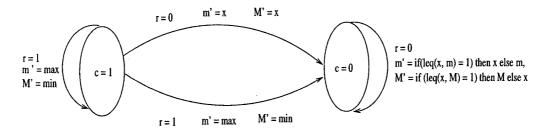

Example 2.4.1 (MinMax) The ASM shown as Figure 2.2 models a simple machine to pick up the minimal and maximal numbers from a set of natural numbers. The circles in the figure correspond to the control states, and the arrows correspond to the control transitions of the machine. The transition labels specify the conditions under which each transition is taken and an assignment of values to the abstract next state variables. The machine has 2 input variables r, x and 3 state variables c, m, M, where r describes the reset signal, x represents the input number, c stands

for the states of machine, and m, M stores the minimal or maximal number obtained so far. r and c are defined as variables of concrete sort and x, m, M are defined as variables of abstract sorts wordn. There are no output variables in the machine. A function symbol, leq, is an operator to compare two variables a and b of sort wordn. leq(a,b)=1 if and only if a is less than or equal to b. The initial states are  $F_I: c=1 \land m=max \land M=min$ . The transition relation  $F_T$  is

$$(c = 1 \land r = 1 \land m' = max \land M' = min \land c' = 1) \lor$$

$$(c = 1 \land r = 0 \land m' = x \land M' = x \land c' = 0) \lor$$

$$(c = 0 \land r = 1 \land m' = max \land M' = min \land c' = 1) \lor$$

$$(c = 0 \land r = 0 \land leq(x, m) = 1 \land leq(x, M) = 1 \land m' = x \land M' = M \land c' = 0) \lor$$

$$(c = 0 \land r = 0 \land leq(x, m) = 0 \land leq(x, M) = 1 \land m' = m \land M' = M \land c' = 0) \lor$$

$$(c = 0 \land r = 0 \land leq(x, m) = 1 \land leq(x, M) = 0 \land m' = x \land M' = x \land c' = 0) \lor$$

$$(c = 0 \land r = 0 \land leq(x, m) = 0 \land leq(x, M) = 0 \land m' = m \land M' = x \land c' = 0) \lor$$

Figure 2.2: The ASM of the Minmax

#### 2.4.3 State Exploration and Invariant Checking

Given an abstract state machine description  $D = (X, Y, Z, F_I, F_T, F_O)$ , we can compute the set of the reachable states of a state machine  $M = (\Phi_X^{\psi}, \Phi_Y^{\psi}, \Phi_Z^{\psi}, S_I, R_T, R_O)$  represented by D, for any interpretation  $\psi$  and  $\psi$ -compatible assignments  $\Phi$ , using the MDG algorithms mentioned above. During the computation, the algorithm checks if an invariant condition holds on all the reachable states. The invariant is

represented by an MDG C of type  $W \to Z$ , where W is a set of abstract variables disjoint from X, Y, Y, Z and U. For a given interpretation y, an output vector is deemed to satisfy the invariant iff  $\psi, \phi \models (\exists W)C$ ; therefore,  $Set_Z^{\psi}(C)$  is the set of output vectors that satisfy the invariant.

The Reachability Analysis (ReAn) algorithm [21] can be described by the following pseudo-code:

```

Algorithm 2.4.1 (Reachability Analysis Algorithm)

```

```

1 ReAn(D,C)

2 R := F_I; Q = F_I; K := 0;

3

loop

4

K := K + 1:

5

I := \operatorname{\mathsf{Fresh}}(X, K);

O := RelP(\{I, Q, F_O\}, X \cup Y, \emptyset);

P := PbyS(O, C);

7

8

if P \neq Fthen return failure;

N := \text{RelP}(\{I, Q, F_T\}, X \cup Y, Y \rightarrow Y);

g

Q := \mathsf{PbyS}(N, R);

10

if Q = Fthen return success;

11

R := \mathsf{PbyS}(R, Q);

12

R := Disj(R, Q);

13

14 end loop;

15 end ReAn;

```

The variables I, N, P, Q and R represent sets of states, and O represents a set of output vectors. Before each iteration, R contains the states reached so far, while Q is the frontier set, i.e., a subset of  $\Phi_Y^{\psi}(R)$  containing at least all those states that entered  $\Phi_Y^{\psi}(R)$  for the first time in the previous iteration. In line 5, Fresh(X,K) constructs a one-disjunct directed formula representing a conjunction of equation x = u, one for each abstract input variable  $x \in X$ , where u is a fresh variable from the set of auxiliary abstract variables U. The value of the loop counter K is used to generate the fresh

variables. This one-disjunct directed formula is assigned to I, which represents the set of input vectors. In line 6, the relation product (ReIP) operation is used to compute the directed formula representing the set of output vectors produced by the states in the frontier set. The resulting directed formula is assigned to O, Then, in line 7, the pruning-by-subsumption (PbyS) operation is used to remove from O those disjuncts that represent output vectors which satisfy the invariable C. The resulting directed formula is assigned to P. In line 8, if P is not F, then the procedure stops and reports failure. If P is F, then every output vector produced by a state in the frontier set satisfies the invariant and the verification procedure continues. In line 9, the relational product operation is used again; this time compute the directed formula representing the set of states that can be reached in one step from the frontier set of states. Note that the directed formula Q represents the frontier set. Lines 10 and 11 check whether  $\Phi_{\mathcal{V}}^{\psi}(N) \subset \Phi_{\mathcal{V}}^{\psi}(R)$  by the same method used in lines 7 and 8, respectively. If it is the case, then every state reachable from the frontier set was already in  $\Phi_{\nu}^{\psi}(R)$ . The fixpoint has been reached and R represents all the reachable states. Therefore, the procedure terminates and reports success. Otherwise, the directed formula assigned to Q in line 10 represents the new frontier set. Line 12 simplifies R by removing it any disjuncts that are subsumed by Q, using PbyS. There may be such disjuncts because Q was not computed earlier as an exact difference. Line 13 then computes the new value of R by taking the disjunction of R and Q which represents the set of states  $\Phi_Y^{\psi}(R) \cup \Phi_Y^{\psi}(Q)$  and assigns it to R.

## 2.5 MDG Verification Applications

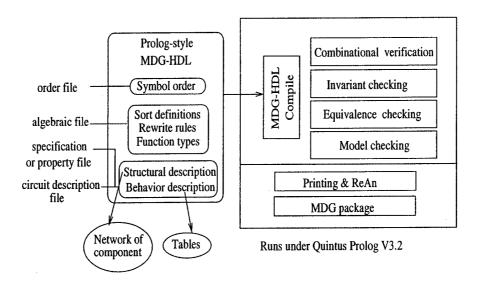

At present, there exists several MDG-based hardware verification applications, which constitute an MDG tool set. Figure 2.3 depicts the components. The MDG tools accept a Prolog-styled Hardware Description Language (HDL), called MDG-HDL [85] which allows the use of abstract variables and uninterpreted function symbols. MDG-HDL supports structural descriptions, behavioral descriptions, or the mixture of structural descriptions and behavioral descriptions. A structural description is usually a netlist of components (predefined in MDG-HDL) connected by sig-

nals. A behavioral description is given by a tabular representation of the transition/output relation or truth table [83].

Besides circuit descriptions, a variety of information, such as sort and function type definitions, symbol ordering and invariant specification, etc., has to be provided in order to use the applications. All of these are organized into four kinds of input files: that algebraic file, the symbol order file, the circuit description file, and the invariant specification file. All these files are compiled into internal MDG data structures by the MDG-HDL compiler. The MDG package supplies the MDG operation algorithms described above. The reachability procedure implements the ReAn algorithm and printing facility provides various printing options. On top of them are built a set of verification application including combinational equivalence checking, safety property invariant checking, sequential equivalence checking, and model checking.

Figure 2.3: The MDG tool set

Combinational equivalence checking. Given two combinational circuits, an MDG is computed for each of them to represent its input-output relation by combining the MDGs of the components of the circuit using the relational product operations. Because of the canonicity of MDG, comparing the functionality of two combinational

circuits reduces to computing the MDGs representing their input/output relations. If the two circuits have the same functionality, the two MDGs must represent logically equivalent formulas, and hence they must be isomorphic.

Invariant checking. This safety property checking is based on the reachability analysis procedure. Given a state machine M and an invariant condition C, the procedure checks if C holds in all the reachable states of M. An invariant condition is specified by a combinational circuit whose output signals are named by the variables that occur in the condition. Pruning-by-subsumption is used to check that the invariant is satisfied for the states in each frontier set.

Sequential equivalence checking. One application of invariant checking is the behavioral equivalence checking of two sequential circuits. To verify that two ASMs produce the same sequence of outputs for every sequence of inputs, the same inputs are feed to the two circuits, i.e., the product state machine is formed. Then, a reachability analysis is performed on this parallel composition using an invariant that asserts the equality of the corresponding outputs in all the reachable states. For machines with different time scales, it is possible to synchronize them first if they have cyclic behaviors. Then the reachability analysis can be performed on the product machine as usual.

Model checking. Model checking algorithms for a subset of Abstract-CTL\* called  $\mathcal{L}_{MDG}$  was developed by Xu [81]. It can verify both safety and liveness properties. To check a property p in  $\mathcal{L}_{MDG}$  on an ASM M, additional ASMs  $M_j$  are first built for basic sub-formulas of p in which only the temporal operator X is allowed (called Next\_let\_formulas), and then these additional ASMs are composed with M. Finally, appropriate algorithms are applied to verify the transformed simplified properties on the composite machine. We will describe the details on  $\mathcal{L}_{MDG}$  in Chapter 3.

## 2.6 Conclusion

This chapter reviewed the basic concepts of Multiway Decision Graphs (MDGs), which underlying logic is a many-sorted first-order logic and described by the well-formed first-order formulas (directed formulas). We reviewed the MDG data structure and basic operators. We also described the implicit abstract state enumeration procedure and various existing MDG based verification techniques.

# Chapter 3

# Model Checking and $\omega$ -Automata

Model checking is a technique to algorithmically check whether a design model satisfies its specification. The model is represented by a Kripke structure M, and its specification is described as a formula p in some temporal logic. The satisfaction problem can be expressed mathematically as the decision of  $M \models p$ . The symbolic model checking sets a new milestone in the development process of model checking techniques. Symbolic model checking encodes the sets and the transition relations with Reduced Ordered Binary Decision Diagrams (ROBDDs), which are canonical representation of the Boolean characteristic function once an order on the variables has been established. The implicit enumeration technique greatly increases the state spaces that can be accepted by model checking [5].

In this chapter, we first introduce the notion of Kripke structure and its symbolic representation, and also give the definition of bisimulation relation over two Kripke structures. Then we give the different logics (propositional, first-order, and temporal logics) for describing properties. Finally, we focus on the  $\omega$ -automata based model checking method, which we intend to lift from propositional to first-order logic.

## 3.1 Kripke Structure

Model checking describes system design as a Kripke Structure. We will introduce the definition and give the bisimulation relation over Kripke Structures in this section.

#### 3.1.1 ROBDD Representation

For model checking, the system design is as a Kripke structure [54], which can be viewed as a labeled Finite State Machine (FSM).

**Definition 3.1.1** Let AP be a set of atomic propositions. A Kripke structure M over AP is a four-tuple  $M = (S, S_0, R, L)$ , where

- S is the set of states,

- $S_0 \subseteq S$  is the set of initial states,

- $R \subseteq S \times S$  is the transition relation, which must be total, i.e., for every state  $s \in S$ , there is a state  $s' \in S$  such that R(s, s'), we write  $s \to s'$  for clarity,

- $L: S \to \mathcal{P}(AP)$  is a function that labels each state with the set of atomic propositions true in that state.

A path (computation) in M starting from a state s is an infinite sequence of states  $\pi = s_0 s_1 s_2 \ldots$ , such that  $s_0 = s$  and for every  $i \geq 0$ ,  $s_i \to s_{i+1}$ . The suffix of  $\pi$  from state  $s_i$  is denoted  $\pi^i$ .

A symbolic representation of the Kripke structure is implemented by describing the state set and transition relation with Boolean characteristic functions. Let  $AP = \{p_1, \dots, p_n\}$ . A state s is represented by a vector of Boolean variables  $X = \{x_1, \dots, x_n\}$ , where  $x_i = p_i$  or  $x_i = p_i$  (the negation of  $p_i$ ). A set of states can be represented by a Boolean characteristic function  $Q = \{X | f(x_1, \dots, x_n) = 1\}$ . Similarly, the relation  $R \subseteq S \times S$  can be represented by a Boolean characteristic function of two sets of variables  $R = \{(X, X') | f(x_1, \dots, x_n, x'_1, \dots, x'_n) = 1\}$ .

To illustrate the above definitions, we give an example.

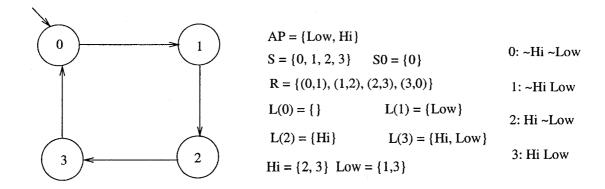

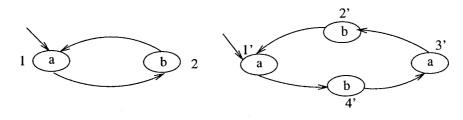

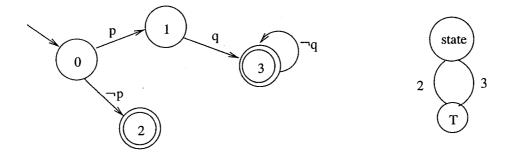

**Example 3.1.1** A modulo-4 counter counts  $0, 1, 2, 3, 0, 1, 2, 3, 0, 1, 2, \cdots$  Initially the counter is zero. Let  $AP = \{Hi, Low\}$  be the set of two propositional variables to encode the four states. The Kripke structure graph and its corresponding symbolic representation are show in Figure 3.1.

Figure 3.1: The Kripke structure of a modulo-4 counter

#### 3.1.2 Bisimulation Relation

Let AP be a set of atomic propositions and let  $M_1 = (S_1, S_{01}, R_1, L_1)$  and  $M_2 = (S_2, S_{02}, R_2, L_2)$  be two Kripke structures. The *bisimulation relation* defined in [68] is described as below:

**Definition 3.1.2** (Bisimulation) A relation  $H \subseteq S_1 \times S_2$  is said to be a bisimulation relation over  $M_1$  and  $M_2$  if the following conditions hold:

- 1. For every  $s_1 \in S_{01}$ , there is  $s_2 \in S_{02}$  such that  $H(s_1, s_2)$ . Moreover, for every  $s_2 \in S_{02}$ , there is  $s_1 \in S_{01}$  such that  $H(s_1, s_2)$ .

- 2. For every  $(s_1, s_2) \in H$

- $L_1(s_1) = L_2(s_2)$  and

- $\forall t_1 [R_1(s_1, t_1) \rightarrow \exists t_2 [R_2(s_2, t_2) \land H(t_1, t_2)]]$

- $\forall t_2 [R_2(s_2, t_2) \rightarrow \exists t_1 [R_1(s_1, t_1) \land H(t_1, t_2)]].$

We write  $s_1 \equiv s_2$  for  $H(s_1, s_2)$ . We call  $M_1$  and  $M_2$  are bisimular (denote  $M_1 \equiv M_2$ ) if there exists a bisimulation relation H over  $M_1$  and  $M_2$ .

To illustrate this concept, we give an example shown in Figure 3.2, where the relation H is shown in the bottom.

Bisimulation relation produces both correct positives and correct negatives, which is shown in the following theorem.

$H = \{(1,1'),(2,4'),(1,3'),(2,2')\}$

Figure 3.2: An example of the bisimulation relation

**Theorem 3.1.1** (see [14]) Let  $M_1$  and  $M_2$  be two Kripke models. If  $M_1 \equiv M_2$ , then for every  $CTL^*$  formula f (with atomic propositions in AP),  $M_2 \models f$  if and only if  $M_1 \models f$ .

## 3.2 $\omega$ -Automata Theory

Model checking using  $\omega$ -automata theory transfers both the system and property into  $\omega$ -automata, thus reduces the checking problem into a language containment problem. Automaton can be viewed as a transition system structure with an acceptance condition.  $\omega$ -automata deviate from the traditional finite automaton by interpretation of the acceptance conditions: there are no final states; instead, acceptance is determined with respect to the set of states that are visited infinitely often. Different types of acceptance conditions are studied [76]. In the thesis, we mainly focus on Büchi conditions.

**Definition 3.2.1** A Büchi automaton  $\mathcal{B} = (Q, I, \delta, F)$  over an alphabet  $\Sigma$  is given by a finite set Q of states, a non-empty set  $I \subseteq Q$  of initial states, a transition relation  $\delta \subseteq Q \times \Sigma \times Q$ , and a set  $F \subseteq Q$  of acceptance states. A run r of  $\mathcal{B}$  over an  $\omega$ -word  $\omega = a_0 a_1 \ldots \in \Sigma^{\omega}$  is an infinite sequence  $r = q_0 q_1 \ldots$  of states  $q_i \in Q$  such that  $q_0 \in I$  and  $(q_i, a_i, q_{i+1}) \in \delta$  hold for all  $i \geq 0$ . The run r is accepted iff there exists some  $q \in F$  such that  $q_i = q$  holds for infinitely many times.

The language  $\mathcal{L}(\mathcal{B}) \subseteq \Sigma^{\omega}$  is the set of  $\omega$ -words, for which there exists some accepted run r of  $\mathcal{B}$ . A language  $\mathcal{L} \subseteq \Sigma^{\omega}$  iff  $\mathcal{L} = \mathcal{L}(\mathcal{B})$  for some Büchi automaton  $\mathcal{B}$ .

The following are some properties of Büchi automaton that establish the foundation of application in the  $\omega$ -automata based model checking [76, 79].

**Proposition 3.2.1** For every LTL formula  $\varphi$  of length n, there exists a Büchi automaton  $\mathcal{B}_{\varphi} = (Q, I, \delta, F)$  with  $2^{O(n)}$  states, which accepts precisely  $\omega$ -words that satisfy  $\varphi$ .

**Proposition 3.2.2** For a Büchi automaton  $\mathcal{B}$  with n states over alphabet  $\sigma$ , there is a Büchi automaton  $\overline{\mathcal{B}}$  with  $2^{O(n\log n)}$  states such that  $\mathcal{L}(\overline{\mathcal{B}}) = \Sigma_{\omega} \setminus \mathcal{L}(\mathcal{B})$ .

**Proposition 3.2.3** For a Büchi automaton  $\mathcal{B}$  with n states, it is decidable in time O(n) whether  $\mathcal{L}(\mathcal{B}) = \emptyset$  or not.

The Büchi automaton type we considered is generalized Büchi automaton  $\mathcal{B}$ . The acceptance condition of  $\mathcal{B}$  is defined by a finite set  $\mathcal{F} = \{F_1, \ldots, F_n\}$  of sets of states. A run is accepted if some states from each  $F_i$  are visited infinitely often. Note that in the special case  $\mathcal{F} = \emptyset$  all infinite runs of the generalized Büchi automaton  $\mathcal{B}$  are accepted.

**Proposition 3.2.4** Let  $\mathcal{A}$  be a generalized Büchi automaton  $(Q, Q_0, \delta, \mathcal{F})$  over the alphabet set  $\Sigma$ , where  $\mathcal{F} = \{F_1, F_2, \dots, F_n\}$ . We can construct a Büchi automaton  $\mathcal{B}$  that  $\mathcal{L}(\mathcal{A}) = \mathcal{L}(\mathcal{B})$ .

The construction is based on the sets in  $\mathcal{F}$ , which is given as follows:

- $\mathcal{F} = \emptyset$ :  $\mathcal{B} = (Q, Q_0, \delta, Q)$ ,

- $\mathcal{F} = \{F_1\}: \mathcal{B} = (Q, Q_0, \delta, F_1),$

- $\mathcal{F} = \{F_1, F_2, \dots, F_n\}$ , where  $n \ge 2$ :  $\mathcal{B} = (Q', Q'_0, \delta', F'_1)$ , where  $-Q' = Q \times \{1, 2, \dots, n\}$ ,

$$-Q_0'=Q_0\times\{1\},$$

-  $\delta'$  is defined as follows:  $(q', j) \in \delta((s, i), a)$  iff  $s' \in \delta(s, a)$  and  $((s \notin F_i \text{ and } j = i) \lor ((s \in F_i) \text{ and } j = (i \text{ mod } n) + 1))$ , and -  $F'_1 = F_1 \times \{1\}$ .

Note that the automaton for the system design  $\mathcal{B}_M$  should accept all paths produced by M, and a generalized Büchi automaton with  $\mathcal{F} = \emptyset$  accepts all infinite runs of  $\mathcal{B}$ . In particular, we assume the fairness conditions to be expressed as part of the property formula. Thus, the automaton for the system design is a generalized Büchi automaton without any acceptance condition. For simplicity, we will use M to represent  $\mathcal{B}_M$  in the sequel.

## 3.3 Property Specification Language

Model checking checks the satisfaction of a Kripke structure with respect to properties given in some kinds of temporal logics, which we describe next.

#### 3.3.1 Propositional Logic

Successful symbolic model checking is based on the propositional logic. A propositional logic [59] consists of a set of propositions  $AP = \{p, q, ...\}$  and Boolean connectives  $\land$ ,  $\lor$ , and  $\neg$ , representing and, or and not, respectively. The formulas are composed of AP and Boolean connectives. The symbols  $\rightarrow$  (implication) and  $\leftrightarrow$  (equivalence) can be interpreted as follows:  $p \rightarrow q$  abbreviates  $\neg p \lor q$  and  $p \leftrightarrow q$  abbreviates  $p \rightarrow q$  and  $q \rightarrow p$ , respectively.

The semantics of the proposition formulas can be induced with following rules.

- $\neg p$  is *True* iff p is *False*.

- $p \lor q$  is True iff p is True or q is True.

- $p \wedge q$  is True iff both p and q are True.

- $p \rightarrow q$  is True iff p is True then q is True.

- $p \leftrightarrow q$  is True iff both  $p \to q$  is True and  $q \to p$  is True.

#### 3.3.2 First Order Logic

The developed model checking technique in this thesis is based on the first-order logic. A first-order logic [30] language  $\mathcal{L}$  consists of a set of signature symbols (countable sets of symbols for constant, functions, predicates, and variables), a set of standard Boolean connectives and quantifiers.

Symbols of  $\mathcal{L}$  are composed of a set of function symbols, a set of predicate symbols and a set of individual variables. The 0-ary function symbols comprise the subset of constant symbols; and the 0-ary predicate symbols are known as the propositional symbols. The following notations are used to represent the above symbols:

- 1.  $\phi, \varphi, \ldots$ , etc. for n-ary,  $n \ge 1$ , predicate symbols,

- 2.  $P, Q, \ldots$ , etc. for propositional symbols,

- 3.  $f, g, \ldots$ , etc. for n-ary,  $n \ge 1$ , function symbols,

- 4.  $c, d, \ldots$ , etc. for constant symbols, and

- 5.  $y, z, \ldots$ , etc. for variable symbols.

- 6. Binary predicate symbols (the equality symbols)  $\approx$  is based in the standard infix fashion.

- 7. Quantifier symbols ∀ and ∃, denoting universal and existential quantification, are applied to individual variable symbols according to the usual rules regarding scope of quantifiers.

Syntax of  $\mathcal{L}$  The terms of  $\mathcal{L}$  are defined inductively by the following rules:

- 1. Each constant c is a term.

- 2. Each variable y is a term.

- 3. If  $t_1, \ldots, t_n$  are terms and f is an n-ary function symbol, then  $f(t_1, \ldots, t_n)$  is a term.

The atomic formulas of  $\mathcal{L}$  are defined by the following rules:

- 1. Each 0-ary predicate symbol (i.e., atomic proposition) is an atomic formula.

- 2. If  $t_1, \ldots, t_n$  are terms and  $\phi$  is an n-ary predicate, then  $\phi(t_1, \ldots, t_n)$  is an atomic formula.

- 3. If  $t_1$  and  $t_2$  are terms, then  $t_1 \approx t_2$  is also an atomic formula.

Finally, the (compound) formulas of  $\mathcal{L}$  are defined inductively as follows:

- 1. Each atomic formula is a formula.

- 2. If p, q are formulas then  $(p \land q)$ ,  $\neg p$  are formulas.

- 3. If p is a formula and y is a free variable in p, then  $\exists y p$  is a formula.

**Semantics of**  $\mathcal{L}$ . The semantics of  $\mathcal{L}$  is provided by an interpretation I over some domain D. B represents the Boolean domain, which is a domain D with true and false values. The interpretation I assigns an appropriate meaning over D to the (non-logic) symbols  $\mathcal{L}$  as follows:

- For an n-ary predicate symbol  $\psi$ ,  $n \geq 1$ , the meaning  $I(\psi)$  is a function  $D^n \to B$ .

- For a proposition symbol P, the meaning I(P) is an element of B.

- For an n-ary function symbol  $f, n \ge 1$ , the meaning I(f) is a function  $D^n \to D$ .

- For an individual constant symbol c, the meaning I(c) is an element of D.

- For an individual variable symbol y, the meaning I(y) is an element of D.

The interpretation I is extended to arbitrary terms inductively:

$$I(f(t_1,\ldots,t_n))=I(f)(I(t_1),\ldots,I(t_n))$$

The truth meaning of a formula P under interpretation I, written  $I \models P$ , is defined as follows:

•  $I \models P$ , where P is an atomic proposition, iff I(P) = true.

- $I \models \psi(t_1, \ldots, t_n)$ , where  $\psi$  is an n-ary predicate and  $t_1, \ldots, t_n$  are terms,  $I(\psi)(I(t_1), \ldots, I(t_n)) = true$ .

- $I \models t_1 \approx t_2 \text{ iff } I(t_1) = I(t_2)$

- $I \models p \land q \text{ iff } I \models p \text{ and } I \models q.$

- $I \models \neg p$  iff not the case the  $I \models p$ .

- $I \models \exists y \ p$ , where y is a free variable in p, iff there exists some  $d \in D$  such that  $I[y \leftarrow d] \models P$ , where  $I[y \leftarrow d]$  is the interpretation identical to I except that y is assigned a value d.

#### 3.3.3 Temporal Logics

Properties of model checking are described as some kinds of temporal logics. A temporal logic [30] is a formalism for describing sequences of transitions between states in a reactive system. It provides a formal system for qualitatively describing and reasoning about how the truth values of assertions change over time. There are four basic operators in temporal logic:

- GP ("always P", also read as "henceforth P") is true in state s if P is true in all future states from s (including s).

- FP ("sometimes P", also read as "eventually P") is true in state s if P is true in some future states from s.

- XP ("nexttime P") is true in state s if P is true in the next state from s.

- $P \cup Q$  ("P until Q") is true in state s if either Q is true in s itself or it is true in some future state of s and until then P is true at every intermediate state.

The following three classes of properties can be easily expressed in temporal logic:

• Safety properties - assert that nothing "bad" happens, typically represented as  $\models GP$ , i.e., P holds at all times in all models;

- Liveness properties assert that eventually something "good" happens, typically represented as  $\models P \rightarrow \mathsf{F}Q$ , i.e., in all models, if P is initially true, then Q will eventually be true;

- Precedence properties assert the precedence order of events, typically represented as  $\models P \cup Q$ , i.e., in all models, P will hold until Q becomes true.

Based on the difference in viewing the notion of time, temporal logics can be classified into two kinds. In the first, time is characterized as a single linear sequence of events, leading to linear time temporal logic. In the second, a branching view of time is taken, such that at any instant there is a branching set of possibilities into the future. This view leads to Branching Time (Temporal) Logic.

#### Propositional Linear Temporal Logic

In a Propositional Linear Time Temporal Logic (PLTL) the underlying structure of time is assumed to be isomorphic to the natural numbers with their usual order (N, <) [30]. Let AP be an underlying set of atomic proposition symbols. A linear-time structure M = (S, x, L) is defined such that S is a set of states,  $x : N \to S$  is an infinite sequence of states, and  $L : S \to 2^{AP}$  is a labeling of each state with the set of atomic propositions in AP that are true in the state.

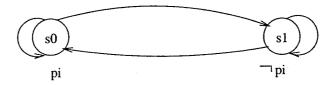

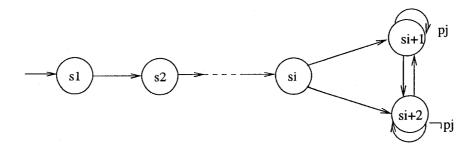

Usually, the notation  $x=(s0,s1,s2,\cdots)=(x(0),x(1),x(2),\cdots)$  is employed to denote the timeline x, which is also referred to as a full path, or a computation sequence, or a computation.