# Design for Verification of a PCI-X Bus Model

## Haja Moinudeen

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements

for the Degree of Master of Applied Science at

Concordia University

Montréal, Québec, Canada

February 2006

© Haja Moinudeen, 2006

Library and Archives Canada

Branch

Published Heritage Dir

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-494-14274-X Our file Notre référence ISBN: 0-494-14274-X

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

#### ABSTRACT

### Design for Verification of a PCI-X Bus Model

#### Haja Moinudeen

The importance of re-usable Intellectual Properties (IPs) cores and the system-level design languages have been increasing due to the growing complexity of today's System-on-Chip (SoC) and the need for rapid prototyping. In this respect, the SystemC language is becoming an industrial standard to be used as a modeling language for SoCs at the system level. Nevertheless, it is of paramount importance to have SystemC IPs in particular bus standards in order to facilitate SoC designs using SystemC. PCI-X is the fastest and latest extension of PCI (Peripheral Component Interconnect) technologies that is backward compatible to previous PCI versions. It plays a crucial role in today's SoC since it helps to connect various on chip IPs. In this thesis, we provide a design for verification approach for the PCI-X bus. We use different modeling levels, namely UML, AsmL and SystemC to design and verify the PCI-X. From informal specifications, we first represent the PCI-X model in UML where a precise capture of design requirements is possible. From the UML representation, we construct an AsmL model of the bus and define various properties using the Property Specification Language (PSL). Finally, we translate the AsmL model to SystemC. The verification of the PCI-X models is conducted using both model checking and model based testing (MBT). For the former, we use the AsmL model, which we check against the PSL properties. For MBT, we use the SystemC model to generate finite state machines (FSMs) from which we produce test cases. To do this, two new FSM generation algorithm are developed in this thesis. Experimental results allowed us to explore the potential of MBT for SystemC designs in contrast to model checking.

To my parents, and sisters

### **ACKNOWLEDGEMENTS**

First and foremost, I would like to put forward my sincere gratitude to my research advisor, Dr. Sofiène Tahar for his support and encouragement throughout my M.A.Sc. program. His expertise and competent advice have shaped the character of my research.

This thesis would not have come into its entirety without the constant and invaluable technical guidance of Dr. Ali Habibi, Research Associate, Hardware Verification Group (HVG), Concordia University. I extensively benefitted from his deep knowledge and insight in the subject.

I would also like to thank all the members of the HVG for their help and support during my study at Concordia. Special acknowledgements to my examination committee members, for reviewing my thesis and giving me feedbacks.

# TABLE OF CONTENTS

| LI | ST O | F TABI  | LES                       | ζ          |

|----|------|---------|---------------------------|------------|

| LI | ST O | F FIGU  | JRES                      | i          |

| LI | ST O | F ACR   | ONYMS xiv                 | 7          |

| 1  | Intr | oducti  | on 1                      | L          |

|    | 1.1  | Motiva  | ation                     | L          |

|    | 1.2  | Metho   | dology                    | 5          |

|    | 1.3  | Relate  | d Work                    | 7          |

|    | 1.4  | Thesis  | Contributions             | 2          |

|    | 1.5  | Thesis  | Outline                   | 3          |

| 2  | Pre  | limina  | ries 14                   | 1          |

|    | 2.1  | Unified | d Modeling Language (UML) | 4          |

|    |      | 2.1.1   | Class Diagrams            | 3          |

|    |      | 2.1.2   | Sequence Diagrams         | 7          |

|    | 2.2  | Abstra  | act State Machines (ASM)  | 7          |

|    |      | 2.2.1   | Functions                 | 7          |

|    |      | 2.2.2   | States                    | 3          |

|    |      | 2.2.3   | Terms                     | 9          |

|    |      | 2.2.4   | Locations and Updates     | <b>(</b> ) |

|   |     | 2.2.5 Transition Rules                 | 20 |

|---|-----|----------------------------------------|----|

|   | 2.3 | Abstract State Machine Language (AsmL) | 22 |

|   | 2.4 | Property Specification Language (PSL)  | 23 |

|   | 2.5 | SystemC                                | 24 |

| 3 | PC  | I-X Bus Modeling                       | 28 |

|   | 3.1 | PCI-X Bus                              | 28 |

|   | 3.2 | UML Modeling                           | 32 |

|   | 3.3 | AsmL Modeling                          | 36 |

|   | 3.4 | Translation to SystemC                 | 40 |

| 4 | Мо  | del Checking                           | 44 |

|   | 4.1 | Background                             | 44 |

|   | 4.2 | Model Checking Approach                | 45 |

|   | 4.3 | Model Properties                       | 46 |

|   | 4.4 | Experimental Results                   | 51 |

| 5 | Gei | nerating FSM from SystemC              | 53 |

|   | 5.1 | Background                             | 53 |

|   | 5.2 | SystemC Syntactical Domain             | 54 |

|   | 5.3 | Collecting Inputs                      | 57 |

|   | 5.4 | FSM Generation Algorithm               | 58 |

|   |     | 5.4.1 Helper Functions                 | 60 |

|   |        | 5.4.2   | Direct FSM Generation      | 61 |

|---|--------|---------|----------------------------|----|

|   |        | 5.4.3   | Grouping FSM Generation    | 63 |

|   | 5.5    | Exper   | imental Results            | 66 |

|   | 5.6    | Discus  | ssion                      | 74 |

| 6 | Mod    | del-Ba  | sed Testing                | 76 |

|   | 6.1    | Backg   | round                      | 77 |

|   | 6.2    | Test C  | Generation                 | 81 |

|   |        | 6.2.1   | Chinese Postman Tour (CPT) | 81 |

|   |        | 6.2.2   | RandomWalk                 | 82 |

|   |        | 6.2.3   | Test Sequences             | 82 |

|   | 6.3    | Discus  | ssion                      | 84 |

| 7 | Cor    | ıclusio | ${f n}$                    | 85 |

|   | 7.1    | Sumn    | nary                       | 85 |

|   | 7.2    | Discus  | ssion and Future Work      | 86 |

| B | ibliog | graphy  | •                          | 89 |

# LIST OF TABLES

| 3.1 | PCI-X Signals                                                    | 30 |

|-----|------------------------------------------------------------------|----|

| 4.1 | Model Checking Results                                           | 52 |

| 5.1 | Link between SystemC Design and FSM Generation Algorithm Inputs. | 57 |

| 5.2 | FSM Generation: Direct Algorithm                                 | 67 |

| 5.3 | FSM Generation: Grouping Algorithm (using G1)                    | 70 |

# LIST OF FIGURES

| 1.1  | Design for Verification Methodology of PCI-X    | 5  |

|------|-------------------------------------------------|----|

| 2.1  | SystemC Language Architecture [17]              | 26 |

| 2.2  | A Simplified SystemC MetaModel [35]             | 27 |

| 3.1  | General Architecture of PCI-X                   | 29 |

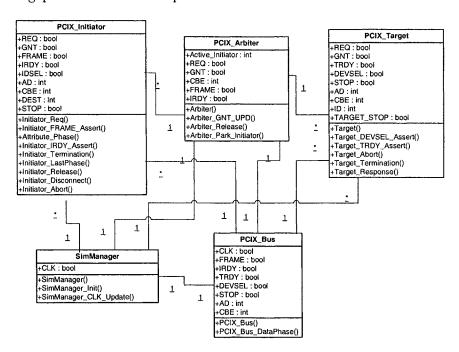

| 3.2  | Class Diagram of PCI-X                          | 33 |

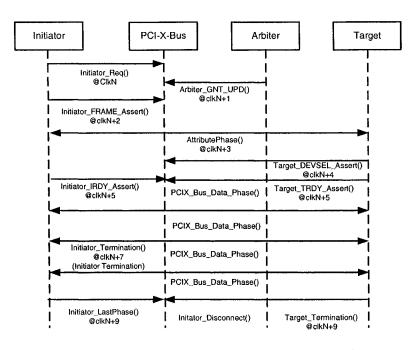

| 3.3  | Sequence Diagram of Mode 1 Transaction          | 34 |

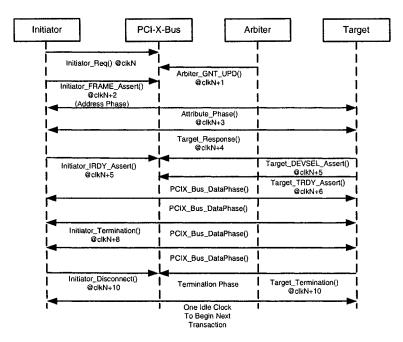

| 3.4  | Sequence Diagram of Mode 2 Transaction          | 35 |

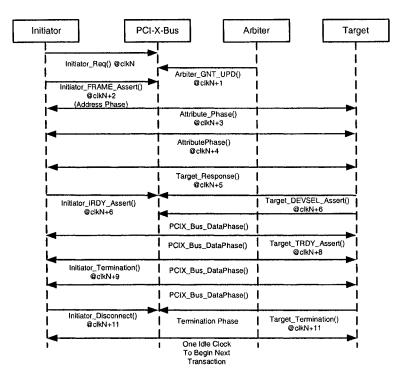

| 3.5  | Sequence Diagram of Mode 2 Transaction (16 bit) | 36 |

| 3.6  | Used AsmL Enumeration Types                     | 37 |

| 3.7  | Arbiter Grant AsmL Method                       | 38 |

| 3.8  | Target Assert AsmL Method                       | 38 |

| 3.9  | Initiator Termination AsmL Method               | 39 |

| 3.10 | Clock Update AsmL Method                        | 39 |

| 3.11 | Data Phase AsmL Method                          | 40 |

| 3.12 | Arbiter Class Declaration in SystemC            | 42 |

| 4.1  | Property <i>P1</i>                              | 47 |

| 4.2  | Property <i>P2</i>                              | 47 |

| 4.3  | Property <i>P3.</i>                             | 47 |

| 4.4  | Property <i>P4</i>                | 48 |

|------|-----------------------------------|----|

| 4.5  | Property <i>P5</i>                | 48 |

| 4.6  | Property <i>P6</i>                | 49 |

| 4.7  | Property <i>P7.</i>               | 49 |

| 4.8  | Property <i>P8</i>                | 49 |

| 4.9  | Property <i>P9.</i>               | 50 |

| 4.10 | Property <i>P10.</i>              | 50 |

| 4.11 | Property <i>P11</i>               | 51 |

| 4.12 | Property <i>P12</i>               | 51 |

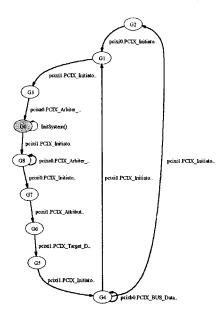

| 5.1  | Direct FSM Generation Algorithm   | 62 |

| 5.2  | Grouping FSM Generation Algorithm | 65 |

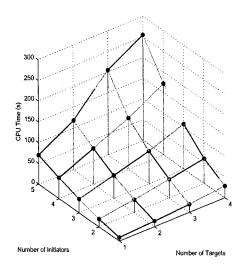

| 5.3  | Direct Algorithm Results          | 68 |

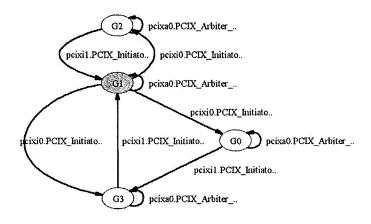

| 5.4  | Grouping Condition $G1.$          | 69 |

| 5.5  | Grouped FSM Using G1              | 69 |

| 5.6  | Grouping Algorithm Results (G1)   | 71 |

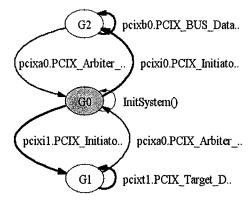

| 5.7  | Grouping Condition $G2$           | 72 |

| 5.8  | Grouped FSM Using G2              | 72 |

| 5.9  | Grouping Condition $G3$           | 73 |

| 5.10 | Grouped FSM Using G3              | 73 |

| 5.11 | Grouping Condition $G4$           | 74 |

| 5.12 | Grouped FSM Using $G4$            | 74 |

| 6.1 | Test Sequences for Grouped FSM of G1 using CPT          | • | 82 |

|-----|---------------------------------------------------------|---|----|

| 6.2 | Test Sequences for Grouped FSM of $G2$ using Randomwalk | • | 83 |

| 6.3 | Test Sequences for Grouped FSM of $G3$ using CPT        |   | 83 |

| 6.4 | Test Sequences for Grouped FSM of G4 using CPT          |   | 83 |

### LIST OF ACRONYMS

AGP Accelerated Graphics Port

ASIC Application Specific Integrated Circuits

ASM Abstract State Machines

AsmL Abstract State Machine Language

BCA Bus Cycle Accurate

CPP Chinese Postman Problem

CPT Chinese Postman Tour

ECC Error Correction Code

EDA Electronic Design Automation

EFSM Extended Finite State Machine

FSM Finite State Machine

HDL Hardware Description Language

IC Integrated Circuit

IP Intellectual Property

MBT Model Based Testing

MC Model Checking

OO Object Oriented

PCI Peripheral Component Interconnect

PCI-X Peripheral Component Interconnect-Extended

PSL Property Specification Language

RTL Register Transfer Level

SLL System Level Languages

SoC System-On-Chip

UML Unified Modeling Language

VLSI Very Large Scale Integration

# Chapter 1

# Introduction

## 1.1 Motivation

With the rapid advances in semiconductor processing technologies, the density of gates on the die increased in line with what Moore's law predicted. This helped in the realization of more complicated designs on the same Integrated Circuit (IC). Over the last few years, with the advent of high technology applications, an increasingly evident need has been that of incorporating the traditional microprocessor, memories and peripherals or in other words the whole system on a single silicon. This is what has marked the beginning of the System-on-Chip (SoC) era.

An SoC can be viewed as a collection of various Intellectual Property (IP) cores, with interconnecting buses running among them. Since IPs are obtained from different vendors, and are often meant to be re-used at various stages of the SoC

design, there is a dire need for standard buses to connect them. One such and latest bus standard is PCI-X [40]. PCI-X is a high performance bus for interconnecting chips, expansion boards, and processor/memory subsystems. It has the performance to feed the most bandwidth-hungry applications and helps to alleviate the I/O bottleneck problem while at the same time maintaining complete hardware and software backward compatibility to previous generations of PCI [40]. PCI-X was adopted as an industrial standard administered by the PCI Special Interest Group (PCI-SIG) [40]. Nevertheless, bus protocols in general are not easy to model and verify correctly due to their complex nature and PCI-X is no exception.

Until recently, modeling IP architectures required pin-level hardware descriptions, typically Register Transfer Level (RTL). Design and simulation at this level of detail is tediously slow. Therefore, designers turned to the system level, where only details needed for developing the system components and sub-system for a particular task in the development process are considered [17]. In other words, system and sub-system communication and functionality can be developed and refined independently. By modeling only the necessary details, design teams can realize huge gains in modeling speed. Moreover, the benefits of adopting system level are derived from early software development, early functional verification, and higher system quality.

In this thesis, we propose a design for verification of a PCI-X bus model at the system level by partially using the top-down methodology presented by Habibi in [19]. We start with an informal specification of PCI-X and model it with the Unified Modeling Language (UML) [42] in order to have a clear view of the design modules and their interactions. UML is a non-proprietary, object modeling and specification language used in software engineering. UML includes a standardized graphical notation that may be used to create an abstract model of a system: the UML model. From the UML model, we manually construct an Abstract Machine Language (AsmL) [18] model from the UML representation. AsmL is an object-oriented, executable specification language developed at Microsoft Research [28]. It can be used to capture the abstract structure and step-wise behavior of discrete systems such as integrated circuits, software components, and devices that combine both hardware and software.

We define a set of properties of the PCI-X in the Property Specification Language (PSL) [1]. PSL is a language developed by Accellera for specifying properties or assertions about hardware designs. PSL is an implementation independent language to define properties and addresses the lack of information about properties and design characteristics. PSL has become IEEE standard in September 2004. The PSL properties can be simulated or formally verified using model checking. We embed the defined properties with the AsmL model of the PCI-X model and run model checking [9] against the properties defined.

Finally, we translate the AsmL model to SystemC [32]. SystemC is among a group of system level languages (SLL) being proposed to raise the abstraction level for embedded system design and verification. The SystemC library of classes and

simulation kernel extend C++ to include the support for concurrent behavior, a notion of time sequential operations, data types for describing hardware, structure hierarchy and simulations. It is expected to make an adverse effect in the arenas of architecture, co-design and integration of hardware and software. As SystemC is becoming a main player in SoC design, it is becoming mandatory to have large collection of IPs in SystemC especially bus standards.

To validate the SystemC model of the PCI-X, we use model based technique (MBT) [36]. MBT is an evolving technique in the area of testing. MBT is an approach in which the behavior of a system is defined in terms of actions that change the state of the system. Such a model of the system results in a well-defined Finite State Machine (FSM) which helps understand and predict the systems behavior. For this reason, it is inevitable to provide an FSM generation algorithm from SystemC that produces a correct FSM of the system. In this thesis, we extend two FSM generation algorithms from SystemC that have been originally proposed for the generation of FSMs from Abstract State Machines (ASM) [3]. Using existing graph traversing techniques, test cases are obtained from the generated FSMs to validate the PCI-X model.

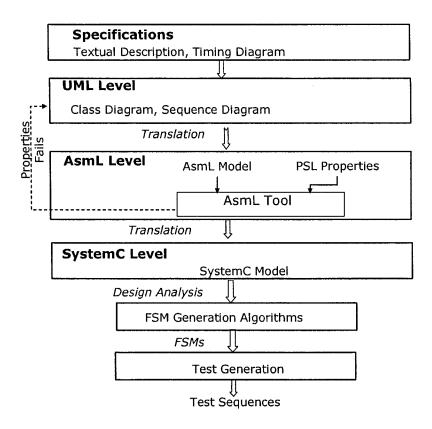

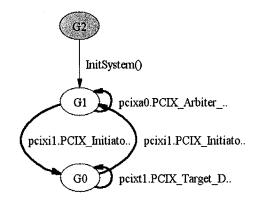

Figure 1.1: Design for Verification Methodology of PCI-X.

## 1.2 Methodology

Figure 1.1 depicts the methodology we want to adopt for the design for verification of the PCI-X model. This methodology is partially derived from a top down approach for verifying SystemC designs proposed by Habibi [19]. At first the design requirements are obtained from the specification in the from of textual description and timing diagrams [40].

From the gathered design requirements, we model the PCI-X in UML using

class and sequence diagrams in order to capture all the design requirements efficiently. Class diagrams are used to represent all the core components of the PCI-X bus and the sequence diagrams are used to model all the sequences of various transactions. The reason of this UML modeling is to represent the system graphically and the ability to represent the notion of sequences of the bus transaction using sequence diagrams. Besides, using our UML representation, any designer can be able to model the bus in any Object Oriented languages.

Then, from the UML representation we design a PCI-X model in AsmL. The translation from UML representation to AsmL is manual but straightforward. We map the UML classes into AsmL classes and the sequence diagrams are used to represent the order of method executions in AsmL. Unlike the UML model, the AsmL model can be executed and validated.

The properties of the bus design are specified in PSL and embedded with the AsmL model. They are basically extracted from the sequence diagrams and encoded in the PSL syntax. Next, model checking is performed on the AsmL model using AsmL tester (Asmlt) [30]. The model checking process ends to: (1) a completion either with success or failure of the property; or (2) a state explosion. In case of failure, we correct the UML representation and redo the AsmL translation. This procedure is repeated until all the properties pass with success or do not complete. The model checking approach of the PCI-X and the results are vividly discussed in Chapter 4. Once the model checking of AsmL model is completed, we perform the

translation of AsmL to SystemC.

It is not always feasible to verify all the properties that we define due to state explosion problem and also writing properties is time consuming that eventually hinders the verification process. Also, the SystemC model has to be validated since the translation of AsmL to SystemC can be erroneous. In order to address these issues, we perform model based testing (MBT) of the PCI-X SystemC model. To accomplish this, we developed two algorithms to generate FSMs from SystemC models. These algorithms have been originally proposed for abstract state machines (ASM) in [15, 5]. The first algorithm (direct algorithm) performs a direct state exploration procedure to generate an FSM and the second (grouping algorithm) involves a notion of state grouping to group states in the FSM. The formalization of these two algorithms is presented in Chapter 5. The generated FSMs are used to generate test cases using available techniques such as Chinese Postman Tour (CPT) [36] and RandomWalk [36]. Furthermore, the generated FSM can also be used for conformance checking [2] between two design abstraction levels (AsmL and SystemC for example). The MBT details and the experimental results of PCI-X are explained in Chapter 6.

### 1.3 Related Work

In his PhD thesis, Habibi [19] proposed a combination of various techniques to verify system level languages in particular SystemC. In [19], a top-down approach to verify

SystemC designs was proposed. In that approach, the verification was integrated as part of the design process and an AsmL model was first designed. The AsmL was mapped from UML representations of the systems. From the AsmL model, model checking was performed against some system properties. The verified AsmL model is translated to SystemC. The SystemC model is also verified through assertion-based verification.

Similar to the work of [19] described earlier, Habibi et al. proposed in [21] a bottom-up verification methodology where starting from an existent Accelerated Graphics Port (AGP) IP in SystemC, an AsmL model was developed. Like in [19], an FSM was generated from the AsmL model and then the systems properties were verified at the ASM level. Our work is an application of the top-down methodology presented in [19] to model and verify the PCI-X bus standard. In addition, in our work, we made an attempt to explore MBT to validate the PCI-X design when model checking is not feasible due to state explosion. Furthermore, in [19], MBT technique was not considered in the verification approach.

There exists some other related work to ours in the context of PCI technologies design and verification environment. For instance, Shimizu et al. [39] presented a specification of the PCI bus as a Verilog monitor. This approach, however, makes any modification or refinement of the model complex since the level of specification of the PCI is very low. Ournalou et al. [33] implemented the PCI bus in SystemC [32]. First, they specified the bus in UML; then, mapped the UML representation

to AsmL and finally translated the AsmL code into SystemC. In [20], Habibi et al. specified and implemented the Look-Aside Interface [29] using the same approach as in [33]. Our approach is similar to the work of [33] and [20], but distinguishes itself by correctly designing and verifying the latest high-speed bus standard (PCI-X) including its very complex transaction rules and validating the PCI-X model through MBT.

In [8], a bridge for PCI Express and PCI-X was designed in Verilog at RTL and also verified and synthesized. Chang et al [6] proposed a simulation based PCI-X verification environment using C and Verilog. Similarly, Wang et al. [43] proposed a similar verification environment for PCI-X bus functional models using VERA. In [44], Yu et al. extended the verification environment in [6] to support PCI, PCI-X and PCI-Express in a single platform. In all the afore-mentioned work [6, 43, 44], the authors defined some pseudo model of masters and slaves to substantiate their approach. But, they failed to include some of the PCI-X specific transactions such as Split transactions. The merit of our work is on the modeling of the PCI-X and verifying using various techniques such as model checking and MBT.

For work related to FSM generation, we cite Grieskamp et al. [15], in which, given a model in AsmL, they provide an algorithm to generate an FSM. The state transitions of the ASM are used to generate a link between hyperstates which is based on single state groupings. The notion of hyperstates in here is analogous to data abstraction. But, the drawback of this algorithm is the use of single state grouping,

which is not adequate to solve the state space explosion problem. Moreover, this algorithm is specific for ASM based languages.

Campbell et al. [5] extended the work of [15] to lessen the number of states in the generated FSM. The FSM generation algorithm from AsmL (or Spec# [27]) in [5] is based on multiple state groupings which is an extension of the concept of hyperstates. Using this algorithm, there is a significant reduction of states and transitions in the final FSM. This notion of multiple state groupings is synonymous to predicate abstraction. The problem with this work is that it is only applicable for AsmL and Spec# and is not directly applicable to SystemC or similar system level languages.

Other related work concerns generating FSM from hardware description languages (HDL). For instance, in [7], a translation procedure from Verilog into timed FSM model was proposed. The resulting timed FSM was used to verify the system using model checkers. Lohse et al. presented in [24] an approach to generate BDD-based FSMs from VHDL code. This is performed in two phases: (1) declarations are annotated with BDDs and processes are compiled into control graphs; and (2) the control graphs are then compiled into an FSM and optimization of the FSM was performed. The generated FSM was mainly used as an input for the model checking tool SMV [26]. However, the approach in both [7] and [24] is restricted to a synthesizable subset of Verilog and VHDL, respectively.

The work of Vikram et al. [38] was more specific to SystemC, where the

design (in SystemC) is first translated to C, then, the FSM is generated from the C code. This approach is problematic in the sense that translating SystemC to C is not always feasible. All previously mentioned techniques could not be applied to SystemC considering the object oriented nature of its library and that only a small subset of SystemC is synthesizable. In [13], Ferrandi et al. proposed to use FSMs to perform functional verification of SystemC designs. They constructed an FSM directly from the code and then use it to guide the test generation. In that work, the FSM generation algorithm was not precisely explained and does not consider the semantics of the SystemC simulator.

Regarding the application of MBT, as far as we know, Dick et al. [11] were the first to introduce automated techniques for extracting FSMs from model-based specifications for the purpose of test case generation. The approach of [11] is based on a finite partitioning of the state space of the model using full disjunctive normal forms (DNF) of the conditions in the specification and is called the DNF approach. Heuristics are used in the DNF approach as part of theorem proving, whereas, we propose in this thesis to use heuristics (grouping conditions) to prune the search space. The DNF approach suffers from two problems: (1) state explosion and (2) the use of theorem proving (time-consuming).

FSM based testing was initially driven by problems arising in functional testing of low level hardware circuits. The bulk of the work in this area has dealt with deterministic FSMs [23, 34]. Then, Extended Finite State Machine (EFSM) approaches

have been introduced to cope with the state explosion problem [4]. More work related to FSM-based software testing can be found on the home page of Model-Based Testing [36].

All the afore-mentioned work regarding FSM based testing do not consider SystemC. We will show in this thesis how FSM based testing could be a promising techniques and well suitable for SystemC as it is meant to be used in higher abstraction level.

## 1.4 Thesis Contributions

In light of the above related work review and discussions, we believe the contribution of the thesis are as follows:

- We model the PCI-X in UML, AsmL and SystemC. Thus, providing a PCI-X

IP in SystemC to accommodate the dire need of bus standard IPs in SystemC.

- 2. We define properties in PSL and verify the PCI-X using model checking.

- 3. We derived and formalized two FSM generation algorithms from SystemC.

- 4. We perform model based testing of the PCI-X using the above FSM generation algorithms.

- 5. We provide a better understanding of the problem of state explosion in model checking and a good comparison with MBT.

## 1.5 Thesis Outline

The thesis is organized as follows: In Chapter 2, we provide an overview of UML, ASM, AsmL, PSL and SystemC. This chapter lays a foundation for the better understanding of the thesis. Chapter 3 presents the PCI-X and included the modeling of PCI-X in UML, AsmL and SystemC. In Chapter 4, we describe the verification of PCI-X using model checking of the AsmL model against the properties defined in PSL. In Chapter 5, we present the FSM generation algorithms from SystemC. It includes the formalization of the two (direct and grouped) FSM generation algorithms and experimental results applied on a PCI-X model. Chapter 6 discusses the model based testing of PCI-X model using the algorithms presented in Chapter 5. Chapter 7 provides the summary of the thesis with some discussions regarding the FSM generation algorithms and PCI-X IP. It also draws major conclusions and lessons learned from this work. In addition, it highlights some future research directions that can be stemmed from this thesis.

# Chapter 2

# **Preliminaries**

In this chapter, we give an insight on UML, ASM, AsmL, PSL and SystemC language and its architecture. This chapter would provide a good foundation for the understanding of the rest of thesis.

# 2.1 Unified Modeling Language (UML)

The Unified Modeling Language (UML) [42] is the standard visual modeling language used for modeling businesses, software application, and system architecture. In other words, it includes a standardized graphical notation that may be used to create an abstract model of a system: the UML model [25].

While the UML is used to specify, visualize, construct, and document softwareintensive systems, it is not restricted to modeling software. It has its strengths at higher, more architectural levels and has been used for modeling hardware and is commonly used for business process modeling, systems engineering modeling, and representing organizational structure. In UML, a *diagram*, is the layout and visualization of different modeling elements as described within the UML. Each UML diagram is used for specific purposes, typically to visualize a certain aspect of your system.

The UML contains two different basic diagram types: structure diagrams and behavior diagrams. Structure diagrams depict the static structure of the elements in your system. The various structure diagrams are as follows [25]:

- Class diagrams

- Component diagrams

- Object diagrams

- Deployment diagrams

- Composite Structure

- Package diagrams

Behavior diagrams depict the dynamic behavior the elements in your system.

The various behavior diagrams are as follows [25]:

- Activity diagrams

- Use case diagrams

- Statechart diagrams

- Collaboration diagrams

- Sequence diagrams

- Timing diagrams

- Interaction overview diagrams

In our approach we mainly use class diagrams and sequence diagrams and they are explained below.

## 2.1.1 Class Diagrams

Class diagrams are a type of static structure diagrams that describes the structure of a system by the showing the system's classes and the relationships between them. A class in the software system is represented by a box with the name of the class written inside it. A compartment below the class name can show the class's attributes. Each attribute is shown with at least its name, and optionally with its type, initial value, and other properties. The class's operations (i.e. its methods) can appear in another compartment. Each operation is shown with at least its name, and optionally also with its parameters and return type. Different types of associations in a class diagram is used to show the relationship between classes.

### 2.1.2 Sequence Diagrams

In contrast to class diagrams, sequence diagrams can depict the dynamic behavioral aspects of the system being modeled. It is used to show the processes that execute in sequence. The sequence diagram shows the sequence of messages, which are exchanged among roles that implement the behavior of the system, arranged in time. It shows the flow of control across many objects that collaborate in the context of a scenario.

## 2.2 Abstract State Machines (ASM)

Abstract State Machines (ASM) [3] is a specification method for software and hard-ware modeling, where a system is modeled by a set of states and transition rules which specifies the behavior of the system. Transition rules specify possible state changes according to a certain condition. The notation of ASM is efficient for modeling a wide range of systems and algorithms as the number of case studies demonstrates [22].

#### 2.2.1 Functions

The ASM notation includes static functions and dynamic functions. Static functions have the same interpretation in every state, while dynamic functions may change their interpretation during a run. There are also external functions which cannot

be changed by the system itself, but by the outer environment.

#### **2.2.2** States

An ASM model consists of states and transition rules. States are given as many sorted first-order structures, and are usually described in terms of functions. A structure is given with respect to a signature. A signature is a finite collection of function names, each of a fixed arity. The given structure fixes the syntax by naming sorts and functions, and provides carrier sets and a suitable symbol interpretation on the carrier sets, which assigns a meaning to the signature. So a state can be defined as an algebra for a given signature with *universes* (domains or carrier sets) and an interpretation for each function symbol.

States are usually described in terms of functions. The notion of ASM includes static functions, dynamic functions and external functions.

- Static functions have a fixed interpretation in each computation state: that is, static functions never change during a run. They represent primitive operations of the system, such as operations of abstract data types (in software specifications) or combinational logic blocks (in hardware specifications).

- *Dynamic functions* whose interpretation can be changed by the transition occurring in a given computation step, that is, dynamic functions change during a run as a result of the specified system's behavior. They represent the internal state of the system.

- External functions whose interpretation is determined in each state by the environment. Changes in external functions which take place during a run are not controlled by the system, rather they reflect environmental changes which are considered uncontrollable for the system.

- Derived functions whose interpretation in each state is a function of the interpretation of the dynamic and external function names in the same state.

Derived functions depend on the internal state and on the environmental situation (like the output of a Mealy machine). They represent the view of the system state as accessible to an external observer.

#### 2.2.3 Terms

Variables and *terms* are used over the signature as objects of the structure. The syntax of terms is defined recursively, as in first-order logic:

- A variable is a term. If a variable is Boolean, the term is also Boolean.

- If f is an r-ary function name in a given vocabulary and  $t_1, \ldots t_r$  are terms, then  $f(t_1, \ldots t_r)$  is a term. The composed term is Boolean if f is relational.

#### 2.2.4 Locations and Updates

States are described using functions and their current interpretations. The state transition into the next state occurs when its function values change. Locations and

updates are used to capture this notion.

A location of a state is a pair of a dynamic function symbol and a tuple of elements in the domain of the function. For changing values of locations the notion of an update is used. An update of state is a pair of a location and a value. To fire an update at the state, the update value is set to the new value of the location and the dynamic function is redefined to map the location into the value. This redefinition causes the state transition. The resulting state is a successor state of the current state with respect to the update. All other locations in the next state are unaffected and keep their value as in the current state.

#### 2.2.5 Transition Rules

Transition rules define the changes over time of the states of ASMs. While terms denote values, transition rules denote *update sets*, and are used to define the dynamic behavior of an ASM. ASM runs starting in a given initial state are determined by a closed transition rule declared to be the *program*. Each next state is obtained by firing the update sets at the current state. Basic transition rules are *skip*, *update*, *block*, and *conditional rules*.

The *skip* rule is the simplest transition rule. This rule specifies an "empty step". No function value is changed. It is denoted as

skip

The *update* rule is an atomic rule denoted as

$$f(t_1, t_2, \dots, t_n) := t$$

It describes the change of interpretation of function f at the place given by  $(t_1, t_2, \dots, t_n)$  to the current state value of t.

A *block* rule is a group of sequence of transition rules. The execution of a block rule is the simultaneous execution of the sequence of the transition rules. All transition rules that specify the behavior of the ASM are grouped into a block indicating that all of them are fired simultaneously.

block

$R_1$

$R_2$

endblock

In *conditional rules* a precondition for updating is specified.

if g

then  $R_1$  else  $R_2$

endif

where g is a first order Boolean term.  $R_1$  and  $R_2$  denote arbitrary transition rules. The condition rule is executed in state S by evaluating the guard g, if  $true\ R_1$  fires, otherwise  $R_2$  fires.

#### 2.3 Abstract State Machine Language (AsmL)

Abstract State Machine Language (AsmL) [18] is an executable specification language based on the theory of ASM. It is fully object-oriented and has strong mathematical constructs in particular, sets, sequences, maps and tuples as well as set comprehension, sequence comprehension and map comprehension. ASMs steps are transactions, and in that send AsmL programming is transaction based. AsmL is fully integrated into the .NET framework and Microsoft development tools providing inter-operability with many languages and tools. Although the language features of AsmL were chosen to give the user a familiar programming paradigm, the crucial features of AsmL, intrinsic to ASMs are massive synchronous parallelism and finite choice. These features give rise to a cleaner programming style than is possible with standard imperative programming languages. Synchronous parallelism and inherently AsmL provide a clean separation between the generation of new values and the committal of those values into the persistent state.

AsmL is integrated with Microsoft's software development environment including Visual Studio, MS Word, and Component Object Model (COM), where it can be compiled and connected to the .NET framework. AsmL effectively supports specification and rapid prototyping of different kinds of models. The AsmL tester [30] can also be used for FSM generation or test case generation.

#### 2.4 Property Specification Language (PSL)

Property Specification Language (PSL) [1] is an implementation independent language to define properties (also called assertions). It does not replace, but complements existing verification methodologies like VHDL and Verilog test benches. PSL presents a different view of the design and may imply FSMs in the implementation. The syntax of PSL is very declarative and structural which leads to sustainable verification environments. Both VHDL and Verilog flavors are provided. PSL consists of four layers based on the functionality:

The Boolean layer to build expressions which are used in other layers, specifically the temporal layer. Boolean expressions are evaluated in a single evaluation cycle.

The temporal layer is used to describe properties of the design, in addition to simple properties, this layer can describe properties that involve complex temporal relations. Temporal expressions are evaluated over a series of evaluation cycles.

The verification layer is used to tell the verification tool what to do with the properties described by the temporal layer.

The modeling layer is used to model behavior of design inputs for formal verification tools, and to model auxiliary parts of the design that are needed for verification.

This layered approach allows the expressing of complex properties from simple primitives. A property is built from three types of building blocks: Boolean expressions, sequences, which are themselves built from Boolean expressions, and finally

subordinate properties. Sequences, referred to as SEREs (Sequential Extended Regular Expressions), are used to describe a single or multicycle behavior built from Boolean expressions. In this thesis, we use only the first three layers of PSL.

#### 2.5 SystemC

SystemC is an open standard controlled by a steering group composed of thirteen major companies in the Electronic Design Automation (EDA) industries [32]. It is one of the most promising system-level design languages and has been recently standardized by IEEE (IEEE 1666) [41] for system-level chip design. It has evolved in response to a pervasive need for a language that improves overall productivity for designers of electronic systems. SystemC offers real productivity gains by letting engineers design both the hardware and software components together at a high level of abstraction. This gives the design team a fundamental understanding early in the design process of the intricacies and interactions of the entire system and enables better system trade-offs, better and earlier verification, and overall productivity gains through reuse of early system models as executable specifications.

SystemC provides mechanisms crucial to modeling hardware while using a language environment compatible with software development. It offers several hardware-oriented constructs that are not normally available in a software language but are required to model hardware. All of the constructs are implemented within the context of the C++ language. The major hardware-oriented features implemented

within SystemC include:

- Timed models

- Hardware data types

- Module hierarchy to manage structure and connectivity

- Communications management between concurrent units of execution

- Concurrency models

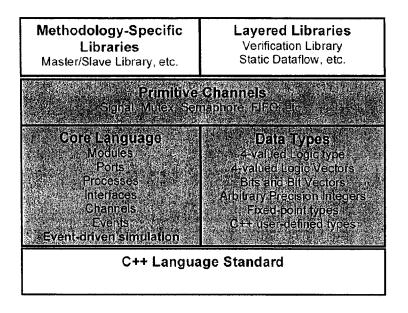

The SystemC language architecture is shown in Figure 2.1. The language is built on top of standard C++. The first layer of shaded gray blocks are part of the so called core layer (or layer 0) of the standard SystemC language. The second shaded gray layer immediately after the kernel layer is the layer 1 of SystemC; it comes with a predefined set of interfaces, ports and channels. Finally, the layers of design libraries above the layer 1 are considered separate from the SystemC language. The user may choose to use them or not. Over time other standard- or methodology-specific libraries may be added and conceivably be incorporated into the standard language.

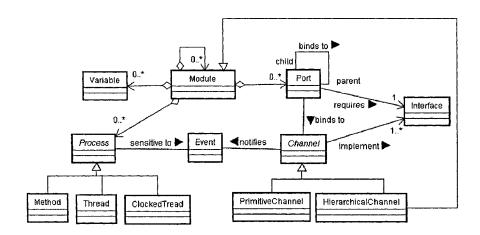

Figure 2.2 depicts a simplified metamodel [35] of the main SystemC terms and abstractions. SystemC has a notion of a container class, called *module*, that provides the ability to encapsulate structure and functionality of hardware/software blocks for partitioning system designs. A system is essentially broken down into a containment hierarchy of *modules*. Each module may contain *variables* as simple data members,

Figure 2.1: SystemC Language Architecture [17].

ports for communication with the outside environment and processes for performing modules functionality and expressing concurrency in the system. Three kinds of processes are available: method processes, thread processes, clocked thread processes. They run concurrently in the design and may be sensitive to events which are notified by channels. A port of a module is a proxy object through which the process accesses a channel interface. The interface defines the set of access functions (methods) for a channel, while the channel provides the implementation of these functions to serve as a container to encapsulate the communication of blocks. There are two kinds of channels: primitive channels and hierarchical channels. Primitive channels do not exhibit any visible structure, do not contain processes, and cannot (directly) access other primitive channels. A hierarchical channel is a module, i.e., it can have

structure, it can contain processes, and it can directly access other channels.

Figure 2.2: A Simplified SystemC MetaModel [35].

As mentioned earlier, SystemC permits to model a system at different levels of abstraction: functional untimed, functional timed, transactional, behavioral, bus cycle accurate (BCA) and register transfer level (RTL) [17]. These description levels may be freely mixed in the same design, however, hardware modeling is made at RTL or behavioral level. Typically, hardware modeling in SystemC is obtained by restricting the description style to the following rules: (i) modeling the communication by signals; (ii) modeling the functionality by processes sensitive to clocks and signals; (iii) use of modules to describe hierarchical designs.

## Chapter 3

# PCI-X Bus Modeling

In this chapter, we elucidate the PCI-X architecture and its modeling using the methodology that we presented in Chapter 1. It includes UML modeling, AsmL modeling and translation of AsmL to SystemC of the PCI-X.

#### 3.1 PCI-X Bus

Improvements in processors and peripheral devices have caused conventional PCI technology to become a bottleneck to performance scalability. The introduction of the PCI-X technology [40] has provided the necessary bandwidth and bus performance needed to avoid the I/O bottleneck, thus achieving optimal system performance. For instance, version 2.0 of PCI-X specifies a 64-bit connection running at speeds of 66, 133, 266, or 533 MHz, resulting in a peak bandwidth of 533, 1066, 2133 or 4266 MB/s, respectively.

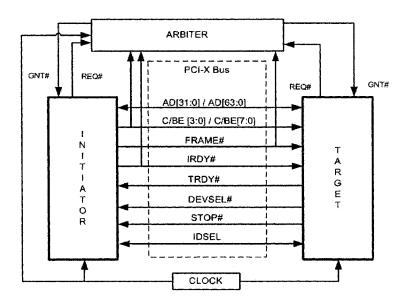

PCI-X provides backward compatibility by allowing devices to operate at conventional PCI frequencies and modes. Moreover, PCI-X peripheral cards can operate in a conventional PCI slot, although only at PCI rates and may require a 3.3 V conventional PCI slot. Similarly, a PCI peripheral card with a 3.3 V or universal card edge connector can operate in a PCI-X slot, however the bus clock will remain at a frequency acceptable to the PCI card. Figure 3.1 shows the general architecture of PCI-X with one initiator (master) and target (slave) and in Table 3.1, we show a list of PCI-X signals and it meanings. There is an arbiter that performs the bus arbitration among multiple initiators and targets. Unlike the conventional PCI bus, the arbiter in PCI-X systems monitors the bus in order to ensure good functioning of the bus.

Figure 3.1: General Architecture of PCI-X.

Table 3.1: PCI-X Signals

| Signals | Meanings                                   |  |  |

|---------|--------------------------------------------|--|--|

| AD      | Address of the data read or write          |  |  |

| C/BE    | Specifies the type of the command          |  |  |

| FRAME#  | Transaction initiation                     |  |  |

| IRDY#   | Signals the readiness of initiators        |  |  |

| TRDY#   | Signals the readiness of targets           |  |  |

| DEVSEL# | Enables to allow minimum decoding speed    |  |  |

| STOP#   | Signals the termination of the transaction |  |  |

| IDSEL#  | Configuring transactions timing            |  |  |

Both PCI-X initiator and target have a pair of arbitration lines that are connected to the arbiter. When an initiator requires the bus, it asserts REQ#. If the arbiter decides to grant the bus to that initiator, it asserts GNT#. FRAME# and IRDY# are used by the Arbiter to decide the granting of an initiator request for the bus. Unlike PCI, the targets can only insert wait states by delaying the assertion of TRDY#. TRDY# and IRDY# have to be asserted for a valid data transfer. An initiator can abort the transaction either before or after the completion of the data transfer by de-asserting the FRAME# signal. In contrast, a target can terminate a bus transaction by asserting STOP#. If STOP # is asserted without any data transfer, the target has issued a retry and if STOP# is asserted after one or more data phases, the target has issued a disconnect. Unlike PCI, the target has also REQ# and GNT# that are connected to the arbiter. This facilitates the Split

Transaction of PCI-X which does not exist in conventional PCI. In Split Transaction, the initiators and targets switch their roles. Split Transaction is very useful if a target can not be able to continue the current transaction. In this case, the target will memorize the transaction and signal a Split-telling the initiator not to retry IO read. When the data is ready, the target will send the initiator a Split Completion containing the data. The addition of PCI-X Split Completion frees up the bus for other transactions, making PCI-X more efficient than PCI. This notion of split transaction of PCI-X and its high bandwidth capacity makes the PCI-X bus pretty complex.

PCI-X supports two modes of operations: Mode 1 and Mode 2. Mode 1 operates at either 66 or 133 MHz and uses a parity error checking scheme and Error Correction Code (ECC) as optional. In Mode 1 operation, data transfers always use common clock. The higher transfer rates (266 or 533 MHz) in PCI-X 2.0 are defined in Mode 2, which uses ECC as its error correcting scheme. Mode 2 operation of PCI-X also supports 16 bit bus interface which facilitates low cost interface. Split Transactions in PCI-X replace Delayed Transactions in conventional PCI [40]. If a target cannot complete the transaction within the target initial latency limit, the target must complete that transaction as Split Transaction. If the target meets its initial latency limits, it can optionally complete the transaction immediately. All these aforementioned transactions' sequences are described vividly using sequence diagrams in Section 3.2.

#### 3.2 UML Modeling

UML representation is helpful for programmers, who talk different languages. From the specification of PCI-X, we identify the core components, i.e., initiators, targets, and arbiters, which will be represented as classes, where specific instances of the components are called as objects. In addition to these four components, we also added another component, the Simulation Manager (SimManager), in order to have a notion of updates. Figure 3.2 shows these five classes, where each has its own data members and methods with their access types. It also shows the relationship among each classes. For instance, the relationship between the arbiter and the initiators is one-to-many (1 - \*). It is because there can be only one arbiter which is connected to many initiators. For another example, the relationship between the SimManager and arbiter is one-to-one (1 - 1) as there can be only one SimManager and one arbiter in the system.

In order to model the system's architecture in UML, we had two options: (1) class diagram, or (2) composite structure diagram [25]. This latter representation offers more information about the object interaction. However, since our objective at the UML level was to identify the main modules in the system, the class diagram was enough expressive to answer our needs. For instance, we provide a complete and formal definition of the modules interactions at the AsmL level.

We modeled different modes and types of operations of PCI-X using sequence

diagrams. Sequence diagrams enable us to model the bus in AsmL easily and efficiently. Also, they help to extract the properties of the system being modeled, which can be used to verify using model checking. In addition, UML modeling helps to close the gap between informal specification and formal models in AsmL.

Figure 3.2: Class Diagram of PCI-X.

In Figure 3.3, we show the protocol sequence of a typical Mode 1 transaction of the PCI-X using a sequence diagram. Figure 3.3 is a best case scenario of Mode 1 transactions, with one initiator and one target and without any wait states. In the first clock cycle, the initiator asserts the REQ# signal to get the control of the bus by executing the methods  $Initiator\_Req()$ . The arbiter asserts the GNT# signal to that initiator through  $Arbiter\_GNT\_UPD()$ . In the third clock cycle, the address

Figure 3.3: Sequence Diagram of Mode 1 Transaction.

phase takes place and also the FRAME# signal is asserted by the initiator to signal the start of the transaction using the method Initiator\_FRAME\_Assert(). In the next clock cycle, the attribute phase takes place, where additional information included with each transaction is added. In clock cycle N+4, the DEVSEL# signal is asserted by the target using Target\_DEVSEL\_Assert() and in the next clock cycle, the data phase is started with the assertion of the IRDY# (Initiator\_IRDY\_Assert()) and TRDY# (Target\_TRDY\_Assert()) signals by the initiator and the target, respectively. Before the last data phase, the FRAME# signal is de-asserted using Initiator\_Termination() to signal the completion of the data transfer and in the termination phase all the other signals are de-asserted. In order to represent the clock constraints of the PCI-X transaction, we added an additional operator, "@",

to specify at which clock cycle a particular action should occur.

Figure 3.4 shows the protocol sequence of a typical Mode 2 transaction of PCI-X using a sequence diagram. Mode 2 transaction is pretty similar to Figure 3.3, except that there is an additional delay of one clock cycle (*Target Response Phase*) and one additional idle clock between any two transactions.

Figure 3.4: Sequence Diagram of Mode 2 Transaction.

In Figure 3.5, we show the transaction sequences of a 16 bit interface of Mode 2 transaction. In this transaction, the attribute phase takes two cycles unlike the transaction types. Other signal activities of this transaction are the same as the generic Mode 2 transaction. In the coming section, we present the AsmL modeling of PCI-X from UML.

Figure 3.5: Sequence Diagram of Mode 2 Transaction (16 bit).

### 3.3 AsmL Modeling

In this section, we show our approach of modeling the PCI-X in AsmL from UML representation by showing some of the important *methods* used. By having class diagrams in UML, it is easy to implement the classes in any language. We use AsmL's class features to model all the five core components of PCI-X discussed in the previous section. Each of these has its own data members (signals) and methods (behavior) in addition to the constructors. We also use enumeration features (*enum*) of AsmL to model different modes of PCI-X, different types of transaction phases, the state of the system and the clock (see Figure 3.6).

enum SystemStatus enum Clock CLK\_UP INIT CLK\_DOWN STARTED enum Transaction\_Mode enum Transaction\_Phase IDLE\_PHASE MODE\_1 ADDR\_PHASE MODE\_2 ATTR\_PHASE TGT\_RES\_PHASE DATA\_PHASE INR\_TER\_PHASE TURN\_AROUND\_PHASE

Figure 3.6: Used AsmL Enumeration Types.

In addition, we exhaustively use the require and ":=" statements of AsmL in our design approach. require is the pre-condition statement in AsmL used to check if a certain condition is satisfied in order to enable a method, and the operator ":=" represents an update statement used to change the system state. Figure 3.7 shows the AsmL model of the arbiter grant method (Arbiter\_GNT()). As the name of the method says it acts as an arbiter for granting the bus to the requesting initiator. In order to grant the bus to the requested initiator, this method has the following pre-conditions (require) to be met: (1) there must be at least one initiator requesting the bus and that initiator has not been granted the bus at the time of the request; (2) the clock is on the rising edge; and (3) the mode can be either Mode 1 or Mode 2. If these pre-conditions are met, the arbiter updates the GNT# signal.

In Figure 3.8, we show how a target can signal its readiness using TRDY# signal. We call this method as  $Target\_TRDY\_Assert()$ . The pre-conditions are the

Figure 3.7: Arbiter Grant AsmL Method.

following: TRDY# is false, FRAME# and DEVSEL# are true, CLK is CLK\_UP, Phase is DATA\_PHASE\_FIRST and the AD of the Bus should be the ID of the target. If the pre-conditions are true, then TRDY# will be asserted.

Figure 3.8: Target Assert AsmL Method.

Figure 3.9 shows the initiator termination method (*Initiator\_Termination*). This method basically signals the end of a transaction if *BYTECOUNT* is less than 2. *BYTECOUNT* indicates the number of bytes of data transfer in a transaction. This signaling is done by de-asserting the FRAME# signal and updating the transaction phase to the initiator termination phase (INI\_TER\_PHASE). This method

has a specific pre-conditions that need to be true so that it can terminate the transactions. The pre-conditions (require) are the following: initiator's REQ#, GNT#, FRAME#, IRDY#, DEVSEL#, TRDY# are asserted, BYTECOUNT is less than 2, and the clock is on the rising edge. If all the above pre-conditions are true, this method updates the FRAME# signal to false and the phase to INI\_TER\_PHASE. After this FRAME# signal de-assertion, the initiator's last phase method (Initiator\_LastPhase()) is invoked.

Figure 3.9: Initiator Termination AsmL Method.

Figure 3.10 shows the clock update method. It is a method of the SimManager class, which checks if the system and simulation are started in order to update the clock.

```

public SimManager_CLK_Update()

require SystemFlag = STARTED and SimStatus = RUNNING

if CLK = CLK_UP then

CLK := CLK_DOWN

else

CLK := CLK_UP

```

Figure 3.10: Clock Update AsmL Method.

Figure 3.11: Data Phase AsmL Method.

Figure 3.11 shows the data phase method of the AsmL code. The method decreases the *BYTECOUNT* by 1 based on the following pre-conditions: IRDY#, DEVSEL#, TRDY# are asserted, the phase has the value *DATA\_PHASE*, the clock is on the rising edge, and the system started running.

#### 3.4 Translation to SystemC

After the ASM model of PCI-X is verified against the PSL properties, we translate it to SystemC as this is the ultimate goal. The verification of the AsmL using model checking is discussed in the next chapter. The transformation of AsmL to SystemC is syntactical based on a set of rules developed in [19] and summarized as follows:

- Basic types: AsmL basic types are mapped to their equivalent SystemC types (e.g. Integer to int, Byte to unsigned char)

- Class members are translated into SystemC signals having the same basic type.

(e.g. var val as Integer to sc\_signal <int> val)

- Class methods in AsmL contain two parts: first one defining the pre-/post

conditions for its invocation and the second is the method itself. The first part is integrated in SystemC module's *constructor*. The method itself is integrated as is in the SystemC module.

• Global methods are integrated in the SystemC's main procedure sc\_main.

To illustrate the translation procedure, we show a sample code in Figure 3.12, the Arbiter class of the PCI-X in SystemC. All classes in AsmL modeling are represented as module (SC\_MODULE) in SystemC and the data members in AsmL are mapped as signals (sc\_signal) in SystemC. It is also possible to represent them as ports (sc\_port). The methods in AsmL class are represented as SC\_METHOD. SC\_METHOD is one type of modeling process in SystemC. In some sense, it is similar to the Verilog always@ block or the VHDL process. The SystemC simulation engine usually calls the SC\_METHOD process repeatedly based on the static or dynamic sensitivity. Static sensitivity establishes the parameters during elaboration (i.e., before simulation begins). It is established with a call to the sensitive() method or the overload stream operator << that is placed just following the registration of a process.

Dynamic sensitivity can also be used by means of the next\_trigger() method. It is somewhat similar to the traditional wait statement in HDLs. In our translation procedure, we use the static sensitivity scheme and the stream operator << for modeling the pre-condition statement (require) of AsmL. The method registration with sensitivity list is done in the constructor method (SC\_CTOR).

```

SC_MODULE (PCIX_Arbiter) {

sc_signal <int> Active_Initiator

sc_signal <bool> REQ;

sc_signal <bool> GNT;

sc_signal <int> CBE;

sc_signal <bool> FRAME;

sc_signal <bool> IRDY;

sc_signal <bool> STOP;

SC_CTOR (PCIX_Arbiter) {

Active_Initator = 0;

REQ = false;

GNT = false;

CBE = 0;

FRAME = false;

IRDY = false;

STOP = false;

SC_METHOD(PCIX_Arbiter_REQ_UPD);

sensitive << Initiators.REQ << Initators.GNT

<< REQ << GNT << Smanager.CLK;

SC_METHOD(PCIX_Arbiter_GNT_UPD);

sensitive << REQ << GNT << Smanager.CLK;</pre>

SC_METHOD (PCIX_Arbiter_Release);

sensitive << Initiators(me.Active_Initiator).REQ

<< Initiators(me.Active_Initiator).GNT</pre>

<< REQ << GNT << Smanager.CLK;

}

};

```

Figure 3.12: Arbiter Class Declaration in SystemC.

In Figure 3.12, we first show the data members of the class using  $sc\_signal$ . Then, we show the constructor definition of the class ( $SC\_CTOR$  ( $PCIX\_Arbiter$ )). In the constructor, we first do the initialization of the data members which is one of the purposes of having constructor in OO modeling. After that, we include the method registration using  $SC\_METHOD$  with the use of static sensitivity (sensitive) in order to fire that particular method.

The correctness of the above translation rules from AsmL to SystemC and vice versa, has been provided in [19] using abstract interpretation [10].

## Chapter 4

# **Model Checking**

In the last chapter, we have seen the AsmL modeling of PCI-X. In this chapter, we are going to define a set of properties in PSL in order to verify the AsmL model through model checking. The properties are easy to obtain from the sequence diagrams of the UML representation and also from the specifications. This chapter also includes the model checking results and its limitation.

### 4.1 Background

Model checking [9] is an FSM based formal verification technique that can be used to determine the validity of the properties written in some temporal logic with respect to a behavioral model of a system but it is impossible to determine whether the given specification covers all the properties that the system should satisfy. Model checking is based on the state space exploration technique, and uses the reachability state

graph as a Kripke structure, which encodes the set of all possible sequences of states for a system over computation trees. Model checking tools are effective as debugging aids for industrial designs, and since they are fully automated, minimal user effort and knowledge about the underlying technology is required to be able to use them. However, there are two drawbacks with model checking. The first drawback is the state space explosion and how to avoid it, and the second is the difficulty of judging whether the verified property completely characterizes the desired behavior of the system.

#### 4.2 Model Checking Approach

The way we perform model checking is different than the classical approach. In the classical approach, the properties and the design being modeled are given separately to the model checking tool. But, in our approach, once the modeling of PCI-X in AsmL is done, we include the defined PSL properties in the AsmL design. Then, the AsmL design with the properties is fed to the Asmlt tester that generates an FSM of the model. Using Asmlt, we perform state exploration which gives the notion of model checking. We encode the properties evaluation in every state, which enables checking its correctness on-the-fly while executing the FSM generation algorithm [15] (part of the Asmlt). Any incorrect property detection halts the reachability algorithms and outputs a sub-portion from the complete FSM, which can be used to identify counter-examples.

Properties are embedded in every state in the FSM generated by the Asmlt and is represented by two Boolean state variables  $P_{eval}$  and  $P_{val}$ .  $P_{eval}$  represents whether a property can be evaluated or not and  $P_{val}$  denotes the state of the property in the current state. A violated property is detected if  $P_{eval} = true \ P_{val} = false$ . A correct verification process results on the generation of the system's FSM. If the property is not verified, then an error trace would be generated. In the case of state explosion, the FSM generation will become unsuccessful. In the next section, we show the properties that we defined.

#### 4.3 Model Properties

We define various properties of the PCI-X bus in PSL. The properties are obtained from the sequence diagrams and the informal specification. Some of the properties that we show are generic to any bus protocols and others are specific to PCI-X. The first property P1 shown in Figure 4.1, is a common behavior for any bus standard. It states that if an initiator is requesting the bus (!Initiator.REQ == true), it will eventually be granted (!Initiator.GNT == true). This also makes sure the fact that no initiator will be using the bus indefinitely. It is to be noted that all signals of PCI-X are active-low.

Property P2 in Figure 4.2 is about the termination of a PCI-X transaction be it Mode 1 or Mode 2. It means that if an initiator is terminating the bus by asserting the STOP signal, then eventually the bus will be released by de-asserting the

```

Property P1:

forall Initiator in {Initiator0, ..., Initiator4}

if(!Initiator.REQ == true) then

eventually (!Initiator.GNT == true)

```

Figure 4.1: Property P1.

FRAME signal and targets will be released by de-asserting TRDY and DEVSEL.

```

Property P2:

forall Initiator in {Initiator0, ..., Initiator4}

if((!Initiator.STOP == true) and

(!Initiator.GNT == true)) then

eventually {(!Bus.FRAME == false) and

forall Target in {Target0, ..., Target4}

(!Target.TRDY == false) and

(!Target.DEVSEL == false)}

```

Figure 4.2: Property P2.

```

Property P3:

forall Initiator in {Initiator0, ..., Initiator4}

if(!Initiator.GNT == true) then

next[0] (!Initiator.FRAME == true)

```

Figure 4.3: Property P3.

Property P3 in Figure 4.3 is for the assertion of FRAME signals. This property is important for the start of the transaction. If an initiator is granted to the bus, then in the next clock cycle the FRAME signal has to be asserted.

Property P4 (Figure 4.4 is to check the phase (ADDR\_PHASE, ATTR\_PHASE, IDLE\_PHASE) of the transaction. If the initiator FRAME signal is asserted, then in the next clock cycle, the phase of the transaction will be the attribute phase (ATTR\_PHASE).

```

Property P4:

forall Initiator in {Initiator0, ..., Initiator4}

if(!Initiator.FRAME == true) then

next[0] (Transaction_Phase == ATTR_PHASE)

```

Figure 4.4: Property P4.

```

Property P5:

forall Initiator in {Initiator0, ..., Initiator4}

forall Target in {Target0, ..., Target4}

if((!Target.GNT == true) and

(!Initiator.DEST == Target.ID)) then

eventually {(!Bus.FRAME == true) and

(!Initiator.TRDY == true) and

(!Target[ID].TRDY == true) and

(!Target.GNT == false)}

```

Figure 4.5: Property P5.

Property P5 in Figure 4.5 is regarding the arbitration of the bus. If an initiator is selected by the arbiter, then it will be able to get access to the bus by setting !Bus.FRAME. Then, its destination target will be activated by setting its !Target.TRDY and the initiator will release the bus once !Initiator.GNT is set to false.

Property P6 in Figure 4.6 is to check the initiation of a transaction termination when data transfer is about to be completed. If BYTECOUNT is equal to one (data transfer is in the penultimate cycle), then in the current cycle FRAME will be deasserted.

Property P7 (Figure 4.7 is somewhat similar to P6. The property says that if the data transfer is over (BYTECOUNT == 0), then in the next clock cycle, initiator's IRDY will be de-asserted.

Property P8 in Figure 4.8 is to check the response of a target when it has been selected as destination. This property is specific for Mode 1 transaction. The property says that if the transaction mode is MODE\_1 and the initiator's FRAME is asserted, then eventually the IRDY and TRDY of the initiator and target respectively, will be asserted.

Figure 4.7: Property P7.

```

Property P8:

forall Initiator in {Initiator0, ..., Initiator4}

forall Target in {Target0, ..., Target4}

if((!Initiator.FRAME == true) and

(Transaction_Mode == MODE_1)) then

eventually {(!Initiator.IRDY == true) and

(!Target.TRDY == true)}

```

Figure 4.8: Property P8.

Property P9 in Figure 4.9 is similar to P8 but it is related to the Mode 2 transaction. If FRAME is asserted and transaction is Mode 2 then eventually IRDY and DEVSEL will be asserted together.

Property P10 shown in Figure 4.10 is about the target response property of

Figure 4.9: Property *P9*.

Mode 2 transaction. If FRAME, IRDY, DEVSEL are asserted and transaction is Mode 2, then in the next clock cycle, TRDY will be asserted.

```

Property P10:

forall Initiator in {Initiator0, ..., Initiator4}

forall Target in {Target0, ..., Target4}

if(!Initiator.FRAME == true) and

(!Initiator.IRDY == true) and

(!Target.DEVSEL == true) and

(Transaction_Mode == MODE_2) then

next (!Target.TRDY == true)

```

Figure 4.10: Property P10.

Property P11 in Figure 4.11 checks the idle phase of Mode 2 transaction after a transaction has completed. It says that if IRDY, STOP, DEVSEL, TRDY are de-asserted then in the next clock cycle, the phase of the transaction will be idle. In other words, the bus will be idle.

Property P12 in Figure 4.12 is about the initiation of Split transaction. In split transaction, the target can request for the bus (!Target.REQ == true) and it can be eventually granted (!Target.GNT == true).

Figure 4.12: Property P12.

#### 4.4 Experimental Results

Table 4.1 details the results of model checking of PCI-X model (5 initiators and 5 targets). In the table, we show the CPU time, number of states and transitions for the PCI-X model with the various properties defined. The experiments were performed on a Pentium IV processor (2.4 GHz) with 768 MB of memory. As can be seen from the table, all properties have been verified except Property 6 and Property 7 due to a state explosion problem. This is due to the fact that these properties are related to the successful completion of a data transfer. When the BYTECOUNT is large, the action PCIX\_BUS\_DataPhase() will be enabled many times and would lead to state explosion. This is a classical problem of model checking and many techniques have been proposed in the recent past to alleviate this problem but not

Table 4.1: Model Checking Results

| Property | CPU Time (s) | States | Transitions |

|----------|--------------|--------|-------------|

| P1       | 385.24       | 2169   | 3250        |

| P2       | 194.23       | 1800   | 2563        |

| P3       | 150.52       | 1578   | 2156        |

| P4       | 130.45       | 1489   | 2096        |

| P5       | 156.35       | 1478   | 2265        |

| P6       | _            | _      | -           |

| P7       | _            |        |             |

| P8       | 173.50       | 1925   | 2439        |

| P9       | 174.47       | 2013   | 2698        |

| P10      | 178.42       | 1873   | 2359        |

| P11      | 256.63       | 2192   | 2980        |

| P12      | 143.52       | 1356   | 1923        |

to eradicate it. Even though, the CPU time to verify the properties is relatively shorter, we also have to consider the time spent to write the properties and to learn the tool. It is also possible to model check the SystemC design but the state space explosion will be worse considering the complexity of the SystemC simulation semantics and the OO nature of the language.

## Chapter 5

# Generating FSM from SystemC

In the last chapter, the model checking of the PCI-X in AsmL model was shown. Once the model checking of the AsmL model is done, we translate it to SystemC. In order to the validate the SystemC model, we provide two FSM generation algorithms from which MBT can be applied. In this chapter, we provide the formalization of these two algorithms and the experimental results.

### 5.1 Background

The work in [15] derives an FSM from the ASM languages like AsmL. The FSM-generating algorithm is a particular kind of graph reachability algorithm. It starts from the initial state and builds up a labeled state transition graph by invoking actions that are parts of the ASM. The FSM generation allows them to integrate with the existing tools (Asmlt) to derive test suites to achieve model based testing.

In [5], the FSM generation algorithm is extended from [15] to have compact FSMs using the notion of state groupings. The work in [5] considers both AsmL and Spec# as the source language. Nevertheless, these two works can be only applicable for ASM languages. For SystemC, these algorithms can not be used directly as its syntax is different and the notion of SystemC simulator has to be considered.

To tackle this issue, we provide a formalization of two algorithms to generate FSM from SystemC. These two algorithms are extended from [15, 5]. We adapt the work in [15, 5] based on the existing SystemC semantics [19, 14] to generate FSM from SystemC. At first, the given SystemC design is analyzed to collect the necessary inputs for the FSM generation. Then, we apply one of the two algorithms that we propose to generate FSMs. We call the first *Direct Algorithm* and the second one as *Grouping Algorithm*. Both algorithms perform a state exploration procedure in order to discover all possible system's state starting from a set of initial states. The grouping algorithm's exploration procedure is very similar to the direct one but it has grouping conditions as an additional input. More details about grouping algorithm will be discussed in Section 5.4.3. In the coming sections, we detail the SystemC syntactical domains that are needed to collect the inputs for the algorithms.

## 5.2 SystemC Syntactical Domain

The SystemC language has a large number of syntactical domains. These, however, are based on the single SC\_Module domain [19]. Hence, the minimum representation

for a general SystemC design is a set of modules.

In SystemC, the structural decomposition is specified with modules, which are the basic building blocks. A SystemC description consists of a set of connected modules, each encapsulating some behavior or functionality. Modules can be hierarchical, containing instances of other modules. The nesting of hierarchy can be arbitrarily deep, which is an important requirement for structural design representation. The formal definition of an SC\_Module is given in the following:

#### Definition 5.2.1. SystemC Module: (SC\_Module)

A SystemC Module is a tuple (DMem, Ports, Chan, Mth, SC\_Ctr), where DMem is a set of the module data members, Ports is a set of ports, Chan a set of SystemC channels, Mth is a set of methods (functions) definition and SC\_Ctr the module constructor.

The simplest means of connecting together different SystemC modules is by using ports (SC\_Port) and signals. Formally, a SystemC port is a tuple (IF, N, SC\_In, SC\_Out, SC\_InOut), where IF is a set of the virtual methods declarations, N is the number of interfaces that may be connected to the port, SC\_In is an input port (provides only a Read method), SC\_Out is an output port (provides only a Write method) and SC\_InOut is an input/output port (provides Read and Write functions).