# Design, Fabrication and Characterization of RF MEMS Inductors and Switches

Alireza Hajhosseini Mesgar

A Thesis

In

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at Concordia University Montréal, Québec, Canada

April 2006

© Alireza Hajhosseini Mesgar, 2006

Library and Archives Canada

Branch

Published Heritage

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-494-14259-6 Our file Notre référence ISBN: 0-494-14259-6

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

## **Abstract**

Design, Fabrication and Characterization of RF MEMS Inductors and Switches

Alireza Hajhosseini Mesgar

MicroElectroMechanical Systems (MEMS) concept covers different miniature devices in different disciplines, including but not limited to biological, chemical, electrical, fluidic, magnetic, optical, and thermal applications. The driving forces for the miniaturization of systems include cost, size, speed, weight, precision and reliability while providing an effective interface between the macro and micro world. In this thesis RF MEMS switches and inductors are studied.

Initially, the background of MEMS, RF MEMS and fabrication technologies are introduced. Then switch and inductor are introduced. Theory, different configurations, designs, and fabrication technologies are considered. Finally proposed designed components are given. Each design is verified through software simulations.

Modeling and simulation is the next step. Switches are simulated by MATLAB. Inductors are designed using MATLAB and simulated by ADS-Momentum.

Switches are fabricated in the Multi-User MEMS Process (MUMPs) which uses a surface micromachining technique. Inductors are fabricated in both MUMPs and CMOS processes. MUMPs chips require a simple post-fabrication processing that is soaking them in hydrofluoric acid to remove the sacrificial silicon oxide layer For CMOS inductors, bulk-micromachining required post-processing is performed after fabrication.

Device characterization is done using the appropriate methods. For switches, in order to find pull-in voltage, DC test is performed, but for inductors, to find the variation of impedance with frequency, RF measurement using on-wafer probes and vector network analyzer is done. Then measurement results are given and are interpreted.

Finally, conclusions, some suggestion to improve the designs, and future work are given.

# Acknowledgements

First of all I have to thank my supervisor Dr. Mojtaba Kahrizi.

Also I have to thank Dr. Oleg Grudin and Mechanical Eng. Lab. for assistance in wire bonding the chips, Jun Chen for SEM photography, Shailesh Prasad (lab facilities), Tommy Tsang, and Dr Mourad El-Gamal from McGill RFIC Lab for performing some measurements, David Celemencki, Ibrahem Abdella and Dr. Christopher Trueman from Concordia Microwave Lab for their helps(measurements), Joseph Woods from Power Lab (equipment).

Doing this project was not possible without partial support from NSERC and fabrication grants and some equipment from CMC Microsystems.

I thank all of my colleagues in Concordia Microfabrication lab for all the constructive discussions. I specially thank my friend Siamak Fouladi for his collaboration.

I'm much indebted to my parents for their support during my studies and my whole life.

# **Table of Contents**

| List of F | guresix                                  |

|-----------|------------------------------------------|

| List of T | ablesxiv                                 |

| 1. Introd | action                                   |

| 1.1       | Motivation                               |

| 1.2       | RF MEMS Inductors                        |

| 1.3       | RF MEMS Switches2                        |

| 1.4       | Thesis Outline2                          |

| 2. Backg  | round4                                   |

| 2.1       | MEMS4                                    |

| 2.1.      | 1 What is it?                            |

| 2.1.      | 2 History of MEMS                        |

| 2.1.      | Fabrication and Materials5               |

| 2.2       | MEMS Devices and Applications            |

| 2.3       | RF MEMS Devices                          |

| 2.3.      | 1 RF MEMS Switches                       |

| 2.3.      | 2 RF MEMS (Fixed) Capacitors             |

| 2.3.      | RF MEMS Varactors (Variable Capacitors)  |

| 2.3.      | 4 RF MEMS Inductors 12                   |

| 2.3.      | 5 Microwave Components                   |

| 2.4       | Fabrication Technologies                 |

| 2.4.      | 1 Wafer-level processes                  |

| 2.4.      | Pattern Transfer Methods                 |

| 2.4.      | The Complete Process                     |

| 2.5       | Micromachining Techniques                |

| 2.5.      | Surface Micromachining Technique         |

| 2.5.      | 2 Bulk Micromachining Technique          |

| 2.5.      | Other Methods                            |

| 2.6       | PolyMUMPS Surface Micromachining Process |

| 2.6  | .1   | Process Definition                                           | 22     |

|------|------|--------------------------------------------------------------|--------|

| 2.6  | .2   | Releasing the PolyMUMPS Devices                              | 25     |

| 2.7  | CM   | OS Process Technology                                        | 25     |

| 2.7  | .1   | TSMC CMOS 0.35 Specifications                                | 26     |

| 2.7  | .2   | Silicon Bulk Micromachining Techniques for CMOS Process      | 29     |

| 2.8  | Isot | ropic Wet Etching of Silicon                                 | 33     |

| 2.9  | Ani  | sotropic Wet Etching of Silicon                              | 34     |

| 2.9  | .1   | EthyleneDiamine-Pyrocatechol Water                           | 37     |

| 2.9  | .2   | Potassium and Sodium Hydroxide (KOH and NaOH)                | 38     |

| 2.9  | .3   | Ammonium Hydroxide (NH4OH)                                   | 39     |

| 2.9  | .4   | Hydrazine (NH2NH2)                                           | 39     |

| 2.9  | .5   | Tetramethyl Ammonium Hydroxide                               | 40     |

| 2.9  | .6   | Silicon Etching with TMAH and Additives                      | 41     |

| 2.10 | Isot | ropic Dry Etching of Silicon                                 | 45     |

| 2.11 | Ani  | sotropic Dry Etching of Silicon                              | 46     |

| 2.12 | Oxi  | de Removal Methods                                           | 46     |

| 2.1  | 2.1  | Oxide Wet Etching                                            | 47     |

| 2.1  | 2.2  | Dry Etching of Oxide                                         | 48     |

| 2.13 | Swi  | tches                                                        | 48     |

| 2.1  | 3.1  | Mechanical (Electromechanical) Switches                      | 48     |

| 2.1  | 3.2  | Solid State Switches                                         | 49     |

| 2.1  | 3.3  | RF Switches                                                  | 49     |

| 2.14 | RF   | Switches in MEMS Technology (Compared with Semiconductor Swi | tches) |

|      | 50   |                                                              |        |

| 2.15 | App  | olications of RF MEMS Switches                               | 51     |

| 2.16 | Swi  | tch Parameters                                               | 53     |

| 2.17 | Act  | uation mechanisms                                            | 54     |

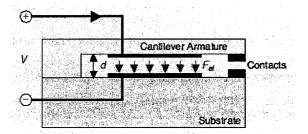

| 2.1  | 7.1  | Electrostatic                                                | 54     |

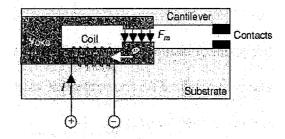

| 2.1  | 7.2  | Magnetic                                                     | 55     |

| 2 1  | 73   | Piezoelectric                                                | 55     |

|    | 2.17   | .4    | Thermal                                      | 56 |

|----|--------|-------|----------------------------------------------|----|

|    | 2.17   | .5    | Hybrid actuation mechanisms                  | 57 |

| 3. | Design | and   | Simulation of MEMS RF Switches               | 58 |

|    | 3.1    | Elect | trostatic Actuation Mechanism                | 58 |

|    | 3.2    | Adva  | antages and Disadvantages                    | 60 |

|    | 3.3    | Desi  | gn                                           | 61 |

| 4. | Design | and ! | Simulation RF MEMS Inductors                 | 76 |

|    | 4.1    | Indu  | ctors                                        | 76 |

|    | 4.1.1  | l     | Inductor Structures                          | 77 |

|    | 4.1.2  | 2     | Variable (Tunable) Inductors                 | 78 |

|    | 4.2    | Indu  | ctor Design                                  | 79 |

|    | 4.2.1  | l     | Modified Wheeler Inductor Model              | 80 |

|    | 4.2.2  | 2     | Current Sheet Approximation                  | 81 |

|    | 4.2.3  | 3     | Data-Fitted Monomial Expressions             | 81 |

|    | 4.2.4  | 4     | Strip (Ribbon) Inductor                      | 82 |

|    | 4.2.5  | 5     | Loop Inductor                                | 83 |

|    | 4.2.€  | 5     | Bonding wire inductor                        | 84 |

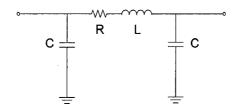

|    | 4.3    | Lum   | ped-Element Models of Inductors              | 84 |

|    | 4.4    | Spira | al Layout Parameters                         | 86 |

|    | 4.5    | Indu  | ctor Design Considerations                   | 87 |

|    | 4.6    | Indu  | ctor Calculations Using given Models         | 87 |

|    | 4.7    | Desi  | gns                                          | 88 |

|    | 4.7.1  | l     | MUMPS Designs                                | 88 |

|    | 4.7.2  | 2     | CMOS Designs                                 | 91 |

|    | 4.8    | Indu  | ctor Simulation                              | 93 |

|    | 4.8.1  | 1     | Quality Factor Calculation from S-Parameters | 93 |

|    | 4.9    | Etch  | Simulation                                   | 99 |

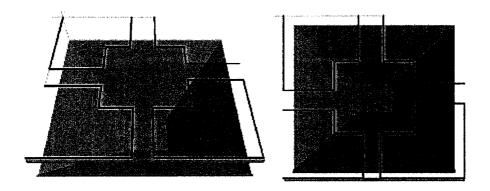

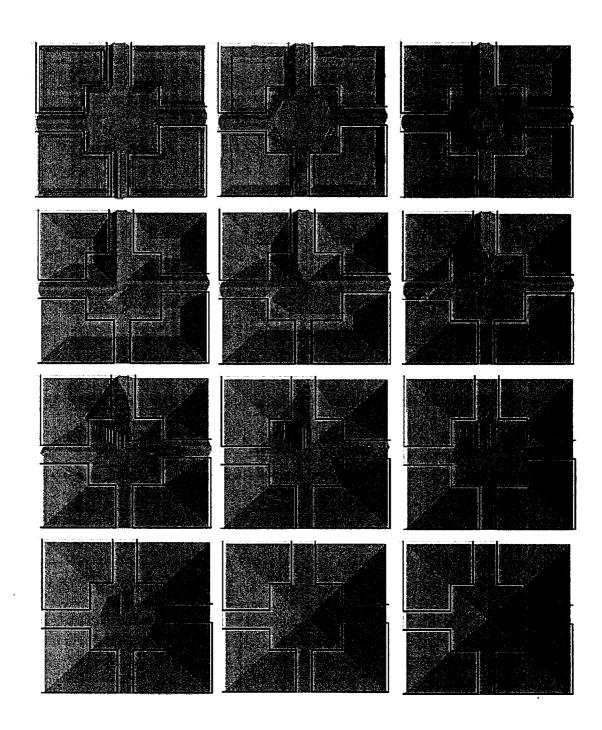

|    | 4.9.1  | l     | Anisotropic Wet Etching Using Etch Mask 2 1  | 01 |

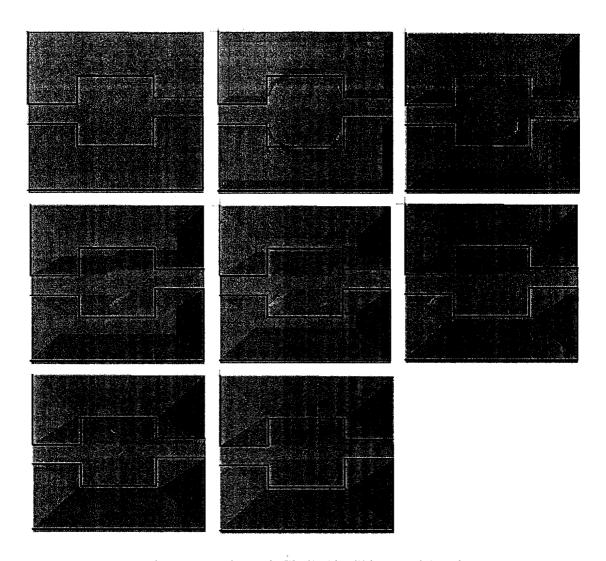

|    | 4.9.2  | 2     | Isotropic Wet Etching Using Etch Mask 2 1    | 01 |

|    | 4.9.3  | 3     | RIE Using Etch Mask 2                        | 02 |

|    | 4.9.   | 4      | Anisotropic Wet Etching Followed by RIE                     | 103        |

|----|--------|--------|-------------------------------------------------------------|------------|

|    | 4.9.   | 5      | RIE Followed by Anisotropic Wet Etching Using Etch Mask 2   | 103        |

|    | 4.9.   | 6      | Isotropic Wet Etching Followed by Anisotropic Wet Etching U | Jsing Etch |

|    | Mas    | sk 2   | 106                                                         |            |

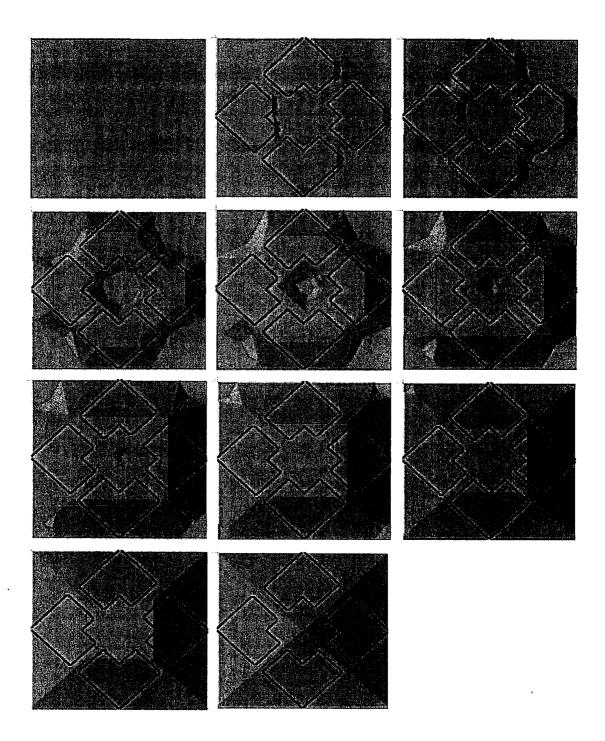

|    | 4.9.   | 7      | Anisotropic Wet Etching Using Etch Mask 4                   | 108        |

|    | 4.9.   | 8      | Anisotropic Wet Etching Using Etch Mask 6                   | 108        |

|    | 4.9.   | 9      | Anisotropic Wet Etching Using Etch Mask 5                   | 110        |

|    | 4.9.   | 10     | Anisotropic Wet Etching Using Etch Mask 7                   | 111        |

|    | 4.9.   | 11     | Anisotropic Wet Etching Using Etch Mask 8                   | 112        |

| 5. | Fabric | ation  | and Post-Processing                                         | 115        |

|    | 5.1    | Fabi   | rication                                                    | 115        |

|    | 5.2    | Post   | -Processing                                                 | 118        |

|    | 5.2.   | 1      | Wet Oxide Removal by Buffered HF                            | 118        |

|    | 5.2.   | 2      | Dry Oxide Removal by RIE                                    | 120        |

|    | 5.2.   | 3      | Bulk Micromachining                                         | 123        |

| 6. | Charae | cteriz | ation                                                       | 126        |

|    | 6.1    | DC     | Characterization of Switches (Pull-in Voltage Measurement)  | 126        |

|    | 6.2    | RF o   | characterization using VNA                                  | 131        |

| 7. | Conch  | usion  |                                                             | 135        |

|    | 7.1    | Con    | clusions                                                    | 135        |

|    | 7.2    | Sug    | gested Future Work                                          | 136        |

| 8. | Refere | nces   |                                                             | 137        |

| 9. | Apper  | ıdix 1 | Least Square Estimation                                     | 153        |

# **List of Figures**

| Figure 2.1 Backshooter Printhead [23]                                                      |

|--------------------------------------------------------------------------------------------|

| Figure 2.2 CMOS Micromachined Power Divider [36]                                           |

| Figure 2.3 Micromachined CMOS Coplanar Waveguide [37]                                      |

| Figure 2.4 Tapered Slot Antenna on Micromachined Photonic Bandgap Dielectrics [38]         |

| 14                                                                                         |

| Figure 2.5 Furnace for Silicon Oxidation                                                   |

| Figure 2.6 Pressure Sensor Using Wafer Bonding for Packaging [44]                          |

| Figure 2.7 A Photolithography and Etching Sequence [1]                                     |

| Figure 2.8 LIGA Process Steps                                                              |

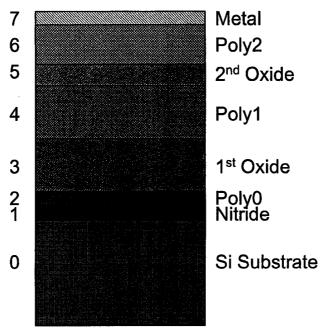

| Figure 2.9 PolyMUMPS Layers                                                                |

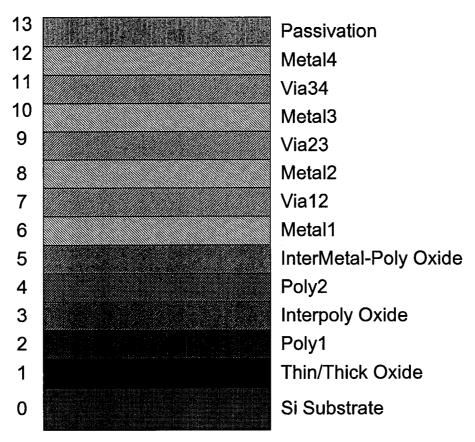

| Figure 2.10 CMOS 0.35 Layers                                                               |

| Figure 2.11 Cross Section of an Isotropic Silicon Etch                                     |

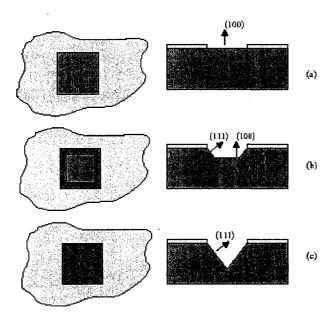

| Figure 2.12 A square mask opening results in an inverted pyramidal cavity. Initially, only |

| (100) silicon is exposed (a). As the (100) silicon etches, the slowly etching (111)        |

| planes become exposed (b), until etching terminates on the intersection of four (111)      |

| type planes (c).                                                                           |

| Figure 2.13 Arbitrary dark field mask openings result in inverted pyramidal cavities with  |

| the base defined by the smallest rectangle that completely contains the mask pattern.      |

|                                                                                            |

| Figure 2.14 Required amount of dissolved silicon to passivate exposed aluminum for various |

| TMAH concentrations [73]                                                                   |

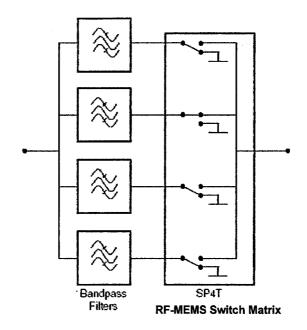

| Figure 2.15 Structure of a MEMS RF Switch [94]                                             |

| Figure 2.16 Application of Switches (a) Phased Arrays, (b) Switched Filter Banks for       |

| Wireless Applications, and (c) SP2T T/R Switches [94] 52                                   |

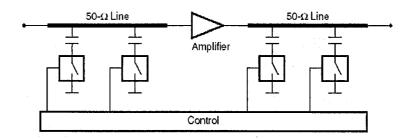

| Figure 2.17 A Reconfigurable Filter [2]                                                    |

| Figure 2.18 A Reconfigurable Amplifier [2]                                                 |

| Figure 2.19 Electrostatic Actuation Mechanism                                              |

| Figure 2.20 Magnetic Actuation Mechanism                                                   |

| Figure 2.21 Piezoelectric Actuation Mechanism                                     | 56             |

|-----------------------------------------------------------------------------------|----------------|

| Figure 2.22 Thermally actuated switch                                             | 57             |

| Figure 2.23 Themally-Electrically Actuated Switch [104]                           | 57             |

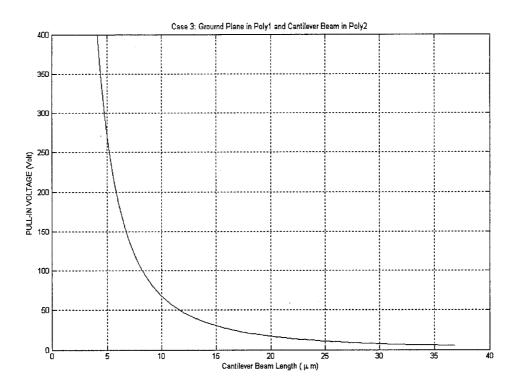

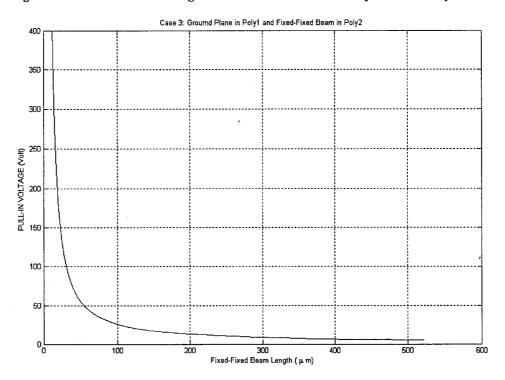

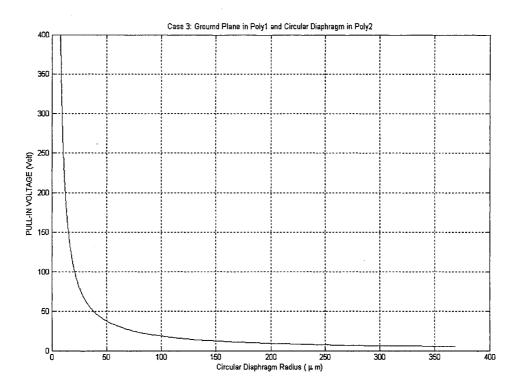

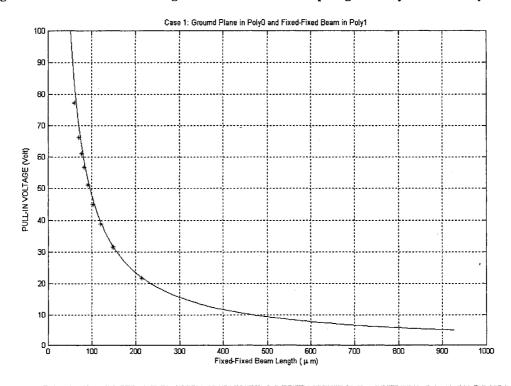

| Figure 3.1 Possible Test Structures [106-108]                                     | 63             |

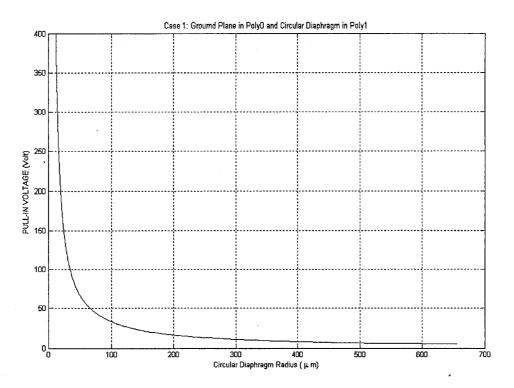

| Figure 3.2 Case 1: Pull-in Voltage Between a Fixed Beam in Poly1 and the          | e Poly0 Plane  |

|                                                                                   | 6 <del>6</del> |

| Figure 3.3 Case 1: Pull-in Voltage Between a Fixed-Fixed Beam in Poly1 a          | and the Poly(  |

| Plane                                                                             | 6 <del>6</del> |

| Figure 3.4 Case 1: Pull-in Voltage Between a Circular Diaphragm in Poly1 a        | and the Poly(  |

| Plane                                                                             | 67             |

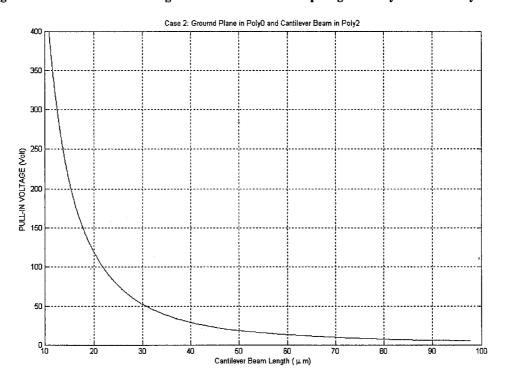

| Figure 3.5 Case 2: Pull-in Voltage Between a Fixed Beam in Poly2 and the          | •              |

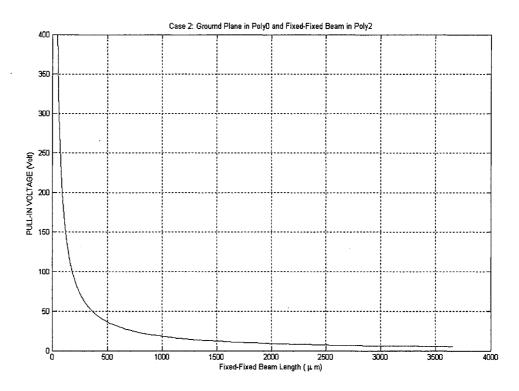

| Figure 3.6 Case 2: Pull-in Voltage Between a Fixed-Fixed Beam in Poly2 a          | •              |

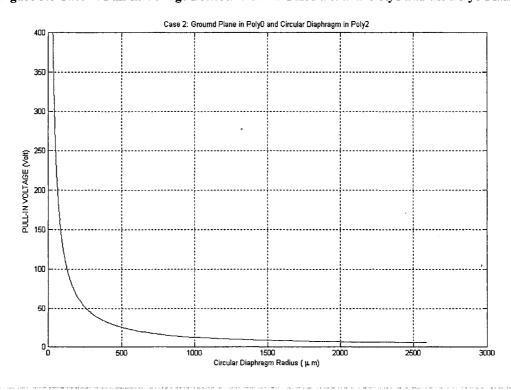

| Figure 3.7 Case 2: Pull-in Voltage Between a Circular Diaphragm in Poly2 a        | •              |

| Figure 3.8 Case 3: Pull-in Voltage Between a Fixed Beam in Poly2 and the          | •              |

| Figure 3.9 Case 3: Pull-in Voltage Between a Fixed-Fixed Beam in Poly2 a          | •              |

| Figure 3.10 Case 3: Pull-in Voltage Between a Circular Diaphragm in P Poly1 Plane | •              |

| Figure 3.11 Pull-in Voltages Between Designed Fixed-Fixed Beams in P              | oly1 and the   |

| Poly0 Plane                                                                       | 70             |

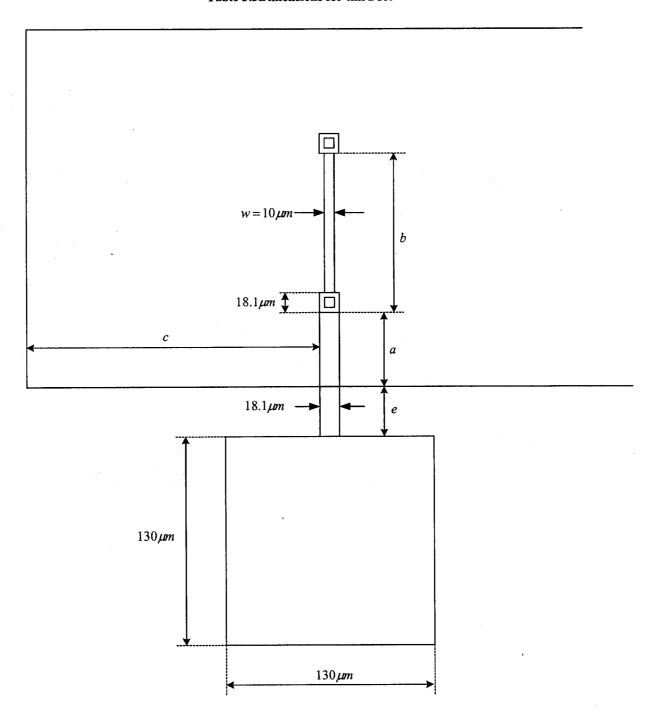

| Figure 3.12 Top View of a FB Connected to a Pad                                   | 72             |

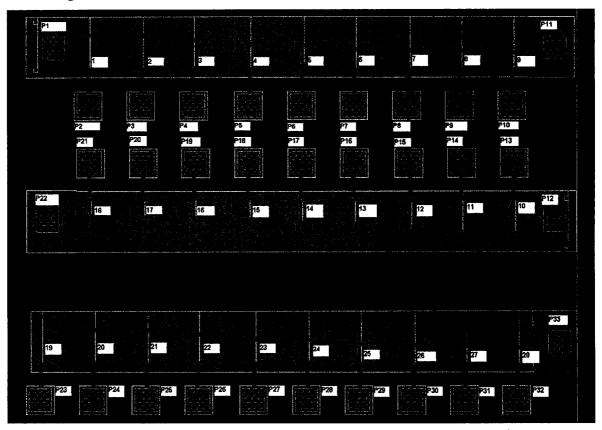

| Figure 3.13 Layout of the Beams Designed by Cadence                               | 73             |

| Figure 3.14 Top View of a Beam with Etch Holes                                    | 74             |

| Figure 3.15 3D View of a Beam with Etch Holes                                     | 74             |

| Figure 3.16 View of One Row of Beams                                              | 75             |

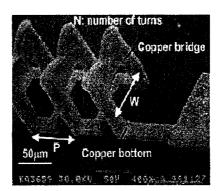

| Figure 4.1 Surface Micromachined Solenoid [110]                                   | 7 <sup>'</sup> |

| Figure 4.2 Tunable Inductor [111]                                                    |

|--------------------------------------------------------------------------------------|

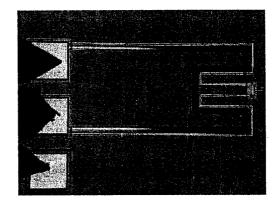

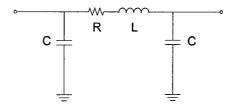

| Figure 4.3 Strip Inductor                                                            |

| Figure 4.4 Circuit Model of a Strip Inductor                                         |

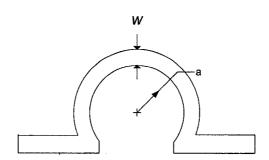

| Figure 4.5 Loop Inductor                                                             |

| Figure 4.6 Circuit Model of Loop Inductor                                            |

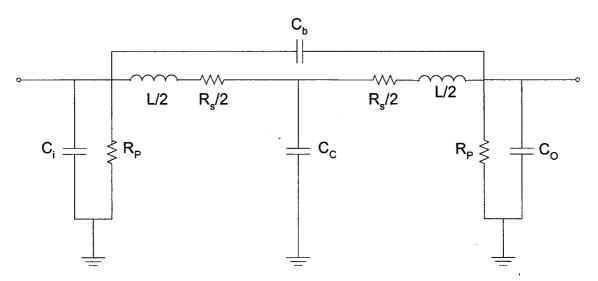

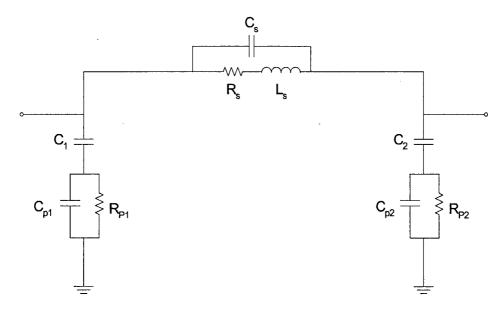

| Figure 4.7 Inductor Model 1 [17]                                                     |

| Figure 4.8 Inductor Model 2 [9]                                                      |

| Figure 4.9 Inductor Model 3 [117]                                                    |

| Figure 4.10 square spiral inductor Figure 4.11 Hexagonal Spiral Inductor 86          |

| Figure 4.12 Octagonal Spiral Inductor Figure 4.13 Circular Spiral Inductor 86        |

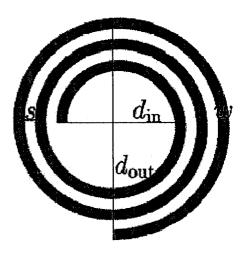

| Figure 4.14 MUMPS Inductor IND1: n=6, w=12μm, s=3μm, d <sub>in</sub> =50μm           |

| Figure 4.15 MUMPS Inductor IND2: n=4, w=12μm, s=3μm, d <sub>in</sub> =50μm90         |

| Figure 4.16 MUMPS Inductor IND3: n=3, w=12μm, s=3μm, d <sub>in</sub> =50μm90         |

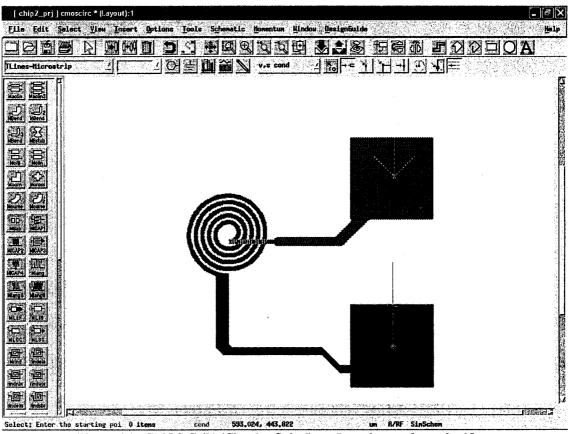

| Figure 4.17 CMOS Coil1 (Circular Spiral): n=5, w=6μm, s=2μm, d <sub>in</sub> =18μm   |

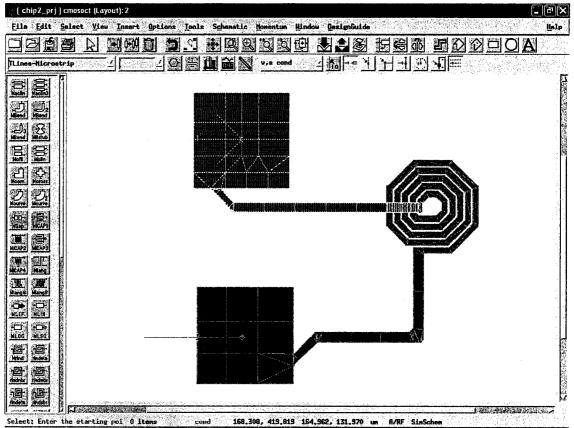

| Figure 4.18 CMOS Coil2 (Octagonal Spiral) : n=5, w=6μm, s=2μm, d <sub>in</sub> =19μm |

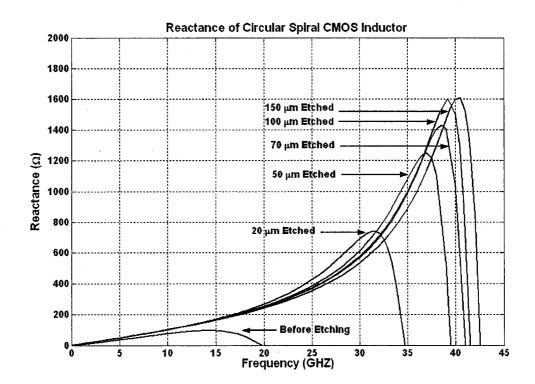

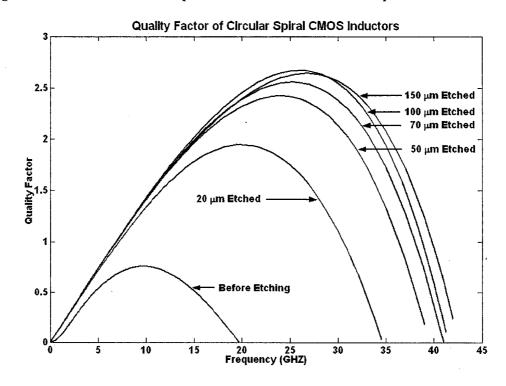

| Figure 4.19 Reactance of CMOS Spiral Inductor for Different Etch Depths Beneath the  |

| Inductor96                                                                           |

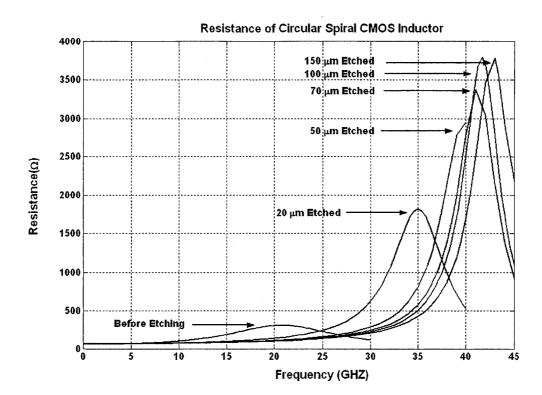

| Figure 4.20 Resistance of CMOS Spiral Inductor for Different Etch Depths Beneath the |

| Inductor                                                                             |

| Figure 4.21 Quality Factor of CMOS Spiral Inductor for Different Etch Depths Beneath |

| the Inductor                                                                         |

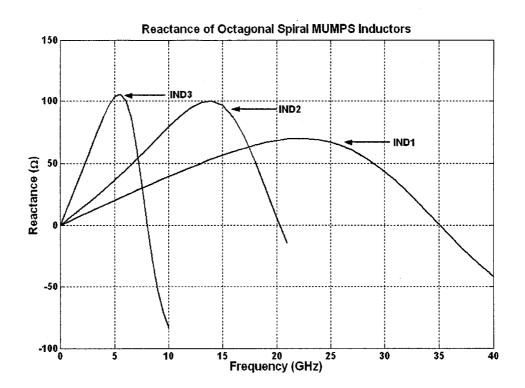

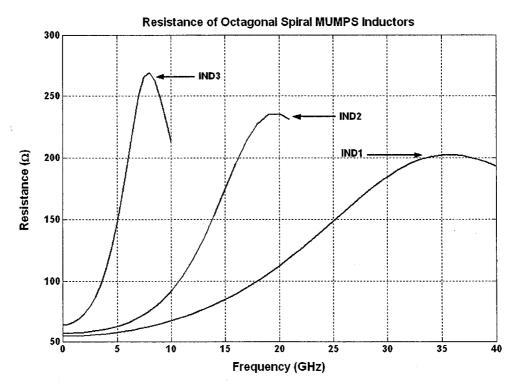

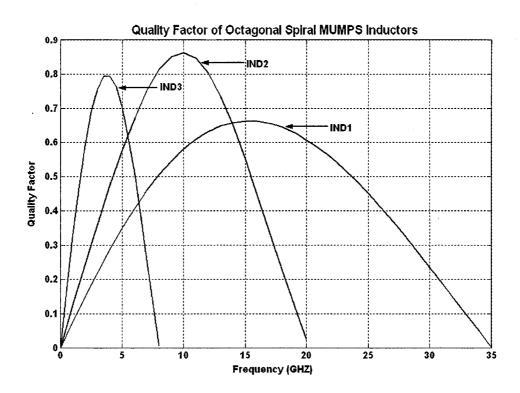

| Figure 4.22 Reactance of MUMPS Spiral Inductors (See Table 4.4 for Inductor          |

| Specifications)98                                                                    |

| Figure 4.23 Resistance of MUMPS Spiral Inductors (See Table 4.4 for Inductor         |

| Specifications)98                                                                    |

| Figure 4.24 Quality Factor of MUMPS Spiral Inductors (See Table 4.4 for Inductor     |

| Specifications)99                                                                    |

| Figure 4.25 Anisotropic Wet Etching using Etch Mask 2                                |

| Figure 4.26 Isotropic Wet Etching Using Etch Mask 2                                  |

| Figure 4.27 RIE Using Etch Mask 2                                                    |

| Figure 4.28 RIE Followed by Anisotropic Wet Etching Using Etch Mask 2 105            |

|--------------------------------------------------------------------------------------|

| Figure 4.29 Final Structure Resulting from RIE by Anisotropic Wet Etching Using Etch |

| Mask 2                                                                               |

| Figure 4.30 Isotropic Wet Etching Followed by Anisotropic Wet Etching Using Etch     |

| Mask 2                                                                               |

| Figure 4.31 Anisotropic Wet Etching Using Etch Mask 4                                |

| Figure 4.32 Anisotropic Wet Etching Using Etch Mask 6                                |

| Figure 4.33 Anisotropic Wet Etching Using Etch Mask 5                                |

| Figure 4.34 Anisotropic Wet Etching Using Etch Mask 7                                |

| Figure 4.35 Anisotropic Wet Etching Using Etch Mask 8                                |

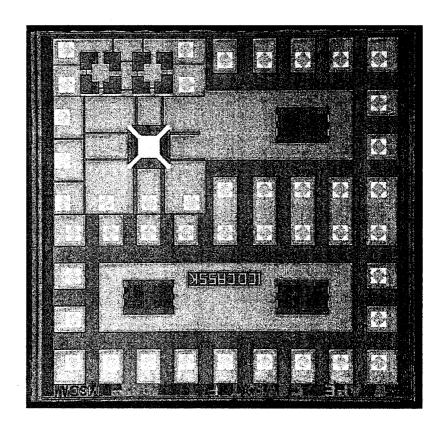

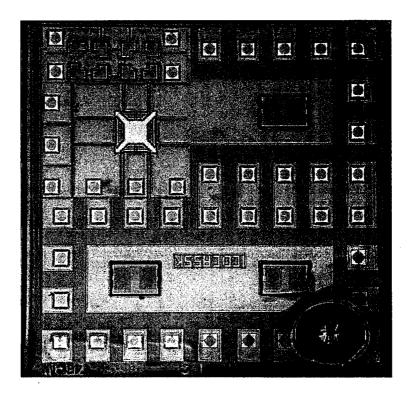

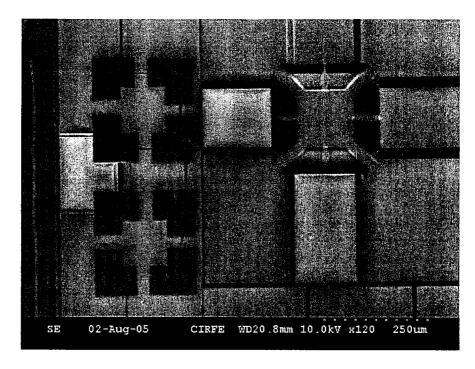

| Figure 5.1 Top View of the MUMPS Chip Showing Bonding Pads, Connections and The      |

| Switches                                                                             |

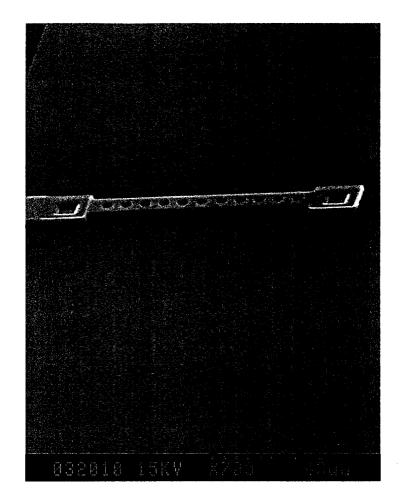

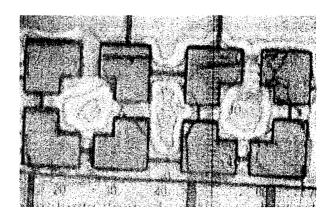

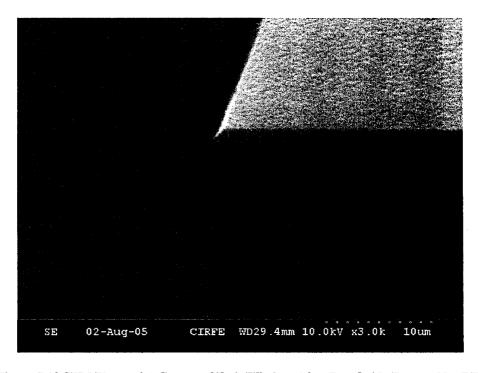

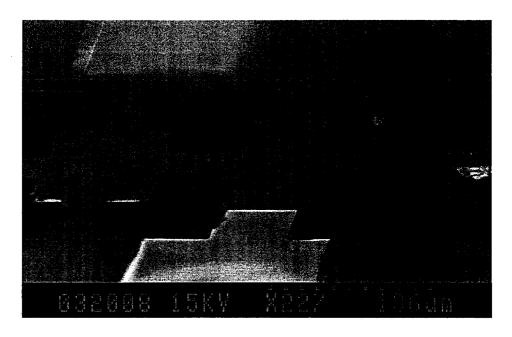

| Figure 5.2 SEM Photo of One Beam with Etch Holes                                     |

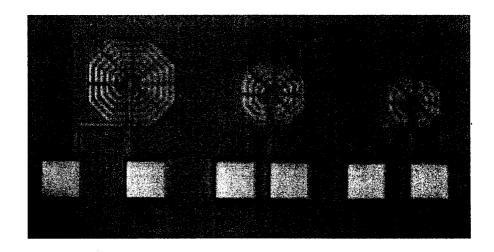

| Figure 5.3 Top View of the Three Inductors and Bonding Pads, Fabricated in           |

| PolyMUMPS Process                                                                    |

| Figure 5.4 CMOS Chip Before Post-Processing (Inductors are at the Upper Left Corner) |

|                                                                                      |

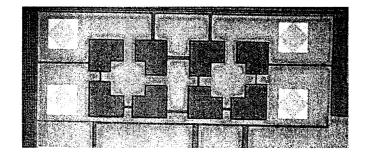

| Figure 5.5 CMOS Inductors Before Post-Processing                                     |

| Figure 5.6 CMOS Chip with Patterned Photoresist on It                                |

| Figure 5.7 CMOS Inductors after Wet Oxide Removal by Buffered HF                     |

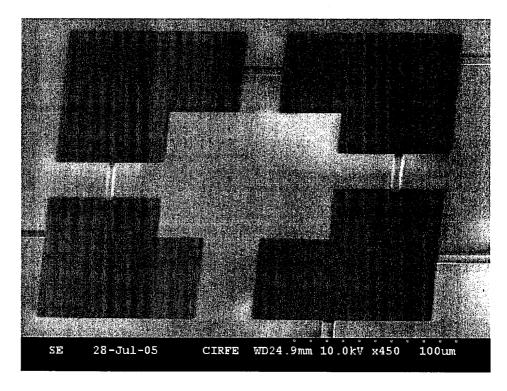

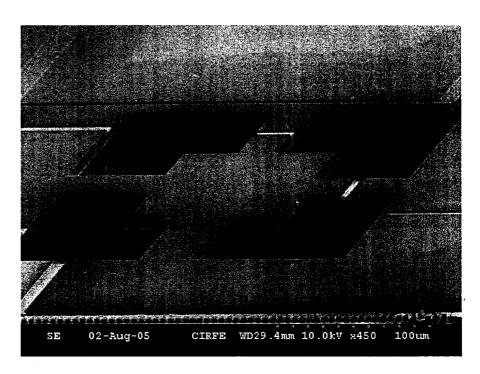

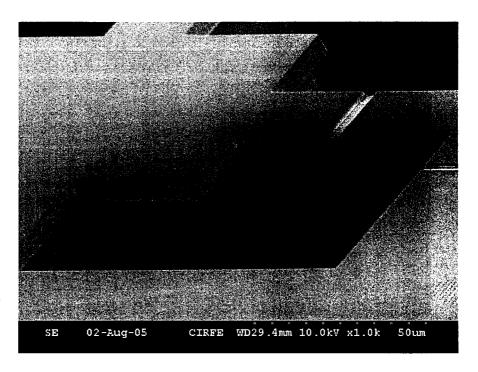

| Figure 5.8 SEM Photo of Inductors After Wet Oxide Removal by Buffered HF 119         |

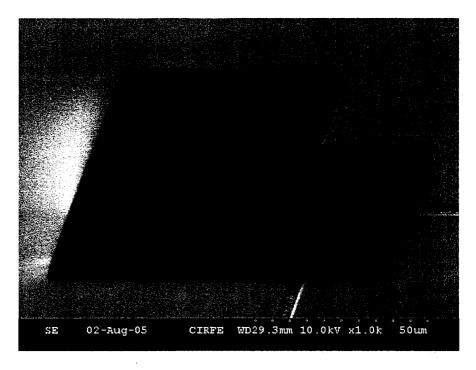

| Figure 5.9 One Corner of Etch Window After Wet Oxide Removal by Buffered HF 120      |

| Figure 5.10 SEM Photo of CMOS Inductors After Dry Oxide Removal by RIE 121           |

| Figure 5.11 SEM Photo of CMOS Inductor After Dry Oxide Removal by RIE 121            |

| Figure 5.12 SEM Photo of One Etch Window After Dry Oxide Removal by RIE 122          |

| Figure 5.13 SEM Photo of A Corner of Etch Window After Dry Oxide Removal by RIF      |

|                                                                                      |

| Figure 5.14 CMOS Chip after TMAH Etching                                             |

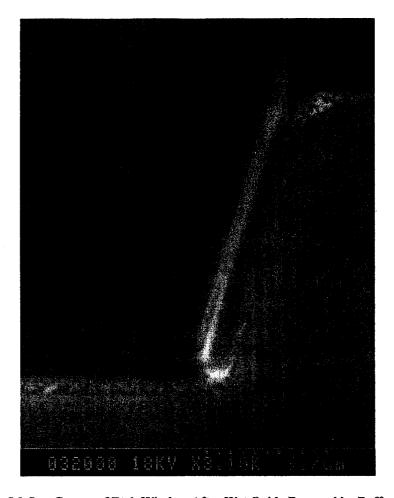

| Figure 5.15 SEM Photo of CMOS Inductors After TMAH Etching                           |

| Figure 5.16 SEM Photo of Inductor of Figure 4.14 After TMAH Etching                  |

| Figure 5.17 SEM Photo of One Etch Window of Figure 4.18                   | 125        |

|---------------------------------------------------------------------------|------------|

| Figure 6.1Test Setup                                                      | 133        |

| Figure 6.2 Probe During Measurement                                       | 133        |

| Figure 6.3 A Measurement Result: Variation of Impedance vs. Frequency on  | the Smith  |

| Chart                                                                     | 134        |

| Figure 6.4 Another Measurement Result: Variation of Impedance vs. Frequen | ncy on the |

| Smith Chart                                                               | 134        |

# List of Tables

| Table 2.1 Typical Thickness of PolyMUMPS Layers                              | 23   |

|------------------------------------------------------------------------------|------|

| Table 2.2 Typical Electrical Properties of MUMPS Layers                      | 24   |

| Table 2.3 Typical Thickness of CMOS 0.35 Layers                              | 27   |

| Table 2.4 Typical Electrical Properties of CMOS 0.35 Layers                  | 28   |

| Table 2.5 Comparison of Silicon Etchants [15]                                | 32   |

| Table 2.6 Four Possible Etching Methods                                      | 33   |

| Table 3.1 Dimensions for first set                                           | 71   |

| Table 3.2 Dimensions for second set                                          | 71   |

| Table 3.3Dimensions for third set                                            | 72   |

| Table 4.1 Modified Wheeler Model Parameters                                  | 80   |

| Table 4.2 Parameters of Current Sheet Approximation Model                    | 81   |

| Table 4.3 Data Fitting Constants                                             | 82   |

| Table 4.4 Specifications of Designed MUMPS Inductors                         | 89   |

| Table 4.5 CMOS 0.35 Inductor Specifications                                  | 91   |

| Table 4.6 Etch Masks                                                         | 100  |

| Table 4.7 Results of The Etching Simulations                                 | 114  |

| Table 6.1 Measured Pull-In Voltages of Fixed-Fixed Beams Fabricated in PolyM | UMPS |

| Technology                                                                   | 128  |

# 1. Introduction

#### 1.1 Motivation

Expansion and development of fixed, mobile, wired and wireless telecommunications networks and devices and introduction of multiple standards drives the need for more efficient components. In mobile wireless communication devices, parts that are smaller, operate in a broader/narrower frequency range (depending on the application), support multiple standards, and consume less power, lead to increased efficiency and decreased prices. MEMS (MicroElectroMechanical Systems) technology (also known as Microsystems) can address these requirements.

Many components in a radio frequency (RF) device can be replaced by their MEMS counterparts that exhibit superior performance. These components are mainly concentrated in RF front-end block that contains duplexers, impedance matching networks, filters, multiplexers, mixers, oscillators, phase shifters, amplifiers [1-4] that they themselves contain passive microwave components, transmission lines, capacitors, inductors for active and passive circuits, switches, resonators, and components.

This project is part of a bigger project on RF MEMS filters that involves RF MEMS capacitors [5-6], resonators [5], and inductors and switches which are investigated in this work.

#### 1.2 RF MEMS Inductors

Inductors are widely used in radio frequency integrated circuits (RFICs). They are used in passive tuning circuits (filters), as high impedance RF chokes, and also being used in

matching networks, oscillators and voltage-controlled oscillators (VCOs) [7-8], and amplifiers.

Planar processes that are utilized to fabricate RFICs create some problems. The trace capacitance to ground and the substrate resistivity lower both the self-resonance frequency and quality factor of the inductor. These effects can be diminished in some extent by optimizing the physical layout of the inductor.

Substrate micromachining methods can be utilized to improve the quality factor and resonance frequency of the inductor by removing the substrate beneath the inductor so the parasitic capacitance of substrate is reduced.

#### 1.3 RF MEMS Switches

Switches and switching have a key role in RF systems. For example they are used in blocks such as phased array antennas, tunable matching networks, transmit/receive switches and switching matrices. The hardware overhead can reduce by using reconfigurable blocks (for different condition/frequencies/standards). Switches determine the signal path in this type of circuits. MEMS switches, in addition to being small, have very good RF properties in terms of insertion loss, isolation, power consumption, and linearity that makes them a desirable alternative [9-10].

#### 1.4 Thesis Outline

This thesis focuses on RF MEMS switches and inductors. Different aspects of MEMS RF switches and inductors are discussed.

In chapter 2, MEMS and RF MEMS are reviewed and different fabrication methods for MEMS devices are explained.

.In chapter 3 and 4 the design and simulation of switches and inductors are presented.

MEMS switches are introduced and compared with electronic switches. A switch design in MUMPS is given and modeled in MATLAB. Switch layouts are given, too. Then integrated inductors are introduced. Different layouts, models and design equations are given. Several spiral inductors are designed in MATLAB and then some of them are selected for fabrication in CMOS and MUMPS processes. Designed inductors are simulated in ADS Momentum and their layouts are given.

In chapter 5 fabrication details of designed MEMS devices are described. Then performed silicon bulk micromachining (post-processing) steps for CMOS process are given

In chapter 5 characterization methods are introduced and test procedures are explained.

Then measurement results are discussed.

Finally in chapter 6, conclusions are highlighted and some future-works to continue this project are suggested.

In appendix 1, least-square estimation method which is used in chapter 6 to estimate the material properties from a set of measured parameters, is presented.

# 2. Background

#### **2.1 MEMS**

#### **2.1.1** What is it?

MEMS stands for "MicroElectroMechanical Systems". Some properties can be inferred directly from this name, Micro tells that they are miniature devices, electro suggests either electricity or electronics or both, mechanical introduces the presence of mechanical structures or moving parts, and System suggest some degree of complexity. But MEMS concept (that some times is also called Microsystems, Microstructures, or Micromachines) is more general and covers different miniature devices, including but not limited to biological, chemical, electrical, fluidic, magnetic, optical, and thermal applications. MEMS research involves different disciplines in science and engineering. The driving forces for the miniaturization of mechanical systems include cost, size, speed, weight, precision and reliability while providing an effective interface between the macro and micro world.

#### 2.1.2 History of MEMS

When in 1959 Richard Feynman [11] in his famous speech, "There is plenty of room at the bottom" introduced the idea of miniaturization, he proposed only a few applications that he dreamed about, and of course they weren't realizable at that time.

But now, many miniature devices in scale of microns or even less are implemented, and many of Feynman's imaginations are actualized thanks to advances in fabrication processes for MEMS. One of the first silicon pressure sensors was isotropically micromachined by Honeywell [12] in 1962. Crystal orientation etch-rate dependency led

to more precise definition of structures and increased interest. Anisotropic etching was introduced in 1976 [13]. In the 1960s the first surface michromachined structures using metal mechanical layers were presented [14]. These are a few examples of early years MEMS devices. In the last two decades of twentieth century MEMS research has boomed in the world and has lead to thousands of different devices in different application areas. Now MEMS is reaching slowly to maturity but still there aren't many MEMS devices commercially available in the market. Cost and reliability are two limiting factors. Commercialization is the new challenge that MEMS industry is facing with.

#### 2.1.3 Fabrication and Materials

Although MEMS researchers take advantage of VLSI processes, the MEMS processes are not standardized like IC fabrication processes that are mature and well established.

The conventional IC fabrication process that is based on photolithography and chemical etching is not directly suitable to realize three-dimensional MEMS structures, but after a few post-processing steps, it is possible to have MEMS devices and digital and analog circuitry on the same chip. The idea of integrated MEMS and electronics is very promising for many applications, but with some considerations.

The IC fabrication process creates a planar (2D) structure. To shape the third dimension of a 3D MEMS device, bulk micromachining and surface micromachining techniques are designed [15].

In surface micromachining, there are two types of layers; structural layers to make the structure in it and sacrificial layers that separate structural layers but will be removed during later steps or at the end of the fabrication. The process of sacrificial layer removal

is called the *release* process. There is a problem called *stiction* associated with structure release. The nature of stiction problem and the solutions are given later in this chapter.

In bulk micromachining, the substrate (usually silicon) is etched away by dry or wet methods, isotropically or anisotropically. This way the substrate under certain devices is removed to achieve some design goals. Bulk-micromachining will be explained thoroughly later on.

It is also possible to combine bulk micromachining and surface micromachining techniques.

Similar to ICs, silicon is the key material used to build MEMS structures. Also depending on the application, other semiconductor materials like GaAs [16] as well as metals, ceramics, polymers (polyimides, etc.) [17-18], and composites are used.

Another process, namely LIGA, is used to create 3D high aspect ratio structures on substrate surface [19].

# 2.2 MEMS Devices and Applications

MEMS devices in contrast to similar normal-sized devices are very tiny, occupy a small area on the chip, and consume negligible power. These unique properties make them attractive for almost every application, but especially for applications that either space (area) or power is a limiting factor such as portable devices, wireless communications, and defense systems. Handsets, base stations (cell phone industry) and satellites (cellular communications) are a few of them.

There are numerous possible applications for MEMS. They are used in automotive and aerospace industries, military, medical, telecommunications (RF-MEMS), and many other industries.

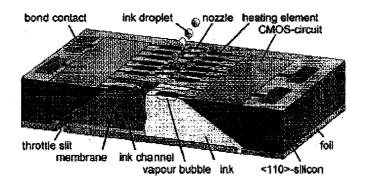

For example, MEMS devices serve as impact sensors in the accelerometers of automobile airbags [20], as micronozzles in commercial inkjet printers (Figure 2.1) [21-23], as tiny blood pressure sensors [24], for DNA amplification and identification [25], as temperature sensor [20] and gas sensors [26].

Figure 2.1 Backshooter Printhead [23]

#### 2.3 RF MEMS Devices

High frequency communication systems are benefiting noticeably from the advent of the RF-MEMS technology. MEMS technology is revolutionizing the RF industry. Electrical components such as inductors and tunable capacitors can be improved significantly compared to their integrated counterparts using MEMS technology. With the integration of such components, the performance of communication systems will be enormously improved, while the total circuit area, power consumption and cost will be reduced.

The manufacturers compete to add more functionality to wireless system equipment. A 3G/4G<sup>1</sup> "smart" phone, PDA, or base station, for example, will require the functionality to support TDMA (Time Domain Multiple Access), CDMA (Code Division Multiple Access), Bluetooth and GSM (Global System for Mobile Communications). A huge increase in component count is required to accomplish this task. Other wireless equipments are facing the same challenge. While the market demands the new functions, it also expects smaller form factors, lower costs and reduced power consumption [1-3, 10].

Discrete passive devices such as RF switches, varactors, high-Q<sup>2</sup> resonators and filters, have been identified as components that can be replaced by RF-MEMS counterparts.

RF-MEMS research can be divides into four categories:

- RF MEMS Switches, Capacitors (Varactors), and Inductors: In this category, inductors are the only devices that are not moving.

- Micromachined Transmission Lines (Microwave Components), High-Q Resonators,

Filters, and Antennas (Non-Moving Devices): These devices are fabricated on thin-dielectric membranes or take advantage of bulk micromachining.

- Thin Film Bulk Acoustic Resonators (FBARs) and Filters: In these devices, acoustic resonance in thin films is used. They demonstrate high Qs.

<sup>&</sup>lt;sup>1</sup> Third Generation/Fourth Generation mobile telephone technology

<sup>&</sup>lt;sup>2</sup> Quality Factor

• RF Micromechanical Resonators and Filters: The mechanical vibrations of small structures are used to achieve high-Q resonances.

#### 2.3.1 RF MEMS Switches

Switches are a fundamental part of many RF and microwave circuits and system functions; for instance tunable matching networks, receive/transmit switches, switching matrices, and phased array antennas/smart antennas. Since MEMS technology provides near ideal switches in terms of power consumption, insertion loss, isolation, and linearity, extensive efforts have been aimed at attaining devices exhibiting both good RF properties and low actuation voltage.

An RF switch has two parts: the actuator (mechanical) part and the electrical part (signal path). The actuation force for mechanical movement can be obtained from electrostatic, magnetic, piezoelectric, or thermal mechanism. In addition, the mechanical switch, as developed by several research groups, is a key component with huge potential in various microwave circuits. The movement of switch could be vertical or lateral. In the electrical part, switch can be placed in series or shunt configurations. There are two types of contacts, metal-to-metal contact and capacitive contact.

Considering the above divisions, 32 different types of RF switches can be built using different actuation mechanisms, movement planes, contact types, and circuit configurations.

Application areas of RF MEMS switches are switching networks, reconfigurable networks, portable wireless systems, and phased arrays in communication and radar systems. Applications include: SPNT (single-pole N-throw) switches for filter and

amplifier selection,  $N \times N$  switching matrices, SPDT (single-pole double-throw) and DTDT (double-pole double-throw) routing switches, very high isolation switches (instrumentation), programmable attenuators, phase shifters, reconfigurable matching networks, switched filter banks, and much more [9-10].

#### 2.3.2 RF MEMS (Fixed) Capacitors

Fixed capacitors are frequently employed for dc blocking and in matching networks. Generally two types of passive capacitors are used in microwave circuits, the interdigital and the metal-insulator-metal (MIM) capacitors.

Micromachining is used to reduce the quality factor and parasitic capacitance of interdigital capacitors [27].

#### 2.3.3 RF MEMS Varactors (Variable Capacitors)

With the proliferation of multimode, multi-standard wireless applications, the need for high-quality varactors capable of large tunability range, at low tuning voltage spans, is a rather pressing one. Traditionally the monolithic implementation of functions requiring tunability, such as high-performance voltage controlled oscillators (VCOs), has been prevented by the unavailability of high-quality on-chip varactors. Since the available on-chip varactors exhibit low tuning range and low Q, numerous efforts aimed at applying micromachining to overcome these shortcomings have been undertaken. Accordingly, based on the well-known parallel-plate capacitor equation ( $C = \frac{\varepsilon A}{d}$ ), efforts have aimed at varying one of the three variables: d, the interplate distance, A, the plate area or  $\varepsilon$ , the dielectric constant.

The development of MEMS varactors has not progressed at the pace of MEMS switches. Their capacitance ratio is normally 1.2-2.5, while standard solid-state varactors have a capacitance ratio of 4-6 and there is ongoing research in order to increase the capacitance ratio. Also, it is hard to build MEMS varactors with capacitance off 5-50 pF, which are needed for 30 to 600 MHz applications.

MEMS capacitors suffer from Brownian, acceleration, acoustic, and bias-noise effects

especially for low-spring-constant designs that are necessary for low actuation voltages. But, there is still a pressing need for MEMS varactors. First they have the potential of very high-Q (100-400) operation, especially at millimeter-wave frequencies. Also, they can be designed to withstand large RF voltage swings and therefore result in very high IIP3<sup>3</sup> tunable networks. MEMS varactors don't need biasing and therefore don't pass current under high-power operations [27-28].

Currently there are three different technologies for building MEMS variable capacitors. The first one is based on the parallel-plate approach (vertical design), and a variable capacitance is achieved by changing the gap between the capacitor plates [28-30]. The second approach is based on an interdigital (horizontal) design: and again, the gap is changed to achieve a variable capacitance [31-32]. The third approach consists of building a fixed capacitance bank and using MEMS switches to select the required total capacitance [33-34].

<sup>&</sup>lt;sup>3</sup> Third Intercept point

The switches and capacitors operate with almost the same principles. Switch is a variable capacitor whose capacitance changes from a minimum (open state) to a maximum (closed state).

#### 2.3.4 RF MEMS Inductors

Inductors play an ever-increasing role in RFICs. In addition to being frequently employed in passive tuning circuits or as high impedance chokes, they are used in matching networks, oscillators and voltage-controlled oscillators (VCOs) [7-8], and amplifiers [35]. When fabricated in a planar process, the trace capacitance to ground and the substrate conductivity tend to lower the inductor self-resonance frequency and its quality factor. While optimization of the spiral geometry is essential to tailor the frequency of maximum Q, this only addresses minimization of the trace ohmic-losses and substrate capacitance. Many attempts have been pursued to use conventional processing techniques to diminish the substrate losses created by Eddy currents induced by the magnetic field of the spiral. Various approaches to overcome the limitations of silicon substrate by utilizing bulk micromachining, surface micromachining, or a combination of surface micromachining and self-assembly are addressed.

RF MEMS Inductors, capacitors and varactors fall into the general category of micromachining-enhanced lumped elements. These structures may be fabricated small enough comparing to microwave wavelengths, so that is a good approximation to take their voltages and currents as if they are lumped at a point (i.e. position independent). The lumped-element circuits are small in size, low-cost and have wideband characteristics. These features are particularly important. These elements are usually utilized in high-power oscillators, power amplifiers, and broadband circuit applications (such as

impedance matching). The performance of these elements is limited by the appearance of parasitic effects, which changes the properties of the pure elements into those of a RLC circuit (including the resonance). In the case of an inductor, it will exhibit capacitive behavior above the self-resonance frequency. Since the main source of the parasitic effects is the dielectric substrate supporting the elements, it is natural to aim at improving the situation by eliminating the substrate.

#### 2.3.5 Microwave Components

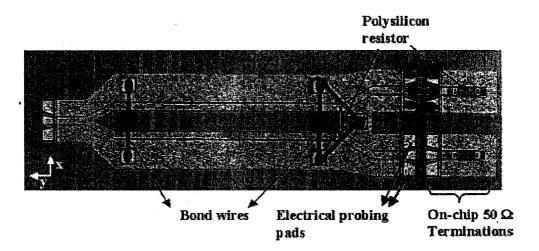

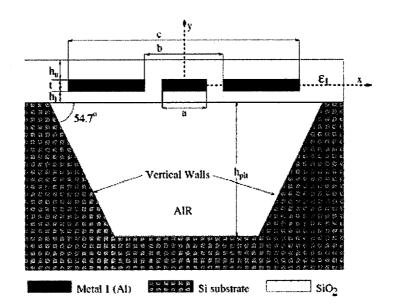

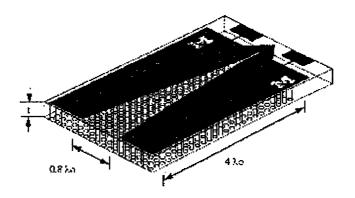

Various microwave devices can take advantage of MEMS technology. Examples are CMOS micromachined power divider [36] (Figure 2.2), micromachined CMOS coplanar waveguide [37] (Figure 2.3), tapered slot antenna on micromachined photonic bandgap dielectrics [38] (Figure 2.4), and aperture-coupled micromachined microstrip antenna [39].

Figure 2.2 CMOS Micromachined Power Divider [36]

Figure 2.3 Micromachined CMOS Coplanar Waveguide [37]

Figure 2.4 Tapered Slot Antenna on Micromachined Photonic Bandgap Dielectrics [38]

# 2.4 Fabrication Technologies

MEMS devices are fabricated with a variety of methods that is commonly referred to as microfabrication methods. Microfabrication, as practiced in microelectronics and MEMS, is based on planar technologies. Electronic and MEMS devices are fabricated on substrates that are initially flat. Microelectronics industry has invested enormous amounts

of money in the development of wafer-based process technologies in a long time. It is an advantage for MEMS industry to use these mature technologies. Microfabrication methods can be grouped in two main parts, wafer-level processing and pattern transfer.

#### 2.4.1 Wafer-level processes

Wafer-level processes include all the chemical, mechanical, thermal and electrical processes that put new layers on the wafer or put new materials in the wafer or any other layer on the wafer.

Wafers are available in different material and diameters. Single crystal silicon, single crystal quartz, glass, fused (amorphous) quartz, and gallium arsenide are some of them. Round wafers are sold in different diameters, types (n-type or p-type), doping levels and crystal orientations (in the case of single crystal materials).

Wafer-level processes include following processes:

- Wafer preparation and cleaning: This step involves using a standard cleaning procedure such as RCA cleans [40] to remove organic residues and ion contaminations in wafer.

- One of the most attractive properties of silicon is that a high quality oxide can be grown on its surface. If pure oxygen is used as the oxidant, it is called dry oxidation. Oxidation in presence of oxygen and water vapor is called wet oxidation. Dry oxidation creates higher quality oxides than wet oxidation, but it is a slow process. When quality of oxide is not an issue, wet oxidation is used. [41].

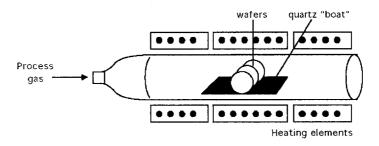

Oxidation is performed in a special furnace as it is shown in Figure 2.5.

Figure 2.5 Furnace for Silicon Oxidation

- Doping: It is the process which small quantities of impurities are added to semiconductor crystals, thereby modifying the electrical properties of it. Undoped silicon behaves like an insulator while highly doped silicon acts like metals. The conductivity of silicon can be changed in a broad range from very low to very high, all by changing the doping. Impurities are placed in two steps: deposition and drive-in. Dopant atoms are delivered to a region near the wafer surface in drive-in step by ion implantation or by applying it as a gel. Then they are redistributed by diffusion when heated in the a furnace similar to the furnace that is used for oxidation [41-42].

- Thin-Film Deposition: Many microfabrication steps involve deposition and subsequent patterning of a thin film. Depending on the material, thin-films are deposited with a variety of methods such as physical vapor deposition (PVD), chemical vapor deposition (CVD), electrodeposition, and spin casting [19, 41-42].

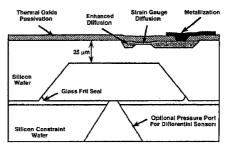

- Wafer bonding (flip-chip technology) is a method for joining two wafers to create a stacked wafer layer. This method is used both in MEMS fabrication and packaging (for an example see Figure 2.6) [1, 43-45].

Figure 2.6 Pressure Sensor Using Wafer Bonding for Packaging [44].

#### 2.4.2 Pattern Transfer Methods

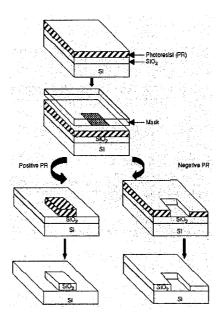

ICs and MEMS devices are formed by defining patterns in the various layers created by wafer-level process steps. Pattern transfer consists of two parts: a photo-process, whereby the desire pattern is photographically transferred from an optical plate (mask) to a photosensitive film coating the wafer, and a chemical or physical process of either removing or adding materials to create the pattern. The photo-process is called optical photolithography and the material removal process is called etching.

Optical photolithography: It is very similar to the photographic process of producing a print from a negative. First the wafer surface is coated by photoresist material (an optically-sensitive polymer) by spin casting. Following spinning, the resist is prebaked at low temperature to remove solvent. A photomask coating the patterns to be transferred is brought into close proximity of the coated wafer. Ultraviolet light is directed through the mask onto the wafer, exposing unprotected portions of the resist, which change their chemical properties due to light exposure. What happens after exposure depends on the chemical specification of the photoresist. Negative photoresist functions like the photographic printing process. Ultraviolet light exposed regions of the photoresist become insoluble in the developer, while the protected regions remain soluble and removed after immersion in the developer. The result is a

transfer of pattern into the photoresist so that the opaque regions of the mask become regions cleared of photoreist. The resist must be hardened by baking it to make it chemically inert. After postbake, the underlying layer may be etched through photoresist windows. Positive photoreist works oppositely to negative photoresist. UV exposed regions become soluble in the developer. After development, the protected regions of resist remain on the wafer [1, 41-42].

Before the photolithography process, the photomask should be designed and made. The mask is designed according to the pattern we want to be transferred. Limitations in the resolution of photolithography and also developers, are expressed as a set of design rules that should be respected to achieve acceptable results.

#### Figure 2.7 shows a photolithography sequence.

- Etching: Process of removing the material is called etching. Etching can be done in wet or dry environment. Also it can be isotropic or anisotropic.

- Wet Etching: In this method, patterned substrates are immersed in a liquid chemical that attacks exposed region of the substrate and leaves the protected regions alone.

- Dry Etching: Chemically reactive vapors and the reactive species in glow-discharge plasma are highly effective etchants.

- Etch Directionality: It is a measure of the relative etch-rates in different directions, usually vertical versus lateral. Isotropic etching occurs when etch rates are the same in all directions. In anisotropic etching, less lateral etching occurs. When etching a single crystal, certain etchants exhibit orientation-dependent etch-rates [41, 46-47].

Figure 2.7 A Photolithography and Etching Sequence [1]

## 2.4.3 The Complete Process

A typical process consists of a sequence of wafer-level and pattern transfer processes. Even for a simple process, many steps of wafer-level and pattern transfer processes are required. The best examples of process technologies are different CMOS processes that are used mainly for analog and digital IC fabrication.

#### 2.5 Micromachining Techniques

Micromachining is a very powerful approach for fabrications of actuators, sensors and microstructures. There are a few true three-dimensional processes capable of yielding arbitrary curved surfaces. Since microfabrication tools are almost applied with successive photolithographic patterning, any 3D aspects of micromachined devices are due to patterning of the 2D layers, interaction of stacked and patterned 2 layers, selective etching of the layers or the substrate, or the use of bending or hinged structures.

Micromachining is performed in two ways: bulk and surface micromachining [15, 19, 41, 48-49].

### 2.5.1 Surface Micromachining Technique

Surface micromachining [50-51] includes processes that add material above the surface of the substrate. Many of them are more common in typical integrated circuit fabrication than bulk etching. Surface micromachining techniques include:

- Non-Metallic Thin-films: Deposition of thin-films of silicon oxide, silicon nitride,

polysilicon, organic materials, etc and etching them after patterning

- Metallic Films: Deposition of gold, copper, aluminum, nickel, chrome, etc and etching them after patterning

- Sacrificial Process: Several interesting processes have been demonstrated that rely on sacrificial materials that are used as forms or spacers to make desired shapes and are later removed. As described by Howe [52], CVD phosphosilicate glass (PSG) etches much faster in HF<sup>4</sup> than thermally grown or undoped oxide, making it an attractive sacrificial layer for undercutting polysilicon structures. Fan, et al. [53] used such a process to realize moving mechanical structures. Oxidized porous silicon etches even faster, making it another very useful sacrificial layer material [54]. Aluminum, photoresist, and a number of other materials common in microfabrication labs can be used as sacrificial or structural layers [1]. The Multi User MEMS Processes (or MUMPS) provided by MEMSCAP company, are surface micromachining processes based on an oxide sacrificial layer that is removed at the end of the process. Three processes offered in MUMPS are PolyMUMPS [55], Metal MUMPS [56] and

<sup>&</sup>lt;sup>4</sup> Hydrofluoric Acid

SOIMUMPS [57]. The PolyMUMPS process will be described in detail later in this chapter.

#### 2.5.2 Bulk Micromachining Technique

Many etching methods are available for bulk processing of silicon. Wet and dry etchants are selected on the basis of a large number of characteristics, including selectivity to etch masks, exposed metallization and other materials; availability of etch-stop methods, etch rate, degree of surface roughness created, safety, disposal difficulty, circuit compability, cost, etc. Very often, the etchants are used for post-processing of prefabricated structures that may contain CMOS circuitry and aluminum metallization which places significant constraints on the choice of etchants [58-62].

#### 2.5.3 Other Methods

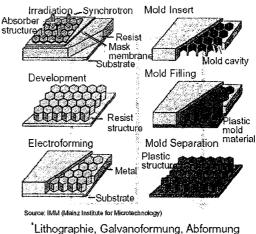

W. Ehrfeld, et al. at Karlsruhe Germany [63] developed a process called "Lithographie, Galvanoformung, Abformung" (acronymed as LIGA), for lithography, electroplating, and molding that can yield extremely high-aspect-ratio metallic structures thanks to the use of extremely well-collimated synchrotron radiation (X-rays). Steps of LIGA process are shown in Figure 2.8.

#### LIGA', Deep UV

Lithographie, Galvanotormung, Abtormung

Figure 2.8 LIGA Process Steps

Polyimides that are used in electronics industry [64-65] for different applications can also be used to fabricate MEMS devices [17-18, 66-67].

Flip-chip and Wafer bonding methods are also used to fabricate microstructures [43].

## 2.6 PolyMUMPS Surface Micromachining Process

#### 2.6.1 Process Definition

PolyMUMPS [55] technology provided by MEMSCAP company is a simple 3 poly, one metal process that gives the designers the opportunity to fabricate their MEMS designs in an affordable way compared to IC fabs. It is a surface micro machining process based on an oxide sacrificial layer that is removed at the end of the process. MUMPS foundry The layers in the process are shown in Figure 2.9. The layer names and thicknesses are given in Table 2.1 and their electrical properties are given in Table 2.2.

Figure 2.9 PolyMUMPS Layers

| Layer | Name                  | Material        | Thickness (µm) |  |

|-------|-----------------------|-----------------|----------------|--|

| 0     | Si                    | Silicon         |                |  |

| 1     | Nitride               | Silicon Nitride | 0.6            |  |

| 2     | Poly0                 | Polysilicon     | 0.5            |  |

| 3     | 1 <sup>st</sup> Oxide | Silicon Dioxide | 2.0            |  |

| 4     | Poly1                 | Polysilicon     | 2.0            |  |

| 5     | 2 <sup>nd</sup> Oxide | Silicon Dioxide | 0.75           |  |

| 6     | Poly2                 | Polysilicon     | 1.5            |  |

| 7     | Metal                 | Gold            | 0.5            |  |

Table 2.1 Typical Thickness of PolyMUMPS Layers

| Layer Name            | Relative Permitivity | Sheet Resistance |  |

|-----------------------|----------------------|------------------|--|

|                       | $(\epsilon_{\rm r})$ | $(\Omega/)$      |  |

| Si                    | 11.9                 | 22.23            |  |

| Nitride               | 7.5                  | N/A              |  |

| Poly0                 | 11.9                 | 15               |  |

| 1 <sup>st</sup> Oxide | 3.9                  | N/A              |  |

| Poly1                 | 11.9                 | 10               |  |

| 2 <sup>nd</sup> Oxide | 3.9                  | N/A              |  |

| Poly2                 | 3.7                  | 20               |  |

| Metal                 | 1                    | 0.06             |  |

Table 2.2 Typical Electrical Properties of MUMPS Layers

The fabrication process imposes some limitations in design to be fabricated. These limitations are presented as Design Rules. Design rules limit the maximum or minimum dimensions in each layers of the design and also specify the maximum or minimum distance or overlap of patterns on different layers [55].

All designs are to be checked against design rules before submission for fabrication. Normally design rule check (DRC) is performed by the layout design software and the DRC violations are shown graphically and are listed in a table. All the violation should be checked and corrected, unless they are intentional and acceptable by the manufacturer.

CMC Microsystems [68] provides subsidized access to PolyMUMPS to Canadian Universities.

# 2.6.2 Releasing the PolyMUMPS Devices

The final step in PolyMUMPS process is removing the sacrificial oxide layer or releasing the devices. It can be done by the fabricating company or by the user. According to PolyMUMPS handbook [55], to release the chips, they should be immersed in a bath of 49% HF at room temperature 1.5-2 minutes. Then chip should be immersed in DI<sup>5</sup> water for several minutes followed by immersion in alcohol or acetone for several minutes to prevent stiction problem. After all of immersion steps, chips are supposed to be dried in an oven at 110°C. All of the steps after the HF release are to prevent the stiction problem. Stiction happens due to attractive capillary (surface tension) forces of drying liquid (generally water). Those forces keep released structures stuck together and prevent them from moving. Immersion in warm alcohol or acetone that evaporates easily in room temperature is one of the solutions. Drying in the oven is another solution. Critical point drying by CO<sub>2</sub> is another solution suggested by MEMSCAP [55].

# 2.7 CMOS Process Technology

There are various CMOS technologies available with different layer combinations, feature sizes and electrical and physical properties. All of these processes are designed and optimized for fabrication of analog and digital integrated circuits. But they are also used for fabrication of MEMS devices although the process is not intended for that.

CMC Microsystems provides subsidized access to several CMOS processes to Canadian Universities. Between them the TSMC (Taiwan Semiconductor Manufacturing

<sup>&</sup>lt;sup>5</sup> De-Ionized

Company) CMOS 0.35 is an appropriate process for MEMS fabrication regarding the minimum feature size, area and cost.

# 2.7.1 TSMC CMOS 0.35 Specifications

The layers in the CMOS 0.35 process are shown in Figure 2.10.

Figure 2.10 CMOS 0.35 Layers

The layer names and thicknesses are given in Table 2.3 and their electrical properties are given in Table 2.4.

| Layer | Name         | Material        | Thickness(µm) |

|-------|--------------|-----------------|---------------|

| 0     | Si           | Silicon         | ~750          |

| 1     | Thin/Thick   | Silicon Dioxide | 0.18/0.29     |

|       | Oxide        |                 |               |

| 2     | Poly1        | Polysilicon     | 0.275         |

| 3     | Interpoly    | Silicon Dioxide | 0.037         |

| 4     | Poly1        | Polysilicon     | 0.18          |

| 5     | Inter Poly1- | Silicon Dioxide | 0.605         |

|       | Metal1       |                 |               |

| 6     | Metal1       | Aluminum        | 0.665         |

| 7     | Via12        | Silicon Dioxide | 1             |

| 8     | Metal2       | Aluminum        | 0.64          |

| 9     | Via23        | Silicon Dioxide | 1             |

| 10    | Metal3       | ^Aluminum       | 0.64          |

| 11    | Via134       | Silicon Dioxide | 1             |

| 12    | Metal4       | Aluminum        | 0.925         |

| 13    | Passivation  | Silicon Dioxide | 3             |

|       |              | Silicon Nitride |               |

|       |              | Glass           |               |

Table 2.3 Typical Thickness of CMOS 0.35 Layers

| Layer Name       | Relative Permittivity (ε <sub>r</sub> ) | Sheet Resistance (Ω/) |  |  |

|------------------|-----------------------------------------|-----------------------|--|--|

| Si               | 11.9                                    | 10                    |  |  |

| Thin/Thick Oxide | 3.9                                     | N/A                   |  |  |

| Poly1            | 11.9                                    | 8                     |  |  |

| Interpoly        | 3.9                                     | N/A                   |  |  |

| Poly2            | 11.9                                    | 50                    |  |  |

| Inter Poly1-     | 3.9                                     | N/A                   |  |  |

| Metal1           |                                         |                       |  |  |

| Metal1           | . 1                                     | 0.083                 |  |  |

| Via12            | 3.9                                     | N/A                   |  |  |

| Metal2           | 1                                       | 0.08                  |  |  |

| Via23            | 3.9                                     | N/A                   |  |  |

| Metal3           | 1                                       | 0.08                  |  |  |

| Via134           | 3.9                                     | N/A                   |  |  |

| Metal4           | 1                                       | 0.051                 |  |  |

| Passivation      | 3.9                                     | N/A                   |  |  |

**Table 2.4 Typical Electrical Properties of CMOS 0.35 Layers**

Like the PolyMUMPS process, CMOS 0.35 also has some design rules [69] and they are much more complicated than MUMPS. These design rules are provided to guarantee the fabrication of ICs with the minimum nominal feature size. But in case of MEMS devices, intentionally violating many of them is not a problem. But some of these design rules are

critical for the quality of the fabricated chips. Densities of metal1, metal2, metal3, metal4 and poly1 and poly 2 shouldn't be less than minimums specified in design rules to make sure that in fabricated chips stress of layers are balanced

Design should be critical DRC violation free before submission for fabrication.

At the beginning of the use of CMOS for MEMS fabrication, it was allowed to make big vias to open windows down to silicon substrate for the bulk micromachining process. But some problems showed up and quality of ICs degraded. So it is not anymore possible to have big vias in the layouts and those windows should be opened in post-processing steps that will be presented later in chapter 3.

# 2.7.2 Silicon Bulk Micromachining Techniques for CMOS Process

Invention of post-processing techniques made it possible for MEMS designers to take advantage of regular IC fabrication processes to make microstrucures to avoid costly custom designed processes. But IC fabrication processes are not designed to make microstrucures. They are designed, developed, and optimized for IC fabrication and there isn't any consideration for MEMS fabrication in them. Therefore it is up to the designers to adapt their design in such a way that it can be fabricated in a CMOS process and then can be released by micromachining post-fabrication steps.

Specialized processes may not automatically allow for on-chip integration of electronics and require the development and implementation of a circuit process along microstructures with the MEMS process. Backside etching also involves additional masks and alignment and therefore adds more complexity. Concurrently, there is also strong interest in developing microtransducers that are compatible with a commercial CMOS process.

Compatibility with a commercial CMOS process allows for monolithic integration of analog and digital circuits, which provide signal conditioning, interface control, and wireless remote communication. After receiving the chips, the microsensors or microactuators are then released by an additional frontside postprocessing etch.

Silicon micromachining is the key technology to fabricate microtransducers and actuators.

Depending on the design, suspended microtransducers can be realized using either an isotropic or anisotropic etch. While structures with sizes ranging from 40–200 microns can readily be realized with either an isotropic or anisotropic post etching, larger or longer microstructures, such as microwave coplanar waveguides and passive components, cannot be achieved with either an isotropic or anisotropic etch alone. Large structures require unacceptably long anisotropic etch times, which, in turn, cause other negative effects. Therefore, etching is the limiting factor in realizing large suspended microstructures.

Microstructures are made of thin films, either homogeneous or multilayer. The multilayer thin-film structures made from the prior post-CMOS micromachining process usually have large residual stress gradients, which cause curling. This limits the maximum layout size of microstructures, which is critical for providing large proof mass in inertial sensors. Moreover, release holes and unwanted curvature of microstructures degrade their application in the optical domain. [70-71].

To realize microtransducers at low cost, there are several requirements on the postprocessing etching.

- be low temperature to not change the doping profiles (junction depths) of MOS transistors.

- 2. be compatible with materials used in the commercial CMOS processes, namely, silicon dioxide, silicon nitride, and exposed aluminum.

- 3. not contaminate the gate dielectrics with impurities such as mobile alkali ions, which shift the flatband voltage and affect the circuits.

- 4. create structure with long term reliability,

- 5. not impose unacceptable stress levels on chip,

- 6. be easy to handle and safe

The most common etches used for micromachining are those for silicon, and are summarized in Table 2.5 and then are explained in detail.

|                 | HNA      | Alkali-  | EDP       | ТМАН     | XeF <sub>2</sub> | SF <sub>6</sub> | DRIE    |

|-----------------|----------|----------|-----------|----------|------------------|-----------------|---------|

|                 |          | ОН       |           |          |                  | Plasma          |         |

| Etch type       | wet      | wet      | wet       | wet      | dry              | dry             | dry     |

| Anisotropic     | no       | yes      | yes       | yes      | no               | varies          | yes     |

| Availability    | common   | common   | moderate  | moderate | limited          | common          | limited |

| Etch rate       | 1 to 3   | 1 to 2   | 1 to 30   | ≈1       | 1 to 3           | ≈1              | >1      |

| (µm/min)        |          |          |           |          |                  |                 |         |

| Roughness       | low      | low      | low       | variable | high             | variable        | low     |

| Nitride Etch    | low      | low      | low       | 1 to 10  | ?                | low             | low     |

|                 |          |          |           | nm/min   |                  |                 |         |

| Oxide Etch      | 10 to 30 | 1 to 10  | 1 to 80   | ≈1       | low              | low             | low     |

|                 | nm/min   | nm/min   | nm/min    | nm/min   |                  |                 |         |

| Al Selective    | no       | no       | no        | yes      | yes              | yes             | yes     |

| Au Selective    | likely   | yes      | yes       | yes      | yes              | yes             | yes     |

| P+ etch stop    | no       | yes      | yes       | yes      | no               | no              | no      |

| Electrochemical | ?        | yes      | yes       | yes      | no               | no              | no      |

| Stop            |          |          |           |          |                  |                 |         |

| CMOS            | no       | no       | yes       | yes      | yes              | yes             | yes     |

| Compatible      |          |          |           |          |                  |                 |         |

| Cost            | low      | low      | moderate  | moderate | moderate         | high            | high    |

| Disposal        | low      | easy     | difficult | moderate | N/A              | N/A             | N/A     |

| Safety          | moderate | moderate | low       | high     | moderate         | high            | high    |

Table 2.5 Comparison of Silicon Etchants [15]

Where HNA is a mixture of Hydrofluoric (HF), Nitric (HNO<sub>3</sub>), and Acetic (CH<sub>3</sub>COOH) acids, Alkali-OH such as KOH, EDP is Ethylene-Diamine Pyrocatecol, TMAH is Tetra Methyl Ammonium Hydroxide, and DRIE stands for .Deep Reactive Ion Etching.

Silicon etching can be performed in wet or dry methods. Etching could be isotropic (same etch rate in vertical and lateral directions) or anisotropic (with vertical or angled sidewalls after etching). Depending on the device conditions, wet or dry etching, isotropic or anisotropic may be desirable. We will consider all four possible cases given in Table 2.6.

| Etching Method | Wet or Dry | Isotropic or | Example(s)                         |  |

|----------------|------------|--------------|------------------------------------|--|

|                |            | Anisotropic  | -                                  |  |

| 1              | Wet        | Isotropic    | HNA                                |  |

| 2              | Wet        | Anisotropic  | KOH, EDP, TMAH                     |  |

| 3              | Dry        | Isotropic    | XeF <sub>2</sub> , SF <sub>6</sub> |  |

| 4              | Dry        | Anisotropic  | RIE, DRIE, SF <sub>6</sub>         |  |

**Table 2.6 Four Possible Etching Methods**

# 2.8 Isotropic Wet Etching of Silicon

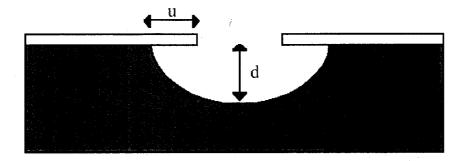

A typical isotropic silicon etchant is a combination of hydrofluoric acid (HF), nitric acid (HNO<sub>3</sub>) and acetic acid (CH<sub>3</sub>COOH), also known as HNA. A cross section of a cavity etched with an isotropic etchant is illustrated in Figure 2.11. The undercut ratio is defined as u/d, which is close to unity. The chemical reaction for silicon etching in HNA involves an oxidation step, followed by a dissolution step. The relative concentration of the three ingredients determines which step limits the overall etch rate and what type of etching profile results [72]. Due to the lateral of undercutting and resulting lack of dimensional control, isotropic etchants are not often used in micromachining [73].

Figure 2.11 Cross Section of an Isotropic Silicon Etch.

# 2.9 Anisotropic Wet Etching of Silicon

In an anisotropic, or orientation dependent silicon etch, the etch rate varies with the crystallographic direction of the semiconductor crystal. Slower etching crystal planes will appear over time as faster etching planes are consumed. Anisotropic silicon etchants include ammonium, sodium, cesium, and potassium hydroxides (NH<sub>4</sub>OH, NaOH, CeOH, KOH), hydrazine (NH<sub>2</sub>NH<sub>2</sub>), ethylenediamine (NH<sub>2</sub>(CH<sub>2</sub>)<sub>2</sub>NH<sub>2</sub>), and tetramethyl ammonium hydroxides (TMAH). Alkaline anisotropic etchants are used at elevated temperatures (60°C-100 °C).

Alkali metal hydroxides such as potassium hydroxide (KOH) have high silicon etch rate and anisotropy. Unfortunately, KOH is not post-CMOS compatible because it attacks aluminum and SiO<sub>2</sub> and contaminates the gate oxides with mobile alkali metal ions.

The quaternary ammonium hydroxides fulfill the requirements of CMOS compatibility. In this group, tetramethylammonium hydroxide (TMAH) is the preferred etchant because it has fairly high silicon etch rate.

Another CMOS etchant, which might be a potential candidate for silicon micromachining, is ammonium hydroxide doped with dissolved silicate and hydrogen

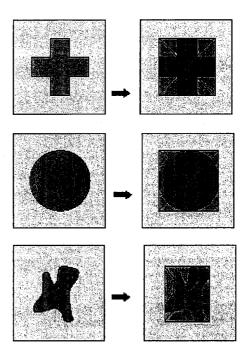

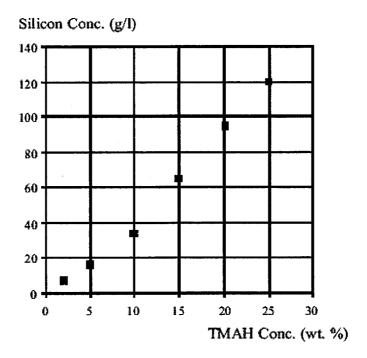

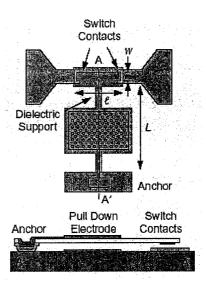

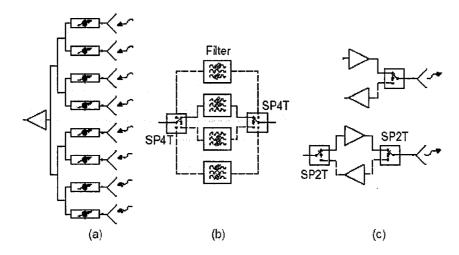

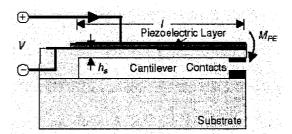

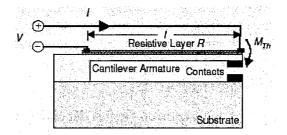

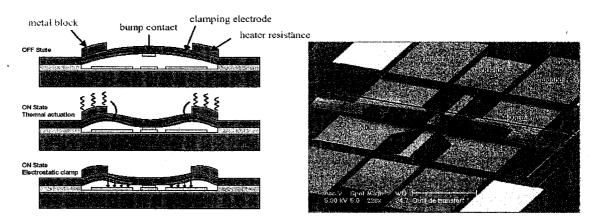

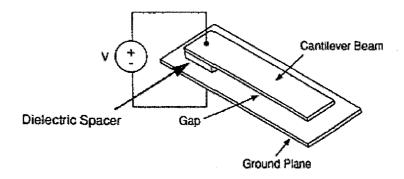

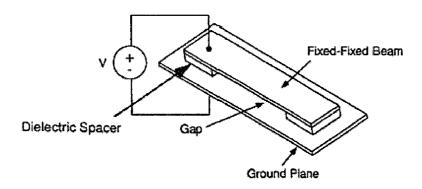

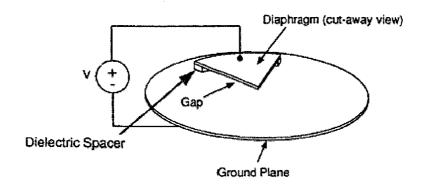

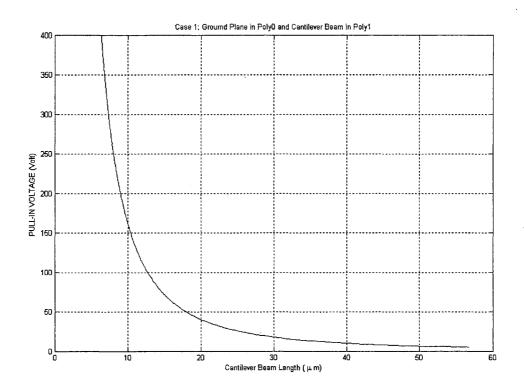

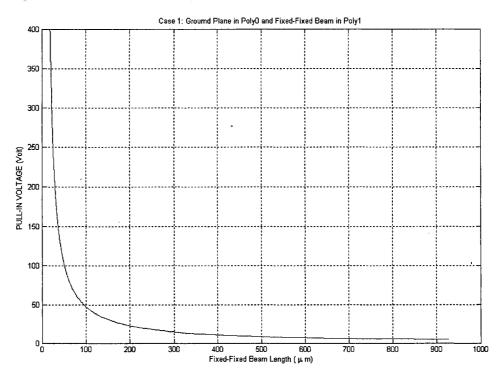

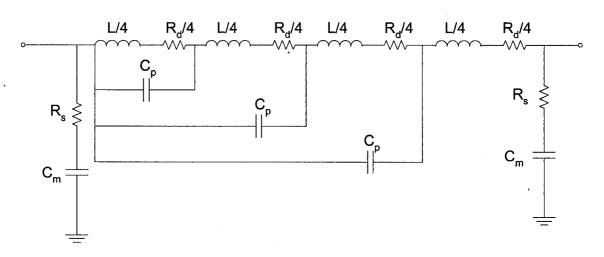

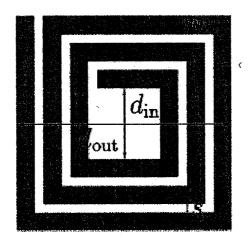

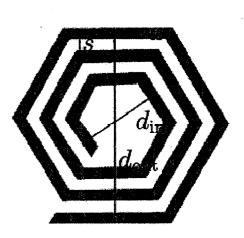

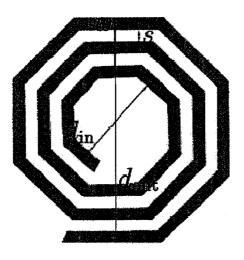

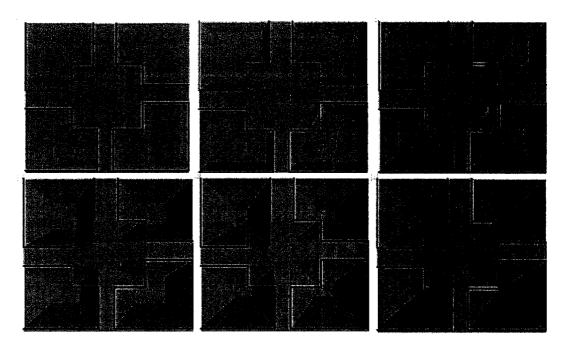

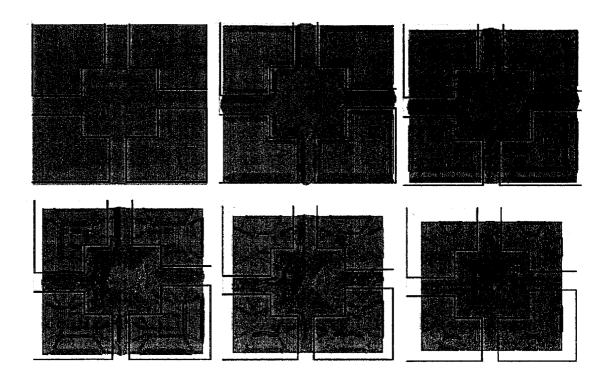

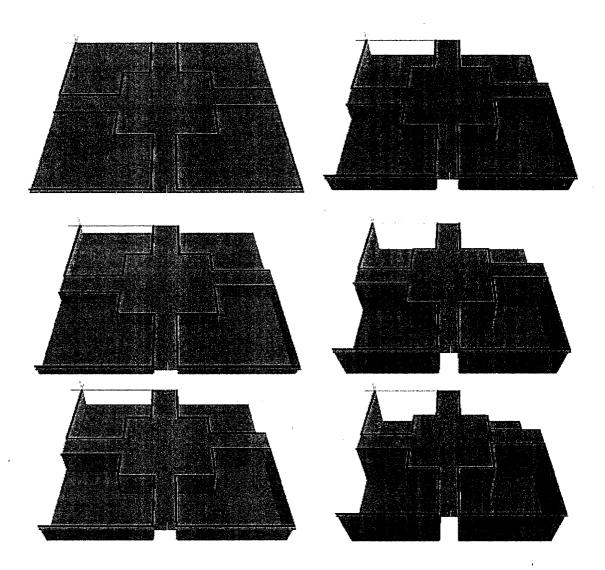

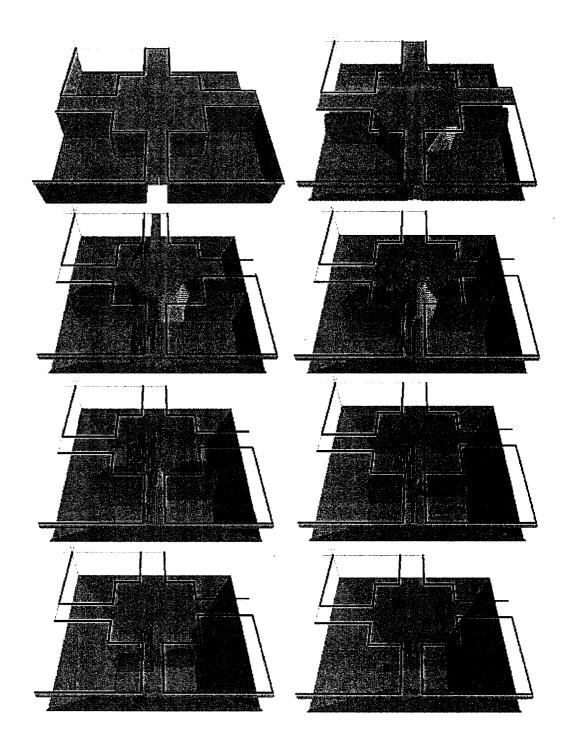

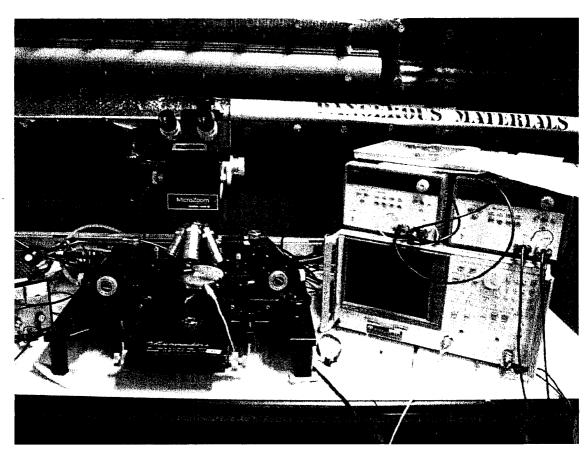

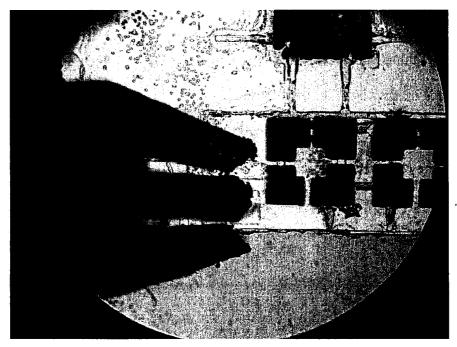

peroxide. Aqueous ammonium hydroxide was not considered here because it has very low silicon etch rate, poor reproducibility, and problems with hillock formation. The parameter window for ammonium hydroxide to work properly is very small; hence, a high-accuracy real-time monitoring of the loss of ammonia, OH ion, hydrogen peroxide, and contaminants appeared to be needed. Only small chips have been etched successfully with this etchant in this work; larger chips and chips that were packaged did not even start to etch.