### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

| ` |  |  |

|---|--|--|

|   |  |  |

# REASONING SYSTEM FOR REAL TIME REACTIVE SYSTEMS

GHAYATH HAIDAR

A THESIS

IN

THE DEPARTMENT

OI

COMPUTER SCIENCE

Presented in Partial Fulfillment of the Requirements

For the Degree of Master of Computer Science

Concordia University

Montréal, Québec, Canada

DECEMBER 1999 © GHAYATH HAIDAR, 2000

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-47844-0

## **Abstract**

## Reasoning system for real time reactive systems

#### Ghayath Haidar

Real time reactive systems are complex systems that react with their environment through stimulus response behaviour. TROMLAB development environment is a formal system being developed at Concordia University. It is the basis of the real time reactive system that will be described in this thesis.

One of the main uses of the simulation tool is debugging. The *Reasoning System* is a very good complement of the simulation tool.

The scope of this thesis is the study of a *Reasoning System* that can be used along with the simulation tool to help debug the design and verify system properties during the development phase in **TROMLAB** environment.

To my wife and my children.

## Acknowledgments

I would like to thank my wife who supported me during these last three years without her help this would have been impossible. I would also like to thank my children and hope to compensate them for all the time we did not spend together. I would like to thank my professor **Dr. V.S. Alagar**. He was very helpful and always available, without him this thesis would not be possible. He guided me and helped me a lot. I will never forget all the exciting debates we had during this work. I would also like to thank D.Muthiayen for his big contribution in the discussions we had. I would also like to thank V. Srinivasan for all the help he offered, and all the "white nights" we spent together during this work.

I would also like to thank my parents:

<sup>&</sup>quot;slamat"

# Contents

| L                      | ist of | Figur           | es                                                     | ix |  |  |

|------------------------|--------|-----------------|--------------------------------------------------------|----|--|--|

| Li                     | ist of | Table           | s                                                      | xi |  |  |

| 1                      | Intr   | roduction       |                                                        |    |  |  |

|                        | 1.1    | Real '          | Time Reactive Systems                                  | 1  |  |  |

|                        | 1.2    | Scope           | of the Thesis                                          | 3  |  |  |

| 2                      | TRO    | OMLAE           | B Environment - a brief review of initial design       | 4  |  |  |

|                        | 2.1    | TROM            | MLAB Formalism                                         | 5  |  |  |

|                        |        | 2.1.1           | Data Abstraction Tier                                  | 7  |  |  |

|                        |        | 2.1.2           | TROM Tier                                              | 7  |  |  |

|                        |        | 2.1.3           | Subsystem Specification Tier                           | 8  |  |  |

|                        | 2.2    | Syntax          | x and Semantics                                        | 8  |  |  |

| 2.3 TROMLAB Components |        | ILAB Components | 13                                                     |    |  |  |

|                        |        | 2.3.1           | The Interpreter                                        | 13 |  |  |

|                        |        | 2.3.2           | The simulator                                          | 15 |  |  |

| 3                      | Mod    | lificati        | ion to the Initial Design                              | 18 |  |  |

|                        | 3.1    | Necess          | sity for re-engineering                                | 18 |  |  |

|                        | 3.2    | Impro           | vements                                                | 21 |  |  |

|                        |        | 3.2.1           | Interpreter                                            | 21 |  |  |

|                        |        | 3.2.2           | Simulator                                              | 24 |  |  |

| 1                      | Desi   | gn an           | d Implementation of the Modified Interpreter and Simu- |    |  |  |

|                        | lator  | •               |                                                        | 25 |  |  |

|                        | 4.1    | Class           | liagrams                                               | 25 |  |  |

|   |     | 4.1.1  | Interpreter                                                     | 26  |

|---|-----|--------|-----------------------------------------------------------------|-----|

|   |     | 4.1.2  | Simulator                                                       | 30  |

|   | 4.2 | Langu  | nage of choice                                                  | 32  |

|   |     | 4.2.1  | JavaCC                                                          | 32  |

|   |     | 4.2.2  | JJTree                                                          | 33  |

|   | 4.3 | Imple  | mentation                                                       | 33  |

|   |     | 4.3.1  | Interpreter                                                     | 33  |

|   |     | 4.3.2  | Simulator                                                       | 38  |

|   |     | 4.3.3  | Interfacing with the simulator                                  | 39  |

| 5 | Rea | soning | g System: Requirements                                          | 40  |

|   | 5.1 | Reaso  | ning System as a Debugging Tool                                 | 41  |

|   | 5.2 | Reaso  | ning Based on Hypothetical Queries                              | 43  |

|   | 5.3 | Using  | the Reasoning System for Validation of the Specifications       | 44  |

| 6 | Rea | soning | System: Design and Implementation                               | 47  |

|   | 6.1 | Debug  | gging tool                                                      | 49  |

|   | 6.2 | Hypot  | hetical Queries                                                 | 55  |

|   | 6.3 | Valida | ation of the Specifications                                     | 58  |

| 7 | Ca  | se Stu | dy: Robotics Assembly example                                   | 63  |

|   | 7.1 | Introd | croduction                                                      |     |

|   | 7.2 | Proble | Study: Robotics Assembly example troduction                     |     |

|   |     | 7.2.1  | Informal Problem Description                                    | 63  |

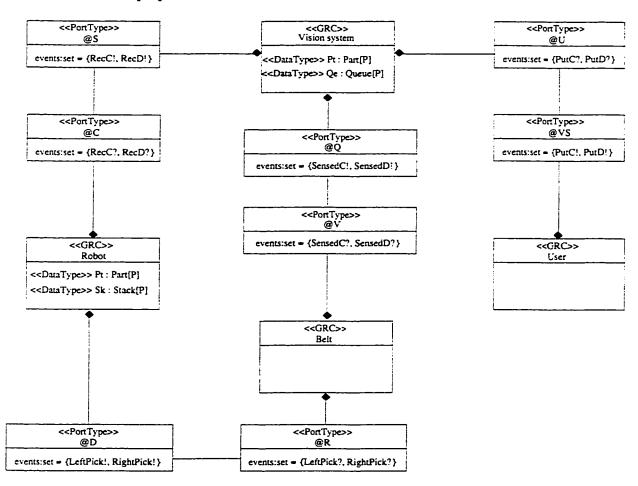

|   |     | 7.2.2  | Class Diagram for Robotics Assembly                             | 66  |

|   |     | 7.2.3  | Formal Problem Description                                      | 67  |

|   | 7.3 | Reason | ning on the Robotics Assembly                                   | 76  |

|   |     | 7.3.1  | The Reasoning System as a Debugging tool                        | 76  |

|   |     | 7.3.2  | Hypothetical Queries                                            | 92  |

|   |     | 7.3.3  | Using the Reasoning System for Validation of the Specifications | 110 |

| 8 | Con | clusio | n and Future Work                                               | 115 |

|   | 8.1 | Work s | synthesis                                                       | 115 |

|   | 8.2 | Future | e Work                                                          | 115 |

|   |     | Q O 1  | Interpreter                                                     | 116 |

| 8.2.2        | Simulator        | 116 |

|--------------|------------------|-----|

| 8.2.3        | Reasoning System | 116 |

| Bibliography |                  | 117 |

| Appendix A   |                  | 120 |

| Appendix B   |                  | 126 |

# List of Figures

| 1  | Three tier                                                    | 6  |

|----|---------------------------------------------------------------|----|

| 2  | Set trait                                                     | 7  |

| 3  | Train class specifications                                    | S  |

| 4  | Gate class specifications                                     | ç  |

| 5  | Controller class specifications                               | 10 |

| 6  | SCS                                                           | 10 |

| 7  | Architecture of interpreter                                   | 15 |

| 8  | Architecture of simulation tool                               | 17 |

| 9  | Future TROMLAB environment                                    | 21 |

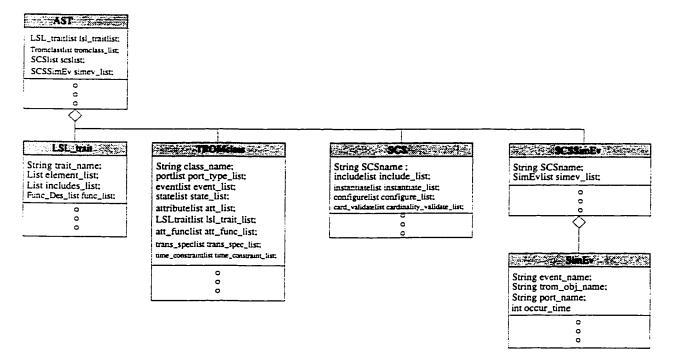

| 10 | AST Structure                                                 | 23 |

| 11 | Interpreter Class diagram (Old)                               | 26 |

| 12 | Interpreter Class diagram - Detailed (Old)                    | 26 |

| 13 | Interpreter Class diagram - Detailed (Old)                    | 27 |

| 14 | Interpreter Class diagram (New)                               | 28 |

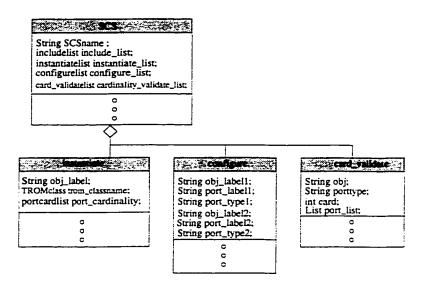

| 15 | Interpreter Class diagram - SCS (New)                         | 29 |

| 16 | Interpreter Class diagram - TROMclass (New)                   | 29 |

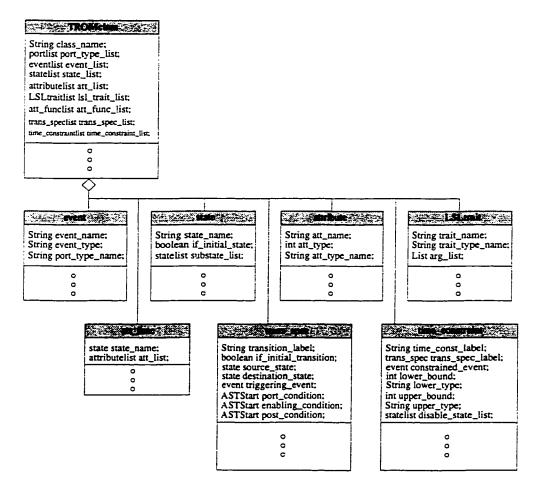

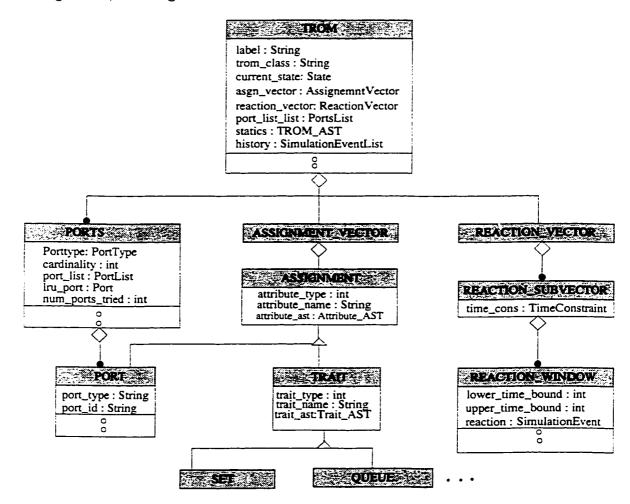

| 17 | Simulator Class diagram - TROM class diagram(New)             | 30 |

| 18 | Simulator Class diagram - Simulation Event Object model (New) | 31 |

| 19 | Simulator Class diagram - Subsystem Object model (New)        | 31 |

| 20 | Simulation event list                                         | 36 |

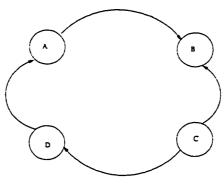

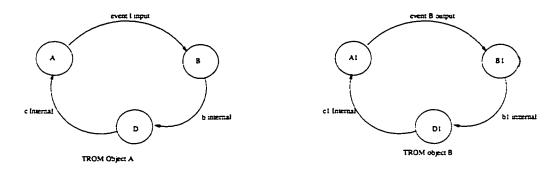

| 21 | Unreachable state within a TROM                               | 45 |

| 22 | Unreachable state in SCS                                      | 46 |

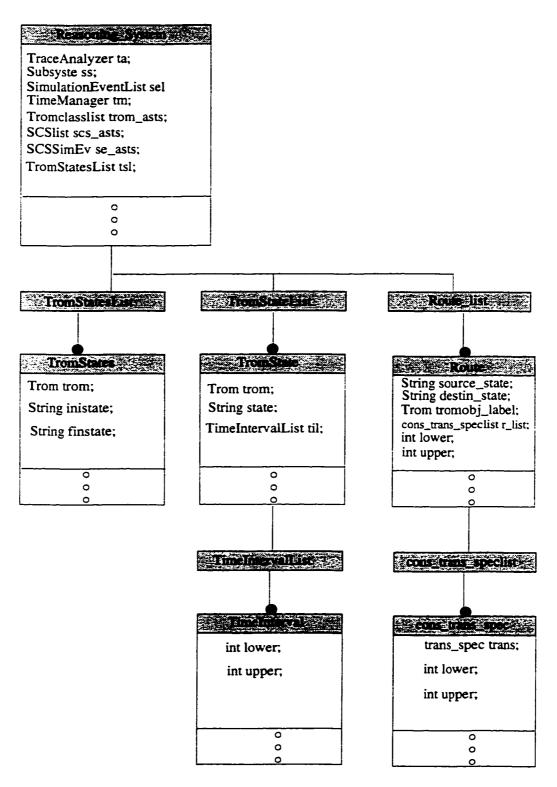

| 23 | Class Diagram Of the Reasoning Systemm                        | 48 |

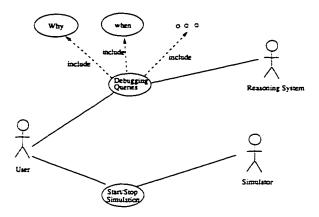

| 24 | Use Case Diagram For Debugging Tool                           | 50 |

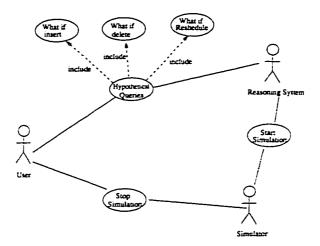

| 25 | Use Case Diagram For Hypothetical Queries                     | 56 |

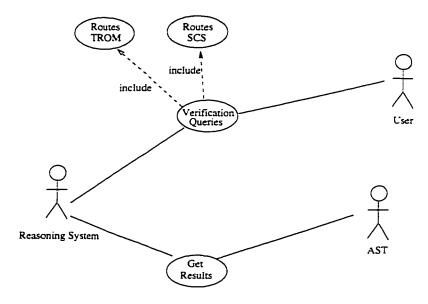

| 26 | Use Case Diagram For Verification Tool                        | 59 |

| 27 | Need for cyclic routes in related TROM objects          | 61 |

|----|---------------------------------------------------------|----|

| 28 | Robotics System Class diagram                           | 67 |

| 29 | User TROM class - Textual representation                | 68 |

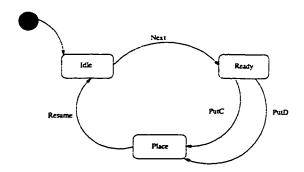

| 30 | User TROM class - State machine representation          | 68 |

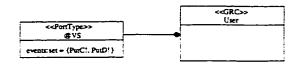

| 31 | User TROM class - UML model                             | 69 |

| 32 | Vision system TROM class - Textual representation       | 69 |

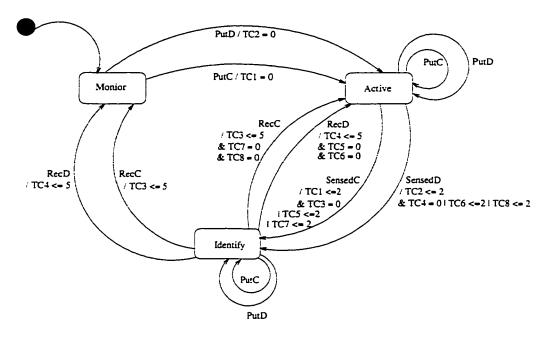

| 33 | Vision system TROM class - State machine representation | 70 |

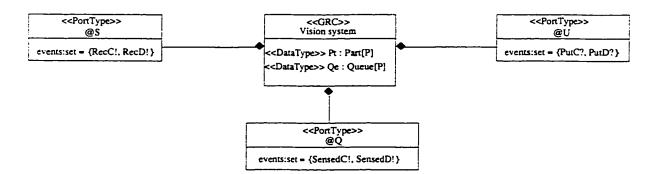

| 34 | Vision system TROM class - UML model                    | 70 |

| 35 | Belt TROM class - Textual representation                | 71 |

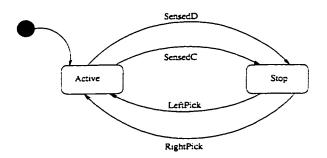

| 36 | Belt TROM class - State machine representation          | 71 |

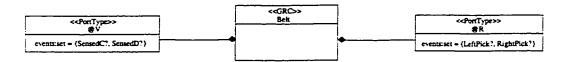

| 37 | Belt TROM class - UML model                             | 71 |

| 38 | Robot TROM class - Textual representation               | 72 |

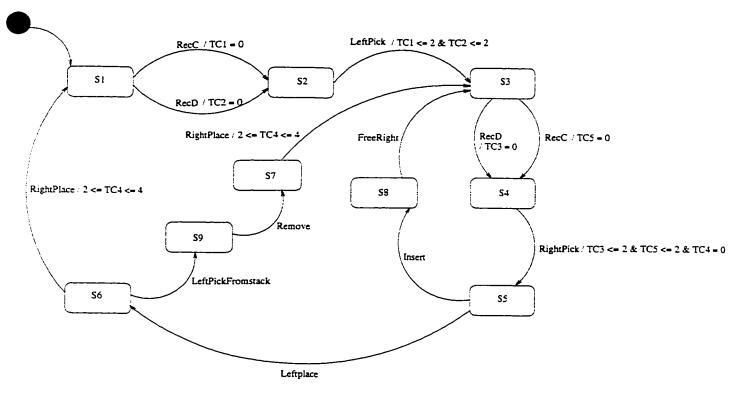

| 39 | Robot TROM class - State machine representation         | 73 |

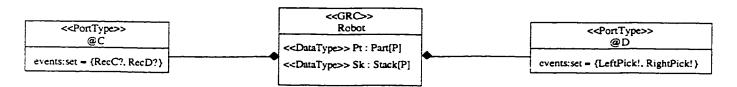

| 40 | Robot TROM class - UML model                            | 73 |

| 41 | SCS - Textual representation                            | 74 |

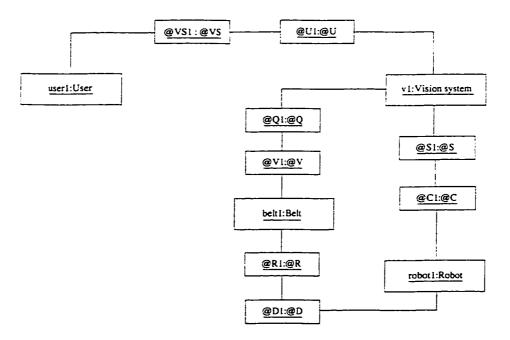

| 42 | SCS - UML model                                         | 74 |

| 43 | Sample Simulation Event List                            | 75 |

| 44 | Part LSL Trait                                          | 75 |

| 45 | Queue LSL Trait                                         | 76 |

| 46 | Stack I SI. Trait                                       | 76 |

# List of Tables

| 1  | States of Robot Manipulator.                     | 6   |

|----|--------------------------------------------------|-----|

| 2  | Grammar for generic reactive class specification | 120 |

| 3  | Grammar for generic reactive class title         | 120 |

| 4  | Grammar for events                               | 121 |

| 5  | Grammar for states                               | 121 |

| 6  | Grammar for attributes                           | 121 |

| 7  | Grammar for LSL traits                           | 122 |

| 8  | Grammar for attribute functions                  | 122 |

| 9  | Grammar for transition specifications            | 123 |

| 10 | Grammar for time constraints                     | 124 |

| 11 | Grammar for subsystem configuration              | 124 |

| 12 | Grammar for include section                      | 125 |

| 13 | Grammar for instantiate section                  | 125 |

| 14 | Grammar for configure section                    | 125 |

# Chapter 1

## Introduction

Research in real-time reactive systems revolve around languages and methods for specification and design, methodologies for verification and validation, and development of tools and user interfaces for hiding the complexity of rigorous formalisms. This thesis addresses the issue of simulated debugging and reasoning, an important part of a validation technique for real-time reactive systems. The *Reasoning System* is integrated with the *Simulator* of TROMLAB, a rigorous real-time reactive systems development environment being built in the Department of Computer Science, Concordia University.

## 1.1 Real Time Reactive Systems

Reactive systems maintain a continuous ongoing interaction with their environment. Such systems are largely event driven, interact intensively with the environment through stimulus-response behaviour, and are regulated by strict timing constraints. Further these systems might also consist of both physical components and software components controlling the physical devices in a continuous manner. Although reactive systems are interactive systems, there is a fundamental difference between these two systems. Whereas both environment and processes have synchronisation abilities in interactive systems, a process in a reactive system is solely responsible for the synchronisation with its environment. That is, a process in a reactive system is fast enough to react to stimulus from the environment, and the time between stimulus and response is acceptable enough for the dynamics of the environment to be

receptive to the response. For example, a human-computer interface is an interactive system, whereas a controller for a collision-free coordinated motion of autonomous robots is clearly reactive. In the case of real-time reactive systems, stimulus-response behaviour is also regulated by timing constraints and the major design issue is one performance. Examples of real-time reactive systems include telephony, air traffic control systems, nuclear power reactors, and avionics.

Several factors contribute to the complexity of real time reactive systems. They are:

- largeness: telephony and air traffic control systems are made up of a large number of components;

- time constraints: telephony imposes soft time constraints, a violation of which may not cause any catastrophe; however, avionics and nuclear power reactor control systems impose hard (strict) time constraints, which if violated will cause damage and injury to human safety;

- criticality: nuclear power reactor controller is a safety-critical system;

- heterogeneity: sensors, actuators, and system processes have different functional and time sensitive capabilities.

The reactive behaviour of the system is a combination of its functional behaviour, causal dependencies of actions, and real-time durations governing them. Due to these three layers of interaction, understanding or reasoning about the behaviour of real-time reactive systems becomes difficult. In TROMLAB, these are resolved through the introduction of the following steps:

- appropriate formalisms for specification and design refinement,

- process model support for iterative design, animated analysis, and design-time debugging,

- browser support for active reuse of design and specification artifacts, and

- an integrated GUI supporting all the above features.

## 1.2 Scope of the Thesis

In designing TROMLAB environment we have been motivated by the need for rigorous development methods for real-time reactive systems. The class diagrams, state machine representations, and the subsystem configuration have formal syntax and semantics. Before committing a system design to its implementation, the process model in TROMLAB requires the modelled system to be validated and verified for the satisfaction of system properties. The central piece of the *Animator* is a simulator which simulates the specified system strictly according to the specification. The current thesis is an important contribution to the simulated debugging and reasoning within the animator.

The thesis briefly reviews the architecture and design components of TROMLAB environment in Chapter 2. The planning stage of the Reasoning System identified the twin needs: the ability to integrate with the Simulator and the GUI. Since the design of GUI forced a complete re-engineering of the Interpreter, and the Animator, we discuss the design of these components in Chapters 3, and 4. Having defined the context in which the Reasoning System is to function, we discuss a set of requirements of the Reasoning System in Chapter 5. In Chapter 6, we give descriptions of the algorithms for processing different queries, and comment on their complexities. Chapter 7 gives a dialogue of the Reasoning System, implemented in Java, for Robotics Assembly case study. Chapter 8 concludes the thesis with a summary of the contributions and possible extensions to the reasoning system.

## Chapter 2

# TROMLAB Environment - a brief review of initial design

The TROMLAB environment is an integrated facility based on TROM formalism [Ach95] and built around a process model that incorporates iterative development, incremental design, and application of formalism through the different stages of design. The process model incorporates an iterative development approach, the benefits of which are well-known for:

- reducing risks by exposing them early in the development process.

- giving importance to the architecture of the software unit, and

- designing modules for large scale software reuse.

The TROMLAB environment provides facilities for modular design of TROM classes, modular composition of objects to build subsystems and analyse system capabilities through simulation and verification [Mut96]. An *Interpreter* and *Animator* were the first components to be built. Recently, a *Browser* has been added. In conjunction with the current effort, the following components have been built:

- 1. Reasoning system:- to aid simulated debugging and reasoning of systems during development;

- 2. PVS axiom generator:- a tool based on the verification methodology given in [Pom99] to generate axiomatic descriptions of specified classes and subsystems in PVS:

- 3. Mechanised verifier:- a verification assistant which can be used to prove safety properties of the system stated as lemmas in PVS theories.

- 4. Graphical User Interface: to provide a comprehensive interface to all the above stages of reactive systems development.

## 2.1 TROMLAB Formalism

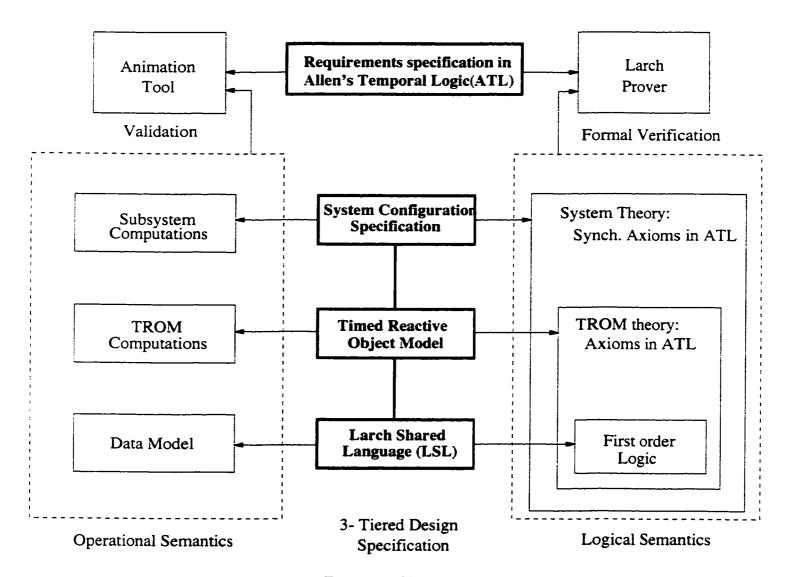

The three tier structure of the object oriented methodology introduced by [Ach95], as shown in Figure 1, is the basis of TROMLAB environment for developing reactive systems. The benefits derived from the object oriented techniques include modularity and reuse, encapsulation, and hierarchical decomposition using inheritance. In this methodology, the system requirement is specified in temporal logic. The system is modelled using a three tier design language.

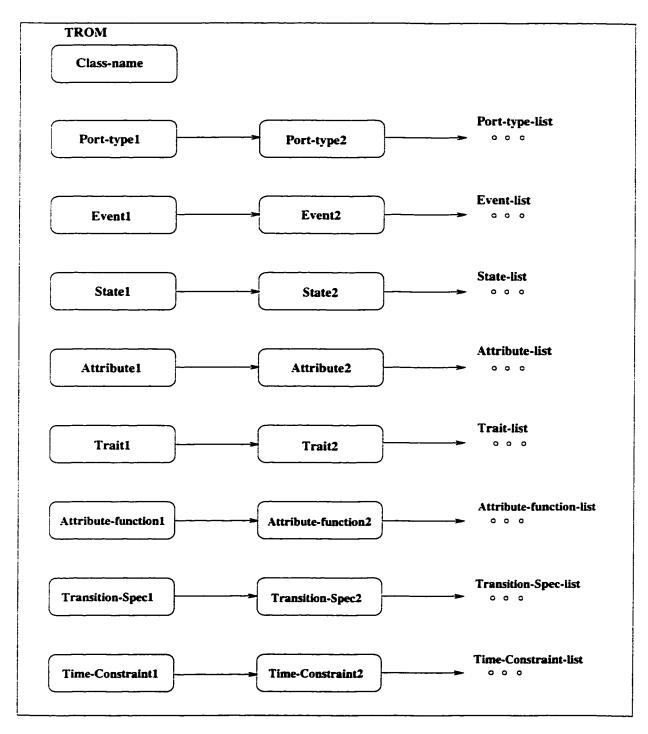

The three tiers independently specify the system configuration, reactive classes, and the abstract data types included in reactive class definitions. Lower-tier specifications are imported into upper tiers. TROM is a hierarchical finite state machine augmented with ports, attributes, logical assertions on the attributes, and time constraints. The middle-tier formalism specifies TROM classes. Abstract data types are specified as LSL(Larch Shared Language) traits in the lowest tier, and can be used by objects modelled by TROM. The upper-most tier specifies object collaboration where each object is an instance of a TROM.

The three tiers are briefly described in the following three subsections.

Figure 1: Three tier

#### 2.1.1 Data Abstraction Tier

This level specifies the abstract data types included in the class definition of the middle tier. An abstract data type is defined as Larch Shared Language (LSL) trait. Larch provides a two tier approach to specification:

- First tier, called Larch Interface Language (LIL), is used to describe the semantics of a program module.

- Second tier, called Larch Shared Language (LSL), is used to specify mathematical abstractions which can be referred to in any LIL specification.

In the present implementation of TROMLAB, only LSL traits are included. An LSL trait for set data type is shown in Figure 2.

```

Trait: Set(e, S)

Includes: Integer, Boolean

Introduce:

creat: -> S;

insert: e, S -> S;

delete: e, S -> S;

size: S -> Int;

member: e, S -> Bool;

isEmpty: S -> Bool;

belongto: e, S -> Bool;

end

```

Figure 2: Set trait

#### 2.1.2 TROM Tier

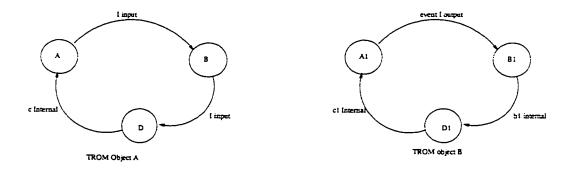

A TROM models a Generic Reactive Class (GRC). A GRC is an augmented finite state machine with port types, attributes, hierarchical states, events triggering transitions and future events constrained by strict time bounds. A state is an abstraction denoting an environment information or a system information during a certain interval of time. An event denotes an instantaneous signal. The events are classified into three types: *input*, *output*, and *internal*. Input (output) events occur at the ports of a TROM, synchronising with the output (input) events of another TROM in

Its environment. The ports are abstraction of synchronous communication between TROMs. TROM objects can only interact through the port linking them as defined SCS. Only compatible ports can be linked, such that event sent at one port is acceptable as an input event at the other port at the same time [Ach95]. The specification of a transition states the conditions under which an event may occur, and the consequences of such an occurrence. The time constraints enumerate the events triggered by a transition and the time bounds within which such events should occur. Thus, a GRC is a class parameterised with port types, and encapsulates the behaviour of all TROM objects that can be instantiated from it. A formal definition of TROM is given in [Ach95].

The occurrence of an event e at a port p at time t triggers an activity which may take a finite amount of time to complete. These events may lead the TROM(s) affected by the event to undergo a state change and may further lead to the occurrence of new events as specified by the timing constraints.

### 2.1.3 Subsystem Specification Tier

This level is the top most tier which constitutes subsystem configuration specifications (SCS). We define the number of ports for each port type parameter in a GRC to create an object of that GRC. As in OO paradigm, several objects can be created from one GRC. These objects may have different number of ports for each port type, and consequently have the ability to communicate and interact differently with their environment. We can also include other subsystem configurations in defining a subsystem.

## 2.2 Syntax and Semantics

The structure and behaviour of TROM can be described either textually or visually. The templates for textual descriptions of TROMs and subsystems are shown in Figure 3, Figure 4, Figure 5, and Figure 6.

The visual representation of a reactive system includes the class diagrams, state machine diagrams, and the collaboration diagrams. These are discussed in Chapter.

```

Class Train [@C]

Events: Near!@C, Out, Exit!@C, In

States: *idle, cross, leave{*11,12}, toCross

Attributes: cr:@C

Traits:

Attribute-Function: idle -> {};cross -> {};leave -> {};toCross -> {cr};

Transition-Specifications:

R1: <idle,toCross>; Near(true); true => !cr'=pid;

R2: <cross,leave>; Out; true => true;

R3: <leave,idle>; Exit(!pid=cr); true => true;

R4: <toCross,cross>; In; true => true;

Time-Constraints:

TCvar2: R1, Exit, [0, 6), {};

TCvar1: R1, In, (2, 4), {};

end

```

Figure 3: Train class specifications

```

Class Gate [@S]

Events: Lower?@S, Down, Up, Raise?@S

States: *opened, toClose, toOpen, closed

Attributes:

Traits:

Attribute-Function:

Transition-Specifications:

R1: <opened,toClose>; Lower(true); true => true;

R2: <toClose,closed>; Down; true => true;

R3: <toOpen,opened>; Up; true => true;

R4: <closed,toOpen>; Raise(true); true => true;

Time-Constraints:

TCvar1: R1, Down, [0, 1], {closed}

TCvar2: R4, Up, [1, 2], {};

end

```

Figure 4: Gate class specifications

```

Class Controller [@P.@G]

Events: Lower!@G, Near?@P, Raise!@G, Exit?@P

States: *idle, activate, deactivate, monitor

Attributes: inSet:PSet

Traits: Set[@P.PSet]

Attribute-Function: activate -> {inSet};deactivate -> {inSet};monitor -> {inSet};idle -> {};

Transition-Specifications:

R1: <activate,monitor>; Lower(true); true => true;

R2: <activate,activate>; Near(!(member(pid,inSet))); true => inSet'=insertpid,inSet);

R3: <deactivate,idle>; Raise(true); true => true;

R4: <monitor,deactivate>; Exit(member(pid,inSet)); size(inSet)=1 => inSet'delete(pid,inSet);

R5: <monitor,monitor>; Near(!(member(pid,inSet))); true => inSet'=insert(pd,inSet);

R6: <monitor,monitor>; Exit(member(pid,inSet)); size(inSet)>1 => inSet'=deete(pid,inSet);

R7: <idle,activate>; Near(true); true => inSet'=insert(pid,delete(pid, inSt));

Time-Constraints:

TCvar1: R7, Lower, [0, 1], {};

TCvar2: R4, Raise, [0, 1], {};

end

Figure 5: Controller class specifications

SCS TCG

Includes:

Instantiate:

t1::Train[@C:2];

t2::Train[@C:2];

t3::Train[@C:2];

c1::Controller[@P:3,@G:1];

c2::Controller[@P:3,@G:1];

g1::Gate[@S:1];

g2::Gate[@S:1];

Configure:

t1.@C1:@C <-> c1.@P1:@P;

t1.@C2:@C <-> c2.@P1:@P:

t2.@C1:@C <-> c1.@P2:@P;

t2.@C2:@C <-> c2.@P2:@P;

t3.@C1:@C <-> c1.@P3:@P;

t3.@C2:@C <-> c2.@P3:@P;

c1.@G1:@G <-> g1.@S1:@S;

c2.@G1:@G <-> g2.@S1:@S;

```

Figure 6: SCS

end

The TROM model incorporates the essential features for describing reactive entities. A TROM object has a single thread control and communicates with its environment through ports by synchronous message passing. The ports represent access points for by directional communication between the objects. A port type determines the messages that are allowed at a port of that type. A TROM can have several port types associated with it and several ports of the same port type. An event represents an instantaneous activity, while an action represents an activity taking a non-atomic time interval of finite duration. At any instant, a TROM exhibits a signal representing a message, an internal activity, or idleness. The signal describes the occurrence of an event at the specific time instant, at a specific port.

Informally, the templates in Figure 3, Figure 4, and Figure 5 have the following elements:

- A set of events partitioned in three sets: input, output, and internal events.

- A set of states: A state can have sub-states.

- A set of typed attributes: The attributes can be one of the following:

- abstract data types,

- port reference type.

- An attribute function defining the association of attributes to states.

- A set of transition specification: Each specification describes the computational step associated with the occurrence of an event. The transition specification has three assertions: a pre- and post-condition as in Hoare logic, and the port -condition specifying the port at which the event can occur.

- A set of time-constraints: Each time constraint specifies the reaction associated

with a transition. A reaction can fire an output or an internal event within a

defined time period. Associated with a reaction is a set of disabling states. An

enabled reaction is disabled when an object enters any of the disabling states

of the reaction.

The status of a TROM captures the state in which the TROM is at that instant, the value of the attributes at the instant as reflected in the assignment vector, and the timing behaviour of TROM as specified in the reaction vector. The reaction vector associates the set of reaction windows with each time constraint, where a reaction window represents a outstanding timing requirement to be satisfied by the output event or the internal event associated with the time constraint. When the reaction vector is null the TROM is in a stable status.

The occurrence of an activity stipulated by an interaction with the environment, or by an internal transition leads to a change in the status of a TROM. The current state of a TROM, its assignment vector, and its reaction vector can only be modified by an incoming message, by an outgoing message, or an internal signal. The status of a TROM is thus encapsulated, and cannot be modified in any other way.

A computational step [Ach95] of a TROM is an atomic step which takes the TROM from one status to its succeeding status as defined by the transition specifications. Every computational step of a TROM is associated with the transition of the TROM and every transition with either an interaction signal or an internal signal or a silent signal. The computational step occurs when the TROM receives a signal and there exists a transition specification such that the following conditions are satisfied: the triggering event for the transition is the event causing the signal; the TROM is in the source state or in a sub-state of a source state of transition specification; the port condition is satisfied if the signal is in the interaction and the enabling condition is satisfied by the assignment vector. The effects of the computational step are: the TROM enters the destination state; the assignment vector is modified to satisfy the post condition; and the reaction vector is modified to reflect the firing, disabling, and enabling of reactions. Each computational step is associated with the transition in the state machine of the TROM. After the transition is taken the current state will be the destination state of the transition. The port at which the interaction must satisfy the port condition associated with the transition, thereby constraining the objects with which the TROM can interact at that instance.

A computational step causes time-constrained responses to be activated or deactivated. If the constraint event of the outstanding reaction is the event associated with the transition, and the time of occurrence of the event associated with the transition is within the reaction window of the outstanding reaction, then the reaction is fired. If the destination state of the transition associated with the computational step is a disabling state for an outstanding reaction then the reaction is disabled. Whenever a reaction is time-constraint by the transition associated with the computational

step, the reaction is enabled. The operational semantics ensures that the time cannot advance past reaction window without either firing or disabling the associated outstanding reaction.

The factors determining whether a TROM is well formed are:

- There is at least one transition leaving every state, thus forbidding a final terminating state.

- If there is more than one transition leaving a state, then the enabling conditions of transitions should be mutually exclusive.

- Before a TROM starts executing, the value of only the active attributes in the initial state are specified. An attribute will acquire a value only when it reaches the first state in which it is active.

- Every computational step in a TROM results in some computation of the TROM.

A subsystem is composed by instantiating TROM objects from GRCs and configuring them through port links. Only compatible ports are linked between TROM objects. An already composed subsystem may also be included in composing a new subsystem: one or more of the unused ports in the objects of the included subsystem are configured with some ports of the instantiated objects in the new subsystem being composed. The objects communicate and synchronise through the configured links. The computational step of a subsystem is a vector of computational steps of the TROMs included in it.

## 2.3 TROMLAB Components

In this section we briefly review the functionality of the *Interpreter* [Tao96], and the *Animator*[Mut96].

## 2.3.1 The Interpreter

The interpreter is the first tool to be implemented in TROMLAB. The tool, as designed by Tao [Tao96], checks the textual specification for syntactic correctness and builds

an internal representation of the formal specification of a reactive system. In order to build the internal representation it performs the following tasks:

- Syntactic analyses: It makes sure that the files are syntactically correct; that is, consistent with TROM grammar.

- Semantic analysis: It does simple semantic analysis such as

- states of a TROM have different names.

- an LSL trait is used after being declared,

- every transition has an outgoing and incoming state, and

- transition specifications are well-formed logical formulas

- Internal structure: Based on a syntactically and semantically correct text file it generates all the internal data structures that would be used by all the other tools in TROMLAB.

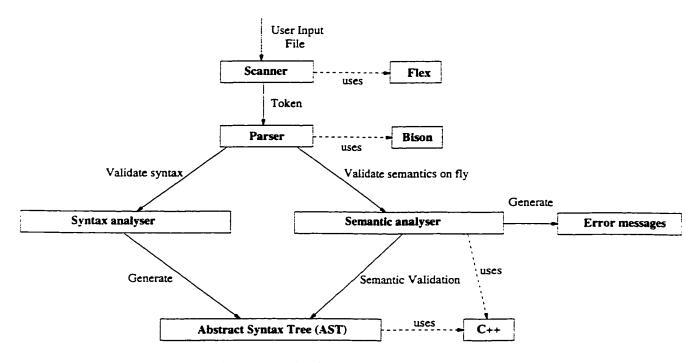

The components of interpreter are the following:

#### Scanner

A single text file containing LSL traits, TROM class specifications, subsystem specification, and an initial event list is taken as input to the scanner. Using Flex the scanner performs lexical analysis and identifies the tokens to be used by the parser.

#### • Parser

This uses Bison to certify the syntactic correctness of the tokens received from the scanner.

### • Syntax analyser

Using predefined grammars for TROM and subsystem this module evaluates the syntactic correctness of tokens received by Bison. Any error at this stage will be communicated by Bison to the user and will terminate the execution of the interpreter.

#### • Abstract syntax tree generator

An abstract syntax tree is generated for each TROM and subsystem input to the interpreter.

#### • Semantic analyser

This is a C++ program that uses the well-formedness rules of the formalism to perform simple semantic analysis.

#### • Error message handler

This is part of semantic analyser functionality. Every semantic error detected will be saved in a file until the end of semantic analysis.

Figure 7: Architecture of interpreter

The interpreter uses YACC and LEX for syntactic analysis and is implemented in C++. This tool had some limitations: all the information had to be in a single file, which makes it difficult to incrementally design a complex system. The data structure generated by this tool also has several limitations. This will be discussed in Chapter 3.

#### 2.3.2 The simulator

The simulator tool was designed and implemented by Muthiayen [Mut96]. This work was started in parallel with the work on the interpreter. The simulator interfaces with the abstract syntax tree built by the interpreter to extract the information for

simulation. It builds a simulation event list to keep track of all outstanding events in the system. The simulator can work in one of two modes:

- Debugger mode: In this mode the developer can, at the end of every handled event, invoke the debugger and use it to query the system. The system can be rolled back and new events can be injected.

- Normal mode: In this mode the simulation will go on uninterrupted until the system goes into a stable state. The result of a the simulation is one scenario of what could happen, given the initial set of events.

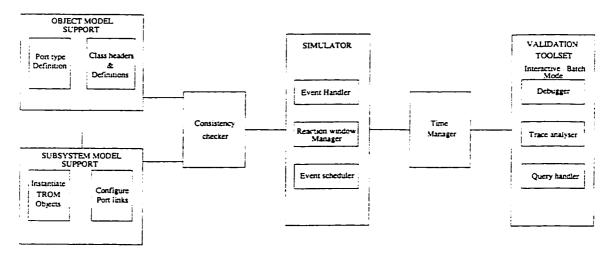

The simulation tool consists of the following components:

- Simulator: It consists of an event handler, a reaction window manager, and an event scheduler.

- Event handler is responsible for handling the events which are due to occur and detects the transition which the event will trigger.

- The reaction window manager is responsible in activating the computational step to handle the transition causing events to be fired, disabled or enabled.

- The event scheduler causes an enabled event to occur at a random time within the corresponding reaction window. It schedules output events through the least recently used port using a round robin algorithm.

- Consistency checker: It ensures the continuous flow of interactions by detecting deadlock configurations.

- Validation tool: It consists of a debugger, a trace analyser, and a query handler.

- The debugger supports system experimentation by allowing the user to examine the evolution of the status of the system throughout the simulation process. It also supports interactive injection of simulation event, and simulation rollback to a specific point in time.

- The trace analyser includes facilities for the analysis of the simulation scenario. It gives feedback on the evolution of the status of the objects in the system, and the outcome of the simulation event.

- The query handler allows examining the data in the AST for the TROM class to which the object belongs, and supporting analysis of the static components during simulation.

- Object model support: It supports the specification of the TROM classes and the evaluation of the logical assertions included in the transition specifications.

- Subsystem model support: It creates subsystems by instantiating included subsystems from object and port links.

- Time manager. It maintains the simulation clock updating it regularly. It allows setting the pace of the clock to suit the needs of analysis of simulation scenarios. It also allows freezing the clock while analysing the consequences of a computation.

#### SIMULATION TOOL

Figure 8: Architecture of simulation tool

# Chapter 3

# Modification to the Initial Design

Evolving systems need to have a flexible design with abilities to absorb changing requirements with minimal changes to the design. In the absence of a flexible design, it may be necessary to re-engineer and rebuild several of the system components. The initial TROMLAB design is an example of a design which can not be adapted to a graphical user interface front-end. However, GUI has been recognised as an important requirement for the usability of the entire system. Moreover reasoning with partial subsystems was not possible. This is a severe limitation of a large system for which different components may become available at different times. One of the goals of reasoning is to be able to reason modularly and compose the consequences. This is the major reason that a re-engineering of the initial design was undertaken.

## 3.1 Necessity for re-engineering

The three important criteria for TROMLAB design have been identified as *scalability*, *portability*, and *flexibility*. The TROM methodology provides the support to design systems in a compositional and incremental fashion. This can be translated to the implementation layer only if the language of implementation allows composition and specialisation of class instances. The current implementation in C++ does not meet the above criteria:

1. The *Interpreter* program required one input file containing the textual specifications of all TROMs, subsystems, and LSL descriptions. Moreover, it required

that the data be organised in a certain order. This requirement is quite stringent, acts against the principles of modular and incremental development of the system. Separate compilation of each specification was not possible. Hence, GUI facilities such as individual composition and compilation of TROMs could not be handled by the *Interpreter*.

- 2. The AST constructed by the interpreter had a complex data structure, and its interface to the simulator was poorly designed. Consequently, it became necessary to write interface functions whenever a need arose. This posed severe problems in the maintenance of the *Interpreter*.

- 3. The language of implementation was C++, which can not be integrated with some of the currently available graphical libraries for Unix platform. In particular, graphical libraries for Unix are written in Java, and do not interface with C++.

- 4. The current programs run under Unix and are not portable to other platforms.

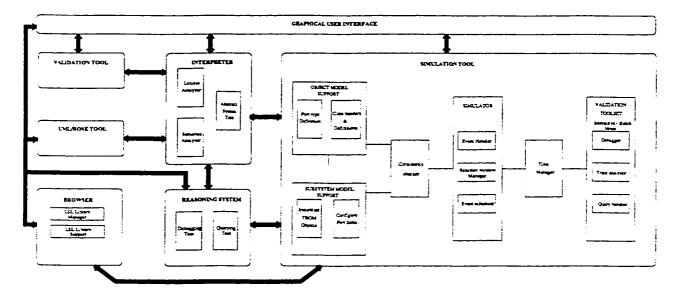

The revised model of TROMLAB environment is shown in Figure 9. It consists of the following components, each designed and implemented to meet the three criteria stated above:

- 1. Interpreter: It should be possible to type check and compile one specification at a time. The order of input is irrelevant. It should be possible to interface with GUI, the simulator, and the verifier. The capabilities of the modified interpreter are discussed in the next section.

- 2. Simulator: It should be possible to simulate any subsystem that has been type checked by the *Interpreter*. It should be possible to view the simulated scenarios and histories through GUI. The capabilities of the modified simulator are discussed in the next section.

- 3. Browser: This tool has been implemented in Java [Nag99]. It can be invoked from within the GUI or it can be invoked as a stand-alone tool. The user can view LSL traits, TROMs, and subsystems from the reuse library database, and query the system for their versions and dependencies.

- 4. UMLRT support: This tool is the front-end for visually composing reactive system specifications using UMLRT support. Class diagrams, state charts, sequence diagrams, and collaboration diagrams can be constructed using Rose. Using stereotypes, an extensional facility in UML, a minimal set of extensions has been provided in to model real-time reactive systems in Rose. The UMLRT support [Oan99] extracts the information from these models and generates formal specifications in the syntax defined in TROM methodology.

- 5. Reasoning system: This tool is the subject of this thesis. It will be described in more details in the following chapters. It gives the user the ability to query the simulated scenario and reason about changes to the past and understand the future consequences due to such changes.

- 6. GUI: The graphical user interface provides a comprehensive interaction facility: it interfaces with Rose/UML tool for composing specifications graphically, which is interfaced with interpreter for syntactic and semantic analysis; simulation scenarios can be viewed, and queries of the Reasoning System can be composed, verification steps can be viewed.

- 7. Verification Assistant: The Simulator with Reasoning System constitute the validation tool. A tool to automatically generate axiomatic descriptions of specifications from the abstract syntax tree is being built now [Pom99]. The results produced by this tool will serve as an input to a mechanised verifier that is being designed.

Integrating all these components in TROMLAB to meet the three design principles cited earlier demand the following:

- 1. An Object oriented development environment:

- 2. A good graphics library which supports GUI development:

- 3. Need for compatibility between different components: UML RT support has been developed under Windows platform; the browser has been implemented in Java.

Based on these constraints we have chosen Java as the language of implementation for the re-engineered components as well as the yet to be implemented components of the verifier.

Figure 9: Future TROMLAB environment

## 3.2 Improvements

It is the *Interpreter* that required a totally new design and implementation. The major changes in the *Animator* include its interfacing to the new *Interpreter*, additional query handling facilities, and enhancements to simulation event list.

## 3.2.1 Interpreter

1. Scanners: Having a single scanner makes the design process harder for the user. The user has to create all the formal specifications at the same time before it can be checked for syntactic correctness. It is quite hard for a single scanner to generate easy-to-understand error messages for a large system consisting of numerous specifications. Whenever a new specification is added to an existing set of specifications it would require re-compilation of the whole set of specifications. A more efficient technique is to have separate scanners, one for each type of component. In the new design we have constructed separate scanners, one for LSI trait, one for TROM class specification, one for SCS, and one for simulation event list. This makes it easier for the user to design, debug and validate different components independently before doing the actual semantic analysis. As a result, the user can reuse the compiled components of any one type without having to wait for the compilation of other specifications. Thus,

the new design conforms to the principle of separation of concerns ingrained in OO methodology and is faithful to the three-tier methodology stated in Chapter 2.

- 2. Error messages: In the old design the error messages were generated by Flex and Bison. Hence, the messages were neither specific to any one specification nor sufficiently explanatory for the user to understand and correct the errors. In the new design, although JavaCC tool is used to parse and compile the specifications, the error messages are not handled by JavaCC; instead, the error messages generated by the new Interpreter module are quite specific to the source of errors.

- 3. Changes to the Grammar. According to the previous grammar in the configure section of the SCS the user could not specify the name of the ports, and in turn it was generated by the Interpreter itself based on the cardinality of the specific port type. In the new grammar the user has to specify the port name for each TROM object in the configure section. The other changes to the grammar were made in the initial simulation event list. The name of SCS was added, along with the port type name added to the initial events. This change triggered changes to the semantic analyser. The description of the Grammar is in the Appendix A.

- 4. Semantic analysis: In the previous design the semantic analysis was conducted in two stages: on the fly analysis and AST validation. In the new design, semantic analysis also conforms to the principle of encapsulation in OO technology: semantic analysis internal to a class specification, and semantic analysis relating objects in a subsystem configuration. When a class is syntax checked, it is also semantically validated independently for its encapsulated properties. Once a class is semantically checked and a subsystem of objects is created, the user can initiate the second phase of semantic analysis which does the semantic validation related to the different objects in the subsystem.

- 5. AST Structure: The structure of AST has been simplified. The Figure 10 below describes the new AST structure.

Figure 10: AST Structure

#### 3.2.2 Simulator

- 1. Object Model Support: Due to the changes in the AST structure the existing Object model support needed several modifications. Consequently the way in which the assertions(port, enabling, and post) were evaluated had to be modified.

- 2. Simulation Event: The existing simulation event structure was augmented to have an attribute pointing to the causing event facilitating the tracing of history. This is helpful for later additions, especially in the Reasoning System. Consequently, various data structures had to be modified to manipulate the new attribute.

- 3. Query Handler: The simulation tool provides the user with a rollback option. In the previous design the rollback would remove all the events that were scheduled after the time of rollback including the output unconstrained events. Since these events are external to the system, the new design does not remove these events even if they are scheduled after the rollback time. Consequently, these events had to rescheduled.

- 4. Event Scheduler: The simulation tool is capable of handling only deterministic transitions, i.e. only one unconstrained transition going out from a single state. In the case study of Robotics Assembly given the later chapter, we encountered a scenario where we had more than one unconstrained transition going out from a single state. In order to solve this non-determinism we had to make few changes to the EventScheduler in order that it can handle the non-determinism.

- 5. LSL Library Support: The Simulation tool supports only the Set trait. In order to facilitate the design process, we added a few commonly used LSL traits like Stack, and Queue according to their definitions as part of the Browser

# Chapter 4

# Design and Implementation of the Modified Interpreter and Simulator

In this chapter we compare the new design of *Interpreter*, and the *Simulator* with their old designs to emphasise the significant improvements made according to the description given in the previous chapter. We also discuss the tools which were used to implement the *Interpreter*. The *Reasoning System* is built to work synchronously with the new system.

# 4.1 Class diagrams

The class diagrams of the old and new design of *Interpreter*, and the *Simulator* are drawn using OMT notation. There are major design changes to the *Interpreter* with regard to the design of the classes, and relationship between the classes. The old design of the *Interpreter* was more rigid, and complex with no scope for further improvements, which motivated us towards doing a more flexible design. We took this opportunity to implement the improvements of the *Interpreter* that are described in the previous chapter. There are only minor design changes for the *Simulator*, i.e. the designs differ in the way the classes are structured, and the relationship between them.

# 4.1.1 Interpreter

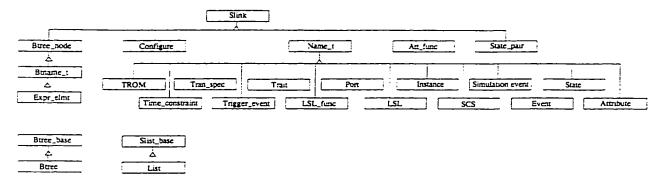

The class diagram for the old *Interpreter* consists of one class *Slink* which is inherited by the classes *Btree node*, *Configure*, *Name-t*, *Att-func*, and *State pair*. The class *Btree node* encapsulates the structure of logical expressions arising in transition specifications. A high-level class diagram of the old *Interpreter* is shown in Figure 11. A detailed class diagram of the old *Interpreter* is shown in Figure 12 and Figure 13.

Figure 11: Interpreter Class diagram (Old)

Figure 12: Interpreter Class diagram - Detailed (Old)

Figure 13: Interpreter Class diagram - Detailed (Old)

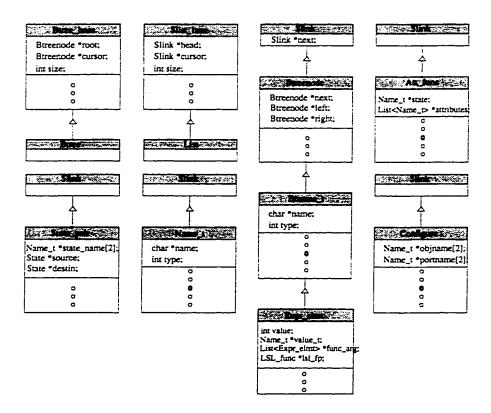

The high-level class diagrams of the new *Interpreter* are shown in Figure 14. A detailed class diagram of the new *Interpreter* is shown in Figure 15 and Figure 16. They reflect the true OO features inherent in the problem domain: an abstract syntax tree is an aggregation of *LSL trait*, *TROMclass*, *SCS*, and *SCSSimEv*. These are precisely the classes required to model the entities in the three tires, and the simulation events; the detailed class diagram for each class shows the internal structures and the interface. These diagrams explicitly convey the modularity in the design and the coupling between classes - modifying any one class will not affect any other class.

Figure 14: Interpreter Class diagram (New)

Figure 15: Interpreter Class diagram - SCS (New)

Figure 16: Interpreter Class diagram - TROMclass (New)

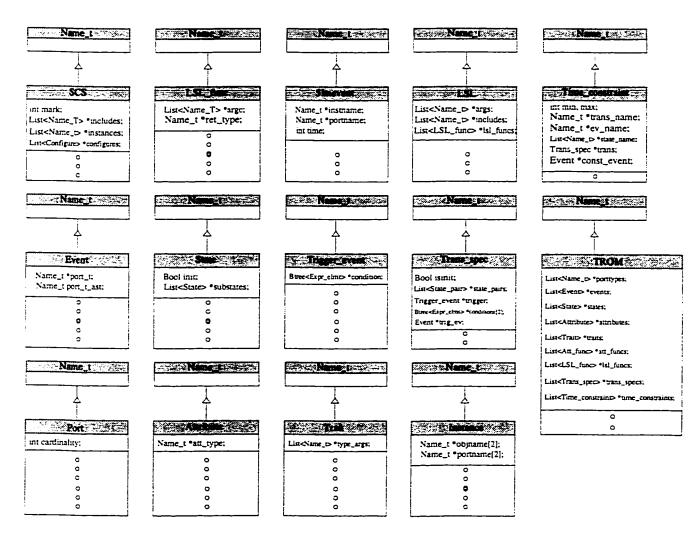

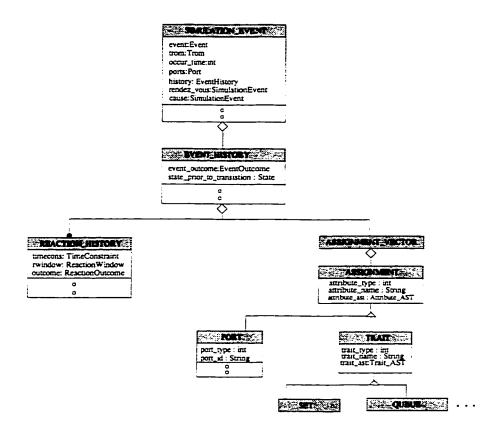

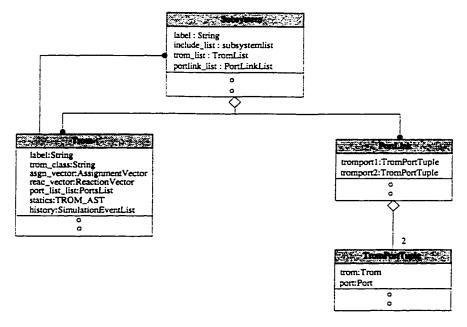

### 4.1.2 Simulator

Class diagram: Since there were no major changes in the design of Simulator, we only show the modified class diagrams. The modifications are based on the improvements suggested in the previous chapter. The detailed class diagrams are shown in Figure 17, Figure 18, and Figure 19.

Figure 17: Simulator Class diagram - TROM class diagram (New)

Figure 18: Simulator Class diagram - Simulation Event Object model (New)

Figure 19: Simulator Class diagram - Subsystem Object model (New)

# 4.2 Language of choice

We have chosen Java as the language of implementation due to the reasons mentioned in the previous chapter namely

- An Object oriented development environment,

- The need to support portability,

- Good graphical library support.

This choice smoothly integrates the different components of TROMLAB with GUI. We use JavaCC and JJTree, which are preprocessors for Java, to generate the parser(s) as part of the Interpreter.

#### 4.2.1 JavaCC

Java Compiler (JavaCC) is currently the most popular parser generator for use with Java applications. A parser generator is a tool that reads a grammar specification and converts it to a Java program that can recognise matches to the grammar. In addition to the parser generator itself, JavaCC provides other standard capabilities related to parser generation such as tree building, actions, and debugging.

JavaCC is a Java parser generator written in Java. It produces pure Java code. Both JavaCC and the parsers generated by JavaCC can be run on a variety of Java platforms. JavaCC generates top-down (recursive descent) parsers as opposed to bottom-up parsers generated by other tools, such as YACC. This allows the use of more general grammars (although left-recursion is disallowed). Top-down parsers have other advantages (besides allowing more general grammars):

- it is easier to debug.

- the ability to parse to any non-terminal in the grammar, and

- and the ability to pass values (attributes) both up and down the parse tree during parsing.

The lexical specifications such as regular expressions, strings, etc. and the grammar specifications (the BNF) are written together in the same file. It makes the grammars easier to read (since it is possible to use regular expressions inline in the grammar specification) and also easier to maintain.

### 4.2.2 JJTree

JJTree is a preprocessor for JavaCC that inserts parse tree building actions at various places in the JavaCC source. The output of JJTree is run through JavaCC to create the parser. By default, JJTree generates code to construct parse tree nodes for each nonterminal in the language. This behaviour can be modified so that some nonterminals do not have nodes generated, or so that a node is generated for a part of a production's expansion. Although JavaCC is a top-down parser, JJTree constructs the parse tree bottom up. To achieve this it uses a stack where it pushes nodes after they have been created. When it finds a parent for them, it pops the children from the stack and adds them to the parent, and finally pushes the new parent node

# 4.3 Implementation

We discuss the implementation of the parsers, the syntax for the specifications, and the interfaces to the other components of TROMLAB system.

# 4.3.1 Interpreter

The parsers, implemented in JavaCC and JJTree, are used to build the assertion trees. The other classes are implemented in Java. The input to the Interpreter is a textual formal specification file(s). The Interpreter parses the file and creates the internal representation of the AST (see Figure 10) as a result of syntax checking and on the fly semantic analysis. If the input specification is not syntactically correct, error messages are given, and AST is not created. Once the user has correctly composed the class specifications, and subsystem specification (which may be compiled independently) the overall semantic analysis for the fully specified system is done. Semantic errors at this stage indicate an incorrect or incomplete system specification. When an object which is not a correct instantiation of a correctly compiled class is referred to in the specification of a subsystem, the user might be referring to a class which was not specified (incompleteness) or the user might be incorrectly referring to an existing object (error). When the specifications are syntactically and semantically correct, the user may use the simulator to analyse its behaviour.

A brief description of the implementation of the four parsers is given below:

1. LSL trait parser: The LSL trait parser takes a LSL trait file as input and generates the corresponding objects for that file and adds them to the AST. In the same LSL trait file more than one LSL trait can be defined, and these LSL traits will be represented by different nodes in the LSL trait's list. If the user submits more than one LSL trait file for the same system, the resulting objects will be in the same list. An example LSL trait file is shown in the Figure 2 in the Chapter 2.

On the fly semantic checks performed on this file is as follows:

- (a) Trait names should not be duplicated in the *Includes* section.

- (b) A Trait cannot include itself.

- (c) No duplicate functions are allowed in the *Introduce* section (Note: two functions can have same name provided their signatures are different).

- (d) The return type and the parameter types of a function defined in *Introduce* should be defined either in the *Includes* section or in the signature part of the trait. (Note: Integer and Boolean type are assumed to be defined. Int or Integer refers to an integer type, and Boolean refers to a Boolean type.)

All these semantic checks are done independently of the other sections in the AST and are performed at parse time itself.

2. TROM class specification parser: The TROM class specification parser takes a TROM class specification file and generates the corresponding objects for that file, and adds them to the AST. In the same TROM class specification file there can be more than one TROM class specification defined, and these classes will be represented by different nodes in the TROM class list. If more than one TROM class specification file for the same system is submitted, the resulting objects will be in the same list. An example of TROM class specification is shown in the Figure 3, Figure 4, and Figure 5 in the Chapter 2.

The following semantic checks are performed while checking the syntactic correctness of TROM files:

(a) The port types cannot be duplicated.

- (b) The event names cannot be duplicated.

- (c) The port types used in the event section should be defined in the port section.

- (d) Only the input and output events defined in the event section can have ports associated with them.

- (e) There is only one initial state.

- (f) The state names cannot be duplicated.

- (g) A complex state can have only one entry state which is the initial state for that complex state.

- (h) The attribute names cannot be duplicated in the attribute section.

- (i) If the attribute is of port type then the port type has to be defined in the port section.

- (j) The trait names can not be duplicated in the Trait section.

- (k) The port types listed in the signature of the Traits have to be defined in the ports section.

- (l) The attributes listed in the signature of the Traits have to be defined in the attribute section.

- (m) The state names listed in the attribute-function section should be defined in the state section.

- (n) The attribute names listed in the attribute-function section should be defined in the attribute section.

- (o) The state names listed in the transition specification section should be defined in the state section.

- (p) The transition names cannot be duplicated.

- (q) The attribute names listed in the transition specification should be defined in the attribute section.

- (r) The event names listed in the transition specification should be defined in the event section.

- (s) The time constraint names cannot be duplicated.

- (t) The transition names listed in the time constraint should be defined in the transition specification section.

- (u) The event names listed in the time constraint should be defined in the event section.

- (v) The time interval defined in the time constraint should be valid, i.e. the upper bound should be greater than the lower bound.

- (w) The set of states listed in the time constraint should contain only the states that are defined in the states section.

- 3. SCS parser: The SCS parser takes an SCS file as input and generates the corresponding objects for that file, and adds them to the AST. In the same SCS file there can be more than one SCS defined, and these SCS will be represented by different nodes in the SCS list. If more than one SCS file for the same system is submitted, the resulting objects will be in the same list. An example of SCS is shown in the Figure 6 in the Chapter 2.

The following semantic checks are performed while syntax checking an SCS file:

- (a) SCS names listed in the Includes section cannot be duplicated.

- (b) TROM objects defined in the instantiate list cannot be duplicated.

- (c) All the port types listed in the configure section should be instantiated in the instantiate section of this or any of the included subsystem.

- 4. Initial Simulation event list Parser: The simulation event list parser accepts a simulation event list file as input and generates the corresponding objects for that file, and adds them to the AST. An example of simulation event list is as follows:

```

SEL: TCG

Near, t1, @C1, 3;

Near, t2, @C2, 5;

Near, t3, @C1, 7;

end

```

Figure 20: Simulation event list

Since the objects added to the AST have been generated independently, and are however dependent on each other, an overall semantic analysis has to be performed once the user is finished with the design. The overall semantic analysis checks for the following properties:

- Between LSL traits and TROM class specification the following dependencies must hold:

- 1. Every LSL trait used in a TROM class has to be defined.

- 2. The signature of every LSL trait function used in the assertion expressions of the transition specification section of a TROM class should match the signature defined in the corresponding LSL trait.

- 3. The return type of the LSL trait function used in the assertion expression of the transition specification of a TROM class should match the operands used in the expression.

- Between TROM class specification and SCS the following properties should hold:

- 1. Every TROM object defined in the *Instantiate* section of a SCS must be an instance of a TROM class in the *AST*.

- 2. Every TROM object defined in the *Instantiate* section of a SCS should have its ports associated to the port type defined in the TROM class.

- 3. Links can exist between two instantiated TROM objects, or between an instantiated TROM object and an open port of a subsystem included in SCS.

- 4. Every subsystem listed in the *Includes* section must have been compiled earlier.

- Between SCS and SCS the following properties hold:

- 1. The number of ports of a port type used for a TROM object should be less than or equal to the cardinality of that port type defined in the instantiate section. This has to be checked taking into consideration all the included subsystems in the Include section of SCS.

- 2. All the TROM objects listed in the configure section should be defined in the instantiate section. This has to be checked taking into consideration all the included subsystems in the Include section of SCS.

- 3. Port names of the same port type defined in the configure section cannot be duplicated. This has to be checked taking into consideration all the included subsystems in the Include section of SCS.

- 4. All the TROM objects defined in all the included SCS's cannot have duplicate names.

- 5. Only compatible ports can be linked.

- Between Simulation event list, SCS, and TROM class specification the following properties hold:

- 1. Every TROM object listed in the simulation event list should be defined in the SCS or in any one of the included SCS's of that SCS. (The name of the SCS appears in the Simulation event list)

- 2. For every TROM object listed in the simulation event list, the corresponding event name should be defined in the corresponding TROM class in the event section and this event should be of the type output and unconstrained.

- 3. For every TROM object listed in the simulation event list, the port name listed should be defined in the SCS or in any of the included SCS's of that SCS for that corresponding TROM object.

## 4.3.2 Simulator

The simulator was implemented based on the existing design using Java. Simulator makes use of the AST generated by the Interpreter and generates one of the possible scenarios for the given system and the initial simulation event list.

The simulation steps are as follows [Mut96]:

1. Instantiate TROM objects: Adds the dynamic information (assignment vector, and reaction vector) for each TROM object instantiated in the SCS to be simulated.

- 2. Instantiate simulation event list: Schedules unconstrained internal events from initial states. Schedules the initial simulation event and their corresponding rendezvous.

- 3. Handle the events: Traverses the simulation event list with respect to time and handles the events by evaluating the port, pre and post conditions and taking an action accordingly of firing or disabling the corresponding transition, and scheduling the resulting events.

- 4. Handle the history: Saves the state, assignment, and reaction vector prior to the transition.

- 5. If the system is in debugger mode, it asks the user after handling of each event if he wants to invoke the debugger.

- 6. Debugger: The debugger allows the user to perform different kind of queries and also allows to invoke the trace analyser.

- 7. Trace analyser: Trace analyser allows the user to query the static information of the different TROM objects in the subsystem and of the subsystem itself.

# 4.3.3 Interfacing with the simulator

Since the design of *Interpreter* was changed drastically from the previous version, there was a major change in the way *Simulator* interfaced with the *Interpreter*. We had to make sure that the *Simulator* could interface with the *Interpreter* to perform its task. Thus in the *Interpreter* we had to implement all the methods used to by the *Simulator*. We had to modify the simulator in certain aspects:

- 1. In the previous implementation of the *Simulator* the port names were generated automatically, but in the new version the port names are taken from the user in the *Configure* section. Thus the *Simulator* has to interface with the *Interpreter* in order to get this port name list.

- 2. Since the structure of assertion tree was changed in the *Interpreter*, the evaluation of these assertion tree in the *Simulator* had to be modified. Thus it lead to major modification in the Object Model support.

# Chapter 5

# Reasoning System: Requirements

Real time reactive systems are very complex. Any error in the design would lead to catastrophic consequences. We need to be able to debug and verify the design before the implementation. The *Simulator* is a very powerful tool, that helps the user to simulate his design. However this tool has some limitation. In simulating complex systems the history of the simulation becomes very big and very hard to manage and understand. The history of the simulation is seen only from one point of view, that is the *Simulation Event List* point of view. It does not allow the user to look at the history of particular events and particular TROM objects. The tool doesn't allow the user to modify the timing of events. This modification of the timing of the events may help the user in seeing different scenarios in a more controlled environment, not relying on the randomness of the simulation. It offers no tools to study the routing of static data structure and the study of possible timing conflicts.

The Reasoning System is a good compliment to the simulation tool. The simulation goes forward in time whereas a debugging tool that reasons about the behaviour of the system needs to go backward in time. The Simulator that we have described in the previous chapters goes forward in time while keeping a trace of the history. Our Reasoning System has three main roles:

• Debugging tool: This role is served by answering questions that give different points of views on the results of the simulation. These questions will allow the user to view the results of the simulation from the TROM object point of view, from the event point of view and from the Simulation Event List point of view. They will also allow the user to have a better understanding of what caused

certain events and transition to occur. The queries that will permit this are described the following sections of this chapter.

- Hypothetical queries: This set of queries will allow the user to have more control on the timing of the events. A detailed description of the hypothetical queries is given in the following sections of this chapter.

- Validity of the Specifications: The *Reasoning System* has to give the user a way to see the reachability of the states, and the correctness of the timing constraints. To do that the *Reasoning System* will provide a set of queries that will be described later in this chapter.

# 5.1 Reasoning System as a Debugging Tool

By answering the following set of queries we will give a clearer image of the history, from different points of views. These queries will help the user in his debugging process. These queries are:

- Why: This will tell the user why the system went from one state to another. This query will be invoked when the simulation is stopped in debugging mode. It will tell the user what are the events that caused the system to go from one state to the other. It will also give the reason behind the occurrence of these events. This query gives the user a perspective on the history from the point of view of states.

- When: This will give the user an easy way to check for the timing of certain events. It will also allow the user to see when a set of TROM objects were in a certain state, which would be almost impossible if we relied only on the Simulation Event List, given the large number of TROM objects and the complexity of the reactive systems. This set of queries will give the user a perspective on the simulation from the timing point of view. This query will be divided into six different sub-queries:

- 1. When was the system or the specified TROM object in a specific state?:

This query will be invoked when the simulation is stopped in debugging

- mode. The user will be able to get a list of time intervals during which the system or the TROM object was in a specific state.

- 2. When did the system or a specified TROM object go out of a specific state?: This query will be invoked when the simulation is stopped in debugging mode. This will allow the user to know at what times did his system or the TROM object gets out of a critical state.

- 3. When an event was fired?: This query will be invoked when the simulation is stopped in debugging mode. It will provide the user with a set of times when a particular event was fired.

- 4. When an event was disabled?: This query will be invoked when the simulation is stopped in debugging mode. It will provide the user with a set of times when a particular event was disabled. That is when the system went into a disabling state.

- 5. When an event was enabled?: This query will be invoked when the simulation is stopped in debugging mode. It will provide the user with a set of times when a particular event was enabled. That is the time when the event that caused this event to be enabled was fired.

- 6. When an event was scheduled?: This query will be invoked when the simulation is stopped in debugging mode. It will provide the user with a set of times when a particular event was scheduled to be fired or disabled later.

- Show the assignment vector at a particular time: This query will allow the user to see the values of the different attributes at specific times. Since the assignment vector changes dynamically the Simulator does not keep an image of this vector at all times. It would be almost impossible for the user to reconstruct an image of this vector relying on the Simulation Event List. This query allows the user to understand better the values of the attributes at certain critical times in the simulation.

- Show the reaction vector at a particular time: This query will allow the user to view the outstanding reactions of the reaction vector at a particular time. Since this vector could grow to be a very big data structure as time progresses, the simulator only keeps the necessary information, and the user would not be able to reconstruct this vector relying only on the Simulation Event List. This

query allows the user to understand better the outstanding reactions at certain critical times in the simulation.

- Does the system go into a specific state?: This will give the user the possibility to see if the system, or a set of objects in the system went into a state during a time interval. This would be very hard without this tool given the large number of TROM objects in a complex reactive system. This query allows the user to debug his design by showing that some objects were in some states when they were not supposed to.

- Does the system go into a specific state more than once?: If the user wants to see if there is a pattern in the behaviour of the system this query would allow him to see that behaviour on the system or on a set of objects in the System.

- Show the TROM status during a time interval: This query will allow the user to see the variation in a TROM object without taking into consideration other TROM objects in the system It allows the user to isolate and have a better understanding of the behaviour of a particular TROM object.

- Show the simulation event list of a particular TROM object: This query will allow the user to isolate the simulation event list of a particular TROM object from the very complex Simulation Event List of the system.

# 5.2 Reasoning Based on Hypothetical Queries

By answering the following set of queries we will give the user possible scenarios to see when the timing of certain events are modified. We will give the user the possibility to insert new events and see the effect they will have on the behaviour of the system. We will also allow the user to remove certain events and understand the effect that it has on the results of the simulation. Theses queries have to respect certain criteria that would prevent them from violating the requirement of the simulation. Theses criteria will be described in more details in Chapter 6.

• What if we insert an event?: This query will allow the user to interactively insert new events, thus allowing the study of new scenarios without having to modify the Original Simulation Event List, compiling it again and running the