# Formalization of Uniprocessor and Multiprocessor Scheduling of Real-Time Systems Using Supervisory Control of Discrete-Event Systems

Vasudevan Janarthanan

A Thesis

In

The Department

Of

Electrical & Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy at Concordia University Montréal, Québec, Canada

©Vasudevan Janarthanan, 2007

Library and Archives Canada

Branch

Published Heritage

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-30136-4 Our file Notre référence ISBN: 978-0-494-30136-4

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

## **Abstract**

Formalization of Uniprocessor and Multiprocessor Scheduling of Real-Time Systems Using Supervisory Control of Discrete-Event Systems

Vasudevan Janarthanan, Ph.D. Concordia University, 2007

The theory of supervisory control of discrete-event systems has been applied to real-time systems. The contribution of our proposed work lies in the development of a formal constructive method for controlling the preemptive execution of real-time tasks on both uniprocessor and multiprocessor systems. The set of all possible timed traces of the system is specified by a discrete timed automaton, where each transition is associated with an event occurrence or the passage of one unit of time. This approach allows a unified view of scheduling theory based on the timing analysis of models of real-time applications, meaning that the problem of determining schedulability and finding out a suitable scheduling algorithm are assumed to be intermingled issues, with the solution of one in turn is a solution to the other too.

First, a framework for designing universal schedulers for real-time tasks on uniprocessors based on Supervisory Control Theory (SCT) is presented. For this purpose, priorities are introduced in SCT and applied to the setting of discrete timed automata in order to develop a formal and unified framework for task scheduling on a single CPU. A universal scheduler nondeterministically selects a task for execution in such a way that all timing constraints are met in a minimally restrictive fashion, while it contains all feasible deterministic scheduling policies.

We then extend that framework by providing a formal constructive method for controlling the preemptive and migrative execution of hard real-time tasks while scheduling them on a set of uniform processors. The methodology relies on the idea that the model of the scheduled system can be obtained by successive and appropriate restrictions of controllable actions of a model representing the real-time application. In uniform multiprocessors, each processor is characterized by its own computing capacity, with the interpretation that a task that executes on a processor of computing capacity  $\mathbf{s}$  for  $\tau$  time units completes  $\mathbf{s}\tau$  units of execution.

Since we represented explicitly discrete time in our scheduler design, model sizes were considerably large. The complexity in the synthesis of a scheduler using supervisory control [62] stems from the fact that, with the synchronous product, the number of states of a composite Timed Discrete-Event System (TDES) increases exponentially with the number of real-time tasks. We have attempted to alleviate some of the state explosion problems we had faced while designing schedulers for real-time systems using supervisory control of discrete-event systems framework [39, 41], by providing an informal procedure to design schedulers with reduced state space.

# Acknowledgments

I was fortunate and privileged to have Dr. Peyman Gohari as my advisor. He shaped my path to research by guiding me through his extensive knowledge, and at the same time opened up doors so that I could gain from the expertise of others. He has shown extreme enthusiasm for my progress and supported me when I was struggling, and it was he who introduced me into the area of supervisory control, nurturing me along in the last three years. He has been extraordinarily patient and supportive, having been always available for discussion and responding speedily to research reports. I would like to take this opportunity to thank him for his continued encouragement and guidance throughout the course of my research.

I owe a lot of gratitude to my thesis committee for their advice and patient reading of my thesis. Dr.Anjali Agarwal, Dr.Rachida Dssouli and Dr.Olga Ormandjieva gave me insightful critical advice, both in overview and in detail, and it was always reassuring to hear from them that I was on the right track during my research progress in the last three years.

This work would not have been possible without the environment at Concordia's Electrical and Computer Engineering department, with stimulating top-notch research, and at the same time an atmosphere that I can hardly imagine friendlier. I am grateful to all my fellow colleagues in the research group for their valuable discussions during this research.

Finally, and most importantly, thanks to my parents and my wife, to whom I owe what I am, who encouraged and supported me all these years, and who accepted the hardships of being far away so that I could see this through.

Vasudevan Janarthanan

I dedicate this work to my loving Dad, Mom and Wife......

# Contents

|   | List | of Figures                                          | $\mathbf{x}^{i}$ |

|---|------|-----------------------------------------------------|------------------|

|   | List | of Tables                                           | xiv              |

| 1 | Intr | oduction                                            | 1                |

|   | 1.1  | Real-Time Systems                                   | 1                |

|   | 1.2  | Continuous And Discrete Time                        | 3                |

|   | 1.3  | Real-Time Scheduling                                | 4                |

|   | 1.4  | Discrete-Event Systems                              | 7                |

|   | 1.5  | Supervisory Control Of Discrete-Event Systems       | 8                |

|   | 1.6  | Supervisory Control Of Timed Discrete-Event Systems | 9                |

|   | 1.7  | Uniprocessor Scheduler Design                       | 11               |

|   | 1.8  | Multiprocessor Scheduler Design                     | 12               |

|   | 1.9  | Symbolic Scheduler Design                           | 13               |

|   | 1.10 | Contribution Of The Thesis                          | 14               |

|   | 1.11 | Organization Of The Thesis                          | 15               |

| 2 | Pre  | vious Work                                          | 17               |

| 3 | Unij | processor Scheduler Design                          | 22               |

|   | 3.1 Priority-Based Supervisory Control Of Discrete-Event Systems . |         |                                                   | 23 |

|---|--------------------------------------------------------------------|---------|---------------------------------------------------|----|

|   |                                                                    | 3.1.1   | Priority Relations                                | 23 |

|   |                                                                    | 3.1.2   | Theory Of Priority-Based Supervisory Control      | 24 |

|   |                                                                    | 3.1.3   | Computation of priority-based supervisory control | 27 |

|   | 3.2                                                                | Real-T  | Γime Systems And Specifications                   | 29 |

|   |                                                                    | 3.2.1   | Discrete Timed Automaton                          | 29 |

|   |                                                                    | 3.2.2   | General Task Model                                | 32 |

|   |                                                                    | 3.2.3   | Task Requirements                                 | 33 |

|   | 3.3                                                                | Exam    | ple                                               | 36 |

|   |                                                                    | 3.3.1   | Preemptive Scheduling                             | 38 |

|   |                                                                    | 3.3.2   | Nonpreemptive Scheduling                          | 42 |

|   | 3.4                                                                | Concl   | usion                                             | 43 |

| 4 | Mu                                                                 | ltiproc | essor Scheduler Design                            | 45 |

|   | 4.1                                                                | Types   | Of Multiprocessors                                | 46 |

|   | 4.2                                                                | Timin   | g Model                                           | 47 |

|   |                                                                    | 4.2.1   | Basic Task Model                                  | 52 |

|   |                                                                    | 4.2.2   | Task Requirements                                 | 53 |

|   | 4.3                                                                | Exam    | ple                                               | 56 |

|   | 4.4                                                                | Concl   | usion                                             | 60 |

| 5 | Mo                                                                 | dified  | Symbolic Scheduler Design                         | 61 |

|   | 5.1                                                                | Basic   | Definitions                                       | 62 |

|   |                                                                    | 5.1.1   | Symbolic Discrete Timed Automaton                 | 62 |

|   |                                                                    | 5.1.2   | Region Graph                                      | 63 |

|   |                                                                    | 5.1.3   | Modified Symbolic Graph                           | 65 |

|   |                                                                    | 5.1.4   | Simulation Graph                                  | 66 |

| Bibliography                 |     |                                                                                 | 90 |

|------------------------------|-----|---------------------------------------------------------------------------------|----|

|                              | 6.1 | Future Work                                                                     | 97 |

| 6 Conclusion and Future Work |     | 96                                                                              |    |

|                              | 5.6 | Conclusion                                                                      | 94 |

|                              | 5.5 | Modified Symbolic Scheduler Design for Preemptive Real-Time Tasks               | 86 |

|                              | 5.4 | Example                                                                         | 74 |

|                              | 5.3 | ${\it Modeling of Real-Time Systems \ Under \ Non-Preemptive \ Assumption} \ .$ | 71 |

|                              | 5.2 | Framework for Scheduler Design with Reduced State Space                         | 68 |

|                              |     | 5.1.5 Pre-Stable Condition                                                      | 67 |

# List of Figures

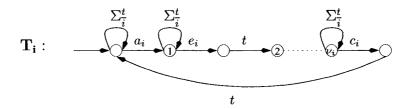

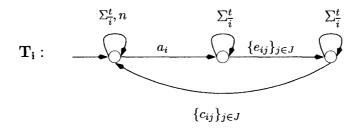

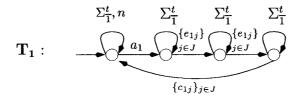

| 3.1  | General model of task $\mathbf{T_i}$ . State labels indicate which segment of task                     |    |  |

|------|--------------------------------------------------------------------------------------------------------|----|--|

|      | i is to be executed next                                                                               | 33 |  |

| 3.2  | Specification for making $\mathbf{T_i}$ periodic with period $\wp_i$ ( $\wp_i = 4$ )                   | 34 |  |

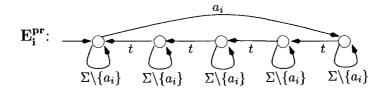

| 3.3  | Specification for making $\mathbf{T_i}$ nonpreemptible                                                 | 35 |  |

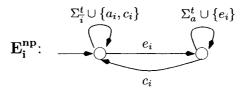

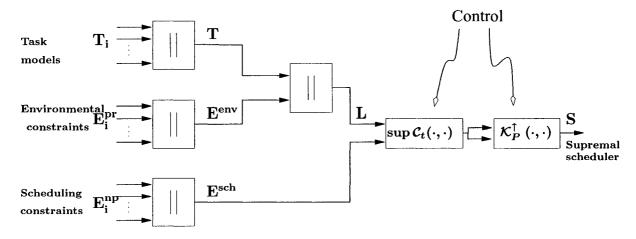

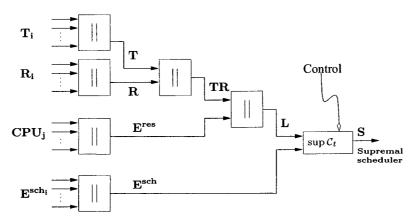

| 3.4  | Procedure of scheduler design                                                                          | 36 |  |

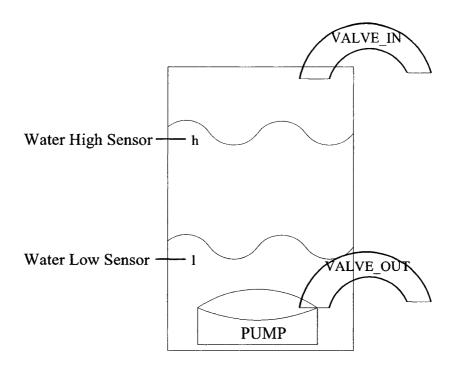

| 3.5  | Water controller                                                                                       | 37 |  |

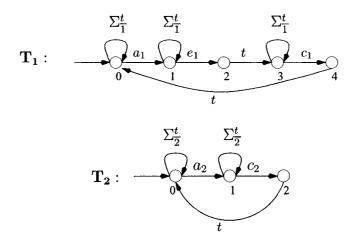

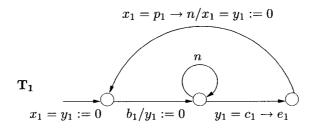

| 3.6  | Task automata                                                                                          | 39 |  |

| 3.7  | Automata for periodicity of tasks                                                                      | 39 |  |

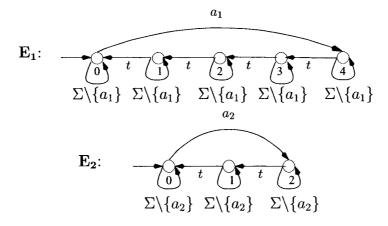

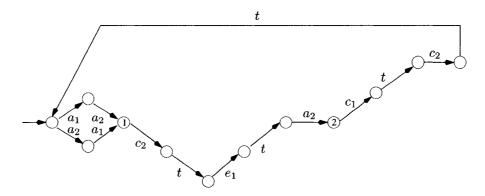

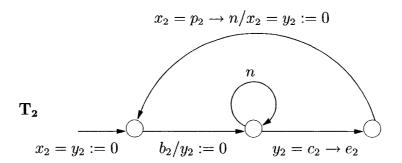

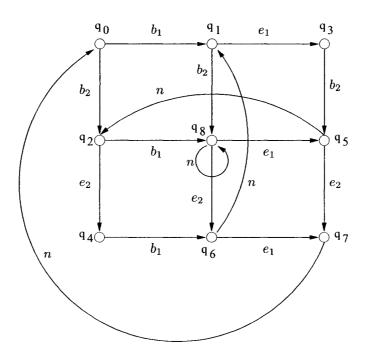

| 3.8  | The universal scheduler for $\mathbf{T_1}$ and $\mathbf{T_2}$ $(P = \emptyset, E^{sch} = \Sigma^*)$    | 40 |  |

| 3.9  | Prioritized task                                                                                       | 41 |  |

| 3.10 | The (supremal) scheduler for $\mathbf{T_1}$ and $\mathbf{T_2}$ , with $P = \{(e_1, c_2), (c_1, c_2)\}$ |    |  |

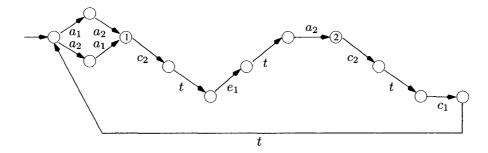

|      | and when preemption is allowed                                                                         | 42 |  |

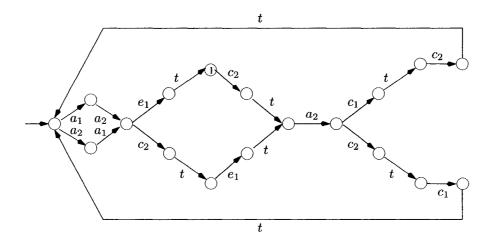

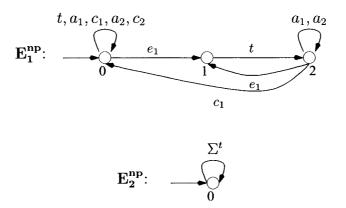

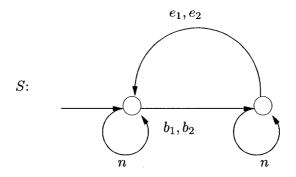

| 3.11 | Automata expressing the non-preemptiveness of tasks                                                    | 42 |  |

| 3.12 | The (supremal) scheduler for $\mathbf{T_1}$ and $\mathbf{T_2}$ when preemption is not al-              |    |  |

|      | lowed $(P = \emptyset)$                                                                                | 43 |  |

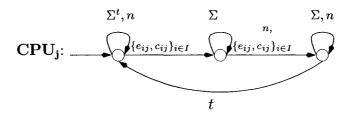

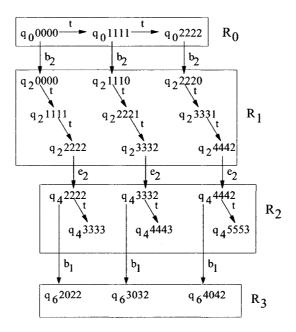

| 4.1  | Complete model of task $i$ ( $\nu_i=2$ )                                                               | 53 |  |

| 4.2  | Specification of $\mathbf{T_i}$ with release time of two time units                                    | 54 |  |

| 4.3  | Specification for a $CPU_j$ with $\mathbf{s} = 2$                                                      | 54 |  |

| 4.4  | Specification for $\mathbf{T_i}$ with deadline of four time units            | 55 |

|------|------------------------------------------------------------------------------|----|

| 4.5  | Procedure of scheduler design                                                | 55 |

| 4.6  | Task $T_1$ 's automaton                                                      | 56 |

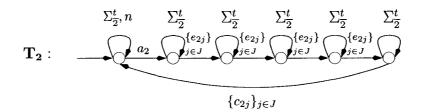

| 4.7  | Task $T_2$ 's automaton                                                      | 56 |

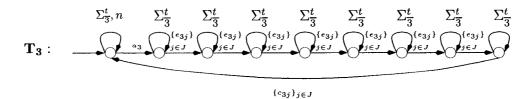

| 4.8  | Task $T_3$ 's automaton                                                      | 56 |

| 4.9  | Specification for the release time $(r_1)$ of $\mathbf{T_1}$                 | 57 |

| 4.10 | Specification for the release time $(r_2)$ of $\mathbf{T_2}$                 | 57 |

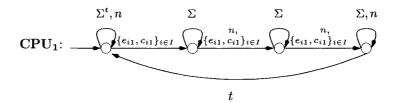

| 4.11 | Specification for $\mathbf{CPU_1}$ with $s=3.$                               | 58 |

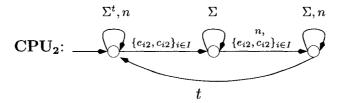

| 4.12 | Specification for $\mathbf{CPU_2}$ with $s=2.\ldots\ldots\ldots$             | 58 |

| 4.13 | Specification for deadline of $\mathbf{T_1}$                                 | 58 |

| 4.14 | Specification for deadline of $\mathbf{T_2}$                                 | 59 |

| 4.15 | Specification for deadline of $\mathbf{T_3}$                                 | 59 |

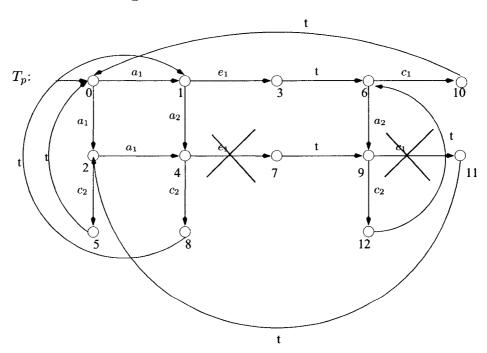

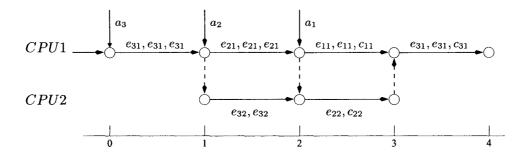

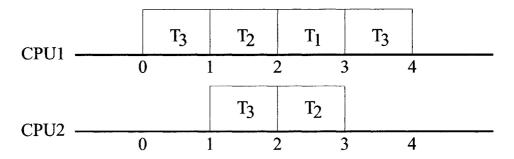

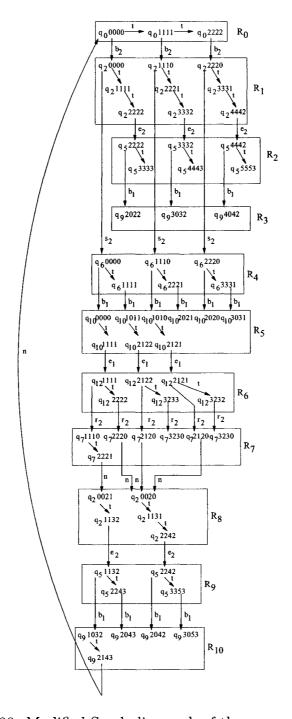

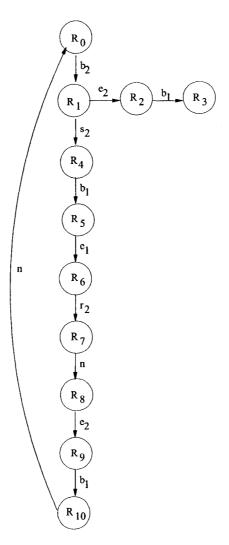

| 4.16 | Multiprocessor scheduler                                                     | 60 |

| 4.17 | The (supremal) scheduler for $\mathbf{T_1},\mathbf{T_2}$ and $\mathbf{T_3}.$ | 60 |

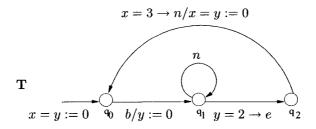

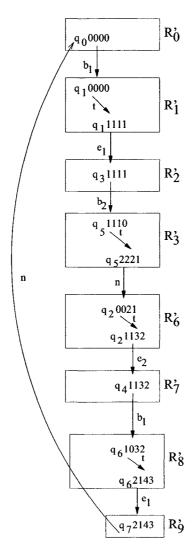

| 5.1  | Symbolic DTA of task T                                                       | 62 |

| 5.2  | Equivalent DTA of task T                                                     | 63 |

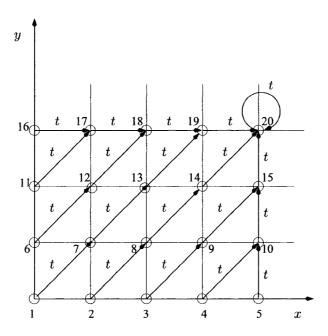

| 5.3  | Region graph of task T                                                       | 64 |

| 5.4  | Modified symbolic graph of task <b>T</b>                                     | 66 |

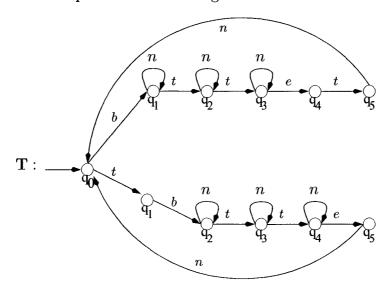

| 5.5  | Simulation graph of task T                                                   | 67 |

| 5.6  | Pre-stable modified symbolic graph of task <b>T</b>                          | 68 |

| 5.7  | Pre-stable simulation graph of task T                                        | 69 |

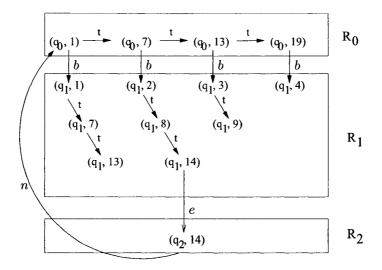

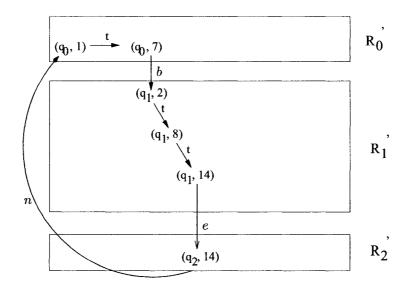

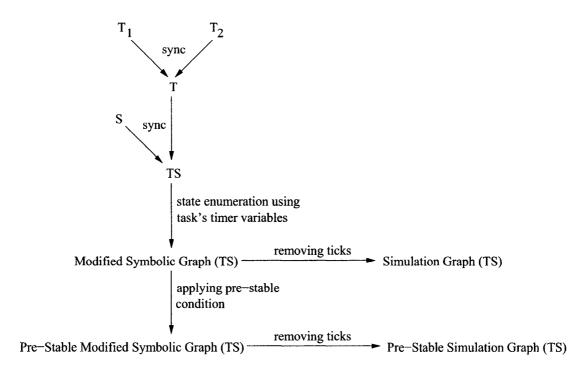

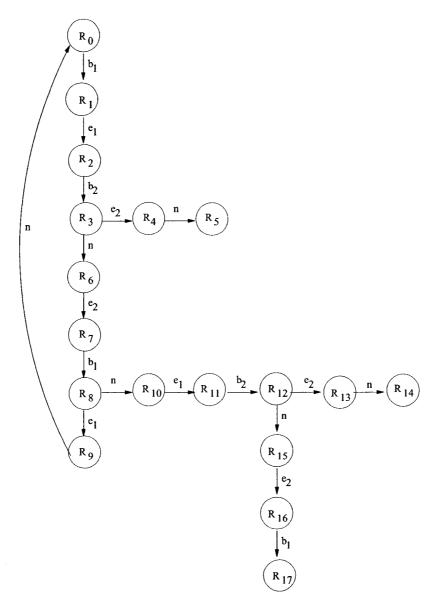

| 5.8  | Framework for reducing state space                                           | 70 |

| 5.9  | Task model of $\mathbf{T_1}$ .                                               | 71 |

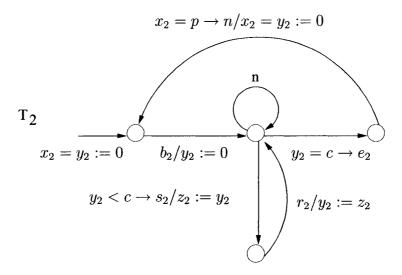

|      | Task model of $\mathbf{T_2}$ .                                               | 72 |

|      | Composed automaton of tasks T <sub>1</sub> and T <sub>2</sub>                | 72 |

| 5.12 | Specification for non-preemption of $\mathbf{T_1}$ and $\mathbf{T_2}$     | 73 |

|------|---------------------------------------------------------------------------|----|

| 5.13 | Automaton used to design schedulers with reduced state space              | 73 |

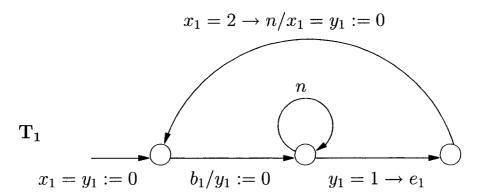

| 5.14 | Task model of $\mathbf{T}_1$                                              | 74 |

| 5.15 | Task model of $\mathbf{T_2}$                                              | 75 |

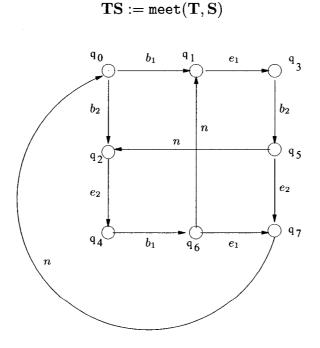

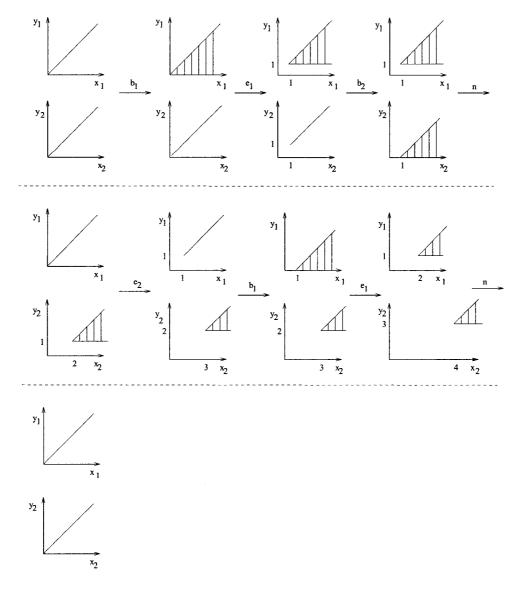

| 5.16 | Modified symbolic graph of the composed task taking event $b_1$ first     | 76 |

| 5.17 | Modified symbolic graph of the composed task taking event $b_2$ first     | 77 |

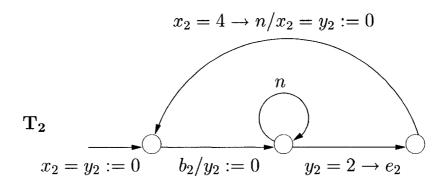

| 5.18 | Simulation graph of the composed tasks                                    | 78 |

| 5.19 | Pre-stable modified symbolic graph of the composed tasks ( $b_1$ is taken |    |

|      | at the initial state)                                                     | 79 |

| 5.20 | Pre-stable simulation graph of the composed tasks ( $b_1$ is taken at the |    |

|      | initial state).                                                           | 80 |

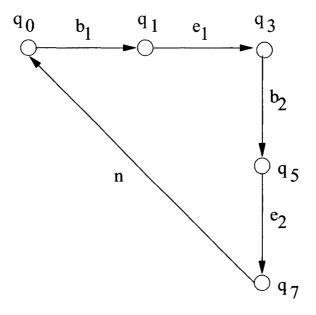

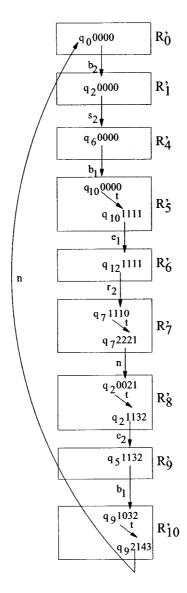

| 5.21 | Automaton of the scheduler                                                | 81 |

| 5.22 | Zonal representation of the scheduler automaton                           | 82 |

| 5.23 | Automaton of a non-feasible scheduler                                     | 84 |

| 5.24 | Zonal representation of a non-feasible scheduler automaton                | 85 |

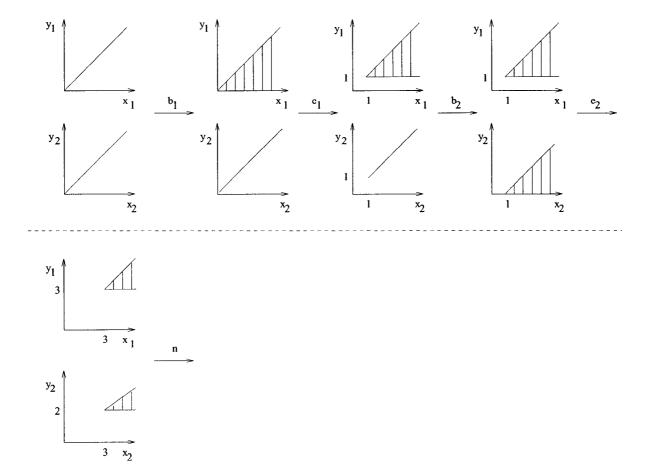

| 5.25 | Automaton of Task $\mathbf{T_1}$ under preemptive assumption              | 86 |

| 5.26 | Automaton of Task $\mathbf{T_2}$ under preemptive assumption              | 87 |

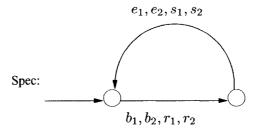

| 5.27 | Specification for preemptive tasks                                        | 87 |

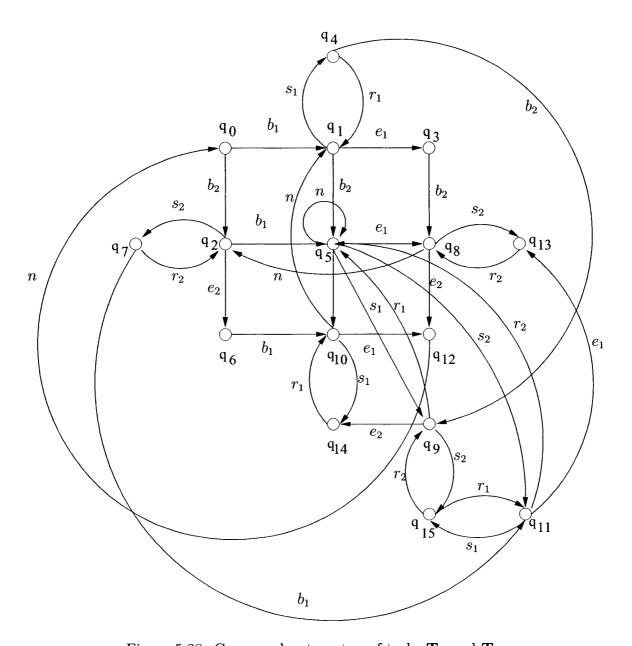

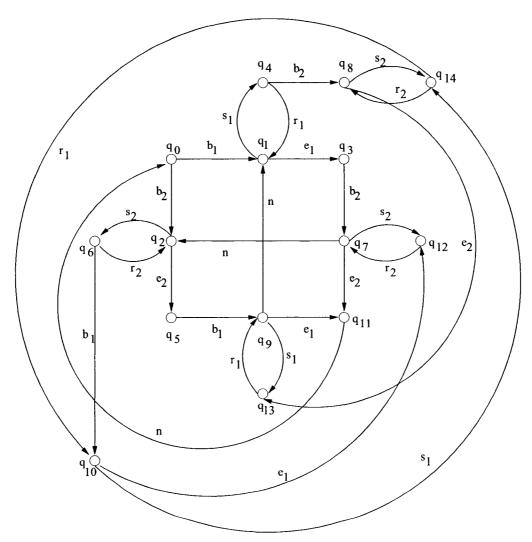

| 5.28 | Composed automaton of tasks $T_1$ and $T_2$                               | 88 |

| 5.29 | Automaton used to design schedulers with reduced state space              | 89 |

| 5.30 | Modified Symbolic graph of the composed tasks                             | 91 |

| 5.31 | Simulation graph of the composed tasks                                    | 92 |

| 5.32 | Pre-stable modified symbolic graph of the composed tasks                  | 93 |

| 5.33 | Pre-stable simulation graph of the composed tasks                         | 94 |

# List of Tables

| 3.1 | Event sets used for uniprocessor scheduler design.   | <br>33 |

|-----|------------------------------------------------------|--------|

| 4.1 | Event sets used for multiprocessor scheduler design. | <br>53 |

# Chapter 1

## Introduction

In this chapter an overview of real-time systems in terms of their various constraints and scheduling techniques are presented. Also a brief introduction to Discrete-Event Systems (DES), Timed Discrete-Event Systems (TDES) and Supervisory Control of TDES are provided. Then we introduce the design procedure for schedulers on uniprocessor and multiprocessor systems, followed by our methodology for solving the state space explosion problem, which we had encountered during the design procedure.

#### 1.1 Real-Time Systems

Real-time systems [55] are a form of control systems having constraints on the execution time of their tasks. These constraints are expressed as real-time constraints. A real-time constraint can be defined as a condition on the timing of enabling, firing, initiation and termination of system events. A real-time constraint can be expressed as a boolean condition on the values of clock variables, whose values increase with time. A real-time constraint of a task could be either the specification of its deadline or its complete execution.

A real-time system can be designed as a set of tasks that can be differentiated based on their timing requirements as hard real-time, soft real-time and non real-time tasks. A hard real-time task is defined as one whose timely and logically correct execution is considered crucial for the normal operation of the entire system. The deadline of a hard real-time task is referred to as hard deadline, because of the criticality of meeting the deadline. Hence it is obvious that missing a hard deadline can potentially result in a catastrophic system failure. On the other hand, a soft real-time task is characterized by an execution deadline which when met is desirable, but not critical for the functioning of the system. The deadline of a soft real-time task is referred to as soft deadline. Non real-time tasks are those having no real-time requirements at all.

Real-time tasks are further classified as periodic, aperiodic and sporadic tasks. Periodic tasks are those that occur, and will have to be executed, at regular intervals of time. Examples of applications where such tasks are commonly used are nuclear reactors and aircraft control systems, which are characterized by hard deadlines. On the other hand, aperiodic tasks are those whose executions are determined by the occurrence of internal or external events. For example, a task responding to a request from an external operator can be modeled by an aperiodic task. These tasks are usually characterized by soft deadlines. Finally, sporadic tasks are aperiodic tasks that are characterized by hard deadlines. For example, tasks dealing with emergency requests from a shuttle operator can be modeled by sporadic tasks.

The time domain in a real-time system can be either discrete or dense. Among the two, discrete-time allows for simpler analysis and design procedures since the real-time tasks could then be simply taking turns. A smallest measurable time unit is specified a priori in the discrete-time model. The clock used in our work includes an explicit tick transition, making time a global state variable. Each tick increments time by some predetermined time quantum. Also, in our model, events between the  $i^{th}$  and  $(i+1)^{th}$  clock ticks are assumed to occur at some unspecified time between times i and (i+1).

#### 1.2 Continuous And Discrete Time

In order to formalize the notion of time, two different varieties of time have been studied in the literature. One of them is the dense (continuous) modeling of time, wherein the time domain is equated with the set of nonnegative real numbers  $\mathbb{R}^+ \cup \{0\}$ . In this model, an event or a transition occurs at an arbitrary time point on the real scale. Whereas, the discrete modeling of time allows transitions to occur only at discrete time quantums. Here, the modeling of time is done using the set of nonnegative integer numbers  $\mathbb{N}$ . In [12, 36], the authors have done a comparative study on the relative merits of the two approaches.

If we compare the two timing models in terms of their expressiveness and their efficiency, then the dense time model is more expressive than the discrete time model. Further, while modeling delays that are arbitrarily small, it is beneficial to employ dense (continuous) timing model [12, 36]. Also, by using the dense modeling of time, there is no need to check if the granularity of the clock is suitable for modeling the various behaviors of the system; and in case of composing two dense-time systems, there is no need to check if the granularity of the two clocks match or not.

But for some classes of timed systems, using discrete time model helps in preserving certain properties. In [35, 36], the authors discuss timed transition systems, while showing that all qualitative, time-independent and some common quantitative properties such as time-bounded invariance and time-bounded response are preserved by discrete-time model. Also, they argue that if a property expressed in a certain timed

logic holds in the continuous-time model, a weaker, derived property is guaranteed to hold in the discrete time model.

However, in [16], the author shows that certain qualitative properties are not preserved if a discrete-time model is used instead of the continuous time model. In that paper, the author analyzes combinational circuits, wherein the timing constraints are expressed as bounded delays which are imposed on the output of each gate. For acyclic circuits, a discretization quantum is found such that the qualitative behavior is preserved. But in addition, there also exist certain cyclic circuits whose continuous time qualitative behavior is not preserved by any discretization.

In terms of efficiency, both discrete and continuous time models have their pros and cons. But according to [25], practical results for discrete-time models have been found to be better than the dense-time models. Discrete-time techniques allow efficient representation techniques from the untimed domain to be used, such as binary decision diagrams [27]. However, discrete-time techniques tend to be more sensitive to the size of the constants appearing in the model description, and large constants can result in state space explosion.

#### 1.3 Real-Time Scheduling

Real-time scheduling is defined as assigning the exact execution times for a set of real-time tasks such that all the temporal constraints are satisfied. In a real-time system, the purpose of the scheduling algorithm is to determine the sequence of execution of the real-time tasks, thereby ensuring their adherence to resource and timing constraints. While designing a real-time system, the choice of an appropriate scheduling algorithm or policy depends on factors like task synchronization methods, number of processors available in the system and the priorities of the tasks. In

addition, characteristics of tasks pertaining to a particular application may influence the choice of a scheduling algorithm. For example, real-time application tasks can be preemptable or non-preemptable. A preemptable task is one whose execution can be suspended by other tasks, and resumed later; whereas a non-preemptable task must run until it finishes its execution, without interruption. Thus, both preemptive and non-preemptive algorithms have been proposed in [48].

Scheduling may be time-driven or priority-driven. A time-driven scheduling algorithm determines the exact execution time of all tasks. A priority-driven scheduling algorithm assigns priorities to tasks and determines which task is to be executed at a particular moment. Depending on the type of priority assignments, scheduling algorithms can be classified as fixed priority, dynamic priority and mixed priority scheduling algorithms. When the priorities assigned to tasks are fixed and do not change between job executions, the algorithm is called fixed priority scheduling algorithm. When priorities change dynamically between job executions, the algorithm is called dynamic priority scheduling. When a subset of tasks is scheduled using fixed priority assignment and the rest using dynamic priority assignment, the algorithm is called mixed priority scheduling.

The scheduling of periodic tasks on a single processor was one of the first scheduling problems analyzed in real-time systems [48]. In that paper, two different approaches were proposed to solve this problem. The approaches were based on the assignment of either a fixed or a dynamic priority value to each real-time task. These two approaches in turn led to the emergence of a number of preemptive scheduling policies. Among them are Rate Monotonic (RM), Earliest Deadline First (EDF) and Least Slack Time First (LSTF) policies.

In the RM algorithm, a task is assigned a fixed priority value based on the condition that shorter the task period, higher the task priority. In [48], the authors show

that the RM policy is optimal among fixed priority policies, meaning that for a given set of tasks, the RM policy always produces a feasible schedule if any other algorithm which is based on fixed priorities can do so. In the EDF algorithm, a task is assigned a priority value dynamically based on the condition that earlier the deadline of a task, higher the priority assigned to that task. In the LSTF policy, a task gets its priority based on its slack time, which is defined as the difference between the amount of time (from the current time value) to the deadline of the task, and the amount of time that the task requires to complete its computation. In the LSTF policy, smaller the slack time of a task, higher the priority value assigned to that task.

For the purpose of scheduling aperiodic tasks, five different policies were proposed in [46]. According to the first policy, aperiodic tasks are allowed to do their computations and thereby get scheduled only when no periodic tasks are active. In the second policy, a fixed priority periodic process is formed in order to serve the aperiodic task requests. This method is sometimes called polling. While this policy is cyclic, aperiodic tasks are bursty in nature. This leads to a huge incompatibility problem.

According to [46], the third and fourth policies are Priority Exchange (PE) and Deferrable Server (DS) policies. In both policies, a high priority periodic server is used to handle aperiodic task requests. The server preserves the execution time allocated to it if no aperiodic task requests are pending. This in turn improves the responsiveness of aperiodic tasks. The only difference between the two policies is in the way they manage the high priority of their periodic servers. In the PE policy, the server exchanges its priority with that of the pending highest priority periodic task if no aperiodic task requests occur at the beginning of the server period. Whereas in the DS policy, the server maintains its priority for the duration of its entire period. Therefore, aperiodic task requests can be handled at the servers high priority, provided that the servers execution time for the current period has not been exhausted.

The fifth policy that has been proposed in [46] is the Sporadic Server (SS) policy, which has been designed to handle the scheduling of aperiodic soft real-time tasks. This policy is also based on the creation of a periodic server of aperiodic requests, but the difference is in the lower implementation complexity of this policy compared to that of PE and DS policies.

#### 1.4 Discrete-Event Systems

A discrete-event system (DES) is a dynamic system that evolves with the occurrence of events, such as the arrival of a job or the completion of a task. Because of the complex dynamics resulting from the various interactions between such events over time, modeling, design, and optimization of DES can be challenging problems. At the same time, the study of such systems has become increasingly important in recent times because of modern technological advances and wide use of computers in control applications. Such systems normally have discrete quantities that must be controlled, for example, communication networks. In a logical DES, the system is characterized by a set of states and the transitions (triggered by events) among these states. The behavior of the system is thus described by sequences of events. The occurrence of an event, caused by some unmodelled mechanism internal to the system, moves the system to a new state.

Discrete-event systems have been studied by researchers from various fields for the last couple of decades. During that time, a number of models have been proposed and analyzed with respect to the modeling, analysis and control of DES. These models can be classified as untimed DES models and timed DES models. In the untimed DES model, only the logical behavior of the system is considered. This means that the sequence of states visited is of concern; for instance, whether or not the system

will enter a particular state, but we do not care when the system enters that state or how long the system remains there. In a timed model [31], both logical behavior and timing information are considered. That is, we are concerned not only with the problem of whether or not the system will enter a particular state, but also with when the system enters that state and how long the system will remain there.

#### 1.5 Supervisory Control Of Discrete-Event Systems

A discrete-event system, which is considered as a plant, is controlled by a supervisor that observes the events that occur in the plant. Each time an event is observed, the supervisor presents the plant with a set of events to be *disabled*. The supervisor, while doing that, tries to keep the plant away from *forbidden* states and prevent undesirable event sequences from occurring. A common objective of DES designers is to compute supervisors that ensure that the controlled behavior is within a specified *legal* behavior.

Peter J. Ramadge and W. Murray Wonham [54] devised a control theoretic formalism that facilitated the study of DES systems. They modeled such systems as state machines that permit, from an initial state, a set of event sequences or strings to occur. The set of such strings forms a language that contains every possible event sequence that can occur in the DES. When a supervisor disables events in the plant, the resulting behavior is another language (i.e., set of event sequences) called the closed-loop language. In order to make sure that the controlled behavior of the plant is within a specified legal behavior, we specify the legal behavior as a legal language that contains all allowable event sequences. The objective of the supervisor is to ensure that every event sequence possible in the controlled system is in the legal language.

Formally, when the plant and specification are represented by languages L and E, respectively, we say the system or the plant satisfies the specification if  $L \subseteq E$ , that is, if every event sequence generated by the plant is acceptable by the specification. When this is not the case, the objective of supervisory control is to design a supervisor S that restricts the behavior of the plant in such a way that the supervised system, whose behavior we denote by K, satisfies the specification, i.e.  $K \subseteq E$ . An important issue in supervisory control is to identify those sublanguages K of a given language E that can be the behavior of the supervised plant under some supervisory control. A supervisor is called *optimal* if it restricts the behavior of the plant to the supremal controllable sublanguage of the specification language. The supremal controllable sublanguage is computed in time polynomial in the state sizes of plant and specification when they are modeled by finite automata.

# 1.6 Supervisory Control Of Timed Discrete-Event Systems

In a timed discrete-event system (TDES), the behavior of the system is influenced in addition by the temporal characteristics of event sequences. As a matter of fact, in a TDES, the state transition could be triggered either by some unmodelled mechanism acting on the system, or by the passage of time. Supervisory control of a TDES [47], [51] in essence means timely disablement or enforcement of certain events in the transition structure of the TDES such that its behavior meets certain specifications. A supervisor which prevents events from occurring only when absolutely necessary is described as minimally restrictive. The minimally restrictive behavior of a supervisor is expressed in a so-called supremal controllable sublanguage. The work reported here

adopts the framework for supervisory control of TDES originally proposed in [26]. This section summarizes the key concepts essential to the subsequent developments.

A TDES can be expressed as a five-tuple  $\mathbf{G} := (Q, \Sigma, \delta, q_0, Q_m)$ , where Q is a set of states,  $\Sigma$  is a finite set of events, including a special event denoting a tick of the global digital clock, the partial function  $\delta: Q \times \Sigma \to Q$  is a transition function which determines the new state of the system after the occurrence of an event,  $q_0$  is the initial state of the system, and  $Q_m$  is a set of marker states which can be interpreted as the completion of certain tasks of the system. Let  $\Sigma^*$  denote the set which contains, in addition to an empty string, all possible finite sequences over  $\Sigma$ . A state  $q \in Q$  is reachable if there is a string  $s \in \Sigma^*$  such that  $\delta(q_0, s) = q$ . A state  $q \in Q$  is coreachable if there is a string  $s \in \Sigma^*$  such that  $\delta(q_0, s) \in Q_m$ . A TDES is trim if all its states are reachable and coreachable.

A TDES can be obtained from an Activity Transition Graph (ATG). An ATG is an automaton in which each event  $\alpha$  is defined with two time bounds, i.e.,  $(\alpha, l_{\alpha}, u_{\alpha})$ , where  $l_{\alpha} \in T$  and  $u_{\alpha} \in T$  are the lower and upper time bounds, respectively. The interpretation for such a definition is that  $\alpha$  may occur after  $l_{\alpha}$  ticks, and must occur at the latest after  $u_{\alpha}$  ticks. An event is called *prospective* if  $0 \leq l_{\alpha} \leq u_{\alpha} < \infty$ , and remote if  $0 \leq l_{\alpha} < u_{\alpha} = \infty$ . Each event is thus associated with a timer interval between 0 and the event's upper time bound, i.e.,  $T_{\sigma} = [0, u_{\sigma}]$  for event  $\sigma$  (if  $\sigma$  is prospective), or the event's lower time bound, i.e.,  $T_{\sigma} = [0, l_{\sigma}]$  for event  $\sigma$  (if  $\sigma$  is remote).

The notion of supervisory control of a TDES is based on the concept of controllability. Controllability is defined in the context that the set of events in a TDES is partitioned into a set of controllable events  $\Sigma_c$  and a set of uncontrollable events  $\Sigma_u$ . An event is controllable if it can be prevented from occurring at a specific point in a logical event sequence or in time, and is uncontrollable otherwise. In a hard real-time system, an event must occur at the latest at its deadline. Supervision of a TDES then must include a mechanism for forcing certain events to occur before a specific time instant. For this reason, an additional type of events, called forcible events, is defined to describe events that can preempt a tick of the global clock. In this work, our concern is on tasks having a finite hard deadline. Therefore, all execution events considered are forcible unless stated otherwise. A supervisor of a TDES G can be considered as an automaton V that monitors the states of G, and enables, disables or forces certain events in G when necessary so as to influence the behavior of G. The readers are referred to [26] and [62] for a complete exposition of the theory of supervisory control of TDES.

#### 1.7 Uniprocessor Scheduler Design

Any real-time application consists of a set of tasks that interact with each other, and the tasks' executions are subject to various temporal constraints such as completion times, deadlines, periods, resource sharing and synchronization delays. The crucial aspect of real-time scheduling is to make sure that these tasks satisfy their temporal constraints and that the overall system performs correctly according to its specification. Given this fact, we propose a framework for designing such schedulers for hard real-time systems upon uniprocessors based on Supervisory Control Theory (SCT) for timed discrete-event systems.

In order to design a scheduler, we first model the execution of a set of tasks as a TDES and then compute the supremal controllable sublanguage of timing constraints with respect to task TDES to find the desired behaviour of the system. For ensuring tasks' schedulability, we simply check the supremal controllable sublanguage for emptiness. Nonemptiness implies that a *legal* and controllable execution sequence of

all tasks exists such that all scheduling requirements are met.

The approach followed in this work to design a scheduler is independent of a priori fixed scheduling policies. That is, the scheduler need not be constrained to follow a predefined scheduling policy but may adopt its decisions based on the behavior of the environment and the property to be satisfied, as is the case with the controller synthesis of [26]. The method for designing schedulers is based on successive restriction of the system to be scheduled by the use of constraints derived from scheduling requirements.

As in [6, 49, 56], this approach allows a unified view of scheduling theory based on the timing analysis of models of real-time applications. One of the main contributions of this work is the synthesis of a *universal* scheduler, which contains all feasible deterministic scheduling policies. A universal scheduler nondeterministically selects a task for execution in such a way that all timing constraints are met in a minimally restrictive fashion.

#### 1.8 Multiprocessor Scheduler Design

The problem of scheduling hard real-time systems upon multiprocessor platforms has been extensively dealt with in [18], [19], [20], [21]. However, no formal treatment has been provided in these works. A formal semantics must be provided so that the behavior of the scheduler (read supervisor) and the meaning of the specifications are clearly defined. For the above-mentioned reasons, we have utilized the theory of supervisory control of TDES to formalize and realize the scheduler design procedure for real-time systems. We synthesize schedulers using the proof by construction approach, wherein we demonstrate the existence of a scheduler capable of scheduling tasks on multiple CPUs by providing a method for constructing such a scheduler.

We discuss the scheduling procedure of hard real-time tasks on uniform multiprocessor [18, 19] platforms based on the assumptions that task preemption and interprocessor migration are permitted, while intra-task parallelism is forbidden (i.e., at any instant in time each task may be executing on at most one processor). In uniform multiprocessors, each processor is characterized by its own computing capacity, with the interpretation that a task that executes on a processor of computing capacity s for  $\tau$  time units completes  $s\tau$  units of execution. The scheduler design procedure for hard real-time tasks on uniform multiprocessors is similar to the one followed in uniprocessor platform.

#### 1.9 Symbolic Scheduler Design

In [39, 41], we had shown that supervisory control theory (SCT) of timed discreteevent systems could be applied to the scheduling of hard real-time systems. In particular, we had presented a formal framework for the synthesis of real-time schedulers on uniprocessor systems using priority-based supervisory control of timed discreteevent systems. The execution of a set of tasks was modeled as a Discrete Timed Automaton (DTA). Then the supremal controllable sublanguage [26, 62] of timing constraints with respect to task DTA subject to a priority relation was computed to find all executions in which no deadline was missed. We had also provided a method for designing schedulers on uniform multiprocessor systems based on SCT [40, 42].

Since we represented discrete time explicitly, model size for each task is considerably large and proportional to its period. The complexity in the synthesis of a scheduler using supervisory control [62] stems from the fact that, with the synchronous product, the number of states of a composite TDES increases exponentially with the number of real-time tasks. As far as complexity in both time and space is concerned,

the procedure TDES3 = sync(TDES1, TDES2), which computes the synchronous product of two TDES, has complexity proportional to the product of the state sizes of the two machines. Theoretically, the number of states of the synchronous product of two TDES is less than or equal to the product of their number of states. But in reality it is often much less than their product for a nontrivial system. Therefore, we often need to allocate much more space than is actually required to store the result.

One approach to confine this "state explosion problem" relies on the *symbolic* representation [13], [28], [38], [50] of sets of states, and computes the set that satisfies a formula as a fixpoint of a functional on state predicates. In our model, the formula is a guard for the transition from one state to the next. We have presented an informal idea to address state space explosion in scheduler synthesis for real-time tasks on uniprocessor systems using symbolic methods [24]. The scheduler thus designed is a feasible one for a given set of real-time tasks, and also smaller than the ones designed with any other known mechanism.

#### 1.10 Contribution Of The Thesis

1. In this thesis, we have utilized the concept of supervisory control theory (SCT) of discrete-event systems in order to formalize the process of scheduling hard real-time tasks on single processor platforms. For this purpose, we have provided a formal framework which helps in synthesizing real-time schedulers on single processor systems using priority-based supervisory control of timed discrete-event systems. We name such synthesized schedulers universal since they contain all feasible deterministic scheduling policies. In other words, a universal scheduler nondeterministically selects a task for execution in such a way that all timing constraints are met in a minimally restrictive fashion.

- 2. We have then extended our formalization technique to multiple processor systems by presenting a framework for designing schedulers for hard real-time systems upon *uniform* multiprocessors based on Supervisory Control Theory (SCT) for timed discrete-event systems. Our contribution in this respect has been the development of a formal constructive method for controlling the preemptive and migrative execution of real-time tasks on a set of uniform processors.

- 3. As we had considered discrete time models in our scheduler design, the state sizes were substantially large, and increased exponentially with the number of real-time tasks. In order to reduce the state space explosion problem in our models, we have utilized a modified form of symbolic modeling methodology [24], along with the pre-stable algorithm proposed in [24], for reducing state space while designing schedulers for real-time tasks on uniprocessor systems. The main contribution here has been the development of an informal procedure for uniprocessor scheduler design with reduced state space for both non-preemptive and preemptive real-time tasks.

#### 1.11 Organization Of The Thesis

The rest of the thesis is organized as follows. Chapter 2 delves in detail into some of the previous work related to our thesis that has been found in the literature. In Chapter 3, we introduce the theory of priority-based supervisory control of discrete-event systems, and propose a method for constructing a universal scheduler. The chapter also provides an example illustrating in depth the procedure followed in designing a scheduler for hard real-time tasks under various temporal constraints on a single processor system. Chapter 4 illustrates various multiprocessor set ups, and looks into specific reasons for considering uniform multiprocessors in our models. Further, it

presents a formal framework for scheduling preemptive and migrative hard real-time tasks on uniform multiprocessors, followed by an example to illustrate the design procedure. In Chapter 5, we provide the framework for scheduler design with reduced state space using modified symbolic technique. The framework is supplemented by an exhaustive example that clearly illustrates the procedure followed in designing a scheduler for non-preemptive real-time tasks with reduced state space. This chapter also explains the scheduler design procedure under preemptive conditions. Finally in Chapter 6, we conclude the thesis with a brief note on some of the future prospectives of our work.

## Chapter 2

### **Previous Work**

Controller synthesis has been studied extensively, both for discrete-time and densetime systems. One of the oldest discrete-event frameworks is the one of supervisory control of discrete-event systems [54]. Within the control community, Ramadge and Wonham [54] have built an extensive automata-theoretic framework for defining and solving control synthesis problems for discrete-event systems. In the paradigm of standard supervisory control theory, the authors have formulated the supervisory control problem by two languages that correspond to minimal acceptable behavior and legal behavior, respectively. In this formulation, both general and nonblocking solutions are well discussed.

Various formalisms have been developed to model timed discrete-event systems, including [8] and [26]. Work in [26] corresponds to discrete-time using a single system timer as opposed to [8] where the dense-time model includes several asynchronous clocks and is more expressive than other formalisms, allowing composition of timed processes and independent timing conditions for each system component. Here, we are concerned with timed automata as defined in [26].

The idea of applying synthesis to timed automata was first explored in [60]. Here

the methods of Ramadge and Wonham [54] are adapted to construct a supervisor for a dense real-time discrete-event system modeled by a timed automaton using untiming procedures. The control problem is tackled by completely discretizing the timed automaton into a finite state automaton and then the discrete synthesis problem is solved, which is somewhat similar to what we have proposed in our work.

An algorithm for safety controller synthesis for timed automata, based on operation on zones, was first reported in [49] and later in [13], where an example of a simple scheduler was given. In these and other works on treating scheduling problems as synthesis problems for timed automata, such as [4], the emphasis has been on existence properties, such as the existence of a feasible schedule in the presence of an uncontrolled adversary. The approach followed in our work for the construction of a scheduler is somewhat similar to [4, 5, 6, 14, 49, 56], but time in our work is discrete and it is explicitly represented, as opposed to dense-time which is often implicitly represented in the aforementioned references. In implicit representation of time, a set of inequalities over timer variables are used to define conditions on the firing of transitions (known as guards), as well as to specify timing requirements on the system behavior. The method for designing schedulers is based on successive restriction of the system to be scheduled by the use of constraints defined from the scheduling requirements.

Ostroff and Wonham were among the pioneers in the modeling and analysis of real-time discrete-event systems. In [52, 53], the authors had presented a framework/procedure for supervisory control of possibly infinite state real-time discrete-event systems using timed transition models (TTMs) and real-time temporal logic (RTTL). TTM has been used to represent the processes of plants and controllers, while RTTL has been used as the assertion language for specifying the legal plant behaviour, and it is shown that the controller indeed satisfies the required specification.

In [2], the synthesis algorithm computes iteratively, from a constraint K characterizing scheduling requirements, the maximal control invariant K':  $K' \Rightarrow K$ . The formula K' denotes the set of states from which K is guaranteed. The behavior of the scheduled system is obtained by restricting the controllable actions of the processes so as to respect the control invariant K'. As in [4, 5, 6, 14, 49, 56], our approach allows a unified view of scheduling theory based on the timing analysis of models of real-time applications.

The problem of scheduling the non-preemptive execution of a set of periodic tasks with hard deadlines on a single processor is considered in [29, 30]. For this purpose, the authors have used the theory of supervisory control of discrete-event systems [54]. It has also been shown there that the computation of the supremal controllable sublanguage with respect to a finite timed discrete-event system can be completed in polynomial time. The present work is also based on the unified approach, i.e., schedulability check and finding a scheduling algorithm are considered as one problem. But our proposed approach not only schedules non-preemptive tasks but also preemptive ones as well.

In [43, 44, 45], real-time behavior is represented using timed automaton which uses a dense model of time. The control is achieved by prioritized synchronous composition of a plant and a supervisor timed automaton. The notion of prioritized synchronization for the untimed systems has been extended to the real-time setting. The authors have also shown that the prioritized synchronous composition is associative and under certain mild conditions, which hold in the supervisory control setting, can be reduced to the strict synchronous composition by using a technique known as augmentation.

A methodology for treating the problem of scheduling partially-ordered tasks (task graph) on parallel machines has been considered in [1]. The authors have shown how

one can schedule tasks on a limited number of identical machines, while respecting some precedence constraints. In the framework, the scheduling problem admits a state-space representation, and an optimal schedule corresponds to a shortest path in the timed automaton. This work shows how formal state-based models can be used to express parallel scheduling problems and support efficient algorithms for solving such problems.

The problem of scheduling hard real-time systems upon multiprocessor platforms has been extensively dealt with in [18, 19, 20, 21, 32, 33, 34, 58]. It has been shown there that earliest deadline first remains a predictable and resource-efficient algorithm to use in multiprocessor systems. Also, through the results in their work, the authors conclude that scheduling upon multiprocessor platforms is not an obvious extension of one's knowledge concerning the uniprocessor case, but a lot more than that. But no formal treatment has been provided in these works, which is what we seek in our work.

Our approach to confine the *state explosion* problem, which we faced while designing schedulers for uniprocessor and multiprocessor systems, relies on the *symbolic* representation of sets of states, which in essence computes the set that satisfies a formula as a fixpoint of a functional on state predicates. In our model, the formula is a guard for the transition from one state to the next. In [38], the authors illustrate the working of a symbolic model checking algorithm that works on a quotient of the region graph that depends on the formula being checked. They have shown how a symbolic fixpoint approach can be used to test if a guarded-command real-time task is non-zeno and, if not, how it can be converted into an equivalent non-zeno task. But this algorithm fails to terminate if no such quotient exists. Also, this algorithm requires that the explicit representation of discrete structure of the automaton be constructed a priori.

In [17], the author has introduced an approximation scheme that further reduces the complexity related to timing. The work in that paper is based on the observation that not all the timing information in the description of a timed system is usually needed to guarantee the satisfaction of a given property. This approximation scheme has been used in the model-checker RT-Cospan [9]. In [9], the underlying untimed description of the system is composed with an automaton representing the time bounds, and only the bounds that are necessary to verify the given property are introduced in the composition.

In [37], the authors have employed on-the-fly and space-efficient model-checking methods to solve the state explosion problem. Using the first method on a real-time program, they explore only the regions needed for checking the satisfaction of a specification. The second method is used to store only necessary and minimal information in the memory. But the main drawback in [37] is that in the worst case situation, the on-the-fly method explores the entire region graph.

The authors in [24] have proposed an algorithm combining the symbolic and onthe-fly approaches. Their algorithm performs an on-the-fly exploration of the symbolic graph. The authors name the resulting graph as *simulation* graph, and they show in their paper that simulation graphs are much smaller than region graphs. They also perform model-checking for a temporal logic formula using simulation graph in [24]. We have incorporated the algorithm proposed in [24] in our work for the purpose of designing schedulers for real-time tasks on uniprocessor systems rather than for model-checking.

# Chapter 3

# Uniprocessor Scheduler Design

In this chapter we formalize real-time task scheduling by applying an extension of Supervisory Control Theory (SCT) of discrete-event systems to real-time models. The set of all possible timed traces of the system is specified by a discrete timed automaton, where each transition is associated with an event occurrence or the passage of one unit of time. We introduce priorities to SCT, and apply them to the setting of discrete timed automata in order to develop a formal and unified framework for task scheduling on a single CPU.

The chapter is organized as follows. Section 3.1 introduces the theory of priority-based supervisory control of DES, which is ultimately used to synthesize schedulers. Section 3.2 sets up a framework for modeling real-time systems and specifications based on a timed automata called Discrete Timed Automata (DTA), and proposes a method for constructing an *universal* scheduler. Section 3.3 provides a comprehensive example illustrating in detail the procedure followed in designing a scheduler under the various task requirements of Section 3.2. Finally, we conclude this chapter in Section 3.4.

# 3.1 Priority-Based Supervisory Control Of Discrete-Event Systems

In real-time scheduling theory, priorities are assigned to tasks in order to improve their schedulability. When several tasks are ready for execution, the one with the highest priority will be executed first. In addition, if allowed, a higher-priority task can *preempt* a lower priority task. In this section we formalize priorities in supervisory control of DES framework. The theory developed will be extended to timed models in the next section to synthesize supervisors for scheduling real-time tasks.

## 3.1.1 Priority Relations

In supervisory control of DES [54] the desired behavior of a system is often specified by a language<sup>1</sup> E over the alphabet of system events  $\Sigma$ . After observing a string s generated by the plant, a supervisor will guarantee that the specification is met by offering the plant with events from a set  $\gamma(s) \subseteq \Sigma$  that if executed, the resulting behavior stays in E, i.e.,  $\{s\}\cdot\gamma(s)\subseteq E$ . In classical supervisory control theory all events in the set  $\gamma(s)$  have equal "priority", in the sense that one is nondeterministically selected for execution by the plant. However, in some applications it may be desirable to give an event priority of execution over another when they are competing for a shared resource. A convenient way to state this property is by introducing a priority relation.

**Definition 1** A priority relation P is an antisymmetric relation over  $\Sigma_c$  with the interpretation that  $(\alpha_1, \alpha_2) \in P$ , denoted by  $\alpha_1 \prec \alpha_2$ , when  $\alpha_2$  has a higher priority than  $\alpha_1$ .

<sup>&</sup>lt;sup>1</sup>We assume that all languages are prefix-closed.

Remark. Priorities are introduced to enhance a controller's scheduling ability. For example, a controller assigns higher priorities of execution to tasks with smaller deadlines to improve the probability of meeting all the deadlines. As such, it is a reasonable assumption to define a priority relation between controllable events only.

The relation  $\prec$  is assumed to be antisymmetric, that is, if  $\alpha_2$  has a higher priority than  $\alpha_1$ , then  $\alpha_1$  cannot have a higher priority than  $\alpha_2$ . In the next subsection we will see how priority relations can be taken into account in supervisory control design.

## 3.1.2 Theory Of Priority-Based Supervisory Control

Let  $\Sigma$  be an alphabet,  $P \subseteq \Sigma_c \times \Sigma_c$  be a priority relation, and L and E be two prefixclosed languages over  $\Sigma$  representing plant and specification behaviors, respectively. For the sake of convenience assume for now that E is controllable with respect to L. Then in the absence of a priority relation E can be thought of as the language generated by a controller that when coupled with the plant, the closed-loop behavior  $E \cap L$  is controllable with respect to the plant and satisfies the specification:  $E \cap L \subseteq$ E.

However, not all strings in  $E \cap L$  respect the priority relation P. In particular, if  $\alpha_1 \prec \alpha_2$  and at a string  $s \in E \cap L$  both  $\alpha_1$  and  $\alpha_2$  are possible continuations of s in  $E \cap L$ , then for the priority relation to be respected a supervisor must disable the event with the lower priority (i.e.  $\alpha_1$ ). The following definition characterizes the class of languages that respect a priority relation.

**Definition 2** Let  $P \subseteq \Sigma_c \times \Sigma_c$  be a priority relation and  $N, M \subseteq \Sigma^*$  be prefix-closed languages. We say N conforms to P with respect to M, denoted by  $N \vdash_M P$  if:

$$\forall s \in \Sigma^* \forall \alpha_1, \alpha_2 \in \Sigma_c. \ \alpha_1 \prec \alpha_2 \land s\alpha_2 \in M \Rightarrow s\alpha_1 \notin N$$

In the sequel, we set M equal to a controllable sublanguage of  $E \cap L$  and  $N \subseteq M$ . The definition states that in the presence of higher priority events in a string of M, to conform to a priority relation a controller must disable all lower priority events at that string in N.

Remark. From the above definition it can be inferred that N conforms to P when, for one reason or another, high priority events are disabled by a controller; in particular, in order to meet the specification of some legal behavior. Thus, there is no need to further restrict a behavior by disabling low-priority events when high-priority events are already disabled. As we will see shortly this makes it possible to properly define maximally permissive behaviors conforming to a given priority relation.  $\Box$

When a prefixed-closed language  $N \subseteq \Sigma^*$  does not conform to P with respect to M, additional control may be required to remove low priority events that compete with high priority ones. To this end we define the class of sublanguages of N in which all low priority events are disabled when they compete with high priority events in M:

$$\mathcal{K}_P(N;M) = \{ K \subseteq N | K \vdash_M P \}$$

The following result states that  $\mathcal{K}_P(N;M)$  contains its supremal element.

**Proposition 1** The supremum of  $K_P(N; M)$ , denoted by  $K_P^{\uparrow}(N; M)$ , exists and belongs to  $K_P(N; M)$ .

**Proof.** For simplicity we drop references to N and M. First observe that  $\mathcal{K}_P$  is nonempty since  $\emptyset \in \mathcal{K}_P$ , and therefore  $\mathcal{K}_P^{\uparrow} = \bigcup \mathcal{K}_P$ , where  $\bigcup \mathcal{K}_P$  denotes the union of all members of  $\mathcal{K}_P$ . To show that  $\bigcup \mathcal{K}_P \in \mathcal{K}_P$ , we first note that  $\bigcup \mathcal{K}_P \subseteq N$ , which is immediate since N is an upperbound of  $\mathcal{K}_P$  and is therefore larger than its least

upperbound. Let  $s \in \Sigma^*$  and  $\alpha_1, \alpha_2 \in \Sigma_c$  be such that  $\alpha_1 \prec \alpha_2$ . We have:

$$s\alpha_1 \in \bigcup \mathcal{K}_P \implies s\alpha_1 \in K; \text{ for some } K \in \mathcal{K}_P$$

$\Longrightarrow s\alpha_2 \notin M; \text{ since } K \vdash_M P$

Therefore  $\mathcal{K}_P^{\uparrow} \in \mathcal{K}_P$ , as desired.

Note that if N conforms to P with respect to M then  $N = \mathcal{K}_P^{\uparrow}(N; M)$ . In this case, priorities of the competing events in N are not comparable.

Recall from classical supervisory control theory [54] that a supervisor that generates the supremal controllable sublanguage of a given specification language E, denoted by  $\sup \mathcal{C}(E)$ , restricts the system behavior in a minimally restrictive fashion. When a priority relation between controllable events is defined, the language  $\mathcal{K}_P^{\uparrow}(\sup \mathcal{C}(E);\sup \mathcal{C}(E))$  is minimally restrictive in the sense that a controllable event is disabled at a string  $s \in \mathcal{K}_P^{\uparrow}(\sup \mathcal{C}(E);\sup \mathcal{C}(E))$  only when it leads to the violation of the safety specification E, or else when it competes with higher priority events at s. Note that since P is defined between controllable events,  $\mathcal{K}_P^{\uparrow}(\sup \mathcal{C}(E);\sup \mathcal{C}(E))$  remains controllable and can therefore be implemented by a supervisory control map  $V: L \to \Gamma$  [62].

Corollary 2 Let L and E be plant and specification languages, respectively, and P be a priority relation. Then a generator for  $\mathcal{K}_P^{\uparrow}(\sup \mathcal{C}(E);\sup \mathcal{C}(E))$  controls the system in a minimally restrictive fashion, in the sense that  $\mathcal{K}_P^{\uparrow}(\sup \mathcal{C}(E);\sup \mathcal{C}(E))$ :

- 1. is controllable with respect to L,

- 2. conforms to P with respect to  $\sup C(E)$ ,

3. is a subset of E, and:

4. For any supervisor **K** generating a language K, if K satisfies (1), (2), and (3) then  $K \subseteq \mathcal{K}_P^{\uparrow}(\sup \mathcal{C}(E); \sup \mathcal{C}(E))$ .

## 3.1.3 Computation of priority-based supervisory control

We assume that M and N are represented by two automata  $\mathbf{M} = (X, x_0, \Sigma, \xi)$  and  $\mathbf{N} = (Y, y_0, \Sigma, \eta)$ , respectively. We would like to compute the language  $\mathcal{K}_P^{\uparrow}(N; M)$  of the previous subsection.

**Definition 3** The *prioritized system*, denoted by  $\mathbf{M}_{\mathbf{P}}$ , is a 4-tuple  $(X, x_0, \Sigma, \xi_P)$ , where  $\xi_P : X \times \Sigma \to X$  is defined on a pair  $(x, \sigma) \in X \times \Sigma$ , denoted by  $\xi_P(x, \sigma)!$ , if and only if  $\xi$  is defined on that pair and

$$\forall \sigma' \in \Sigma. \ \sigma \prec \sigma' \Rightarrow \neg \xi(x, \sigma')!$$

in which case  $\xi_P(x,\sigma) := \xi(x,\sigma)$ .

The language generated by  $\mathbf{M}_{\mathbf{P}}$  has the property that when intersected with any language N it will produce  $\mathcal{K}_{P}^{\uparrow}(N;M)$  restricted to M. This is formally stated and proved in the following proposition.

**Proposition 3** Let  $M, N \subseteq \Sigma^*$  be prefixed-closed languages and  $P \subseteq \Sigma_c \times \Sigma_c$  be a priority relation. Then we have:

$$N \cap M_P = \mathcal{K}_P^{\uparrow}(N; M) \cap M$$

where  $M_P$  is the language of the prioritized system. Thus, when  $N \subseteq M$  we have  $K_P^{\uparrow}(N;M) = N \cap M_P$ .

**Proof.** Denote  $\mathbf{M} := (X, x_0, \Sigma, \xi)$ ,  $\mathbf{M}_{\mathbf{P}} := (X, x_0, \Sigma, \xi_P)$  and  $\mathbf{N} := (Y, y_0, \Sigma, \eta)$ . We start by observing that

$$\mathcal{K}_{P}^{\uparrow}(N;M) \cap M = \mathcal{K}_{P}^{\uparrow}(N \cap M;M)$$

To show  $N \cap M_P = \mathcal{K}_P^{\uparrow}(N \cap M; M)$ , we must show that 1)  $N \cap M_P \in \mathcal{K}_P(N \cap M; M)$ , which implies  $N \cap M_P \subseteq \mathcal{K}_P^{\uparrow}(N \cap M; M)$ , and 2)  $N \cap M_P$  is an upper bound for  $\mathcal{K}_P(N \cap M; M)$ , which implies  $N \cap M_P \supseteq \mathcal{K}_P^{\uparrow}(N \cap M; M)$ .

- 1. Since  $M_P \subseteq M$  it follows that  $N \cap M_P \subseteq N \cap M$ . Let  $s \in \Sigma^*$  and  $\sigma, \sigma' \in \Sigma$  be such that  $\sigma \prec \sigma'$ . If  $s\sigma \in N \cap M_P$  then  $s\sigma \in M_P$ . Denote  $x := \xi_P(x_0, s) = \xi(x_0, s)$ . Since  $s\sigma \in M_P$  we have  $\xi_P(x, \sigma)!$ , and therefore it follows from the definition that  $\neg \xi(x, \sigma')!$ , i.e.  $s\sigma' \notin M$ . We conclude that  $N \cap M_P \in \mathcal{K}_P(N \cap M; M)$ .

- 2. Let  $K \in \mathcal{K}_P(N \cap M; M)$ . We must show  $K \subseteq N \cap M_P$ , i.e. for all  $s \in \Sigma^*$ ,

$$s \in K \Rightarrow s \in N \cap M_P$$

We prove this by induction on the length of s.

- Base: If  $\epsilon \in K$  it follows that  $N \cap M \neq \emptyset$ ; therefore  $N \cap M_P \neq \emptyset$  and  $\epsilon \in N \cap M_P$ .

- Inductive step: suppose for all s of length  $|s| \leq n$  we have  $s \in K \Rightarrow s \in N \cap M_P$ . Let  $s\sigma \in K$ . We must show  $s\sigma \in N \cap M_P$ . Since  $K \vdash P$  and  $s\sigma \in K$  it follows that:

$$\forall \sigma' \in \Sigma. \ \sigma \prec \sigma' \Rightarrow s\sigma' \notin M \tag{3.1}$$

Note that  $s\sigma \in K$  and  $K \subseteq N \cap M$  implies  $s\sigma \in N$  and  $s\sigma \in M$ . In addition, since K is prefix-closed it follows that  $s \in K$ , implying by the induction assumption that  $s \in M_P$ . Let  $x := \xi_P(x_0, s) = \xi(x_0, s)$ . Since  $s\sigma \in M$ , we have  $\xi(x, \sigma)!$ , implying by (3.1) that  $\xi_P(x, \sigma)!$ , i.e.  $s\sigma \in M_P$ . Thus we have shown that  $s\sigma \in N \cap M_P$ .

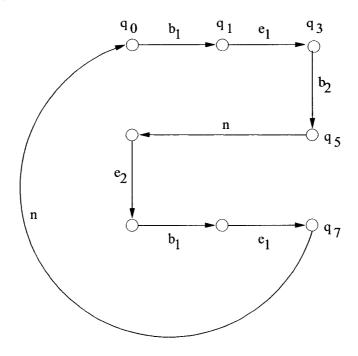

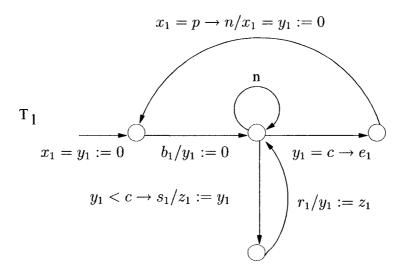

So far we have shown how priorities can be taken into account when computing a supervisor for an untimed system. In the next section, we apply our method to real-time systems by modeling real-time tasks and specifications using a simple extension of automata called Discrete Timed Automata (DTA). First the execution of a set of tasks is modeled as a DTA. Then the supremal controllable sublanguage of timing constraints with respect to task DTA subject to a priority relation is computed to find all executions in which no deadline is missed.

# 3.2 Real-Time Systems And Specifications

In this section we set up a general framework for modeling real-time systems and specifications. DTA is used to model real-time systems and to specify requirements on their behavior, including timing constraints. Time is assumed to be *discrete* (as opposed to dense [8]), and it is *explicitly* represented in our models (as opposed to implicit representation).

#### 3.2.1 Discrete Timed Automaton

A Discrete Timed Automaton (DTA) is a four-tuple  $\mathbf{L} := (X, x_0, \Sigma^t, \delta)$ , where X is the state set,  $x_0$  is the initial state,  $\Sigma^t$  is an alphabet, and  $\delta : X \times \Sigma^t \to X$  is a partial transition function. We assume that  $\Sigma^t := \Sigma \dot{\cup} \{t\}$ , where  $\Sigma$  is the alphabet of system

events and t is a special symbol which denotes the passage of one unit of time, or one tick of the global digital clock. We denote by tickcount a function over the set of all strings that returns the number of ticks in a string:

$$tickcount: \Sigma^{t^*} \to \mathbb{N}: s \mapsto \text{ the number of } t$$

's in  $s$

Time is measured in discrete steps; if  $x = \delta(x_0, s)$  and  $tickcount(s) = n \in \mathbb{N}$  then at state x discrete-time is equal to n while the value of real time could be anywhere in the real interval [n, n+1). As before, we assume that the system events are instantaneous.

For a DTA to model a real-time system, time always has to have a chance to advance. We say a DTA satisfies *time-progress* property if

$$\forall x \in X. \exists u \in \Sigma^*. \ \delta(x, ut)!$$

In our work, we restrict our attention to the class of DTA that satisfies the timeprogress property.

Let L be a prefix-closed language over  $\Sigma^t$ . We call L a timed language if

$$\forall s \in L. \exists u \in \Sigma^*. sut \in L$$

It is immediate from the definitions that if  $\mathbf{L}$  is a DTA satisfying time-progress property, then the language generated by  $\mathbf{L}$ , denoted by L, is a timed language.

An important property of timed languages is that they are closed under arbitrary union. Then, when the language returned by a control algorithm is not a timed language, it is guaranteed that a largest timed sublanguage of the behavior exists.

Formally, for  $E \subseteq \Sigma^{t^*}$  let

$$\mathcal{T}(E) := \{K \subseteq E | K = \overline{K} \wedge K \text{ is a timed language}\}$$

**Proposition 4** The supremum of  $\mathcal{T}(E)$ , denoted by  $\mathcal{T}^{\uparrow}(E)$ , belongs to  $\mathcal{T}(E)$ .

**Proof.** First notice that since  $\emptyset \in \mathcal{T}$  the set  $\mathcal{T}$  is nonempty and therefore  $\mathcal{T}^{\uparrow} = \bigcup \mathcal{T}$ . It can be readily verified that  $\bigcup \mathcal{T}$  is prefix-closed and a subset of E. Let  $s \in \bigcup \mathcal{T}$ . It follows that  $s \in K$  for some  $K \in \mathcal{T}$ . Since K is a timed language it follows that

$$\exists u \in \Sigma^*$$

.  $sut \in K$ ; since  $K$  is a timed language  $\exists u \in \Sigma^*$ .  $sut \in \bigcup \mathcal{T}$ ; since  $K \subseteq \bigcup \mathcal{T}$

Therefore  $\mathcal{T}^{\uparrow} = \bigcup \mathcal{T}$  is a timed language.

Let E' denote the largest timed sublanguage of E. Then it can be readily shown that the DTA  $\mathbf{E}'$  is obtained from  $\mathbf{E}$  by recursively removing all states from which time does not have a chance to advance.

In [62] it is shown that the class of controllable and prefix-closed sublanguages of a given language is also closed with respect to arbitrary union, resulting in the following corollary.

#### Corollary 5 Let

$C_t(E,L) := \{K \subseteq E \middle| K = \overline{K} \land K \text{ is a timed language} \land K \text{ is controllable with respect to } L\}$

Then  $C_t(E, L)$  has a largest element, which we denote by  $\sup C_t(E, L)$ .

To calculate the supremal element of  $C_t(E, L)$ , we first find the supremal controllable sublanguage of E [62]. If the result is a timed language, the procedure terminates.

Otherwise, we obtain its largest timed sublanguage by recursively removing from  $\sup \mathcal{C}(E, L)$  all states in which time has no chance to advance, and repeat the above procedure if necessary.

### 3.2.2 General Task Model

In this subsection we study a system consisting of n tasks that are to be scheduled on a single CPU. For  $i \in I := \{1, 2, ..., n\}$  let  $\mathbf{T_i}$  denote a task with an execution time of  $\nu_i \in \mathbb{N}$  time units. Each task is modeled by a DTA, so that the *composite* task model can be described as:

$$\mathbf{T} := \left| \left| \int_{i \in I} \mathbf{T_i} \right|$$

where the operator || denotes synchronous product [62].

A task consists of several identical instances. Arrival of an instance of a task  $\mathbf{T_i}$  is denoted by an event  $a_i$  called arrival of the task  $\mathbf{T_i}$ . We divide execution of an instance into  $\nu_i$  segments, where each segment has a duration of one time unit. While execution of an instance can be interrupted, a segment—which can be regarded as the unit of execution—is uninterruptible. We denote the execution of segment j,  $j \in [1, \nu_i)$ , of any instance of task i by an event  $e_i$ . In our DTA model of task i we follow  $e_i$  by a tick to indicate that the execution of each segment consumes one unit of the processor time. We introduce a new symbol  $c_i$  to denote the execution of the last segment of  $\mathbf{T_i}$ . The general model of task  $\mathbf{T_i}$  is shown in Figure 3.1. According to Figure 3.1, other tasks can always be executed except when the execution of a segment of the current task is in progress.

For future reference we define sets of events as shown in Table 3.1.

Figure 3.1: General model of task  $T_i$ . State labels indicate which segment of task i is to be executed next.

| Alphabet                                            | Description                                |