# An FPGA Implementation of the Advanced Encryption Standard with Support for Counter and Feedback Modes

James Steven Grabowski

A Thesis

in

The Department

of

The Concordia Institute for Information Systems Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science (Information Systems Security) at Concordia University Montreal, Quebec, Canada

August 2007

© James Steven Grabowski, 2007

Library and Archives Canada

Branch

Published Heritage

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-34745-4 Our file Notre référence ISBN: 978-0-494-34745-4

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

### **Abstract**

## An FPGA Implementation of the Advanced Encryption Standard with Support for Counter and Feedback Modes

#### James Steven Grabowski

The Advanced Encryption Standard (AES) is a symmetric key block cipher approved by the National Institute of Standards and Technology (NIST). AES replaced the Data Encryption Standard (DES) as a standard encryption algorithm within the United States government. It is widely used in both software and hardware applications and transactions.

Different confidentiality modes of operation allow a symmetric key block cipher to provide additional data confidentiality by altering the output in respect to previously processed input data. These modes include Cipher Block Chaining, Cipher Feedback, Output Feedback and Counter modes. Electronic Codebook (ECB) mode does not enhance the confidentiality of the original cipher.

This thesis presents an implementation of AES on a field-programmable gate array (FPGA). The design improves upon similar implementations that only employ ECB mode by supporting all five confidentiality modes of operation. The unified design supports all applicable key sizes and offers competitive throughput and resource utilization compared to designs lacking additional confidentiality modes. The design occupies 7452 slices of a Xilinx Virtex-II Pro XC2VP50 and features a maximum clock speed of 56.3*MHz*. Throughputs up to 480.427*Mbps*, 423.906*Mbps* and 379.284*Mbps* for

128-bit, 192-bit and 256-bit keys are produced for all five modes of operation. A straightforward level of key agility allows encryption and decryption operations to proceed uninterrupted at the expense of throughput. This feature is ideal when it is necessary to change the key for each block of data. A physical hardware prototype of the design is employed as further demonstration of the design's functional abilities.

### Acknowledgements

To my professor and supervisor Dr. Amr Youssef, thank you for encouraging my interests in information security, for your guidance and infinite patience toward a full-time student with full-time commitments. I hope that the end result lives up to your expectations.

When I took my first course in VHDL, I couldn't fully grasp how it would translate into a real-world application. That didn't change the fact that I enjoyed it immensely. Many thanks to Ted Obuchowicz, M.Eng., Concordia's resident VLSI/CAD Specialist, and my friend. Without you I probably would not have chosen this route, nor would I have all the devices I've used at my disposal. The late night classes may be gone, but Keith is eternal.

To my friend Adam Szporer, B.Eng., and soon to be trapped writing acknowledgements of his own, it has been a long trip. Thanks for sticking with me through the years and experiencing the same highs and lows. The Fish will always be around for another sequel.

To my love Jennifer Ricard, M.A., thank you for being there when times were tough, for your encouragement and for being my second reader. Because of your dedication, I can pretend it's not my fault when someone finds a grammatical oversight.

Thank you, my family, for your support and for the phone calls. I hope you enjoy everything that follows.

### **Table of Contents**

| List of Figuresix                                                  |

|--------------------------------------------------------------------|

| List of Tablesxii                                                  |

| List of Acronymsxiv                                                |

| Chapter 1 – Introduction1                                          |

| 1.1 Types of Cryptographic Algorithms                              |

| 1.2 The Advanced Encryption Standard                               |

| 1.3 Confidentiality Modes                                          |

| 1.4 Scope of the Implementation                                    |

| Chapter 2 – Theoretical Background                                 |

| 2.1 Finite Field and Galois Mathematics                            |

| 2.1.1 Addition and Subtraction                                     |

| 2.1.2 Multiplication                                               |

| 2.1.3 Multiplication by 'x' – <i>xtime</i>                         |

| 2.1.4 Addition of Polynomials with Coefficients in $GF(2^8)$       |

| 2.1.5 Multiplication of Polynomials with Coefficients in $GF(2^8)$ |

| 2.2 Advanced Encryption Standard                                   |

| 2.2.1 States                                                       |

| 2.2.2 Keys and Key Expansion                                       |

| 2.2.3 Encryption                                                   |

| 2.2.4 Decryption 20                                                |

| 2.3 Modes of Operation                        | 26 |

|-----------------------------------------------|----|

| 2.3.1 ECB Mode                                | 26 |

| 2.3.2 CBC Mode                                | 27 |

| 2.3.3 CFB Mode                                | 29 |

| 2.3.4 OFB Mode                                | 31 |

| 2.3.5 CTR Mode                                | 33 |

| Chapter 3 – Core AES Implementation           | 35 |

| 3.1 Top-Level View                            | 35 |

| 3.2 Hardware Component View                   | 36 |

| 3.2.1 PREPROC Component                       | 39 |

| 3.2.2 KEYEXP Component                        | 10 |

| 3.2.3 KEYSTR Component                        | 12 |

| 3.2.4 ENCDEC Component                        | 13 |

| 3.2.5 POSTPROC Component                      | 19 |

| Chapter 4 – Confidentiality Modes             | 50 |

| 4.1 Top-Level View5                           | 50 |

| 4.2 Hardware Component View                   | 52 |

| 4.2.1 IVREG Component                         | 54 |

| 4.2.2 PREPROC Component                       | 55 |

| 4.2.3 POSTPROC Component                      | 56 |

| Chapter 5 – Hardware Implementation           | 59 |

| 5.1 Key Expansion Verification                | 59 |

| 5.2 AES Round Verification (ECB Verification) | 51 |

|   | 5.3 Verification of Other Modes of Operation            | . 64 |

|---|---------------------------------------------------------|------|

|   | 5.4 Resource Utilisation                                | . 68 |

|   | 5.5 Timing Behaviour and Throughput                     | . 69 |

|   | 5.5.1 Processing with a New 128-bit Key                 | . 70 |

|   | 5.5.2 Processing with a Previously Expanded 128-bit Key | . 72 |

|   | 5.5.3 Processing with a New 192-bit Key                 | . 74 |

|   | 5.5.4 Processing with a Previously Expanded 192-bit Key | . 75 |

|   | 5.5.5 Processing with a New 256-bit Key                 | . 76 |

|   | 5.5.6 Processing with a Previously Expanded 256-bit Key | . 77 |

|   | 5.6 Comparison to Similar Works                         | . 78 |

|   | 5.7 Prototype Implementation                            | . 82 |

| C | Chapter 6 – Conclusion and Future Work                  | . 88 |

| R | eferences                                               | . 90 |

### **List of Figures**

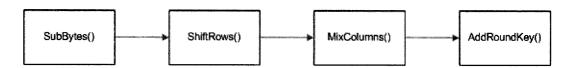

| Figure 1: AES Encryption Round Function                | 11 |

|--------------------------------------------------------|----|

| Figure 2: AES Decryption Round Function.               | 11 |

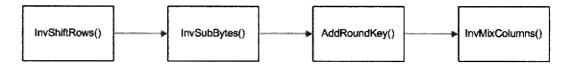

| Figure 3: State Byte Ordering (4x4 Matrix)             | 11 |

| Figure 4: State Byte Ordering (4x4 Matrix; Row-Column) | 12 |

| Figure 5: Key Expansion Pseudo-Code                    | 13 |

| Figure 6: RotWord Operation                            | 14 |

| Figure 7: SubWord Operation                            | 15 |

| Figure 8: Encryption Pseudo-Code                       | 16 |

| Figure 9: SubBytes Operation                           | 17 |

| Figure 10: ShiftRows Operation                         | 19 |

| Figure 11: Decryption Pseudo-Code                      | 21 |

| Figure 12: InvShiftRows Operation                      | 22 |

| Figure 13: InvSubBytes Operation                       | 23 |

| Figure 14: ECB Mode (Encryption and Decryption)        | 26 |

| Figure 15: CBC Mode (Encryption)                       | 28 |

| Figure 16: CBC Mode (Decryption)                       | 28 |

| Figure 17: CFB Mode (Encryption)                       | 30 |

| Figure 18: CFB Mode (Decryption)                       | 30 |

| Figure 19: OFB Mode (Encryption)                       | 32 |

| Figure 20: OFB Mode (Decryption)                       | 32 |

| Figure 21: CTR Mode (Encryption)                                              | 33 |

|-------------------------------------------------------------------------------|----|

| Figure 22: CTR Mode (Decryption)                                              | 34 |

| Figure 23: Hardware Component Flowchart (VHDL Code, AES Only)                 | 38 |

| Figure 24: PREPROC Component (AES Only)                                       | 39 |

| Figure 25: KEYEXP Component (Normal Rounds)                                   | 41 |

| Figure 26: ENCDEC Component (Encryption / SubBytes & ShiftRows)               | 44 |

| Figure 27: ENCDEC Component (XTime)                                           | 45 |

| Figure 28: ENCDEC Component (Encryption / MixColumns)                         | 45 |

| Figure 29: ENCDEC Component (Decryption / InvShiftRows & InvSubBytes)         | 47 |

| Figure 30: ENCDEC Component (Decryption / InvColumns)                         | 48 |

| Figure 31: Hardware Component Flowchart (VHDL Code, Complete)                 | 53 |

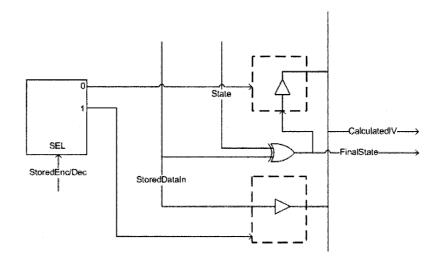

| Figure 32: IVREG Component                                                    | 54 |

| Figure 33: PREPROC Component (Complete)                                       | 55 |

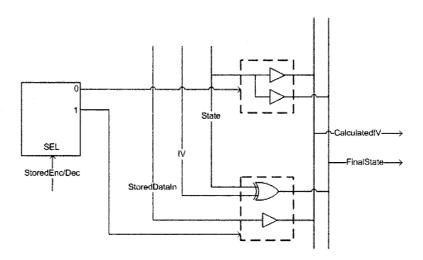

| Figure 34: POSTPROC Component (CBC Post-Processing)                           | 57 |

| Figure 35: POSTPROC Component (CFB Post-Processing)                           | 58 |

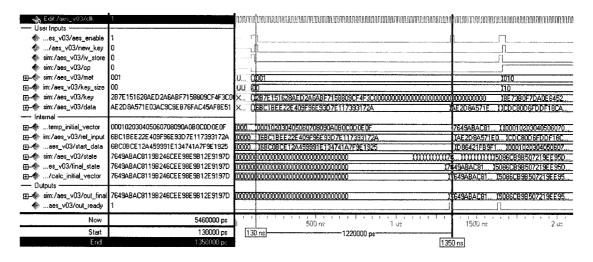

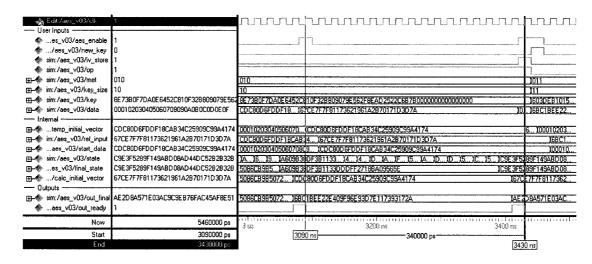

| Figure 36: Timing Diagram for AES-CBC Encryption with a New 128-bit Key       | 72 |

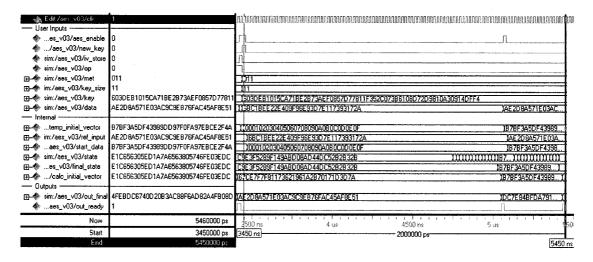

| Figure 37: Timing Diagram for AES-CBC Encryption with an Expanded 128-bit Key | 74 |

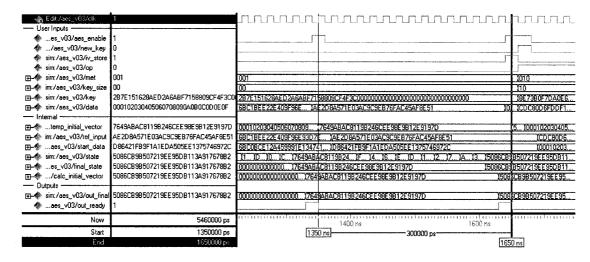

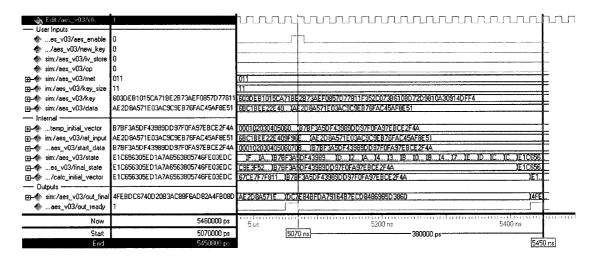

| Figure 38: Timing Diagram for AES-CFB Decryption with a New 192-bit Key       | 75 |

| Figure 39: Timing Diagram for AES-CFB Decryption with an Expanded 192-bit Key | 76 |

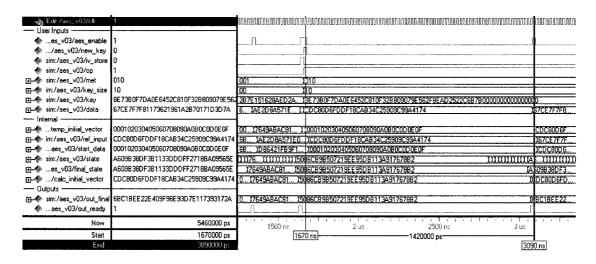

| Figure 40: Timing Diagram for AES-OFB Encryption with a New 256-bit Key       | 77 |

| Figure 41: Timing Diagram for AES-OFB Encryption with an Expanded 256-bit Key | 78 |

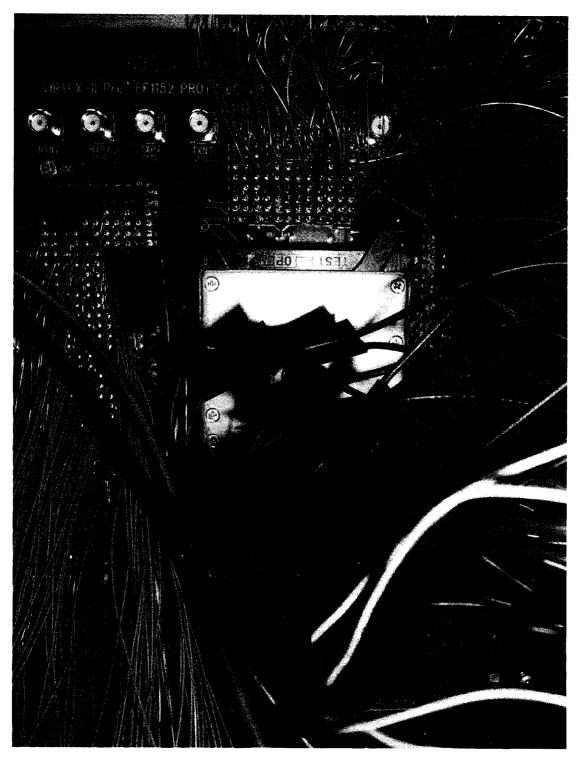

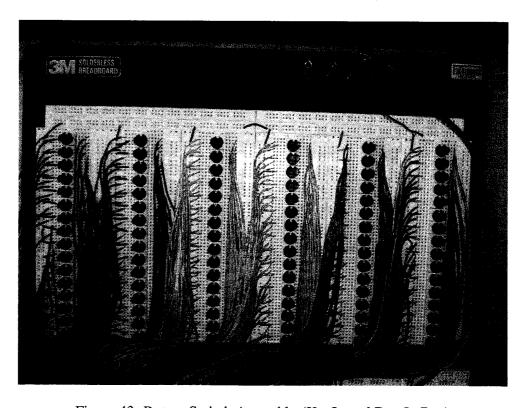

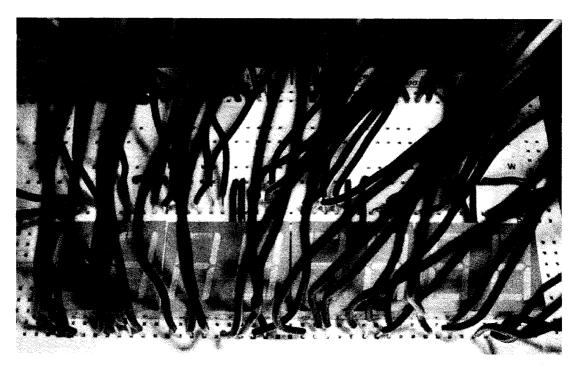

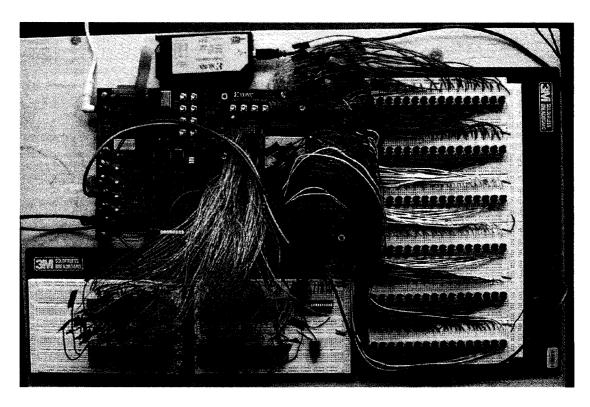

| Figure 42: Xilinx HW-AFX-FF1152-300 Prototype Board & Virtex-II Pro XC2VP50   | 83 |

| Figure 43: Rotary Switch Assembly (KeyIn and DataIn Bus)                      | 84 |

| Figure 44: Output Assembly (Block 1 and 3)      | 85 |

|-------------------------------------------------|----|

| Figure 45: Output and Operation/Enable Assembly | 86 |

| Figure 46: Complete Prototype Assembly          | 87 |

### **List of Tables**

| Table 1: Rcon Array                                               | 15 |

|-------------------------------------------------------------------|----|

| Table 2: AES S-box                                                | 18 |

| Table 3: Inverse S-box                                            | 24 |

| Table 4: Core Implementation Ports                                | 35 |

| Table 5: Major Hardware Components                                | 37 |

| Table 6: Additional Implementation Ports                          | 50 |

| Table 7: New and Updated Major Hardware Components                | 52 |

| Table 8: AES Key Expansion (128-bit) – Fourty-four 32-bit Subkeys | 60 |

| Table 9: AES Key Expansion (192-bit) – Fifty-two 32-bit Subkeys   | 60 |

| Table 10: AES Key Expansion (256-bit) – Sixty 32-bit Subkeys      | 61 |

| Table 11: AES ECB Encryption (128-bit)                            | 61 |

| Table 12: AES ECB Decryption (128-bit)                            | 62 |

| Table 13: AES ECB Encryption (192-bit)                            | 62 |

| Table 14: AES ECB Decryption (192-bit)                            | 63 |

| Table 15: AES ECB Encryption (256-bit)                            | 63 |

| Table 16: AES ECB Encryption (256-bit)                            | 64 |

| Table 17: CBC Mode Encryption (128-bit, 4 Blocks)                 | 64 |

| Table 18: CBC Mode Decryption (128-bit, 4 Blocks)                 | 65 |

| Table 19: CFB128 Mode Encryption (192-bit, 4 Blocks)              | 65 |

| Table 20: CFB128 Mode Decryption (192-bit, 4 Blocks)              | 66 |

| Table 21: OFB Mode Encryption (256-bit, 4 Blocks)    | 66   |

|------------------------------------------------------|------|

| Table 22: OFB Mode Decryption (256-bit, 4 Blocks)    | 67   |

| Table 23: CTR Mode Encryption (128-bit, 4 Blocks)    | 67   |

| Table 24: CTR Mode Decryption (128-bit, 4 Blocks)    | 68   |

| Table 25: Hardware Resource Summary                  | 69   |

| Table 26: Comparison of AES Hardware Implementations | . 79 |

### **List of Acronyms**

AES Advanced Encryption Standard

BRAM Block RAM

CBC Cipher Block Chaining

CFB Cipher Feedback

CTR Counter

DES Data Encryption Standard

DIP Dual In-line Package

ECB Electronic Codebook

FIPS Federal Information Processing Standards

FPGA Field-Programmable Gate Array

GCLK Global Clock

GF Galois Field

IOB Input/Output Block

ISE Integrated Software Environment

IV Initialisation Vector

JTAG Joint Test Action Group

LUT Lookup Table

Mbps Megabits per second

MHz Megahertz

MUX Multiplexer

NIST National Institute of Standards and Technology

ns Nanoseconds

OFB Output Feedback

PCB Printed Circuit Board

SP Special Publication

Rcon Round Constant

USB Universal Serial Bus

VHDL VHSIC Hardware Description Language

VHSIC Very High-Speed Integrated Circuit

VLSI Very-Large-Scale Integration

XOR Exclusive Or

### **Chapter 1**

### Introduction

Cryptography is the study of mathematical techniques which support confidentiality, data integrity, entity authentication and data origin authentication [11]. The word *cryptography* in contemporary use often refers to data encryption. *Encryption* is the masking of data using ciphers. A basic *cipher* is a set of mathematical functions which produce an output value from an input value and a key. A *key* is an input to a cipher that behaves as a variable of the cipher's mathematical functions.

An example of a basic (insecure) cipher is the shift cipher. A *shift cipher* will shift the value of an input up or down a fixed amount. The fixed amount is a shift cipher's key. For example, if the entire number space for data values is the ten integers from  $\theta$  to  $\theta$ , and an individual wants to encrypt the data values  $3-5-9-\theta-4$  with a key of  $\theta$ , the output of the cipher will be  $\theta-8-2-3-7$ .

#### 1.1 Types of Cryptographic Algorithms

Cryptographic algorithms are generally divided into two categories, asymmetric (public key) and symmetric. Diffie and Hellman [12] were the first to publicly propose asymmetric, or public key algorithms. Each entity that transfers data in a public key system is assigned a pair of keys, a private key and a public key. The entity keeps their

private key secret and makes their public key available to other entities. A message encrypted with an entity's public key may be decrypted with their private key and vice versa. For example, Alice can send Bob a message that only Bob can read by encrypting the message with Bob's public key. The message can only be decrypted with Bob's private key, and only Bob possesses this private key. Similarly, Bob can send Alice a message that only Alice can read by encrypting the message with Alice's public key. Information encrypted by a key pair is compromised only if the secrecy of a pair's private key is compromised. Public key encryption systems typically require more calculations (and time) than symmetric key systems. Well-known examples of asymmetric algorithms include the Diffie-Hellman cipher by Diffie and Hellman [12] and the RSA cipher by Rivest, Shamir and Adleman [13].

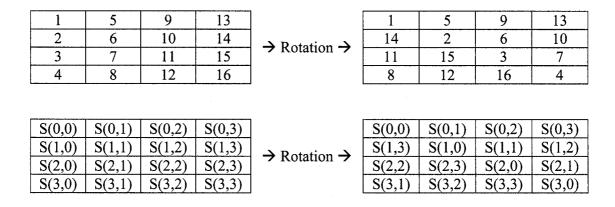

Symmetric key algorithms normally require the same key for both encryption and decryption operations. All entities that exchange data in a symmetric key system require access to this key. Information encrypted by a key is compromised if the key is compromised. Symmetric key systems are generally faster than public key systems and are ideal for encrypting large volumes of data in small amounts of time. These systems include block ciphers, which perform cryptographic operations on fixed input block sizes, or stream ciphers, which combine plaintext with values from the cipher's state. Symmetric key systems generally accommodate alternating keys more easily than public key systems. Well-known examples of symmetric key algorithms include the Data Encryption Standard (DES) cipher [14], the Blowfish cipher by Schneier [15] and the Advanced Encryption Standard (AES) cipher [1].

#### 1.2 The Advanced Encryption Standard

AES originated not as a definitive cryptographic algorithm but as a search for a new cryptographic standard. The National Institute of Standards and Technology (NIST) posted a request for comments in January 1997 regarding the selection of a replacement for DES [16]. This was followed up in September 1997 with a request for draft submissions for AES [17]. The minimum requirement was a symmetric key block cipher that supported encryption of 128-bit data blocks using 128-bit, 192-bit or 256-bit keys. Fifteen algorithm submissions were presented at the First AES Conference in August 1998 [18]. Five of the fifteen algorithms were selected as finalists: MARS [19], RC6 [20], Rijndael [21], Serpent [22] and Twofish [23]. Technical analysis of the five finalists was presented at the Third AES Conference in April 2000 [24]. NIST selected a subset of the Rijndael algorithm as the new standard in October 2000 [25]. The standard was ratified in Federal Information Processing Standards Publication 197 (FIPS 197) in November 2001 [1].

#### 1.3 Confidentiality Modes

Several mechanisms exist which improve data confidentiality for symmetric key ciphers. A block cipher typically exhibits a one-to-one relationship between its input and output. The same input block and same key will always produce the same output regardless of the location of an input block in a message. Confidentiality modes allow a block cipher to provide additional data confidentiality by altering the output in respect to previously processed input data. The five fundamental confidentiality modes of operation published by NIST in Special Publication (SP) 800-38A are Electronic

Codebook (ECB), Cipher Block Chaining (CBC), Cipher Feedback (CFB), Output Feedback (OFB) and Counter (CTR) [2]. Each mode consists of alternative pre-cipher and post-cipher processing algorithms.

#### 1.4 Scope of the Implementation

This dissertation provides a hardware-based solution that combines the full AES standard with user-configurable data confidentiality capabilities. The design improves upon similar implementations that only employ ECB mode by supporting all five confidentiality modes of operation. The additional modes achieve improved data confidentiality by masking the encrypted data in respect to previously encrypted input data. The unified design supports all applicable key sizes and offers competitive throughput and resource utilization compared to designs lacking additional confidentiality modes.

The findings of this dissertation are detailed in four main chapters. Chapter 2 explains the theoretical concepts of AES and the five modes of operation in detail. A brief introduction to Galois field mathematics relevant to AES [1] provides a basis for several AES mathematical manipulations. Chapter 3 outlines this design's hardware implementation of AES through the relationship of the major hardware components constructed in VHSIC Hardware Description Language (VHDL). Chapter 4 builds upon Chapter 3 by enhancing the design with the five confidentiality modes for all AES key sizes and operations. Chapter 5 verifies the correctness of the design using well-publicised test vectors, explores the design's performance, simulation and practical behaviour, and presents a physical prototype implementation.

### **Chapter 2**

### **Theoretical Background**

The implementation of AES in this design is based on the algorithm outlined in FIPS 197 [1]. Likewise the implementation of the five confidentiality modes of operation is based on the algorithms presented in SP 800-38A [2]. This chapter first presents a brief outline of finite field and Galois mathematics to clarify some of the more complex mathematical manipulations in the AES algorithm. Detailed descriptions of the AES algorithm and an explanation of the five confidentiality modes of operation follow.

#### 2.1 Finite Field and Galois Mathematics

A finite field, also referred to as a Galois field (GF), contains a finite number of elements [26]. The number of elements in a given GF is equal to  $p^i$  for any prime number p and any integer i greater than or equal to I. Certain AES mathematical manipulations occur in  $GF(2^8)$  which by definition contains 256 elements. Bytes are regarded as elements of  $GF(2^8)$  since they have 256 distinct values. Galois mathematics allows addition and multiplication using a different rule set than standard addition and multiplication.

#### 2.1.1 Addition and Subtraction

The addition of two elements in a GF is performed by adding the coefficients of an element's corresponding polynomials and taking the result modulo 2. This is more simply represented as a XOR operation between the two elements. Subtraction is an identical operation to addition due to the nature of the XOR operation. An example using the elements  $\{FA\}$  and  $\{B4\}$  follows.

$$\{x^7 + x^6 + x^5 + x^4 + x^3 + x\} + \{x^7 + x^5 + x^4 + x^2\} = \{x^6 + x^3 + x^2 + x\}$$

$$\{11111010\} \oplus \{10110100\} = \{01001110\}$$

$$\{FA\} \oplus \{B4\} = \{4E\}$$

#### 2.1.2 Multiplication

Multiplication in  $GF(2^8)$  is equivalent to the multiplication of polynomials modulo a polynomial of the eighth degree whose divisors are only I and itself. The AES implementation uses the following irreducible polynomial.

$$m(x) = x^8 + x^4 + x^3 + x + 1$$

This polynomial can be expressed in hexadecimal notation as  $\{01\}\{1b\}$ . An example of modulo multiplication follows, demonstrating how  $\{57\} \bullet \{83\} = \{c1\}$ . Reduction by  $mod\ m(x)$  causes the resulting binary polynomial to have a degree less than eight and can be represented as a byte.

$$(x^{6} + x^{4} + x^{2} + x + 1)(x^{7} + x + 1) = x^{13} + x^{11} + x^{9} + x^{7} + x^{5} + x^{3} + x^{2} + x + 1$$

$$= x^{6} + x^{4} + x^{2} + x + 1$$

$$= x^{13} + x^{11} + x^{9} + x^{8} + x^{6} + x^{5} + x^{4} + x^{3} + 1$$

$$x^{13} + x^{11} + x^{9} + x^{8} + x^{6} + x^{5} + x^{4} + x^{3} + x + 1 \mod(x^{8} + x^{4} + x^{3} + x + 1) = x^{7} + x^{6} + 1$$

The multiplicative inverse  $b^{-1}(x)$  of any nonzero polynomial b(x) whose degree is less than eight can be expressed as the modulo reduction of a polynomial a(x) by m(x) where  $a(x) \cdot b(x) \mod m(x) = 1$ .

$$b^{-1}(x) = a(x) \operatorname{mod} m(x)$$

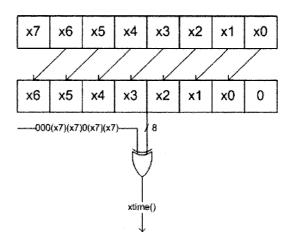

#### 2.1.3 Multiplication by 'x' - xtime

A byte can be represented as a binary polynomial b(x) whose degree is seven or less. Multiplying b(x) by  $x (\{02\})$  in hexadecimal representation) produces the following polynomial.

$$b_7 x^8 + b_6 x^7 + b_5 x^6 + b_4 x^5 + b_3 x^4 + b_2 x^3 + b_1 x^2 + b_0 x$$

Reducing this polynomial by  $mod \ m(x)$  results in  $x \cdot b(x)$ . If  $b_7$  is 0, the polynomial is already reduced, but if  $b_7$  is 1, the reduced form is obtained by XORing the polynomial with m(x). Multiplication by x can be further expressed as the XOR of  $\{1b\}$  with the left shift of b(x); x is represented as  $\{02\}$  and m(x) as  $\{01\}\{1b\}$  in hexadecimal notation. This operation is referred to as the xtime function [1].

$$xtime(\{Byte\}) = \{b_6b_5b_4b_3b_2b_1b_00\} \oplus \{1b\}$$

Higher powers of x can be represented by additional applications of xtime.

$$\{Byte\} \bullet \{02\} = \{Byte\} \bullet x = xtime(\{Byte\})$$

$$\{Byte\} \bullet \{04\} = \{Byte\} \bullet x^2 = xtime(xtime(\{Byte\}))$$

$$\{Byte\} \bullet \{08\} = \{Byte\} \bullet x^3 = xtime(xtime(xtime(\{Byte\})))$$

$$\{Byte\} \bullet \{10\} = \{Byte\} \bullet x^4 = xtime(xtime(xtime(xtime(\{Byte\}))))$$

Such results can determine the multiplication of any two values in  $GF(2^8)$ . An example,  $\{1D\} = \{10\} \oplus \{08\} \oplus \{04\} \oplus \{01\}$ , follows.

$$\{Byte\} \bullet \{1D\} = \{Byte\} \bullet (\{10\} \oplus \{08\} \oplus \{04\} \oplus \{01\})$$

$$= \{Byte\} \oplus xtime(xtime(xtime(xtime(xtime(Byte\})))) \oplus time(xtime(xtime(Byte\}))) \oplus xtime(xtime\{Byte\}))$$

#### 2.1.4 Addition of Polynomials with Coefficients in GF(28)

A four-term polynomial a(x) has coefficients where each value  $[a_3, a_2, a_1, a_0]$  has a value of a finite field element in  $GF(2^8)$ . Each value is one byte, and four bytes together form one *word*. The addition of a(x) and a second four-term polynomial b(x) with the same properties as a(x) can be expressed as follows.

$$a(x) + b(x) = (a_3 \oplus b_3)x^3 + (a_2 \oplus b_2)x^2 + (a_1 \oplus b_1)x + (a_0 \oplus b_0)$$

The XOR of the a and b terms in the above equations then follows the rules set out in Chapter 2.1.1.

#### 2.1.5 Multiplication of Polynomials with Coefficients in GF(28)

c(x) is produced by the multiplication of two four-term polynomials a(x) and b(x). This is written as  $a(x) \cdot b(x) = c(x)$ . c(x) is first expanded to give the following formula and coefficients.

$$c(x) = c_{6}x^{6} + c_{5}x^{5} + c_{4}x^{4} + c_{3}x^{3} + c_{2}x^{2} + c_{1}x + c_{0}$$

$$c_{0} = a_{0} \bullet b_{0}$$

$$c_{1} = a_{1} \bullet b_{0} \oplus a_{0} \bullet b_{1}$$

$$c_{2} = a_{2} \bullet b_{0} \oplus a_{1} \bullet b_{1} \oplus a_{0} \bullet b_{2}$$

$$c_{3} = a_{3} \bullet b_{0} \oplus a_{2} \bullet b_{1} \oplus a_{1} \bullet b_{2} \oplus a_{0} \bullet b_{3}$$

$$c_{4} = a_{3} \bullet b_{1} \oplus a_{2} \bullet b_{2} \oplus a_{1} \bullet b_{3}$$

$$c_{5} = a_{3} \bullet b_{2} \oplus a_{2} \bullet b_{3}$$

$$c_{6} = a_{3} \bullet b_{3}$$

The result c(x) is a seven-term polynomial. This c(x) must be reduced modulo a polynomial of degree four to become a word. This  $4^{th}$  degree polynomial is  $(x^4+1)$  for AES.

A four-term polynomial d(x) is the modulo product of a(x) and b(x) and is written with the following coefficients.

$$d(x) = d_3 x^3 + d_2 x^2 + d_1 x + d_0$$

$$d_0 = (a_0 \bullet b_0) \oplus (a_3 \bullet b_1) \oplus (a_2 \bullet b_2) \oplus (a_1 \bullet b_3)$$

$$d_1 = (a_1 \bullet b_0) \oplus (a_0 \bullet b_1) \oplus (a_3 \bullet b_2) \oplus (a_2 \bullet b_3)$$

$$d_2 = (a_2 \bullet b_0) \oplus (a_1 \bullet b_1) \oplus (a_0 \bullet b_2) \oplus (a_3 \bullet b_3)$$

$$d_3 = (a_3 \bullet b_0) \oplus (a_2 \bullet b_1) \oplus (a_1 \bullet b_2) \oplus (a_0 \bullet b_3)$$

The above equation can be represented as the following matrix if the polynomial a(x) is fixed.

$$\begin{bmatrix} d_0 \\ d_1 \\ d_2 \\ d_3 \end{bmatrix} = \begin{bmatrix} a_0 & a_3 & a_2 & a_1 \\ a_1 & a_0 & a_3 & a_2 \\ a_2 & a_1 & a_0 & a_3 \\ a_3 & a_2 & a_1 & a_0 \end{bmatrix} \begin{bmatrix} b_0 \\ b_1 \\ b_2 \\ b_3 \end{bmatrix}$$

The polynomial  $(x^4+1)$  is not irreducible in  $GF(2^8)$  and as such multiplication by a fixed a(x) is not necessarily invertible. A specific a(x) that does have an inverse is defined for AES as follows.

$$a(x) = \{03\}x^3 + \{01\}x^2 + \{01\}x + \{02\}$$

$$a^{-1}(x) = \{0b\}x^3 + \{0d\}x^2 + \{09\}x + \{0e\}$$

The resulting simplification of the modulo product formulas are ideal for the MixColumns and InvMixColumns of AES and are further explained in Chapters 2.2.3.4 and 2.2.4.4.

#### 2.2 Advanced Encryption Standard

The Advanced Encryption Standard is a block cipher derived from the Rijndael algorithm. Both algorithms support the use of 128-bit, 192-bit and 256-bit keys. AES supports 128-bit block sizes while Rijndael also supports 192-bit and 256-bit block sizes. AES involves two major components, key expansion and encryption/decryption of a data block, or state, over a series of rounds. Each round consists of a series of four operations collectively called the *round function*. Figures 1 and 2 show the round functions for encryption and decryption respectively.

Figure 1: AES Encryption Round Function

Figure 2: AES Decryption Round Function

Chapter 2.2.1 first describes the functionality of a state. Chapter 2.2.2 outlines the key expansion procedure. Chapters 2.2.3 and 2.2.4 explain the above encryption and decryption round functions in greater detail.

#### **2.2.1 States**

The 16 individual bytes composing the data block are referred to as a *state*. The state is processed during each round's encryption or decryption calculations. Figure 3 shows the ordering of the state bytes as identified with numbers 1-16.

| 1 | 5 | 9  | 13 |

|---|---|----|----|

| 2 | 6 | 10 | 14 |

| 3 | 7 | 11 | 15 |

| 4 | 8 | 12 | 16 |

Figure 3: State Byte Ordering (4x4 Matrix)

Figure 4 shows the byte ordering as referred to using row and column indices.

|   | S(0,0) | S(0,1) | S(0,2) | S(0,3) |

|---|--------|--------|--------|--------|

|   | S(1,0) | S(1,1) | S(1,2) | S(1,3) |

|   | S(2,0) | S(2,1) | S(2,2) | S(2,3) |

| ſ | S(3,0) | S(3,1) | S(3,2) | S(3,3) |

Figure 4: State Byte Ordering (4x4 Matrix; Row-Column)

#### 2.2.2 Keys and Key Expansion

The key used for encryption or decryption may be 128-bits, 192-bits or 256-bits in size. The required number of rounds (iterations of the encryption/decryption round function) is 10, 12 and 14 for the respective key sizes. Both encryption and decryption processes require an initial *round key* of identical size to the state being processed plus one round key for each round. Therefore the original key is expanded to (# of rounds + 1) 128-bit keys. This is 11, 13 or 15 keys of 128-bits each, or alternatively 44, 52 or 60 words of 32-bits each.

Figure 5 shows the pseudo-code for the key expansion process. Nk is the number of 32-bit words in the key, Nb is the number of 32-bit words used in a cipher block (always 4 for AES) and Nr is the number of rounds for the associated key size.

```

KeyExpansion(byte key[4*Nk], word w[Nb*(Nr+1)], Nk)

begin

word temp

i = 0

while (i < Nk)

w[i] = word(key[4*i], key[4*i+1], key[4*i+2], key[4*i+3])

i = i+1

end while

i = Nk

while (i < Nb * (Nr+1)]

temp = w[i-1]

if (i \mod Nk = 0)

temp = SubWord(RotWord(temp)) xor Rcon[i/Nk]

else if (Nk > 6 \text{ and i mod } Nk = 4)

temp = SubWord(temp)

end if

w[i] = w[i-Nk] xor temp

i = i + 1

end while

end

```

Figure 5: Key Expansion Pseudo-Code [1]

The expanded key is constructed as follows:

- 1. The original key forms the beginning of the expanded key (4, 6 or eight 32-bit words for the three respective key sizes), indexed as subkeys 0-3, 0-5 or 0-7 respectively.

- 2. For all remaining indices of the expanded key (4-43, 6-51 or 8-59 for the three respective key sizes), store the most recently calculated subkey from the expanded key.

- a. If the index is a multiple of the number of words in the original key, obtain

the quotient of the index and the number of words in the original key.

Perform a RotWord and SubWord operation on the stored word and XOR

it with the Roon of the quotient.

- b. Otherwise if the original key is 256-bits and the current index is 12, 20, 28,36, 44 or 52, only perform a SubWord operation on the stored word.

- 3. XOR the result of Step 2 with the subkey of the expanded key that is one original key length prior to the current index. The final value is the most current subkey in the expanded key. Increment the index by 1.

- 4. Repeat steps 2 and 3 until the entire expanded key has been calculated.

- 2.2.2.1 **RotWord Operation**. The RotWord operation mentioned in Step 2a of Chapter 2.2.2 rotates the first byte of a 32-bit word from the beginning of the word to its end. Figure 6 demonstrates RotWord on a 32-bit word subdivided into four bytes.

|                 | (before R      | otWord)        |                |  |

|-----------------|----------------|----------------|----------------|--|

| $\mathbf{w}_0$  | $\mathbf{w}_1$ | W <sub>2</sub> | W3             |  |

| (after RotWord) |                |                |                |  |

| $\mathbf{w}_1$  | W <sub>2</sub> | W3             | $\mathbf{w}_0$ |  |

Figure 6: RotWord Operation

2.2.2.2 **SubWord Operation**. The SubWord operation mentioned in Steps 2a and 2b of Chapter 2.2.2 performs an S-box substitution on the four separate bytes of a 32-bit word and returns a 32-bit word with the four results ordered in the same relative positions. Figure 7 demonstrates SubWord on a 32-bit word subdivided into four bytes. Chapter 2.2.3.2 provides more information about S-box substitution. One S-box is capable of operating on one byte of data at a time. Four S-boxes are required to perform SubWord as a parallel operation.

| (before SubWord)                                |                |                |                |  |  |

|-------------------------------------------------|----------------|----------------|----------------|--|--|

| $\mathbf{w}_0$                                  | $\mathbf{w}_1$ | $\mathbf{w}_2$ | W <sub>3</sub> |  |  |

| (after SubWord)                                 |                |                |                |  |  |

| $sbox(w_0)$ $sbox(w_1)$ $sbox(w_2)$ $sbox(w_3)$ |                |                |                |  |  |

Figure 7: SubWord Operation

2.2.2.3 **Rcon**. The Rcon mentioned in Step 2a of Chapter 2.2.2 refers to a *round* constant array. Table 1 shows the values of this array.

Table 1: Rcon Array

| Index | Value (Hex) |

|-------|-------------|

| 1     | 01          |

| 2     | 02          |

| 3     | 04          |

| 4     | 08          |

| 5     | 10          |

| 6     | 20          |

| 7     | 40          |

| 8     | 80          |

| 9     | 1B          |

| 10    | 36          |

#### 2.2.3 Encryption

Encryption may begin once the original key is at least partially expanded. Encryption consists of 10, 12 or 14 rounds depending on whether a 128-bit, 192-bit or 256-bit key is used. Figure 8 shows pseudo-code for the encryption algorithm.

```

Cipher(byte in[4*Nb], byte out[4*Nb], word w[Nb*(Nr+1)])

begin

byte state[4,Nb]

state = in

AddRoundKey(state, w[0, Nb-1]) // See Sec. 5.1.4

for round = 1 step 1 to Nr-1

SubBytes(state) // See Sec. 5.1.1

ShiftRows(state) // See Sec. 5.1.2

MixColumns(state) // See Sec. 5.1.3

AddRoundKey(state, w[round*Nb, (round+1)*Nb-1])

end for

SubBytes (state)

ShiftRows(state)

AddRoundKey(state, w[Nr*Nb, (Nr+1)*Nb-1])

out = state

end

```

Figure 8: Encryption Pseudo-Code [1]

The following steps summarise the encryption process:

- 1. Store the original 128-bit block of data as the state.

- 2. Perform AddRoundKey on the state using the first round key from the expanded key.

- 3. For each subsequent round excluding the final round:

- a. Perform SubBytes on the state.

- b. Perform ShiftRows on the state.

- c. Perform MixColumns on the state.

- d. Perform AddRoundKey on the state using the next available round key from the expanded key.

- 4. Repeat Step 3 for the final round, excluding the MixColumns transformation. The final state is the encrypted output of the AES cipher.

2.2.3.1 **AddRoundKey Operation**. The AddRoundKey operation mentioned in Steps 2 and 3d of Chapter 2.2.3 is a bitwise XOR operation of the given round key and the state, effectively adding the round key to the state.

2.2.3.2 **SubBytes Operation**. The SubBytes operation mentioned in Step 3a of Chapter 2.2.3 performs an S-box substitution on the 16 separate bytes of the 128-bit state. SubBytes returns a new 128-bit state with the 16 results ordered in the same relative positions. Figure 9 demonstrates SubBytes on a 128-bit state. One S-box is capable of operating on one byte of data at a time. Sixteen S-boxes are required to perform SubBytes as a parallel operation.

| S(0,0) | S(0,1) | S(0,2) | S(0,3) |                                     | S'(0,0) | S'(0,1) | S'(0,2) | S'(0,3) |

|--------|--------|--------|--------|-------------------------------------|---------|---------|---------|---------|

| S(1,0) | S(1,1) | S(1,2) | S(1,3) | $\rightarrow$ [S-box] $\rightarrow$ | S'(1,0) | S'(1,1) | S'(1,2) | S'(1,3) |

| S(2,0) | S(2,1) | S(2,2) | S(2,3) | 7 [3-00x] 7                         | S'(2,0) | S'(2,1) | S'(2,2) | S'(2,3) |

| S(3,0) | S(3,1) | S(3,2) | S(3,3) |                                     | S'(3,0) | S'(3,1) | S'(3,2) | S'(3,3) |

Figure 9: SubBytes Operation

The S-box is a 256 byte table where the hexadecimal values of the input value reference the position in the table. For example, if the input value is  $\{57\}$  in hexadecimal, then the x coordinate of the table is 5, the y coordinate of the table is 7 and the result is an output value of  $\{5b\}$ . The S-box is constructed by taking the multiplicative inverse in  $GF(2^8)$  (mapping  $\{00\}$  to itself) and applying the following affine transformation over GF(2).  $b_i$  is the  $i^{th}$  bit of a byte, and  $c_i$  is the  $i^{th}$  bit of a byte c with the value  $\{63\}$ .

$$b'_{i} = b_{i} \oplus b_{(i+4) \bmod 8} \oplus b_{(i+5) \bmod 8} \oplus b_{(i+6) \bmod 8} \oplus b_{(i+7) \bmod 8} \oplus c_{i} \longrightarrow 0 \le i < 8$$

Table 2 [1] shows the AES S-box.

Table 2: AES S-box [1]

| By             | te | Bits 3-0 (Y) |            |    |    |    |    |    |    | ٠  |    |    |    |    |    |    |    |

|----------------|----|--------------|------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| (X)            | Y) | 0            | 1          | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | a  | b  | c  | d  | e  | f  |

|                | 0  | 63           | 7c         | 77 | 7b | f2 | 6b | 6f | c5 | 30 | 01 | 67 | 2b | fe | d7 | ab | 76 |

|                | 1  | ca           | 82         | c9 | 7d | fa | 59 | 47 | f0 | ad | d4 | a2 | af | 9c | a4 | 72 | c0 |

|                | 2  | b7           | fd         | 93 | 26 | 36 | 3f | f7 | cc | 34 | a5 | e5 | fl | 71 | d8 | 31 | 15 |

|                | 3  | 04           | <b>c</b> 7 | 23 | c3 | 18 | 96 | 05 | 9a | 07 | 12 | 80 | e2 | eb | 27 | b2 | 75 |

|                | 4  | 09           | 83         | 2c | 1a | 1b | 6e | 5a | a0 | 52 | 3b | d6 | b3 | 29 | e3 | 2f | 84 |

| _              | 5  | 53           | d1         | 00 | ed | 20 | fc | bl | 5b | 6a | cb | be | 39 | 4a | 4c | 58 | cf |

| $ \mathbf{S} $ | 6  | d0           | ef         | aa | fb | 43 | 4d | 33 | 85 | 45 | f9 | 02 | 7f | 50 | 3c | 9f | a8 |

| 4-7            | 7  | 51           | a3         | 40 | 8f | 92 | 9d | 38 | f5 | bc | b6 | da | 21 | 10 | ff | f3 | d2 |

| S 7            | 8  | cd           | 0c         | 13 | ec | 5f | 97 | 44 | 17 | c4 | a7 | 7e | 3d | 64 | 5d | 19 | 73 |

| Bits           | 9  | 60           | 81         | 4f | de | 22 | 2a | 90 | 88 | 46 | ee | b8 | 14 | de | 5e | 0b | db |

|                | a  | e0           | 32         | 3a | 0a | 49 | 06 | 24 | 5c | c2 | d3 | ac | 62 | 91 | 95 | e4 | 79 |

|                | b  | e7           | c8         | 37 | 6d | 8d | d5 | 4e | a9 | 6c | 56 | f4 | ea | 65 | 7a | ae | 08 |

|                | c  | ba           | 78         | 25 | 2e | 1c | a6 | b4 | с6 | e8 | dd | 74 | 1f | 4b | bd | 8b | 8a |

|                | d  | 70           | 3e         | b5 | 66 | 48 | 03 | f6 | 0e | 61 | 35 | 57 | b9 | 86 | c1 | 1d | 9e |

|                | e  | e1           | f8         | 98 | 11 | 69 | d9 | 8e | 94 | 9b | 1e | 87 | e9 | ce | 55 | 28 | df |

|                | f  | 8c           | a1         | 89 | 0d | bf | e6 | 42 | 68 | 41 | 99 | 2d | 0f | b0 | 54 | bb | 16 |

2.2.3.3 **ShiftRows Operation**. The ShiftRows operation mentioned in Step 3b of Chapter 2.2.3 performs a forward cyclical shift on each row of the state by 0, 1, 2 or 3 bytes for the first, second, third and fourth rows respectively. Figure 10 demonstrates ShiftRows using both the numbering notation and the row/column notation for depicting the state.

| 1 | 5 | 9  | 13 |              | 1  | 5  | 9  | 13 |

|---|---|----|----|--------------|----|----|----|----|

| 2 | 6 | 10 | 14 | → Rotation → | 6  | 10 | 14 | 2  |

| 3 | 7 | 11 | 15 |              | 11 | 15 | 3  | 7  |

| 4 | 8 | 12 | 16 |              | 16 | 4  | 8  | 12 |

| S(0,0) | S(0,1) | S(0,2) | S(0,3) |              | S(0,0) | S(0,1) | S(0,2) | S(0,3) |

|--------|--------|--------|--------|--------------|--------|--------|--------|--------|

| S(1,0) | S(1,1) | S(1,2) | S(1,3) | → Rotation → | S(1,1) | S(1,2) | S(1,3) | S(1,0) |

| S(2,0) | S(2,1) | S(2,2) | S(2,3) |              | S(2,2) | S(2,3) | S(2,0) | S(2,1) |

| S(3,0) | S(3,1) | S(3,2) | S(3,3) |              | S(3,3) | S(3,0) | S(3,1) | S(3,2) |

Figure 10: ShiftRows Operation

2.2.3.4 **MixColumns Operation.** The MixColumns operation mentioned in Step 3c of Chapter 2.2.3 multiplies each column of the state modulo  $(x^4+1)$  over  $GF(2^8)$  with the polynomial a(x) from Chapter 2.1.5. The new column of the state is presented as the following matrix multiplication.

$$\begin{bmatrix} s'_{0,c} \\ s'_{1,c} \\ s'_{2,c} \\ s'_{3,c} \end{bmatrix} = \begin{bmatrix} 02 & 03 & 01 & 01 \\ 01 & 02 & 03 & 01 \\ 01 & 01 & 02 & 03 \\ 03 & 01 & 01 & 02 \end{bmatrix} \begin{bmatrix} s_{0,c} \\ s_{1,c} \\ s_{2,c} \\ s_{3,c} \end{bmatrix}$$

$$0 \le c \le N_b \qquad (N_b = 4)$$

This is reduced to the following calculations per column as an expression of logical XOR operations [1].

$$\begin{split} s'_{0,c} &= (\{02\} \bullet s_{0,c}) \oplus (\{03\} \bullet s_{1,c}) \oplus (\{01\} \bullet s_{2,c}) \oplus (\{01\} \bullet s_{3,c}) \\ s'_{1,c} &= (\{01\} \bullet s_{0,c}) \oplus (\{02\} \bullet s_{1,c}) \oplus (\{03\} \bullet s_{2,c}) \oplus (\{01\} \bullet s_{3,c}) \\ s'_{2,c} &= (\{01\} \bullet s_{0,c}) \oplus (\{01\} \bullet s_{1,c}) \oplus (\{02\} \bullet s_{2,c}) \oplus (\{03\} \bullet s_{3,c}) \\ s'_{3,c} &= (\{03\} \bullet s_{0,c}) \oplus (\{01\} \bullet s_{1,c}) \oplus (\{01\} \bullet s_{2,c}) \oplus (\{02\} \bullet s_{3,c}) \\ \end{split}$$

Multiplication over  $GF(2^8)$  can be simplified as an expression of simpler logic functions. Multiplication by  $\{01\}$  over  $GF(2^8)$  by definition is multiplication by I. All terms denoted as  $(\{01\}^*s_{r,c})$  can be replaced by  $(s_{r,c})$ .

The function *xtime* in Chapter 2.1.3 shows the multiplication of  $\{02\}$  over  $GF(2^8)$ . A version of *xtime* targeting bit operations in hardware is presented by Zhang and Parhi [3].  $\{02\}X$  can be expressed as the following (X is represented by an 8-bit value  $(a_7, a_6, a_5, a_4, a_3, a_2, a_1, a_0)$ ).

$$\{02\} \bullet a = a_6 a_5 a_4 a_3 a_2 a_1 a_0 0 \oplus 000 a_7 a_7 0 a_7 a_7$$

Multiplication by  $\{03\}$  over  $GF(2^8)$  can be calculated as the XOR of the value of  $\{01\}$  and  $\{02\}$ . This is depicted as follows.

$$\{03\} \bullet a = (\{01\} \bullet a) \oplus (\{02\} \bullet a) = a \oplus (\{02\} \bullet a)$$

MixColumns can be developed in a format suitable for the target platform using the above methods for calculating  $\{02\}$  and  $\{03\}$ .

#### 2.2.4 Decryption

Decryption begins once the original key is at least partially expanded. AES decryption is the inverse of AES encryption. Decryption consists of 10, 12 or 14 rounds depending on whether a 128-bit, 192-bit or 256-bit key is used. Figure 11 shows pseudocode for decryption.

```

InvCipher(byte in[4*Nb], byte out[4*Nb], word w[Nb*(Nr+1)])

begin

byte state[4,Nb]

state = in

AddRoundKey(state, w[Nr*Nb, (Nr+1)*Nb-1]) // See Sec. 5.1.4

for round = Nr-1 step -1 downto 1

InvShiftRows(state) // See Sec. 5.3.1

InvSubBytes(state) // See Sec. 5.3.2

AddRoundKey(state, w[round*Nb, (round+1)*Nb-1])

InvMixColumns(state) // See Sec. 5.3.3

end for

InvShiftRows(state)

InvSubBytes(state)

AddRoundKey(state, w[0, Nb-1])

out = state

end

```

Figure 11: Decryption Pseudo-Code [1]

The following steps summarise decryption:

- 1. Store the original 128-bit block of data as the state.

- 2. Perform AddRoundKey on the state using the last round key from the expanded key.

- 3. For each subsequent round excluding the final round:

- a. Perform InvShiftRows on the state.

- b. Perform InvSubBytes on the state.

- c. Perform AddRoundKey on the state using the preceding round key from the expanded key.

- d. Perform InvMixColumns on the state.

- 4. Repeat Step 3 for the final round, excluding the InvMixColumns transformation.

The final state is the decrypted output of the AES cipher.

2.2.4.1 **AddRoundKey Operation.** The AddRoundKey operation mentioned in Steps 2 and 3c of Chapter 2.2.4 is a bitwise XOR operation of the given round key and the state, effectively adding the round key to the state. There is no difference between AddRoundKey in encryption and decryption.

2.2.4.2 **InvShiftRows Operation**. The InvShiftRows operation mentioned in Step 3a of Chapter 2.2.4 performs a reverse cyclical shift on each row of the state by  $\theta$ , t, t or t bytes for the first, second third and fourth rows respectively. Figure 12 demonstrates InvShiftRows using both the numbering notation and the row/column notation for depicting the state.

Figure 12: InvShiftRows Operation

2.2.4.3 **InvSubBytes Operation**. The InvSubBytes operation mentioned in Step 3b of Chapter 2.2.4 performs an Inverse S-box substitution on the 16 separate bytes of the 128-bit state. InvSubBytes returns a new 128-bit state with the 16 results ordered in the same relative positions. Figure 13 demonstrates InvSubBytes on a 128-bit state. One

inverse S-box is capable of operating on one byte of data at a time. Sixteen inverse S-boxes are required to perform InvSubBytes as a parallel operation.

| S(0,0) | S(0,1) | S(0,2) | S(0,3) |                            | S'(0,0) | S'(0,1) | S'(0,2) | S'(0,3) |

|--------|--------|--------|--------|----------------------------|---------|---------|---------|---------|

| S(1,0) | S(1,1) | S(1,2) | S(1,3) | → [S-box <sup>-1</sup> ] → | S'(1,0) | S'(1,1) | S'(1,2) | S'(1,3) |

| S(2,0) | S(2,1) | S(2,2) | S(2,3) | 7 [3-00x ] 7               | S'(2,0) | S'(2,1) | S'(2,2) | S'(2,3) |

| S(3,0) | S(3,1) | S(3,2) | S(3,3) |                            | S'(3,0) | S'(3,1) | S'(3,2) | S'(3,3) |

Figure 13: InvSubBytes Operation

The inverse S-box is a 256 byte table where the hexadecimal values of the input value reference the position in the table. For example, if the input value is  $\{57\}$  in hexadecimal, then the x coordinate of the table is 5, the y coordinate of the table is 7 and the result is an output value of  $\{da\}$ . For the inverse S-box, the inverse of the affine transformation in Chapter 2.2.3.2 is applied and then the multiplicative inverse in  $GF(2^8)$  is performed. Table 3 shows the inverse S-box [1].

Table 3: Inverse S-box [1]

| By   | te | Bits 3-0 (Y) |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|------|----|--------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| (XY  | Y) | 0            | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | a  | b  | c  | d  | e  | f  |

|      | 0  | 52           | 09 | 6a | d5 | 30 | 36 | a5 | 38 | bf | 40 | a3 | 9e | 81 | f3 | d7 | fb |

|      | 1  | 7c           | e3 | 39 | 82 | 9b | 2f | ff | 87 | 34 | 8e | 43 | 44 | c4 | de | e9 | cb |

|      | 2  | 54           | 7b | 94 | 32 | a6 | c2 | 23 | 3d | ee | 4c | 95 | 0b | 42 | fa | c3 | 4e |

|      | 3  | 08           | 2e | al | 66 | 28 | d9 | 24 | b2 | 76 | 5b | a2 | 49 | 6d | 8b | d1 | 25 |

|      | 4  | 72           | f8 | f6 | 64 | 86 | 68 | 98 | 16 | d4 | a4 | 5c | cc | 5d | 65 | b6 | 92 |

| _    | 5  | 6c           | 70 | 48 | 50 | fd | ed | b9 | da | 5e | 15 | 46 | 57 | a7 | 8d | 9d | 84 |

| 8    | 6  | 90           | d8 | ab | 00 | 8c | bc | d3 | 0a | f7 | e4 | 58 | 05 | b8 | b3 | 45 | 06 |

| 4-7  | 7  | d0           | 2c | 1e | 8f | ca | 3f | 0f | 02 | c1 | af | bd | 03 | 01 | 13 | 8a | 6b |

| S 7  | 8  | 3a           | 91 | 11 | 41 | 4f | 67 | dc | ea | 97 | f2 | cf | ce | f0 | b4 | e6 | 73 |

| Bits | 9  | 96           | ac | 74 | 22 | e7 | ad | 35 | 85 | e2 | f9 | 37 | e8 | 1c | 75 | df | 6e |

|      | a  | 47           | fl | 1a | 71 | 1d | 29 | c5 | 89 | 6f | b7 | 62 | 0e | aa | 18 | be | 1b |

| ł    | b  | fc           | 56 | 3e | 4b | c6 | d2 | 79 | 20 | 9a | db | c0 | fe | 78 | cd | 5a | f4 |

|      | c  | 1f           | dd | a8 | 33 | 88 | 07 | c7 | 31 | bl | 12 | 10 | 59 | 27 | 80 | ec | 5f |

|      | d  | 60           | 51 | 7f | a9 | 19 | b5 | 4a | 0d | 2d | e5 | 7a | 9f | 93 | c9 | 9c | ef |

|      | e  | a0           | e0 | 3b | 4d | ae | 2a | f5 | b0 | c8 | eb | bb | 3c | 83 | 53 | 99 | 61 |

|      | f  | 17           | 2b | 04 | 7e | ba | 77 | d6 | 26 | e1 | 69 | 14 | 63 | 55 | 21 | 0c | 7d |

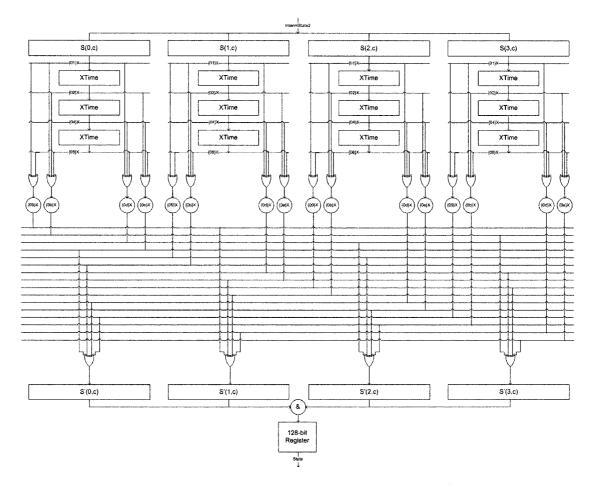

2.2.4.4 **InvMixColumns Operation.** The InvMixColumns operation mentioned in Step 4d of Chapter 2.2.4 multiplies each column of the state modulo  $(x^4+1)$  over  $GF(2^8)$  with the inverse of the polynomial in MixColumns,  $a^{-1}(x)$ , from Chapter 2.1.5. The new column of the state is presented as the following matrix multiplication.

$$\begin{bmatrix} s'_{0,c} \\ s'_{1,c} \\ s'_{2,c} \\ s'_{3,c} \end{bmatrix} = \begin{bmatrix} 0e & 0b & 0d & 09 \\ 09 & 0e & 0b & 0d \\ 0d & 09 & 0e & 0b \\ 0b & 0d & 09 & 0e \end{bmatrix} \begin{bmatrix} s_{0,c} \\ s_{1,c} \\ s_{2,c} \\ s_{3,c} \end{bmatrix}$$

$$0 \le c \le N_b \qquad (N_b = 4)$$

This is reduced to the following calculations per column [1].

$$\begin{split} s'_{0,c} &= (\{0e\} \bullet s_{0,c}) \oplus (\{0b\} \bullet s_{1,c}) \oplus (\{0d\} \bullet s_{2,c}) \oplus (\{09\} \bullet s_{3,c}) \\ s'_{1,c} &= (\{09\} \bullet s_{0,c}) \oplus (\{0e\} \bullet s_{1,c}) \oplus (\{0b\} \bullet s_{2,c}) \oplus (\{0d\} \bullet s_{3,c}) \\ s'_{2,c} &= (\{0d\} \bullet s_{0,c}) \oplus (\{09\} \bullet s_{1,c}) \oplus (\{0e\} \bullet s_{2,c}) \oplus (\{0b\} \bullet s_{3,c}) \\ s'_{3,c} &= (\{0b\} \bullet s_{0,c}) \oplus (\{0d\} \bullet s_{1,c}) \oplus (\{09\} \bullet s_{2,c}) \oplus (\{0e\} \bullet s_{3,c}) \\ \end{split}$$

Multiplication over  $GF(2^8)$  can again be simplified as an expression of simpler logic functions.  $\{01\}$  and  $\{02\}$  were calculated in Chapter 2.2.3.4.  $\{04\}$  is calculated as the *xtime* of  $\{02\}$  and  $\{08\}$  is calculated as the *xtime* of  $\{04\}$  as per the following.

$$\begin{array}{lll} \{04\} \bullet a = & \{02\}a_6\{02\}a_5\{02\}a_4\{02\}a_3\{02\}a_2\{02\}a_1\{02\}a_0\,0 \oplus \\ & 000\{02\}a_7\{02\}a_7\,0\{02\}a_7\{02\}a_7\\ \{08\} \bullet a = & \{04\}a_6\{04\}a_5\{04\}a_4\{04\}a_3\{04\}a_2\{04\}a_1\{04\}a_0\,0 \oplus \\ & 000\{04\}a_7\{04\}a_7\{04\}a_7\{04\}a_7\\ \end{array}$$

$\{03\}$  was calculated as the addition (bitwise XOR) of  $\{02\}$  and  $\{01\}$  in Chapter 2.2.3.4. This method is used to calculate  $\{09\}$ ,  $\{0b\}$ ,  $\{0d\}$  and  $\{0e\}$ .

$$\{09\} \bullet a = (\{08\} \bullet a) \oplus (\{01\} \bullet a) = (\{08\} \bullet a) \oplus a$$

$$\{0b\} \bullet a = (\{09\} \bullet a) \oplus (\{02\} \bullet a)$$

$$\{0d\} \bullet a = (\{09\} \bullet a) \oplus (\{04\} \bullet a)$$

$$\{0e\} \bullet a = (\{08\} \bullet a) \oplus (\{04\} \bullet a) \oplus (\{02\} \bullet a)$$

InvMixColumns can be developed in a format suitable for the target platform using these methods for calculating {09}, {0b}, {0d} and {0e}.

### 2.3 Modes of Operation

There are five primary modes of operation defined by SP 800-38A [2] for use with symmetric key block ciphers to provide data confidentiality. These modes are ECB, CBC, CFB, OFB and CTR.

#### 2.3.1 ECB Mode

ECB mode [2] consists of a direct one-to-one relationship between plaintext and ciphertext. For example, if word1 encrypted by a key results in word2, then word2 decrypted by that same key results in word1. Each block of data is operated on independently. The cipher function is applied to a block of plaintext to produce a block of ciphertext and the inverse cipher function is applied to a block of ciphertext to produce a block of plaintext. Figure 14 displays the dataflow for encryption and decryption operations in ECB mode.

Figure 14: ECB Mode (Encryption and Decryption) [2]

This mode has the advantage of allowing for parallel computation of multiple data blocks as there is no dependency on the order in which the data is computed. This mode's drawback is its one-to-one correlation between ciphertext and plaintext. This consistent relationship may be undesirable in certain applications.

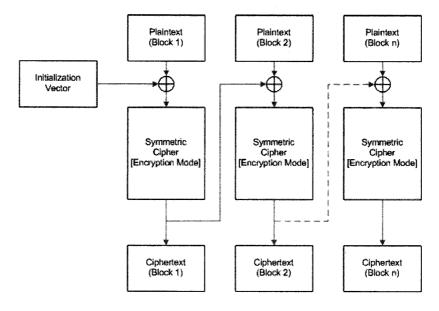

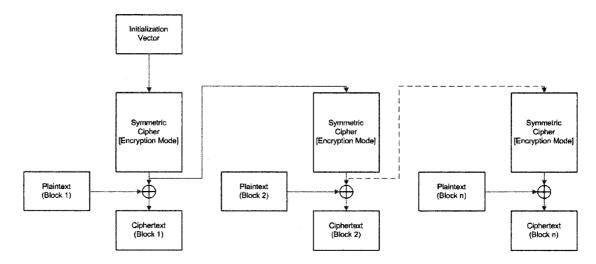

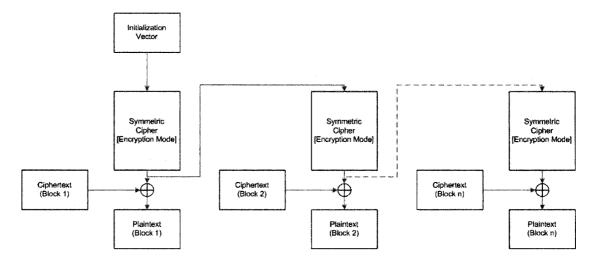

#### 2.3.2 CBC Mode

CBC mode [2] combines the plaintext block with a previous ciphertext block of a CBC calculation. This mode requires the preceding block's ciphertext be calculated to determine the subsequent block's ciphertext, effectively chaining the calculation from one block to the next. Unlike ECB mode, there is no one-to-one correlation between plaintext and ciphertext blocks since the result of a CBC calculation depends on the previous ciphertext value in addition to the current input value. The first calculation in the chain requires a non-secret but unpredictable initialisation vector (IV) in place of a ciphertext block.

Encryption steps in CBC mode XOR together the plaintext and previous step's ciphertext block and input the result into the cipher function. Decryption steps XOR together the previous step's ciphertext block and the output of the inverse cipher function. Figures 15 and 16 show the dataflow for CBC mode encryption and decryption respectively.

Figure 15: CBC Mode (Encryption) [2]

Figure 16: CBC Mode (Decryption) [2]

This mode does not feature the potentially undesirable property of a one-to-one correspondence between plaintext and ciphertext. However, it is not possible to encrypt in parallel due to the chaining property of the encryption process. Decryption can still be performed in parallel presuming the availability of the entire ciphertext stream.

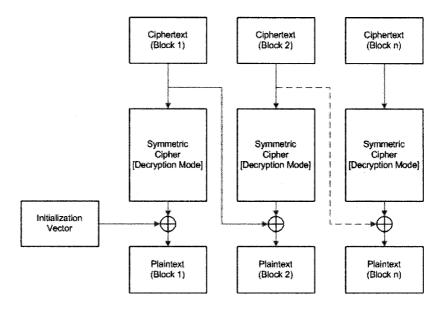

#### 2.3.3 CFB Mode

CFB mode [2] requires the feedback of a calculated ciphertext block as the input to the next calculation. This mode requires calculating the preceding block's ciphertext to determine the subsequent block's ciphertext as with CBC mode. The first calculation requires a non-secret but unpredictable IV in place of a ciphertext block. The block size of the input has b bits.

CFB mode encryption XORs together the s most significant bits of the cipher function output with the corresponding s bits of the plaintext to produce s bits of ciphertext output. The remaining b-s bits of the input are then concatenated with the s bits of ciphertext to produce the next input block. The procedure is repeated until all corresponding s bit segments of the plaintext have been processed. CFB mode decryption XORs together the s most significant bits of the inverse cipher function output with the corresponding s bits of the ciphertext to produce s bits of plaintext output. The remaining s-s bits of the input are then concatenated with the s-bits of plaintext to produce the next input block. The procedure is repeated until all corresponding s-bits segments of the ciphertext have been processed. Figures 17 and 18 show the dataflow for CFB mode encryption and decryption respectively.

Figure 17: CFB Mode (Encryption) [2]

Figure 18: CFB Mode (Decryption) [2]

1-bit, 8-bit, 64-bit and 128-bit CFB modes are all listed in SP 800-38A [2]. Theoretically, any symmetric cipher processing data of b bytes can operate in a CFB mode of s bits where s evenly divides b. For the purposes of this design's hardware implementation, s is a constant 128 bits. In this encryption scenario the entire 128-bit

block of plaintext is XORed with the entire cipher function output, producing a 128-bit block of ciphertext to serve as the next input block. The same scenario applies to decryption. The entire 128-bit block of ciphertext is XORed with the entire inverse cipher function output, producing a 128-bit block of plaintext.

This mode is similar to CBC in that it does not feature the potentially undesirable property of a one-to-one ratio between plaintext and ciphertext. Encryption cannot take place in parallel. Decryption can be performed in parallel presuming the availability of the entire ciphertext stream.

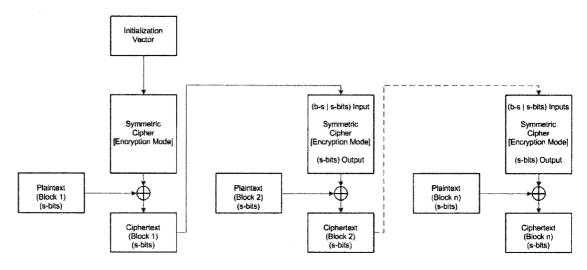

#### 2.3.4 OFB Mode

OFB mode [2] requires the output of the forward cipher function for the input of the next calculation. This mode requires calculating the preceding block's ciphertext to determine the subsequent block's ciphertext as with CBC and CFB modes. The first calculation requires the IV as an input block. The IV must be a unique nonce for each key used, otherwise it is possible to compromise data confidentiality.

Encryption and decryption steps in OFB mode are identical, the only difference being the application of plaintext or ciphertext. The output of the forward cipher function is XORed together with the plaintext to produce a ciphertext block for encryption. Similarly, for decryption the output of the forward cipher function is XORed together with the ciphertext to produce a plaintext block. In both cases the output of the forward cipher function also serves as the input of the subsequent calculation. Figures 19 and 20 show the dataflow for OFB mode encryption and decryption respectively.

Figure 19: OFB Mode (Encryption) [2]

Figure 20: OFB Mode (Decryption) [2]

The same IV supplied with the same key will result in the same forward cipher function outputs for each data block. Encryption and decryption may be performed in parallel if the IV is known and the forward cipher function outputs are calculated in advance. The inverse cipher function is not used in the decryption stage.

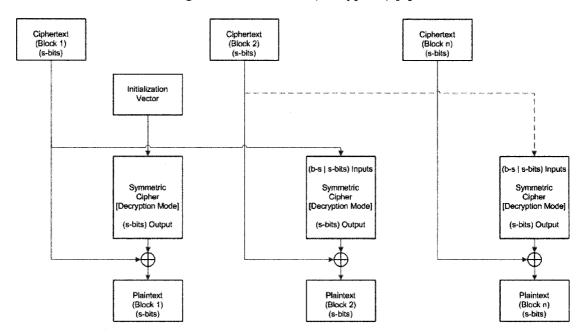

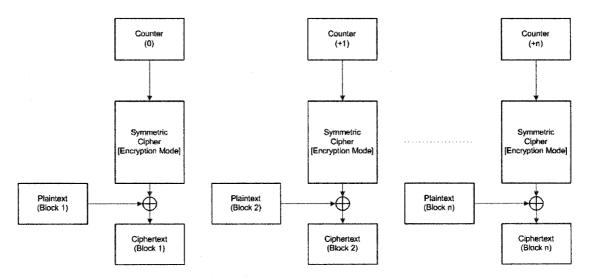

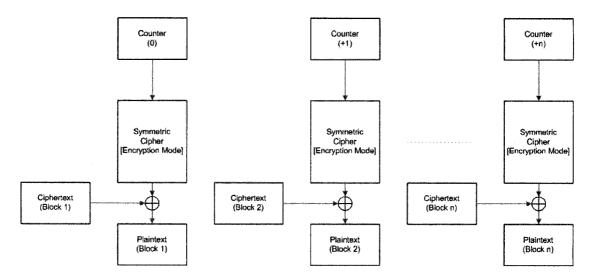

#### 2.3.5 CTR Mode

CTR mode [2], similar to OFB mode, only uses the forward cipher function. The IV is replaced by a series of input blocks, called *counters*. These counters must be distinct for each message block. These counters must also be distinct for all messages for a specific key to preserve data confidentiality.

Encryption and decryption steps in CTR mode are identical, the only difference being the application of plaintext or ciphertext. The output of the forward cipher function is XORed together with the plaintext to produce a ciphertext block for encryption. Similarly, for decryption the output of the forward cipher function is XORed together with the ciphertext to produce a plaintext block. In both cases the input of the cipher function consists of unique counters. Identical counters should only be used for the corresponding encryption and decryption stages. Figures 21 and 22 show the dataflow for CTR mode encryption and decryption respectively.

Figure 21: CTR Mode (Encryption) [2]

Figure 22: CTR Mode (Decryption) [2]

The same counter supplied with the same key will result in the same forward cipher function outputs for each data block. A counter value from an encryption calculation should only be reused with the same key for the corresponding decryption calculation. Encryption and decryption may be performed in parallel if the counters are known and the forward cipher function outputs are calculated in advance.

The counter function has been made a simple incremental function for the purposes of this design's hardware implementation. Once an initial counter value is supplied the remainder of the counter values are automatically calculated at each stage.

## **Chapter 3**

# **Core AES Implementation**

The core AES implementation is written in VHDL. An overview of the core AES implementation and a description of its major hardware components follow. The chapter first presents a top-level view with a description of how an external user or device interacts with the implementation. This is supplemented with a summary of the implementation's major hardware components and an expanded description of each.

### 3.1 Top-Level View

The core AES device consists of seven input and two output ports. All inputs and outputs are parallel, comprising a total of 519 bits. Table 4 lists the ports.

Table 4: Core Implementation Ports

| Signal      | Bits | Type | Description                                          |

|-------------|------|------|------------------------------------------------------|

| CLK         | 1    | In   | Clock signal; internal processes wake up and         |

| CLK         | 1    |      | calculations are performed when this signal is high. |

| DataIn      | 128  | In   | 128-bit data block bus.                              |

| KeyIn       | 256  | In   | 256-bit key block bus (128/192/256-bit sizes).       |

| KeySize     | 2    | In   | 2-bit input; 3 selectable key sizes.                 |

| Enc/Dec     | 1    | In   | 1-bit input; selectable encryption/decryption.       |

| NewKey      | 1    | In   | 1-bit input; selectable key expansion operation.     |

| Enable      | 1    | In   | 1-bit input; processing enable.                      |

| DataOut     | 128  | Out  | 128-bit ciphertext block bus.                        |

| OutputPoody | 1    | Out  | 1-bit data strobe alerts external devices that a new |

| OutputReady | 1    | Out  | ciphertext block has stabilised on the DataOut bus.  |

The device is operated via the following procedure:

- 1. Attach an independently functioning clock to the CLK output.

- 2. Set the *Enc/Dec* input to 0 for an encryption operation and 1 for a decryption operation.

- 3. Set the *NewKey* input to 0 for AES processing only and 1 to expand a new key in addition to AES processing.

- 4. Set the *KeySize* input to 00 or 01 for a 128-bit key, 10 for a 192-bit key or 11 for a 256-bit key. This input value is irrelevant when *NewKey* is set to 0.

- 5. Supply a 256-bit value to the *KeyIn* bus. Bits 1-128 are used for calculations of all key sizes. Bits 129-192 are also used for 192-bit and 256-bit key sizes. Bits 193-256 are used for 256-bit keys only. This input value is irrelevant when *NewKey* is set to 0.

- 6. Supply a 128-bit value to the *DataIn* bus.

- 7. Trigger the *Enable* input. The device produces a signal at the *DataOut* bus corresponding to the stored input values. The signal *OutputReady* is high for one clock cycle at the same time a new stable value appears at *DataOut*. This operation cannot be interrupted until it has been completed. Changing the input values during this process has no effect on the operation.

## 3.2 Hardware Component View

The design is separated into five major hardware components. Table 5 summarises these components. The remainder of the chapter expands on each of these hardware components.

Table 5: Major Hardware Components

| Name     | Description                                                             |

|----------|-------------------------------------------------------------------------|

| PREPROC  | Buffers and stores Enable, Enc/Dec, DataIn, KeyIn, KeySize and          |

|          | NewKey signals. Signals stored by PREPROC are used by the other         |

|          | hardware components for an AES processing cycle.                        |

| KEYEXP   | Performs key expansion based on the KeySize and KeyIn signals           |

|          | stored by PREPROC. This component is only active when a 1 is            |

|          | stored for NewKey.                                                      |

| KEYSTR   | Contains the expanded subkeys produced by KEYEXP. The contents          |

|          | of KEYSTR are updated only when a 1 is stored for NewKey.               |

| ENCDEC   | Performs the encryption/decryption operation based on the <i>DataIn</i> |

|          | signal stored by PREPROC and the stored expanded key contained in       |

|          | KEYSTR. The result is a 128-bit vector.                                 |

| POSTPROC | Outputs DataOut and sets OutputReady high during the same clock         |

|          | cycle.                                                                  |

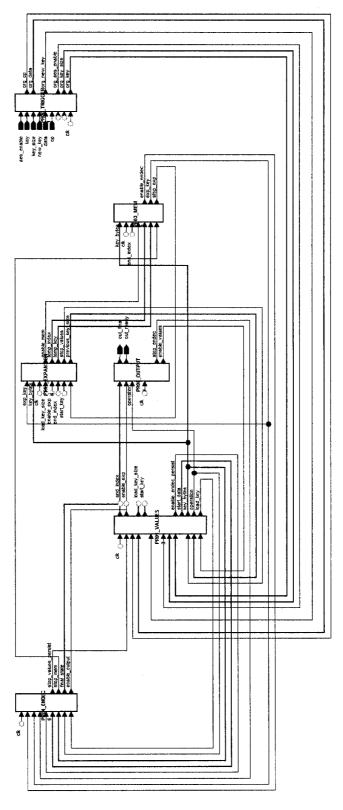

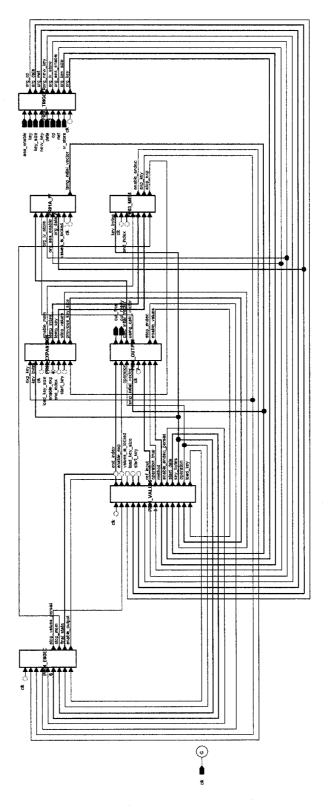

Figure 23 shows the relationship between the hardware components as written in VHDL. At this abstraction level there are six logical constructs which correspond to the five major hardware components. These are *TRIGGER* and *VALUES* (PREPROC), *EXPANSION* (KEYEXP), *MEMORY* (KEYSTR), *ENDEC* (ENCDEC) and *OUTPUT* (POSTPROC).

Figure 23: Hardware Component Flowchart (VHDL Code, AES Only)

A central control unit is not listed among either the major hardware components or the VHDL constructs. This is because the major hardware components are each responsible for signalling and micro-managing other components as to when they may operate and what functions they may perform. Therefore, the role of a central control unit is a distributed function of this design. Discussion of any control constructs is intentionally simplified.

#### 3.2.1 PREPROC Component

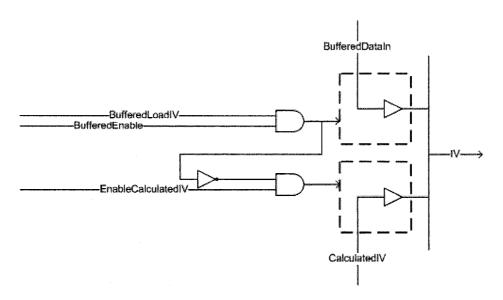

The PREPROC hardware component buffers and stores the *Enable*, *Enc/Dec*, *DataIn*, *KeyIn*, *KeySize* and *NewKey* signals. The component consists of registers that buffer the value of these signals every clock cycle. The buffered values are referred to in the diagrams as *Buffered* signals, the currently stable input signals. The PREPROC component uses the buffered signals, as opposed to directly accessing the inputs, to avoid signal glitches caused by unstable or rapidly changing inputs.

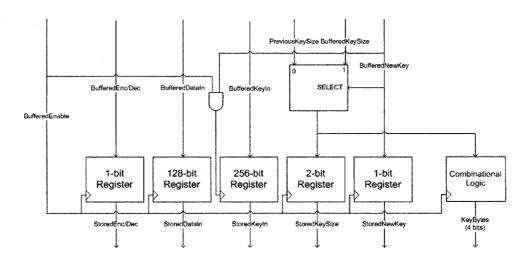

Figure 24 shows PREPROC's hardware design for manipulating Buffered signals.

Figure 24: PREPROC Component (AES Only)

The majority of signals stored by PREPROC are referred to in the diagrams as the *Stored* signals, the stable input signals that have been selected for AES processing. While the *Enc/Dec*, *DataIn* and *NewKey* values are stored in a straightforward manner, the remaining signals require additional processing.

The stored *KeySize* depends on whether a new key has been stored or the previously expanded key has been retained. The previous key size, recorded by the KEYEXP component, is stored for *KeySize* if 0 is buffered for *NewKey*. The buffered *KeyIn* is disregarded in this case. The buffered *KeySize* and *KeyIn* are stored if 1 is buffered for *NewKey*. The value *KeyBytes* is calculated based on the output of the MUX. *KeyBytes* corresponds to the number of bytes in the input key, either four (128-bit), six (192-bit) or eight (256-bit). This values is used by the KEYEXP and KEYSTR components.

#### 3.2.2 KEYEXP Component

The KEYEXP hardware component performs key expansion based on the *KeySize* and *KeyIn* signals stored by PREPROC. This component is only active when a *1* is stored for *NewKey*. One 32-bit subkey is created per clock cycle, requiring 44 clock cycles for a 128-bit key, 52 clock cycles for a 192-bit key and 60 clock cycles for a 256-bit key.

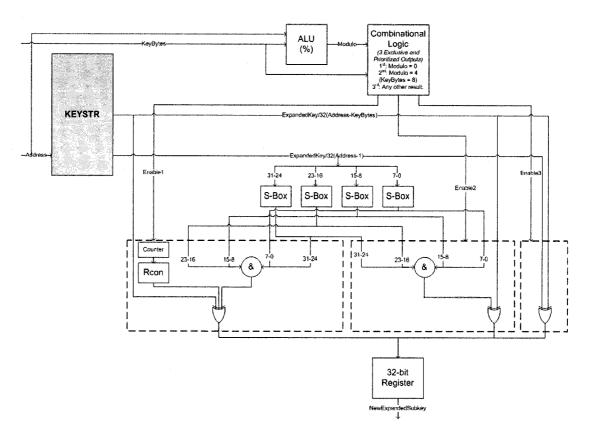

The first portion of the expanded key is a copy of the original key. The relevant bits of the stored *KeyIn* are temporarily stored in 32-bit increments. Each subkey in turn is stored by the KEYSTR component. Figure 25 shows KEYEXP's hardware design for all rounds after the original key has been copied.

Figure 25: KEYEXP Component (Normal Rounds)

For each key expansion round, the previous subkey and the subkey one *KeyBytes* length away from the current subkey are read. The key expansion algorithm varies based on the value of *KeyBytes* and the modulus of the current subkey index and *KeyBytes*. Three mutually exclusive paths accommodate this in hardware. If the resulting modulo operation is  $\theta$  the first enable signal is active, otherwise if the resulting modulo operation is  $\theta$  for a 256-bit key (*KeyBytes* is  $\theta$ ) the second enable signal is active. If both these conditions fail the third enable signal is active.

The first and second paths separate the previous subkey into four 8-bit units that are each processed by an S-box.

The first path concatenates the 8-bit outputs of each S-box in the order of bits 23-16, 15-8, 7-0 and 31-24. This value is XORed with the Rcon value and the subkey one *KeyBytes* length away from the current subkey. The counter attached to the Rcon look-up table (LUT) is the LUT's index and increments each time the first enable signal changes from low to high.

The second path concatenates the 8-bit outputs of each S-box in their original order. This value is XORed with the subkey one *KeyBytes* length away from the current subkey.

The third path concatenates the previous subkey and the subkey one *KeyBytes* length away from the current subkey.

KEYEXP records the value of the stored key for the next AES processing cycle in the event *NewKey* is stored low. This storage is not explicitly depicted in the above figure.

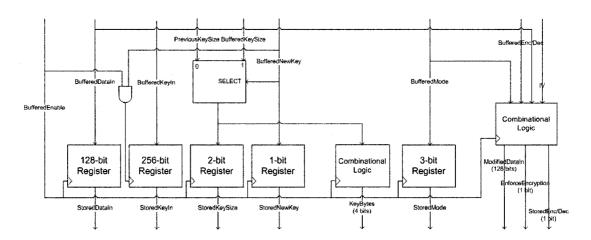

### 3.2.3 KEYSTR Component

The KEYSTR hardware component contains the expanded subkeys produced by KEYEXP. The contents of KEYSTR are updated only when a 1 is stored for NewKey. Figure 32 shows KEYSTR's hardware design. The component consists of 60 registers of 32-bits each. The first 44 are used for an expanded 128-bit key. The next eight are also used for an expanded 192-bit key and the remaining eight are also used for an expanded 256-bit key. Each register is updated with a corresponding subkey after that subkey is calculated by KEYEXP.

#### 3.2.4 ENCDEC Component

The ENCDEC hardware component performs the encryption/decryption operation based on the *DataIn* signal stored by PREPROC and the stored expanded key contained in KEYSTR. The result is a 128-bit vector. The encryption round function follows the pattern of SubBytes(), ShiftRows(), MixColumns() and AddRoundKey(). The decryption round function follows the pattern of InvShiftRows(), InvSubBytes(), AddRoundKey() and InvMixColumns(). First, the hardware required for initialising the state and the hardware required for the major components of an encryption round are presented. Second, the hardware required for initialising the state and the hardware required for the major components of a decryption round are presented.

3.2.4.1 **Encryption Operation.** The first four subkeys of the expanded key are concatenated and XORed with the stored *DataIn*, producing the initial *State*. The encryption round function performs all calculations starting from the initial *State*.

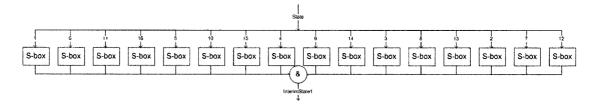

The encryption round function is divided into three hardware components: a SubBytes/ShiftRows unit, a MixColumns unit and an AddRoundKey unit. The output of AddRoundKey is the new *State* and is the input for the next iteration of the round function. The round function iterates 10 times for a 128-bit key, 12 times for a 192-bit key and 14 times for a 256-bit key. Figure 26 shows ENCDEC's SubBytes/ShiftRows encryption unit.

Figure 26: ENCDEC Component (Encryption / SubBytes & ShiftRows)

The functionality of the SubBytes and ShiftRows operations are merged into a single hardware unit. This takes advantage of the reversible property of SubBytes and ShiftRows. The *State* is separated into sixteen 8-bit units and reordered as in Chapter 2.2.3.3. Each unit is applied to an S-box that generates a corresponding value. The resulting values are concatenated together producing an interim state. This completes the SubBytes and ShiftRows operations of the round function. This hardware unit is active for all rounds.

Figure 27 shows ENCDEC's *XTime* function as presented by Zhang and Parhi [3]. The XTime function was presented in Chapter 2.1.3 and greatly simplifies the MixColumns and InvMixColumns *GF* operations. Any appearances of *XTime* blocks hereon can be replaced by this implementation. Figure 28 shows ENCDEC's MixColumns encryption unit.

Figure 27: ENCDEC Component (XTime)

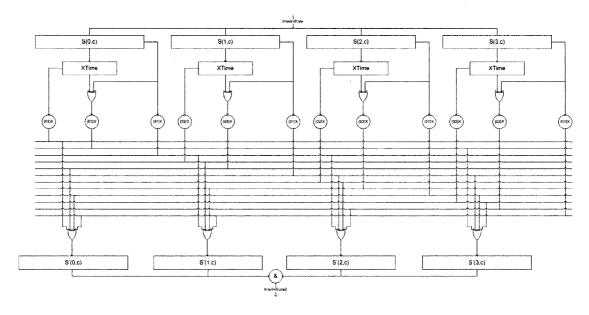

Figure 28: ENCDEC Component (Encryption / MixColumns)

The MixColumns unit is based off an implementation proposal by Zhang and Parhi [3]. The interim state is separated into four 32-bit words corresponding to the four columns of the state. Each column in turn is separated into four 8-bit subwords. An XTime unit is applied to the initial subword to produce  $\{02\}X$ . A subword's  $\{02\}X$  and the original subword are XORed to produce  $\{03\}X$ .  $\{03\}X$ ,  $\{02\}X$ ,  $\{01\}X$  and  $\{01\}X$

values are XORed together as in Chapter 2.2.3.4 to produce the transformed subwords. This is repeated for the other three columns of the state. The transformed subwords are concatenated together producing a second interim state value. This completes the MixColumns operation of the round function. This hardware unit is active for all but the final round.

The AddRoundKey unit is similar to the initialisation unit. The second interim state is XORed with the next four unprocessed subkeys of the expanded key, producing the new *State*. This completes the AddRoundKey operation of the round function, and the current round. This hardware unit is active for all rounds. The *State* produced in the final round is the AES ciphertext value for the expanded key and stored *DataIn*.

3.2.4.2 **Decryption Operation.** The last four subkeys of the expanded key are concatenated and XORed with the stored *DataIn*, producing the initial *State*. The decryption round function performs all calculations starting from the initial *State*.

The decryption round function is divided into three hardware components: an InvShiftRows/InvSubBytes unit, an AddRoundKey unit and an InvMixColumns unit. The output of InvMixColumns is the new *State* and is the input to the next iteration of the round function. The round function iterates 10 times for a 128-bit key, 12 times for a 192-bit key and 14 times for a 256-bit key.

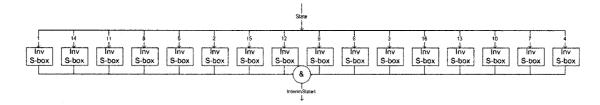

Figure 29 shows ENCDEC's InvShiftRows/InvSubBytes decryption unit.

Figure 29: ENCDEC Component (Decryption / InvShiftRows & InvSubBytes)

The functionality of the InvShiftRows and InvSubBytes operations are merged into a single hardware unit as with SubBytes and ShiftRows. The *State* is separated into sixteen 8-bit units and reordered as in Chapter 2.2.4.2. Each unit is applied to an inverse S-box that generates a corresponding value. The resulting values are concatenated together producing an interim state. This completes the InvSubBytes and InvShiftRows operations of the round function. This hardware unit is active for all rounds.