## New MOSFET Modeling Algorithms and Their Use in CAD of Analog IC Building Blocks

Kaustubha Mendhurwar

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements

for the Degree of Master of Applied Science (Electrical and Computer Engineering) at

Concordia University

Montreal, Quebec, Canada

April 2008

© Kaustubha Mendhurwar, 2008

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-40891-9 Our file Notre référence ISBN: 978-0-494-40891-9

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

### **ABSTRACT**

# New MOSFET Modeling Algorithms and Their Use in CAD of Analog IC Building Blocks

#### Kaustubha Mendhurwar

Analog integrated circuit (IC) design has undergone several technical advancements following Moore's law, and tends to become extremely challenging with the continued downscaling of the devices and supply voltages. However, not many sophisticated and detailed design tools are available to aid analog designers in exploiting the complete potential of these technical advancements. Most of the available commercial and in-house design tools model the basic building blocks (e.g. transistor) and employ these device models to predict the performance of a complete circuit/system. As such, accuracies of these device models are crucial in order to develop efficient design tools. Typically, accurate models could be complex, while simple models could be inaccurate. As such, new modeling algorithms leading to simple yet accurate device models and satisfactory design tools continued to be in great demand.

In this thesis, neural networks that offer advantages like simple calculations and a wide spectrum of applications, are employed for the modeling purpose. Firstly, new modeling algorithms based on binning concepts that offer accurate device modeling over wider input parameter space of the problems that have outputs highly non-linear to one of the inputs are proposed. Both single and multi- dimensional modeling algorithms are developed, and illustrated through device modeling examples. A new neural modeling approach based on a correction model is then introduced for the first time to develop accurate device level models for highly non-linear input-output behaviours that are difficult/impossible to model with simple structures. The proposed approach simplifies the modeling process for a novice/inexperienced designer as it eliminates the need of in depth understanding of the neural network concepts by virtue of using well known simple 3-layer MLP networks. MOSFET modeling example confirms that the approach leads to accurate neural models while keeping the model structure simple.

Finally, device models developed using the aforementioned modeling algorithms are employed to build an accurate and extendable computer aided design (CAD) tool for the design of analog IC building blocks (e.g. current sources/sinks, single stage amplifiers, simple and cascode current mirrors, voltage divider, differential amplifier, and three stage operational amplifier).

## Acknowledgements

I would like to express my sincere gratitude towards my supervisors Dr. Rabin Raut and Dr. Vijay Devabhaktuni for their tireless efforts in the advancement of my education, career and life goals. Their continued guidance and encouragement helped me overcome the usual teething troubles involved in the research. They provided me their valuable time and extensive technical knowledge from pillar to post of my thesis work.

I would also like to appreciate valuable suggestions and efforts of my colleagues in the CAD group at Concordia University, without whom, this work would not have been possible. I would like to make a mention for Rajasekhar Kakumani, Niladri Roy, Li Zhu, Arash Kashi, Navid Arbabi, Farzin Manouchehri, Mani Najamabadi, Ahmad Zbeeb, and Joshua Frankel for their continued support and friendship.

Last, but not the least, I would like to extend my heartfelt appreciation to my family (especially my brother Jay) and friends for their ongoing support and understanding.

To my loving parents Rekha & Ashok

## Table of Contents

| List of Figures xi  List of Tables xiv  List of Symbols and Abbreviations xvii |        |

|--------------------------------------------------------------------------------|--------|

|                                                                                |        |

| 1.1 Metal-Oxide Semiconductor Field-Effect Transistor (MOS                     | SFET)1 |

| 1.2 Design Automation in Analog Domain                                         | 3      |

| 1.3 Objectives and Motivation                                                  | 6      |

| 1.4 Thesis Outline                                                             | 7      |

| Chapter 2 Overview of MOSFET Modeling and Des                                  | ign 10 |

| 2.1 Introduction                                                               | 10     |

| 2.2 Analog Design Approaches                                                   | 11     |

| 2.2.1 Optimization Based Design Approach                                       | 11     |

| 2.2.2 Layout Based Design Approach                                             | 12     |

| 2.2.3 Knowledge-Based Design Approach                                          | 13     |

| 2.3 Current MOSFET Modeling Approaches                                         | . 16   |

| 2.3.1 Hand Calculation Approach                   | 16          |

|---------------------------------------------------|-------------|

| 2.3.2 Trial and Error Approach                    | 19          |

| 2.3.3 Motivation                                  | 20          |

| 2.4 Neural Network Models                         | 21          |

| 2.4.1 Introduction                                | 21          |

| 2.4.2 Multilayer Perceptrons (MLP)                | 22          |

| 2.5 Need for New Modeling Algorithms              | 29          |

| 2.6 Summary                                       | 29          |

| Chapter 3 MOSFET Modeling Based on Binning Co     | oncepts 30  |

| 3.1 Introduction                                  | 30          |

| 3.2 Standard Neural Modeling Approach             | 31          |

| 3.3 Proposed Single Dimensional Binning Algorithm | 32          |

| 3.4 Proposed Multi-Dimensional Binning Algorithm  | 35          |

| 3.5 Illustration Examples                         | 38          |

| 3.5.1 Single Dimensional Example (MOSFET)         | 38          |

| 3.5.2 Multi- Dimensional Example (MOSFET)         | 41          |

| 3.6 Summary                                       | 45          |

| Chapter 4 MOSFET Modeling Based On Correction     | n Model. 47 |

| 4.1 Introduction                                  | 47          |

| 4.2 Standard Neural Modeling Approach             | 48          |

| 4.3 Proposed ANN Modeling Approach                | 49          |

| 4.4 Illustration Example (MOSFET)              | 52 |

|------------------------------------------------|----|

| 4.5 Summary                                    |    |

| Chapter 5 Design Tool and Examples             | 56 |

| 5.1 Introduction                               | 56 |

| 5.2 Design Phases of the Tool                  | 57 |

| 5.2.1 Simulation                               | 57 |

| 5.2.2 Efficient Processing                     | 58 |

| 5.2.3 Neural Modeling                          | 59 |

| 5.2.4 Programming Interface                    | 59 |

| 5.3 Design Examples for 0.5 Micron Technology  | 60 |

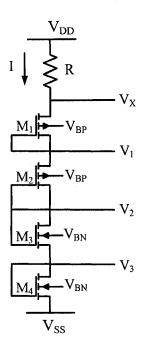

| 5.3.1 Current Sources                          | 61 |

| 5.3.2 Simple Current Mirrors                   | 62 |

| 5.3.3 Cascode Current Mirror                   | 63 |

| 5.3.4 Common Drain Amplifier                   | 64 |

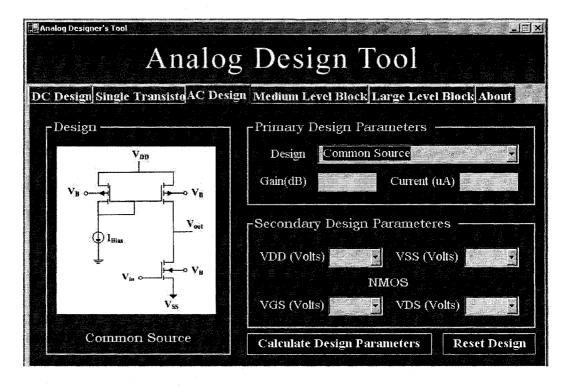

| 5.3.5 Common Source Amplifier                  | 66 |

| 5.3.6 Common Gate Amplifier                    | 68 |

| 5.3.7 Push-Pull Amplifier                      | 70 |

| 5.3.8 Validations for 0.5µm Technology         | 71 |

| 5.4 Design Examples for 0.18 Micron Technology | 72 |

| 5.4.1 Current Sources                          | 72 |

| 5.4.2 Simple Current Mirrors                   | 72 |

| 5.4.3 Cascode Current Mirror                   | 73 |

| 5.4.4 Voltage Divider                          | 74 |

| 5.4.5 Com   | mon Drain Amplifier                                 | 75         |

|-------------|-----------------------------------------------------|------------|

| 5.4.6 Com   | mon Source Amplifier                                | 76         |

| 5.4.7 Com   | mon Gate Amplifier                                  | 76         |

| 5.4.8 Push  | -Pull Amplifier                                     | 77         |

| 5.4.9 Valie | dations for 0.18µm Technology                       | 77         |

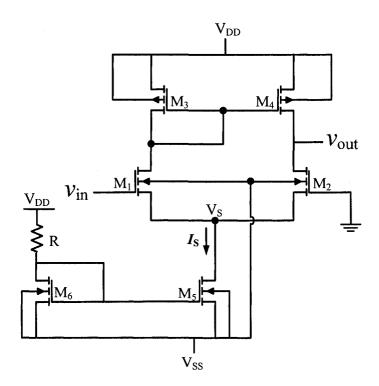

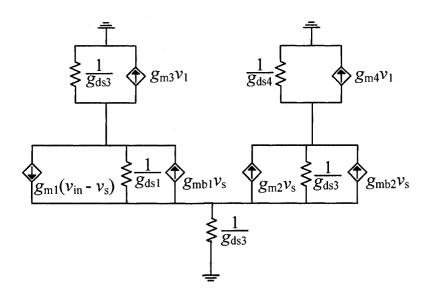

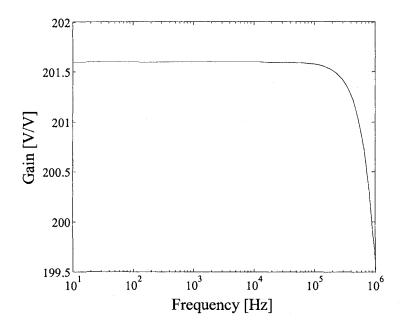

| 5.4.10 Dif  | ferential Amplifier with Active Current Mirror Load | 78         |

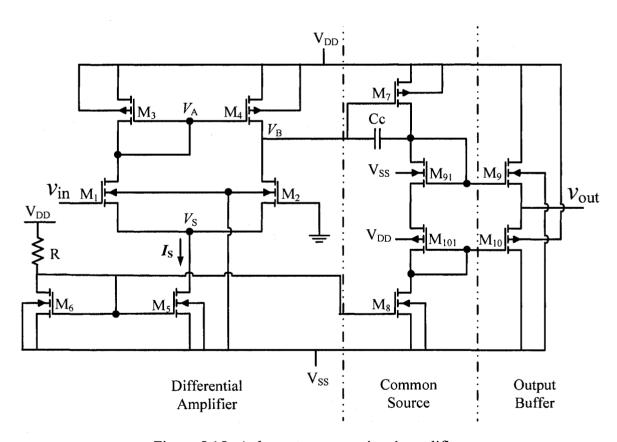

| 5.4.11 Thr  | ee Stage Operational Amplifier                      | 80         |

| 5.5 Summa   | nry                                                 | 84         |

| Chapter 6   | Conclusions                                         | 86         |

| 6.1 Contrib | outions                                             | 86         |

| 6.2 Future  | Work                                                | 89         |

| References  | · · · · · · · · · · · · · · · · · · ·               | 90         |

| Appendice   | s                                                   | 94         |

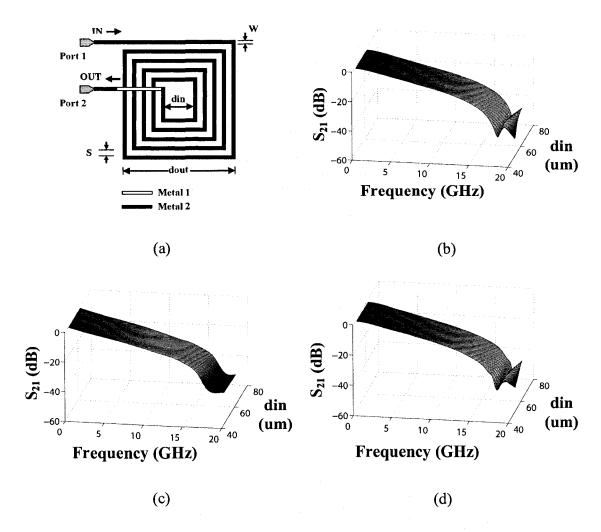

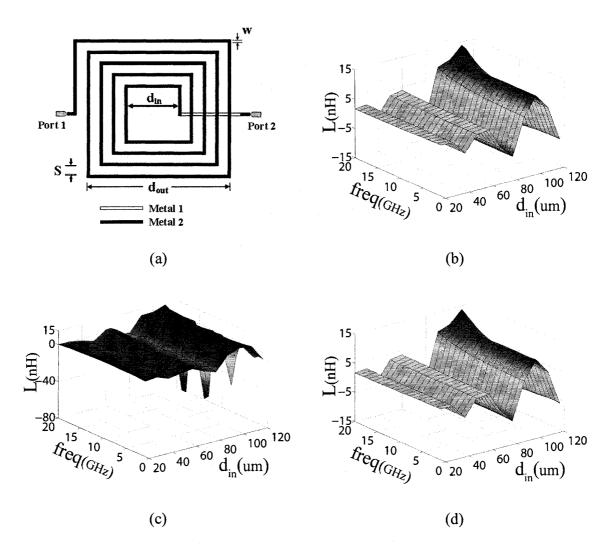

| Appendix A  | Application of Binning Concepts based Modeling A    | Algorithms |

|             | to a Passive Component                              | 94         |

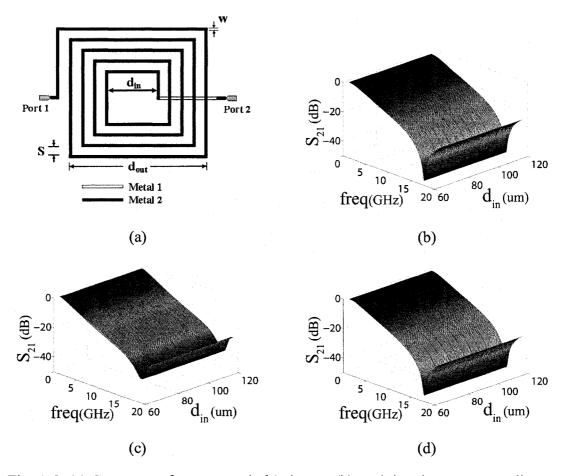

| Appendix B  | Application of Correction Model based Neural Mod    | leling     |

|             | Approach to a Passive Component                     | 100        |

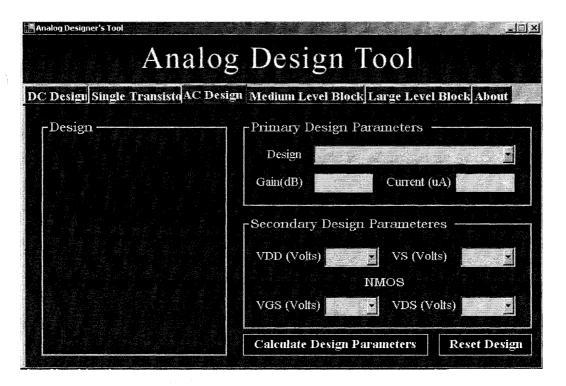

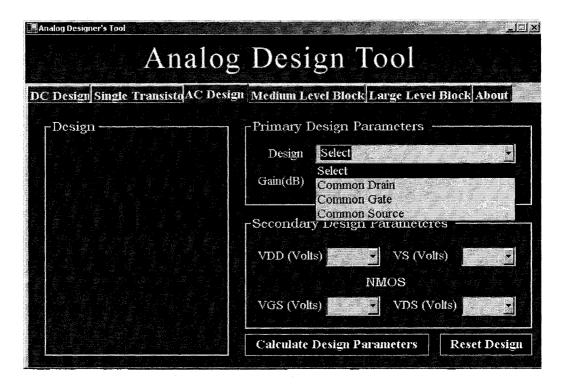

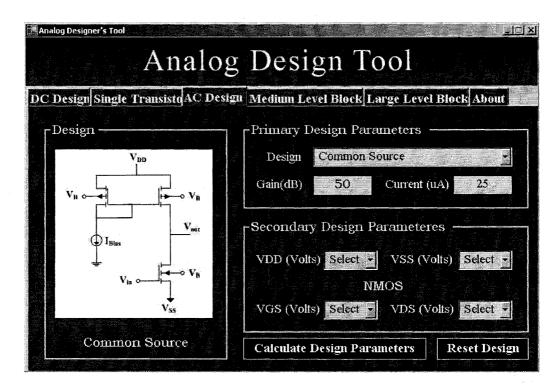

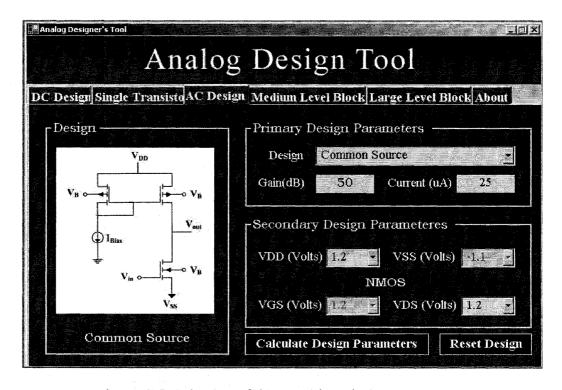

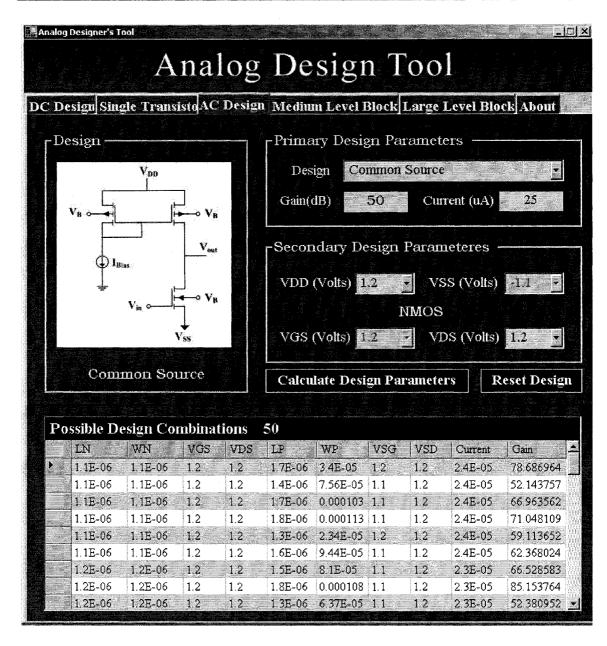

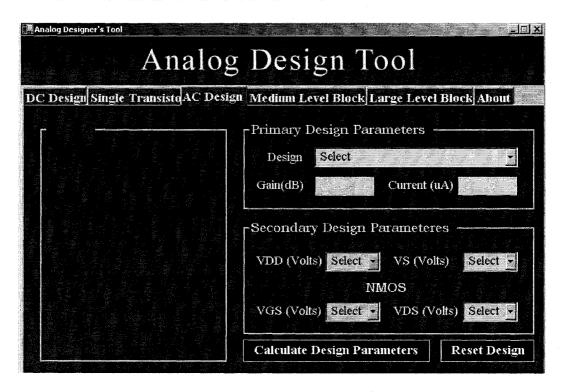

| Appendix C  | Screenshots of Single Stage Amplifier design modu   | le of the  |

|             | developed tool                                      | 103        |

| Appendix D  | Source code for Common Source Amplifier             | 108        |

## List of Figures

| Figure 1.1 | Physical structure of an NMOS transistor                                                      |

|------------|-----------------------------------------------------------------------------------------------|

| Figure 1.2 | Analog integrated circuit design process5                                                     |

| Figure 1.3 | Flowchart showcasing the outline of the thesis                                                |

| Figure 2.1 | Block diagram showcasing the hierarchy in analog circuits                                     |

| Figure 2.2 | Flowchart of the trial and error approach used in the first hand analysis of                  |

|            | transistorized circuits19                                                                     |

| Figure 2.3 | Multilayer perceptrons (MLP) network23                                                        |

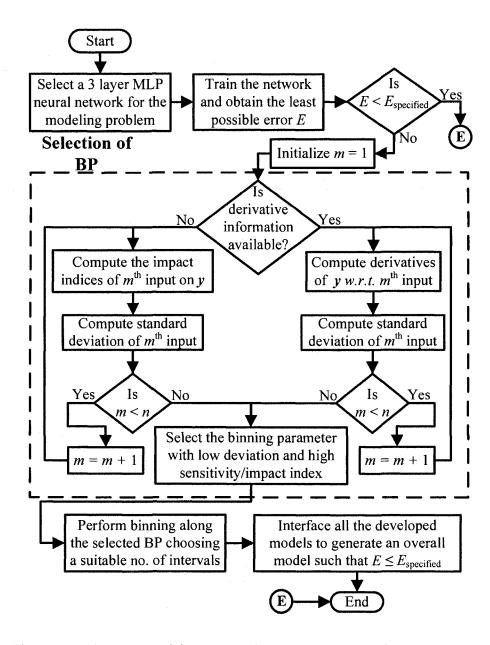

| Figure 3.1 | Flow-chart illustrating the proposed single dimensional binning algorithm                     |

|            | 34                                                                                            |

| Figure 3.2 | Overall model developed using the proposed binning algorithm (assuming                        |

|            | $x_3$ to be the binning parameter)35                                                          |

| Figure 3.3 | Flow-chart illustrating the proposed multi dimensional binning algorithm                      |

| -          | 37                                                                                            |

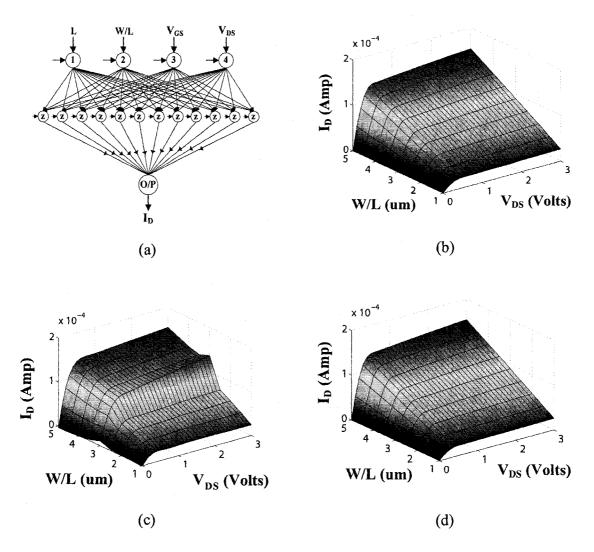

| Figure 3.4 | (a) Implemented 3-layer MLP model for the standard approach, (b)                              |

|            | Training data corresponding to $V_{GS} = 1.4 \text{V}$ , $L = 1 \text{um}$ , (c) Neural Model |

|            | responses using standard approach, and (d) Neural Model responses using          |

|------------|----------------------------------------------------------------------------------|

|            | proposed single dimensional binning algorithm40                                  |

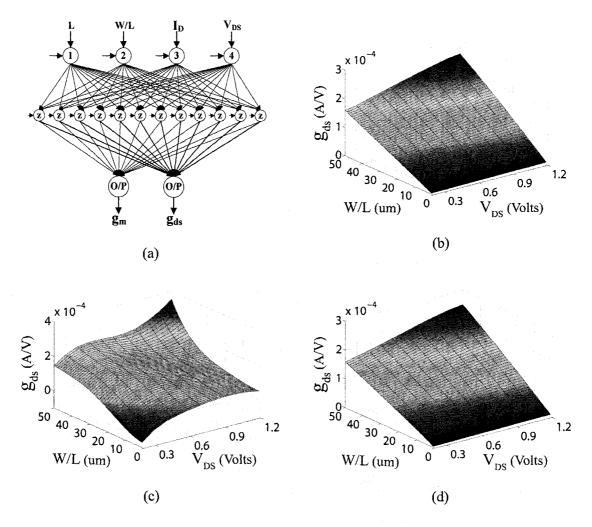

| Figure 3.5 | (a) Implemented 3-layer MLP model for the standard approach, (b)                 |

|            | Training data corresponding to $V_{\rm GS}$ = 1.4V, $L$ = 1um. (c) Neural Model  |

|            | responses using standard approach, and (d) Neural Model responses using          |

|            | proposed multi-dimensional binning algorithm44                                   |

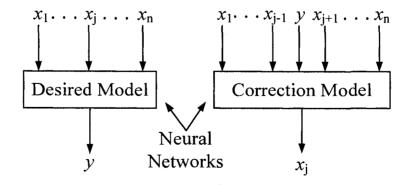

| Figure 4.1 | Pictorial depiction of desired and correction models50                           |

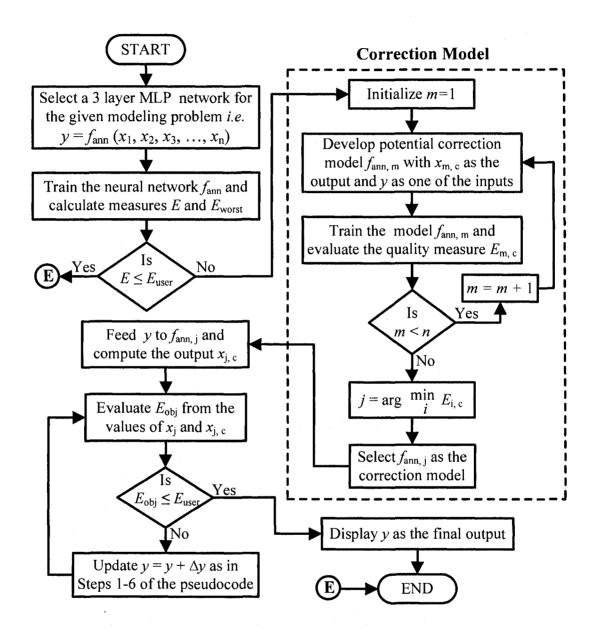

| Figure 4.2 | Flow-chart illustrating the proposed modeling approach                           |

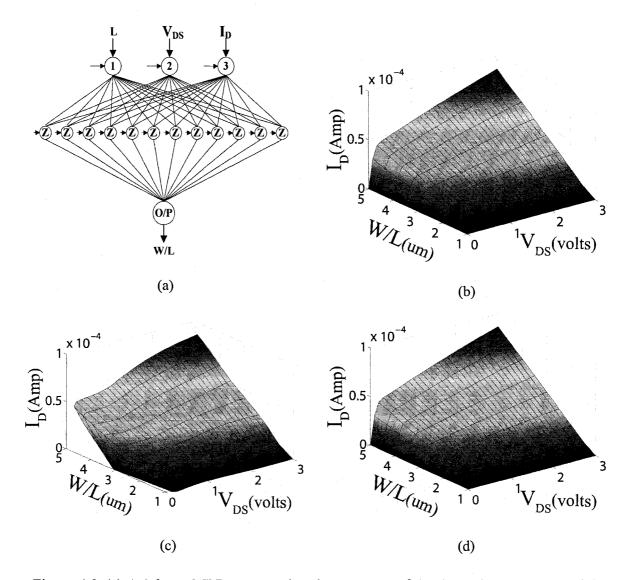

| Figure 4.3 | (a) A 3-layer MLP representing the structure of the desired MOSFET               |

|            | model, (b) Training data corresponding to $L = 0.5 \mu m$ , (c) Responses of the |

|            | stand-alone neural model, and (d) Responses of the proposed neural model         |

|            | 54                                                                               |

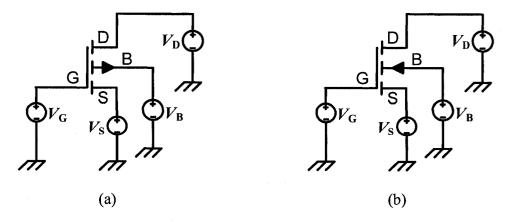

| Figure 5.1 | Transistors (a) PMOS and (b) NMOS simulated in the Cadence's HSPICE              |

|            | simulator                                                                        |

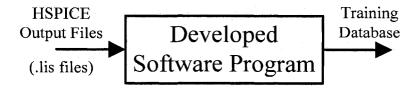

| Figure 5.2 | Block diagram of the developed software program                                  |

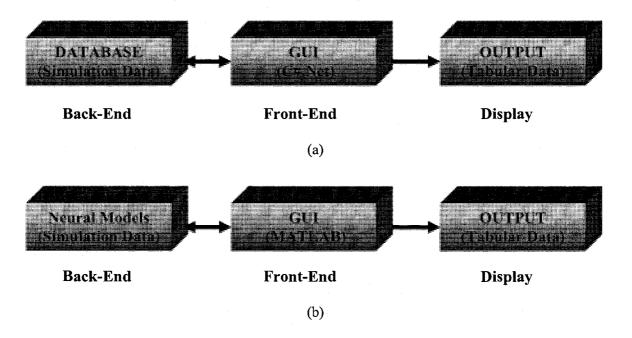

| Figure 5.3 | Architectures of the tools designed using (a) C#.Net and (b) MATLAB              |

|            | interfaces60                                                                     |

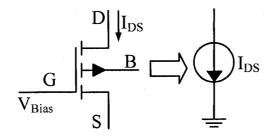

| Figure 5.4 | Basic current source and its equivalent representation61                         |

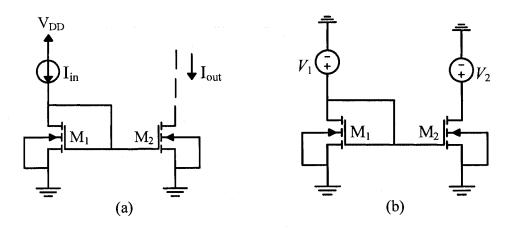

| Figure 5.5 | (a) Simple NMOS current mirror, and (b) circuit simulated in HSPICE62            |

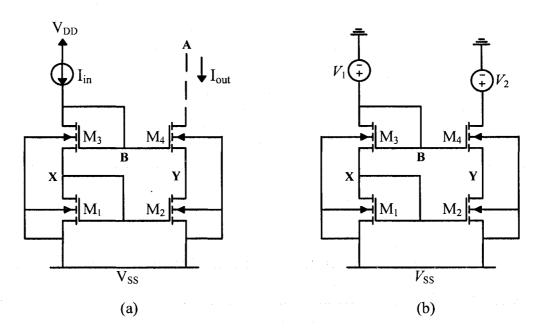

| Figure 5.6 | (a) Cascode current mirror, and (b) circuit simulated in HSPICE63                |

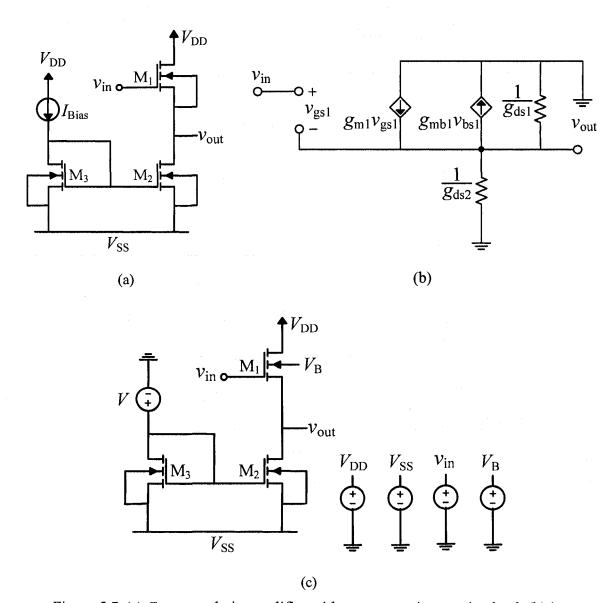

| Figure 5.7  | (a) Common drain amplifier with a current mirror active load, (b) its     |  |

|-------------|---------------------------------------------------------------------------|--|

|             | equivalent small signal model, and (c) circuit simulated in HSPICE65      |  |

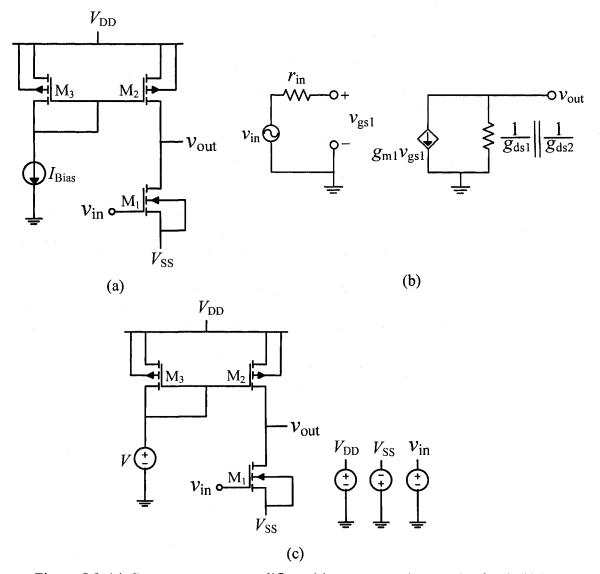

| Figure 5.8  | (a) Common source amplifier with a current mirror active load, (b) its    |  |

|             | equivalent small signal model, and (c) circuit simulated in HSPICE67      |  |

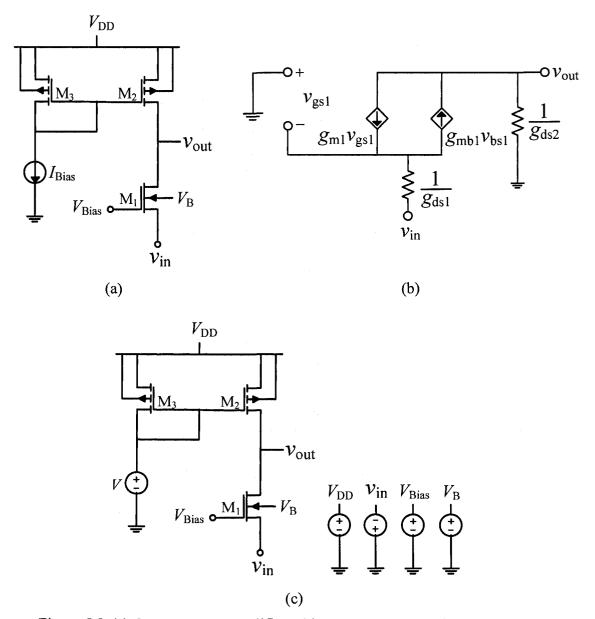

| Figure 5.9  | (a) Common gate amplifier with a current mirror active load, (b) its      |  |

|             | equivalent small signal model, and (c) circuit simulated in HSPICE69      |  |

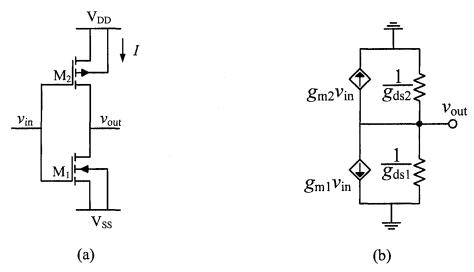

| Figure 5.10 | (a) A push-pull amplifier, (b) its equivalent small signal model, and (c) |  |

|             | circuit simulated in <i>HSPICE</i> 71                                     |  |

| Figure 5.11 | Voltage divider designed for 0.18um technology74                          |  |

| Figure 5.12 | A differential amplifier with active current mirror load                  |  |

| Figure 5.13 | An equivalent small signal model for the differential amplifier79         |  |

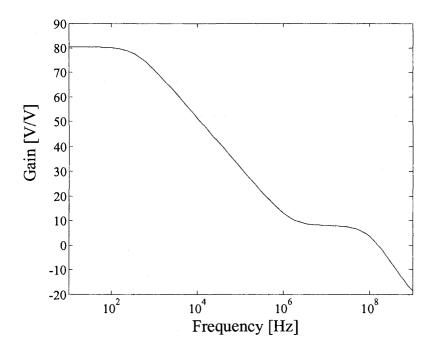

| Figure 5.14 | Gain curve of the differential amplifier plotted from the HSPICE data80   |  |

| Figure 5.15 | A three stage operational amplifier                                       |  |

| Figure 5.16 | Overall gain curve of the operational amplifier plotted from HSPICE data. |  |

|             | 84                                                                        |  |

## List of Tables

| Table 3.1 | Comparison of Model Accuracies for the Single Dimensional MOSFE      | Т  |

|-----------|----------------------------------------------------------------------|----|

|           | Example                                                              | 41 |

| Table 3.2 | Comparision of Model Accuracies for the Muti-Dimensional MOSFE       | Γ  |

|           | Example                                                              | 45 |

| Table 4.1 | Comparison of Model Accuracies for the MOSFET Example                | 53 |

| Table 5.1 | Parameters and Ranges used for the Desired Model                     | 58 |

| Table 5.2 | Design Parameters Obtained from the Tool and Their Verification from | n  |

|           | HSPICE for Current Source.                                           | 61 |

| Table 5.3 | Design Parameters Obtained from the Tool and Their Verification from | n  |

|           | HSPICE for NMOS Current Mirror                                       | 63 |

| Table 5.4 | Design Parameters Obtained from the Tool and Their Verification from | n  |

|           | HSPICE for Cascode Current Mirror                                    | 64 |

| Table 5.5 | Design Parameters Obtained from the Tool and Their Verification from | n  |

|           | HSPICE for Common Drain Amplifier with Active load                   | 66 |

| Table 5.6  | Design Parameters Obtained from the Tool and Their Verification from | 1  |

|------------|----------------------------------------------------------------------|----|

|            | HSPICE for Common Source Amplifier with Active load                  | 68 |

| Table 5.7  | Design Parameters Obtained from the Tool and Their Verification from | 1  |

|            | HSPICE for Common Gate Amplifier with Active load                    | 70 |

| Table 5.8  | Design Parameters Obtained from the Tool and Their Verification from | ì  |

|            | HSPICE for Push-Pull Amplifier                                       | 71 |

| Table 5.9  | Design Parameters Obtained from the Tool and Their Verification from | 1  |

|            | HSPICE for Current Source.                                           | 72 |

| Table 5.10 | Design Parameters Obtained from the Tool and Their Verification from | ì  |

|            | HSPICE for NMOS Current Mirror                                       | 73 |

| Table 5.11 | Design Parameters Obtained from the Tool and Their Verification from | ì  |

|            | HSPICE for Cascode Current Mirror                                    | 73 |

| Table 5.12 | Design Parameters Obtained from the Tool and Their Verification from | ì  |

|            | HSPICE for Voltage Divider                                           | 75 |

| Table 5.13 | Design Parameters Obtained from the Tool and Their Verification from | 1  |

|            | HSPICE for Common Drain Amplifier with Active load                   | 75 |

| Table 5.14 | Design Parameters Obtained from the Tool and Their Verification from | 1  |

|            | HSPICE for Common Source Amplifier with Active load                  | 76 |

| Table 5.15 | Design Parameters Obtained from the Tool and Their Verification from | 1  |

|            | HSPICE for Common Gate Amplifier with Active load                    | 77 |

| Table 5.16 | Design Parameters Obtained from the Tool and Their Verification from |

|------------|----------------------------------------------------------------------|

|            | HSPICE for Voltage Divider7                                          |

| Table 5.17 | Design Parameters Obtained from the Tool and Their Verification from |

|            | HSPICE for a Diffrential Amplifier with Active Current Mirror Load79 |

| Table 5.18 | Design Parameters Obtained from the Tool and Their Verification from |

|            | HSPICE for a Three Stage Operational Amplifier83                     |

## List of Symbols and Abbreviations

$\eta$  Learning rate

kT/q Thermal voltage

γ Body effect constant

$\lambda$  Body effect parameter

$2\phi_{\rm F}$  Surface potential parameter

$\mu_n$  Charge-carrier mobility

A/D Analog to digital

AM Amplitude modulation

ANN Artificial Neural Network

A<sub>V</sub> Open loop gain

BSIM Berkely short-channel IGFET model

BP Binning parameter

CAD Computer aided design

CMOS Complementary metal oxide semiconductor

CNT Carbon nano tube

Cox Gate capacitance across the oxide per unit area

CPU Central processing unit

D/A Digital to analog

DA Design automation

DC Direct Current

$E_{\text{avg}}$  Aggregate error measure

$E_{\rm C}$  Critical field

$E_{\rm user}$  User-specified error

E<sub>worst</sub> Worst-case error

$g_{ds}$  Output conductance

g<sub>m</sub> Transconductance

g<sub>mb</sub> Body effect transconductance

GUI Graphic user interface

$I_{\text{bias}}$  Biasing current

IC Integrated circuits

$I_{\rm DS}$  Drain source current

KBNN Knowledge based neural networks

L Effective gate length of the transistor

MLP Multi layer perceptrons

MNT Micro nano technology

MOS Metal oxide semiconductor

MOSFET Metal oxide semiconductor field effect transistor

NMOS N channel metal oxide semiconductor

OPAMP Operational amplifier

OTA Operational transconductance amplifier

PMOS P channel metal oxide semiconductor

V Volts

$V_{\rm BS}$  Bulk source voltage

$V_{\rm DD}$  Supply voltage

$V_{\rm DS}$  Drain source voltage

$V_{\rm Dsat}$  Drain saturation voltage

$V_{\rm GS}$  Gate source voltage

$V_{\rm T}$  Threshold voltage

$V_{T0}$  Zero bias threshold voltage

W Gate width of transistor

μA Micro ampere

μm Micro meter

μW Micro watt

## CHAPTER 1

### Introduction

# 1.1 METAL-OXIDE SEMICONDUCTOR FIELD-EFFECT TRANSISTORS (MOSFETS) AND THEIR MODELS

Recent advances in MOSFET technology, such as the continued downscaling of the physical dimensions, use of higher electric fields and continuing decrease in the power supply voltage, have made their behavior highly useful yet complex. Unfortunately, these technological advancements have not been followed up with concurrent improvements in analog design approaches. Most of the analog design approaches are still employing the

methods based on much simpler first hand approximations of MOSFET behavior. This has created an unwanted scenario, in which the circuit designers are applying outdated methodologies on newer technologies. As such, designers may not be able to realize the entire potential of modern deep submicron complementary metal-oxide semiconductor (CMOS) technology [1].

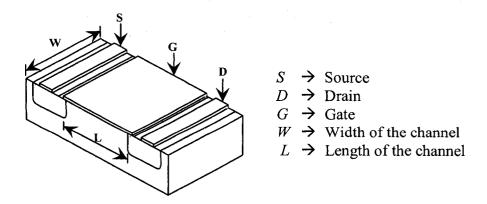

Transistors are key components in modern circuit design. Transistor based circuits are used globally, not only in analog but in digital circuits as well. Furthermore, transistors are more often than not the basic building blocks on which performance of the entire circuit depends. Playing such an important role in a multitude of circuits, one would think that the perfect understanding of its operation would be paramount. Unfortunately, this is not the case. Several slow and cumbersome methods (to be discussed in detail in chapter 2) are available that are based on approximations/assumptions. These assumptions may not hold true in every situation but often assumed to be true. As such, the development of new modeling methods for this key component becomes important. Geometrical/physical parameters involved in transistor modeling are illustrated by the physical structure of an NMOS transistor, depicted in Fig. 1.1.

Figure 1.1 Physical structure of an NMOS transistor.

A typical design problem for analog designers is to determine functional relationship f such that

$$[L, W/L] = f(V_{BS}, V_{GS}, V_{DS}, I_{D}),$$

(1.1)

where, L and W represent length and width of the MOS transistor.  $V_{\rm BS}$ ,  $V_{\rm GS}$ , and  $V_{\rm DS}$  represent the bulk voltage, gate voltage, and drain voltage respectively, and  $I_{\rm D}$  represent the drain current.

As a side note, it is imperative to acknowledge that the design of the MOSFET has the potential to affect the overall design of several widely used building blocks *e.g.* current sinks/sources, current mirrors, differential amplifier, *etc.* It is therefore substantial that the MOSFET be designed with utmost diligence. Device modeling is critical/vital to enabling design automation of circuits and systems.

#### 1.2 DESIGN AUTOMATION IN ANALOG DOMAIN

Analog design is known to be a knowledge-intensive, multiphase, and iterative task. It usually stretches over a significant period of time and is performed by designers with a large portfolio of skills [2]. Text books as well as publications may not be readily useful in exploiting good design techniques for successful analog circuit generation as these techniques reside mainly in the experience and expertise treasured by relatively very few analog designers. The advent of computers has led to what are known as Computer Aided Design (CAD) tools or design automation (DA) tools. Typically, a CAD or DA tool is a computerized program/software that assists circuit designers in the accomplishment of a design objective. The CAD tools have a property to automate a part/whole of the design

process. Silicon compilers fall in this category of CAD tools as they produce integrated circuit layouts straight from certain higher level specifications [3][4].

In the recent years, smaller feature sizes and higher scales of integration have resulted in an increased circuit design complexity. In order to deal with the design complexity, the need for automated design tools arises, as does the need for optimization tools to be able to automate several aspects of the design process while adhering to the tight process technology constraints [4]. Irrespective of the technological advancements in the analog domain, analog CAD tools still are in the nascent stages. In particular, in terms of design time, analog CAD tools lag considerably in comparison with the thoroughly detailed and highly sophisticated digital CAD tools. An example typically quoted is that while 90% of an integrated circuit may be digital with only 10% analog, most of the design time and effort is still devoted to the analog part.

Since the real-world signals are analog in nature, implementation of both analog and digital functionalities on the same chip has always been a necessity as well as a design challenge. Hence, for the efficient design of analog integrated circuits, present and future trend is to develop more robust industrial analog CAD tools. These tools are designed with primary focus on the evolution in areas like, circuit and system synthesis, symbolic analysis, automated layout generation, and testing and optimization of the circuit designs to meet critical specifications of the high-performance designs.

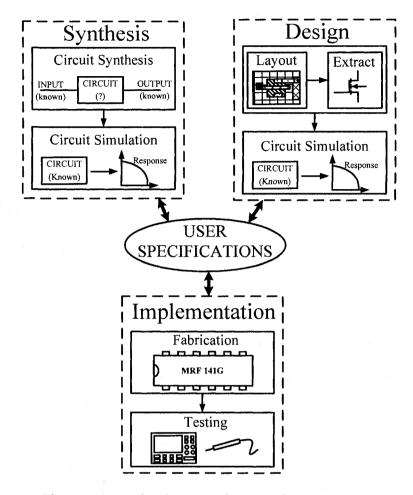

The analog integrated circuit (IC) design process is comprised of three major phases, namely (i) synthesis, (ii) design, and (iii) implementation. These three phases of analog integrated circuit design process are depicted, in detail, in Fig. 1.2.

Figure 1.2 Analog integrated circuit design process.

(i) Synthesis: This phase focuses on identifying the circuit topology that satisfies given input-output behavior. This phase can be tiresome as sometimes there can be no solution and more often the solution is not unique. Analog circuits, especially the most useful and frequently needed, are rarely novel in the strict sense of the word [2]. Most often same building blocks are adjusted and tailored to suit the specific application goals. As such, the synthesis phase is not that crucial in analog IC design. Designers can deal with and can predict performance of circuits, comprising of fewer transistors, confidently owing to their design expertise/experience. Designers often make appropriate assumptions/guesses in terms of the initial circuit, based on their design experience and expertise.

(ii)Design: This phase deals with the actual design of the circuit obtained in the synthesis phase. In this phase, circuit designers have to find meaningful values for components of the circuit obtained from synthesis that satisfy the design goals. Simulators e.g. HSPICE contribute a great deal in this phase, as simulation is the only means to foresee the circuit response without actually fabricating the circuit. There are numerous design approaches (discussed in detail in chapter 2), and an appropriate one is selected depending on the design specifications. The design process is tedious as identifying the design variables that should be tuned, itself requires considerable design expertise. Furthermore, the decision about direction and amount of tuning relies on the designer's knowledge and experience on the circuit under consideration. As a result, designers invest enormous amount of time in fine tuning the design variables, in order to satisfactorily meet the user specifications. In conclusion, it may be noted that the design/optimization loop requires knowledge of a multitude of disciplines, and can be unending for a novice designer. (iii) Implementation: This is the concluding phase of the process, where the designed circuit is fabricated and tested extensively for the given user specifications. Depending on

In essence, all of the above phases would benefit tremendously from research and development of CAD tools.

the testing results, fabricated circuits are either sent for mass production or back to the

#### 1.3 OBJECTIVES AND MOTIVATION

designers for further fine tuning.

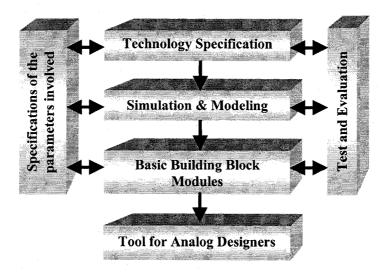

As mentioned earlier, this thesis is primarily motivated by an aspiration to simplify the complex and time consuming design automation process for analog circuits. Scarce efforts

involved in analog domain to augment the present status of available design automation tools, only aggravate the problem for analog designers. Research in the design automation area is inadequate to match the technological advancements and as a result, prevents the complete exploitation of advanced technologies. Dearth of design expertise in the analog domain is the major driving force for the need of design automation tools. Therefore, the principal objective of this thesis is to introduce some new modeling algorithms at the device level, to produce accurate device models, and employ those models at the circuit level to aid and enhance the design process. From an industry perspective, this work is practical as it intends to make the design process simple and technology independent for novice users. Detailed objectives of the thesis work are depicted in Fig. 1.3.

Figure 1.3 Flowchart showcasing the outline of the thesis.

#### 1.4 THESIS OUTLINE

In essence, this thesis provides new modeling algorithms that help develop accurate and advanced device models. The device models are employed as basic building block modules at the circuit level leading to a CAD tool for analog designers to design basic to

complex circuits. Finally, application of this tool to  $0.5~\mu m$  and  $0.18~\mu m$  technologies is illustrated through several design examples.

Chapter 2 commences with some analog design history and importance of MOSFET modeling, followed by some background theory on commonly used MOSFET modeling approaches and artificial neural networks (ANN) that is relevant to the thesis objectives. In-practice modeling approaches are briefly described and the need for new modeling methods/techniques is discussed. Neural networks, as the potential modeling approach, is manifested through basic theory, their implementation areas, and the benefits they offer.

Chapter 3 introduces two novel MOSFET modeling algorithms based on the concept of binning. Single and multi-dimensional binning algorithms are proposed and showcased using neural networks as a case study. Proposed algorithms help model devices that show a relatively linear behaviour along certain axes and more non-linear behaviour along other axes. The chapter concludes with application of proposed algorithms to modeling problem on hand (*i.e.* MOSFET modeling).

Chapter 4 introduces a new neural network modeling approach based on a correction model concept for accurate modeling of devices/components. A detailed flow-chart of the proposed modeling approach is presented along with a pictorial depiction of the concept. The proposed approach helps model the problems that are difficult/impossible to model using the standard neural modeling approach. It has the potential to simplify the modeling process for a common user, without much background knowledge. In the final section of this chapter, the proposed approach is employed to design problem of a MOSFET.

Chapter 5 showcases the design tool, developed as a part of this thesis, employing the modeling algorithms presented in chapters 3 and 4, in detail with all its development

phases described briefly. Several design examples for 0.5 µm technology are provided along with the simulation verification results. In addition, the design tool is extended for 0.18 µm technology, and design examples from basic block *e.g.* current source/sink to advanced/complex block *e.g.* a three stage operational amplifier for 0.18 µm technology are presented.

Chapter 6 provides a discussion on the thesis' contributions as well as possible future extension of the work.

Finally, four appendices are included for better reader comprehension. Appendix A provides passive domain examples of modeling algorithms based on the binning concept. Appendix B contains passive domain example of the neural modeling approach based on a correction model. Appendix C illustrates the common source amplifier module of the developed design tool through snapshots. Appendix D provides the sample code of the common source amplifier module.

### CHAPTER 2

### **OVERVIEW OF**

### MOSFET MODELING AND DESIGN

#### 2.1 Introduction

As discussed earlier, MOSFET is more often than not the basic building block on which performance of the entire circuit depends. As such, MOSFET modeling is crucial. In this chapter, top-to-bottom approach is adopted for explaining the MOSFET modeling concept properly. Starting with the complete system *i.e.* design automation; first a brief summary of the analog design approaches used in the design automation is presented. Moving on to the basic building block *i.e.* MOSFET, significance of MOSFET modeling for the design of analog IC is discussed, and some of the currently employed MOSFET

models for the design/analysis of circuits containing MOSFETs are reviewed. Limitations of these models are put forward, and possible alternate models (e.g. neural networks) that can potentially address those limitations are reviewed. It should be understood that when a device or circuit being modeled is complex and/or the model being developed is expected to cover a wider input parameter space, two or more modeling techniques can be combined [5] to meet the desired objective.

#### 2.2 ANALOG DESIGN APPROACHES

Progress, in terms of the technological advancements, in the analog domain has been substantial. However, research in the analog design automation has been relatively slow. Consequently, not many new tools are developed to aid the analog designers in modeling and designing state of the art analog circuits [6]. This section provides a brief summary of the design approaches, generally employed in commercial and in-house CAD tools.

#### 2.2.1 Optimization Based Design Approach

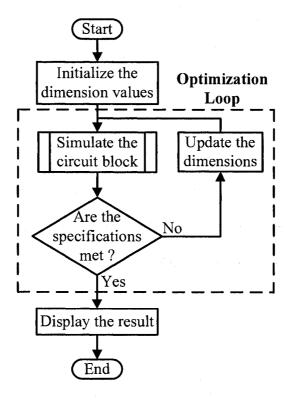

One of the commonly used analog design approaches was optimization based. In such an approach, sizing of a transistor (*i.e.* geometry of a transistor) for a user-specified circuit topology is formulated as an optimization problem. This concept is reported to be adapted in DELIGHT.SPICE [7], ECSTACY [8], and ADOPT [9]. Transistor sizes are adjusted in an iterative fashion, to satisfactorily meet the user-specifications, employing various optimization tools (e.g. Newton Raphson, Quassi Newton, steepest descent, *etc*). The optimization loop is comprised of a simulator that evaluates the circuit performance at the end of each iteration, and an update block.

Optimization based design approaches have the following limitations.

- Selection of optimization algorithm: Selection of a good and appropriate optimization algorithm is vital. Poor choice of optimization algorithm can lead to a local minimum.

- Selection of optimization variables: Selection of apt optimization variables is crucial in this approach and design expertise is the key to successful completion of this step.

- *Initial values:* Setting initial values of the optimization variables is an important step in this approach. Lack of design experience can lead to a local minimum, thereby making the optimization meaningless.

- Design experience: As discussed in the afore-mentioned steps, a designer should have certain design experience not only regarding the circuit under test, but also with the optimization algorithm used, in case of potential convergence problems.

- Speed: This approach could be tedious/tiresome in situations where optimization step enters an infinite loop (e.g. getting stuck in some local minima).

- Lack of design expertise and patience: Design expertise and patience are two of the chief qualities required in the designer and their deficiency makes this design approach difficult/impossible to be employed.

#### 2.2.2 Layout Based Design Approach

This approach borrows its theme from the extensively used standard cell, gate array, and parameterized cells found in the digital domain [10]. This approach is also referred to as semi-custom/bottom-up approach because of the designs being primarily controlled by layout. In analog domain this concept is implemented with the help of numerous predesigned blocks of various sizes/configurations. However, this design approach suffers a serious drawback in terms of the design flexibility for performance analog circuits. Pre-

designed blocks implemented in this approach can realize only a small number of discrete points whereas the analog circuits have a wide spectrum of continuous space. A high amount of silicon is wasted in the design of these blocks, making them a costly affair.

Standard cells that are pre-designed and laid-out blocks of varying complexity, residing in the database of the design automation system, address the issue of silicon usage[11]-[13]. These cells, although very popular in the digital domain, are not practical in the analog domain owing to the difficulty in maintaining a rich enough library of these cells to accommodate such a wide spectrum of possible applications in analog domain.

Parameterized cells reported in AIDE2 [14] and CONCORDE [15] improve on the issue of flexibility as these cells fully or partly are customized according to the required function. However, these fixed-layout configurations impose/enforce major restrictions in terms of performance of the analog circuits.

#### 2.2.3 Knowledge-Based Design Approach

This approach employs the available knowledge of the circuit/system to design it. As such, this approach offers the maximum flexibility and therefore covers a wide spectrum of the circuit's performance owing to its fully customized design methodology. A circuit grammar, adapting this concept, to generate bipolar operational amplifiers (OPAMPs) is presented in [16]. However, this approach can not be extended to handle transistor sizing in MOS integrated circuits. Also the grammar itself follows certain conventions, and as such can restrict the approach in the design of unconventional designs. Highly popular design topologies among the designers, namely (i) *Hierarchical*, (ii) *Fixed-Topology* and (iii) *Combined Hierarchical and Fixed Topology*, are reviewed briefly below.

(i) Hierarchical Approach: The underlying idea of this approach is to segment the entire circuit into finite distinct blocks. Each of these blocks is assigned a set of specifications so as to satisfactorily meet the desired circuit performance, when are put together. Thissegmentation/partition process is repeated for finite blocks at various hierarchical levels, and number of levels depends on the circuit being designed, and grammar of the design system. This partition is performed with the help of domain knowledge and hence a great deal of domain knowledge is required.

The knowledge is mainly in the form of design equations and heuristics (basic rules that convey circuit performance upon variations in design parameters). Systems designed with this approach have the highest degree of freedom. Hence, a comparatively small architecture library can lead to a large number of different topologies. Systems designed using this approach are easy to extend and maintain, and make better use of the existing design knowledge. This approach is reported to be adopted in tools like PROSAIC [17], BLADES [18], OASYS [19], and An\_Com [20].

(ii) Fixed-Topology Approach: This approach employs a sizing method to compute apt sizes (i.e. geometry) of the devices with the given fixed circuit topology. These fixed, unsized, device level circuit topologies are stored in a knowledge base together with the necessary domain knowledge for dimensioning the devices [21]. The domain knowledge to be stored depends on how the device sizes are computed. This approach is employed in IDAC [22], OPASYN [23], and OAC [24]. This approach takes into account, only the device dimensions as the legitimate design variables, thereby imposing the strictest limits on the design flexibility among the various knowledge-based approaches.

(iii) Combined Hierarchical and Fixed Topology Approach: In this approach, features of hierarchical and fixed topology approaches are combined. The circuit topology is put together in a hierarchical manner whereas the sizing of transistors is done in a fashion similar to that in the fixed topology. Consequently, this approach offers a higher degree of design flexibility. However, systems designed using this approach are not as flexible as the systems designed using the full-custom hierarchical approach. This approach is presented elaborately in ASAIC [25] and CAMP [26][27].

All the above reviewed approaches have their own advantages and are implemented by various commercial and in-house design tools. However, insufficient use of simulators during the design phase, longer design time, lack of accuracy, and storage space for the knowledge database are some of the limitations imposed. As a part of this thesis work, a design tool is developed exploiting advantages offered by hierarchical and fixed topology approaches. New modeling algorithms are proposed to replace highly accurate but CPU intensive simulators and are used optimally to improve the accuracy of the design.

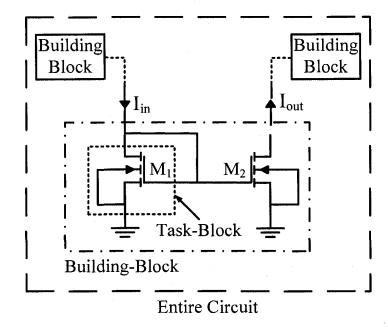

Hierarchical approach offers reusability of design knowledge by breaking down large and complex circuits into smaller building blocks. Building-blocks, extensively used in circuit design, are simple circuit-blocks that carry out fundamental functions. Current source/sink, current mirror, source follower are few classic examples of building-blocks used in numerous circuits. These blocks are generally comprised of some smaller device-blocks commonly referred as task-blocks (see Fig. 2.1). As discussed earlier, MOSFETs can be considered as the task-blocks in analog domain and breaking of a large circuit to task-block generalizes the circuit design process and ensures the optimum knowledge reusability. As such, accurate modeling of MOSFET is crucial and is discussed further.

Figure 2.1 Block diagram showcasing the hierarchy in analog circuits.

#### 2.3 REVIEW OF MOSFET MODELING APPROACHES

Device modeling is a bottleneck to design tools; consequently, a robust modeling approach for the modeling purpose is needed. In this section some of the device level (*i.e.* MOSFET level in this case) modeling approaches are reviewed.

#### 2.3.1 Hand Calculation Approach

Commonly used approaches to analog design usually involve some sort of hand calculations. These hand calculations at times can be very lengthy and complex. They are carried out based on assumptions that do not hold true in all the situations. In the hand calculation approach, empirical equations are employed that are solved by the designer to calculate the physical dimensions of the device. Some of the empirical equations used in a first hand calculation approach are listed below.

In the linear/triode region, the Drain Current  $(I_D)$  is calculated as [28]

$$I_{\rm D} = k' \frac{W}{L} \left[ (V_{\rm GS} - V_{\rm T}) V_{\rm DS} - \frac{{V_{\rm DS}}^2}{2} \right]$$

(2.1)

In the Drain in saturation region, the Current  $(I_D)$  is calculated as

$$I_{\rm D} = \frac{k'W}{2L} (V_{\rm GS} - V_{\rm T})^2 (1 + \lambda V_{\rm DS})$$

(2.2)

In the velocity saturated region, the Drain Current  $(I_D)$  is calculated as [29]

$$I_{\rm D} = \frac{1}{1 + \left(\frac{V_{\rm DS}}{E_{\rm C}L}\right)} k' \frac{W}{L} \left[ (V_{\rm GS} - V_{\rm T}) V_{\rm DS} - \frac{{V_{\rm DS}}^2}{2} \right] (1 + \lambda V_{\rm DS})$$

(2.3)

In the sub-threshold region, the Drain Current  $(I_D)$  is calculated as

$$I_{\mathrm{D}} = I_{\mathrm{S}} e^{\frac{V_{\mathrm{GS}}}{\eta k T/q}} \left( 1 - e^{\frac{V_{\mathrm{DS}}}{\eta k T/q}} \right) \tag{2.4}$$

The Threshold Voltage  $(V_T)$  is given by

$$V_{\rm T} = V_{\rm T0} + \gamma \left( \sqrt{|-2\varphi_{\rm F} + V_{\rm SB}|} - \sqrt{|-2\varphi_{\rm F}|} \right), \tag{2.5}$$

and

$$k' = \mu_{\rm n} \times C_{\rm OX} \tag{2.6}$$

where,

W: Gate width of the transistor.

L : Effective gate length of the transistor.

V<sub>GS</sub> : Gate source voltage.V<sub>T</sub> : Threshold voltage.

$V_{\rm DS}$ : Drain source voltage.

$\lambda$ : Body effect parameter.

$E_{\mathbf{C}}$ : Critical Field.

$I_{\rm S}$ : Current in strong inversion region.

$\eta$  : Sub-threshold slope factor.

kT/q: Thermal voltage.

$V_{T0}$ : Zero bias threshold voltage.

$\gamma$ : Body effect constant.

$2\phi_{\rm F}$  : Surface potential parameter.

$V_{\rm SB}$ : Source bulk voltage.

$\mu_n$ : Charge-carrier mobility.

$C_{\text{ox}}$ : Gate capacitance across the oxide per unit area.

These hand calculations are based on first-hand knowledge of the device, and could fail for the modern sub-micron CMOS technology. For instance, in large MOSFETs (*i.e.* MOSFETs having larger L), the classical "square-law" current-voltage (I-V) is valid for transistors operating in strong inversion and saturation, while a simple exponential I-V relation works well in sub-threshold region (*i.e.* weak inversion). In the extreme short channel limit, the "square-law" becomes linear and also loses its 1/L dependence.

Apart from these cases, accurate hand calculation methods are not available for the MOSFET. One can use  $V_{\rm DS}-g_{\rm ds}$  trade-off through the simulation to resolve the problem. A study of various analog design texts shows that this problem is overcome largely by ignoring it. Use of these assumptions has tended not to be fatal, since there has been a considerable margin for error. However, in modern processes, there is little margin for such error. For instance, consider a simple cascode circuit with two transistors and a load. Tolerance for voltage margins in the calculation of  $V_{\rm Dsat}$  (drain saturation voltage) is small, since the "voltage budget" across these three elements is very tight. Designers are

forced to use lower DC gate voltages to keep the transistors biased in saturation. This forces transistors to be biased in moderate inversion (rather than strong inversion), a region where there are no good hand calculation formulae. Hence, a more modern and coherent approach for the design and analysis of MOSFET based circuits is required.

#### 2.3.2 Trial and Error Approach

Trial and error is another popular approach used in analog design. This approach is explained with the help of the flowchart depicted in Fig 2.2. In this approach, first, device dimensions are initialized and simulator is employed to check the circuit performance. Values are updated iteratively until the circuit response obtained from the simulator block satisfactorily meets the given user specifications. The simulator block used ensures more accurate design of the circuit/system.

Figure 2.2 Flowchart of the trial and error approach used in the first hand analysis of transistorized circuits.

From the flowchart shown in Fig 2.1, it is obvious that the process is iterative in nature. As in any iterative process, modifications are made at each iteration. Should these modifications be improperly done, the approach can turn into a not so useful infinite loop. In simpler words it can be said that, this process demands experience from a designer so as to ensure proper transitions from one iteration to the next. Once again, the problem lies in the shortage of experienced designers.

This process is fairly tedious, and can be highly frustrating for a designer who does not have good intuition. Even if a designer has experience, achieving correct results in a short time may not always be possible, and finally, since the approach involves manual intervention, it is slower as compared to the automated processes.

#### 2.3.3 Motivation

On one hand, there are several existing modeling approaches that are simple but each with their own limitations. One common disadvantage of all the discussed systems lies in the insufficient use of circuit simulators. Circuits designed from the knowledge (based on available equations) do not necessarily meet user specification, since the equations used to design the circuit usually suffer in terms of accuracy. Few systems incorporate circuit simulators in a loop to design a circuit by iteratively sizing various devices employing numerical algorithms or expertise/heuristics. These systems have potential to produce more efficient designs; however, these systems suffer in terms of longer design time owing to numerous iterations, and hence limit the circuit design exploration.

On a positive side, there are some physics based device simulators that simulate a device accurately but can be cumbersome (e.g. Minimos) and accurate models but with too many parameters (e.g. BSIM3). It would be nice to develop compact models using

accurate data from such simulators. In the following sections, neural network modeling approach is discussed that has a potential to achieve the accurate compact models for the data obtained from device/circuit simulators.

#### 2.4 Neural Network Models

#### 2.4.1 Introduction

Neural networks, also called artificial neural networks (ANNs), are the information processing systems with their design inspired by studies of the ability of the human brain to learn from observations and to generalize by abstraction [30]. The very fact that neural networks can be trained to learn any arbitrary nonlinear input—output relationships from corresponding data has resulted in their use in areas such as pattern recognition, speech processing, control, biomedical engineering, *etc* [31]. ANNs have been applied to the modeling of semiconductor devices, circuits and their fabrication processes as well.

Neural networks are first trained to model the electrical behavior of active/passive devices/components. These trained neural networks, often referred to as neural-network models (or simply neural models), can then be used in high-level simulation and design, providing fast answers to the task they have learned. ANNs are efficient alternatives to conventional methods like numerical modeling methods, which could be computationally expensive, or analytical methods, which could be difficult to obtain for new devices, or empirical models, whose range and/or accuracy could be limited [32][33].

A neural network is a set of mathematical equations representing a physical model, relating its output vector  $\mathbf{v}$  to its input vector  $\mathbf{x}$ . The neural model can then be stated by

$$y = f_{\text{ann}}(x, w), \tag{2.7}$$

where  $f_{ann}$  is the neural network and w represents a vector of model parameters. Hence, as with any other mathematical modeling techniques, neural networks can also be used to model laboratory data sets. The objective of the neural network approach is to determine w by a "learning process" using the given input-output laboratory data set. Once the w is determined, the neural model can be used to simulate the phenomenon represented by the given data. One of the main advantages of ANNs is that the output and the input vectors (y and x) can be multidimensional. Parallel processing capability, simple calculations and wide applications are a few other notable advantages. ANNs are generic and have a wider range of applications. In the next section, one of the most commonly used ANNs called the multilayer perceptrons (MLP) network is introduced.

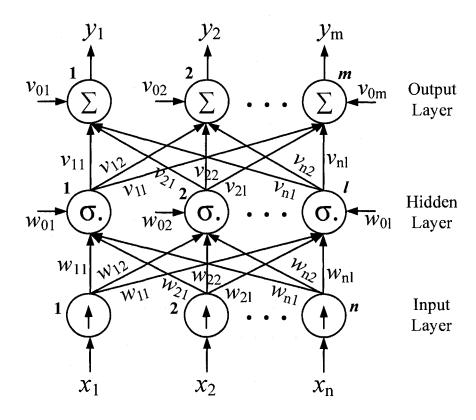

#### 2.4.2 Multilayer Perceptrons (MLP)

Multilayer perceptrons or MLP are the most commonly used neural networks owing to simplicity in terms of their structure and ease in terms of their training. It consists of n number of layers,  $1^{st}$  and  $n^{th}$  layers are input and output layers respectively and layers from 2 to n-1 are hidden layers. In this work 3-layer MLP that consists of  $1^{st}$ ,  $2^{nd}$ , and  $3^{rd}$  layers as input layer, hidden layer, and output layer respectively is employed. A MLP network consists of two parameters namely, nodes or neurons and links connecting the nodes or neurons.

A 3-layer MLP network with n input neurons, l hidden neurons and m output neurons is depicted in Fig. 2.2. The number of neurons in the input and output layer are fixed according to the problem definition but the number of neurons in the hidden layer can vary. More neurons in hidden layer may result in overlearning and fewer neurons may result in underlearning. For a given modeling problem, deciding the number of neurons in

hidden layers remains an open question. As discussed above,  $f_{ann}$  is a set of mathematical equations, representing the MLP network itself and processes faster than any other network. Model parameter vector w is determined and neural network ( $f_{ann}$ ) acts as a neural model with input x and output y. The process of computing the outputs of the neural network starting from its inputs is referred to as "feed-forward computation".

Figure 2.3 Multilayer perceptron (MLP) network.

#### A. Definition of Parameters

$\mathbf{x} = [x_1 x_2 \dots x_n]^T$  is the input vector.

$\mathbf{y} = [y_1 y_2 \dots y_m]^T$  is the output vector.

$w_{0h}$  is the bias parameter of  $h^{th}$  hidden neuron.

$v_{0i}$  is the bias parameter of the  $j^{\text{th}}$  output neuron.

$w_{\rm gh}$ ,  $1 \le g \le n$ ,  $1 \le h \le l$  is the weight parameter of the link between  $g^{\rm th}$  input and  $h^{\rm th}$  hidden neuron.

$v_{hi}$ ,  $1 \le j \le m$  is the weight parameter of the link between  $h^{th}$  hidden and  $j^{th}$  output neuron.

The weight parameter vector w consists of all the weight parameters of the links and the bias parameters (i.e. a total of  $[(n \times l) + (m \times l) + m + l]^T$  elements). Order of the elements is not vital as it remains same in the updated weight matrix too.

#### B. Activation Functions

Calculation at different layers is not same. Each neuron in the neural network has an activation function that processes its input to produce an output. Activation function for neuron in each layer is different (represented by  $\uparrow$  for input layer,  $\sigma$ . for hidden layer and  $\Sigma$  for output layer) as shown in Fig. 2.2. A neuron belonging to the input layer acts as a relay neuron producing an output equivalent to its input. For hidden layer neurons, there are a variety of activation functions like sigmoid, arctangent, hyperbolic tangent *etc*. Commonly used sigmoid function is chosen for this work. The activation function for the neuron in the output layer is summation function. As such, the output of an output neuron is just the weighted sum of its inputs. In case, total input to some neuron in hidden layer or output layer is zero, the output will also be zero. To avoid this situation, an extra weight is attached to each neuron in hidden layer and in output layer which is called bias. Consequently, even if input to that neuron is zero the output is not zero.

#### C. Feed-forward Computation

- (i) Input neuron acts as a relay neuron and there is no calculation/processing. at neurons in input layer.

- (ii) The processing by the hidden layer neuron depends on its activation function. The output of the  $h^{th}$  hidden neuron with a sigmoid activation function is given by

$$z_{\rm h} = \frac{1}{1 + e^{-\gamma_{\rm h}}} \tag{2.8}$$

and

$$\gamma_{\rm h} = w_{0\rm h} + \sum_{g=1}^{n} w_{\rm gh} x_{\rm g}. \tag{2.9}$$

(iii) For output layer neurons processing/calculations involve simple summation function. Thus, output of the  $j^{th}$  output neuron is the weighted sum of its inputs given by

$$y_{j} = v_{0j} + \sum_{h=1}^{l} v_{hj} z_{h}.$$

(2.10)

When neural network is employed for the optimization task, derivative information of parameters of the network is required to decide, by how much these parameters are to be modified and in which direction.

#### D. Derivative Computation

Let's consider a sample calculation for output  $y_1$ . Output at  $y_1$  is given by

$$y_1 = v_{01} + v_{11}z_1 + v_{21}z_2 + ... + v_{I1}z_1.$$

(2.11)

(i) Derivative of  $y_1$  w.r.t. bias of the output neuron (i.e.  $v_{01}$ ) can be estimated as

$$\frac{\partial y_1}{\partial v_{01}} = 1. \tag{2.12}$$

In general, (2.10) can be written as  $1 \le j \le m$ ,

$$\frac{\partial y_{j}}{\partial v_{0j}} = 1. \tag{2.13}$$

(ii) Derivative of  $y_1$  w.r.t. weight parameters (i.e. links) between hidden layer and output layer can be estimated as

$$\frac{\partial y_1}{\partial v_{11}} = 1; \quad \frac{\partial y_1}{\partial v_{11}} = 1; \quad \frac{\partial y_1}{\partial v_{11}} = 1. \tag{2.14}$$

In general, (2.12) can be written as  $1 \le h \le l$ ,

$$\frac{\partial y_{j}}{\partial v_{hj}} = Z_{h}. \tag{2.15}$$

(iii) Derivative of  $y_1$  w.r.t. bias of the hidden layer neuron (i.e.  $w_{01}$ ) involve following calculations. Chain rule needs to be implemented for this computation which is given by

$$\frac{\partial y_1}{\partial w_{01}} = \frac{\partial y_1}{\partial z_1} \cdot \frac{\partial z_1}{\partial \gamma_1} \cdot \frac{\partial \gamma_1}{\partial w_{01}}.$$

(2.16)

From (2.7), (2.8), and (2.10)

$$\frac{\partial z_1}{\partial \gamma_1} = z_1(1 - z_1); \quad \frac{\partial \gamma_1}{\partial w_{01}} = 1; \quad \frac{\partial y_1}{\partial z_1} = v_{11}. \tag{2.17}$$

From (2.14) and (2.15)

$$\frac{\partial y_1}{\partial w_{01}} = v_{11} \cdot z_1 (1 - z_1). \tag{2.18}$$

In general, (2.16) can be written as

$$\frac{\partial y_{j}}{\partial w_{0h}} = v_{hj} \cdot z_{h} (1 - z_{h}). \tag{2.19}$$

(iv) Finally, derivative of  $y_1$  w.r.t. weight parameters (i.e. links) between input layer and hidden layer can be estimated using chain rule as

$$\frac{\partial y_1}{\partial w_{11}} = \frac{\partial y_1}{\partial z_1} \cdot \frac{\partial z_1}{\partial \gamma_1} \cdot \frac{\partial \gamma_1}{\partial w_{11}}.$$

(2.20)

From (2.15) and (2.8)

$$\frac{\partial z_1}{\partial \gamma_1} = z_1 (1 - z_1); \quad \frac{\partial \gamma_1}{\partial w_{01}} = x_1; \quad \frac{\partial y_1}{\partial z_1} = v_{11}. \tag{2.21}$$

From (2.18) and (2.19)

$$\frac{\partial y_1}{\partial w_{11}} = v_{11} \cdot z_1 (1 - z_1) \cdot x_1. \tag{2.22}$$

In general, (2.20) can be written as

$$\frac{\partial y_{j}}{\partial w_{gh}} = v_{hj} \cdot z_{h} (1 - z_{h}) \cdot x_{n}. \tag{2.23}$$

This concludes the discussion about the derivative computation of various parameters of the network. The next section describes use of these derivatives in optimization methods. Widely used conjugate gradient method is selected for this work. Optimization in neural network is done by training them with sampled data. Training is of two types (i) sample training where network is trained with one sample data, and (ii) batch training where set of sample data is used to train the network. Batch training is selected for this work.

#### E. Conjugate Gradient Method

This method is employed for optimization which is called training in neural networks. This method simply calculates values of weight vector  $\mathbf{w}$  for which  $\mathbf{f}_{ann}$  defined in (2.6) closely represents the original problem behavior. First of all, an error function is defined.

$$E = \frac{1}{2} \sum_{k=1}^{p} \sum_{j=1}^{m} (d_{jk} - f_{ann, j}(\mathbf{x}_{k}, \mathbf{w}))^{2}.$$

(2.24)

Derivative of E w.r.t. weight vector w is estimated using chain rule as

$$\frac{\partial E}{\partial w} = \frac{\partial E}{\partial y} \cdot \frac{\partial y}{\partial w}.$$

(2.25)

From (2.22)

$$\frac{\partial E}{\partial y} = \sum_{k=1}^{p} \sum_{j=1}^{m} (f_{\text{ann, j}}(\mathbf{x}_{k}, \mathbf{w}) - d_{jk}). \tag{2.26}$$

Calculation of derivatives of y w.r.t. each parameter of vector w is described in detail in the derivative computation section. Conjugate gradient method can then be implemented to minimize error E to zero by adjusting vector w, and is described in following steps:

Step #1: Weight vector w of the size  $[(n \times l) + (m \times l) + m + l]^T$  is constructed and initialized. Order of the vector elements is not crucial as it remains same for updated weight vector w.

**Step #2**: All the required derivatives are calculated as discussed in previously.

Step #3:  $\frac{\partial E}{\partial w}$  is calculated using previously obtained derivative information and (2.23).

Step #4: Weight vector w is modified using following formulae.

$$w_{\text{new}} = w_{\text{old}} + \eta d \tag{2.27}$$

and

$$\boldsymbol{d} = -\boldsymbol{g} \tag{2.28}$$

and

$$\mathbf{g} = \frac{\partial E}{\partial \mathbf{w}} | \mathbf{w} = \mathbf{w}_{\text{old}} , \qquad (2.29)$$

where  $\eta$  is called learning rate and is generally considered to be small, say 0.1, to avoid cancellation of present and past values of weights, d is successive update direction vector and g is gradient vector.

#### 2.5 NEED FOR NEW MODELING ALGORITHMS

When a device/component being modeled is highly nonlinear and/or when the model being developed is expected to cover a wider input parameter space, advanced ANNs utilizing knowledge (e.g. knowledge based neural networks or KBNN) are employed [33][34]. Alternatively, two or more existing modeling techniques can be integrated [5]. However, such approaches lead to increased model complexity. Besides, such advanced approaches require the users to have an in-depth understanding of ANN concepts for them to be able to develop satisfactorily accurate models. Thus new modeling algorithms are needed to enhance the modeling process and to make it simple for the novice users.

#### 2.6 SUMMARY

In this chapter, some basic concepts regarding the electrical (*i.e.*, I-V relation) model of a MOSFET along with analog design approaches in practice have been presented. Motivation for the work owing to shortcomings of current approaches has been briefly discussed. The concept of neural networks is briefly introduced along with the most commonly used neural models, and the need for new modeling algorithms is elucidated. In the following few chapters the goal of modeling is pursued and hence, novel modeling algorithms are proposed that offer substantial advantage towards accuracy and efficiency as regards the computational resources are concerned.

## CHAPTER 3

# MOSFET MODELING BASED ON

## **BINNING ALGORITHMS**

### 3.1 Introduction

Neural approaches to developing device/component models have been described in [29]-[31]. As discussed in chapter 2 (section 2.5), when a 3-layer MLP network fails to model the given device accurately, additional hidden layer neurons or additional hidden layers can be added. A recent trend is to employ the existing knowledge to architect advanced structures, known as Knowledge Based Neural Networks (KBNN), described in

[32][33]. For a given model accuracy, KBNN have been shown to reduce the need for training data. However, such advanced approaches require the users to have an in-depth understanding of ANN/KBNN concepts, to be able to develop satisfactorily accurate models. Motivated by this, the goal is to keep the model structure simple, while attaining satisfactory model accuracies.

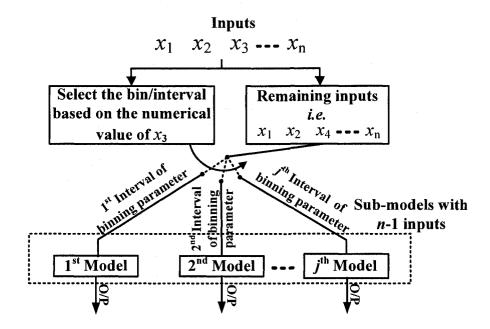

In this chapter, new device modeling algorithms are proposed, which allow accurate device modeling over a wider input parameter space. Starting from a given training data set, proposed algorithms employ simple 3-layer MLP structures and generate a set of submodels. Each of these models represents the device behaviors in a subspace of the overall input space. The sub-models are interfaced to generate an overall model that satisfactorily meets the given accuracy specification. Illustration examples confirming the validity of both the algorithms in active as well as passive domain are developed. Since examples of passive component modeling are not part of the thesis framework, they are included in appendix A.

#### 3.2 STANDARD NEURAL MODELING APPROACH

Let  $x = [x_1, x_2, ..., x_n]^T$  represent a vector of inputs or design parameters, and y represent response of the device/component being modeled. The objective of modeling is to determine a relationship f, e.g. neural network, such that

$$y = f(\mathbf{x}). \tag{3.1}$$

In standard neural modeling, a 3-layer MLP is chosen to deduce f. Let k represent the number of available training data of the form  $(x^i, y^i)$ , where i = 1, 2, ..., k. Let  $f_{ann}$  represent the trained neural model. A percentage average error E of the neural model can

be calculated as,

$$E = \sqrt{\frac{1}{k} \sum_{i=1}^{k} \left( \frac{y^{i} - f_{\operatorname{ann}}(\boldsymbol{x}^{i})}{y^{i}} \right)^{2}} \times 100.$$

(3.2)

In situations, where data is expensive/scarce, training data may also be used for model validation, although not advisable. For simplifying the discussion, E is assumed to represent the model accuracy. Assuming that the output y is highly sensitive to one of the inputs, say  $x_2$ , it could be difficult/impossible to deduce  $f_{ann}$  that satisfies user-specified accuracy. One possibility, as discussed earlier, is to add more hidden neurons or layers, but this may not always work. Advanced structures, e.g. KBNN, can also be employed; however, such an approach requires an in-depth understanding of ANN/KBNN concepts.

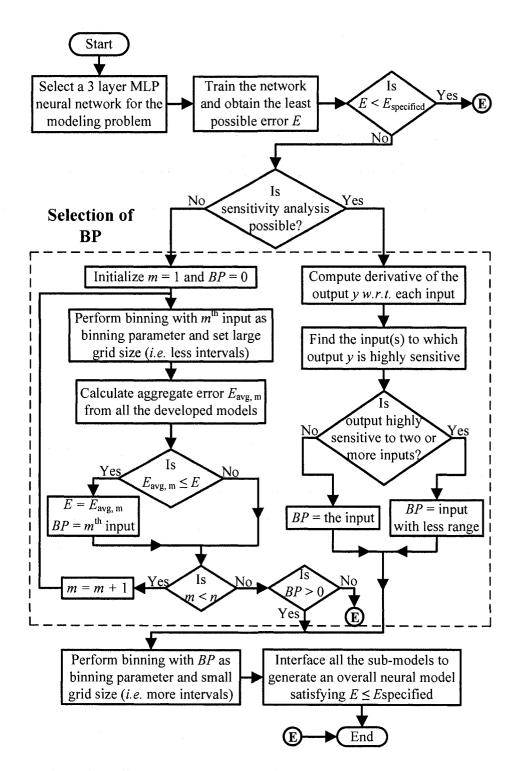

#### 3.3 BINNING ALGORITHM FOR SINGLE DIMENSIONAL MODELS

Binning/partitioning means dividing the model input parameter space into subspaces and developing corresponding sub-models that collectively span the entire input space of interest. In those challenging situations mentioned above, where the standard algorithm fails to generate a neural model with a lower or satisfactory E, the highly nonlinear input parameter, say  $x_2$ , is removed from vector x. The reduced input space is then divided into finite intervals using uniform-grids along the  $x_2$  axis. A model  $f_{\text{ann},j}$  is deduced for each of these intervals, where j denotes the j<sup>th</sup> interval. Parameter  $x_2$  is referred to as the binning parameter, and the process is referred to as binning. Given a modeling problem, the challenge is to identify the binning parameter. Based on the device being modeled, there can be two cases: (i) Sensitivity analysis of the device is possible. (ii) Sensitivity analysis

is impossible (*i.e.* empirical equations are unavailable) or it is impractical (*i.e.* available equations are CPU-intensive).

Consider case (i), where simple first-hand analysis equations of form (3.1), for the component being modeled, are available but do not hold true for the latest technology. Derivatives of output y corresponding to each of the inputs  $i.e. \frac{\partial y}{\partial x_1}, \frac{\partial y}{\partial x_2}, ..., \frac{\partial y}{\partial x_n}$  are first computed over the entire space of interest. The resulting sensitivity information is analyzed and the input that highly affects the output y is chosen as the binning parameter (BP). If the output is equally sensitive to two or more inputs, the input with the least range is selected as the binning parameter. In case (ii), selection of the binning parameter based on a trial-and-error method is proposed. Considering one input at a time, the process of binning is repeated n times. For each of the n potential binning parameters, an aggregate error measure  $E_{avg}$  is computed from corresponding sub-models in a manner similar to (2). The candidate parameter leading to the least  $E_{avg}$  is selected as the binning parameter. In the trial-and-error step of the proposed algorithm, the number of intervals corresponding to each of the binning parameters is chosen to be small.

In either case, once the binning parameter is identified, it is removed from the input vector x and the remaining subspace is divided into finite intervals using uniform-grids along the binning parameter. In this sub-model development step, a relatively larger number of intervals are advocated. A 3-layer MLP sub-model is developed for each of these intervals and these sub-models are interfaced to generate an accurate overall model. A flow-chart of the proposed single dimensional binning algorithm is depicted in Fig. 3.1. The overall model generated using the proposed algorithm is depicted in Fig. 3.2. As can be seen, the value of the binning parameter helps select an appropriate sub-model during

the utilization of the model.

Figure 3.1 Flow-chart illustrating the binning algorithm for single dimensional problems.

Figure 3.2 Overall model developed using the proposed binning algorithm (assuming  $x_3$  to be the binning parameter).

#### 3.4 BINNING ALGORITHM FOR MULTI-DIMENSIONAL MODELS

In this section, an enhanced modeling algorithm, which is an extension of the binning concept, presented in earlier section, to multi-dimensional modeling, is proposed. Starting from a given training data set, the algorithm employs simple 3-layer MLP structures and generates a set of sub-models similar to the earlier proposed algorithm. The sub-models are interfaced to generate an overall model that meets the given accuracy specification. Division of the parameter space into subspaces is facilitated by the binning concept. In situations where derivative information of the device output *w.r.t.* the input parameters is easy to compute/estimate, such sensitivity information is used to divide the input space. In situations where such analysis is not feasible, computation of impact indices of the inputs over all the outputs is advocated. In addition, standard deviation of each input is evaluated, and binning is performed using such statistical information.

As mentioned earlier, based on the device being modeled, there can be two cases. (i) Sensitivity analysis of the device/component is possible, (ii) Sensitivity analysis is impossible (*i.e.* unavailability of empirical equations) or it is impractical (*i.e.* available equations are CPU-intensive).

Consider case (i), where simple first-hand equations of form (3.1) for the device are available; however, these equations are not satisfactorily accurate. Derivatives of output y w.r.t. each of the inputs  $i.e. \frac{\partial y_1}{\partial x_1}, \frac{\partial y_2}{\partial x_1}, \dots, \frac{\partial y_p}{\partial x_1}, \frac{\partial y_1}{\partial x_2}, \frac{\partial y_2}{\partial x_2}, \dots, \frac{\partial y_p}{\partial x_n}$ , are derived over the entire input parameter space that leads to an approximate sensitivity analysis. In case (ii), selection of the binning parameter is proposed based on impact indices. For instance, impact index of  $x_m$  on  $y_p$  is estimated (via training data) as

$$g_{\rm mp} = \sqrt{\sum_{i=1}^{s_{\rm m}} \left[ \frac{\left(y_{\rm p}^{\rm i+1} - y_{\rm p}^{\rm i}\right)}{\left(x_{\rm m}^{\rm i+1} - x_{\rm m}^{\rm i}\right)} \right]^2},$$

(3.3)

where  $s_{\rm m}$  is the number of grids along  $m^{\rm th}$  input (i.e.  $x_{\rm m}$ ). Standard deviation ( $\sigma_{\rm m}$ ) of the  $m^{\rm th}$  input parameter is also calculated as

$$\sigma_{\rm m} = \sqrt{\frac{1}{S_{\rm m}} \sum_{i=1}^{S_{\rm m}} \left( x_{\rm m}^{\rm i} - \overline{x_{\rm m}} \right)^2}, \tag{3.4}$$

where  $\overline{x_m}$  is the mean of  $x_m$  over all data samples.

In either case, the input parameter with low deviation and high sensitivity (or impact index) is selected as the binning parameter. It is then removed from vector x and the remaining subspace is divided into a finite number of intervals using uniform-grids along the binning parameter. A 3-layer MLP sub-model is developed for each of these intervals

and these sub-models are interfaced to generate an overall model.

Figure 3.3 Flow-chart of the proposed multi-dimensional binning algorithm.

## 3.5 ILLUSTRATION EXAMPLES

For both the proposed modeling algorithms, illustrative examples covering active device modeling are presented in this section, while those covering passive component modeling are included in appendix A.

#### 3.5.1 Single Dimensional Modeling Example (MOSFET)

Commercial models (e.g. BSIM3) involve numerous model parameters, and model reduction is preferable. The modeling problem can be stated as

$$I_{\rm D} = f(L, W/L, V_{\rm GS}, V_{\rm DS}),$$

(3.5)

where L and W represent gate length and width,  $V_{\rm GS}$  and  $V_{\rm DS}$  are gate and drain voltages, and  $I_{\rm D}$  represents drain current. Training data for modeling the transistor is obtained using a detailed transistor model from a well-known simulator, namely HSPICE. A datasheet of  $I_{\rm D}$  is generated by sweeping the input parameters L, W/L,  $V_{\rm DS}$ , and  $V_{\rm GS}$  along uniform grids. As an example, the training data corresponding to  $L=1\mu m$  and  $V_{\rm GS}=1.4V$  is shown in Fig. 3.4(b).

First, a neural network model of the transistor is developed using the standard approach. A 3-layer MLP with four inputs and one output shown in Fig. 3.4(a) is used. NeuroModeler [34] is used for training, resulting in a best possible neural model. Model responses corresponding to the training data in Fig. 3.4(b) are shown in Fig. 3.4(c). In an attempt to closely inspect the neural model, model errors for different sub-ranges along the  $V_{GS}$  axis are computed (see Table 3.1). "Too high", implies that the error is so high and the neural model fails to emulate the training data. Assuming that the acceptable average error is 5%, the model appears to be good for  $V_{GS} > 1.2V$ ; however, exhibits

worst-case errors > 38.2%, which is not acceptable.

For the transistor, first-hand analysis equations are known but the equations do not hold true in the submicron region. The standard equation for estimating drain current of a CMOS transistor operating in saturation region is given by

$$I_{\rm D} = \frac{\mu_{\rm n} C_{\rm ox} W (V_{\rm GS} - V_{\rm T})^2 (1 + \lambda V_{\rm DS})}{2L},$$

(3.6)

where  $\mu_n$  is electron mobility,  $C_{ox}$  is gate-oxide capacitance per unit area,  $V_T$  is threshold voltage, and  $\lambda$  represents channel length modulation. As such, the proposed binning algorithm can be applied. In order to identify the binning parameter, sensitivity analysis needs to be performed. In other words, derivatives of the output  $I_D$  w.r.t. all the inputs need to be computed. For instance, derivative of  $I_D$  w.r.t.  $V_{GS}$  can be computed using

$$\frac{\partial I_{\rm D}}{\partial V_{\rm GS}} = \frac{\mu_{\rm n} C_{\rm ox} W (V_{\rm GS} - V_{\rm T}) (1 + \lambda V_{\rm DS})}{L}.$$

(3.7)