## Integrated Sorting, Noise Estimation, Object Detection and Contour Analysis on one FPGA for Video Object Segmentation

Kumara Ratnayake

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements

for the Degree of Master of Applied Science (Electrical and Computer Engineering) at

Concordia University

Montréal, Québec, Canada

June 2007

© Kumara Ratnayake, 2007

Library and Archives Canada

Canada Archives Canada

Published Heritage Branch

Direction du Patrimoine de l'édition

395 Wellington Street Ottawa ON K1A 0N4 Canada 395, rue Wellington Ottawa ON K1A 0N4 Canada

Bibliothèque et

Your file Votre référence ISBN: 978-0-494-34453-8 Our file Notre référence ISBN: 978-0-494-34453-8

#### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

#### ABSTRACT

## Integrated Sorting, Noise Estimation, Object Detection and Contour Analysis on one FPGA for Video Object Segmentation

#### Kumara Ratnayake

Although solutions for robust video processing methods, such as compression or segmentation, have been considerably investigated using general-purpose processors (GPPs), these software implementations are too slow to achieve real-time performance due to the computational complexity and memory bandwidth involved in present complex video processing methods. As such, efficient hardware accelerations are inevitable for fast video systems. The state-of-the-art field programmable gate arrays (FPGAs) fill the gap between very inflexible, but high performance ASICs and flexible, yet performance-constrained GPPs. Thus, FPGAs are increasingly employed on hardware platforms in many signal and video processing applications.

This thesis proposes an FPGA-based architecture that integrates four video processing methods (sorting, noise estimation, object detection, and contour analysis) on one FPGA, which takes a video signal and outputs a contour filled video sequence along with the corresponding contour chain codes. The proposed architecture aims at segmenting moving objects in video signals. A video object segmentation consists of several steps: pre-processing (e.g., noise estimation), object detection (i.e., separation of objects and background), and contour analysis. The proposed architecture is simulated, synthesized and verified for its functionality, accuracy and performance on an actual hardware platform consisting of a Xilinx Virtex-4 SX35 FPGA.

Compared to related work, our architecture obtains orders of magnitude performance improvements utilizing minimal hardware resources and power, and possesses key algorithmic features, which are inherently required in many video processing applications.

#### Acknowledgments

This thesis is based on three years of research on my part, but would not have been possible without inspiration, education and support from a number of people.

First, I would like to express my deepest appreciations and gratitude to my supervisor Dr. Aishy Amer. Her guidance and support have been instrumental in my success. With your enthusiasm, inspiration, and great efforts to explain things clearly and simply, you helped me to succeed in this wonderful research world. Thank you for guiding me through the writing of all the reports, papers and, of course, this thesis, and for all the corrections and revisions made to each of them.

I would like to thank all my colleagues at VidPro for their support: Chang Su, M. Ghazal, Firas, François, El Helali, Hanif, Julius, Bin and Ken.

Last, but not least, I am forever indebted to my entire family for their love, understanding, endless patience and encouragement when it was most required.

To my daughter Melina Seneli Ratnayake.

# Contents

| Li | st of | Figures                                                      | ix   |

|----|-------|--------------------------------------------------------------|------|

| Li | st of | Tables                                                       | xii  |

| Li | st of | Notations                                                    | xiii |

| 1  | Intr  | oduction                                                     | 1    |

|    | 1.1   | Motivation                                                   | 1    |

|    | 1.2   | Summary of Related Work                                      | 4    |

|    |       | 1.2.1 Noise Estimation and Sorting                           | 4    |

|    |       | 1.2.2 Object Detection                                       | 6    |

|    |       | 1.2.3 Object Contour Tracing and Filling                     | 7    |

|    | 1.3   | Background on FPGAs                                          | 8    |

|    | 1.4   | Overview of Contributions                                    | 12   |

|    | 1.5   | Thesis Outline                                               | 13   |

| 2  | A M   | Iodified Counting Sort Algorithm and its FPGA Implementation | 15   |

|    | 2.1   | Introduction                                                 | 15   |

|    | 2.2   | Related Work Review                                          | 17   |

|    | 2.3   | A Modified Counting Sort Algorithm                           | 19   |

|    | 2.4   | Proposed Sorting Architecture                                | 21   |

| C | ONT | ENTS                                                        | vii |

|---|-----|-------------------------------------------------------------|-----|

|   |     | 2.4.1 TEMPORAL KEY MANAGEMENT Module                        | 22  |

|   |     | 2.4.2 Architecture of the HISTOGRAM UNIT                    | 23  |

|   |     | 2.4.3 Architecture of the INITIAL ADDRESS CONTROL Module .  | 24  |

|   |     | 2.4.4 OUTPUT INDEXING Module                                | 24  |

|   | 2.5 | Simulation and Verification Results                         | 25  |

|   | 2.6 | Synthesis and Implementation Results                        | 26  |

|   |     | 2.6.1 Implementation                                        | 26  |

|   |     | 2.6.2 Comparison to the Existing Methods                    | 27  |

|   | 2.7 | Chapter Summary                                             | 29  |

| 3 | Imp | proved FPGA-based Implementation of Noise Estimation        | 30  |

|   | 3.1 | Introduction                                                | 30  |

|   | 3.2 | Related Work Review                                         | 31  |

|   | 3.3 | Overview of the Reference Noise                             |     |

|   |     | Estimation Algorithm                                        | 31  |

|   | 3.4 | Proposed FPGA-based Architecture                            | 33  |

|   | 3.5 | Implementation Results                                      | 34  |

|   | 3.6 | Chapter Summary                                             | 35  |

| 4 | FP  | GA-based Implementation of Spatio-Temporal Object Detection | 36  |

|   | 4.1 | Introduction                                                | 36  |

|   | 4.2 | Overview of the Reference Spatio-Temporal                   |     |

|   |     | Object Detection Algorithm                                  | 37  |

|   | 4.3 | Proposed Pipelined Architecture                             |     |

|   |     | and Implementation                                          | 39  |

|   |     | 4.3.1 Proposed DMA Architecture                             | 40  |

|   |     | 4.3.2 Scalable Motion Detection Implementation              | 41  |

| patio-Temporal Thresholding Architecture               | 42<br>44<br>45<br>45                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rification, Synthesis and cation Result                | 45                                                                                                                                                                                                                                                                                         |

| rification                                             |                                                                                                                                                                                                                                                                                            |

| rification                                             |                                                                                                                                                                                                                                                                                            |

|                                                        | 45                                                                                                                                                                                                                                                                                         |

| nthesis Result                                         |                                                                                                                                                                                                                                                                                            |

|                                                        | 47                                                                                                                                                                                                                                                                                         |

| mparison to the Existing Methods                       | 47                                                                                                                                                                                                                                                                                         |

|                                                        | 48                                                                                                                                                                                                                                                                                         |

| Implementation of Chaotic Contour Tracing and Fill-    |                                                                                                                                                                                                                                                                                            |

| Objects on Reconfigurable Hardware                     | 49                                                                                                                                                                                                                                                                                         |

| on                                                     | 49                                                                                                                                                                                                                                                                                         |

| Vork                                                   | 50                                                                                                                                                                                                                                                                                         |

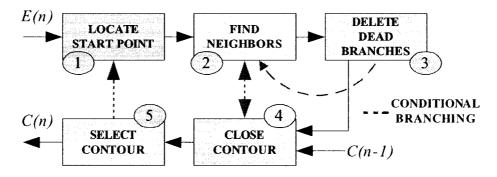

| of the Reference Contour Tracing and Filling Algorithm | 52                                                                                                                                                                                                                                                                                         |

| racing Algorithm                                       | 52                                                                                                                                                                                                                                                                                         |

| lling Algorithm                                        | 54                                                                                                                                                                                                                                                                                         |

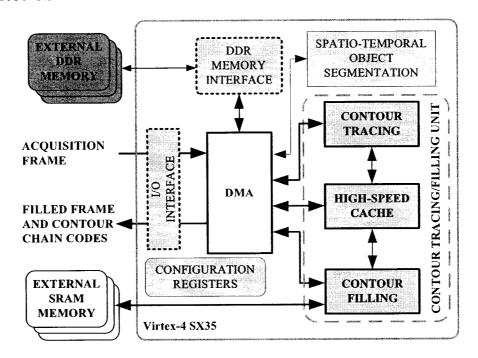

| Architecture                                           | 55                                                                                                                                                                                                                                                                                         |

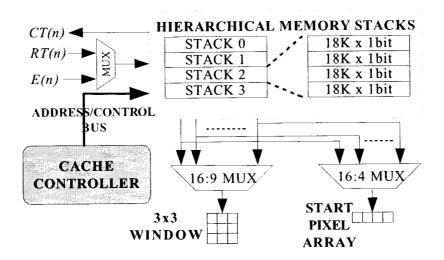

| rchitecture of HIGH-SPEED CACHE                        | 55                                                                                                                                                                                                                                                                                         |

| chitecture of CONTOUR TRACING Module                   | 57                                                                                                                                                                                                                                                                                         |

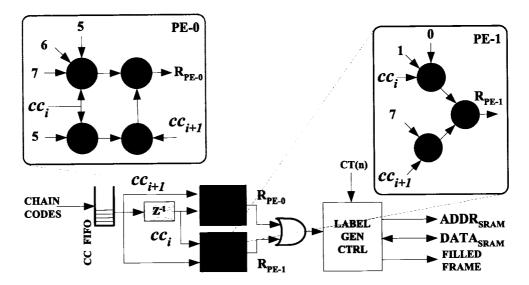

| ONTOUR FILLING Architecture                            | 59                                                                                                                                                                                                                                                                                         |

| proved DMA Architecture                                | 60                                                                                                                                                                                                                                                                                         |

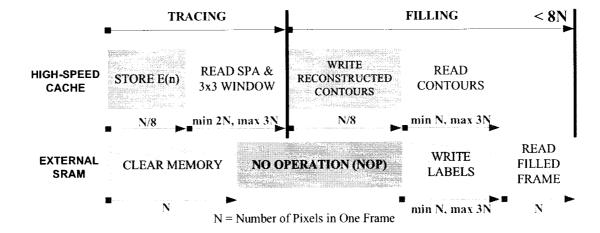

| peline Scheduling                                      | 61                                                                                                                                                                                                                                                                                         |

| ntal Results                                           | 62                                                                                                                                                                                                                                                                                         |

| erification                                            | 62                                                                                                                                                                                                                                                                                         |

| enthesis and FPGA Implementation                       | 63                                                                                                                                                                                                                                                                                         |

| omparison to the Existing Methods                      | 64                                                                                                                                                                                                                                                                                         |

|                                                        | 65                                                                                                                                                                                                                                                                                         |

| i i i i i i i i i i i i i i i i i i i                  | racing Algorithm  Algorithm  Architecture  rchitecture of HIGH-SPEED CACHE  chitecture of CONTOUR TRACING Module  ONTOUR FILLING Architecture  aproved DMA Architecture  peline Scheduling  ntal Results  erification  ynthesis and FPGA Implementation  omparison to the Existing Methods |

| 6 Conclusion and Future Work | 67 |

|------------------------------|----|

| Bibliography                 | 70 |

# List of Figures

| 1.1 | Proposed FPGA-based Implementation of Video Object Segmentation.     | 3  |

|-----|----------------------------------------------------------------------|----|

| 1.2 | Typical FPGA Design Flow                                             | 10 |

| 2.1 | Overall System Level Sorting Architecture.                           | 22 |

| 2.2 | Detailed Circuit Diagram of the Sorting Architecture                 | 23 |

| 2.3 | Complexity comparison between a CPU and FPGA                         | 25 |

| 2.4 | Simulation environment with VHDL Testbench and C/MATLAB              | 26 |

| 2.5 | Sample comparison between VHDL and MATLAB results                    | 27 |

| 2.6 | Internal FPGA resources utilization                                  | 29 |

| 3.1 | Proposed Architecture of the Noise Estimation Algorithm              | 33 |

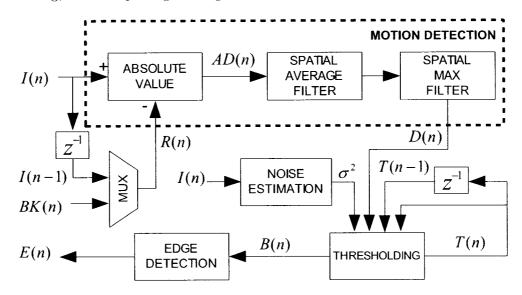

| 4.1 | Block Diagram of the Object Detection [1]                            | 38 |

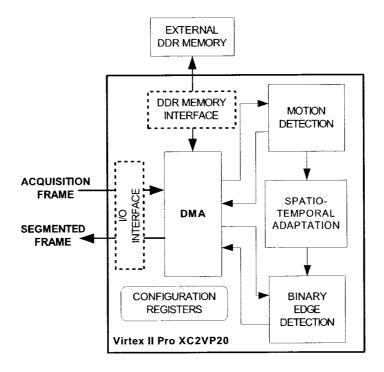

| 4.2 | System-Level Architecture of Object Detection                        | 40 |

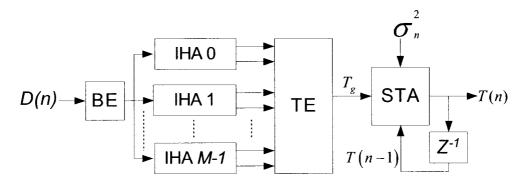

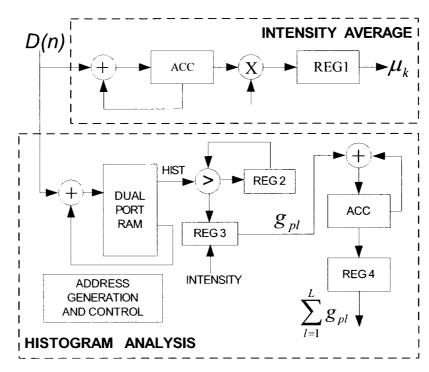

| 4.3 | High-Level Architecture of Spatio-Temporal Threshold                 | 42 |

| 4.4 | Architecture of Intensity Histogram Analysis Module                  | 43 |

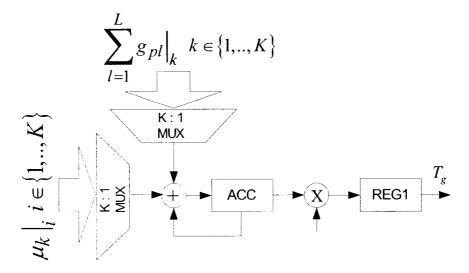

| 4.5 | Threshold Estimator Architecture.                                    | 44 |

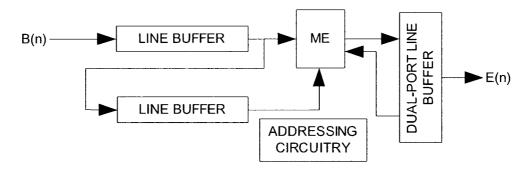

| 4.6 | Circuitry for Morphological Edge Detection                           | 45 |

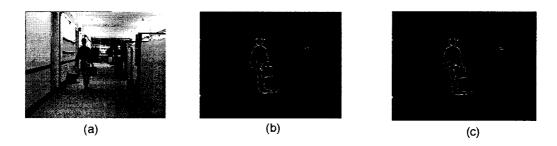

| 4.7 | (a) 54th frame in the captured video sequence, (b) segments with the |    |

|     | reference C implementation, and (c) FPGA segments.                   | 45 |

LIST OF FIGURES xi

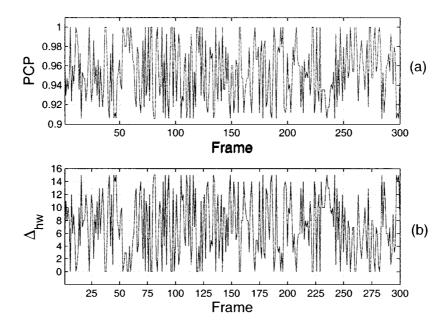

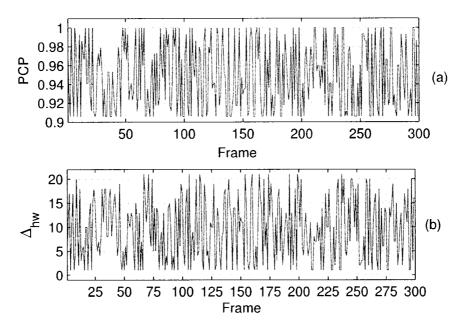

| 4.8 | (a) Comparison between software and hardware implementations with         |    |  |

|-----|---------------------------------------------------------------------------|----|--|

|     | PCP objective measure [2], and (b) difference of total pixels between     |    |  |

|     | software and hardware implementations $\Delta_{hw}$                       | 46 |  |

| 5.1 | Contour Tracing Algorithm [1]                                             | 53 |  |

| 5.2 | System-Level Architecture of Contour Tracing and Filling                  | 56 |  |

| 5.3 | Scalable Architecture of the HIGH-SPEED CACHE                             | 57 |  |

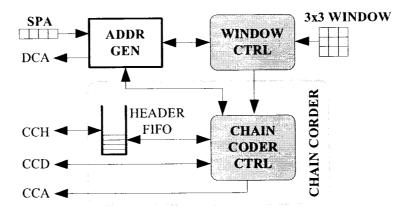

| 5.4 | Overall Schematic of the CONTOUR TRACING Module                           | 58 |  |

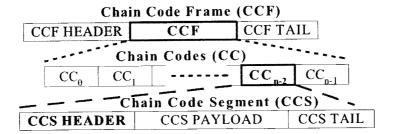

| 5.5 | Contour Bit Stream Structure.                                             | 59 |  |

| 5.6 | Architecture of the Contour Filling Module.                               | 60 |  |

| 5.7 | Overall Pipeline Timing of the Proposed Architecture                      | 62 |  |

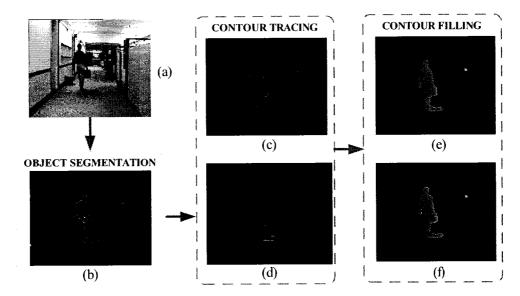

| 5.8 | Subjective comparison between the FPGA and software implementa-           |    |  |

|     | tion results - (a) 54th frame in the captured video sequence. (b) Spatio- |    |  |

|     | temporal object segmentation of [1], (c) Contour tracing results with C,  |    |  |

|     | and with the proposed FPGA implementation (d), (e) Contour filling        |    |  |

|     | with C, and with the proposed FPGA implementation (f)                     | 63 |  |

| 5.9 | (a) Comparison between software and hardware implementations with         |    |  |

|     | PCP objective measure [2], and (b) difference of total pixels between     |    |  |

|     | software and hardware implementations $\Delta_{hw}$                       | 64 |  |

# List of Tables

| 2.1 | Original Counting Sort Algorithm [3]                                    | 20 |

|-----|-------------------------------------------------------------------------|----|

| 2.2 | Proposed Modified Counting Sort Algorithm                               | 21 |

| 2.3 | Performance and area comparison for sorting 128 keys of 8 bits with [4] |    |

|     | and proposed method                                                     | 28 |

| 3.1 | Architectural and Performance Comparison of the Noise Estimation        |    |

|     | Implementation between [5] and the Proposed Method.                     | 35 |

## List of Notations

#### General Acronyms

| One Dimensional                          |

|------------------------------------------|

| Two Dimensional                          |

| Application Specific Integrated Circuits |

| Connected Component Labeling             |

| Common Intermediate Format               |

| Configurable Logic Blocks                |

| Digital Clock Manager                    |

| Direct Memory access                     |

| Digital Signal Processing                |

| Electronic Design Interchange Format     |

| Finite Impulse Response                  |

| Formal Hardware Verification             |

| Field Programmable Gate Array            |

| General Purpose Processor                |

|                                          |

IO Input Output LUT Look Up Tables

HDTV

NTSC National Television Standards Committee

High Definition Television

PAL Phase Alternate Line RAM Random Access Memory SNR Signal to Noise Ratio

SRAM Static RAM

SBSRAM Synchronous Burst SRAM

DRAM Dynamic RAM

DDR Double Data Rate

BOM Bill Of Materials

RTL Resistor Transistor Level

VHDL Very high speed integrated circuit Hardware Description Language

VLSI Very Large Scale Integration

#### Sorting and Video Noise Estimation

$egin{array}{ll} a_i & & {

m Unsorted \ Keys} \\ d_i & & {

m Stably \ Sorted \ Keys} \\ \end{array}$

$I_{i,j}$  Pixel Intensity at Position (i,j)

W Block Size

$\xi_{Bh}$  Block Homogeneity Measure

$\sigma_{Bh}^2$  Block Variance  $\mu_{Bh}$  Block Sample Mean  $\sigma_{REF}^2$  Reference Variance

$t_{\sigma}$  User Defined Homogeneity Threshold

$\sigma_n^2$  Image Global Noise Variance

#### **Object Segmentation**

Current Discrete Time Instant AD(n)Absolute Frame Difference I(n)Current Frame R(n)Reference Frame BK(n)Background Frame I(n-1)Previous Frame D(n)Spatially-Filtered Frame  $T_g$ Global Spatial Threshold  $W_k$ kth Consecutive Non-Overlapping Block KNumber of Consecutive Non-Overlapping Blocks Number of Sections in  $W_k$  Histogram L

$\mu_k$  Mean Value of  $W_k$ a Noise Scaling Factor  $E_{hw}(n)$  Hardware Result (Frame)  $E_{sw}(n)$  Software Result (Frame)

$\Delta_{hw}$  Absolute Different between the  $E_{hw}(n)$  and  $E_{sw}(n)$

PCP Product of Correctly Classified Proportions

### Contour Tracing and Filling

| E(n)       | Gaps Free Edge Image         |

|------------|------------------------------|

| $p_i$      | A Point in an 8-Neighborhood |

| $p_w$      | White Point                  |

| $p_b$      | Background (Black) Point     |

| $p_s$      | Starting Point               |

| $p_c$      | Current Point                |

| $p_p$      | Previous Point               |

| $d_s$      | Searching Direction          |

| $C_c$      | Current Contour              |

| $C_p$      | Previous Contour             |

| C(n)       | Current Contour List         |

| C(n-1)     | Previous Contour List        |

| $cc_i$     | Current Contour Point        |

| $cc_{i+1}$ | Next Contour Point           |

|            |                              |

## Chapter 1

## Introduction

#### 1.1 Motivation

The computational complexity involved in today's complex video processing algorithms [6–10] make virtually impossible to achieve real-time performance on general purpose sequential processor-based systems. Thus, an efficient hardware acceleration is inevitable. There exists three possible hardware-based solutions: 1) parallel computing, 2) Application Specific Integrated Circuit (ASIC), and 3) FPGAs. The parallel computing gives the highest flexibility among the three solutions, but heat dissipation and area are all increased. Traditional full custom ASIC provides the highest processing speed with minimal power consumption, but suffers from longer development time and expensive engineering cost. In contrast, emerging FPGAs with embedded multipliers, memory blocks and high pin counts, are increasingly employed on hardware platforms in many signal/video processing applications [11]. Moreover, FPGA reconfigurability is an attractive feature which allows an FPGA-based systems to be adopted for an another purpose.

Video object segmentation, which classifies pixels of a frame into multiple moving regions, plays a key role in many video processing applications such as video compres1.1. MOTIVATION 2

sion, video surveillance, machine vision, and enabling techniques such as object-based motion estimation. Video object segmentation methods [12] can be classified based on their automation, spatial accuracy, temporal stability, and computation load. Computationally expensive methods give, in general, accurate results while low-computation methods may fail. However, few of the methods are tested on a large number of videos, throughout long videos, on noisy videos, images with artifacts, and without parameter tuning.

The non-parametric object segmentation method, described in [1], features low computation and noise and temporal stability. These features forgo spatial accuracy, e.g., at object boundaries. Such a method is most appropriate to applications, e.g., video surveillance, where stability under varying conditions is of more concern than accurate object boundaries. Consequently, the video object segmentation algorithm [1] first estimates the noise [13] to effectively detect moving video objects from background and then performs contour tracing and filling of these detected objects.

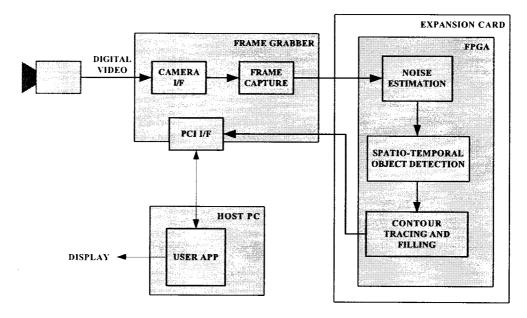

In this thesis, we propose a real-time, robust, scalable, and compact FPGA-based architecture and its implementation of video object segmentation algorithm [1]. Our finding to the existing related work confirms that the proposed architecture is much more feasible and cost effective. Furthermore, performance analysis shows that our hardware approach achieves an order of magnitude performance improvement over the existing pure software-based implementations. Fig.1.1 illustrates a high-level block diagram of the proposed FPGA-based implementation of the video object segmentation. Note that the output of the proposed system is an image of filled objects and the corresponding contour chain codes. Therefore, final results of the FPGA are presented in chapter 5.

Noise is inevitable in video signals due to video acquisition, processing, and transmission. Moreover, noise can significantly affect the performance and effectiveness

1.1. MOTIVATION 3

Figure 1.1: Proposed FPGA-based Implementation of Video Object Segmentation.

of many video processing algorithms, such as edge detection, object segmentation, motion estimation, and video filtering [13]. Thus, measuring noise, through noise estimation algorithms, in a corrupted video signal and adapting the video processing algorithms accordingly is fundamental and important feature for stable video processing systems.

In general, the noise estimation algorithms use spatial or temporal image characteristics to measure noise. Temporal noise estimation methods require one or more previous frames, and are more computationally intensive, while most of the spatial methods rely on intra-frame block-based variance or smoothing. The intra-field block-based noise estimation method [13] gives reliable estimates both in highly noisy and good quality images. This homogeneity-based technique utilizes a novel homogeneity measure, by taking image structure into account, rather than variance alone to determine if a block is homogeneous. Moreover, the methods requires to sort 10% of the block variances with respect to the homogeneous measure. The main computational bottleneck of the noise estimation algorithm [13] resides in this sorting process.

Sorting (in ascending order) is a process to rearrange a given set of keys  $a_0, a_1,..., a_{N-1}$  into a set  $d_0=a_{i_0}, d_1=a_{i_1}, ..., d_{N-1}=a_{i_{N-1}}$  such that  $d_0 \leq d_1 \leq$

Contour tracing is a method that links connected neighborhood pixels in a binary edge frame, whereas contour filling fills the region inside a contour with a specific gray-level value, uniquely labeling each objects in an image. Contour tracing and filling are a fundamental element in many video and image processing applications such as object segmentation [1], medical image processing [15], computer vision [16] and pattern recognition [17].

## 1.2 Summary of Related Work

This section summarizes the architectures and implementations of video noise estimation, sorting, video object detection, video object contour trace and filling on FPGA and VLSI devices. Detailed related work review is given in chapters 2, 3, 4 and 5.

## 1.2.1 Noise Estimation and Sorting

To the best knowledge of the author, only Lapalme, in [5], has presented an FPAG-based architecture for estimating noise in digital video, but [5] requires a significant amount of FPGA resources, runs at a slower speed, and employs two SRAM devices. In contrast, the proposed architecture outperforms [5] significantly and avoids the

utilization of external SRAM modules, which increase the area, cost, power and verification time of the overall video processing system.

Much research has been carried out implementing parallel sorting algorithms on VLSI recently, but very little emphasis has been put on FPGA-based implementations. Most of the FPGA-based architectures, which are based on pure comparison sorting algorithms, require an enormous of silicon area when sorting has to be performed on a very larger volume of data.

A hybrid implementation of a hardware sorter is studied in [18]. Here, the architecture is split into a sequential merge sorting algorithm running on a sequential processor, and a systolic insertion sorting algorithm running on a Xilinx XCV1000 FPGA co-processor. Huang et al. propose another architecture in [4] for merge-sorting networks with a fixed size Batcher's sorting network. However, performance of this architecture is considerably low for applications that require real-time sorting performance such as in [13]. Another VLSI architecture is presented in [14], which sorts small continuous data sequences up to 256 keys and partially sorts longer sequences. The architectures in [14,18] are based on comparative based sorting methods, therefore implementing them on FPGAs require more resources (area) than the proposed architecture based on a modified counting sort.

In signal processing, sorting is widely used in rank-order filters which are preferred over linear filters [19]. Here, the complexity of sorting is relatively small as the resolution and the number of data becomes small and no stable sorting is required. Several FPGA implementations for median filters have been presented [19–22] each of them exploiting different approaches for sorting architectures. Maheshwari et al. [19] propose a simple approach to a  $3\times3$  median filter implementation on an FPGA, by sorting the elements in the  $3\times3$  kernel vertically, horizontally and diagonally. In [20], a bit serial sorting algorithm and implementation are introduced for a general purpose

median filter on an FPGA. Hamid et al. [21] present a genetic algorithm on a Xilinx Spartan-II FPGA device to optimize the tasks of the soft morphological filter (SMF), whereas Fahmy et al. [22] propose an efficient implementation of one dimensional (1D) median filters based on cumulative histogram approach. Although implementation in [22] can process 72 MPixels/s for 8 bit pixel depth, it is not extended to 2D median filters. Moreover, achieving timing constraints on the implementation [20] can be very difficult for higher pixel depths, due to the nature of the priority encoder. Although the comparative methods proposed in [19–22] can theoretically be extended to sort a large number of keys, implementation of such methods on a resources constrained hardware such as FPGAs would not be feasible due to the large silicon area required.

#### 1.2.2 Object Detection

The method described in [23] demonstrates how a number of object detection algorithms can be implemented on FPGAs with dynamic reconfigurability feature. Another FPGA implementation for segmenting text in images is in [24]. Experimental results show that this algorithm implemented in FPGA achieved a speedup of close to 250 compared to a general purpose CPU implementation. However, [24] runs at 5 MHz which is well below the real-time performance. The study in [25] partially involves FPGA-based implementation of image segmentation based on the resistive-fuse network model. An extensive comparison between FPGA and DSP implementations of image classifier for object detection is in [26]. Although the performance of the FPGA implementation significantly overpasses that of the DSP implementation, its performance and scalability is heavily limited and embedded by the hardware platform chosen.

### 1.2.3 Object Contour Tracing and Filling

Agi et al. in [27] propose a full custom VLSI CMOS design for extracting contours, by attempting to minimize the memory usage by partitioning the input frame into smaller regions and distributing these regions to an array of processing elements (PEs). Each PE in [27] consists of its own memory and a contour tracing unit, and uses a  $2\times2$  window for extracting partially completed contour lists. However, the technique in [27] fails to produce completed contour tracing, unless a full object can be completely stored in the relatively small processing memory. A parallel VLSI architecture consisting of N+1 processing elements for generating the chain codes of object contours in a binary frame with N raws is presented in [28]. The algorithm proposed in [28] completes contour extraction in 3N cycles, but heavy parallel memory access required in [28] makes its architecture virtually infeasible to implement with presently available memory devices.

Although studies have been carried out to implement Connected Component Labeling, CCL, algorithms on hardware [29–33], no previous work has been dedicated on, to the authors' best knowledge, FPGA-based contour filling methods. The CCL methods assign a label to a pixel such that its adjacent and identical pixels have the same label. As such, the CCL algorithms can only label filled objects imposing a significant constraint in many video processing applications. A CCL architecture proposed for by Rasquinha et al. in [29] using N processing elements for  $M \times N$  image. In [30], Crooks et al. present an FPGA architecture for CCL, which requires scanning iteratively the input and intermediate images until no change in the resulting image occurs. However, [30] achieves real-time performance only for images with simple objects, and therefore, fails to completely label real video objects in applications such as video surveillance. Another VLSI architecture, consisting of four processors, for CCL is presented by [31], and Jablonski et al. [32] present an implementation of Classical

CCL in Handel-C language. A fast and parallel VLSI architecture for object labeling in binary images, using a 3×4 window, is presented by Shyue et al. in [33]. The CCL can be exploited for parallelism, but contour filling methods are inherently sequential, therefore implementing sequential contour filling algorithms are more challenging than CCL on parallel hardware devices such as FPGAs.

## 1.3 Background on FPGAs

Historically, FPGAs were known as prototyping and integration devices for lower volume digital systems due to their higher cost and lower performance. However, deep sub-micron (e.g., 65-nm copper CMOS) silicon process technology has dramatically changed in recent years allowing new levels of integration onto reprogrammable chips with more features and capabilities. Consequently, state-of-the-art FPGAs have already exceeded densities of tens of million system gates operating at speeds surpassing 400 MHz, and therefore these are increasingly employed in digital embedded system as a compromise to inflexible full-custom ASIC devices and performance-constrained sequential processors.

It is, however, noteworthy to mention disadvantages of FPGAs when compared to the ASICs. The fact that an ASIC is designed from scratch for a specific task allows optimizing the area, speed and power up-to the gate-level. This level of optimization is not available for FPGAs, since the FPGA devices are already manufactured by the FPGA vendors. Thus, for a given algorithm implemented on an FPGA lags behind the same implementation on an ASIC in silicon area, performance and power dissipations. Moreover, a unit cost of an FPGA is relatively higher than an ASIC having the same functionality, hence it is difficult to justify to design embedded systems with FPGAs for high-volume applications such as those in consumer markets. However, in this thesis we have chosen FPGAs over ASICs for the implementation

because FPGAs provide the ability to change the hardware entity with their inherent reconfigurability feature allowing the FPGA-based platform to be upgraded or enhanced throughout the product life time after the deployment. Furthermore, ASICs are intrinsically based on high-risk methodology requiring massive volume to recoup the Non-Recurring Engineering (NRE) costs required to create an ASIC at the beginning. Hence, FPGAs' flexibility with low risk and shorter development cycles make them as the optimal choice for a hardware implementation.

Widely known and available SRAM-based FPGAs can be configured, reconfigured or partially reconfigured by writing a bit-stream to the FPGAs, depending on the application requirements. In general, FPGAs are fabricated with matrices of few fundamental building blocks: configurable logic blocks (CLBs), embedded multipliers (or digital signal processing slices - DSP48E), blocks of random access memory (BRAMs), clock buffers (BUFGs), clock synthesizers (DCMs), and programmable interconnection network among these elementary components. Additionally, some FPGA families include hard-processors such as PowerPC in Xilinx Virtex4FX family. Throughout this thesis, we have used FPGAs from Xilinx and not Altera or any other vendors, primarily because Xilinx FPGAs possess some architectural features such as the ability to configure four input Look-up-tables (LUTs) into sixteen shift registers (SRL16) and availability of hardcore PowerPC processors, which are not present in FPGAs, for e.g., from Altera.

Synchronous or combinatorial logic circuits are implemented by configuring CLBs, which, in Xilinx Virtex-5 FPGAs [34], are comprised of two slices each containing four LUTs and four flip-flops. Each DSP48E slice contains a two complement 25x18 multiplier and a 48-bit signed adder/accumulator. Excessively available DSP48Es are ideal for parallel implementation of many signal and video processing functions such as FIR filters, 2D convolution and correlation. BRAMs are 36 Kbit true dual-port

memory blocks which are programmable from 32Kx1 to 512×72, in various depth and width configurations or can be configured to operate as two, independent 18 Kbit dual-port memory blocks. These BRAMs are extensively utilized from simple first in first out (FIFO) memories to line buffers and histogram computations.

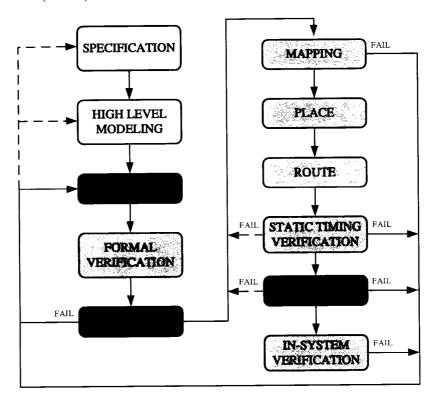

Figure 1.2: Typical FPGA Design Flow.

Fig. 1.2 illustrates a typical FPGA design flow, which, throughout this thesis work, has been used. Starting with specification defined in floating point C/C++ for all algorithms - noise estimation, sorting, object detection and contour tracing and filling - we model a virtual hardware with fixed-point C/C++ and MATLAB. These fixed point high-level models are extensively analyzed to formalize the final hardware design correlate maximally with the original specification. In addition, parallelism of the video processing algorithms are explored.

The high-level models are then coded and formally verified in a hardware description language - VHDL, which is extensively used as one of the modern approaches

11

of designing digital circuits. Due to the complexity and scale of the hardware designs targeted to video processing systems, it is vital to perform vigorous verification through formal hardware verification (FHV) methods to ensure that the final design is relatively bug-free. We have modeled a verification platform that automates most of the formal verification tasks by combining high level languages, such as C/C++ and MATLAB, with VHDL test-benches. The state-of-the-art VHDL simulation tools allow co-simulations with MATLAB, which provides a higher level of verification environment, facilitating simulation of the design modules such as sorting quickly. Moreover, our verification platform accepts, not just a mere set of VHDL stimuli, but a video sequence which is passed through the synthesizable hardware design. The resulting data, composed of a video sequence and/or contour chain codes, are then automatically compared with the high level specification, originally written in C/C++. In addition, the environment generates various objective and subjective measurements of the hardware result, which facilitate comparing the intended hardware design with the original specification.

The VHDL codes are then synthesized with Synplicity Synplify, which translates the design into a technology specific netlist file format - Electronic Design Interchange Format (EDIF). Synthesis reports provide approximate timing and resources utilization of the target FPGA. If the synthesis results are not satisfactory, the design may require more optimization for area and timing, or, in some instances, changes to specification and overall architecture.

The place and route tools (Xilinx ISE) take the EDIF netlist and map into appropriate fundamental building blocks, for e.g., CLBs. Once the design has been placed, the tools perform an *iterative* routing procedure to interconnect the mapped blocks producing a routed design with minimal interconnection delays. Here, static timing verifications are performed and critical paths of the circuits are analyzed to improve

the overall design performance. The routed FPGA design is then programmed into the FPGA to verify its functionality. In system verification tools, such as Xilinx Chipscope  $Pro^{TM}$  [35], are thoroughly used throughout the course of prototyping and circuit debugging. In the case of the routed design does not meet the timing, area and power, or if it is not functional correctly in real hardware in accordance with the specification or design goals, the complete design flow may require running a number of iteration, even from the specification level.

#### 1.4 Overview of Contributions

The following list states which parts of this thesis are original to the knowledge of the author at the time the proposed methods of this thesis were developed <sup>1</sup>:

- A hardware-friendly modified counting sort algorithm.

- A single-chip scalable and compact FPGA-based architecture of the proposed counting sort algorithm which specifically addresses the issue of sorting large volume of integer or fractional data.

- An improved FPGA-based noise estimation where the following improvements have been made:

- Excludes highly undesirable external SRAM.

- Removes 53% BRAM utilization in logorithmic computation.

- the 2006 IEEE International Conference on Image Processing (object detection) [36],

- the 41st IEEE Conference on Information Sciences and Systems (sorting) [37],

- the 2007 IEEE International Conference on Image Processing (contour tracing) [38], and

- the 2007 IEEE International Conference on Systems, Man, and Cybernetics (contour filling) [39].

<sup>&</sup>lt;sup>1</sup>At the time of this thesis publication, four papers based on this thesis are published in the Proceedings of:

- 13

- Integrates into one FPGA device where video object detection and contour tracing and filling are implemented.

- A scalable and compact architecture for FPGA-based object detection.

- An implementation of chaotic contour tracing and filling of video objects on FPGA.

Various referenced architectures and implementation for sorting, video noise estimation, object detection and contour tracing and filling are studied, and their characteristics and performance are analyzed and compared with the proposed methods.

#### 1.5 Thesis Outline

The remainder of the thesis is organized as follows.

Chapter 2 presents the proposed FPGA-based implementation of modified counting sort algorithm which is utilized in the implementation of spatial video noise estimation. Section 2.2 describes the related work to both sorting large volume. The modified counting sort algorithm and its adaptation to the FPGA implementation, verification and results are described in section 2.3 through 2.6.

In chapter 3, we outline an efficient hardware architecture in section 3.4 of the reference homogeneity-based noise estimation algorithm, which is described in section 3.3. The improvements of the proposed architecture and results are discussed in section 3.5.

Chapter 4.1 proposes a robust real-time, scalable and modular FPGA-based implementation of a spatio-temporal video objects detection. Section 4.2 outlines the reference algorithm and section 4.3 depicts the proposed architecture. Section 4 contains Verification and synthesis results are given in section 4.4.

14

In chapter 5, we propose novel FPGA-based architecture and its implementation of contour tracing and filling of video objects. Section 5.2 describes the related work and section 5.3 gives an overview of the contour tracing and filling algorithms [8]. Our proposed architecture is outlined in section 5.4, while section 5.5 contains experimental results. Note that the output of the proposed system is an image with filled moving objects, and their corresponding contour chain codes. Therefore, final results of the FPGA are presented in chapter 5.

Chapter 6 concludes the thesis and suggests future work.

# Chapter 2

# A Modified Counting Sort

# Algorithm and its FPGA

## Implementation

Many video processing algorithms, such as video noise estimation [13], often require sorting large volume of data. This chapter proposes a single-chip scalable and compact FPGA-based architecture of a modified counting sort algorithm, which specifically addresses the issue of sorting large volume of integer or fractional data.

### 2.1 Introduction

Sorting (in ascending order) is a process to rearrange a given set of keys  $a_0, a_1, ..., a_{N-1}$  into a set  $d_0 = a_{i_0}, d_1 = a_{i_1}, ..., d_{N-1} = a_{i_{N-1}}$  such that  $d_0 \le d_1 \le d_1$

Sorting a large volume of integer data is computationally intensive and is often

16

required in diverse applications such as video processing [13] and ATM switching [14]. Software-based implementation for sorting large volume of data is still slow for real-time applications, hence hardware acceleration is inevitable. Although parallel computing based solutions are inherently very flexible, heat dissipation and area are all increased. Designing a full-custom ASIC chip provides the highest processing speed with minimal power consumption, but requires a longer design cycle, expensive engineering cost, and is extremely inflexible. FPGAs, which fill the gap between general purpose sequential processors (GPPs) or parallel computers and ASICs are, therefore, utilized in many embedded systems. Evolving high-density FPGA architectures, such as those with embedded multipliers, high number/amount of memory blocks and high pin count, make FPGAs as an ideal solution for accelerating heavy number crunching operations such as those required in video processing.

The choice of an optimal sorting algorithm and adapting it to FPGAs are critical to have an optimized compact implementation. In applications that require sorting, it is most likely that sorting is a very small part of the whole application [13, 40]. The use of dedicated sorting chips is not a choice in cost-sensitive system designs as this would increase bill of material (BOM) costs. Implementing comparative based sorting methods [14, 18] would consume an enormous amount of FPGA resources.

In this chapter, we propose a modified counting sort algorithm [3] and an architecture such that it is well suited for an FPGA-based implementation. The primary motivation for designing a compact and efficient implementation for sorting large data volumes comes from the need to gain real-time performance in video processing algorithms [13,40]. The noise estimation algorithm in [13] requires to sort approximately 8000 fractional keys (variances) in real time, which is 33 ms for a standard video source running at 30 frames/s. The number of keys to be sorted could be well over 8000 for higher video frame sizes such as HDTV video resolution, and sorting is a

very small part of [13] and many other video processing applications [40]. Hence a scalable, real-time and compact implementation for sorting variable and large volume of data is needed.

#### 2.2 Related Work Review

In recent years, much research has been carried out implementing parallel sorting algorithms on ASICs, but very little emphasis has been put on FPGA-based implementations. Most of the FPGA-based architectures are based on pure comparison sorting algorithms. The area and time complexity becomes an enormous issue when sorting has to be performed on a very larger volume of data.

Studies carried out in [18] investigate trade-off of cost versus performance for a hybrid sorting algorithm of large data. This hybrid sorting algorithm is split into a sequential merge sorting algorithm running on a sequential processor, and a systolic insertion sorting algorithm running on a Xilinx XCV1000 FPGA co-processor at 66 MHz. Results in [18] show that having an FPGA as a co-processor improves the overall performance of the hybrid sorting algorithm up to a speed-up factor of 4. Furthermore, this speed-up factor is increased up to 100, using as many as 16 FPGA co-processors to sort 4096 keys.

Huang et al. propose a hardware design architecture in [4] for merge-sorting networks with a fixed size Batcher's sorting network. The number of sorting data N can be increased by modifying an address controller which controlls the memory accesses and increasing the amount of memory. However, performance of this architecture is considerably low for applications that require real time sorting performance such as in [13]. Our proposed architecture achieves a significant speed-up factor of 165 when compared to the architecture presented in [4].

A VLSI architecture presented in [14] sorts small continuous data sequences up

to 256 keys and partially sorts longer sequences. Here, a regular architecture based on a chain of basic sorting units (BSU) is introduced which can handle a maximum operating frequency of 50 MHz.

The architectures in [14, 18] are based on comparative based sorting methods, therefore implementing [14, 18] on FPGAs would consume more FPGA internal resources (slices) than the proposed architecture.

In video processing, sorting is widely used in rank-order filters which are preferred over linear filters [19]. Here, the complexity of sorting is relatively small as the resolution and the number of data becomes small and no stable sorting is required. Several FPGA implementations for median filters have been presented [19–22] each of them exploiting different approaches for sorting architectures.

Maheshwari et al. [19] have taken a simple approach to a 3x3 median filter implementation on a Xilinx XC series FPGA. The elements in the 3x3 kernel are first sorted vertically, followed by horizontally, thereby producing the median in the center of the 3x3 kernel.

A bit serial sorting algorithm, similar to Quicksort, is introduced in [20], and a general purpose median filter is implemented on a Xilinx XC4010E FPGA. The implementation is very compact, occupying only 15 CLBs, but achieves real-time performance of 25 fps for 512x512 8 bits/pixel.

Hamid et al. [21] present a genetic algorithm on a Xilinx Spartan-II FPGA to optimize the tasks of the soft morphological filter (SMF). The genetic algorithm implementation essentially consists of a quick parallel sort algorithm, Biotonic Megasort. The maximum speed that the design can run is 56 MHz and it consumes about 87% slices in the FPGA.

Fahmy et al. [22] propose an efficient implementation of one dimensional (1D) median filters based on the cumulative histogram of the input samples. The imple-

mentation can process 72 MPixels/s for 8 bit pixel depth. The main drawback of [22] is that it is not extended to 2D median filters. Achieving timing constraints on the implementation may be very difficult for higher pixel depths, due to the nature of the priority encoder.

For sorting a large number of keys, although the comparative methods proposed in [19–22] can theoretically be extended, implementation of such methods on a resources constraint hardware such as FPGAs would not be feasible due to the large silicon area required.

## 2.3 A Modified Counting Sort Algorithm

In this section, we describe the proposed modified hardware-oriented sorting based on the counting sort algorithm [3] invented in 1954.

Table 2.1 lists the steps of a pseudo code of the original counting sort algorithm [3]. It starts sorting N integer elements by first counting the number of occurrences for every element in the input unsorted array, A[0..N-1]. The 'rank' of each element is then determined by counting the number of elements less than or equal to the element being considered, and is stored in the array  $C[0..2^k-1]$ . Each element in the input array is read from the 'right' and put in the array D[0..N-1] (which contains the sorted elements) at the location stored in the array  $C[0..2^k-1]$ . At first, the array  $C[0..2^k-1]$  provides the position of sorted array D[0..N-1] for the first distinct element read from the array A[0..N-1]. If there are multiple occurrences for any element in A[0..N-1], the next position is obtained by simply subtracting one from the corresponding location in  $C[0..2^k-1]$ , and the new result is stored back into the array  $C[0..2^k-1]$ . Once all the elements in the input array are read and scanned for the location of the array D[0..N-1] from the array  $C[0..2^k-1]$ , the array D[0..N-1] contains the stably sorted elements.

Table 2.1: Original Counting Sort Algorithm [3].

```

Input : A[0..N-1], N integer keys in the

range of 0, ..., 2^k - 1 to be sorted.

Output : D[0..N-1], Sorted keys.

// Initialize array B[0..2^k - 1] to \theta.

B[0..2^k - 1] \leftarrow 0

// Count same integers in A[0..N-1]

3:

for i \leftarrow 0 to N-1 do

4:

B[A[i]] \leftarrow B[A[i]] + 1

5:

6: // Initialize C[0..2^k - 1] and set C[0] = 0

// Compute the rank of each elements in A[0..N-1].

for i \leftarrow 1 to 2^k - 1 do

8:

C[i] \leftarrow B[i] + C[i-1]

9:

10: // Read each element from array A[0..N-1]

// starting from right and place them in D[0..N-1]

// at the position given by the content of C[0..2^k-1].

for i \leftarrow N-1 to 0 do

11:

D[C[A[i]]] \leftarrow A[i]

12:

C[A[i]] \leftarrow C[A[i]] - 1

13:

\mathbf{return}(D[0..N-1])

14:

```

We propose two modifications to this algorithm so that it is well suited for a hardware implementation. First, the array  $C[0...2^k - 1]$  is computed as

$$C(i) = \sum B(j)$$

for  $i \in \{0, ..., N-1\}$  ,  $j \in \{0, ..., i\}$ . (2.1)

With this modification C[0] = B(0), whereas in the original algorithm C[0] = 0.

Second, instead of using a decrementor in the step 13 of Table 2.1 ( $C[A[i]] \leftarrow C[A[i]] - 1$ ), the modification requires an incrementor ( $C[A[i]] \leftarrow C[A[i]] + 1$ ), which adds no additional cost in terms of hardware resources, timing or design complexities. The proposed modified algorithm is listed in Table 2.2.

The direct hardware implementation of the sorting algorithm [3] requires reading the array A[0..N-1] in the reverse direction (right to left) as it was written to. For applications which require real-time performance, ability to stream data continuously

Table 2.2: Proposed Modified Counting Sort Algorithm.

```

Input: A[0..N-1], N integer keys in the

range of 0, ..., 2^k - 1 to be sorted.

Output: D[0..N-1], Sorted keys.

// Initialize array B[0..2^k-1] to \theta.

B[0..2^k - 1] \leftarrow 0

2:

// Count same integers in A[0..N-1]

3:

for i \leftarrow 0 to N-1 do

4:

B[A[i]] \leftarrow B[A[i]] + 1

5:

// Initialize C[0...2^{k}-1] and set C[0] = B[0]

for i \leftarrow 1 to 2^k - 1 do

7:

C[i] \leftarrow B[i] + C[i-1]

8:

9: // Read each element from array A[0..N-1]

// starting from left and place them in D[0..N-1]

// at the position given by the content of C[0...2^k-1].

for i \leftarrow 0 to N-1 do

10:

11:

D[C[A[i]]] \leftarrow A[i]

12:

C[A[i]] \leftarrow C[A[i]] + 1

13:

\mathbf{return}(D[0..N-1])

```

is an important factor. If a memory is read in the reverse order, then all the data in that memory must be read before the next data can be written, unless additional logic is implemented to handle reverse reading efficiently. This means that the overall throughput of the system is reduced by 50%. However, if the data can be read in the same order as it is written to (in a First In First Out (FIFO) fashion), then this problem is eliminated and design complexities and resources are both reduced. The proposed modifications to [3] allow us to use the array A as a FIFO, hence the proposed architecture is able to continuously stream unsorted keys without any timing or additional area overheads.

## 2.4 Proposed Sorting Architecture

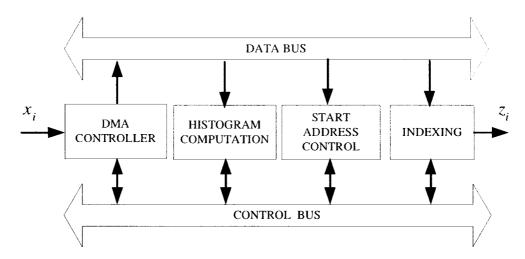

This section describes the proposed architecture of a *single chip* FPGA implementation for the counting sort algorithm described in the previous section. Fig. 2.1 depicts

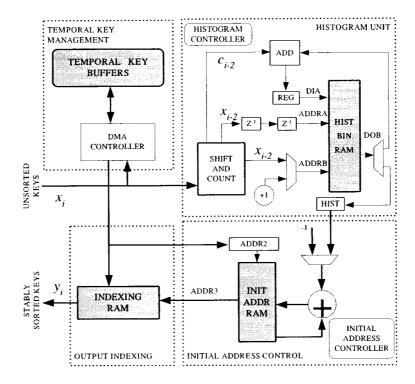

the overall system level architecture, which takes the unsorted keys  $x_i$ , i=1,...,N as input and outputs stably sorted keys  $z_i$ . A more detailed block diagram is shown in Fig. 2.2. It can be seen that the implementation performs a number of tasks to stably sort a set of unsorted input keys. The input keys are buffered in the TEMPORAL KEY BUFFERS since all the data in a sequence is required to complete counting the same integers in A[0..N-1] (building a histogram), which is performed in the HISTOGRAM UNIT. Once the histogram is computed, INITIAL ADDRESS CONTROL module reads the histogram and generates the initial starting addresses (C[i], step 8 in Table 2.2). In the next step, the Direct Memory Access (DMA) reads the data from the TEMPORAL KEY BUFFERS and indexes into to the INDEXING RAM based on the address stored in the INIT ADDR RAM. The detailed description of each module is given in the next sections.

Figure 2.1: Overall System Level Sorting Architecture.

#### 2.4.1 TEMPORAL KEY MANAGEMENT Module

The core of the TEMPORAL KEY MANAGEMENT module is the DMA controller that is responsible of moving input data between the memory and the appropriate processing nodes at high speed to sustain real-time performance. Our implementation performs

Figure 2.2: Detailed Circuit Diagram of the Sorting Architecture.

the histogram computation as new data is being arrived and are written into the TEMPORAL KEY BUFFERS by the DMA. While the previous set of data is being sorted at the back-end of processing, it is necessary to read those data from the TEMPORAL KEY BUFFERS while the new data is being written. Our DMA architecture manages these data transfers seamless to the other processing nodes.

#### 2.4.2 Architecture of the HISTOGRAM UNIT

We implemented histogram computation using a number of concatenated dual-ported Block of RAMs (BRAMs) in order to support sorting higher resolution integers. The architecture is scalable and flexible since the implementation automatically computes the minimum required BRAMs and concatenates them at design compile time. The port A of the BRAMs is dedicated for histogram computation while port B is used for reading it out and clearing the content of the memory at the end of a sequence. The

SHIFT AND COUNT module counts co-occurrence of 3 consecutive keys so that reading data from an address of the RAMs is avoided while writing to the same location. The HISTOGRAM CONTROLLER controls all controlling logic required in the HISTOGRAM UNIT.

## 2.4.3 Architecture of the INITIAL ADDRESS CONTROL Module

The Initial addresses control module is responsible for computing the starting addresses for each unsorted keys which are stored in the TEMPORAL KEY BUFFERS. These starting addresses, stored in the Init addresses are retrieved from the Output Indexing unit. For each histogram bin, the output of the Histogram unit is added to the content of the Init addresses for all the bins are computed, the Initial addresses controller triggers the DMA to output unsorted keys. For each unsorted keys, corresponding starting addresses are retrieved from the Init addresses are retrieved from the Init addresses the indexing ram is subtracted by one, which becomes the next starting address.

#### 2.4.4 OUTPUT INDEXING Module

At this final sorting stage, the unsorted keys are written in the INDEXING RAM. The write addresses to the INDEXING RAM are obtained from the INITIAL ADDRESS CONTROL module. Once the DMA has transferred a complete set of keys, the content of the INDEXING RAM is stably sorted keys, which are read by the OUTPUT CONTROLLER sequentially. Moreover, OUTPUT CONTROLLER clears the content of the INDEXING RAM at the end of each sequence.

#### 2.5 Simulation and Verification Results

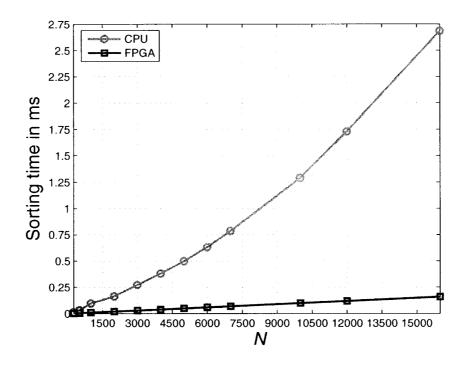

The modified counting sort algorithm was implemented in C on a PC with an Intel Pentium-IV 2.4 GHz processor for performance comparison between software and hardware implementations. Simulation results are shown in Fig. 2.3 for k = 12, where k is the number of bits in N. The execution time for the FPGA implementation includes data load and result unload time. The proposed FPGA implementation achieves greater than an order of magnitude performance improvements over the software implementation for N > 10000.

Figure 2.3: Complexity comparison between a CPU and FPGA.

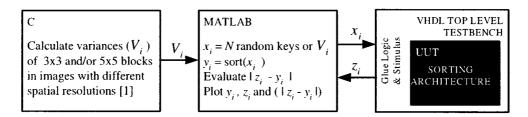

The video noise estimation algorithm [13], written in C, produces variances  $V_i$ ,  $i = 1, ..., N, N \in \mathbb{Z}$  of 3x3 or 5x5 blocks in an image, which are required to be sorted for further processing. As it can be seen from Fig. 2.4, a part our verification process consists of using these variances as test stimulus  $x_i$  to the VHDL testbench of the proposed sorting design, Unit Under Test (UUT), through the MATLAB environment.

Figure 2.4: Simulation environment with VHDL Testbench and C/MATLAB.

Further verification was performed by using MATLAB to generate N random keys, and setting them as stimulus for the UUT. The sorted keys  $z_i$  from VHDL environment are then compared with the appropriate MATLAB sorted keys  $y_i$ . We have extensively run this simulation with different number of N and verified the accuracy of our implementation. For instance, we obtained large and different amount of elements  $(V_i)$  with [13] by using images with different spatial resolutions and setting the block size to 3x3 or 5x5.

A Virtex II-Pro evaluation board was used for actual hardware verification. We sent  $x_i$  and read-back  $z_i$  through a parallel port and result were successfully verified with  $y_i$ .

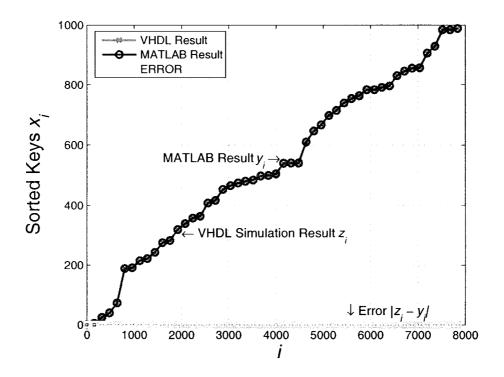

Fig. 2.5 reveals that the sorted elements  $z_i$  obtained from the proposed implementation are identical to the MATLAB sorted elements  $y_i$ .

#### 2.6 Synthesis and Implementation Results

#### 2.6.1 Implementation

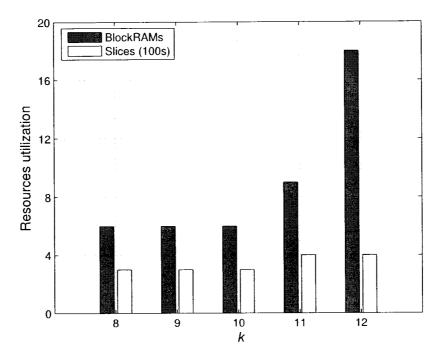

The proposed architecture was synthesized with Synplicity Synplify 7.3. and placed and routed targeting an XC2VP20 FPGA with Xilinx ISE 6.3 Alliance place and route tool. The synthesis and place and routed implementation results indicate that the complete architecture is very compact occupying only about 15 % of slices and about 30 % of the BRAMs for 12 bits wide (integer or fractional), 16K (16384) keys.

Furthermore, the proposed design was synthesized for various values of k, and Fig. 2.6 depicts the FPGA resources utilization. Note that the proposed architecture is single-chip solution for sorting a large number of keys and it uses internal BRAMs for local data storage. Hence, BRAM utilization is directly proportional to k, however the slices usage remain very low. The proposed architecture was easily routed constraining a 7.5 ns clock cycle, hence the design can be clocked at 133 MHz with the slowest FPGA speed grade (-5). At a 133 MHz clock, Xilinx XPower tools to estimated 1.8 W power dissipation of our design for a toggle-rate of 50 %.

Figure 2.5: Sample comparison between VHDL and MATLAB results.

#### 2.6.2 Comparison to the Existing Methods

Table 2.3 lists performance and architectural differences between the proposed method and the architecture described in [4]. Notice that [4] is a  $0.35\mu m$  CMOS based ASIC architecture, therefore timing and area optimization can be performed better than

Table 2.3: Performance and area comparison for sorting 128 keys of 8 bits with [4] and proposed method.

|               | Ref [4]                           | Proposed               |

|---------------|-----------------------------------|------------------------|

| Max Clock     | 50 MHz                            | 133 MHz                |

| Sorting Time  | $158.72~\mu s$                    | $0.962~\mu \mathrm{s}$ |

| Area (Memory) | 128 Bytes                         | 640 Bytes              |

| Gates         | 3185 Gates                        | approx. 9000 Gates     |

| Architecture  | $0.35\mu\mathrm{m}~\mathrm{CMOS}$ | FPGA                   |

on an FPGA. For comparison purpose we have chosen 128 keys of 8 bits for our implementation and verification in order to match with the test vectors used in the reference method [4]. As it can be seen from Table 2.3, the performance of our proposed method is significantly higher (165 times faster) than [4]. Although the area complexity of the proposed method is higher than in [4], our implementation does not utilize considerable amount of resources on presently available FPGAs.

Furthermore, the proposed architecture contains many advantages over the sorting architecture presented in [18], which requires a CPU processor in addition to an FPGA to complete the sorting. For sorting very large number of keys in real-time, the technique described in [18] would require multiple FPGAs. In contrast, our proposed architecture is a compact and based on a single chip FPGA device which is capable of sorting a large number of keys.

The comparative methods presented in [14,19–22] can be extended to sort a large number of keys on a resources unconstrained hardware platform such as a dedicated ASIC. However, this would increase both the cost and complexity of the overall implementation, specially when sorting is a very small part of a complete application such as in video processing [13,40].

Figure 2.6: Internal FPGA resources utilization.

### 2.7 Chapter Summary

In this chapter, we proposed a modified counting sort algorithm and a novel, scalable and compact single chip FPGA architecture for stably sorting a large volume of integer and fractional keys in real-time for video processing applications. The proposed architecture of the sorting is scalable to gain higher throughput by trading off only the FPGA internal memory resources. The proposed implementation was successfully verified on an actual hardware platform that consists of a Xilinx XC2VP20 FPGA. Sorting performance comparisons showed that the proposed implementation is significantly better than the existing methods. Furthermore, when compared to pure software implementation for large N, we obtained a speed-up factor of more than 10 with the proposed architecture. In addition, an efficient noise estimation implementation which eliminates the need of SRAM was proposed.

## Chapter 3

## Improved FPGA-based

## Implementation of Noise

### **Estimation**

In this chapter, we outline an improved FPGA-based noise estimation implementation of Lapalme's et al. [5]. The focus of this thesis is to implement and integrate all of the core video processing algorithms (video noise estimation, moving object detection, and contour analysis) required in the moving video object segmentation [1], into one FPGA. As such, it is imperative to device an efficient hardware architecture.

#### 3.1 Introduction

The effectiveness of video processing systems heavily depend on the amount of unwanted noise contained in a corrupted video signal due to, for e.g., video acquisition, processing, storage or transmission. Hence, reducing the noise in video signals by means of noise estimation algorithms is an active research field. The state-of-the-art noise estimation methods calculate the level of noise, and facilitate the video processing algorithms to enhance the quality of video sequences to the amount of noise present. Thus, a noise estimation algorithm, such as [13], which reliably estimates noise both in highly noisy and good quality images, is imperative to demodulate vital content from a corrupted video sequence. Intra-field and block-based noise estimation method proposed in [13] finds the noise variances of a set of blocks classified as the most homogeneous blocks to estimate the global image noise variance. The algorithm [13] requires to sort large amount of data, which is the primary computational bottleneck in its hardware as well as software implementations.

#### 3.2 Related Work Review

Except the architecture proposed in [5], no previous studies have been carried out on FPGA-based implementation of noise estimation algorithms, to the best knowledge of the author. Although, Lapalme's FPGA implementation [5] of the reliable spatial video noise estimation algorithm [13] runs real-time, it requires a significant amount of FPGA resources and runs at a slower speed. The motivation to improve the architecture [5], by means of the proposed modified counting sort algorithm comes from the need to integrate the proposed improved noise estimation implementation with other high-level video processing tasks, described in the chapters 4 and 5, within a single FPGA device.

#### 3.3 Overview of the Reference Noise

#### **Estimation Algorithm**

In this section we outline the noise estimation algorithm [13]. The spatial noise estimation method [13], which produces reliable estimates, finds homogeneous regions

by taking image structure into account. To reject structured blocks the algorithm [13] first divides the image into equal blocks of the size  $W \times W$ . For each block, a homogeneity measure  $\xi_{Bh}$  is then computed using eight high-pass directional filters. The mask of the horizontal direction scanning window on the image function I for W = 5 is illustrated in Eq. 3.1.

$$I_o(i) = -I(i-2) - I(i-1) + 4 \times I(i) - I(i+1) - I(i+2). \tag{3.1}$$

The homogeneity measure  $\xi_{Bh}$  is obtained by adding the absolute values of all eight high-pass directional filters.

The variance  $\sigma_{Bh}^2$  of each block is then calculated with

$$\sigma_{Bh}^2 = \frac{\sum_{(i,j)\in W_{ij}} (I(i,j) - \mu_{Bh})^2}{W \times W}.$$

(3.2)

Here,  $\mu_{Bh}$  is the sample mean defined as

$$\mu_{Bh} = \frac{\sum_{(i,j)\in W_{ij}} I(i,j)}{W \times W}.$$

(3.3)

The homogeneity measures  $\xi_{Bh}$  is sorted and variances  $\sigma_{Bh}^2$  corresponding to the top 10% of sorted  $\xi_{Bh}$  are selected. However, only the variances satisfying the condition given in Eq. 3.4 are averaged to obtain the global noise variance (estimation)  $\sigma_n^2$ .

$$|log(\sigma_{Bh}^2) - log(\sigma_{REF}^2)| < t_{\sigma}. \tag{3.4}$$

In Eq. 3.4,  $\sigma_{REF}^2$  is defined as a reference variance, which chosen as the median of the variances of the three most homogeneous blocks, and  $t_{\sigma}$  is a user defined threshold value.

#### 3.4 Proposed FPGA-based Architecture

The improvements achieved to the FPGA implementation presented in [5], primarily with the proposed modified counting sort algorithm described in sections 2.3 and 2.4 are outlined next. Fig. 3.1 illustrates the overall architecture of the noise estimation algorithm. Primary improvement was obtained by adopting the proposed modified counting sort algorithm described in sections 2.3 and 2.4 to [5]. The FPGA implementation in [5] requires two external SRAM memory modules for sorting. SRAMs are costly and increase the physical area and power consumption of the overall system. Thus it is highly desirable to minimally use these devices, except for other processing tasks, which inherently require the utilization of SRAMs for their implementation, such as HIGH-SPEED CACHE for contour tracing and filling described in chapter 5. Moreover, [5] implements logarithmic computation by means of a large look-up table, which requires more than 53% of BRAMs in the implemented FPGA device. In the proposed implementation, we employ an efficient logorithmic arhitecture [41], which utilizes zero BRAMs but only two multipliers and few slices.

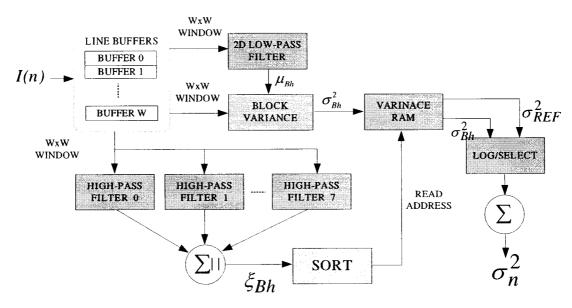

Figure 3.1: Proposed Architecture of the Noise Estimation Algorithm.

As can seen in Fig. 3.1, LINE BUFFERS are utilized with BRAMs, which generate  $W \times W$  blocks. In the 2D LOW-PASS FILTER block, the sample mean  $\mu_{Bh}$  is produced and passed BLOCK VARIANCE module which computes the variance  $\sigma_{Bh}^2$ . These block variances are then stored in the VARIANCE RAM. A set of eight HIGH-PASS FILTERS produces directional filters, and absolute value of the result of the directional filters are summed to produce the homogeneity measures  $\xi_{Bh}$ . The proposed modified counting sort algorithm described in detail in sections 2.3 and 2.4 is implemented in the SORT module, which sort the  $\xi_{Bh}$ , and indexes of the 10 % most homogeneous blocks are sent as the read address to the VARIANCE RAM, which outputs corresponding  $\mu_{Bh}$  and  $\mu_{REF}$ . LOG/SELECT block finds the logarithmic value of  $\mu_{Bh}$  and  $\mu_{REF}$ , which are compared to an application-dependent threshold as seen in Eq. 3.4 to select only the valid varinces. These varinces are are then summed in the accumulator to obtain the global noise variance (estimation)  $\sigma_n^2$ .

#### 3.5 Implementation Results