## AN OBSERVABLE DATA CACHE MODEL FOR FPGA

## **PROTOTYPING**

## PARTHASARATHY RAVISHANKAR

A Thesis

in

The Department

Of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements for the

Degree of Master of Applied Science (Electrical and Computer Engineering)

at

Concordia University Montréal, Québec, Canada

March 2013

© PARTHASARATHY RAVISHANKAR, 2013

# CONCORDIA UNIVERSITY SCHOOL OF GRADUATE STUDIES

| This is to cert | ify that the thesis prepared                               |                        |                                   |

|-----------------|------------------------------------------------------------|------------------------|-----------------------------------|

| By:             | Parthasarathy Ravishankar                                  |                        |                                   |

| Entitled:       | "An Observable Data Cache M                                | Iodel for FPGA Proto   | typing"                           |

| and submitted   | in partial fulfillment of the requ                         | uirements for the degr | ee of                             |

|                 | Master of App                                              | olied Science          |                                   |

| -               | n the regulations of this Univers<br>ginality and quality. | ity and meets the acce | pted standards with               |

| Signed by the   | final examining committee:                                 |                        |                                   |

|                 | Dr. Rabin Raut                                             |                        | Chair                             |

|                 | Dr. Benjamin Fung                                          |                        | Examiner, External To the Program |

|                 | Dr. Sofiene Tahar                                          |                        | Examiner                          |

|                 | Dr. Samar Abdi                                             |                        | Supervisor                        |

| Approved by:    | Dr. W. E. Lynch, Department of Electrical and              |                        | g<br>g                            |

| March           | 2013                                                       |                        |                                   |

|                 |                                                            |                        | A. L. Drew f Engineering and      |

Computer Science

## **ABSTRACT**

#### An Observable Data Cache Model for FPGA Prototyping

#### Parthasarathy Ravishankar

This work presents design of a configurable and observable model of L1 data cache memory and a novel method for integrating the model into an FPGA prototype. Embedded system software designers use in-circuit emulation on FPGA platforms to validate the functionality and performance of embedded software. Data cache, particularly L1, has a major impact of system performance, yet remains unobservable during software debugging and analysis. Our solution is to model the data cache as an on-chip hardware peripheral that can be integrated into the processor system and can display the state of the data cache at any given time. The model is synthesized on Xilinx Virtex 5 FPGA and validated using several benchmarks. The experimental results show that the model can accurately track cache hits and misses and can estimate the run time of an embedded software application with an average error of only 5.4%, and a worst case error of only 13.7%.

#### **ACKNOWLEDGEMENTS**

Foremost, I would like to express my gratitude to my supervisor Dr. Samar Abdi, for his support, motivation and patience throughout my study and research. I thank him for his generous contribution of time and expertise which guided me to successful completion of Master's thesis.

Besides my supervisor, I would like to thank the rest of my thesis committee members, Dr. Sofiene Tahar and Dr. Benjamin Fung for their invaluable comments and questions. I also thank Ted Obuchowicz - Engineering specialist, who was helpful every time I had difficulties with my software.

I would also like to thank my fellow labmates: Zaid, Richard, Paul, Karim, Ali, Ehsan and Kazem for your suggestions and all the discussions we had. It was always fun to work with you guys. I thank all my greatest friends in Canada and KDs for always cheering me on.

Finally I would like to thank my wonderful parents, grandparents and brother for their unconditional love and continuous support. My parents have been my biggest source of inspiration and I cannot thank them enough for whatever they have done to me.

To my parents

# **CONTENTS**

| List of | Table | es                                               | ix   |

|---------|-------|--------------------------------------------------|------|

| List of | Figu  | res                                              | x    |

| List of | Acro  | nyms                                             | xiii |

| List of | Princ | cipal Symbols                                    | xiv  |

| 1 Int   | trodu | ction                                            | 1    |

| 1.1     | Mo    | otivation                                        | 2    |

| 1.2     | En    | nbedded System Validation                        | 2    |

| 1.2     | 2.1   | Software simulation                              | 2    |

| 1.2     | 2.2   | FPGA Prototyping                                 | 3    |

| 1.3     | Ra    | tionale for modeling direct mapped L1 data cache | 3    |

| 1.4     | Me    | ethodology                                       | 5    |

| 1.5     | Re    | lated Work                                       | 7    |

| 1.5     | 5.1   | Analytical model                                 | 7    |

| 1.5     | 5.2   | Trace driven simulation                          | 8    |

| 1.5     | 5.3   | Single pass simulation                           | 9    |

| 1.5     | 5.4   | Partial trace simulation                         | 10   |

| 1.5     | 5.5   | High level simulation                            | 12   |

| 1.5     | 5.6   | Novelty of pCache                                | 14   |

| 1.6     | Th    | esis Contribution                                | 15   |

| 1.7     | Th    | esis Organization                                | 16   |

| 2 Pe    | riphe | eral Cache                                       | 17   |

| 2.1     | рC    | ache - Interface                                 | 17   |

|   | 2.2   | pCache Architecture                   | 18 |

|---|-------|---------------------------------------|----|

|   | 2.3   | Write Policies                        | 19 |

|   | 2.3.  | 1 Write through policy                | 19 |

|   | 2.3.2 | 2 Write back policy                   | 20 |

|   | 2.4   | Control Unit                          | 21 |

|   | 2.5   | pCache – Features                     | 23 |

|   | 2.5.  | 1 Write policy                        | 24 |

|   | 2.5.2 | 2 Line size                           | 24 |

|   | 2.5.3 | 3 Cache size                          | 24 |

|   | 2.5.4 | 4 Cacheable address range             | 24 |

| 3 | Fund  | ctional Validation                    | 25 |

|   | 3.1   | Built-in cache based reference system | 25 |

|   | 3.2   | pCache based model                    | 26 |

|   | 3.3   | Validation of Write through mode      | 28 |

|   | 3.3.  | 1 Read transactions                   | 28 |

|   | 3.3.2 | 2 Write transactions                  | 31 |

|   | 3.4   | Validation of Write back mode         | 33 |

|   | 3.4.  | 1 Read transactions                   | 33 |

|   | 3.4.2 | 2 Write transactions                  | 37 |

|   | 3.5   | Validation using Software debugger    | 41 |

| 4 | Tim   | ning Analysis                         | 45 |

|   | 4.1   | Bus Characteristics                   | 46 |

|   | 4.1.  | 1 PLB Behavior                        | 46 |

|   | 4.1.2 | 2 XCL Behavior                        | 47 |

|   | 4.2   | Parameterized cache timing model      | 48 |

| 4.3     | Characterization of the Write through Cache     | 49 |

|---------|-------------------------------------------------|----|

| 4.4     | Characterization of the Write back Cache        | 50 |

| 4.5     | Timing Validation                               | 52 |

| 4.6     | Run-time Estimation Error                       | 64 |

| 4.6     | 5.1 Sources of Error                            | 65 |

| 4.6     | 5.2 Error Reduction                             | 66 |

| 4.7     | Speed                                           | 67 |

| 4.8     | Performance optimization using observable cache | 68 |

| 4.9     | Cache Design Exploration                        | 71 |

| 5 Co    | onclusion and Future work                       | 76 |

| Append  | lix                                             | 78 |

| A.1     | Cache Controller                                | 78 |

| B.1     | Tag memory                                      | 91 |

| Referen | nces                                            | 96 |

# **List of Tables**

| Table 1 The configuration parameters of pCache                       | 23 |

|----------------------------------------------------------------------|----|

| Table 2 Average XCL delay in Write through cache                     | 49 |

| Table 3 Average XCL delay in 4-word Write back cache                 | 50 |

| Table 4 Average XCL delay in 8-word Write back cache                 | 51 |

| Table 5 Performance estimation of Dhrystone in 4-word WT data cache  | 52 |

| Table 6 Performance estimation of Dhrystone in 8-word WT data cache  | 53 |

| Table 7 Performance estimation of Quicksort in 4-word WT data cache  | 54 |

| Table 8 Performance estimation of Quicksort in 8-word WT data cache  | 55 |

| Table 9 Performance estimation of JPEG in 4-word WT data cache       | 56 |

| Table 10 Performance estimation of JPEG in 8-word WT data cache      | 57 |

| Table 11 Performance estimation of Dhrystone in 4-word WB data cache | 58 |

| Table 12 Performance estimation of Dhrystone in 8-word WB data cache | 59 |

| Table 13 Performance estimation of Quicksort in 4-word WB data cache | 60 |

| Table 14 Performance estimation of Quicksort in 8-word WB data cache | 61 |

| Table 15 Performance estimation of JPEG in 4-word WB data cache      | 62 |

| Table 16 Performance estimation of JPEG in 8-word WB data cache      | 63 |

| Table 17 Average error in timing estimation using pCache based model | 65 |

| Table 18 Comparison of run time of JPEG application                  | 67 |

# **List of Figures**

| Figure 1.1 Processor-Memory gap [20]                                                  | 1  |

|---------------------------------------------------------------------------------------|----|

| Figure 1.2 Influence of associativity of cache on energy [P. Marwedel et al., ASPDAC, |    |

| 2004]                                                                                 | 4  |

| Figure 1.3 Modeling methodology                                                       | 5  |

| Figure 2.1 Block diagram of pCache - processor bus interface.                         | 17 |

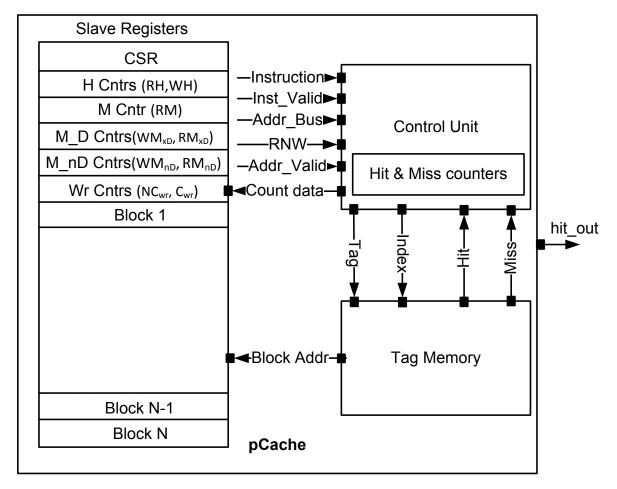

| Figure 2.2 Block diagram of pCache.                                                   | 18 |

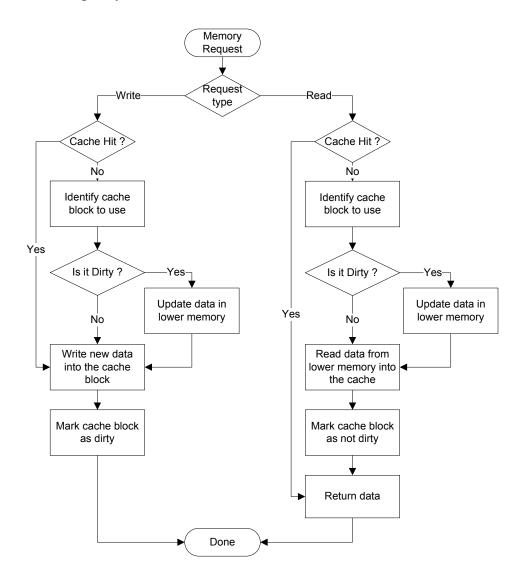

| Figure 2.3 Flow chart describing write through policy.                                | 19 |

| Figure 2.4 Flow chart describing write back policy.                                   | 20 |

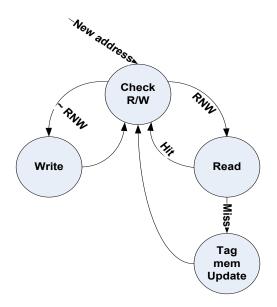

| Figure 2.5 Control Unit FSM – Write through policy.                                   | 21 |

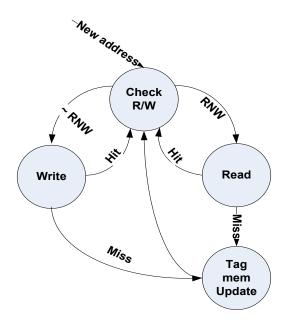

| Figure 2.6 Control Unit FSM – Write back policy.                                      | 22 |

| Figure 3.1 Block diagram of MicroBlaze core with built-in data cache                  | 25 |

| Figure 3.2 Block diagram of MicroBlaze core with pCache module.                       | 26 |

| Figure 3.3 Block diagram of datapath with pCache module                               | 27 |

| Figure 3.4 Read miss in 4 word WT built-in data cache                                 | 28 |

| Figure 3.5 Read miss in pCache                                                        | 28 |

| Figure 3.6 Read hit in built-in WT data cache                                         | 30 |

| Figure 3.7 Read hit in pCache                                                         | 30 |

| Figure 3.8 Consecutive writes in built-in WT data cache                               | 31 |

| Figure 3.9 Non consecutive write in built-in WT data cache                            | 32 |

| Figure 3.10 Non consecutive and consecutive write in pCache                           | 33 |

| Figure 3.11 Read hit in built-in WB data cache                                        | 34 |

| Figure 3.12 Read hit in pCache                                                        | 34 |

| Figure 3.13 Read miss (1 dirty) in built-in WB data cache                          | 35 |

|------------------------------------------------------------------------------------|----|

| Figure 3.14 Read miss (1 dirty) in pCache                                          | 35 |

| Figure 3.15 Read miss not dirty in built-in WB data cache                          | 36 |

| Figure 3.16 Read miss not dirty in pCache                                          | 37 |

| Figure 3.17 Write hit in built-in WB data cache                                    | 38 |

| Figure 3.18 Write hit in pCache                                                    | 38 |

| Figure 3.19 Write miss 1 dirty in built-in WB data cache                           | 39 |

| Figure 3.20 Write miss 1 dirty in pCache                                           | 39 |

| Figure 3.21 Write miss not dirty in built-in WB data cache                         | 40 |

| Figure 3.22 Write miss not dirty in pCache                                         | 40 |

| Figure 3.23 Result of the test code in 4 word built-in write back data cache model | 42 |

| Figure 3.24 Result of the test code in 4 word write back pCache based model        | 42 |

| Figure 3.25 Contents of the pCache.                                                | 43 |

| Figure 4.1 Read and write operations to off-chip DDR memory via PLB                | 46 |

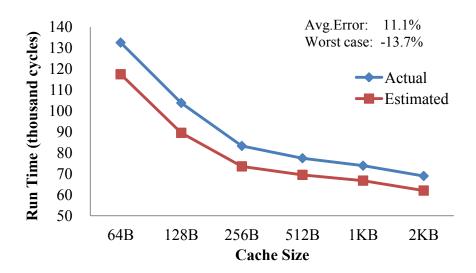

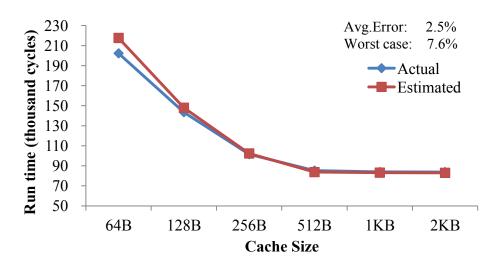

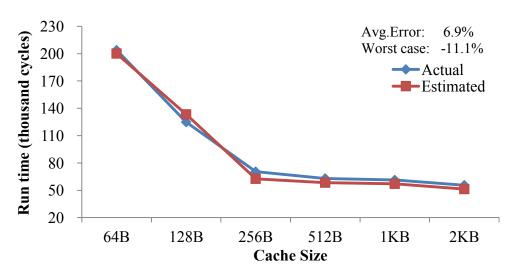

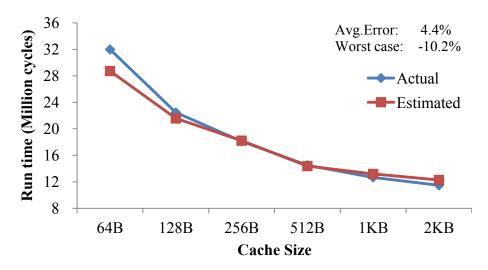

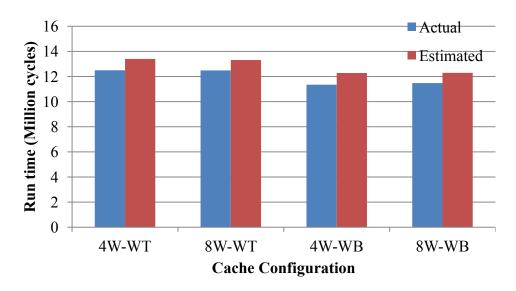

| Figure 4.2 Plot of performance estimation of Dhrystone in 4-word WT data cache     | 53 |

| Figure 4.3 Plot of performance estimation of Dhrystone in 8-word WT data cache     | 54 |

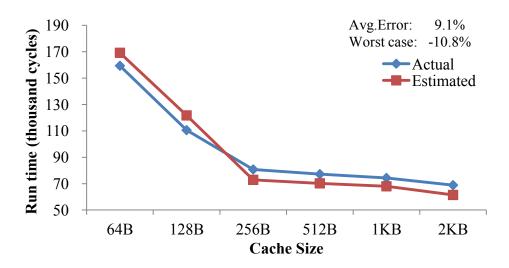

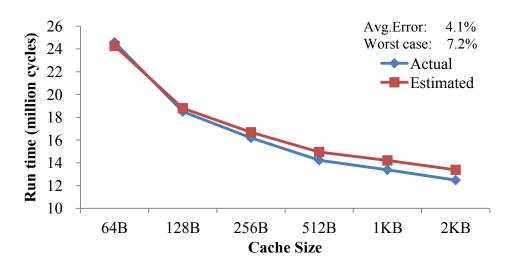

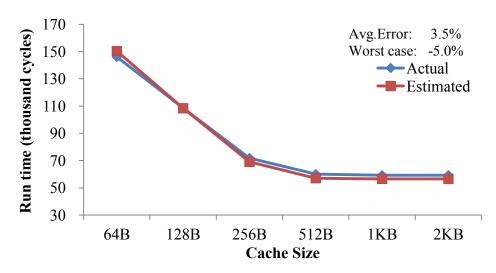

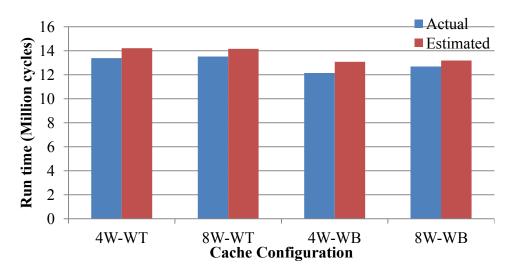

| Figure 4.4 Plot of performance estimation of Quicksort in 4-word WT data cache     | 55 |

| Figure 4.5 Plot of performance estimation of Quicksort in 8-word WT data cache     | 56 |

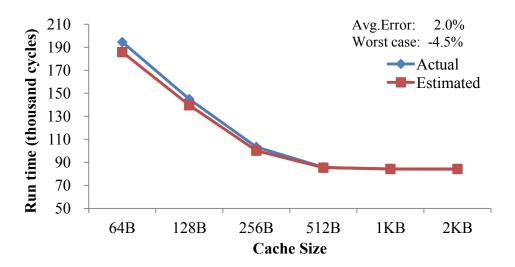

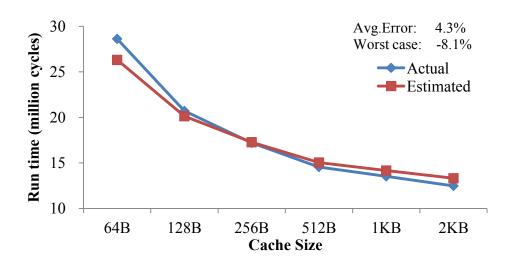

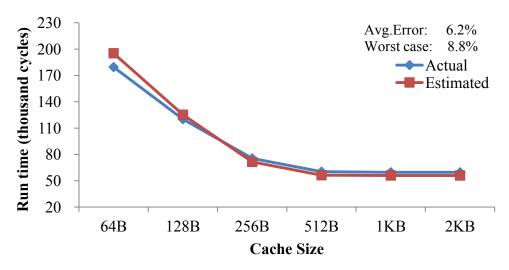

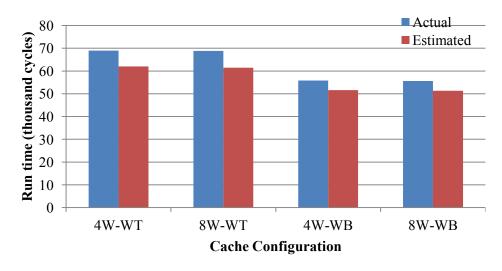

| Figure 4.6 Plot of performance estimation of JPEG in 4-word WT data cache          | 57 |

| Figure 4.7 Plot of performance estimation of JPEG in 8-word WT data cache          | 58 |

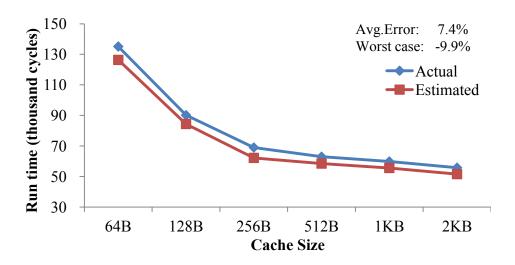

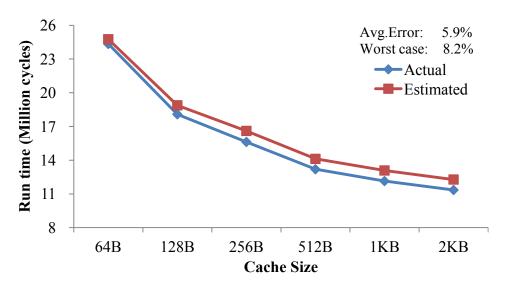

| Figure 4.8 Plot of performance estimation of Dhrystone in 4-word WB data cache     | 59 |

| Figure 4.9 Plot of performance estimation of Dhrystone in 8-word WB data cache     | 60 |

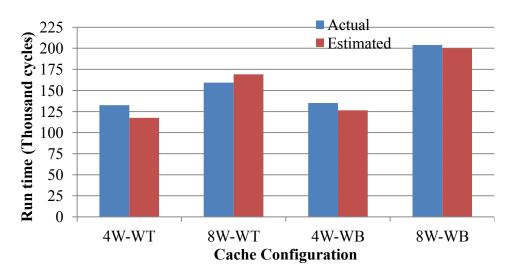

| Figure 4.10 Plot of performance estimation of Quicksort in 4-word WB data cache    | 61 |

| Figure 4.11 Plot of performance estimation of Quicksort in 8-word WB data cache | 62 |

|---------------------------------------------------------------------------------|----|

| Figure 4.12 Plot of performance estimation of JPEG in 4-word WB data cache      | 63 |

| Figure 4.13 Plot of performance estimation of JPEG in 8-word WB data cache      | 64 |

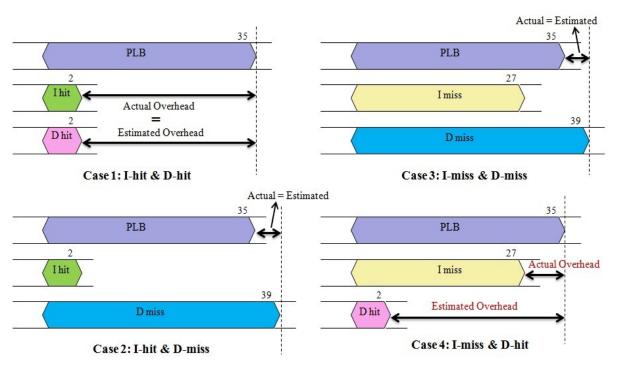

| Figure 4.14 Impact of Instruction Cache on Overhead                             | 66 |

| Figure 4.15 Address conflict in data cache (1)                                  | 69 |

| Figure 4.16 Address conflict in data cache (2)                                  | 70 |

| Figure 4.17 Design space exploration of 2KB data cache for JPEG                 | 72 |

| Figure 4.18 Design space exploration of 1KB data cache for JPEG                 | 73 |

| Figure 4.19 Design space exploration of 2KB data cache for Dhrystone            | 74 |

| Figure 4.20 Design space exploration of 64B data cache for Dhrystone            | 74 |

| Figure 4.21 Design space exploration of 256B data cache for Quicksort           | 75 |

## **List of Acronyms**

FPGA Field Programmable Gate Array

SRAM Static Random Access Memory

L1 Level 1

TLM Transaction Level Modeling

ASIC Application Specific Integrated Circuit

DDR2 SDRAM Double Data Rate Synchronous Dynamic Random Access Memory

LRU Least Recently Used

ILA Integrated Logic Analyzer

CRCB Configuration Reduction approach by the Cache Behavior

CSR Control Status Register

FSM Finite State Machine

RNW Read Not Write

WT Write Through

WB Write Back

pCache Peripheral Cache

ICache Instruction Cache

DCache Data Cache

R/W Read or Write

BRAM Block Random Access Memory

UART Universal Asynchronous Receiver Transmitter

DLMB Data Local Memory Bus

ILMB Instruction Local Memory Bus

PLB Processor Local Bus

DXCL Data-Xilinx Cache Link

IXCL Instruction-Xilinx Cache Link

EDK Embedded Development Kit

JTAG Joint Test Action Group

XMD Xilinx Microprocessor Debugger

FSL Fast Simplex Link

## **List of Principal Symbols**

T<sub>pcache</sub> Run time in pCache based model

T<sub>est</sub> Estimated run time

T<sub>built-in</sub> Run time in built-in cache system

H Number of hits

M Number of misses

$T_{xel\text{-hit}}$  Average time for hit via CacheLink

T<sub>xcl-miss</sub> Average time for miss via CacheLink

T<sub>plb</sub> Average time for access via PLB

RH Number of read hits

RM Number of read misses

NC<sub>wr</sub> Number of non-consecutive writes

C<sub>wr</sub> Number of consecutive writes

$N_{rf\ eye}$  Number of refresh cycles

T<sub>rd</sub> Average time for read via PLB

T<sub>wr</sub> Average time for write via PLB

T'<sub>rh</sub> Average time for read hit via XCL

T'<sub>rm</sub> Average time for read miss via XCL

T'nc-wr Average time for non consecutive writes via XCL

T'<sub>c-wr</sub> Average time for consecutive writes via XCL

WH Number of write hits

WM<sub>nD</sub> Number of write miss not dirty

$WM_{xD}$  Number of write miss with x dirty bits

RM<sub>nD</sub> Number of read miss not dirty

RM<sub>xD</sub> Number of read miss with x dirty bits

T'wh Average time for write hit via XCL

T'<sub>wm-nD</sub> Average time for write miss not dirty via XCL

$T'_{wm-xD}$  Average time for write miss with x dirty bits via XCL

T'<sub>rm-nD</sub> Average time for read miss not dirty via XCL

$T'_{rm-xD}$  Average time for read miss with x dirty bits via XCL

# **CHAPTER 1**

## Introduction

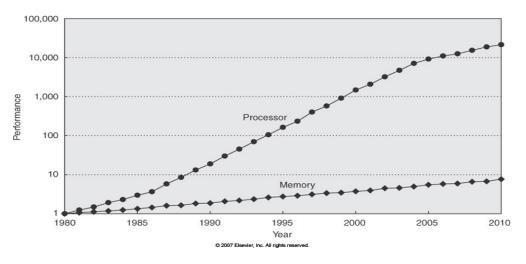

The gap between processor performance and the time taken to access main memory keeps growing continuously as shown in Figure 1.1 [20]. This increasing performance gap is a major drawback in the overall computer system performance [20, 21].

Figure 1.1 Processor-Memory gap [20]

In order to bridge the gap, cache memory was introduced between the processor and the memory. Cache is a small, fast, expensive memory made of SRAM, which reduces the average time to access memory. Since fast memory is expensive, the memory hierarchy is divided into multiple levels, such as registers, L1 cache, L2 cache, L3 cache and main memory. Each level in the hierarchy is smaller, faster, and more expensive per byte than the next lower level. The objective is to provide cost-effective and high performance memory system.

#### 1.1 Motivation

The size and configuration of L1 data cache in embedded processors have a great impact on software performance. However, data caches are unobservable by the embedded software designer. As such, it is difficult for the software designer to observe the cache state and performance, for specific instances of code execution. Such feedback is useful to optimize the software for improving cache hits [1]. Moreover, during design space exploration, it is desirable to modify the cache configuration of a given processor core in order to evaluate cache design choices. In order to accomplish the above objectives, we need a fast, observable, configurable and timing accurate model of the data cache.

## 1.2 Embedded System Validation

Validation broadly refers to the process of determining that a design is functionally correct.

The two most commonly used methods for early system level validation are software simulation and FPGA prototyping.

#### 1.2.1 Software simulation

Software simulation refers to an event driven logic simulator that operates by propagating input changes through the design to simulate the operation of the digital circuit [9]. Software simulators use languages such as Verilog, VHDL and SystemC to describe the design and verification environment. Cycle accurate software models of processor cores and the memory hierarchy provide excellent observability. The cycle accurate models can also be easily configured to reflect different design choices. However, it becomes extremely difficult to model the processor subsystem, bus and the memory hierarchy altogether. Such cycle accurate model requires large amounts of computing resources and time. Abstract software

simulation models, such as *Transaction-level Models* (TLMs), are very useful for early system modeling, but they compromise cycle accuracy for greater simulation speed.

## 1.2.2 FPGA Prototyping

FPGA based prototyping refers to the process of prototyping SoC and ASIC design on FPGA for hardware verification and early software development. FPGA prototypes are created by instantiating the processor cores and other system components on an FPGA chip. This technique enables pre-silicon embedded software development and allows hardware and software co-development. Moreover, once the design process is over, the FPGAs are ready for production, while ASICs take much longer time to reach production. As such, it helps improve time to market window and avoids expensive silicon re-spin. FPGA prototypes are typically, several orders of magnitude faster than cycle accurate software simulation models, while still providing cycle accuracy. In-circuit emulation techniques can be used to debug software and observe the addressable memory in FPGA prototypes. However, L1 caches cannot be easily probed and observed in FPGA prototypes since they are not bus-addressable.

## 1.3 Rationale for modeling direct mapped L1 data cache

The rationale for modeling direct mapped L1 data cache is

• We do not target the instruction cache (ICache) to be modeled, because the performance of instruction cache is generally good. Instruction access pattern is sequential and less random when compared to data access pattern. The effect of change in configuration of ICache has less impact on the performance of software.

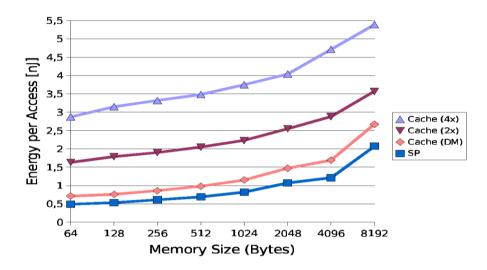

Figure 1.2 Influence of associativity of cache on energy [P. Marwedel et al., ASPDAC, 2004]

For example, increasing the block size of ICache will lead to increase in performance.

- Direct mapped cache is preferred to set associative cache because direct mapped cache is extremely quick to search and consumes less energy as shown by Figure 1.2

[33]. The set associative caches consume more energy which reduces the performance of embedded systems.

- Level 1 (L1) cache has the greatest impact on system performance. As such, embedded systems may have only L1 cache and ignore other hierarchy. Hence, the pCache focuses on modeling L1 cache.

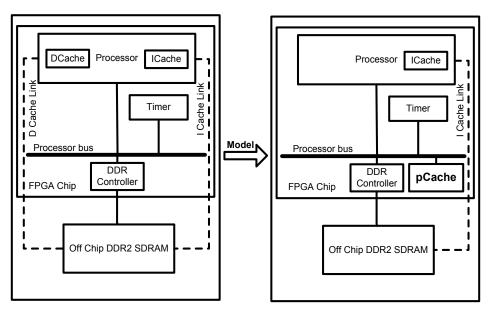

- (a) Processor system with built-in cache

- (b) Processor system with pCache

Figure 1.3 Modeling methodology

## 1.4 Methodology

Figure 1.3 illustrates our modeling methodology. The target design of the processor system with built-in L1 data cache (DCache) is shown in Figure 1.3 (a). The peripherals such as timer and DDR controller are connected to the processor bus. There is also dedicated cache link connecting the processor to the off chip memory. Upon cache miss, the block of data corresponding to the missed address is fetched from the off chip memory over the dedicated cache link. Software debuggers, typically, can display only the processor internal registers and the contents of memories mapped on the processor bus. As such it is not possible to display the cache state at run time using software debuggers. In order to provide an observable cache to the embedded software designers, we model this system as shown Figure 1.3 (b).

The pCache-based model consists of the processor system without a built-in data cache. In the case of hard processor cores, the data cache can simply be disabled in software, since most embedded processors provide instructions to turn off the data cache. The processor can access data from off chip memory only through the processor bus. The pCache module is a custom hardware component that interfaces to the processor using the processor bus. It monitors the processor address signals and Read/Write signals in the processor bus to track every data transaction targeted to the main memory, and to register a cache hit or miss. Memory mapped registers within pCache are used to store the cached memory addresses and are accessible using a software debugger. The run time of a software application in pCache system will be higher because of the absence of built-in data cache and the missing cache link. However, with the data from hit and miss counters we can derive the estimated run time of the software application in processor system with built-in cache. The pCache module is also configurable, enabling the designer to explore different cache architectures by changing its parameters.

The advantages of a pCache based model are

- (i) **Observability**: an observable data cache model and a debugger can be used by embedded software developers to easily identify code with poor cache behavior and explore opportunities for code optimization.

- (ii) **At-speed simulation**: since the cache model is built into the FPGA prototype, the embedded software is executed on the actual processor, implemented as a soft or hard core in FPGA. As such, there is no need to use a slow cycle accurate software simulation model of the processor to generate the memory trace.

(iii) **Easy reconfiguration**: The processor, if available as soft-core, can be treated as a black box. The cache model can be reconfigured without having to re-synthesize the processor in FPGA. If the processor core is implemented as a hard core on the FPGA/board, the built-in cache cannot be reconfigured. Therefore, for modeling purposes, the built-in cache can be turned off and the pCache model can be used.

#### 1.5 Related Work

There are different ways to model and simulate cache memory behavior. It can be broadly divided into Trace driven simulation, Analytical model (trace analysis) and high level functional simulation.

## 1.5.1 Analytical model

Analytical model uses parameters extracted from address trace of programs to quickly predict the performance of cache. As such these models require a mechanism to collect address trace and to store them. Such mathematical approach requires various assumptions about the statistical properties of address traces and data use patterns to formulate analytical equations.

Several analytical models [26, 27 and 28] have been proposed which are limited mainly to analyzing perfect loop nests, with straight line assignments and no call statements in the program. Xue et.al. [3] proposed an analytical model of data cache which is applicable to whole programs, including loop nests. The model is applicable only to programs with compile time predictable memory accesses, and so is less accurate for programs with data dependent constructs.

An analytical cache model is proposed in [2] that analyses parameters extracted from the address trace to predict average cache miss rate. The miss rate calculated from the model is compared to the simulation results. Although the computation cost is low, the miss rate predictions by the model are consistently lower than simulated miss rates for caches of size 8K through 32K. The mean relative error in miss rate for certain cache configuration is quite significant at 23% and the worst case error in prediction is 39%.

In 2003, Ghosh et al. [19] proposed an analytical model of the cache combined with an algorithm to compute cache parameters satisfying desired performance constraints. Their objective was to obtain a set of optimal cache pairs (Depth, Associativity) for a given number of desired cache misses. However, to limit the number of design points in design space exploration, they do not consider the cache line size as a varying parameter. Likewise, they have assumed fixed Least Recently Used (LRU) and write back cache policies. As such, they have cache size and associativity only as varying configuration parameters.

#### 1.5.2 Trace driven simulation

Trace driven simulation [25] has been the typical approach to evaluate cache performance. It requires the application software to be simulated once to generate memory reference trace (address trace). This address trace is then processed by a cache simulator for each cache configuration that needs to be evaluated. The advantage of trace simulation is that it is more accurate than the analytical model. However, processing only one configuration on each simulation pass during design space exploration can prove to be tedious and time consuming. Moreover, address traces that are very long requires large storage space requirement and longer simulation time.

One such simulator is Dinero IV [11], in which there is no notion of simulation time or cycles. It just gives information on hits and misses for an address trace. It also has the drawback of requiring repeated simulation runs resulting in lengthy design space exploration time. In 2012, Atanasovski et al [12] proposed a highly configurable trace driven cache simulator MMCacheSim. The simulator, implemented as a set of java classes predicts the performance of multiple levels of cache. In order to validate, they compare the average CPU cycles for memory access in the simulator and in real multiprocessors. The results show that the simulated values are not very accurate and there is no discussion on the actual error percentage. Moreover, the simulator is specific to matrix related applications and is not validated against standard benchmarks.

### 1.5.3 Single pass simulation

In order to overcome the disadvantage of repeated cache simulation in conventional trace driven simulation, the single pass simulation technique based on inclusion property [13] was first proposed by Mattson et al. An efficient Stack data structure was used to determine the performance of multiple cache architectures in one pass of the address trace. In 2010, Haque et al developed a single pass L1 cache simulator, SCUD [14]. It has a special data structure that is made up of Central look-up table, binomial tree and miss counter table to calculate the cache miss rate of an application trace. The central look-up table holds hit/miss information of memory addresses for all possible cache configurations. The SCUD uses several properties of its data structure like binary search and binomial tree to simplify the decision making process during simulation. Simulation times for various benchmarks are compared to the simulation time in conventional Dinero IV [11] cache simulator. It shows an average

speed up of 10 times over Dinero IV. However, for memory intensive workloads like Mpeg2, the SCUD simulation time is as high as 6.5 hours.

In order to further decrease the time complexity of simulation during design space exploration of caches, Janapsatya et al. [15] proposed a simulation algorithm based on Cache Inclusion properties. The basic idea of the approach in [15] is, given two caches with same associativity using LRU replacement policy, the following are applicable.

- Whenever a cache hit occurs, all caches that have larger set sizes will also guarantee

a cache hit.

- Whenever a cache miss occurs, all caches that have smaller set sizes will also guarantee a cache miss.

The time complexity of finding the best configuration among all the cache configurations by this approach is reduced by skipping simulation based on the above assumptions. The results of this method are consistent with the Dinero IV [11] simulator, and have an average speed up of 45 times over the later. In 2009, Tojo et al. [6] proposed CRCB1 and CRCB2 algorithm to improve Janapsatya's [15] simulation approach. Both the cache simulation algorithms are based on Cache inclusion property. It reduces the number of hit/miss judgements that are required for simulating all the cache configurations compared to conventional full trace simulation approaches. The cache configuration with minimum total memory access time is obtained by analyzing the stored address trace only once.

#### 1.5.4 Partial trace simulation

Many partial address trace simulation techniques to simulate the cache architectures are available. They do not simulate the entire length of address trace, leading to an increase in

simulation speed. Statistical trace sampling techniques to form smaller clusters of trace have been proposed. But it leads to the problem of cold start bias, in which there is no consistency in state of the cache from one cluster to other. The accuracy of such cache simulation techniques depends on the method used for repairing the state of the cache at the beginning of each sample.

To solve the above state repair problem, Conte et al. [4] proposed two techniques *fill flush* and *no state loss*. The first technique *fill flush* is based on Stone's approach [16] to the single pass technique. In *fill flush* approach, unique references with unknown cache state are removed from the address trace. The miss ratio for a cache configuration by this method is expressed as,

$$\rho = \frac{N - (R[B] - D[C, B, S])}{N - F[B]}$$

where [C,B,S] is the notation used to represent the dimension of a cache of size 2<sup>C</sup> bytes, with a block size of 2<sup>B</sup> bytes and 2<sup>S</sup> blocks in each set. N is the total number of references and R[B] is the total number of recurrences (hits) for block size B. D[C,B,S] is the total number of dimensional conflicts (misses) for that particular configuration. F[B] is the number of references whose cache state is unknown. The *fill flush* method is fast, because only small clusters of trace are simulated. However, since the cache is flushed at the beginning of each cluster and references with unknown cache state are removed from calculating the miss ratio, the method is not very accurate. In the *no state loss* method, statistical sampling is applied only to the conflict metric D and R[B] and N are recorded for the whole trace. The miss ratio for this method is calculated as,

$$\rho = \frac{N - R[B]}{N} - \frac{D'[C, B, S]}{N_s L_s}$$

where  $N_s$  is the number of sampled clusters each of length  $L_s$ . The advantage of this method is the state of all the references within the sample is known since state of the cache is maintained throughout simulation. On average only 6% of the address trace is sampled in this method. Since most of the trace is processed, this method is accurate but very slow.

To overcome the state repair problem arising from sampling the address trace, X.Li et al. [17] proposed cache simulation using compressed traces. This technique is based on SEQUITUR algorithm [18] for trace compression and cache inclusion properties. The SEQUITUR algorithm identifies the repeating memory reference sequences present in the trace. Cache simulation for each repeating sequence is performed only once, leading to significant reduction in simulation time. This lossless compression scheme produces accurate cache hit/miss results. But the downside of this technique is that, the compression ratio will be very less if there are very few repetitive patterns.

Space sampling and time sampling techniques on address trace are propose by Chen et al. [7]. Although they reduce space and time requirements in trace driven simulation, the estimation of Miss per Instruction (MPI) by space sampling is not consistently accurate. For instance, Eqnott benchmark reports an error of 37.75%. The time sampling is applicable to loop iterations only and requires additional pre-processing to detect loops.

#### 1.5.5 High level simulation

Transaction Level Modeling (TLM) [29] is the widely used approach for system modeling and simulation. This increased level of abstraction in system modeling can increase the

simulation speed by two or three orders of magnitude compared to conventional Instruction Set Simulator approach. In TLM, the source program is back annotated with execution delay information of the target processor. This annotated program is then compiled and executed on the host machine. The total execution time can be estimated by summing up the annotated timing numbers.

Early transaction level model [30] provides increased simulation speed, but do not model the behavior of cache during execution delay estimation. Such model compromises timing accuracy for greater speed. Fast Veri [31] a product of InterDesign Technologies, uses a high speed TLM model for hardware/software co-simulation. In order to maintain timing accuracy, the program is back annotated with delays from their cache model. However, their work is proprietary and not easily extendable for other transaction level models.

Pedram et al. [8] extended the transaction level model in [30], by integrating a cache model into a TLM. The address information obtained from synthesized target binary and the basic block timing information obtained from ISS is used in back annotated cache calls. The model dynamically updates its status and returns appropriate delay for each access. The disadvantage is the process of inserting cache calls is done manually. Experimental results for only a simple matrix multiplication program is provided. As such, the method has not been demonstrated on realistic benchmark applications.

Pieper et al. [7] performed high level cache simulation by back annotating the original trace with memory access delays. They used stack distance histogram which records the delay since last reference to an address and this data is used to simulate the behavior of cache. Since the delays for each memory address is too large for back annotation, they proposed

compression techniques to reduce the size required to store the data inside a histogram. However, the accuracy for large direct mapped cache is poor. The worst case miss prediction error for a 2KB direct mapped cache is 337%.

Lin et al. [32] proposed source level timing annotation for generating accurate TLM model. The source program is divided into basic blocks and annotated with timing information. Moreover, by analyzing the assembly code through a target processor model, they take into account features like pipeline, branch prediction and cache architectures. However, since the target assembly code is not executed, the exact address of data access is unknown. As such, they use average cycle number to model the delay of each data access. Hence, their data cache model does not precisely calculate the data cache access latency.

## 1.5.6 Novelty of pCache

The pCache based model is novel and provides significant improvement over existing models as explained below.

- Analytical models of cache extract parameters from the stored address trace for computation. Such models are fast, but the estimation is highly error prone. In contrast, the pCache model is fast, accurate and does not require storing address trace.

- Trace driven simulation is an accurate method to evaluate cache performance, but the simulation runs are very long. Since only one configuration can be processed in each simulation pass, it is prohibitively slow to be used in design space exploration. In contrast pCache is fast and can be easily used in cache design space exploration.

- Single pass simulation technique evaluates multiple cache configurations in single run. It is faster than conventional trace driven simulation but slower compared to pCache model.

- Partial trace simulation applies sampling technique to reduce the length of address trace to be simulated. But it leads to cache cold start problem that make such simulations inaccurate. In contrast, pCache can be used which is fast and accurate.

- Transaction level model of cache is fast compared to other simulation techniques, but is not cycle accurate. Alternatively, pCache is fast and cycle accurate.

## 1.6 Thesis Contribution

In this thesis, we present an observable cache model called pCache that can be used in FPGA prototyping. A pCache based model combines the observability of software simulation with the speed and cycle accuracy of FPGA prototyping. The contributions of this work are,

- We designed and implemented a cycle accurate, observable and fast functional model of L1 data cache on the FPGA, which is a new technique not currently possible with bus analyzers. The module can be integrated into a prototype of a processor system on an FPGA.

- The model is several orders of magnitude faster than conventional software simulation. Examples show FPGA based model can simulate designs in milliseconds as opposed to several hours in software simulation.

- A highly configurable pCache model which allows us to create models of direct mapped, L1 caches of any size, of any block size, with write through and write back techniques.

- We developed a parameterized timing model of the cache for accurate performance estimation of embedded software, with different cache configuration.

- A methodology for cache design space exploration using the timing model.

- Demonstration of software optimizations such as loop splitting and fusion using the observable cache model.

## 1.7 Thesis Organization

The rest of this thesis is organized as follows. In Chapter 2, we outline the design of the peripheral cache, called pCache, and its features. In chapter 3, the built-in cache based reference design and pCache based model is introduced. A complete functional validation of both the write policies, write through and write back, is also presented. A detailed timing analysis of the pCache based model is presented in Chapter 4. The parameterized cache timing model and equations to estimate overhead in pCache model are also presented. Timing validation against standard benchmarks is shown in section 4.5.

# CHAPTER 2

## **Peripheral Cache**

In this chapter, the architecture of the peripheral cache (pCache), its various features and interface are described in detail.

## 2.1 pCache - Interface

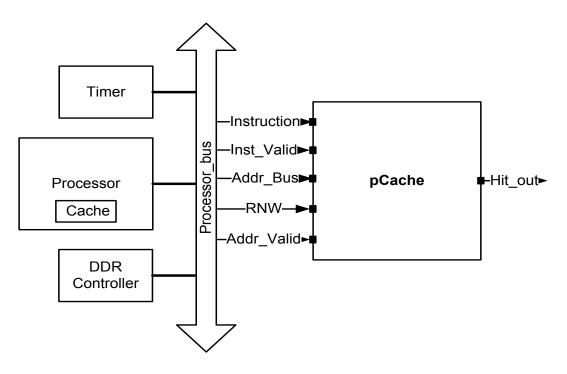

Figure 2.1 Block diagram of pCache - processor bus interface.

Figure 2.1 shows the interface between pCache and the processor bus. The pCache module is connected as a slave peripheral to the processor bus. The input signals to the pCache are Instruction bus, Instruction valid, Address bus, Read/Write and Address valid. The result of the data access (hit/miss) is shown by the Hit out output signal from pCache.

## 2.2 pCache Architecture

Figure 2.2 Block diagram of pCache.

Figure 2.2 shows the block diagram of direct mapped pCache. pCache consists of the following sub modules: Slave registers, Control Unit, Tag Memory, Control Status Register (CSR) and Hit and Miss Counters. CSR is a 32 bit control register for pCache that allows the processor to Reset, Enable and Disable pCache. Tag Memory is a 2D array of registers that store the tags of memory locations being accessed. The pCache model does not store the actual data being cached but stores only the address of the memory locations being accessed. Hence, we are not interested in tracking any of the data signals in the processor bus. In order to display the contents of the cache, we write the address of the first location of the block of

memory on to slave registers labeled Block 1 to Block N in Figure 3. Cache timing parameters are kept in specific slave registers: H Cntrs (hit counters), M Cntr (miss counter), M\_D Cntrs (miss-dirty counters), M\_nD Cntrs (miss-not-dirty counters) and Wr Cntrs (write counters). We will elaborate on the timing parameters in Section 4.2.

## 2.3 Write Policies

The write policies on write hit distinguish cache designs into Write Through and Write Back caches.

#### 2.3.1 Write through policy

Figure 2.3 Flow chart describing write through policy.

The operation of write through policy is explained by the flow chart shown in Figure 2.3. When a write hit occurs, the data is updated both in the cache and main memory. On a write miss, the data is written directly into the main memory. On a read miss, the existing block in

cache is replaced by a new block from the main memory. The advantage of this method is that the main memory always has the most recent value of the data. But this makes write slower, since every write requires a main memory access.

### 2.3.2 Write back policy

Figure 2.4 Flow chart describing write back policy.

Figure 2.4 describes the procedure for write back policy. On a write hit, the data is modified in the cache and the dirty bit is set high. On a write miss, the selected cache block's dirty bit is checked. If dirty, the modified block of data is updated in the memory and is replaced with

a new block. Similarly on a read hit, the data is read from the cache and on a read miss, the data is updated in the memory if dirty bit is high. Else it is replaced by a new block from the main memory and marked not dirty.

## 2.4 Control Unit

The pCache Control Unit models the write through and write back behaviors described in section 2.3. The Control Unit is responsible for tracking address and Read/Write signals in the processor bus and updating the pCache state. The operation of Control Unit is described using finite state machines shown in Figure 2.5 and 2.6. We define four states that the system may be in while running: *Check R/W*, *Read*, *Write*, and *Tag\_mem update*. Control signals are assigned specific values in each of the states.

Figure 2.5 Control Unit FSM – Write through policy.

Figure 2.5 shows the FSM that implements write through policy. Upon receiving a new valid address, the controller checks the RNW signal. If RNW is '1' the controller goes to *Read* state where the tag memory is checked to know if the requested data is cached. The

controller waits until it receives hit/miss signal from the tag memory. Upon receiving miss, the miss counter is incremented, and the controller moves to *Tag\_mem update* state. The tag memory is updated and the system returns to *Check R/W* state. Upon receiving hit, the hit counter is incremented and the system returns to *Check R/W* state. If RNW is logic '0' the controller goes to *Write* state. In this state, it waits for the arrival of hit/miss signal from the Tag memory. Upon receiving hit/miss result, the respective counters are incremented and the controller returns to *Check R/W* state irrespective of hit or miss.

Figure 2.6 Control Unit FSM – Write back policy.

Figure 2.6 shows the FSM that implements write back policy. Upon receiving a new valid address, the controller checks the RNW signal. If RNW is '1' the controller goes to *Read* state where the tag memory is checked to know if the requested data is cached. Upon hit, the hit counter is incremented and the controller returns to *Check R/W* state. Upon miss, the miss counter is incremented and the controller moves to *Tag\_mem update* state where the tag memory is updated. If RNW is logic '0', the system moves to *Write* state. The tag memory is

checked and the controller waits for the hit/miss result. Upon hit, the hit counter is incremented and the system returns to *Check R/W* state. Upon miss, the miss counter is incremented and the controller moves to *Tag\_mem update* state. The tag memory is updated and the system returns to *Check R/W* state.

## 2.5 pCache – Features

The pCache module has user configurable parameters that can be used to describe the behavior of pCache model. It can be configured before synthesis using the parameters shown in Table 1. The parameters and its corresponding features are described below. The design of pCache makes it generic enough to be used with most buses. The configurability makes it flexible enough to model most direct mapped cache architectures used in embedded systems.

Table 1 The configuration parameters of pCache

| Parameter                                 | Description                         | Possible values | Default<br>value |  |

|-------------------------------------------|-------------------------------------|-----------------|------------------|--|

|                                           | Write policy                        |                 | 1                |  |

| write_select                              | 1 = Write through<br>0 = Write back | 0, 1            |                  |  |

| cache_line_size                           | Cache line length                   | 4, 8            | 4                |  |

| index_bits                                | Number of rows in cache             | 1 - 7           | 4                |  |

| mem_addr_size                             | mem_addr_size Size of DDR2 memory   |                 | 14               |  |

| mem_base_addr Base address of DDR2 memory |                                     | 0xXXXXXXXX      | User<br>defined  |  |

## 2.5.1 Write policy

The parameter *write\_select* is used to select the write policy in pCache. When set to '1', write through policy is selected and when set to '0', write back policy is selected.

### 2.5.2 Line size

Each cache block in pCache can hold 4 or 8 words of data. The size of the block in pCache module can be configured by the parameter *cache line size*.

#### 2.5.3 Cache size

The size of the pCache (number of rows) can be modified using *index\_bits* parameter. The pCache can hold 2<sup>index\_bits</sup> rows. To demonstrate the operation of pCache, we have chosen the possible values to this parameter to be in the range of 1 to 7. This translates to cache size of 64 Bytes to 2K Bytes. However, the pCache can also have size more than 2KB.

### 2.5.4 Cacheable address range

The parameters *mem\_addr\_size* and *mem\_base\_addr* are used to determine the cacheable address range of the main memory. The parameter *mem\_base\_addr* represents the base address assigned to the off-chip DDR2 memory.

# **CHAPTER 3**

# **Functional Validation**

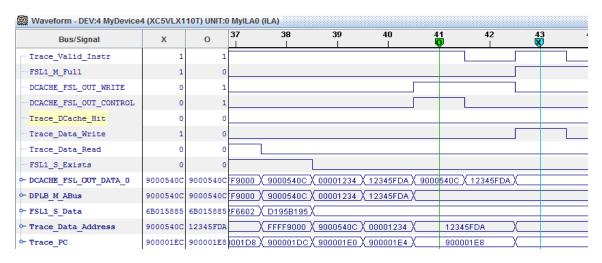

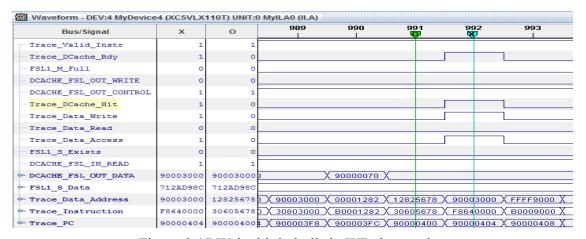

In this chapter, we validate the functional correctness of the pCache model manually by comparing its cycle accurate simulation to that of the reference design with built-in cache. Chipscope Pro Analyzer with an ILA (Integrated Logic Analyzer) core was used to validate and debug the pCache model.

# 3.1 Built-in cache based reference system

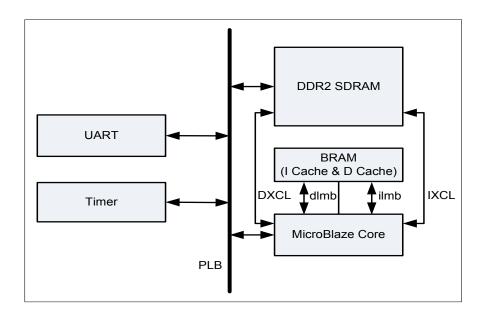

Figure 3.1 Block diagram of MicroBlaze core with built-in data cache

Figure 3.1 is the design of MicroBlaze based system with built-in data cache and instruction cache, similar to the one shown in Figure 1.3 (a). On-chip Block RAM connected to the MicroBlaze processor by data local memory bus (dlmb) and instruction local memory bus (ilmb) is utilised to implement the cache. When a new data is requested, the built-in cache

controller performs a lookup on the tags to check if the requested data is currently cached. On a cache miss, the built-in controller requests the new data block over data CacheLink (DXCL). The Universal Asynchronous Receiver Transmitter (UART) connects to the PLB and provides the interface for asynchronous serial data transfer between the system on FPGA and the HyperTerminal. The timer connected to PLB is used to measure the runtime of the embedded software executed by the processor.

## 3.2 pCache based model

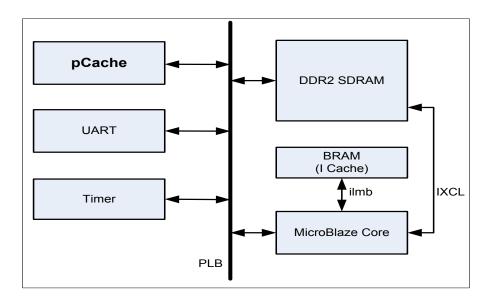

Figure 3.2 Block diagram of MicroBlaze core with pCache module.

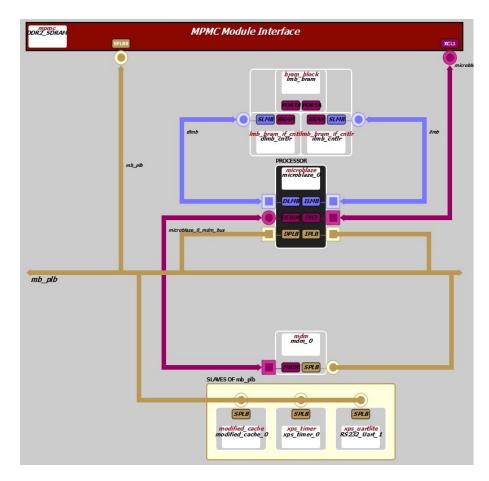

Figure 3.2 is the model with pCache attached to the PLB as a peripheral, similar to the one shown in Figure 1.3 (b). Since the data cache is disabled, there is no DXCL bus in this model. The MicroBlaze processor accesses data from the main (DDR) memory via PLB. Instructions are fetched by the processor from the main memory via IXCL bus. Figure 3.3 shows the actual block diagram of datapath with MicroBlaze processor and the slave peripherals including pCache, timer and the UART.

Figure 3.3 Block diagram of datapath with pCache module

The pCache design was implemented on a Xilinx Virtex 5 XC5VLX110T FPGA. The Xilinx Embedded Development Kit (EDK) supports debugging of a program on MicroBlaze processor running on an FPGA. The JTAG interface on board is used to communicate with the design and to capture internal bus signals via Chipscope bus analyzer. The trigger setup in Chipscope was configured to capture specific data in the design. The captured data in Chipscope is used to validate the pCache model against the reference design. The time for completion of a transaction shown in the following section, is specific to the particular case under consideration. The average delays for different types of transactions are discussed in Chapter 4.

# 3.3 Validation of Write through mode

#### 3.3.1 Read transactions

Listing 1. Sample code to test read miss in WT cache

```

//Read miss

XIo In32(0x90001A20);

imm

-28672

r3, r0, 6688

addik

r3, r3, 0

lwi

XIo In32(0x900019AC);

//Read miss

-28672

imm

addik

r3, r0, 6572

lwi

r3, r3, 0

```

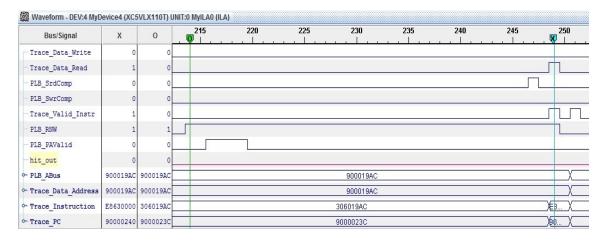

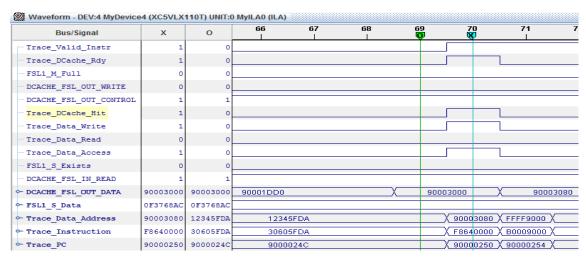

Figure 3.4 Read miss in 4 word WT built-in data cache

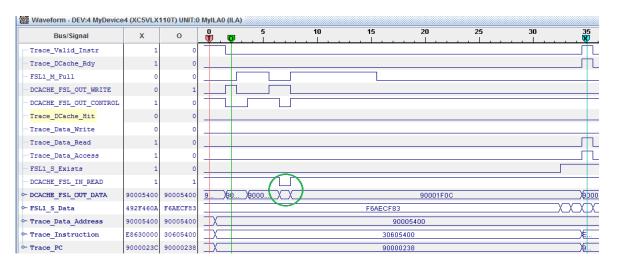

Figure 3.5 Read miss in pCache

Listing 1 shows the code to test read miss transaction in write through data cache. The XIo\_In32 and XIo\_Out32 macros read and write 32 bit data, respectively, into the memory. The assembly instructions that make up the macro are also shown in the listing 1. A 4 word data cache of size 256B is used for the test case. The first read operation to memory location 0x90001A20 results in a miss. The second read operation to memory location 0x900019AC, which is mapped to the same cache block as the previous address, also results in a miss. Figure 3.4 and Figure 3.5 shows the screenshot of read miss on data address 0x900019AC, in built-in data cache and pCache model respectively. The circled portion in Figure 3.4 shows 4 words of data being fetched over DXCL bus on a read miss. Pointers O and X point to the start and finish time of the data fetch. The missed data is read from off-chip memory in 32 clock cycles. Read miss in pCache is shown in Figure 3.5 by the highlighted signal hit\_out. The hit signal remains low and takes 35 cycles to read data from main memory via PLB.

Listing 2. Sample code to test read hit in WT cache

| XIo_In32(0x90       | //Read miss                          |            |

|---------------------|--------------------------------------|------------|

| imm<br>addik<br>lwi | -28672<br>r3, r0, 21504<br>r3, r3, 0 |            |

| XIo_In32(0x90       | 005408);                             | //Read hit |

| imm                 | -28672                               |            |

| addik<br>lwi        | r3, r0, 21512<br>r3, r3, 0           |            |

Listing 2 shows the code to test read hit transaction in 4 word write through cache. The first read operation to memory location 0x90005400 results in a miss. The new block of data consisting 4 words is fetched into the data cache. The second read operation to memory location 0x90005408 results in a hit in data cache.

Figure 3.6 Read hit in built-in WT data cache

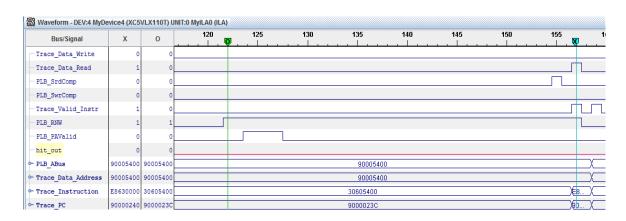

Figure 3.7 Read hit in pCache

Figure 3.6 and Figure 3.7 shows the screenshot of read hit on data address 0x90005408, in built-in data cache and the pCache model respectively. We can see the *Trace\_Dcache\_Hit* signal in built-in data cache and *hit\_out* signal in pCache model go high for this memory transaction. We note, read hit takes 2 cycle delay in built-in data cache and in pCache model, it takes 35 cycles to complete the read from main memory via PLB.

#### 3.3.2 Write transactions

Listing 3. Sample code to test consecutive writes in WT cache

| asm("swi | r5, r19, 48"); | //Write to 0x900019E8 |

|----------|----------------|-----------------------|

| asm("swi | r6, r19, 52"); | //Write to 0x900019EC |

| asm("swi | r7, r19, 56"); | //Write to 0x900019F0 |

| asm("swi | r8, r19, 60"); | //Write to 0x900019F4 |

Listing 4. Sample code to test non consecutive write in WT cache

| XIo_Out32(0x90 | 00540C, | 0x12345FDA); | //Write to 0x9000540C |

|----------------|---------|--------------|-----------------------|

| imm            | -28672  |              |                       |

| addik          | r4, r0, | 21516        |                       |

| imm            | 4660    |              |                       |

| addik          | r3, r0, | 24538        | // 0x12345FDA         |

| swi            | r3, r4, | 0            |                       |

Listing 3 shows the assembly code to test consecutive write operation in write through data cache. Since *XIo\_Out32* macro consists of both arithmetic instructions and store instruction, we cannot use it to have consecutive write to main memory. Hence, we use the store instruction *swi* to generate four consecutive write to memory addresses 0x90019E8, 0x900019EC, 0x900019F0 and 0x900019F4.

Figure 3.8 Consecutive writes in built-in WT data cache

Figure 3.9 Non consecutive write in built-in WT data cache

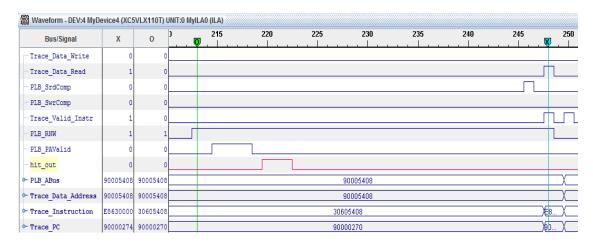

Listing 4 shows the code to test non consecutive write in write through cache. The data 0x12345FDA is written to memory location 0x9000540C. The *swi* instruction in the macro follows an arithmetic instruction *addik*. Figure 3.8 and Figure 3.9 show the screenshot of consecutive and non–consecutive writes in built-in data cache respectively. Since write to the write through cache always result in write to the main memory, the bus protocol used in write through policy does not set hit signal to high even if it results in a hit. In the Figure 3.8, we can see a sequence of writes to main memory via DXCL bus. The pointers in Figure 3.8 show the write operation to memory address 0x900019F4, that has a delay of 14 clock cycles. The non consecutive write to memory address 0x9000540C shown in Figure 3.9 has 3 cycles delay. The reason for the difference in delay between consecutive and non consecutive write is discussed under the heading characterization of write through cache in section 4.3.

Listing 5 shows the code to test non consecutive and consecutive write in write through pCache. The first write operation to memory address 0x9000540C is a non consecutive write which follows an *addik* instruction. The second write instruction to

Listing 5. Sample code to test write in WT pCache

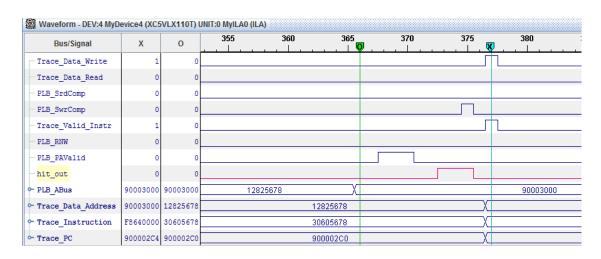

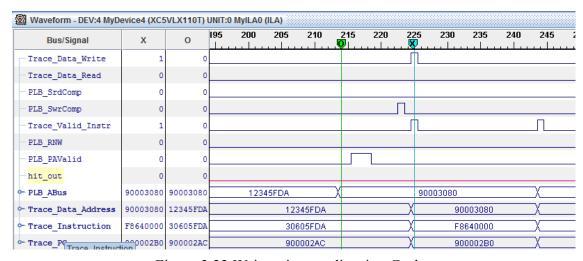

Figure 3.10 Non consecutive and consecutive write in pCache

memory address 0x900022AC is a consecutive write to main memory. Figure 3.10 shows the screenshot of non-consecutive and consecutive write in the pCache model. The pointers show a write transaction to memory address 0x9000540C. We can see, both the types take 11 cycles only to complete the write into main memory via PLB.

### 3.4 Validation of Write back mode

#### 3.4.1 Read transactions

Listing 6. Sample code to test read hit in WB cache

| XIo_In32(0x90006800); | //Read miss |

|-----------------------|-------------|

| XIo_In32(0x90006804); | //Read hit  |

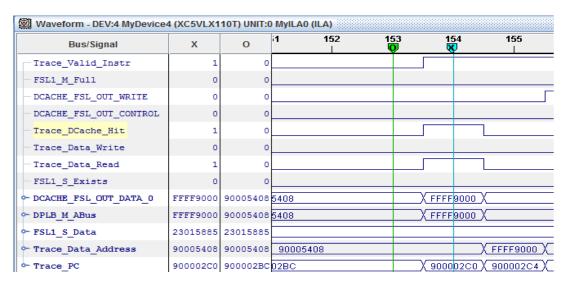

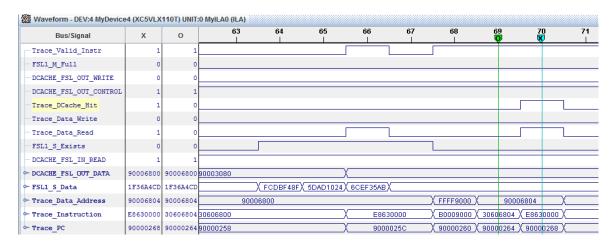

Figure 3.11 Read hit in built-in WB data cache

Figure 3.12 Read hit in pCache

Listing 6 shows the code to test read hit in 4 word write back cache. The first read operation to memory address 0x90006800 results in a miss. The corresponding block of data from main memory is fetched into the data cache. The second read operation to memory address 0x90006804 results in a hit in data cache. Figure 3.11 and Figure 3.12 shows the screenshot of read operation to memory address 0x9000540C, in built-in write back data cache and pCache respectively. The transaction results in a cache hit in both the models. The pointers X and O show the start and end of the read transaction. We note from the screenshot, the read hit in built-in data cache via DXCL bus takes 2 cycles only to be executed and 35 cycles via PLB in pCache model.

Listing 7. Sample code to test read miss (1D) in WB cache

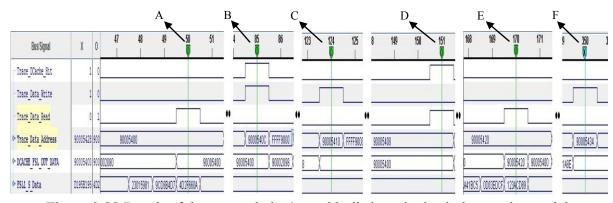

Figure 3.13 Read miss (1 dirty) in built-in WB data cache

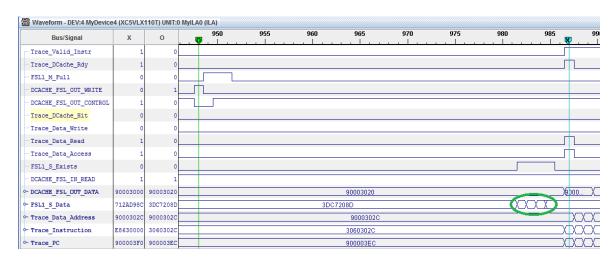

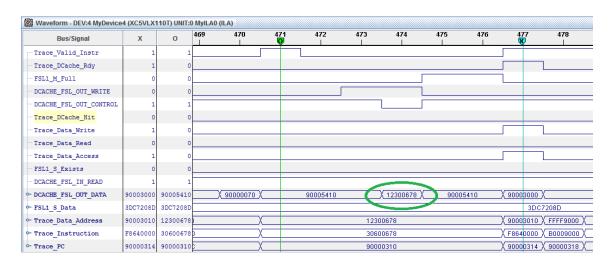

Figure 3.14 Read miss (1 dirty) in pCache

Listing 7 shows the code to test read miss with 1 dirty bit in 4 word write back data cache. The first read operation to memory address 0x9000230C results in a cache miss and a block of data is fetched into the data cache. The second write operation modifies the data in the cache block. The next read operation to memory address 0x90005400 results in a miss

with 1 dirty word. Figure 3.13 and Figure 3.14 shows the screenshot of read transaction in built-in write back data cache and pCache model respectively. The read to memory address 0x90005400 results in a miss with 1 dirty bit in both the models. Note the signal *hit\_out* in Figure 3.14, which is low in the region between the pointers X and O. The circled portion in Figure 3.13 shows the modified data in the cache block being written back to main memory before it is replaced with a new block. We see the time for read miss with 1 dirty bit to be 33 cycles in built-in data cache and 35 cycles in pCache model.

Listing 8. Sample code to test read miss notD in WB cache

| XIo_In32(0x90003120); | //Read miss           |

|-----------------------|-----------------------|

| XIo_In32(0x9000302C); | //Read miss not Dirty |

Figure 3.15 Read miss not dirty in built-in WB data cache

Listing 8 shows the code to test read miss no dirty in 4 word write back data cache. The first read operation to memory address 0x90003120 results in a read miss in data cache. The next read operation to memory address 0x9000302C which maps to the same cache block, results in a read miss with no dirty bit. Figure 3.15 and Figure 3.16 shows the screenshot of read transaction in built-in write back data cache and pCache models

Figure 3.16 Read miss not dirty in pCache

respectively. The read to memory address 0x9000302C results in a miss with no dirty bits in both the models. Since the block of data that is replaced in the cache is not dirty, we do not find any data being written back to main memory in Figure 3.15. The new block of data that is being fetched from the main memory to data cache is shown by the circled region in Figure 3.15. We see the time for read miss with no dirty bits to be 39 cycles in built-in data cache and 35 cycles in pCache model.

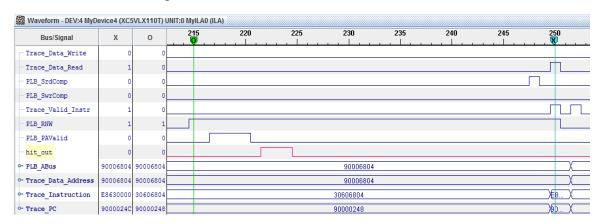

#### 3.4.2 Write transactions

Listing 9. Sample code to test write hit in WB cache

Listing 9 shows the code to test write hit in 4 word write back data cache. The first read operation to memory address 0x90003004 results in a miss in data cache. The corresponding block of data is fetched from main memory to data cache. The write operation to memory address 0x90003000 results in a hit in data cache. Figure 3.17 and Figure 3.18 shows the screenshot of write transaction in built-in write back data cache and pCache models

Figure 3.17 Write hit in built-in WB data cache

Figure 3.18 Write hit in pCache

respectively. The write to address 0x90003000 in main memory results in a hit in both the models. The hit signals, *Trace\_Dcache\_hit* and *hit\_out* are set high in the region between the pointer X and O. We see the time for write hit to be 2 cycles in built-in cache and 11 cycles in pCache model.

Listing 10. Sample code to test write miss (1D) in WB cache

XIo\_Out32(0x90005410, 0x12300678); //Write hit

XIo\_Out32(0x90003010, 0x12300678); //Write miss 1D

Figure 3.19 Write miss 1 dirty in built-in WB data cache

Figure 3.20 Write miss 1 dirty in pCache

Listing 10 shows the code to test write miss with 1 dirty bit in 4 word write back data cache. The first write operation to memory address 0x90005410 results in a cache hit and the data is modified in the cache. The second write operation to memory address 0x90003010 which maps to the same cache block, results in a miss with 1 dirty bit. Figure 3.19 and Figure 3.20 shows the snapshot of write transaction in built-in write back data cache and pCache models respectively. The write to address 0x90003010 in main memory results in a miss in cache with 1 dirty bit. The circled portion in Figure 3.19 shows the modified data in

cache being written back to main memory before it is replaced by a new block. The *hit\_out* signal in the pCache model shown in Figure 3.20 is low in the region between the pointers X and O. We see the time for write miss with 1 dirty bit to be 7 cycles in built-in cache and 11 cycles in pCache model.

Listing 11. Sample code to test write miss notD in WB cache

XIo\_Out32(0x90003180, 0x12300678); //Write miss

XIo\_Out32(0x90003080, 0x12345FDA); //Write miss notD

Figure 3.21 Write miss not dirty in built-in WB data cache

Figure 3.22 Write miss not dirty in pCache

Listing 11 shows the code to test write miss with no dirty bits in write back data cache. The first write operation to memory address 0x90003180 results in a miss in data cache. The write operation to memory address 0x90003080 which maps to the same cache block, results in a miss with no dirty bits. Figure 3.21 and Figure 3.22 shows the screenshot of write transaction in write back data cache and pCache models respectively. The write to address 0x90003080 in main memory results in a miss with no dirty bits in both the cache models. Upon write miss with no dirty bits, the bus protocol used in write back policy sets the hit signal *Trace\_Dcache\_hit* to high in the built-in data cache model. This can be seen in Figure 3.21shown by the pointer X. But in the case of pCache model, the *hit\_out* signal is at logic 0 during similar scenario. We see the time for write miss with no dirty bits to be 2 cycles in built-in data cache and 11 cycles in pCache model.

## 3.5 Validation using Software debugger

The Xilinx Microprocessor Debugger (XMD) provided by EDK is used to debug programs running on the FPGA. We used the sample code shown in Listing 12 to validate the correctness of pCache model. Software breakpoints were set and the contents of memory mapped registers were tracked using the software debugger.

Listing 12. Sample code used in functional validation

| XIo_In32(0x90005400);              | //Read miss  | (A) |

|------------------------------------|--------------|-----|

| XIo_Out32(0x9000540C, 0x12345FDA); | //Write hit  | (B) |

| XIo_Out32(0x90005410, 0x12300678); | //Write miss | (C) |

| XIo_In32(0x90005408);              | //Read hit   | (D) |

| XIo_In32(0x90005420);              | //Read miss  | (E) |

| XIo_Out32(0x90005434, 0x12300678); | //Write miss | (F) |

The first memory transaction A, reads address 0x90005400 which is not cached. This results in a cache read miss. Transaction B writes data 0x12345FDA into the address 0x9000540C. Since the cache block holds 4 words, (0x90005400, 0x90005404, 0x90005408 and 0x9000540C) transaction B results in a write hit. Transaction C writes data into memory location 0x90005410 which is not present in cache and results in a write miss. Transaction D results in a read hit on address 0x90005408, which is present in the cache. Transaction E and F reads memory address 0x90005420 and writes data into address 0x90005434 respectively, which are not cached resulting in read miss and write miss.

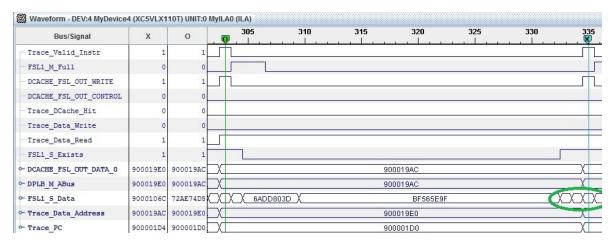

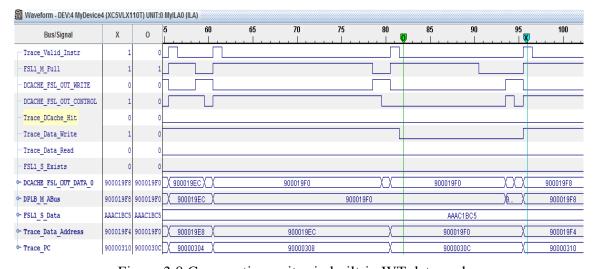

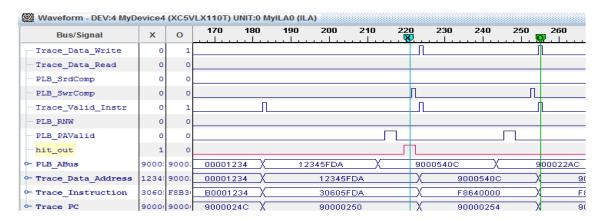

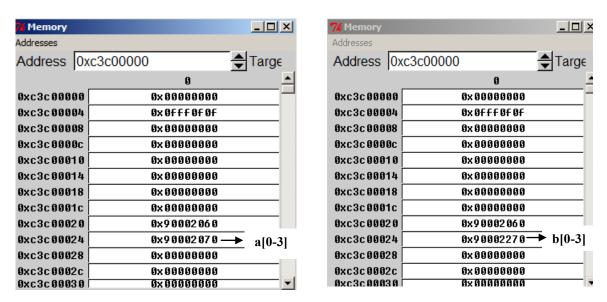

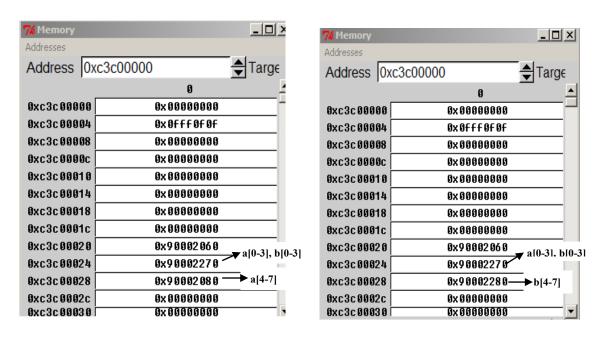

Figure 3.23 Result of the test code in 4 word built-in write back data cache model

Figure 3.24 Result of the test code in 4 word write back pCache based model.

The cache hit signal *Trace\_Dcache\_Hit* in the reference built-in cache design was compared to the *Hit\_out* signal of the pCache model. The screenshot of internal signals resulting from the execution of the test program in listing 1 is shown in Figure 3.23.

- Pointer A shows read miss at address 0x90005400

- Pointer B shows write hit at address 0x9000540C

- Pointer C shows write miss at address 0x90005410

- Pointer D shows read hit at address 0x90005408

- Pointer E shows read miss at address 0x90005420

- Pointer F shows write miss at address 0x90005434

Figure 3.24 shows the screenshot of signals viewed through Chipscope while simulating the pCache model. We note that the pointers A to F follow the same sequence as in the built-in cache. The hits in pCache are generated for the same memory addresses as in built-in cache design. This demonstrates the functional correctness of the pCache-based model.

| 76 Memory       |                      | _IOIX  |

|-----------------|----------------------|--------|

| Addresses       |                      |        |

| Address 0xc3c00 | 0000 Target          | is BIG |

|                 | 6                    | ASCII  |

| 0xc3c00000      | 0×00000000           |        |

| 0xc3c00004      | 0×0fff0f0f           |        |

| 0xc3c00008      | 0×90005400 ← A, B, D | T.     |

| 0xc3c0000c      | 0x90005410 ← C       | T.     |

| 0xc3c00010      | 0x90005420 ← E       | T      |

| 0xc3c00014      | 0x90005430 ← F       | TO     |

Figure 3.25 Contents of the pCache.

Figure 3.25 shows the contents of the data cache using XMD, after executing the test program in pCache model. Addresses of the first location of the block of memory being

accessed are written to the slave register dedicated to the corresponding cache block. The block address for the data being accessed in instructions A, B and D is 0x90005400. The block addresses for the data being accessed in instructions C, E and F are 0x90005410, 0x90005420 and 0x90005430 respectively. Theoretically, the bus analyzer can be used to determine the state of the cache. However, since the bus analyzer has small memory, which allows tracing for only upto 1024 cycles, the cache state must be computed manually for long runs of software execution. Moreover, the software developer needs to be familiar with hardware design and signal tracing, which is clearly impractical. Using pCache-based model, the entire content of the data cache is easily observable at run-time using a software debugger. The software developer does not need to be familiar with any hardware details.

# **CHAPTER 4**

# **Timing Analysis**

In this chapter, we present cache timing analysis using the example of a MicroBlaze based system [9].

The pCache based model has a longer software execution time due to two reasons.

- Accessing data from the off-chip main memory via PLB takes longer than access via CacheLink.

- The absence of an on-chip data cache.

We will define the number of additional cycles taken by the pCache-based model, compared to the built-in cache design, as the *overhead*. We also define  $T_{pcache}$  as the number of cycles taken for software execution in the pCache-based model.  $T_{pcache}$  can be easily measured using a timer peripheral. The timer is reset and started before a given block of code, and stopped after. The *overhead* cycles due to cache hit and miss are calculated, and subtracted from  $T_{pcache}$  to determine the estimated run time  $T_{est}$ .

$$T_{est} = T_{pcache} - \left\{ H * \left( T_{plb} - T_{xcl-hit} \right) + M * \left( T_{plb} - T_{xcl-miss} \right) \right\}$$

Equation 1

In Equation 1,  $T_{plb}$  is the average time to access a single word from main memory.  $T_{xcl-hit}$  is the average time to access data in the built-in data cache and  $T_{xcl-miss}$  is the average time to access data not in cache, over the XCL bus. The overhead due to a single cache hit in pCache is  $T_{plb} - T_{xcl-hit}$ . This factor is multiplied with the number of hits H in pCache to determine the total overhead due to cache hits. Similarly, the overhead due to each cache miss in pCache  $T_{plb} - T_{xcl-miss}$  is multiplied with the number of misses M to determine the overhead due to cache misses.

### 4.1 Bus Characteristics

In order to model the estimated software execution time ( $T_{est}$ ) in pCache based model, we need to understand the behavior of PLB and XCL buses. The following sub sections provide details about bus protocol and main memory access delay for both the buses. Chipscope Pro bus analyzer [10] is used to observe the bus activity and to measure the main memory access time.

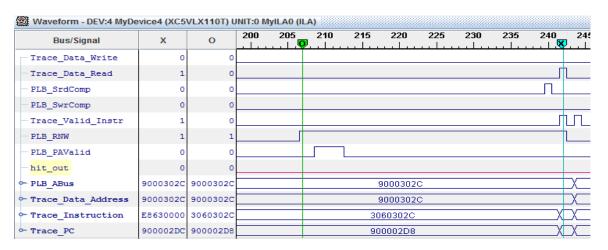

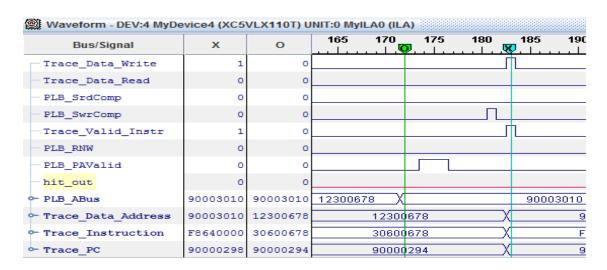

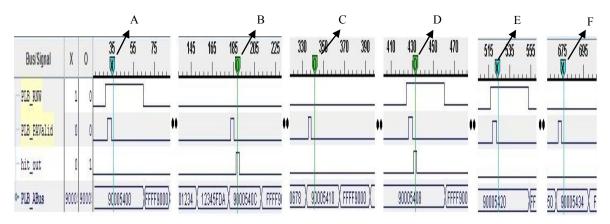

#### 4.1.1 PLB Behavior

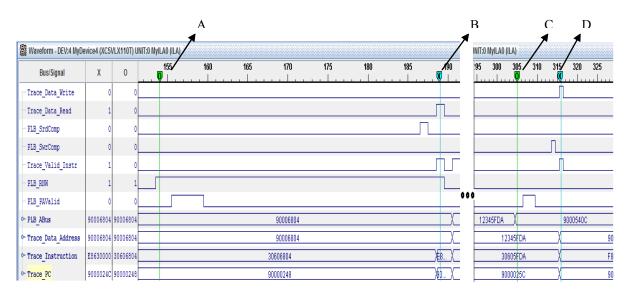

Figure 4.1 Read and write operations to off-chip DDR memory via PLB

Figure 4.1 shows snapshot of PLB transactions. It shows a valid read and write transaction to DDR main memory. To measure the number of cycles for an operation, we count from the start of *PLB\_PAValid* the valid address signal (shown by pointers A and C) till where the instruction gets executed (shown by pointers B and D). The delay in main memory can vary due to factors such as bus turnaround time, column address latency and refresh rate. Therefore, the measured time for read/write operation is not always constant. We model the PLB access delay by averaging the read and write times for several transactions which gives us 35 cycles for a read and 11 cycles for a write transaction.

#### 4.1.2 XCL Behavior

The XCL bus is a point to point FSL connection between the MicroBlaze processor and the DDR main memory. During data miss, the processor uses this connection to fetch data from the off-chip main memory. In data cache with write through policy, the cache link uses DXCL protocol [9] to communicate with the main memory. Upon read miss, the DXCL protocol follows critical word first method to read data from the main memory. By this method, the requested word is first read followed by the remaining 3 or 7 words. Upon read hit, the hit signal is asserted, however during write hit the hit signal is not set to high. The writes to data cache in write through mode will always result in a write over cache link regardless of whether there was a hit or miss as explained in section 2.3.

In the case of write back policy, the cache link uses DXCL2 protocol [9]. Upon read miss, the DXCL2 protocol follows linear fetch method to read the new block from main memory. In linear fetch, the data words are read in the order in which they are stored in the main memory. Write is performed only to the cache and the dirty bit is set high. Upon write miss the modified cache block is written back to the main memory before getting replaced.

# 4.2 Parameterized cache timing model

The parameters needed to calculate the overhead in write through cache timing model are as follows. The first four parameters are variables obtained from respective counters in the pCache module. The last six parameters are constants measured using the bus analyzer, used in overhead calculation. We will discuss the last six parameters in detail in section 4.5.

• RH : Number of read hits

• RM : Number of read miss

• NC<sub>wr</sub> : Number of non-consecutive writes

• C<sub>wr</sub> : Number of consecutive writes

• N<sub>rf cyc</sub> : Number of refresh cycles

•  $T_{rd}$  : Average time for read via PLB

•  $T_{wr}$ : Average time for write via PLB

• T'<sub>rh</sub> : Average time for read hit via XCL

• T'<sub>rm</sub> : Average time for read miss via XCL

• T'nc-wr : Average time for non consecutive writes via XCL

• T'<sub>c-wr</sub> : Average time for consecutive writes via XCL

Additional parameters are needed to calculate the overhead in a write back cache timing model as follows. The first five parameters are variables obtained from respective counters and the next five parameters are assigned constant values, based on measurements using the bus analyzer. The time for write/read miss in a write back cache depends on the number of dirty bits that are set, which we denote by x.

• WH : Number of write hits

•  $WM_{nD}$  : Number of write miss not dirty

•  $WM_{xD}$  : Number of write miss with x dirty bits

• RM<sub>nD</sub> : Number of read miss not dirty

•  $RM_{xD}$  : Number of read miss with x dirty bits

• T'wh : Average time for write hit via XCL

• T'wm-nD : Average time for write miss not dirty via XCL

•  $T'_{wm-xD}$  : Average time for write miss with x dirty bits via XCL

• T'<sub>rm-nD</sub> : Average time for read miss not dirty via XCL

•  $T'_{rm-xD}$  : Average time for read miss with x dirty bits via XCL

## 4.3 Characterization of the Write through Cache

Table 2 Average XCL delay in Write through cache

| Memory Access         | Delay (cycles) |

|-----------------------|----------------|

| Read hit              | 2              |

| Read miss             | 32             |

| Non-Consecutive Write | 3              |

| Consecutive Write     | 14             |

Table 2 shows the memory access type and its average delay via XCL in write through cache. The total overhead in the write through cache is computed by the following equation:

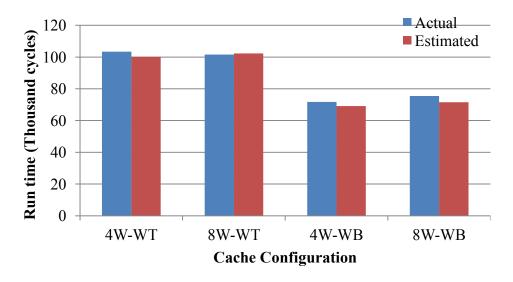

$$O_{WT} = \left\{ [RH * (T_{rd} - T'_{rh})] + [RM * (T_{rd} - T'_{rm})] + [NC_{wr} * (T_{wr} - T'_{nc-wr})] + [C_{wr} * (T_{wr} - T'_{c-wr})] + N_{rf-cyc} \right\}$$