# FRAMEWORK FOR AUTOMATIC VERIFICATION OF UML DESIGN MODELS: APPLICATION TO UML 2.0 INTERACTIONS

VITOR NUNES DE LIMA

A THESIS

IN

THE DEPARTMENT

$\mathbf{OF}$

Information Systems Engineering

PRESENTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF MASTER OF APPLIED SCIENCE IN INFORMATION SYSTEM

SECURITY

CONCORDIA UNIVERSITY

MONTRÉAL, QUÉBEC, CANADA

January 2010 © Vitor Nunes de Lima, 2010

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-67140-5 Our file Notre référence ISBN: 978-0-494-67140-5

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### **AVIS:**

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

#### Abstract

Framework for Automatic Verification of UML Design Models: Application to UML 2.0 Interactions

#### Vitor Nunes de Lima

Software-intensive systems have become extremely complex and susceptible to defects and vulnerabilities. At the same time, the consequences of software errors have also become much more severe. In order to reduce the overall development cost and assure the security and reliability of the final product, it is of critical importance to investigate techniques able to detect defects as early as possible in the software development process, where the costs of repairing a software flaw are much lower than at the maintenance phase. In this research work, we propose an approach for detecting flaw at the design phase by combining two highly successful techniques in the information technology (IT) industry in the field of modeling languages and verification technologies. The first one is the Unified Modeling Language (UML). It has become the de facto language for software specification and design. UML is now used by a wide range of professionals with very different background. The second one is Model Checking, which is a formal verification technique that allows the desired properties to be verified through the inspection of all possible states of the model under consideration. Despite the fact that Model Checking gives significant capabilities to developers in order to create a secure design of the system, they are still not very popular in the UML community. There are many challenges faced by UML developers when it comes to combine UML with model checking (e.g., developer are not familiar with formal logics, the verification result is not in the UML notation, and the generation of the model checkers code from UML models is a problematic task). The proposed approach addresses these problems by implementing a new verification framework with support to property specification without using the complexity of formal languages, UML-like notation for the verification results, and a fully automatic verification process.

## Acknowledgments

I would like to express my sincere gratitude to my thesis supervisors Prof. Mourad Debbabi and Prof. Lingyu Wang at the Concordia Institute for Information System Engineering. Their expertise, advices and guidance had a major influence for the success of the thesis. I would like also to thank Ericsson Canada Software Research, especially Dr. Makan Pourzandi, for funding and scientific cooperation that made possible this research initiative. Also, a very special thanks to all MOBS2 team colleagues for help, hard work and support.

Last but certainly not least, I would like to dedicate my thesis to my parents and rest of my family for great encouragement and valuable moral support. My thesis is especially dedicated to my beloved wife Juliellen for her irreplaceable love, friendship and support.

## Contents

| List of Figures vi |       |                                                           |    |

|--------------------|-------|-----------------------------------------------------------|----|

| Li                 | st of | Tables                                                    | x  |

| 1                  | Intr  | oduction                                                  | 1  |

|                    | 1.1   | Objectives                                                | 6  |

|                    | 1.2   | The Approach                                              | 7  |

|                    | 1.3   | Framework                                                 | 9  |

|                    | 1.4   | Related Publication                                       | 11 |

|                    | 1.5   | Structure of the Thesis                                   | 11 |

| 2                  | Rev   | iew of Literature                                         | 13 |

|                    | 2.1   | The OMG Unified Modeling Language                         | 13 |

|                    |       | 2.1.1 UML Diagrams                                        | 15 |

|                    |       | 2.1.2 Views of the Model                                  | 17 |

|                    | 2.2   | Software Verification                                     | 19 |

|                    |       | 2.2.1 Formal Methods for Verification                     | 20 |

|                    |       | 2.2.2 Temporal Logics                                     | 25 |

|                    | 2.3   | Property Specification for UML Design                     | 31 |

|                    | 2.4   | Verification of UML Design Models                         | 37 |

| 3                  | Pro   | perty Specification for UML Design                        | 39 |

|                    | 3.1   | Property Specification Using UML Artifacts                | 41 |

|                    |       | 3.1.1 Stereotype and Tagged Values                        | 41 |

|                    |       | 3.1.2 Object Constraint Language (OCL)                    | 43 |

|                    |       | 3.1.3 Behavior Diagrams                                   | 44 |

|                    | 3.2   | Property Specification by Extending the UML Meta-language | 46 |

|   | 3.3 | Prope    | erty Specification by Creating New Meta-languages            | 47 |

|---|-----|----------|--------------------------------------------------------------|----|

|   | 3.4 | Usabi    | lity Discussion                                              | 48 |

|   |     | 3.4.1    | Stereotypes and Tagged Values                                | 48 |

|   |     | 3.4.2    | OCL                                                          | 49 |

|   |     | 3.4.3    | Behavior Diagrams                                            | 51 |

|   |     | 3.4.4    | Extending the UML Metalanguage                               | 52 |

|   |     | 3.4.5    | Creating a New Metalanguage                                  | 53 |

|   | 3.5 | Our A    | Approach for Property Specification                          | 54 |

|   |     | 3.5.1    | State Machine-Based Properties                               | 54 |

|   |     | 3.5.2    | MOBS2 Language for Property Specification                    | 56 |

| 4 | Ver | ificatio | on and Validation of UML 2.0 Interactions                    | 59 |

|   | 4.1 | Seman    | ntics of UML Interactions                                    | 61 |

|   | 4.2 | Trans    | lation of UML 2.0 Combined Fragments into PROMELA            | 62 |

|   |     | 4.2.1    | Basic Elements                                               | 62 |

|   |     | 4.2.2    | Interaction Fragments and Weak Sequencing Combined Frag-     |    |

|   |     |          | ments                                                        | 63 |

|   |     | 4.2.3    | Alternative and Option Combined Fragments                    | 65 |

|   |     | 4.2.4    | Parallel Combined Fragments                                  | 66 |

|   |     | 4.2.5    | Loop Combined Fragments                                      | 67 |

|   |     | 4.2.6    | Break Combined Fragments                                     | 69 |

|   | 4.3 | Using    | Source/Destination and Send/Receive Events for Sequence Dia- |    |

|   |     | grams    | V&V                                                          | 70 |

|   |     | 4.3.1    | Tracking the execution state                                 | 70 |

|   |     | 4.3.2    | Using flags to specify LTL properties                        | 72 |

|   | 4.4 | Case S   | Study                                                        | 74 |

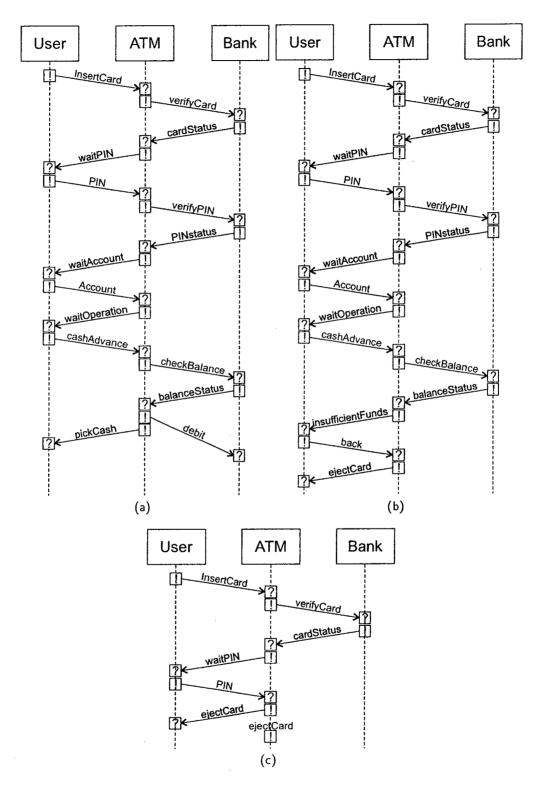

|   |     | 4.4.1    | LTL properties                                               | 74 |

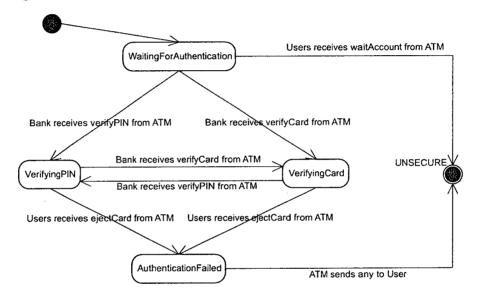

|   |     | 4.4.2    | State Machine property                                       | 77 |

|   |     | 4.4.3    | ATM Case Study Results                                       | 77 |

| 5 | Imp | lemen    | tation of the Tool Support                                   | 80 |

|   | 5.1 | Frame    | ework Implementation                                         | 81 |

|   |     | 5.1.1    |                                                              | 81 |

|   |     | 5.1.2    | Transformation Layer                                         | 83 |

|   |     | 513      |                                                              | 85 |

| 6   | Conclusion | 88 |

|-----|------------|----|

| Bil | oliography | 91 |

## List of Figures

| 1  | Software lifecycle and error introduction, detection, and repair cost [6] | 2  |

|----|---------------------------------------------------------------------------|----|

| 2  | Approach Overview                                                         | 7  |

| 3  | Framework Components Overview                                             | 10 |

| 4  | UML diagrams classification                                               | 16 |

| 5  | UML Examples                                                              | 17 |

| 6  | Kruchten's 4+1 view model                                                 | 18 |

| 7  | Model Checking Approach Overview [6]                                      | 24 |

| 8  | SPIN structure [25]                                                       | 26 |

| 9  | Semantics of Temporal Operators                                           | 28 |

| 10 | Semantics of CTL operators                                                | 30 |

| 11 | Expressiveness of CTL vs. LTL                                             | 31 |

| 12 | An Activity diagram: admission of patients in a medical institution .     | 41 |

| 13 | An example of specifying properties using stereotypes                     | 43 |

| 14 | Fair exchange requirement inside medical application                      | 46 |

| 15 | Enforcing the security requirement of Figure 14 in the activity diagram   |    |

|    | of Figure 12                                                              | 46 |

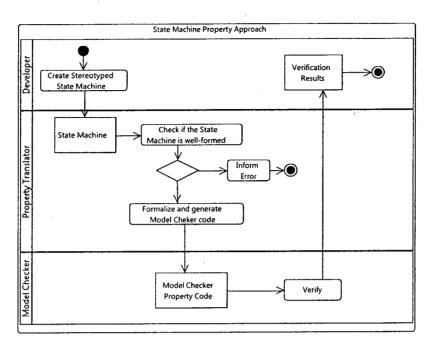

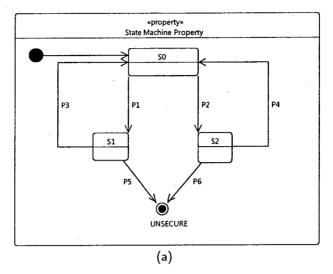

| 16 | State Machine Property Approach                                           | 55 |

| 17 | (a) A generic state machine property, (b) respective never claim state-   |    |

|    | ment used by SPIN                                                         | 56 |

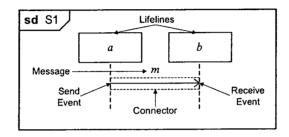

| 18 | Simple Sequence Diagram                                                   | 63 |

| 19 | (a) Simple Interaction Fragment, (b) Weak Sequencing Combined Frag-       |    |

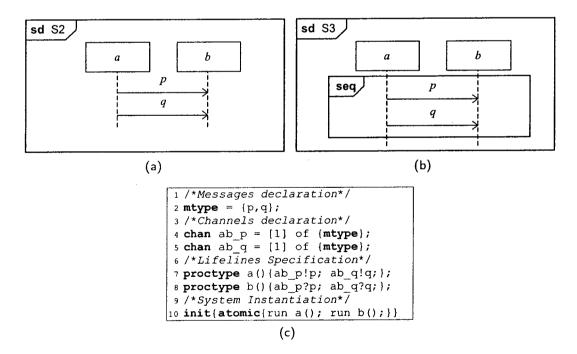

|    | ment and (c) their corresponding PROMELA Code                             | 64 |

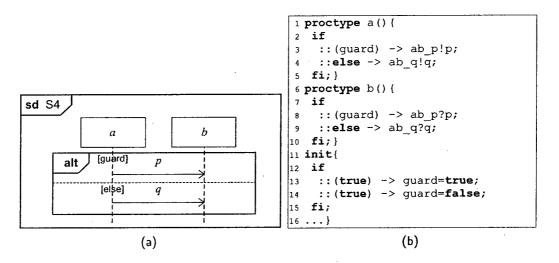

| 20 | (a) Alternative Combined Fragment, (b) Respective PROMELA code            | 66 |

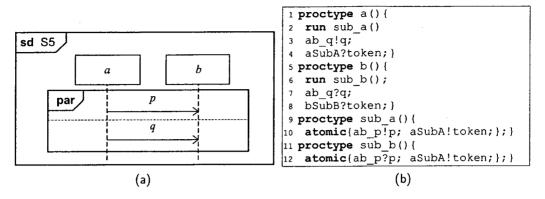

| 21 | (a) Parallel Combined Fragment, (b) Respective PROMELA Code               | 68 |

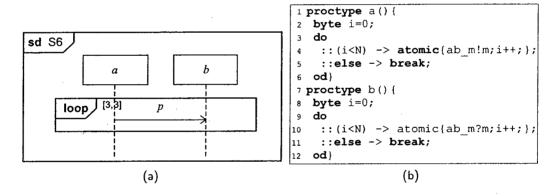

| 22 | (a) Loop Combined Fragment, (b) Respective PROMELA Code                   | 68 |

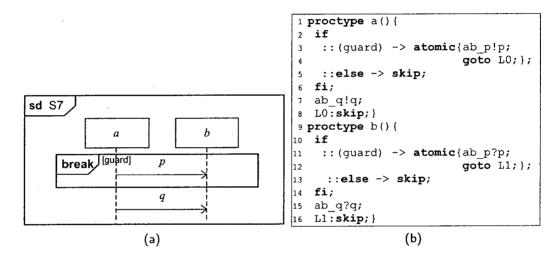

| 23 | (a) Break Combined Fragment, (b) Respective PROMELA Code                  | 69 |

| 24 | PROMELA code of the diagram in figure 19(a)                               | 72 |

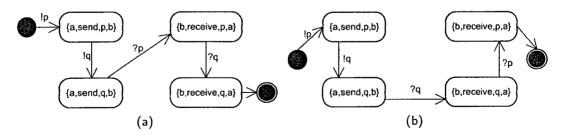

| 25 | SPIN counterexamples                                                        | 73 |

|----|-----------------------------------------------------------------------------|----|

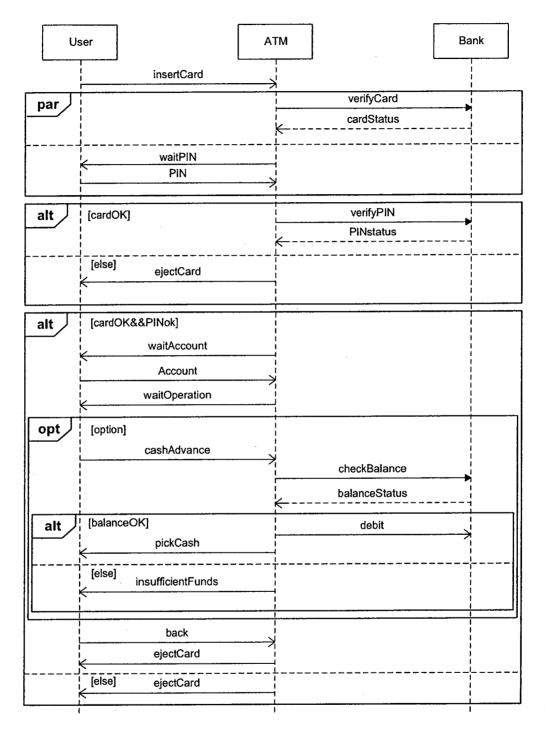

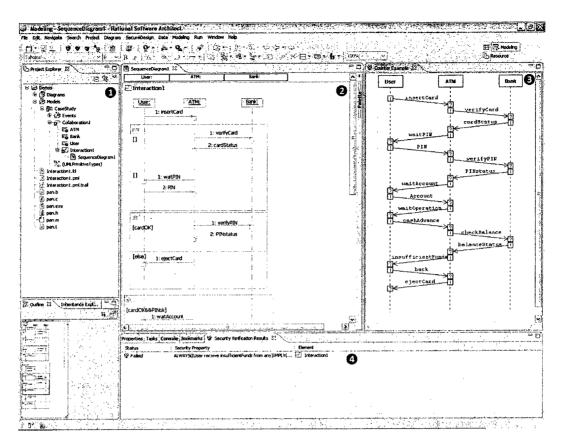

| 26 | ATM Sequence Diagram                                                        | 75 |

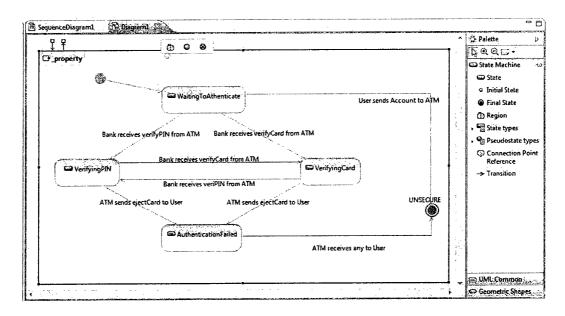

| 27 | Property specified using state machine                                      | 77 |

| 28 | SPIN counterexamples for LTL properties: (a)counterexample of prop-         |    |

|    | erty ii, (b) counterexample of property iii, (c) counterexample of prop-    |    |

|    | erty iv                                                                     | 78 |

| 29 | Components of the framework implemented in our tool                         | 81 |

| 30 | Eclipse window showing the verification progress                            | 82 |

| 31 | Piece of the model checker code from the Lifeline <i>User</i> in figure 26. | 84 |

| 32 | Screenshot of the IBM RSA workspace                                         | 86 |

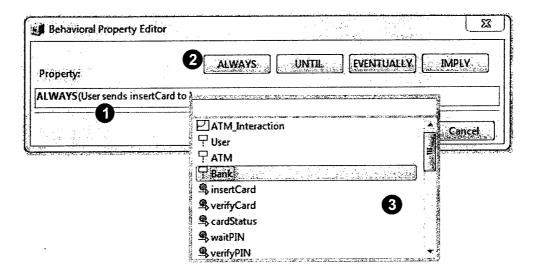

| 33 | Textual property editor                                                     | 87 |

| 34 | State machine property editor                                               | 87 |

## List of Tables

| 1 | UML diagrams [58]                                                    | 18 |

|---|----------------------------------------------------------------------|----|

| 2 | The Use of Security Specification Approaches in the State of the Art | 40 |

| 3 | Mapping rules from logical and temporal operators to the MOBS2       |    |

|   | Language                                                             | 57 |

| 4 | Mapping of basic UML Sequence Diagrams into PROMELA                  | 63 |

| 5 | Summary of the results                                               | 79 |

### Chapter 1

### Introduction

Software-related systems are nowadays part of our everyday life. From simple electronic gadgets to complex satellites, people lives surrounded by these technological innovations. It is evident all the benefits brought by this scientific progress. On the other hand, software products have become extremely complex and susceptible to defects and vulnerabilities. At the same time, the consequences of software errors have also become much more severe. Consequently, the software engineering discipline must now play a predominant role in the process of building secure and reliable software.

The construction of complex software-related systems includes, in summary, requirements engineering, design, code implementation and testing. Requirement engineers typically prepare a requirements document in order to describe the required or expected behavior of the new software. Usually, this document is written in prose with no formalism [5]. The requirements state the anticipated behavior of a system

component in reaction to a sequence of external stimulus. The requirements document is then used, at the design phase, as input for designing models that reflect the desired properties of the system. Developers use these models to build the code at the implementation phase. The models may also serve as input in designing test cases to test the code at testing phase [5].

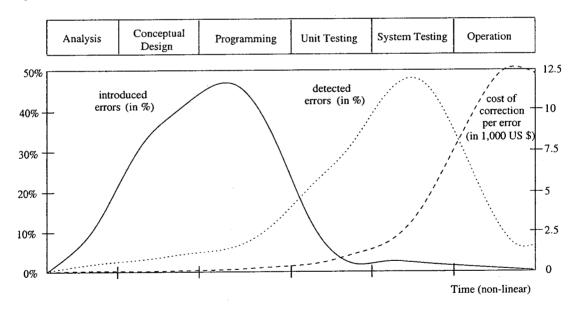

A great need in software development process is to advance error detection to early phases of the software life cycle. It has been shown that costs of repairing a software flaw during maintenance are approximately 500 times higher than fixing them at early design phase [6]. Figure 1 gives a clear idea of how error introduction, detection and repair costs are distributed through the developments process.

Figure 1: Software lifecycle and error introduction, detection, and repair cost [6]

From the figure, only 15% of flaws are detected at the initial design phase, whereas the cost of fixing them at this phase are extreme low when compared with the cost of corrections at the testing stage where most of the errors are found. E.g., if a design

model contains errors, the errors are transited to the developers during the coding and to the test engineers during the test design. Any code or test case construct will likely present the same errors as the model. These defects may not be revealed until the acceptance test, or worse, after the system is fully installed [5]. Therefore, in order to reduce the overall development cost and assure the security and reliability of the final product, it is of critical importance to investigate techniques able to detect defects as early as possible in the software development process.

For the purpose of advancing error detection, the verification of design models appears as one of the most prominent solutions. Briefly, the objective of this verification is to determine whether the design models actually possess the desired properties specified at the requirement phase. In the state-of-the-art, there are many verification techniques targeting at design models. Including informal approaches such as peer reviewing and testing, as well as formal methods, static analysis, theorem proving, model checking, etc. Different approaches are usually more applicable to different areas.

In this research work, we combined two highly successful techniques in the information technology (IT) industry in the field of modeling languages and verification technologies. The first one is the **Unified Modeling Language** (UML) [44]. It has become the de facto language for software specification and design. UML is now used by a wide range of professionals with very different background, e.g.: software architects, database professionals, business planner, software developer and etc. The second one is **Model Checking**. It is a formal verification technique which allows the desired properties to be verified through the inspection of all possible states of

the model under consideration. The attractiveness of model checking is the following: it is completely automatic, it offers counterexamples in case a model fails to satisfy a property assisting as a valuable debugging in information, and finally, the performance of model-checking tools has proven to be mature since they have been used by a number of successful industrial applications [6]. The combination of UML and Model Checking gives significant capabilities to developers in order to create a secure design of the system and, at the same time, verify the correctness of models at the beginning of the software life cycle.

Even though the model checkers have been successful in implementing high-performance verification algorithms, they are still not very popular in the UML community. There are many challenges faced by UML developers when it comes to combine UML with model checking. First, most of developers are not familiar with formalism used by model checkers. Concepts like temporal logics and labeled transition system are some prerequisites to use model checking techniques. However, most of developers are resistant to get used to these concepts. Second, even if the developers are able to deal with the formalism, the output from the verification tool is not similar to the UML notation and it is not easy be understood in the UML context. Finally, the generation of model checkers code is a very problematic task. It demands specialized knowledge such as: (1) a detailed understanding of the semantics of the UML diagrams in order to extract the correct behavior from the models. (2) an advanced knowledge about the semantics and syntax of the model checker language to guarantee that the generated code reflects exactly the behavior extracted from the UML model. In addition to that problems, a simple UML model may require many lines of model checker code,

which makes it a very tedious and demanding task when the code generation is done manually.

The approach proposed in this thesis addresses all these problems by implementing a new verification framework with support to property specification without using the complexity of formal languages, UML-like notation for the verification results, and a fully automatic verification process. As the model checking verification process is completely automatic, this mechanism can be incorporated into the development methodology without the need to give training to users about the mathematical foundations and the verification algorithms. The result of this approach is an efficient tool for advancing error detection. This tool inherits the rigor and soundness of formal techniques (which is of vital importance when it comes to verification of security-critical and high-reliable software) and, simultaneously, it hides its complexity. Moreover, since it targets at the early stages of the development process, it can reduce considerably the overall development cost.

This thesis is part of the research initiative supported by Ericsson Canada Software Research. This cooperation program aims at developing a Model-Based Framework for Engineering Secure Software and System (MOBS2)<sup>1</sup>. The targeted security concerns are: capturing security requirements, specification and design of security mechanisms, verification and validation of security properties/policies, and automatic generation of secure code. Appropriate security profiles and UML language extensions will be used in the capture of security requirements as well as the specification and design of security solutions.

<sup>&</sup>lt;sup>1</sup>http://mowglish.ciise.concordia.ca

In the following, we enumerate the objectives of this research work along with the proposed approach and the framework designed to achieve these goals.

#### 1.1 Objectives

This main objective of this thesis consist in proposing a mechanism to advance error detection in the software development process by creating verification framework capable of analyze UML design models using model checking techniques and provide meaningful and easy-to-understand results. This framework needs to provide support for properties specification without using the complexity of formal languages. In addition, the verification procedures need to be transparent to the developer, meaning that the proposed approach should be as much as possible automated in order to hide the complexity of model checking.

More specifically, the detailed goals are the following:

- Investigate the state of the art approaches in the fields of properties specification and software verification at the design level.

- Provide alternatives for the property specification using behavior diagrams, and propose a new language on top of formal logics.

- Define the translation rules of UML models and properties into the input language of the model checker.

- Prototype the approach into a framework for verification design models, and incorporate it into a Integrated Development Environment (IDE).

• Conduct case studies with the objective of demonstrating the feasibility and effectiveness of the proposed approach.

#### 1.2 The Approach

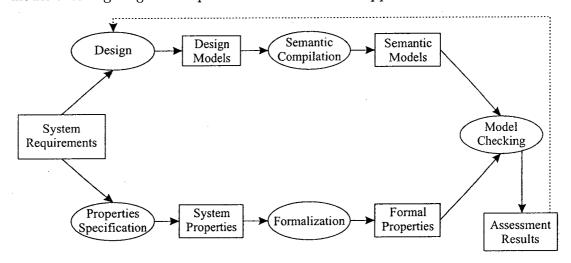

As previously mentioned, our approach comes from the harmonious combination of two successful techniques, software modeling with UML and formal verification using model checking. Figure 2 depicts the overview of our approach.

Figure 2: Approach Overview

The verification process stars with the *System Requirements* developed by the requirement engineers. Typically, this artifact is a well-structured document containing all what the system should and should not do. The *System Requirements* are then used as input to two important activities: *Design* and *Properties Specification*.

The *Design* has the purpose of translating the requirements into a specification that describes how to implement the system [32]. The output of this activity is the *Design Models* having the structural and behavioral specification of the system. In

this thesis, we assume UML as the modeling language used in this activity, since it has proved to be very powerful, versatile and well-accepted by the industry.

The *Design Models* needs to be accompanied with a specification of properties of interest to be verified. At the *Property Specification* activity, we provide developer with alternatives (e.g., UML profile, templates, etc) to facilitate the task of writing properties without the need to uses formal languages.

The subsequent steps of the proposed approach are all automatic. The verification engine receives the models and the properties and transforms them into *Semantic Models* and *Formal Properties*, respectively. The *Semantic Models* are derived from the models by following the OMG UML specification [44]. For the *Formalization* of system properties, Linear Temporal Logics (LTL), Computational Tree Logic (CTL), and automata-based properties are used as the underlying formal language.

The *Model Checking* algorithms are implemented by the existing model checking tools. In this work, we decided to use **SPIN** which is a well-known model checker. SPIN is one of most popular and powerful tool for detecting software defects in concurrent system designs. It has been developed at Bell Labs in the eighties and nineties. In 2002 SPIN was recognized by the Association for Computing Machinery (ACM) with its most prestigious *Software System Award*. The tool has been applied in several application from verification of complex call processing software that is used in telephone exchanges, to the validation of intricate control software for interplanetary spacecraft [24].

Finally, the results are presented as an easy-to-understand graph automatically generated by analyzing the model checker's outputs. These results are then utilized by the developers to refine the design models in order to remove all the found errors.

This main contributions introduced in this approach are the followings: (1) In the property specification activity, the new proposed alternatives to write properties are based on UML state machine diagrams and natural language, which are appealing to developers. Moreover, the work of formalization and translation to the input language of the model checker is completely transparent to the developer. (2) The semantic compilation is also automatic and transparent to the developer. In addition, our approach can handle the new element of UML 2.0 interaction, which allows developer to verify very complex scenarios with non-straightforward execution trace. Finally, (3) in the assessment results, our approach address the problem of output generated by the verification tool not being similar to the UML notation. Our tool generates graphical results that can be easily compared to model being analyzed. Consequently, a developer can quickly identify the problem when reading results.

#### 1.3 Framework

Our framework demands an underlying UML modeling tool where the developers can create the UML design models. We have chosen IBM Rational Software Architect<sup>2</sup> (RSA) as the environment for development, since it contains a very powerful UML modeler. In addition, it can be augmented with Eclipse plug-ins, which allows the verification engine to be embedded into the development environment.

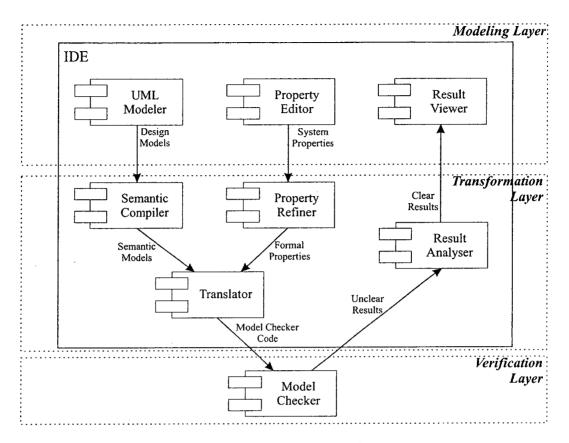

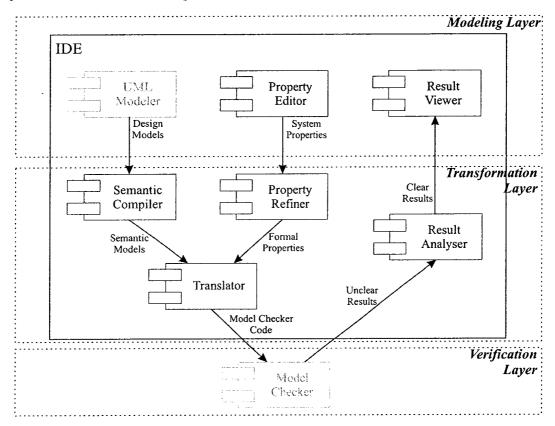

Figure 3 shows the structure of the main components of the framework. We decided to divided our tool into three layers. The first one is the *Modeling Layer*. This is

<sup>&</sup>lt;sup>2</sup>http://www.ibm.com/software/awdtools/architect/swarchitect/

Figure 3: Framework Components Overview

the layer that interacts directly with the user (the developer). It is composed of UML Modeler, Property Editor and Result Viewer. The UML modeler comes as part of the IBM RSA and its elements are accessed using eclipses plug-ins. We developed the property editor and the Result Viewer to facilitate the specification of system properties and to present the result in a friendly manner, respectively. The second layer is responsible to translate models and properties into the input language of the model checker by extracting the semantic models (Sematic Compiler), formalizing the properties (Property Refiner), and translating then into the model checker code (Translator). Moreover, this layer receives the output from the model

checker and analyzes it (Result Analyzer) in order to produce meaningful and easy-to-understand results. Finally, the third layer contains the actual verification engine. Herein, we consider only model checking tools, but this layer can expanded to also include other verification tools such as theorem provers or static analyzers. It is import to mention that the first two layers are into the IDE. This feature makes the incorporation of the verification mechanism very smooth and reduces considerably the work with configuration and training.

#### 1.4 Related Publication

The significance of this research work gained scientific visibility with the following publications:

- In [57], we present an extensive survey about usability of security specification approaches for UML Design. It shows how the main adopted can be used for property specification along with a comparative study. The details of this study can be found in chapters 2 and 3.

- In [37], we present an efficient technique for formal V&V of UML 2.0 sequence diagrams. This paper focus on the semantics of UML sequence diagrams and its verification using SPIN model checker. The details about the proposed approach can be found in chapter 4.

#### 1.5 Structure of the Thesis

The reminder of the thesis is organized as follows:

- Chapter 2 provides a review of literature. It shows the theoretical background about the OMG Unified Modeling Language, and software verification. It also depicts the state-of-the-art survey of property specification and verification of UML diagram.

- Chapter 3 shows different alternatives for writing properties. It shows how UML

artifacts can be used for property specification. In the end, it presents the new

alternatives using UML behavior diagrams and a new language on top of the

formal logics.

- Chapter 4 presents the application of our approach in UML interactions. It starts

presenting the semantics of UML interactions. Then it shows how to compile

interaction semantics into PROMELA semantics, which is used as the input for

the SPIN model checker. Subsequently it presents a case study to demonstrating

the feasibility and effectiveness of the proposed approach.

- Chapter 5 gives a detailed description of the tool implemented to support our approach.

- Chapter 6 presents the summarizing conclusion of the thesis.

### Chapter 2

## Review of Literature

This chapter introduces the main concepts needed to support the work developed in this thesis. We present the theoretical background on modeling languages (with focus on UML), starting from the classification of UML diagrams to the different views of the models. In addition, the foundation on software verification is also presented. Finally, the state-of-the-art survey on property specification in UML and UML models verification is detailed in the end of this chapter.

#### 2.1 The OMG Unified Modeling Language

Nowadays, models appear constantly in our routine. Any person, even with no modeling background, is used to read models representing, for example, driving directions, furniture assembling instructions, device safety procedures, and so on. Models are an appealing way of representing a system in many different fields. It is not a surprise that modeling languages are increasingly becoming more and more important in software engineering. Modeling abstracts a real system to a level where only the essentials

aspects matter. It provides means of understanding extremely complex software, as well as it makes the communication among the development team much more efficient and effective [58]. Hereafter, we introduce the modeling language which has become the de facto standard language for software specification and design: UML.

The Unified Modeling Language (UML) is a language and notation system used to specify, construct, visualize, and document models of software systems. Before UML, software developers used to have a collection of mismatched diagram techniques, notation, and semantic approaches [36]. The creation of UML came as solution in order to have an *unified* notation and semantic model. UML covers a wide range of applications and is suitable for technical (concurrent, distributed, time-critical) systems and so-called commercial systems [62]. It is now used in many different ways by people with very different backgrounds. Weilkiens and Oestereich, in [62], enumerate some interesting examples of professionals using UML:

- business planners, as a language to specify the planned operation of a business process, perhaps in concert with a business process language such as the Business Process Modeling Notation (BPMN) [45].

- consumer device engineers, as a way to outline the requirements for an embedded device and the way it is to be used by an end user.

- software architects, as an overall design for a major stand-alone software product.

- IT professionals, as an agreed-on set of models to integrate existing applications.

- database professionals, to manage the integration of databases into a data warehouse, perhaps in concert with a data warehousing language such as the Common

Warehouse Metamodel (CWM) [46].

• software developers, as a way to develop application that are flexible in the face of changing business requirements and implementation infrastructure.

UML is now at the version 2.2. A major update has been done at version 2.0 compared to the version 1.x. UML 2.0 improved behavioral modeling by deriving all behavioral diagrams from a fundamental definition behavior, In contrast to UML 1.X where different behavioral models were completely independent [42]. It also improved relationship between Structural and Behavioral Models. Now UML allows to designate that (for example) a State Machine or Sequence is the behavior of a class or a component.

The new version of UML goes beyond the Classes and Objects modeled by UML 1.x to add the capability to represent not only behavioral models, but also architectural models, business process and rules, and other models used in many different parts of computing and even non-computing disciplines [42].

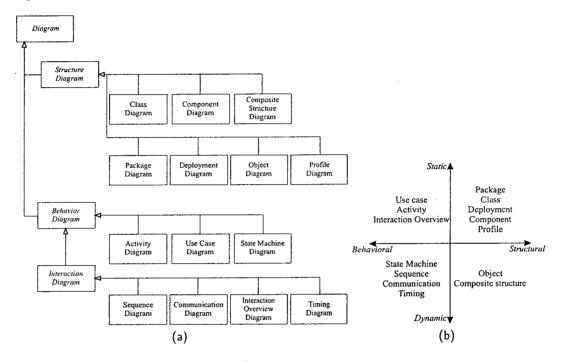

#### 2.1.1 UML Diagrams

There is a wide range of UML diagrams with different capabilities. The OMG UML specification classifies the models into two main categories: structural and behavioral diagrams. A Structural model shows the static structure of the objects in a system [44], i.e., how the elements are composed. A behavioral model shows the dynamic behavior of the objects in a system, including their methods, collaborations, activities, and state histories [44]. Unhelkar, in [58], proposed an additional classification for

UML diagrams based on the *time* dependency of each diagram. He suggests that UML models can have either a *static* or a *dynamic* nature. Dynamic models are those which display various states of elements and the events that causes state changes, and those diagrams which are *frozen* in time are then static.

Figure 4: (a) OMG classification of UML diagrams, (b) Diagrams classification including structural and characteristics as well as their static versus dynamic nature [58]

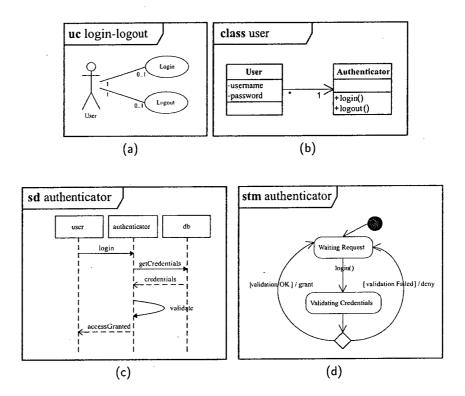

To illustrate the different applications of UML diagrams, figure 5 depicts a hypothetical situation where the system needs to implement two use cases (login and logout). This requirement is shown in figure 5(a) by the Use Case diagram. In order to implement these use cases, a developer can decide to define two classes which are:

User and Authenticator. The static structure of these classes is shown in figure 5(b) as a Class diagram. The interaction among the instances of the classes in the login scenario is presented as a Sequence diagram in figure 5(c). This diagram shows that

a database with user credentials should also be implemented in this system. Finally, internal behavior of the authenticator is specified using a *State Machine Diagram*.

Figure 5: Example of using UML diagrams

Table 1 provide a brief description of all diagrams. It is possible to see that each diagram has a different purpose and a precise strength for particular tasks inside the software development process. Choosing the right set of diagrams to model a system is very important to make the design understandable and approachable [58].

#### 2.1.2 Views of the Model

There are many ways to break up UML diagrams into perspectives or views that capture a particular aspect of a system. In this research work, we follow the Kruchten's

| UML Diagrams         | Represents                                        |

|----------------------|---------------------------------------------------|

| Use case             | system functionality from the user's viewpoint    |

| Activity             | a sequence of actions of a flow within the system |

| Class                | class, entities, business domain, database        |

| Sequence             | interactions between objects                      |

| Interaction Overview | interactions at a general high level              |

| Communication        | interactions between objects                      |

| Object               | objects and their links                           |

| State Machine        | the run-time life cycle of an object              |

| Composite Structure  | component of object behavior at run-time          |

| Component            | executables, linkable libraries, etc.             |

| Deployment           | hardware nodes and processor                      |

| Package              | subsystems, organization units                    |

| Timing               | time concept during object interactions           |

| Profile              | UML extensions                                    |

Table 1: UML diagrams [58]

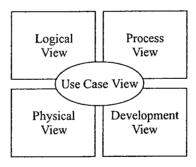

4+1 view model [31] to describe the role of each diagram in the overall model. This approach has become a de facto standard to classify the views of the model. The 4+1 view model organizes a description of a software architecture using five concurrent view, each of which address a specific set of concerns [31], as shown in Figure 6.

Figure 6: Kruchten's 4+1 view model

Each view is defined in the following [40]:

The logical view describes the abstract description of a system's parts. Used to

model what a system is made up of and how the parts interact with each other.

The UML diagrams typically used in this view are class, object, state machine,

and interaction diagrams.

- The *process view* describes the processes within your system. It is particularly helpful when visualizing what must happen within your system. This view typically contains activity diagrams.

- The *development view* describes how your system's parts are organized into modules and components. It is very useful to manage layers within your system's architecture. This view typically contains package and components diagrams.

- The *physical view* describes how the system's design, as described in the three previous view, is then brought to life as a set of real-world entities. The diagrams in this view show how the abstract parts map into the final deployed system. This view typically contains deployment diagrams.

- The use case view describes the functionality of the system being modeled from the perspective of the outside world. This view is needed to describe what the system is supposed to do. All of the other view rely on the use case view to guide them. This view typically contains use case diagrams, descriptions, and overview diagrams.

#### 2.2 Software Verification

During the recent years, a number of approaches have been proposed to insure the correctness of software-intensive systems. These techniques are either informal or formal as well as manual or automated. *Software verification* approaches focus on checking if a product is being built correctly, i.e., they make sure that the program

functions have the expected behavior. We also investigate *software validation* techniques. These approaches ensure whether the software meets the user's needs, i.e., they check if the correct product is being built.

Among all the proposed approaches, formal methods are now getting a considerable attention from the research community because of their rigor and soundness. This attribute has even more importance in the software security development where the need of vulnerabilities-free software is main goal. Next sections describes the main formal verification approaches as well as the formal language used in these approaches.

#### 2.2.1 Formal Methods for Verification

Due to the fact that software architectures are becoming increasingly complex, it is each time more difficult to assure the satisfaction of all required properties only by using of test-based techniques. In order to overcome this problem, formal methods appears as very important option to guarantee high-quality of software-based systems. Formal methods are techniques based on logics, set theory, and algebra for the specification of software systems models and verification of models' properties [15]. The use of formal methods has become widespread, especially during early phases of the software development process. The concept is to create an abstract model of a software system which can be used to verify whether the software under development satisfies a given set of properties. Indeed, the detection and prevention of faults is one of the main motivation for using formal methods. Verifying a formal system specification can help to detect many design flaws; furthermore, if the specification is given in an executable language, it may also be exploited to simulate the execution of the

system, making the verification of properties easier (early prototyping) [15]. Static Analysis, Theorem Proving and Model Checking are the three major approaches in the state-of-the-art. These approaches are described below.

#### Static Analysis

Static Analysis techniques are those approaches that scan for errors using the static specification of a system. In other words, any tool that analyzes a code without executing it is performing static analysis [13]. Static analysis tools are often compared with spell checkers. The latter can rise an alert when the writer makes a well-known mistake, nevertheless they are unable to interpret a text and detect a misuse of certain word (e.g., spell checkers may not tell that you should have used meet instead of meat). Currently, there exist many commercial and open-source static analysis tools and they are widely used in the software development process. Type checking, style checking, vulnerability finding, security review are only few examples of the applicability of static analysis.

Despite its popularity, there is a common complaint against static analysis tools regarding the number of false positives. A false positive is a defect reported by the verification engine where no problem actually exists. Since the runtime behavior is not used in this technique, at many points the tool is not able to determine whether an unclear situation has a real bug. Consequently, it gives several alarms. A very important motivation to generate many false positives is to minimize the number of false negatives. A false negative is the most undesired situation where a real problem actually exists, but the verification engine does not report it. On the other hand, a

large number of false positives can induce the developer to overlook some severe bugs.

#### Theorem Proving

Theorem proving tool is an application that, given a calculus (for some logic) and a formula, attempts to find a proof by repeatedly applying the inference rules of the calculus [54]. There are two main types of theorem provers: Interactive Theorem Provers (ITPs) and Automated Theorem Provers (ATPs). ITPs are tools where the application of operations and inference rules is performed manually by executing commands and creating command scripts. Whereas ATPs algorithms perform automatic search for a proof. There also rare cases where due to the formalism involved (e.g. hidden circular references leading to a logical paradox), a given conjecture cannot be either proven or disproven [11]. The high level of complexity of this technique is one of the main reasons why it is not yet widely used for the verification of software-related systems.

#### **Model Checking**

Model checking is a formal verification approach for detecting behavioral flaws (including safety, reliability, and security-related flaws) of software systems based on suitable models of such systems [15]. Model checking is fully automatic, has a very good coverage, produces valuable results (counterexamples), and it can uncover software defects that might go undetected using other verification techniques. However, there are still some shortcomings in model checking. Indeed, there are still several barriers to fully integrate it into software development process. More specifically, model

checking has a major scalability issue; also, there is still a gap between model checking concepts and notations and the models used by engineers to design systems [15].

Unfortunately, the number of states may proliferate even for relatively simple programs, making the model checking approach computationally very expensive. However, space search algorithms allowing more than  $10^{20}$  states have been available for several years now, and today's model checkers can easily manage millions of state variables. In addition, a number of techniques have been developed to prevent state explosion and to enable formal verification of realistic programs and designs [15].

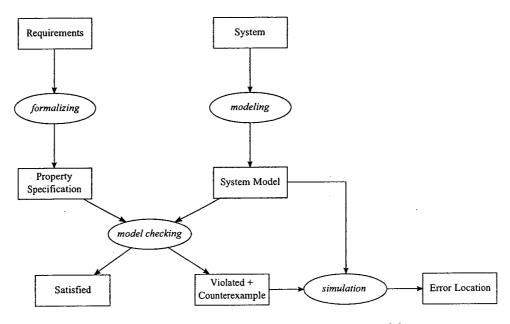

The theoretical concept supporting model checking techniques is state reachability analysis, which has the advantage of being conceptually simple. Basically, the verifier states the properties it would like the program to possess; then a model checker tool searches the program state space looking for error states, where the specified properties do not hold [15]. It is important to mention that the property specification prescribes what the system should do and what it should not do, while the model description address how the system behaves. If the tool is able to find a state for which the property under consideration fails, it provides a counterexample that indicates how the model could reach the undesired state. The counterexample describes an execution path from the initial system state to a state that violates the property being verified. With a simulator, the user can replay the violating scenario, obtain useful debugging information, and adapt the model (or the property) accordingly [6]. Figure 7 shows an overview of the model checking approach.

From figure 7, it is possible to see that the model checking approach has a very good similarity with the approach proposed in figure 2. Both approaches have activities

Figure 7: Model Checking Approach Overview [6]

to generate system properties and design models. The assessment results from figure 2 would encapsulate the elements after the model checking in figure 7 (i.e. satisfied, violated + counterexample, simulation and error location). This was one of the main reasons why we decided to choose model checkers as the verification engine supporting the error detection in UML diagrams. In the following, we introduce the SPIN Model Checker, which is verification tool chosen for this research work.

#### SPIN Model Checker

SPIN is a generic verification system that supports the design and verification of asynchronous process systems [25]. SPIN verification algorithms focus on proving the correctness of process interactions. These interactions can be specified using SPIN rendezvous primitives that allow specification of asynchronous messaging passed through buffered channels and accessed by shared variables. The name SPIN was originally

chosen as an acronym for Simple PROMELA Interpreter, since the specification language that it accepts is called PROMELA. SPIN can be used in two basic modes: as a simulator or as a verifier. In simulation mode, SPIN is used to get a quick impression of the types of behavior that are captured by a system model, as it is being built. This can be of considerable help in the debugging of models. However, no amount of simulation can prove the satisfaction or not of a given property; only a verification run can do so [24]. In the verification mode, SPIN checks if there is at least one execution path that leads to an undesired state, the it uses the simulation mode to display the error trace.

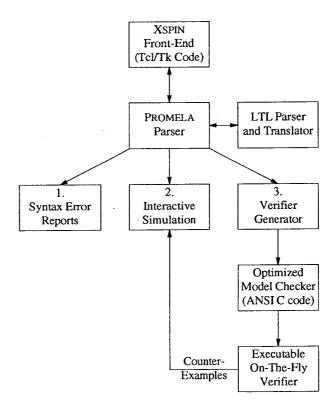

The internal structure of SPIN is shown in figure 8. SPIN comes with a graphical front-end: XSPIN. The PROMELA parser is able to receive properties written in Linear Temporal Logic (LTL) and translate them into the PROMELA language. For the verification purpose, SPIN generates an optimized C code from the PROMELA specification. This code needs to be compiled by a C compiler and the output of the executable file is the result of the verification. If a property fails, an execution trace is generated from the verifier and it can be used guide a simulation showing the steps that lead to undesired situation.

#### 2.2.2 Temporal Logics

Temporal logic is a form of logic specifically tailored for statements reasoning which involve the notion of order in time [8]. Although the term temporal suggest a relationship with the real-time behavior, this is only true in an abstract sense. A temporal logic allows the specification of relative order of events. It does not support any

Figure 8: SPIN structure [25]

means to refer to the precise timing of events. In terms of transition systems, neither the duration of taking a transition nor state residence times can be specified using the elementary modalities of temporal logics. Instead, these modalities allows the specification of the order in which state labels occur during an execution, or to assess that certain state labels occurs infinitely often in a (or all) system execution [6].

Temporal logic also offers concepts immediately ready for use. Its operators mimic linguistic constructions (the adverbs "always", "until", the tenses of verbs, etc.) with result the natural language statements and their temporal logic formalization are fairly close. Finally, temporal logic comes with a *formal semantics*, an indispensable specification language tool [8].

In the following, we describe the two most commonly used temporal logics in model checking tools: Linear Temporal Logic (LTL), a temporal logic that is based on a linear-time perspective, and Computational Tree Logic (CTL), a logic that is based on a branching-time view.

#### Linear Temporal Logic (LTL)

Linear Temporal Logic is a logic for reasoning about properties of computational paths. A LTL formula, in the context of a given execution, considers only one possible future in a moment. It cannot examine alternative executions which split of the execution when a nondeterministic choice is possible [8].

The basic ingredients of LTL-formulae are atomic propositions, the Boolean connectors like conjunction  $\land$ , negation  $\neg$ , and two basic temporal modalities  $\bigcirc$  (next) and  $\mathbf{U}$  (until). The  $\bigcirc$  operator is a unary prefix operator. The formula  $\bigcirc \phi$  holds at the current moment, if  $\phi$  holds in the next "step". The  $\mathbf{U}$  operator is a binary operator. The formula  $\phi_1 \mathbf{U} \phi_2$  holds at the current moment, if there is some future moment for which  $\phi_2$  holds and  $\phi_1$  holds at all moments until that future moment [6].

The until operator allows deriving the temporal modalities eventually (denoted  $\Diamond$ ) and always (denoted  $\Box$ ) as follow:

$$\Diamond \phi \stackrel{\text{\tiny def}}{=} \text{true} \mathbf{U} \phi \tag{1}$$

$$\Box \phi \stackrel{\text{def}}{=} \neg \Diamond \neg \phi \tag{2}$$

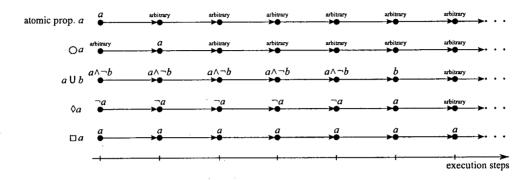

Figure 9 shows the semantics of temporal operators for the case where the arguments are just atomic propositions.

Figure 9: Semantics of Temporal Operators

#### Computational Tree Logic (CTL)

Computational Tree Logic is a branching-time logic. The semantics of this temporal logic is not based on a linear notion of time, but on a branching notion of time (an infinite *tree* of states). Branching time means that at each moment there may be different future paths. The semantics of branching temporal logic is defined in term of an infinite, directed *tree* of states. Each traversal of the tree starting from its root represent a single path [6].

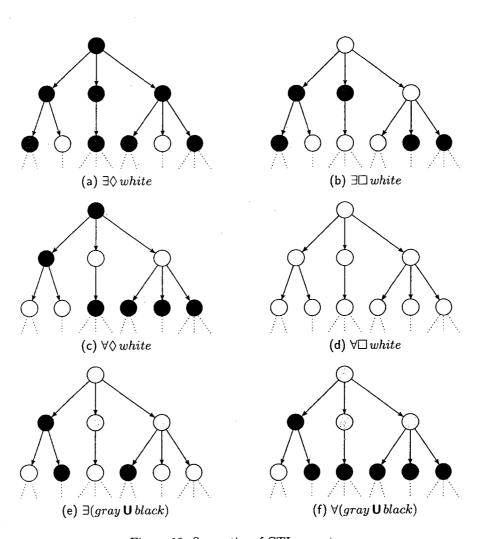

The temporal operator in branching-temporal logic permit the expression of properties of *some* or *all* computations that start in a state. In order to allow this kind of expressions, CTL supports the existential (denoted  $\exists$ ) and universal (denoted  $\forall$ ) path quantifiers. Figure 10 presents the semantics of the CTL operators.

• In figure 10(a), there are two paths that is possible to reach a white circle. Since the condition to  $\exists \Diamond white$  be true is to have at least one path reaching a white

circle, this property holds in that tree.

- In figure 10(b), there is one path that the color is always white. This makes the property ∃□ white true in that scenario.

- In figure 10(c), for all paths there is at least one white color. This is condition

for ∀◊ white to be true.

- In figure 10(d), all the colors are white, then  $\forall \Box white$  holds in this scenario.

- In figure 10(e), there is a path where the colors are gray until the first black. In

other words, grays is true until black. Therefore, ∃(gray U black) is true.

- In figure 10(f), the condition grays is true until black holds in all path. Then

∀(gray U black) is true.

#### Expressiveness of CTL vs. LTL

Even though CTL and LTL allow the specification of many important properties, those logics are not comparable in terms of their expressiveness. In other words, there are properties that can only be expressed using LTL, whereas some other properties can only be expressed in CTL. Below are some examples of the difference between LTL and CTL.

- LTL ⊈ CTL

- $-\lozenge \Box a \in LTL$ , but  $\lozenge \Box a \notin CTL$  (idea:  $\forall \lozenge \forall \Box a \neq \forall \lozenge \Box a$ )

- CTL ⊈ LTL

- $\forall \Box \exists \Diamond a \in CTL$ , but  $\forall \Box \exists \Diamond a \notin LTL$  (idea: no  $\exists$  in LTL)

Figure 10: Semantics of CTL operators

Figure 11: Expressiveness of CTL vs. LTL

There are still many debates regarding the complexity of the verification algorithms in both languages. However, in practice there is no measure that can reliably tell which method can solve a given problem more efficiently [24]. CTL model checkers have been very popular in the development of the early tools for hardware verification, while LTL model checkers have become dominant in applications of software verification [24]. The logic itself, though, is not the only factor that determines the success of a model checkers. Implementation issues as well as the domain where the tool is being applied could also be mentioned as important factors to its performance.

## 2.3 Property Specification for UML Design

In this section, we present a survey on the main state of the art contributions that are related to specifying and designing security for UML.

The UMLSec approach by Jürjens is among the first efforts in extending UML for the development of security-critical systems [27]. It provides a UML profile where general security requirements such as secrecy, integrity, fair exchange, etc are encapsulated using UML stereotypes and tagged values. It also defines a tailored formal semantics to formally evaluate UML diagrams against weaknesses. In order to analyze security specifications, the behavior of a potential adversary that can attack various parts of a system is formally modeled. However, UMLSec lacks in expressiveness since security properties are predefined using UML stereotypes and tagged values. This framework cannot be used to specify user-defined properties.

Pavlich-Mariscal et al. propose an aspect-oriented approach to model access control policies [48]. They augment UML with new diagrams to represent Role-Based Access Control (RBAC), Mandatory Access Control (MAC) and Discretionary Access Control (DAC) schemes, that are separated from the main design. MAC, DAC and RBAC are decomposed into security features which represent specific elements of an access control policy, e.g. permissions, MAC security properties, delegation rules, etc. This is the only approach that combines MAC, DAC and RBAC into a set of security diagrams separated from the main design. Modeling security as aspects reduces the scattering of access control definitions in the entire application. It is also possible to make changes to the design without impacting the entire security of the application. Moreover, Pavlich et al. supports an AOP [29] code generation to enforce access control policies at execution time. However, this approach is limited to access control policies.

Zisman proposes a framework to support the design and verification of secure peer-to-peer applications [64]. The design models and security requirements are specified using UMLSec. The modeling of abuse cases to represent possible attack scenarios and potential threats helps designers to identify the security properties to be verified in the system. In addition, this approach artifacts expressing properties to be verified by defining a graphical template language. It also allows verification of the models against the properties and visualization of the verification results.

Lodderstedt et al. (SecureUML) propose an approach to model RBAC policies for model-driven systems [38]. It also provides additional support to specify authorization constraints related to the state of the system. In contrast to other approaches, SecureUML proposes a general schema for building systems by combining design modeling languages with a security modeling language; it does not fix one particular design modeling language. However, it only focuses on specifying RBAC model, and does not support secure code generation.

The approach of Doan et al. incorporates RBAC, MAC and lifetimes into UML for time-sensitive application design [17]. The main focus of this approach is that the process of designing and integrating security in a software application captures not only the current design state, but allows tracking the entire design evolution process via the creation and maintenance of a set of design instances over time. The design tracking allows a software/security engineer to recover to an earlier design version that satisfies specific security constraints.

Montangero et al. (For-LySa, DEGAS project) present two UML profiles to model authentication protocols [41]: the Static For-LySa profile which describes how the authentication protocol concepts (Server, Principals, Keys, Messages, etc.) can be modeled using UML class diagrams, and the For-LySa profile which models the dynamic aspects of the protocol in sequence diagrams, as well as the information needed to analyze the protocol. In order to validate a protocol, the approach For-LySa defines a specification language with semantics to write pre/post conditions and invariant constraints. This approach focuses only on the modeling of authentication protocols.

and MAC frameworks and then compose them manually to produce a hybrid access control policy [50]. It is the first approach that attempts to combine RBAC and MAC. However, it focuses only on how to model RBAC and MAC systems in UML without considering how this approach can be used to design a secure software system. In another effort [56], Ray et al. integrate RBAC and MAC policies into an application using an aspect-oriented approach to separate access control features from other application features.

Alghathbar and Wijesekera (AuthUML) propose a framework to incorporate access control policies into use case diagrams only [4]. The aim of AuthUML is analyzing (not necessarily modeling) access control policies during the early stages of the software development life cycle before proceeding to the design modeling to ensure consistent, conflict-free and complete requirements.

Popp et al. propose an extension to the conventional process of developing use case oriented processes [49]. In addition to modeling security properties with UML, this approach provides a method to incorporate these security aspects into a use case oriented development process.

Painchaud et al. (SOCLe project) provide a framework that integrates security into the design of software applications [47]. It also includes verification of UML specifications and a graphical user interface tool that allows the designer to visualize the verification results and to inspect the diagrams' execution graph. But in this approach, security policies are simply specified using the Object Constraint Language (OCL) constraints.

Ledru et al. (EDEMOI project) aim at modeling and analyzing airport security [34]. The security properties are first extracted from natural language standards and documents, and integrated into UML diagrams as stereotypes in a UML profile. The UML specifications are then translated into formal models for verification purposes. This approach is not general enough to be used for software development. Epstein and Sandhu's work is one of the first approaches that investigate the use of UML to model RBAC policies [18]. However, it is limited to only one specific RBAC model which is the RBAC Framework for Network Enterprises (FNE). The FNE model contains seven abstract layers that are divided in two different groups. This approach allows to present each of the FNE model's layers using UML notation by defining new stereotypes. This approach can assist the "role engineering" process, however, it does not include subtle properties of RBAC such as separation of duty constraints and it does not provide a method for deriving roles. In addition, there is no formal semantics for verifying UML models.

Ahn and Shin propose a technique to describe the RBAC model with three views: static view, functional view and dynamic view using the UML diagrams [1]. This approach focuses only on the way that UML elements can be used to model RBAC policies rather than taking a larger view of examining secure software design. It does not provide a systematic modeling approach that can be used by developers to create applications with RBAC models.

Brose et al. extend UML models to support the automatic generation of access control policies for CORBA-based systems [9]. They specify both permissions and

prohibitions on accessing system's objects since the analysis phase in use case diagrams. The UML design is used to generate an access control policy in VPL (View Policy Language) that is deployed together with the CORBA application.

Vivas et al. propose an approach for the development of business process-driven systems where security requirements are integrated into the business model [61]. Security requirements are first stated at the high level of abstraction within a functional representation of the system given by UML diagrams using tagged values. Next, the UML specification is translated into XMI representation that allows automatic processing of the specification. Finally, the resulting specification is translated into a formal notation for consistency checking, verification, validation and simulation.

Fernandez provides a methodology to build secure systems using patterns [19]. The main idea of this approach is that security principles should be applied through the use of security patterns at every stage of the software development process (requirements, analysis, design and implementation stages). At the end of each stage, audits are performed to verify that the security policies are being followed.

Chan and Kwok [12] propose a design methodology for e-commerce systems to specify design details for three processes: Risk, Engineering, and Assurance, which represent the main areas of security engineering in the systems security engineering capability maturity model (SSE-CMM) on which this methodology is based. A security design pattern is used to specify each of those processes.

### 2.4 Verification of UML Design Models

During the recent years, many techniques have been proposed for verification and validation of UML diagrams, e.g., static analysis, theorem proving, model checking, etc. Those approaches have different strengths in different areas. Since model checkers provide automated tools for verification of a given behavioral property, they have often been used in behavioral diagrams to ensure whether the system meets the predefined requirements. Though, most of the proposed approaches target only activity and state machine diagrams [10, 21, 22, 28, 33, 39, 53, 55]. There are some approaches targeting sequence diagram [3, 60]. However, when it comes to interactions, it is important to analyze the type of messages being exchanged, as well as their source and destination, and their send and receive events. The proposed approaches targeting sequence diagram mainly focus on getting a formal representation of interactions, and they miss a well-defined methodology to analyze all these important elements. Moreover, those works either do not take into account UML combined fragments (components newly introduced to UML 2.0 that allow designers to describe a number of traces in a compact and concise manner [44]) or their semantics models are not in accordance with the semantics defined in the UML 2.0 specification.

Alawneh [3] proposes a framework for V&V of some popular UML diagrams (Class, State Machine, Activity and Sequence diagrams). In this approach, a semantics model called configuration transition system (CTS) is extracted from behavioral diagrams and then translated into NuSMV [14] code. This approach allows V&V of behavioral models against properties written in computational tree logic (CTL). Even though

this approach is dealing with some UML 2.0 sequence diagrams elements, the proposed semantics model is not in full accordance with the standard semantics specified in [44] due to the lack of send and receive events. As a consequence, some traces cannot be captured in this approach.

Leue [35] presents a detailed description of the translation of Message Sequence Charts (MSCs) [26] into PROMELA. Since the MSCs are the basis of UML sequence diagrams [52], many of the proposed translation decisions can be applied to sequence diagrams. However, the proposed approach deals only with the basic components and decisions; consequently, its PROMELA representation of MSCs does not cover the behavior of combined fragments introduced in UML 2.0 interactions diagrams.

Amstel [59, 60] proposes a set of techniques to improve the quality of sequence diagrams. One of these techniques is trace analysis by using model checkers. To obtain PROMELA code from sequence diagrams, this technique provides a translation scheme that is based on [35]. However, since this approach is intended to UML 1.5 diagrams, combined fragments are not taken into account. In addition, the authors do not propose a mechanism to use source and destination for writing formal properties.

In [16,30,53], they determine whether a given interaction can be successfully executed in a system where the behavior is specified using state machines. These works assume sequence diagrams as properties to be verified.

## Chapter 3

# Property Specification for UML

## Design

In this chapter we investigate properties specification for UML design. It starts with the detail explanation of the main adopted approaches in the area. Section 3.1 presents how to specify properties using the existing UML artifacts. Section 3.2 and section 3.3 show how to define properties by extending the UML meta-language and creating a new meta-language, respectively. In the section 3.4, we compare these approaches through a usability discussion. Finally, in section 3.5, we address the problems of the existing approaches by providing our new mechanism to specify properties.

From the state of the art presented in the previous chapter, three main UML artifacts can be used for property specification: (1) stereotypes and tagged values, (2) OCL, and (3) behavior diagrams. In addition, two other approaches can be used: (1) extending the UML metalanguage or (2) creating a new metalanguage. Table

2 summarizes the use of these approaches to specify security requirements by the contributions presented previously.

| Contributions           | Stereotypes and | OCL      | Behavior | Extending UML | New meta- |

|-------------------------|-----------------|----------|----------|---------------|-----------|

|                         | tagged values   |          | diagrams | metalanguage  | language  |

| UMLSec [27]             | <b>√</b>        |          |          |               |           |

| P. Mariscal et al. [48] | ✓               |          |          | <b>√</b>      |           |

| SecureUML [38]          | ✓               | <b>V</b> |          |               | ✓         |

| Zisman [64]             |                 |          | ✓        |               |           |

| SOCLe [47]              |                 | <b>1</b> |          |               |           |

| For-LySa [41]           | ✓               |          |          |               |           |

| Epstein and Sandhu [18] | ✓               |          |          |               |           |

| Brose et al. [9]        | ✓               |          |          |               |           |

| Ahn and Shin [1]        |                 | <b>V</b> |          |               |           |

| AuthUML [4]             |                 | <b>✓</b> |          |               |           |

Table 2: The Use of Security Specification Approaches in the State of the Art

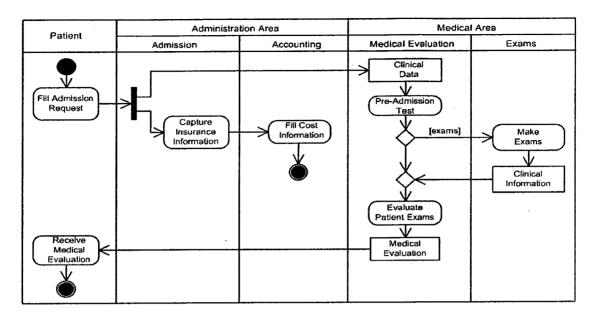

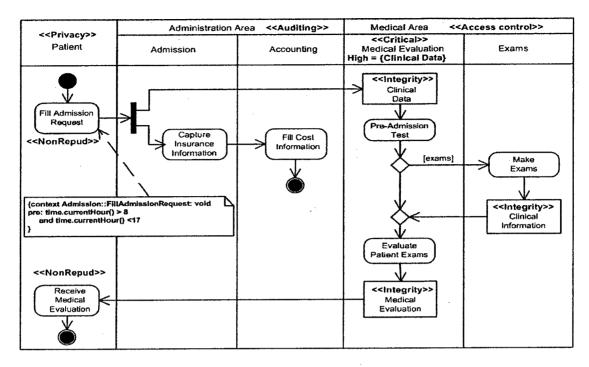

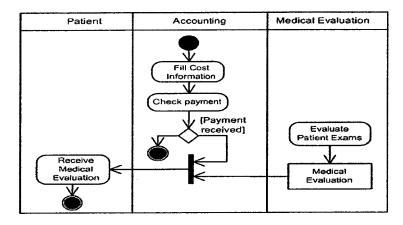

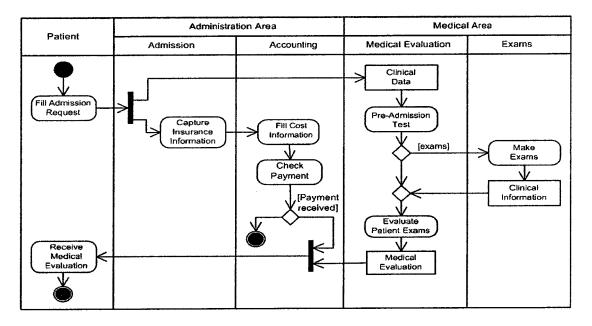

In the following, we present each of those approaches and explain how it can be used for security specification. The activity diagram of Figure 12 will be used throughout the following subsections to show how security requirements can be specified for UML design. The diagram specifies the behavior related to the admission of patients in a medical institution. This example is a simplified version of the business process used in [51]. The activity diagram consists of three main partitions: (1) Patient who starts the activity by filling out an admission request, (2) Administration areawhere insurance and cost information are collected, and (3) Medical area which is responsible for admission tests, exams, medical evaluations and sending the medical results to the patient.

Figure 12: An Activity diagram: admission of patients in a medical institution

## 3.1 Property Specification Using UML Artifacts

#### 3.1.1 Stereotype and Tagged Values

Stereotypes are provided as a mechanism for extending the UML meta-language. Therefore, a stereotype is considered as a user-defined meta-element. Its structure matches the structure of an existing UML meta-element which is referred to as "base class". In that sense, a stereotype represents a subclass (subtype) of the base class. It has the same form but with a different intent. A stereotype can have tagged values used to define the additional information needed to specify the new stereotype intent. Besides, constraints can be defined on both the base class attributes as well as the tagged values. Code generators and other tools, such as those used for verification and validation, reserve special treatment to stereotypes.

Use for Property Specification: System requirements are specified by attaching stereotypes along with their associated tagged values to selected elements of the design (e.g., subsystems, classes, etc.). Thus a specific profile should be created by some expert for the specification of these stereotypes. The compiler used to parse UML diagram is then modified such that it can read and interpret the stereotypes annotating the design. This interpretation consists in generating a formal representation of the property corresponding to the used annotation. This requirement is generated on the basis of the intent of the expert while taking into consideration the specificities of each design. In addition, a formal semantics is associated with the design. Then, the formal properties together with the formal semantics are provided as inputs to a verification tool (usually a model checker). The result of verifying the property on the design is translated into some representation that any non-expert developer can understand. Some stereotypes are parameterized over the adversary type. These stereotypes are used to specify security properties that need to be verified against a specification of an attacker (adversary). Fair exchange, secrecy, and authenticity are examples of these properties. The adversary type specifies the adversary's computation capabilities and initial knowledge. Figure 13 shows how stereotypes can be used to specify security requirements on the UML design of Figure 12. The used stereotypes are Privacy, Auditing, Access Control, Critical, Integrity, and Non Repudiation. For example, the stereotype Privacy is attached to the Patient partition to specify that unauthorized disclosure of sensitive information about the patient is not permitted.

Figure 13: An example of specifying properties using stereotypes

### 3.1.2 Object Constraint Language (OCL)

The OCL is a formal language used to express constraints over UML diagrams. These constraints mainly specify those conditions that must be satisfied by the system being modeled. The OCL is mainly used to specify application specific requirements for UML models. In addition it is used to specify invariants of the UML meta-language. More precisely, the main purposes for which OCL can be used are the followings: (1) To specify invariants on classes and types in the meta-language, (2) to specify type invariant for Stereotypes, (3) to describe pre and post conditions on operations and methods, and (4) to describe guards [43].

Use for Property Specification: Since OCL is a language for constraints specification, it is natural to be used for property specification. OCL has been used for

security specification following three main directions. First, for the security profiles extending UML for security specification, OCL is used to define constraints on elements described by stereotypes and tagged values. Second, for those stereotypes used for the specification of access control properties, OCL can be used by the designer to define access control constraints (pre conditions and authorization guards). Third, some OCL extensions [63] allow the specification of temporal logic formulas and thus are used to specify security requirements in temporal logics, e.g., LTL, CTL, etc. Figure 13 shows how OCL can be used to specify a constraint on the action "Fill admission request". This constraint restricts the execution of this action to the working hours. This will protect the system from malicious use during nights. The condition start by specifying its context, i.e., the method on which it is applied, which is the method FillAdmissionRequest of the class Admission. Then the constraint specifies the pre-condition to be satisfied before executing the controlled method.

#### 3.1.3 Behavior Diagrams

Behavior diagrams are UML diagrams used to depict the behavior features of the system under design. These include activity, state machine, and use case diagrams as well as four interaction diagrams.

Use for Property Specification: Behavior diagrams can be used for property specification in two ways. The First one is to specify the behavior that 'MUST' be observed by the system and the second one is to specify the behavior that 'MUST NOT' be observed by the system. The later has been investigated by some recent