## FABRICATION AND MAGNETOTRANSPORT STUDIES OF Bi<sub>2</sub>Se<sub>3</sub> TOPOLOGICAL INSULATOR TRANSISTORS

JAMES PORTER

A thesis in The Department of Physics

Presented in Partial Fulfillment of the Requirements For the Degree of Master of Science (Physics) Concordia University Montréal, Québec, Canada

> September 2015 © James Porter, 2015

#### CONCORDIA UNIVERSITY School of Graduate Studies

This is to certify that the thesis prepared

## By: James Porter Entitled: Fabrication and Magnetotransport Studies of Bi<sub>2</sub>Se<sub>3</sub> Topological Insulator Transistors

and submitted in partial fulfillment of the requirements for the degree of

#### Master of Science (Physics)

complies with the regulations of this University and meets the accepted standards with respect to originality and quality.

Signed by the final examining commitee:

| <br>_ A. Champagne (Chair)      |

|---------------------------------|

| <br>_ M. Frank (Examiner)       |

| <br>_ T. Vo Van (Examiner)      |

| <br>_ A. Champagne (Supervisor) |

Approved \_\_\_\_\_\_ Chain of Demonstration Cracks

Chair of Department or Graduate Program Director

\_\_\_\_\_ 20 \_\_\_\_\_

Andre Roy, Dean Faculty of Arts and Sciences

#### Abstract

#### Fabrication and Magnetotransport Studies of Bi<sub>2</sub>Se<sub>3</sub> Topological Insulator Transistors

James Porter

Topological insulators (TI) are a unique class of materials that can support 2dimensional (2D) metallic states on the surfaces of 3-dimensional insulating crystals. These 2D surface states are predicted to be spin polarized and topological, leading to potential applications in spintronics and quantum computing. While signs of surface transport have recently been observed in magneto transport experiments, many applied and theoretical questions remain to produce robust Bi<sub>2</sub>Se<sub>3</sub> transistors. We first present the fabrication methods we developed to create high quality devices. We address the first main road block the community is facing to explore topological charge transport: making low resistance contacts to TI's. Using our devices, we then explore magneto transport. At cryogenic temperatures we observe the classical Hall effect as well as Shubnikov-de Haas oscillations consistent with the presence of Landau levels and surface transport in Bi<sub>2</sub>Se<sub>3</sub> thin crystals. We focus on a thin crystal made of two regions with two thicknesses. We use our data to address the second major roadblock faced by the TI community: bulk-defect conduction versus surface transport. We discuss the evidence we have to support 2D surface transport in our devices, and the outlook for the exploration of the topological aspects of these surface states.

## Acknowledgments

Many thanks to the pioneers of the Champagne group: Vahid, Serap, Joshua and Andrew for paving the way to success. I would like send a warm thank you to my supervisor Alex for mentoring me through this project, without whose skills and insight this would never have been possible. Finally, endless thanks to my family and friends who encouraged me every step of the way, this is for you.

## Contents

#### List of Figures

| 1        | Introduction |         | 1                                                                                                          |    |

|----------|--------------|---------|------------------------------------------------------------------------------------------------------------|----|

|          | 1.1          | Introd  | luction to thin Bismuth Selenide topological insulators $\ldots$ .                                         | 2  |

|          | 1.2          | Summ    | hary of our fabrication and transport results in $Bi_2Se_3$                                                | 7  |

|          | 1.3          | Struct  | cure of thesis                                                                                             | 8  |

| <b>2</b> | Fab          | ricatio | on of ultra-thin $\mathbf{Bi}_2\mathbf{Se}_3$ transistors                                                  | 12 |

|          | 2.1          | Coord   | linate grid on $Si/SiO_2$ substrates $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$             | 14 |

|          | 2.2          | Depos   | sition of thin $Bi_2Se_3$ crystals $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 15 |

|          |              | 2.2.1   | Mechanical Exfoliation                                                                                     | 15 |

|          |              | 2.2.2   | Vapor-Solid growth of $Bi_2Se_3$ nanocrystals $\ldots \ldots \ldots \ldots$                                | 17 |

|          | 2.3          | Struc   | tural characterization of deposited thin films                                                             | 20 |

|          |              | 2.3.1   | Optical microscope characterization                                                                        | 21 |

|          |              | 2.3.2   | Atomic Force Microscope measurements                                                                       | 22 |

|          | 2.4          | Makin   | ng electrical contacts to ultrathin topological $\mathrm{Bi}_2\mathrm{Se}_3$ crystals $\ . \ .$            | 23 |

|          |              | 2.4.1   | Electron beam lithography of micron-sized contacts                                                         | 24 |

|   |      | 2.4.2 Metal contact evaporation and device packaging                                      | 28 |

|---|------|-------------------------------------------------------------------------------------------|----|

|   | 2.5  | Electronic measurement setup and cryostat                                                 | 32 |

| 3 | Cha  | $ {\bf aracterizing \ and \ optimizing \ electrical \ contacts \ to \ thin \ Bi_2Se_3 } $ |    |

|   | crys | stals                                                                                     | 38 |

|   | 3.1  | Brief overview of electron transport in $Bi_2Se_3$ transistors $\ldots \ldots$            | 40 |

|   |      | 3.1.1 Background on Bismuth Selenide transistors                                          | 41 |

|   |      | 3.1.2 $Bi_2Se_3$ transistors: recent results and challenges                               | 45 |

|   | 3.2  | Quantifying the impact of surface oxidation on contact resistance $\ .$ .                 | 51 |

|   | 3.3  | Contact resistance vs microfabrication techniques                                         | 60 |

|   | 3.4  | Gating $Bi_2Se_3$ transistors and thickness effects $\ldots \ldots \ldots \ldots$         | 65 |

| 4 | Mag  | gneto-transport in $\mathbf{Bi}_2\mathbf{Se}_3$ and evidence for topological surface      |    |

|   | stat | es                                                                                        | 68 |

|   | 4.1  | Selected devices and classical Hall behaviour                                             | 70 |

|   |      | 4.1.1 High quality $Bi_2Se_3$ transistors                                                 | 71 |

|   |      | 4.1.2 Classical Hall effect                                                               | 73 |

|   |      | 4.1.3 Extracting the Hall density                                                         | 75 |

|   | 4.2  | Testing for localization effects: the quantum diffusive regime $\ldots$ .                 | 79 |

|   | 4.3  | Shubnikov-de Haas oscillations on the surface of $\mathrm{Bi}_2\mathrm{Se}_3$ thin films  |    |

|   |      | transistors                                                                               | 85 |

|   |      | 4.3.1 Gateable Shubnikov de Haas density                                                  | 86 |

|   |      | 4.3.2 Two different contact geometries: $R_{xx}$ vs $R_{xy}$                              | 90 |

|          | 4.4          | Fabry-Perot                                                                                     | 91  |

|----------|--------------|-------------------------------------------------------------------------------------------------|-----|

| <b>5</b> | Con          | clusion                                                                                         | 96  |

|          | 5.1          | Main results                                                                                    | 97  |

|          | 5.2          | Outlook: suspended $Bi_2Se_3$ devices $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 101 |

| Aj       | Appendices 1 |                                                                                                 | 112 |

|          | .1           | Deriving the density of states                                                                  | 113 |

## List of Figures

| 1.1.1 Bandstructure in solids                                                              | 3  |

|--------------------------------------------------------------------------------------------|----|

| $1.1.2 \operatorname{Bi}_2\operatorname{Se}_3$ Bandstructure                               | 4  |

| $1.1.3 \operatorname{Bi}_2\operatorname{Se}_3$ crystal structure                           | 6  |

| 1.2.1 R vs B in thin film $Bi_2Se_3$                                                       | 9  |

| 1.2.2 OM of fabricated Hall bar device                                                     | 10 |

| 2.0.1 Pre patterned Gold electrodes on a thick $Bi_2Se_3$ flake $\ldots$ $\ldots$ $\ldots$ | 13 |

| 2.2.1 VS Growth                                                                            | 18 |

| 2.2.2 VS Growth Ribbons                                                                    | 19 |

| 2.2.3 Nanoribbon AFM                                                                       | 19 |

| 2.3.1 Optical Characterization of thick flakes                                             | 21 |

| 2.3.2 AFM of thin $Bi_2Se_3$ flake                                                         | 24 |

| 2.4.1 Device Diagram                                                                       | 25 |

| 2.4.2 EBL preparation                                                                      | 26 |

| 2.4.3 EBL defined Hall bar transistor                                                      | 27 |

| 2.4.4 Thermal evaporator                                                                   | 28 |

| 2.4.5 Gold and Chromium source materials                                                   | 30 |

| 2.4.6 Crystal thickness monitor                                                                                                           | 30 |

|-------------------------------------------------------------------------------------------------------------------------------------------|----|

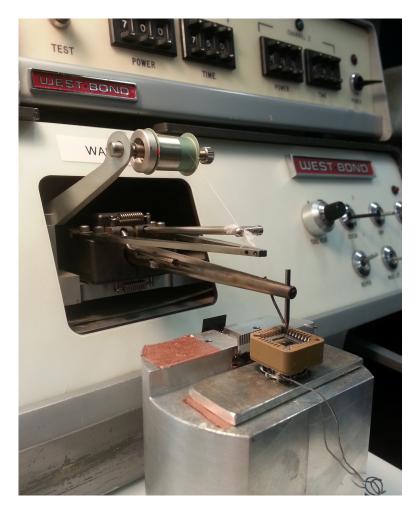

| 2.4.7 Wirebonder                                                                                                                          | 31 |

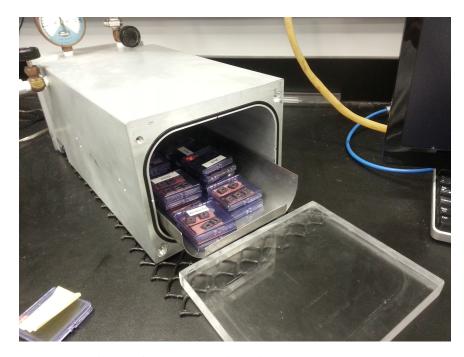

| 2.4.8 Vacuum Storage chamber                                                                                                              | 32 |

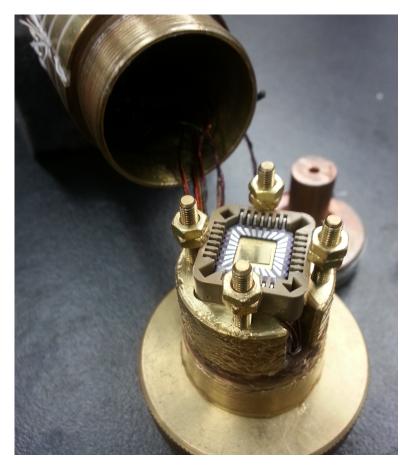

| 2.5.1 Sample measurement probe                                                                                                            | 33 |

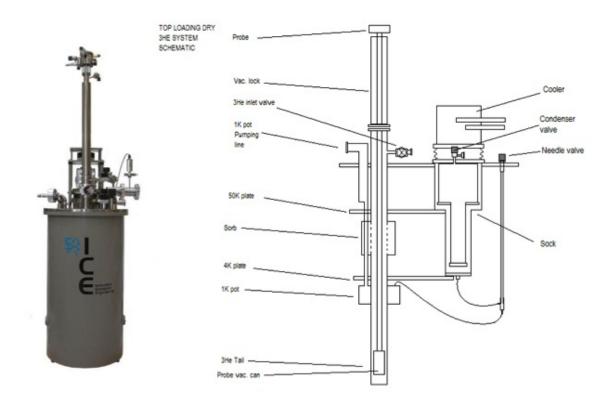

| 2.5.2 Helium-3 cryostat                                                                                                                   | 35 |

| 2.5.3 2-point Circuit setup                                                                                                               | 37 |

| 2.5.4 4-point Circuit setup                                                                                                               | 37 |

| $3.1.1 \operatorname{Bi}_2\operatorname{Se}_3$ crystal structure and FBZ $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 42 |

| 3.1.2 TI band structure                                                                                                                   | 44 |

| 3.1.3 EBL defined Hall bar on thin-film $BI_2Se_3$                                                                                        | 48 |

| 3.1.4 Thin-film transport: gate leakage                                                                                                   | 48 |

| 3.1.5 Thick-film bias sweep                                                                                                               | 50 |

| 3.1.6 Thick-film gate sweep                                                                                                               | 51 |

| 3.2.1 Oxidation of $Bi_2Se_3$                                                                                                             | 52 |

| 3.2.2 XPS Spectra of oxidation                                                                                                            | 54 |

| 3.2.3 Pre patterned 4-point device                                                                                                        | 55 |

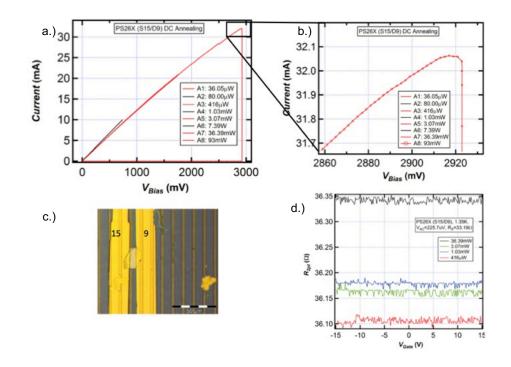

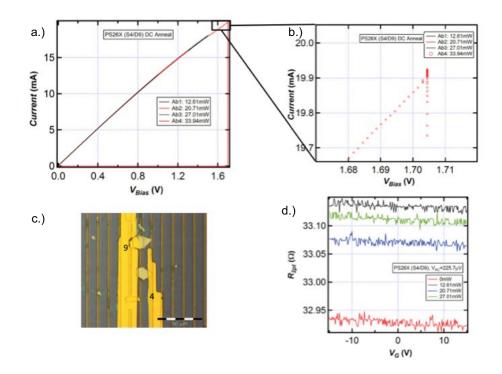

| 3.2.4 Low-exposure bias sweeps                                                                                                            | 55 |

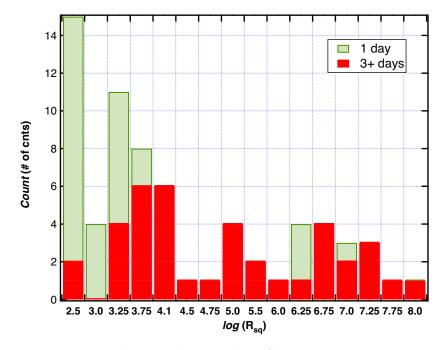

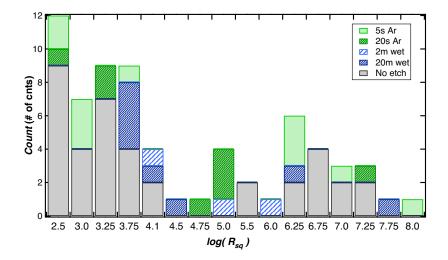

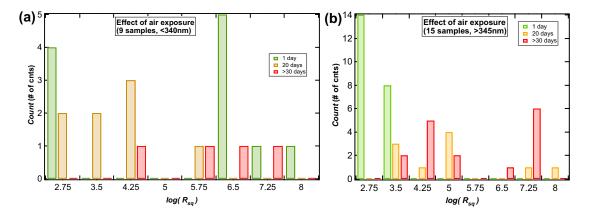

| 3.2.5 Air exposure vs contact resistance histogram                                                                                        | 58 |

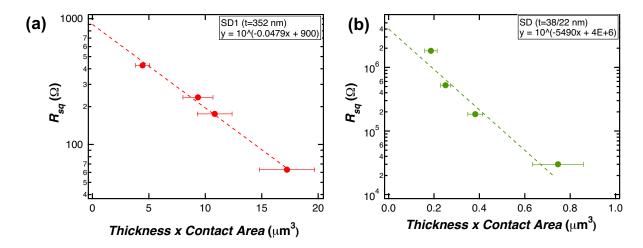

| 3.2.6 Contact resistance vs thickness                                                                                                     | 59 |

| 3.3.1 Argon etching the $Bi_2Se_3$ surface $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                        | 61 |

| 3.3.2 Contact etching a 2-point device                                                                                                    | 62 |

| 3.3.3 Contact resistance vs Fabrication techniques histogram                                                                              | 64 |

| 3.3.4 Contact resistance vs air exposure time                                                | 64 |

|----------------------------------------------------------------------------------------------|----|

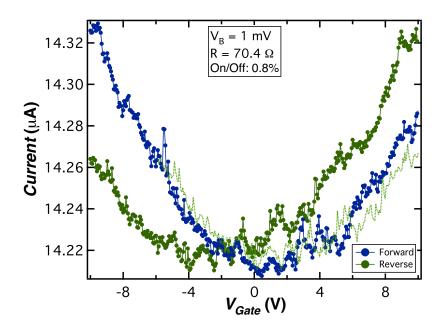

| 3.4.1 Low-R sample gatesweep                                                                 | 66 |

| 4.1.1 Chapter 4 sample set                                                                   | 72 |

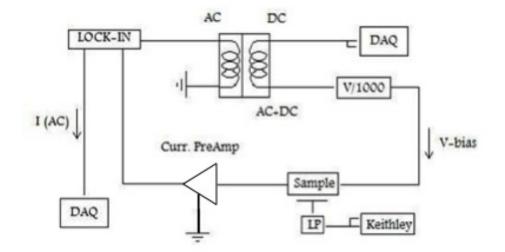

| 4.1.2 4-point AC + DC measurement circuit $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 73 |

| 4.1.3 Hall Effect                                                                            | 74 |

| 4.1.4 4-point magnetoresistance: classical Hall Effect                                       | 76 |

| 4.1.5 Magnetoresistance in other samples                                                     | 77 |

| 4.1.6 R vs B for varying gate voltages                                                       | 77 |

| 4.1.7 Nonlinear magnetoresistance in a $Bi_2Se_3$ thin film $\ldots \ldots \ldots \ldots$    | 79 |

| 4.2.1 Ballistic and diffusive regimes                                                        | 81 |

| 4.2.2 WAL vs WL effect                                                                       | 81 |

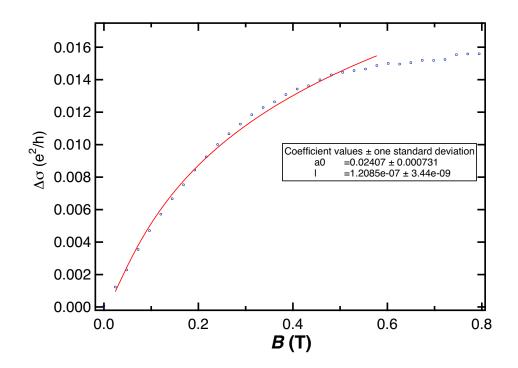

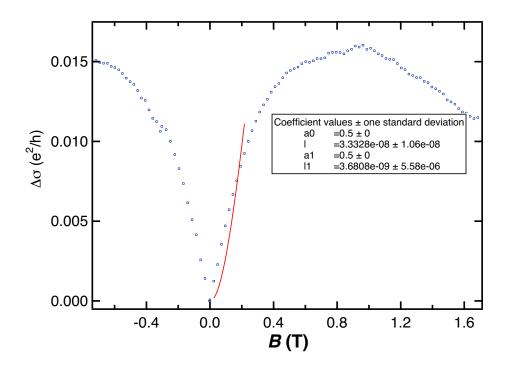

| 4.2.3 Fitting magnetoresistance data to HLN model                                            | 83 |

| 4.2.4 Fitting magnetoresistance data to HLN model - 2                                        | 84 |

| 4.3.1 SdH effect                                                                             | 87 |

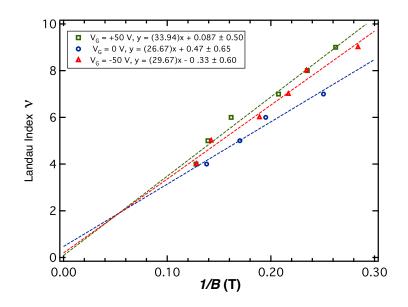

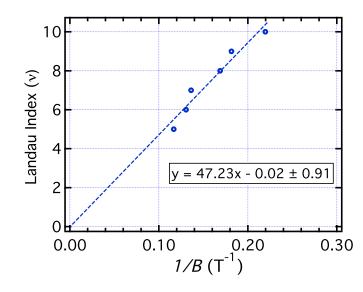

| 4.3.2 Landau fan diagram for thin film $Bi_2Se_3$                                            | 88 |

| 4.3.3 Landau fan diagram for varying gate voltages                                           | 89 |

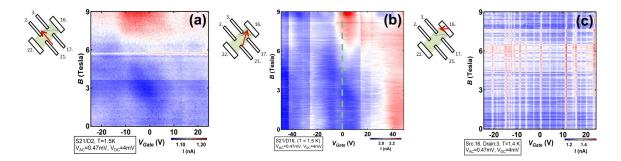

| 4.3.4 Landau filling fraction assignments                                                    | 90 |

| 4.3.5 Landau fan diagram for charge rearrangement                                            | 91 |

| 4.4.1 Current peaks in gatesweep                                                             | 92 |

| 4.4.2 2D fringe mapping                                                                      | 95 |

| 5.1.1 EBL defined Hall bar device                                                            | 98 |

| 5.1.2 Lan fan diagram vs gate voltage                                                        | 99 |

| 5.2.1 Magnetotransport in suspended samples | 102 |

|---------------------------------------------|-----|

| 5.2.2 Magnetotransport vs temperature       | 103 |

| 5.2.3 Annealing suspended samples           | 104 |

| 5.2.4 Annealing suspended samples           | 105 |

| .1.1 Sphere in k-space                      | 113 |

### Chapter 1

## Introduction

Over the last several years a new class of materials known as topological insulators (TI's) has been studied both theoretically [1, 3], and experimentally [39, 16]. The unique quality of a three-dimensional topological insulator is that they can support 2-dimensional (2D) metallic states on their surfaces while their bulk is an insulating crystal [28]. Bismuth Selenide (Bi<sub>2</sub>Se<sub>3</sub>), long known for its thermoelectric properties, was only recently fully investigated in thin films, is selected as the TI material for our studies due to its large bandgap of 0.3 eV [15], which makes it more likely that its topology is robust against disorder. Optical studies have probed the surface states of Bi<sub>2</sub>Se<sub>3</sub>, and confirmed the Dirac surface dispersion [21]. Experimental electron transport in topological Bismuth Selenide is still waiting to take fully off. Much of the material's potential remains to be unlocked due to fabrication difficulties and material impurites. Predicted to be spin polarized, the 2D surface states (see Figure 1.1.1(b)) could have applications in spintronics and quantum computing [15]. There

are several competing methods to make  $Bi_2Se_3$  thin films, such as crystal growth and mechanical exfoliation. We present the fabrication methods and measurement techniques required to explore the magneto transport properties of nanometer scale  $Bi_2Se_3$  samples.

The structure of this chapter is as follows: section 1.1 gives a short introduction to topological insulators, in particular  $Bi_2Se_3$ , and section 1.2 gives an overview of the fabrication processes we developed, transistor specifications we could produce and the the magneto transport properties observed in our fabricated devices.

## 1.1 Introduction to thin Bismuth Selenide topological insulators

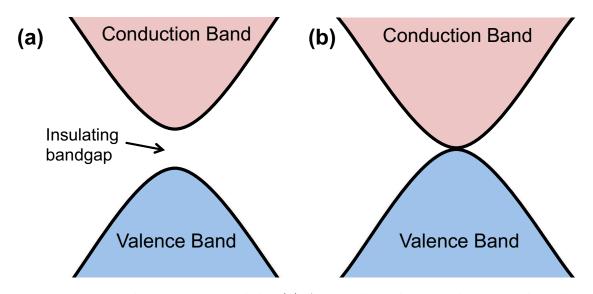

Topological insulators are characterized by an insulating bulk band gap and protected surface or edge states [28, 4, 3]. To show how these surface states come about, we first explain what how topology of a material is defined. Figure 1.1.1 (a) shows the band structure of a trivial insulator with a large insulating bandgap. As there are no points at which the valence and conduction bands meet this is referred to as a  $Z_0$ topology. In panel (b) the conduction and valence bands meet and there is a finite density of states at all energies. In this case, one point of crossing is referred to as a  $Z_1$  topology.

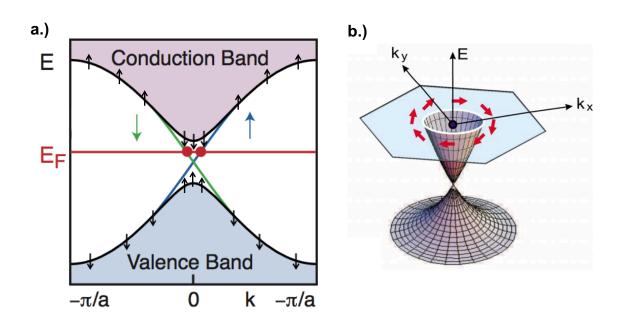

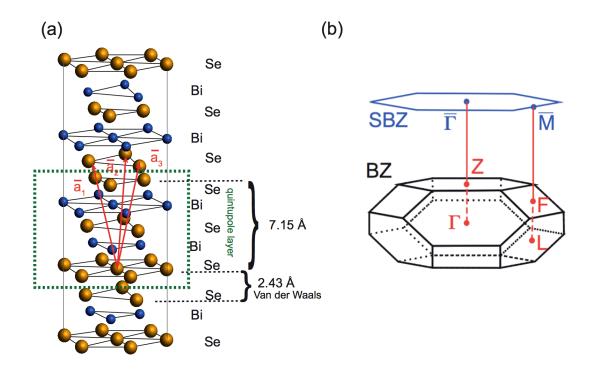

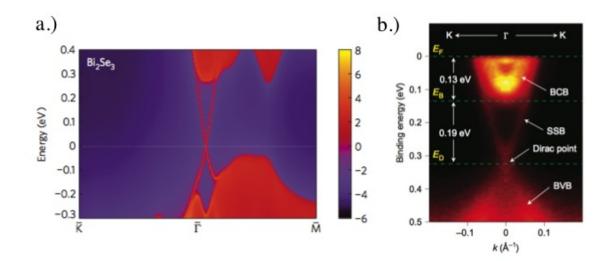

Topological insulator materials exhibit a strong spin-orbit interaction (SOI), arising from the coupling of an electron's magnetic spin to the magnetic field setup by the motion of the electron around it's orbital. This coupling can lead to the bending of energy bands in solids, which is known as the Rashba Effect [31, 33]. In topological insulators and particularly  $Bi_2Se_3$ , the SOI is so strong that the valence and conduction energy bands will actually switch places. Figure 1.1.2 (a) shows the band structure of a topological insulator, in which the valence and conduction band have two crossing points or a  $Z_2$  topology. The valence and conduction bands are inverted (switch places) near the  $\Gamma$ -pt in reciprocal momentum space, creating topologically protected surface states (straight lines in Figure 1.1.2 (a)) within a bulk bandgap [28, 3]. The black arrows represent the conduction (up) and valence (down) bands [24]. The insulating bandgap opened by the band inversion in the material must close at the boundaries in order to re-open to the vacuum bandgap, which is topologically different in that it has a  $Z_0$  band structure of a trivial insulator.

Figure 1.1.1: Band structure in solids: (a) A trivial insulator with  $Z_0$  topology has a large insulating energy gap where no conduction occurs, (b) When the valence and conduction bands meet, a  $Z_1$  crossing occurs resulting in metallic conduction states

Figure 1.1.2: Band Structure of a topological insulator. (a) Band inversion results in topologically protected surface states in a bulk bandgap (green and blue lines). Figure adapted from *Hasan* et al. [28] (b) Spin-momentum locking on a topological surface state. Figure from *Hsieh* [3].

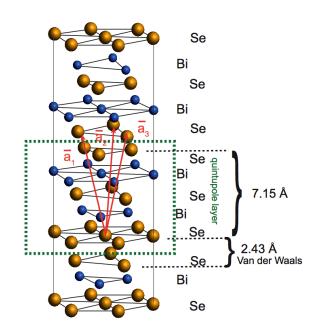

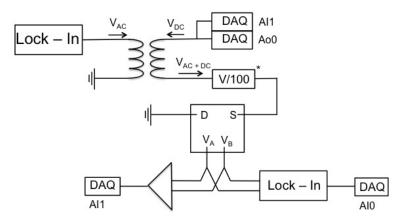

At the surfaces (i.e. boundaries) of the material we therefore have a nonzero density of states, represented by the conducting surface states which are protected by the topology of the band inversion. As a result of the strong SOI, surface carriers are spin-polarized due to a locking of spin to momentum, shown in Figure 1.1.2 (b). The spin of surface carriers (red arrows) related to their position in k-space. With a single cone on each surface, up and down spin states are prevented from collapsing due to their large separation distance setup by an insulating bulk. Bi<sub>2</sub>Se<sub>3</sub> is a layered crystal made up of alternating planes of Bi and Se trigonal lattice. Figure 1.1.3 shows how adjacent planes bond together 5 at a time to form so called quintuple layers (QL). Bonded together by Van der Waals forces, the layers may be easily separated from one another to make thin films from the bulk material. Previously known for its thermoelectric qualities, Bi<sub>2</sub>Se<sub>3</sub> has become popular again in the search for topological surface states. Due to its large bandgap, Bi<sub>2</sub>Se<sub>3</sub> supports a robust topological state, predicted by theory to survive even up to room temperature [15].

So called parity-inversion symmetry (see section 3.1.1 for more details) leads to charge carriers having a negative effective, meaning we have band inversion (holes and electrons switch places) [26]. By tuning the Fermi Energy (using a back gate electrode) we should theoretically be able to observe scatter free spin-polarized surface states up to room temperature. In practice it has proven impossible to obtain pure surface transport without contamination from bulk defect mediated transport. Impurities in the bulk such as Se vacancies contribute charge carriers which may overwhelm the surface transport. Similar to many other topological insulator materials,  $Bi_2Se_3$

Figure 1.1.3: The crystal structure of bismuth selenide is made of planar trigonal lattices, bonded together 5 layer stacks at a time. Figure taken from *Bianchi* et al. [26]

belongs to the chalcogenides compound group known to readily react with oxygen [36]. Oxidation leads to Se vacancies and contamination of the surface transport properties.

The  $Bi_2Se_3$  electronic Hamiltonian in equation (1), shows a parabolic energy vs momentum dispersion in the bulk, as well as a linear energy dispersion for surface carriers:

$$H(k) = -Dk^2 + v_F(k_y\hat{\sigma}_x - k_x\hat{\sigma}_y) \tag{1}$$

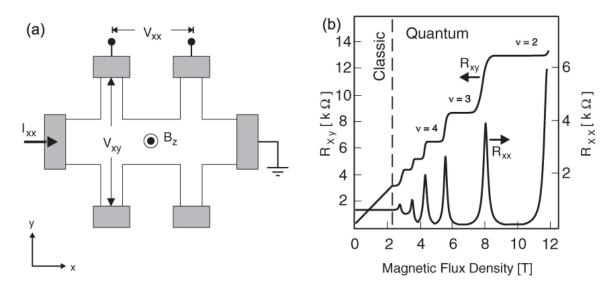

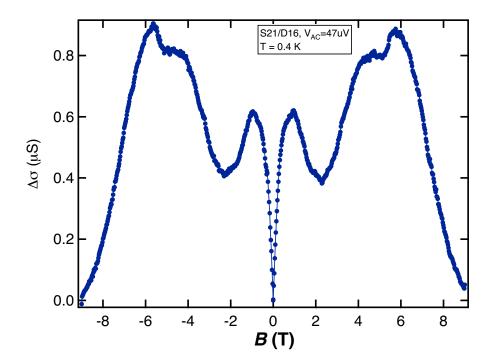

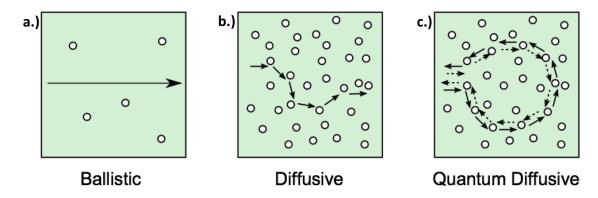

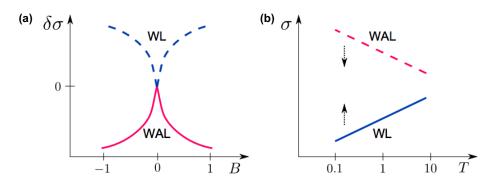

We expect to observe both the classical and quantum Hall effects in thin films at low temperatures, which would allow the measurement of the charge carrier densities pertaining to respectively the bulk and surface transport contributions. Some experiments have recently shown that thin  $Bi_2Se_3$  can exhibit a non linear magnetoresistance, in the way of Shubnikov-de Haas oscillations (not fully formed quantum Hall phases) and localization effects [10, 25, 21].

## 1.2 Summary of our fabrication and transport results in $Bi_2Se_3$

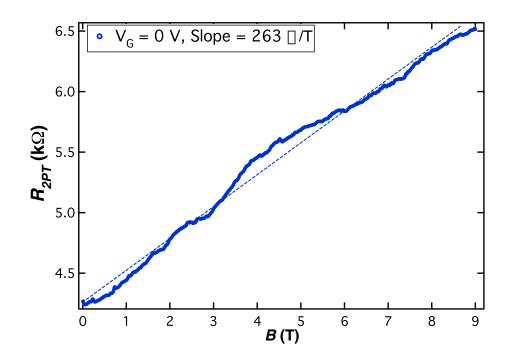

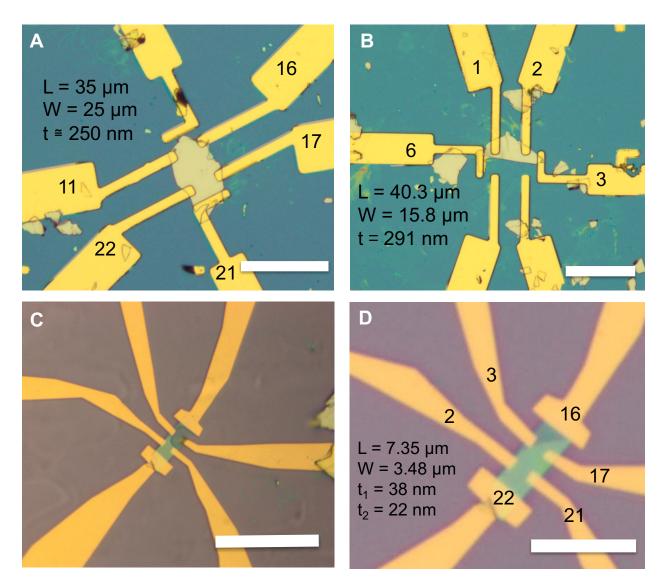

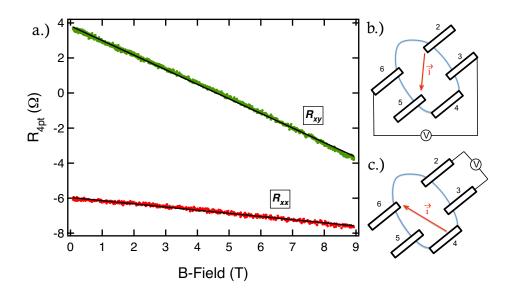

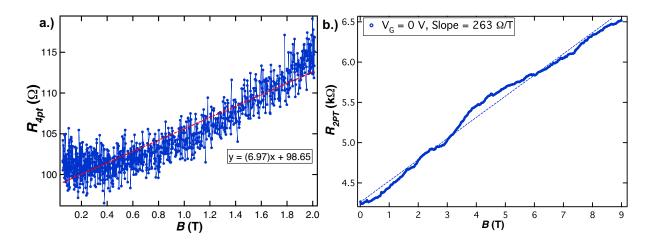

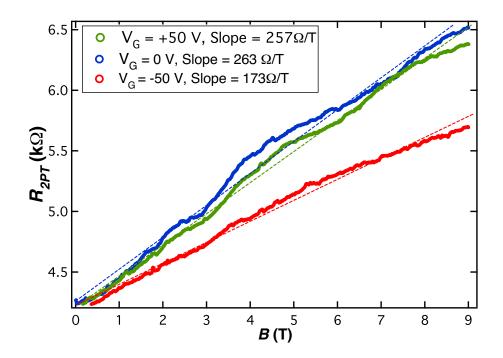

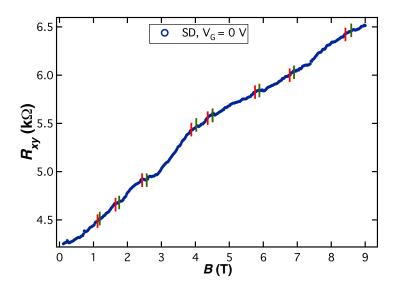

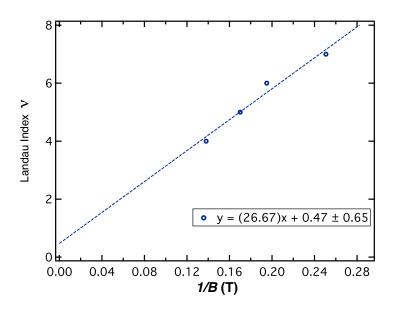

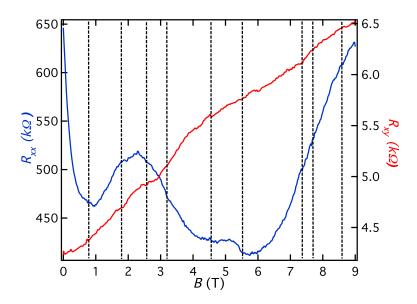

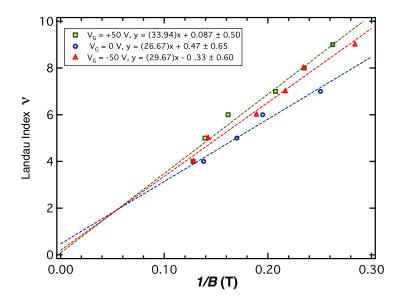

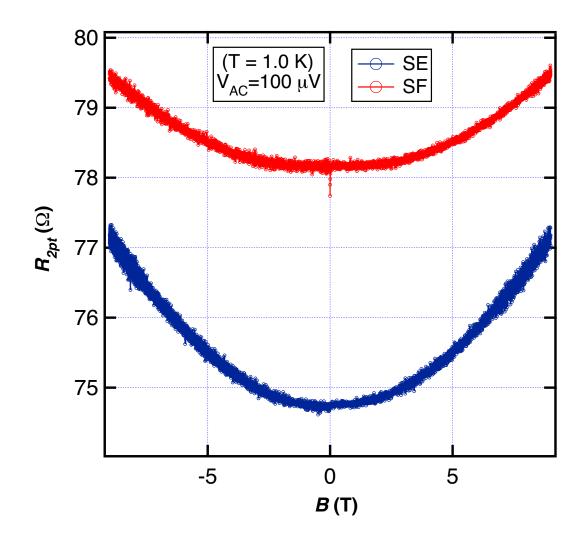

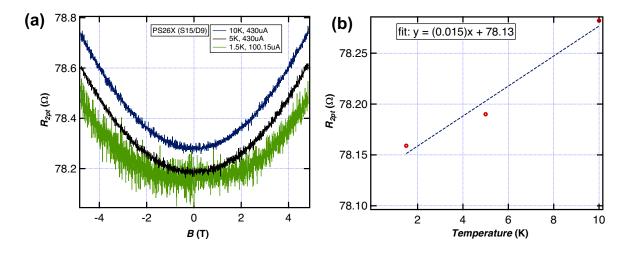

In this work we use mechanical exfoliation to produce  $Bi_2Se_3$  thin films of thicknesses ranging from several hundred microns down to a few nanometers. Low resistance contacts were fabricated after minimizing the crystal surface oxidation effects. This was done through a combination of vacuum storage, rapid fabrication and plasma etching oxidized regions under the contact areas. A catalogue of devices was created so that the fabrication methods could be evaluated and calibrated based on the measured electron transport properties of the devices. A few select devices were selected for detailed magneto transport studies as a function of crystal thickness, gate voltage, and magnetic field at cryogenic temperatures. Figure 1.2.1 shows the magnetoresistance of a 38 nm thick crystal measured at 1.5 K. The Classical Hall density,  $n_{Hall} =$  $7.48 \times 10^{14} cm^{-2}$ , is found from the slope of  $R_{xy}$  vs B. This value indicates the sample is in the electron-doped (n-doped) regime, likely due to carrier contributions from the bulk layers. On top of the linear behaviour of  $R_{xy}$  vs B, Shubnikov-de Haas oscillations are visible, indicating the formation of Landau levels. The extracted 2D charge density of  $n_{SdH}^{2D} = 6.45 \times 10^{11} \text{ cm}^{-2}$  suggests that we are measuring a combination of bulk and top layer surface transport, in parallel.

#### **1.3** Structure of thesis

Chapter 2 will present the the microfabrication techniques we developed to fabricate thin film  $Bi_2Se_3$  field effect transistors. In Chapter 3 we discuss the electron transport measurement techniques and transport data allowing the performance classification of the fabricated devices. In Chapter 4 we take an in depth look at the magneto transport behaviour of a few selected devices. The data is tested for the weak antilocalization (WAL) and Shubnikov-de Haas (SdH) effects. We demonstrate both

Figure 1.2.1: Resistance vs magnetic field in sample C shows small oscillations on top of a linear slope, indicating parallel bulk and surface transport

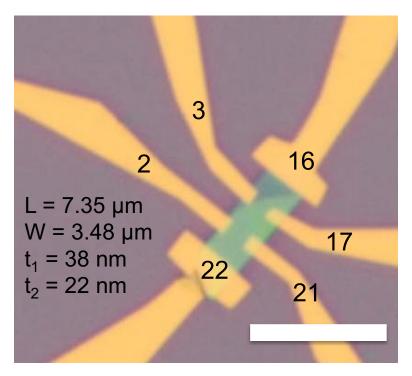

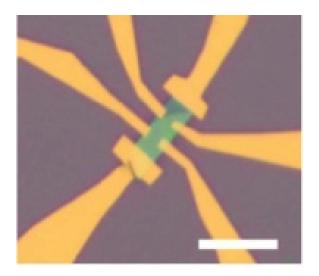

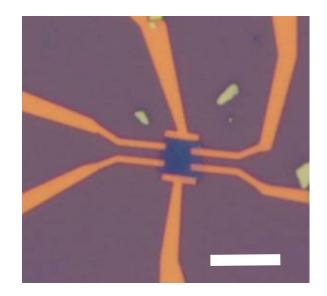

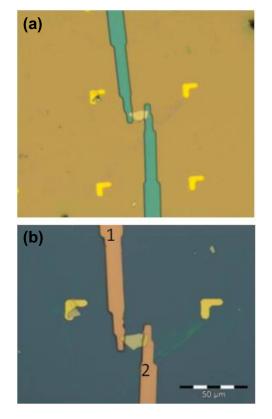

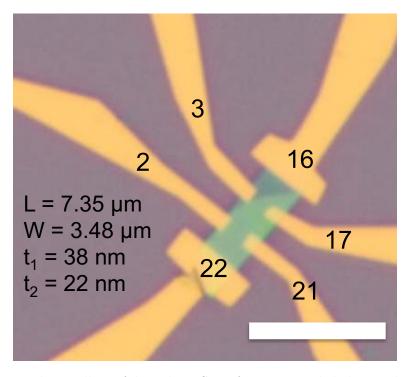

Figure 1.2.2: Mechanically exfoliated  $\rm Bi_2Se_3$  of 22 nm with lithographically defined Gold electrodes. Scale bar is 10  $\mu m.$

linear and oscillatory behaviour of transverse resistance  $R_{xy}$ , and oscillatory behaviour of the longitudinal resistance  $R_{xx}$  in magnetic fields. We extract 2D carrier densities on the order of  $10^{12}$  cm<sup>-2</sup>, indicative of surface transport. Finally, future experiments and conclusions are presented in Chapter 5.

## Chapter 2

## Fabrication of ultra-thin $Bi_2Se_3$ transistors

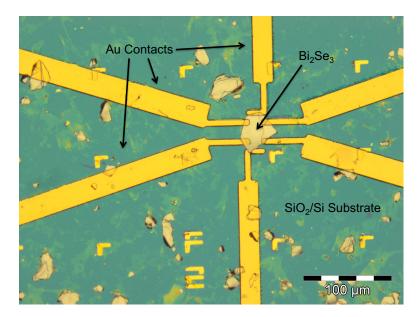

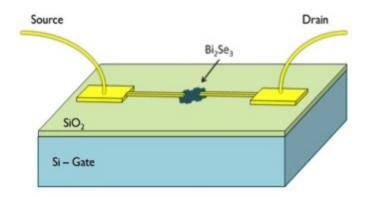

In this chapter we describe the fabrication methods we developed to make thin  $Bi_2Se_3$  transistors suited for the magneto-transport studies which will be discussed in chapters 3, 4 and 5. Figure 2.0.1 depicts a thick  $Bi_2Se_3$  flake contacted with prepatterned Gold electrodes. These devices have the standard source/drain/back gate geometry of a field effect transistor to tune the Fermi energy of the gold leads and the carrier density in the crystal.

The foremost hurdles to achieving transport will be synthesizing thin films with a uniform crystal surface, making low resistance contacts including an efficient gate electrode without current leakage. We make 2-point and 4-point contact geometries on crystals of varying thickness, from hundreds of nanometers down to the 20 nm in the ultra thin regime. We use either an etched substrate or suspension techniques

Figure 2.0.1: Photolithographically defined electrodes on a  $Bi_2Se_3$  crystal with a Hall bar geometry

to compare against on-substrate devices of varying thickness, in order to study both the effect of crystal thickness and substrate disorder. This chapter begins with the substrate preparation for and mechanical exfoliation of  $Bi_2Se_3$  thin films in section 2.1. In section 2.2 we discuss methods for obtaining  $Bi_2Se_3$  thin film structures that may used for measurement devices. In section 2.3 we outline the methods of characterizing the crystal sample for thickness and surface uniformity, using optical and atomic force microscopy. In section 2.4 we explain the photolithography and electron beam lithography techniques, as well as metal evaporation methods employed in making electrical contact to the crystal surface. Finally in section 2.5 we introduce the cryogenic fridge and measurement setup to be used in low-temperature studies of  $Bi_2Se_3$  devices at magnetic fields up to 9 Tesla. In Chapter 3 we will study the contact resistance of these devices, and in Chapter 4 we investigate the magnet-transport properties in search of 2D topological surface states.

#### 2.1 Coordinate grid on $Si/SiO_2$ substrates

The substrates used in this experiment are highly doped  $Si/SiO_2$  wafers, polished on one side on which a 300 nm thick  $SiO_2$  film is grown. We use a reactive ion etch with  $\mathrm{CHF}_3$  plasma to remove the insulating  $\mathrm{SiO}_2$  on the back side only to allow for back gate electrical connection. Due to the exfoliated deposition method (see 2.2), crystal flakes of  $Bi_2Se_3$  are randomly distributed over the substrate surface. In order to facilitate locating and connecting the crystals, the substrates are prepared with coordinate grids made of evaporated gold markers (see Figure 2.4.2) on photolithographically defined patterns. Gold is used for the alignment markers since its large reflectance makes them visible under both optical and scanning electron microscopes. The coordinate grids spans from A1 to I9, with L-markers spaced apart by 100  $\mu$ m. The L-shapes double as size comparison standards, with dimensions 5 x 15  $\mu$ m. The wafers are highly polished on one surface for crystal deposition, while we etch the other side clean of  $SiO_2$  for back gate connection. We use a reactive ion plasma etch with a recipe of 9 sccm  $CHF_3$ , 1 sccm  $O_2$  at 100 mTorr pressure and 300 W for 15 m. On certain chips designated for suspended devices, the same plasma etch recipe is done after photolithography to define trenches in the substrate surface (discussed in chapter 5). Prepared substrates are diced, labelled and stored in an anti-static Gel-Pak until needed.

#### 2.2 Deposition of thin $Bi_2Se_3$ crystals

Since the explosion of graphene studies in the mid 2000's [11], the method of mechanical exfoliation has revolutionized the synthesis of atomically thin materials. Although other growth techniques such as molecular beam epitaxy (MBE) are capable of delivering single-layer sheets with large surface area, the quality provided by mechanical exfoliation is unmatched. Whereas MBE grown films are plagued by surface wrinkles and the challenge of transferring the crystal to a desired substrate, mechanical exfoliation deposits two-dimensional flakes of pristine crystallinity onto the substrate of choice. Verified by AFM and Raman spectra, exfoliated graphene crystals are single layer with uniform surfaces and regular edges. Here we demonstrate the mechanical exfoliation technique as applied to Bismuth Selenide (Bi<sub>2</sub>Se<sub>3</sub>), and show that it also produces thin flakes with uniform surfaces. As Bi<sub>2</sub>Se<sub>3</sub> is a topological insulator, which is predicted to exhibit novel surface states, it is imperative that we preserve its surface quality.

#### 2.2.1 Mechanical Exfoliation

Manual mechanical exfoliation, known colloquially as the tape peeling method, is in principal very simple and cheap to carry out. However, it can be difficult to calibrate the procedure and get reproducible results. The crystal structure of  $Bi_2Se_3$  is divided up into so called quintuple layers two embedded sheets of Bi sandwiched between layers of Se on all sides. Adjacent quintuple layers are held together by the rather weak van der Waals forces making Se - Se bonds at a distance of up to 350 pm [36]. This layered stacking is what allows the crystal to be easily cleaved during mechanical exfoliation. Tearing quintuple layers apart from one another, the exfoliation process leaves a layered crystal with a Se terminated surface.

We begin exfoliation with a bulk piece of  $Bi_2Se_3$ , and breaks it up into the thinnest slices possible by hand using a razor blade. We then place a thin slice onto the sticky side of a piece of adhesive tape, and the tape is folded onto itself to sandwich the  $Bi_2Se_3$  flake. Since the in-plane bonding of atoms within the crystal is much stronger than the Van der Waals interactions holding the sheets together, an interlayer tear can propagate through the crystal as the scotch tape is peeled apart. The process of folding and peeling the tape is repeated several times, separating the crystal layer by layer. If we make the approximation that the crystal thickness is halved with each peel, then the crystal height after n peels will be  $h_0^*(1/2)^n$ , where  $h_0$  is the initial thickness before exfoliation. It is easy to see then how a macroscopic piece of bulk  $Bi_2Se_3$  can be thinned down to the nanometer scale with this technique, as 20 folds results in a height reduction of over one million times. Once the  $Bi_2Se_3$  thin films have been prepared, they are ready to be deposited onto the substrates for device design. We use 550  $\mu$ m thick highly doped silicon wafers (N/ARS,  $\rho < 0.005 \ \Omega cm$ ), with a 300 nm thick layer of SiO<sub>2</sub> to insulate the source and drain electrodes from the back gate (Si wafer). The flake deposition procedure is straightforward: place the diced substrates facedown onto the sticky side of the scotch tape (uniformly covered with Bi<sub>2</sub>Se<sub>3</sub> flakes of various thickness), and then peel off the tape. The substrates are left to sit underneath the tape for 10 minutes before removing, massaging the tape on top of the substrates to encourage crystal adhesion. When the tape is removed, it is done carefully and slowly, attempting to have the best transfer from the tape to substrate, to minimize any further tearing of the crystals. Substrates bearing crystal flakes are immediately placed into vacuum storage in order to protect the freshly cleaved crystal surfaces from oxygen degradation in atmosphere. This oxidation and the strategies to deal with it will be the subject of Chapter 3. The sample storage space contains a desiccant to aid in dehumidifying the chamber.

#### 2.2.2 Vapor-Solid growth of Bi<sub>2</sub>Se<sub>3</sub> nanocrystals

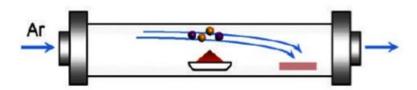

An alternate method to fabricate thin films of  $Bi_2Se_3$ , is the Vapor-Solid (VS) growth method, which we also investigated. Figure 2.2.1 shows the growth setup: a 99.999%  $Bi_2Se_3$  solid source crystal is placed at the center of a quartz tube furnace and heated to 700 C. The source crystals were either freshly cleaved using scotch tape, or powdered to maximize their surface area. We did not find that powderizing the source crystal yielded better results than using a large piece of bulk crystal with a clean surface. Solvent cleaned and  $N_2$  dried target substrates of  $SiO_2/Si$  were placed 14 - 15.5 cm down the tube, where it was determined to have an optimal temperature gradient for crystal condensation, based on the methods of *D. Kong* et al [6]. Gas flow rates are set to 200 sccm Argon and 5 sccm Hydrogen while the furnace heats up. Argon is used as an inert transport gas to flow vaporized  $Bi_2Se_3$  down the tube towards the deposition region. The Hydrogen gas acts as a catalyst for the process and is turned off once the temperature peaks at 700 C. Once the temperature reaches 700 C, the Argon transport gas is kept on, as the furnace is allowed to cool down.

Figure 2.2.1: Argon transport gas flows  $Bi_2Se_3$  vapour down the quartz tube towards target substrate. Figure from *Mlack* [23]

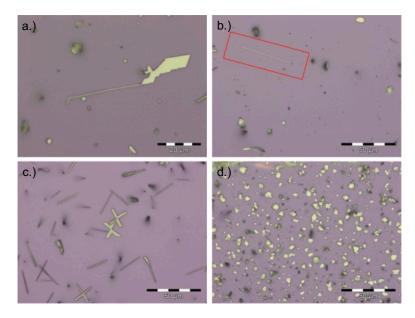

The morphologies of the deposited thin  $Bi_2Se_3$  crystal varies with their position along the quartz tube. Depending on the temperature (i.e. distance from the center of the tube) at the location where the crystals condensed, we may find a spectrum of crystal density and appearance. Flat surfaces and straight or stepped edges are indicators that the vapour has condensed into a crystalline form. Of potential crystal candidates to make transistor devices, the most interesting are  $Bi_2Se_3$  nanoribbons (1 x 50  $\mu$ m in dimension), and large surface area platelets. The VS method offers a spectrum of morphologies to study the effects of edge versus surface transport in thin (< 50 nm) films of topological  $Bi_2Se_3$ . Using these VS grown crystals poses additional challenges, fabrication steps, due to the need for a clean surrounding area

Figure 2.2.2: Vapor-Solid growth from powderized  $Bi_2Se_3$  a.) Interesting step-like growth results in a nanoribbon attached to a planar crystal with many corners b.) 50  $\mu$ m long nanoribbon c.) X-shaped crystals d.) Triangular and hexagonal stacked nano plates.

Figure 2.2.3: AFM measurement of a 15 nm thick ribbon with uniform edges

of neighbouring crystals for electrical contacts. This could be done by making a box of photoresist to protect the target crystal, and plasma etching the surrounding area clean. For an eventual mass production of these transistors the VS growth method could dominate mechanical exfoliation in terms of throughput. However, in the pursuit of individual working transistors, the scotch tape method is more suitable to us.

## 2.3 Structural characterization of deposited thin films

To start our fabrication of thin Bi<sub>2</sub>Se<sub>3</sub> transistors, we have to sift through the synthesized flakes and select the best candidates for devices. Optical microscopy gives a good initial impression of a flake's surface roughness, edge uniformity and relative thickness. A large number of crystals can be inspected quickly using optical microscopy and we, catalogue those with potential for transistor application. To get precise thickness measurements and surface information, we use atomic force microscopy (AFM) to build a topographical image of the flake. This process is much longer than optical investigation, therefore only a few selected crystals are imaged using AFM. Imaging can also be done after completing the charge transport measurements on a device in order to avoid wasting time imaging devices which end up failing for various reasons.

#### 2.3.1 Optical microscope characterization

The mechanical exfoliation method gives us a random dispersion of crystals of varying shapes and sizes across the substrates. Individually diced silicon substrates are inspected one by one with optical microscopy, while the other samples awaiting characterization remain under vacuum. The microscope we used is an Olympus BX51M, with a digital camera attached directly to a desktop computer for taking pictures. The substrate grids (see section 2.1) are slowly scanned, looking for flakes which are thin, uniform, large and isolated from the other flakes. The thickness of the flakes can be approximated to within 20 nm for thin flakes, and 100  $\mu$ m for thick flakes, by observing the colour of the crystal and the uniformity of the surface.

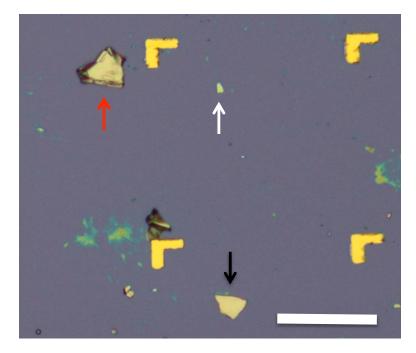

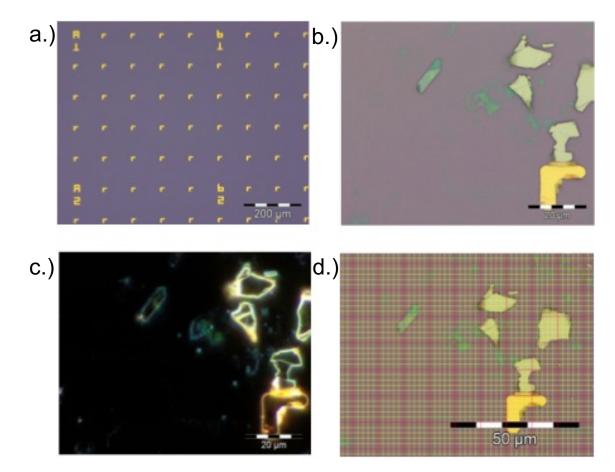

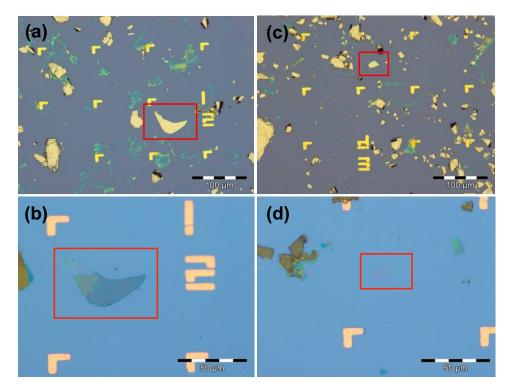

Figure 2.3.1: Preliminary characterization of mechanically exfoliated flakes using an optical microscope

In Figure 2.3.1 we see how thicker flakes are easily discerned by the multilayering of opaque yellow surfaces and dark, jagged edges (red arrow). Flakes of this kind are typically  $800 + \mu m$ . A singular edge and flat surface (black arrow) indicates a thickness of 100-300  $\mu$ m. Thinner flakes on the order of 30-80 nm will begin to show translucent blue coloured edges (white arrow). High quality flakes are characterized by having a uniform surface thickness and more straight, crystalline edges. Dark-field imaging is very useful in noticing height changes on the surface of a crystal. In this setting of the optical microscope, light that is scattered off the surface is collected, as opposed to the reflected light observed in usual optical microscopy. A directory of flakes is constructed, and selected samples will go for precise height measurement by atomic force microscopy (AFM). Samples are chosen based on their thickness, uniformity, surface area, and their location on the substrate. Typically, lithography patterns will require 500 -1,000  $\mu m$  of free space, so the flakes which land close to each other or close to the substrate's edges need to have custom designed electrodes in order to prevent discontinuities of the contacts. Sometimes flakes landing too close to the substrate edge are overlooked, as edge effects when spinning photoresist lead to a non-uniform resist thickness.

#### 2.3.2 Atomic Force Microscope measurements

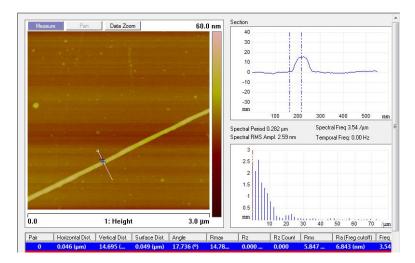

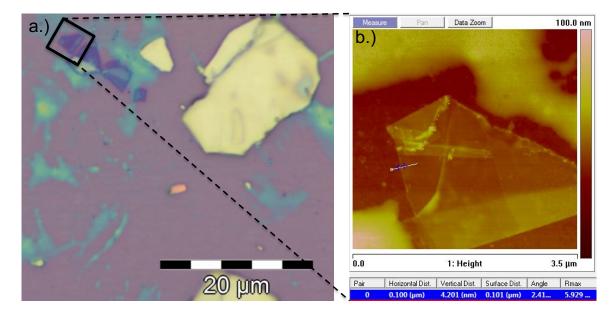

For precise thickness measurements of our devices, we use atomic force microscopy (AFM) to obtain 3-dimensional height maps of the crystals. Figure 2.3.2 shows a translucent thin film identified by optical microscopy and measured by AFM.

The AFM operates by reflecting a laser beam off a cantilever tip towards a CCD photodiode. The cantilevers we use were typically made of Silicon. Upon analyzing the received signal, the cantilevers vibrational amplitude is determined, and translated into a height (z-position). The tool used in these studies is a digital instrument 622VJ, operated in tapping mode. A vertical resolution better than 5 nm is easily attained. Height measurements can be taken on the crystal before lithography, or after metal evaporation to include the of gold contacts.

Line scans are assembled into 2-dimensional height maps, with colour denoting the z-axis. The data is analyzed by taking line cuts perpendicular to crystal edges and along surfaces. Exact thickness values are necessary for extracting transport properties from transport data (e.g. change density, mobility) and will thus be very useful in the following chapters.

# 2.4 Making electrical contacts to ultrathin topological $Bi_2Se_3$ crystals

Here we discuss the construction of a  $Bi_2Se_3$  thin film transistor. Figure 2.4.1 shows a cartoon of a device with source, drain, and electrostatic ally coupled gate electrodes. The two methods used in this project for designing micron-scale circuits are the traditional photolithography, using ultraviolet exposure of photoresist, and the higherprecision electron beam lithography (EBL), which makes use of a shorter wavelength beam of electrons for fine details. Photolithography has a higher throughput, making

Figure 2.3.2: Thin flake characterization: a.) Optical and b.) Atomic Force Microscope images of a 6 nm-thick exfoliated  $Bi_2Se_3$  flake

use of predefined patterns on a photomask, whereas EBL is used for custom designs, in which the beam writes out the circuit according to a CAD file. Metal electrodes are evaporated onto the lithographic patterns using a diffusion vacuum pumped thermal evaporator. Following the metal evaporation, the samples are placed into an acetone bath (at 60 C) for lifting off the photoresist. The entire fabrication process takes on average one week for a round of samples, but can be done in one day to minimize the samples exposure to air.

#### 2.4.1 Electron beam lithography of micron-sized contacts

To prepare samples for EBL exposure, substrates with selected crystals are spincoated first with a copolymer (MMA 8.5 MAA) at 4000 rpm for 60 seconds. They are

Figure 2.4.1: Source and drain electrodes physically contact the  $Bi_2Se_3$  crystal, while the gate is capacitively coupled via the  $SiO_2$  dielectric film.

then baked at 170 C for 15 minutes, then spin-coated with another layer of PMMA 2% at 2000 rpm for 60s, and given another 15 minute hard bake. This bi-layer resist technique adds resolution to the exposure by the fact that the 2 layers will absorb energy and develop at slightly different rates. This results in what is called an "undercut", which helps to have clean metal liftoff for narrow and close together electrodes (distances here of the order of 1  $\mu$ m).

The electron beam lithography system we used is a Hitachi SU-70 with a thermal emission Zinc Oxide coated tungsten tip. EBL contact patterns are designed in the lab beforehand using the Nanometer Pattern Generation System (NPGS) software, by overlaying computer designed grids on optical images of device candidates. Circuit patterns can be tested with a mock exposure before final execution. The EBL system uses a 20 kV voltage, accelerating the beam electron through a focusing aperture onto the sample. The sample chamber is under high vacuum  $(1 \times 10^{-8} \text{ Pa})$ . The Gold-L reference markers are used to adjust the substrate rotation and align the

Figure 2.4.2: a.) Prepatterned Gold reference grid for flake location b.)  $Bi_2Se_3$  flakes are exfoliated onto the grid c.) Dark field imaging shows surface and edge uniformity, suggesting the crystalline nature of the flake d.) Optical image overlaid with a digital coordinate system for CAD design of EBL electrodes

Figure 2.4.3:  $Bi_2Se_3$  flake with Hall bar geometry after metal electrode evaporation (scale bar is 10  $\mu$ m)

design file with the actual substrate via a global coordinate grid. Once the crystal position has been found, the beam is moved to a nearby empty space for focusing and stigma optimization. The electron beam must be blanked off during translations to avoid exposing the sample area. Once the coordinates have been verified and the beam is tuned, the system is put into automatic mode for exposure, which takes roughly half an hour depending on the area enclosed by the contacts. Once the exposure is completed the sample is removed from the vacuum chamber and developed. Due to the long time required to expose large contacts, generally only the fine electrodes contacting small crystals will be written using EBL, and larger electrode arms and contact pads will be added using standard patterns selected from one of our photomasks. This is done in another round of photolithography, using the MA4 photo-aligner. Chips are coated using S1813 photoresist and developed for 45 seconds in MF319 developer. Chips are then placed into a hand pumped vacuum container for transport, and are ready for metal deposition. A finished device is shown in Figure 2.4.3.

#### 2.4.2 Metal contact evaporation and device packaging

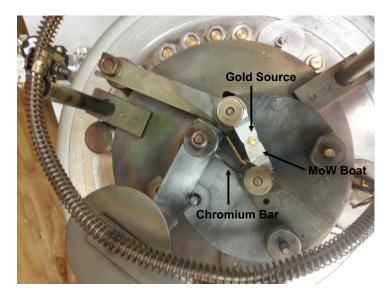

Metal contacts are laid onto lithography patterns using our thermal evaporation system. Samples are loaded into a bell jar which is pumped down to a pressure of  $5 \times 10^{-6}$  Torr, evacuated by an oil diffusion pump backed by a roughing pump.

Figure 2.4.4: Metal deposition of the contacts is done using a diffusion pumped thermal evaporator

The sample stages are suspended face down above the source materials, in this case a chromium bar and a gold nugget placed in a tungsten-molybdenum boat. The electrical circuit is setup to pass current through one source at the time, using an external switches enabling the chamber to remain under vacuum. The standard evaporation recipe used here calls for a 5 nm sticking layer of Chromium, followed by 80 nm of Gold contacts. The crystal thickness monitor shown in Figure 2.4.6 employs a quartz microbalance calibrated to each material to display live readouts of film thickness during deposition. This results in a high level of confidence and reproducibility in the deposited thickness across many evaporations, even though the deposition rates and times will vary. A shutter is opened between the source material and the lithographically patterned substrates once an acceptable deposition rate is achieved, and closed upon reaching the desired thickness. The bell jar is kept under vacuum while the source materials cool off, at which point the freshly coated substrates can be put into warm acetone for photoresist or EBL resist liftoff. At this stage the device is ready to be checked for electrical connection under a probe station and packaged for permanent safe keeping.

The prepared transistors are mounted onto a 24-pin carrier using conductive Silver paint, making electrical contact to the silicon backside of the substrate for gate connection. Once the metal contacts and back gate are connected the sample is susceptible to electrostatic shocks. It is at this packaging stage of microfabrication that the sample is at a high risk of being damaged. Utmost care is given to grounding during wire bonding and while transferring the sample to and from storage. Our WestBond wirebonder shown in Figure 2.4.7 uses a microscope and lever arm setup to scale down the user's movements, allowing delicate control of the ultrasonic tooltip.

Even with proper grounding safeguards for static electricity, the tooltip itself can

Figure 2.4.5: Current is passed through either a Chromium bar or a Gold nugget, creating metal vapour under vacuum

Figure 2.4.6: The resonance frequency of the crystal thickness monitor is measured by a RF circuit, and is sensitive to nanometer thick metal layers

Figure 2.4.7: Device packaging: our wire bonder scales down the users movements in order to precisely attach 25 micron thick Aluminum wires using an ultrasonic pulse

easily damage the contact pads and cause gate leakage if the ultrasonic power or stage height are improperly tuned. Aluminum wire is bonded from the gold contact pads on the  $SiO_2/Si$  surface to the chip carrier. The chip must be either transferred directly to a measurement probe or safely stored in anti-static GelPaks under vacuum until it will be measured (storage container shown in Figure 2.4.8). The attached wire bonds act as antennae for ambient electric fields, and for this reason the sample is generally measured immediately after packaging.

Figure 2.4.8: Prepared samples are stored under vacuum to minimize exposure to air

## 2.5 Electronic measurement setup and cryostat

While  $Bi_2Se_3$  is known to display good thermoelectric properties across a range of temperatures [4], we aim to observe signatures of coherent 2D surface transport at

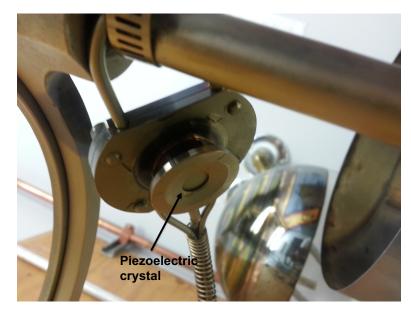

Figure 2.5.1: Sample testing: A packaged sample, loaded in the measurement probe of our  ${}^{3}$ He cryostat

low energies. Due to the high signal sensitivity required to resolve delicate quantum effects, the samples must be cooled as much as possible. Taking transport data at cryogenic temperatures allows for precise electronic measurements due to the reduction of thermal fluctuations which add noise to the current. Figure 2.5.2 shows our liquid Helium-3 (LHe-3) cryostat, capable of reaching temperatures as low as 0.3 K. This cryogen free system recirculates LHe-3 and LHe-4 with no need of refilling. A cold trap freezes out impurities down to 77 K in the <sup>4</sup>He gas lines, and should be refilled with liquid Nitrogen (LN2) periodically. Packaged transistors are loaded into the sample probe shown in Figure 2.5.1 and tested electrically at room temperature. The probe stick is pumped to high vacuum and checked for leaks before loading into the fridge. The LHe-3 cryostat is also equipped with a 9 Tesla (-/+ 9 T) superconducting magnet for B-field studies.

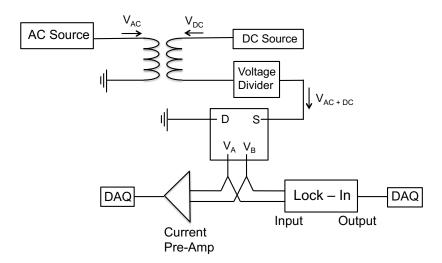

Data is collected using a custom user interface and a National Instruments Data Acquisition system (DAQ). As static electricity poses a constant threat of sending a shock to the sample, a grounding strap is worn on the wrist and contact electrodes are left grounded between measurements. Different electronic circuit setups can be used depending on the type of measurement we would like to make. For making 2-point resistance measurements and taking gatesweeps, a DC circuit is used. In this configuration, the DAQ card is used as a bias voltage source, sending a source signal through a voltage divider towards the sample. The drain current goes through an Ithaco 1211 current preamplifier and sent to a desktop computer. Our custom

Figure 2.5.2: 0.3 K fridge: The LHe-3 cryostat has an inner sample space buffered by a LHe-4 pot held at 1.2 K. The needle valve allows controlling the flow of LHe-4

MotorCurve software plots the data sweep in realtime and saves the data in a text file to the hard disk. Sampling rates, time constants and sensitivities are optimized, and offsets zeroed to optimize the data. For instance, the rise time on the current preamplifier should be inversely proportional to the sampling rate. Usually an extra factor of 3 is introduced to prevent taking the same data point twice. A low pass filter on the Keithley gate source prevents high voltage spikes from reaching the sample. Data is analyzed using Igor Pro software. Using an AC circuit, we can directly measure the differential conductivity by using the low noise circuit shown in Figure 2.5.3. Using a transformer we add the signals of a DC and AC voltage sources. A lock-in amplifier syncs onto the source frequency of the AC signal, filtering out noise. In this fashion, we can make use of the lock-in amplifier's ability to take a precise reading of a small signal ( $\mu V$  range), while either sweeping the source/drain bias, or holding the bias constant and taking a gate voltage sweep. We use a SR560 voltage preamplifier to modify the circuit when taking 4-point data. In this chapter we summarized the deposition of thin films of  $Bi_2Se_3$  on  $Si/SiO_2$  substrates, and the patterning of electrical contact on them to create transistor devices. These samples are then loaded into a cryostat for electron transport measurements. In the next chapter we will discuss the electronic characterization of our samples and our solutions to the contact resistance problems faced by all research groups working on  $Bi_2Se_3$  thin crystals.

Figure 2.5.3: Our AC circuit uses a transformer to add an AC perturbation atop a DC source signal

Figure 2.5.4: The 4-pt AC circuit uses a transformer to add an AC perturbation atop a DC source signal and measure the DC bias separately from the AC contribution

# Chapter 3

# Characterizing and optimizing electrical contacts to thin $Bi_2Se_3$ crystals

This project's main objective is to explore electronic transport in  $Bi_2Se_3$  topological insulator transistors, and to distinguish bulk conduction from surface state conduction. Cleaved  $Bi_2Se_3$  was chosen as the TI of interest due to its large bandgap of 0.3 eV which is topologically non-trivial as observed in optical experiments [9]. Now that we have fabricated thin film transistors, it is important that we ensure the quality of electrical contact to the  $Bi_2Se_3$  crystal and trust that our transport data reflects the physics of the  $Bi_2Se_3$  channel rather than the contacts before moving on to making magneto-transport measurements. It is known that the  $Bi_2Se_3$  crystal surfaces oxidize in open atmosphere, creating Se vacancies and affecting the topological surface transport [36]. Very few successful transport experiments have been reported in  $Bi_2Se_3$  in large part due to the difficulty to make good electrical contacts to the crystal. We would like to investigate the effect of atmosphere exposure on the quality of our electrical contacts, and see if modestly oxidized crystals can be contacted with low resistance contacts. Device design elements such as the contact surface area and the crystal thickness are explored as parameters affecting the contact resistance. We also attempt various etches prior to contact deposition.

This chapter begins with section 3.1, where we present data for contact resistance on  $Bi_2Se_3$  crystals in recent literature, and use these as benchmarks to achieve in order to be able to carry out magneto-transport studies on Bi<sub>2</sub>Se<sub>3</sub> crystals. The measurement methods we use to characterize the contact quality of our Bi<sub>2</sub>Se<sub>3</sub> transistors include both DC and AC + DC circuit configurations with either 2point (voltage probes are also injecting and draining the current) or 4-point (separate voltage probes and current leads) contact geometries. In section 3.2 we discuss the problem of oxidation in  $Bi_2Se_3$  thin films, and what can be done to minimize its effects. In section 3.3 we collect statistics on fabrication methods to understand that inter-dependence of the controlling factors are thickness, contact area, and we find that minimizing the amount of air exposure is the most important aspect to produce high quality  $Bi_2Se_3$  thin film transistors. We show a decrease in 2-point resistances for samples on which we used a short plasma etch prior to metal contact deposition. We reach a satisfactory understanding of the optimization of Bi<sub>2</sub>Se<sub>3</sub> transistors and show electrical contact resistance comparable to key references [30, 8]. In section 3.4 we discuss the effect of thickness on contact resistance. We are then ready to move on to studying samples' the magnetic transport properties of interest in Chapter 4.

# 3.1 Brief overview of electron transport in $Bi_2Se_3$ transistors

In this section we will present a review of selected theoretical and experimental aspects of electron transport in topological Bi<sub>2</sub>Se<sub>3</sub> transistors. This information will be useful for discussing our data in Chapters 3, 4 and 5. Since the discovery of the topological insulator as a phase of matter, theoretical advances have abounded [1, 2, 38], while transport realization of devices lags behind [27, 7]. There has been some success, however, with a few groups achieving good contacts and interesting transport data. We will present some of these as references for the transistors we should aim to achieve in order to study the behaviour of topological insulators at low temperature and high magnetic field. Following this review we will present the results of corresponding contact resistance measurements taken on the devices we fabricated in Chapter 2. we evaluate the status of transport in these devices with respect to literature, the initial challenges faced, and outline the steps we took towards improving the contact to a satisfactory level.

#### 3.1.1 Background on Bismuth Selenide transistors

The crystal structure of  $Bi_2Se_3$  is made up of alternating layers of trigonal lattices made of Bi and Se. These layers are bonded into so-called quintuple layers (QL's) held together by Van der Waals forces (see Figure 3.1.1 (a)). The topological nature of Bi<sub>2</sub>Se<sub>3</sub> follows from a parity inversion at zero momentum (the  $\Gamma$  point) in the first Brillouin Zone (FBZ). In quantum mechanics the parity transformation operator acts on the wave function  $\psi$  such as:  $\mathbf{P}\psi(r) = e^{i\phi/2}\psi(-r)$ . The operator is unitary and therefore must satisfy  $P^2\psi(r) = e^{i\phi}\psi(r)$ , meaning that P is an internal symmetry of the system and rotates its eigenstates by  $e^i\phi$ . To illustrate this, consider any timereversal invariant momenta  $\Gamma_i$  characterized by  $-\Gamma_i = \Gamma_i + G$ , where G is lattice vector in k-space (Figure 3.1.1 (b)) [26]. It can be seen that the  $\Gamma$ -point acts as a center for parity inversion in the BZ. In a  $Z_2$  class topological insulator, one can take linear combinations of the quantum states giving either an even or odd parity ( $\pm 1$  refers to the combination being symmetric or antisymmetric under such a parity transformation). The parity invariant can be found by multiplying all parity eigenvalues at each momentum. The  $\Gamma$ -point is the only point which gives a -1parity invariant, with all other points giving 1. This product of all points with time reversal invariant momenta gives -1, which ensures the bulk is a strong topological insulator [26].

The low-energy bandstructure of Bismuth Selenide is composed of surface states with a linear energy-momentum dependence that span a bulk bandgap. Spin-orbit coupling reduces the quantum degrees of freedom, the surface state dispersion exhibits

Figure 3.1.1: (a) The lattice structure and (b) the bulk and surface Brillouin zones of crystal  $Bi_2Se_3$  Figure from *Bianchi* [26]

a single Dirac cone per surface compared to graphene's double spin degeneracy [8]. The effective Hamiltonian for charge carrying electrons on the surfaces of a 3-dimensional TI is given in equation (2):

$$H(k) = -Dk^2 + v_F(k_y\hat{\sigma}_x - k_x\hat{\sigma}_y) + (\frac{\Delta}{2} - Bk^2)\tau_z\hat{\sigma}_z + g\hat{\sigma}_z$$

(2)

The first term leads to band inversion (with non-trivial topology) when  $B^2 - D^2 >$ 0. The next two terms are for isolated surfaces (top and bottom surface of the crystal) with v<sub>F</sub> the Fermi velocity of charge carriers, and  $\sigma$ 's are the Pauli spin matrices:

$$\sigma_x = \begin{pmatrix} 0 & 1 \\ 1 & 0 \end{pmatrix}, \ \sigma_y = \begin{pmatrix} 0 & -i \\ i & 0 \end{pmatrix}, \ \sigma_z = \begin{pmatrix} 1 & 0 \\ 0 & -1 \end{pmatrix}$$

(3)

The  $\tau_z$  term represents the coupling that occurs between opposing surfaces in film of sufficiently low thickness [13], with  $\tau_z = 1$  and  $\tau_z = -1$  representing the bonding and anti-bonding regimes, respectively. The hybridization gap  $\Delta$  can be controlled by thickness, and is related to the inter-surface tunnelling time by  $\tau_t = h/2\Delta$  [4]. This  $\tau_t$  will play a role in the crossover from the Weak Localization (WL) regime to one where it is suppressed (discussed further in chapter 4). Here we do not approach the ultra thin regime of < 6 nm in which inter-surface coupling occurs (except maybe one device discussed in Chapter 4.3), and this coupling term can therefore be omitted. In the last term g represents the strength of the exchange field in the crystal. J. Chen et al. [20] showed that this term is negligible in Bi<sub>2</sub>Se<sub>3</sub> as the strong spin orbit interaction suppresses the Zeeman splitting term, and so we leave this term out as well. Upon these omissions we look at our effective, simplified Hamiltonian:

$$H(k) = -Dk^2 + v_F(k_y\hat{\sigma}_x - k_x\hat{\sigma}_y) \tag{4}$$

The conductive surface states can be thought of as semi metallic and spin-polarized as opposed to having both up and down spin states everywhere on the Fermi surface [28]. Figure 3.1.2 depicts (a.) the theoretically calculated, and (b.) experimentally obtained density of states for  $Bi_2Se_3$ . The bandstructure was observed in-situ using angle resolved photoemission spectroscopy (ARPES) on 10 nm-thick grown films [8].

Figure 3.1.2: The band structure of crystal Bi<sub>2</sub>Se<sub>3</sub>: a.) Theoretically calculated local density of states [9], and b.) The bandstructure experimentally observed via ARPES [8]

While the surface states are theorized to be topologically protected, these states are difficult to realize in practice due to selenium vacancy defects in the bulk layers. These vacancies add free charge carriers which n-dope the sample and wash out or dilute the surface state signal [8]. Selenium vacancies arise during oxidation of the crystal when the surface is exposed to open atmosphere. We expect that thicker crystals will show little or no gate-voltage tunability of the Fermi level of the 2D surface states due to screening from the bulk layers. Our goals are first to make low resistance contacts to the crystal surface, then search for evidence that the transport is across the contacted surface, the bulk layers, or some mixture of the two. Evidence for surface transport can be found in the thickness dependence of the crystal's resistance and in magneto-transport [29, 14]. The effects of sample thickness on the device resistance will be discussed further in section 3.4. Next we look at what has been achieved recently in transport experiments on  $Bi_2Se_3$ , and what difficulties remain in the field of experimental transport in topological insulators.

#### 3.1.2 $Bi_2Se_3$ transistors: recent results and challenges

Topological insulators are a playground for theoretical physicists yet remain difficult to study experimentally due to fabrication challenges. Here I present some of the few examples in recent literature of working Bi<sub>2</sub>Se<sub>3</sub> transistors that show magnetotransport behaviour. I will discuss how these devices are characterized electronically, and compare them to the fabricated devices. The purpose is to show a roadmap towards improving contact and device performance.

The first and simplest measurement to characterize a sample is to measure its 2-point resistance. The resistance is obtained from the slope of y-axis current versus x-axis source-drain bias voltage (V<sub>B</sub>) graph. The  $I-V_{bias}$  plot shows whether the gold

electrodes have made good contact, and if the crystal is conducting. The source-drain voltage is initially set to a modest range (such as -10, +10 mv) to avoid damaging or heating the sample. Output current is typically in the microamps range for a sample with k $\Omega$  resistance.

Taking a look at contact resistance in recent literature, M. S. Fuhrer et al. achieved a Bi<sub>2</sub>Se<sub>3</sub> sheet resistance of 140  $\Omega$ /sq and a contact resistance of 176  $\Omega$ (on a 70 nm-thick crystal). Contact patterns were etched using N<sub>2</sub> plasma before evaporating Cr/Au (10/100 nm) metal contacts [30]. H. Peng et al. measured bias sweeps on a 10 nm-thick sheet of Bi<sub>2</sub>Se<sub>3</sub>, epitaxially grown on a mica substrate. Researchers found a sheet resistance of 330  $\Omega$ /sq with a contact resistance of 30  $\Omega$ per contact. Contacts were evaporated Cr/Au (5 nm/50 nm) [8]. These benchmarks provide a target for us to achieve in order to be in line with the best experimental research to date.

Here we discuss representative  $I - V_{Bias}$  and  $I - V_{Gate}$  for as fabricated Bi<sub>2</sub>Se<sub>3</sub> transistors from Chapter 2. Despite efforts to select suitable device candidates based on optical and atomic force microscopy, samples must ultimately be characterized via electron transport. What we are looking for are devices that have a high signal to noise ratio, and ones with low enough contact resistance such that it does not dominate the transport. Following microfabrication, another hurdle we had to be overcome was gate leakage. It often reduced the sample yield below a useful level. Gate leakage occurs when the insulating oxide on the substrate breaks down and one or more of the gold electrodes contacting the crystal making a connection to the gate electrode. This short circuits the device and makes it unfit for transport studies. Gate leakage can occur due damage to the oxide layer, or electrostatic damage. A device with an undamaged oxide should be able to withstand gate voltages up to 60 V without problem. Any small scratch on the surface of the substrate will increase the probability of gate leakage. Thus, care must be taken to transport unmounted chips in GelPaks so that they do not touch one another, as their sharp edges can easily scratch the surfaces. Plastic tipped-tweezers are used for handling the substrates during fabrication to protect the oxide layer. The main source of oxide damage was wirebonding (see Chapter 2.4.2). The metal tooltip we use is sharp and can poke right through the 80 nm-thick contact pads. If the ultrasonic power is not tuned such that the first attempt at bonding is a success, successive attempts will often tear the gold film from the surface. This leaves exposed areas of SiO<sub>2</sub> that are susceptible to scratching by the tooltip. Figure 3.1.3 shows an example of a thin (12 nm-thick) film device which shows gate leakage:

Oxide breakdown is rarely caused by electrostatic shocks for on-substrate samples (i.e. not suspended) since the gate is protected from short voltage spikes by a lowpass filter in the circuit. The main causes of gate leakage are fabrication related. The diagnosis of the problem, however, can only be done through the electrical testing of the device. This is why the sample is tested upon loading into the probestick at room temperature, thereby avoiding going through the lengthy cool down process only to find that the sample is faulty.

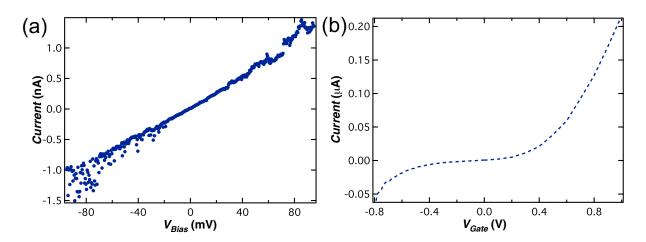

Looking at the transport data for this sample, the bias sweep (shown in Figure

Figure 3.1.3: Ultrathin  $Bi_2Se_3$  crystal with EBL defined contacts (Scale bar = 10  $\mu$ m)

Figure 3.1.4: (a) A 2-point bias sweep reveals a large resistance  $R = 74 \text{ M}\Omega$ , and shows disorder, (b) With constant source/drain voltage, the gate voltage is swept over  $\pm 1 \text{ V}$ . A breakdown of the SiO<sub>2</sub> substrate leads to the backgate making a current connection directly to the gold electrodes

3.1.4 (a)) alone shows that a few things are wrong; it deviates from a linear line shape at higher biases, and gives an extremely high device resistance (74 M $\Omega$ ). The high resistance could possibly either be due to the extremely low crystal thickness, high contact resistance of leakage from source to the gate such that no current reaches the drain electrode. This can be clarified by  $I - V_G$  data (Figure 3.1.4 (b)) current versus  $V_G$  data. This means that the device is shorted by leakage to the gate electrode, i.e. no current passes through the actual crystal. Such a sample cannot be studied. Repeated tests showed that the wire bonder we were using was causing many cases of gate leakage, so we carefully re-calibrated the instrument. We found that the highest bonding success rate occurred at a power/time setting of 700 mW/500 ms. Stage levelling and height adjustments are also extremely important settings when it comes to bonding to the delicate gold films without damage. Figure 3.1.5 shows the I - Vplot for sample G. This thick flake (estimated thickness 600 nm) should be n-doped due to bulk defects and its channel having a low resistance. From the slopes of two bias sweeps using different sets of contacts (all other unused contacts would be floated during the sweep), we measure resistances respectively of 58 k $\Omega$  and 1.8 M $\Omega$ .

These high device resistances are very likely due to the contacts, and not the actual  $Bi_2Se_3$  crystal. By the fact the two values differ by a factor of more than 20x, we can rule out the possibility that these are readings of crystal resistance simply by a geometric factor (contact geometry could account for a L/W ratio of up to 3x). Further, if we apply a constant bias voltage (20 mV) and vary the back gate voltage, we obtain a gatesweep plot that shows the carrier density on the crystal is relatively

Figure 3.1.5: I - V plot shows a linear source/drain dependence. 2pt resistance is extracted from the slope

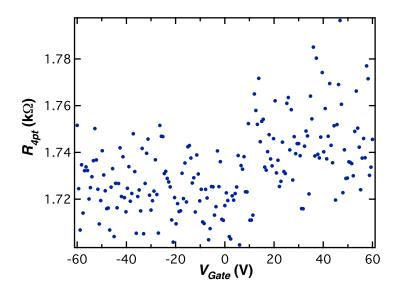

unaffected in a 120 V range (see Figure 3.1.6).

It is not surprising that this sample shows no gate tuning of the resistance given the thickness and measured resistance of the device. To make gate-tunable devices we need to make contacts with a lower resistance on thinner crystals. High contact resistance can arise from a number of factors. One of the main causes is that immediately after bulk Bi<sub>2</sub>Se<sub>3</sub> is cleaved in air, it begins to oxidize. High R contacts can be due to an oxide barrier between the gold contacts and Bi<sub>2</sub>Se<sub>3</sub> crystal. We next try to better quantify this oxidation effect and determine a microfabrication route to make low-resistance devices.

Figure 3.1.6: With a constant source/drain voltage applied, the 4-point resistance does not show gate dependence

### **3.2** Quantifying the impact of surface oxidation on

### contact resistance

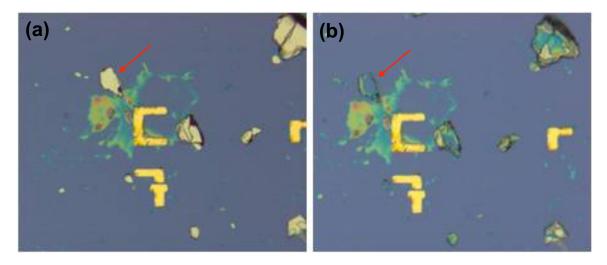

Along with many other topological insulators,  $Bi_2Se_3$  belongs to the halcogenides compound group known to be highly reactive with oxygen [36]. Unlike other halcogenides whose cleaved surfaces are generally inert,  $Bi_2Se_3$  will react with oxygen in the open air to the point of complete crystal degradation. Figure 3.2.1 shows two images of the same crystals taken a few months apart. In the meantime, the crystals had been continuously exposed to air. One can clearly see the devastating effect this exposure had on the crystals. Exfoliated flakes of  $Bi_2Se_3$  were etched away, from hundreds of nanometers to only a few or no quintuple layers. By optical microscopy alone it is easy to see the drastic change in colour due to thickness changes, from an opaque yellow to varying shades of green and blue indicative of sub 50 nm thicknesses. The flake above and to the left of the C7 marker appears to be the thinnest in the left picture, judging by it's smooth surface. In the right image there is almost nothing left of the crystal.

Figure 3.2.1: (a) Freshly exfoliated  $Bi_2Se_3$  crystal flakes, (b) Left in open air for 3 months, the crystals are severely degraded

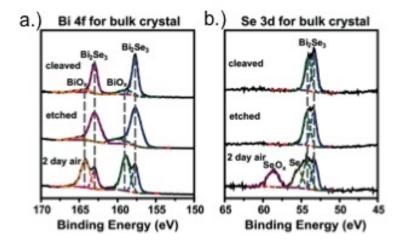

This is an extreme case of air exposure, as no sample intended for transport studies would be left in the open for so long. While long term exposure is observed to cause irreparable damages to the crystal structure, in this project we are concerned with the effect short term air exposure on the electron transport properties of the material. Short air exposures have been shown to cause an n-type doping, contaminating the surface state contribution to transport [21]. *D. Kong* et al. found upon conducting an X-Ray Photoelectron Spectroscopy (XPS) study that a native oxide growth occurs on Bi<sub>2</sub>Se<sub>3</sub> for both nanoribbons and bulk crystals that have been exposed to air [7]. Figure 3.2.2 shows the XPS spectra for Bi<sub>2</sub>Se<sub>3</sub> bulk crystals under vacuum. The

topmost spectra were taken on fresh crystal surfaces, transferring samples within 10s of cleavage into vacuum with an inert  $N_2$  gas flux. Adjacent to the expected  $Bi_2Se_3$  peaks, the oxidized form of Bismuth  $BiO_x$  appears small following cleavage and increases with continued exposure time. The  $BiO_x$  grows over a period of 2 days to the point of surpassing the  $Bi_2Se_3$  signal. This corresponds to the formation of a layer of oxide on the crystal surface with an estimated thickness of 0.38 nm at the outset to an estimated 1.94 nm after 2 days. The appearance of the small  $BiO_x$  signal in the initial spectra indicates that the surface of freshly cleaved  $Bi_2Se_3$ begins to oxidize very quickly. The fact that  $SeO_x$  is also observed (Figure 3.2.2 (b)) suggests that the oxidation diffuses into the crystal, affecting both the Bi and the Se crystal planes within a quintuple layer. Kong et al. propose a transport model where carriers from the bulk layers and the surface oxide layer both contribute to the transport signal along with the topological surface state. How much each one of these different regions appears in the measurements depends on the thickness of the sample and the amount of oxygen exposure it received. These researchers found that a short Argon (Ar) ion etch (5 min, 10 mA, 5 kV) resulted in a reduction of the oxide peak to about 19% to 13% weight (middle panels, Figure 3.2.2). This means that the crystal's surfaces can be improved prior to transport studies even if a significant oxidation took place.

In the next section we will test plasma etching on our sample, but for now we take a look at the effect of the duration of air exposure on the sample resistance. To compare against the sample discussed in section 3.1.2 (sample G, with  $R_{2pt} =$

Figure 3.2.2: (a) Bi and (b) Se XPS Spectra for  $Bi_2Se_3$  shows the formation of an oxide layer over 2 days, with both Bi and Se binding to Oxygen in the air. Samples etched with an Argon plasma (middle panel) display a reduction in the level of oxidation [7]

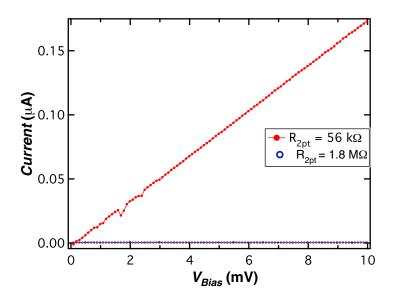

56 k $\Omega$ ) we present another sample fabricated with only a moderate exposure to the atmosphere. The exposure time was limited to 20 days, corresponding to roughly half the time of sample G, which was approximately 6 weeks.

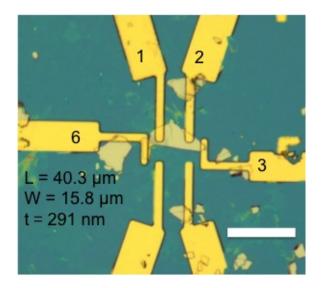

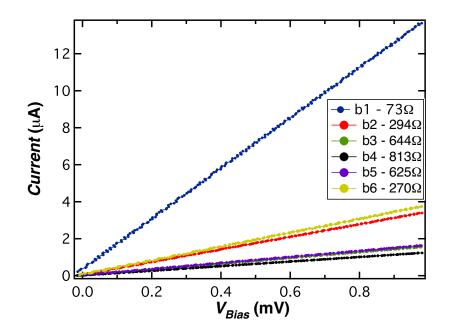

Figure 3.2.3 shows the 4-point device sample B, which is roughly 291 nm-thick, as recorded by AFM. Intuitively, the lower thickness of sample B compared to sample G (600 nm) should correspond to fewer layers of parallel conduction and a higher resistance. In fact, the measured resistance of sample B of Figure 3.2.4 is dramatically lower than for sample G.

Everything about the fabrication process was the same for these two samples, from lithography recipes to metal electrodes, excluding only the time of air contact. With the 2-point signal coming from a combination of the crystal itself and the contact resistance at the metal-surface interfaces we decomposed  $R_{2pt}$  into its constituent

Figure 3.2.3: 4-point sample B, fabricated with moderate air exposure (20 days)

Figure 3.2.4: Current-Bias curves show a significantly lower resistance compared to sample G

parts:

$$R_{2pt} = R_{Crystal} + R_{C1} + R_{C2} \tag{5}$$

Where  $R_{C1}$  and  $R_{C2}$  are the series contributions to the resistance due to the contacts at each of the two metal-Bi<sub>2</sub>Se<sub>3</sub> interfaces. In principle, it is difficult to ascertain how much of the signal is coming from the crystal and how much is due to contact resistance with only 2 contacts. However, devices patterned with 4 or more contacts permit a more accurate calculation of Bi<sub>2</sub>Se<sub>3</sub> sheet resistance via the Van der Pauw method [37]:

$$\rho_{VdP} = \frac{\pi d}{2ln2} \frac{R_{AB,CD} + R_{BC,DA}}{2} f(\frac{R_{AB,CD}}{R_{BC,DA}}) \tag{6}$$

where the sheet resistance  $\rho_{VdP}$  can be measured directly using a 4-contact geometry. The 4-pt resistance  $R_{AB,CD}$  refers to the resistance value attained by dividing the voltage measured across contacts A and B with the current flowing between contacts C and D. The measurement orientation is then rotated, and the 2 resistances are averaged. The correction coefficient f is a function of the ratio of  $R_{AB,CD}/R_{BC,DA}$ , which varies from 0 to 1. Another method can also be employed for devices with multiple contacts. By constructing a system of linear equations for each set of 2-pt resistances, one can determine the resistance of each contact, as well as the Bi<sub>2</sub>Se<sub>3</sub> sheet resistance. Using the bias sweeps from sample B as an example, we constructed the linear system of equations of the type shown in equation (6). Here, the  $R_{Crystal} = \frac{L}{W}\rho$ , and we solve for the sheet resistivity,  $\rho$  and compare it with the one from the Van der Pauw method.

$$\begin{bmatrix} 1 & 0 & 0 & 1 & 1.05 & 769 \\ 0 & 1 & 0 & 1 & 1.07 & 581 \\ 0 & 0 & 1 & 1 & 1.07 & 600 \\ 1 & 0 & 1 & 0 & 1.17 & 250 \\ 1 & 1 & 0 & 0 & 1.19 & 226 \end{bmatrix}$$

(7)