# Analysis of Single Event Upsets Propagation at Register Transfer Level in Combinational and Sequential Circuits Based on Satisfiability Modulo Theories

Ghaith Kazma

#### A Thesis

in

The Department

#### of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements

for the Degree of Master of Applied Science (Electrical and Computer Engineering) Concordia University Montréal, Québec, Canada

> May 2017 © Ghaith Kazma, 2017

### CONCORDIA UNIVERSITY School of Graduate Studies

This is to certify that the thesis prepared

By:Ghaith KazmaEntitled:Analysis of Single Event Upsets Propagation at RegisterTransfer Level in Combinational and Sequential CircuitsBased on Satisfiability Modulo Theories

and submitted in partial fulfillment of the requirements for the degree of

#### Master of Applied Science (Electrical and Computer Engineering)

complies with the regulations of this University and meets the accepted standards with respect to originality and quality.

Signed by the final examining committee:

|       |                       | Chair             |

|-------|-----------------------|-------------------|

|       | Dr. R. Raut           |                   |

|       |                       | External Examiner |

|       | Dr. J. Bentahar       |                   |

|       |                       | Internal Examiner |

|       | Dr. S. Hashtrudi Zad  |                   |

|       |                       | Co-Supervisor     |

|       | Dr. O. Ait Mohamed    | 1                 |

|       |                       | Co-Supervisor     |

|       | Dr. Y. Savaria        | -                 |

| Appro | oved by:              |                   |

|       | Dr. W.E. Lynch, Chair |                   |

Department of Electrical and Computer Engineering

\_\_\_\_\_ 2017

Dr. Amir Asif, Dean, Faculty of Engineering and Computer Science

### Abstract

Analysis of Single Event Upsets Propagation at Register Transfer Level in Combinational and Sequential Circuits Based on Satisfiability Modulo Theories

#### Ghaith Kazma

The progressive scaling of semiconductor technologies has led to significant performance improvements in digital designs. However, ultra-deep sub-micron technologies have increased the vulnerability of VLSI designs to soft errors. In order to allow a cost-effective reliability aware design process, it is critical to assess soft error reliability parameters in early design stages. This thesis proposes a new technique to model, analyze and estimate the propagation of Single Event Upsets (SEUs) in combinational and sequential designs described at the Register Transfer Level (RTL) using Satisfiability Modulo Theories (SMT). The propagation of SEUs through RTL bit-vector constructs is modeled as a Satisfiability problem using the SMT theory of bit-vectors.

At first, for combinational designs, two different analysis techniques, concrete and abstract modeling, are used in order to investigate the efficiency and accuracy of a data type reduction technique for soft error analysis. To analyze the vulnerability of the combinational circuits, we compute the Soft Error Rate (SER), which is a summation of the propagation probabilities. Concrete modeling uses two versions of the design, one faulty and one fault-free, in order to analyze SEU propagation. Abstract modeling uses a data type reduction technique to evaluate the difference in performance and accuracy over the first method. Experimental results demonstrate that the loss in accuracy due to abstract modeling depends on the design behavior. However, abstract modeling allows to reduce processing time significantly. Following this first approach, the methodology is then extended to model and analyze SEU propagation in sequential circuits at RTL. In order to estimate the vulnerability of sequential circuits to soft errors, the methodology must be adapted to represent state transitions. To do so, we present an approach that uses circuit unrolling. This approach uses multiple unrolled copies of the design to represent the various state transitions. The fault propagation is then analyzed through a certain number of states. Useful information regarding the vulnerability to SEUs of the sequential circuit can then be generated. The propagation probabilities can be computed from the SEU injection cycle to multiple subsequent cycles. These results are then used to estimate the circuit Soft Error Rate (SER). Experimental results demonstrate the effectiveness and the applicability of the proposed approach.

Finally, we present a new methodology to estimate digital circuit vulnerability to soft errors at Register Transfer Level (RTL). Single Event Upsets (SEUs) propagation through RTL bit-vector operations is modeled and analyzed using a different modeling approach based on Satisfiability Modulo Theories (SMTs). The objective of this new approach is to improve the efficiency of the analysis. For instance, the bit-vector reduction operators and arithmetic operators were modeled in SMT to include the fault propagation properties. This approach uses only one copy of the design to do the analysis. This means that the fault propagation properties are embedded within the SMT equivalent of the RTL constructs themselves, and therefore does not require two-copies of the design to analyze. In order to illustrate the practical utilization of our work, we have analyzed different RTL combinational circuits. Experimental results demonstrate that the proposed framework is faster than other comparable contemporary techniques. Moreover, it provides more accurate and detailed results of the circuit vulnerability allowing a more efficient applicability of fault tolerance techniques.

To my parents

# Acknowledgments

Firstly, I would like to thank Dr. Otmane Ait Mohamed for giving me the opportunity to pursue a Master's degree under his supervision. Dr. Ait Mohamed has taught me both professional and personal skills that will greatly benefit my career.

I would also like to thank Dr. Yvon Savaria for accepting to be my Co-Supervisor. His support was of great importance to the completion of my thesis. I am grateful to him for his encouragement and feedbacks.

Many thanks to all the Hardware Verification Group members for their support and encouragement. Every member, helped me in some way or another, throughout my Master's degree.

Finally, I would like to thank my family for their love and encouragement.

# Contents

| Li            | List of Figures xi |                                                            |      |  |

|---------------|--------------------|------------------------------------------------------------|------|--|

| $\mathbf{Li}$ | List of Tables xii |                                                            |      |  |

| Li            | st of              | Acronyms                                                   | xiii |  |

| 1             | Intr               | Introduction                                               |      |  |

|               | 1.1                | Motivation                                                 | 2    |  |

|               | 1.2                | Thesis Contribution                                        | 5    |  |

|               | 1.3                | Thesis Outline                                             | 6    |  |

| <b>2</b>      | $\mathbf{Pre}$     | liminaries and Related Works                               | 8    |  |

|               | 2.1                | Single Event Upsets                                        | 8    |  |

|               | 2.2                | State of the Art                                           | 11   |  |

|               |                    | 2.2.1 Techniques at Gate Level                             | 12   |  |

|               |                    | 2.2.2 Techniques at Register Transfer Level                | 12   |  |

|               | 2.3                | Boolean Satisfiability (SAT)                               | 13   |  |

|               | 2.4                | Satisfiability Modulo Theories (SMT)                       | 14   |  |

|               | 2.5                | Summary                                                    | 15   |  |

| 3             | Cor                | acrete and Abstract SMT Modeling and Analysis of SEUs Prop | -    |  |

|               | aga                | tion in Combinational Circuits                             | 16   |  |

|               | 3.1                | Introduction                                               | 16   |  |

|               | 3.2                | Data Type Reduction                                        | 18   |  |

|          | 3.3           | Propo   | sed Methodology                                            | 20 |

|----------|---------------|---------|------------------------------------------------------------|----|

|          |               | 3.3.1   | Concrete Modeling                                          | 21 |

|          |               | 3.3.2   | Abstract Modeling                                          | 24 |

|          |               | 3.3.3   | Estimate SER due to SEUs                                   | 25 |

|          |               | 3.3.4   | SMT Model Count                                            | 26 |

|          |               | 3.3.5   | Examples                                                   | 26 |

|          | 3.4           | Exper   | imental Results                                            | 32 |

|          |               | 3.4.1   | Accuracy Analysis                                          | 32 |

|          |               | 3.4.2   | Performance Analysis                                       | 34 |

|          | 3.5           | Summ    | ary                                                        | 36 |

| 4        | $\mathbf{SM}$ | T Mod   | leling and Analysis of SEUs Propagation in Sequential Cir- | -  |

|          | cuit          | s       |                                                            | 37 |

|          | 4.1           | Introd  | luction                                                    | 37 |

|          | 4.2           | Appro   | ximate Model Counting                                      | 38 |

|          | 4.3           | SMT I   | Modeling of Sequential Circuits                            | 38 |

|          |               | 4.3.1   | SMT Modeling of the Combinational Part                     | 39 |

|          |               | 4.3.2   | Unrolling of the Sequential Circuit                        | 41 |

|          | 4.4           | SEU I   | Propagation and SER Estimation                             | 43 |

|          |               | 4.4.1   | Soft Error Rate Calculation                                | 44 |

|          |               | 4.4.2   | SEU Injection and Propagation                              | 44 |

|          |               | 4.4.3   | Soft Error Rate Computation                                | 45 |

|          |               | 4.4.4   | SMT Model Count                                            | 46 |

|          | 4.5           | Exam    | ple                                                        | 48 |

|          | 4.6           | Exper   | imental Results                                            | 51 |

|          | 4.7           | Summ    | nary                                                       | 53 |

| <b>5</b> | Effi          | cient S | MT Modeling and Analysis of SEUs Propagation in Com-       | -  |

|          | bina          | ational | Circuits                                                   | 55 |

|          | 5.1           | Introd  | luction                                                    | 55 |

|          |               |         |                                                            |    |

|                  | 5.2            | Model  | ling of RTL Constructs                     | 56 |

|------------------|----------------|--------|--------------------------------------------|----|

|                  |                | 5.2.1  | Bit-Vector Signals                         | 57 |

|                  |                | 5.2.2  | Logical Operators                          | 57 |

|                  |                | 5.2.3  | Reduction Operators                        | 61 |

|                  |                | 5.2.4  | Arithmetic Operators                       | 64 |

|                  |                | 5.2.5  | If Statements and Case Statements          | 64 |

|                  |                | 5.2.6  | Concatenation, Extraction, and Extension   | 65 |

|                  | 5.3            | Analy  | sis of SEUs Propagation and SER Estimation | 65 |

|                  | 5.4            | Exam   | ple                                        | 67 |

|                  | 5.5            | Exper  | rimental Results                           | 70 |

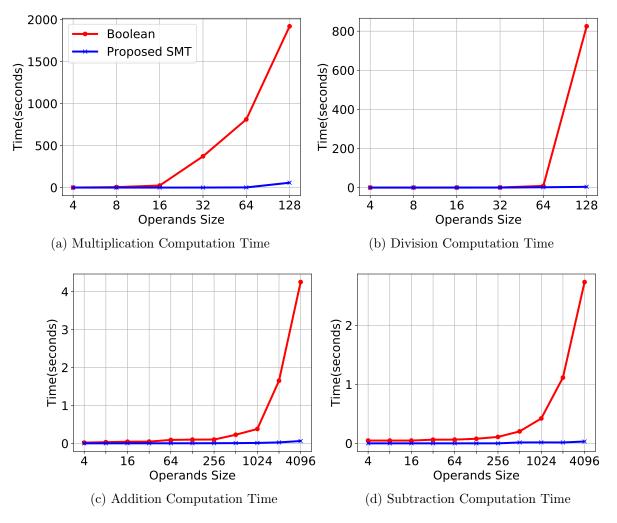

|                  |                | 5.5.1  | Performance Analysis                       | 71 |

|                  |                | 5.5.2  | Accuracy Analysis                          | 73 |

|                  | 5.6            | Summ   | nary                                       | 76 |

| 6                | Con            | clusio | n and Future Work                          | 77 |

|                  | 6.1            | Concl  | usion                                      | 77 |

|                  | 6.2            | Future | e Work                                     | 78 |

| Bi               | ibliog         | graphy |                                            | 79 |

| $\mathbf{A}_{]}$ | ppen           | dices  |                                            | 86 |

| A                | $\mathbf{Pyt}$ | hon Sl | MT Library of RTL Constructs               | 87 |

|                  | A.1            | Logica | al AND Operator                            | 87 |

|                  | A.2            | Logica | al OR Operator                             | 88 |

|                  | A.3            | Logica | al XOR Operator                            | 88 |

|                  | A.4            | Logica | al NOT Operator                            | 88 |

|                  | A.5            | Reduc  | ced AND Operator                           | 89 |

|                  | A.6            | Reduc  | ced OR Operator                            | 89 |

|                  | A.7            | Signed | d Extend Operator                          | 89 |

|                  | A.8            | Unsig  | ned Extend Operator                        | 90 |

| в | Python Soft Error Analysis Scripts | 93 |

|---|------------------------------------|----|

|   | A.14 Division Operator             | 92 |

|   | A.13 Multiplication Operator       | 91 |

|   | A.12 Subtraction Operator          | 91 |

|   | A.11 Addition Operator             | 91 |

|   | A.10 Extract Operator              | 90 |

|   | A.9 Concatenation Operator         | 90 |

# List of Figures

| 3.1 | Example of Fault Propagation in a 2-bit Multiplexer                         | 20 |

|-----|-----------------------------------------------------------------------------|----|

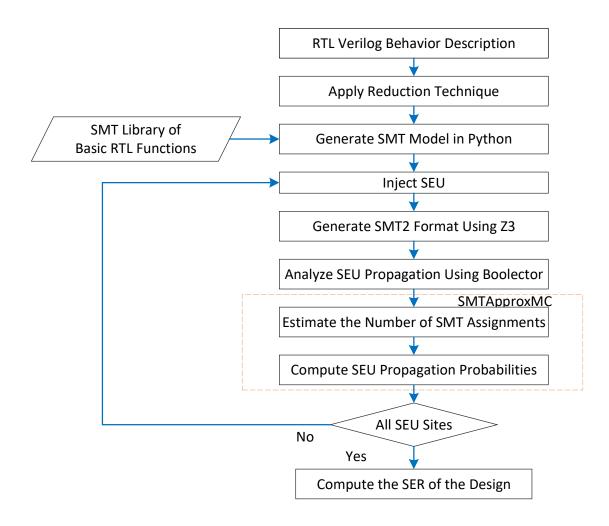

| 3.2 | Main Steps of the Proposed Methodology                                      | 21 |

| 3.3 | Proposed Modeling of SEU Propagation Using the Fault-Free and Faulty        |    |

|     | Versions Model                                                              | 23 |

| 3.4 | RTL Structure of the 74L85 Benchmark That is a 4-bit Magnitude              |    |

|     | Comparator                                                                  | 27 |

| 3.5 | RTL Structure of the 74283 Benchmark that is a Fast Adder Circuit .         | 30 |

| 4.1 | Main Steps of the Proposed Methodology for the Analysis of SEU              |    |

|     | Propagation in Sequential Circuits                                          | 39 |

| 4.2 | Methodology for Fault Propagation Analysis in Sequential Circuits Us-       |    |

|     | ing Unrolling                                                               | 42 |

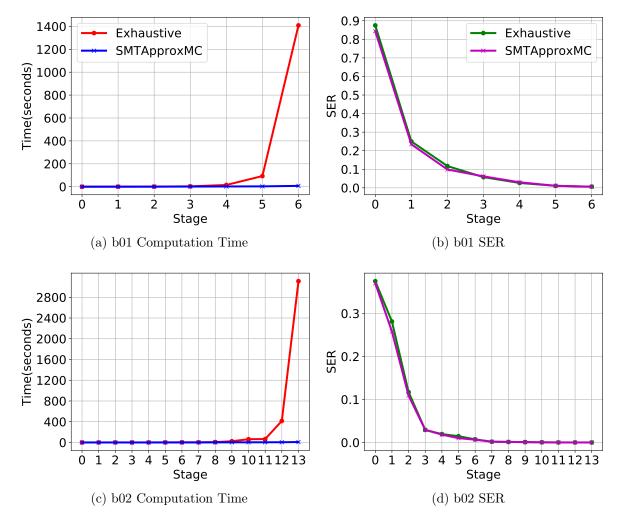

| 4.3 | Comparison of the Computation Time and SER Between Exhaustive               |    |

|     | Model Counting and SMTApproxMC                                              | 53 |

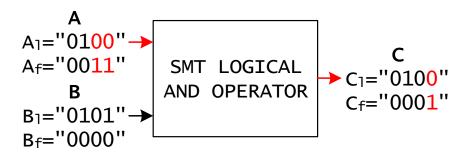

| 5.1 | SMT Logical And Operator                                                    | 58 |

| 5.2 | ${\it Main Steps of the Proposed Modeling and Analysis of SEU Propagation}$ |    |

|     | at RTL                                                                      | 66 |

| 5.3 | RTL Structure of the 74L85 Benchmark that is a 4-bit Magnitude              |    |

|     | Comparator                                                                  | 68 |

| 5.4 | Comparison of the Computation Time Between the Boolean Based                |    |

|     | Modeling and the Proposed SMT Modeling for Different Sizes of Arith-        |    |

|     | metic Operations                                                            | 73 |

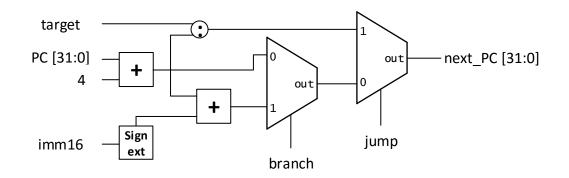

| 5.5 | Program Counter Datapath                                                    | 75 |

# List of Tables

| 1  | SEUs Propagation Probabilities for the 74L85 4-bit Magnitude Com-              |    |

|----|--------------------------------------------------------------------------------|----|

|    | parator Circuit                                                                | 29 |

| 2  | Comparison Between the SER of the Concrete Modeling Technique                  |    |

|    | and the Abstract Modeling Technique                                            | 33 |

| 3  | Comparison Between the Computation Time for the Concrete Model-                |    |

|    | ing Technique and the Abstract Modeling Technique $\ \ldots \ \ldots \ \ldots$ | 35 |

| 4  | The Ratio of the Speed-Up in CPU Time over the Percentage Difference           |    |

|    | in Computed SER                                                                | 36 |

| 5  | SER of 4-bit Unsigned Up Counter with Synchronous Reset for Stage              |    |

|    | 0 and Stage 1                                                                  | 50 |

| 6  | SER of 4-bit Unsigned Up Counter with Synchronous Reset for Stage              |    |

|    | 2 and Stage 3                                                                  | 51 |

| 7  | Computation Times and SERs for ITC99 Benchmark Circuits $\ . \ . \ .$          | 54 |

| 8  | Logical Operators SMT Function Table                                           | 61 |

| 9  | SEU Propagation Probabilities and Derived Vulnerabilities for the $74L85$      |    |

|    | 4-bit Magnitude Comparator Circuit                                             | 69 |

| 10 | Comparison of the Computation Time between the Proposed Method-                |    |

|    | ology, the Technique Proposed in [1] and the Two-Versions Technique            | 72 |

| 11 | Comparison of the Computed Soft Error Rate (SER) Between the                   |    |

|    | Proposed Methodology, the Technique Proposed in [2] and the Two-               |    |

|    | Versions SMT Modeling                                                          | 74 |

|    |                                                                                |    |

### List of Acronyms

| COTS  | Commercial Off The Shelf             |

|-------|--------------------------------------|

| PRISM | Probabilistic Symbolic Model Checker |

| SAT   | Boolean Satisfiability Problem       |

| SEE   | Single Event Effect                  |

| SET   | Single Event Transient               |

| SEU   | Single Event Upset                   |

| SMT   | Satisfiability Modulo Theories       |

# Chapter 1

# Introduction

A Single Event Upset (SEU) is a type of Single Event Effect (SEE). SEEs can be caused by galactic cosmic rays, cosmic solar particles or trapped protons in radiation belts [3]. SEEs induced by heavy ions, protons, and neutrons can seriously affect the reliability of electronic devices. For this reason, this has stimulated research on understanding and reducing the effects of SEEs by means of mitigation techniques [4]. Cosmic ray neutrons were recently found to cause errors even at ground level [5].

SEUs are a major source of soft errors in digital designs and modern electronic systems. Soft errors induced by SEUs have become one of the most challenging issues that impact the reliability of modern electronic systems. Digital circuits are more vulnerable to SEUs as the technology scales down. It is important to analyze and estimate the impact of SEUs on the behavior of digital designs.

In this section we present the motivation behind our work. We first discuss why there is a need to develop better and more efficient techniques to analyze the impact of SEUs in digital circuit early in the design cycle. We then discuss the contributions and the outline of this thesis.

### 1.1 Motivation

Soft errors induced by Single Event Effects (SEEs) such as Single Event Upsets (SEUs) and Single Event Transients (SETs) have become one of the most challenging issues that impact the reliability of modern electronic systems. The Soft Error Rate (SER) per chip has been reported to increase 100-fold from the 180nm to the 16nm CMOS technology nodes [6].

Aggressive technology scaling over the last several decades has made it harder for designers to guarantee the correct functionality of chips in the field. Although exponential growth in the number of transistors per chip has brought tremendous progress in the performance of semiconductor devices, it has increased their vulnerability to soft errors. Soft errors due to SEUs are one of the major reliability concerns in digital designs. There is, therefore, a growing need to analyze and estimate the impact of soft errors at an early stage in the design cycle.

A single particle hit on the state elements of a digital circuit can propagate through the circuit and affect the output at different clock cycles. Thus, in order to achieve cost efficient and reliable computing, it is crucial to take the reliability into consideration alongside the conventional area, power, and performance metrics in the design flow.

Moreover, analyzing soft errors in digital circuits is even more important due to the increased demand of commercial off the shelf (COTS) electronic components for avionics.

SEUs were responsible for the catastrophic failure and the recall of many safety critical systems. Such systems include implantable cardiac pacemakers [7] and implantable cardiac defibrillators [8].

This kind of failure has made it critical to analyze the vulnerability to soft errors and to apply efficient fault mitigation techniques to circuits used in critical systems. It is much more efficient for designers to apply fault mitigation techniques, such as Triple Modular Redundancy (TMR) [9], early in the design cycles.

Most contemporary techniques analyze the effect of SEUs and SETs at circuit

level and gate level. SETs are affected by logical masking, electrical masking and latching window masking, while SEUs are only affected by logical masking. SETs are pulses with a certain duration and therefore, they can be masked due to electrical masking. For an SET or an SEU to propagate, it must be on a sensitized path from the location where it occurred to a primary output or a state element. This means that it should not be masked by the logical operations of the gates on its propagation path. For an SET, depending on the electrical properties of the gates it goes through on its propagation path, its duration (or pulse width) can be attenuated and masked before reaching a latch. If the pulse does not reach the state elements within the latching window, it is said to be masked by the latching window.

SEUs occur directly at the state elements, i.e., a bit-flip due to a direct particle hit, occurs at the latch itself. In this case, only logical masking can prevent an SEU from propagating to the primary outputs of a combinational circuit, or other state elements at subsequent clock cycles. Consequently, RTL descriptions of digital circuits provide sufficient information to analyze the propagation of SEUs, since only information regarding logical masking properties is required.

Early in the design cycle, digital circuits are defined at higher abstraction levels. This work deals with the soft error analysis of circuits described at Register Transfer Level (RTL). At RTL, circuit level details are not available and therefore this work focuses on the analysis of SEUs propagation in combinational and sequential circuits.

Conventionally, analyzing soft error glitches was done at circuit level, which requires a level of detail not available early in the design flow. However, applying mitigation techniques at later stages in the design cycle can be very costly. For this reason, there is an important need to develop techniques to analyze the impact of SEUs earlier.

At circuit level, parameters extraction and detailed simulations can provide a certain level of accuracy for phenomena such as electrical masking and SET width variation. However, when dealing with SEUs, this level of detail is not necessary. Moreover, the analysis at circuit level is very computationally intensive and would be intractable at the chip level. In other words, this type of analysis could be conducted on hundreds of transistors at most. Moreover, this type of approach are not applicable to RTL level constructs, due to a much higher level of abstraction. Therefore, the techniques at circuit level are not efficient to model SEU propagation at RTL.

At gate level, several techniques have been developed to analyze the effects of SEUs and SETs. Performing such analysis at the gate level requires the synthesis of RTL designs to gate level to be able to analyze their vulnerability to SETs and SEUs. Some of these techniques are very resource hungry and fail to analyze complex digital designs.

At RTL, the state of the art is lacking in techniques to analyze the soft error rates. At higher level of abstraction, the work focuses on analyzing the propagation of SEUs, since in RTL descriptions, loading and timing details are not available. Although some techniques allow the analysis of SEUs at high level, they still require the synthesis of RTL designs, due to their inability to model the higher level constructs used at RTL, e.g. *case* statements, *if* statements and linear arithmetic.

As we will see in Section 2.2.2, some techniques have recently been proposed to analyze SEU propagation at RTL. Researchers have proposed modeling approaches that use probabilistic model checking while other techniques use Boolean Satisfiability (SAT) modeling to analyze soft errors at RTL. Some of these techniques fail to handle moderately sized circuits while others cannot handle high level RTL constructs. Such techniques will still require the synthesis of the design from RTL to gate level in order to be applicable.

To summarize, due to the risks caused by SEUs in safety critical systems, it has become crucial to develop new techniques to analyze the impact of SEUs on digital circuits. This will give designers better insight regarding design vulnerability to soft errors early in the design stages. Most available techniques can only deal with the analysis of SEU propagation at gate level and circuit level. However, in order to apply efficient fault mitigation techniques, it is important to obtain Soft Error vulnerability in digital designs in early stages of design.

### 1.2 Thesis Contribution

In previous work, SEUs are analyzed at gate level and RTL through simulation based techniques and formal based techniques. Simulation based techniques often suffer from accuracy problems. In fact, even for small designs, simulation for all input vectors to study fault propagation becomes intractable which results in loss of accuracy.

In formal based techniques, several methodologies were proposed. Such techniques include modeling the SEU propagation at RTL as Discrete Time Markov Chains (DTMCs) such as [10] and [2]. Those properties are then verified against the constructed model using the PRISM model checker [11]. Some techniques use SAT Solvers to model the propagation of SEUs at RTL such as [1]. Using Pure Boolean SAT to model RTL constructs require to convert most RTL operations to Pure Boolean form. Therefore, those techniques require the synthesis of the design into a gate level netlist to be able to analyze the SEU propagation using a set of assertions.

In this work, we propose a new modeling and analysis approach to verify the propagation of SEUs using Satisfiability Modulo Theories (SMTs). Our approach is significantly faster than simulation based techniques while still offering great accuracy. Our technique is used to compute propagation probabilities and the Soft Error Rate (SER). The SER is essentially a measure to estimate the overall vulnerability of a circuit. Our work focuses on the logical masking property since at RTL, the information for electrical masking and latching window masking is not available. We model and analyze the fault propagation problem into a satisfiability problem using SMT and the Microsoft Z3 SMT solver [12].

We investigate the benefits and disadvantages of using a data type reduction technique with our proposed SMT modeling of SEU propagation. We also investigate the advantages of using SMT modeling over Pure Boolean SAT modeling when analyzing high level RTL circuits. SMTs allow to model RTL constructs into SMT format and verify the SEU propagation against a set of assertions. The advantage of SMT over SAT, is that SAT based techniques require the use of synthesis tools, to take the RTL hardware description and produce a gate level netlist in order to apply the SAT level modeling.

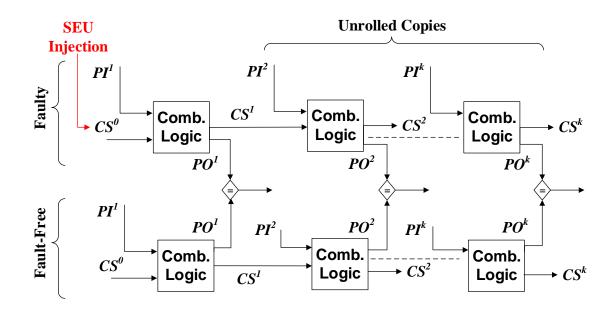

We use our approach to analyze the vulnerability of combinational circuits at first, then the technique is extended and applied to sequential circuits. At first, the developed SMT model will use two copies of the design, one fault-free and one faulty version. The SEU is injected at one version and the outputs are compared to check fo fault propagation. For analyzing SEU propagation in sequential circuits, the combinational part of the design is unrolled to simulate the propagation of SEU through several clock cycles.

To improve our first modeling approach, we developed a library of SMT functions using Microsoft Z3's Python API [12]. The purpose of this new approach, is to create Python functions that use SMT operations to model the basic Verilog and VHDL RTL operations by including the fault propagation properties within the functions. This allows to directly model RTL designs without requiring two copies of the design.

In addition to the proposed modeling, we investigate the applicability of the proposed analysis by analyzing the vulnerability of several benchmark circuits from the ISCAS85 benchmarks [13] for combinational circuits and from the ITC99 benchmarks [14] for the sequential circuits.

To the best of our knowledge, techniques to model the propagation of SEUs at RTL using SMT have not been previously proposed. Our work was published in [15], [16] and [17].

#### 1.3 Thesis Outline

The rest of this thesis is organized into four more chapters. In Chapter 2, we provide some preliminaries on the subject. We start by describing what SEEs are and discussing the difference between SETs and SEUs. Then we introduce the current state of the art at gate level and at RTL. Following this we describe what is Boolean Satisfiability (SAT) and Satisfiability Modulo Theories (SMTs) and their applications.

In Chapter 3, we present our first approach at modeling combinational circuits using SMTs. To investigate the vulnerability to Soft Error, we use an approach involving two copies of the circuits under test. We also investigate the impact of a data type reduction technique on the accuracy and efficiency of the analysis. In order to do so, two modeling techniques are developed, concrete and abstract modeling.

In Chapter 4, we model and investigate the propagation of SEUs in sequential circuits. The modeling proposed in this chapter allows the analysis of SEUs propagation from each vulnerable node to the output of subsequent cycles of the sequential circuit. This is done by using multiple unrolled copies of the design to represent multiple state transitions of the sequential circuit. Moreover, the proposed modeling and analysis provides an early estimate of the Soft Error Rate (SER) of the design based on an approximate model counting approach.

In Chapter 5, we present a new modeling approach which embeds the fault propagation properties within the SMT model of the RTL design itself. In this approach, one copy of the design is used. For the analysis, an SMT model approximate counter is used to investigate the propagation of SEUs. Moreover, to investigate the efficiency of SMT versus Pure Boolean SAT in modeling RTL circuits, a comparison of the performance of the two modeling approaches is done on different sizes of arithmetic circuits.

# Chapter 2

# Preliminaries and Related Works

In this chapter we discuss the preliminaries and the related works. The goal of this chapter is to give the reader the required information to better understand the motivation behind our work and the tools required.

First, we define the Single Event Upset (SEU) and the logical masking effect. Next, we present the various state of art techniques at the gate level and Register Transfer level (RTL). We also provide an overview of Boolean Satisfiability (SAT) and Satisfiability Modulo Theories (SMT) as well as their respective most popular solver engines.

### 2.1 Single Event Upsets

A Single Event Upset (SEU) is a type of Single Event Effect (SEE). SEEs can be divided into two main categories: Destructive SEEs and Non-Destructive SEEs, also known as Hard Errors and Soft Errors respectively. This work focuses on the Non-Destructive SEEs (Soft Errors) and more specifically on SEUs. The two main types of Non-Destructive SEEs are Single Event Upsets (SEUs) and Single Event Transients (SETs). Both of those single events change the state of a device without affecting its functionality. In other words, an SET or an SEU can potentially propagate to one or several outputs, thus causing an error, but the overall functionality of the circuit is not permanently affected.

In combinational logic, SETs are transient pulses generated in a gate that may propagate in a combinatorial circuit path and eventually be latched. SETs cause data on a wire to change logic for a short period of time. They are represented as a pulse with a certain duration and polarity, i.e., a pulse from logic "0" to logic "1" or logic "1" to logic "0".

In memory devices, single event effects are called SEUs. An SEU is said to have occurred when a change in the state of a storage element such as memory or registers has occurred. SEUs have no pulse width, since they affect memory elements, when they occur, the value of the bit is flipped. On the other hand, in combinational logic, SETs are transient pulses that occur in a gate and may propagate through the combinational path and be latched by a flip-flop. SETs may potentially never be latched in a flip-flop if their pulse width is not strong enough.

The propagation of SETs through combinational designs is affected by logical, electrical and temporal masking (latching window masking) while the propagation of SEUs is only affected by logical masking. The low-level circuit details, that are required to analyze electrical masking and temporal masking, are not yet available in RTL descriptions of designs. Therefore, at RTL, the vulnerability of circuits can only be analyzed due to SEUs.

The effects that can prevent an SEE from propagating to an output are logical masking, electrical masking and latching window masking. It is important to note that all three effects can prevent an SET from propagating due to its nature, i.e., a pulse with a certain width. On the other hand, only logical masking affects SEU propagation, which are bit-flips that occur at flip-flops. The masking effects can be described as follows:

- 1. Logical masking: An SET or SEU can propagate if the input vector opens a sensitized path so that it reaches the design output.

- 2. Electrical masking: An SET requires a minimum width, which can be affected

by the gates on its propagation path, in order to reach the primary outputs or flip-flops.

3. Latching window masking: An SET can be latched by a register if it reaches the registers within the latching window with a large enough pulse width.

Soft errors occur when an SEU reaches the primary outputs of a design. SEUs can only be affected by logical masking. As mentioned earlier, logical masking can be described as follows: to cause an error, an SEU must propagate on a sensitized path from the location where it occurred to a primary output or a latch. When an SEU reaches the input of a gate, the fault will be logically masked if at least one of the other inputs of the same gate has a controlling value. This will prevent the SEU to reach any of the outputs and causing an error.

The same logic that is applied to these basic gate level operations is applicable to the equivalent logical operators at RTL. Different operators have different controlling logic and different logical masking probabilities. The *NOT* operator will always propagate an error since its output depends on only one input. The propagation probability for the *AND*, *OR*, *NAND* and *OR* operators depends on the number of inputs of the operator. The *AND* and *NAND* operators have a controlling logic of "0" while the *OR* and *NOR* operators have a controlling logic of "1". For example, for an *AND* operator with 2 inputs, if one of the inputs has a logic value "0" (controlling logic), the output of the operator will be "0" regardless of the value of the other input. Therefore, an error at the other input will be logically masked. Furthermore, an SEU will always propagate through an *XOR* and *XNOR* operators.

Higher level synthesizable RTL constructs have an equivalent gate level representation. Therefore, any information regarding logical masking that is acquired from RTL descriptions of designs is equivalent to information gathered at the gate level. This is due to the fact that logical masking only depends on the logical operations of the circuit. The logical masking effect depends on the inputs, since for different input vectors, different paths are sensitized. In the following chapters, the computation of the SEU propagation probabilities will be used to compute the Soft Error Rate (SER). We will explain in more details, how the propagation probabilities will be computed when analyzing some RTL benchmark circuits.

### 2.2 State of the Art

There has been considerable progress in functional verification of digital designs. However, the same cannot be said about non-functional verification. Non-functional verification investigates the behavior of designs in the presence of different uncertainties. Investigating non-functional properties is challenging due to the complexity of the modeling and the analysis. Moreover, many details about the uncertainties are not available at high abstraction levels.

In this section, we present the state of the art available at the gate level and RTL. Certain techniques analyze SEU propagation while other deal with SET propagation. It should be noted that, techniques that are used to model SET propagation can also be applied to analyze SEUs, since those techniques usually cover the effects of logical masking. The propagation of SET through combinational designs is affected by logical masking, electrical masking and temporal masking. As discussed in Section 2.1, logical masking occurs while the SET or SEU is propagating through a gate and at least one of the other inputs has a controlling logic value (e.g., "**0**" for a *NAND* gate). Electrical masking occurs when the duration of the SET pulse is less than the threshold of the gates on its path before reaching a latch. Temporal masking occurs if the SET pulse arrives at the flip-flop input outside of the latching window of registers.

On the other hand, SEUs occur at registers, and their propagation is only affected by logical masking, which is an effect that most technique that deal with SET propagation cover.

#### 2.2.1 Techniques at Gate Level

Several techniques have been proposed at the gate level to deal with the analysis of SEUs. Those include simulation based techniques such as [18], [19], [20], [21] and formal based techniques such as [22], [23], [24]. More recently, formal techniques using an SMT based approach at gate level have been proposed such as [25].

Simulation based techniques have serious shortcomings as they are very time consuming for large circuits with many primary inputs. Furthermore, these techniques have their drawbacks in terms of accuracy. This is mainly because their accuracy is determined by the ratio of the simulated sample size over the total vector space size. These approaches have a scalability problem and cannot be applied on all types of designs.

The problem with the techniques developed to analyze SEU and SET propagation at gate level is that they cannot be applied at earlier stages in the design. RTL descriptions of digital circuits contain higher level constructs such as *if* statements, *case* statements and linear arithmetic operators that cannot be handled by the above techniques. In the next section, we present a literature review on the current techniques that deal with SEU propagation at RTL.

#### 2.2.2 Techniques at Register Transfer Level

At Register Transfer Level (RTL), there is far less techniques to analyze SEU propagation. However, some techniques to analyze SEU propagation have been proposed. Those include fault simulation techniques such as [18] [26] and formal verification methods such as [10], [1], [2].

However, the techniques to analyze SEU propagation at gate level are not applicable at an early design stage. Moreover, simulation techniques at RTL are very time consuming. Even formal based techniques fail to handle moderately sized circuits. For instance, existing formal based techniques, such as Reduced Ordered Binary Decision Diagrams (ROBDDs) [23] and Multi-Terminal BDDs (MTBDDs) [2], are computationally expensive i.e., suffer from a state explosion problem.

Formal verification based techniques are resource hungry when used to analyze a complex digital design at RTL. For example, formal techniques run out of memory, even when trying to analyze moderate size designs, e.g., a 14-bit adder [10].

Some techniques have been developed to analyze SEU propagation at RTL using Pure Boolean SAT such as [1]. Those techniques require the conversion of the SEU propagation in a behavioral description into an instance of a SAT problem. In order to do this, they require intermediate steps, since pure Boolean SAT cannot support various RTL constructs. The RTL description of the circuit is modified to include the fault propagation properties using a method that uses two copies of the design and compares the outputs using an XOR operation. The resulting RTL description is then converted to an equivalent conjunctive normal form (CNF) which is sent to a SAT solver. The CNF is the equivalent SAT Boolean function converted to a product-of-sums. It contains the logical AND of the set of clauses that represent the formula. This conversion requires two intermediate steps. The modified RTL Verilog description is converted to SMV format using the Cadence SMV tool [27]. Then tools in the AIGER library [28] were used to convert from SMV format to CNF. The resulting CNF file can then be sent to a SAT solver.

In this work we overcome this limitation by using SMT to model SEU propagation. The basic RTL constructs can be modeled directly into SMT format which does not require intermediate conversions steps.

#### 2.3 Boolean Satisfiability (SAT)

SAT is an abbreviation for the Boolean Satisfiability Problem. The SAT problem is the problem of determining whether theres exists a variables assignment such that a given propositional formula evaluates to True. In other words, the problem is to determine whether values (True or False) can be assigned to the variables of the formula for it to be True (satisfiable). If no such assignment can be found, then the formula is said to be UNSAT, or unsatisfiable.

The problem of Boolean Satisfiability (SAT) is not only of interest in computer science, since it has also received great attention in other areas where it has seen significant practical applications [29].

Boolean Satisfiability (SAT) is often used an increasing number of applications in Electronic Design Automation (EDA) as well as many other engineering fields [30]. More specifically, SAT has been used to formulate EDA problems such as test pattern generation, circuit delay computation, logic optimization, combinational equivalence checking, bounded model-checking and functional test vector generation.

Some well known SAT solvers include: MiniSat [31], MiniSat2 [32], PicoSAT [33], RSat 2.0 [34] and Glucose [35].

### 2.4 Satisfiability Modulo Theories (SMT)

The advent of Satisfiability Modulo Theories (SMTs) [36] solved the problem of being restricted to a pure Boolean representation, which is not efficient and sometimes inadequate when representing several classes of systems. SMT is an extension of the SAT decision problem, where the formulas are expressed in first-order logic, with associated background theories. SMTs have been used to model and solve software and hardware engineering problems. In this work, we show how linear arithmetic and bit-vector theories can be used to model SEUs propagation.

SMT solvers that support the theory of bit-vectors provides concrete models for bit-vector operations. Bit-vectors can be used to model designs directly on the wordlevel. This proves to be useful when converting bit-vector RTL operations to SMT operations.

High level behavioral and structural RTL descriptions of circuits include a variety of RTL operations not available at gate level. This includes arithmetic operations operations, *if* statements and *case* statements. SMT solvers support bit-vector arithmetic operations such as addition, subtraction, multiplication and division. Moreover, they support *If-Then-Else* statements (*ITE*).

Some modern SMT solvers include: Microsoft Z3 [12], Boolector [37], Yices [38], Yices 2 [39] and CVC4 [40].

### 2.5 Summary

In this chapter, we discussed the preliminaries required to better understand our proposed methodology. We described SEUs and their effects on modern digital circuits. Then we discussed the related works dealing with the analysis of SEUs both at the gate level and RTL level. There are far more techniques developed to tackle this problem at gate level. We described Boolean Satisfiability (SAT) and Satisfiability Modulo Theories (SMT) in order to understand the main differences and our motivation behind using SMT to model the problem of SEU propagation.

# Chapter 3

# Concrete and Abstract SMT Modeling and Analysis of SEUs Propagation in Combinational Circuits

### 3.1 Introduction

In this chapter, a methodology is proposed to analyze Single Event Upset (SEU) propagation in combinational designs described at Register Transfer level (RTL). In this approach we use a well-known technique that utilizes two copies of a given design, one fault-free and one faulty, where an SEU is injected. The accuracy of the two-versions modeling approach was proven in [1]. The outputs of both copies are then compared to check if they are different. In that case, the SEU propagated to the output and caused an error.

Our methodology utilizes Satisfiability Modulo Theories (SMT) to model SEU propagation in RTL designs as a Satisfiability problem. We propose two modeling approaches to analyze the vulnerability of RTL designs to SEUs, i.e., concrete modeling and abstract modeling.

- 1. Concrete Modeling of SEU Propagation: In this approach, the generated SMT models preserve the full functionality of the RTL description and is modeled using the SMT theory of bit-vectors. Two copies of the generated SMT model are used, the first is a fault-free version and the second is a faulty version where an SEU is injected. The outputs of both circuits are compared to check if the SEU caused an error at the output.

- 2. Abstract Modeling of SEU Propagation: In this approach, based on a SEU injection scenario, the SMT model is reduced to improve the scalability by adapting the data type reduction technique used in [2]. This technique is a form of abstraction which comprises two main elements. First, bit-vectors are reduced to 1-bit signals and second, operators are abstracted with a simplified error propagation model. As shown later, this simplified error propagation model is often quite pessimistic because it predicts propagation over whole bit-vectors rather than specific bits.

The proposed technique starts by translating the Verilog RTL behavioral description of the design into an SMT equivalent model. RTL operations such as logical, reduction, arithmetic, *if* statements and *case* statements are converted into their SMT equivalent using the theories of bit-vectors and linear arithmetic. Then, based on the adopted modeling approach, the proposed methodology allows the analysis of SEUs propagation using a set of assertions. To estimate the vulnerability of digital circuits, we compute the Soft Error Rate (SER). The SER is a summation of the propagation probabilities of SEUs injected at individual bits, therefore it can be greater than 1.

Experimental results demonstrate that the loss in accuracy due to abstract modeling depends on the design behavior. For example, for some circuits, the loss in accuracy (percentage difference between the computed SERs) was around 187%, while for other circuits it was as low as 0.03%. The percentage of error for individual injection scenarios cannot exceed 100% since the propagation probabilities range from 0 to 1. Since we are computing the percentage difference between the SERs, our values can exceed 100%. However, abstract modeling allows reducing processing time significantly and an average reduction factor of 67.33 is reported. The reported results demonstrate that the abstract modeling technique yields considerable speed-up in computation time at a certain cost in accuracy. The generated results are used to investigate the trade-off between the speed-up of abstract modeling and the accuracy of concrete modeling.

The rest of this chapter is organized as follows. Section 3.2 explains the data type reduction technique used and how it affects the accuracy of SEU propagation analysis. Section 3.3 explains our proposed modeling and the analysis of SEUs propagation at RTL. In Section 3.4, we explain our experiments and results. Section 3.5 concludes by summarizing the analysis and experiments.

### 3.2 Data Type Reduction

Existing formal analysis methods can be combined with different reduction techniques to improve their scalability. SEUs propagation behavior at RTL can be reduced using a data type reduction technique. The data type reduction technique proposed in [2] is adapted to our SMT model to investigate its effect on our modeling approach. In this work, we define the data type reduction technique used as follows:

- 1. For a bit-vector signal, if one bit is faulty, then the whole vector is considered faulty. In other words, a multi-bit signal is considered as a 1-bit signal.

- 2. SEU propagation through register transfer operations such as addition and multiplication is modeled to transparently propagate from inputs to outputs. This modeling loses track of the exact location of faults. For example, in an addition involving two input *n*-bit signals **A** and **B** and output **C**, a fault occurring at bit k of signal **A**, cannot propagate to bit i of output **C**, given i < k. These details would be abstracted when using a data type reduction technique. A

faulty input signal in an addition operation will automatically imply a faulty output, without providing details regarding specific bit vulnerabilities.

3. For a *case* statement or a block of *if* statements, which represents a multiplexer, if the selection signal is faulty, then the output is considered to be faulty as well, regardless of the values of the input signals. If one of the input signal is faulty, the output will be faulty if the selection signals currently select the faulty input.

The main issue with the utilization of such a reduction technique is that we lose track of the exact error location. In other words, it is not possible to identify the specific faulty bits in the bit-vector signals.

To better understand the impact of such modeling, consider the RTL signal assignment shown in Listing 3.1. The bit-vectors **next\_addr** and **start\_addr** are 32-bit signals.

| $next_addr = start_addr + 4;$     |

|-----------------------------------|

| $addr_msb = next_addr[31:16];$    |

| $addr_{lsb} = next_{addr}[15:0];$ |

Listing 3.1: RTL Assignment Example

Instead of performing an SEU injection at every bit of the 32-bit start\_addr signal, the signal is reduced to a single bit. It is assumed that if start\_addr is faulty, then next\_addr is faulty.

However, a certain output of the circuit may only depend on the value of certain bits of the **next\_addr** signal while the fault is present in some other bits. In Listing 3.1, the **addr\_msb** signal depends on the uppermost 16 bits of **next\_addr** while **addr\_lsb** depends on the lower 16 bits. In this case, the output may mistakenly be considered faulty for several SEU injection scenarios.

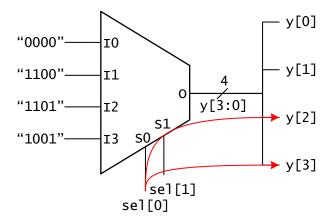

As another example, consider the 2-bit RTL multiplexer shown in Figure 3.1.

If the select signal sel is faulty, then the output  $\mathbf{y}$  is considered as faulty. However, in this example, a faulty sel signal can cause at most 2 bits of  $\mathbf{y}$  to be faulty.

Figure 3.1: Example of Fault Propagation in a 2-bit Multiplexer

If sel[0] signal is faulty, then this fault will only propagate to y[2] and y[3]. The propagation of the fault is conditional on having an active path from the sel signal to the output i.e., the fault is not logically masked. Given sel[0] is faulty, an error will occur at y[3] only if sel[1] is "0". On the other hand, a fault at sel[0] will always propagate to y[2], regardless of the state of sel[1]. Similarly, a fault at sel[0] will never propagate to outputs y[0] and y[1]. However, this level of detail is fully abstracted when using this data type reduction technique. Therefore, the computed vulnerability of the circuit is inaccurate.

### 3.3 Proposed Methodology

The proposed methodology introduces a new formal modeling and analysis of SEU propagation at RTL using Satisfiability Modulo Theories. In this section, we propose two modeling approaches: concrete and abstract modeling.

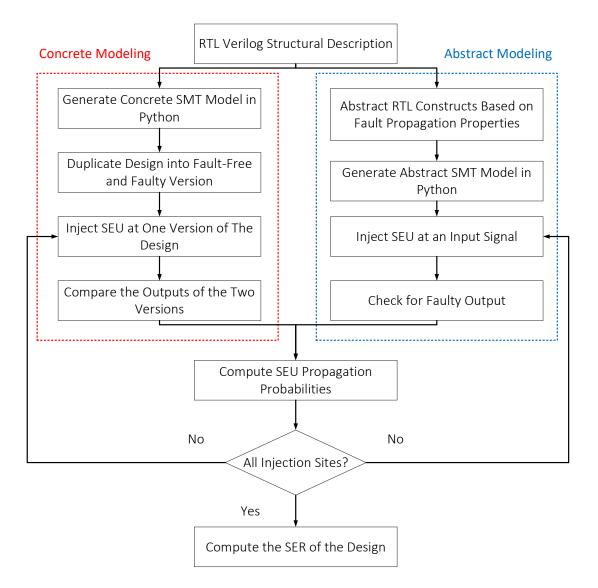

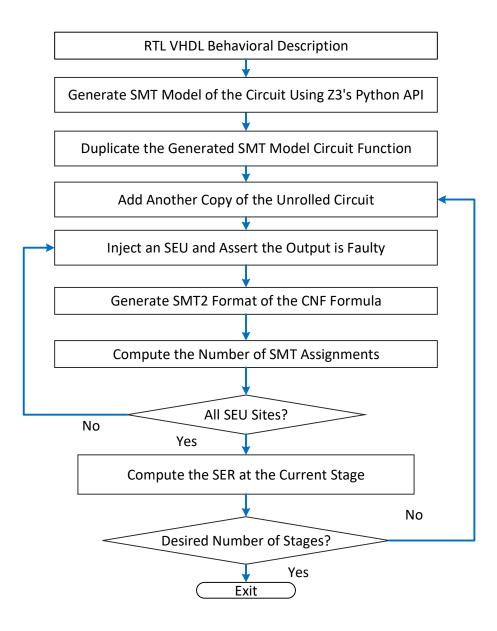

The main steps of both approaches are presented in Figure 3.2. For both modeling techniques, the RTL signals and operations are converted into SMT format. The SMT solver used to model and analyze the propagation of SEUs in the RTL circuits given is Microsoft's Z3 [12]. In order to automate the analysis steps such as fault injection and

SEU propagation probability computation, we used Python scripting. Microsoft's Z3 provides a Python API for such application.

Figure 3.2: Main Steps of the Proposed Methodology

#### 3.3.1 Concrete Modeling

The modeling and analysis starts with an RTL Verilog description of the designs under test.

#### Generate Concrete SMT Model in Python

The first step in our methodology for the concrete modeling approach, shown in Figure 3.2, is to convert the RTL Verilog description into a Python SMT model. The SMT library includes operators supporting the theory of bit-vectors, which allows us to model basic bit-vector arithmetic and bitwise operations. Therefore, all RTL bit-vector operations were modeled using the SMT library. The circuit under test will be modeled as a Python function and maps the RTL constructs to equivalent SMT operations. The input parameters of the Python function representing the circuit are the primary inputs of the circuit and the function will return the outputs as shown in Listing 3.2.

```

def circuit (PI):

...

Circuit Logic

...

return PO

```

Listing 3.2: Python Function Defining the Combinational Circuit

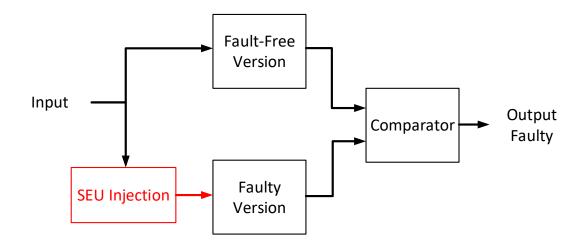

#### Duplicate design into fault-free and faulty version

The generated model is then duplicated into one version considered as the fault-free and the other as the faulty version as shown in Figure 3.3. The SEUs are injected at the inputs of the faulty version of the circuit. The inputs of the combinational circuits are assumed to be latched. The outputs of the faulty and fault-free versions of the combinational circuits are compared to check if the SEU caused an error at the output.

This is done in the SMT Python model by having two sets of inputs (i.e. **PI** and **PI\_f**) and two sets of outputs (i.e. **PO** and **PO\_f**) to represent the fault-free and faulty versions as shown in Listing 3.3.

Figure 3.3: Proposed Modeling of SEU Propagation Using the Fault-Free and Faulty Versions Model

PO = circuit(PI) $PO_f = circuit(PI_f)$

Listing 3.3: Python Functions of the Fault-Free and Faulty Versions

#### Inject SEU at one version of the design

The input vectors of both versions are asserted to be equal except for 1 bit. For a *n*-bit input vector A, all bits are asserted to be equal except for a bit k, where k < n - 1 as shown in Listing 3.4. The variable **formula** is a list containing all the assertions for a specific injection scenario. The next step is to add the assertions for fault propagation then check for the Satisfiability of the conjunction of all assertions added to the **formula**.

```

def injectSEU(k):

formula = []

for i in range(n):

if(i == k):

formula.append(Extract(i,i,PI) != Extract(i,i,PI_f))

else:

formula.append(Extract(i,i,PI) == Extract(i,i,PI_f))

return formula

```

Listing 3.4: Fault Injection Function

#### Compare the outputs of the two versions

In [1], the fault injection and output comparison mechanisms are added to the design in the RTL description of the design and then the whole design is converted into a SAT instance. The outputs of the fault-free design and the faulty version are compared using an **XOR** operation. Every output bit of the fault-free version is **XOR**ed with its corresponding output bit in the faulty version. For each **XOR** operation, if the output is a "1", it means that the SEU propagated to this specific output bit. The outputs of the **XOR** operations are then **OR**ed together to generate one output. This output bit is a "1" if the injected SEU propagated to at least one output, otherwise it is a "0". The RTL Verilog was then converted into SMV format and then the SMV format was converted to CNF which is then sent to the SAT Solver.

In our modeling, the RTL Verilog designs are directly converted into SMT format without intermediate conversion steps. Therefore, SEU propagation is analyzed by simply verifying that the outputs of the faulty and fault-free versions are not equal as shown in Listing 3.5.

| $formula.append(PO != PO_f)$ |  |

|------------------------------|--|

|                              |  |

#### Listing 3.5: Fault Propagation Assertion

In this assertion, we verify if under any input condition the injected SEU will lead to an error at the output, i.e., the output of the faulty version is not equal to the output of the fault-free version.

#### 3.3.2 Abstract Modeling

In this approach, we adapt the data type reduction technique used in [2]. The purpose of this approach is to investigate the effect and the applicability of a data type reduction technique on the modeling proposed in Section 3.3.1. The main steps of this modeling technique are shown in Figure 3.2.

The first steps starts by abstracting all RTL signals and operations based solely

on fault propagation properties, i.e., the correct functionality of the circuit is not preserved. The multi-bit vectors are reduced to smaller bit-vectors. This results in a much smaller circuit and a smaller input vector search space.

RTL assignments, such as in Listing 3.1, are reduced to 1-bit operations. This is equivalent to a transparent channels, i.e., a faulty **start\_addr** will result in a faulty **next\_addr** signal. Since bit-level information is not available using the data type reduction technique, this directly implies faulty **addr\_msb** and **addr\_lsb** signals.

#### 3.3.3 Estimate SER due to SEUs

In order for an SEU to result in a soft error, it must reach the primary outputs of the design. In other words, an active path must exist between the node or register where the SEU originates and the primary outputs of the circuit. If no active path exists, an SEU is said to be logically masked by the logical operation on its propagation path.

The probability that the injected SEU propagates to the output is computed as shown in equation (1). This probability is computed by dividing the total number of satisfying assignments (i.e.,  $Num\_Assignments$ ) over the reduced randomized search space N of the total number of possible input vectors.

$$P(SEU_i) = \frac{Num\_Assignments_i}{N} \tag{1}$$

The Soft Error Rate (SER) is a rate used to classify the vulnerability of digital circuits to Soft Errors. In this specific case, we define the SER as being the summation of the propagation probabilities of all injections scenarios to any output.

Therefore, the Soft Error Rate (SER) of a design, which has m fault injection sites, is calculated as follows:

$$SER = \sum_{i=0}^{m-1} P(SEU_i) \tag{2}$$

#### 3.3.4 SMT Model Count

In equation (1), *Num\_Assignments*, represents all satisfiable assignment for a given formula representing an SEU injection scenario. This number is computed iteratively by generating all solutions as shown in Listing 3.6. After generating the formula that includes the fault injection and propagation assertions, the total model count is computed and divided over the total search space to compute the vulnerability (denoted as vuln).

In this function we generate all satisfiable assignments using Z3's Python API. In order to do so, we generate a satisfiable assignment for the current injection scenario, and then add a new constraint that prevents the previous model from being generated again. This is repeated until the formula becomes unsatisfiable. This algorithm is shown in Listing 3.6.

```

def genModels(formula):

s = Solver()

s.add(formula)

count = 0

while(s.check() == sat):

m = s.model()

block = [x != m.eval(x) for x in variables]

s.add(Or(block))

count += 1

return count

```

Listing 3.6: Function to Generate All Satisfiable Assignments of a Given Formula

#### 3.3.5 Examples

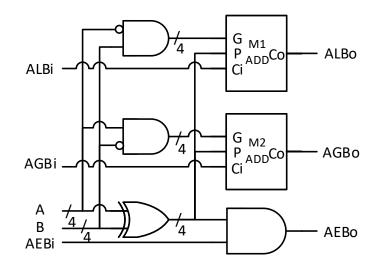

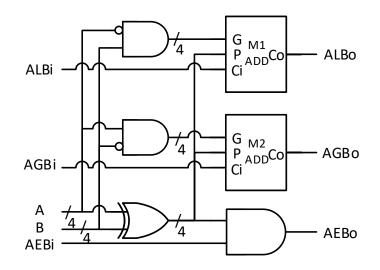

As an example, the proposed methodology was implemented on the 4-bit magnitude comparator circuit shown in Figure 3.4 to illustrate its main steps and investigate the results.

Figure 3.4: RTL Structure of the 74L85 Benchmark That is a 4-bit Magnitude Comparator

The comparator has 11 inputs and 3 outputs. The Verilog behavioral model of the circuit is shown in Listing 3.7.

```

module 74L85 (ALBi, AGBi, AEBi, A, B, ALBo, AGBo, AEBo);

input [3:0] A, B;

input ALBi, AGBi, AEBi;

output ALBo, AGBo, AEBo;

wire [4:0] CSL, CSG;

assign CSL = ~A + B + ALBi;

assign ALBo = ~CSL [4];

assign CSG = A + ~B + AGBi;

assign AGBo = ~CSG [4];

assign AEBo = ((A == B) && AEBi);

endmodule

```

Listing 3.7: RTL Verilog Description of the 74L85 4-bit Magnitude Comparator Circuit

The RTL Verilog description of the module is then translated into an equivalent SMT model. Using Microsoft Z3's Python API, the description of the circuit is defined within a Python function as shown in Listing 3.8. The function's input parameters are the primary inputs of the designs and it returns the outputs as a tuple, which is a sequence of objects in Python.

```

def circuit (ALBi, AGBi, AEBi, A, B):

CSL = ZeroExt(1,A) + ZeroExt(1,B) + ZeroExt(4,ALBi)

ALBo = \sim Extract(4,4,CSL)

CSG = ZeroExt(1,A) + ZeroExt(1,\sim B) + ZeroExt(4,AGBi)

AGBo = \sim Extract(4,4,CSG)

AEBo = BVRedAnd(\sim (A ^ B)) & AEBi

return ALBo, AGBo, AEBo

```

Listing 3.8: Python Function Definition of the 74L85 4-bit Magnitude Comparator Circuit

In the main part of the program we create SMT bit-vector variables defining the inputs of the design for both the faulty and fault-free versions. Both sets of inputs are used as inputs to the function defining the circuit shown in Listing 3.8. The tuples returned are then unpacked into the outputs of the fault-free and faulty versions. The main part of the program is shown in Listing 3.9.

```

A = BitVec('A', 4)

B = BitVec('B', 4)

ALBi = BitVec('ALBi', 1)

AGBi = BitVec('AGBi', 1)

AEBi = BitVec('AEBi', 1)

A_EBi = BitVec('AEBi', 1)

A_f = BitVec('A_f', 4)

B_f = BitVec('B_f', 4)

ALBi_f = BitVec('ALBi_f', 1)

AGBi_f = BitVec('AGBi_f', 1)

AEBi_f = BitVec('AEBi_f', 1)

AEBi_f = BitVec('AEBi_f', 1)

ALBo, AGBo, AEBo = circuit(ALBi, AGBi, AEBi, A, B)

ALBo_f, AGBo_f, AEBo_f = circuit(ALBi_f, AGBi_f, AEBi_f, A_f, B_f)

```

Listing 3.9: Python Two-Versions Model of the 74L85 4-bit Magnitude Comparator Circuit

The fault injection and propagation assertions are then added to the formula as previously shown in Listing 3.4 and Listing 3.5. The propagation probabilities are then computed for every injection scenario. The results for the 74L85 are shown in Table 1.

| Primary Inputs (PIs)  | <b>Propagation Probability</b> $P(SEU_i)$ |

|-----------------------|-------------------------------------------|

| A[3]                  | 0.765625                                  |

| A[2]                  | 0.53125                                   |

| A[1]                  | 0.28125                                   |

| A[0]                  | 0.15625                                   |

| B[3]                  | 0.765625                                  |

| B[2]                  | 0.53125                                   |

| B[1]                  | 0.28125                                   |

| B[0]                  | 0.15625                                   |

| ALBi                  | 0.0625                                    |

| AGBi                  | 0.0625                                    |

| AEBi                  | 0.0625                                    |

| Soft Error Rate (SER) | 3.65625                                   |

Table 1: SEUs Propagation Probabilities for the 74L85 4-bit Magnitude Comparator Circuit

It is possible to verify the computed propagation probabilities and the SER by analyzing the design structure. An SEU injected at input signal **AEBi** can only propagate to output **AEBo** under the condition that the input bit-vectors **A** and **B** are equal, i.e., A == B. There exists a total of 128 input vector combinations that satisfy this condition out of a total of  $2^{11}$  which results in a propagation probability of 0.0625. When using concrete modeling, the computed SER is 3.65.

When using abstract modeling, we reduce the bit-vectors  $\mathbf{A}$  and  $\mathbf{B}$  to 1-bit signals and compute the propagation probabilities. It is assumed that all the bits of an *n*-bit signal have equal vulnerabilities, and that the vulnerability of each bit is equal to the computed vulnerability of the reduced bit-vector. This will results in a propagation probability of 1 for SEUs injected at inputs  $\mathbf{A}$  and  $\mathbf{B}$ . Assuming equal vulnerability for all the bits, this results in an SER of 10.5. Using abstract modeling in this cases results in a loss in accuracy of 187.2%. However, the computation time is 0.6 seconds while for concrete modeling the computation time is 17.55 seconds.

As another example, the proposed methodology was implemented on the 74283 Fast Adder circuit shown in Figure 3.5.

Figure 3.5: RTL Structure of the 74283 Benchmark that is a Fast Adder Circuit

This circuit has 9 inputs and 5 outputs. The Verilog behavioral model of the circuit is shown in Listing 3.10.

The RTL Verilog description of the module is then translated into an equivalent SMT model. Using Microsoft Z3's Python API, the description of the circuit is defined within a Python function as shown in Listing 3.11.

module 74283 (C0, A, B, S, C4);

input [3:0] A, B;

input C0;

output [3:0] S;

output C4;

wire [4:0] CS;

assign CS = A + B + C0;

assign S = CS[3:0];

assign C4 = CS[4];

endmodule

Listing 3.10: RTL Verilog Description of the 74283 Fast Adder Circuit

```

def circuit (C0, A, B):

CS = ZeroExt(1,A) + ZeroExt(1,B) + ZeroExt(4,C0)

S = Extract(3,0,CS)

C4 = Extract(4,4,CS)

return S, C4

```

Listing 3.11: Python Function Definition of the 74283 Fast Adder Circuit

The main part of the program is shown in Listing 3.12. The 74283 Fast Adder Circuit has two 4-bit input vectors **A** and **B**, and a 1-bit input **CO**. An SEU injected at those inputs will always propagate to one of the two outputs **S** and **C4**. This will result in a uniform propagation probability of 1 for all bits of all inputs, which results in an SER of 9.0.

When using abstract modeling, we reduce the input bit-vector signals  $\mathbf{A}$  and  $\mathbf{B}$  to 1-bit signals. When computing the propagation probabilities using the abstract model, we obtain the same value in SER of 9.0. The computation time for concrete modeling in this case is 6.56 seconds while for abstract modeling it is 0.14 seconds.

We used these two examples to provide a detailed step-by-step description of our methodology. Moreover, these two examples show that abstract modeling, which utilizes our proposed adaptation of a data type reduction technique, can sometimes

```

A = BitVec('A', 4)

B = BitVec('B', 4)

C0 = BitVec('C0', 1)

A_f = BitVec('A_f', 4)

B_f = BitVec('B_f', 4)

C0_f = BitVec('C0_f', 1)

S, C4 = circuit(C0, A, B)

S_f, C4_f = circuit(C0_f, A_f, B_f)

```

Listing 3.12: Python Two-Versions Model of the 74283 Fast Adder Circuit

result in great improvement in computation time with little or no loss in accuracy. However, in other cases it can result in significant loss in accuracy of the computed SER.

In the next section we apply our proposed approach on more ISCAS85 benchmarks to investigate its efficiency on larger designs.

### 3.4 Experimental Results

In this section, we report the experiments used to validate the proposed methodology and its efficiency. The proposed modeling and analysis are fully automated using the Microsoft Z3 SMT solver [12] and Python scripts. Our experiments were performed on a workstation with an Intel(R) Core(TM) i7-6820HQ running at 2.70 GHz and with 16 GB RAM.

#### 3.4.1 Accuracy Analysis

The goal of this analysis is to evaluate the loss in accuracy when the abstract modeling technique is used. For this analysis, different ISCAS85 benchmarks [13] and MSI components in the 74xxx series were analyzed. In order to compare the accuracy, the same designs were modeled, analyzed, and their SERs were estimated under both modeling techniques. The results of this analysis are reported in Table 2. The second

column shows the number of primary inputs of the design. The third column shows the number of input multi-bit signals. For example, the MSI component 74283 has three input signals: two 4-bit input signals and one 1-bit input signal, that is, 9 primary inputs. The computed SERs based on concrete modeling and abstract modeling are presented in columns 4 and 5 of Table 2 respectively. The percentage difference in the computed SERs is presented in column 6 of Table 2.

| Circuit | ΡIs  | Signals | Concrete | Abstract | Percentage |  |

|---------|------|---------|----------|----------|------------|--|

| Circuit | 1 10 | Signais | SER      | SER      | Difference |  |

| 74283   | 9    | 3       | 9        | 9        | 0          |  |

| 74182   | 9    | 3       | 4.57     | 8.25     | 80.36      |  |

| 74181   | 14   | 5       | 7.02     | 5.37     | 23.44      |  |

| 74L85   | 11   | 5       | 3.65     | 10.5     | 187.67     |  |

| c432    | 36   | 4       | 6.88     | 8.46     | 22.97      |  |

| c499    | 41   | 3       | 32.00    | 32.01    | 0.03       |  |

Table 2: Comparison Between the SER of the Concrete Modeling Technique and the

Abstract Modeling Technique

It is observed that in some cases the difference in the computed SER varies greatly when the abstract modeling is used, depending on the analyzed design. For example, the difference in the computed SER can be as high as 187.67% in the case of the MSI component 74L85. On the other hand, the difference can be as low as 0 for the case of the 74283 circuit.

This difference in the estimated SERs between the concrete and the abstract modeling techniques can be explained by the following reasons:

• The concrete modeling allows the injection of SEUs at every input bit of the design. Therefore, the vulnerability of every bit is obtained and summed up to

obtain the exact SER of the whole design. However, with the abstract modeling, we do not have access to the affected bits and therefore, the whole vector is assumed to be faulty. This assumption will lead to an over approximation in the SER in most cases since all the bits are treated as equally critical.

- With the concrete modeling, the propagation of the SEUs can be accurately traced. However, when the abstract modeling is used, we can only keep track of the fault state of the whole signal. Therefore, tracking faults at every bit becomes impossible since the correct functionality of the circuit is lost and only error propagation properties at the level of signals is available.

- With the concrete modeling, it is possible to exhaustively analyze the input vector search space for each injection scenario, to obtain an accurate SER value. However, with the abstract modeling such analysis is not possible and only an over approximation or an under approximation of the percentage of input vectors that affects the SEU propagation is generated.

Next, we investigate how much the performance can be improved at a cost in accuracy when using abstract modeling instead of concrete modeling.

#### 3.4.2 Performance Analysis

The second analysis compares the performance in terms of computation time for both the abstract and the concrete modeling. Although it is known that abstraction reduces computation time, the goal here is to investigate the trade-off between the loss in accuracy and the gained speed-up in analysis time. Table 3 shows the computation times for analyzing the same circuits using the two modeling approaches. The fourth and fifth column represent the computation times of the concrete and abstract modeling, respectively. The average speed-up of the abstract modeling over the concrete modeling for all circuits analyzed is around 67.33.

| Circuit | $\mathbf{PIs}$ | Signals  | Concrete       | Abstract       | Speed  |

|---------|----------------|----------|----------------|----------------|--------|

| oncur   | 1 15           | orginais | CPU Time (sec) | CPU Time (sec) | Up     |

| 74283   | 9              | 3        | 6.56           | 0.14           | 46.86  |

| 74182   | 9              | 3        | 3.14           | 0.18           | 17.06  |

| 74181   | 14             | 5        | 370.65         | 2.29           | 162.21 |

| 74L85   | 11             | 5        | 17.5           | 0.6            | 29.17  |

| c432    | 36             | 4        | 505.25         | 3.54           | 142.50 |

| c499    | 41             | 3        | 92.94          | 14.98          | 6.20   |

| Average | -              | -        | 166.01         | 3.62           | 67.33  |

Table 3: Comparison Between the Computation Time for the Concrete Modeling Technique and the Abstract Modeling Technique

Table 4 represents the ratio of the loss in accuracy in the estimated SER over the gain in the analysis time. A small ratio implies a better trade-off, i.e., a small loss in SER accuracy over a large speed-up of the analysis time.

Based on the results, it can be observed that the abstract modeling has a different impact based on the design behavior. For example, the best trade-off was observed in the case of the 74283 and the c499. For the c499 design, the speed-up is around 6 while the percentage of the loss in accuracy is only 0.03%. This is due to the fact that, all the bits in every input signal have equal vulnerabilities. However, for the case of the 74L85 benchmark, the speed-up is around 29 while the percentage of the loss in accuracy is around 29 while the percentage of the loss in accuracy is around 187%. This can be partially explained by the fact that this design is a comparator, i.e., with the abstract modeling many of the injected SEUs are considered to propagate to the output while they should have been logically masked.

|         |     |         | Percentage | Speed       |       |

|---------|-----|---------|------------|-------------|-------|