# Performance and Energy Evaluation of Parallelization Strategies for Network on Chip Communication Architectures: Case Study of Canny Edge Detector Application

By

## Harikrishna Menon Thelakkat

A Thesis

In

The Department

Of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the

Degree of Master of Applied Science (Electrical and Computer Engineering)

at

Concordia University

Montréal, Québec, Canada

June 2018

#### ©HARIKRISHNA MENON THELAKKAT, 2018

i

#### CONCORDIA UNIVERSITY SCHOOL OF GRADUATE STUDIES

This is to certify that the thesis prepared

By: Harikrishna Menon Thelakkat

Entitled:

"Performance and Energy Evaluation of Parallelization Strategies for Network on Chip Communication Architectures: Case Study of Canny Edge Detector Application"

and submitted in partial fulfillment of the requirements for the degree of

Master of Applied Science (Electrical and Computer Engineering)

Complies with the regulations of this University and meets the accepted standards with respect to originality and quality.

Signed by the final examining committee:

|          |                        | Chair              |

|----------|------------------------|--------------------|

|          | Dr. D. Qiu             |                    |

|          |                        | Examiner, External |

|          | Dr. L Narayanan        | to the Program     |

|          |                        |                    |

|          |                        | Examiner           |

|          | Dr. Y. Liu             |                    |

| _        |                        | Supervisor         |

|          | Dr. Jelena Trajkovic   |                    |

|          |                        |                    |

| Approved |                        |                    |

|          | Dr. W. E. Lynch, Chair |                    |

Department of Electrical and Computer Engineering

June 2018

Dr. Amir Asif Dean, Faculty of Engineering and Computer Science

## ABSTRACT

The substantial amount of research pertaining to the usage of optical networks for communication between cores in a multicore processor underlines the need for effective communication schemes. This necessitates the exploration of the efficiency of an optical network with a suitable benchmark which compares the different features essential for having an effective communication between the cores. As far as communication in a network is considered, the parameters that are most crucial are the delays and energy consumption. This thesis focuses on an industrial-sized application from the image processing field, Canny Edge Detector, to compare the performance in terms of network parameters which are the contention delay, latency and the energy consumption with the different settings on the network on chip simulator. The Canny Edge Detector application is implemented with various software parallelization schemes for better performance as compared to the normal serialized application. Also, to analyze the effectiveness of multicore processors, a comparison among sequential and parallelized coding techniques is performed in this thesis. Software parallelization schemes applied to the algorithm executed on optical network architectures improve the latency and delay of the network up to 60% in the best case, while the total energy consumption values have a worst case overhead of around 50%. For almost all the configuration parameters, the parallelized schemes provide much better results for the outputs than the sequential implementation. The design parameters help determine the optimal amount of resources required for efficient execution of an image processing algorithm using a moderate to heavy workload on an NoC based on the minimal delay and energy consumption values.

## ACKNOWLEDGEMENTS

First of all, I would like to express my sincere gratitude towards my Supervisor, Dr. Jelena Trajkovic, for providing me an opportunity to work under her on this thesis. I also thank her for her constant support and guidance without which this would never have been possible. My work under her has improved my technical knowledge and presentation skills, while helping me embark on my desired career path for which I am ever so grateful.

I would like to thank my examining committee members, Dr. Lata Narayanan and Dr. Yan Liu for reviewing my thesis and for their invaluable suggestions. I am also grateful to all the professors who taught me at Concordia University. They have helped me strengthen my knowledge on the fundamental concepts and introduced me to new ideas and challenges.

I would like to extend my thanks to the CSAIL group form MIT for the provision of Graphite multi-core network on chip simulator, which has formed an integral part of all the experiments in this thesis.

Next, I would like to express my gratitude towards all my lab mates, for this whole period of time for all their aid and assistance. I am especially thankful to Sara Karimi, for her unmatched support and help. My friends – Paul Leons, Alex Joseph and Sarath Somasekharan have been a great help and guidance from the beginning of my life in Canada and have provided immense support throughout my master's program for which I am much indebted to them. I am extremely thankful to all my family members, especially my mom, dad and grandmother who have always believed in me and provided me with all the moral support. I dedicate this thesis work to all three of them.

Last but not least, I would like to thank God Almighty for giving the strength and knowledge to pursue this endeavor and successfully complete it.

## CONTENTS

| ABSTRACT                                         | iii |

|--------------------------------------------------|-----|

| ACKNOWLEDGEMENTS                                 | iv  |

| List of Equations                                | ix  |

| List of Tables                                   | x   |

| List of Figures                                  | xi  |

| Chapter 1                                        | 1   |

| Introduction                                     | 1   |

| 1.1 Motivation and Problem Statement             | 2   |

| 1.2 Proposed Solution                            |     |

| 1.3 Thesis Contribution                          | 4   |

| 1.4 Outline                                      | 5   |

| 1.5 Related Work                                 | 6   |

| 1.5.1Networks on Chip                            | 6   |

| 1.5.2 Optical Networks on Chip Architectures     | 7   |

| 1.5.3 NoC Simulators                             |     |

| 1.5.4 Application and Parallelization strategies | 9   |

| 1.6 Thesis Organization                          |     |

| Chapter 2                                        |     |

| Networks on Chip – Components and Architectures  |     |

| 2.1 Networks on Chip (NoC)                       |     |

| 2.2 Optical Networks on Chip (ONoC)              |     |

| 2.2.1 Wavelength Division Multiplexing           | 21  |

| 2.3 Optical Components in ONoC                   |     |

| 2.3.1 Communication Process                      |     |

| 2.4 Network Architectures Investigated           |     |

| 2.4.1 Emesh Network on Chip Architecture         |     |

| 2.4.2 ATAC Optical Network on Chip Architecture  |     |

| 2.4.3 ORNoC Optical Network on Chip Architecture |     |

| Chapter 3                                        |     |

| Canny Edge Detection - Application Theory        |     |

| 3.1 Application Used                             |     |

| 3.1.1 Gaussian Blur                                            |           |

|----------------------------------------------------------------|-----------|

| 3.1.2 Gradient Calculation                                     |           |

| 3.1.3 Magnitude and Phase Calculation                          |           |

| 3.1.4 Non-maxima Suppression (NMS)                             |           |

| 3.1.5 Hysteresis Thresholding                                  |           |

| 3.1.6 Edge thinning                                            |           |

| 3.2 Parallelization Schemes                                    |           |

| 3.2.1 Pure Data Parallelization Scheme                         |           |

| 3.2.2 Mixed Parallelization Scheme                             |           |

| 3.3 Parallelization of the Canny edge detection                |           |

| 3.3.1 POSIX Threads                                            | 40        |

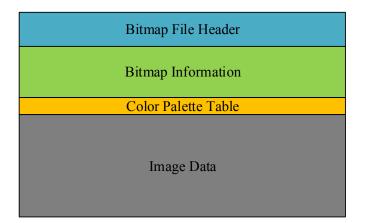

| 3.4 The Bitmap Image                                           | 41        |

| 3.4.1 Bitmap File Header                                       | 41        |

| 3.4.2 Bitmap Information                                       | 42        |

| 3.4.3 Color Palette table                                      |           |

| 3.4.4 Image data                                               |           |

| Chapter 4                                                      | 45        |

| Canny Edge Detection Implementation and NoC Simulation         | 45        |

| 4.1 Tools and Coding Platforms                                 | 45        |

| 4.2 Implementation                                             | 46        |

| 4.3 NoC Simulator Framework                                    |           |

| 4.4 Makefiles                                                  | 60        |

| Chapter 5                                                      |           |

| Experimental Results                                           |           |

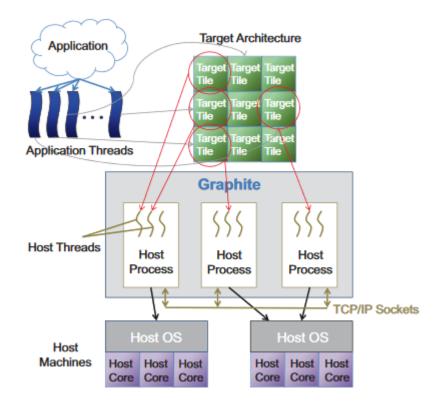

| 5.1 Analysis with varying Image sizes                          | 68        |

| 5.1.1 Results for Packet Latency for varying Image Sizes       | 69        |

| 5.1.2 Results for Contention Delay for varying Image Sizes     | 73        |

| 5.1.3 Results for Static Energy for varying Image Sizes        | 77        |

| 5.1.4 Results for Dynamic Energy for varying Image Sizes       |           |

| 5.1.5 Results for Total Energy for varying Image Sizes         |           |

| 5.2 Analysis with varying number of Cores                      |           |

| 5.2.1 Results for Packet Latency for varying number of Cores   |           |

| 5.2.2 Results for Contention Delay for varying number of Cores | 93        |

| 5.2.3 Results for Static Energy for varying number of Cores    | 96        |

| 5.2.4 Results for Dynamic Energy for varying number of Cores   | 100<br>vi |

| 5.2.5 Results for Total Energy for varying number of Cores                       | 103   |

|----------------------------------------------------------------------------------|-------|

| 5.3 Analysis with varying number of Clusters                                     | 105   |

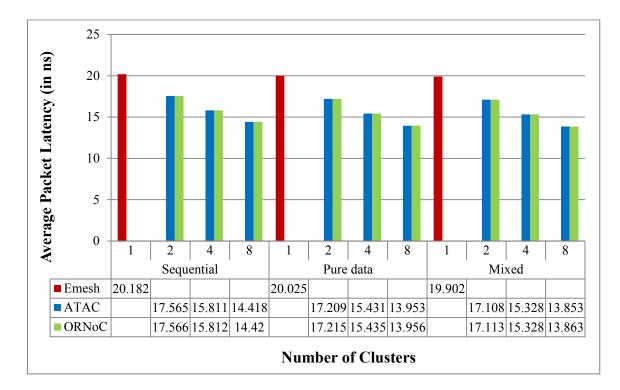

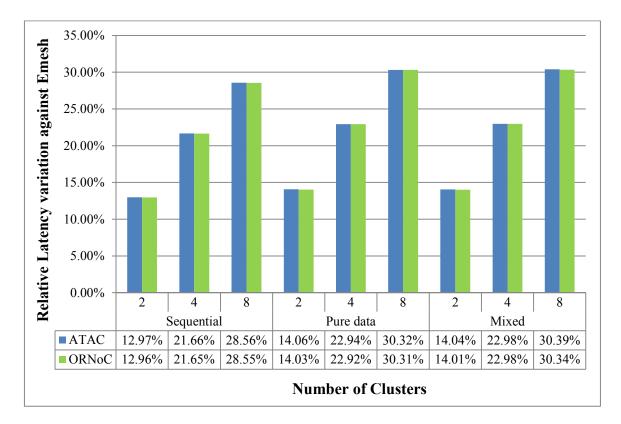

| 5.3.1 Results for Packet Latency for varying number of Clusters                  | . 107 |

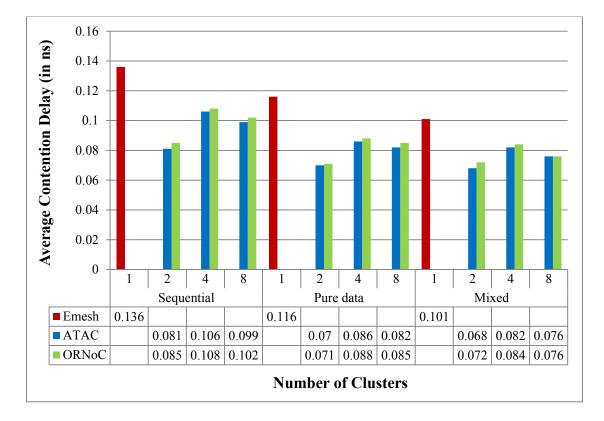

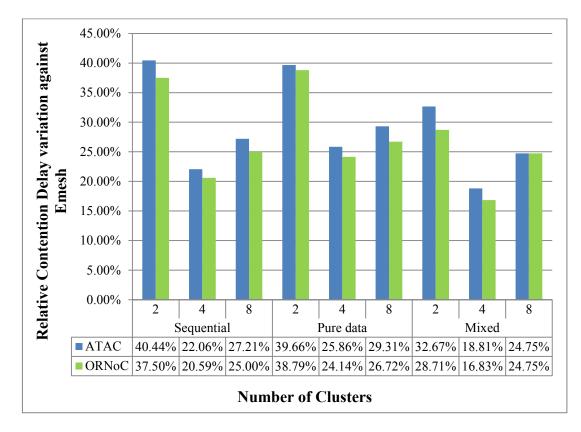

| 5.3.2 Results for Contention Delay for varying number of Clusters                | .110  |

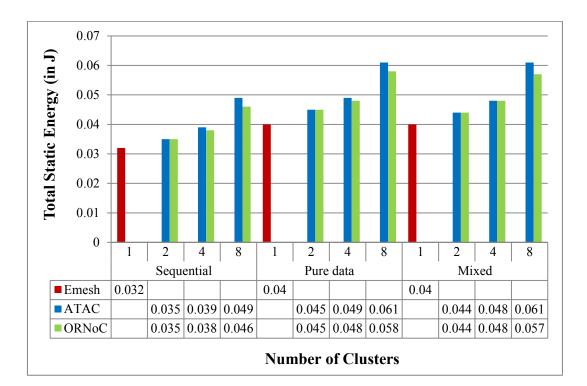

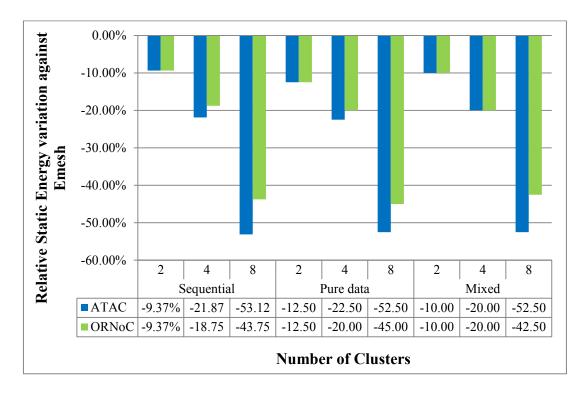

| 5.3.3 Results for Static Energy for varying number of Clusters                   | .114  |

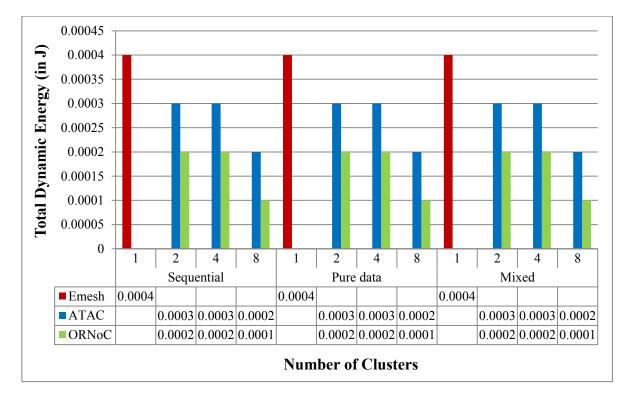

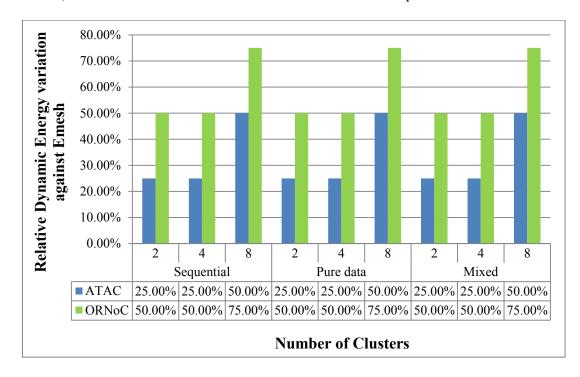

| 5.3.4 Results for Dynamic Energy for varying number of Clusters                  | .117  |

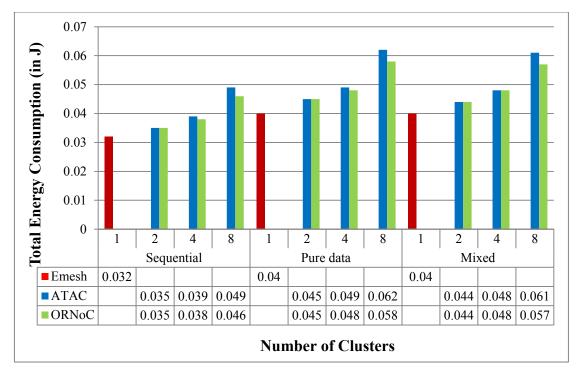

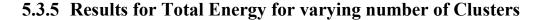

| 5.3.5 Results for Total Energy for varying number of Clusters                    | . 119 |

| 5.4 Analysis with varying Optical Access points                                  | .122  |

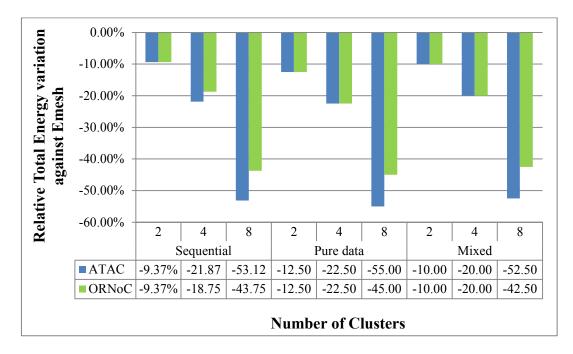

| 5.4.1 Results for Packet Latency for varying number of Optical Access points     | 123   |

| 5.4.2 Results for Contention Delay for varying number of Optical Access points . | .127  |

| 5.4.3 Results for Static Energy for varying number of Optical Access points      | .131  |

| 5.4.4 Results for Dynamic Energy for varying number of Optical Access points     | .135  |

| 5.4.5 Results for Dynamic Energy for varying number of Optical Access points     | .137  |

| 5.5 Analysis with varying Routing strategies                                     | .140  |

| 5.5.1 Results for Packet Latency for varying Routing strategies                  | .142  |

| 5.5.2 Results for Contention Delay for varying Routing strategies                | .145  |

| 5.5.3 Results for Static Energy for varying Routing strategies                   | . 149 |

| 5.5.4 Results for Dynamic Energy for varying Routing strategies                  | 152   |

| 5.5.5 Results for Total Energy for varying Routing strategies                    | 155   |

| 5.6 Analysis with varying Flit Width Values                                      | 158   |

| 5.6.1 Results for Packet Latency for varying Flit Width Values                   | 159   |

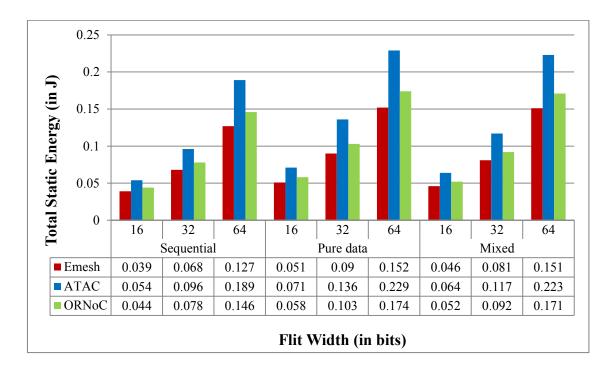

| 5.6.2 Results for Contention Delay for varying Flit Width Values                 | 162   |

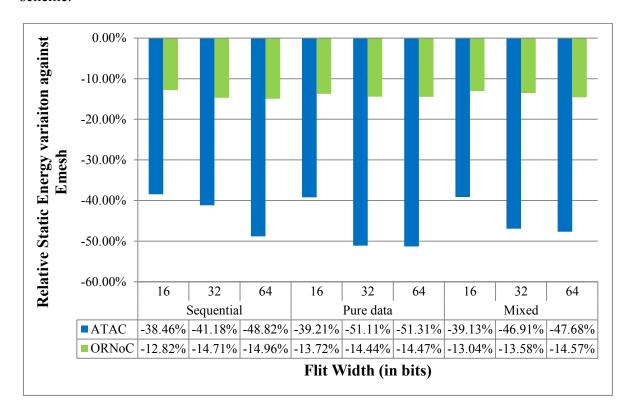

| 5.6.3 Results for Static Energy for varying Flit Width Values                    | 166   |

| 5.6.4 Results for Dynamic Energy for varying Flit Width Values                   | 170   |

| 5.6.5 Results for Total Energy for varying Flit Width Values                     | 172   |

| 5.7 Analysis with varying Cache Line Size                                        | .175  |

| 5.7.1 Results for Packet Latency for varying Cache Line Sizes                    | . 177 |

| 5.7.2 Results for Contention Delay for varying Cache Line Sizes                  | 181   |

| 5.7.3 Results for Static Energy for varying Cache Line Sizes                     | 185   |

| 5.7.4 Results for Dynamic Energy for varying Cache Line Sizes                    | 188   |

| 5.7.5 Results for Total Energy for varying Cache Line Sizes                      | . 191 |

| 5.8 Analysis with varying Size of L1-Data Cache                                  | . 194 |

| 5.8.1 Results for Packet Latency for varying Size of L1-Data Cache               | . 196 |

| 5.8.2 Results for Contention Delay for varying Size of L1-Data Cache             | . 199 |

| 5.8.3 Results for Static Energy for varying Size of L1-Data Cache                | 203   |

|                                                                                  | vii   |

| 5.8.4 Results for Dynamic Energy for varying Size of L1-Data Cache |  |

|--------------------------------------------------------------------|--|

| 5.8.5 Results for Total Energy for varying Size of L1-Data Cache   |  |

| Chapter 6                                                          |  |

| Conclusion                                                         |  |

| Chapter 7                                                          |  |

| Future Work                                                        |  |

| References                                                         |  |

| Appendix                                                           |  |

| A1.1 Configurations for varying Image Sizes                        |  |

| A1.2 Configurations for varying Number of Cores                    |  |

| A1.3 Configurations for varying Number of Clusters                 |  |

| A1.4 Configurations for varying Number of Optical Access Points    |  |

| A1.5 Configurations for varying Routing Strategies                 |  |

| A1.6 Configurations for varying Flit Widths                        |  |

| A1.7 Configurations for varying Cache Line Sizes                   |  |

| A1.8 Configurations for varying L1 Data Cache Sizes                |  |

| A2.1 All Results for the Sequential Implementation Scheme          |  |

| A2.2 All Results for the Pure data Implementation Scheme           |  |

| A2.3 All Results for the Mixed Implementation Scheme               |  |

# List of Equations

| Equation 1: 2D Gaussian kernel equation                       | 49 |

|---------------------------------------------------------------|----|

| Equation 2: Kernel Size Calculation                           | 49 |

| Equation 3: Sobel kernels in the X (G1) and Y (G2) directions |    |

| Equation 4: Magnitude of the image pixels                     | 52 |

| Equation 5: Phase of the image pixels                         | 53 |

| Equation 6: Equation for Relative Variation                   | 68 |

# List of Tables

| Table 1: Bitmap File Header[51]                       | 42 |

|-------------------------------------------------------|----|

| Table 2: Bitmap Information[51]                       | 43 |

| Table 3: Configuration parameters for the Experiments | 67 |

| Table 4: Default configuration parameters             | 67 |

# **List of Figures**

| Figure 1: The Shared Bus Architecture                                                   | 16 |

|-----------------------------------------------------------------------------------------|----|

| Figure 2: Buffered Crossbar Architecture                                                | 17 |

| Figure 3: Electrical Mesh (Emesh) architecture                                          | 18 |

| Figure 4: Optical Micro Ring Resonator[42]                                              | 23 |

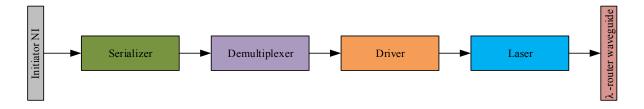

| Figure 5: Data transmission in the Electro-Optical Network[35]                          | 25 |

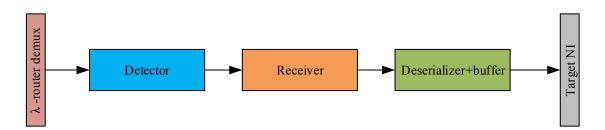

| Figure 6: Data reception in the Electro-Optical Network[35]                             |    |

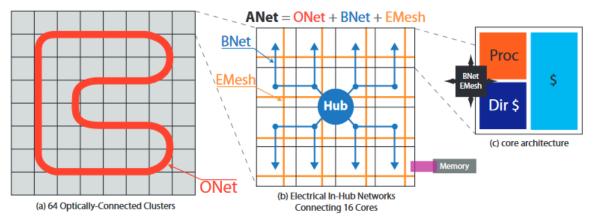

| Figure 7: The ATAC Architecture[15]                                                     | 27 |

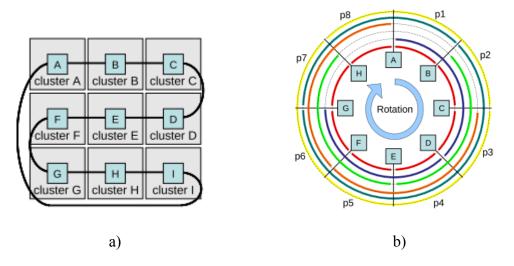

| Figure 8: a) The ORNoC 2D Architecture [10] b) Wavelength Reuse Implementation [10]     | 29 |

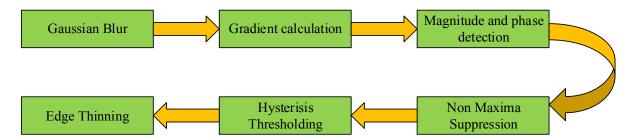

| Figure 9: Process flow in the serial Canny edge detection algorithm                     | 32 |

| Figure 10: Classification of neighbouring pixels                                        | 34 |

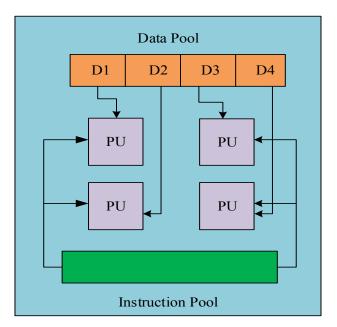

| Figure 11: Pure Data Parallelism (a.k.a SIMD)                                           | 36 |

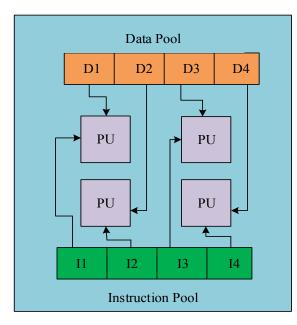

| Figure 12: Nested Instruction and Data Parallelism (a.k.a. MIMD)                        | 37 |

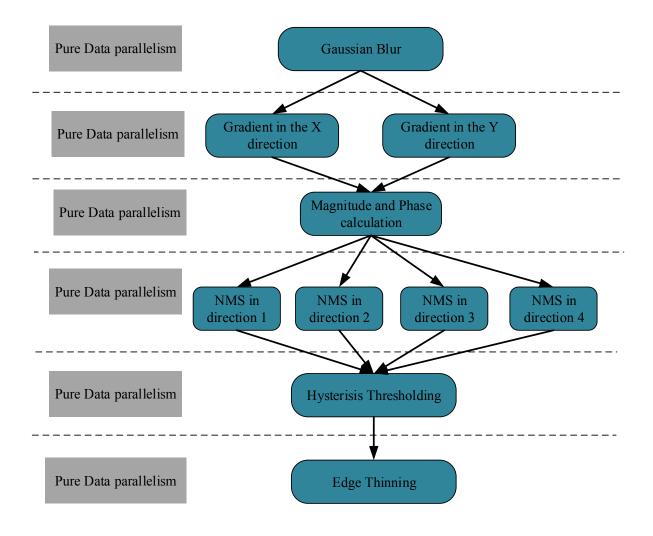

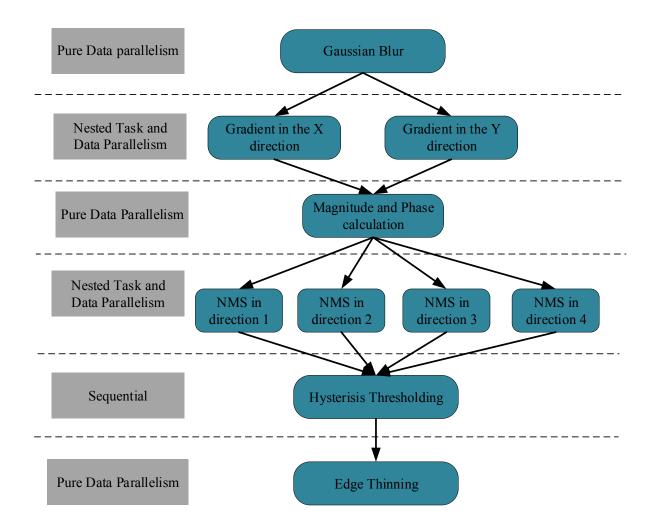

| Figure 13: Flow diagram for Pure data Implementation [4]                                | 38 |

| Figure 14: Flow diagram for Mixed Implementation [4]                                    | 39 |

| Figure 15: Internal file structure of a bitmap image                                    | 41 |

| Figure 16: Gaussian blurred image with $\sigma = 0.9$                                   | 50 |

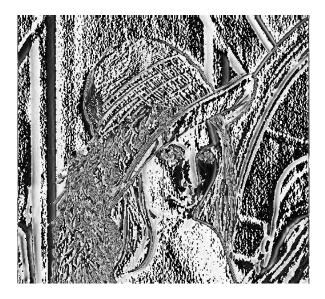

| Figure 17: Image gradient along the X direction                                         | 51 |

| Figure 18: Image gradient along the Y direction                                         | 52 |

| Figure 19: Magnitude of the image                                                       | 53 |

| Figure 20: Phase of the image                                                           | 54 |

| Figure 21: Image after Non Maxima Suppression                                           | 55 |

| Figure 22: Image after Hysteresis Thresholding                                          | 56 |

| Figure 23: Final image after Canny Edge Detection                                       | 56 |

| Figure 24: High level achitecture of Graphite simulator [7]                             | 58 |

| Figure 25: Average Packet Latency for Image Sizes NxN, N = {512, 1024, 2048}            | 69 |

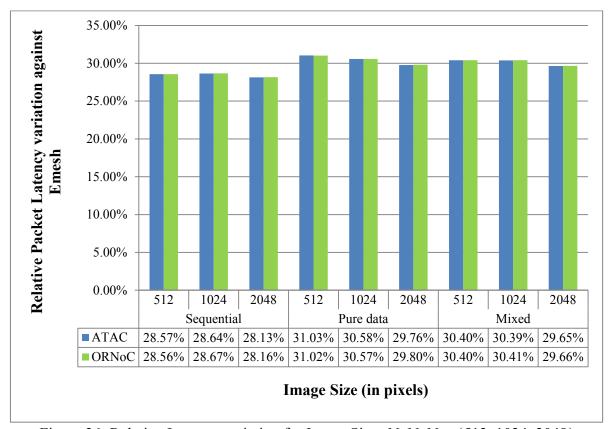

| Figure 26: Relative Latency variation for Image Sizes NxN, N = {512, 1024, 2048}        | 72 |

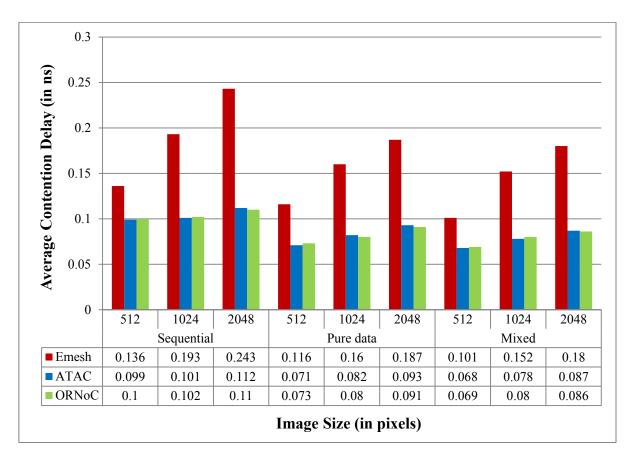

| Figure 27: Average Contention Delay for Image Sizes NxN, N = {512, 1024, 2048}          | 73 |

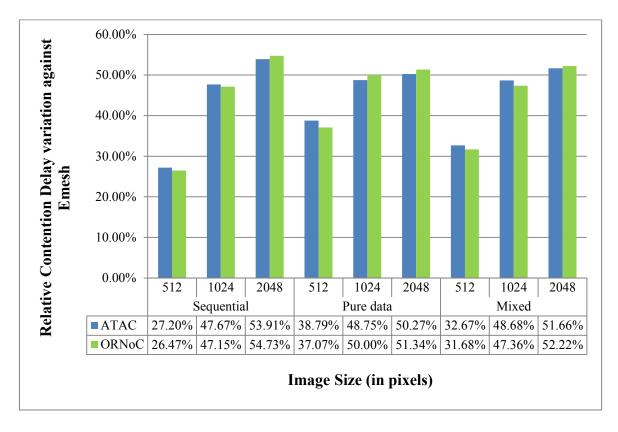

| Figure 28: Relative Contention Delay variation for Image Sizes NxN, N = {512, 1024,     |    |

| 2048}                                                                                   | 76 |

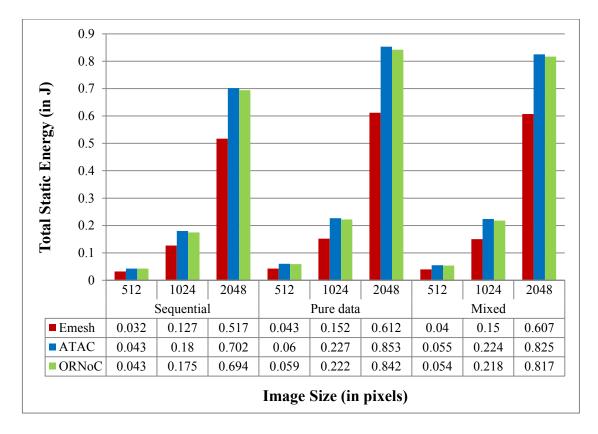

| Figure 29: Total Static Energy for Image Sizes NxN, N = {512, 1024, 2048}               | 77 |

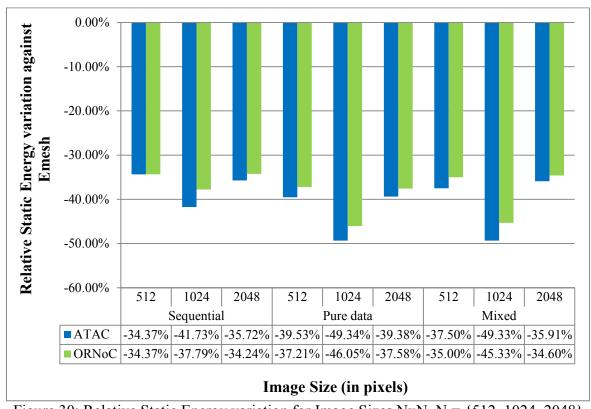

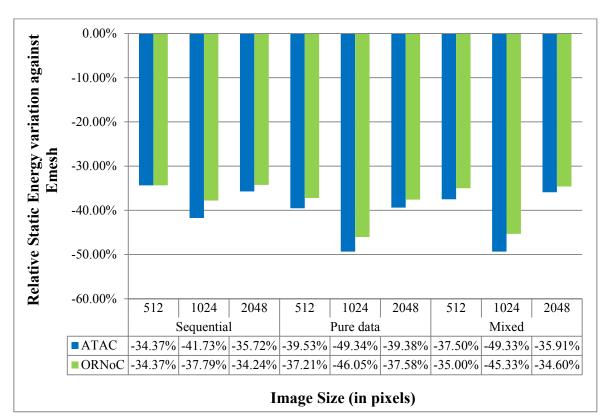

| Figure 30: Relative Static Energy variation for Image Sizes NxN, N = {512, 1024, 2048}. | 80 |

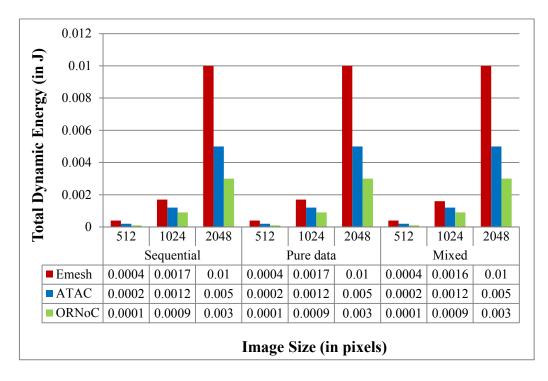

| Figure 31: Total Dynamic Energy for Image Sizes NxN, N = {512, 1024, 2048}              | 82 |

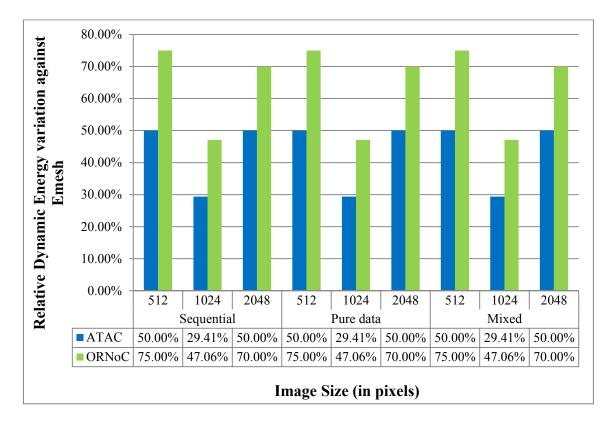

| Figure 32: Relative Dynamic Energy variation for Image Sizes NxN, N = {512, 1024, 204   | 8} |

|                                                                                         | 84 |

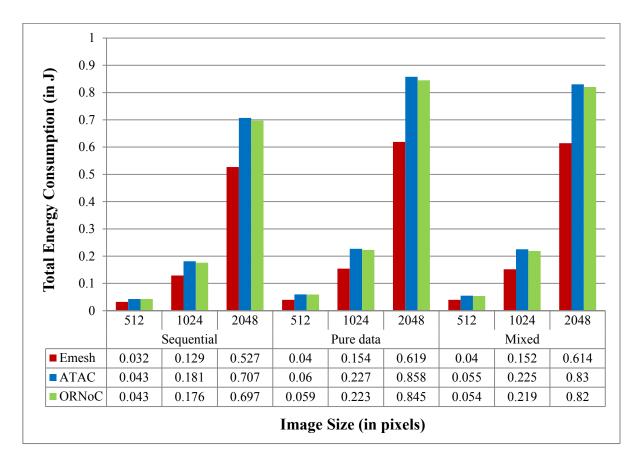

| Figure 33: Total Energy Consumption for Image Sizes NxN, N = {512, 1024, 2048}          | 85 |

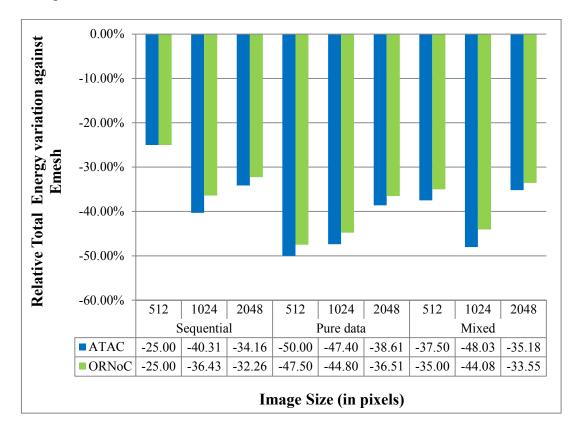

| Figure 34: Relative Total Energy variation for Image Sizes NxN, N = {512, 1024, 2048}   | 87 |

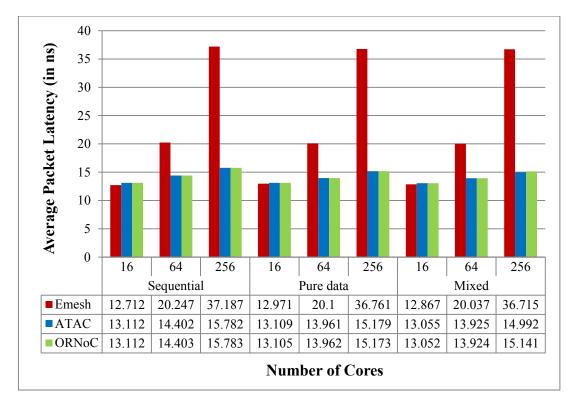

| Figure 35: Average Packet Latency for Number of Cores N={16,64,256}                     | 89 |

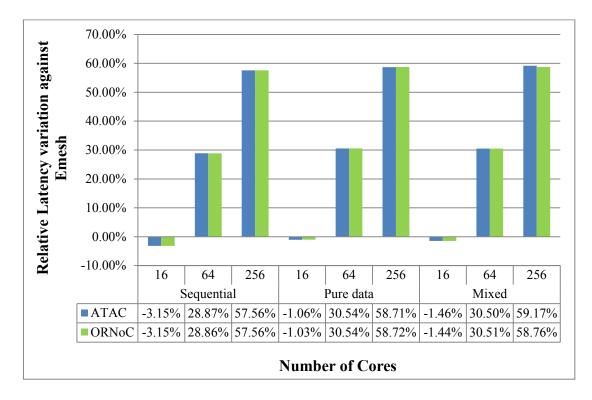

| Figure 36: Relative Latency variation for Number of Cores N={16,64,256}                 | 92 |

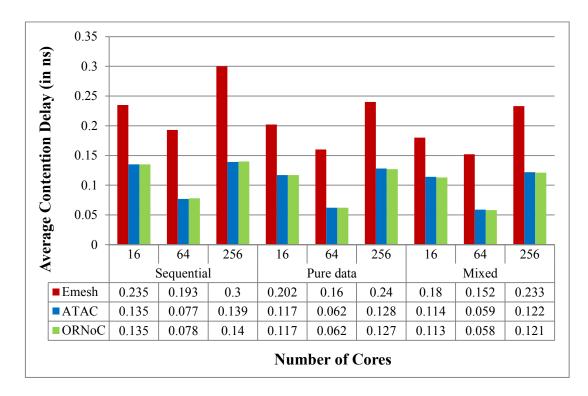

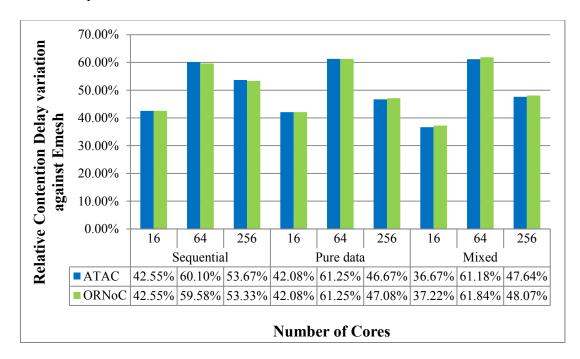

| Figure 37: Average Contention Delay for Number of Cores N={16,64,256}                   | 93 |

| Figure 38: Relative Contention Delay for Number of Cores N={16,64,256}                                                                                                                       | 95  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

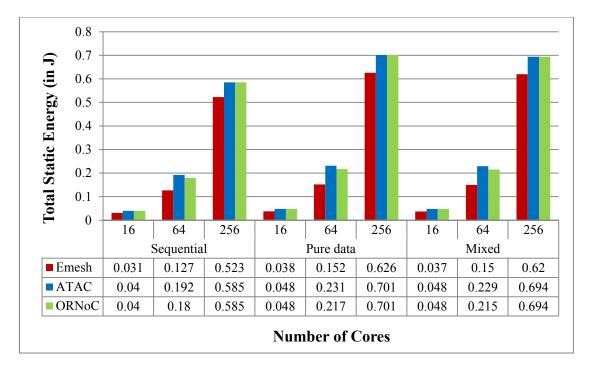

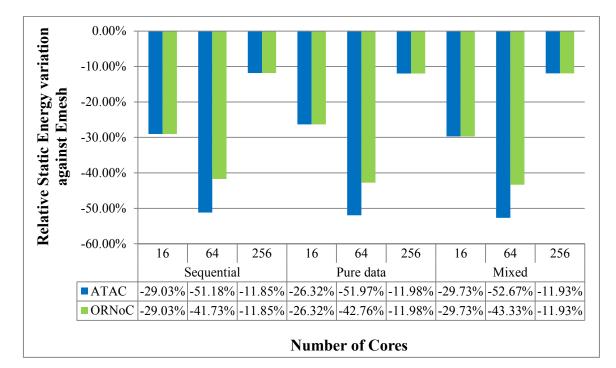

| Figure 39: Total Static Energy for Number of Cores N={16,64,256}                                                                                                                             |     |

| Figure 40: Relative Static Energy variation for Number of Cores N={16,64,256}                                                                                                                |     |

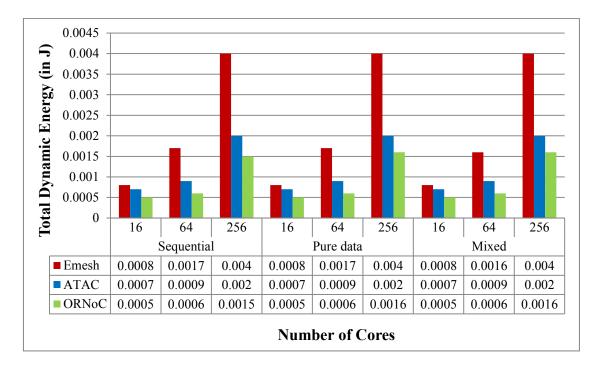

| Figure 41: Total Dynamic Energy for Number of Cores $N = \{16, 64, 256\}$                                                                                                                    |     |

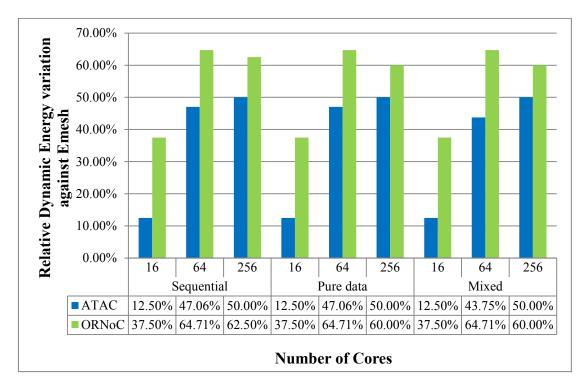

| Figure 42: Relative Dynamic Energy variation for Number of Cores N={16,64,256}                                                                                                               |     |

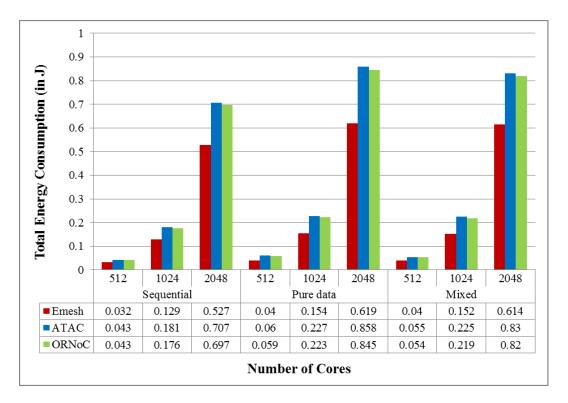

| Figure 43: Total Energy Consumption for Number of Cores $N = \{16,64,256\}$                                                                                                                  |     |

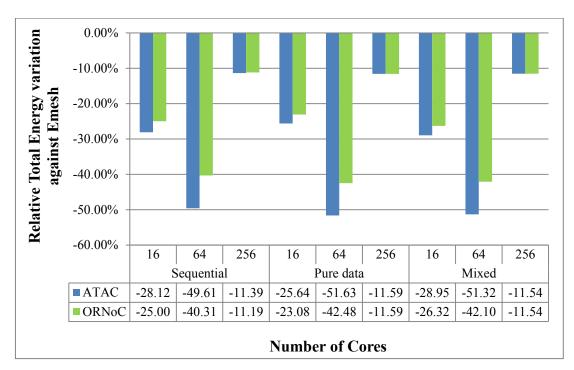

| Figure 44: Relative Total Energy variation for Number of Cores $N = \{16, 64, 256\}$                                                                                                         |     |

| Figure 45: Average Packet Latency for the Number of Clusters $N = \{1, 2, 4, 8\}$                                                                                                            |     |

| Figure 46: Relative Latency variation for Cluster Numbers $N = \{1,2,4,8\}$                                                                                                                  |     |

| Figure 47: Average Contention Delay for Cluster Numbers $N = \{1,2,4,8\}$                                                                                                                    |     |

| Figure 48: Relative Contention Delay variation for Cluster Numbers $N = \{1,2,4,8\}$                                                                                                         |     |

| Figure 49: Total Static Energy for Cluster Numbers $N = \{1,2,4,8\}$                                                                                                                         |     |

| Figure 50: Relative Static Energy variation for Cluster Numbers $N = \{1,2,4,8\}$                                                                                                            |     |

| Figure 50: Relative Static Energy variation for Cluster Numbers $N = \{1, 2, 4, 8\}$                                                                                                         |     |

| Figure 51: Relative Dynamic Energy for Cluster Numbers $N = \{1, 2, 4, 8\}$                                                                                                                  |     |

| Figure 52: Total Energy Consumption for Cluster Numbers $N = \{1, 2, 4, 8\}$                                                                                                                 |     |

| Figure 55: Four Energy consumption for Cluster Numbers $N = \{1, 2, 4, 8\}$                                                                                                                  |     |

| Figure 54: Relative Total Energy for Cluster Rullbers $N = \{1, 2, 4, 8\}$<br>Figure 55: Average Packet Latency for Optical Access points per Cluster $N = \{0, 2, 4, 8\}$ .                 |     |

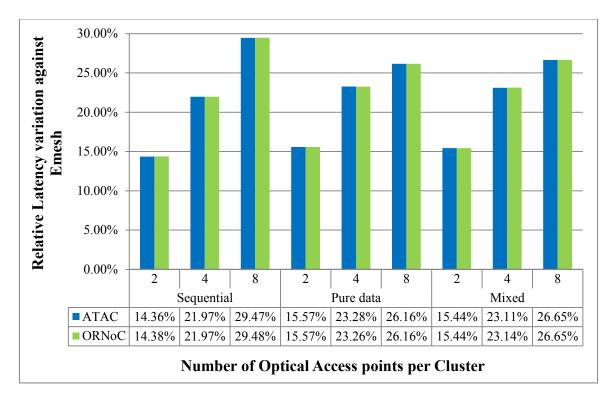

| Figure 55: Average Facket Latency for Optical Access points per Cluster $N = \{0,2,4,8\}$ .<br>Figure 56: Relative Latency variation for Optical Access points per Cluster $N = \{0,2,4,8\}$ |     |

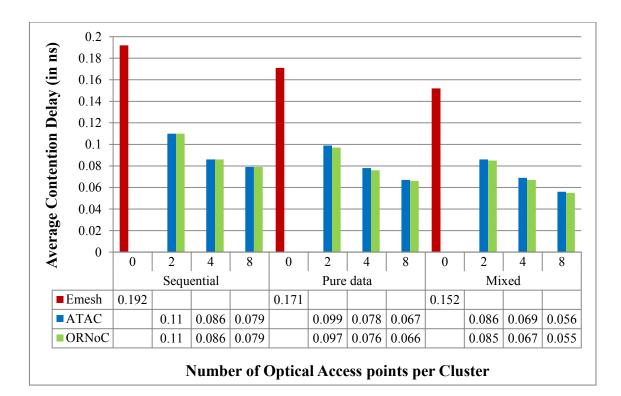

| Figure 50: Relative Eatency variation for Optical Access points per Cluster $N = \{0,2,4,8\}$<br>Figure 57: Average Contention Delay for Optical Access points per Cluster $N = \{0,2,4,8\}$ |     |

| Figure 57. Average Contention Delay for Optical Access points per Cluster IV = {0,2,4,8}                                                                                                     |     |

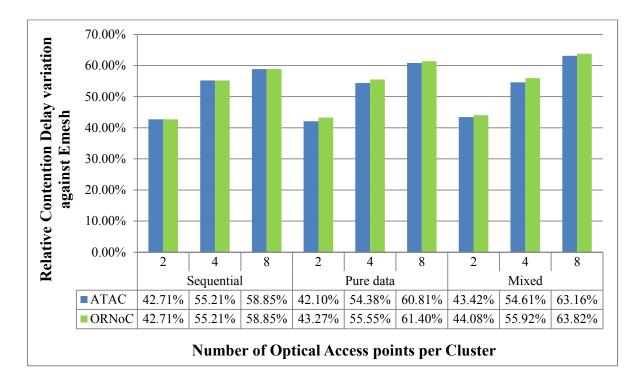

| Figure 58: Relative Contention Delay variation for Optical Access points per Cluster N =                                                                                                     | 127 |

| {0,2,4,8}                                                                                                                                                                                    | 129 |

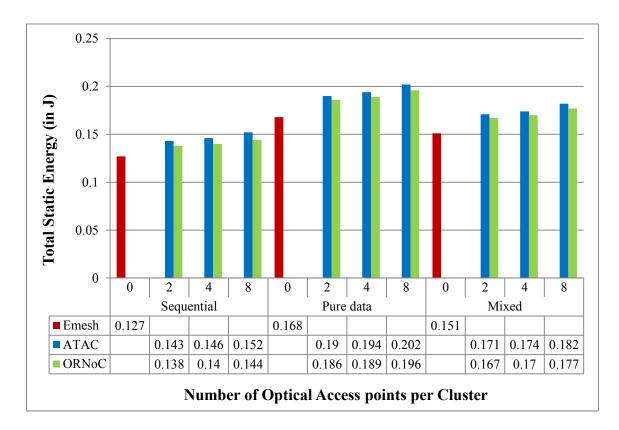

| Figure 59: Static Energy for Optical Access points per Cluster $N = \{0,2,4,8\}$                                                                                                             |     |

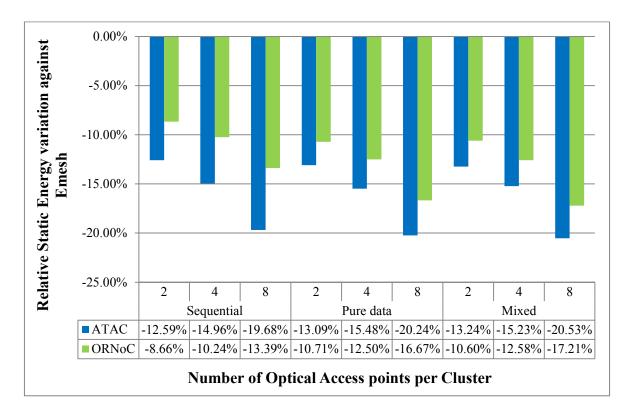

| Figure 60: Relative Static Energy variation for Optical Access points per Cluster N =                                                                                                        | 101 |

| {0,2,4,8}                                                                                                                                                                                    | 133 |

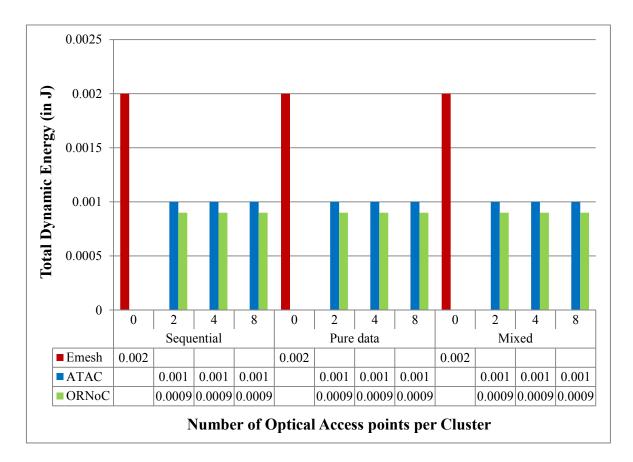

| Figure 61: Dynamic Energy consumption for Optical Access points per Cluster N =                                                                                                              | 100 |

| {0,2,4,8}                                                                                                                                                                                    | 135 |

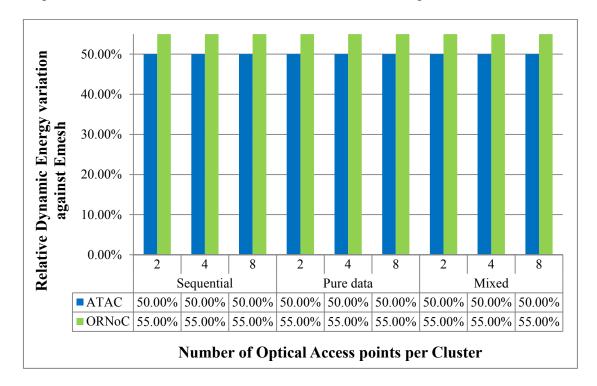

| Figure 62: Relative Dynamic Energy variation for Optical Access points per Cluster N =                                                                                                       |     |

| {0,2,4,8}                                                                                                                                                                                    | 136 |

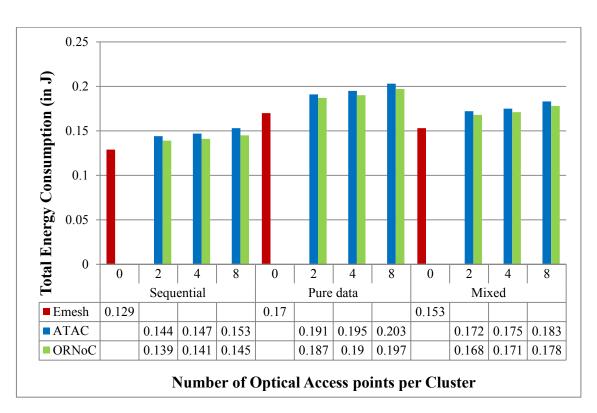

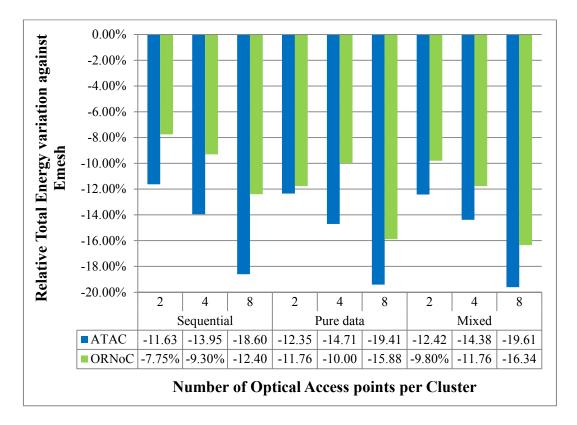

| Figure 63: Total Energy Consumption for Optical Access points per Cluster N = $\{0,2,4,8\}$                                                                                                  |     |

|                                                                                                                                                                                              |     |

| Figure 64: Relative Total Energy variation for Optical Access points per Cluster N =                                                                                                         | 10, |

| {0,2,4,8}                                                                                                                                                                                    | 139 |

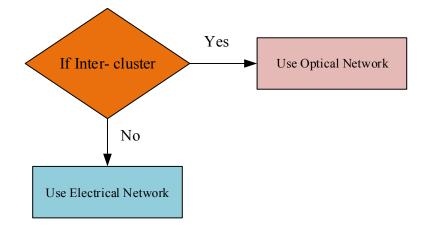

| Figure 65: Cluster based Routing Topology                                                                                                                                                    |     |

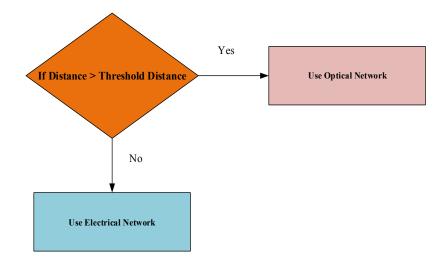

| Figure 66: Distance based Routing Topology                                                                                                                                                   |     |

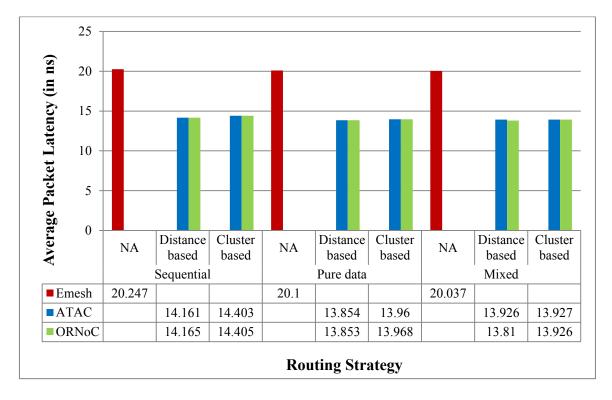

| Figure 67: Average Packet Latency for Routing Strategies $N = \{\text{distance, cluster}\}$                                                                                                  |     |

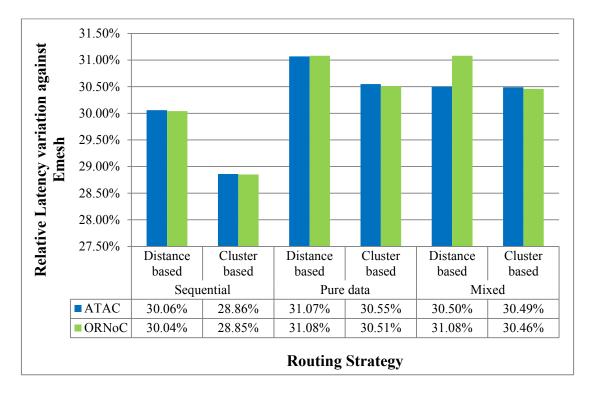

| Figure 68: Relative Latency variation for Routing Strategies N = {distance, cluster}                                                                                                         |     |

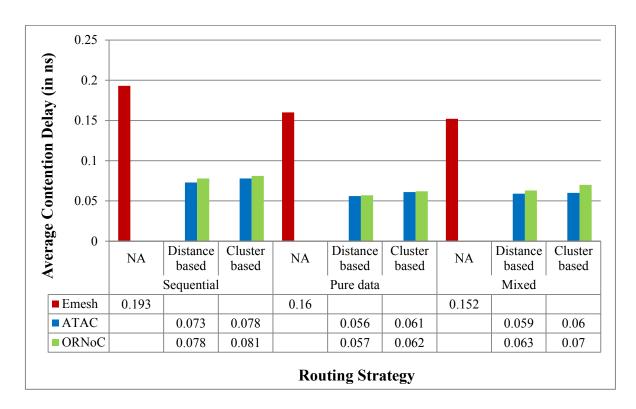

| Figure 69: Average Contention Delay for Routing Strategies $N = \{\text{distance, cluster}\}$                                                                                                |     |

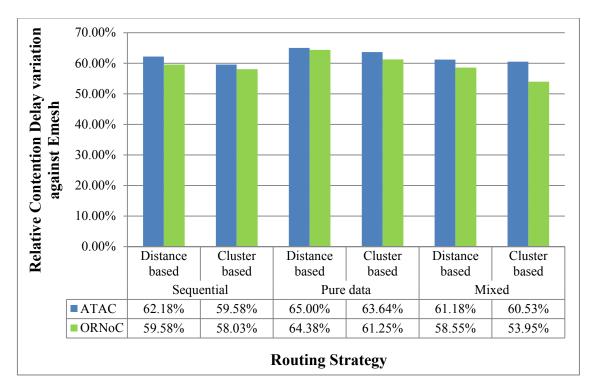

| Figure 70: Relative Contention Delay variation for Routing Strategies $N = \{$ distance,                                                                                                     | -   |

| cluster}                                                                                                                                                                                     | 147 |

|                                                                                                                                                                                              | .,  |

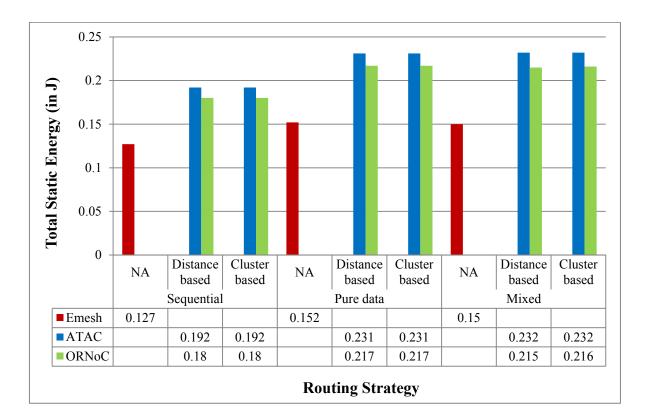

| Figure 71: Total Static Energy consumption for Routing Strategies N = {distance, cluster}                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

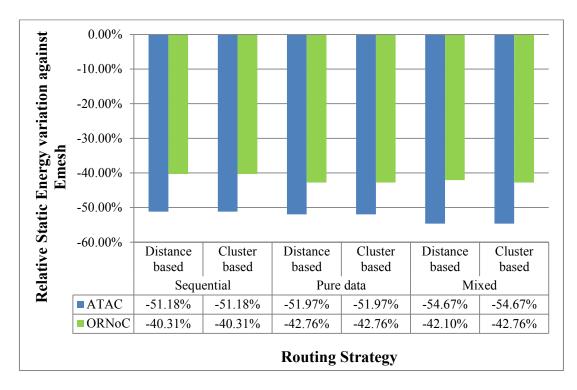

| Figure 72: Relative Static Energy consumption for Routing Strategies N = {distance,<br>cluster}                                                                                                                                                                                                                                                                                      |

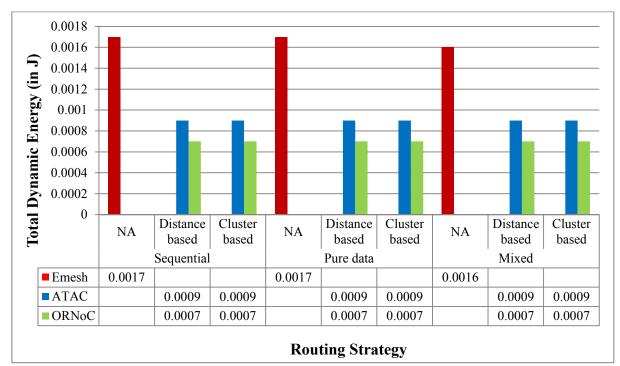

| Figure 73: Total Dynamic Energy consumption for different Routing Strategies N = {distance, cluster}                                                                                                                                                                                                                                                                                 |

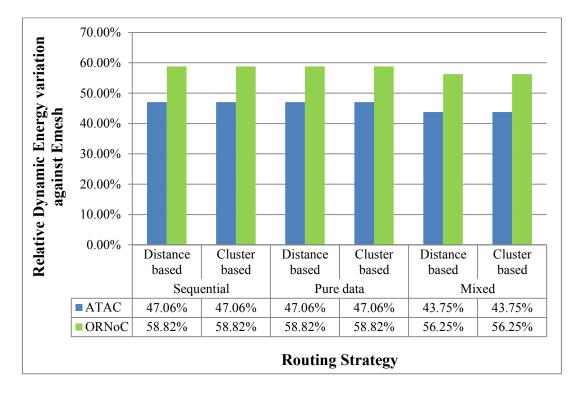

| Figure 74: Relative Dynamic Energy consumption variation for Routing Strategies N = {distance, cluster}                                                                                                                                                                                                                                                                              |

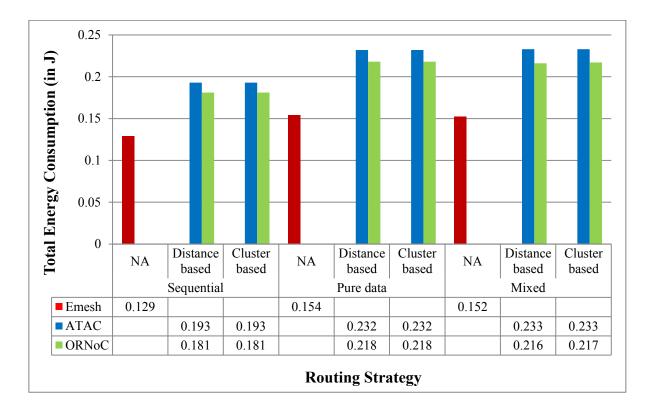

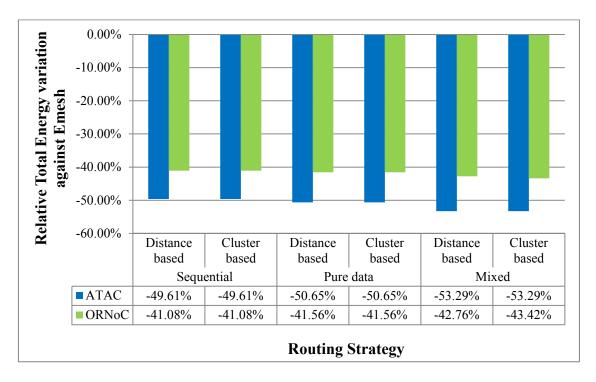

| Figure 75: Total Energy consumption for Routing Strategies $N = \{\text{distance, cluster}\} \dots 155$<br>Figure 76: Relative Total Energy variation for Routing Strategies $N = \{\text{distance, cluster}\} 157$                                                                                                                                                                  |

| Figure 77: Average Packet Latency for Flit Widths $N = \{16, 32, 64\}$                                                                                                                                                                                                                                                                                                               |

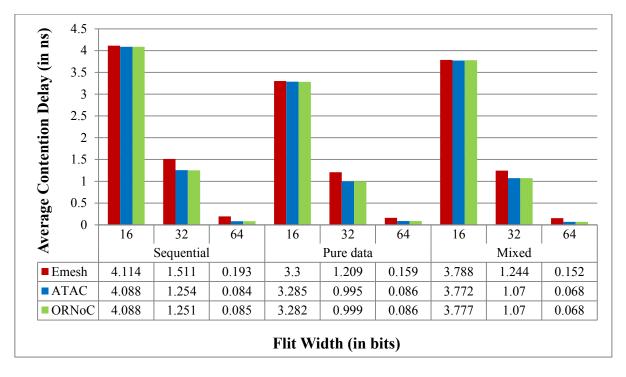

| Figure 78: Relative Latency variation for Flit Widths N = $\{16, 32, 64\}$ 161Figure 79: Average Contention Delay for Flit Widths N = $\{16, 32, 64\}$ 162                                                                                                                                                                                                                           |

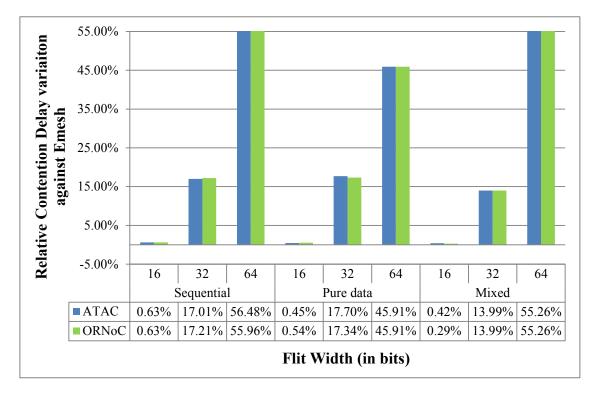

| Figure 80: Relative Contention Delay variation for Flit Widths $N = \{16, 32, 64\}$ 164<br>Figure 81: Total Static Energy for Flit Widths $N = \{16, 32, 64\}$                                                                                                                                                                                                                       |

| Figure 82: Relative Static Energy variation for Flit Widths $N = \{16, 32, 64\}$                                                                                                                                                                                                                                                                                                     |

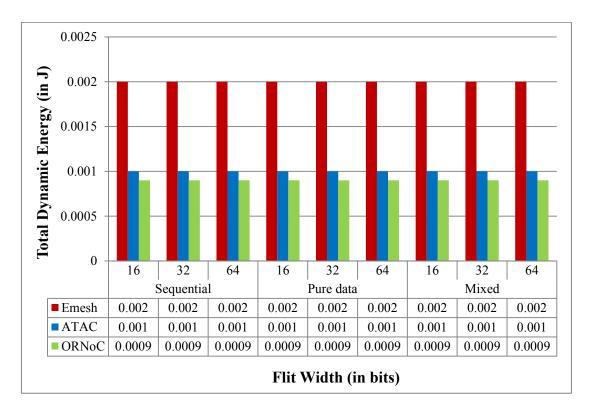

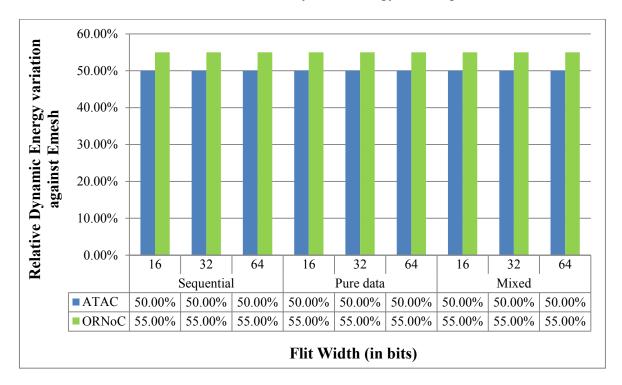

| Figure 84: Relative Dynamic Energy variation for Flit Widths $N = \{16, 32, 64\}$                                                                                                                                                                                                                                                                                                    |

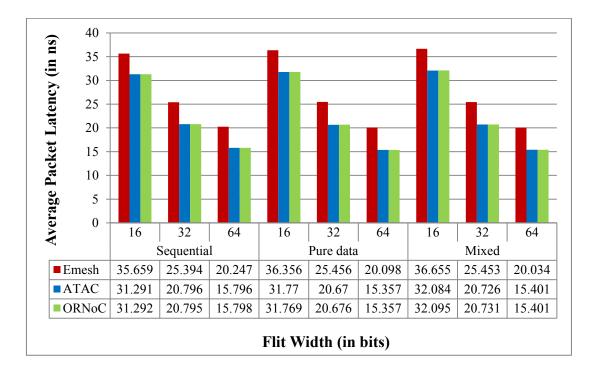

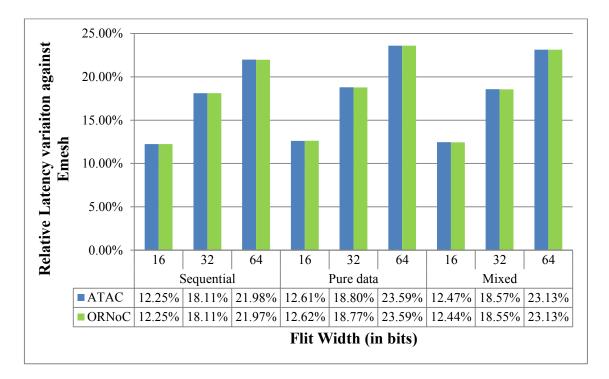

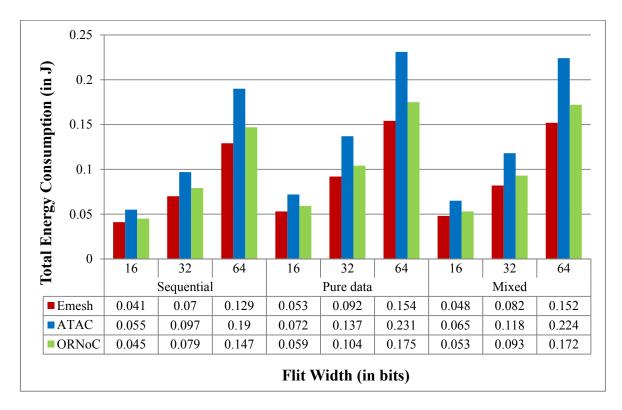

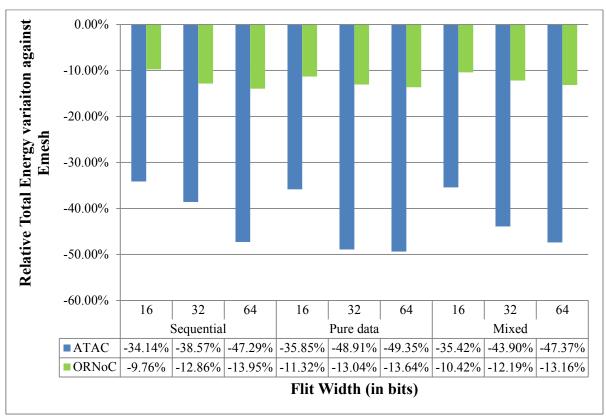

| Figure 86: Relative Total Energy variation for Flit Widths $N = \{16, 32, 64\}$                                                                                                                                                                                                                                                                                                      |

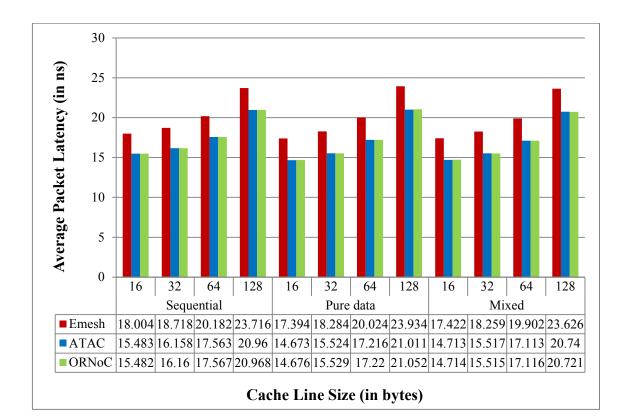

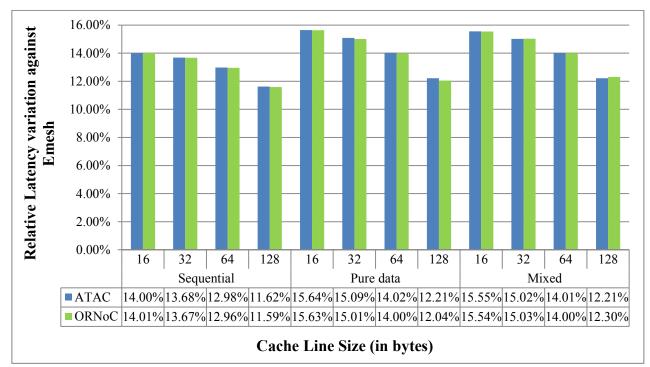

| Figure 88: Relative latency variation for Cache Line Sizes $N = \{16, 32, 64, 128\}$                                                                                                                                                                                                                                                                                                 |

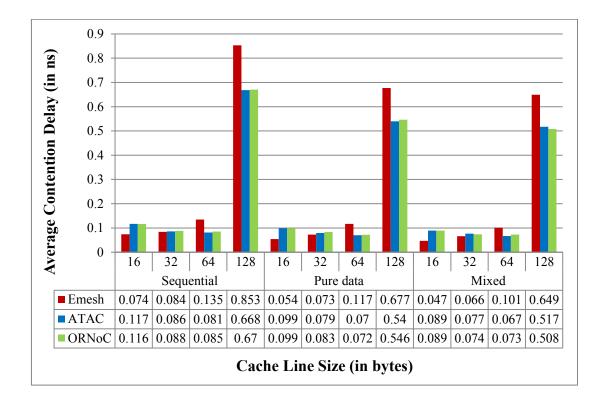

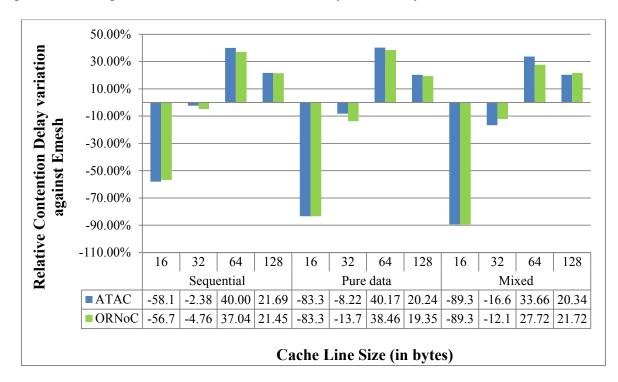

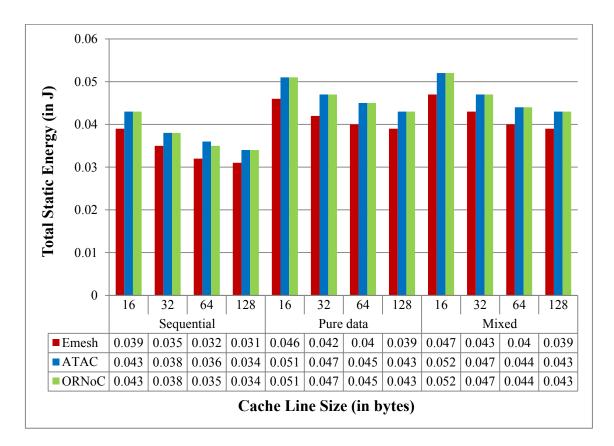

| 183         Figure 91: Total Static Energy for Cache Line Sizes N = {16, 32, 64, 128}                                                                                                                                                                                                                                                                                                |

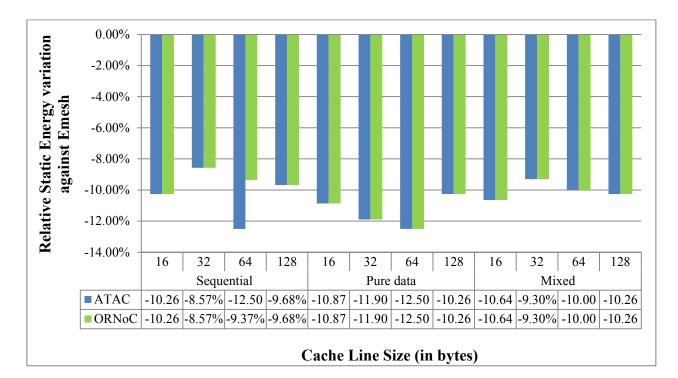

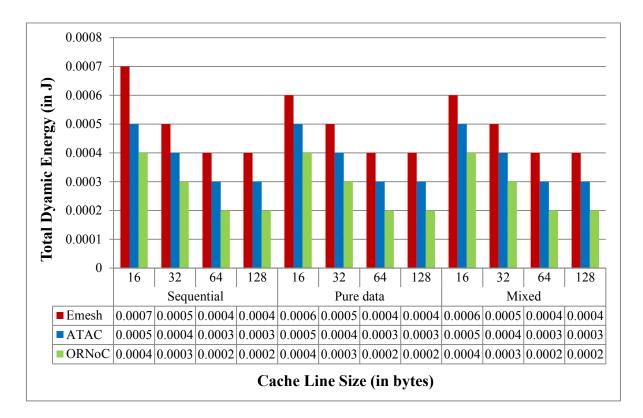

| Figure 92: Relative Static Energy variation for Cache Line Sizes $N = \{16, 32, 64, 128\} 187$<br>Figure 93: Total Dynamic Energy for Cache Line Sizes $N = \{16, 32, 64, 128\} 188$                                                                                                                                                                                                 |

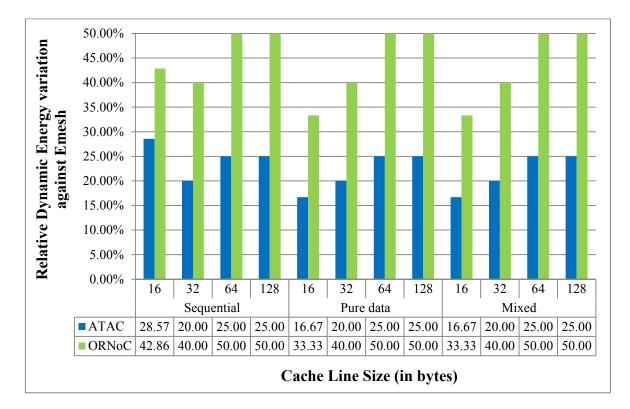

| Figure 94: Relative Dynamic Energy variation for Cache Line Sizes N = {16, 32, 64, 128}<br>190                                                                                                                                                                                                                                                                                       |

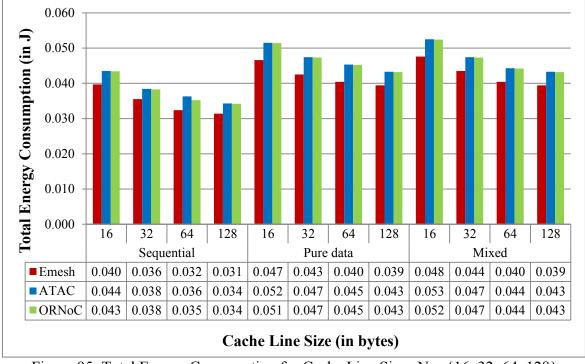

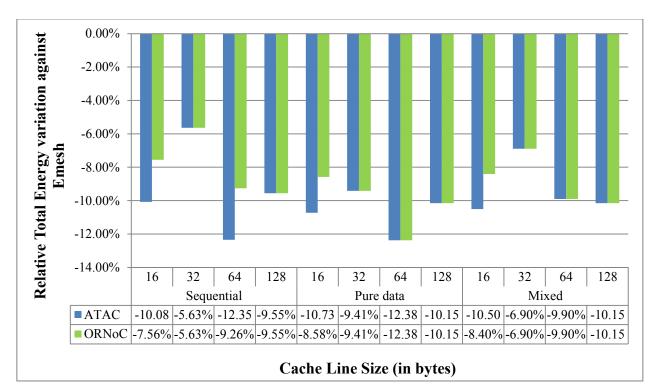

| Figure 95: Total Energy Consumption for Cache Line Sizes $N = \{16, 32, 64, 128\}$                                                                                                                                                                                                                                                                                                   |

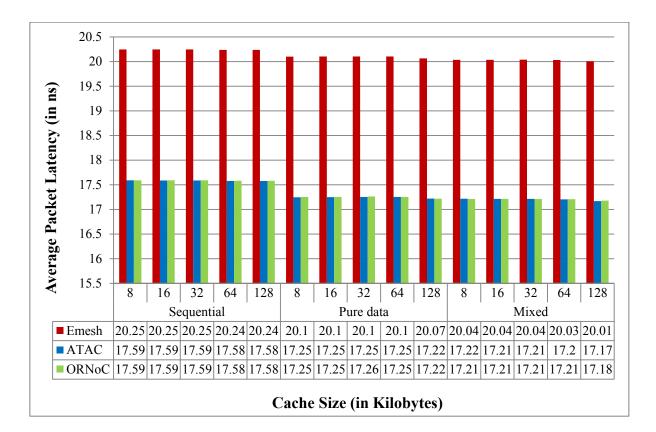

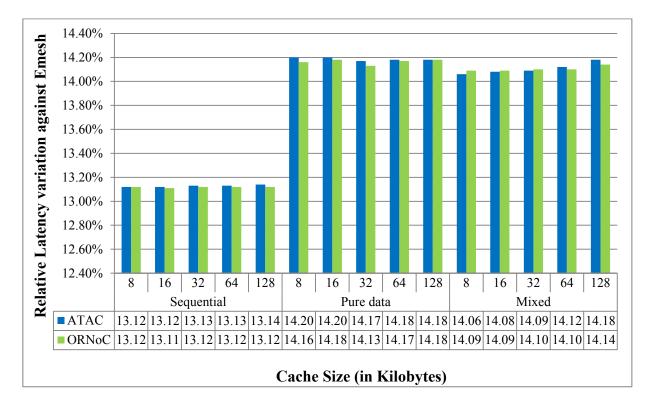

| Figure 97: Average Packet Latency for Cache Sizes $N = \{8, 16, 32, 64, 128\}$                                                                                                                                                                                                                                                                                                       |

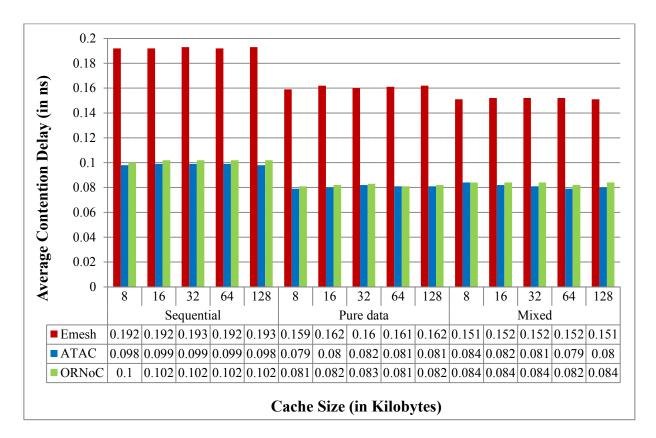

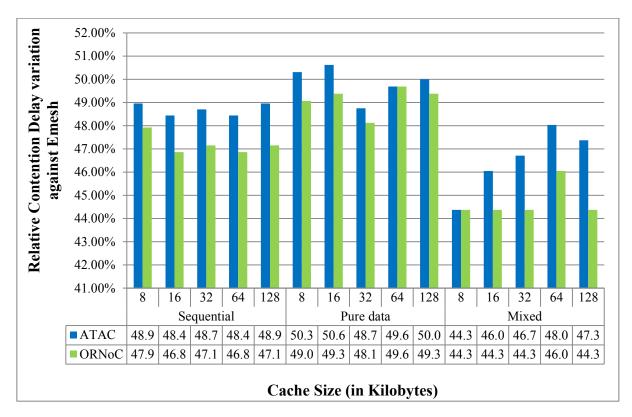

| Figure 99: Average Contention Delay for Cache Sizes $N = \{8, 16, 32, 64, 128\}$ 199<br>Figure 100: Relative Contention Delay variation for Cache Sizes $N = \{8, 16, 32, 64, 128\}$<br>                                                                                                                                                                                             |

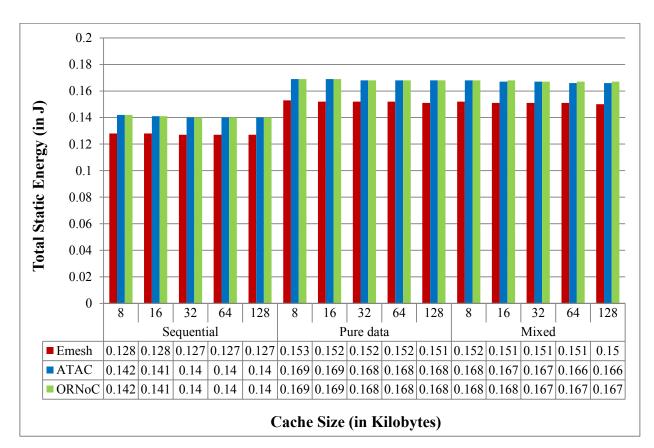

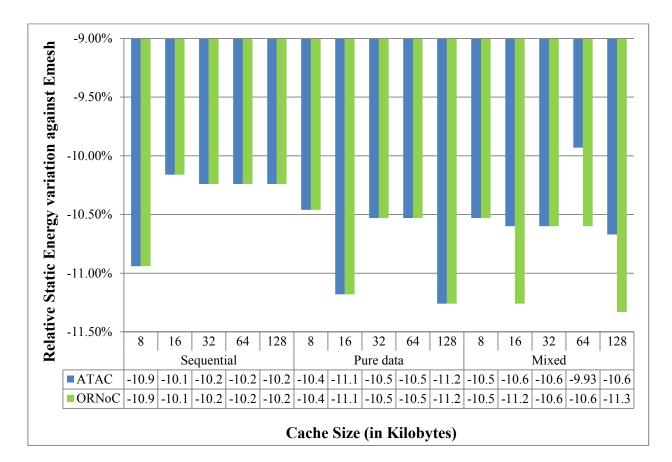

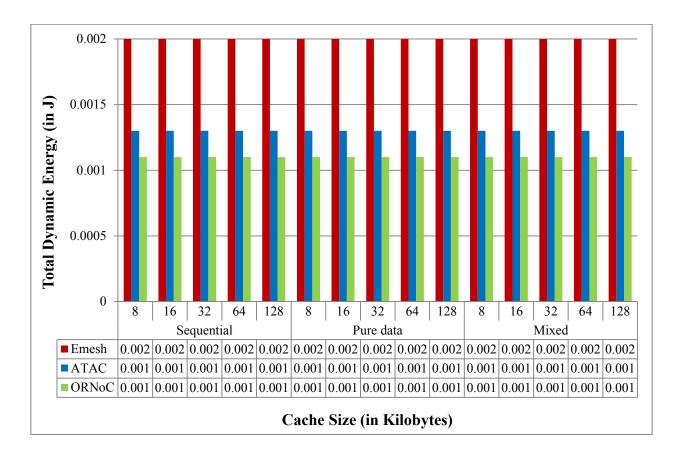

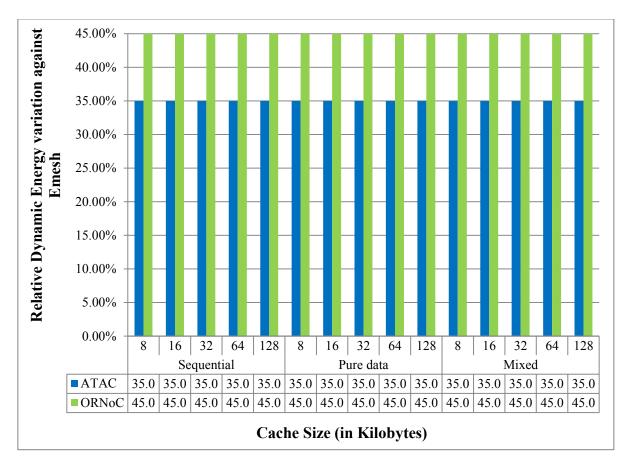

| Figure 101: Static Energy consumption for Cache Sizes $N = \{8, 16, 32, 64, 128\}$ 203<br>Figure 102: Relative Static Energy variation for Cache Sizes $N = \{8, 16, 32, 64, 128\}$ 205<br>Figure 103: Dynamic Energy consumption for Cache Sizes $N = \{8, 16, 32, 64, 128\}$ 207<br>Figure 104: Relative Dynamic Energy variation for Cache Sizes $N = \{8, 16, 32, 64, 128\}$ 207 |

|                                                                                                                                                                                                                                                                                                                                                                                      |

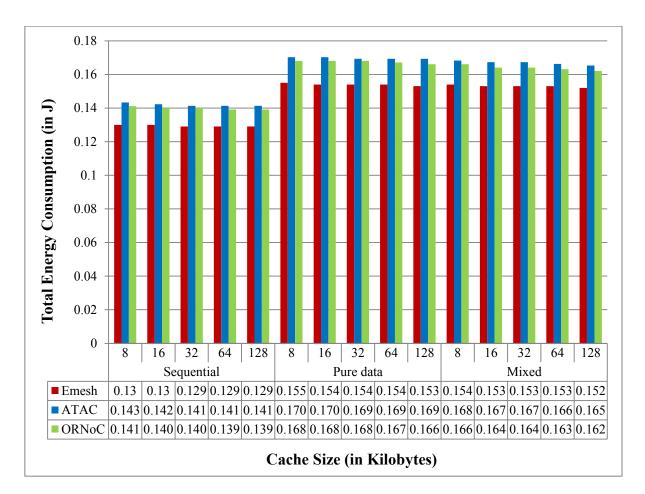

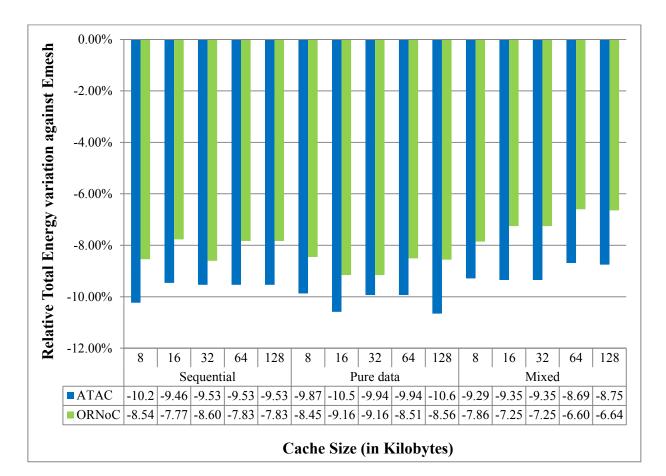

Figure 105: Total Energy consumption for Cache Sizes  $N = \{8, 16, 32, 64, 128\}$  ...... 209 Figure 106: Relative Total Energy variation for Cache Sizes  $N = \{8, 16, 32, 64, 128\}$  ...... 211

# **Chapter 1**

## Introduction

The advent of multicore processors has enforced two significant changes in the perception of solving complex computational challenges. Primarily, applications need to be developed keeping in mind the extent of software parallelization that can be extracted from each processing element. The main emphasis from the software perspective is modularization of the task at hand to be processed by multiple processing elements. Parallel computing platforms such as Nvidia CUDA[1] and Intel TBB[2] provide an environment for development of parallelizable code for multiple core graphics processing units and multicore processors respectively for the existing hardware.

The second area that demands attention is the requirement of novel and effective communication strategies for the effective distribution of tasks to the different cores to effectively address resource requirements. With the ever increasing numbers of processing cores that can be accommodated on a single chip, the communication among the processing units remains one of the main bottlenecks affecting the performance. Research on this field has unveiled the idea of networks on chip which has introduced different network architectures for managing the network traffic. Network on chip architectures have improved the scalability and performance of multicore systems. The observations from [3] indicate the advantages offered by photonic networks on chip, which have been enabled by advancements in the field of silicon photonics. They claim to have lesser power requirements and can provide higher bandwidth for communication of data between the cores. The field of optical networks on chip, which is relatively newer as compared to electrical NoCs and still under extensive research, require benchmarks and applications to validate their efficiency in different areas for software simulations.

An effective implementation of software parallelized application can improve the performance and reduce the latency[4]. It can be used to compare the performance of different network on chip architectures and also enables the hardware designers to choose the optimal design parameters.

### **1.1 Motivation and Problem Statement**

The field of optical network on chips offers vast avenues for exploration. Extensive research on the development of viable photonic network on chip architectures with varying routing strategies and communication protocols has been continuing over the past few years. Before the development of chips integrated with photonic networks, the efficiency of different architectures needs to be studied to tailor the needs of hardware designers.

Although there are other benchmarks that support multithreaded workloads, such as SPLASH [5] and PARSEC [6] do not have multiple parallelized versions of the same application. Having different parallelized versions of the application provides the freedom for software designers to choose the type of implementation based on their requirements. Software simulations can estimate the behaviour of an application on the actual hardware. Moreover they also provide the flexibility of running multiple test cases for multiple configurations and provide valuable data which forms the base for actual implementation in hardware. Hardware designers can use the simulation results from a benchmark to choose the NoC architectures to best suit their requirements. Also, comparison of NoC architectures in terms of software parallelized versions of a single application has not been performed yet.

The impact of different configuration parameters on the overall efficiency also needs to be studied to extract maximum hardware performance.

Hardware designers mostly have specific design requirements pertaining to resource utilization and trade-off between performance parameters like latency and power consumption for their application. Even though generalized experiments can provide an approximate estimate on the performance of a particular application in hardware, the demand for more accurate results necessitate the exploration of that specific application and generation of results based on them. The integration of photonic components on the silicon based chips can enable bring the efficiency of optics on intra chip communication.

The advancements in the field of technology and medicine have enabled the use of image processing applications for various needs and one such application uses the aid of edge detection in laproscopic surgery that requires very good accuracy and throughput[4]. Performing a surgery requires high precision and accuracy as mistakes would be life threatening. Since the surgical procedures need to be performed in real time, the communication needs to be efficient and real time. Canny edge detection is chosen in thesis keeping in mind the relative importance and for this particular usage in the medical field.

### **1.2** Proposed Solution

In order to extract the maximum performance and optimal resource utilization from the network architectures, it is necessary to have an application that effectively incorporates the different software parallelization schemes. Hence, an edge detection application, one of the most common and significant image processing algorithms, is chosen as the application to perform the experiments for its use in the field of laproscopic surgery which requires fast

processing. Moreover, the application has multiple stages of implementation and has the scope to allow different types of software parallelization techniques to extract maximum performance. This caters to the need of fully utilizing the parallel programming capability of a multicore chip.

The performance results are extracted based on the software implementation as well as the variation of the NoC design parameters. It is expected to provide invaluable information to the hardware designers regarding the choice of NoC architecture and the resources to be considered based on their design constraints.

### **1.3** Thesis Contribution

This thesis provides the following contributions:

- Implementing different software parallelization schemes to the Canny edge detection algorithm to estimate the optimal resource utilization.

- Comparison of chosen NoC and ONoC architectures to quantify the performance metrics like delay and energy consumption for the Canny edge detection algorithm.

- Provision of the software parallelized versions of the Canny edge detector application in an open source manner for benchmarking.

As mentioned above, this work aims at employing the Canny edge detection application, one of the simplest and most accurate edge detection application for the performance comparison of different NoC architectures, predominantly classified as electrical and optical. Our experiments address the need to explore an application which is optimized in terms of the parallelization schemes used for software development for observing the performance of network on chip architectures. Experiments are performed on the developed

application to compare and contrast the network features that influence the execution of an application on a multicore platform. Apart from helping to analyze the effectiveness of software parallelization of the algorithm in comparison with the sequential implementation, it also acts as an effective benchmark for the comparison of different on chip architectures. This also helps the designers choose the desired configuration for their architecture and the nature of implementation. It also explores the performance of network architectures based on variations to many input design parameters. Moreover, we hope that both analysis of the different parallel implantations of the Canny edge detection application and the analysis of different network-on-chip and communication parameters could be useful for the future designers in order to facilitate shorter time-to-market.

### 1.4 Outline

Our primary goal was to choose an application with widespread usage and that offers sufficient room to employ different parallelization strategies. Edge detection applications form the preliminary stages for many image processing, computer vision and machine learning applications for image segmentation and extraction of data[7]. We chose the Canny edge detection [8] algorithm to implement as our application because of its high accuracy and the parallelization schemes that can be applied to the different stages of the algorithm. The first step in the implementation involves development of the application and its execution in the native system. This process is carried out for all the three different implementations and observation of results.

The second stage involved porting of the algorithm to a multicore Network on Chip (NoC) simulator to analyze and compare the chosen outputs for the NoCs. We use the Graphite

multicore simulator[9], which extracts the network performance based on different configuration parameters.

#### 1.5 Related Work

This thesis explores related work in 4 different domains, which are: the necessity for Networks on Chip, Optical Networks on Chip and their advantages over NoC, comparison of NoC simulators and the application used for implementation including their parallelization strategies.

#### **1.5.1** Networks on Chip

The trend of using multi-core processors at a lesser clock frequency to increase the chip performance has introduced packet-based routing networks for global intra-chip communication, commonly known as network on chip. The increase in the number of processing elements that can be accommodated on a chip has increased the shared buses can be easily implemented, has a simple topology and low area cost. The different types of communication networks on a chip include shared buses, direct networks, indirect networks and hybrid networks[10]. The direct networks have direct connection between each of the cores which does not require any specific routing mechanism, while the indirect networks operate with routing schemes among nodes to provide full connectivity. The hybrid networks utilize a mixture of both the direct and indirect networks. The increased contention delays, the energy consumption, larger latency and lower bandwidth proves to be disadvantageous for a larger sized network in the case of shared buses [11]. The crossbar networks[10], a form of indirect network that has indirect connection between all the cores were introduced as an improvement over the shared buses, which provide better bandwidth and reduces the contention for data path. But, the advantages of shared buses are not reciprocated by

crossbars as they have larger energy consumption, larger global wire placement issues in case of a large network and have lesser scalability[10]. With further increase in the size of on-chip networks, the requirement for increased bandwidths, lesser contention and data latency, lesser global wires to reduce area consumption needed to be introduced. The 2D mesh topology provides direct connection between the cores and is one of the easiest yet efficient implementation of the above requirements at the expense of routers for proper routing between cores[10].

#### **1.5.2 Optical Networks on Chip Architectures**

The electrical NoCs restrict the scalability due to increase in the propagation delay and losses due to inductive and capacitive coupling[12] and limited bandwidth. This has inspired researchers to work with opto-electrical components to create photonic network on chip and its advantages techniques over the conventional electrical networks have been a subject of research for many publications. The idea and improvements offered by photonic networks on chip over the electrical networks are given in [13]. The challenge of scaling the bandwidth and minimizing latency keeping the power consumption values in check is identified in [3] and a hybrid photonic network on chip with electrical network for the local communication while utilizing the optical network for global communication. A 2x2 photonic switching matrix that uses micro ring resonators is used for the photonic network implementation is presented in [3]. There are many optical network on chip architectures proposed like Corona[14], CHAMELEON (CHANNEL Efficient Optical Network On Chip)[15], Firefly[16], ATAC[17] and ORNOC[12] each with their unique style of integration of photonic and electrical components for creating a communication network within the chip. While [18] proposes the usage of an electrical control network and photonic data transmission which causes contention in the system, [19], [20] proposes architectures that do

not allow wavelength reuse and hence, affects the scalability. Corona[14] performs multiple writes and hence, needs arbitration to solve for write conflicts in the network. Firefly[16] tries to reduce the power consumption by using a separate data initialization packet for switching on the data receiver resources. This causes additional latency and in turn rapidly reduces throughput. FlexiShare[21] uses token stream based arbitration scheme to transfer the packets. CHAMELEON[22] provides an extension to the ORNoC architecture by opening point-to-point connections at run time, using a reconfiguration layer thereby increasing the bandwidth with respect to the network traffic and reducing the power consumption in the optical network. But, it requires a separate electrical layer to act as a control network over the optical network for the configuration process. This causes additional area and power overhead, hence making it disadvantageous. ATAC[17] uses a cluster (refers to a group of nodes) based architecture with all the nodes. ORNoC, similar to ATAC uses a cluster based arrangement, but uses a ring based routing scheme which assigns specific wavelengths for communication between the cores while allowing reuse of wavelengths in possible cases, to reduce power consumption. Both ATAC and ORNoC propose contention-free architecture, where the data packets do not need arbitration before they are transferred via the network. Out of these, ATAC and ORNoC are considered for evaluation in this thesis are as they have arbitration free architecture and do not require a separate control layer and hence, reduces power and area consumption.

#### **1.5.3 NoC Simulators**

The research in the area of photonics NoCs is still progressing and the performance evaluation makes use of different multi core simulators. NocSim[23] implements different electrical network topologies like the torus and star topologies exclusively for electrical NoCs. Orion[24] implements the power and area modelling for electrical networks. It has a

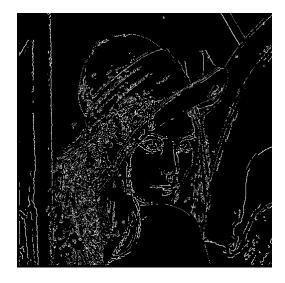

lot of shortcomings like incomplete architecture and router timings, not being scalable, very low accuracy for current models and incapability in the expansion of current models. PhoenixSim[25] introduces a parametrized modeling of optical networks. But, it uses the electrical modelling from Orion, which includes all its disadvantages, and moreover does not have suitable interconnection between electrical and photonic networks. Graphite[9] is a comprehensive multicore simulator which implements both electrical and photonic NoCs. It uses Design Space Exploration for Networks Tool (DSENT) [26] for evaluating the power and delay consumption in the network. DSENT provides a good interface between optical and electrical networks and also models the networks better as compared to ORION. Graphite, irrespective of not being a cycle accurate simulator, implements synchronization schemes to give almost near cycle accurate performance with lesser simulation time as compared to the cycle accurate simulators. The three synchronization schemes supported by Graphite are: the lax, the lax with barrier synchronization and the lax with point-to-point synchronization. While the lax synchronization assigns local clocks to each of the cores, the lax barrier scheme waits on a fixed number of cycles to synchronize the execution of threads. In the lax with point-to-point synchronization, each tile periodically synchronizes with another tile and when the difference is greater than a certain number of cycles, the tile that is ahead sleeps for some time. Graphite achieves 41x slowdown compared to execution in the native machine while the cycle accurate simulators require a 1000x to 100,000x slowdown overhead for increased accuracy. Hence, we use the Graphite simulator for analysis of the results and comparison of the NoC architectures.

#### **1.5.4 Application and Parallelization strategies**

The Canny edge detection[8] application has been implemented in CUDA[27] and used for evaluating improvement in the performance of GPUs over CPUs in[28]. The application is

also used to study its performance on multicore central processing units and many core graphics processing units in [9], which implements the different steps for edge detection with different parallelization schemes. This approach, along with sequential[29] and pure data parallelism approaches has been implemented to observe and evaluate their performance on the network on chip architectures. While SPLASH benchmark suite has more applications mainly in the field of High Performance Computing like *barnes*, *cholesky*, fmm, lu and ocean, PARSEC benchmark suite supports applications in more variety of fields like Computer Vision, Data Mining, Media Processing and Financial Analysis. While the SPLASH[5] and PARSEC[6] benchmarks are provided in the simulator for performance comparison of the architectures, they do not implement different parallelization schemes for the same application. We compare three different types of software parallelized implementations of the Canny Edge Detection. A handful of design parameters from a comparatively large design space are modified to simulate and obtain the results. These parameters are chosen based on their significant effect on the performance and energy consumption of the network and direct impact on network traffic while saving additional simulation costs.

### **1.6 Thesis Organization**

The thesis is organized as follows: In Chapter 2, we discuss the theory behind network on chips and optical network on chips. Additionally, we explore the design of the NoC architectures used for comparison. In Chapter 3, we introduce in detail, the steps involved in the edge detection application used for performing the comparison of the architectures. We also elaborate on the parallelization schemes considered for implementation and the structure

and organization of the bitmap images which are used as workloads for edge detection in this thesis. In Chapter 4, we describe the software implementation of the edge detection application along with the Graphite simulator framework. The experiments for different configurations performed with the multicore architectures and simulation results are presented in Chapter 5. The conclusions are provided in Chapter 6 and the future work is described in Chapter 7.

# **Chapter 2**

## Networks on Chip – Components and Architectures

This chapter provides an insight into the components and working of different network on chip (NoC) architectures for multicore systems. The general NoC components are introduced in the context of an electrical and two hybrid opto-electrical NoCs. The hybrid networks discussed in this thesis are clustered architectures: the intra-cluster communication uses electrical network, whereas the inter-cluster network uses an optical ring network. The first section introduces the concept of network on chip and the corresponding components that constitute an on-chip electrical network used for intra cluster communication in the photonic architectures under consideration. It also describes the electrical network on chip architecture considered for the experiments, which uses the electrical mesh topology, which is also the stand-alone, electrical network for our experiments. The knowledge of the operation of intrachip networks provide an estimate of the various challenges that are present and how the proper choice of network parameters helps in effectively analyzing them. The second section goes on to explain optical network on chip and the additional photonic components applicable for the network communication in this case. The third section introduces the photonic network on chip architectures considered for evaluation.

The necessity of processing data quickly and efficiently has been and is still, a major concern in the field of embedded technology. The processing power offered by a single processor has been exhausted for some time and the attention gradually shifted to the need for multiple processing units on a single chip to magnify the processing power that was provided by the single processing unit[30]. The number of transistors on a chip, which in turn escalates the processing power, doubles every eighteen months, according to Moore's law[31]. This enables addition of more and more processing elements on a smaller die.

Nowadays, with the market supporting many computing systems with multiple processing units has paved way for a new challenge which is having efficient communication between the multiple processing units to solve the computational tasks quickly and efficiently. The coding techniques also require to be revised for parallel execution rather than the conventional serial programming methodology for efficient distribution of tasks among the chip multi processors[32]. Thus, the overall efficiency of an application became dependent on a lot more parameters which are related to the communication network between the processors as well. A consideration of whether the communication between the processing units is going to slow down or speed up the execution of the program compared to its execution with a single or minimal number of processors proves to be vital in choosing the number of processors and the corresponding communication architectures for a particular application.

The traditional single core processors and systems with very limited number of cores managed power efficient and optimum bandwidth communication using shared buses for data transfer. This can be accounted to the limited communication requirements in such systems. Ref. [33] identifies scalability as one of the prominent issues with bus based networks, due to the increased bus parasitic capacitance and arbitration complexities in case of larger networks. With the gradual increase in the number of processing cores, bus based communication schemes became tedious and less effective in power efficient, high bandwidth communication [1] and hence on-chip electrical interconnect architectures were introduced [34]. Usage of electrical links as a medium of communication in the network on

chip proved to be sufficient at first, as additional data lines and control lines could easily be implemented by means of single wire connections. Although this would suffice in the case of a smaller system with few processors, it can prove to be highly disadvantageous in the case of a network with a large number of processing units. The scenario of global electrical interconnects in larger networks introduce a case where the propagation delay and interconnect noise increases which in turn affects the bandwidth and ultimately the system performance[12]. The idea of pipelined interconnects for global communication increases the delays and also, the power requirements for the network increases due to higher clock frequency and the requirement of additional registers[12]. The performance-per watt scaling for increasing physical cores in chip multiprocessors is also not addressed efficiently by pure electrical interconnects[3].

The advancements in the field of silicon photonics have provided feasible methods for combining the traditional electrical interconnects with optical interconnects that have high bandwidth and low latency[12]. They also provide bit rate transparency, where the power consumption is independent of the number of bits transmitted. Optical fibers are used as the communication channel in the network and the laser sources are used to produce lights of different wavelengths for communication between different processing units. Micro ring resonators which respond differently to different wavelengths of light act as switches that filter the resonant wavelengths to enable transport of data between the different processing units[35]. Wavelength Division Multiplexing (WDM) technique enables the usage of multiple wavelengths for simultaneous data transmission with minimal losses[36]. This improves the throughput as optical networks use light as the medium of transmission which is much faster than electrical signals and has better immunity to electromagnetic noise[12].

There are different types of architectures proposed for implementation of optical network on chip and with different properties like the physical layout, the number of wavelengths used and the topology used for communication. This thesis is aimed at providing a comparison between the different features of the optical and electrical networks on chip and how it affects the efficiency of the specific application in consideration, with different combinations of network features like the network type, number of processor cores used, the number of clusters, the routing strategy, the number of optical access points, the flit width and the cache properties, used and the workload of the application.

The network on chip architectures considered for the experiments are: one electrical NoC using the mesh topology named Emesh, and two different optical NoCs namely ATAC and ORNoC. They have been modeled on the Graphite [9] multicore simulator which provides a set of configuration parameters that can be used to create different designs.

### 2.1 Networks on Chip (NoC)

Processing units that are interconnected by means of wires can be categorized based on their communication pattern or topology. The important ones include shared network bus interconnection, point-to-point (crossbars) networks, indirect networks which use NoCs[37].

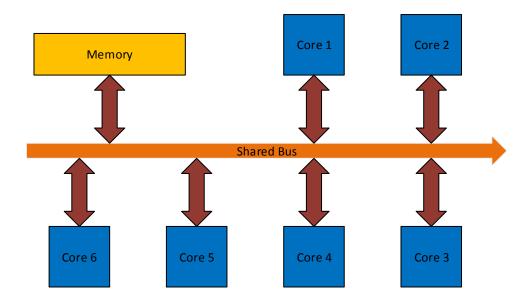

Figure 1: The Shared Bus Architecture

The shared bus architecture uses a shared bus as the name suggests, for communicating between the components in the system. The components follow an arbitration scheme to access control of the bus and transfer data. The main shortcoming of the bus based scheme is the competition for the control of the bus which increases with increase in the number of components connected to it. According to [37], it is also incompetent in addressing the increase in power consumption when more units are attached to the system. Furthermore, it complicates the arbitration process in the cases of buses with multiple masters. The bus based communication structure is depicted in Figure 1.

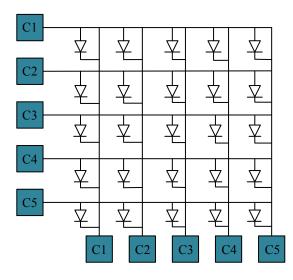

Figure 2: Buffered Crossbar Architecture

The crossbar communication scheme overcomes the contention problem in shared buses and provides good results for smaller networks. The crossbar network involves direct point-to-point connections between all the components in the network. For a smaller network, this provides better connectivity with lesser contention as compared to buses at the expense of more power consumption due to the increased number of connections. The dedicated point-to-point communication topology also introduces improvement in the simplicity of the design and better bandwidth and latency. But, the number of connections increases exponentially with the increasing number of cores. With increasing network size, this leads to increase in the on-chip area consumption and also complicates the wiring layout and routing[37]. The buffered cross bar structure is shown in Figure 2 where C1, C2 etc are the cores and connected by means of tri state buffers.

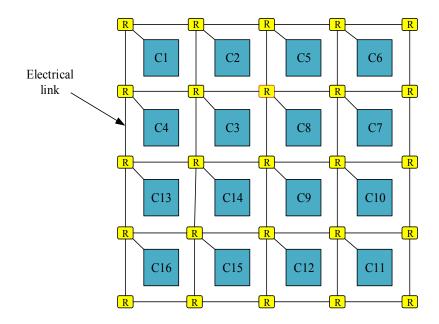

Figure 3: Electrical Mesh (Emesh) architecture

The concept of network on chip provides an organized structure for efficient communication. This implements a network along with proper routing strategies for the specific hardware to reduce the complexity and global foot print. It enables reuse of the components without incurring high scalability costs. It also has lower complexity of design and implementation expense. The electrical network architecture considered in our application is the electrical mesh network which is among the simplest of networks and supported by the simulator. Emesh or electrical networks form a square mesh connecting the cores in the network and uses the XY routing or transfer of data between the cores. Section 2.4.1 explains the XY routing in detail. The electrical mesh network is portrayed in Figure 3, where C1, C2 etc. represent the core numbers and R represents the routers.

According to [38], the major components of any network are links, routers and network interfaces and are described below. The router implements routing strategies based on protocols which are used for transmission of data packets to the next link or the destination core to which they are addressed. The routing protocol has methods laid out mainly to deal

with network contention, to increase throughput and avoid data race situations in the network. The network interfaces establish a connection between the IP cores and the network, which helps in incorporating distinct protocols that each IP might have with respect to the whole network.

**Links:** The links are represented by wires which form the physical connection between routers in the network. Full-duplex communication enabled networks have dual channels for enabling bidirectional communication simultaneously and the channel bandwidth is represented by the number of wires that constitute the channel. Synchronous as well as asynchronous links can be established in a network based on the bandwidth and throughput requirements.

**Routers**: Each router needs to be connected to the network as a whole for proper guiding of the packets, a switching matrix for identifying the next router or IP core to pass the packets to and ports to access the IP cores which are connected to it. The routing algorithm defined in a router decides which path the data packet should take to reach its destination. The choice of a routing algorithm depends on the trade-off between the throughput and the latency of the network. The switching scheme emphasizes on how the data transmission takes place, whether through a predefined path by reserving it at the start of the transmission or a more dynamic strategy in which the path to be followed is chosen by the amount of network traffic. When there are multiple requests for data transmission to the same output port, the arbitration policy is responsible for selecting one router input port from which the output port receives the data. When there is a delay in the data transfer, in case of dynamic routing there is a need for the storage of packets temporarily before the network can resume sending them, which is taken care of by the buffering policy.

19

**Network Interfaces**: The network interfaces handle the unique protocols that each core has with the network and acts as the boundary between the actual processing and communication. The front end of the network interfaces deal with the requests and acknowledgements for the core while the back end supports the network on chip by mainly ensuring that the packets are encoded and decoded correctly, and synchronizing the data received by the buffers.

### 2.2 Optical Networks on Chip (ONoC)

Electrical NoCs are advantageous in the case of small-scale networks, which require lesser communication between the cores. With the advent of newer technologies that propose to enhance the processing power of devices, using thousands of cores the shortcomings of the electrical networks are highlighted over their advantages.

Optical networks on chip are introduced as an alternative for efficient communication between multiple cores on a single chip. They make use of silicon photonics for better and effective communication in addition to electrical networks for communication. These ONoCs are offer better scalability with reduced latency and increased bandwidth.

The communication uses a light source and optical waveguides for transmission of data over the optical network. There are optoelectronic interfaces at both the transmitting and receiving ends of the network. The electrical signals are converted to optical signals at the transmitting end before passing it to the network as photons through the waveguide. At the receiving end, a light sensing device like a photodiode detects the photons and they are converted back to the electrical signals and distributed to the respective cores.

#### 2.2.1 Wavelength Division Multiplexing

Wavelength division multiplexing is the optical multiplexing scheme proposed for communication in the optical network on chip architectures in consideration. Different wavelengths of light are multiplexed to be propagated through a single fiber and are demultiplexed at the receiver end wavelengths. The reduced power requirement for this data transmission scheme also makes it a primary choice for on chip networks.

The number of channels used for communication and the spacing between the wavelengths are directly related. Although there is a theoretical advantage in terms of data transfer rates in having a single channel, multiple channels are often used with proper separation between different wavelengths, to reduce the adverse effects of dispersion and crosstalk. The choice of optimum number of channels required for transmission relies on the trade-off between the speed of transmission needed and the integrity of communication. The imperfections or deformities in the optical fiber while manufacturing also add to the list of losses happening in the waveguide. These losses due to improper manufacturing are common to all media used for transmission.

#### 2.3 Optical Components in ONoC

The integration of silicon and photonics portrays a need for additional components for efficient conversion of signals from electrical to optical domain, transmission and reception and vice versa. Minimal losses in the conversion and transmission processes are necessary to justify the usage of optical network on chip communication architectures. The network is composed of both active and passive optical components that contribute to the electro-optical and opto-electric conversions, their routing and proper detection to regenerate the transmitted electrical signals.

**Waveguides:** Waveguides are the fundamental unit for optical data transmission. The propagation of optical signals uses the principle of total internal reflection. The difference in refractive induces of the core and cladding components of the waveguide helps guide light through it. Optical waveguide losses need to be minimized for efficient optoelectronic communication. The losses in optical waveguides can be predominantly classified into two – scattering losses occurring due to abnormalities in the core and cladding interfaces during fabrication and absorption losses due to the different bonds in the waveguide material[39]. Such interconnects also undergo process variations due to fabrication imperfections which can result in high losses[39]. The bending radius of the optical fibers, and in turn, its cross sectional dimensions needs to be sufficiently large enough to have low bending losses[40]. Ref. [40] also discusses etchless waveguides that can reduce bending losses while allowing for better integration as compared to ridge waveguides.

**Lasers:** The light sources for communication in the optical interconnects are lasers of multiple wavelengths. Both on-chip and off-chip laser sources are available, each having their respective pros and cons. The off-chip lasers have high light emitting efficiency along with good stability with temperature at the expense of relatively higher coupling losses while integration with an silicon chip[41]. On the other hand, on chip laser sources provide better integration capability, energy efficiency and proportionality with a compact size, with the problem of only the low emission rates of Si limiting the integration process[41]. The important geometric parameters to be considered for the laser sources are: the waveguide distance, the length between the source and the waveguide, the waveguide width, which is the relative difference in radii between the core and cladding, the nominal micro disk laser

radius and the minimum source to source spacing in the case of multiple single wavelength sources.

**Modulators:** Ring modulators along with the modulator drivers are used for the conversion of electrical signals into optical signals at the opto-electric interface. They also couple the different wavelengths of light into the waveguides at the beginning of transmission in the optical network.

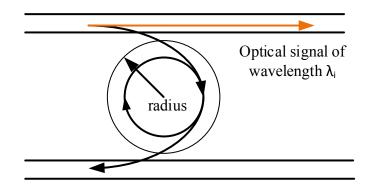

**Micro-ring Resonators:** The optical switching of different wavelengths of light in ONoCs are carried out by filtering the signals based on the resonant wavelengths by passive optical components called micro ring resonators. They select and redirect the light signals based on their wavelength to the respective destinations. Figure 4 depicts the structure of an optical modulator and the filtering process.

Optical signal of wavelength  $\lambda_n$ - the resonant wavelength

Figure 4: Optical Micro Ring Resonator[42]

The micro ring resonators are sensitive to different wavelengths of light in such a way that they act as filters for coupling a particular wavelength of light into a specific plane of the waveguide relative to the input signal. It works based on the following principle[35]:

- when λ = λ<sub>n</sub>, the signal couples into the resonators, and outputs into a waveguide in the same plane as that of the input, where λ<sub>n</sub> is the resonant wavelength.

- when  $\lambda \neq \lambda_n$ , the signal propagates along the same waveguide and the output is obtained on a different plane as that of the input, where  $\lambda_n$  is the resonant wavelength.

Here, signifies the wavelength being transmitted in a given waveguide at a given time, while shows the resonant wavelength for which the transmitted light is passed to the receiver network and finally the destination core.

**Photodetectors:** The photodetectors form a vital component of the reception part of the ONoC receiver side. The light signals are detected by the photodetectors, which are converted initially to photocurrent based on the wavelength of the light signals used, and transferred to a driver circuit which converts the analog current signals to digital signals. The digital signal is de-serialized and then transferred to the electrical network[43].

### **2.3.1 Communication Process**

The communication process in an ONoC can be broadly classified into intra-layer and interlayer communications. While the intra-layer communication defines the communication between cores in the *same* electrical layer, the inter-layer communication specifies the communication between *different* electrical layers[43]. The intra-layer communication as per [43] uses purely electrical signals in a 2D mesh architecture with XY routing for communicating between the nodes, where node includes a processor and its local memory.

The inter-layer communication process is slightly more complicated, which uses electrical signals for communicating to the optical network interface (ONI), where the electro-optical conversion of the signals occur followed by the optical routing and the optical signals are received and converted back at the optical network interface and transmitted to the destination node via electrical signals. The optical routing of signals uses the optical

switches mentioned in the previous section to direct the optical signals to the respective ONI. The steps for inter-layer communication[43] is mentioned below:

• Electro-optical conversion: this step achieves the conversion by initially serializing the input data and the data is segregated using de-multiplexers. This data is further converted to photonic current by the drivers and used to generate light from the laser. This in turn controls the light intensity of the laser source and assigns specific wavelengths. These wavelengths are then modulated into the waveguides. This procedure is depicted in Figure 5.

Figure 5: Data transmission in the Electro-Optical Network[35]

- **Optical Routing**: the different wavelengths of light are routed with the help of micro ring resonators, which identifies the path based on the wavelength used, and this process of routing continues till it reaches the destination photodetector.