# Efficient Scheduling and High-Performance Graph Partitioning on Heterogeneous CPU-GPU Systems

Bahareh Goodarzi

A Thesis

in the Department

of

Computer Science and Software Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy (Computer Science) at Concordia University Montréal, Québec, Canada

> July 2018 © Bahareh Goodarzi, 2018

## CONCORDIA UNIVERSITY Engineering and Computer Science

This is to certify that the thesis prepared

By: Bahareh Goodarzi Entitled: Efficient Scheduling and High-Performance Graph Partitioning on Heterogeneous CPU-GPU Systems and submitted in partial fulfillment of the requirements for the degree of

#### Doctor of Philosophy (Computer Science)

complies with the regulations of this University and meets the accepted standards with respect to originality and quality.

Signed by the final examining commitee:

|                           | Chair               |

|---------------------------|---------------------|

| Dr. Nizar Bouguila        |                     |

|                           | External Examiner   |

| Dr. Michel Dagenais       |                     |

|                           | External to Program |

| Dr. Anjali Agarwal        |                     |

|                           | Examiner            |

| Dr. Brigitte Jaumard      |                     |

|                           | Examiner            |

| Dr. Hovhannes Harutyunyan |                     |

|                           | Supervisor          |

| Dr. Dhrubajyoti Goswami   | -                   |

Approved by \_\_\_\_

Dr. Volker Haarslev, Graduate Program Director

Tuesday, August 21, 2018

Dr. Amir Asif, Dean Faculty of Engineering and Computer Science

### Abstract

### Efficient Scheduling and High-Performance Graph Partitioning on Heterogeneous CPU-GPU Systems

Bahareh Goodarzi, Ph.D.

Concordia University, 2018

Heterogeneous CPU-GPU systems have emerged as a power-efficient platform for high performance parallelization of the applications. However, effectively exploiting these architectures faces a number of challenges including differences in the programming models of the CPU (MIMD) and the GPU (SIMD), GPU memory constraints, and comparatively low communication bandwidth between the CPU and GPU. As a consequence, high performance execution of applications on these platforms requires designing new adaptive parallelizing methods. In this thesis, first we explore embarrassingly parallel applications where tasks have no inter-dependencies. Although the massive processing power of GPUs provides an attractive opportunity for high-performance execution of embarrassingly parallel tasks on CPU-GPU systems, minimized execution time can only be obtained by optimally distributing the tasks between the processors. In contemporary CPU-GPU systems, the scheduler cannot decide about the appropriate rate distribution. Hence it requires high programming effort to manually divide the tasks among the processors. Herein, we design and implement a new dynamic scheduling heuristic to minimize the execution time of embarrassingly parallel applications on a heterogeneous CPU-GPU system. The scheduler is integrated into a scheduling framework that provides pre-implemented automated scheduling modules, liberating the user from the complexities of scheduling details. The experimental results show that our scheduling approach achieves better to similar performance compared to some of the scheduling algorithms proposed for CPU-GPU systems. We then investigate task dependent applications, where the

tasks have data dependencies. The computational tasks and their communication patterns are expressed by a task interaction graph. Scheduling of the task interaction graph on a cluster can be done by first partitioning the graph into a set of computationally balanced partitions in such a way that the communication cost among the partitions is minimized, and subsequently mapping the partitions onto physical processors. Aside from scheduling, graph partitioning is a common computation phase in many application domains, including social network analysis, data mining, and VLSI design. However, irregular and data-dependent graph partitioning sub-tasks pose multiple challenges for efficient GPU utilization, which favors regularity. We design and implement a multilevel graph partitioner on a heterogeneous CPU-GPU system that takes advantage of the high parallel processing power of GPUs by executing the computation-intensive parts of the partitioning sub-tasks on the GPU and assigning the parts with less parallelism to the CPU. Our partitioner aims to overcome some of the challenges arising due to the irregular nature of the algorithm, and memory constraints on GPUs. We present a lock-free scheme since fine-grained synchronization among thousands of GPU threads imposes too high a performance overhead. Experimental results demonstrate that our partitioner outperforms serial and parallel MPI-based partitioners. It performs similar to shared-memory CPU-based parallel graph partitioner. To optimize the graph partitioner performance, we describe an effective and methodological approach to enable a GPU-based multi-level graph partitioning that is tailored specifically for the SIMD architecture. Our solution avoids thread divergence and balances the load over GPU threads by dynamically assigning an appropriate number of threads to process the graph vertices and irregular sized neighbors. Our optimized design is autonomous as all the steps are carried out by the GPU with minimal CPU interference. We show that this design outperforms CPU-based parallel graph partitioner. Finally, we apply some of our partitioning techniques to another graph processing algorithm, minimum spanning tree (MST), that exhibits load imbalance characteristics. We show that extending these techniques helps in achieving a high performance implementation of MST on the GPU.

# Acknowledgments

First and foremost, I would like to express my special gratitude to my supervisor Dr. Dhrubajyoti Goswami for his invaluable guidance, support, patience, trust and encouragement during the course of my PhD. I am always indebted to him for inspiring me in digging the new research paths and providing me with every bit of guidance, expertise, assistance and valuable understanding. His constructive feedback and guidance, steered me in the right direction throughout my research. I also learned form him professionalism, commitment and compassion.

I would like to thank my committee members, Dr. Brigitte Jaumard, Dr. Hovhannes Harutyunyan and Dr. Anjali Agarwal, for their insightful comments and encouragement, to widen my research from various perspectives.

I am grateful to Dr. Martin Burtscher, form Texas State University and Dr. Farzad Khorasani and Dr. Vivek Sarkar from Georgia Institute of Technology for their effective collaboration during my research work.

I gratefully acknowledge the support of NVIDIA Corporation with the donation of two high performance GPUs used for this research.

I extend my appreciation to NSERC Strategic Grant and Concordia University for the support of my research.

I am greatly thankful to my precious colleagues and friends, Upama, Shayan, Shyam, Mahsa, Nazanin and Myriam for their friendship and continuous support specially when things would get a bit discouraging.

This dissertation would not have been possible without constant support, understanding, patience, love and encouragement of my husband Navid. I would like to express my deepest appreciation to my amazing family, my mother, Zahra, my Father, Ramin and my lovely sister, Mahsa for their unconditional love and support throughout my life. They have been always my brightest stars in the darkest nights.

Last but not the least, I would like to thank my friends Shagha, Ali, Farnaz, Sya, Shadi and Farnoush who have been always there for me and supported me in the tough moments of this journey.

# Contents

| List of | Figure | es                                                | x    |

|---------|--------|---------------------------------------------------|------|

| List of | Tables | 3                                                 | xiii |

| Chapter | 1 Int  | roduction                                         | 1    |

| 1.1     | Overvi | ew and Objectives                                 | 1    |

| 1.2     | Proble | m Statement                                       | 6    |

| 1.3     | Contri | bution                                            | 10   |

| 1.4     | Thesis | Outline                                           | 13   |

| Chapter | 2 Lit  | erature Review                                    | 14   |

| 2.1     | The C  | PU-GPU System Architecture                        | 15   |

| 2.2     | CUDA   | Programming Model                                 | 16   |

| 2.3     | GPU I  | Performance Constraints                           | 18   |

|         | 2.3.1  | Thread Divergence                                 | 18   |

|         | 2.3.2  | Un-coalesced Memory Access                        | 18   |

|         | 2.3.3  | Limited Memory Size                               | 20   |

|         | 2.3.4  | Low-Level Programming Models                      | 20   |

|         | 2.3.5  | Synchronization Latency                           | 20   |

| 2.4     | Schedu | lling Heuristics on Heterogeneous CPU-GPU Systems | 21   |

|         | 2.4.1  | Static Heuristics                                 | 22   |

|         | 2.4.2  | Dynamic Heuristics                                | 25   |

|         | 2.4.3  | Scheduling Frameworks                             | 27   |

| 2.5             | Graph      | Partitioning                                                  | 28     |

|-----------------|------------|---------------------------------------------------------------|--------|

|                 | 2.5.1      | Serial Multilevel Graph partitioning                          | 29     |

|                 | 2.5.2      | Parallel Multilevel Graph Partitioning on Distributed Systems | 33     |

|                 | 2.5.3      | Parallel Multilevel Graph Partitioning on Shared-Memory Sys-  |        |

|                 |            | tems                                                          | 35     |

|                 | 2.5.4      | Matching Algorithms on GPU                                    | 36     |

| 2.6             | Optin      | nization Techniques on GPU                                    | 38     |

|                 | 2.6.1      | Scan                                                          | 38     |

|                 | 2.6.2      | Reduction                                                     | 40     |

|                 | 2.6.3      | Atomics                                                       | 41     |

| Chapter         | 3 A I      | Oynamic Scheduling Heuristic for Embarrassingly Parallel      | Appli- |

| $\mathbf{cati}$ | ions on    | Heterogeneous CPU-GPU Systems                                 | 42     |

| 3.1             | Motiva     | ation                                                         | 43     |

| 3.2             | Schedu     | ıler Architectural Model                                      | 44     |

|                 | 3.2.1      | Partitioner                                                   | 45     |

|                 | 3.2.2      | Load Bundler                                                  | 46     |

| 3.3             | HASS       | : A Dynamic Scheduling Algorithm                              | 48     |

|                 | 3.3.1      | Initialization Phase                                          | 51     |

|                 | 3.3.2      | Execution Phase                                               | 52     |

|                 | 3.3.3      | Adaptation Phase                                              | 53     |

| 3.4             | Experi     | mental Evaluation                                             | 54     |

| 3.5             | Conclu     | nsion                                                         | 58     |

| Chapter         | <b>4</b> A | Parallel Multilevel Graph Partitioner on the CPU-GPU          | Archi- |

| tect            | ture       |                                                               | 59     |

| 4.1             | Motiva     | ation                                                         | 60     |

| 4.2             | Design     | Challenges                                                    | 62     |

| 4.3             | A Mul      | tilevel Graph Partitioner for CPU-GPU Architectures           | 63     |

|                 | 4.3.1      | Data Structures for Graph Representation                      | 65     |

|         | 4.3.2   | Coarsening.                                          | 66  |

|---------|---------|------------------------------------------------------|-----|

|         | 4.3.3   | Initial Partitioning                                 | 75  |

|         | 4.3.4   | Un-coarsening                                        | 76  |

| 4.4     | Comp    | parison with mt-metis                                | 79  |

| 4.5     | Exper   | imental Evaluation                                   | 80  |

| 4.6     | Concl   | usion                                                | 84  |

| Chanta  | . E . A | High Donformon on Multilevel CDU based Crowb Dentiti |     |

| Chapter |         | High Performance Multilevel GPU-based Graph Partitio |     |

| 5.1     |         | ation                                                | 87  |

| 5.2     | Multi   | level GPU-based Graph Partitioning                   | 88  |

|         | 5.2.1   | Matching                                             | 91  |

|         | 5.2.2   | Contraction                                          | 95  |

|         | 5.2.3   | Initial Partitioning                                 | 100 |

|         | 5.2.4   | Un-Coarsening                                        | 101 |

|         | 5.2.5   | Additional Optimization: Custom Memory Allocator     | 104 |

| 5.3     | Exper   | imental Evaluation                                   | 105 |

|         | 5.3.1   | Performance Comparison                               | 106 |

|         | 5.3.2   | Performance Analysis                                 | 109 |

|         | 5.3.3   | Sensitivity Analysis                                 | 110 |

| 5.4     | Exten   | ding the Coarsening Techniques to MST                | 111 |

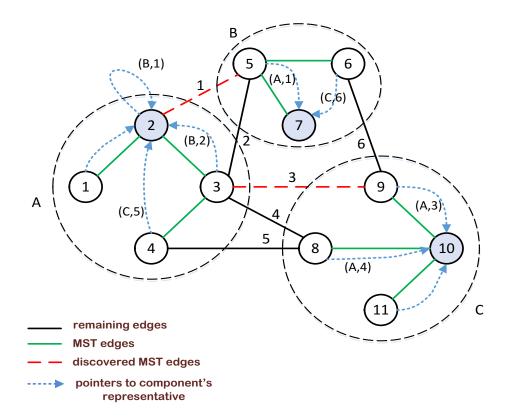

|         | 5.4.1   | Efficient Edge Discovery                             | 112 |

|         | 5.4.2   | Experimental Evaluation                              | 115 |

| 5.5     | Concl   | usion                                                | 117 |

| Chapter |         | onclusion and Future Work                            | 118 |

| 1       |         |                                                      |     |

| 6.1     | Futur   | e Directions                                         | 121 |

| Bibliog | graphy  |                                                      | 123 |

# List of Figures

| 1.1  | A single-CPU multi-GPU system                                             | 3  |

|------|---------------------------------------------------------------------------|----|

| 2.1  | Heterogeneous CPU-GPU architecture.                                       | 15 |

| 2.2  | CUDA thread hierarchy.                                                    | 17 |

| 2.3  | Two memory access patterns for a set of GPU threads                       | 19 |

| 2.4  | Matrix multiplication experiment in a CPU-GPU system. Matrix size         |    |

|      | is 6000. The notation "X/Y" on the x-axis means X% of work mapped         |    |

|      | to the GPU and Y% of work mapped to the CPU [62]                          | 22 |

| 2.5  | Training and partitioning phases of Qilin method [62]                     | 23 |

| 2.6  | Task queue scheme for scheduling on GPU [56]                              | 26 |

| 2.7  | An overview of multilevel graph partitioning                              | 30 |

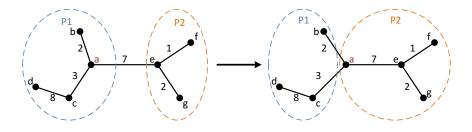

| 2.8  | Positive gain for vertex $a$ and transferring from $P_1$ to $P_2$         | 32 |

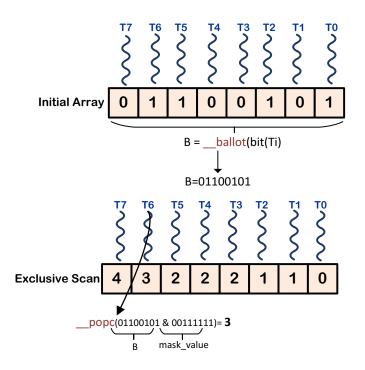

| 2.9  | Intra-warp binary exclusive scan. Warp size is assumed 8                  | 39 |

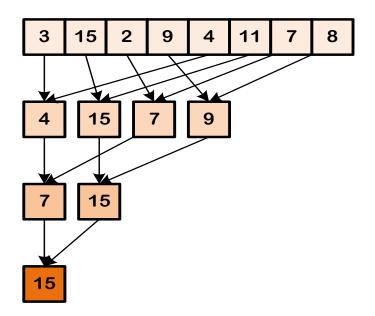

| 2.10 | Intra-warp reduction on the maximum value. Warp size is assumed 8.        | 40 |

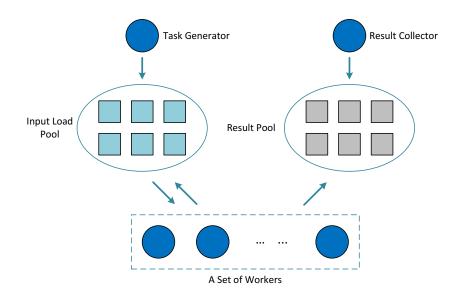

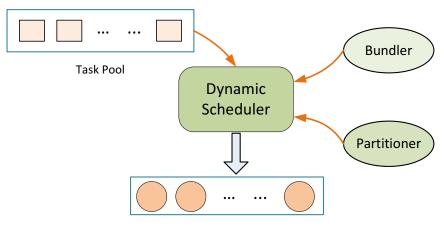

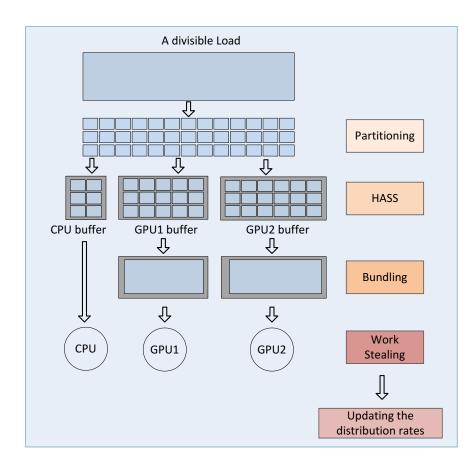

| 3.1  | Dynamic scheduling architecture for embarrassingly parallel applications. | 45 |

| 3.2  | Our designed dynamic scheduler architecture.                              | 46 |

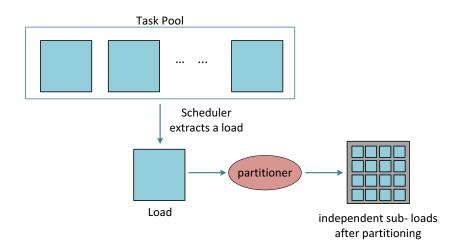

| 3.3  | Our partitioner function                                                  | 47 |

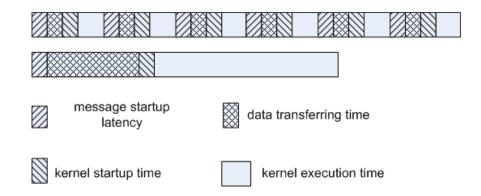

| 3.4  | Schematic showing the reduction of processing time due to load bundling.  | 48 |

| 3.5  | Scheduler flowchart over one round                                        | 53 |

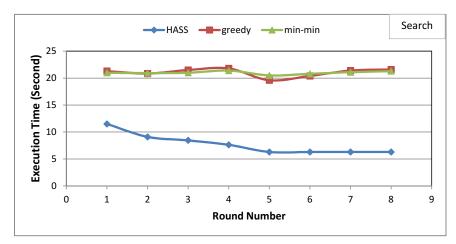

| 3.6  | Execution time comparison in a single-CPU multi-GPU system. $\ . \ .$     | 55 |

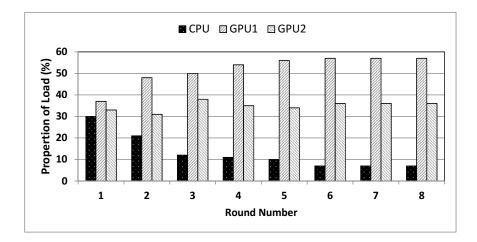

| 3.7  | The distribution of loads over the three processors in Matrix Multipli-   |    |

|      | cation when using $HASS$                                                  | 56 |

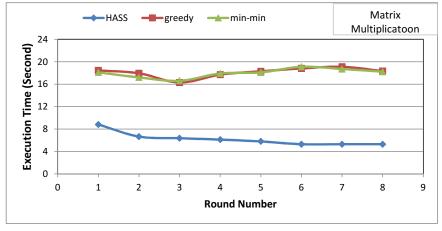

| 3.8  | Matrix Multiplication execution time comparison of $HASS$ with the       |     |

|------|--------------------------------------------------------------------------|-----|

|      | three other scheduling algorithms in a single-CPU single-GPU system.     | 56  |

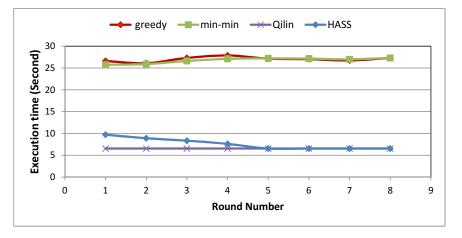

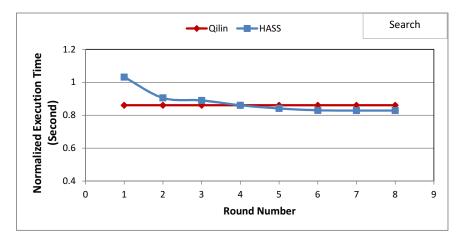

| 3.9  | Execution time comparison of $HASS$ and Qilin with the training size     |     |

|      | less than $30\%$ of the real problem size                                | 57  |

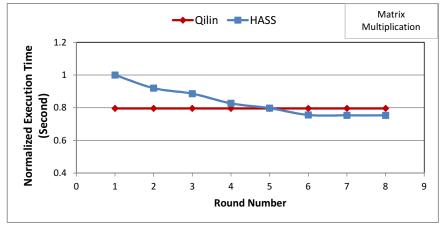

| 4.1  | Proposed heterogeneous graph partitioning scheme                         | 64  |

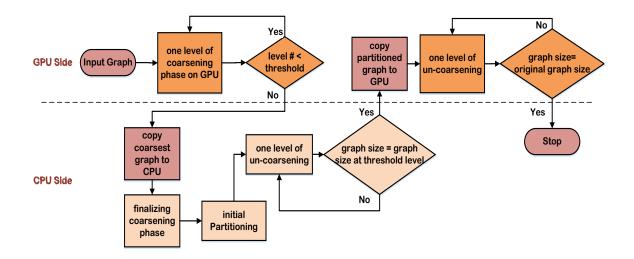

| 4.2  | Graph data structures used in our design shown for an example. CSR       |     |

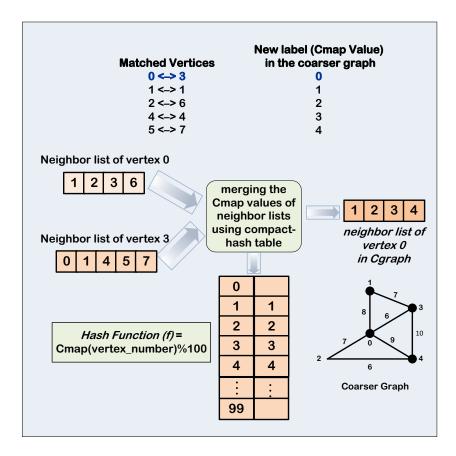

|      | format of the graph is accompanied with $M$ and $Cmap$ auxiliary arrays. |     |

|      | These arrays are constructed for every intermediate partitioning level.  | 66  |

| 4.3  | Memory coalescing                                                        | 67  |

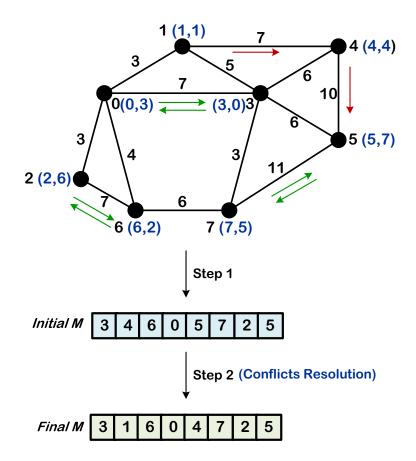

| 4.4  | Matching array creation.                                                 | 68  |

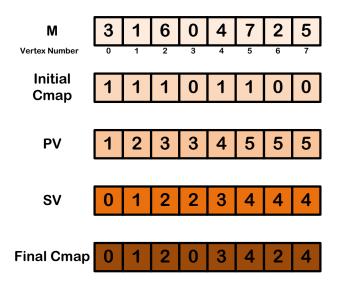

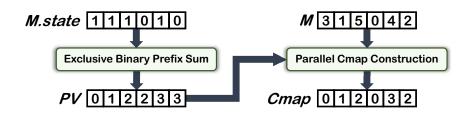

| 4.5  | Cmap creation steps.                                                     | 70  |

| 4.6  | Contraction procedure                                                    | 76  |

| 4.7  | Edge cut increment by concurrent movement of boundary vertices           | 77  |

| 4.8  | Boundary vertex movement requests insertion procedure                    | 79  |

| 4.9  | Speedup of ParMetis, mt-metis, and CPU-GPU partitioner over Metis        |     |

|      | (Titan GPU)                                                              | 81  |

| 4.10 | Speedup of ParMetis, mt-metis, and CPU-GPU partitioner over Metis        |     |

|      | (K40 GPU)                                                                | 82  |

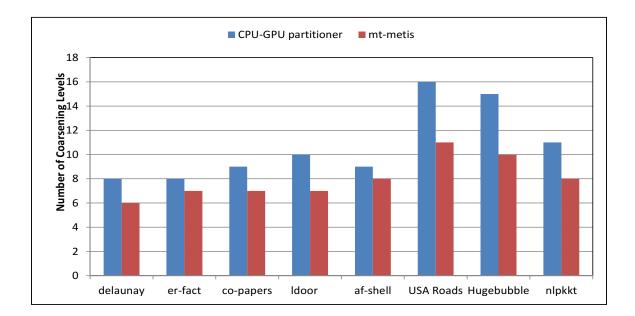

| 4.11 | Comparison of coarsening levels for mt-metis, and CPU-GPU partitioner.   | 84  |

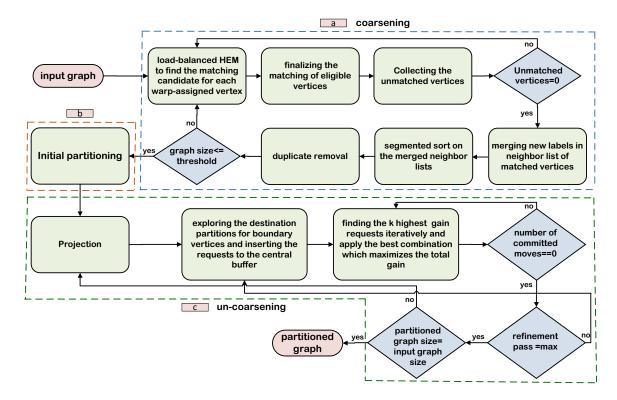

| 5.1  | GPU graph partitioning flowchart. Green-colored boxes represent GPU      |     |

|      | operations and blue-colored boxes specify the host actions               | 89  |

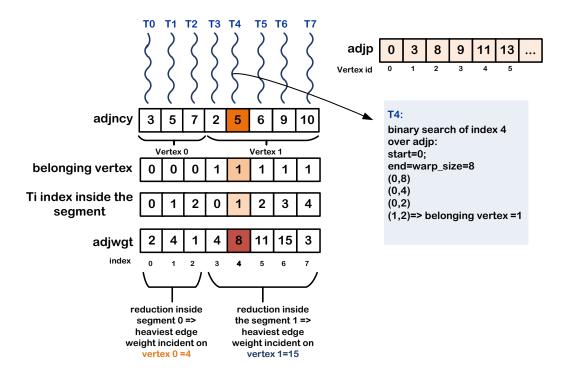

| 5.2  | Heavy edge matching process inside a warp. Warp size is assumed 8.       | 93  |

| 5.3  | Cmap construction procedure for the graph shown in Figure 4.2. Num-      |     |

|      | ber of vertices in the coarser graph is 4                                | 96  |

| 5.4  | Visualizing contraction using the example graph in Figure 4.2            | 97  |

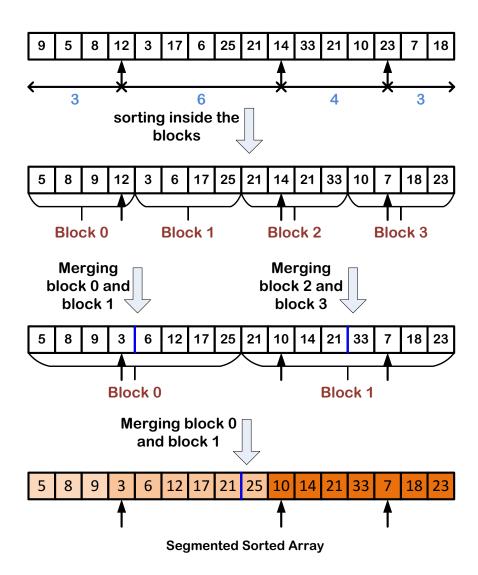

| 5.5  | Segmented sort on an array with four different sized segments            | 98  |

| 5.6  | Prefix sum code.                                                         | 100 |

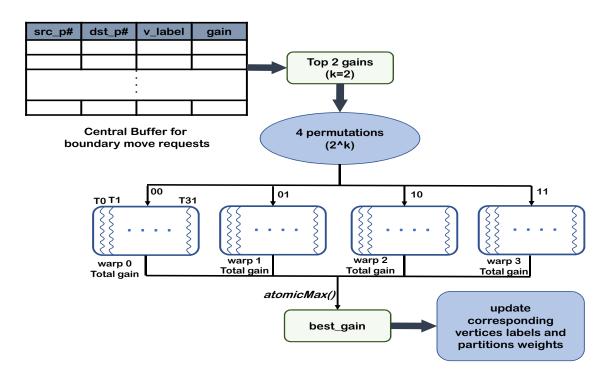

| 5.7  | Refinement procedure with assumed k value of 2                           | 102 |

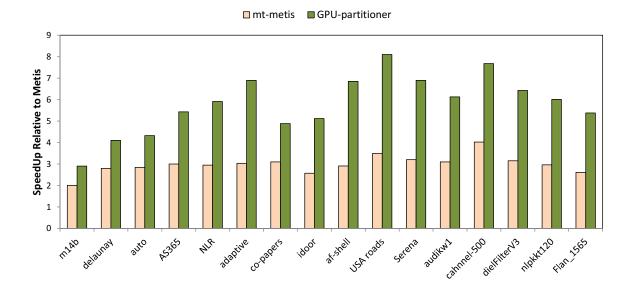

| 5.8  | Speedup of mt-metis and GPU-partitioner relative to Metis 1              | 107 |

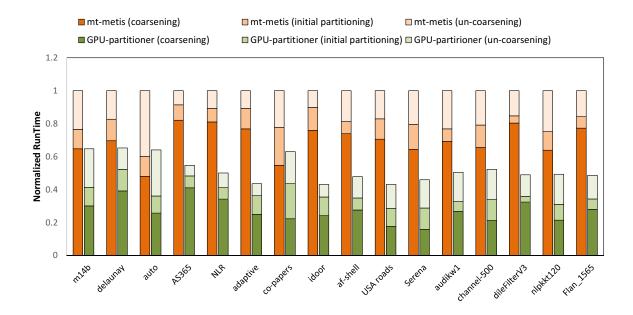

| 5.9  | Time distribution of 3 partitioning phases of mt-metis and GPU-partition         | er108 |

|------|----------------------------------------------------------------------------------|-------|

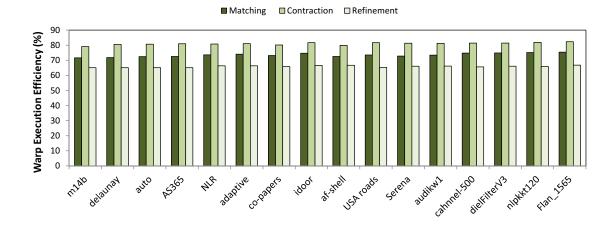

| 5.10 | Profiled average warp execution efficiency in different kernels                  | 109   |

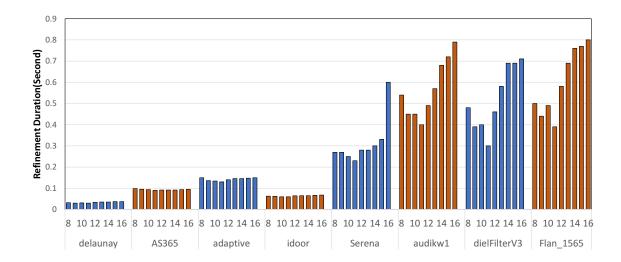

| 5.11 | Refinement phase duration changes relative to different values of $k$            |       |

|      | ranging from 8 to 16                                                             | 110   |

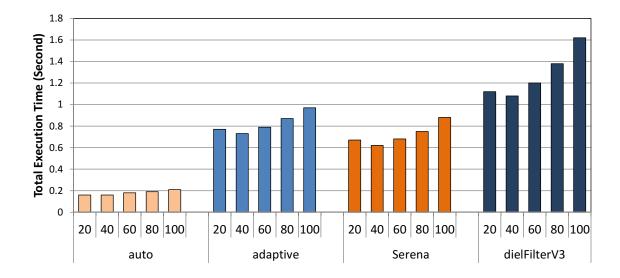

| 5.12 | Total graph partitioning execution time changes relative to increasing           |       |

|      | the coefficient in the denominator of $CoarsenTo$ formula from 20 to 100         | 111   |

| 5.13 | Edge discovery phase scheme.                                                     | 114   |

| 5.14 | Execution time comparison of STM-based GPU implementation of                     |       |

|      | $\operatorname{MST}$ and serial implementation over random/R-MAT graphs with 30M |       |

|      | edges and varying number of vertices                                             | 116   |

# List of Tables

| 4.1 | Input graphs used for the experiments                               | 80  |

|-----|---------------------------------------------------------------------|-----|

| 4.2 | ParMetis, mt-metis, and CPU-GPU partitioner runtimes (in seconds).  | 82  |

| 4.3 | ParMetis, mt-metis, and CPU-GPU partitioner Edge cut ratios in com- |     |

|     | parison to Metis.                                                   | 83  |

| 5.1 | Input graphs used for the experiments                               | 106 |

| 5.2 | Edge cut ratio in comparison to Metis                               | 108 |

| 5.3 | Input graphs used for the experiments                               | 115 |

| 5.4 | Speedup of STM-based GPU implementation of MST (using Tesla         |     |

|     | K40) relative to serial and multi-core STM-based implementations.   | 116 |

## Chapter 1

# Introduction

### 1.1 Overview and Objectives

Heterogeneous multi-core systems are gradually surpassing the homogeneous systems due to their high performance and flexibility. To respond to the high demands for more computational power, these parallel architectures have also been integrated with various heterogeneous technologies (e.g., powerXCell processors, DSPs or GPGPUs). Currently the top 500-leading IBM RoadRunner machines are composed of CPUs and accelerators [26].

The growing computational power of GPUs gives them significantly higher peak computing power compared to other accelerators and it makes them a compelling platform for computationally demanding tasks in a wide variety of application domains. The deployment of GPUs as general purpose accelerators, which started about a decade ago has now become mainstream. General-purpose graphics processing units (GPGPU) allow a host CPU to offload a wide variety of scientific computing applications, not just graphics, to a GPU. The high computing power provided by many-core processing units leverages this parallel architecture for non-graphic computations by achieving high speedup and providing other benefits, such as power efficiency and low cost. Modern GPU <sup>1</sup> processors are massively parallel, and are fully programmable.

<sup>&</sup>lt;sup>1</sup>In the rest of this thesis we use the term GPU instead of GPGPU

The parallel floating point computing power of a modern GPU is orders of magnitude higher than that of a CPU [67]. Thus, intelligently combining the best features of both has positioned the integrated multi-core CPU and the many-core GPUs as a meritorious alternative to traditional heterogeneous multi-core systems in high performance parallelization of applications.

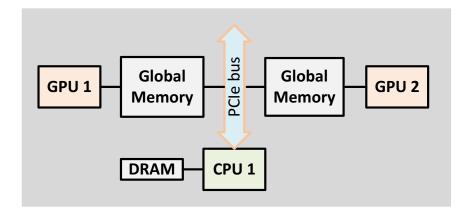

Figure 1.1 demonstrates the general structure of a heterogeneous CPU-GPU system with one CPU and two GPUs. As the figure shows, the CPU communicates with GPUs through the PCI-X buses. A GPU consists of a set of Streaming Multiprocessors (SM), each of which is comprised of a number of Streaming Processors (SPs). In CUDA programming model [1], which is the most common GPU programming model, the program on the GPU is executed by launching a set of threads across the SMs. Each set of 32 contiguous threads constitutes a warp. The GPU performs SIMD (Single instruction-multiple data) execution at the warp level and all the threads inside a warp execute the same instruction at any given time.

The GPU memory system provides on-chip and off-chip memories. The off-chip memory is generally referred to as the global memory of the GPU, and all the threads running across the SMs have the read/write access to this memory. However, in terms of access latency this memory is slow. The on-chip memory includes the shared memory and thread registers. The shared memory is located on each of the SMs and, consequently is as fast as accessing a register  $^2$ .

Due to different programming paradigms of the CPU (MIMD) and GPU (SIMD), optimizing the execution of different applications in terms of performance and efficiency requires considering the characteristics of both architectures for making workload distribution decisions. The difference in the applications characteristics and the proper modification of the existing parallel algorithm also need to be taken into account to fulfill the potential performance of heterogeneous platforms with single or multiple GPUs.

A large group of parallel applications fall into embarrassingly parallel category [21,

$<sup>^2\</sup>mathrm{We}$  discuss the details of the CPU-GPU systems in  $\,$  Chapter 2  $\,$

Figure 1.1: A single-CPU multi-GPU system.

66, 83] where tasks have no inter-dependencies and their operations and memory access patterns are regular. Simultaneous executing of these applications workloads on the CPU and the GPUs can result in substantial performance due to the massive computation capability of GPU in the execution of the independent parallel tasks. The minimized execution time, however, can only be obtained if we optimally distribute the tasks over the processors and avoid the idle time for all the processing units.

Several studies [45, 62, 71] showed that the appropriate load distribution over the CPU and GPU raises the efficient computation resources utilization and, consequently, archives better performance in comparison to executing the loads on either the CPU or the GPU. Nonetheless, the traditional GPU scheduler cannot automatize the distribution of workload over the CPU and GPU devices, and the programmer should manually schedule the tasks over the available devices. Furthermore, determining the best distribution rates to ensure that the makespan is minimized is a challenging problem.

The scheduling methods proposed for heterogeneous clusters [8, 13, 63, 87, 98] or multi-core environments [18, 97] are not applicable to CPU-GPU systems in a straightforward way. Unlike the traditional heterogeneous systems, where the hetero-geneity comes from difference in the speed or network bandwidths of the processors, in heterogeneous CPU-GPU system, the architecture and programming model of the

processors are different. Other challenges include the transfer latency between the CPU and the GPU, GPU memory limitations and the high programming effort to distribute the workloads manually.

There are several proposed static and dynamic scheduling algorithms on CPU-GPU systems. However, these suffer either from performance or scalability limitations. The static methods [33, 62, 94] are applicable only to a system integrated with a single GPU and have a heavy and inaccurate training phase for large loads. The dynamic techniques [44, 89] underutilize the GPU processing cores, and some of them are not scalable to more than one integrated GPU [84]. The other groups require many scheduling hints from the user, and the scheduler cannot schedule the loads over the processing devices independently and adaptively [82]. As a result, designing a high performance adaptive and scalable scheduling method for embarrassingly parallel applications which minimizes the user interference as well is non-trivial.

Task dependent applications, another category of parallel applications, have data dependency limitations and irregular memory access patterns. In this category, the computation is naturally expressible in the form of a static task interaction graph with tasks of known size [55]. Each graph vertex shows a task and each edge represents a data interaction link between two incident tasks.

Scheduling the task interaction graph on a homogeneous or heterogeneous cluster can be done by partitioning the graph. Simply stated, a graph partitioner is an integrated module of the scheduler. First, the graph needs to be divided into a set of computationally balanced partitions in such a way that communication cost among the partitions is minimized. Subsequently, the partitions are scheduled to the target platform. Designing a high performance graph partitioner on the heterogeneous CPU-GPU platform is compelling since the unique features of the heterogeneous CPU-GPU system can speed up the scheduling process indirectly by performing a fast graph partitioning. Furthermore the graph partitioning, which goes beyond the scheduling domain, has extensive applications in various areas of computing such as data mining, geographical information systems, social networks and VLSI design. Graph partitioning is a subcategory of the clustering problem with two specific objectives. The first is to balance the weights of the partitions, and the second is to minimize the communication cost among the partitions. Multilevel graph partitioning approach [14, 15, 39] is one of the most successful heuristics proposed for efficient graph partitioning. The idea is to first reduce the graph size by matching and collapsing the vertices in multiple coarsening levels until the number of vertices is below a threshold; then, the coarsened graph is partitioned; finally, the partitioning is projected back through the multiple levels onto the original graph. Although many sub-tasks of multilevel graph partitioning are serial in nature, several parallel implementation version of it have been proposed for distributed and multi-core systems. The quality of the partitions produced by parallel algorithms is lower than that produced by serial algorithms. Nonetheless, the parallel schemes deliver significant speedups compared to the serial version.

Designing a graph partitioner on a heterogeneous CPU-GPU systems is a doubleedged sword. On one hand, the high processing power of GPU cores in collaboration with a CPU can achieve higher performance compared to distributed and multi-core graph partitioners. On the other hand, unlike data-parallel applications, irregular, non-uniform, and data-dependent graph partitioning sub-tasks pose multiple challenges for efficient GPU utilization. These challenges include thread divergence, load imbalance, non-coalesced memory accesses, warp execution inefficiency, and limitedsize GPU memory. Consequently the existing graph partitioning parallel algorithms need to be modified for an efficient implementation.

In this thesis, we address the above challenges in the heterogeneous CPU-GPU systems. First, we develop an adaptive and automated scheduler for embarrassingly parallel applications aimed at minimizing the makespan. Then, we design and implement high performance graph partitioning methods for task dependent applications. Finally, we extend some of our developed techniques for parallelizing the other graph processing algorithms on a CPU-GPU platform.

### **1.2** Problem Statement

Modern heterogeneous systems have evolved from the traditional heterogeneous systems with CPUs of different speeds to the new generation systems equipped with accelerators. The massively data parallel computation and power efficiency of GPUs have led to the collaboration between CPUs and GPUs in achieving the high-performance parallelization of the applications. However, it is important to be mindful of the differences between the architecture and programming models of CPU (MIMD) and GPU (SIMD) in order to fully exploit the processing power of these heterogeneous platforms.Effectively parallelizing application on theses platforms may also require heavy modifications to the existing parallel algorithms.

A wide range of applications fall into embarrassingly parallel category [66] in which tasks are completely independent. In these applications, the problem is decomposed into many identical but independent tasks that can cooperatively produce the desired results in a parallel fashion. Although the high processing power of GPUs makes the CPU-GPU systems excellent candidates for parallelizing the embarrassingly parallel applications, an ideal execution time can only be achieved if the application tasks are optimally distributed over the CPU and GPUs to minimize the underutilization of the processing cores. This is challenging since determining the proper portion of workload for each device is an NP-complete [43] scheduling problem.

Another problem related to scheduling of embarrassingly parallel applications in a CPU-GPU environment is the programming effort required to distribute loads over the CPU and GPU cores. The traditional GPU scheduler cannot automatize the distribution of load over the CPU and GPUs, so the programmer must manually partition the workload. This process is tedious and does not scale well beyond solving small problems. Hence, fully automatic techniques are required to take advantage of processing strength of heterogeneous computing. While uniform programming environments like OpenCL have emerged, these do not give a programmer full control over optimal task scheduling. OpenCL offers transparency to the programmer by hiding most of the underlying architectural differences, but this advantage comes at the cost of performance since the programmer does not have explicit control over scheduling decisions.

Meanwhile, several static scheduling algorithms have been proposed to execute embarrassingly parallel applications on CPU-GPU systems [33, 59, 94]. However, they have significant overheads due to their extensive profiling phases and are not accurate due to non-linear and black-box nature of GPU performance characteristics. Some researchers have proposed dynamic scheduling heuristics [44, 82, 84, 89] for CPU-GPU environments. A few of them have considered executing multiple applications on a CPU-GPU system and dynamically assigning each application to one of the processors without any load partitioning between the CPU and GPU [44, 89]. Some other works present solutions that are not scalable to more than one integrated GPU [84]. In [24], the authors proposed a general framework, which does not consider the distribution of tasks and schedules the entire kernel, for scheduling applications on a heterogeneous CPU-GPU system. StarPU [4] is a framework that requires some hints from the user for scheduling purposes.

In summary, majority of proposed scheduling heuristics cannot take full advantage of the computational powers of the devices in heterogeneous CPU-GPU architectures. Most of the contemporary schedulers, in fact, are application-dependent and require the user's interference for scheduling decisions and low-level programming skills for scheduling implementation. As a result, designing a high performance adaptive and scalable heuristic for embarrassingly parallel applications while hiding the scheduling complexities is essential.

A large domain of applications are non-embarrassingly parallel which includes task dependent problems with data dependency. For these applications, the computational tasks and their communication patterns can be represented by a weighted undirected graph in which the vertices represent the tasks and the edges represent the communication costs of the tasks. Many large-scale and complex real-world problems, such as social network interactions, can be expressed as task interaction graphs. Scheduling of a task interaction graph on a heterogeneous or homogeneous cluster of processors can be done based on a primary partitioning of the graph. In other words, the graph partitioner is an integral part of the scheduler; it divides the graph into a set of equal weigh partitions in such a way that the communication cost (known as edge cut) among the partitions is minimized. Subsequently, the partitions are scheduled over the available processors. Using an efficient graph partitioner for the parallel implementation of these applications is non-trivial

Besides scheduling, graph partitioning has extensive application in many computing areas, including geographical information systems, VLSI design and data mining. Graph partitioning is also a key preprocessing step in many high performance parallel graph algorithms like Page-Rank and Breadth-First Search.

The graph partitioning problem is NP-complete. Consequently, many heuristic algorithms have been proposed [47, 70, 80]. Multilevel graph partitioning techniques [15, 39, 47, 77, 91] are generally preferred over other techniques such as spectral partitioning [80] due to higher quality of partitions at a faster computation time. Handrickson and Leland [39] validated this claim using extensive experiments. In the multilevel graph partitioning, first the graph size is reduced by matching and collapsing the vertices in multiple coarsening levels until the number of vertices is less than a certain threshold; then the coarsened graph is partitioned, and finally the partitioning is projected back iteratively onto the original graph during the un-coarsening phase <sup>3</sup>.

The widespread applications of graph partitioning in different areas of computing have encouraged its parallel implementation on multi-core architectures [57, 88] as well on distributed systems [19, 40, 48, 49, 92]. Although serial graph partitioning and its parallel implementations on distributed and multi-core systems have been well studied, designing a graph partitioner on heterogeneous CPU-GPU systems has yet to be investigated. As a throughput-oriented device, GPU hides the memory access latency through high degrees of multi-threading. This indicates an excellent opportunity to accelerate the graph partitioning task on a heterogeneous CPU-GPU

$<sup>^{3}</sup>$ A detailed diagram of multilevel graph partitioning is shown in Chapter 2

system.

In addition, some GPU applications require graph partitioning to balance the workload among the threads and to increase the parallelism. A high performance GPU-based graph partitioner reduces host-device high data transfer costs. For example, Delaunay mesh refinement (DMR) [74] application requires graph partitioning to minimize the conflicts among the cavities processed by the GPU threads and to increase parallelism. Using a contemporary partitioning algorithm would oblige the entire graph to be transferred to the CPU, partitioned there, and moved back to the GPU. Designing a high-performance GPU graph partitioner can resolve this problem while maintaining good performance in comparison with CPU-based partitioners.

GPU allows thousands of threads to be resident on its Streaming Multiprocessors. The SIMD GPU programming paradigm demands repetitive processing patterns on regular data which is contrary to the irregular nature of real-world graphs. Therefore, an acceptable implementation of CPU-GPU graph partitioning must utilize the collective computation force of threads. This prominent difference makes proposed approaches on distributed and multi-core systems not applicable on CPU-GPU partitioner in a straightforward way. Furthermore, when processing an irregular application like graph partitioning, designing an efficient parallelization strategy becomes challenging. Particularly when dealing with large and irregular real-world graphs, non-uniform and data-dependent graph partitioning sub-tasks result in imbalanced load distribution among threads, consequently deteriorate the performance of the graph-partitioning kernels executed on the GPU.

Some of the challenges we have to overcome in our design include the following: (1) proper redesigning of the existing parallel algorithms to maximize the graph partitioner efficiency on a CPU-GPU architecture; (2) GPU memory constraints to hold large graphs; (3) the irregular nature of the graph data structure, which can result in thread divergence and poor locality in memory accesses, deteriorating the performance of the graph-partitioning code running on the GPU; (4) synchronization costs, which are much more pronounced on GPUs running tens of thousands of threads as compared to multi-core CPUs that only run tens of threads; (5) a suitable workload distribution strategy between the CPU and the GPU; and (6) data transfer latency between the CPU and the GPU.

In summary, efficient parallelization of the multilevel graph partitioning in a heterogeneous CPU-GPU system is a challenging task. On the one hand, the highly serial and data-dependent nature of coarsening and un-coarsening phases makes it difficult to exploit the data parallelism within each phase. On the other hand, straightforward porting of existing parallelization heuristics results in inefficient GPU programs, or if the heuristic sacrifices accuracy at the expense of parallelism, it can result in poor partition qualities. These problems determine the need for a multilevel graph partiioner in a CPU-GPU platform that accelerates this task by being tailored specifically for the SIMD architecture, and at the same time, prov

iding reasonable partition qualities compared to serial and multi-core solutions.

### **1.3** Contribution

In this thesis we explore the followings: 1- design and implementation of an adaptive and automated scheduling technique for embarrassingly parallel applications on a heterogeneous CPU-GPU system; (2) design and implementation of efficient parallel multilevel graph partitioning methods for task dependent applications on heterogeneous systems; and (3) investigate the application of some of our partitioning techniques to other graph processing algorithms.

The main contribution of the thesis are as follows:

• We explore the scheduling problem for embarrassingly parallel applications on a heterogeneous environment by designing and implementing a new dynamic scheduling heuristic for embarrassingly parallel applications, where tasks have no inter-dependencies. The goal is to distribute the load among the processors adaptively so that the application makespan is minimized. Meanwhile, the scheduler aims to take advantage of full processing powers of the GPUs' processing cores and to minimize user interference into the scheduling criteria. Our proposed dynamic scheduler is scalable to any number of GPUs integrated in the heterogeneous CPU-GPU system. We employ runtime techniques like profiling and work stealing to address the efficient load distribution between the CPU and GPUs. The scheduler is integrated into a scheduling framework that provides pre-implemented automated scheduling modules. The user is liberated from the complexities of scheduling details and from manually distributing the workload over the CPU and GPU cores. The experimental results show that our scheduling approach achieves better to similar performances compared to some of the well-known scheduling algorithms for the CPU-GPU systems.

• We design and implement multilevel graph partitioner on a heterogeneous CPU-GPU system that takes advantage of the high parallel processing power of GPUs by executing the computation-intensive parts of the partitioning sub-tasks on the GPU and assigning the parts with less parallelism to the CPU. The partitioner aims to overcome some of the challenges arising due to the irregular nature of the partitioning algorithm, load imbalance, and memory constraints on GPUs. Our design also minimizes the lock usage and does not degrade performance through fine-grained synchronization among the threads. To mitigate the global memory size limitation, we use Compressed Sparse Row (CSR) representation, which is an efficient compact format for representing large and sparse graphs inside the limited GPU memory. Our partitioner handles the aforementioned challenges through redesigning of the existing parallel multilev partitioning algorithms, considering the heterogeneity of the architecture, and exploits special characteristics of GPUs. To the best of our knowledge, this is the first proposed multilevel graph partitioner designed for and implemented on a heterogeneous CPU-GPU system. Our CPU-GPU graph partitioner outperforms the serial and distributed multilevel graph partitioners and performs similar to mt-metis, the state-of-the-art CPU-based parallel graph partitioner.

• Next we identify the performance bottlenecks of our developed CPU-GPU graph partitioner to optimize our design accordingly so that it outperforms the CPUbased partitioner as well. We discover that our first solution is prone to load imbalance in some of the partitioning phases. The reason for this problem is that in the coarsening and un-coarsening phases of partitioning, the graph vertices are distributed among the GPU threads, and each thread serially processes the neighbor lists of its assigned vertices. Consequently, the irregular sized neighbor lists of the graph vertices results in thread divergence and in non-coalesced accesses to edge and vertex indices. To resolve this problem, instead of assigning a GPU thread to process the neighbor list of a vertex, we exploit the lock-step processing power of warps, and the warp threads process the neighbor list of a vertex in parallel. This prevents the thread divergence and underutilization of SIMD resources while balancing the load over the GPU threads.

Furthermore, during transferring the less computational sections of the partitioning sub-tasks to the CPU, comparatively low communication bandwidth between the CPU and GPU creates performance overhead. Therefore, we design and implement a high performance multilevel partitioner that performs all the phases of partitioning on the GPU with minimal CPU interventions. We develop new coarsening and un-coarsening parallel algorithms to speedup our partitioner. Despite the irregular inter-dependency of graph partitioning subtasks, our approach balances load over the SIMD threads and prevents thread divergence.

We also mitigate recurrent GPU memory allocation overhead and optimize our design by deploying a custom regional memory allocation technique, which reduces the cost for allocating data on GPU and increases the partitioning efficiency. This partitioner is autonomous as all the steps are carried out by the GPU with minimal CPU interference. Extensive experiments on our newly designed GPU-based partitioner over a set of graphs from various computing areas demonstrate better performance in terms of partitioning speed while delivering a reasonable partition quality in comparison to multi-core graph partitioners.

• Finally we apply some of the techniques we developed specifically in the coarsening phase of our graph partitioner to another graph processing application that exhibits such characteristics as thread divergence and imbalance load distribution. Minimum Spanning Tree (MST) is a well-known graph processing algorithm that creates a subset of the edges of a connected, edge-weighted undirected graph that connects all the vertices without any cycle. One of the well-known proposed MST algorithms is that of Borůvka [12], which is known to be suitable for parallelization. This algorithm finds the minimum weighted outgoing edge at each vertex and merges the connected vertices into supervertices. Since Borouvka's algorithm provides natural parallelism, many parallel MST algorithms are based on this approach. In the first phase of parallel Borůvka's algorithm, all the vertices find the minimum-weight crossing edge among their neighbors on the other components. This phase has a similar function to the matching process in the coarsening phase of our designed graph partitioner. Extending our developed techniques to the first phase of Boruvka's algorithm helps in achieving a high-performance implementation of MST algorithm on the GPU.

#### 1.4 Thesis Outline

The rest of this thesis is organized as follows. Chapter 2 discusses the background and related work. Chapter 3 presents the design and implementation of a dynamic and automated scheduler for embarrassingly parallel applications on CPU-GPUs systems. Chapter 4 describes our solutions for enabling multilevel graph partitioning on a heterogeneous CPU-GPU system. Chapter 5 proposes our high performance multilevel GPU-based graph partitioner and discusses the extension of our techniques to parallel MST implementation on a GPU. Chapter 6 concludes the thesis by summarizing our work and provides a discussion on potential future research.

# Chapter 2

# Literature Review

Heterogeneous CPU-GPU platforms benefit from using the combined potential of both CPU and GPU computing power and features. GPUs have evolved significantly in the past decade. The new generation of GPUs has thousands of cores and multiple gigabytes of global memory. Modern GPU processors are massively parallel and are fully programmable [76]. The emergence of these heterogeneous CPU-GPU systems and the rapid programmability and capability of GPUs present a unique opportunity for speeding up parallel computations. However, deep understanding of the underlying architecture restrictions and performance challenges of the GPU is crucial to adapting the parallelization algorithms accordingly.

In this chapter, we first give a brief background of the heterogeneous CPU-GPU system architecture and CUDA programming model. Then, we provide an overview of GPU performance challenges and constraints on high-performance parallel execution of applications. Subsequently, we review some of the proposed static and dynamic scheduling heuristics for heterogeneous CPU-GPU environments. Afterward, we discuss the multilevel graph partitioning problem and cite contemporary and relevant research on serial and parallel graph-partitioning algorithms. Finally we elaborate on several parallel optimization techniques proposed for the GPUs.

Figure 2.1: Heterogeneous CPU-GPU architecture.

### 2.1 The CPU-GPU System Architecture

Figure 2.1 illustrates the general configuration of a single CPU-multiple GPU architecture consisting of two GPUs. CPU is the dominant processor (called the host) and the GPUs are the subordinate processors (called the devices) under the control of the CPU. CPU communicates with the GPUs through the PCI-X buses. A GPU consists of a scalable number of Streaming Multiprocessors (SMs), each of which comprises a number of Streaming Processors (SPs), which are also called GPU cores.

The GPU memory system provides both on-chip and off-chip memories. The offchip memory is generally referred as the Global Memory of the GPU, and all the threads running across the SMs have read/write access to this memory. However, in terms of access latency, this memory is slow [17]. The on-chip memory includes the shared memory and thread registers. Shared memory is located on each of the SMs and consequently is almost as fast as accessing a register. However, shared memory size is limited to less than 100 KB per SM.

### 2.2 CUDA Programming Model

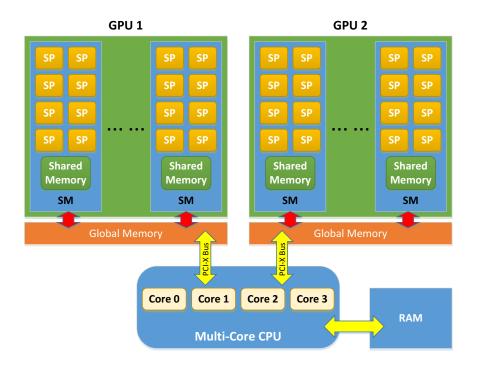

The development of GPU programming models and tools has been as important as the advancement of the GPU as a general purpose processing unit. CUDA (Compute Unified Device Architecture) [1] is a common GPU programming model developed by Nvidia that provides a framework for developing parallel applications on a GPU and enables the parallel execution of thousands of threads on the GPU. Simply stated, CUDA is a software layer that gives direct access to the GPU parallel computation units. CUDA provides a set of extensions to existing languages such as C and C++ that supports useful primitives and functions to interface with the GPU. A CUDA program consists of two parts: one part is made up of the portions to be executed on the GPU, also known as the kernel; the other part is the program that is to be executed on the host.

CUDA supports a hierarchy of thread grouping for the execution of a program on the GPU. The highest level is called a grid, which encapsulates all of the threads executing an application. A grid consists of a set of thread blocks that execute a kernel function. The blocks are organized into a one-dimensional, two-dimensional, or three-dimensional grid of thread blocks. All threads within a block are executed concurrently on the GPU. Each thread within a block has a thread ID that is unique only among threads within the same block. Furthermore, each block has a block ID that identifies its position in the thread grid. These two IDs generate a unique thread ID for each thread at the grid level.

The threads within one block are grouped into a series of 32 threads that construct what is called a warp. The threads within a warp are executed in locksteps, i.e., all threads within a warp execute one common instruction at the same time. Threads within one block can share data using shared memory and can be synchronized at a barrier with very low latency. However, different blocks can communicate just through the global memory with much higher access latency. Figure 2.2 shows the CUDA thread hierarchy paradigm.

Figure 2.2: CUDA thread hierarchy.

To execute a CUDA program on a GPU the host process launches a set of kernels on GPU the selection of which depends on the application. For each kernel, the host process determines how many threads are required to execute the kernel and how many thread blocks (TB) these threads should be equally divided into. The required data for the execution should be transferred from the CPU to the GPU a priori to be able to run a kernel. This data is copied to the global memory of the GPU. The hardware schedules and distributes TBs to SMs with available execution capacity. One or multiple TBs can reside concurrently on one SM, given sufficient hardware resources such as register files and shared memory. Each thread is mapped to one SP core.

### 2.3 GPU Performance Constraints

Understanding the GPU architecture constraints and performance bottlenecks helps programmers exploit the full processing power of GPUs and enables the redesign of parallel algorithms accordingly to increase productivity. Below, we review some of the key performance constraints of the GPU architecture.

#### 2.3.1 Thread Divergence

Generally, a GPU performs a SIMD (single instruction-multiple data) execution at the warp level and all the threads run in lockstep. If threads within a warp diverge, the entire warp will execute both code paths until all the threads re-converge. Simply stated, thread divergence can happen if threads of the warp take different execution paths, which results in the execution being serialized. For instance the presence of conditional statements such as if-else blocks causes thread divergence because a conditional statement may evaluate to true for some warp lanes and false for the other lanes.

Thread divergence can degrade the performance significantly, and this is a critical issue in exploiting the processing power of a GPU, especially in applications with irregular data accesses. Structuring the code to minimize divergence within warps for high-performance GPU computing is non-trivial.

#### 2.3.2 Un-coalesced Memory Access

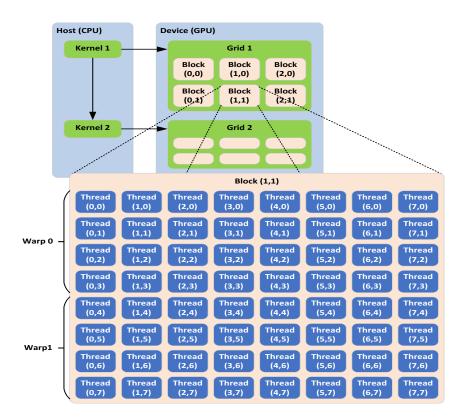

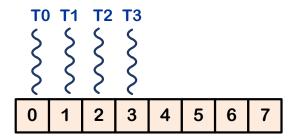

Leveraging the performance of GPU applications requires streaming memory access patterns in which threads read from and write to large consecutive blocks located in separate regions of memory. A coalesced memory access is the combination of multiple memory accesses into a single transaction. In modern CUDA-capable GPUs, sets of 32 contiguous threads constitute a warp. When all threads in a warp execute a memory instruction, the hardware checks which memory locations the threads access.

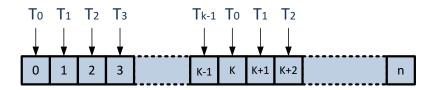

a) coalesced memory access (single memory transaction)

| Т0 |   |   | <b>T1</b> |   | Т2 |   | Т3 |

|----|---|---|-----------|---|----|---|----|

| S  |   |   | S         |   | S  |   | S  |

| 5  |   |   | 5         |   | S  |   | 5  |

| 2  |   |   | ξ         |   | 2  |   | 2  |

| 0  | 1 | 2 | 3         | 4 | 5  | 6 | 7  |

b) un-coalesced memory access (multiple memory transactions)

Figure 2.3: Two memory access patterns for a set of GPU threads.

Ideally, if all the memory accesses within a warp can be combined into a naturallyaligned 128-byte block in the global memory, the hardware coalesces the accesses into one transaction. Otherwise, the irregular access patterns penalize the memory performance with crossed relations between data and threads. In such a case, multiple memory transactions have to be issued, which reduces the efficiency and amortizes the throughput. Figure 2.3 shows two cases for the access pattern of a set of GPU threads.

Although regular memory access facilitates the coalescence of memory access on the GPU, coalescing will be challenging for irregular programs with the complex data structures such as graph and tree. Consequently, efficient parallelization of these programs on the GPU is more challenging and requires a mechanism to hide the latency associated with the non-coalesced memory accesses.

#### 2.3.3 Limited Memory Size

Present-day high-end GPUs offer up to 16 gigabytes of global memory. This relatively limited size of the GPU memory prevents application of the GPU to process big data problems. This obliges the programmer to optimize memory allocations on the GPU to be able to handle the large-sized real-world computations on the GPU and mitigate the GPU memory bottleneck. Heterogeneous systems with multiple-GPUs are also proposed as a solution to scale to even bigger datasets. Nonetheless, they introduce additional latency and synchronization challenges.

#### 2.3.4 Low-Level Programming Models

There is a trade-off between low-level access to the GPU, which accelerates the execution time, and high-level GPU programming languages, which enable productivity and flexibility for the users. Consequently, obtaining high performance on a GPU requires high programming effort to understand the low-level architecture of the GPU including the functionality of the processing cores, memory access patterns on shared and global memory, and the thread scheduling schemes.

Although researchers proposed several libraries for high-level programming approaches that make the data transfer between the CPU and the GPU more implicit [59, 76], most of the complex parallel applications achieve better performance through using lower-level programming models like CUDA, which are closer to hard-ware languages.

#### 2.3.5 Synchronization Latency

A GPU has a relatively limited global memory size of up to 16 gigabytes in the latest generation of GPUs. While CUDA provides a barrier function to synchronize threads within a thread block, it does not support any mechanism for communications across thread blocks. Consequently, device level synchronization is possible through the global memory with large access latency. In order to avoid data races in GPU applications that share data on the global memory, accesses from different thread blocks must be protected by locks. The huge number of GPU threads exacerbates the lock-based programming challenges.

Although locking is a contemporary practical mechanism for ensuring atomic accesses to shared data on the GPU, the improper usage of locks can degrade the performance. With the advent of atomic functions on GPUs, such as compare-and-swap (atomicCAS()), it is possible to perform non-blocking synchronization techniques among the threads. Recently, GPUs can resolve atomics within internal caches and spin-locks are now relatively fast. Nevertheless, due to the high large access latency of global memory, programmers consider avoiding synchronized access over the global memory or using the fast on-chip shared memory, which enables fast synchronization within the thread block.

# 2.4 Scheduling Heuristics on Heterogeneous CPU-GPU Systems

A large number of problems can be cast to the embarrassingly parallel applications, where the computation can be divided into a number of tasks with no interdependencies. Proper scheduling of these independent computational tasks on a given set of processors is a key factor for high performance computing. The scheduling methods proposed for heterogeneous clusters [8, 13, 63, 87, 98] or multi-core environments [18, 97] are not applicable to heterogeneous CPU-GPU systems in a straightforward way. The differences in the programming paradigm of the CPU and the GPU, requires designing efficient scheduling heuristics, to maximize the performance by optimally distributing the workload over the CPU and the GPU cores.

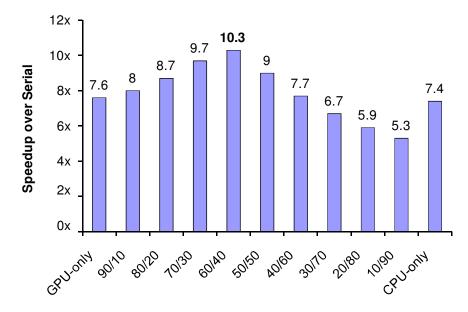

Although the SIMD programming paradigm of GPUs makes them excellent candidates for accelerating the embarrassingly parallel application, proper distribution of parallel tasks over both the CPU and the GPU, results in better performance in comparison to CPU-only or GPU-only execution. Figure 2.4 validate this claim by

Figure 2.4: Matrix multiplication experiment in a CPU-GPU system. Matrix size is 6000. The notation "X/Y" on the x-axis means X% of work mapped to the GPU and Y% of work mapped to the CPU [62].

measuring the parallelization speedups of the matrix multiplication application in a heterogeneous system consisted of an Intel multicore CPU and an Nvidia 8800 GTX GPU [62].

Since the scheduling problem for heterogeneous CPU-GPU system is an NPcomplete problem, several static and dynamic scheduling heuristics and frameworks are proposed in the literature [71]. We review some of these heuristics in the following.

#### 2.4.1 Static Heuristics

Min-min is a well-known static heuristic proposed for task scheduling on a general heterogeneous environment [13]. In the min-min heuristic, the next minimum sized task is always removed from the list of tasks waiting for the execution, and it will be executed on a device, which provides the earliest expected completion time. This process repeats until all the task are mapped to the processors. The parallel GPU-based implementation of min-min heuristic has been studied as well [78].

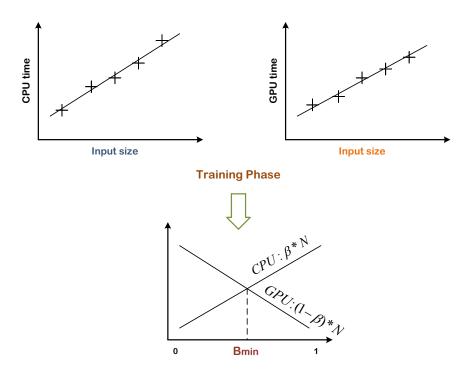

Figure 2.5: Training and partitioning phases of Qilin method [62].

There are several studies on how to statically distribute the massively parallel computations over the CPU and GPU cores on a heterogeneous environment. Qilin [62] focuses on a on a single-CPU single-GPU system. It employs an adaptive mapping scheme that involves a training phase. The training phase interpolates a system of linear equations based on empirical results from adaptive mappings. Adaptive mapping starts with a training phase in which two linear equations are built based on calculating the execution time of different sized sub-tasks of an arbiter data parallel problem size on CPU and GPU separately. Solution of these equations provides the best partitioning between the CPU and the GPU.

Figure 2.5 shows the training and partitioning phases of Quilin method. If  $\beta$  shows the fraction of input load assigned to CPU,  $(1 - \beta)$  shows the portion of the load assigned to GPU. The intersection of the two diagrams in Figure 2.5, determines the value of  $\beta$  that minimizes the makespan. If  $\beta < 0$ , all the input workload is mapped to GPU. If  $\beta \ge 1$ , all the workload is mapped to CPU and, If  $0 < \beta < 1$ , the distribution rate of actual problem size over CPU and GPU is determined according to the value of  $\beta$ .

The most serious problem in the Qilin approach is the overhead of the training phase. Furthermore according to the empirical results, the method is efficient when the problem size in the training phase is at least 30% of the actual problem size. Consequently, when executing a very large-size problem, implementation of the training phase can impose a prohibitive overhead. Finally, this strategy is applicable in a single-CPU single-GPU system and is not scalable.

Another static task partitioning scheme for heterogeneous CPU-GPU systems [33] extracts the code features of a program at compile time by utilizing machine-learning techniques [73] and, based on some training data, the best partitioning among the processors is predicted using a two level predictor. In the first level, it filters the programs which are mapped to either CPU or GPU. The remaining programs are passed to the second level and based on their futures are classified in to 11 groups. These prediction steps are done during the run-time when the problem input size is known and it has a negligible overhead. However, the complexity related to designing the predictor and lack of suitable training data could degrade the accuracy of this approach.

Wang et al. [94] proposed a static scheduling, where task are modeled into two different computing and communicating categories using a hierarchical control data flow graph. The computing-intensive subtasks are executed by GPU, and the communication-intensive subtasks are assigned to CPU. Although the authors compared the proposed algorithm with the traditional scheduling algorithms, the details of implementation have not been well documented. Furthermore it is only applicable in a heterogeneous system equipped with a single GPU.

Boratto et al. [11] applied a static scheduling technique, to partition the workload of the matrix computation constructed for solving the landform attributes representation, over a heterogeneous CPU-GPU systems. However, the portion of workload delivered to each device is an input to the scheduler provided by the user manually.

#### 2.4.2 Dynamic Heuristics

The greedy heuristic is a common dynamic heuristics for the heterogeneous system in which, once a processor becomes idle it greedily picks up a task from the task pool. Yuan et al. [95] implemented the dynamic greedy heuristic on a heterogeneous CPU-GPU system, and showed that it achieves better speedup in comparison to GPU-only and CPU-only policies. Choi et al. [20] discussed a similar scheduling heuristic which maps an incoming task on the first available device.

Ravi et al. [82] developed a compiler and a runtime scheduler for heterogeneous distributed systems, dedicated for map-reduce applications [23], which involves a generalized reduction. Each node has a multicore CPU and a GPU; it receives a number of chunks and partitions the chunks dynamically to the processors based on a master-worker paradigm. However, the optimal split size has not been determined in this work. The approach is restricted to specific application types that fit into the map-reduce model.

V. Jiménez et al. [44] explored the scheduling in multi-programmed heterogeneous systems based on a performance history aimed to fully utilize all the available processors in CPU-GPU devices. In the initiation phase, each application runs on different devices and a performance history will be created which is used in the next phase to assign the programs to the processors. Nevertheless there is not any load-partitioning algorithm in this method and the main goal is to improve the performance where several applications are concurrently scheduled in the system.

Scogland et al. [84] proposed several compiler and runtime strategies to schedule the iteration-based OpenMP [16] loads across a single-CPU single-GPU architecture. Initially a static scheduler calculates the distribution ratio of load over the devices based on the number of cores. Then a dynamic scheduler attempts to predict the portion of loads on each device in the upcoming rounds based on the execution time of the load portion in the current round. Nonetheless, this approach is not scalable to more number of GPUs and it is not accurate due to non-linear properties of the GPU for different load sizes.

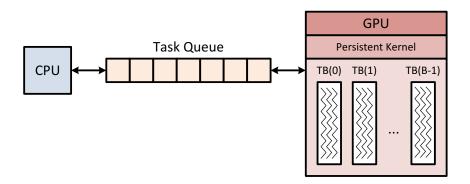

Figure 2.6: Task queue scheme for scheduling on GPU [56].

Hamano et al. [89] considered the estimated energy consumption of the CPU and GPU in the idle and busy states, as the criteria of the scheduling decision. According to their energy consumption model, each task is mapped to the device that leads to minimum energy consumption.

Some researchers have addressed the scheduling and load balancing techniques on the GPU devices. In [56], the authors proposed a dynamic task-based load balancing technique for single and multi-GPU systems. In conventional CUDA paradigm, multiple kernels are launched sequentially to execute several tasks. However, in this work, they use a task-based queue scheme and instead of launching several kernels, a persistent kernel [34] with B thread blocks (B is the maximum number of concurrent active blocks in a GPU Device) is launched. These thread blocks dequeue the tasks in a wait-free [41] approach and execute them concurrently according to the pre-defined tasks information. The details of this method can be seen in Figure 2.6.

Tzeng et al. [90] employed a similar technique to schedule the irregular parallel workloads dynamically on a single GPU. They implement a distributed work-queue based system, but work units are inserted to the queue in the size of warp. Also a persistent kernel model is utilized in which sufficient number of warps is launched a priori to keep all the cores busy. Each warp worker reads as many work units as possible from its dedicated queue and enqueues the possibly dynamic created work units back to the queue. To balance the load among the cores, some of the workers can steal some works from other queues or donate their work in case of queue overflow.

One shortcoming of this work is that all the applications are not fit in the warp-size work units. This degrades the generality of this scheduling method. Furthermore this technique just supports the independent work units.

In [60], the authors developed a task-based method for scheduling the loads on GPU by grouping small tasks together and executing them on a multi-kernel supporting GPU. They also proposed a methodology for executing a set of the tasks in the most efficient sequence.

#### 2.4.3 Scheduling Frameworks

Harmony [24] is a general runtime model for heterogeneous multi-core systems in which each application is composed of a set of kernels with different types of dependencies. Whenever the dependencies of one kernel have been resolved it will be scheduled dynamically over the CPU and different accelerators, based on a greedy scheduling heuristic.

StarPU [4] is a run-time framework for plugging in and executing scheduling algorithms on a heterogeneous CPU-GPU system. The programming environment accesses the low-level libraries indirectly by building over the framework interfaces. Different scheduling algorithms have been proposed including greedy scheduling and performance-based scheduling. However, the programmers have to use a new API proposed by the system, because the tasks are demonstrated with codelet [25] abstraction, which consists of tasks augmented with their input and output specifications.

In [17], the authors designed a work stealing run-time on the GPU to execute irregular applications with dynamic task parallelism across the SMs on GPU and to balance the workload among them. They employ a work queue in which, the tasks are copied from the host and are executed over the SMs with the block granularity. Since some tasks may be created dynamically the work-stealing method among the SMs will balance the loads among the SMs on GPU.

# 2.5 Graph Partitioning

Graph partitioning and graph clustering have extensive applications in various areas of scientific computing. While graph clustering [3, 6] identifies the groups of the vertices in a graph that show the same behavior or similar characteristics, graph partitioning is a sub-category of the clustering problem with two specific objectives; The first is to decompose a graph into k sets of partitions such that communication cost between the partitions are minimized and the second is to balance the weights of partitions.

Formally, given an undirected graph represented by a tuple  $(V, E, W_V, W_E)$ , where V is the set of vertices, E is the set of edges,  $W_{v_i}$  is the weight of each vertex  $v_i$ , and  $W_{e_i}$  is weight of each edge  $e_i$ , graph partitioning is to divide the graph G into k partitions  $\{p_1, p_2, \dots, p_k\}$  such that:

$$p_i \cap p_j = \emptyset \text{ if } i \neq j \text{ and } \bigcup_{i=1}^k p_i = V$$

(2.1)

A quality approach keeps the partitions as balanced as possible with respect to their accumulated vertex weights, i.e., if we show the total weight of all vertices in partition  $p_i$  using  $W_{p_i}$ , then we expect:

$$W_{p_i(i=1,2,\cdots,k)} \simeq \frac{\sum_{i=1}^k W_{p_i}}{k}$$

(2.2)

Another common expectation is to minimize the accumulated edge cut weights (total communication cost) where an edge cut is defined as:

$$edge \ cut = \sum_{\substack{e=(a,b)\in E\\p(a)\neq p(b)}} W_e$$

(2.3)

The graph partitioning problem is NP-complete. Consequently, many heuristics

have been proposed to quickly find a near-optimal solution [47, 70, 80]. Spectral partitioning methods [80] calculate the Laplacian matrix associated with the graph and, divide the vertices of the graph into the two subgraphs by using one of the eigenvectors of the Laplacian matrix. Although the spectral methods produce high quality partitioning, they are slow, sine they need expensive computations for calculating the eigenvector. Geometric graph partitioning methods [70] are applicable only when the graph vertices coordinates are available and they produce the partitions with lower quality in comparison to the spectral methods.

The most successful heuristic for partitioning large graphs used in scientific computations is the multilevel graph partitioning approach [39, 47, 77, 91]. The idea is to first reduce the graph size by matching and collapsing the vertices in multiple coarsening levels until the number of vertices is below a threshold; then the coarsened graph is partitioned, and finally the partitioning is projected back through the multiple levels onto the original graph. Multilevel graph partitioning has become the standard approach for developing high quality and computationally efficient solutions for graph partitioning.

### 2.5.1 Serial Multilevel Graph partitioning

Multilevel graph partitioning techniques [15, 39, 47, 77, 91] are generally preferred over other techniques such as spectral partitioning [80] due to higher quality of partitions at a faster computation time. Handrickson and Leland [39] validated this claim using extensive experiments. Metis [47], Scotch [77], and Jostle [91] are the well-known multilevel graph partitioning solutions.

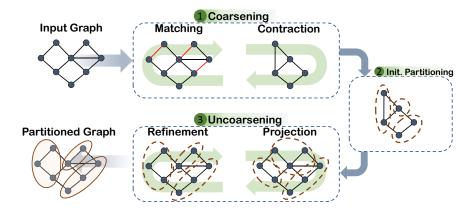

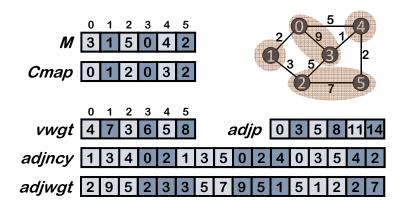

Figure 2.7 gives an overview of the multilevel graph partitioning algorithm. The algorithm consists of three distinct phases that we describe below.

**Coarsening.** In this phase, the graph is iteratively shrunk by matching and collapsing vertices in order to construct a compact version of the graph. Every iteration includes two steps commonly known as *matching* and *contraction*. The matching step finds a set M of edges such that no pair within the set is incident on the same vertex,

Figure 2.7: An overview of multilevel graph partitioning.

while the contraction step collapses all the matched vertex pairs together.

Serial algorithms find the maximal matching where it is not possible to add another independent edge to the set whereas parallel algorithms usually relax this assumption to avoid its overhead. Although several polynomial time algorithms have been proposed for graph matching [27, 68], they are very slow and difficult to be parallelized for large real-world graphs. Approximation algorithms such as Random Matching [39], Heavy Edge Matching [50, 81], and Light Edge Matching [47] are typically favored over polynomial time algorithms due to enabling a better trade-off between the computation time and the quality of partitions. Heavy Edge Matching (HEM) exhibits the best results where each vertex is searched for the neighbor connected with the edge having the maximum weight since iterative application of this procedure minimizes the edge weights in the coarser graph. Metis, Scotch, and Jostle all employ HEM for the matching graph vertices in the coarsening phase.

For two collapsed vertices u and v, the weight of the newly created vertex  $c(W_c)$  in the coarser graph is equal to  $W_u + W_v$ . Also, if there is one vertex z that is connected to both u and v in the finer graph, then there will be one edge in the coarser graph from z to c with the weight  $W_{u,z} + W_{v,z}$ . The coarsening step hierarchically creates the successive coarser graphs until the number of vertices in the resulted graph is less than a threshold value or equal to the number of required partitions.

The matching and contraction steps terminate based on a specific criterion. In

Metis and Scotch, the matching ends when the number of vertices of the coarse graph is O(p), where p is the number of partitions, or if the difference in the number of vertices in the coarser graph  $G_{i+1}$  compared to the number of vertices in the next finer graph  $G_i$  is less than a threshold value. Jostle terminates the matching when the number of vertices in the coarse graph is equal to the number of required partitions.

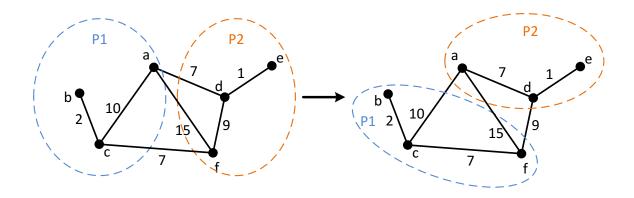

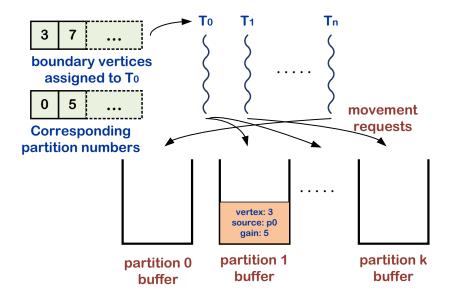

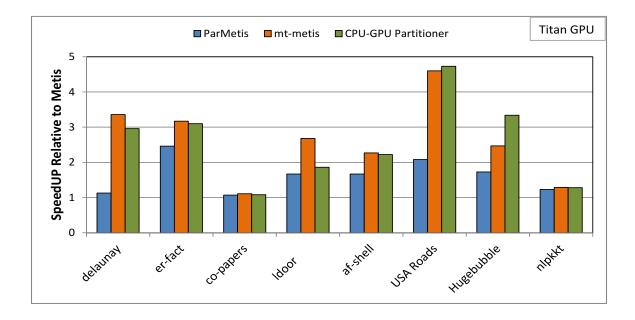

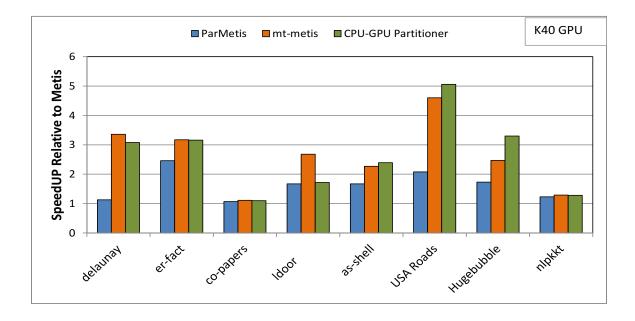

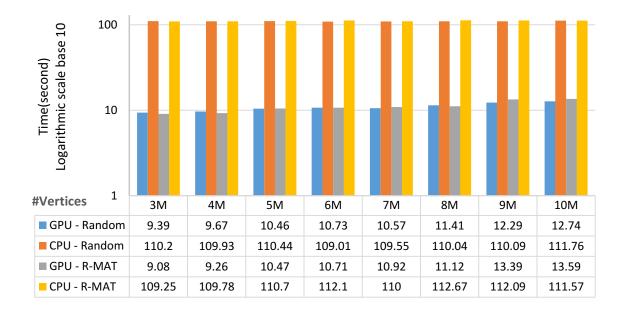

*Initial Partitioning.* This phase creates a preliminary partition from the coarsest graph. With vertices grouped together in larger entities, it is easier to reason about the approximate partition weights and initial edge cuts. The initial partition created in this phase drives the partitioning of the finer graphs in the next phase.