## High-Level Analysis of the Impact of Soft-Faults in Cyberphysical Systems

Marwan Ammar

$\begin{array}{c} {\rm A~thesis} \\ {\rm in~The~Department} \\ {\rm of} \\ \\ {\rm Electrical~and~Computer~Engineering} \end{array}$

Presented in Partial Fulfillment of the Requirements

For the Degree of

Doctor of Philosophy (Electrical and Computer Engineering) at

Concordia University

Montréal, Québec, Canada

November 2019 © Marwan Ammar, 2019

#### **CONCORDIA UNIVERSITY**

#### SCHOOL OF GRADUATE STUDIES

| Inis is to certify                   | that the thesis prep      | ared                                                             |

|--------------------------------------|---------------------------|------------------------------------------------------------------|

| By:                                  | Marwan Ammar              |                                                                  |

| Entitled:                            | High-Level Ana<br>Systems | lysis of the Impact of Soft-Faults in Cyberphysical              |

| and submitted in                     | partial fulfillment       | of the requirements for the degree of                            |

|                                      | Doctor Of Philoso         | phy (Electrical and Computer Engineering)                        |

| complies with the originality and qu | •                         | University and meets the accepted standards with respect to      |

| Signed by the fin                    | al examining com          | nittee:                                                          |

| Dr. Luis                             | Amador-Jimene             | Chair                                                            |

| Dr Ron                               | i Khazaka                 | External Examiner                                                |

|                                      |                           | External to Program                                              |

| Dr. Ling                             | yu Wang                   |                                                                  |

| Dr. Abd                              | elwahab Hamou-            | Examiner<br>Lhadj                                                |

| Dr. Ferh                             | at Khendek                | Examiner                                                         |

| Dr. Otm                              | ane Ait Mohame            | Thesis Co-Supervisor                                             |

| Dr Yvo                               | n Savaria                 | Thesis Co-Supervisor                                             |

|                                      |                           |                                                                  |

| Approved by                          |                           |                                                                  |

|                                      | Dr. Rastko                | Selmic, Graduate Program Director                                |

| January 8, 2020                      | Dr                        | Amir Asif, Dean na Cody School of Engineering & Computer Science |

|                                      | Ul                        | ia cody behoof of Engineering & Computer selence                 |

### Abstract

### High-Level Analysis of the Impact of Soft-Faults in Cyberphysical Systems

Marwan Ammar, Ph.D.

As digital systems grow in complexity and are used in a broader variety of safety-critical applications, there is an ever-increasing demand for assessing the dependability and safety of such systems, especially when subjected to hazardous environments. As a result, it is important to identify and correct any functional abnormalities and component faults as early as possible in order to minimize performance degradation and to avoid potential perilous situations. Existing techniques often lack the capacity to perform a comprehensive and exhaustive analysis on complex redundant architectures, leading to less than optimal risk evaluation. Hence, an early analysis of dependability of such safety-critical applications enables designers to develop systems that meets high dependability requirements. Existing techniques in the field often lack the capacity to perform full system analyses due to state-explosion limitations (such as transistor and gate-level analyses), or due to the time and monetary costs attached to them (such as simulation, emulation, and physical testing).

In this work we develop a system-level methodology to model and analyze the effects of Single Event Upsets (SEUs) in cyberphysical system designs. The proposed methodology investigates the impacts of SEUs in the entire system model (fault tree level), including SEU propagation paths, logical masking of errors, vulnerability to specific events, and critical nodes. The methodology also provides insights on a system's weaknesses, such as the impact of each component to the system's vulnerability, as well as hidden sources of failure, such as latent faults. Moreover, the proposed methodology is able to identify and categorize the system's components in order of criticality, and to evaluate different approaches to the mitigation of such criticality (in the form of different configurations of TMR) in order to obtain the most efficient mitigation solution available.

The proposed methodology is also able to model and analyze system components individually (system component level), in order to more accurately estimate the component's vulnerability to SEUs. In this case, a more refined analysis of the component is conducted, which enables us to identify the source of the component's criticality. Thereafter, a second mitigation mechanic (internal to the component) takes place, in order to evaluate the gains and costs of applying different configurations of TMR to the component internally. Finally, our approach will draw a comparison between the results obtained at both levels of analysis in order to evaluate the most efficient way of improving the targeted system design.

## Acknowledgments

It has been an amazing experience and a privilege to pursue my doctorate in the Hardware Verification Group (HVG) at Concordia. It certainly would not have happened without the support and guidance of several people to whom I owe a great deal.

First of all, I would like to thank my supervisor, Dr. Otmane Ait Mohamed. It is he who offered me the opportunity to join the group. He was fully supportive, understanding, involved and present during all the phases of my research. I have learned many things from him in regard to research, academia, and life in general.

Secondly, I sincerely thank my co-supervisor, Prof. Yvon Savaria, for always being there to listen and to offer me guidance in the moments I needed the most. This thesis would not have been possible without his advice, his support and his encouragement.

Next, I'd like to thank all the members of HVG for their help and encouragement, particularly to Dr. Ghaith Bany Hamad.

Last but not least, I thank my close family, my parents, and my little bunny. They have a great deal of credit on everything I have accomplished in my life and for everything I'm yet to accomplish in the future.

### Contributions of Authors

**Article I:** Formal Analysis of Fault Tree using Probabilistic Model Checking: A Solar Array Case Study

This paper was the result of my first effort into modeling and analyzing safety-critical systems exposed to single-event upsets (SEUs). The idea was to apply probabilistic model checking to resolve the system's fault diagram expressed in fault tree notation, which is normally resolved through simulation. In this article, I am responsible for all the methodology reasoning, all the modeling, all the experiments and interpretation of the data. The contribution of the co-author (Khaza Anuarul Hoque) were helping to find the case-study and reviewing the paper before submission.

**Article II:** Efficient Probabilistic Fault Tree Analysis of Safety Critical Systems via Probabilistic Model Checking

In this article, I have conducted a study on the impact of redundant architectures (namely, triple modular redundancy) on systems exposed to SEUs. The methodology proposed in this article is the first of its kind, utilizing probabilistic model-checking and high-level system modeling through fault trees to locate possible system vulnerabilities and evaluate the best mitigation solution. In this article, I am responsible for all the modeling, methodologies applied, experiments and data interpretation. The co-author in this work (Ghaith Bany Hamad) helped me to conduct model validation and reviewing the text.

**Article III:** System-Level Analysis of the Vulnerability of Processors Exposed to Single-Event Upsets via Probabilistic Model Checking

This article presents my component-level analysis methodology. Based on my previous work, I identified two sources of problems with fault tree analysis: 1) the high-level of abstraction of fault trees lacks the information to solve some problems, such as

"where does the fault originate from" or "how to avoid it"; 2) in the literature, fault trees are only generated after the system is manufactured and running. How can I generate a fault tree early in the design cycle? Initially, this idea was conceived (and subsequently published) in a paper entitled "Comprehensive Vulnerability Analysis of Systems Exposed to SEUs via Probabilistic Model Checking", published in the 16th IEEE Conference on Radiation Effects on Components and Systems (RADECS) in 2016. For this article, I have conducted the SEU analysis of two microprocessors. The analysis was conducted with probabilistic model-checking and the modeling was done based on the Register-transfer level (RTL) representation of the targeted processors. Furthermore, one of the products of this approach is the generation of a faultpropagation diagram, that can be easily converted into a fault tree. I was responsible for the conception of the idea, all the modeling and experiments and interpretation of results. The co-author (Ghaith Bany Hamad) offered help with the interpretation of the RTL diagrams, model validation and text review. This article was invited for extension and subsequently published as a chapter in the book Radiation Effects on Integrated Circuits and Systems for Space Applications [136].

# **Article IV:** Reliability Analysis of the SPARC V8 Architecture via Fault Trees and UPPAL-SMC

This article was my first attempt at solving a new issue that was highlighted to me by the collection of my previous works. This issue was that fault trees were fundamentally not suitable for an early system analysis of SEU exposure. The reason for this is that a traditional fault tree can only capture a single moment in time. However, SEUs are dynamic events that may occur and reoccur at random intervals. Furthermore, the effects of SEUS may be permanent or only temporary, and the only way to capture these phenomena is to perform a dynamic analysis over time. This paper utilizes my methodology to obtain a fault tree from an RTL diagram and it presents my first effort to perform a fault tree analysis over time. I am responsible for the idea, all the modeling and experiments, as well as interpretation of the results. The co-author (Ghaith Bany Hamad) has helped me with the interpretation of the SPARC V8 architecture and by reviewing the text.

Article V: Towards an Accurate Probabilistic Modeling and Statistical Analysis of

Temporal Faults via Temporal Dynamic Fault-Trees (TDFTs)

This article presents the culmination of the idea introduced by Article IV. My work has demonstrated that the analysis over time of conventional fault trees can only produce accurate results for a very short period or time, after which the results become unreliable (based on comparison with results obtained by radiation ground testing). To address this, I have proposed a completely new type of time-enabled fault trees, with dynamic properties and dynamic events. Along with a new analysis methodology, the conducted experiments and the results demonstrate that this technique can be used early in the design cycle to predict SEU effects in complex systems. In this paper, I am responsible for all the modeling and analysis and all the experiments and data interpretation. The co-author (Ghaith Bany Hamad) has helped me to conduct model validation and has reviewed the text.

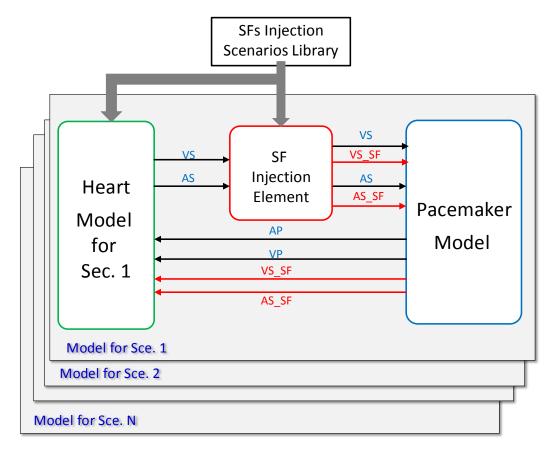

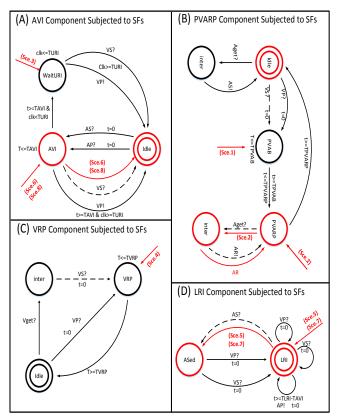

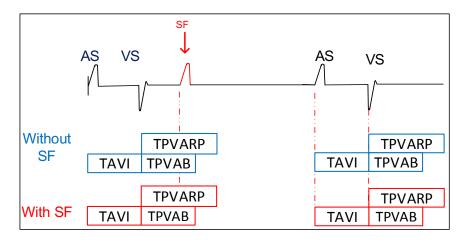

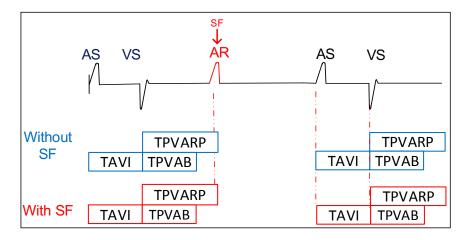

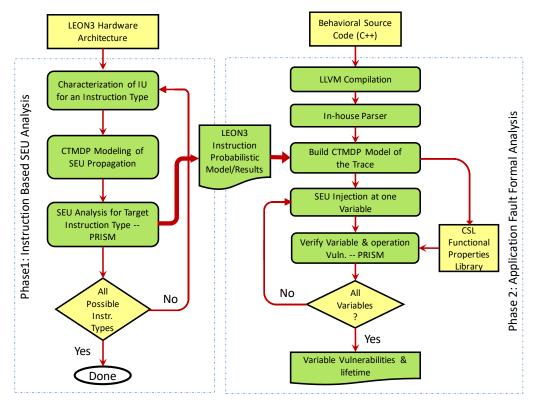

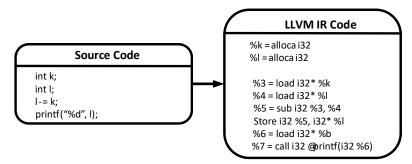

**Applications:** In addition to the articles presented in the body of this thesis, I have been co-author and have applied my methodology in two journal papers, shown in Chapter 10. In the first article, titled "New Insights Into Soft-Faults Induced Cardiac Pacemakers Malfunctions Analyzed at System-Level Via Model Checking" [21], we perform a comprehensive component-level analysis on a common model of implantable pacemaker exposed to SEUs. In this paper, I am responsible for all the modeling and analysis, all the experiments and for writing about 40% of the text. The first author (Ghaith Bany Hamad) is responsible for the idea of the work, all the background research, the model validation and for writing about 60% of the text. Both authors contributed to the interpretation of the results. In the second article, titled "System-Level Characterization, CTMDP Modeling, and Analysis of Computing Systems Reliability Applied to the LEON3 Processor" (not submitted) we work on improving my component-level methodology by proposing a system-level analysis based on the application that the system under test is running. This involves the characterization of the micro architecture, as well as each possible operation and the sequence of operations in the application. Initially, this idea was conceived (and subsequently published) in a paper entitled "System-Level Characterization, Modeling, and Probabilistic Formal Analysis of LEON3 Vulnerability to Transient Faults", published in the 18th IEEE Conference on Radiation Effects on Components and Systems (RADECS) in 2018. In this article, I am responsible for all the modeling and analysis, all the experiments and for writing approximately 40% of the text. The first author (Ghaith Bany Hamad) is responsible for the characterization of the LEON3 architecture and for writing approximately 60% of the text. Both authors contributed to the characterization of the applications and the interpretation of the results.

## Contents

| Li | ist of                       | Figures                                                         | $\mathbf{x}\mathbf{v}$ |

|----|------------------------------|-----------------------------------------------------------------|------------------------|

| Li | ist of                       | Tables                                                          | viii                   |

| 1  | Intr                         | roduction                                                       | 1                      |

|    | 1.1                          | Motivation and Problem Formulation                              | 3                      |

|    |                              | 1.1.1 Radiation Ground Testing                                  | 4                      |

|    |                              | 1.1.2 Radiation Testing through Simulation                      | 5                      |

|    |                              | 1.1.3 Radiation Testing through Formal Verification             | 6                      |

|    | 1.2                          | Thesis Objectives                                               | 6                      |

|    | 1.3                          | Thesis Contributions                                            | 7                      |

|    |                              | 1.3.1 Fault-Tree Analysis Phase                                 | 9                      |

|    |                              | 1.3.2 Component-Level Analysis Phase                            | 12                     |

|    | 1.4                          | Thesis Organization                                             | 15                     |

| 2  | $\operatorname{Lit}\epsilon$ | erature Review                                                  | 18                     |

| 3  | Bac                          | kground Information                                             | 21                     |

|    | 3.1                          | Fault Tree Analysis                                             | 21                     |

|    | 3.2                          | Triple Modular Redundancy                                       | 23                     |

|    | 3.3                          | Probabilistic Model Checking                                    | 24                     |

|    |                              | 3.3.1 PRISM Model Checker                                       | 24                     |

|    |                              | 3.3.2 UPPAAL-SMC                                                | 25                     |

| 4  | Art                          | icle I: Formal Analysis of Fault Tree using Probabilistic Model |                        |

|    | $\mathrm{Ch}\epsilon$        | ecking: A Solar Array Case Study                                | 27                     |

|    | 4.1                          | Introduction                                                    | 28                     |

|   | 4.2            | Preliminaries                                                        | 29 |

|---|----------------|----------------------------------------------------------------------|----|

|   |                | 4.2.1 Probabilistic Model Checking with PRISM                        | 29 |

|   |                | 4.2.2 Fault Tree Analysis                                            | 30 |

|   | 4.3            | Related Works                                                        | 31 |

|   | 4.4            | Modeling                                                             | 33 |

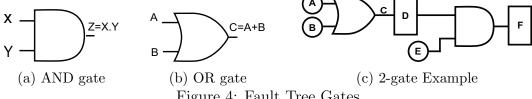

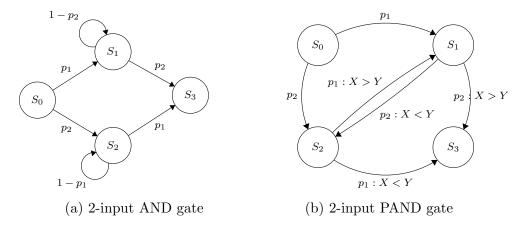

|   |                | 4.4.1 Modeling of an AND Gate                                        | 33 |

|   |                | 4.4.2 Modeling of an OR Gate                                         | 35 |

|   |                | 4.4.3 Sample Modeling of a 2-Gate System                             | 36 |

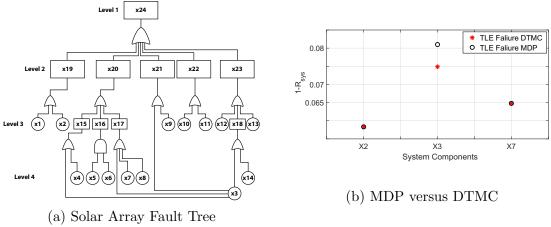

|   | 4.5            | Case Study                                                           | 38 |

|   | 4.6            | Conclusion                                                           | 41 |

| 5 | Art            | icle II: Efficient Probabilistic Fault Tree Analysis of Safety Crit- |    |

|   | ical           | Systems via Probabilistic Model Checking                             | 43 |

|   | 5.1            | Introduction                                                         | 44 |

|   | 5.2            | Related Work                                                         | 46 |

|   | 5.3            | Proposed Methodology                                                 | 47 |

|   |                | 5.3.1 Probabilistic Modeling of Fault Trees                          | 48 |

|   |                | 5.3.2 Modeling of TMR                                                | 52 |

|   | 5.4            | Experimental Results                                                 | 54 |

|   | 5.5            | Conclusion                                                           | 60 |

| 6 | $\mathbf{Art}$ | icle III: System-Level Analysis of the Vulnerability of Processors   |    |

|   | Exp            | posed to Single-Event Upsets via Probabilistic Model Checking        | 62 |

|   | 6.1            | Introduction                                                         | 63 |

|   | 6.2            | Markov Modeling of Self-Repair Systems                               | 65 |

|   | 6.3            | Proposed Probabilistic Modeling of SEUs Propagation in Processors .  | 67 |

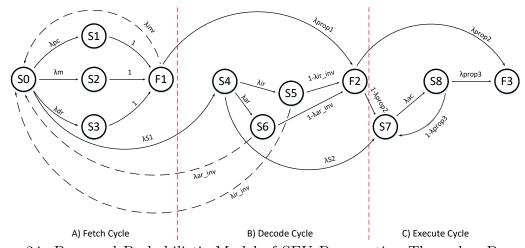

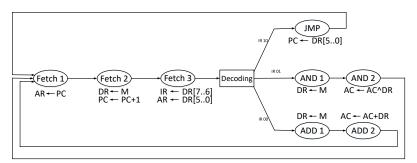

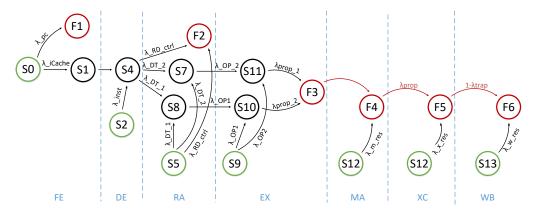

|   |                | 6.3.1 Fetching Phase                                                 | 69 |

|   |                | 6.3.2 Decoding Phase                                                 | 70 |

|   |                | 6.3.3 Execution Phase                                                | 71 |

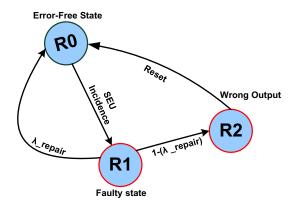

|   |                | 6.3.4 Self-Repair Routine                                            | 72 |

|   | 6.4            | Proposed Formal Modeling and Analysis in PRISM                       | 72 |

|   | 6.5            | Experimental Analysis                                                | 74 |

|   | 6.6            | Conclusion and Future Work                                           | 81 |

| 7 | Art   | icle IV | : Reliability Analysis of the SPARC V8 Architecture via       | l   |

|---|-------|---------|---------------------------------------------------------------|-----|

|   | Fau   | lt Tree | es and UPPAL-SMC                                              | 82  |

|   | 7.1   | Introd  | uction                                                        | 82  |

|   | 7.2   | Existin | ng Fault Analysis of SPARC V8                                 | 84  |

|   | 7.3   | Model   | ing the SPARC V8 Pipeline as DFT                              | 84  |

|   |       | 7.3.1   | General Considerations and Assumptions                        | 85  |

|   |       | 7.3.2   | System Level Fault Abstraction                                | 85  |

|   |       | 7.3.3   | PTA Model Composition                                         | 87  |

|   | 7.4   | Stocha  | astic Soft-fault Analysis with UPPAAL                         | 88  |

|   | 7.5   | Conclu  | usion and Future Work                                         | 91  |

| 8 | Art   | icle V: | Towards an Accurate Probabilistic Modeling and Statisti-      | -   |

|   | cal . | Analys  | sis of Temporal Faults via Temporal Dynamic Fault-Trees       | 8   |

|   | (TL)  | OFTs)   |                                                               | 92  |

|   | 8.1   | Introd  | uction                                                        | 93  |

|   | 8.2   | Relate  | d Works                                                       | 95  |

|   | 8.3   | Prelim  | inaries                                                       | 97  |

|   |       | 8.3.1   | The UPPAAL Formalism                                          | 97  |

|   |       | 8.3.2   | Fault Tree Analysis                                           | 97  |

|   | 8.4   | Propos  | sed TDFT Modeling and Analysis Methodology                    | 98  |

|   |       | 8.4.1   | Proposed Probabilistic Model of the Temporal AND Gate         | 100 |

|   |       | 8.4.2   | Proposed Probabilistic Model of the Temporal OR Gate          | 103 |

|   |       | 8.4.3   | Proposed Probabilistic Model of the Temporal FDEP gate $$     | 104 |

|   |       | 8.4.4   | Proposed Probabilistic Model of the Temporal PAND gate $$     | 106 |

|   |       | 8.4.5   | Proposed Probabilistic Model of the Temporal COMB Gate $$ .   | 107 |

|   |       | 8.4.6   | Proposed Analysis Methodology                                 | 110 |

|   | 8.5   | Exper   | imental Results                                               | 111 |

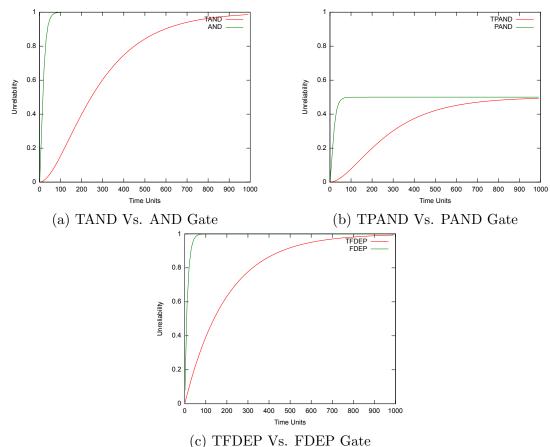

|   |       | 8.5.1   | Unreliability Evaluation Over Time                            | 111 |

|   |       | 8.5.2   | Scalability of the Proposed TDFT Analysis                     | 112 |

|   |       | 8.5.3   | Comparison between TDFTs and Temporal Fault Trees (TFTs)      | 116 |

|   |       | 8.5.4   | Failure Estimation of the SPARC V8 Architecture with TDFTs $$ | 117 |

|   | 8.6   | Concli  | ısion                                                         | 120 |

| 9  | Con  | clusio  | and Future Work                                                 | 122   |

|----|------|---------|-----------------------------------------------------------------|-------|

|    | 9.1  | Conclu  | ısion                                                           | 122   |

|    | 9.2  | Future  | e Work                                                          | 124   |

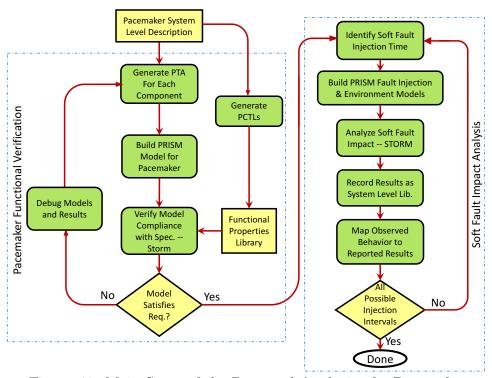

| 10 | App  | licatio | ons                                                             | 127   |

|    | 10.1 | New I   | nsights Into Soft-Faults Induced Cardiac Pacemakers Malfunc-    |       |

|    |      | tions A | Analyzed at System-Level Via Model Checking                     | 127   |

|    |      | 10.1.1  | Introduction                                                    | 128   |

|    |      |         | Existing Observations of the Impact of Soft-Faults on Pacemaker | rs130 |

|    |      |         | Formal Modeling and Analysis of the Functionality of the Pace-  |       |

|    |      |         | makers                                                          | 131   |

|    |      | 10.1.2  | Probabilistic Model Checking (PMC) & $Storm$                    | 132   |

|    |      | 10.1.3  | Steps of the Proposed Pacemaker Analysis                        | 132   |

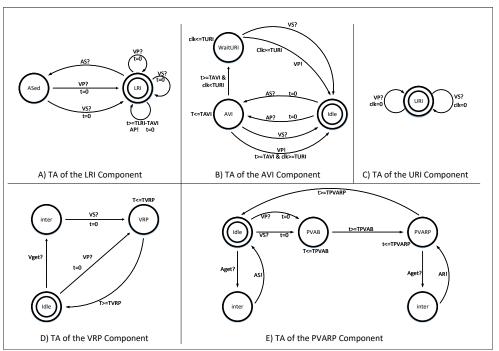

|    |      | 10.1.4  | Behavior of the DDD Pacemaker                                   | 134   |

|    |      | 10.1.5  | PTA Modeling & Functional Analysis of Pacemaker                 | 135   |

|    |      | 10.1.6  | Non-functional Analysis of the Pacemaker Vulnerability to Soft- |       |

|    |      |         | Faults                                                          | 139   |

|    |      |         | Soft-Fault Classification                                       | 140   |

|    |      |         | Formal Modeling and Analysis of Soft-Faults                     | 141   |

|    |      | 10.1.7  | New Insights on Possible Pacemaker Malfunctions Induced by      |       |

|    |      |         | Soft-Faults                                                     | 145   |

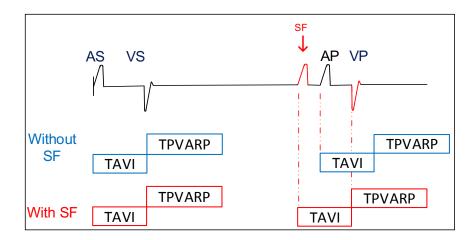

|    |      |         | SF-Induced Pacemaker Oversensing                                | 146   |

|    |      |         | SF-Induced Pacemaker Undersensing                               | 150   |

|    |      |         | SF-Induced Output Failure                                       | 151   |

|    |      | 10.1.8  | Conclusion                                                      | 151   |

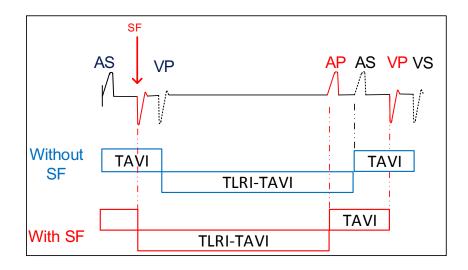

|    | 10.2 | System  | n-Level Characterization, CTMDP Modeling, and Analysis of       |       |

|    |      | Comp    | uting Systems Reliability Applied to the LEON3 Processor        | 152   |

|    |      | 10.2.1  | Introduction                                                    | 153   |

|    |      | 10.2.2  | Main Steps of the Proposed Framework                            | 156   |

|    |      | 10.2.3  | Instruction Based Characterization, Modeling, and Analysis $$ . | 159   |

|    |      |         | Characterization of Radiation-Induced Soft-Errors               | 159   |

|    |      |         | Microarchitecture-Based Characterization                        | 160   |

|    |      |         | Instruction-Based Markov Modeling                               | 161   |

|    |      | 10 2 4  | Fault Injection and Analysis Through CTMDP                      | 162   |

| Bibliography |                                             | 171 |

|--------------|---------------------------------------------|-----|

| 10.2.7       | Conclusion                                  | 170 |

| 10.2.6       | Experimental Results                        | 166 |

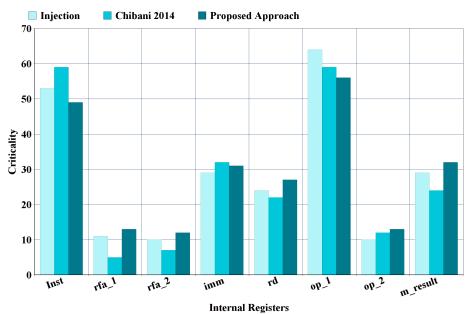

| 10.2.5       | Application Based SEU Modeling and Analysis | 165 |

# List of Figures

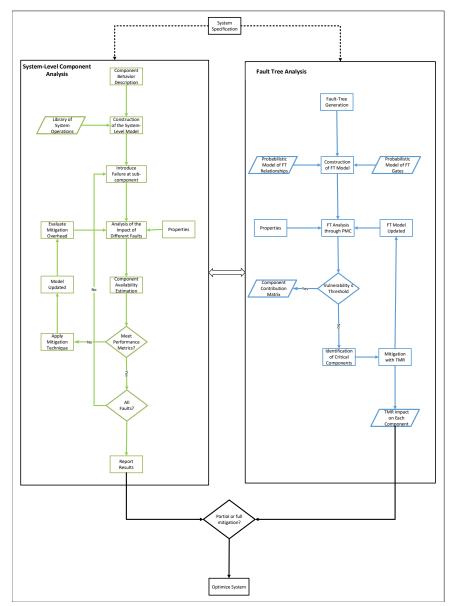

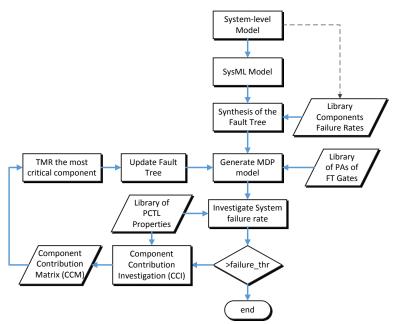

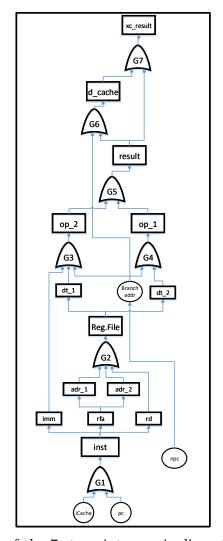

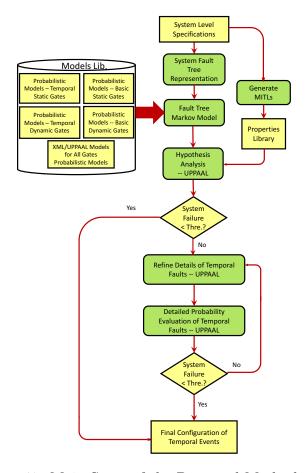

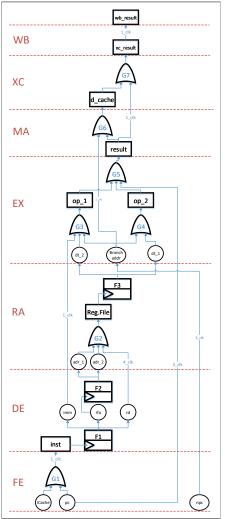

| 1  | Overview of the Proposed Framework                                        | 9  |

|----|---------------------------------------------------------------------------|----|

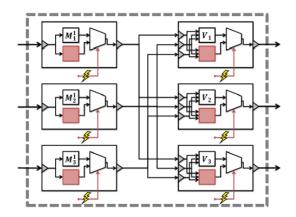

| 2  | Example of TMR Applied to a Generic Component                             | 23 |

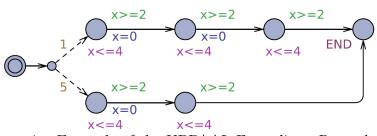

| 3  | Illustrative Example of the UPPAAL Formalism. Reproduced from [46].       | 26 |

| 4  | Fault Tree Gates                                                          | 33 |

| 5  | 2-input AND gate DTMC                                                     | 34 |

| 6  | PRISM modeling of an AND gate                                             | 35 |

| 7  | 2 input OR gate DTMC                                                      | 36 |

| 8  | PRISM modeling of an OR gate                                              | 36 |

| 9  | 2-gate DTMC                                                               | 37 |

| 10 | PRISM modeling of the 2-gate example                                      | 37 |

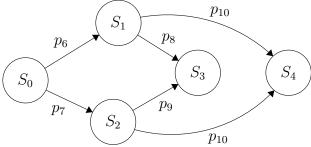

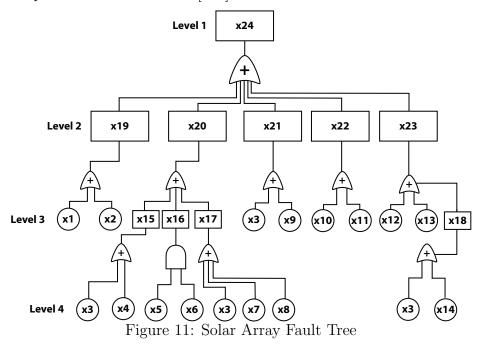

| 11 | Solar Array Fault Tree                                                    | 38 |

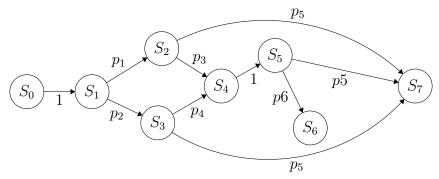

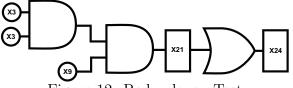

| 12 | Redundancy Test                                                           | 41 |

| 13 | Main Steps of the Proposed Methodology                                    | 48 |

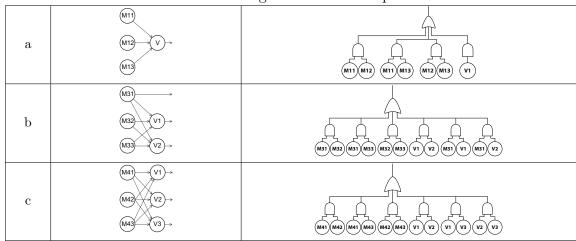

| 14 | Example of Fault Tree Gate Automata                                       | 50 |

| 15 | Modeling FT as MDP versus DTMC                                            | 52 |

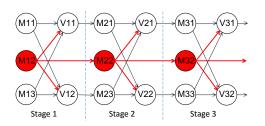

| 16 | Example of different TMR arrangements                                     | 54 |

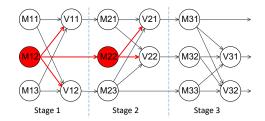

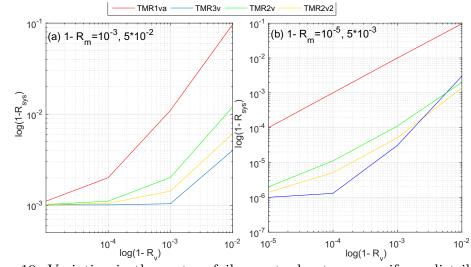

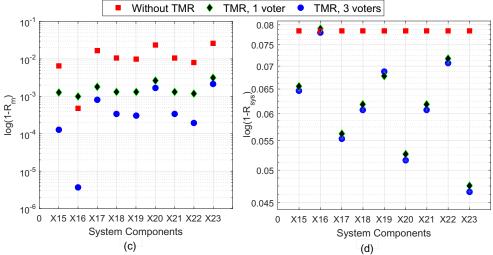

| 17 | Results of Investigating the Proposed Methodology's Scalability $$ . $$ . | 56 |

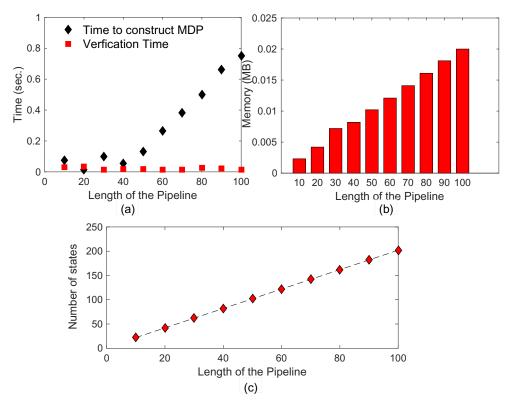

| 18 | TMR chain with uniform failure rates                                      | 57 |

| 19 | Variation in the system failure rate due to non-uniform distribution .    | 58 |

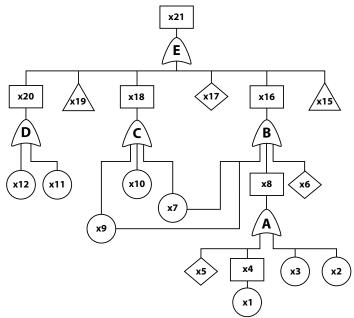

| 20 | Hermes Cubesat HSCOM Fault Tree                                           | 59 |

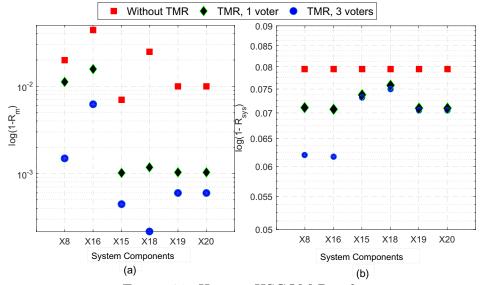

| 21 | Hermes HSCOM Results                                                      | 59 |

| 22 | Solar Array TMR Results                                                   | 60 |

| 23 | Time Progression of a Fault-Tolerant Micro-Electronic System Exposed      |    |

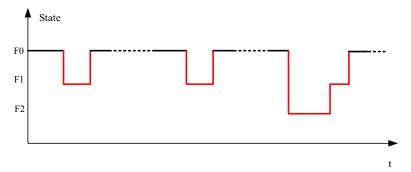

|    | to SEUs [9]                                                               | 66 |

| 24 | Proposed Probabilistic Model of SEU Propagation Through a Proces-         |    |

|    | sor Instruction Cycle                                                     | 67 |

| 25 | Instruction Cycle Example                                              |

|----|------------------------------------------------------------------------|

| 26 | FSM of the Self-Repair Routine [9]                                     |

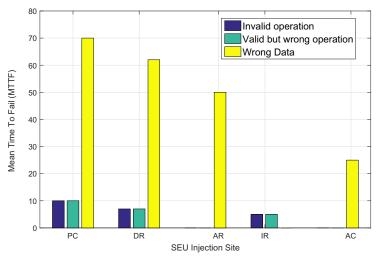

| 27 | Mean Time to Failure                                                   |

| 28 | Mean Time to Recover                                                   |

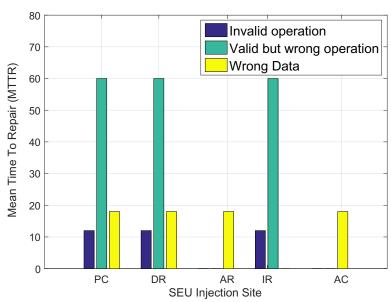

| 29 | Steady State Availability                                              |

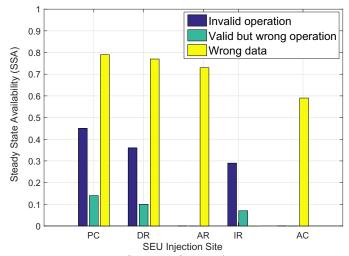

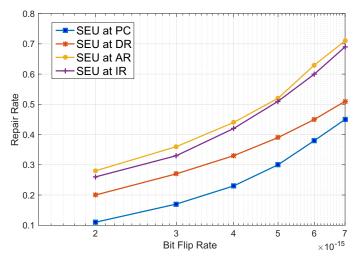

| 30 | Vulnerability of Different Registers                                   |

| 31 | DFT of the 7-stage integer pipeline of the SPARC V8                    |

| 32 | Sample of an OR Gate PTA                                               |

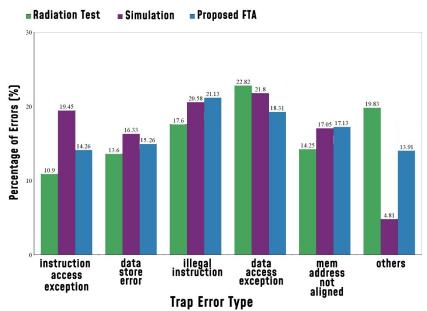

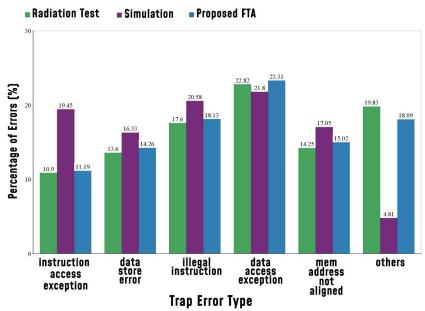

| 33 | Probability of Trap Exceptions in different approaches. Simulation and |

|    | radiation test results are reproduced from [29]                        |

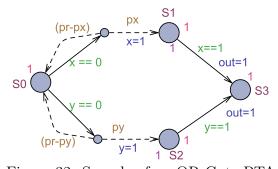

| 34 | Illustrative Example of the UPPAAL Formalism. Reproduced from [46]. 98 |

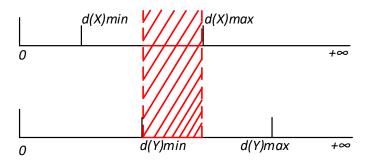

| 35 | Possible Time Window of a TAND output                                  |

| 36 | Example of a 2-Input Leaf TAND Gate                                    |

| 37 | Example of a Simple Fault tree                                         |

| 38 | Example of a 2-Input Variant TAND Gate                                 |

| 39 | Example of a 2-Input Leaf TOR Gate                                     |

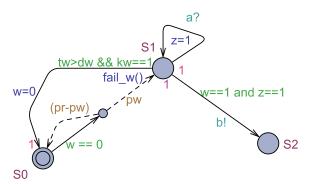

| 40 | Example of a TFDEP Gate                                                |

| 41 | Example of a 2-Input Leaf TPAND Gate                                   |

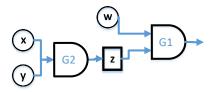

| 42 | Example of a 2-of-3 Leaf TComb Gate                                    |

| 43 | Main Steps of the Proposed Methodology                                 |

| 44 | Comparison of the Estimated Unreliability Over Time of TDFTs and       |

|    | DFTs                                                                   |

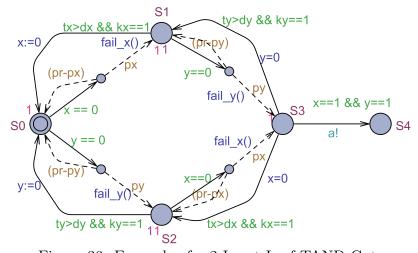

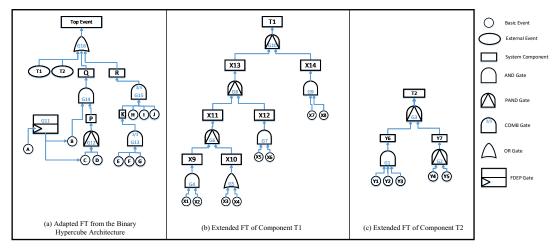

| 45 | Modular FT Analysis of the Binary Hypercube Architecture 111           |

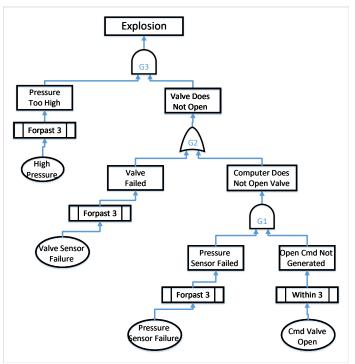

| 46 | Temporal Fault Tree of the Pressure Chamber Case-Study 116             |

| 47 | DFT of the 7-stage Integer Pipeline of the SPARC-V8 Architecture . 118 |

| 48 | Probability of Trap Exceptions in different approaches. Simulation and |

|    | radiation test results are reproduced from [29]                        |

| 49 | Main Steps of the Proposed Analysis of a Pacemaker                     |

| 50 | TAs of the Components of the DDD Pacemaker                             |

| 51 | Proposed Formal Analysis of Soft-Faults Propagation                    |

| 52 | Effects of SFs on the Pacemaker Components                             |

| 53 | Timing Diagram of SF at Aget During TPVAB                              |

| 54 | Timing Diagram of an SF at Aget During TPVARP                          |

| 55 | Timing Diagram of the Impact of SF During TURI                     | 148 |

|----|--------------------------------------------------------------------|-----|

| 56 | Timing Diagram of the Impact of SF During TVRP                     | 149 |

| 57 | Timing Diagram of SF-Induced Oversensing                           | 149 |

| 58 | Timing Diagram of SF-Induced Oversensing                           | 150 |

| 59 | SF-Induced Undersensing                                            | 151 |

| 60 | Output Failure due to Missed Ventricular Pacing                    | 152 |

| 61 | The main steps of the proposed methodology                         | 157 |

| 62 | Example of C++ to LLVM Conversion                                  | 158 |

| 63 | Proposed Probabilistic Model of SEU Propagation Through a the Pro- |     |

|    | cessor Pipeline in an ADD Instruction                              | 161 |

| 64 | Example of Variable Lifetime Estimation                            | 163 |

| 65 | Probabilistic Model of SEU Propagation Through a Sequence of In-   |     |

|    | structions Based on the Target Application                         | 163 |

| 66 | Criticality Evaluation of the LEON3 Pipeline Registers (CRC Bench- |     |

|    | mark). Injection and Chibani 2014 results reproduced from [40]     | 169 |

## List of Tables

| 1  | TMR configurations and Respective FTs                                      | 22  |

|----|----------------------------------------------------------------------------|-----|

| 2  | Elements of a Fault Tree                                                   | 31  |

| 3  | Fault Probability of Bottom Events                                         | 40  |

| 4  | Top Event Failure Probability(DTMC)                                        | 40  |

| 5  | Top Event Failure Probability(MDP)                                         | 40  |

| 6  | Modeled FT gates                                                           | 51  |

| 7  | TMR configurations and Respective FTs                                      | 53  |

| 8  | Operations                                                                 | 69  |

| 9  | MTTR and MTTF in Different Techniques                                      | 80  |

| 10 | AVR ATmega103 Analysis Comparison                                          | 80  |

| 11 | SPARC V8 Probability of Failure Over Time                                  | 90  |

| 12 | Estimated Availability of Component T1 After 100 Seconds. Failure          |     |

|    | rate of basic events is assumed to be $0.05$ . Temporal events are assumed |     |

|    | to last up to 3 seconds                                                    | 113 |

| 13 | Estimated Availability of Component T2 After 100 Seconds. Failure          |     |

|    | rate of basic events is assumed to be $0.05$ . Temporal events are assumed |     |

|    | to last up to 3 seconds                                                    | 113 |

| 14 | Estimated Availability of the Binary Hypercube System After 100 Sec-       |     |

|    | onds. Temporal events are assumed to last up to 3 seconds                  | 114 |

| 15 | Estimated Reliability of the Pressure Chamber System After 100 Sec-        |     |

|    | onds. (Fault=X in the table refers to the time duration of the fault,      |     |

|    | with X being units of time.)                                               | 115 |

| 16 | SPARC-V8 Probability of Failure Over Time                                  | 120 |

| 17 | Results of the verification of the functional properties of the pacemaker  | 136 |

| 18 | Results of the verification of the non-functional properties related to    |     |

|    | the impact of SFs on the pacemaker                                         | 142 |

| 19 | Application Based Analysis of Fault Propagation | 168 |

|----|-------------------------------------------------|-----|

| 20 | Average Fault Propagation and Fault Latency     | 168 |

| 21 | Analysis Time for Criticality Evaluation        | 169 |

## Chapter 1

### Introduction

Cyber-physical systems (CPS) are a new class of embedded Information and Communication Technologies (ICT) systems. These systems require tight integration of computing, communication, and control technologies to achieve performance, stability, reliability, efficiency and robustness in physical systems targeting many application domains. Embedded systems have been successfully employed in almost every aspect of our daily lives, ranging from medical devices, buildings, mobile devices, robots, transportation, and energy systems. Such applications impose requirements that are among the most challenging for CPSs being designed today. Furthermore, advancements in technology are likely to increase the complexity of these CPSs even more, with systems required to perform more functions while being smaller in size. Combined with tight time, cost, and design constraints, these factors contribute to making the development of CPSs a major technical challenge. In addition, many CPSs are critical in nature, and they must be highly dependable, even in unknown and hostile environments. This requires powerful methods for failure detection, diagnosis, and recovery to ensure correct system operation. For instance, the failure rate per chip has been reported to increase 100-fold from the 180nm to the 16nm CMOS technology node [111]. Exponential growth in the number of transistors per chip with time has brought tremendous progress in the performance of semiconductor devices; however, it may also increase the device's vulnerability to some types of radiation.

State-of-the-art verification techniques that investigate the unreliability of safety-critical CPSs are very costly, time consuming, and inefficient. In industry, the verification of CPSs is mainly conducted at high level through simulation based techniques,

or at low level through hardware testing. Simulation based techniques are less than optimal, since they rely on the generation of input vectors, which means that the full verification of a complex design is generally unattainable. Moreover, the shortcomings of these techniques are made evident in scenarios where exceptional or low probability events (e.g., failure caused due to non-functional sources) have to be evaluated. For example, despite all the testing and certification that medical devices are submitted to, there are several reports of death induced by pacemaker malfunctions. Reportedly, these malfunctions have originated from the unforeseen effects of external radiation originated in MRI machines, x-rays, and even cosmic ray exposure during a commercial flight [58, 111]. The main challenge in the analysis of CPSs comes from the fact that these systems are very complex, since they comprise several sub-systems and sub-components. The verification of such systems requires the analysis of the vulnerability of all the sub-components and sub-systems individually, as well as the analysis of the interactions between them. Safety-critical systems are often timecritical. Thus, the safety of these systems depends on their ability to correctly collect and process data with real-time requirements. Specification and verification of timing constraints further adds to the complexity of the system. Therefore, efficient ways to analyze these complex systems are of decisive importance. Furthermore, a new methodology which integrates different analysis techniques of this type of systems is required. This methodology must be able to accommodate all the sub-components of the system, and the synergies between them, at different levels of abstraction.

Due to the previously mentioned complexity and composition of cyber-physical systems, the efficient and effective design of distributed multi-scale systems is still an unsolved problem. The design process of these systems must encompass heterogeneous components, often uncertain in specification, their interconnections, and their relationship to the environment. The dynamic of all these elements is critical to the reliability of the system. Technology advances further increase the challenges to the design process, adding the possibility of placing significantly more functionality into products, but also increasing interconnectivity at the risk of unwanted system interactions. Currently in the industry, overdesign is the most used path for safe system design and deployment. However, due to the reasons explained above, this approach is rapidly becoming intractable and it will soon reach its saturation point. Furthermore, some critical CPSs are required to operate with very tight power, area,

and cost constraints. Medical implants, for example, are required to be very small and to have very low power consumption, in order to operate within the patient's body for extended periods of time. To obtain reliable CPSs without excessive overdesign, we need a rigorous methodology for system-level functional verification that is able to: 1) Provide guarantees of performance and reliability against the requirements, even is extremely harsh environments. 2) Produce scalable, fast and cheap verification environments for complex CPS. 3) Exploit analytical tools and techniques to determine design choices and ensure robust system performance. 4) Achieve these goals through the coordinated execution of a prescriptive, repeatable, and measurable process. These points are further elaborated below, in Section 1.3.

### 1.1 Motivation and Problem Formulation

The failure of a critical CPS can be due to different classes of uncertainties, such as manufacturing defects, aging, end of life failures, and transient faults. An example of the existing reliability analysis of CPSs is the analysis of the impact transient faults due to external radiation have on implantable devices. Radiation are of special interest in critical CPSs as they keep occurring even if these systems are otherwise fault-free and defect-free, in which case such systems could wrongly be expected to have a 0-failure rate. Due to the criticality of many CPSs, the most accepted way of evaluating their vulnerability to the effects of radiation is through a process called dynamic radiation testing [82]. This method consists in exposing the target system to a radiation flux and counting the number of errors observed. However, this method is very expensive and time-consuming, since any change in the application requires a new dynamic test. Alternative methods have emerged, with the goal of reducing the time and cost constraints associated with dynamic radiation ground testing. These techniques are mostly based on system vulnerability analysis through emulation and simulation [17]. However, current techniques are not able to scale to the complexity of these systems. Moreover, such analysis normally consumes large amounts of time and requires full details of the design structure and of the characteristics of the fault. In other words, with detailed circuit level techniques, normally required for detailed modeling, this type of analysis would be intractable at the chip level and is only tractable at the cell level (for hundreds of transistors at most) to get a certain level of accuracy. Moreover, the verification of CPSs requires accurate fault and system models, as well as the use of comprehensive methods of analyzing the impact of faults in each of the components. This is only possible with an analysis method that works at several levels of abstraction. However, it is unlikely that the existing single verification techniques will suffice at every level. A collection of techniques with suitable integration of the results is required.

There has been much interest in developing formal verification frameworks to verify the correctness of the implementation of CPSs, at different abstraction levels. These formal verification techniques are very efficient in providing guarantees about the model correctness, as well as locating corner-cases and hard-to-find bugs. For example, different formal verification frameworks were developed to verify the implementation of pacemaker's systems. In the work proposed by [66, 75, 76, 131], a model-based framework for the automatic verification of the functionality of cardiac pacemakers was developed. The authors developed a detailed model of a basic dual chamber pacemaker. This model is constructed based on the timed automata (TA) of each of the pacemaker sub-components. Moreover, in this work, the authors have developed a TA of the heart behavior. The functionality of the pacemaker model has been verified using statistical model checking. However, existing formal-based techniques are designed to detect implementation bugs in the CPS (i.e., identification of functional errors) [121, 122]. In other words, such techniques assume that the CPS always operates in an error free environment. Therefore, with these techniques, it is not possible to detect non-functional faults, such as radiation-induced soft-errors. These errors are often generated when a sensitive area of a CPS is hit by a strong enough flux of external ionizing radiation, such as X-rays and Gama-rays. These external radiation fluxes may change the output of a transistor for a short period of time, which, in turn, may the value stored in a state element. This event is known as a Single Event Upset (SEU).

### 1.1.1 Radiation Ground Testing

The traditional and most direct approach to evaluate the SEU vulnerability of a system (i.e., an application running in a processor) is through a process called *dynamic* radiation ground testing [26, 133]. This method consists in exposing the target system to a radiation flux and counting the number of errors observed. The outcome is

computed in the form of a parameter known as the dynamic cross section  $(\sigma)$ , which is defined as the ratio between the number of errors observed at the output of a design configured into the SRAM-based FPGA, divided by the fluence of hitting particles [116]. A problem with that metric is that any change in the application requires a new dynamic test, thus resulting in a very expensive and time-consuming method. Alternative methods for SEU estimation have emerged, with the goal of reducing the time and cost constraints associated with dynamic radiation ground testing. In [16, 117, 135], the authors introduce a method of injecting SEUs at random time intervals through emulation, by making use of an interrupt routine to alter values within the processor's internal registers and memory. Fault injection through emulation is also used in the direct memory access SEU emulation method [55], where a dedicated hardware component, controlled externally, selects the time instant and the bit to be altered in the memory. This approach is further explored in [56, 57], where the SEU injection is performed through probabilistic models of the system, with the goal of estimating the system's time to failure (TTF) and time to recover (TTR). However, this technique still requires emulation in order to obtain certain system rates which the model is built upon (i.e., coverage factor, error factor, and failure factor).

### 1.1.2 Radiation Testing through Simulation

Another branch of SEU estimation techniques focus on fault injection through simulation, which is usually done by injecting faults at logical or electrical levels [48, 64, 83, 85]. The advantage of these techniques is the high level of control over the fault injection scenarios, since the user has free access to the entirety of the system and the timing of the injections is very accurate. However, emulation and simulation based techniques have severe drawbacks. Disregarding the considerable time required to simulate or to emulate a scenario of thousands of injected faults [17], both approaches are limited in terms of accuracy. This problem arises due to the fact that these techniques are not exhaustive (only consider a small subset of the possible fault injection scenarios) [84].

#### 1.1.3 Radiation Testing through Formal Verification

Recently, the use of formal based techniques to analyze soft errors at logical and higher abstraction levels has been proposed, such as the work done in [15, 23, 101]. These techniques provide new insights into the vulnerability of digital designs to SEUs. This is mainly because they are exhaustive and not limited by the number of test vectors as in simulation based techniques. However, at logical abstraction level, these techniques suffer from the state explosion problem [65]. Therefore, it is expected for these techniques to be more efficient at higher abstraction levels, such as system-level.

The need to take the complete digital system design into consideration for quantitative safety analysis has led to the widespread acceptance of Fault Trees (FTs). FTs are top-down graphical representations of various combinations of lower level events that may cause the system to reach a top level failure (i.e., system failure) [138]. Fault Tree Analysis (FTA) can provide insightful information to designers regarding the reliability of their systems, such as how is their system most likely to fail and what are the most efficient ways to make it safer. However, the traditional way of conducting FTA is either through paper and pencil proof or through computer simulation techniques, which are inefficient and prone to inaccuracy. The most prominent use of FTA in the literature is by converting the system's FT into a Boolean function and simulating that function with different low level component failure rates [35, 51, 124]. However, these approaches are also costly in time and resources. This is mainly due to the fact that their modeling of FT is limited to the Boolean representation, which may exponentially increase the resource requirements to reach the desired results.

### 1.2 Thesis Objectives

Since the vast majority of techniques found in the literature rely heavily on low-level testing (i.e., after manufacturing) the main scientific objectives of this thesis are to provide practical frameworks to evaluate and improve CPS reliability at early stages of development and to reduce the complexity of the reliability analysis while improving the accuracy of the results. Due to technological limitations, however, the work presented in this thesis is limited to the analysis of the main processing units of CPSs. Namely, this thesis seeks to provide answers for the following questions:

- Q1: How to accurately model a CPS processing unit, at high-level of abstraction?

- Q2: How to abstract the SEU propagation behavior observed at transistor level at high-levels of abstraction?

- Q3: How to efficiently utilize formal verification methods to model and analyze SEU vulnerability at high-levels of abstraction?

- Q4: How to utilize formal verification methods to evaluate and to propose improvements to the system design?

- Q5: How to measure the vulnerability of complex designs, at high-level, without losing the accuracy provided from the low-level analyses?

- Q6: Is it possible to improve scalability while preserving accuracy?

### 1.3 Thesis Contributions

In this work, I propose and develop a solution to the aforementioned issues found in the literature. A multi-phased cross-layer methodology is proposed to compute an accurate early estimation of a design's vulnerability to errors. This methodology is also able to identify and isolate the most critical components of the design, and to pinpoint the most efficient ways to mitigate the design's weaknesses through the implementation of architectural mitigation, such as TMR. The methodology is also able to investigate the source of a component's vulnerability and to propose the implementation of redundancy inside of the critical component, if that option is deemed to be the most beneficial. This is achieved by investigating the dependability results obtained from the Fault Tree Abalysis (FTA) and the component-level analysis of a design. This work includes the construction of a library of models of FT gates and relationships, as well as a library of models of component-level elements (i.e., registers, ALU, logic gates, etc.). Much like classes in an object-oriented language, these libraries can be used to generate any FT diagram and any component-level description needed. The analysis of these elements is performed through Probabilistic Model Checking (PMC) and Stochastic Model Checking (SMC), both of which provide automatic investigation of the design at multiple levels of detail. To the best of our knowledge, the above capabilities are not shared by any other existing vulnerability estimation technique. Furthermore, those capabilities will allow us to provide a more comprehensive study of the system and its vulnerability to the designers, before the system is manufactured.

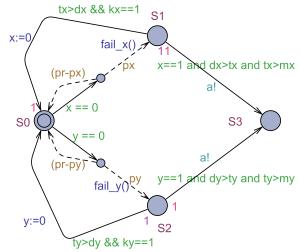

The analysis methodology proposed in this thesis follows cross-layer approach, with the purpose of improving the scalability and efficiency of the modeling as well as of the analysis of the reliability of CPSs. The methodology is composed by two core phases: the fault-tree analysis phase and the component-level analysis phase, as depicted in Figure 1.

Figure 1: Overview of the Proposed Framework

### 1.3.1 Fault-Tree Analysis Phase

At the highest level of abstraction, the design's vulnerability is evaluated through FTA. The objective of this phase is to conduct an analysis on the complete system design. This provides an estimation of the probabilistic failure rates of the system, the probabilistic failure rates of each individual component, the fault propagation rates between different components (i.e., how different components impact each other as well as how they impact the overall system vulnerability), and the most relevant

causes of failure to be considered. This phase include the following steps:

- First, a fault tree of the design is generated from the high-level system specifications. This can be done either manually or through special tools, such as the tool introduced in [99], which is able to synthesize the fault tree of a design from its SysML model representation [61]. At this stage, each component of the system is treated as a black box.

- Next, the probabilistic model of the fault tree is constructed from the fault tree diagram representation. This fault tree model is constructed in the language of the probabilistic model checker to be used (in this case, PRISM). The fault tree model is build from our existing libraries of FT gates and relationships.

- A set of properties is derived from the system specifications, denoting how the system is expected to perform.

- With the fault tree model and the properties ready, probabilistic model checking is performed in order to evaluate the design's vulnerability to faults, as well as the impact of each component to the system vulnerability.

- The impact of each component to the vulnerability of the system is recorded in a library called *Component Contribution Matrix* (CCM).

- If the system's estimated vulnerability is below the accepted threshold, the analysis stops. However, if the system's vulnerability is higher than the threshold, a new step is performed, in which the most critical components of the system are identified within the CCM.

- Next, the components classified as the most critical are isolated and a study is

performed on them with the goal of identifying the best TMR configuration to

help mitigating the component's vulnerability.

- The final step in this phase is to record the impact of the different TMR configurations on each critical component, and to update the fault tree model with the most efficient TMR configuration, followed by a new analysis with probabilistic model checking.

Many different modeling and analysis advancements have been incorporated in the fault-tree analysis phase of the proposed methodology. The problem tackled in this phase encapsulates questions Q1. Q2, Q4 and Q5, presented in Section 1.2. The contributions of this work to the state-of-the-art are the following:

1. Investigate the impact of different stochastic models on the analysis of a system: The modeling methodology is applied to a case study of a solar array mechanical system. Next, multiple experiments are conducted on the same system, first by modeling it using Discrete-Time Markov Chain (DTMC) to model known environment scenarios where the probabilistic distribution of the system's behavior is known, and then using Markov Decision Process (MDP) to model the non-deterministic behavior of the system when subjected to unknown environments. These analyses have led to the following publication:

C1: Ammar, M., Hoque, K.A., Ait Mohamed, O. Formal analysis of fault tree using probabilistic model checking: A solar array case study. In Annual IEEE Systems Conference (SysCon 2016).

2. Investigate system vulnerability to soft-faults and how to efficiently mitigate it: Redundant architectures, such as Triple Modular Redundancy (TMR), are broadly used as alternatives for fault tolerance, in order to improve the reliability of safety-critical systems. However, the type and placement of the redundant architecture may have a significant impact on the outcome. The experiments that I have conducted demonstrate that redundancy may have negative impacts on the system, in some cases. To avoid issues, an early-analysis is required to determine the type and location of the fault mitigation option. This analysis resulted in the following publication:

C2: Ammar, M., Bany Hamad, G., Ait Mohamed, O., Savaria, Y. Efficient probabilistic fault tree analysis of safety critical systems via probabilistic model checking. In Forum on Specification and Design Languages (FDL 2016).

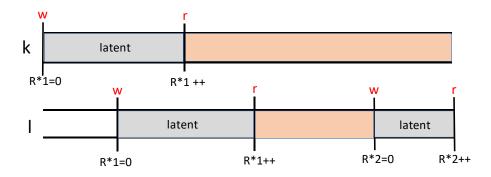

3. High-level modeling and vulnerability analysis of complex real systems over time: Fault-trees are an excellent tool to investigate fault propagation in the system, identifying the ways in which the system is most likely to fail. However, most FTA approaches are not suitable for safety-critical analysis, since current FT modeling techniques cannot capture sequences of actions. Moreover, the binary representation of FTs is not adequate for systems with complex state-spaces. Finally, FTA is unable to predict the state of the system over a period of time. To solve these shortcomings, I have proposed e new fault-tree paradigm entitled Temporal-Dynamic Fault Trees (TDFTs). I have proposed a new analysis method, based on stochastic model checking, and new FT gate models that evolve over time and that are sensitive to temporal events, such as SEUs. The proposed modeling and analysis advance the state-of-theart, allowing the power and efficiency of FTs to be used in predictive system evaluation, as well as in significantly more accurate vulnerability assessment to soft-errors. These advances have resulted in the following publications:

C3: Ammar, M., Bany Hamad, G., Ait Mohamed, O. and Savaria, Y., 2018, December. Reliability Analysis of the SPARC V8 Architecture via Fault Trees and UPPAL-SMC. In 2018 25th IEEE International Conference on Electronics, Circuits and Systems (ICECS) (pp. 437-440). J1: Ammar, M., Bany Hamad, G., Ait Mohamed, O., and Savaria, Y. Towards an Accurate Probabilistic Modeling and Statistical Analysis of Temporal Faults via Temporal Dynamic Fault-Trees (TDFTs). IEEE Access Volume 7, page(s): 29264 – 29276 DOI:10.1109/ACCESS.2019.2902796, 2019.

### 1.3.2 Component-Level Analysis Phase

In this phase, the analysis of vulnerability is focused on each individual component that forms the system design. Unlike the fault tree analysis phase, where the components were treated as black boxes, in this phase each component is further elaborated and analyzed based on its internal architecture. The goal of this phase is to identify the sources of the component's vulnerability and to study the most efficient ways to internally mitigate that vulnerability. This phase include the following steps:

- Obtention of the component's behavior description. For example, if the component to be analyzed is an Arithmetic Logic Unit (ALU), we must obtain information about it's architecture, what operations it performs, what is it connected to, etc.

- Next, a library of system operations is built. Much like classes in an object oriented language, this library contains models of the operations (subcomponents) that serve as the building blocks for the component to be analyzed, such as logic gates, adders, multipliers, etc.

- Based on the component's behavior description, operations from the library

of system operations are instantiated in order to construct the model of the

component at system-level.

- Once the model is ready, an exhaustive fault injection analysis is conducted in order to identify any weaknesses in the component.

- The component, subjected to fault injections, is verified against a set of properties derived from the system specifications. This verification process is done through probabilistic model checking with PRISM. With this analysis, the impact of each fault injection scenario is obtained.

- Next, with the results obtained through the probabilistic analysis, the limit of the component's availability is estimated.

- If the availability of the component does not meet the preestablished performance metrics, TMR mitigation is applied to the most critical subcomponents. In this case, the model is updated to reflect the changes, and an evaluation of the mitigation overhead is conducted. Then, the probabilistic analysis process is repeated.

- If the availability of the component meets the preestablished performance metrics partially (i.e., the component passes the test but some of its subcomponents do not), fault mitigation must be applied to the critical components and the model must be reevaluated, restarting the fault injection process.

- If all the availability metrics are met (component overall, and all the subcomponents), the phase ends and the results are reported.

• Finally, an additional step takes place, in which the mitigation proposed by each of the phases is compared and the most efficient solution is chosen.

The problems addressed by this phase of the methodology are encapsulated in questions Q1. Q2, Q3, Q5 and Q6, presented in Section 1.2. The advancements achieved by the proposed techniques are the following:

- 1. Investigate the impact of soft-errors at system-level using PMC: The proposed system-level approach consists in modeling the system to be tested with all its components and their expected logical behaviors. Then, the fault-injection points are identified and the fault propagation paths are obtained by counter-example generation with PMC. Subsequently, the analysis performed consists in the probabilistic evaluation of several vulnerability metrics, such as Mean Time to Failure and Mean Time To Recover. These metrics are evaluated for each individual type of fault in the system. Furthermore, the analysis computes of the contribution of each component of the system to a failure. This idea generated the following publications:

- C4: Ammar, M., Bany Hamad, G., Ait Mohamed, O., Savaria, Y., Velazco, R. Comprehensive vulnerability analysis of systems exposed to SEUs via probabilistic model checking. In IEEE European Conference on Radiation and Its Effects on Components and Systems (RADECS 2016).

- J2: Ammar, M., Bany Hamad, G., Ait Mohamed, O., Savaria, Y. System-Level Analysis of the Vulnerability of Processors Exposed to Single-Event Upsets via Probabilistic Model Checking. IEEE Transactions on Nuclear Science. 2017 Sep;64(9):2523-30.

- B1: Ammar, M., Bany Hamad, G., Ait Mohamed, O., Savaria, Y. (2018). System-Level Modeling and Analysis of the Vulnerability of a Processor to Single Event Upsets (SEUs). Velazco R, McMorrow D, Estela J. Radiation Effects on Integrated Circuits and Systems for Space Applications.: (pp. 13-38), Springer, 2019. DOI: 978-3-030-04660-6-2.

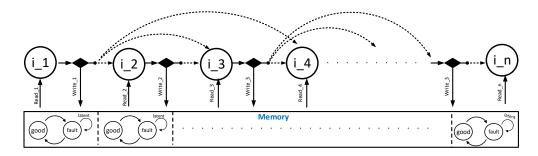

- 2. Application-based analysis of the impact of soft-errors on a CPS using PMC: To provide a better estimation of CPS vulnerability, not only the

hardware but also the software (application) must be considered in the analysis. Based on my component-level modeling approach for fault injection and generation of fault propagation paths, I have proposed a new analysis technique to perform PMC on an application execution trace. For each instruction, the propagation of SEUs is modeled as a Continuous-Time Markov Chain (CTMC), based on the hardware's microarchitecture. From these models, a full estimation of the fault propagation probabilities and latency through each instruction is computed. Furthermore, this model allows the analysis of fault propagation probabilities through the entire program execution. This analysis resulted in the following publications:

C5: Bany Hamad, G., Ammar, M., Ait Mohamed, O., and Savaria, Y. System-Level Characterization, Modeling, and Probabilistic Formal Analysis of LEON3 Vulnerability to Transient Faults. In IEEE European Conference on Radiation and Its Effects on Components and Systems (RADECS 2018).

J3: Bany Hamad, G., Ammar, M., Ait Mohamed, O., and Savaria, Y. New Insights Into Soft-Faults Induced Cardiac Pacemakers Malfunctions Analyzed at System-Level Via Model Checking. IEEE Access. PP. 1-1. 10.1109/AC-CESS.2018.2876318, 2018.

### 1.4 Thesis Organization

The remainder of this thesis is organized as follows:

Chapter 2 briefly discusses the most relevant SEU vulnerability analysis techniques in the literature.

In Chapter 3, the formal verification methods and tools utilized in this thesis to model and analyze the propagation of SEU at high-level abstraction are introduced.

Chapter 4 explains the basics of FT modeling and analysis with PMC. The introduced PMC-based methodology for FTA modeling is easily expandable with state-efficient models that are modular and constructed by parallel composition. The modeling methodology is applied to a case study of a solar array mechanical system, first using

Discrete-Time Markov Chain (DTMC) to model known environment scenarios where the probabilistic distribution of the system's behavior is known, then using Markov Decision Process (MDP) to model the non-deterministic behavior of the system when subjected to unknown environments. This work focuses on evaluating and characterizing fault propagation in FTs.

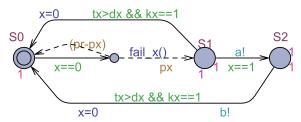

Chapter 5 first introduces a technique, based on FTA and PMC, to evaluate fault mitigation through triple modular redundancy. This approach consists of modeling the behavior of each FT gate as a probabilistic automaton (PA). Thereafter, a Markov Decision Process (MDP) model of the system's FT is obtained by the parallel composition of all the PAs that compose the FT. In the analysis step, a Component Contribution Investigation (CCI) is performed. The CCI consists in the evaluation of the contribution of the failure of each subcomponent to the system's failure. Based on the obtained data, the impact of different types of TMR is evaluated, determining the best location and TMR configuration for the system under analysis.

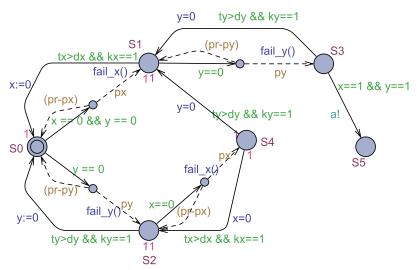

Chapter 6 presents a new system-level approach to compute an accurate estimate of a processor's vulnerability to SEU propagation. The propagation of SEUs is modeled as a Continuous-Time Markov Chain (CTMC). Furthermore, probabilistic model checking is utilized to exhaustively estimate the impact of SEUs on the system's behavior. The proposed CTMC model is analyzed for different SEU injection scenarios and different bit-flip rates. Such analysis is capable of producing an accurate estimation of different reliability metrics, such as Mean Time to Failure (MTTF), Mean Time to Recover (MTTR), and the probability of failure for each SEU injection scenario in the system's subcomponents. Finally, the chapter shows how the proposed probabilistic system-level analysis can also investigate the optimal self-repair rate required in the system to obtain the desired level of availability.

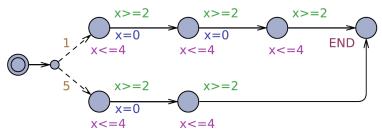

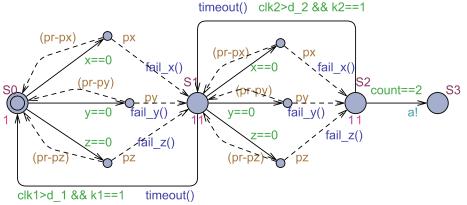

Chapter 7 introduces a new DFT approach to compute an accurate estimation of a system's vulnerability to soft-faults in complex real-world systems, using a new modeling of FT gates that is based on the Priced-Timed Automata theory. The chapter discusses the modeling of FTs of complex systems and it is centered around a case-study of the 32-bit SPARC V8 integer pipeline. The analysis is fully automatic,

conducted through stochastic model checking, with UPPAAL-SMC. The analysis presented consists in the estimation of the probability of each type of Trap Exception (TE) to occur in the targeted architecture, as well as the impact of individual registers to the overall reliability of the processor, and the probability of failures over time. Chapter 8 proposes a new fault tree modeling paradigm, to capture the impact of temporal events in systems, called *Temporal Dynamic Fault Trees (TDFTs)*. The proposed TDFTs are utilized to model fault propagation in complex systems while conserving the characteristics and dependencies between different temporal events, soft-faults, and permanent faults. This chapter also introduces a new analysis approach utilizing stochastic model checking with UPPAAL-SMC, which, combined with efficient modeling, is able to circumvent the state-explosion problem that is inherent to other model-checking approaches. The analysis proposed in this chapter is able to evaluate the impact of temporal faults in systems, as well as to estimate the reliability and availability of the system over extended periods of time.

Chapter 9 provides a general discussion about the present work, which has been detailed in Chapters 4 through 8, and finally Chapter 10 summarizes this thesis and proposes some directions for future work.

# Chapter 2

### Literature Review

The modeling and analysis of SEU relevant faults and their mitigation for dependability analysis is an active research area. The most common approach to evaluate the SEU vulnerability of a system is through a process called *dynamic radiation ground testing* [26, 134]. This method consists in exposing the target system to a radiation flux and counting the number of errors observed. The outcome is computed in the form of a parameter known as the *dynamic cross-section* ( $\sigma$ ), which is defined as the ratio between the number of errors observed at the output of a Design Under Test (DUT), divided by the fluence of hitting particles [116]. A problem with that metric is that any change in the application requires a new dynamic test, thus resulting in an expensive and time-consuming method.

Alternative methods for SEU estimation have emerged, with the goal of reducing the time and cost constraints associated with dynamic radiation ground testing. In [117, 135], the authors introduce a method of injecting SEUs at random time intervals through emulation, by making use of an interrupt routine to alter values within the processor's internal registers and memory. Fault injection through emulation is also used in the direct memory access SEU emulation method [55], where a dedicated hardware component, controlled externally, selects the time instant and the bit to be altered in the memory. This approach is further explored in [56, 57], where the SEU injection is performed through probabilistic models of the system, with the goal of estimating the system's time to failure (TTF) and time to recover (TTR). However, this technique still requires emulation in order to obtain certain system rates which the model is built upon (i.e., coverage factor, error factor, and failure factor). Another

branch of SEU estimation techniques focus on fault injection through simulation, which is usually done by injecting faults at logical or electrical levels [64, 83, 85]. The advantage of these techniques is the high level of control over the fault injection scenarios, since the user has free access to the entirety of the system and the timing of the injections is very accurate. However, emulation and simulation based techniques have severe drawbacks. Disregarding the considerable time required to simulate or to emulate a scenario of thousands of injected faults [17], both approaches are limited in terms of accuracy. This problem arises due to the fact that these techniques are not exhaustive, but rather reliant on input vectors [84]. These approaches are also reliant on detailed models of the DUT, which are not always available.

Recently, the use of formal based techniques to analyze soft errors at logical and higher abstraction levels has been proposed, such as the work done in [23]. These techniques provide new insights into the vulnerability of digital designs to SEUs. This is mainly because they are exhaustive and not limited by the number of test vectors as in simulation based techniques. In formal techniques, the user starts out by stating what output behavior is desirable and then lets the formal checker prove or disprove it. In other words, given a property, formal verification exhaustively searches all possible input and state conditions for failures. However, at logical abstraction level, these techniques suffer from state explosion (i.e., exponential growth in the number of states of the model) [65]. Therefore, it is expected for these techniques to be more efficient at higher abstraction levels, such as system-level.

In recent years, a number of works related to fault tree analysis of SEUs has emerged. In [14] a tool for fault tree analysis is presented, called DFTCalc, which is capable of modeling fault trees via compact representations. That work uses the stochastic technique to perform the analysis of dependability properties. The advantage of DFTCalc is a more expressive syntax for FTD, but it cannot check the correctness and completeness of fault trees. Moreover, an important difference is that their work does not include the possibility of fault masking, whereas in our work this important phenomenon is taken into account. The work presented in [6] gravitates towards theorem proving, using HOL4 and higher-order logics to analyse safety-critical systems through FTA by formalizing the gates of a fault tree and conducting FTA-based failure analysis. However, a model checking approach has several advantages over theorem proving, such as being systematically exhaustive, fully automated, and

more time efficient. However, FTA analysis of SEUs is very limited in the literature, mostly limited to post-error analyses.

## Chapter 3

# **Background Information**

#### 3.1 Fault Tree Analysis

The fault tree analysis method was developed in 1962 by Bell Telephone Laboratories and it is a widely used method for risk assessment, mainly in the area of avionics, nuclear and chemical industries [138]. FTA follows a deductive approach, which means that it starts from an undesirable general event in order to find the origins of said event. In the context of FTA, the general event is known as the *top event*, from which the fault tree branches out vertically. The top event is defined as the failing point of a system in operating conditions, whether those conditions are considered normal or abnormal. A single fault tree can be used to analyse one single top event, which can then be fed into another fault tree as a bottom event. Bottom events are the ones at the very bottom of the fault tree, independent from any other events, and, assuming the FTA is performed following a quantitative evaluation, these events receive fault probabilities that will dynamically spread through the rest of the tree during the analysis. The elements of a Fault Tree and their graphical representations are summarized in Table 2.

Other elements compose the fault tree, such as conditioning events, which are specific restrictions applied to a logic gate within the fault tree, like a mode of operation or a sequence of other events that serve as a prerequisite to its activation. These events can prevent or enforce the activation of a node or a gate, according to the circumstances. An external event is an event expected to occur and it is not considered as a fault; as such it may or may not affect the FTA. Lastly, an undeveloped event is an event

Table 1: TMR configurations and Respective FTs

| Figure | Event             | Type    | Description                                                                                  |

|--------|-------------------|---------|----------------------------------------------------------------------------------------------|

|        | Component         | na      | System component                                                                             |

|        | Bottom Event      | na      | Basic event that may lead to a failure                                                       |

|        | AND Gate          | Static  | The output is true if all inputs are true                                                    |

|        | OR Gate           | Static  | The output is true if at least one input is true                                             |

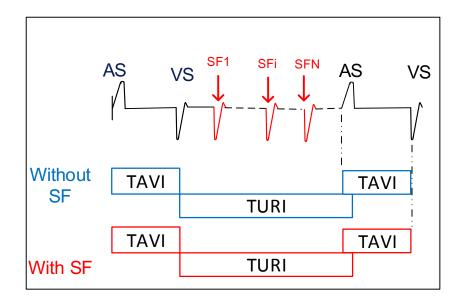

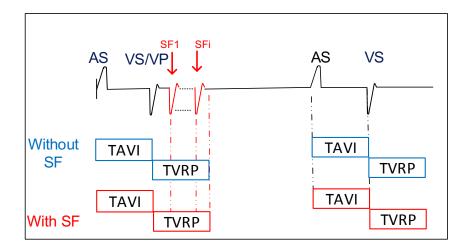

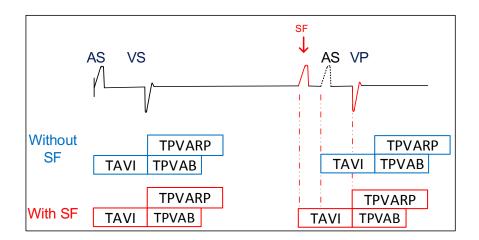

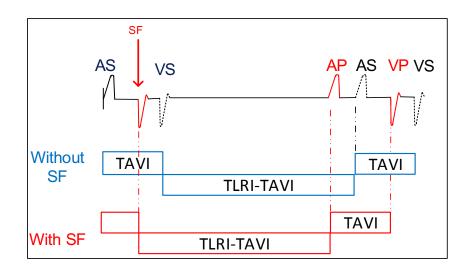

| n      | Combination Gate  | Dynamic | The output is true if $n$ inputs are true                                                    |